## Abstracting Hardware Architectures for Agile Design of High-performance Applications on FPGA

Jean Bruant

## ► To cite this version:

Jean Bruant. Abstracting Hardware Architectures for Agile Design of High-performance Applications on FPGA. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALT096. tel-04019979

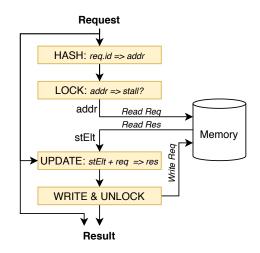

## HAL Id: tel-04019979 https://theses.hal.science/tel-04019979

Submitted on 8 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École Doctorale : Électronique, Électrotechnique, Automatique et Traitement du Signal (EEATS) Spécialité : NANO ÉLECTRONIQUE ET NANO TECHNOLOGIES Unitée de recherche : Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architectures des systèmes intégrés (TIMA)

## Abstracting Hardware Architectures for Agile Design of High-performance Applications on FPGA

Abstractions d'architectures matérielles pour une conception *Agile* d'applications performantes sur FPGA

Présentée par :

## Jean BRUANT

## Encadrement de Thèse :

| Olivier MULLER                                                      | Directeur de thèse    |

|---------------------------------------------------------------------|-----------------------|

| Maître de conférences, Grenoble INP, Université Grenoble Alpes      |                       |

| Frédéric Pétrot                                                     | Co-encadrant de thèse |

| Professeur des Universités, Grenoble INP, Université Grenoble Alpes |                       |

| Pierre-Henri Horrein                                                | Co-encadrant de thèse |

| Ingénieur Docteur, OVHcloud                                         |                       |

### Thèse soutenue publiquement le 8 décembre 2022, devant le jury composé de :

| Florence MARANINCHI<br>Professeur des Universités, Grenoble INP, Université Grenoble Alpes                    | Présidente            |

|---------------------------------------------------------------------------------------------------------------|-----------------------|

| <b>Matthieu ARZEL</b><br>Professeur des Universités, Lab-STICC, IMT Atlantique Bretagne -<br>Pays de la Loire | Rapporteur            |

| <b>Steven DERRIEN</b><br>Professeur des Universités, ISTIC, Université Rennes 1                               | Rapporteur            |

| Roselyne CHOTIN<br>Maître de conférences, LIP6, Sorbonne Université                                           | Examinatrice          |

| <b>Megan WACHS</b><br>Ph.D., VP of Engineering, Sifive                                                        | Examinatrice          |

| <b>Olivier Muller</b><br>Maître de conférences Grenoble INP, Université Grenoble Alpes                        | Directeur de thèse    |

| <b>Frédéric Pétrot</b><br>Professeur des Universités, Grenoble INP, Université Grenoble Alpes                 | Co-encadrant de thèse |

| Pierre-Henri Horrein<br>Ingénieur Docteur, OVHcloud                                                           | Co-encadrant de thèse |

*To our 24 sq.m, at least as dense as this manuscript*

# Abstract

**I** N a context of ever-growing worldwide communication traffic and fast deployment of IoT devices, network attacks have become a daily challenge with record-breaking throughput levels. Compared to software solutions based on general purpose CPUs, FPGA-based mitigation appliances appear as an energy-efficient alternative which combines configurability with guaranteed high-throughput and low-latency. However, implementation of such dedicated hardware accelerators based on the register-transfer level (RTL) abstraction is a much slower and tedious process than functionally equivalent software developments. The latter have indeed benefited from the introduction of countless high-level paradigms over the past decades, whereas traditional hardware description languages (HDLs) have consistently remained rigid and verbose. As a result, the agility gap between hardware and software developments is expanding at a steady pace, leaving hardware design experts frustrated by the lack of re-usability of their carefully crafted architectures.

This thesis tackles this generic hardware development issue within the context of highperformance networking appliance design at OVHcloud. Mimicking the successful trajectory of software evolution, it aims at leveraging a stack of abstraction levels to instill flexibility within hardware descriptions. As a key enabler, Hardware Construction Languages (HCLs) apply some existing software abstractions to hardware design, which permits descriptions of circuit generators with high-level software paradigms, such as object-oriented and functional programming. This thesis first exhibits the relevance of such software inherited paradigms to develop highly re-usable network functions, inspecting both implementation and design perspectives. Based on this powerful base layer, we introduce an additional hardwareoriented abstraction focusing on high-performance pipelined applications. Finally, the integration ability of these novel design methodologies within existing HDL hierarchies is reviewed in detail, yielding two final contributions aiming at ensuring a smooth cohabitation of both methodologies. The first one provides a direct path from existing HDL sources to their functionally equivalent HCL counterparts, thanks to an automated translation tool. This word-for-word translation is intended as the first step of an iterative manual upgrade to truly benefit from high-level abstractions of HCLs. The second one focuses on the smooth integration of HCL-generated hierarchies back into a top-level HDL hierarchy, which is a key acceptance factor for these new methodologies in long-running projects.

# Résumé<sup>1</sup>

D ANS un contexte de forte augmentation des communications numériques à travers le monde et de déploiement rapide de l'internet des objets (IoT), les attaques sur les réseaux de données sont devenues un défi quotidien avec des niveaux de trafic record. Par rapport aux solutions logicielles basées sur des processeurs généralistes, les dispositifs de mitigation construits à partir de FPGA apparaissent comme une alternative économe en énergie qui combine la configurabilité avec à la fois la garantie d'un haut débit et d'une faible latence. Cependant, la mise en œuvre de ces accélérateurs matériels dédiés, basée sur l'abstraction des circuits numériques au niveau registre (RTL), est un processus beaucoup plus lent et fastidieux que les développements logiciels fonctionnellement équivalents. Ces derniers ont en effet bénéficié de l'introduction de nombreux paradigmes de haut niveau au cours des dernières décennies, alors que les langages de description du matériel (HDL) traditionnels sont restés rigides et verbeux. En conséquence, l'écart d'agilité entre les développements matériels et logiciels se creuse à un rythme soutenu, laissant les experts en conception matérielle frustrés par le manque de réutilisabilité de leurs architectures si soigneusement élaborées.

Cette thèse aborde ce problème générique au développement matériel dans le contexte de la conception d'équipements réseau haute-performance chez OVHcloud. En imitant la trajectoire réussie de l'évolution des langages logiciels, elle vise à tirer parti d'un empilement de niveaux d'abstraction pour insuffler de la flexibilité au sein des descriptions matérielles. En particulier, les langages de construction matérielle (HCL) appliquent déjà certaines abstractions logicielles à la conception matérielle, ce qui permet de décrire des générateurs de circuits avec des paradigmes logiciels de haut niveau, tels que la programmation orientée objet et fonctionnelle. Cette thèse montre d'abord la pertinence de l'utilisation de tels paradigmes hérités du monde logiciel pour développer des fonctionnalités réseau hautement réutilisables, en s'intéressant à la fois aux perspectives de mise en œuvre et de conception. Sur cette base, nous présentons une abstraction supplémentaire, spécifique aux développements matériels, qui se concentre sur les applications pipelinées à haute-performance. Enfin, la capacité d'intégration de ces nouvelles méthodologies de conception dans les hiérarchies HDL existantes est examinée en détail, ce qui donne lieu à deux contributions finales visant à assurer une cohabitation harmonieuse entre ces deux méthodologies de développement. Grâce à un outil de traduction automatique, la première fournit un chemin direct depuis des sources HDL existantes vers une version HCL fonctionnellement équivalente. Cette traduction mot à mot est conçue comme la première étape d'une mise à niveau manuelle et itérative pour réellement bénéficier des abstractions de haut niveau fournies par les HCL. La seconde se concentre sur l'intégration sans accrocs des hiérarchies générées par les HCL dans une hiérarchie HDL, ce qui constitue un facteur d'acceptation essentiel de ces nouvelles méthodologies dans les projets au long cours.

<sup>&</sup>lt;sup>1</sup>Traduction basée sur un premier jet fourni par le traducteur DeepL à partir du résumé en langue originale. https://www.deepl.com

# Contents

| 1 Introduction |                                                                      | 1     |  |  |

|----------------|----------------------------------------------------------------------|-------|--|--|

| 2              | Problem Statement                                                    |       |  |  |

|                | 2.1 Introduction                                                     | . 6   |  |  |

|                | 2.2 Network Application Design                                       | . 8   |  |  |

|                | 2.3 Towards Agile and Efficient Hardware Design                      |       |  |  |

|                | 2.4 Conclusion                                                       |       |  |  |

| 3              | State of the Art                                                     | 21    |  |  |

|                | 3.1 Raising the Abstraction Level                                    | . 22  |  |  |

|                | 3.2 High-level Hardware Design Paradigms                             |       |  |  |

|                | 3.3 Implementing Abstractions with Hardware Construction Languages   |       |  |  |

|                | 3.4 Conclusion                                                       |       |  |  |

| 4              | Agile Hardware Design                                                | 43    |  |  |

|                | 4.1 Hardware Construction Languages Usages and Applications          | . 44  |  |  |

|                | 4.2 Bringing Agility to Networking Hardware Development              | . 46  |  |  |

|                | 4.3 Towards In-depth Transformation of Circuit Design                | . 53  |  |  |

|                | 4.4 Conclusion                                                       | . 65  |  |  |

| 5              | Pipeline Design Methodology                                          | 67    |  |  |

|                | 5.1 Introduction                                                     | . 68  |  |  |

|                | 5.2 Towards Latency-aware & Protocol-Polymorphic Pipelines           | . 68  |  |  |

|                | 5.3 Model Construction                                               |       |  |  |

|                | 5.4 Model Resolution: Signal Synchronization                         |       |  |  |

|                | 5.5 Results                                                          |       |  |  |

|                | 5.6 Conclusion                                                       | . 87  |  |  |

| 6              | Integration of Hardware Construction Languages                       | 89    |  |  |

|                | 6.1 Problem Statement                                                | . 90  |  |  |

|                | 6.2 (System)Verilog Upstream Integration by Translation              |       |  |  |

|                | 6.3 HCL-as-IP: Downstream Integration of HCL-Generated Architectures | . 101 |  |  |

|                | 6.4 Conclusion                                                       | . 107 |  |  |

| 7              | Experimentation                                                      | 109   |  |  |

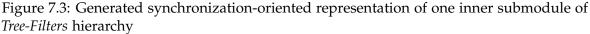

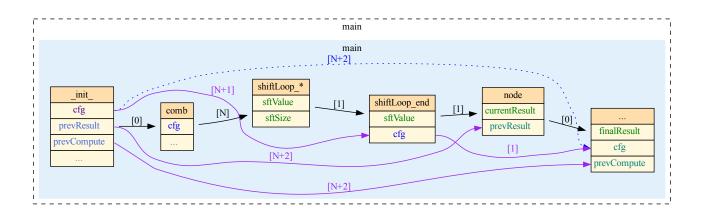

|                | 7.1 Tree Filters Design and SystemVerilog Implementation             | . 110 |  |  |

|                | 7.2 Chisel Translation with <i>sv2chisel</i>                         | . 113 |  |  |

|                | 7.3 Integrating Pipeline Framework                                   | . 122 |  |  |

|                | 7.4 Conclusion                                                       | . 131 |  |  |

| 8              | Conclusion                                                           | 133   |  |  |

| Appendices                                                                                 | 137 |

|--------------------------------------------------------------------------------------------|-----|

| Appendix A Abstract Data Type Schemes         A.1 Complete Protected Hash-Table ADT Scheme |     |

| A.2 ADT Usage Example                                                                      | 142 |

| Appendix B Port Wrapper                                                                    | 145 |

| Appendix C Tree Filters Architecture Details                                               | 147 |

| C.1 Top Level Architecture                                                                 | 147 |

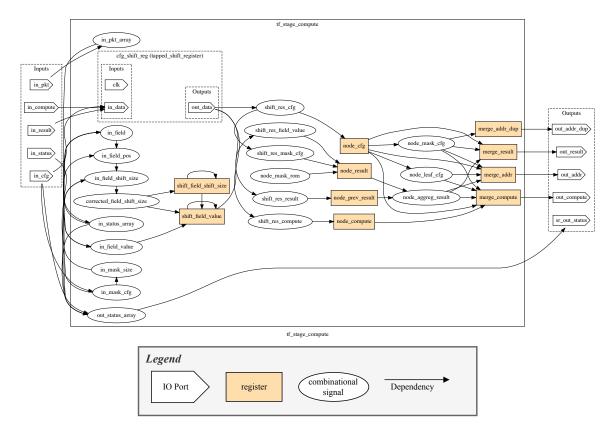

| C.2 Generated Synchronization-oriented Representations                                     | 147 |

| C.3 Pipeline-oriented Representation                                                       | 147 |

| Appendix D Chisel Insights                                                                 | 155 |

| D.1 UInt vs Vec[Bool] and Flattening                                                       | 155 |

| D.2 Antipatterns Translation                                                               | 157 |

| Backmatter                                                                                 |     |

| Publications                                                                               | 161 |

| Bibliography                                                                               | 163 |

# Acknowledgments

I would first like to thank the members of my examining committee for the time they invested in my work: Florence Maraninchi, who accepted to chair the committee, Steven Derrien and Matthieu Arzel, who both accepted to report on the manuscript after being also part of three monitoring committees, Roselyne Chotin and Megan Wachs. The numerous questions they had prepared for the defense led to passionate discussions. A special mention to Megan Wachs, who accepted to be part of the committee of an unknown French PhD candidate on the other side of the world, despite a non-negligible logistical constraint: a 9-hours time difference.

Speaking of a considerable time difference, many thanks to my brother Hugues and his life companion Lilly who assiduously attended the defense, at a very early time in the morning for them as well.

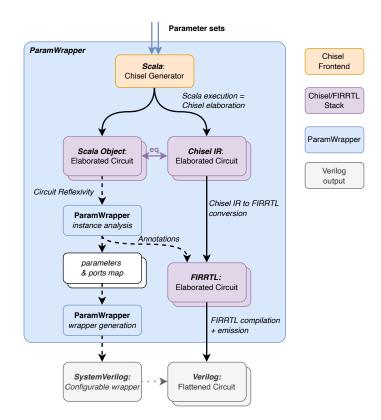

I would then like to thank the members of the Chisel/FIRRTL open-source community, who have warmly welcomed me, despite my small contributions and sparse presence at the dev meetings. From the very beginning of this PhD journey, we knew we needed to pick a mature solution and a dynamic ecosystem to build our academic contributions while retaining viable industrial perspectives. A solution that would not let us down after a few years, and Chisel did not. Special thanks to Jack Koenig and Schuyler Eldridge who introduced me to the power of Chisel/FIRRTL annotations and custom transforms in the Scala FIRRTL compiler. I guess I will again need your help now that Chisel is moving to Circt and the MLIR-based FIRRTL compiler.

My research journey toward this PhD started well before my time at OVHcloud, with my one-year internship at WideNorth in Oslo, Norway. I am especially grateful to Helge, Hallvard and Nicolas who offered my fellow intern Benoît and I the opportunity of a one-year research project with full autonomy and absolute trust. Thank you, Helge for inviting me to give my very first scientific talk at the FPGA forum in Trondheim.

Finally, and before continuing in French, I must acknowledge the tremendous proofreading work provided by my beloved wife Clothilde. Her meticulous and rigorous reading aloud definitively improved the English writing quality of this manuscript.

# Remerciements

La thèse est une aventure, certes personnelle, mais non sans jalons, sans repères, sans un balisage parfois patiemment anticipé par ceux qui en ont été les instigateurs. Tout a commencé dans le bâtiment K2 de Telecom Bretagne au printemps 2015, par la découverte de l'électronique numérique et des FPGA, encadrée par notamment Matthieu Arzel et Pierre-Henri Horrein. Alors jeune étudiant, profitant du bon air marin breton et bien loin de m'imaginer docteur, je m'extasiais devant les résultats - quelques points rouges sur un fond noir – de l'algorithme de détection de contours Sobel que nous venions fièrement d'implémenter avec Benoît. Aux côtés de ce binôme indéfectible et passionné, nos chers encadrants nous vantaient, en toute honnêteté, les mérites de la recherche, tant académique qu'industrielle. Les perspectives d'une thèse apparaissaient alors loin, vraiment loin, au bout d'une formation d'ingénieur qui n'en était alors qu'à son commencement. Bien enterrée, la graine était semée. Une graine que Matthieu et Pierre-Henri ne manqueraient pas de soigner et d'éveiller à la liberté offerte par la recherche. C'est ainsi que, toujours aux côtés de mon fidèle compère Benoît, Matthieu nous offrit l'opportunité d'une année de stage en Norvège, pendant laquelle nous avons pu goûter au grand frisson d'une totale autonomie de recherche. Dès mon retour à Brest, Pierre-Henri me proposa un contrat de professionnalisation chez OVH, un cadre définitivement plus industriel, mais toujours guidé par l'ambition d'innover. C'est dans ce contexte que la thèse est apparue comme une suite logique à ce parcours de formation. Conçue sur mesure dans une confiance presque aveugle avec Tristan, Olivier, Frédéric et Pierre-Henri, l'aventure débuta finalement à l'automne 2018 : quatre saisons plus tard, la dormance était levée. Je manque de mots pour remercier les protagonistes de ce chemin vers la recherche, qui ne manquèrent d'ailleurs pas de rester des acteurs présents pendant la thèse.

Merci Matthieu pour le partage de ta passion, ton suivi régulier et toutes les opportunités que tu m'as offertes jusqu'au surlendemain de la soutenance.

Merci Benoît pour ton amitié sans faille, allant jusqu'à sacrifier les premières heures de tes vacances pour *voler* au secours de ma détresse en LATEX. Merci pour ta rigueur, ton goût donné pour LATEX et les présentations bien faites. Sans cette année à tes côtés en Norvège, je n'aurais sans doute jamais sauté le pas de la thèse.

Merci Pierre-Henri pour ton accompagnement et ton écoute attentive chaque jour depuis les prémices de la thèse, jusqu'à la soutenance et encore aujourd'hui pour poursuivre cette aventure qu'est la recherche, quelles que soient les conditions adverses sur ce noble chemin. Merci pour ces discussions passionnantes qui attisent ma curiosité et mon envie d'aller toujours plus loin. Merci pour ce tout, dont je ne me risquerais pas ici à dresser une liste exhaustive.

Merci à l'équipe FPGA qui m'a accueilli chez OVH, Tristan, Thibault, Clément et Pierre-Henri, puis Paul-Louis. Merci d'avoir été réceptifs à ma démarche de recherche en marge de l'équipe, avant, pendant et encore aujourd'hui après ces quatre années de thèse. Merci également à mes collègues OVHcloud de P19, qui m'ont soutenu jour après jour, en particulier pendant les longs mois de rédaction, entre cafés et plantations. La thèse est une aventure, certes personnelle, mais surtout faite de rencontres. Merci à toute l'équipe SLS de TIMA qui malgré ma présence plus que sporadique à Grenoble, m'a réservé un accueil chaleureux lors de mes séjours trop peu nombreux. Merci Laurence, Julie, Arthur, Frédéric R., Liliana, Adrien, Maxime, Nathan, Marie, Benjamin et tous les compères de passage pour ces discussions passionnantes autour d'un thé, d'un café ou d'une viennoiserie.

Merci Bruno d'avoir été un fidèle co-bureau malgré la distance, et de m'avoir montré la voie jusqu'à la soutenance – *The best thesis defense is a good thesis offense*. Merci pour ton soutien tout au long de ces années avec ces discussions rafraichissantes au milieu de nos péripéties personnelles.

Merci Frédéric P. pour tes références éclairées dès l'écriture du sujet de thèse, quand *Chisel* et *HCL* étaient encore des termes obscurs. Merci pour tes relectures à toute heure, mais toujours attentives et efficaces de nos différents articles et de ce manuscrit.

Merci Olivier pour ta confiance absolue, ou quand une seule discussion désintéressée autour d'un verre suffit à engager une thèse à distance quelques mois plus tard. Merci pour ton accompagnement et ta présence continue malgré la distance maintenue par le Covid. Merci pour ton temps et ton dévouement sans faille, notamment dans les derniers jours jusqu'à la soutenance. Je n'oublierai pas non plus ta relecture marathon du manuscrit!

La thèse est une aventure, certes personnelle, mais partagée. Merci à mes parents, de m'avoir donné le goût de poursuivre de longues études, à mon Papa de m'avoir initié à la recherche, dès mon plus jeune âge lorsque je bricolais de petits circuits électriques pour Playmobil. Merci à mes amis et à ma famille pour leur soutien, j'ai été particulièrement touché par l'engouement suscité par la soutenance, assidûment suivie à distance par un grand nombre d'entre vous.

La thèse est une aventure, mais est-elle finalement si personnelle? Elle finit par embrigader, bon gré mal gré, ceux qui gravitent de trop près autour. En quatre ans, la vie avance, d'étape en étape, péripéties après péripéties. Merci Clothilde d'avoir pris part à cette aventure à mes côtés, depuis 2015, dans le bonheur et dans les épreuves, dans la santé et dans la maladie.

## Chapter 1

# Introduction

While the need for specialized hardware accelerators arises in various contexts, this preliminary chapter intentionally focuses on the concrete industrial motivations which have led to the use of Field Programmable Gate Arrays (FPGAs) at the core of high-performance network devices at OVHcloud.

**B** UILT on universality and equality principles, the Internet is expected to provide a free and unrestricted access to its contents to all individuals. As stated by the IRPC<sup>1</sup> in their 10 Internet Rights and Principles, "everyone has an equal right to access and use a secure and open Internet". This ideal and philanthropic vision is unfortunately endangered by many players, from dictatorships and authoritarian states to greedy companies to malicious individuals. Either to protect their interests or to arbitrary restrain freedom of others, they are determined to enforce their own rules by all means.

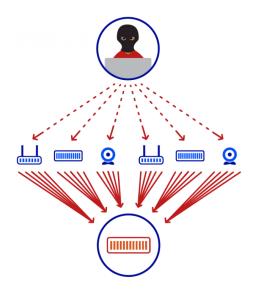

Figure 1.1: Distributed Denial of Service (DDoS) principle

Among the various attack strategies used to disrupt the Internet, one consists in saturating a given service, e.g. a webpage, by throwing at it more requests than it is capable to process. This results in a *Denial of Service* for legitimate users whom are not able to use the service anymore, e.g. they are unable to access the content of the webpage and instead

<sup>&</sup>lt;sup>1</sup>"The Internet Rights and Principles Dynamic Coalition is an open network of individuals and organizations based at the UN Internet Governance Forum (IGF) committed to making human rights and principles work for the online environment." Website: https://internetrightsandprinciples.org

reach a connection timeout without response. As the capacity of web services are sized to handle numerous requests from many users at the same time, generating a sufficient amount of traffic to reach saturation requires a considerable computational power and a solid network connection. To overcome this technical limitation, attackers instead rely on a large group of previously compromised devices, referred as a *botnet*, and order all devices to send as many requests as they can to the same target at a precise time [MSB+06]. Figure 1.1 illustrates such a *Distributed Denial of Service*, based on several kinds of compromised devices such as unsecured IP cameras or misconfigured home routers. Some malicious organizations continuously track down vulnerable devices to create large botnets and rent their harmful powers to the highest bidder, generating attacks above 1.5 terabits per second (Tbps) [Net20, MXSJ17]. The most famous DDoS victims include public administrations and controversial websites, however most attacks are now profit-driven [WCCM18]. In particular, the online gaming industry, which relies on low latencies to provide a satisfying experience to players, appears particularly prone to attacks [BGG+22].

#### **OVHcloud Network Defense Infrastructure**

As there are not only legitimate users of services on the Internet, part of the traffic directed to cloud provider services such as OVHcloud is ill-intentioned. Service providers must protect themselves from DDoS attacks, either targeting specific hosted services or even their own network infrastructure for a larger impact in case of successful disruption. Detecting rogue traffic and mitigating its impact as soon as it enters the network infrastructure, i.e. at the external connection points referred as Points of Presence (POP), is required to defend the network against high-throughput attacks. Early detection and mitigation of such attacks gives them no opportunity to saturate some network nodes before reaching a dedicated mitigation infrastructure.

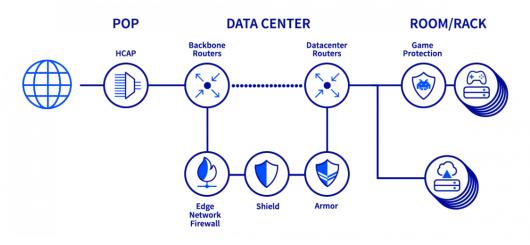

Figure 1.2: OVHcloud's network defense infrastructure

To protect a worldwide network with more than 20 Tbps connected to the Internet, OVHcloud has developed its own anti-DDoS protection system which successfully mitigates thousands of attacks a day. Figure 1.2 illustrates this defense infrastructure, beginning in POPs with *HCAP*, a first coarse-grained mitigation stage based on Field Programmable Gate Arrays (FPGAs). To complete the filtering, it then relies on detection algorithms (omitted in the figure) which redirects suspicious traffic to a mitigation center composed of three fine-grained mitigation elements. The last one, *Armor*, is of particular interest in the context of this thesis as it combines FPGAs and CPUs to deliver high-performance and

advanced mitigation mechanisms at hundreds of gigabits per seconds. This combination of heterogeneous technologies requires keeping hardware developments synchronized with agile software development flows and their continuous improvements.

#### **Thesis Goals**

In this context of pressing need for high-performance network devices, hardware accelerators such as FPGAs appear as energy-efficient alternatives to functionally equivalent software solutions. However, hardware developments struggle to reach the efficiency of their software counterparts and improved hardware development flows are required to deliver regular updates at a steady pace. Among the various available options, this thesis focuses on raising the level of abstraction of the design description, without compromising neither on performance nor on control over the hardware implementation. Representative of this approach, Hardware Construction Languages (HCLs), propose to describe hardware generators with modern software paradigms such as functional and object-oriented programming.

The overall goal of this thesis consists in evaluating the ability of HCLs to abstract hardware architectures, first natively and then as a platform for additional hardwareoriented abstractions. Experimenting with Chisel HCL [BVR<sup>+</sup>12], this thesis reviews the relevance of such abstractions to design highly flexible and re-usable high-performance network devices at OVHcloud.

#### **Thesis Outline**

Chapter 2 introduces in greater details the context and the approach of this thesis, and raises several precise issues we attempt to address with this manuscript.

Chapter 3 reviews prior research regarding hardware-oriented abstraction levels with a comparison to the evolution of abstraction levels in software. In particular, it focuses on Hardware Construction Languages (HCLs) as a first level of zero-cost hardware abstraction.

Chapters 4, 5 and 6 detail the contributions of this thesis. Considering both implementation and design perspectives, we first focus on the abstractions provided by HCLs to develop high-performance network functions. We then propose our own hardware-oriented abstraction to improve parameterization and re-usability of pipelined applications. We finally review the integration of these novel design methodologies within existing HDL hierarchies, which results in the introduction of two tools aiming at smoothening the cohabitation of both methodologies.

Chapter 7 combines the previous contributions in an industrial-scale experimentation. It follows the successive upgrades of a packet classifier from its original SystemVerilog hierarchy, to its re-integration as a pipeline-oriented hardware generator within the surrounding network devices.

Chapter 8 concludes this manuscript with a summary of contributions and details the perspectives of potential future works.

## Chapter 2

# **Problem Statement**

$\mathbf{I}$  This chapter, we present the issues of existing hardware design techniques with regard to agility and high-performance requirements of a constantly evolving network environment. Network devices are expected to flawlessly process very high throughput while providing configurability for both daily-basis operations and long-term evolutions. Designing devices matching both requirements is a complex challenge.

In order to apprehend the needs for more *agile* hardware design techniques, we first inspect the network ecosystem. Secondly, we detail network device design requirements which arise from the ecosystem, then we review existing hardware design solutions. Finally, we focus on hardware generation techniques and question their ability and means to provide the agility hardware designers are looking for.

#### Contents

| 2.1 | Intro | luction                                                 |  |

|-----|-------|---------------------------------------------------------|--|

|     | 2.1.1 | Agile Methodology Definitions6                          |  |

|     | 2.1.2 | Overview of The Internet                                |  |

| 2.2 | Netw  | ork Application Design                                  |  |

|     | 2.2.1 | Design Principles                                       |  |

|     | 2.2.2 | Performance Requirements                                |  |

|     | 2.2.3 | Agility Requirements 11                                 |  |

|     | 2.2.4 | From Architecture to Efficient Implementation           |  |

| 2.3 | Towa  | rds Agile and Efficient Hardware Design 14              |  |

|     | 2.3.1 | Limitations of Leading Hardware Design Methodologies 14 |  |

|     | 2.3.2 | Promises of Advanced Hardware Construction Languages 18 |  |

| 2.4 | Concl | usion                                                   |  |

## 2.1 Introduction

The problem tackled in this thesis lies at the confluence of two usually opposed considerations: performance and flexibility. On the one hand, high-speed networks set high standards of throughput and latency for their devices. On the other hand, their operation requires flexibility due to a constantly evolving usage, from both user and provider perspectives. Before digging into the association of these two considerations, this section first introduces the concept of *agility* and then provides applicative context about the topology of the Internet and the typology of the Internet traffic.

#### 2.1.1 Agile Methodology Definitions

Following the publication of the *Manifesto for Agile Software Development* in 2001 [agi11], the terms *agile* and *agility* have become widely used adjectives to refer to many design and project management methodologies, not exclusively restricted to software [LWC<sup>+</sup>16]. These methods are grounded on the spirit of the manifesto, which emphasizes: *"individuals and interactions over processes and tools, working software over comprehensive documentation, customer collaboration over contract negotiation, and responding to change over following a plan"*. In practice, agile approaches focus on **small and fast iterations**, each delivering an incomplete but working prototype. The adjectives *small* and *fast* are deliberately vague here as they heavily depend on the implementation of the *agile methodology* in a given context. Goals and principles set up for *front-end* software development might indeed largely differ from the one chosen for hardware tape-out.

In this thesis, the terms *agile* and *agility* are used to refer to this common base principle: "*small and fast iterations*", without restricting to a specific implementation. As iterations are at the core of hardware development process, regardless of any project management considerations, we focus exclusively on agility within the hardware design flow itself. From design to implementation, to simulation, to synthesis and final testing, each step indeed requires fine-tuning of the architecture with back and forth to the drawing board. To accelerate these necessary iterations, responsiveness and flexibility of hardware descriptions, tools and design flows are key enablers.

The expression "*user-story*" can sometimes be used to refer to one design iteration, with the idea to demonstrate a user-impacting feature at the end of the fixed timeframe. Large and diverse requirements are split into such user-stories, quickly and regularly delivered as successive minimal functioning prototypes rather than as a single finished product down the line. Flexibility in the development process is required to allow such deliveries without impairing the overall consistency and slowing down the entire process. On the contrary, as these user-stories focus on implementing independent and well-identified features, they are expected to catch and address issues more efficiently. This leads to an overall improvement of the design quality and development time.

Practicing agile methodology requires an appropriate development environment to reach its goals, notably to avoid full redesign for each increment and potential regressions due to the frequent modifications. In particular, this thesis focuses on applying these agile principles to the implementation of high-speed networking devices. The following subsection provides an overview of the wide and heterogeneous ecosystem in which such devices are intended to be integrated: the Internet.

#### 2.1.2 Overview of The Internet

The Internet is a giant computer network connecting just over half of the world population, with more than 3.8 billions users as of 2020 for an estimated global bandwidth of 700 terabits

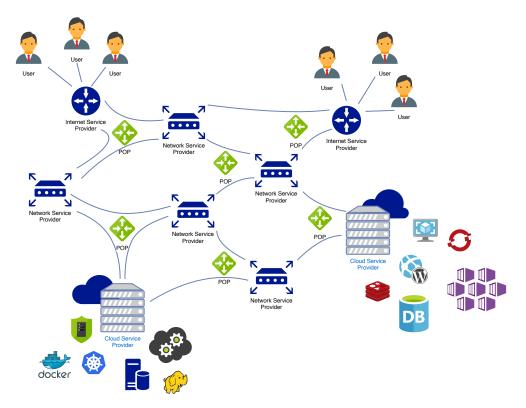

Figure 2.1: Internet topology

per second (Tbps) [BM<sup>+</sup>20]. At the opposite of a homogeneous and centralized system, it gathers thousands of heterogeneous subnetworks respectively providing access to parts of the world.

#### 2.1.2.1 Topology

Such gigantic—and constantly rising—numbers are made possible thanks to the very nature of the Internet: *a multi-tiered, non-hierarchical network topology.* It means that there is no single point in the network centralizing and processing all these 700 Tbps. Instead, a multitude of actors operating infrastructures of various scale, contribute to this worldwide connectivity as Figure 2.1 illustrates. Users usually get an Internet access through a subscription with an *Internet Service Provider (ISP)*. ISPs are connected to multiple *Network Service Providers (NSPs)*, in order to reach the various places where services are located. While contents once used to be hosted on-premise by their respective authors, they are now largely centralized in datacenters managed by hosting companies. As these hosting companies diversified their activities during the last decade, offering many services such as compute, storage or network, they are now best known as *cloud service providers*. OVHcloud is one of such cloud service provider, the largest in Europe and worldwide competing with actors such as Amazon Web Service (AWS), Microsoft Azure and Google Cloud in America or Alibaba Cloud in Asia.

Each interconnection between two service providers requires a physical connection between their respective infrastructures which takes place in *Points-of-Presence* (POPs). In the decentralized topology of the Internet, these POPs are critical centralization points of the traffic, in charge of routing high traffic throughput, ranging from tens of gigabits per second to several terabits per second per interconnection. Due to their strategic value for the network stability, providers generally rely on redundant and oversized links to guarantee

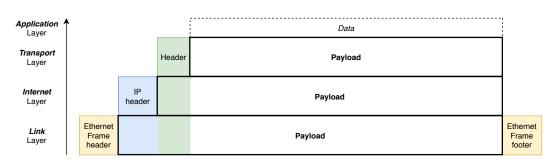

Figure 2.2: Typical IP packet structure in the *Internet protocol suite* (*TCP/IP*) model from *Link* layer to *Application* layer

their coverage of any given part of the Internet at any time.

#### 2.1.2.2 Traffic typology

In all places of the network infrastructure, and in particular in POPs, measuring and forecasting the volume of traffic is crucial. This traffic consists in a raw flow of bits, grouped in independent *packets* which transit through the network from one *source* to a *destination*. Following the *Internet protocol suite* (*TCP/IP*) model, Figure 2.2 illustrates how raw bits are first interpreted as *Ethernet frames* whose payloads are in turn interpreted as *IP packets*, usually simply referred as *packets*. To measure throughput and understand the traffic typology, two key characteristics are considered.

- **Bitrate (bps)** The most commonly used scale to report throughput figures is the amount of bits passing through a link or a device in a given unit of time. Called *bitrate* and measured in bits per second (bps), it offers a raw quantization of the traffic. In particular, at the *link level* this value takes into account all the bits required to transmit a packet over the communication medium, independently of any applicative intents. This physical bitrate is necessary and sufficient to dimension links capacity between nodes of the network. On the other hand, applications only consider the useful payloads and compute a bitrate which is more meaningful to the final user.

- **Packet rate (pps)** This second scale reports the number of packet passing through a link or a device per second. As each packet requires its own set of processing steps, this scale is key to dimension the processing capacity of network devices.

Combining *packet rate* and *bitrate* offers further insight into the traffic typology. While bitrate is used to size the capacity of links and buffers, packet rate is directly linked to the computational power required to process the traffic. For example file storage services are associated with a flow of big packets meaning relatively high bitrate for relatively low packet rate. On the contrary logging platforms process a lot of individual events each consisting of a small packet with little data, leading to relatively high packet rate for low bitrate.

## 2.2 Network Application Design

Following the introduction of general considerations related to network integration context, this section delves into the design of network devices, from principles to detailed requirements.

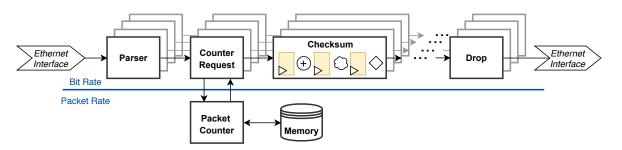

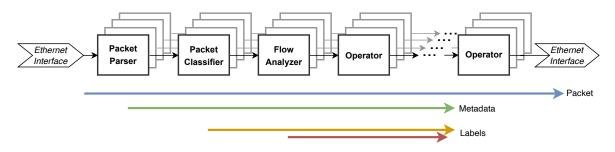

Figure 2.3: Network application representation

### 2.2.1 Design Principles

### 2.2.1.1 Definitions

**Network Application** The expression *network application* relates to the overall functionality offered by a set of network devices, regardless of the choices made for the actual implementation of this functionality. Network devices are *computers* in charge of processing network flows and can indeed be implemented with various hardware and software technologies. Moreover, some functionalities might either be implemented within a single device or shared across multiple devices, each approach providing its own advantages.

**Network Flow** A network flow is a generic term used to identify a communication between two nodes of the network. Depending on the network context and the application goals, these flows will be strictly defined as a set of fields related to the network protocol in use. For example, in the context of IP networks, a flow is often defined with its so-called *5-tuple*, consisting of:

- 1 field for transport protocol identifier<sup>1</sup> (most commonly used are TCP, UDP and ICMP),

- 2 fields for source and destination port of transport protocol (if any),

- 2 fields for source and destination IP addresses.

The 5-tuple is not fully exhaustive given the diversity of transport protocols, however it is a strong basis to identify and keep track of a connection from a user to a service.

**Stateless** The most basic network applications are stateless, meaning that they do not need to keep track of flows over a period of time. An example of such application would be a set of static rules in charge of allowing or denying access to some flows: e.g. accept only traffic towards a given range of public IPs on port number 443 (https), and deny all incoming packets that are not TCP.

**Stateful** More complex applications require keeping track of the flows over time. For example, to compute a throughput, a counter is associated to each flow in a *(key, value)* manner. Appropriate memories are then required and their limitations in terms of latency and throughput are key factors to dimension the implementation according to performance requirements.

<sup>&</sup>lt;sup>1</sup>The transport protocol is the protocol corresponding to the transport layer of the *TCP/IP* model illustrated in Figure 2.2. The protocol identifier is contained into the header of this layer.

#### 2.2.1.2 Generic Architecture

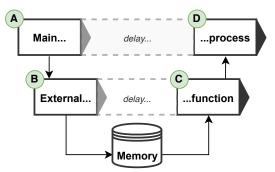

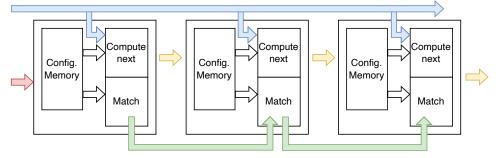

In a network application, some operations such as checksum computation are done at bitrate, while others such as packet filtering or state storage are done at packet rate. This leads—independently of any implementation choice—to a conceptually simple architecture represented in Figure 2.3.

Network packets are provided by the Ethernet interfaces as successive chunks sequentially processed in the application. A reliable and fast interconnection with these interfaces is crucial to meet performance requirements in terms of bitrate. Operations occurring at bit level are chained as a pipeline and a sufficient number of these pipelines are instantiated to reach the required bitrate. These pipelines then access shared operations executed at packet rate.

Packet rate and bitrate requirements for a network application hence have critical and distinct implications with respect to solution implementation. For stateful applications such as Figure 2.3 illustrates, the choice of a memory technology and its characteristics deeply impacts the worst-case achievable performance in terms of packet rate.

#### 2.2.2 Performance Requirements

#### 2.2.2.1 Throughput

At OVHcloud, the network entry points consist of a few dozens of POPs worldwide, providing a peering capacity of over 24 Tbps. Typical peering links capacity can range from tens of gigabits per second (Gbps) for minor actors to tens of terabits per second for large and tightly coupled actors. A typical value used to dimension network devices in POPs, is a peering capacity of 1 Tbps. However, while bitrate is sufficient to scale network links, packet rate is also a primary element to consider for network device design.

Minimal and maximal packet sizes are the key to draw a relationship between these two rates. Without exposing all the structural details of successive protocol layers, the main figure to consider is that the smallest *IP packet* requires 84 bytes<sup>2</sup> on the wire. In contrast, the biggest packets would usually take up to 1538 bytes or even 9038 bytes for so-called *jumbo frames*.

A continuous flow of theses *jumbo frames* at 1 Tbps would require an equivalent packet rate of:

$$\frac{1 \cdot 10^{12}}{9038 \cdot 8} = 13 \cdot 10^6 \text{ pps} = 13 \text{ Mpps}$$

However the required packet rate quickly increases as soon as the packet size decreases. Considering the worst-case scenario of a continuous flow of the smallest possible packets, a device in charge of a 1 Tbps link should be able to process as many packets per second as:

$$\frac{1 \cdot 10^{12}}{84 \cdot 8} = 1.5 \cdot 10^9 \text{ pps} = 1.5 \text{ Gpps}$$

This higher value shall be used, at least as reference, to define the packet rate requirement of any network device. In the context of attack mitigation, the worst case scenario for designer is indeed the best-case scenario for any ill-intentioned user and shall be considered accordingly. Based on statistics of actual traffic typology this requirement might be partially loosened, following a risk analysis which is beyond the scope of this thesis.

<sup>&</sup>lt;sup>2</sup>Minimal size of an Ethernet Frame is 64 bytes (Link layer in Figure 2.2). Transmitting it on the physical layer—as a full Ethernet packet—requires a 8 bytes header and a 12 bytes inter-packet gap (IPG), adding up to 84 bytes [I<sup>+</sup>18].

#### 2.2.2.2 Latency

Latency of a network device is the time for a given packet to fully pass through it, from the input interface to the output interface. Latency is a significant characteristic of network applications, as packets transit and are processed by many network devices before reaching their final destination. Several kinds of Internet uses deeply suffer from high or fluctuant latency, such as Voice over IP (VoIP) communications or video games.

Apart from the raw compute latency induced by the network application itself, a key component of the latency is the time spent between the application and the interface. This duration increases for each intermediate layer in the processing. A latency-optimal network application architecture, as presented in Figure 2.3 would connect as directly as possible the application to the interfaces without any third parties.

#### 2.2.3 Agility Requirements

#### 2.2.3.1 Daily Configurability

Immediate configurability of network applications is a key for fast incident response. Application must therefore be designed in a way to provide instantly adjustable parameters for network operation. Configurability can also be a service for users, with for example configurable firewall rules, manipulated through an Application Programming Interface (API) and potentially updated in a matter of seconds depending on the user's requirements.

However, this kind of instant configurability allows no time for application upgrade. This implies either careful planning of all use-cases at the time of application design, in order to expose all relevant parameters—which would be the opposite of agile methodology, or designing the application in such way that regular upgrades are part of its lifecycle, through *small and fast iterations*. Each of such iteration can then bring new parameterization options for the end-user, with fast response to emerging and unplanned needs. In this thesis we focus on this mid- and long-term upgrade requirements, further detailed in the next subsection.

#### 2.2.3.2 Mid- and Long-term Design Upgrades

High-speed network devices, at the core of the Internet *backbone*, are expensive and expected to last for numerous years, when at the same time services and technologies evolve much faster.

A practical and long-running issue partially caused by outdated network devices is the slow adoption rate of IPv6 protocol, aiming at superseding IPv4 since 1995 but still very unevenly deployed in the world [CAZ<sup>+</sup>14]. Most new network devices now provide IPv6 support, but very few offer the same advanced features for both IPv4 and IPv6 traffic.

Alongside this actually very long-term evolution, many others, with smaller impact but occurring on a regular basis, punctuate a device lifecycle, such as evolution of the Internet uses. An example is the introduction of new technologies and platforms, such as video streaming and videoconferencing services, whose usage has been increasing for years [BM<sup>+</sup>20]. Another factor is the implementation of new higher level network protocols which impact the traffic shape at lower level. The rising utilization of *QUIC* protocol, an equivalent of HTTP/TLS over UDP [IT21, LRW<sup>+</sup>17], is a contemporary example. In addition, some network applications are built on top of various pieces of hardware, and their respective lifecycles impact the application evolution. Older hardware might indeed progressively be discarded, while the application must be adapted to support new references, from various vendors and slightly different specifications. Finally, the above-mentioned incident response which triggers immediate actions sometimes also requires structural changes to the application, to sustainably mitigate newly detected threats.

Assuming that upgrading application design is an option, confidence in the design flow, from language expressiveness to automated validation toolchains, is decisive to achieve an efficient upgrade. The time spent to first, implement a design upgrade, and then validate it, is indeed a considerable factor of responsiveness. The fewer lines of code are impacted and the more localized they are, the faster the upgrade is implemented. From then on, an automated and exhaustive validation flow is a key enabler to efficiently deliver this upgrade. Confidence stands on the ability of a language and its associated toolchain to catch bugs and developer mistakes as early as possible in the development flow. Strongly typed languages with strict compilers and appropriate linters are valuable assets to grow confidence in a toolchain.

#### 2.2.4 From Architecture to Efficient Implementation

Performance requirements of network devices are measured on various scales: bitrate, packet rate, latency and resilience to traffic surge. This thesis focuses on the network design requirements of core network devices, providing the highest standards for each of these requirements with respect to the power-consumption. Such devices are indeed aiming at handling continuously large amount of traffic, at network edge in POPs or within cloud provider network infrastructure. Considering the replication of devices across network infrastructure to process traffic at scale, performance per watt is a key criterion to compare their implementation.

#### 2.2.4.1 Network Processing Units

In a network device context, solutions dedicated to packet processing are known as Network Processing Units (NPUs). One of their key characteristic is their close access to high-speed network interfaces in order to achieve high throughput and low latency.

The generic architecture presented in Figure 2.3, which serves as reference for the implementation of NPUs, is based on a pipeline of processing elements. In particular, usual NPU implementations can be divided in three main categories, depending on the configurability of both their pipeline and their processing elements [Sta15]:

- *Fixed pipeline* **NPUs** exhibit the best performance per watt but little configurability and no evolution ability,

- *Configurable pipeline elements* **NPUs** still constrain the network processing pipeline but support greater configurability and minor midterm evolutions, notably at the level of their processing elements,

- *Fully-configurable pipeline* NPUs are not restricted to any structure of network pipeline nor to a predefined subset of processing operators.

#### 2.2.4.2 Available Implementation Targets

The diversity of configurability intents of NPU architectures leads to various corresponding implementation targets.

**ASICs** Application Specific Integrated Circuits (ASICs) are custom-made integrated circuits, designed and optimized for the application they serve. Typically chosen to implement fixed pipeline NPUs, they achieve the best performance per watt at the cost of limited

configurability and no long-term evolution ability. Their manufacturing cost as well as the time required from design to production makes them hardly suitable for small and fast design iterations.

**CPUs** General purpose Central Processing Units (CPUs) offer full flexibility, with fast shortterm update capabilities and the ability to support long-term evolutions. In charge of both scheduling and processing, CPUs provide the implementation target for fully-configurable NPUs. In such case, the NPU is implemented as a software application, leveraging tools and framework such as DPDK [CAR14], eBPF with XDP [VCP<sup>+</sup>20] or VPP among many others [CDPA<sup>+</sup>18]. These implementations aim at shortening and accelerating the path between network interfaces and user-space where the application runs. However, this approach suffers from the physical distance: entire packets have to transit up and down the software network stack. As a result, this stack becomes a throughput bottleneck which craves for hardware acceleration.

**Mixed Approach** To benefit from both ASIC performance and CPUs flexibility, some NPUs combine both to offer configurability ranging from *Configurable pipeline elements* NPUs to *Fully-configurable pipeline* NPUs. A big agility advantage of these platform is the provided toolchain used to program them: both daily update and long term update can be compiled from the provided language(s) to the device in a matter of minutes. They are hence the most suitable NPUs to match our requirements, however, they come with two pitfalls. First, the extended configurability comes at the cost of lower performance per watt. Second, the long-term evolutions remain strictly restricted to the underlying architecture, including but not restricted to bus sizes and coarse-grain operators available. With respect to the previous IPv6 deployment example, these restrictions would lead to accept a considerable loss of throughput in order to enable IPv6 support on an earlier device. Indeed, the support of IPv6 requires much larger metadata processing: not less than 256 bits instead of 64 bits for a source-destination IPs tuple. Assuming an existing metadata bus of 64 bits, IPv6 packets require 3 additional cycles to be processed on such device.

**FPGAs** Field Programmable Gate Arrays (FPGAs) are reconfigurable devices composed of numerous programmable logic blocks and interconnects. Arbitrary large FPGAs are able to implement virtually any digital circuit, at the cost of limited running frequencies due to their fixed layout of configurable resources. They exhibit an interesting trade-off between performance per watt and lifetime management, which makes them well-suited to build network processing systems. In particular, they are able to implement efficient *fixed pipeline* NPUs while retaining the ability to support a complete architecture upgrade for an updated version of the network application. Compared to ASICs, they do not require the high investments associated with tape-out and are hence able to address niche markets with cost-effective chips.

#### 2.2.4.3 Conclusion

While providing the best configurability, software solutions based on general purpose CPUs are falling behind in terms of performance per watt compared to specialized hardware accelerators [NSS<sup>+</sup>16, CS12]. As a result, dedicated hardware solutions are generally preferred, at least for the wire-rate processing, for development of high-speed network processing units. As ASICs can hardly be described as agile due to their inherent manufacturing cost, FPGAs appear as the best suited implementation targets given our requirements. The following section therefore focus on way to match both agility and performance requirements in the context of hardware design.

## 2.3 Towards Agile and Efficient Hardware Design

### 2.3.1 Limitations of Leading Hardware Design Methodologies

First steps of digital circuit design flows are identical for ASIC and FPGA targets. They both rely on a description of the circuit at Register Transfer Level (RTL). This RTL description can be manually crafted or produced by various tools from a *higher-level input*. It can then be used interchangeably for simulation, FPGA synthesis or ASIC synthesis. In this thesis we focus on the expressiveness and reusability of hardware descriptions at their various abstraction levels. Therefore, without loss of generality, in our experiments we specifically report result of FPGA synthesis due to the previously discussed network context and requirements.

#### 2.3.1.1 Context

Two languages, *VHDL* and (*System*)*Verilog*, have emerged in the 80s to model digital circuits at the Register Transfer Level. Originally designed for simulation rather than synthesis, they intend to offer behavioral models of circuits, which are both Cycle-Accurate and Bit-Accurate (CABA). This level of detail offers the highest fidelity with the actual digital hardware, and was found precise-enough to be directly used as actual hardware description and synthesized into hardware netlist.

This high precision level makes these languages quite verbose, and their roots in behavioral simulation leads to two major issues for hardware description. First, only a restricted subset of the language is supported by synthesis tools, with significant differences among vendors. Second, the event-driven paradigm, particularly fitted to behavioral modeling, leaves the inference of events into actual hardware by the tools, which in practice requires sticking to predefined syntax and code snippets in order to obtain consistent results.

#### 2.3.1.2 HDL Agility Struggle through simple User-stories

In this subsection, we intend to demonstrate that classical HDL such as VHDL and Verilog are hardly compatible with agile methodology. In order to highlight their low agility, we review the code modification required by simple user-stories at the level of a basic addition module. Without loss of generality, the following examples are presented as Verilog code.

**Iteration #0** A first version of the module is created, in its simplest expression, as follows:

```

module add(

input [5:0] a, input [5:0] b, output [6:0] r

);

assign r = a + b;

endmodule

```

This module *add* is computing the arithmetic *operation* r = a + b. The associated architecture is fully combinational and does not involve any protocol signaling.

**Iteration #1** After synthesis of this first module, assuming integration in a larger design, the timing report indicates a long combinational path linked to this module with regard to the rest of the design. For the second design iteration a register stage is hence added to store the result of the addition directly in the module as follows:

Figure 2.4: Potential integration issue with submodule latency evolution

```

module addReg(

1

input clock,

2

3

input [5:0] a, input [5:0] b, output [6:0] r

4

);

logic [6:0] res;

5

always @(posedge clock) begin

6

res <= a + b;</pre>

7

8

end

9

assign r = res;

10

endmodule

```

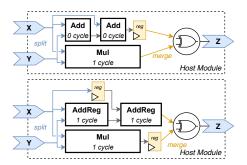

The presence of this additional register is to be considered carefully when integrating this module in larger designs. While breaking the combinational path helps the place & route tool, the latency of the module in clock cycles is increased, with no automated propagation of this information to the rest of the design. Figure 2.4 illustrates how the difference of latency between add and addReg modules must be compensated according to surrounding context in the upper hierarchy. However, such simple example is not representative of the complexity of a real module, in which moving the register in the upper hierarchy might simply not be feasible.

**Iteration #2** While the surrounding design evolves with various needs, a third iteration is now required to add a ready/valid signaling to the *data* signal.

```

module addRegDecoupled(

1

2

input clock,

input [5:0] a, output a_ready, input a_valid,

3

input [5:0] b, output b_ready, input b_valid,

4

output [6:0] r, input r_ready, output r_valid

5

);

6

logic [6:0] res;

7

logic res_valid = '0;

8

always @(posedge clock) begin

9

10

if (r_ready) begin

<= a + b;

11

res

res_valid <= a_valid & b_valid;</pre>

12

13

end

end

14

15

assign a_ready = r_ready;

assign b_ready = r_ready;

16

assign r_valid = res_valid;

17

assign r = res;

18

19

endmodule

```

In this new description the three *data* signals *a*, *b* and *r* are respectively associated with two protocol signals: *ready* and *valid*. This widespread pattern for signaling *data/ready/valid* is also referred as a *decoupled* interface. The introduction of this signaling protocol drastically increases the number of lines and reduces the readability of the user intent, now only counting for a single line of code over 19 of them, while at the first iteration it was also a single line of code but over only 5 in total.

**Iteration #3** Later on, the target FPGA for the design is changed for a more recent technology, allowing longer combinational paths. It is now counter-productive to add a register stage for every instance of *add* in the design. For this fourth iteration, the register stage is therefore removed from the module.

```

module addDecoupled(

1

input [5:0] a, output a_ready, input a_valid,

2

input [5:0] b, output b_ready, input b_valid,

3

output [6:0] r, input r_ready, output r_valid

4

5

);

assign r = a + b;

6

assign r_valid = a_valid & b_valid;

7

assign a_ready = r_ready;

8

assign b_ready = r_ready;

9

endmodule

10

```

This leads to substantial modification of the module and as above-mentioned, special care is once again required to carefully adapt the surrounding design to keep all signals synchronized and meaningful.

**Conclusion** These four user-stories highlight the major impact of basic implementationrelated design upgrade with traditional hardware description languages. In the current example, this impact comes from two main factors. First, protocol signaling is very verbose, it dilutes the essence of the user intent in a lot of additional protocol management, decreasing clarity of code. As a consequence, swapping one protocol for another means an almost complete rewrite of the module which drastically limits reusability and increases validation cost. Second, as Figure 2.4 illustrates, the designer is in charge of mentally inferring and manually propagating latency in terms of register stages from the innermost modules to the top module. This time-consuming and error-prone task further increases the cost of design upgrades, both in terms of development and validation. Developed a few decades ago assuming fixed requirements and specifications, traditional HDLs such as Verilog do not prove suitable for the *small and fast iterations* of agile methodology.

#### 2.3.1.3 Performance Limitations of High-level Design Methods

To overcome the limitations of traditional hardware description language, previous research focused on increasing the abstraction level of hardware development [BRS13, SAW<sup>+</sup>10]. A popular approach consists in expressing functionality instead of describing hardware. This includes High-Level Synthesis (HLS), where software languages are compiled into hardware architectures, and Domain-Specific Languages (DSL), where domain-dependent primitives are provided to describe the design.

**High-Level Synthesis** High-Level Synthesis is an active research area, in quest of efficient and generic algorithms to infer hardware architecture from software algorithms [NSP+16]. One of the goal of HLS approach is to open hardware development—in particular FPGA

as acceleration platform-to software developers with little hardware development experience, leveraging widespread languages such as C or C++. A second objective is the abstraction of the target: allowing a single piece of code to run indifferently on various target (CPUs, GPUs or FPGAs), even considering real-time context-switching between these targets depending on the needs [BMR16]. However, these promising features come at the expense of the development of a complex compilation toolchain. Inferring a functionallyequivalent hardware architecture from a given algorithm is indeed a first challenge in itself but finding an appropriate compromise that fits design constraints among the numerous possible hardware architecture is even harder. To tackle this issue, hints can be provided to the compiler as code annotations. However, this requires to manually provide an architecture for many pieces of code, hence defeating the original purpose. This also considerably slows down the design process, ultimately making it harder to upgrade as annotation might require to be manually adapted at each functional iteration. As a result, high-level synthesis is struggling to bring software agility to hardware design by reusing the exact same languages. In particular this applies to control-oriented design used in network applications, where architecture annotations are required to match throughput performance [NSP+16, MMGC20, GRDT+16]. Due to these annotations, the portability of HLS hardware descriptions between vendors is a complex challenge, which further reduces the actual reusability of such descriptions [XCC21]. While efficiently closing the gap between software algorithms and hardware implementations in various contexts, HLS is not suited to match both performance and agility requirements of high-speed networking applications.

**Application-Specific DSLs** Domain-Specific Languages regroup all languages designed for a restricted set of task or tied to a particular application domain. With respect to the strong network context, we focus here on network application DSLs which are promising for defining a network device at application level. FlowBlaze [SRC<sup>+</sup>19] is a DSL that provides a way to represent stateful applications. Another popular language is P4 [BDG<sup>+</sup>14], which is designed to program network pipelines. It relies on an architecture representation which defines the capabilities of the underlying processing system, and on an application representation based on required fields and operations applicable on packets. Toolchains implementing P4 offer real improvements over baseline HDL implementation. They automate the tedious process of protocol implementation, thus limiting the usual errors in bit manipulation, and speeding up integration of new protocols. They also provide an implementation agnostic view of the application, which eases discussion with non-hardware specialists and helps to focus on the functionality instead of implementation details. However, while P4 increases agility and expressiveness in this context, it is not sufficient. It relies on vendor IPs for function implementation, or on HLS when none exists. As HLS is not really adapted for these control-oriented applications, this leaves the implementation of missing functions unresolved. The tight performance constraints then lead to the need for custom implementations of critical functions. This means that agile development cannot be achieved only through the use of a network-related DSL.

**Conclusion** Providing advanced ways of representing network devices at application level, top-down design methods based on compilation of software languages still struggle to demonstrate clear agility gain when performance guarantees are set as key requirement. High-level hardware design methodologies presented so far fail to improve agility without compromising on architecture control and application performance. To that extend, these approaches are not further considered in this thesis.

#### 2.3.2 Promises of Advanced Hardware Construction Languages

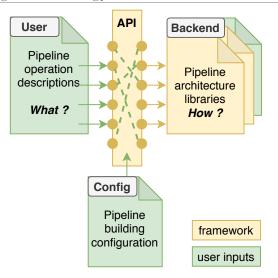

Hardware Construction Languages—or Frameworks (HCFs)—regroup all languages and toolchains that aim at providing generation constructs to produce pieces of digital hardware.

To that extent, thanks to their slight evolution since their creation, traditional HDLs such a (System)Verilog or VHDL can somehow be included in this category as they do provide some basic generation capabilities. However, as we previously demonstrated, their capabilities are too restrictive to match agile methodology requirements.

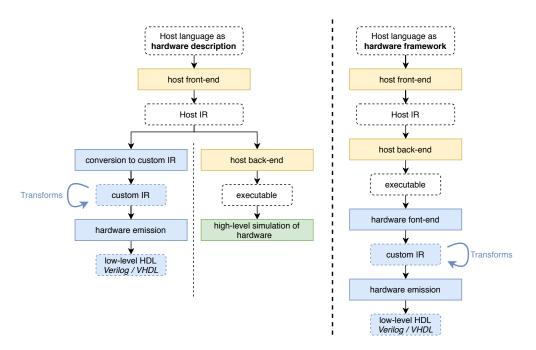

In order to increase abstraction level and provide advanced generation constructs without losing any control on the resulting architecture, three main approaches have been explored. The first consists in processing some pieces of existing hardware descriptions with an external tool to adapt them to various contexts. The second is about introducing new languages, supporting similar paradigms as traditional HDLs as well as new ones and enhanced constructs. The third one is about meta-programming: embedding hardware description languages into existing High-Level Languages (HLLs) which are providing the constructs to generate and further manipulate the circuits. Differences of these approaches will be further reviewed in the next chapter, as we now focus on the principles and objectives they all share.

#### 2.3.2.1 Principles

- **Generation** HCLs are sometimes known as *Hardware Generation Languages (HGLs)* [Max11] to highlight one of their common principle: provide advanced generation capabilities rather than simply describe hardware. Generation capabilities consist of constructs able to instantiate, duplicate and connect programmatically pieces of circuit.

- **Parameterization** Another shared principle is to focus on providing extended parameterization where traditional HDLs are restricted to fixed patterns and limited types. Parameterization is no longer to be limited to basic module parameters and HCLs offer to propagate them in new ways, such as automated negotiation between communicating parts of the design [CTL17, AAB<sup>+</sup>16].

- Additional paradigms While traditional HDLs hardly evolved since their first introduction, software languages, originally very close to machine language and its imperative programming paradigm have since benefited from many innovations. These innovations include among others object-oriented programming and functional programming paradigms. HCLs attempt to make these paradigms available to hardware designers as relevant tool in a hardware generation context [BKK<sup>+</sup>10].

- **Elaboration** The previous principles come with the need to close the gap between highlevel parameterized generators, and existing toolchains for hardware simulation and synthesis. While some works suggest introducing and standardizing an Intermediate Representation (IR) common to all the hardware design tools [SKGB20], the original principle of HCLs consist in leveraging the existing toolchains without requiring them to change. The uneven to nonexistent support among vendors of the features progressively introduced in traditional HDLs has indeed been a considerable issue for hardware designer for years. In order to fit in the existing and quite passive hardware tool ecosystem, HCLs come with their own toolchain to elaborate the highlevel generator into low-level hardware description in the form of traditional HDL code.

#### 2.3.2.2 Objectives

- **Reusability** A first objective of HCLs is to promote code-reuse rather than code duplication. Due to their limited parameterization capabilities, code factorization is often hard to achieve with standard HDLs, which often then leads to code duplication rather than code refactoring. This prevents the concurrent versions of an almost identical design to benefit from the improvements made to one of them, whereas HCLs aim at supporting small and fast iterations on the same pieces of code.

- **Expressiveness** A second objective of HCLs consists in easing the design of complex pieces of hardware based on expressive description patterns. Such patterns aim at improving code readability and reducing boilerplate code to describe complex circuits.

- **Conciseness** A transversal objective of HCLs is code conciseness, which helps with both reusability—shorter code is faster to update and integrate—and expressiveness—as to achieve conciseness the language must provide powerful constructs able to efficiently describe circuits.

## 2.4 Conclusion

In a context of network application setting strong requirements on both performance and agility, traditional HDLs as well as top-down high-level abstractions do not prove sufficient to produce efficient hardware at a steady pace.

While providing base hardware primitives close to HDL ones, Hardware Construction Languages follow a bottom-up approach to increase circuit abstraction. In particular, they support extended constructs to generate hardware, and promise more expressiveness and better code-reusability thanks to these new capabilities. Based on solid principles, HCLs notably claim to efficiently improve the hardware design development flow compared to traditional HDLs, which has been partially verified on some large projects [AAB<sup>+</sup>16]. However, HCLs have not yet fully demonstrated their claims, which raise several questions we aim at answering in this thesis:

- How far can the abstraction level provided by HCLs instill agility into hardware design flow while preserving fine-grained control over implementation?

- How can this abstraction level significantly remodel the design of hardware circuits from the earliest stages?

- What higher-level hardware design abstractions and paradigms can be relevant to improve agility of hardware design?

- How can HCLs provide the foundations to introduce and implement these additional abstraction levels?

- How to integrate HCLs generation-based flow into large existing codebases and their established hardware development flow?

## Chapter 3

# State of the Art

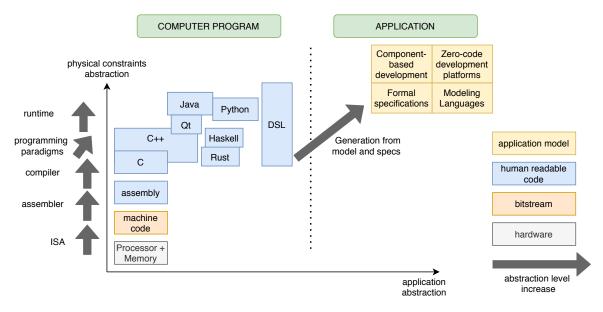

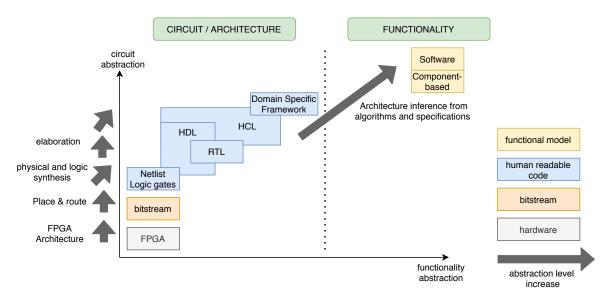

$\mathbf{I}^{N}$  THIS chapter we first establish the position of hardware construction languages (HCLs) in the hardware design ecosystem among the various existing abstraction levels. In particular, we compare the progressive raise in abstraction levels in hardware design to similar evolutions in software-engineering.

As the layering of successive abstraction levels has indeed unlocked new design opportunities in software, in a second part we study candidate high-level design paradigms aiming at remodeling hardware design methodologies. This study focuses notably on pipeline programming and paradigms leaning towards separation of concerns.

Finally, we review how, from shared principles, the diversity of HCLs implementations provides a suitable platform to develop and extend these high-level design paradigms towards increased flexibility and agile development flows.

#### Contents

| 3.1 | Raising the Abstraction Level    2 |                                                           | 22 |

|-----|------------------------------------|-----------------------------------------------------------|----|

|     | 3.1.1                              | Abstraction Levels in Software Engineering                | 22 |

|     | 3.1.2                              | Abstraction Levels in Hardware Design                     | 24 |

|     | 3.1.3                              | Conclusion                                                | 26 |

| 3.2 | High-                              | level Hardware Design Paradigms                           | 27 |

|     | 3.2.1                              | Pipelining Paradigm                                       | 27 |

|     | 3.2.2                              | Dataflow-oriented Programming                             | 30 |

|     | 3.2.3                              | Transaction-level Modeling                                | 30 |

|     | 3.2.4                              | Port and Interface Modeling                               | 31 |

|     | 3.2.5                              | Orthogonalization and Separation of concerns              | 31 |

|     | 3.2.6                              | Conclusion                                                | 32 |

| 3.3 | Imple                              | menting Abstractions with Hardware Construction Languages | 33 |

|     | 3.3.1                              | Review of techniques                                      | 33 |

|     | 3.3.2                              | Usage of HCLs towards Agile Development                   | 38 |

| 3.4 | Concl                              | usion                                                     | 40 |

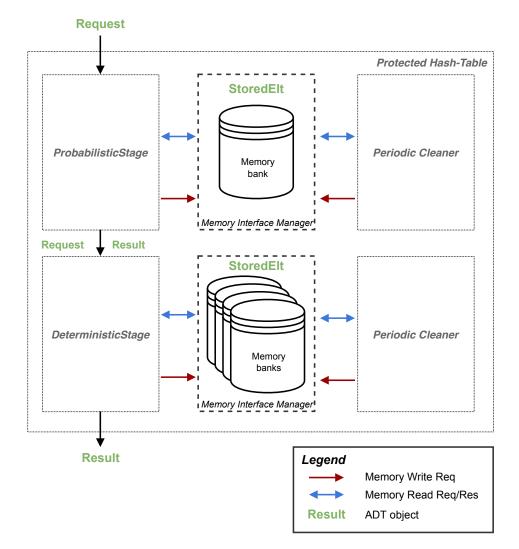

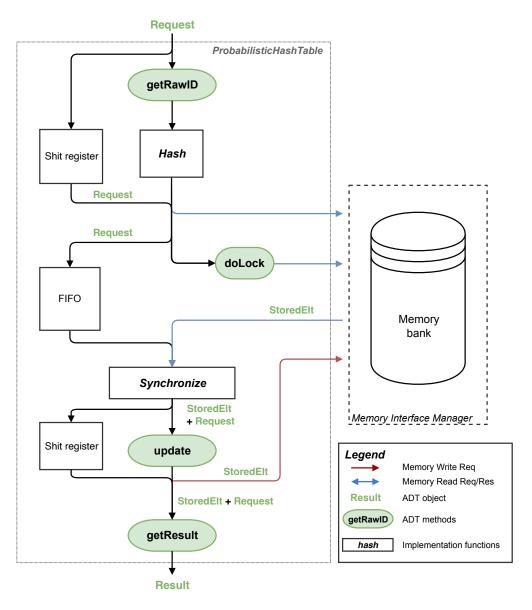

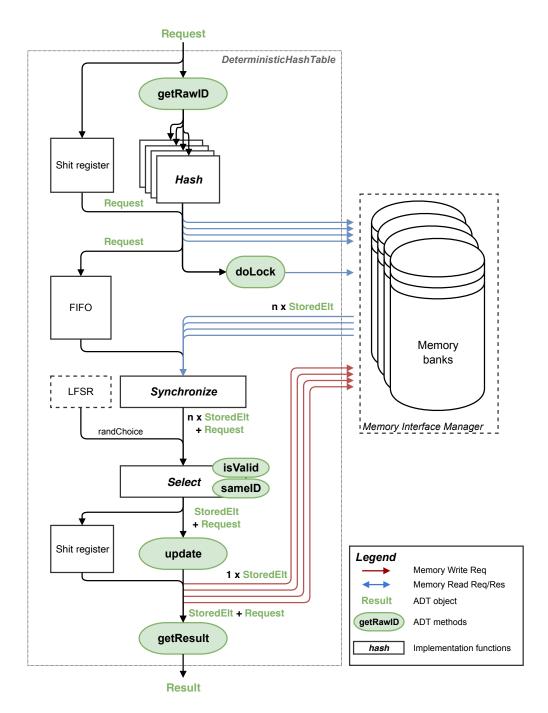

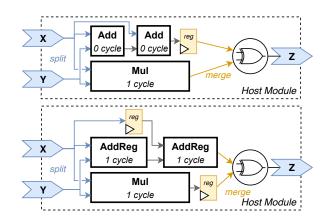

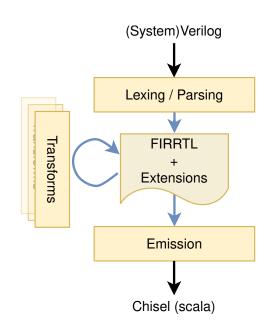

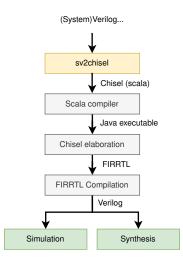

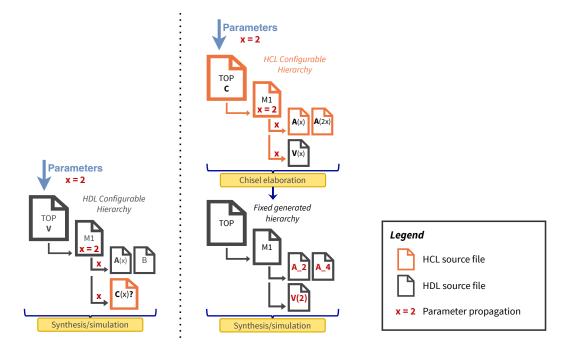

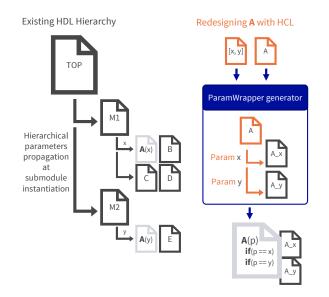

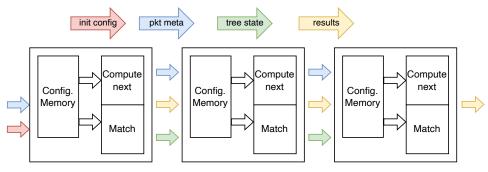

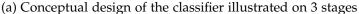

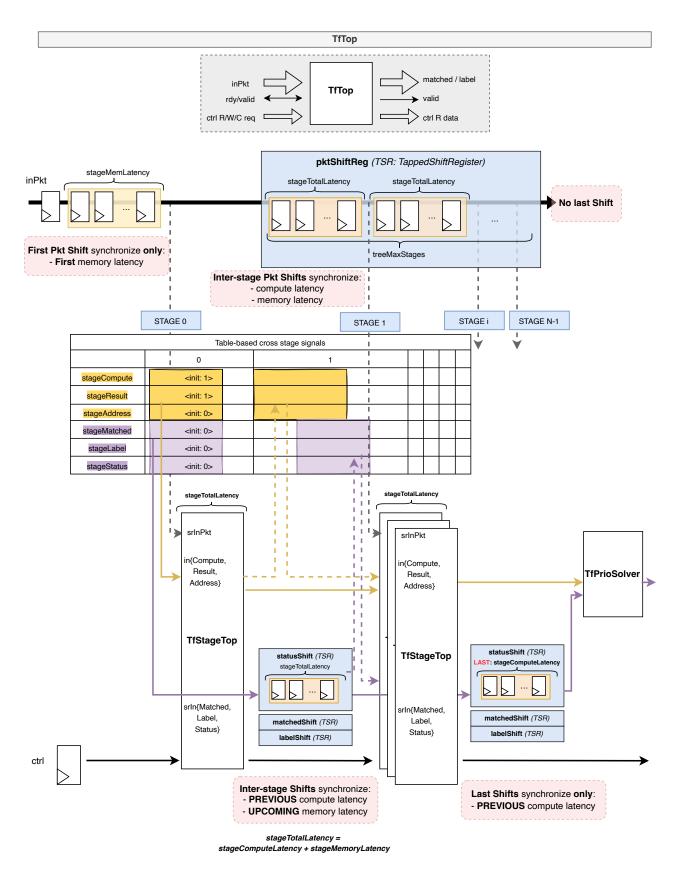

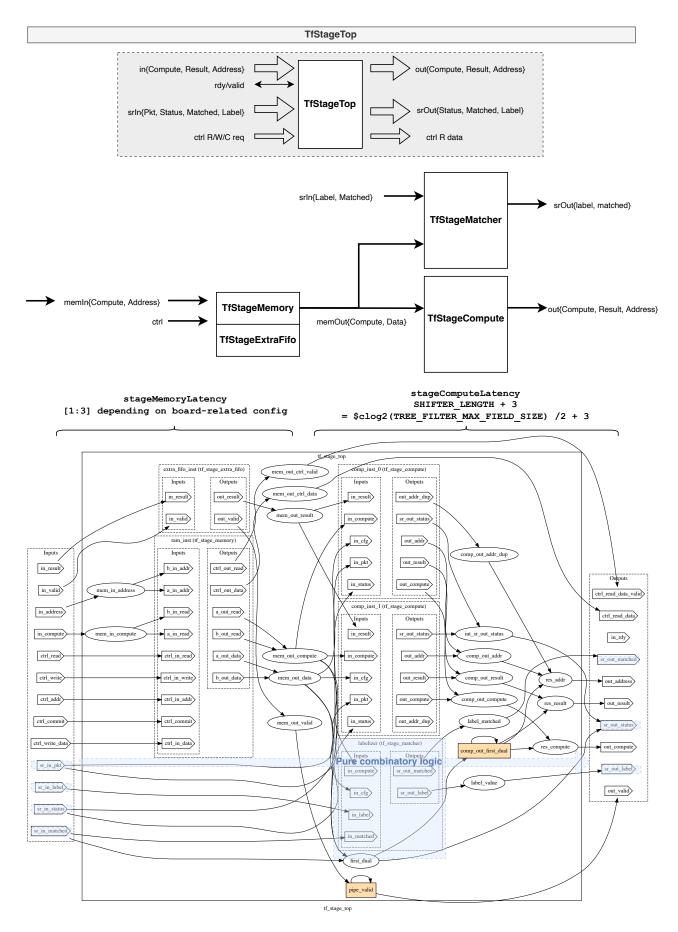

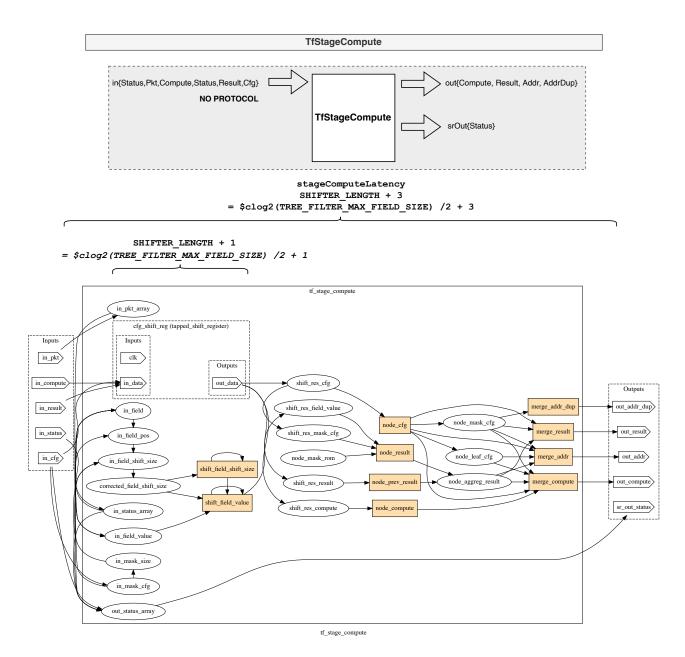

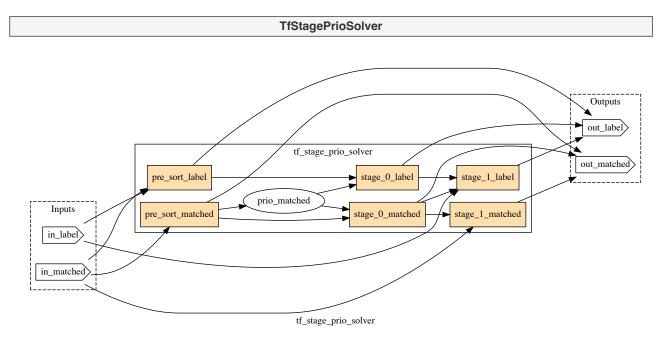

### 3.1 Raising the Abstraction Level