## Architectures to Ensure the Functional Safety of Neural Network based Systems

Stéphane Burel

#### ► To cite this version:

Stéphane Burel. Architectures to Ensure the Functional Safety of Neural Network based Systems. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALT095. tel-04020816

### HAL Id: tel-04020816 https://theses.hal.science/tel-04020816v1

Submitted on 9 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Communauté UNIVERSITÉ Grenoble Alpes

## THÈSE

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Sciences pour l'Ingénieur

Arrêtée ministériel : 25 mai 2016

Présentée par

## Stéphane Burel (doctorant)

Thèse dirigée par Lorena Anghel (directrice) et codirigéee par Adrian Evans (co-directeur)

préparée au sein du Laboratoire CEA/DRT/LIST/DSCIN/LSTA dans l'École Doctorale EEATS

## Architectures pour la sureté de fonctionnement des systèmes à base de réseaux de neurones

Architectures to ensure the functional safety of neural network based systems

Thèse soutenue publiquement le **9 décembre 2022**, devant le jury composé de :

#### Panagiota Morfouli

Professeur des Universités, Université Grenoble Alpes, Grenoble INP, Présidente

#### Alberto Bosio

Professeur des Universités, CNRS, École Centrale de Lyon, Rapporteur

Haralampos-G. Stratigopoulos Directeur de Recherche, CNRS, Sorbonne Universités, Rapporteur

#### Arnaud Virazel

Professeur des Universités, CNRS, Université de Montpellier, LIRMM, Examinateur

Kevin Martin Maître de Conférences, Université Bretagne-Sud, Lab-STICC, Examinateur

#### **Lorena Anghel** Professeur des Universités, Université Grenoble Alpes, CEA, CNRS, Grenoble INP, INAC-Spintec, Co-Encadrante de thèse

## Acknowledgments

Je tiens à remercier l'Université française. C'est elle, plus qu'aucune autre, qui permit au fils de roturier que je suis de m'instruire. C'est grâce à elle que j'ai pu me soustraire des méandres du prolétariat le plus précaire pour rejoindre l'aliénation bourgeoise. Mais je suis un homme fidèle ; Jamais je ne l'oublierai.

Je tiens à remercier ma directrice de thèse. Mme Anghel laissera à mon esprit l'image de l'excellence technique, toujours en étant à l'écoute et accessible. Je tiens également à vivement remercier mon encadrant de thèse, M. Evans.

Je tiens à remercier l'ensemble du jury de la thèse. Votre déplacement fut un plaisir. L'ensemble de vos remarques le jour de la soutenance laisse comprendre que vous avez pris cette soutenance avec autant d'importance que je lui en ai accordé moi-même. Vos avis étaient pertinents et m'ont donné envie de continuer ces projets de recherche.

Je tiens à remercier les membres de mon laboratoire d'accueil et plus particulièrement les membres de l'équipe dédiée à l'accélération neuromorphique. En vous chassant du bâtiment dans lequel nous étions alors, notre département n'a fait que nous unir davantage.

Je tiens à remercier M. Jourlin et l'ensemble du Laboratoire Informatique d'Avignon qui m'ont par un été frais comme on n'en verra jamais plus, au détour d'un stage de recherche, donné l'envie de faire cette thèse.

Je tiens à remercier les rencontres faites sur le bord de la route, tous ceux avec qui j'ai sympathisé et que j'espère côtoyer longtemps encore. Je parle particulièrement de mon ami le zadiste maintenant accompli, de celui qui voulait être suisse mais n'en a pas le sou, de celui qui rêve d'avoir le bras long ou encore de celui qui a l'âme pure mais est resté bloqué dans une série TV.

Merci à vous.

## List of Figures

| 2.1                                                                                      | Artificial Neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                              |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

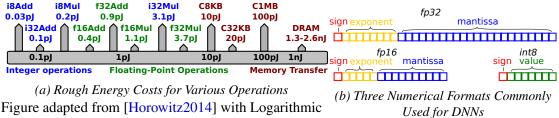

| 2.2                                                                                      | Improvement in Power Efficiency of DNNs with Reduced Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                             |

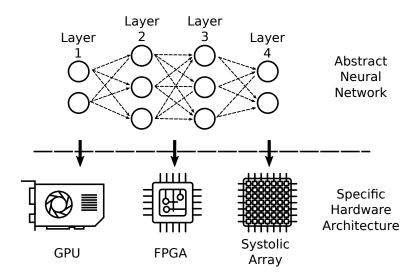

| 2.3                                                                                      | Difference between Abstract and Hardware-Specific Deep Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                             |

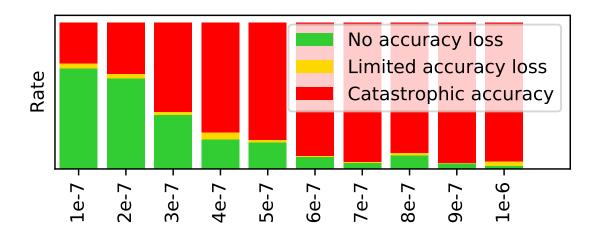

| 2.4                                                                                      | Bimodal Behavior on Floating Point based VGG-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             |

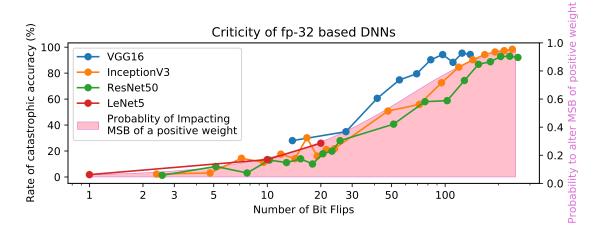

| 2.5                                                                                      | Behavior of Several DNNs at Increasing Number of Bit-Flips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                                             |

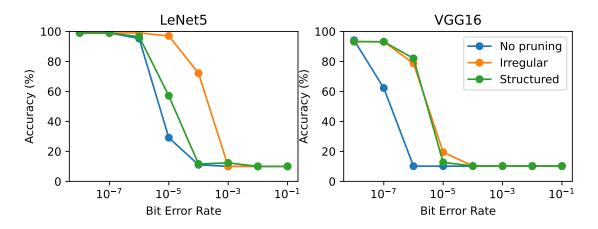

| 2.6                                                                                      | Accuracy of Various Pruned DNNs at Increasing Bit Error Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                             |

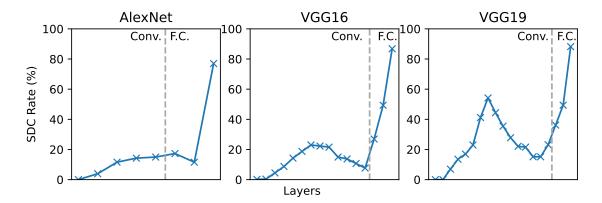

| 2.7                                                                                      | Probability of SDCs of various Layers of Three DNNs at Constant Error Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                             |

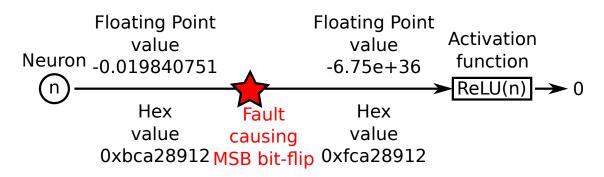

| 2.8                                                                                      | Example of ReLU Masking an Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                             |

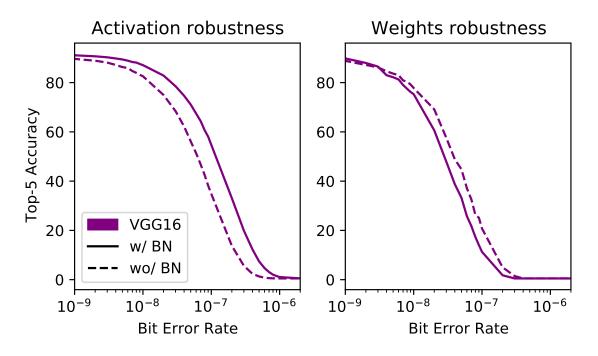

| 2.9                                                                                      | Impact of Batch Normalization on Robustness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                             |

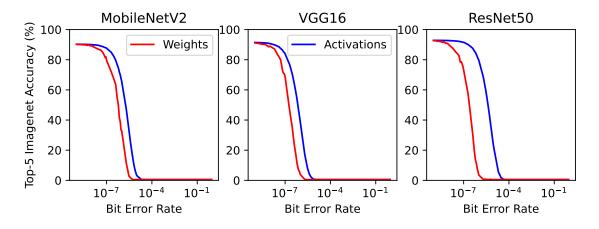

| 2.10                                                                                     | Comparison of the Robustness of Weights and Activations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                             |

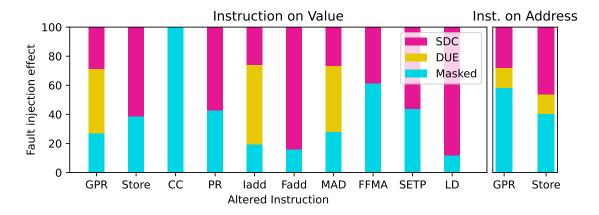

| 2.11                                                                                     | Criticality of Different Instructions of AlexNet on a GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26                                                             |

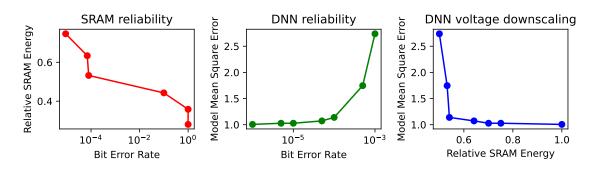

| 2.12                                                                                     | Example of SRAM Cell Voltage Down-Scaling for DNNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                             |

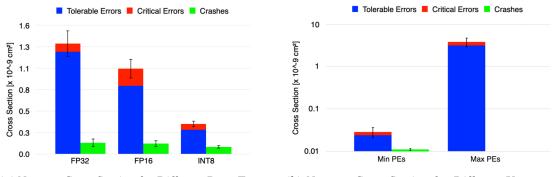

| 2.13                                                                                     | Results of Neutron Beam Experiments on a FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29                                                             |

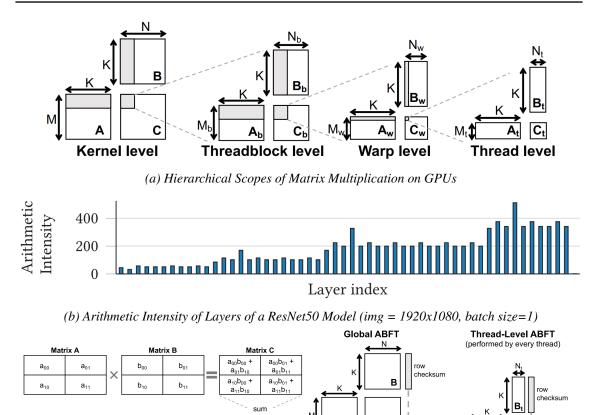

| 2.14                                                                                     | Usage of ABFT on GPU-based DNNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                             |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                             |

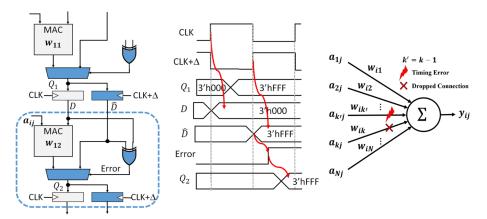

| 2.16                                                                                     | Illustration of Razor Flip-Flop to Detect and Mitigate Timing Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35                                                             |

| 2.17                                                                                     | Masking of Neuron that Exceed a Fault Detection Threshold with Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36                                                             |

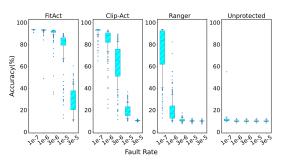

| 2.18                                                                                     | Numerical Range Restriction of Neurons Output to Improve Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 37                                                             |

| 2.19                                                                                     | Summary of the Fault Models in the Literature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                             |

| 2.20                                                                                     | Report of the Number of Articles that Study Specific Parts of DNNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                                             |

| 2.21                                                                                     | Report of the Number of Articles that Employ Specific Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                             |

| 2.22                                                                                     | Report of the Number of Articles that Use Specific Methods to Improve Robustness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                             |

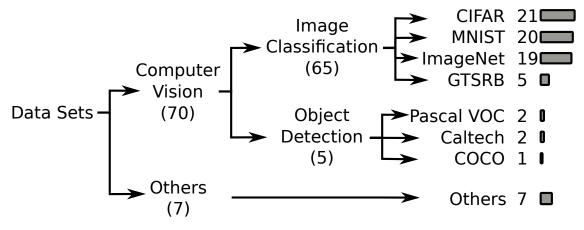

| 2.23                                                                                     | Data Sets Used in the Scientific Literature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                             |

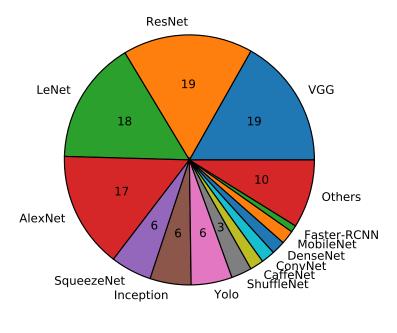

| 2.24                                                                                     | DNNs Topologies Used in the Scientific Literature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                                                             |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |

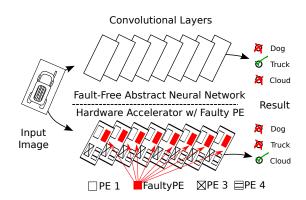

| 3.1                                                                                      | Projection of a Hardware Fault onto the Abstract Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                             |

| 3.2                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                             |

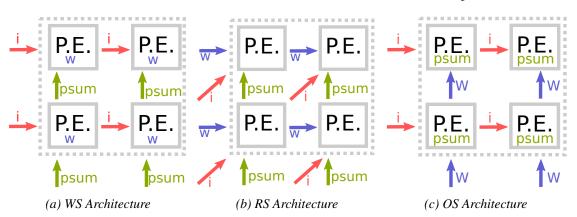

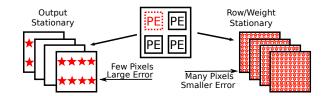

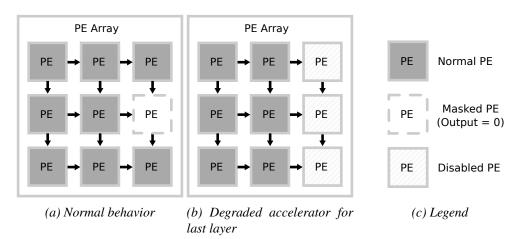

| 3.3                                                                                      | Two Variants of the OS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52<br>53                                                       |

| 3.4                                                                                      | Two Variants of the OS ArchitecturePE Mapping Depending on Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52<br>53<br>54                                                 |

| 3.4<br>3.5                                                                               | Two Variants of the OS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52<br>53<br>54<br>55                                           |

| 3.4<br>3.5<br>3.6                                                                        | Two Variants of the OS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52<br>53<br>54<br>55<br>55                                     |

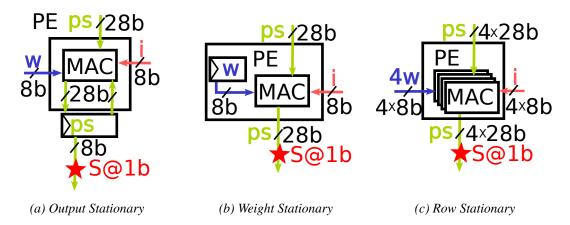

| <ol> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ol>                           | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different Architectures                                                                                                                                                                                                                                                                                                                                                                                                                          | 52<br>53<br>54<br>55<br>55<br>56                               |

| <ol> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ol>              | Two Variants of the OS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52<br>53<br>54<br>55<br>55<br>56<br>57                         |

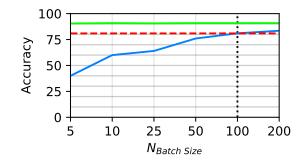

| <ol> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> </ol> | Two Variants of the OS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52<br>53<br>54<br>55<br>55<br>56                               |

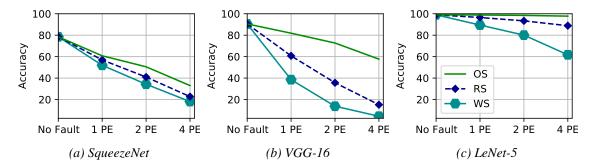

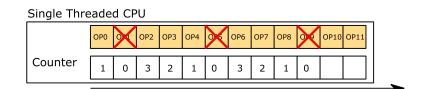

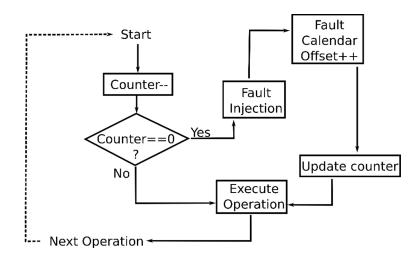

| <ol> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> </ol> | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presence                                                                                                                                                                                                                                                               | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58                   |

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                                           | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PE                                                                                                                                                                                                                                  | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58             |

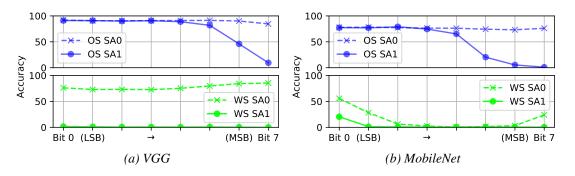

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11                                   | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PEAverage Accuracy versus Faulty Bit Position                                                                                                                                                                                       | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58<br>60       |

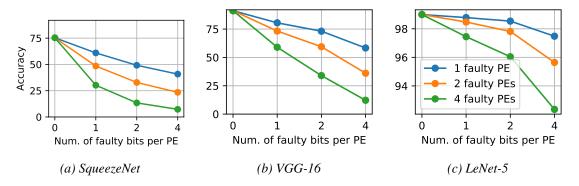

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                           | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesPE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PEAverage Accuracy versus Faulty Bit PositionImpact of Number of Faulty Bits on Three Networks (OS Architecture)                                                                      | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58<br>60<br>60 |

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                           | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesPE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PEAverage Accuracy versus Faulty Bit PositionImpact of Number of Faulty Bits on Three Networks (OS Architecture)                                                                      | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58<br>60       |

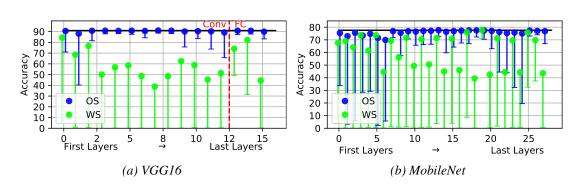

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13                   | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PEAverage Accuracy versus Faulty Bit PositionImpact of Number of Faulty Bits on Three Networks (OS Architecture)Robustness of Various Layer on Tested DNNs                                                                          | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58<br>60<br>60 |

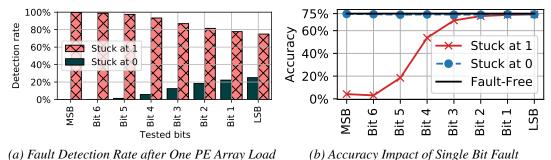

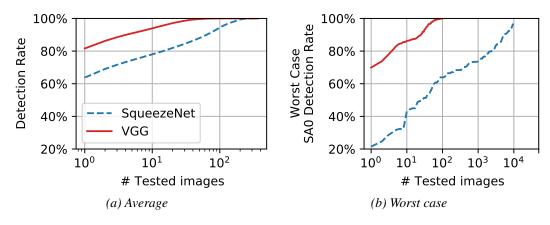

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                           | Two Variants of the OS ArchitecturePE Mapping Depending on ArchitecturePE Fault Models in OS, WS and RS ArchitecturesData Flow Through the PEs for One Output PixelPropagation of a Fault in a PE in Different ArchitecturesVGG-16 Worst Accuracy versus Batch Size - No FaultsFault Injection MethodologyAverage Accuracy of Three Systolic Architectures (OS, RS, WS) in the Presenceof a Single Faulty Bit per PEAverage Accuracy versus Faulty Bit PositionImpact of Number of Faulty Bits on Three Networks (OS Architecture)Robustness of Various Layer on Tested DNNsMOZART+ Provides On-Line Testing and Fault Masking with Graceful Degrada- | 52<br>53<br>54<br>55<br>55<br>56<br>57<br>58<br>58<br>60<br>60 |

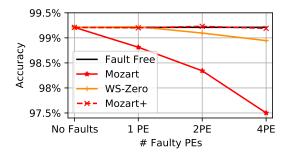

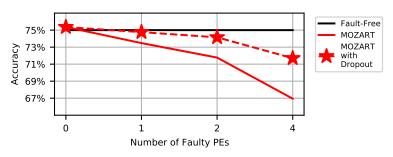

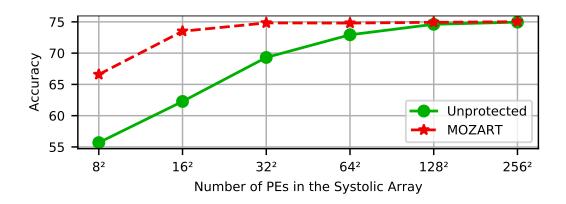

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                               | Schematic of MOZART+Fault Tolerant Scheduling for the Last LayerPE Fault Models in OS, WS and RS ArchitecturesDetection Rate and Accuracy with Single Bit SA Faults on SqueezeNet (OS)Number of Images Required to Detect Latent SA0 FaultsAverage Accuracy with PEs Masked to ZeroFault Tolerance of LeNet-5 with Mozart+ TechniqueSqueezeNet Average Accuracy with Faulty PEs when Trained with DropoutSqueezeNet Average Accuracy for Varying Array Sizes (1 SA fault on 1 PE) | 66<br>67<br>69<br>71<br>71<br>72<br>74<br>74<br>74<br>75        |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

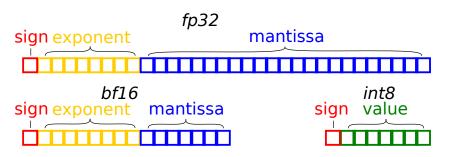

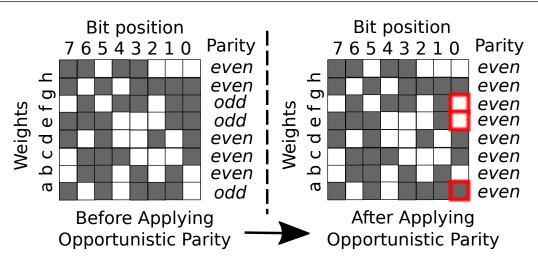

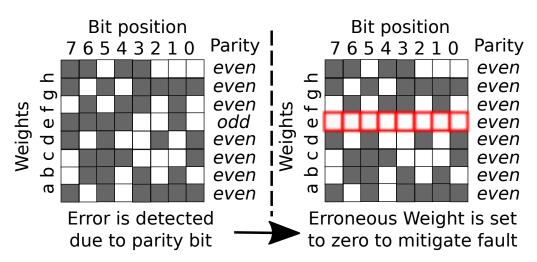

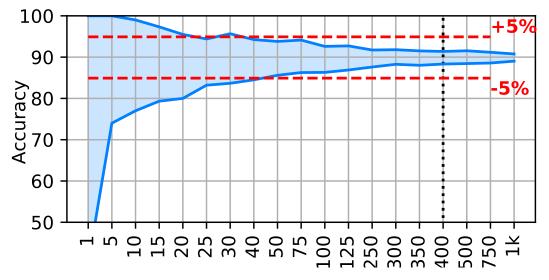

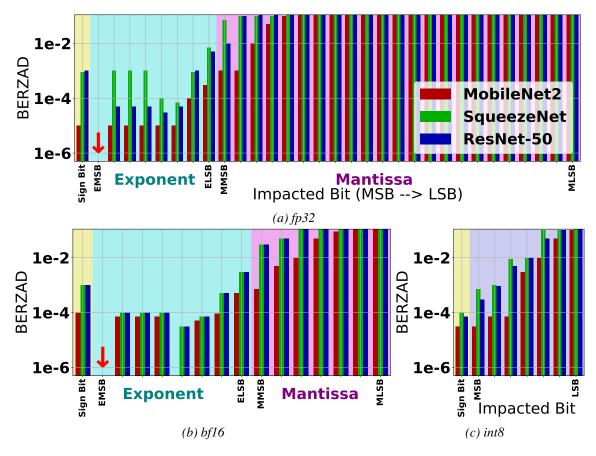

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                                                            | Three Numerical Formats used for CNN Weight ValuesOpportunistic Parity : Altering LSB to Obtain Even ParityOpportunistic Parity : Masking Detected Faults with ZeroRange of Accuracy for a given Batch Size for MobileNetV2 using <i>fp32</i> BERZAD as a Function of Bit Position, for Three Numeric Formats and Three                                                                                                                                                           | 80<br>82<br>82<br>83                                            |

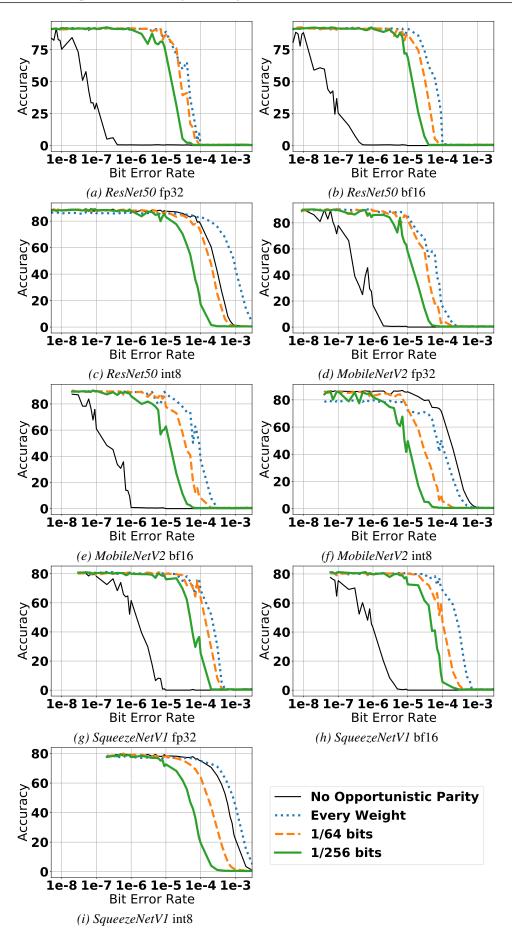

| 5.6                                                                                                        | Networks       Impact of Opportunistic Parity on Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88                                                        |

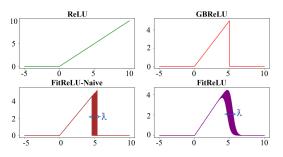

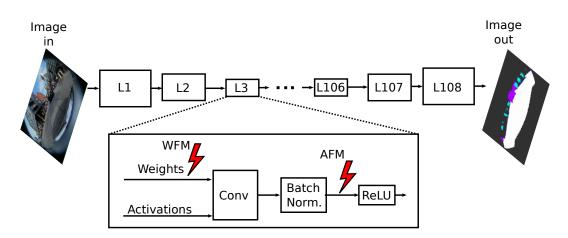

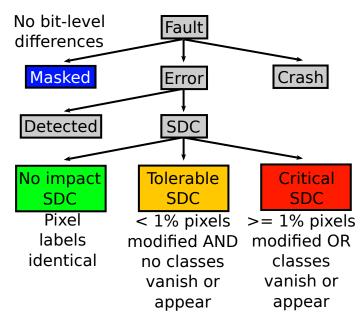

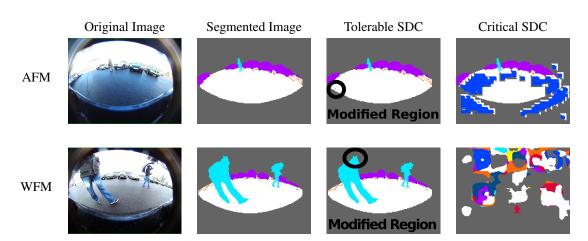

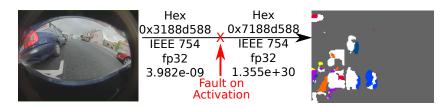

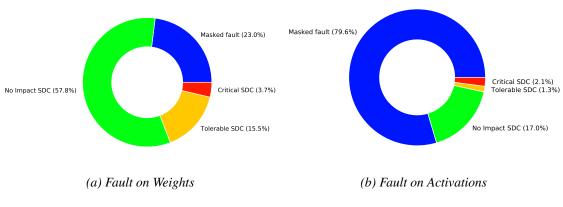

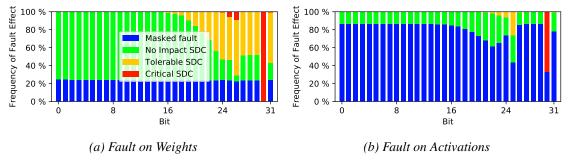

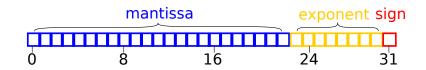

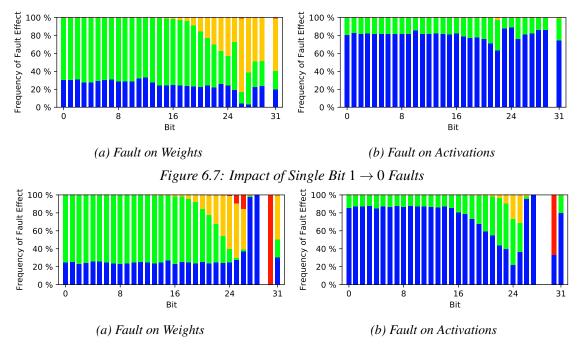

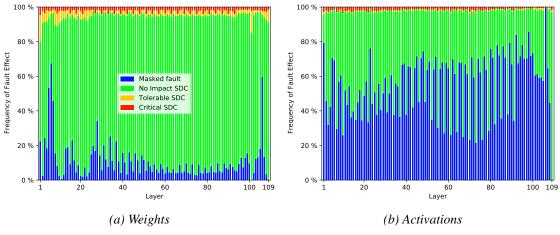

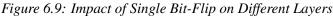

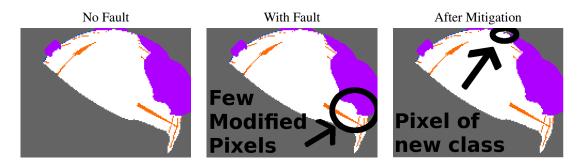

| $\begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9 \\ 6.10 \\ 6.11 \end{array}$ | Faults Model for Weights and Activations                                                                                                                                                                                                                                                                                                                                                                                                                                          | 92<br>93<br>94<br>95<br>95<br>95<br>96<br>96<br>96<br>98<br>100 |

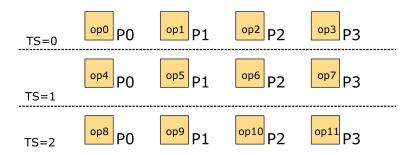

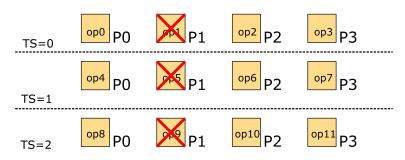

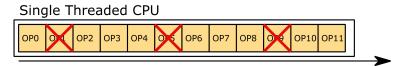

| A.1<br>A.2<br>A.3                                                                                          | Example of Parallel SystemExample of Sequential ExecutionHardware Fault in Parallel System                                                                                                                                                                                                                                                                                                                                                                                        | XVI<br>XVII<br>XVII                                             |

| A.4<br>A.5<br>A.6                                                                                          | Projecting Faults onto Sequential Execution                                                                                                                                                                                                                                                                                                                                                                                                                                       | XVII<br>XVIII<br>XVIII                                          |

## List of Tables

| 2.1 | Activation Functions Used in this Thesis                                | 7    |

|-----|-------------------------------------------------------------------------|------|

| 2.2 | Data Sets Discussed in this Thesis                                      | 9    |

| 2.3 | The Most Considered DNN Models in this Thesis                           | 11   |

| 2.4 | SDC Probability Based on Data Type                                      | 19   |

| 2.5 | Multi-Class Cross Entropy Loss Function                                 | 33   |

| 2.6 | Summary of Hardware Considerations in the Literature                    | 44   |

| 2.7 | Summary of used DNNs and Data-Sets in the Literature                    | 45   |

| 2.8 | Contributions of this Thesis Published in Articles and Patents.         | 48   |

| 3.1 | Parameters for each Fault Injection Campaign                            | 56   |

| 3.2 | Characteristics and Accuracy of Selected Networks                       | 58   |

| 3.3 | Accuracy with Random Stuck-At-0 and Stuck-At-1 Faults in a Single PE    | 59   |

| 4.1 | Characteristics and Accuracy of Selected Networks                       | 68   |

| 4.2 | Percentage of SA1 Faults Detected After N Images                        | 70   |

| 4.3 | Worst Case Accuracy for Batches of 100 Images                           | 73   |

| 4.4 | Number of Loads of a 16x16 OS PE Array for Each Network                 | 74   |

| 5.1 | Characteristics and Accuracy of Selected Networks for ImageNet Data-set | 81   |

| 5.2 | Characteristics and Accuracy of Opportunistic Parity                    | 87   |

| 6.1 | Characteristics of DeepLabV3+                                           | 92   |

| 6.2 | Examples of Tolerable and Critical SDCs                                 | 94   |

| 6.3 | Aggregate Results of Fault Injection (multi-bit fault model)            | 97   |

| 6.4 | Fault Detection Capability with Single Statistic                        | 98   |

| 6.5 | Fault Detection Capability with Two Statistics                          | 99   |

| 6.6 | Fault Mitigation Effect                                                 | 100  |

| A.1 | Initial Fault Calendar for Example                                      | XVII |

- ABFT Algorithm-Based Fault Tolerance. 31, 32, 105

- AFM Activation Fault Model. 92, 94, 96, 98–100

- AI Artificial Intelligence. 3, 6, 10

- ASIC Application-Specific Integrated Circuit. 5, 40, 47

- ASIL-D Automotive Safety Integrity Level D. 65, 91

- AVF Architectural Vulnerability Factor. 46

- AVG AVeraGe. 91, 97, 99, 102

- **BER** Bit Error Rate. 13, 23, 31, 36

- **BERZAD** maximum Bit Error Rate with Zero Accuracy Drop. 84–86

- **bf16** A 16-bit floating point numeric format used in AI accelerators that uses 8 exponent bits and 7 fractional bits. 79, 80, 84, 85, 89

- BIST Built-In Self Test. 66

- **BN** Batch Normalization. 7, 11, 21–23

- **BNN** Binarized Neural Network. 19

- CNN Convolutional Neural Network. 7, 10, 11, 16, 17, 22, 29, 33, 78-82, 89

- CPU Central Processing Unit. 14

- CSDC Critical Silent Data Corruption. 99, 100

- **CSRAM** Configuration Static Random Access Memory, Used to store the configuration in an FPGA. 28, 46

- DMR Dual Modular redundancy. 14, 51, 65

- **DNN** Deep Neural Network. ii, viii, XVI, 3–42, 46–48, 51, 52, 56–58, 60–62, 64–69, 73, 75, 76, 79–81, 86, 87, 90–93, 95, 97, 101, 102, 105, 106

- **DRAM** Dynamic Random Access Memory. 52

- DUE Detected Unrecoverable Error. 13, 26, 27, 93

- ECC Error Correction Code. 13, 14, 26, 86, 87, 106

- **FIT** Failure In Time, 1 FIT corresponds to one failure in 1 billion hours. 65

- **fp32** A 32-bit floating point numeric format defined in IEEE-754. 80, 84–86

- **FPGA** Field-Programmable Gate Array. 5, 12, 15, 19, 25, 28–30, 38, 40, 46, 47, 51, 65, 92

- GPU Graphics Processing Unit. ii, 5, 12, 14, 15, 25–31, 33, 40, 46, 47, 51, 57, 65, 92, 99, 101

int8 8 bits integer numeric format. 84-87, 89

- **IoU** Intersection over Union, A metric used to measure the accuracy in image segmentation and object detection. 8

- LRN Local Response Normalization. 7, 11, 22, 23

- LSB Least Significant Bit. 5, 17, 18, 38, 48, 55, 60, 78, 79, 81, 83–85, 87, 95, 105

- MAC Multiply And Accumulate. 12, 31, 34, 51–55, 57, 68, 80

- MAX MAXimum. 91, 97, 98, 100, 102

- MBU Multiple Bit Upset. 38

- MIN MINimum. 91, 97, 99, 102

- **mIoU** mean Intersection over Union, An average of IoU metric for all the considered labels in image segmentation applications. 9

- ML Machine Learning. 8

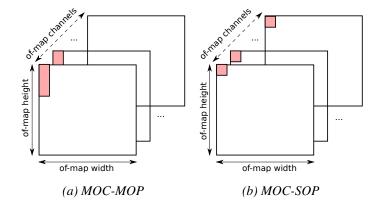

- MOC-MOP Multiple Output Channel-Multiple Output Pixel. 53

- MOC-SOP Multiple Output Channel-Single Output Pixel. 53

- MSB Most Significant Bit. 17, 18, 38, 55, 68, 70, 82, 85, 86, 95

- **OP** Opportunistic Parity. 78, 79, 81–87

- **OS** Output Stationary. iii, iv, 52–56, 59–62, 64–68, 70–74, 105

- PE Processing Element. iii, iv, 12, 39, 51–56, 58–60, 62, 64–76, 105

- **ReLU** Rectified Linear Unit. ii, 17, 21, 23, 36, 101

- **RRAM** Resistive Random Access Memory. 38

- **RS** Row Stationary. 52, 53, 55, 56, 59, 61, 62, 68, 73

- **RTL** Register-Transfer Level. XV

- SA Stuck-At. 60, 62, 68, 70, 72, 75

- SA0 Stuck-At-Zero. 60, 70, 71

- SA1 Stuck-At-One. iv, 60, 70, 75, 76

- SBED Syndrome-Based Error Detection. 32, 33, 35, 36, 48, 91, 97, 98, 101, 105

- **SDC** Silent Data Corruption. ii, 13, 18–20, 26, 27, 32, 36, 46, 93, 97–100, 102

- SEU Single Event Upset. 16

- SIMD Single Instruction Multiple Data. 12, 39, 51, 106

- SoC System on Chip. 5, 28

- SRAM Static Random Access Memory. ii, 15, 25, 27, 28, 30, 37, 46, 51, 52, 92

- STD STandard Deviation. 91, 97, 102

- TMR Triple Modular redundancy. 14, 36, 38

- **TPU** Tensor Processing Unit. 92

- **TSDC** Tolerable Silent Data Corruption. 99, 100

- WFM Weight Fault Model. 92–94, 96, 98, 99

- **WS** Weight Stationary. 52–56, 59, 61, 62, 68, 73, 74

## Contents

|   | Acknowledgments |                                                                               |      |  |  |  |

|---|-----------------|-------------------------------------------------------------------------------|------|--|--|--|

|   | List            | of Figures                                                                    | ii   |  |  |  |

|   | List            | of Tables                                                                     | iv   |  |  |  |

|   |                 | of Terms                                                                      | v    |  |  |  |

|   |                 |                                                                               |      |  |  |  |

|   | Table           | e of Contents                                                                 | viii |  |  |  |

| 1 | Intro           | oduction                                                                      | 2    |  |  |  |

| 2 | Ana             | lysis of DNN Robustness - State of the Art                                    | 4    |  |  |  |

|   | 2.1             | Background                                                                    | 6    |  |  |  |

|   |                 | 2.1.1 Background of DNNs                                                      | 6    |  |  |  |

|   |                 | 2.1.2 Background of DNN Hardware Accelerators                                 | 12   |  |  |  |

|   |                 | 2.1.3 Background on Hardware Failures                                         | 12   |  |  |  |

|   | 2.2             | Understanding the Robustness of DNNs                                          | 15   |  |  |  |

|   |                 | 2.2.1 Robustness of Abstract DNNs                                             | 15   |  |  |  |

|   |                 | 2.2.2 Robustness of DNNs Accelerated on Hardware Platforms                    | 25   |  |  |  |

|   | 2.3             | Improving the robustness of DNNs                                              | 30   |  |  |  |

|   |                 | 2.3.1 Fault Detection Techniques for DNNs                                     | 30   |  |  |  |

|   |                 | 2.3.2 Fault Mitigation Techniques for DNNs                                    | 36   |  |  |  |

|   | 2.4             | Summary of Existing Studies                                                   | 40   |  |  |  |

|   |                 | 2.4.1 Hardware Targets and Fault Models                                       | 40   |  |  |  |

|   |                 | 2.4.2 Fault Tolerance of DNNs                                                 | 41   |  |  |  |

|   |                 | 2.4.3 Data-sets and DNN Topologies                                            | 42   |  |  |  |

|   |                 | 2.4.4 Summary Table                                                           | 42   |  |  |  |

|   | 2.5             | Conclusions on the State Of The Art of Robustness of DNNs to Hardware Faults  | 46   |  |  |  |

|   | 2.6             | Contributions of the Thesis                                                   | 47   |  |  |  |

| 3 | Rob             | ustness of Deep Neural Network Systolic Accelerators                          | 50   |  |  |  |

|   | 3.1             | Hardware Architectures                                                        | 52   |  |  |  |

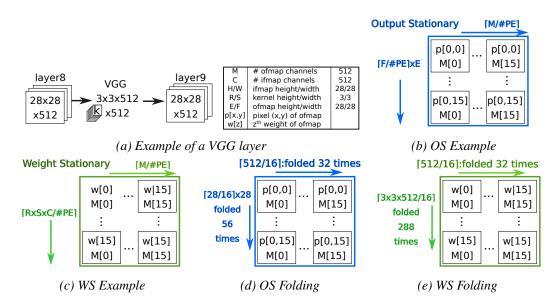

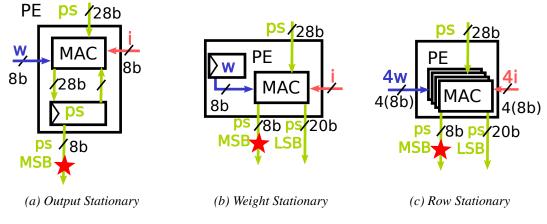

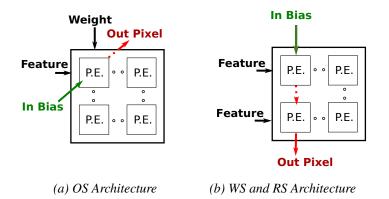

|   |                 | 3.1.1 Systolic DNN Accelerator Architectures                                  | 52   |  |  |  |

|   |                 | 3.1.2 Folding                                                                 | 53   |  |  |  |

|   | 3.2             | Fault Injection Methodology                                                   | 54   |  |  |  |

|   |                 | 3.2.1 Hardware Fault Abstraction                                              | 54   |  |  |  |

|   |                 | 3.2.2 Impact of Computational Errors in Systolic Architectures                | 55   |  |  |  |

|   |                 | 3.2.3 Analyzing the Errors Produced by Faults                                 | 56   |  |  |  |

|   | 3.3             | Fault Injection Results                                                       | 57   |  |  |  |

|   |                 | 3.3.1 Experimental Framework                                                  | 57   |  |  |  |

|   |                 | 3.3.2 Impact of the Architecture on the Robustness of Accelerator to Computa- |      |  |  |  |

|   |                 | tional Faults                                                                 | 58   |  |  |  |

|   |                 | 3.3.3 Impact of PE Array Size on Robustness                                   | 59   |  |  |  |

|   |                 | 3.3.4 Bit-Level Analysis of the Effect of Faults                              | 60   |  |  |  |

|   |                 | -                                                                             |      |  |  |  |

|   |      | 3.3.5 Impact of Faults by Layer                                              | 61 |

|---|------|------------------------------------------------------------------------------|----|

|   | 3.4  | Comparison with State of the Art                                             | 61 |

|   | 3.5  | Future Developments                                                          | 62 |

|   | 3.6  | Conclusions of the Analysis of Fault Tolerance of Systolic Accelerators      | 62 |

| 4 | Desi | gn of a Fault Tolerant Systolic Accelerator                                  | 64 |

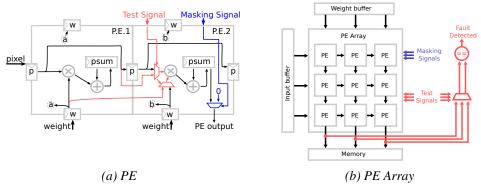

|   | 4.1  | MOZART+ Architecture                                                         | 66 |

|   |      | 4.1.1 Fault Detection and Mitigation with MOZART+                            | 66 |

|   |      | 4.1.2 Unaware Fault-Tolerant Training for Improving Tolerance to Hard Errors | 67 |

|   |      | 4.1.3 Fault Tolerant Scheduling for the Last Layer                           | 67 |

|   | 4.2  | Mozart Evaluation                                                            | 68 |

|   |      | 4.2.1 Applications and Data-Sets                                             | 68 |

|   |      | 4.2.2 Hardware Fault Model                                                   | 68 |

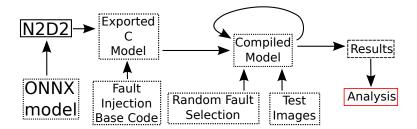

|   |      | 4.2.3 Fault Injection Methodology                                            | 69 |

|   | 4.3  | Fault Injection Results                                                      | 70 |

|   |      | 4.3.1 Effectiveness of On-Line Test                                          | 70 |

|   |      | 4.3.2 Fault Tolerance in MOZART Architecture                                 | 71 |

|   |      | 4.3.3 Efficiency of the Fault Tolerant Scheduling                            | 73 |

|   |      | 4.3.4 Efficiency of Dropout During Training                                  | 74 |

|   |      | 4.3.5 Scalability of MOZART+ on Bigger PE Array                              | 75 |

|   | 4.4  | Comparison with the State of the Art                                         | 75 |

|   | 4.5  | Future Work                                                                  | 76 |

|   | 4.6  | Conclusions of the Design of MOZART+                                         | 76 |

| 5 | Tech | nniques for Protecting the Weights of DNNs                                   | 78 |

|   | 5.1  | Context                                                                      | 79 |

|   |      | 5.1.1 Case Study                                                             | 79 |

|   |      | 5.1.2 Fault Model                                                            | 81 |

|   | 5.2  | Opportunistic Parity                                                         | 81 |

|   |      | 5.2.1 Zero Masking Technique                                                 | 82 |

|   |      | 5.2.2 Bit-Width of Opportunistic Parity                                      | 83 |

|   |      | 5.2.3 Methodology of analysis                                                | 83 |

|   |      | 5.2.4 Methodology of fault injection                                         | 84 |

|   | 5.3  |                                                                              | 84 |

|   |      | 5.3.1 Analysis of DNNs Sensitivity by Bit Position                           | 85 |

|   |      | 5.3.2 Analysis of the Opportunistic Parity Technique                         | 86 |

|   | 5.4  | Comparison with the State of the Art                                         | 86 |

|   | 5.5  | Suggested Improvements                                                       | 87 |

|   | 5.6  | Conclusion of the Opportunistic Parity                                       | 89 |

| 6 | Sym  | ptom Based Error Detection                                                   | 90 |

|   | 6.1  | Context                                                                      | 91 |

|   |      | 6.1.1 Semantic Segmentation and WoodScape                                    | 91 |

|   |      | 6.1.2 Fault Model                                                            | 92 |

|   |      | 6.1.3 Error Taxonomy                                                         | 93 |

|   | 6.2  | Fault Injection Methodology                                                  | 94 |

|   |      | 6.2.1 Impact of Single Bit-Flip                                              | 94 |

|   |      | 6.2.2 Impact of Multiple Bit-Flip                                            | 97 |

|   | 6.3  | Symptom Based Error Detection Technique                                      | 97 |

|   |      | 6.3.1 Single Statistic Approach                                              | 97 |

|   |      | 6.3.2 Double Statistic Approach                                              | 99 |

|   |      | 6.3.3 Implementation and Overhead                                            | 99 |

|    | 6.4<br>6.5<br>6.6<br>6.7 | Fault Mitigation                                                                                                                                       | 101<br>101 |

|----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7  | Con                      | clusions                                                                                                                                               | 104        |

| Bi | bliogr                   | aphy                                                                                                                                                   | Ι          |

| A  | A.1<br>A.2               | endix : Fault Calendar         Introduction         A.1.1         Scientific Background         Fault Calendar         Patenting of the Fault Calendar | XVI        |

# Introduction

Deep Neural Networks are the current cornerstone of various modern artificial intelligence applications [LeCun2015]. The growing number of these applications is due to the breakthroughs they have achieved in diverse fields [Otter2021, Feng2019], where Deep Neural Networks may exceed human accuracy. Safety-critical applications are no exception. In these applications, the system must be resilient to unexpected events, such as hardware faults. This chapter introduces the context of the thesis and the need for designing robust Deep Neural Networks. Deep Neural Network (DNN)s are used in many modern Artificial Intelligence (AI) applications [LeCun2015]. Due to the breakthroughs that DNNs have achieved in natural language processing [Deng2013, Collobert2008] and image recognition [Krizhevsky2012], the number of applications employing DNNs has exploded.

The study of the tolerance of DNNs to hardware failures is important for many reasons. DNNs are already being deployed in critical tasks, where a failure of the system can result in significant physical harm or financial liability. It is estimated that 25% of passenger car miles will be driven by autonomous robotaxis by 2042 and their autonomous driving compute systems will employ multiple DNNs [IDTechEx2022]. It is imperative to ensure that hardware faults in these systems do not result in incorrect decisions, as human safety is at risk. We also note that DNNs are being employed in medical diagnostics [Ronneberger2015], another application where human lives could be impacted by erroneous computations. Even military equipment, such as missiles, are now employing DNN technology [He2021]; a domain where an incorrect result could be catastrophic.

Although neural networks continue to gain in accuracy for many applications, this comes at the cost of a huge number of computations, and thus high power consumption. One of the promising approaches to reduce power, is to operate the compute system at lower voltage [Wu2021a, Yang2017], however, this tends to introduce more faults as the circuit is operating with tighter margins. If DNNs can be made tolerant to hardware faults with minimal cost, low-voltage operation remains a promising path for reducing energy consumption, despite the higher rate of faults. Post-CMOS process technologies (e.g. [Hills2014]) are promising option for future NN accelerators, but as they are known to prone to faults, the system must be designed accordingly.

Sometimes, it is believed that DNNs are intrinsically fault tolerant – as the algorithms are bioinspired. As will be seen in this thesis, the reality is more complex. Many hardware faults have no impact, but there exist critical faults which can cause a DNN to degenerate to random guessing. Understanding and identifying these critical faults is one of the focuses of this thesis.

In industry today, when DNN accelerators must be fault tolerant, such as in existing assisted and autonomous driving systems, manufacturers rely on hardware redundancy. For example, cars manufactured by Tesla incorporate two fully independent Fully Self Driving (FSD) chips along with their own power subsystem, DRAM, and flash memory for redundancy. Each chip boots up from its own storage memory and runs its own independent operating system. These chips are part of a safety system that incorporates dual-core lockstep [Talpes2020]. This is clearly a costly approach to achieve high-reliability - particularly when we consider that neural networks never achieve 100% accuracy, even in the absence of faults. Redundancy based approaches are clearly incompatible with low-power operation.

The goal of this thesis is to provide new insights into how faults alter the behavior of DNNs and to propose new, low-cost and innovative means to improve their robustness.

This thesis is structured as follows :

- Chapter 2 provides an overview of the current scientific literature in the field of DNN fault tolerance, and also gives the necessary background to help understand this thesis.

- Chapter 3 presents a study of the impact of faults in different DNN systolic accelerators.

- Chapter 4 covers a new systolic accelerator specifically designed for fault tolerance.

- Chapter 5 presents a method to protect the contents of weight storage memory with no storage overhead.

- Chapter 6 describes a statistical technique to detect faults occurring in a DNN by monitoring its data-flow.

- Chapter 7 concludes this manuscript and presents ideas for future work.

## 2

## Analysis of DNN Robustness - State of the Art

Deep Neural Networks have been widely deployed as they are able to automate and to exceed human capabilities in many important tasks. They are frequently deployed in safety critical systems, where hardware fault tolerance is important. This chapter presents an overview of the existing works on the reliability of Deep Neural Networks hardware accelerators.

#### Contents

| 2.1 | Backg  | round                                                            | 6  |

|-----|--------|------------------------------------------------------------------|----|

|     | 2.1.1  | Background of DNNs                                               | 6  |

|     | 2.1.2  | Background of DNN Hardware Accelerators                          | 12 |

|     | 2.1.3  | Background on Hardware Failures                                  | 12 |

| 2.2 | Under  | standing the Robustness of DNNs                                  | 15 |

|     | 2.2.1  | Robustness of Abstract DNNs                                      | 15 |

|     | 2.2.2  | Robustness of DNNs Accelerated on Hardware Platforms             | 25 |

| 2.3 | Impro  | ving the robustness of DNNs                                      | 30 |

|     | 2.3.1  | Fault Detection Techniques for DNNs                              | 30 |

|     | 2.3.2  | Fault Mitigation Techniques for DNNs                             | 36 |

| 2.4 | Summ   | ary of Existing Studies                                          | 40 |

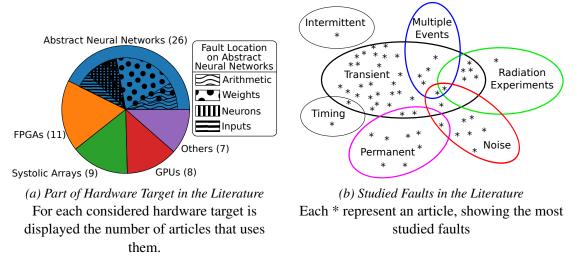

|     | 2.4.1  | Hardware Targets and Fault Models                                | 40 |

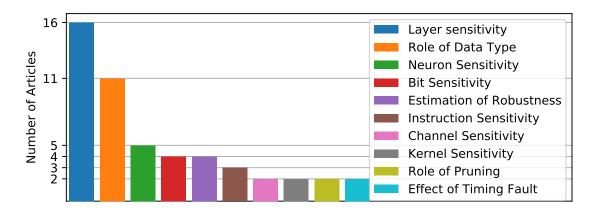

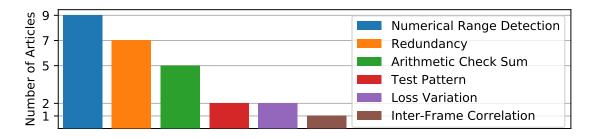

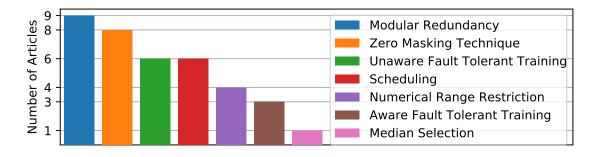

|     | 2.4.2  | Fault Tolerance of DNNs                                          | 41 |

|     | 2.4.3  | Data-sets and DNN Topologies                                     | 42 |

|     | 2.4.4  | Summary Table                                                    | 42 |

| 2.5 | Concl  | usions on the State Of The Art of Robustness of DNNs to Hardware |    |

|     | Faults | •••••••••••••••••                                                | 46 |

| 2.6 | Contr  | ibutions of the Thesis                                           | 47 |

Deep Neural Network (DNN)s have specificities that must be taken into consideration when studying their fault tolerance. For example, the accuracy of DNNs is never perfect, even in the absence of faults, and a certain level of inaccuracy is usually acceptable [LeCun2015]. Furthermore, due to their structure, DNNs have intrinsic redundancy [Yvinec2021] and their activation functions, for example, are able to mask certain errors [Hoang2020]. These particularities of DNNs make them different from traditional computer systems, in terms of their robustness.

However, many other parameters associated with a DNN must be considered. Not only activation functions, but also pooling layers, normalization layers [Li2017] and also the nature of computing layers plays a role in the robustness of a DNN [Xu2019]. Even the training process can alter the fault tolerance capability of a DNN [Zhang2019]. Computational optimizations and the choice of data-type can impact the fault tolerance of a DNN. Another example is the quantization of a DNN, that can improve its robustness by several orders of magnitude [Gambardella2019]. Looking at all these parameters, it becomes obvious that evaluating the fault tolerance of DNNs is a complex task. In the same time, the overall reliability of a system depends on the hardware platforms and the executed application.

To avoid dealing with the underlying hardware platform, some authors considers abstract DNN, and study the fault tolerance of DNNs without considering the complexities of the hardware platform.

Publications on DNN fault tolerance focus on specific hardware platforms, such as Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs) [Reuther2021], each of them having their specific failure modes when executing DNNs.

The special characteristics of DNNs can be exploited to provide low-cost fault tolerance. As an example, techniques such as redundancy currently used in state-of-the-art automotive System on Chip (SoC) solutions [Talpes2020, Matsubara2021] protect all data bits, whereas DNNs are highly tolerant of faults in their Least Significant Bits (LSBs) [Malekzadeh2021].

The scientific literature on the fault tolerance of DNNs is vast. Three survey articles have recently been published [Torres-Huitzil2017, Ibrahim2020, Mittal2020]. These surveys provide an overview of the works in this field of research.

This chapter presents a concise review of the existing state of the art. The remainder of this chapter is organized as follows :

- Sec.2.1 presents the background for understanding this thesis.

- Sec.2.2 presents existing works that analyze the robustness of DNNs.

- Sec.2.3 presents existing techniques to improve the robustness of DNNs.

- Sec.2.4 quantitatively identifies the current focus of the scientific literature in terms of case studies, hardware platforms, fault models, and fault detection and mitigation.

- Sec.2.6 situates the contributions of this thesis relative to the existing works.

- Sec.2.5 concludes this chapter.

#### 2.1 Background

This section presents background material that is helpful for understanding this thesis, and is structured as follows : Sec.2.1.1 presents the background on DNNs. Sec.2.1.2 presents the background on DNN hardware accelerators. Sec.2.1.3 presents the background on hardware faults.

#### 2.1.1 Background of DNNs

#### Artificial Intelligence and DNNs

The field of Artificial Intelligence (AI) is wide and covers many different fields of study. The term AI was coined by John McCarthy, as "the science of creating machines that have ability to achieve goals like human do" [McCarthy2006].

Machine Learning is a sub-field of AI that has recently stimulated scientific interest, and was coined by Arthur Samuel as "the ability for a computer to learn to perform better at a task than the person who programmed the computer" [Samuel1959]. Recent breakthroughs have been made possible by another sub-field of Machine Learning, DNNs.

#### **Artificial Neuron**

Artificial neural networks are mathematical models that are inspired from the study of biological neural networks. Biological neurons are excited by stimuli from other neurons via theirs synapses. When this excitation reaches a threshold, a biological neuron emits a spike that reaches other neurons via other synapses. In artificial neural networks, a neuron computes a weighted sum of its inputs synapses, performs a non-linear function on the result, and then this result, called an activation, is passed to other neurons, as illustrated in Fig. 2.1.

x,w,b,f,y are respectively inputs, weights, bias, activation function and activation value

Figure 2.1: Artificial Neuron

#### Activation function

A non-linear activation function at the output of neurons is essential for the learning process, and required to build multi-layer networks. Many activation functions exist, but in this thesis, we only use the ones summarized in Tab.2.1. In the subsequent sections, the output of the activation function will be referred as an activation.

#### **Different layers**

A DNN consists of layers, and all the neurons in a given layer are evaluated simultaneously. The layers can have different topologies and the most discussed in this thesis are the following :

• **Fully connected** topology implies that every neurons in the current layer propagates its activation to every neurons in the subsequent layer. This structure is typically found in the last layers of a classification DNN.

• **Convolutional layer** implies that a group of neurons in that layer (typically a small 3x3 or 5x5 region) is connected, via a shared set of weights, to the neurons in the next layer. This set of weights is called a kernel. In terms of implementation, convolutional layers require fewer weights, because the same kernel pattern is shared between neurons.

| Name    | Function                                                                 | Derivative                                                             | Range        |

|---------|--------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|

| Sigmoid | $\frac{1}{1+e^{-x}}$                                                     | g(x)(1-g(x))                                                           | (0,1)        |

| ReLU    | $\begin{cases} 0 \text{ if } x \le 0\\ x \text{ if } x > 0 \end{cases}$  | $\begin{cases} 0 \text{ if } x < 0 \\ 1 \text{ if } x > 0 \end{cases}$ | $[0,\infty)$ |

|         | , , , , , , , , , , , , , , , , , , ,                                    | undefined if $x = 0$                                                   |              |

| ReLU6   | $\begin{cases} 0 \text{ if } x \le 0 \\ x \text{ if } x > 0 \end{cases}$ | $\begin{cases} 0 \text{ if } x < 0 \\ 1 \text{ if } x > 0 \end{cases}$ | [0, 6]       |

|         | $6$ if $x \ge 0$                                                         | undefined if $x = 0$                                                   |              |

Table 2.1: Activation Functions Used in this Thesis

#### **Pooling Layers**

Convolutional Neural Networks(CNNs) can include pooling layers along with convolutional layers. Pooling layers reduce the dimensions (height and width) of the layer by combining a cluster of neurons in one layer into a single neuron in the next layer. Pooling layers are typically used to combine small windows of  $2 \times 2$  neurons. Two pooling layer are frequently used :

- Max Pooling forwards the maximum value of each local cluster of neurons to the next layer.

- Average Pooling forwards the average value of the local cluster of neurons to the next layer.

#### **Normalization layers**

During training, the distribution of values in each layer changes when the weights of the previous layers are altered. This significantly slows the training by requiring lower learning rate and makes the training of networks with many layers difficult.

This phenomenon, coined as internal covariate shift by [Ioffe2015], is addressed with Batch Normalization, which is a trainable layer typically used after each convolutional layer which normalize the values of all neurons in a layer for each training mini-batch. As a result, Batch Normalization (BN) allows to use significantly higher learning rate thus improving the training time, and facilitating the training of deep networks. Consequently, BN is generally used in state of the art DNNs [Howard2019].

During the inference process, the trainable parameters of the BN layers are frozen. At this point, BN is simply a linear transformation of activations and hence can be merged with the previous convolutions.

Another normalization layer, the Local Response Normalization (LRN) is a layer that behaves like the Average Pooling layer by normalizing several locally neighbors neurons. Instead of average pooling layers, LRN layers are not used to change the shape of a layer and usually compute an average of neighboring pixels on the three axis (X, Y, Z) of the input layer. While no longer used in recent DNNs, some of the networks that are studied in this thesis have this type layer.

#### Training

As with all Machine Learning algorithms, DNNs are trained from input data. Various types of learning exist such as reinforcement learning that trains a DNN in an environment in order to maximize the cumulative reward, or unsupervised learning that learns patterns from unlabeled data. In this document, we mainly consider supervised learning.

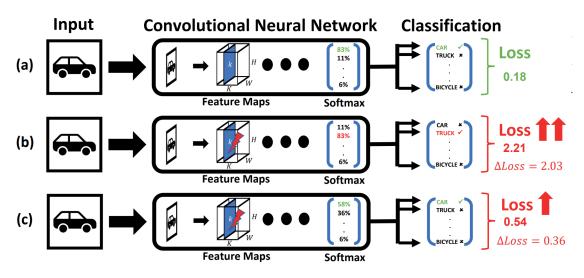

In supervised learning, to each data is assigned a value (single or set of label or continuous value). The behavior of the network is evaluated through a cost function that compares the expected behavior for the input data and the actual behavior of the network. The value of the cost function is called the loss.

The training process alters the weights and biases of the network in order to reduce the loss.

During training, the weights are updated with the gradient descent process. After each iteration of the training process, each weight is updated with gradient descent depending on its partial derivative of the loss. As the iterations of training progress, the loss should be reduced and the network should converge.

After the network is trained, its weights are frozen and it can be deployed to analyze data that has not been used during training. If the training was effective, the DNN will behave as expected on these new data. This is called the inference.

#### Dropout

Dropout is a generalized technique performed during the training of state-of-the-art classification DNNs as it improves the overall accuracy by reducing over-fitting [Srivastava2014].

Dropout is applied on certain layers, typically the last layers of a DNN. For each training iteration, a predefined fraction of the neurons are randomly disconnected from the learning process. During the forward pass, the outputs of these neurons are set to 0. During the backward pass, the weights of these neurons are not modified. At the next training iteration, the neurons are reconnected, and new neurons are randomly selected for the Dropout process.

#### **Data-sets**

The data-sets used to train DNNs used in this thesis are presented in the following and cover three types of tasks :

- **Image classification** relies on data-sets where a label is attributed for each input image. For example, the ImageNet dataset contains images of different classes of objects, such as, for example, teapots. In a DNN trained for classification, a label is associated with each output neuron. For each prediction, each neuron outputs the probability for the input image to be related to its assigned label. The networks accuracy is evaluated based on its ability to assign labels to images that the DNN has not processed during training. Two metrics are used to compute the accuracy of the DNNs in this thesis.

- **Top-1**, where the neuron with the highest probability is considered to be the prediction of the model.