### A semantic approach to machine-level software security Georges-Axel Jaloyan

### ▶ To cite this version:

Georges-Axel Jaloyan. A semantic approach to machine-level software security. Cryptography and Security [cs.CR]. Université Paris sciences et lettres, 2021. English. NNT: 2021UPSLE062 . tel-04023324

### HAL Id: tel-04023324 https://theses.hal.science/tel-04023324v1

Submitted on 10 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

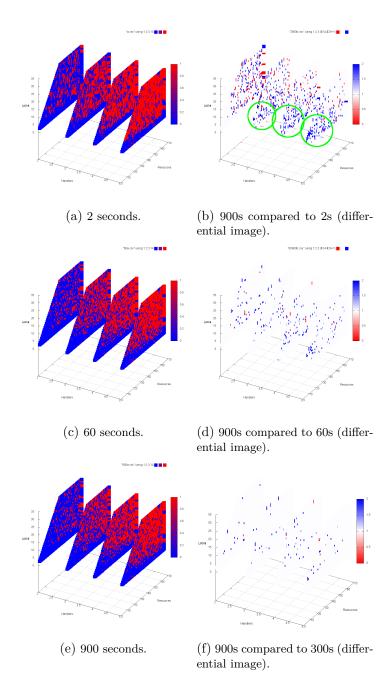

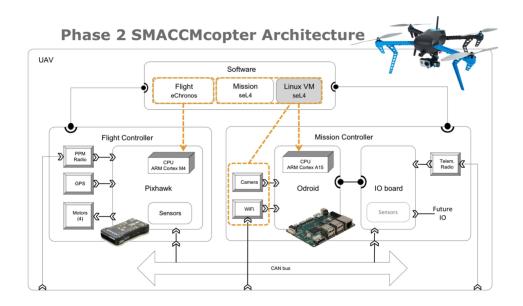

## THÈSE DE DOCTORAT DE L'UNIVERSITÉ PSL

Préparée à l'École normale supérieure

## A Semantic Approach to Machine-Level Software Security

### Soutenue par Georges-Axel JALOYAN

Le 14 septembre 2021

### École doctorale nº386

Sciences Mathématiques de Paris Centre

# Spécialité

Informatique

### Composition du jury :

| Xavier RIVAL<br>Inria – École normale supérieure                                     | Président du jury  |

|--------------------------------------------------------------------------------------|--------------------|

| Lorenzo CAVALLARO<br>University College London                                       | Rapporteur         |

| Sylvain GUILLEY<br>Télécom ParisTech                                                 | Rapporteur         |

| Whitfield DIFFIE<br>Stanford University                                              | Examinateur        |

| Konstantinos MARKANTONAKIS<br>Royal Holloway University of London                    | Examinateur        |

| Clémentine MAURICE<br>Centre national de la<br>recherche scientifique                | Examinatrice       |

| Aymeric VINCENT<br>Commissariat à l'énergie atomique<br>et aux énergies alternatives | Encadrant de thèse |

| David NACCACHE<br>École normale supérieure                                           | Directeur de thèse |

| Hovav SHACHAM<br>University of Texas at Austin                                       | Professeur invité  |

|                                                                                      |                    |

# Résumé

L'informatique se fonde sur de nombreuses couches d'abstraction, allant des couches matérielles jusqu'à l'algorithmique en passant par le cahier des charges à la base de la conception du produit. Dans le cadre de la sécurité informatique, les vulnérabilités proviennent souvent de la confusion résultant des différentes abstractions décrivant un même objet. La définition de sémantiques aide à la description formelle de ces abstractions dans l'objectif de les faire coïncider. Dans cette thèse, nous améliorons différents procédés ou programmes en corrélant les diverses représentations sémantiques sousjacentes.

Nous introduisons brièvement les termes et concepts fondamentaux avec lesquels nous construisons le concept de langage assembleur ainsi que les différentes abstractions utilisées dans l'exploitation de programmes binaires.

Dans une première partie, nous utilisons des constructions sémantiques de haut niveau pour simplifier la conception de codes d'exploitation avancés sur des jeux d'instructions récents. Nous présentons didactiquement trois exemples répondant à des contraintes de plus en plus complexes. Spécifiquement, nous présentons une méthode pour produire des shellcodes alphanumériques sur ARMv8-A et RISC-V, ainsi que la première analyse de faisabilité d'attaques de type return-oriented programming sur RISC-V.

Dans une deuxième partie, nous étudions l'application des méthodes formelles à l'amélioration de la sécurité et de la sûreté de langages de programmation à travers trois exemples : une optimisation de primitives de synchronisation, une analyse statique compatible avec la vérification déductive limitant l'aliasing de pointeurs dans un langage impératif ou encore un formalisme permettant de représenter de façon compacte du code binaire dans le but d'analyser des problèmes de synchronisation de protocole. ii

# Abstract

Computer science is built on many layers of abstraction, from hardware to algorithms or statements of work. In the context of computer security, vulnerabilities often originate from the discrepancies between these different abstraction levels. Such inconsistencies may lead to cyberattacks incurring losses. As a remedy, providing semantics helps formally describe and close the gap between these layers. In this thesis, we improve methods and programs by connecting the various semantic representations involved using their relationship to each level of abstraction.

We briefly introduce the fundamental concepts and terminology to build assembly languages from scratch and various abstractions built atop and used in the context of binary exploitation.

In the first part, we leverage higher-level semantic constructs to reduce the design complexity of advanced exploits on several recent instruction set architectures. In a tutorial-like fashion, we present three examples addressing increasingly more complex constraints. Specifically, we describe a methodology to automatically turn arbitrary programs into alphanumeric shellcodes on ARMv8-A and on RISC-V. We also provide the first analysis on the feasibility of return-oriented programming attacks on RISC-V.

In the second part, we see how the use of formal methods can improve the safety and security of various languages or constructs, through three examples that respectively optimize the implementation of Hoare monitors, a well-known synchronization construct, prevent harmful aliasing in an imperative language without impeding deductive verification, or abstract binary code into a compact representation which enables further protocol desynchronization analyses. iv

# Foreword

Man hitherto has been prevented from realizing his hopes by ignorance as to means. As this ignorance disappears he becomes increasingly able to mould his physical environment, his social milieu and himself into the forms which he deems best. In so far as he is wise this new power is beneficent; in so far as he is foolish it is quite the reverse. If, therefore, a scientific civilization is to be a good civilization it is necessary that increase in knowledge should be accompanied by increase in wisdom.

Bertrand Russell, The Scientific Outlook, 1931

This thesis aims at bringing closer formal methods and computer security, by showing, through practical examples, the techniques that could be leveraged to either improve or exploit various products or platforms.

These four years of research have convinced me that computer security requires a rigorous and empirical approach combining both a thorough understanding of the implementation details as well as grasping the underlying abstract ideas. Any misunderstanding may lead to a vulnerability. Inasmuch as cyberattacks can cause disproportionate damage, computer security is, at its heart, the playground of nitpickers.

Formal methods, on the other end of the spectrum, are historically linked to safety-critical systems, and were only loosely related to security. Recent efforts aiming at forgathering hackers and formal method experts allowed mixed approaches to gain momentum, the example of the 2016 DARPA Cyber Grand Challenge at DEF CON 24 being the most emblematic. This evolution is likely to continue, as formal methods are reaching maturity, with the latest tools improving on scalability, ease-of-use and versatility.

At the beginning of this thesis I used to think that formal methods were just the dual of computer security; the first well suited for defense while the second excels in attacks. Looking back, this proved quite inaccurate as both provide attack and defense mechanisms. In fact, formal methods bridge the gap between a program and its model, through a systematic formally rigorous study of the program's meaning, its *semantics*. Each chapter of this manuscript presents an example of this approach, by means of an extended version of peer-reviewed articles. vi

# Remerciements / Acknowledgments

Il me serait difficile de commencer cette thèse sans constater le nombre important de personnes qui y concoururent. Combien de professeurs, combien de membres de famille, combien d'amis, combien de recontres fortuites, combien d'anonymes partageant une bribe de leur savoir, me permirent de faire ma thèse au sein de deux des plus prestigieuses institutions de la Nation : l'École normale supérieure de la rue d'Ulm, et la Direction des applications militaires du Commissariat à l'énergie atomique et aux énergies alternatives. Jouir d'un tel cadre est une chance et un privilège. Les remerciements subséquents expriment ma gratitude envers les principales personnes et institutions qui m'ont tantôt tiré, tantôt poussé pour m'amener là où je suis aujourd'hui. J'en oublie certainement, souvent anonymes, qui ont permis à cette thèse d'aboutir ; je les remercie donc collectivement.

Ces remerciements commencent par mon directeur David Naccache, qui a placé sa totale confiance en moi dès le premier jour. Cela a commencé à ton cours d'informatique scientifique par la pratique, et cette confiance a perduré jusqu'à ce jour. Tu plaisantais en me disant au début de la thèse que trois ans, c'est bien plus long que certains couples. Cela fait sept ans que tu as été successivement mon professeur, tuteur académique et directeur de thèse, et la joie de travailler avec toi reste entière. Je te dois énormément pour tout ce que tu m'as appris, toutes les fois où tu m'as évité les ennuis, et cette ambiance de travail géniale au sein de l'équipe. Les locaux ne sont pas étrangers à cette ambiance ; l'École normale, par son emplacement, son histoire, ses personnels, ses chercheurs et ses élèves fournit un environnement exceptionnel stimulant la créativité de ceux qui le fréquentent. Je ne pouvais pas trouver meilleur endroit pour faire ma thèse, et remercie David Pointcheval, le directeur du Département d'informatique pour m'avoir hébergé dans ses locaux.

La deuxième personne à qui je dois énormément est mon encadrant de thèse, Aymeric Vincent, qui m'a abreuvé durant ces trois ans de son précieux savoir et de sa longue expérience. Les discussions interminables sur quel type d'automate permet de représenter au mieux le protocole étudié m'ont fait comprendre que la recherche est un processus intellectuel sur le long cours, dont la thèse n'était que le premier pas. En regardant derrière, je me rends compte du progrès réalisé sur mes connaissances en informatique et ma culture scientifique ; tu en es le principal artisan. Là aussi, le cadre n'y est pas étranger, puisque le Commissariat à l'énergie atomique et aux énergies alternatives est un des lieux où s'incarne le mieux cette excellence scientifique. À trente kilomètres de Paris, le site de Bruyères-le-Châtel permet de bénéficier de moyens et d'infrastructures conséquentes pour y mener sa recherche dans les meilleures conditions. C'est bien évidement sans oublier les à côtés, qui font tout le charme du lieu : un paysage magnifique en plein Hurepoix, un restaurant d'entreprise dont la renommée n'est plus à faire, de nombreuses activités permettant de découvrir les équipes de recherches sur le site. Là encore, je ne pouvais pas trouver meilleur endroit, et remercie Pascal Malterre pour m'avoir acceuilli dans son équipe de sécurité informatique.

I would like to thank the jury: Lorenzo Cavallaro, Sylvain Guilley, Konstantinos Markantonakis, Xavier Rival, Clémentine Maurice, Whitfield Diffie, Aymeric Vincent, David Naccache and Hovav Shacham. Their feedback has been very precious, and their guidance through the process very valuable. Similarly, I would like to thank Mathieu Blanc, Colas Le Guernic and Jean-Christophe Filliâtre for being members of my thesis oversight committee, easing any administrative concern through their help and advice.

Science is a collective work, and I am really grateful towards my coauthors who taught me all the tricks of the trade to perform research. I thank especially Hadrien Barral, Claire Dross, Houda Ferradi, Rémi Géraud, Maroua Maalej, Konstantinos Markantonakis, Keith Mayes, Yannick Moy, David Naccache, Raja Naeem Akram, Andrei Paskevich, Lee Pike, David Robin, Carlton Shepherd. I had the privilege to work with two exceptional teams in computer security from ENS and CEA and would like to thank them all for their very productive and interesting scientific and non-scientific discussions.

In French, we say that it's by smithing that someone becomes a blacksmith. I believe that this also true for research. Internships provided highly valued experience working with renowned teams both from industry and academia. I would like to thank my supervisors, their teams and institutions for hosting me; Alwyn E. Goodloe and the Safety-Critical Avionics Systems Branch at NASA Langley Research Center, Lee Pike and the SMACCMPilot team at Galois, Yannick Moy and the SPARK team at AdaCore, Konstantinos Markantonakis and the Smart Cart and IoT Security Centre at Royal Holloway University of London, and Sean McLaughlin and the Automated Reasoning Group at Amazon Web Services.

Je souhaiterais aussi remercier les professeurs qui m'ont donné le goût des mathématiques puis de l'informatique, qui persiste jusqu'à lors, chaque professeur y apportant sa pierre. Comme le club de maths les mardi et jeudi midis depuis la sixième jusqu'en terminale, où Eric Vuillemey enseignait les mathématiques à travers de nombreux jeux et énigmes (backgammon, casse têtes, ...), montrant que les mathématiques ne sont pas qu'une corvée calculatoire. Comme les stages intensifs organisés par France IOI pendant les vacances scolaires, où Mathias Hiron et ses entraîneurs enseignent 10 heures par jour une semaine durant l'algorithmique en vue de préparer aux olympiades internationales d'informatique. Ou encore en prépa à Stanislas, avec Célestin Rakotoniaina qui alterne entre cours de maths, khôlles et concerts de musique classique et le reste de l'équipe pégagogique avec Marie-Christine Pauzin, Anne Gérard et Vincent Desportes.

Mes enseignants à l'ENS ont une place toute particulière dans ces remerciements, en commençant par mes tuteurs Jean Vuillemin et David Naccache, et les excellents professeurs Serge Abiteboul, Alexandre d'Aspremont, Jean-Daniel Boissonnat, Anne Bouillard, Albert Cohen, Sylvain Conchon, Juliusz Chroboczek, Carole Delporte, Jérôme Férêt, Jean-Christophe Filliâtre, Rémi Géraud, Jean Goubault-Larrecq, Emmanuel Haucourt, Jean-Paul Laumond, Claude Marché, Claire Mathieu, Paul-André Melliès, Antoine Miné,Castucia Palamidessi, David Pointcheval, Jean Ponce, Marc Pouzet, Xavier Rival, Pierre Senellart, Nicolas Schabanel, Jacques Stern et Wiesław Zielonka.

J'aimerais aussi remercier mes élèves ainsi que les professeurs qui m'ont donné l'opportunité d'améliorer mes compétences en pédagogie en me confiant une charge d'enseignement : les travaux pratiques de Caml en MPSI à Stanislas avec Alain Camanès, les interventions en cryptographie ou en sécurité informatique à Centrale Paris avec Rémi Géraud, les interventions au MBAsp de l'École des officiers de la Gendarmerie nationale avec David Naccache, les travaux dirigés de systèmes numériques à l'École normale supérieure avec Sylvain Guilley, les travaux pratiques de programmation et de compilation à l'École polytechnique avec Jean-Christophe Filliâtre. De même, je remercie l'Institut des hautes études pour la science et la technologie et le commandement de la cyberdéfense pour m'avoir permis de présenter en vulgarisant une partie des mes travaux à des publics élargis.

Enfin une pensée toute particulière va à ma famille et à mes parents qui m'ont soutenu, encouragé et aidé durant déjà vingt-six années. Sans vous, rien de tout cela ne serait possible. х

# Contents

|          | Fore                     | eword                                                                                                  |                                                              | V                                                                      |  |  |  |  |  |  |

|----------|--------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|--|

|          | Rem                      | nercieme                                                                                               | ents / Acknowledgments                                       | vii                                                                    |  |  |  |  |  |  |

|          | Abb                      | reviatio                                                                                               | ns                                                           | xv                                                                     |  |  |  |  |  |  |

| 1        | Intr                     | Introduction 3                                                                                         |                                                              |                                                                        |  |  |  |  |  |  |

|          | 1.1                      | Outlin                                                                                                 | e                                                            | 3                                                                      |  |  |  |  |  |  |

|          | 1.2                      | Termii                                                                                                 | 10logy                                                       | 4                                                                      |  |  |  |  |  |  |

|          | 1.3                      |                                                                                                        | s and Contributions                                          | 5                                                                      |  |  |  |  |  |  |

|          |                          | 1.3.1                                                                                                  | Thesis Results                                               | 5                                                                      |  |  |  |  |  |  |

|          |                          | 1.3.2                                                                                                  | Personal Bibliography                                        | 6                                                                      |  |  |  |  |  |  |

| <b>2</b> | Pro                      | legome                                                                                                 | ena                                                          | 9                                                                      |  |  |  |  |  |  |

|          | 2.1                      | Assem                                                                                                  | bly 101                                                      | 9                                                                      |  |  |  |  |  |  |

|          |                          | 2.1.1                                                                                                  | Top-down approach                                            | 10                                                                     |  |  |  |  |  |  |

|          |                          | 2.1.2                                                                                                  | Bottom-up approach                                           | 12                                                                     |  |  |  |  |  |  |

|          | 2.2                      | Opera                                                                                                  | ting systems                                                 | 22                                                                     |  |  |  |  |  |  |

|          | 2.3                      |                                                                                                        | $\sim$ exploitation                                          | 29                                                                     |  |  |  |  |  |  |

|          |                          |                                                                                                        |                                                              |                                                                        |  |  |  |  |  |  |

| I<br>st  |                          |                                                                                                        | ng the instruction set architecture for con-<br>loitation    | 35                                                                     |  |  |  |  |  |  |

|          | raine                    | ed exp                                                                                                 | loitation                                                    |                                                                        |  |  |  |  |  |  |

| st       | raine                    | ed exp<br>hanum                                                                                        | loitation<br>eric shellcoding on ARMv8-A                     | 35                                                                     |  |  |  |  |  |  |

| st       | raine<br>Alp             | ed exp<br>hanum<br>Introd                                                                              | loitation                                                    | 35<br>37                                                               |  |  |  |  |  |  |

| st       | raine<br>Alp<br>3.1      | ed exp<br>hanum<br>Introd                                                                              | loitation         eric shellcoding on ARMv8-A         uction | 35<br>37<br>37                                                         |  |  |  |  |  |  |

| st       | raine<br>Alp<br>3.1      | ed exp<br>hanum<br>Introd<br>Prelim                                                                    | loitation         eric shellcoding on ARMv8-A         uction | 35<br>37<br>37<br>38                                                   |  |  |  |  |  |  |

| st       | raine<br>Alp<br>3.1      | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1                                                           | Ioitation         eric shellcoding on ARMv8-A         uction | <ul> <li>35</li> <li>37</li> <li>37</li> <li>38</li> <li>40</li> </ul> |  |  |  |  |  |  |

| st       | raine<br>Alp<br>3.1      | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3                                         | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>38<br>40<br>40                               |  |  |  |  |  |  |

| st       | Alp<br>3.1<br>3.2        | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3<br>Buildin                              | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>37<br>38<br>40<br>40<br>41                   |  |  |  |  |  |  |

| st       | Alp<br>3.1<br>3.2<br>3.3 | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3<br>Buildin                              | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>38<br>40<br>40<br>41<br>42                   |  |  |  |  |  |  |

| st       | Alp<br>3.1<br>3.2<br>3.3 | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3<br>Buildin<br>High-le                   | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>38<br>40<br>40<br>41<br>42<br>45             |  |  |  |  |  |  |

| st       | Alp<br>3.1<br>3.2<br>3.3 | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3<br>Buildin<br>High-la<br>3.4.1          | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>38<br>40<br>40<br>41<br>42<br>45<br>45       |  |  |  |  |  |  |

| st       | Alp<br>3.1<br>3.2<br>3.3 | ed exp<br>hanum<br>Introd<br>Prelim<br>3.2.1<br>3.2.2<br>3.2.3<br>Buildin<br>High-le<br>3.4.1<br>3.4.2 | loitation         eric shellcoding on ARMv8-A         uction | <b>35</b><br><b>37</b><br>38<br>40<br>40<br>41<br>42<br>45<br>45<br>45 |  |  |  |  |  |  |

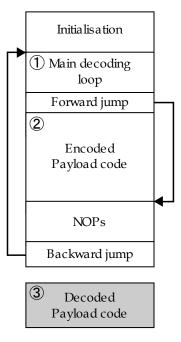

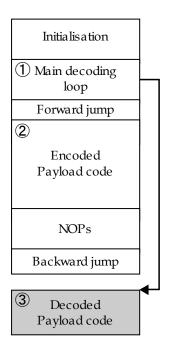

| 3.5            | Fully            | Alphanumeric AArch64                             | 51        |

|----------------|------------------|--------------------------------------------------|-----------|

|                | 3.5.1            | The Encoder                                      | 51        |

|                | 3.5.2            | The Decoder                                      | 51        |

|                | 3.5.3            | Payload Delivery                                 | 52        |

|                | 3.5.4            | Assembly and machine code                        | 52        |

|                | 3.5.5            | Polymorphic shellcode                            | 54        |

| 3.6            | Exper            | imental results                                  | 54        |

|                | 3.6.1            | QEMU                                             | 55        |

|                | 3.6.2            | DragonBoard 410c                                 | 55        |

|                | 3.6.3            | Apple iPhone                                     | 55        |

| 3.7            | Concl            | usion                                            | 56        |

| 3.A            |                  | hary of opcodes in $\mathcal{A}$                 | 57        |

| $3.\mathrm{B}$ |                  | numeric conjunction                              | 57        |

| $3.\mathrm{C}$ |                  | ler's Source Code                                | 59        |

| 3.D            |                  | ler's Source Code                                | 59        |

| $3.\mathrm{E}$ |                  | norphic engines                                  | 62        |

|                | $3. \tilde{E.1}$ |                                                  | 62        |

|                | $3.\mathrm{E.2}$ | Constructs polymorphism                          | 62        |

| $3.\mathrm{F}$ | Hello            | World Shellcode                                  | 64        |

|                |                  |                                                  |           |

| Alp            |                  | neric shellcoding on RISC-V                      | <b>65</b> |

| 4.1            | Introd           | luction                                          | 65        |

|                | 4.1.1            | Prior and related work                           | 66        |

|                | 4.1.2            | Our contribution                                 | 66        |

| 4.2            | RISC-            | -V instruction set                               | 67        |

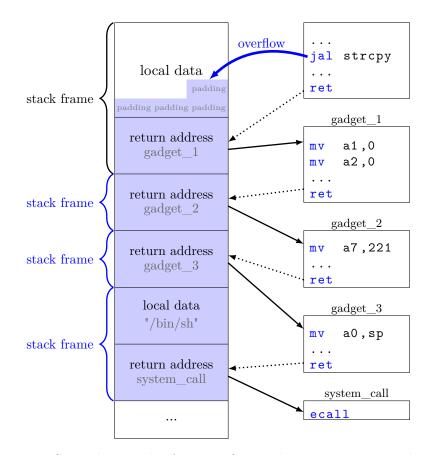

| 4.3            | Alpha            | numeric RISC-V                                   | 68        |

|                | 4.3.1            | Data processing                                  | 69        |

|                | 4.3.2            | Control-flow instruction                         | 70        |

|                | 4.3.3            | Memory processing                                | 70        |

| 4.4            | High-l           | level design                                     | 71        |

| 4.5            |                  | led construction                                 | 72        |

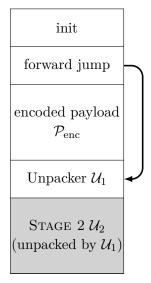

|                | 4.5.1            | Stage 1                                          | 72        |

|                | 4.5.2            | Locating the shellcode and jump over the encoded |           |

|                |                  | payload                                          | 74        |

|                | 4.5.3            | Fixing the store pointer                         | 74        |

|                | 4.5.4            | Unpacking stage 2                                | 74        |

|                | 4.5.5            | Stage 2                                          | 75        |

|                | 4.5.6            | Payload                                          | 76        |

|                | 4.5.7            | Integration/Linking                              | 77        |

|                | 4.5.8            | Shellcoding in /RV64IAC                          | 77        |

|                | 4.5.9            | Shellcoding in 'RV64IDC                          | 78        |

| 4.6            | Evalua           | ation                                            | 79        |

|                |                  |                                                  |           |

|                | 4.6.1            | QEMU                                             | 79        |

$\mathbf{4}$

|   | 4.7                  | Conclusion and future work                                   | 81  |

|---|----------------------|--------------------------------------------------------------|-----|

|   | 4.A                  | Hello World Shellcodes                                       | 82  |

|   |                      | 4.A.1 #RV64IC QEMU Hello World                               | 83  |

|   |                      | 4.A.2 /RV64IAC QEMU Hello World                              | 83  |

|   |                      | 4.A.3 'RV64IDC QEMU Hello World                              | 84  |

|   | $4.\mathrm{B}$       | Source code                                                  | 84  |

| 5 | $\operatorname{Ret}$ | urn-Oriented Programming on RISC-V                           | 85  |

|   | 5.1                  | Introduction                                                 | 86  |

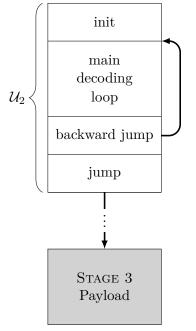

|   | 5.2                  | Background                                                   | 87  |

|   |                      | 5.2.1 Return-Oriented Programming                            | 87  |

|   |                      | 5.2.2 RISC-V                                                 | 89  |

|   | 5.3                  | Threat model and attack overview                             | 89  |

|   |                      | 5.3.1 Closing (stealthily) the gap between vulnerability and |     |

|   |                      | exploitation                                                 | 90  |

|   |                      | 5.3.2 Creating a (concealed) persistent backdoor on a com-   |     |

|   |                      | promised system                                              | 91  |

|   | 5.4                  | Inserting Hidden Gadgets                                     | 92  |

|   | 5.5                  | Chaining the Gadgets                                         | 95  |

|   | 5.6                  | Attack POC on Different Platforms                            | 97  |

|   |                      | 5.6.1 Debian chroot on HiFive Unleashed                      | 97  |

|   |                      | 5.6.2 Fedora $\ldots$                                        | 97  |

|   | 5.7                  | Proposed Countermeasures                                     | 99  |

|   | 5.8                  | Related Work                                                 | 101 |

|   | 5.9                  | Conclusion and Future Work                                   | 103 |

|   | 5.A                  | Source code and artifact                                     | 103 |

# II Improving the safety of programming languages using formal methods 105

| 6 | Lock Optimization for Hoare Monitors |                                                                                                                                                   |     |  |  |

|---|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|   | 6.1                                  | Introduction                                                                                                                                      | 107 |  |  |

|   | 6.2                                  | Hoare monitors                                                                                                                                    | 109 |  |  |

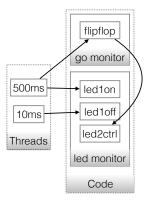

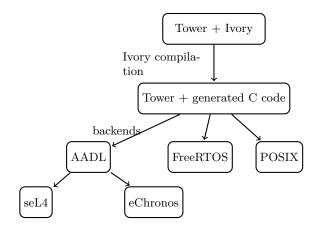

|   |                                      | 6.2.1 Tower: Hoare monitors for real-time systems                                                                                                 | 109 |  |  |

|   |                                      | $6.2.2  \text{Tower toolchain} \dots \dots$ | 112 |  |  |

|   | 6.3                                  | Petri net semantics for Tower                                                                                                                     | 113 |  |  |

|   |                                      | $6.3.1  \text{Petri nets}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                       | 113 |  |  |

|   |                                      | 6.3.2 Denotational semantics of Tower                                                                                                             | 114 |  |  |

|   |                                      | 6.3.3 Safety Properties                                                                                                                           | 117 |  |  |

|   | 6.4                                  | Lock Refinement                                                                                                                                   | 118 |  |  |

|   |                                      | 6.4.1 Lock Optimization                                                                                                                           | 118 |  |  |

|   |                                      | $6.4.2  \text{New semantics}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                    | 121 |  |  |

|   |                                      | 6.4.3 Proofs of Safety                                                                                                                            | 122 |  |  |

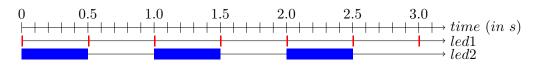

|   | 6.5  | Experimental Results                                                                                                                           |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 6.6  | Case-Study: The SMACCMPilot Autopilot                                                                                                          |

|   |      | 6.6.1 Autopilot Architecture                                                                                                                   |

|   |      | 6.6.2 Optimizing SMACCMPilot                                                                                                                   |

|   | 6.7  | Related work                                                                                                                                   |

|   | 6.8  | Conclusion                                                                                                                                     |

| 7 | Poi  | aters in SPARK 131                                                                                                                             |

|   | 7.1  | Introduction                                                                                                                                   |

|   | 7.2  | Informal Overview of Alias Analysis in SPARK                                                                                                   |

|   | 7.3  | $\mu$ SPARK Language                                                                                                                           |

|   | 7.4  | Alias Safety Rules                                                                                                                             |

|   | 7.5  | Implementation and Evaluation                                                                                                                  |

|   | 7.6  | Related Work                                                                                                                                   |

|   | 7.7  | Future Work                                                                                                                                    |

|   | 7.8  | Conclusion                                                                                                                                     |

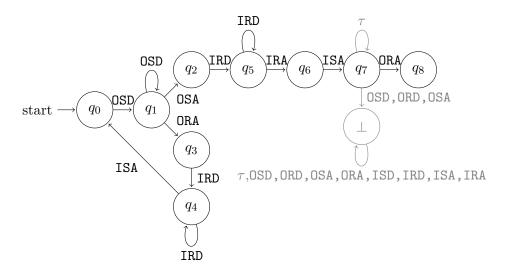

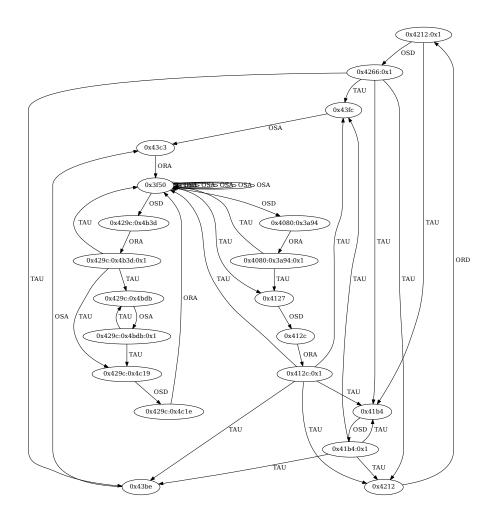

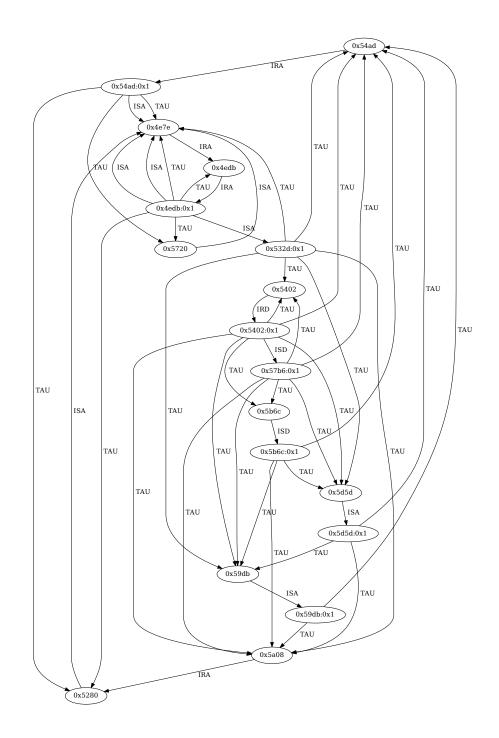

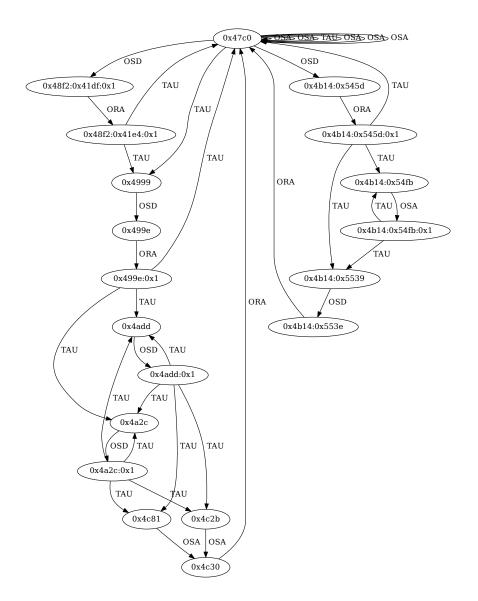

| 8 | Stat | ic Protocol Analysis 151                                                                                                                       |

| 0 | 8.1  | Introduction                                                                                                                                   |

|   | 8.2  | Formal model                                                                                                                                   |

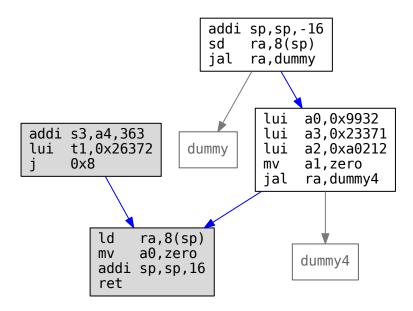

|   | 0.2  | 8.2.1 Lifting binary into graphs                                                                                                               |

|   |      | 8.2.2 Formal semantics                                                                                                                         |

|   | 8.3  | Inter-procedural dataflow analysis                                                                                                             |

|   | 0.0  | 8.3.1 Reaching definitions analysis                                                                                                            |

|   |      | 8.3.2 Liveness analysis                                                                                                                        |

|   | 8.4  | Graph transformations                                                                                                                          |

|   | 0.4  | 8.4.1 Dead-code analysis                                                                                                                       |

|   |      | 8.4.2 Expression propagation                                                                                                                   |

|   |      | 8.4.3 Guard simplification                                                                                                                     |

|   |      | 8.4.4 Guard merging                                                                                                                            |

|   | 8.5  | Program slice                                                                                                                                  |

|   | 8.6  | Implementation and evaluation                                                                                                                  |

|   | 0.0  | 8.6.1 Main idea                                                                                                                                |

|   |      |                                                                                                                                                |

|   |      | 8.6.2 Transition system extraction                                                                                                             |

|   |      | 8.6.3 Detecting violations $\dots \dots \dots$ |

|   | 0 7  | 8.6.4 True positives $\dots \dots \dots$       |

|   | 8.7  | Related work                                                                                                                                   |

|   | 8.8  | Conclusions and future work                                                                                                                    |

|   | 8.A  | Formal grammar                                                                                                                                 |

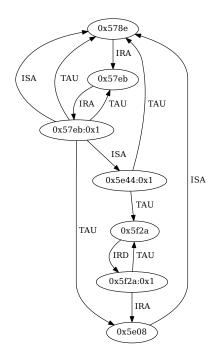

|   | 8.B  | Extracted transition systems                                                                                                                   |

|   |      | 8.B.1 SCP version 8.2 and before                                                                                                               |

|   |      | 8.B.2 SCP version 8.3                                                                                                                          |

xiv

# Abbreviations

In this section, we provide the most-commonly used abbreviations throughout the rest of this manuscript. When using them for the first time, we detail their meaning.

| abbrv.        | meaning                                   | first use |

|---------------|-------------------------------------------|-----------|

| AADL          | Architecture Analysis and Design Language | 6.2.2     |

| ABI           | Application Binary Interface              | 2.1.2     |

| $\mathbf{AC}$ | Access Control                            | 2.2       |

| ACE           | Arbitrary Code Execution                  | 4.1       |

| ACL           | Access-Control List                       | 2.2       |

| ASLR          | Address Space Layout Randomization        | 5.5       |

| CFG           | Control-Flow Graph                        | 5.7       |

| CFI           | Control-Flow Integrity                    | 5.1       |

| CPU           | Central Processing Unit                   | 2.1.1     |

| DEP           | Data Execution Prevention                 | 2.3       |

| FIFO          | First In, First Out                       | 6.2.1     |

| GOT           | Global Offset Table                       | 2.3       |

| HEP           | Hidden Execution Path                     | 5.2.1     |

| IAM           | Identity and Access Management            | 2.2       |

| IR            | Intermediate Representation               | 2.3       |

| ISA           | Instruction Set Architecture              | 4.1       |

| JDK           | Java Development Kit                      | 3.2.3     |

| JNI           | Java Native Interface                     | 3.2.3     |

| LCSAJ         | Linear Code Sequence And Jump             | 5.2.1     |

| LSB           | Least Significant Bit                     | 3.2.2     |

| MEP           | Main Execution Path                       | 5.2.1     |

| PIC           | Position-Independent Code                 | 2.3       |

| PoI           | Point of Interest                         | 5.7       |

| PLT           | Procedure Linkage Table                   | 5.5       |

| PWMS          | Partial Weighted MaxSAT                   | 6.1       |

| ROP           | Return-Oriented Programming               | 5         |

| RTOS          | Real-Time Operating System                | 6         |

| SSP           | Stack-Smashing Protector                  | 5.5       |

| URL           | Uniform Resource Locator                  | 3.2       |

### Hardware specific abbreviations

| abbrv.               | meaning                             | first use |

|----------------------|-------------------------------------|-----------|

| ALU                  | Arithmetic Logic Unit               | 2.1.2     |

| CISC                 | Complex Instruction Set Computer    | 2.1.1     |

| CPU                  | Central Processing Unit             | 2.1.1     |

| $\operatorname{CSR}$ | Control and Status Register         | 2.2       |

| FPU                  | Floating-Point Unit                 | 4.5.9     |

| IA-32                | Intel Architecture, 32-bit          | 3.2.1     |

| ISA                  | Instruction Set Architecture        | 4.1       |

| ISR                  | Interrupt Service Routine           | 2.1.2     |

| LSB                  | Least Significant Bit               | 3.2.2     |

| MMU                  | Memory Management Unit              | 2.2       |

| pc                   | program counter                     | 2.1.2     |

| RAM                  | Random-Access Memory                | 2.1.2     |

| RISC                 | Reduced Instruction Set Computer    | 4.1       |

| ROM                  | Read-Only Memory                    | 2.1.2     |

| SIMD                 | Single Instruction on Multiple Data | 3.3       |

| SoC                  | System on Chip                      | 3.6.2     |

| sp                   | stack pointer                       | 2.1.2     |

### Linux specific abbreviations

| abbrv. | meaning                                 |

|--------|-----------------------------------------|

| fs     | File System                             |

| ID     | Identification                          |

| OS     | Operating System                        |

| root   | The superuser (or administrator)        |

| /      | The root directory of the fs            |

|        | The current working directory in the fs |

| PID    | Process Identifier                      |

| UID    | User ID                                 |

| EUID   | Effective User ID                       |

| SUID   | Saved User ID                           |

| GID    | Group ID                                |

| EGID   | Effective Group ID                      |

| SGID   | Saved Group ID                          |

| setgid | Set Group ID                            |

| setuid | Set User ID                             |

### CONTENTS

CONTENTS

2

# Chapter 1 Introduction

This manuscript assembles various publications in peer-reviewed venues. After a technical introduction in Chapter 2, we discuss a specific use-case of our semantic approach in each chapter, focusing either on the exploitation side in the first part, or on the improvement of programming languages in the second part. Each use-case is an extended version of a published article, with the exception of Chapter 8, which is still work in progress.

### 1.1 Outline

In Chapter 2, we introduce the fundamental concepts and terminology used in binary exploitation. After introducing from scratch assembly languages and various abstractions built atop, we briefly present some binary exploitation techniques as well as their associated mitigation.

In Chapter 3, we describe a methodology to automatically transform arbitrary ARMv8-A programs into alphanumeric executable polymorphic shellcodes. Shellcodes generated in this way can evade detection and bypass filters, broadening the attack surface of ARM-powered devices such as smartphones.

In Chapter 4, we explain how to design RISC-V shellcodes capable of running arbitrary code, whose ASCII binary representation use only letters a-z and A-Z, digits 0-9, and one of the three characters: #, /, '.

In Chapter 5, we provide the first analysis of the feasibility of returnoriented programming (ROP) on RISC-V, by showing the existence of a new class of gadgets, using several linear code sequences and jumps, undetected by current Galileo-based ROP gadget searching tools. We argue that this class of gadgets is rich enough on RISC-V to mount complex ROP attacks, bypassing traditional mitigation like DEP, ASLR, stack canaries, G-Free, as well as some compiler-based backward-edge CFI, by jumping over any guard inserted by a compiler to protect indirect jump instructions. We provide examples of such gadgets, as well as a proof-of-concept ROP chain, using C code injection to leverage a privilege escalation attack on two standard Linux operating systems. Additionally, we discuss some of the required mitigations to prevent these attacks and provide a new ROP gadget finder algorithm that handles this new class of gadgets.

In Chapter 6, we describe a Hoare monitor framework called Tower developed for real-time system programming that targets multiple real-time operating systems. Hoare monitors use coarse-grained locking across all of the methods in a monitor. In a real-time setting, this coarse-grained locking can be too restrictive, but it is difficult and tedious for a programmer to reason about which methods may safely execute in parallel. Therefore, we present an automated compiler optimization for refining locks in Hoare monitors using partially-weighted MAXSAT. We formalize Tower semantics using Petri nets and show that safe concurrency is preserved under the optimization. Finally, we present a number of empirical benchmarks for our optimization as well as a case-study of a real-time autopilot built and optimized with our approach.

In Chapter 7, we introduce pointers to SPARK, a well-defined subset of the Ada language, intended for formal verification of mission-critical software. Our solution uses a permission-based static alias analysis method inspired by Rust's borrow-checker and affine types. To validate our approach, we implemented it in the SPARK GNATprove formal verification toolset for Ada. We give a formal presentation of the analysis rules for a core version of SPARK and discuss their implementation and scope.

In Chapter 8, we present a graph-based formalism to represent binary programs in a much simpler form limited to assignments, procedure calls and conditions. We redefine the reaching definitions and liveness dataflow analyses to extend them—without requiring any procedure signature or calling convention—at an inter-procedural scope. We then provide several basic graph transformations that can be leveraged to extract a compact representation from our formalism, and show through a real example how to combine it with textbook algorithms to investigate a protocol desynchronization issue in scp.

### 1.2 Terminology

Throughout this manuscript, the following conventions are used: plain numbers are in base 10, numbers prefixed by 0x are in hexadecimal format, and numbers prefixed by 0b are in binary format.

The fundamental unit of information we consider is the *bit*. Each bit has either the false or the true value, respectively written as **0b0** or **0b1**. We call *octet* a contiguous sequence of 8 bits, and write it using the symbol o. Each octet is composed of two *nibbles* (also called *quartets*): the higher nibble and the lower nibble each contain 4 bits. An octet can be represented by its two nibbles written in hexadecimal. For instance, the octet whose value is

|          | Symbol    | Meaning                  | Value          |          |

|----------|-----------|--------------------------|----------------|----------|

| -        | KiB       | kibibyte                 | $2^{10}$ bytes |          |

|          | MiB       | mebibyte                 | $2^{20}$ bytes |          |

|          | GiB       | gibibyte                 | $2^{30}$ bytes |          |

|          | TiB       | tebibyte<br>non binary p | $2^{40}$ bytes |          |

| Figure 1 | 1.1: Comn | non binary p             | prefixes of t  | he byte. |

0b01000010 is usually written 0x42.

Although a byte (symbol B) historically designated the smallest contiguous sequence of bits used to encode a character on a given machine, today it is used interchangeably with the term octet. As a result, each byte is also 8 bits long. The byte being a unit, a prefix can be added to the byte to indicate multiples of the units; KB thus means  $10^3$  bytes, TB means  $10^{12}$ bytes. Note that a fraction of a byte (like  $\mu B$ ) has no meaning. In computer science, we instead use binary prefixes, summarized in Table 1.1.

The *word size* designates the size of the data processed by a processor. Therefore, each architecture has its own word size. In this manuscript, we will follow the convention used by RISC-V to define *words* as 4 bytes long, even for other architectures. Consequently, a *half-word* is 2 bytes long, a *double-word* 8 bytes.

### **1.3** Results and Contributions

### 1.3.1 Thesis Results

This thesis presents various scientific contributions, in the form of publications, teaching, reviews, or miscellaneous communication activities.

**Publications** Several articles have been published in this thesis in peerreviewed venues, most of them presented in this manuscript: three articles as lead author [JP17; Jal+20a; Jal+20b] respectively on Hoare monitor optimization, return-oriented programming and static alias analysis, three articles as trailing co-author [Bar+16; Bar+19a; SMJ21] on alphanumeric shellcoding and remote attestation mechanisms (not presented in this manuscript). Furthermore, work on alphanumeric shellcoding was also presented at DEF CON 27 [Bar+19b], a prestigious hacking conference with no published proceedings.

**Teaching** The majority of teaching was for computer science students. However one course targeted a wider audience, helping improve popularization skills. Grouping them by institution: École normale supérieure (*Computer science by practice* and *Digital systems, from algorithms to circuits*), École polytechnique (*Introduction to programming and algorithms* and *Compilation*), École des officiers de la Gendarmerie nationale (*Cyberphysical and*  communications infrastructure security and Digital forensics), EISTI (Reverse engineering), Centrale Supélec (invited lecture on Reverse engineering in the Cybersecurity course).

**Service** Several reviews were performed, either as sub-reviewer (FMCAD 2017, TRUSTCOM2019) or as member of the artifact evaluation committee (Usenix 2020 and Usenix 2021).

**Miscellaneous** Many other activities may be mentioned, targeting either various communications to wide audiences, internships, or non peer-reviewed contributions.

Two talks targeting senior executives of the French public and private sectors: a 20-minute demo on cold-boot attacks at the CyberStrategia conference organized by the French Cyber Defense Command and a 20-minute talk on the use of secrets in computer security at IHEST (Institute of High Studies for Science and Technology).

Many seminars organized at CEA DAM to present and debate about an existing paper with either historic or technical value. Another seminar at University of Luxembourg presented shellcoding techniques (among which alphanumeric and return-oriented programming), while a poster presented return-oriented programming at the Smart Card Center day at Royal Holloway University of London.

Two three-month internships were performed during the thesis, respectively at Royal Holloway University of London (ISG Smart Card and IoT Security Center, supervised by Konstantinos Markantonakis) and at Amazon Web Services (Automated Research Group, supervised by Sean McLaughlin), allowing exchanges of practice and knowledge with foreign research teams.

Finally, non-academic contributions include a vulnerability on scp found and reported under CVE-2020-12062. Two additional vulnerabilities are yet to be reported.

#### 1.3.2 Personal Bibliography

[Bar+16] Hadrien Barral, Houda Ferradi, Rémi Géraud, Georges-Axel Jaloyan, and David Naccache. "ARMv8 Shellcodes from 'A'to 'Z'". In: Proceedings of the 12th International Conference on Information Security Practice and Experience. Berlin, Heidelberg: Springer-Verlag, 2016, pp. 354–377. ISBN: 978-3-319-49151-6. URL: https://link.springer.com/chapter/10.1007/978-3-319-49151-6\_25.

#### 1.3. RESULTS AND CONTRIBUTIONS

- [JP17] Georges-Axel Jaloyan and Lee Pike. "Lock Optimization for Hoare Monitors in Real-Time Systems". In: Proceedings of the 17th International Conference on Application of Concurrency to System Design (ACSD '17). Zaragoza: IEEE Computer Society, 2017, pp. 126–135. URL: https://leepike.github.io/ pub\_pages/acsd17.html.

- [Bar+19a] Hadrien Barral, Rémi Géraud-Stewart, Georges-Axel Jaloyan, and David Naccache. "RISC-V: #AlphanumericShellcoding". In: Proceedings of the 13th USENIX Workshop on Offensive Technologies. Santa Clara, CA: USENIX Association, 2019. URL: https://www.usenix.org/system/files/woot19paper\_barral.pdf.

- [Bar+19b] Hadrien Barral, Rémi Géraud, Georges-Axel Jaloyan, and David Naccache. The ABC of Next-Gen Shellcoding. DEF CON 27. 2019. URL: https://www.youtube.com/watch?v= qHj1kquKNk0.

- [Jal+20a] Georges-Axel Jaloyan, Konstantinos Markantonakis, Raja Naeem Akram, David Robin, Keith Mayes, and David Naccache. "Return-Oriented Programming on RISC-V". In: Proceedings of the 15th ACM Asia Conference on Computer and Communications Security (AsiaCCS '20). New York, NY: ACM, 2020, pp. 417–480. ISBN: 9781450367509. URL: https: //pure.royalholloway.ac.uk/portal/files/37157938/ ROP\_RISCV.pdf.

- [Jal+20b] Georges-Axel Jaloyan, Claire Dross, Maroua Maalej, Yannick Moy, and Andrei Paskevich. "Verification of Programs with Pointers in SPARK". In: Proceedings of the 2020 International Conference on Formal Methods and Software Engineering. Berlin, Heidelberg: Springer-Verlag, 2020, pp. 55–72. URL: https://hal.inria.fr/hal-03094566.

- [SMJ21] Carlton Shepherd, Konstantinos Markantonakis, and Georges-Axel Jaloyan. "LIRA-V: Lightweight Remote Attestation for Constrained RISC-V Devices". In: Proceedings of the 4th IEEE Workshop on the Internet of Safe Things. Oakland, CA: IEEE Computer Society, 2021. URL: https://arxiv.org/abs/2102. 08804. Forthcoming.

# Chapter 2

# Prolegomena

This chapter introduces the fundamental concepts and terminology used in binary exploitation. After introducing from scratch assembly languages and various abstractions built atop, we briefly present some binary exploitation techniques as well as their associated mitigation.

### 2.1 Assembly 101

Assembly languages allow the junction between software and hardware. Indeed, they can both be seen as respectively the lowest and highest abstraction level of each domain. This is why we present assembly languages twice in this chapter, using two different methods.

The first method introduces assembly as the lowest-level human-readable intermediate language of the compilation process, which unsurprisingly turns out to be the target language of the compiler. This method can be portrayed as "yet another programming language" with weird features like discriminating the program's data into addressable memory and a limited number of registers. This method is particularly well illustrated in Section 8.2 of *Compilers: Principles, Techniques, and Tools* (also nicknamed the *Dragon Book*) written by Alfred V. Aho *et al.* [Aho+06], which provides a formal definition of assembly language. I call this method the top-down approach, as opposed to—as you may have guessed—the bottom-up approach that follows.

The second method starts at the transistor level and adds layer upon layer until a simplified processor executing binary code is built. From here, we define assembly as the human-readable equivalent of binary code, with extra features like labels and pseudo-instructions. This is the approach adopted in Chapters 2 and 4 of *Computer Organization and Design* written by David Patterson and John Hennessy [PH13], where assembly instructions are translated into binary statements, and segmented into several smaller fields, which are then sent to different functional units of the processor (ALU, control, registers, ...).

As these two methods complement one another, we will refer to these two methods throughout the thesis. Indeed, the top-down approach explains what assembly instructions can achieve—answering the question "how" whereas the bottom-up approach explicits design choices that may break or miraculously fix our exploits, answering the question "why". Consider, for example, writing constrained exploits where the goal is to perform arbitrary computations using binary code that must respect constraints like a forbidden set of instructions. The top-down approach yields an overview of what type of computation may theoretically be carried out (accessing registers, reading or writing to memory, control-flow transfers), while the bottom-up approach points to a precise insight—such as which registers can be used with the restricted instruction set to build our computations.

#### 2.1.1 Top-down approach

To introduce the first method, let's define a small language resembling a 32bit assembly, called  $\mu$ ASM. Like all other languages, we define the left-values which we call *registers*, then the expressions—we restrict ourselves to scalar values which we call *immediates*—followed by statements or *instructions*. Smash it until it fits and voilà. We can formally express its grammar with the following *Backus-Naur form* [Bac59]:

| $\langle reg \rangle$  | ::= | x0     x31                                                                   | register                    |

|------------------------|-----|------------------------------------------------------------------------------|-----------------------------|

|                        |     |                                                                              |                             |

| $\langle imm \rangle$  | ::= | 0     4294967295                                                             | immediates                  |

| ζ <i>γ</i>             |     |                                                                              |                             |

| $\langle inst \rangle$ | ::= | nop                                                                          | no operation                |

| (                      |     | add $\langle reg \rangle$ , $\langle reg \rangle$ , $\langle reg \rangle$    | 32-bit unsigned addition    |

|                        | ĺ   | and $\langle reg \rangle$ , $\langle reg \rangle$ , $\langle reg \rangle$    | bitwise conjunction         |

|                        | ĺ   | or $\langle reg \rangle$ , $\langle reg \rangle$ , $\langle reg \rangle$     | bitwise disjunction         |

|                        | İ   | xor $\langle reg \rangle$ , $\langle reg \rangle$ , $\langle reg \rangle$    | bitwise exclusion           |

|                        | İ   | addi $\langle reg \rangle$ , $\langle reg \rangle$ , $\langle imm \rangle$   | 32-bit addition to constant |

|                        |     | load $\langle reg \rangle$ , $\langle imm \rangle$ ( $\langle reg \rangle$ ) | 32-bit memory read          |

|                        | Ì   | store $\langle imm \rangle$ ( $\langle reg \rangle$ ), $\langle reg \rangle$ | 32-bit memory write         |

|                        |     | $jmp \langle imm \rangle$                                                    | absolute jump               |

|                        |     | $jz \langle reg \rangle, \langle imm \rangle$                                | absolute conditionnal jump  |

|                        |     |                                                                              | 0 1                         |

|                        |     | jnz $\langle reg  angle$ , $\langle imm  angle$                              | absolute conditionnal jump  |

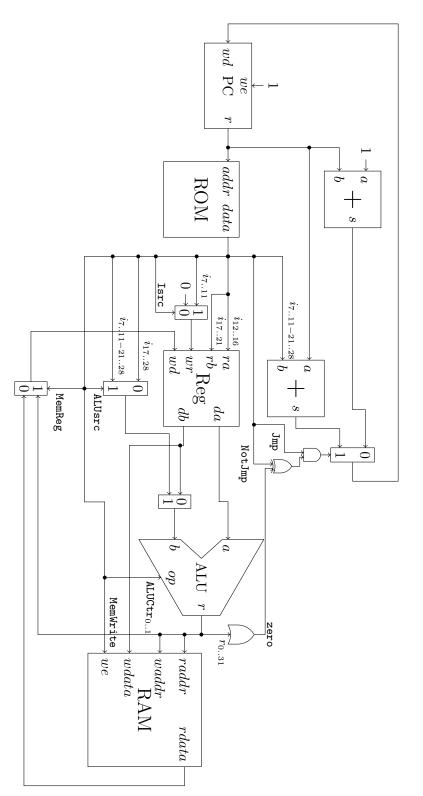

Then we write the small-step operational semantics of the assembly language, detailed in Fig. 2.1. We specify its internal state, as defined by the value of the *program counter* pc, a function  $\Upsilon$  that maps each register  $x0 \dots x31$  to its value, and another one  $\Sigma$  called the *store* mapping

10

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{nop}}$                 | (pc+1)                                           | $,\Upsilon,\Sigma)$                          |

|---------------------------------|---------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\texttt{pc})=\texttt{add}\ r_1, r_2, r_3}$  | $(\texttt{pc}+1,\Upsilon[r_1\leftarrow\Upsilon]$ | $\Upsilon(r_2) + \Upsilon(r_3)], \Sigma)$    |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\texttt{pc})=\texttt{and } r_1, r_2, r_3}$  | $(\mathtt{pc}+1,\Upsilon[r_1\leftarrow\Upsilon]$ | $\Gamma(r_2) \wedge \Upsilon(r_3)], \Sigma)$ |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{or}\ r_1,r_2,r_3}$     | $(\mathtt{pc}+1,\Upsilon[r_1\leftarrow\Upsilon]$ | $\Gamma(r_2) \vee \Upsilon(r_3)], \Sigma)$   |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{xor}\ r_1,r_2,r_3}$    | $(\texttt{pc}+1,\Upsilon[r_1\leftarrow\Upsilon]$ | $\Upsilon(r_2)\oplus\Upsilon(r_3)],\Sigma)$  |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{addi}\ r_1,r_2,k}$     | $(\mathtt{pc}+1,\Upsilon[r_1\leftarrow$          | $\Upsilon(r_2) + k], \Sigma)$                |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\texttt{pc})=\texttt{load } r_1,  k(r_2)}$  | $(\mathtt{pc}+1,\Upsilon[r_1\leftarrow\Sigma])$  | $\Sigma(\Upsilon(r_2)+k)],\Sigma)$           |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{store}\ k(r_1),\ r_2}$ | $(\mathtt{pc}+1,\Upsilon,\Sigma[\Upsilon(r$      | $(1) + k \leftarrow \Upsilon(r_2)])$         |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{jmp}\ k}$              | $(k,\Upsilon,\Sigma)$                            |                                              |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\texttt{pc})=\texttt{jz } r_1, k}$          | $(k,\Upsilon,\Sigma)$                            | if $\Upsilon(r_1) = 0$                       |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\texttt{pc})=\texttt{jz } r_1, k}$          | $(\texttt{pc}+1,\Upsilon,\Sigma)$                | if $\Upsilon(r_1) \neq 0$                    |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{jnz}\ r_1,k}$          | $(k,\Upsilon,\Sigma)$                            | if $\Upsilon(r_1) \neq 0$                    |

| $(\texttt{pc},\Upsilon,\Sigma)$ | $\xrightarrow{\pi(\mathtt{pc})=\mathtt{jnz}\ r_1,k}$          | $(\texttt{pc}+1,\Upsilon,\Sigma)$                | if $\Upsilon(r_1) = 0$                       |

Figure 2.1: Semantics of  $\mu$ ASM.

each address to its value stored in memory. To keep our formalism clean, we limit ourselves to *Harvard architecture* devices which—contrary to *Von Neumann* devices—separate the program from the memory, thus disabling self-rewriting code. To this end, we provide a function  $\pi$  that maps each possible pc value to an instruction. We also assume our memory has a granularity of 32 bits—meaning that the smallest amount of data that can be designated unequivocally by a single address is of size 32 bits, and that the memory is big enough to span the whole addressable space—the set of integer values for which a load or a store is possible. Thus our machine has 16 GiB of memory and the program is 16 GiB long. The semantics can be expressed by providing its transition relation  $\rightarrow$ . Symbolically, we write  $(pc, \Upsilon, \Sigma) \xrightarrow{\pi(pc)=inst} (pc', \Upsilon', \Sigma')$  to denote that upon state  $(pc, \Upsilon, \Sigma)$ , the execution of instruction *inst* at address pc terminates yielding new state  $(pc', \Upsilon', \Sigma')$ .

Let us look at one specific instruction, like add r1, r2, r3. This instruction comprises four elements: add is called the *opcode*, r1 is the *destination register*, while r2 and r3 are the *source registers*. These three registers are called the instruction *operands*. The lexemes "add", "r1", "r2", and "r3" are called *mnemonics*. The add instruction performs the 32-bit modular unsigned addition of its two source operands and stores the result in the destination register, as shown in Fig. 2.1. On most of today's computers, memory has a granularity of 8 bits (instead of 32). Furthermore, the memory does not cover the entire addressable space, leaving room for the use of many peripherals besides the RAM. Furthermore, *central processing units* (CPUs) have *caches* to speed up access to memory, acting like intermediate memories with very short response time. Caches form a hierarchy, usually written L1, L2, ..., where the lowest level is the fastest—and also the smallest in terms of capacity. It works as follows: when the processor tries to dereference a pointer, a read request is sent to the L1 cache. If the cache possesses the requested data, the cache immediately returns the data, and we call it a *cache hit*. Otherwise the read request is transmitted to the next cache and we call it a *cache miss*. If no cache can return the data, the request is sent to the main memory. Caches may store a copy of the data they are missing once its value is returned, often at the cost of discarding older data—this is called *cache eviction*. Many *cache replacement policies* exist, and are implemented by the chip designer.

Harvard architecture devices possess two sets of caches for instructions and data (written L1i and L1d, and so on). Modern CPUs merge both caches above L2, thus allowing some limited forms of program modification: typically when the operating system launches a program, or during just-in-time compilation when the interpreter rewrites itself by compiling parts of the input (called the *bytecode*). This model is called a *modified Harvard architecture* or an *almost Von Neumann architecture*. However, self-modifying programs may not work, as the L1i cache cannot see memory writes carried out through the L1d cache. A special instruction is often provided (*e.g.* fence.i on RISC-V) to keep it in sync with the data memory, usually by *flushing*—evicting all its values—the instruction cache.

$\mu$ ASM belongs to the *reduced instruction set computer* (RISC) family as each instruction has very simple semantics. In contrast, meaning *complex instruction set computers* (CISC) provide instructions with more complex semantics—*e.g.* reading, processing and writing back to the memory in a single instruction.

#### 2.1.2 Bottom-up approach

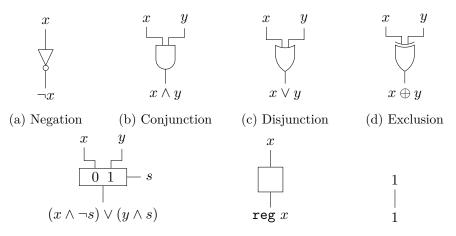

This formal description of the language, usually referred to as the *instruction* set architecture (ISA), can be greatly improved as we point out differences between  $\mu$ ASM and real world CPUs. This is when we call in the second method, as it shows why these differences exist. To keep the example simple, we will start at the logic gate level, instead of at the transistor. Fig. 2.2 recalls the symbols representing usual gates. Our goal is to design a small Harvard architecture CPU that *implements*  $\mu$ ASM—modulo details eluded in the first method.

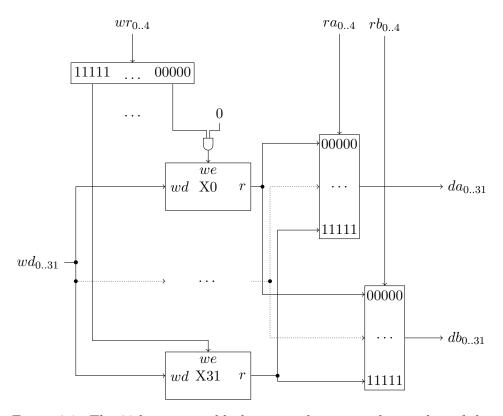

Our processor is segmented into several *blocks* that communicate through sets of *wires*, called *ribbons*, or *hardware buses*. These blocks respectively

12

(e) Selection (multiplexer) (f) Timing (1-bit register) (g) Tautology

Figure 2.2: Examples of logic gates.

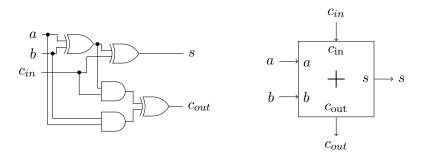

Figure 2.3: A 1-bit full-adder and its black box representation. We use the same black box representation to represent n-bit adders.

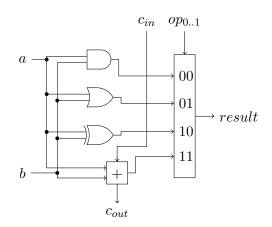

Figure 2.4: A 1-bit ALU. Note that the *op* bus is 2-bit wide.

load the instruction to be executed (*instruction memory*), reading and writing the values of specific registers, decoding the current instruction (*control*), performing arithmetical and logical operations (*arithmetic logical unit* or ALU), as well as storing and reading into the *data memory*.

**ALU block** The most important block is the ALU that performs all arithmetic and logic operations, parameterized by a bus called the *ALU control*. A basic design uses a 1-bit ALU to perform unsigned addition, conjunction, disjunction and exclusion, and then select the required result with a multiplexer, as shown in Fig. 2.4.

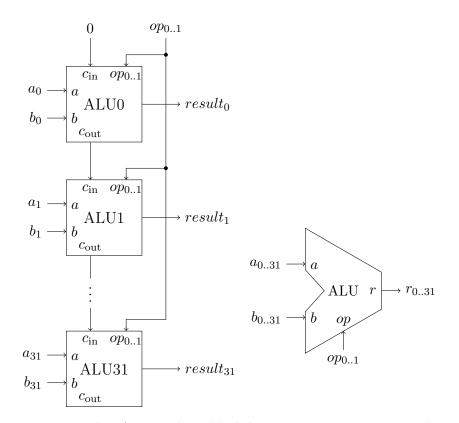

We extend our 1-bit ALU to a full 32-bit ALU in Fig. 2.5, by chaining the outgoing carry signal of a block to the ingoing carry signal of the following block. If we restrict ourselves to the ALU's adder, we recognize a *ripple-carry adder*, whose critical path has linear length in the number of bits. Other ALU designs reduce this critical path, using, for instance, *carry-lookahead adders*.

Figure 2.5: 32-bit ALU and its black-box representation. Note that the output carry signal of the ALU31 is ignored.

#### 2.1. ASSEMBLY 101

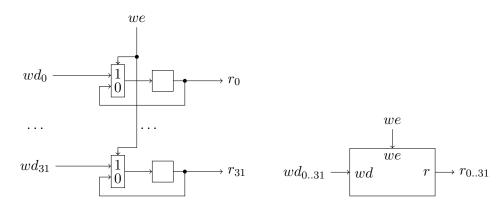

**Register block** The next block is the register block and can be designed in two steps. Step one, shown in Fig. 2.6, extends the concept of a 1bit *hardware register gate* that delays its input for one cycle into a 32-bit *machine register* holding its value for an arbitrary time period. This register can be overwritten with arbitrary input data when a write-enable bit is set.

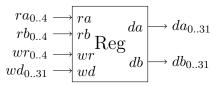

Step two aggregates 32 machine registers into a subsystem receiving as input three 5-bit binary values (called wr, ra, rb) and one 32-bit value (called wd) and returning two 32-bit values (da and db). Practically, da and db must respectively be equal to the values of the ra-th and rb-th machine register, and the wr-th register must be overwritten with the value wd. For this purpose, we introduce a demultiplexer—the inverse operation of a multiplexer—to set one of the 32 write enabling bits of our machine registers. In  $\mu$ ASM, like RISC-V, the register x0 is hardwired to the constant 0 by zeroing its write enable bit (we assume by convention that at startup, all hardware registers have value false). The black box representation for the whole register block is shown in Fig. 2.7.

Figure 2.6: A 32-bit machine register and its black box variant. Its inputs are one 32-bit bus  $wd_{0..31}$ , and a single bit we that allows the values of the registers to be overwritten when set to one.

Figure 2.7: The black box representation for the register block.

Figure 2.8: The 32-bit register block.  $wr_{0..4}$  designates the number of the register to be written,  $ra_{0..4}$  the number of the first register to read,  $rb_{0..4}$  the second register to read, while  $wd_{0..31}$  is the data to write into register  $wr_{0..4}$ . Note that the register X0 is hardwired to zero by deactivating its write enable bit.

**Memory blocks** We add to our Harvard CPU two memories, one for instructions and one for data. The instruction memory is a *read-only memory* (ROM), and when provided a 32-bit unsigned address *addr*, returns a 32bit instruction *data*, noted as ribbon  $i_{0..31}$ . The data memory is a volatile *random-access memory* (RAM), and is able to read and write in different memory areas at each cycle. It takes as input the read address *raddr*, and when its write enable bit *we* is enabled, writes 32-bit data *wdata* to 32-bit address *waddr*. It returns at each cycle the 32-bit data *rdata* read from memory. We use a special 32-bit register **pc** called the *program counter* to store the address of the 32-bit instruction to execute at this cycle. The program counter is incremented at each cycle, except when a jump is taken. Note that both instruction and data memories require 32-bit addresses and return 32-bit values. As with the top-down approach, we have an *address size* of 32 bits and a *memory access granularity* of 32 bits. Similarly, our computer has 16 GiB of instruction memory and 16 GiB of data memory.

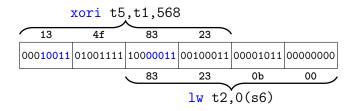

Instruction encoding Here comes the first problem. An instruction is 32 bits long, as is the address referring to it. Absolute jumps as depicted in the top-down approach are not possible, as it would leave 0 bits to the opcode. The most common solution consists in using jumps to a relative offset (which can be negative using two's complement representation) to the program counter, with only a restricted set of offsets available. In  $\mu$ ASM, we restrict ourselves to only 12 bits signed immediate offsets (*i.e.* from -2048 to 2047). This restriction also applies to load and store memory operations, as well as to the addi operation.

To go further into details, we now need to look at the representation of  $\mu$ ASM instructions by looking how much space we need for each operand, taking into account that each register needs 5 bits and each immediate 12 bits. We summarize these requirements in Table 2.1.

| instruction                    | minimum operands size | sum |

|--------------------------------|-----------------------|-----|

| add rd, rs1, rs2               | 5 + 5 + 5             | 15  |

| and rd, rs1, rs2               | 5 + 5 + 5             | 15  |

| or rd, rs1, rs2                | 5 + 5 + 5             | 15  |

| xor rd, rs1, rs2               | 5 + 5 + 5             | 15  |

| addi rd, rs, imm12             | 5 + 5 + 12            | 22  |

| <pre>load rd, imm12(rs)</pre>  | 5 + 12 + 5            | 22  |

| <pre>store imm12(rd), rs</pre> | 12 + 5 + 5            | 22  |

| jmp imm12                      | 12                    | 12  |

| jz rs, imm12                   | 5 + 12                | 17  |

| jnz rs, imm12                  | 5 + 12                | 17  |

Table 2.1:  $\mu$ ASM instructions and the minimal length required for their operands.