## Industrial approach to quantum dots in fully-depleted silicon-on-insulator devices for quantum information applications

Ioanna Kriekouki

### ▶ To cite this version:

Ioanna Kriekouki. Industrial approach to quantum dots in fully-depleted silicon-on-insulator devices for quantum information applications. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..]; Université de Sherbrooke (Québec, Canada), 2022. English. NNT: 2022GRALT102. tel-04032456

### HAL Id: tel-04032456 https://theses.hal.science/tel-04032456v1

Submitted on 30 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

THÈSE

Pour obtenir le grade de

#### DOCTEUR de l'UNIVERSITÉ GRENOBLE ALPES et de l'UNIVERSITÉ DE SHERBROOKE

École doctorale : Electronique, Electrotechnique, Automatique et Traitement du Signal Spécialité : Nanoélectronique et Nanotechnologies Unité de recherche : Laboratoire TIMA

Approche industrielle aux boîtes quantiques dans des dispositifs de silicium sur isolant complètement déplété pour applications en information quantique

#### Industrial approach to quantum dots in fully-depleted silicon-on-insulator devices for quantum information applications

Présentée par :

Kriekouki, loanna

Direction de thèse :

| Philippe GALY<br>Directeur technique, STMicroelectronics<br>Michel PIORO-LADRIERE<br>Professeur, Université de Sherbrooke | Directeur de thèse<br>Co-Directeur de thèse |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Salvador MIR<br>Directeur de recherche, CNRS, TIMA                                                                        | Co-Directeur de thèse                       |

| Manuel J. BARRAGAN<br>Chargé de recherche, CNRS, TIMA                                                                     | Co-Encadrant de thèse                       |

Rapporteurs :

Andrew DZURAK Professeur, University of New South Wales Philippe DOLLFUS Directeur de recherche, CNRS, C2N

#### Thèse soutenue publiquement le 14 décembre 2022, devant le jury composé de :

|    | Skandar BASROUR<br>Professeur, Université Grenoble Alpes      | Président du jury  |

|----|---------------------------------------------------------------|--------------------|

|    | Andrew DZURAK<br>Professeur, University of New South Wales    | Rapporteur         |

|    | Philippe DOLLFUS<br>Directeur de recherche, CNRS, C2N         | Rapporteur         |

|    | Louis HUTTIN<br>Ingénieur de recherche, CEA-Leti              | Examinateur        |

|    | Patrick FOURNIER<br>Professeur, Université de Sherbrooke      | Examinateur        |

|    | Philippe GALY<br>Directeur technique, STMicroelectronics      | Directeur de thèse |

|    | Michel PIORO-LADRIERE<br>Professeur, Université de Sherbrooke | Co-Directeur de th |

| és | 61                                                            |                    |

|    | Salvador MIR                                                  |                    |

orteur orteur inateur inateur teur de thèse recteur de thèse

#### Invité

Directeur de recherche, CNRS, TIMA Manuel J. BARRAGAN Chargé de recherche, CNRS, TIMA

I am among those who think that science has great beauty. A scientist in his laboratory is not only a technician; he is also a child placed before natural phenomena which impress him like a fairy tale.

Marie Curie

Never half-ass two things. Whole-ass one thing.

Ron Swanson

## Résumé

La mise en œuvre des qubits de spin électronique à base de boîtes quantiques réalisés en utilisant une technologie avancée de métal-oxyde-semiconducteur complémentaire (en anglais: CMOS ou Complementary Metal-Oxide-Semiconductor) fonctionnant à des températures cryogéniques permet d'envisager la fabrication industrielle reproductible et à haut rendement de systèmes de qubits de spin à grande échelle. Le développement d'une architecture de boîtes quantiques à base de silicium fabriquées en utilisant exclusivement des techniques de fabrication industrielle CMOS constitue une étape majeure dans cette direction. Dans cette thèse, le potentiel de la technologie UTBB (en anglais: Ultra-Thin Body and Buried oxide) silicium sur isolant complétement déplété (en anglais: FD-SOI ou Fully Depleted Silicon-On-Insulator) 28 nm de STMicroelectronics (Crolles, France) a été étudié pour la mise en œuvre de boîtes quantiques bien définies, capables de réaliser des systèmes de qubit de spin. Dans ce contexte, des mesures d'effet Hall ont été réalisées sur des microstructures FD-SOI à 4.2 K afin de déterminer la qualité du nœud technologique pour les applications de boîtes quantiques. De plus, un flot du processus d'intégration, optimisé pour la mise en œuvre de dispositifs quantiques utilisant exclusivement des méthodes de fonderie de silicium pour la production de masse est présenté, en se concentrant sur la réduction des risques de fabrication et des délais d'exécution globaux. Enfin, deux géométries différentes de dispositifs à boîtes quantiques FD-SOI de 28 nm ont été conçues et leurs performances ont été étudiées à 1.4 K. Dans le cadre d'une collaboration entre Nanoacademic Technologies, Institut quantique et STMicroelectronics, un modèle QT-CAD (en anglais: Quantum Technology Computer-Aided Design) en 3D a été développé pour la modélisation de dispositifs à boîtes quantiques FD-SOI. Ainsi, en complément de la caractérisation expérimentale des structures de test via des mesures de transport et de spectroscopie de blocage de Coulomb, leur performance est modélisée et analysée à l'aide du logiciel QTCAD. Les résultats présentés ici démontrent les avantages de la technologie FD-SOI par rapport à d'autres approches pour les applications de calcul quantique, ainsi que les limites identifiées du nœud 28 nm dans ce contexte. Ce travail ouvre la voie à la mise en œuvre des nouvelles générations de dispositifs à boîtes quantiques FD-SOI basées sur des nœuds technologiques inférieurs.

Π

## Abstract

Electron spin qubits based on quantum dots implemented using advanced Complementary Metal-Oxide-Semiconductor (CMOS) technology functional at cryogenic temperatures promise to enable reproducible high-yield industrial manufacturing of large-scale spin qubit systems. A milestone in this direction is to develop a silicon-based quantum dot structure fabricated using exclusively CMOS industrial manufacturing techniques. In this thesis, the potential of the industry-standard process 28 nm Ultra-Thin Body and Buried oxide (UTBB) Fully Depleted Silicon-On-Insulator (FD-SOI) technology of STMicroelectronics (Crolles, France) was investigated for the implementation of well-defined quantum dots capable to realize spin qubit systems. In this context, Hall effect measurements were performed on FD-SOI microstructures at 4.2 K to determine the quality of the technology node for quantum dot applications. Moreover, an optimized integration process flow for the implementation of quantum devices, using exclusively mass-production silicon-foundry methods is presented, focusing on reducing manufacturing risks and overall turnaround times. Finally, two different geometries of 28 nm FD-SOI quantum dot devices were conceived, and their performance was studied at 1.4 K. In the framework of a collaboration between Nanoacademic Technologies, Institut quantique, and STMicroelectronics, a 3D Quantum Technology Computer-Aided Design (QTCAD) model was developed for FD-SOI quantum dot device modeling. Therefore, along with the experimental characterization of the test structures via transport and Coulomb blockade spectroscopy measurements, their performance is modeled and analyzed using the QTCAD software. The results reported here demonstrate the advantages of the FD-SOI technology over other approaches for quantum computing applications, as well as the identified limitations of the 28 nm node in this context. This work paves the way for the implementation of the next generations of FD-SOI quantum dot devices based on lower technology nodes.

## Acknowledgements

First of all, I would like to express my deepest gratitude to my PhD supervisor and cosupervisors, Dr. Philippe Galy, Prof. Michel Pioro-Ladriere, and Prof. Salvador Mir, as well as to my PhD advisor Dr. Manuel J. Barragan, for their guidance, support, trust, and encouragement throughout the entirety of my PhD journey. Their unwavering belief in my abilities and constant push to excel has been invaluable. I am deeply grateful for the opportunity I have had to work with such experts from diverse domains. All the opportunities they offered me helped me not only to develop my skills and expertise in such a broad field but also to grow as a person. Thank you Philippe for being so supportive and always available to talk and help me, even during my 2.5 years in Canada. Thank you for being so kind and asking me at each one of our weekly meetings about my health and my family's health throughout the years of the pandemic and lockdowns. Thank you Salvador for all the fruitful conversations and thorough comments emphasizing on the details that allowed me to develop my scientific way of thinking. Thank you also for your valuable help and comments with re-reading in detail the entire manuscript of my thesis when I completed it. Thank you Manuel for your guidance and the analytical and pedagogical way you answered all my questions about engineering and microelectronics at the beginning of my PhD. I also greatly appreciate our discussions and your advice on career options. Thank you Michel, for your generosity, optimism and constant motivation. Thank you also from the bottom of my heart for working with me in the lab intensively almost every day with me when my ESD-damaged devices almost drove me crazy, or for finding the time to simply have a coffee and a chat when I was very affected by the challenges of this project. I will stand on this last point to thank you for being so caring and for reminding me all along our work together that success in the longterm does not come by numerous burnouts but by not neglecting our personal life. This realization was a major shift for me and is the one of the main reasons that makes me want to continue research and for that I am deeply grateful to you.

I would like to express my immense gratitude to Thomas Bédécarrats for helping me to understand so many new concepts in electrical engineering at the beginning of my PhD and especially for his priceless support during my first tape-out in STMicroelectronics. I would also like to express my sincere gratitude to Ryan H. Foote for all his tremendous help and invaluable support during almost all the time that I spent in Institut quantique, which allowed me to overcome some of the most difficult challenges. Your broad knowledge is so impressive and you are so enthusiastic that it is really inspiring to work and discuss science with you. I have learnt so much and you have helped me to improve in so many areas, such as how to design and conduct my experiments, my writing and presentation skills, just to name a few.

At this point, I would like to express my gratefulness to the members of my thesis committee, Prof. Philippe Dollfus, Prof. Andrew Dzurak, Prof. Patrick Fournier, Prof. Skandar Basrour and Dr. Louis Huttin for taking the time to review my manuscript and for their insightful feedback and kind words about my work.

I would also like to thank my PhD follow-up committees, Prof. Skandar Basrour (again) and Prof. Sylvain Bourdel from Université Grenoble Alpes, and Prof. René Côté and Prof. Louis Taillefer from Université de Sherbrooke, for their guidance and valuable feedback on my work which allowed me to evolve, as well as to overcome certain obstacles.

I would like to express my warmest thank you to all the people who participated in this research project and contributed to the data presented in this thesis. I would like to especially express my sincere gratitude to Dr. Felix Beaudoin and Dr. Pericles Philippopoulos from Nanoacademic Technologies for their collaboration on the QTCAD device simulations. I am deeply grateful for all the valuable advice and fruitful conversations that allowed me to understand my data, your quick response to my questions, and the trainings on QTCAD either remotely or in person. The experience of working with such excellent professionals like yourselves has taught me so much. Finally, I specifically would like to thank Dr. Pericles Philippopoulos for performing the QTCAD simulations on the second generation of the quantum dot device by himself while I was busy writing my thesis, thus helping to complete this particular study.

I would also like to express my gratitude to all my colleagues for all the support they provided me with during these four years. I would like to thank my colleagues from STMicroelectronics and more specifically, Philippe Cathelin for all the scientific conversations, Gaëlle Masseboeuf for the training in C2M software, Clément Charbuillet for the IT support, Christian Gardin for the numerous discussions on OFDEC simulations and for validating my design for fabrication despite the design rules violations, Franck Arnaud for his support on my layout and MPW fabrication, Alexis Poulin and Kevin Tournon for their support in sample packaging, and Nicolas Guitar for the training in TCAD Process software. In addition, I would like to thank Mamadou Diallo from TIMA for his support in my first layout design. Finally, I would like to thank Prof. Dominique Drouin from Université de Sherbrooke for his support throughout this thesis, Dany Lachance-Quirion for all the valuable lessons I learned from him, even though we did not work together for a long time, Michael Lacerte for all technical support and various trainings in the laboratory, Christian Lupien for his support during my measurements and all productive discussions that allowed me to overcome so many challenges, and Bobby Rivard and Stéphane Pelletier for the excellent organisation and the on-time delivery of the liquid helium I needed daily.

I would also like to express my warmest thank you to all the people that brightened up my working days, with who I shared lunch and coffee breaks, in France or in Canada, and some of whom became dear friends. In particular, I would like to thank, from STMicroelectronics and TIMA, Joao Henrique Quintino Palhares, Giovani Crasby Britton Orozco, Louise De Conti, Mohammed Tmimi, Renan Lethiecq, Valérian Cincon, Geoffrey Delahaye, Tarun Chawla, Thomas Capelli, Guillaume Tochou, Franck Sabatier, Dayana Pino Monroy, Raphael Guillaume, Florian Voineau, David Gaidioz, Romane Dumont, Imadeddine Bendjeddou, Sana Ibrahim, Ankush Mamgain, Ayoub Naoui and Mohamed Khalil Bouchoucha. I would also like to thank, from Institut quantique, Marc-Antoine Roux, Sara Turcotte, Zhiren Wang, Sophie Rochette, Julien Camirand-Lemyre, Mathieu Moras, Pierre Lefloïc, Amélie Lacroix, Joffrey Rivard, Claude Rohrbacher, Martin Schnee, Samuel Desrosiers, Jessica Lemieux, Laurine Marian, Maxime Tremblay, Jean-Olivier Simoneau, Alexandre Rousseau, Marie-Eve Boulanger, Clément Godfrin, Benjamin Bureau, Pierre-Olivier Downey, Clément Girod, Chloé-Aminata Gauvin-Ndiaye, Agustin Di Paolo, Maxime Lapointe Major, Camille le Calonnec, Vishnu Narayanan, Charles Paradis, Maxime Plourde and Nouédyn Baspin.

I am so grateful for all the support and encouragement of my family. Without all your love and support I would not have made it. Mom, thank you for making the impossible possible and for teaching me to be strong. Dad, when I started this project, I was reading scientific papers next to your bed in the hospital. I am so happy that you are still with us today. Thank your being there for me in the way that you can. I also thank from the bottom of my heart my brothers and sister I never had, my cousins. Harry, Poppy and Menios, you helped me go through some of the hardest times.

I am also profoundly thankful for all the amazing and unforgettable people from Greece, France, and Canada, whose presence has made my life more beautiful during these four years. Eva, Konstantina and Alkistis, you are a constant source of inspiration for me, in your own personal way. Katerina, our conversations helped me put my thoughts in order and find peace of mind. Panos, your music always helps me to concentrate when I am working. Antonis, of all the exciting adventures we shared together, thank you most of all for making last summer in Athens so much more fun by being my writing partner while I was writing my thesis. Dorina and Nikolas, although we all live in different countries now, you are forever in my heart my family from Grenoble. Nikos, thank you for making me discover new places in the (any) city. Sebastien, Alexia, Jovian, Suzy, Romy and Martina, thank you for all the hikes, drinks, game nights, horse riding in the mountains, last year's COVID-themed international Christmas dinner (yayyy), travelling and all the beautiful memories. Nefeli, Andreas, Sofia, thank you for the fun movie and pizza nights. Georges, thank you for this wonderful friendship and your brilliant idea to surprise me with an improvised lasagna/birthday cake for my birthday in the first week of the very first lockdown. Matthieu, thank you for your kindness and generosity. Loïc, thank you for reminding me that enjoying life should come naturally and easily. Thank you also, Jose, Michael, Mirenia, Nikolas, Irene, Chryssa, Hugo, Dimitris, Sofia, Giorgios, Theano, Christoforos, Christina, Romeo, Titiksha, Jorge, Wanda, Ulysses, Adela, Kimberly, Renato, Raphael, Camille, Quentin, Valentine, Jessica, Eloïse, Benoît, Pierre-Emmanuel, Antonio, Elyssa, Alessandro, Virginie, Noé, Viktoriia, Anthony, Giverny and Sophie, for all the wonderful moments we shared.

Lastly, I will end by thanking my life partner with whom I share the same curiosity and passion for constant learning and personal growth. Merci, mon Luca. Thank you for understanding me like no one else and for standing by my side in every one of my choices, even when it is not easy. Thank you for your unconditional support, from the very beginning of this journey till the very end, no matter what.

# Contents

| 1 | INTRODUCTION 1 |                  |                                                                                                                                       |  |  |

|---|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 1.1            | Limits           | s of microelectronics 1                                                                                                               |  |  |

|   | 1.2            | Quant            | tum computing era                                                                                                                     |  |  |

|   | 1.3            | Silicon          | n spin qubits                                                                                                                         |  |  |

|   | 1.4            | Scalin           | g up challenges                                                                                                                       |  |  |

|   | 1.5            |                  | emic and industrial landscape                                                                                                         |  |  |

|   | 1.6            | Bridg            | ing the gap: STMicroelectronics' approach 10                                                                                          |  |  |

|   | 1.7            |                  | s outline $\ldots \ldots 12$ |  |  |

| 2 | TEC            | HNOLO            | GY AND INTEGRATION FLOW 15                                                                                                            |  |  |

| - | 2.1            |                  | n UTBB FD-SOI technology                                                                                                              |  |  |

|   | 2.2            |                  | $ration flow \dots \dots$       |  |  |

|   |                | 2.2.1            | Test chip design                                                                                                                      |  |  |

|   |                | 2.2.2            | OFDEC simulation software                                                                                                             |  |  |

|   |                | 2.2.3            | TCAD Process simulation software   25                                                                                                 |  |  |

|   |                | 2.2.4            | QTCAD simulation software                                                                                                             |  |  |

|   |                | 2.2.5            | MPW fabrication                                                                                                                       |  |  |

|   |                | 2.2.6            | Sample preparation                                                                                                                    |  |  |

|   |                | 2.2.7            | Sample characterization                                                                                                               |  |  |

|   |                | 2.2.8            | Data analysis                                                                                                                         |  |  |

|   |                | 2.2.9            | Failure analysis                                                                                                                      |  |  |

|   |                | 2.2.10           | Optimization loop                                                                                                                     |  |  |

|   | <b>2.3</b>     |                  | ter summary                                                                                                                           |  |  |

| 3 | Спл            | DACTE            | RIZATION METHODS FOR QUANTUM DOT SYSTEMS 35                                                                                           |  |  |

| 5 | СпА<br>3.1     |                  | ground                                                                                                                                |  |  |

|   | 0.1            | 3.1.1            | 2D electron gas model                                                                                                                 |  |  |

|   |                | 3.1.1            | Single quantum dot                                                                                                                    |  |  |

|   |                | 3.1.3            | Constant interaction model                                                                                                            |  |  |

|   |                | 3.1.4            | Weak coupling regime                                                                                                                  |  |  |

|   |                | 3.1.4            | Coulomb blockade effect                                                                                                               |  |  |

|   |                | 3.1.6            | Coulomb blockade diamonds                                                                                                             |  |  |

|   |                | 3.1.7            | Sequential tunneling transport                                                                                                        |  |  |

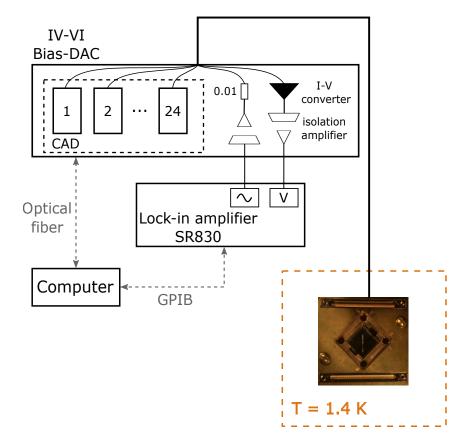

|   | 3.2            |                  | rimental aspects                                                                                                                      |  |  |

|   | 0.4            |                  |                                                                                                                                       |  |  |

|   |                | 321              | Cryogenic measurement systems 47                                                                                                      |  |  |

|   |                | $3.2.1 \\ 3.2.2$ | Cryogenic measurement systems                                                                                                         |  |  |

| 4        | HAL        | L EFFECT MEASUREMENTS AT CRYOGENIC TEMPERATURES    | 59  |

|----------|------------|----------------------------------------------------|-----|

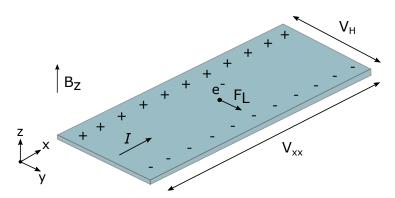

|          | 4.1        | Background                                         | 60  |

|          | 4.2        | Presentation of the device                         | 61  |

|          | <b>4.3</b> | Experimental setup                                 | 62  |

|          | 4.4        | Hall effect measurements                           | 64  |

|          | 4.5        | Chapter summary                                    | 72  |

| <b>5</b> | Une        | DERSTANDING CONDITIONS FOR THE FEW-ELECTRON REGIME | 73  |

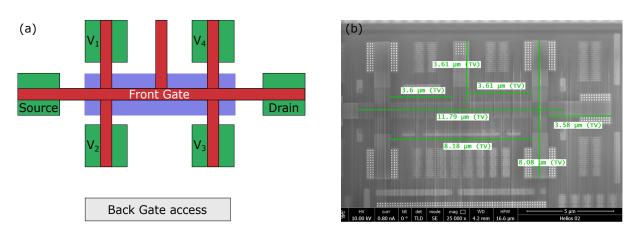

|          | 5.1        | Presentation of the device                         | 74  |

|          | <b>5.2</b> | QTCAD model for the split-gate device              | 75  |

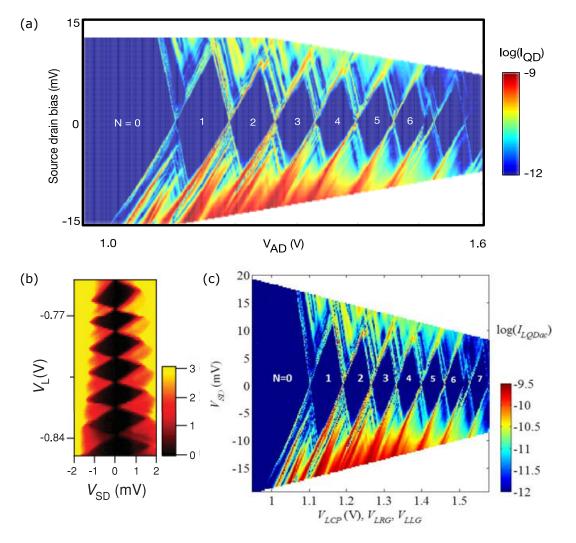

|          | <b>5.3</b> | Back gate transport activation                     | 79  |

|          | <b>5.4</b> | Side-gate activated corner quantum dots            | 80  |

|          | <b>5.5</b> | Requirements for the few-electron regime           | 83  |

|          | 5.6        | Chapter summary                                    | 86  |

| 6        | Exp        | LORATION OF THE LIMITS OF THE $28$ NM NODE         | 89  |

|          | 6.1        | Physical limits of the 28 nm node                  | 90  |

|          | 6.2        | Presentation of the device                         | 92  |

|          | 6.3        | Precision of the gate pitch                        | 93  |

|          | <b>6.4</b> | QTCAD device simulation                            | 96  |

|          | <b>6.5</b> | Device physical analysis                           | 99  |

|          | 6.6        | Device characterization                            | 103 |

|          | 6.7        | Chapter summary                                    | 108 |

| 7        | Con        | ICLUSION AND PERSPECTIVES                          | 109 |

BIBLIOGRAPHY

# Abbreviations

| IC<br>CMOS<br>ESR | Integrated Circuit<br>Complementary Metal-Oxide-Semiconductor<br>Electron Spin Resonance |

|-------------------|------------------------------------------------------------------------------------------|

| SET               | Single Electron Transistor                                                               |

| FD-SOI            | Fully Depleted Silicon-On-Insulator                                                      |

| MOSFET            | Metal-Oxide-Semiconductor Field-Effect Transistor                                        |

| UTBB              | Ultra-Thin Body and Buried oxide                                                         |

| SOI               | Silicon-On-Insulator                                                                     |

| CMP               | Chemical Mechanical Polishing                                                            |

| BOX               | Buried OXide                                                                             |

| LVT               | Low Threshold Voltage                                                                    |

| RVT               | Regular Threshold Voltage                                                                |

| SG                | Standard Gate oxide                                                                      |

| EG                | Extended Gate oxide                                                                      |

| EOT               | Equivalent Oxide Thickness                                                               |

| LDD               | Lightly Doped Drain                                                                      |

| STI               | Shallow Trench Isolation                                                                 |

| BEOL              | Back-End-Of-Line                                                                         |

| VIA               | Vertical Interconnect Access                                                             |

| BG                | Back Gate                                                                                |

| S                 | Source                                                                                   |

| D                 | Drain                                                                                    |

| I/O               | Input/Output                                                                             |

| ÉSD               | Electro-Static Discharge                                                                 |

| FEOL              | Front-End-Of-Line                                                                        |

| LVS               | Layout Versus Schematic                                                                  |

| DRC               | Design Rules Check                                                                       |

| DRM               | Design Rules Manual                                                                      |

| GAGS              | Gds Acceptance Gating Script                                                             |

| OFDEC             | Optical Friendly DEsign Check                                                            |

| C2M               | CAD-to-Mask                                                                              |

| CAD               | Computer-Aided Design                                                                    |

| FEM               | Finite Element Modeling                                                                  |

| TCAD              | Technology Computer-Aided Design                                                         |

| QTCAD             | Quantum TCAD                                                                             |

|                   | Y aminani i Orilo                                                                        |

| MPW  | Multi-Project Wafer                       |

|------|-------------------------------------------|

| FOUP | Front Opening Unified Pod                 |

| TEM  | Transmission Electron Microscopy          |

| FLGA | Fine pitch Land Grid Array                |

| PCB  | Printed Circuit Board                     |

| SEM  | Scanning Electron Microscope              |

| 2DEG | Two-dimensional electron gas              |

| VTI  | Variable Temperature Insert               |

| SMU  | Source-Measurement Unit                   |

| FIB  | Focused Ion Beam                          |

| FGT  | Front Gate Top                            |

| FGB  | Front Gate Bottom                         |

| DOS  | Density Of States                         |

| QD   | Quantum Dot                               |

| RET  | Resolution Enhancement Techniques         |

| NA   | Numerical Aperture                        |

| OPC  | Optical Proximity Correction              |

| STEM | Scanning Transmission Electron Microscope |

|      |                                           |

## Introduction

#### 1.1 Limits of microelectronics

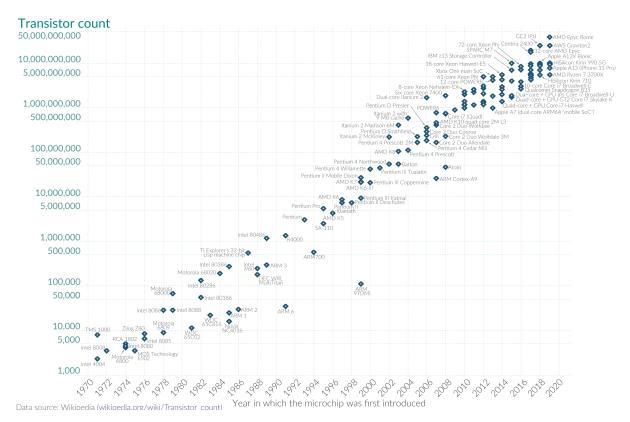

In 1965, Gordon Moore, co-founder of Intel, would publish one of the most famous papers ever written about the evolution of the microelectronics industry in the world. In this seminal paper [1], he predicted that the number of transistors in a dense Integrated Circuit (IC) would double every year, and in 1975, he revised his prediction to doubling every two years [2]. Moore's prediction evolved into Moore's law, describing an exponential growth in computing power (Figure 1.1). Thereby, the improvements in processor speed revolutionized information technology and transformed governments, industry, societies and culture.

Figure 1.1 – Transistor density on integrated circuits versus calendar year. Image taken from our worldindata website<sup>1</sup>.

#### CHAPTER 1 INTRODUCTION

However, it is estimated that miniaturization of semiconductor technologies will face technical limitations as transistors approach the size of atoms. Based on Moore's statements from his publication, as long as the minimum device sizes are not limited by fundamental considerations as the electron charge or the atomic structure of matter, "there is no present reason to expect a change in the trend". Until now, technological innovations, driven by the needs of societies in today's generations, permitted to scale down foundry-fabricated transistor dimensions to only a few tens times the size of a silicon atom, i.e. 0.2 nm [3].

Intel, Samsung, and TSMC are currently the major world-leading companies in the semiconductor technology. Intel's 14 nm technology is currently used for mass production<sup>2</sup> and its 7 nm node is expected to be introduced by 2023. Since 2019, the 5 nm process tools of Samsung and TSMC are available to potential customers for 300 mm chip mass production. In addition, commercial chip volume manufacturing using 3 nm fabrication processes has started only very recently by Samsung<sup>3</sup> and TSMC<sup>4</sup>, whereas both have promised to start production based on the 2 nm technology node by 2025.

With Complementary Metal-Oxide-Semiconductor (CMOS) technology scaling to smaller and smaller dimensions close to the size of a silicon atom, soon purely quantum effects, such as energy quantization or quantum tunneling, will therefore degrade the proper performance of the device and a decrease, or a plateau, in computational power might be noted soon.

#### 1.2 Quantum computing era

Instead of considering quantum effects as an issue that needs to be tackled, the principles of quantum mechanics could be leveraged to process information. Indeed, quantum computing, based on Alan Turing's legacy, the Turing machine [4], first considered in Richard Feynman's paper published in 1982 [5] and then established by David Deutsch in 1985 [6], harnesses the properties of quantum mechanics and promises to revolutionize several scientific and technological fields. Today, small-scale quantum processors are being used to run quantum algorithms and demonstrate the potential of future large-scale systems [6, 7]. Compared to its classical counterpart, a quantum computer guarantees an exponential improvement in calculation times and promises to solve computation problems considered notoriously difficult even for today's most powerful supercomputers [8, 9].

The most known examples of these unsolvable problems include integer factorization, combinatorial optimization problems, and simulation of quantum systems. Shor's quantum algorithm [10] was introduced in 1994 as an answer to the first challenge, by presenting an efficient way to find the prime factors of an integer and made a big impact

<sup>&</sup>lt;sup>1</sup>https://ourworldindata.org/technological-change

<sup>&</sup>lt;sup>2</sup>https://www.intel.ca/content/www/ca/en/silicon-innovations/intel-14nm-technology. html

$<sup>^{3} \</sup>tt https://semiconductor.samsung.com/newsroom/news/samsung-begins-chip-production-\using-3nm-process-technology-with-gaa-architecture/$

<sup>&</sup>lt;sup>4</sup>https://www.tsmc.com/english/dedicatedFoundry/technology/logic/1\_3nm

#### 1.2 QUANTUM COMPUTING ERA

on present cryptography [11, 12]. Grover's quantum algorithm, developped in 1996, introduced a novel way to search through unstructured data [13], with broad applications in various fields, such as machine learning, artificial intelligence, software engineering or applied mathematics [14]. Last, several studies to date are focused on the development of quantum algorithms for analysing and predicting the properties of nature, with broad applications including drug discovery and design [15], novel methodologies for medicine development [16] or optimization of energy consumption [17].

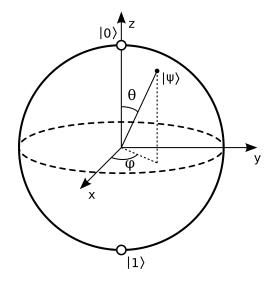

The building block of a classical computer is a bit which can take two discrete values, either 0 or 1. In the proposal of a quantum computer, quantum information is encoded in the so-called quantum bit or qubit, which exploits the principles of quantum mechanics, such as states superposition or quantum entanglement, to perform quantum computation operations using quantum algorithms. The state of a single qubit is described by a two-dimensional quantum state vector  $|\Psi\rangle$  which in the two-dimensional complex Hilbert space is writen as

$$|\Psi\rangle = \alpha |0\rangle + \beta |1\rangle, \qquad (1.1)$$

where the complex numbers  $|\alpha|^2$  and  $|\beta|^2$  are the probabilities for the qubit to be in the  $|0\rangle$  state or the  $|1\rangle$  state, respectively, satisfying  $|\alpha|^2 + |\beta|^2 = 1$ .

By translating these coefficients to the two angles  $\theta$  and  $\phi$ , a single-qubit quantum state can be represented as a three-dimensional real-valued vector. This new representation can be visualized in Figure 1.2. In the framework of this so-called Bloch sphere [18], the state of a single qubit is described by  $|\Psi\rangle = \cos\frac{\theta}{2}|0\rangle + e^{i\phi}\sin\frac{\theta}{2}|1\rangle$  and corresponds to a single point on the spherical surface.

Figure 1.2 – The quantum state  $|\Psi\rangle$  of a single qubit depicted on a Bloch sphere. Image taken from wikipedia website<sup>5</sup>.

In 2000, David P. DiVincenzo proposed the main requirements for the physical implementation of the hardware needed by a quantum computer. These are known as the

<sup>&</sup>lt;sup>5</sup>hrefhttp://en.wikipedia.org/wiki/

DiVincenzo's criteria [19], and are the following:

1. A scalable physical system with well characterized qubits

- 2. The ability to initialize the state of the qubits to a simple fiducial state

- 3. Long relevant decoherence times, with respect to the gate operation time

- 4. A "universal" set of quantum gates

- 5. A qubit-specific measurement capability

#### **1.3** Silicon spin qubits

Even though no full-fledged quantum computer has not been realized yet, several physical systems are currently explored for the realization of a quantum processor, such as superconducting circuits [20, 21], trapped ions [22, 23], optical lattices [24] and many more. Each approach focuses on fulfilling DiVincenzo's criteria and aims to provide a robust device able to process quantum information reliably. Among the most promising candidates, silicon spin qubits have attracted a wide interest [25].

The spin-based qubit architecture was first proposed in two seminal papers in 1998 in two different approaches [26, 27]. In a system based on the first approach, quantum information is encoded in the states of individual spins of electrons or holes confined in quantum dots hosted in semiconductor nanostructures [28]. In a system based on the second approach though, information is encoded in the states of individual spins of electrons or nuclei of dopant atoms introduced in the semiconductor devices [29, 30, 31, 32]. In such systems, there are two spin states in total, which are commonly referred to as 'spin up' and 'spin down'. Thus, such two-level systems are ideal for quantum information processing and the two states of a single qubit  $|0\rangle$  and  $|1\rangle$  are implemented by the spin orientation.

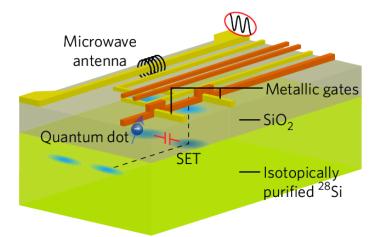

An example of a silicon spin qubit device is illustrated in Figure 1.3. The structure depicted here was fabricated on isotopically purified <sup>28</sup>Si and is presented in [33]. The design of the device has been simplified in the schematic shown here for illustration purposes. In this approach, the confinement is achieved by forming a quantum dot at the  $Si/SiO_2$  interface via electrostatic gates patterned on the top side of the structure. Moreover, additional gate electrodes serve to control the tunnel barrier between the quantum dot and its nearby environment. More specifically, when the device is appropriately biased, a 2DEG is formed in the silicon channel and electrons tunnel through the potential barriers. Then, by controlling carefully the voltages applied to the gates, a single electron is trapped in the quantum dot and is exploited for the implementation of a single qubit.

In this particular example, the manipulation of the qubit state is achieved by Electron Spin Resonance (ESR) pulses generated by an external applied magnetic field. In this manner, due to the Zeeman effect, the energy levels of the confined electron are separated into the two spin states, which are used as the two qubit states. In general, this energy

#### 1.3 SILICON SPIN QUBITS

splitting is at the range of a few and tens of gigahertz. Hence, by applying an oscillating magnetic field, via a co-integrated microwave antenna close to the qubit, with a frequency corresponding to this energy difference, quantum computation operations are performed on the qubit. In addition, a Single Electron Transistor (SET) device is used for charge sensing, and is integrated close to the quantum dot and capacitively coupled to it. The SET is a sensitive electronic device which is able to detect single electron changes in the dot occupancy.

Figure 1.3 – Schematic representation of a silicon-based spin-qubit device fabricated on isotopically purified <sup>28</sup>Si presented in [33]. The gate patterns are simplified in the schematic for narrative purposes. A single electron is confined in a quantum dot, formed at the Si/SiO<sub>2</sub> interface and controlled by metal top-gates, depicted in yellow and orange, which are isolated between them. Readout of the charge state of the dot is performed by a top-gate SET. Electrons are manipulated by ESR pulses generated from a microwave antenna. Image adapted from [34].

Reference [35] is an excellent review to introduce spin-based qubits and their advantages comparing to other candidate technologies for quantum information processing. Indeed, silicon spin-based qubits rise to the top thanks to three main advantages: high operating temperatures, small footprint, and long coherence times. More specifically, most energy scales in both atomic and artificial systems are large enough to allow for operations at a few kelvin, which turns to be a high temperature for most solid-state qubits. Operation of a spin-based quantum processor at such temperatures would reduce significantly the complexity of the control and measurement system. In addition, strong carrier confinement is required so that the lowest orbital energy levels are well isolated from higher-energy electronic states, resulting in small dimensions for silicon qubit devices, compared to other alternatives, which makes them similar in size to the transistors composing today's classical computer chips, allowing to envision dense arrays of spin qubits. Last but not least, natural silicon can be isotopically purified to <sup>28</sup>Si eliminating nuclear spin, which causes decoherence to the electron spins, and resulting in significantly improved qubit coherence time [36, 37].

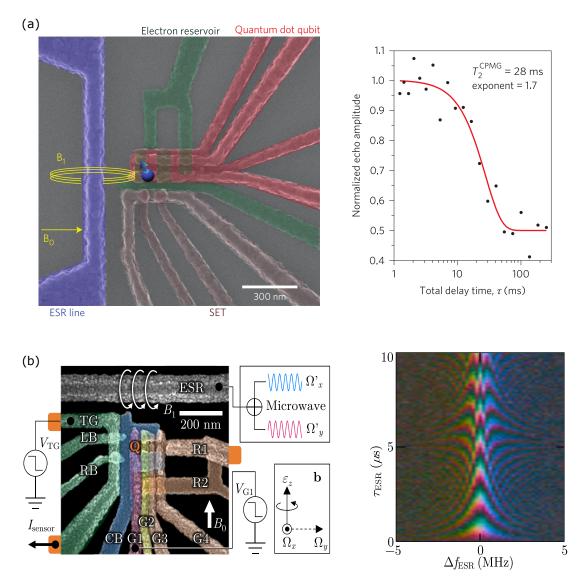

As presented in Figure 1.4, the state-of-the-art of the coherence of a single electron spin confined in a  $^{28}$ Si structure attained tens of milliseconds [33]. Moreover, the highest

#### CHAPTER 1 INTRODUCTION

reported single-qubit fidelity in silicon is 99.96% [38]. The fidelity is a metric widely used to express the quality of the control obtained over the qubit state and is targeted to be higher than 99% in quantum computing systems. In order to achieve a universal gate set and satisfy one of DiVincenzo's criteria, the operation of two or more qubits together is necessary. Recently it has been demonstrated that two-qubit operation can be performed with a fidelity of  $(99.65 \pm 0.15)\%$  [39, 40, 41]. Furthermore, the remarkable technological breakthrough of the experimental demonstration of a spin qubit device operating at 1.5 K reported a few years ago permits to envision device performance at much higher temperatures than other solid-state qubits that require a sub-kelvin environment [42].

Finally, the most striking feature of this technology is the ability that it offers to exploit the advanced mass-production processes from the field of microelectronics that have undergone a decades-long trajectory of development and standardization. In combination with the recent demonstration of a six-qubit quantum processor [43], the CMOS compatibility paves promising avenues not only for the accelerated improvement of single-qubit architectures, but also for scaling up to larger numbers of qubits [35, 44, 45, 46]. For more information on the key advantages of semiconductor spin qubits in general, the reader is referred to [47, 48, 49].

#### 1.4 Scaling up challenges

The CMOS compatibility permits to envision the mass-production of spin qubit devices in silicon foundry facilities of modern computer industries [50, 51, 52]. Fabrication yield and qubit uniformity are expected to benefit from industrial efforts to manufacture quantum dot arrays using the well-matured processes and techniques from the microelectronics industry [53]. In the remainder of the section, the discussion is focused on gate-defined quantum dot qubits in CMOS structures, which is more relevant than other approaches to the work presented in this thesis.

#### CMOS quantum dot qubits

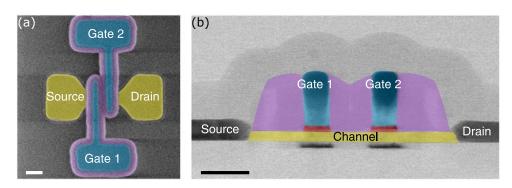

The first CMOS-based hole qubit device is presented in Figure 1.5 [54]. The structure was manufactured using non-standard process methods. Manipulation of the energy landscape in the device was realized through the manipulation of the electrostatic potential formed in the silicon substrate using gate electrodes.

Despite the aforementioned milestones that have been achieved with small-scale qubit structures in silicon, scalable qubit architectures that could enable future quantum computers still remain an issue. In fact, qubit-to-qubit interactions can only occur between the closest neighboring qubits and can currently occur in a range of a few tens of nanometres. The implementation of large-scale quantum computing systems requires qubit connectivity over much larger distances. To this end, linear and bilinear arrays of quantum dots are being explored [44, 45, 53, 55, 56], but no standard-process CMOS technology platforms exist today that could deliver such a 2D gate array design using exclusively industrial

#### 1.4 Scaling up challenges

methods.

Finally, in order to accelerate the evolution marked in qubit performance, device modeling leading to optimized fabrication processes and faster overall turnaround times is also necessary. To date, different empirical simulation tools exist which have only been used though for the interpretation of experimental data in order to analyze different qubit parameters [57, 58, 59].

Figure 1.4 – (a) Coherence time of a single quantum dot qubit reaching tens of milliseconds. Image adapted from [33]. (b) Single-qubit control fidelity exceeding 99.96% in a quantum dot spin qubit architecture. Image adapted from [38].

#### CHAPTER 1 INTRODUCTION

Figure 1.5 - (a) False-colored top-view and (b) cross-section of the first CMOS hole spin qubit device. Image taken from [54].

#### Co-integration with control electronics

In contrast to solid-state qubits which are in most cases operated at cryogenic temperatures approaching the absolute zero, conventional electronics used to initialize, manipulate and readout their state produce a lot of heat and thus need to be kept outside of the cryogenic system and far from the qubit. Moreover, a large-scale quantum computer will eventually need millions of qubits with massive yet very precise control electronics for the manipulation and readout of each qubit and this brute-force approach will no longer be practical. The heat and noise introduced by current room-temperature rack-mounted instruments and few metres long filtered and thermally anchored connecting cables will rapidly be a major issue.

Moreover, extremely high performance is required from the control electronics in terms of bandwidth, fast response times, and noise, in order to ensure accuracy and speed in the manipulation and readout of the qubits [60]. Solutions to this crucial engineering challenge and wiring bottleneck for the closer integration or, even better, on-chip co-integration of classical control and readout electronics with qubit systems have been explored [61, 62, 63, 64, 65]. In fact, the CMOS compatibility permits for closer, or even on-chip, cointegration of spin qubit platforms with the readout and control circuitry fabricated based on standard-process CMOS technology optimized for cryogenic-temperature operation, namely cryo-CMOS, leading to a more compact quantum processor [66, 67, 68, 69, 70]. In this way, a drastic reduction of the complex interconnections between the cryogenic system and the room-temperature measurement electronics can result in enhanced compactness and reliability.

#### 1.5 Academic and industrial landscape

The global effort driving research and development in quantum sciences and technologies is continuously increasing with current investments reaching nearly USD 30 billion worldwide in  $2022^6$ . More specifically, Australia has invested AUD 130 million through

<sup>&</sup>lt;sup>6</sup>https://qureca.com/overview-on-quantum-initiatives-worldwide-update-2022

#### 1.5 Academic and industrial landscape

federal funding in two centres of excellence conducting world-leading research in quantum information, i.e. the Australian Research Council Centre of Excellence for Engineered Quantum Systems and the Centre of Excellence for Quantum Computation and Communication Technology of the University of New South Wales [71]. The Netherlands has invested EUR 135 million in QuTech, the quantum technology institute of the TU Delft, and TNO (Netherlands Organisation for Applied Scientific Research)<sup>7</sup>. The UK has invested more than GBP 1 billion and has established a National Quantum Computing Centre<sup>8</sup> [72]. The European Commission allocated EUR 1 billion of funding to launch the European Quantum Flagship<sup>9</sup>. The French government recently launched an investment plan worth EUR 1.8 billion in quantum technologies<sup>10</sup>. The Canadian government has invested almost CAD 1.4 billion to date and has launched a National Quantum Strategy to accelerate innovation and commercialisation in quantum technologies [73]. The US government established the National Quantum Initiative Act with a USD 1.2 billion budget which will go to institutes such as the National Institute of Standards and Technology (NIST), in order to accelerate the growth of quantum technologies by collaborating with academic institutions and private industry [74].

A few more of these main research centres and institutions participating in the international effort towards a compact spin-based quantum processors are the University of Tokyo in Japan, Harvard University in the United States, and the MOS-Quito project, a European project focused on developing CMOS-based spin qubits which was completed a few years ago. This list is not exhaustive and contains only some of the main programs and efforts in the global ecosystem. Major contributions have also come from spin qubits research groups at CEA-Leti and CNRS in France, Princeton University, Quantum Information Science and Technology at Sandia National Laboratories in the US.

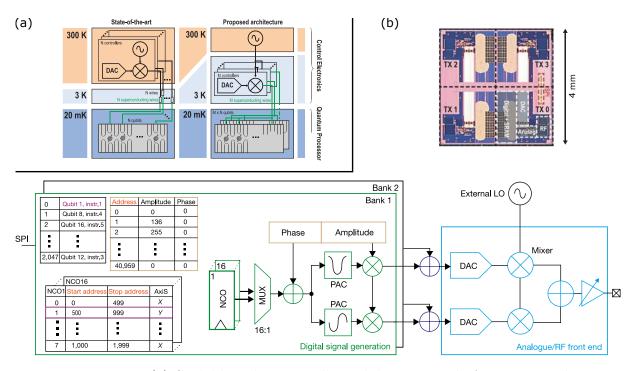

Moreover, several industry leaders in modern computer technology are now participating in the race for quantum supremacy<sup>11</sup>. For instance, IBM is currently exploring qubit systems based on silicon quantum dots, despite the fact that their approach to quantum computers is mainly focused on superconducting qubits [75]. Also, Hitachi Cambridge Laboratory and HRL Laboratories are focused on the study of silicon quantum dot qubits [76, 77]. Moreover, Intel is collaborating with QuTech and is not only focused on developing spin qubits, but also on their co-integration with control electronics (Figure 1.6(a)). Their work on the latter involved the implementation and characterization of a CMOS control electronics architecture operating at 3K while being coupled to a 20 mK qubit [78, 79]. In fact, the first version of this compact cryo-CMOS control chip, illustrated in Figure 1.6 (b) and code-named Horse Ridge, was used for single-qubit readout with a fidelity of 97%.

<sup>&</sup>lt;sup>7</sup>https://www.delta.tudelft.nl

<sup>&</sup>lt;sup>8</sup>https://www.gov.uk/government/news

<sup>&</sup>lt;sup>9</sup>https://qt.eu/about-quantum-flagship/introduction-to-the-quantum-flagship

<sup>&</sup>lt;sup>10</sup>https://www.lemonde.fr/politique/article/2021/01/21

<sup>&</sup>lt;sup>11</sup>https://physicsworld.com/a/silicon-spin-qubits-manufactured-on-an-industrial-scale

CHAPTER 1 INTRODUCTION

Figure 1.6 – (a) Scalable qubit controller exhibiting a wide frequency and output power range suitable for multiple qubit technologies proposed by [78]. Image taken from [78]. (b) Cryogenic CMOS control chip operating at 3K, designed to manipulate and readout silicon quantum dot qubits at 20 mK. Image taken from [79].

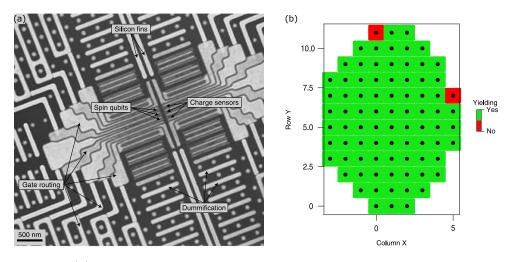

In addition, Intel and QuTech recently achieved an important milestone by demonstrating the first spin qubit using all-optical lithography techniques [80]. The qubit device, presented in Figure 1.7, was fabricated on a 300 mm wafer that demonstrated a fabrication yield of up to 98%, with only two devices not fully functioning. In parallel, several other quantum computing start-up companies and R&D centers are focused on siliconbased quantum hardware including Photonic Inc. in Canada[81, 82], Equal1 Laboratories in Ireland and in the US[83, 84], Quantum Motion in the UK[85, 86], Imec in Belgium [87], Silicon Quantum Computing [88, 89], and, the newly founded start-up companies, Diraq in Australia and Siquance in France.

#### 1.6 Bridging the gap: STMicroelectronics' approach

In the meantime, the microelectronics industry continues to grow and revenues from semiconductor manufacturing have reached hundreds of billions of dollars worldwide over the last few years<sup>12</sup>. In this context, two of the world leaders in the semiconductor sector, STMicroelectronics and GlobalFoundries Inc., are teaming up to build a 300 mm silicon manufacturing facility in France<sup>13</sup>, adjacent to STMicroelectronics' existing 300 mm fa-

<sup>&</sup>lt;sup>12</sup>https://www.semiconductors.org/policies/tax/market-data/?type=post

<sup>&</sup>lt;sup>13</sup>https://www.lemonde.fr/economie/article/2022/07/11/semi-conducteurs-globalfoundries -et-stmicroelectronics-annoncent-la-construction-d-une-usine-a-grenoble\_6134256\_3234 .html

#### 1.6 BRIDGING THE GAP: STMICROELECTRONICS' APPROACH

cility in Crolles<sup>14</sup>. The project has leveraged multi-billion euro collaborative investments including significant financial support from the French government, and this jointly operated facility targets to reach full capacity by 2026, with production of up to 620000 wafers per year. It is indeed a prosperous time for microelectronics industry and all this interest will lead to improvements in materials, manufacturing equipment and processes which could drastically benefit quantum computing hardware research, and more specifically the development of high-quality CMOS-based spin qubit systems.

Figure 1.7 - (a) First industrially fabricated quantum dot spin qubit using all-optical fabrication methods. (b) Reported fabrication device yield up to 98%. Image taken from [79].

The development of a scalable quantum dot architecture that can be integrated into industrial manufacturing processes is of major importance for the realization of largescale high-performance quantum processors. In this perspective, this study is focused on evaluating the potential of different architectures designed and fabricated using the industry-standard process 28 nm Fully Depleted Silicon-On-Insulator (FD-SOI) technology, which has already demonstrated functional operation at cryogenic temperatures [90, 91, 92, 93, 94], managing to combine the advantages of the current state-of-the-art quantum dot architectures and the mass-production industry techniques.

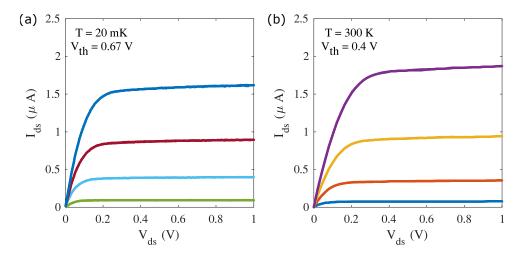

The purpose of this PhD thesis is to continue the investigation that started in 2015 in the framework of the collaboration between STMicroelectronics and Institut quantique of the Université de Sherbrooke. Aiming to explore industrial architectures for the implementation of quantum-dot single spin qubits, a modified Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) structure was characterized at cryogenic temperatures, demonstrating improved maximal carrier mobility, power dissipation and sub-threshold swing compared to room temperature operation [95, 96, 97]. In Figure 1.8, the I-V characteristic curve is shown in the case of transistor operation both at 20 mK and room temperature. This measurement permitted to characterize the technology platform fabricated using exclusively industrial techniques at deep cryogenic temperatures, allowing to

<sup>&</sup>lt;sup>14</sup>https://www.lemonde.fr/economie/article/2022/09/18/en-france-un-investissement-his torique-de-16-milliards-d-euros-dans-la-filiere-electronique\_6142152\_3234.html

envision co-integration of a CMOS-based qubit architecture with its control block technology.

Figure 1.8 – Cryogenic temperature characterization of a modified transistor device fabricated using STMicroelectronics' industry-standard CMOS fabrication processes. (a) I-V characteristic extracted at 20 mK for different values of the voltage applied to the gate varying from 0.65 V0.65 V to 0.85 V by steps of 50 mV. (b) I-V characteristic extracted at 300 K for different values of the voltage applied to the gate varying from 0.5 V to 0.8 V by steps of 100 mV. Image taken from [95].

The electrostatic formation and control of silicon quantum dots in a 300 mm industrystandard process nanostructure was tested next, demonstrating much higher reproducibility in the transport properties compared to devices manufactured in academic laboratories [96, 98]. Moreover, the first steps towards the implementation of linear and matrix array quantum dot architectures with vertical gate access were achieved [98]. Therefore, the study presented in the following chapters is focused on improving the performance of this first generation of the gate-defined quantum dot devices, designed to implement electron spin qubits in silicon and fabricated using state-of-the-art mass-production methods from the field of microelectronics.

#### 1.7 **Thesis outline**

The remainder of the thesis is divided into five chapters.

In Chapter 2, the main characteristics of the technology node used for the design and fabrication of the devices developed in this work are presented. An optimized integration process flow for the implementation of quantum devices in FD-SOI, using exclusively mass-production silicon-foundry methods is presented, focusing on reducing manufacturing risks and overall turnaround times.

In Chapter 3, a summary of the theoretical and experimental aspects is given related to the characterization of single quantum dots hosted in FD-SOI nanostructures. The

#### 1.7 Thesis outline

measurement circuits and methods for the characterization of the samples at room and cryogenic temperatures via electrical transport and differential conductance measurements are presented.

In Chapter 4, the experimental data collected from measuring Hall effect FD-SOI microstructures, sharing the same substrate with the quantum dots, at 4.2 K are reported. Aiming to determine the quality of the technology node for quantum dot applications, the electron density and mobility were extracted at 4.2 K through individual or combined activation of the front and back gate of the samples.

In Chapter 5, the numerical data of the cryogenic temperature simulation of the electrical and quantum behavior of the first generation quantum dot device are presented. Proceeding to a comparison with the measurement data resulted from the characterization of the same device at the same temperature, i.e. 1.4 K, the simulations permit to explain unexpected experimental observations. The study of the first generation of quantum dot devices developed in this thesis resulted in valuable insight for the geometry and bias conditions required for reaching the few-electron regime.

In Chapter 6, the investigation of a second generation of quantum dot devices, based on the previous findings, is discussed. The optical, geometrical and quantum simulations performed on the conceived device design are presented. Optical inspection and characterization of the samples demonstrate the advantages of the FD-SOI technology over other approaches for quantum information applications, as well as the identified limitations of the 28 nm node in this context. This work paves the way for the implementation of the next generations of FD-SOI quantum dot devices based on lower technology nodes.

#### Chapter 1 Introduction

# Technology and integration flow

### Contents

| 2.1 | 28 nm UTBB FD-SOI technology 10 |                                  |    |

|-----|---------------------------------|----------------------------------|----|

| 2.2 | Integr                          | ration flow                      | 19 |

|     | 2.2.1                           | Test chip design                 | 22 |

|     | 2.2.2                           | OFDEC simulation software        | 23 |

|     | 2.2.3                           | TCAD Process simulation software | 25 |

|     | 2.2.4                           | QTCAD simulation software        | 27 |

|     | 2.2.5                           | MPW fabrication                  | 28 |

|     | 2.2.6                           | Sample preparation               | 29 |

|     | 2.2.7                           | Sample characterization          | 31 |

|     | 2.2.8                           | Data analysis                    | 32 |

|     | 2.2.9                           | Failure analysis                 | 32 |

|     | 2.2.10                          | Optimization loop                | 33 |

| 2.3 | Chapt                           | er summary                       | 33 |

2

#### CHAPTER 2 TECHNOLOGY AND INTEGRATION FLOW

In this chapter, the integration methods used to realize the microstructures and nanodevices studied in this work are presented. First, the 300 mm industry-standard process technology platform used for the physical implementation of the devices using mass production techniques is introduced. A thorough overview of the integration process flow is also provided. Although this flow was initially developed based on the technology node used in this study, there is potential for application to other technology platforms. It was continuously improved throughout this study and was optimized for short R&D cycles in the industrial context, paving the way for a large-scale spin-based qubit processor integration with a full CMOS process.

#### 2.1 28 nm UTBB FD-SOI technology

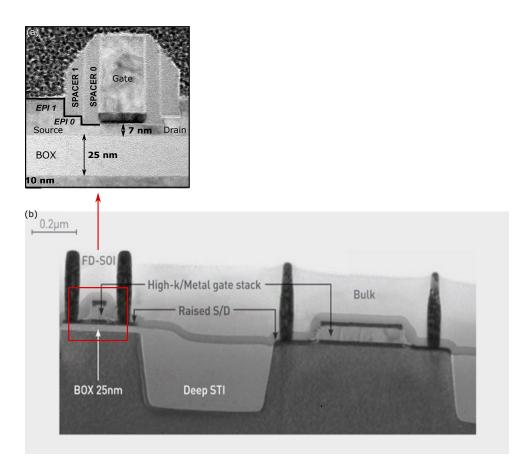

The devices in this work were designed and fabricated using STMicroelectronics' 28 nm Ultra-Thin Body and Buried oxide (UTBB) FD-SOI foundry-level technology [99, 100, 101, 102]. In this section, a typical 28 nm UTBB FD-SOI MOSFET is chosen as an example in order to discuss the main characteristics of the technology platform.

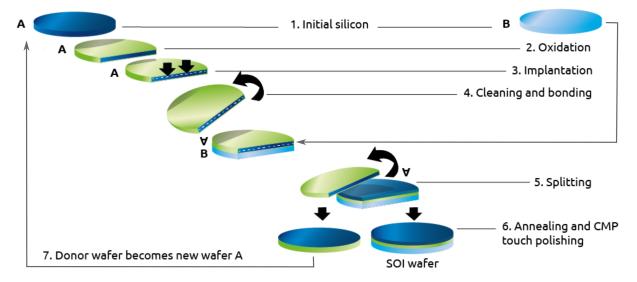

First, the SOI wafer is fabricated using the Smart Cut technology which was invented and patented in CEA-Leti and is now used for commercial mass-production of SOI wafers in Soitec [103, 104]. Based on hydrogen ion implantation and wafer bonding techniques, this method is used to first define a single thin monocrystalline layer on the top side of a wafer and then transfer it to another substrate. An overview of the process flow leading to the fabrication of an SOI wafer based on the Smart Cut technique is illustrated in Figure 2.1.

Figure 2.1 – Schematic representation of the process flow of the Smart Cut technique employed for the manufacture of SOI wafers. Image taken from the official website of Soitec.

The procedure starts with two bulk silicon wafers, wafer A or donor wafer, and wafer B. The process could also be carried out using isotopically purified silicon-28, a very

#### 2.1 28 NM UTBB FD-SOI TECHNOLOGY

promising candidate for the physical implementation of spin qubits due to its purification of excess nuclear spin (See Introduction). The upper side of the wafer A is then oxidized creating an insulating layer with an adjustable thickness corresponding to the thickness of the Buried OXide (BOX) layer of the final SOI wafer. The wafer A is thereafter subjected to a process of hydrogen ion implantation at a controlled depth below its surface depending on the implantation energy. The resulting surface roughness is a key parameter that determines the effectiveness of the back bias control and variability. Once cleaned, the wafer A is flipped over and placed on top of wafer B before both undergo a two-phase heat treatment. During the first phase, the wafer A is divided into the two parts separated by the horizontal plane defined by the implantation depth of the previous step, resulting in the creation of an SOI layer on top of wafer B. The unused part of the wafer A is recycled and will be used in a future SOI fabrication cycle. The connection between this SOI layer and wafer B is reinforced through the second phase of heat treatment. In the end, the final stages involving annealing, and Chemical Mechanical Polishing (CMP) ensure the uniformity of the newly fabricated SOI wafer, whose silicon layer thickness is adjusted to be only a few tens of nanometres by the hydrogen ion implantation energy of the previous step, leading to the key feature of FD-SOI technology, the full depletion of the silicon channel.

Like all transistors, an FD-SOI transistor has four terminals: the source, drain, gate, and back plane. Thanks to the presence of the BOX, the latter can be considered as a back gate. By polarizing the top and back gate appropriately, the conduction channel is activated allowing current to flow through the structure between the source and the drain. A typical FD-SOI transistor fabricated with a standard process manufacturing flow is operated at temperatures ranging from -40 °C to 125 °C. Table 2.1 summarizes the main characteristics of the STMicroelectronics' 28 nm UTBB FD-SOI technology node [101, 105]. More precisely, the undoped silicon channel and the BOX are 7 nm and 25 nm thick respectively, hence the name Ultra Thin Body and BOX technology. In addition, the 28 nm process refers to the minimum gate width of an FD-SOI MOSFET and is used as a basic unit of measurement in IC design for the given technology.

The FD-SOI alternative addresses some of the limitations that have arisen in bulk CMOS technology as the device dimensions decrease in smaller technology nodes [106, 107, 108, 109]. For instance, thanks to the BOX layer, a better electrostatic control is achieved over the channel and the leakage currents between the different regions are reduced [110]. A more elaborate discussion on the subject of FD-SOI solution and the problems appearing in bulk technologies that it manages to tackle can be found in [111]. In the remainder of the section, a brief overview of the main features of STMicroelectronics' 28 nm FD-SOI technology is provided.

The source, drain and back plane are either n-doped or p-doped. The doping in the back place modifies the transistor threshold voltage  $V_{th}$  accordingly, which is defined as the gate voltage at which the device turns on and is a key parameter of the transistor [112, 113, 114, 115]. There are therefore two FD-SOI MOSFET options: the Low Threshold Voltage (LVT) and the Regular Threshold Voltage (RVT) transistor. In the first option, the back plane, source, and drain regions undergo the same type of doping, while in the second option, the doping in the back plane is opposite to the one in the source and drain. Furthermore, for the applications of interest, there are two gate oxide options: the

| Operation | EOT | Major advantage         | Major disadvantage        |

|-----------|-----|-------------------------|---------------------------|

| LVT       | SG  | reduced switching time  | increased leakage current |

| RVT       | EG  | reduced leakage current | increased switching time  |

Table 2.1 – Main characteristics of STMicroelectronics' 28 nm UTBB FD-SOI technology node, suitable for the integration of quantum devices.

thin oxide or Standard Gate oxide (SG) option and the thick oxide or Extended Gate oxide (EG) option. A thin-oxide transistor contains a SiO<sub>2</sub> layer and a high-k dielectric HfO<sub>2</sub> layer with a total Equivalent Oxide Thickness (EOT) of 1.1 nm, leading to enhanced gate control over the conduction channel, but also to increased leakage currents flowing between the gate, the ohmic contacts, and the channel due to a larger number of charge carriers tunneling through the lower potential barrier imposed by the thin gate oxide. On the other hand, a transistor with a thick oxide metal gate consists of a SiO<sub>2</sub> layer and a high-k dielectric HfO<sub>2</sub> layer with a total EOT of 3.4 nm, leading to significantly reduced leakage currents but also to weakened gate-to-channel control.

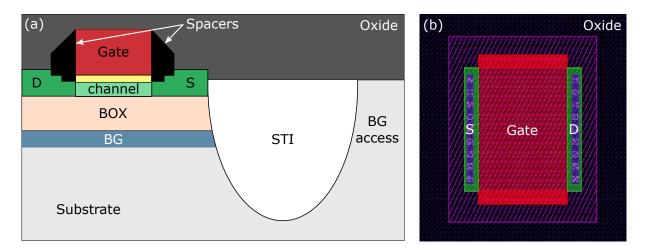

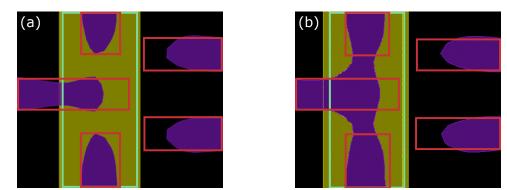

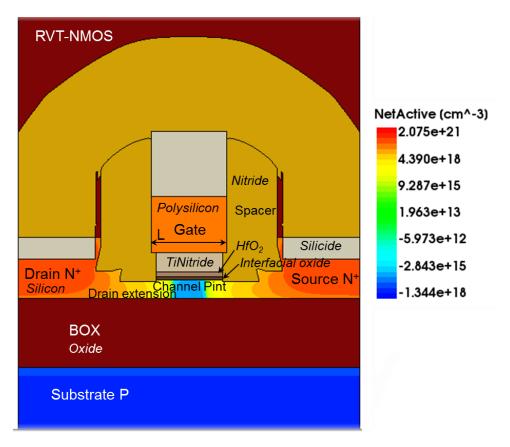

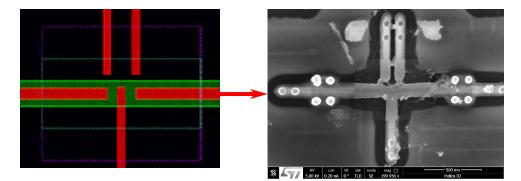

In Figure 2.2, a cross-sectional and top view of the structure of an RVT N-MOS thick-oxide FD-SOI MOSFET are illustrated depicting the different layers composing the device. The source and drain regions are n-doped and are epitaxially grown leading to reduced access resistance. Spacers are used to limit the source/drain extensions, also known as Lightly Doped Drain (LDD) extensions, under the gate. The top gate stack is composed of polysilicon and titanium nitride and is deposited over the high-k thick oxide layer. Electrostatic access to the p-doped back plane is ensured thanks to the oxide trenches created using the Shallow Trench Isolation (STI) technique, which also permits isolation of the transistor from any adjacent device. Electrostatic access to the back plane is achieved through a hybrid area formed by removing the BOX from a specific region of the substrate [116], isolated from the transistor thanks to the STI technique. On top of the source, drain, and top gate, silicide is deposited to reduce access resistance and prepare the ground for the following metallic interconnections. The resulting device is surrounded by field oxide, which is an ensemble of different oxide types (mostly  $SiO_2$ ). Finally, the transistor is electrically connected to the rest of the circuit and the aluminium bonding pads via several Back-End-Of-Line (BEOL) layers, consisting of copper horizontal lines and vias (vertical interconnect access) of different sizes encapsulated by TiN barriers to limit propagation into the field oxide. The type of BEOL routing scheme, e.g. a stack of eight, ten or eleven metal layers, is selected according to the system requirements.

Comparing to bulk technology, the UTBB FD-SOI technology has several advantages [117, 118, 119]. First of all, the ultra-thin silicon film drastically prevents the occurrence of undesired short-channel effects in the transistor, which arise when the gate length becomes too small and lead to a significant loss of gate-to-channel control and are detrimental to the proper operation of the transistor [120, 121, 122, 123, 124, 125]. In addition, the ultra-thin BOX allows the structure to be completely isolated from the back plane and substrate resulting in lower source and drain capacitances, reduced leakage currents flowing from the source and drain areas to the rest of the device, and protection against latch-up issues occurring when a high current flows unexpectedly through the device due to an unwanted short circuit between the supply lines [126]. Furthermore, the absence of impurities in

#### 2.2 INTEGRATION FLOW

Figure 2.2 – (a) Cross-sectional schematic of a 28 nm UTBB FD-SOI MOSFET illustrating the spacers in black, the BOX in light orange, the gate oxide in yellow, and the different layers composing the four terminals of the transistor: the gate in red, the back gate (BG) in blue, the source (S), and the drain (D) in dark green. (b) Design layout of a typical RVT thick-oxide 28 nm UTBB FD-SOI MOSFET based on the STMicroelectronics' design rules. The thick-oxide option is defined by the purple layer in the layout. The pink squares represent the contacts between the active region and the first interconnect layer, which is depicted in blue.

the channel guarantees high performance and reproducibility of the device. Finally, the BOX layer permits to significantly reduce device self-heating [127, 128, 129], whereas the epitaxially raised source and drain regions decrease thermal resistance.

#### 2.2 Integration flow

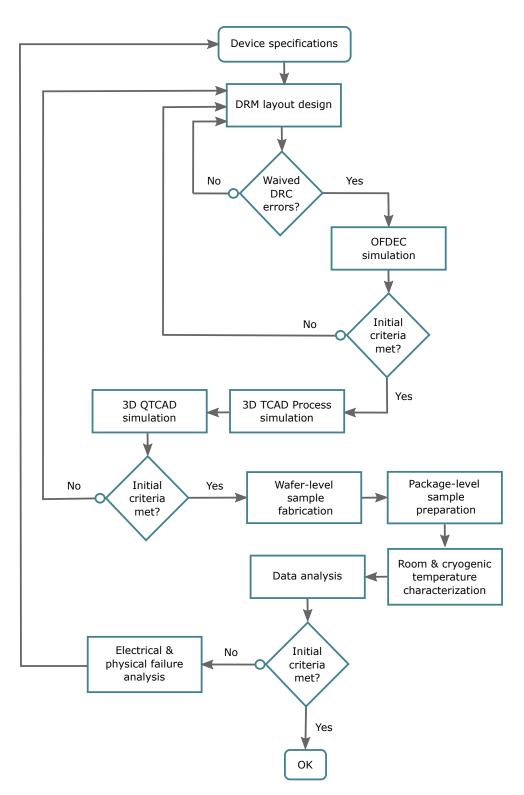

The purpose of this section is to provide a detailed overview of the final version of the fabrication process flow used for the physical implementation of quantum devices and circuits, which was developed during this work and was the result of the application of multiple steps of verification and correction. The following chapters are focused on presenting the numerical and experimental results of this work in detail.

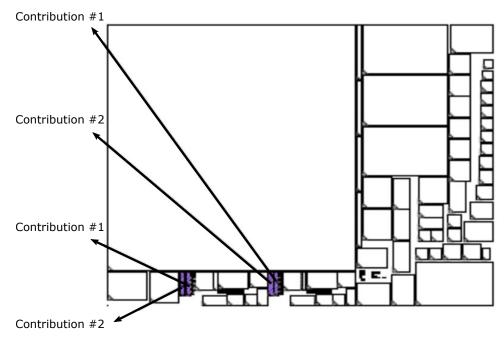

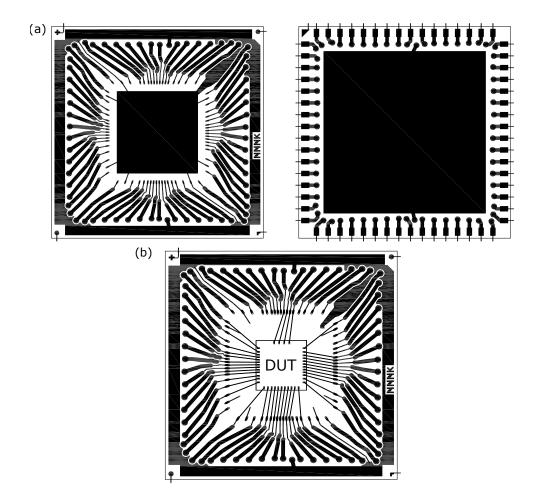

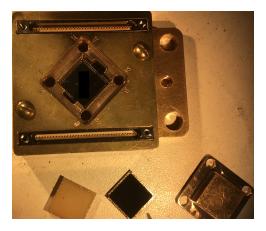

In Figure 2.3, the individual steps leading to the fabrication of quantum devices enclosed inside an IC package are shown, along with their connection to each other. Each block of this diagram corresponds to an individual process flow step. The average turnaround time required to develop and characterize an FD-SOI quantum system based on the proposed workflow here is approximately one calendar year, also including estimated delays due to any revisions and corrections that may have occurred in order to satisfy the specifications. In the remainder of this section, each process step is discussed in detail.

Figure 2.3 – Proposed workflow diagram representing step by step the individual tasks involved in the integration of quantum devices and circuits. Each task is linked to another via an arrow showing how those tasks are related to each other and how the various processes flow through the different stages of the system implementation giving a brief summary of the whole process.

## 2.2 INTEGRATION FLOW

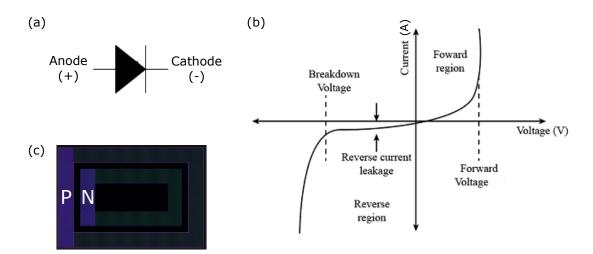

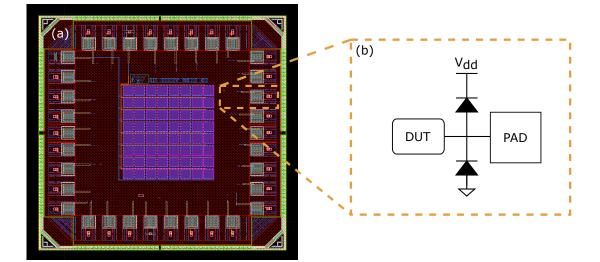

Once the topology of the new device is well defined, the analysis continues for the remaining chip components, including the metal interconnections, bonding pads, and the Input/Output (I/O) protection ring used as an interface between the bonding pads and the chip core. The I/O ring from [130] was used as a basis for the circuit proposed here which consists of diodes designed to protect the fabricated devices from Electro-Static Discharge (ESD) effects [131] and a grid of BEOL metal connections intended to connect the devices to the bonding pads. An ESD event is able to produce hot carrier degradation and melting and can cause significant damage to the oxides, junctions, metals, and even the plastic of the IC package [132, 133, 134, 135, 136, 137, 138, 139, 140]. Notice that other components, such as transistors, can be used to protect the devices against ESD [141, 142].

An ESD stress episode is caused by contact between two electrically charged objects and occurs unexpectedly and instantaneously when an electrostatic discharge occurs between the two. Depending on the nature of charged objects involved in the event, three main ESD types are identified, namely human body ESD, machine ESD and charged device ESD, while the current intensity varies widely from one type to another. For instance, in the different cases of human body and charged device ESD incidents, the current corresponding to a 1 kV discharge ranges from 1 A to 10 A and the duration of the event from 100 ns to 1 ns, respectively [142].

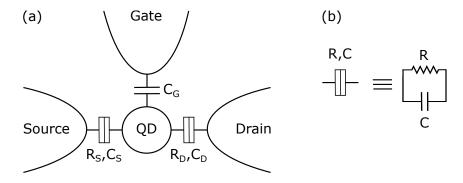

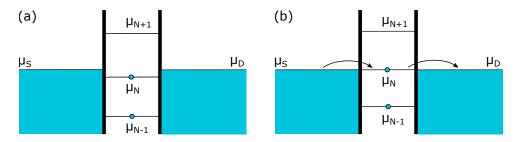

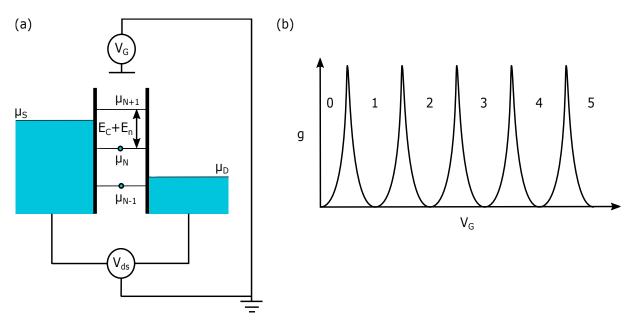

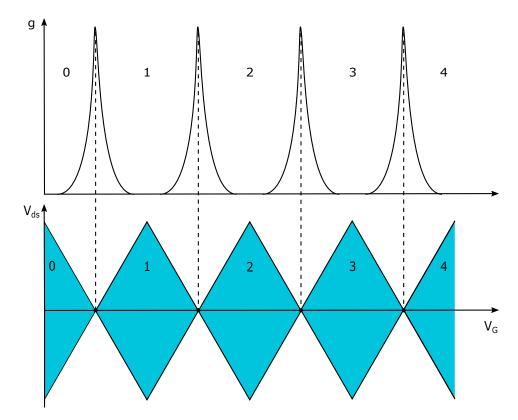

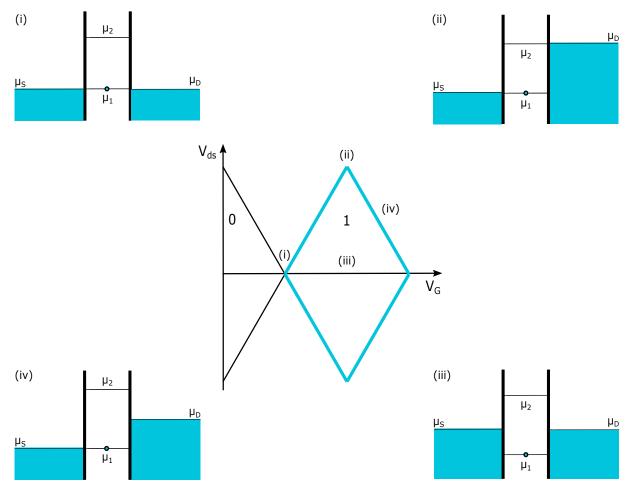

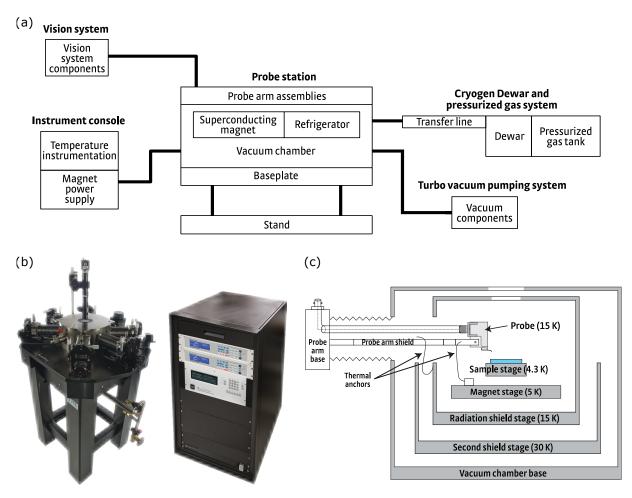

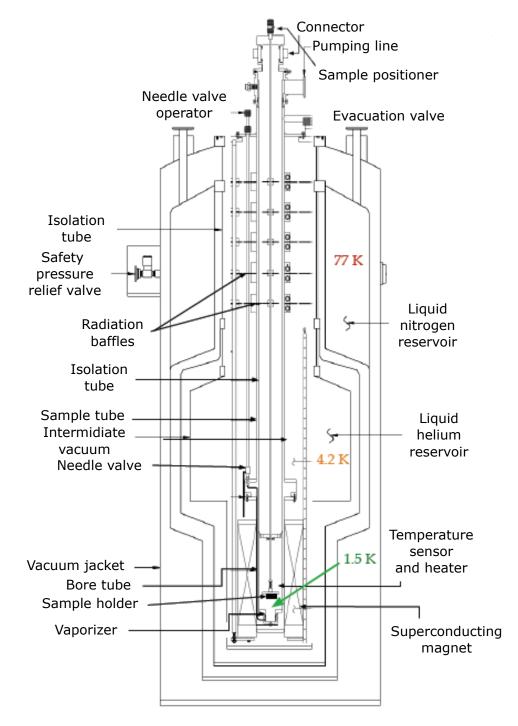

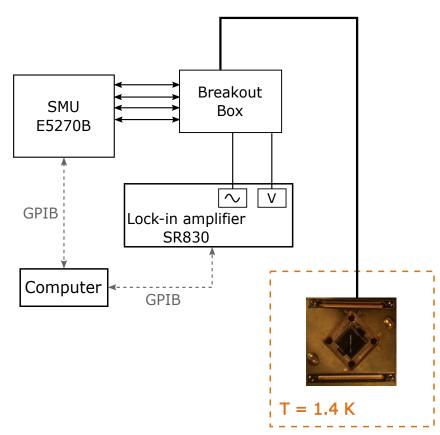

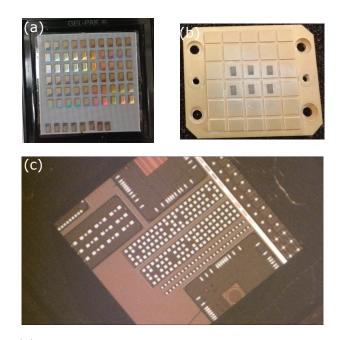

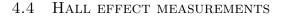

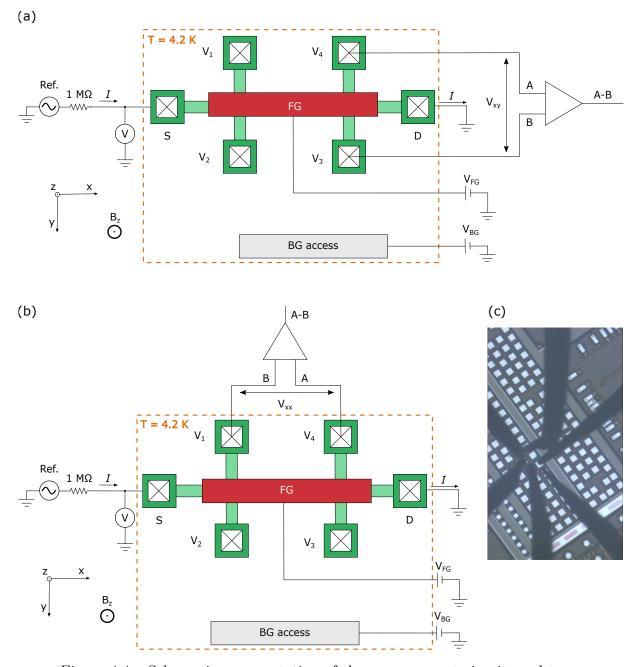

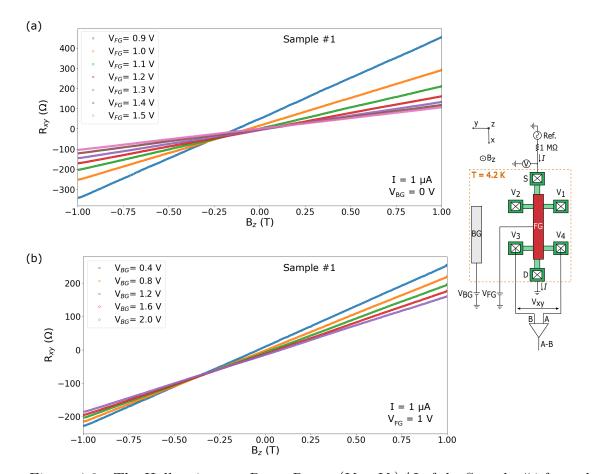

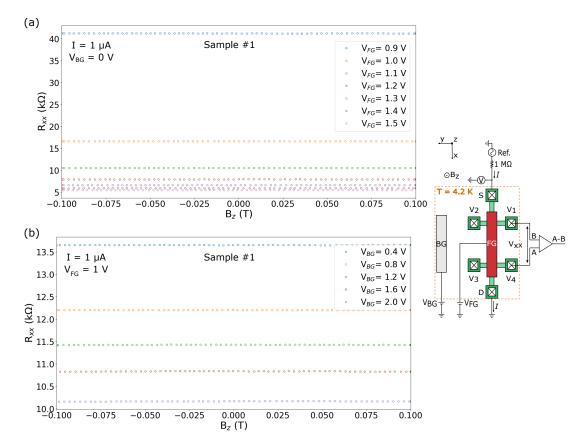

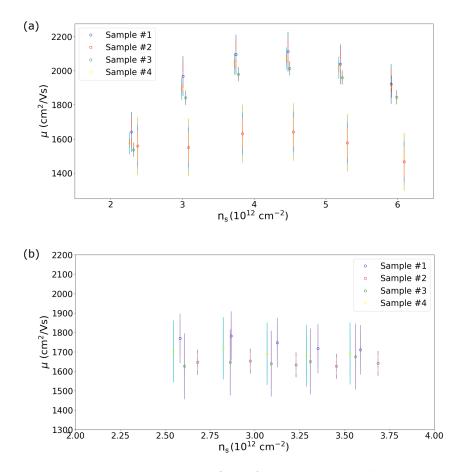

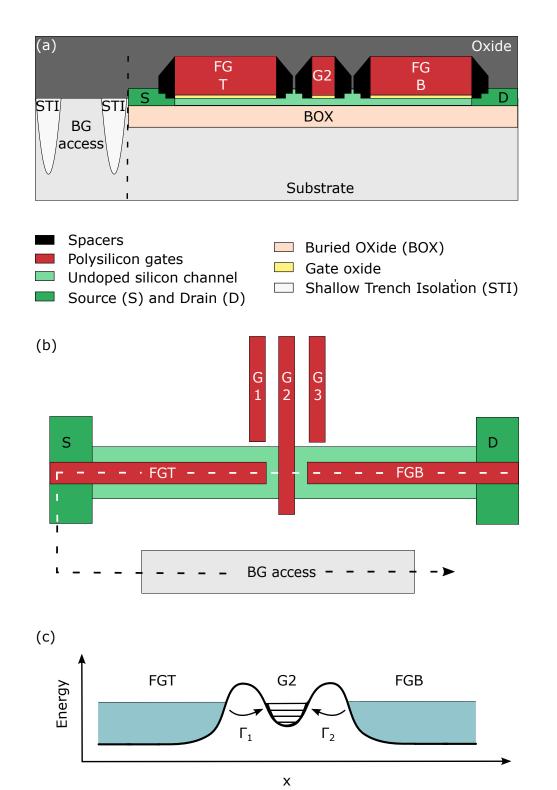

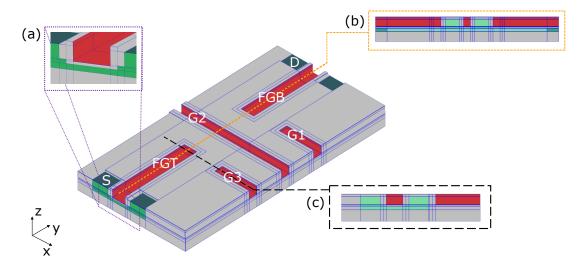

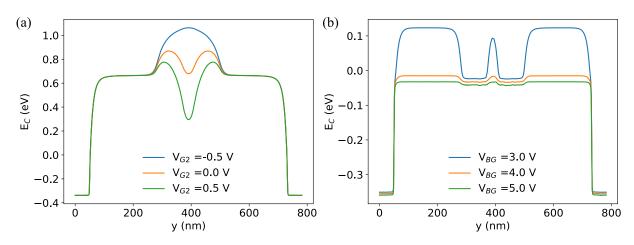

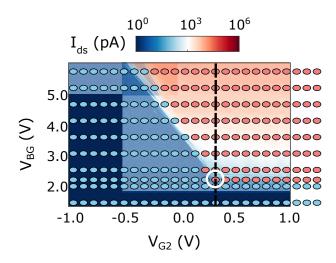

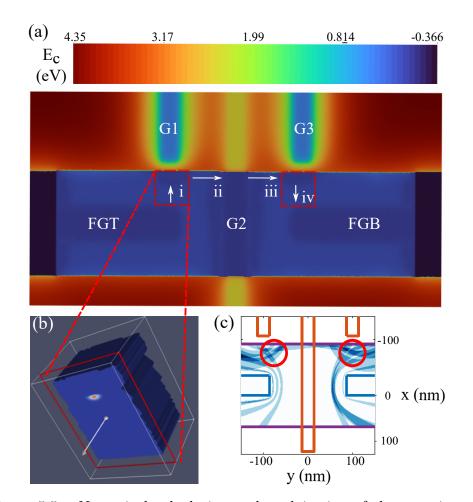

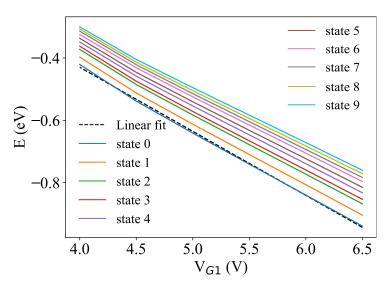

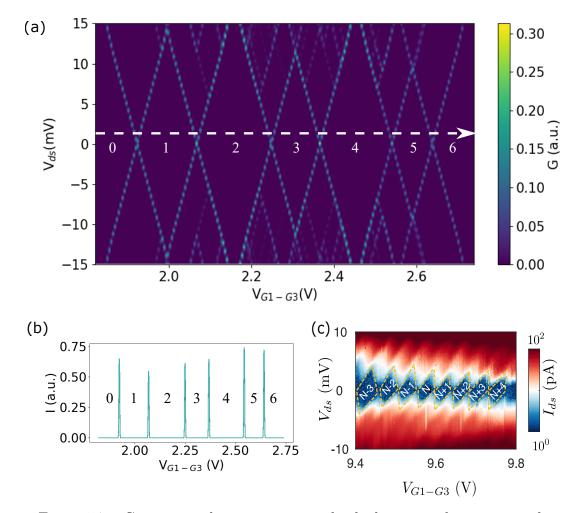

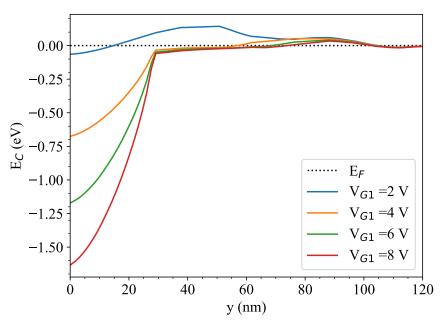

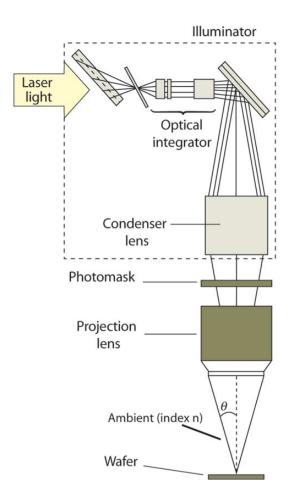

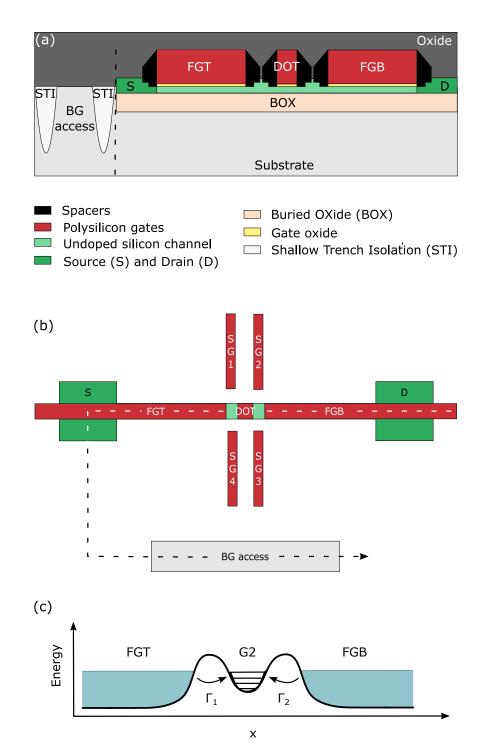

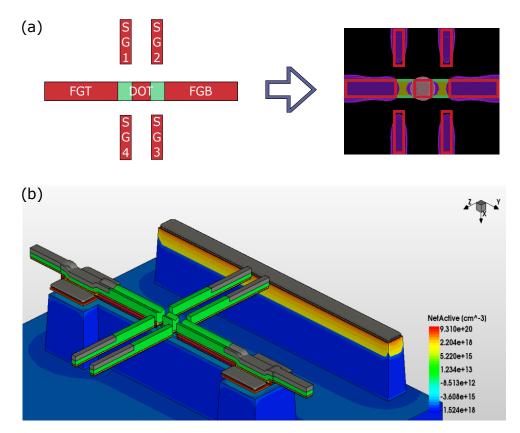

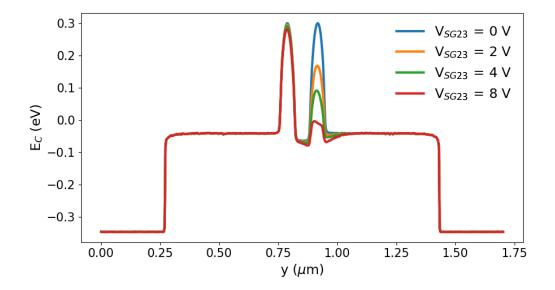

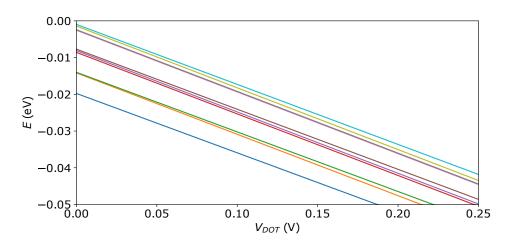

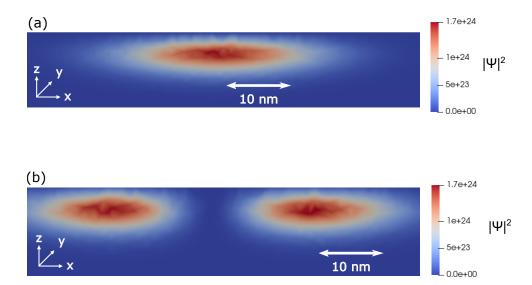

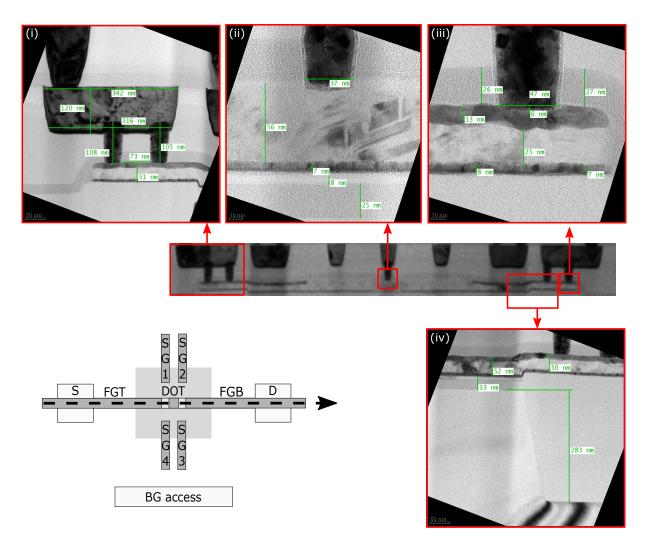

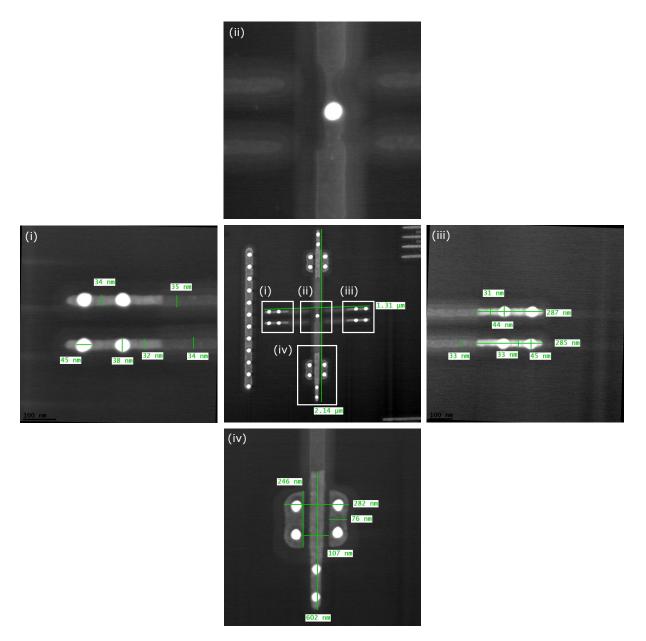

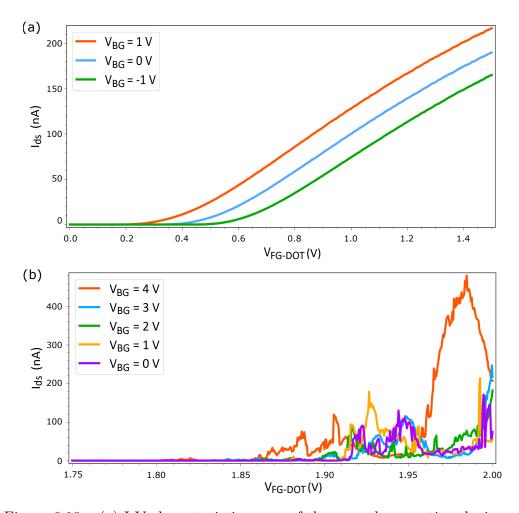

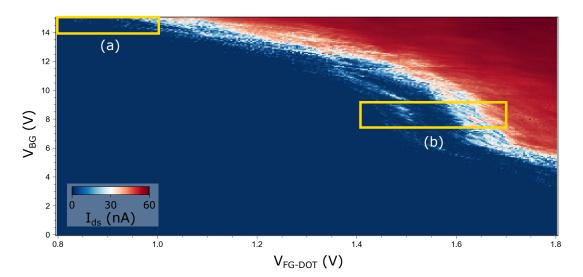

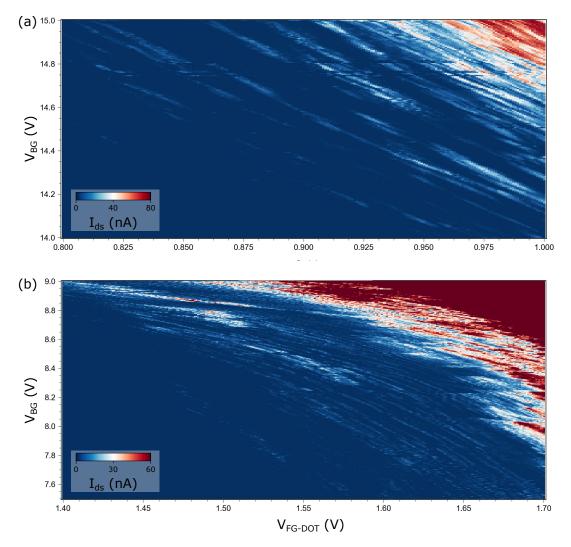

To explain how the I/O ring assists to protect the chip core from ESD problems, the operating principle of a diode is recalled. More specifically, a diode is a unidirectional two-terminal electical device consisting of a p-doped region and an n-doped region that allows electrical current to flow when the proper biasing conditions are applied (Figure 2.4) [143, 144, 145]. The working principle of the diode is based on the difference in energy band levels between these two regions, which generates an electric potential barrier that prevents charge carriers from flowing through the diode. When a forward bias is applied to the diode, the barrier accross the device is reduced. After a certain voltage difference, called the diode threshold voltage, the current starts flowing from the p-doped to the n-doped region. However, at high forward bias voltages, the mobility of the carrier is decreased. On the contrary, a reverse bias applied to the diode increases the barrier potential that blocks electric transport through the diode. At very large reverse bias voltages, above a value called breakdown voltage, a breakdown of the diode occurs leading to a large current flowing through the device, if the current is not limited, causing critical damage to the diode [146, 147].