## Phase Change Memory (PCM) for High Density Storage Class Memory (SCM) Applications

Giusy Lama

### ► To cite this version:

Giusy Lama. Phase Change Memory (PCM) for High Density Storage Class Memory (SCM) Applications. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALT108. tel-04052655

## HAL Id: tel-04052655 https://theses.hal.science/tel-04052655v1

Submitted on 30 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. THÈSE

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) Spécialité : Nano électronique et Nano technologies Unité de recherche : CEA/LETI

Mémoires à Changement de Phase (PCM) pour les applications de Mémoire de Classe de Stockage (SCM) à haute densité

# Phase Change Memory (PCM) for High Density Storage Class Memory (SCM) Applications

Présentée par :

#### **Giusy LAMA**

#### Direction de thèse :

Véronique SOUSA Ingénieur HDR, CEA LETI Gabriele NAVARRO Ingénieur docteur, CEA LETI Directrice de thèse

Co-encadrant de thèse

#### Rapporteurs :

Luca LARCHER PROFESSEUR, Université de Modene Abdelkader SOUIFI PROFESSEUR DES UNIVERSITES, INSA Lyon

#### Thèse soutenue publiquement le 15 décembre 2022, devant le jury composé de :

| Véronique SOUSA                                       | Directrice de thèse |

|-------------------------------------------------------|---------------------|

| INGENIEUR HDR, CEA LETI                               |                     |

| Ahmad BSIESY                                          | Président           |

| PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes |                     |

| Luca LARCHER                                          | Rapporteur          |

| PROFESSEUR, Université de Modene                      |                     |

| Abdelkader SOUIFI                                     | Rapporteur          |

| PROFESSEUR DES UNIVERSITES, INSA Lyon                 |                     |

| Philippe BOIVIN                                       | Examinateur         |

| INGENIEUR DOCTEUR, STMicroelectronics                 |                     |

Invités :

Innocenzo TORTORELLI INGENIEUR, Micron Gabriele NAVARRO INGENIEUR DOCTEUR, CEA LETI

## Contents

| Co | onten               | ts                                                                           | Ι              |

|----|---------------------|------------------------------------------------------------------------------|----------------|

| A  | bstrac              | et                                                                           | III            |

| Li | st of .             | Acronyms                                                                     | V              |

| In | trodu               | ction                                                                        | 1              |

| 1  | <b>Stor</b><br>1.1  | age Class Memory and emerging Non Volatile MemoriesEmerging memories for SCM | 5<br>8<br>9    |

|    |                     | 1.1.3       RRAM                                                             | 10<br>11       |

|    | $1.2 \\ 1.3 \\ 1.4$ | The cross-point architecture: towards a 3D BEOL memory                       | 12<br>14<br>18 |

| 2  | Pha                 | se-Change Memory                                                             | <b>19</b>      |

|    | 2.1                 | PCM working principle                                                        | 20             |

|    | 2.2                 | Crystallization behavior of phase-change materials                           | 22             |

|    | 2.3                 | Conduction in the crystalline and in the amorphous phase                     | 23             |

|    | 2.4                 | The threshold switching                                                      | 25             |

|    | 2.5                 | Resistance drift                                                             | 26             |

|    | 2.6                 | PCM architectures                                                            | 27             |

|    | 2.7                 | PCM reliability                                                              | 29             |

|    |                     | 2.7.1 Endurance and failure mechanisms                                       | 29             |

|    |                     | 2.7.2 Data retention                                                         | 31             |

|    |                     | 2.7.3 Multilevel cell reliability                                            | 33             |

|    |                     | 2.7.4 Scaling effects on PCM reliability                                     | 34             |

|    | 2.8                 | Material engineering in PCM                                                  | 36             |

|    |                     | 2.8.1 Reference PCM materials : GST and GeTe                                 | 36             |

|    |                     | 2.8.2 Doping effects in phase-change materials                               | 37             |

|    |                     | 2.8.3 Multilayer PCM                                                         | 38             |

|    | 2.9                 | Summary of the chapter                                                       | 39             |

| 3  | GeS   | bTe and GeTe based PCMs                    | 41        |

|----|-------|--------------------------------------------|-----------|

|    | 3.1   | Material and electrical characterization   | 42        |

|    |       | 3.1.1 Material characterization            | 42        |

|    |       | 3.1.2 Electrical characterization          | 43        |

|    |       | 3.1.3 The testing protocols                | 46        |

|    | 3.2   | $Sb_2Te_3+Ge$                              | 49        |

|    | 3.3   | GeTe and GeSbTe based Phase Change Memory  | 51        |

|    |       | 3.3.1 Speed analysis                       | 52        |

|    |       | 3.3.2 Data retention analysis              | 54        |

|    |       | 3.3.3 Endurance                            | 55        |

|    | 3.4   | Si-doped GeSbTe                            | 57        |

|    |       | 3.4.1 Si doping effects in PCM devices     | 58        |

|    |       | 3.4.2 MLC analysis in Si-doped PCM         | 61        |

|    | 3.5   | Summary of the chapter                     | 66        |

| 4  | CL    | ich GST                                    | CO        |

| 4  |       |                                            | <b>69</b> |

|    | 4.1   | Multilayered Sb-rich GeSbTe PCM            | 70        |

|    |       | 4.1.1 Materials analysis                   | 70        |

|    |       | 4.1.2 Electrical Characterization          | 72        |

|    | 4.0   | 4.1.3 Discussions                          | 77        |

|    | 4.2   | Sb-rich confined PCM                       | 79        |

|    | 4.3   | Summary of the chapter                     | 80        |

| 5  | Inno  | ovative phase-change materials             | 83        |

|    | 5.1   | TiTe/GST Bi-Layer                          | 84        |

|    |       | 5.1.1 TiTe/GST Programming Characteristics | 84        |

|    |       | 5.1.2 Data Retention                       | 87        |

|    |       | 5.1.3 Endurance                            | 88        |

|    |       | 5.1.4 Applications                         | 90        |

|    | 5.2   | GaSb based PCMs                            | 91        |

|    | 5.3   | Summary of the chapter                     | 95        |

| Ca |       | ions and non-mostives                      | 97        |

| CO | ncius | sions and perspectives                     | 97        |

| Re | feren | ices                                       | 101       |

| Au | thor' | 's publication list                        | 119       |

|    |       |                                            |           |

\_\_\_\_\_

## Abstract - Résumé

## <u>TITLE:</u> Phase-Change Memory (PCM) targeting high density Storage Class Memory (SCM) applications

#### Abstract:

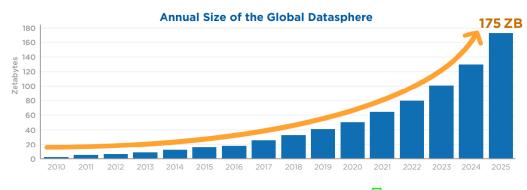

The amount of data generated is increasing exponentially in the last years and is expected to reach 175 Zettabytes by 2025 [1]. This data explosion is pushing memory technologies to their performance and density limits. The access and writing speed of storage memory has emerged as the primary bottleneck of modern systems due the growing speed of data elaboration. The current memory hierarchy consists of a top layer, closest to the processor, which is faster and expensive, and by a bottom layer, that is more dense but slower. Storage Class Memory (SCM) was created to reduce the performance and cost barriers between storage and memory, in particular between DRAM and NAND Flash. PCMs are considered the best candidate for SCM thanks to the good scalability, the high endurance, fast switching time and multilevel cell capability [2]. Material engineering becomes essential to meet the demand for low cost, high programming speed and endurance of SCM applications. In particular, it necessitates the investigation of novel alloys capable of rapid crystallization while maintaining the material stability during the multiple transitions between the amorphous and crystalline phases that occur during the device lifetime. The objective of this thesis is the investigation of innovative phase-change materials to target SCM applications, understanding the failure mechanisms and which parameters can limit the reliability of the device.

#### Speciality: Nanoelectronics and Nanotechnology

**Key Words:** Phase-Change Memory, Storage Class Memory, reliability, phase-change materials.

**Thesis work prepared at**: CEA, LETI, MINATEC Campus, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France.

# <u>TITRE</u>: Mémoires à Changement de Phase (PCM) pour les applications de Mémoire de Classe de Stockage (SCM) à haute densité

#### <u>Résumé:</u>

La quantité de données générées augmente de façon exponentielle ces dernières années et devrait atteindre 175 Zettabytes d'ici 2025 [1]. Cette explosion des données pousse les technologies de mémoire à leurs limites de performance et de densité. La vitesse d'accès et d'écriture de la mémoire de stockage est devenue le principal goulot d'étranglement des systèmes modernes en raison de la vitesse croissante d'élaboration des données.

La hiérarchie mémoire actuelle est constituée d'une couche supérieure, la plus proche du processeur, plus rapide et coûteuse, et d'une couche inférieure, plus dense mais plus lente. La mémoire de classe de stockage (SCM) a été créée pour réduire les barrières de performances et de coûts entre le stockage et la mémoire, en particulier entre la DRAM et la NAND Flash.

Les PCM sont considérés comme les meilleurs candidats pour le SCM grâce à leur bonne scalabilité, leur haute endurance, leur temps de commutation rapide et leur capacité multi-niveaux [2].

L'ingénierie des matériaux devient essentielle pour répondre à la demande de faible coût, de vitesse de programmation élevée et d'endurance des applications SCM. En particulier, cela nécessite l'étude de nouveaux alliages capables de cristalliser rapidement tout en maintenant la stabilité du matériau lors des multiples transitions entre les phases amorphe et cristalline qui se produisent pendant la durée de vie du dispositif.

L'objectif de cette thèse est l'étude de matériaux innovants à changement de phase pour cibler les applications SCM, en comprenant les mécanismes de défaillance et quels paramètres peuvent limiter la fiabilité du dispositif.

#### Spécialité: Nano Électroniques et Nano Technologies

<u>Mots Clés</u>: mémoires à changement de phase, Mémoire de Classe de Stockage, fiabilité, matériaux à changement de phase.

#### Thèse préparée au sein du:

CEA, LETI, MINATEC Campus, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France.

[1] David Reinsel-John Gantz-John Rydning, J Reinsel, and J Gantz. The digitization of the world from edge to core. Framingham: International Data Corporation, 2018.

[2] Scott W Fong, Christopher M Neumann, and H-S Philip Wong. Phase-change memory-towards a storage-class memory. IEEE Transactions on Electron Devices, 64(11):4374?4385, 2017.

## List of Acronyms

| Acronym                | Designation                                       |

|------------------------|---------------------------------------------------|

| 1R                     | One Resistor                                      |

| 1T1C                   | One-Transistor One-Capacitor                      |

| 1T1R                   | One-Transistor-One-Resistor                       |

| AIST                   | $Ag_4In_3Sb_{67}Te_{26}$                          |

| ALD                    | Atomic Layer Deposition                           |

| BEOL                   | Back-End-of-Line                                  |

| C2C                    | cycle-to-cycle                                    |

| D2D                    | device-to-device                                  |

| DRAM                   | Dynamic Random Access Memory                      |

| $\operatorname{FeRAM}$ | Ferroelectric Random Access Memory                |

| GST                    | GeSbTe                                            |

| HDD                    | Hard Disk Driver                                  |

| IPCM                   | Interfacial Phase Change Memory                   |

| I-V                    | Current-Voltage curve                             |

| MIEC                   | Mixed Ionic-Electron Conduction                   |

| MIM                    | Metal-Insulator-Metal                             |

| MIT                    | Metal-Insulator Transition                        |

| MIT                    | Metal-Insulator Transition                        |

| MLC                    | Multilevel Cell Capability                        |

| MOSFET                 | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MRAM                   | Magnetic Random Access Memory                     |

| M-SCM                  | Memory-type Storage Class Memory                  |

| MTJ                    | Magnetic Tunneling Junction                       |

| NDR                    | Negative Differential Resistance                  |

| NVM                    | Non-Volatile Memories                             |

| OTS                    | Ovonic Threshold Swith                            |

| PCM                    | Phase Change Memory                               |

| PMem                   | Persistent Memory                                 |

| PV                     | Program and Verify                                |

| PVD                    | Physical Vapor Deposition                         |

| R-I                    | Resistance-Current curve                          |

| RRAM                   | Resistive Random Access Memory                    |

| R-T                    | Resistivity-Temperature curve                     |

| SCM                    | Storage Class Memory                              |

| SL PCM                 | Superlattice Phase Change Memory                  |

| SRAM                   | Static Random Access Memory                       |

| S-SCM                  | Storage-type Storage Class Memory                 |

|                        |                                                   |

| TEM      | Transmission Electron Microscopy |

|----------|----------------------------------|

| TMR      | Tunnel Magneto-Resistance        |

| V-XPoint | Vertical Cross-Point             |

| XPoint   | Cross-Point                      |

| XRD      | X-Ray Diffraction                |

|          |                                  |

## Introduction

Our digital society is based on data. The word *data* was used for the first time in English in the 1640s with the meaning of "fact given or granted". In the XVIIs, data was employed by the scientific community to indicate experimental or tangible events. In the world of information technology, for the first time *data* was reported as "transmittable and storable information by which computer operations are performed" in 1946 [1]. Raw data is unidentifiable as information, for this reason we collect, measure, clean, analyze, share or transfer data: the information achieved from these operations consents to generate knowledge. In order to ensure this process, the data must be stored on physical media. The first means found for data collection is the Ishango Bone from the Upper Paleolithic, where some scratches in the bone were used as raw data [2]. Later, with the birth of writing, tablets, papyri and finally, books became the new form of mass storage. The birth of internet and of search engines in the 1990s determined the last revolution ensuring data access to anyone in possession of a computer.

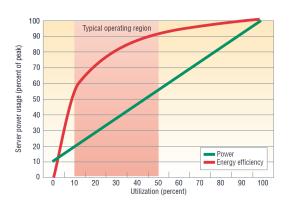

Today the internet users are 4.95 billions [3], a huge number, constantly growing, linked to an ever-increasing flow of data supported by smart connected devices, artificial intelligence and internet of things. Indeed, the amount of data generated is increasing exponentially in the last years and is expected to reach 175 Zettabytes by 2025 (Fig. [3]) [4]. Data have been presented as the new oil of the digital economy [5], since companies are exploiting data to be more competitive, more productive and to create new markets capable of reaching every place in the world. Data centers play an important role in ensuring access to internet data at any time. However, the energy efficiency of data centers is an issue, since they consume a considerable amount of power even when are unused in the idle state (Fig. [1]) [6].

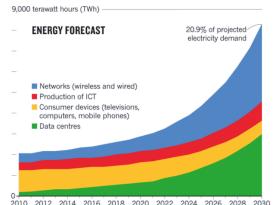

Energy is not consumed only by smart devices, but also by the system that diffuses the contents. Behind the video and music on demand, social networks or shopping websites, huge data centers need to be powered. For example, a Microsoft data center could consume 48 MW, that is enough power for 40000 homes 8. The sector of Information and Communication Technology (ICT) is predicted to consume 20 % of the global electricity demand by 2030. Data centers will require a large slice of this electricity 9, presenting a considerable carbon footprint (Fig. 2).

The main consumers in a data center are CPU and memory 10, where dynamic random access memory (DRAM) is a building block. The interfaces used to access the memory array and provide bits off the chip are responsible for the power consumption in the DRAM system 11. On the other side, access to storage Hard Disk Drivers (HDD) requires energy, which could be saved using Solid State Drivers (SSD) based on NAND Flash. Indeed, SSDs do not have moving parts and exhibit higher speed and density than HDD 12. However, the charge storage mechanism of NAND makes difficult the scaling of this technology, since, as the number of electrons stored in the floating gate is reduced, the loss of just one electron can cause significant reliability issues.

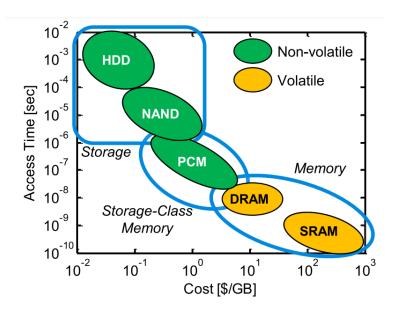

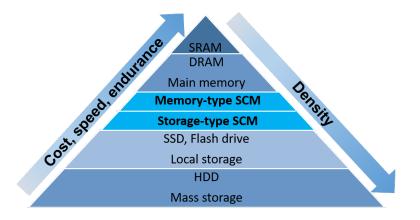

Therefore, the current memory hierarchy is composed on the top by SRAM and DRAM, that require frequent access and, thus, are fast and have a high endurance, and on the bottom by SSD and HDD, that feature a low cost, but low speed and endurance. The speed gap between DRAM and SSD is about 3 orders of magnitude, while the gap in areal density (i.e. cost) is around 2 orders of magnitude. In this context, the traditional memory hierarchy must be modified.

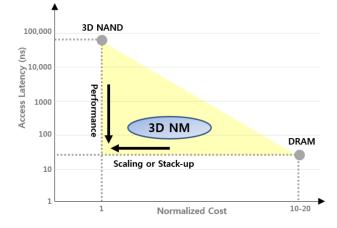

Storage Class Memory introduces a new level in the traditional memory hierarchy to fill the gap in performance and cost between DRAM and SSD. Storage Class Memory (SCM) concept was concretized by the commercialization of Intel and Micron 3D XPoint in 2015, that, however, in July 2022 has ceased the production. In fact, in the storage market, there are already several mature lower cost devices, although Intel 3D XPoint provided superior performance, the high price held back its success. 3D XPoint exploits Phase Change Memories (PCM), that are considered the best candidate for SCM thanks to the good scalability, the high endurance, faster switching time compared to NAND and the multilevel cell capability (Fig. 4) [7]. However, the end of 3D XPoint production demonstrates that there are still certain barriers preventing PCM memory from becoming mainstream mainly due to the high cost linked to the commercialization of a technology that is new compared to NAND Flash.

Material engineering becomes essential to meet the demand for low cost, high programming speed and endurance of SCM applications. In particular, it necessitates the investigation of novel alloys capable of rapid crystallization while maintaining the material stability during the multiple transitions between the amorphous and crystalline phases that occur during the device lifetime.

The objective of this thesis is the development of innovative phase-change materials to target SCM applications, understanding the failure mechanisms and which parameters can limit the reliability of the device.

Fig. 1. Power usage and energy efficiency in a Fig. server 6.

Fig. 2. Energy required by the ICT sector 9.

Fig. 3. Annual global datasphere trend [4].

In the first chapter, we focus on SCM comparing the emerging non-volatile memories (NVM) in terms of the main features for SCM, i.e. scalability, 3D integration, multilevel cell capability, latency and endurance. Moreover, 3D architecture and selector are discussed.

In the second chapter, PCM working principle is described. Then, we examine PCM reliability issues and how they can be overcame thanks to material engineering.

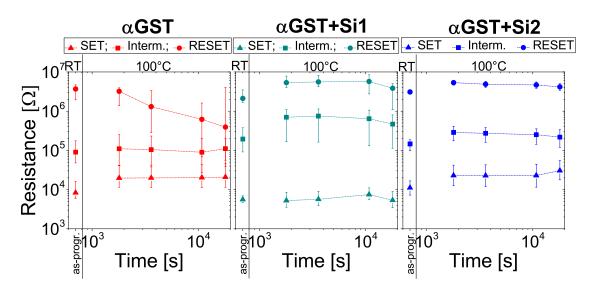

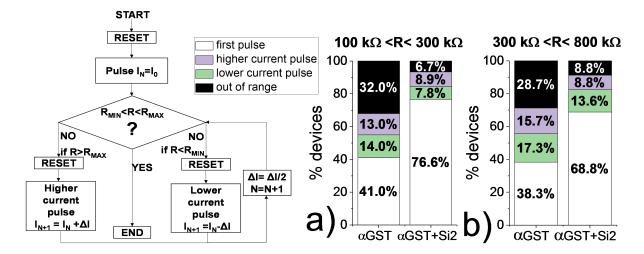

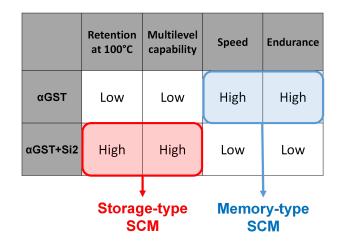

In the third chapter, we compare the performances of GeTe and GeSbTe (GST) based PCMs for SCM focusing on programming speed and material properties evolution during the programming cycles, and we investigate the impact of the pulse energy on endurance. Additionally, we demonstrate that Si doping in GST enhances MLC capacity and retention in PCM devices.

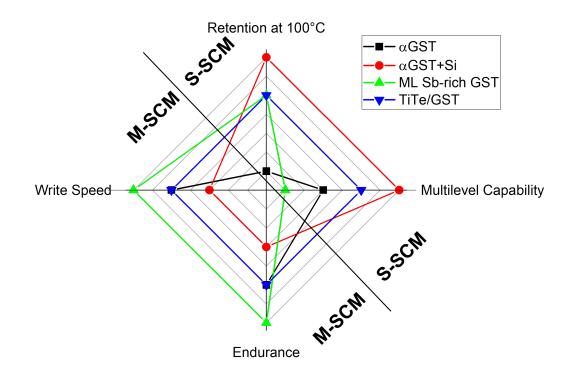

In the fourth chapter, we analyze different Sb-rich GST multilayers obtained by alternating layer deposition of GST and Sb targets, reporting that the best multilayer stack developed exhibits a reduced device-to-device variability with respect to bulk equivalent PCM devices. In the fifth chapter, we explore novel PCMs based on TiTe/GST bi-layer stack that guarantee high speed, high endurance and MLC capability. Then,

Fig. 4. Access time of various memories as a function of the cost. The space between NAND flash and DRAM in the memory hierarchy can be filled by PCM [7].

we investigate GaSb-based PCM demonstrating that C doping aids in reducing segregation, that naturally happens in off-stoichiometric GaSb.

In the conclusions, we summarize the key findings of this work and offer some perspectives for further research on PCM towards SCM applications or even SRAM/DRAM partial or total replacement in the future of the memory hierarchy.

## Chapter 1

## Storage Class Memory and emerging Non Volatile Memories

The two basic components of a computer are the processor and memory. The processor retrieves data from the memory, elaborates it, and then sends it back to the memory. However, the processor speed is increasing more quickly than the memory speed, and even though the processor is extremely fast, the system speed will be affected by the memory bandwidth if the memory cannot send data at that rate. This is called the Memory Wall 14. The memory hierarchy was created in order to address this issue. We are referring to a Von Neumann architecture, where the computation part and the memorization part are separated.

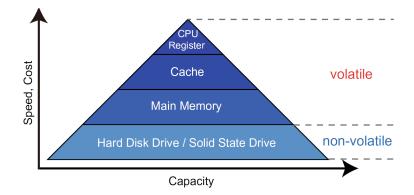

The memory hierarchy is represented as a pyramid: the top layer is the one closest to the processor, which is faster but more expensive and less dense compared to the bottom layers (Fig. 1.1). The different levels are 13:

- 1. the internal memory, constituted by the CPU registers.

- 2. the cache, usually organized with a further hierarchy of multiple levels L1, L2 and L3, where L1 contains the data with high frequency access since it is closer to CPU. Cache is made by static random access memory (SRAM).

- 3. the main memory, made by DRAM.

- 4. the hard disk and SSD.

Fig. 1.1. The classical memory hierarchy in a Von Neumann architecture [13].

The first three levels consist of volatile memories, which must be powered to hold data, the fourth level includes non-volatile memories (NVMs) which retain data even when the power is turned off. In the last years, Flash memories have become the dominant NVM devices for mobile electronics 15. In the next sections, we describe what are the problems related to SRAM, DRAM and Flash memory, why the memory hierarchy should be reorganized and what are the candidates for this revolution.

#### SRAM, DRAM and NAND limits

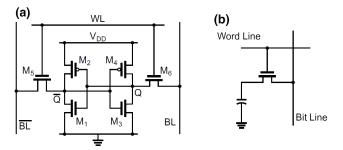

SRAM stores the information, i.e. the bit, in a node of a cross-coupled inverter, while other two transistors are used for write and read operations. Hence, a SRAM consists of six transistors in total, as shown in Fig. 1.2 (a). DRAM is composed by a transistor that modifies the charge of a capacitor as shown in Fig. 1.2 (b). It is clear that DRAM is less expensive and denser that SRAM, since the DRAM cell is smaller; on the other hand SRAM is faster than DRAM. However, both are volatile memories that need to be constantly powered to hold data and, therefore, consume a significant amount of power.

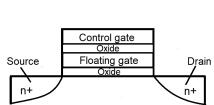

Flash memories are based on a charge storage mechanism, such as DRAM and SRAM, although are distinguished by non-volatility. A Flash memory cell is a floating-gate metal-oxide-semiconductor field-effect transistor (MOSFET), which is basically a MOS-FET with two gates (Fig. 1.3). The stored data is represented by the charge trapped in the floating gate that changes the threshold voltage of the device. NAND and NOR are two types of Flash architectures. The NAND cells are connected in series, while the NOR Flashes are in parallel, meaning that each cell is connected to ground and to the line to access it. NANDs are more diffuse today in stand-alone systems since they are denser than NORs due to the fewer connection lines. However, Flash has reached its scaling limits due to interference between adjacent cells, retention issues and high variability between devices, which impacts the multilevel cell capability when the floating gate is reduced [16]. In addition, Flash features a poor endurance of  $10^4$ - $10^5$  [17], requires an erase operation before the writing, long access time (25 µs) and erasing time (2 ms) due to the block-based architecture [18].

Fig. 1.2. Schematic of SRAM (a) and DRAM (b)cells [13].

Fig. 1.3. Schematic of a Flash memory cell.

#### Storage Class Memory

In the previous section, we have seen that, in the memory hierarchy, the volatile part, also called memory, is characterized by high speed, low density and high cost; the non-volatile part, also called storage, features instead high density, low cost and low speed. This creates a bottleneck in the traditional memory hierarchy. Storage Class Memory (SCM) has the aim to reduce the boundaries in performances and cost between storage and memory. Therefore, SCM should combines performances of DRAM and SSD, preserving speed and endurance higher than NAND Flash and, at the same time, density and cost better than DRAM. In synthesis, the main requirements of SCM are non-volatility, short access and programming time, high endurance and low cost per bit 17. Low cost per bit means high density, which can be provided by three dimensional (3D) integration and multiple bits per cell. The non-volatility ensures a low power consumption compared to DRAM that requires constantly the refresh. SCM does not have the task to simply replace NAND Flash or DRAM, it is a complementary level of the memory hierarchy and might be used for caching or tiering 19. The position of SCM in the memory hierarchy is showed in Fig. 1.4. We can distinguish two types of SCM:

- Memory-type SCM (M-SCM) that shows characteristics closer to DRAM keeping a lower cost and power than DRAM. Speed and endurance are critical in this case: read/write speed must be less than 200 ns and endurance must be higher than 10<sup>9</sup>. The data retention can be moderate.

- Storage-type SCM (S-SCM) that is closer to NAND Flash features. In this case, density and cost are important and must be comparable with NAND Flash. Although speed and endurance are not crucial for S-SCM, they must be higher than NAND Flash. Moreover, S-SCM must be truly non-volatile [20].

The target specifications for the two types of SCM are showed in the table 1.1 next to HDD, NAND Flash and DRAM characteristics.

Fig. 1.4. The new memory hierarchy with SCM.

|                    |                                    | Benchmark                                         |                                 |                                | Target               |  |

|--------------------|------------------------------------|---------------------------------------------------|---------------------------------|--------------------------------|----------------------|--|

| Parameter          | HDD                                | NAND flash                                        | DRAM                            | Memory-type<br>SCM             | Storage-type<br>SCM  |  |

| Read/write latency | 3–10 ms                            | $\sim 100 \mu s$<br>(block erase<br>$\sim 1 ms$ ) | <100 ns                         | <200 ns                        | 1–5 µs               |  |

| Endurance (cycles) | Unlimited                          | $10^{3} - 10^{5}$                                 | Unlimited                       | $>10^{9}$                      | $>10^{6}$            |  |

| Retention          | >10 yr                             | $\sim 10 \text{ yr}$                              | 64 ms                           | >5 d                           | $\sim 10 \text{ yr}$ |  |

| ON power (W/GB)    | 0.003-0.05                         | $\sim 0.01 - 0.04$                                | 0.4                             | < 0.4                          | < 0.10               |  |

| Standby power      | $\sim$ 52–69% of                   | <10% ON                                           | $\sim 25\%$ ON                  | <5% ON                         | <5% ON               |  |

|                    | ON power                           | power                                             | power                           | power                          | power                |  |

| Areal density      | $\sim 10^{11}$ bit/cm <sup>2</sup> | $\sim 10^{11}  \text{bit/cm}^2$                   | $\sim 10^9$ bit/cm <sup>2</sup> | $>10^{10}$ bit/cm <sup>2</sup> | $>10^{10}$ bit/cm    |  |

| Cost (US\$/GB)     | $\sim 0.1 - 1.0$                   | 2                                                 | 10                              | <10                            | <3-4                 |  |

Table 1.1. Target specifications for SCM [20].

## **1.1 Emerging memories for SCM**

In this section, we are going to discuss about the different emerging NVMs that can be possible candidates for SCM and, then, have a place in the memory hierarchy.

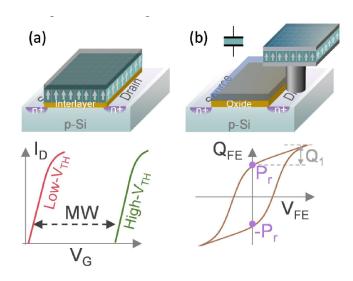

#### 1.1.1 FeRAM

A ferroelectric random access memory (FeRAM) exploits a ferroelectric material, which belongs to a class of crystals that can be polarized in two opposite directions (positive and negative) by the application of an electric field [21]. The two most common structures of FeRAM are the ferroelectric field effect transistor (FeFET) and the capacitor-like one-transistor one-capacitor (1T1C) cell. FeFET is similar to a floating-gate MOSFET cell, where a ferroelectric stack replaces the floating gate. In this structure the ferroelectric polarization modifies the threshold voltage of the transistor and the cell is programmed through the application of a positive or a negative voltage on the gate. However, the write operation in FeFET degrades the endurance due to charge trapping effects and defects generation. In the 1T1C cell, a capacitor composed of a ferroelectric material interposed between two metal electrodes is integrated at the drain of a transistor that acts as a selector. A positive write pulse is applied to sense the polarization state, if the polarization is negative, a large transient current can be detected. However, since this operation is disruptive and the cell must be rewritten, a high endurance of about  $10^{14}$  is required [22, 23]. FeRAM is a good alternative to DRAM due to its high speed and low voltage operation, however due to its difficulties with 3D scaling and integration, FeRAMs cannot be considered good options for SCM [18, 20]. Nevertheless, FeRAMs have gained interest after the discovery of the ferroelectricity of hafnium dioxide thanks to its CMOS compatibility and scalability 24.

Fig. 1.5. (a) Structure of FeFET and ID-VG characteristics of two VTH states. (b) Capacitor based FeRAM and QFE-VFE hysteresis loop [22].

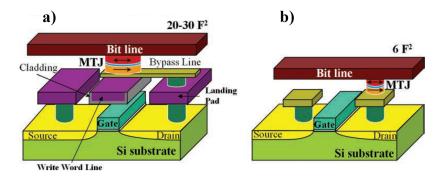

#### 1.1.2 STT-RAM

Spin-transfer torque magnetic random access memory (STT-RAM) is the replacement of magnetic random access memory (MRAM). Both store the information in a magnetic tunneling junction (MTJ), which consists of three elements: a reference layer with a fixed ferromagnetic orientation; a free layer, whose magnetic orientation can be modified, and a tunnel barrier that is a dielectric sandwiched between the two magnetic layers. The storage is possible thanks to the tunnel magneto-resistance (TMR) effect according to which only electrons with the same spin orientation of the second layer can tunnel it. Therefore, the resistance is lower when the two ferromagnetic layers have the same magnetic orientation and is higher when they have opposite orientation [25]. Free layer orientation is obtained differently in MRAM and STT-RAM. In MRAM, memory switching is achieved by an external field, generated by a current passing through two orthogonal metal lines. In STT-RAM, the direction of the current passing through the MJT causes the orientation of the free layer, exploiting the spin-transfer torque effect. Two major issues of MRAM were resolved by STT-RAM: the scalability (since in MRAM the current does not scale with the cell size, resulting in significant energy consumption) and a problem called "half-select", which is an intentional switching of the cells above or below the selected cell due to the magnetic field created. Due to the absence of the additional metallic wires required by MRAM, STT-RAM presents also a simpler and smaller cell compared to MRAM [25].

Since atoms are not moved and only the magnetization is rotated during the write operation, the endurance of STT-RAM can be higher than 10<sup>12</sup>. However, dielectric breakdown of the tunnel barrier can limit the endurance, if high voltages are applied [26, 27]. STT-MRAM is considered a promising candidate in low-level cache since it shows lower leakage power and smaller cell size than SRAM and higher write endurance than any NVMs. The main issue of STT-RAM is the high writing energy to achieve faster write speed [28]. To minimize write energy and latency, a reduction in data retention has been proposed. By decreasing the free layer area of the MJT, the write current decreases reducing write latency and write energy, nevertheless, the data retention time is

Fig. 1.6. (a) A Conventional MRAM cell. (b) A STT-RAM cell. [25]

reduced from 10 years to several ms or  $\mu$ s and, to prevent data loss, a refresh operation is required 29.

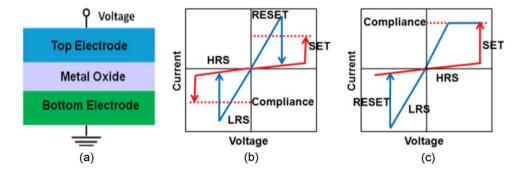

#### 1.1.3 RRAM

A resistive random access memory (RRAM) is characterized by a basic structure called metal-insulator-metal (MIM) that consists of an oxide sandwiched between two metal electrodes (Fig. 1.7a). A reversible resistive switching can bring the insulator to the conductive state by applying a voltage pulse, which causes a large modification in the device resistance. Post-fabrication the resistance of the RRAM cell is high and requires an operation called electroforming, based on the application of a high voltage stress to reduce the resistance of the device. A memory selector is used, since the current flowing through the cell must be limited by a compliance current to avoid the electrical breakdown of the cell. The switching behavior depends on the MIM materials and can be classified as unipolar or bipolar: in the unipolar (or nonpolar) switching, the transition from one resistive state to the other depends only on the amplitude of the voltage; on the contrary, in the bipolar switching it depends on the voltage polarity (Fig. 1.7b-c). The voltage application leads to the formation of a conductive filament in the insulator during the transition to the low resistive state (RESET) [30].

Hafnium oxide  $(HfO_x)$  is one of the most mature RRAM materials explored that is usually used with TiN electrodes to achieve a bipolar switching.  $HfO_x$  based RRAM

Fig. 1.7. (a) Schematic of RRAM MIM structure and schematic of I-V curves for (b) unipolar and (c) bipolar switching 30.

shows high speed operation (<10 ns), large ON/OFF ratio (>100), good endurance (>10<sup>6</sup> cycles) and multilevel storage [31]. Instead, RRAM with TaO<sub>x</sub> (tantalum oxide) is recognized for the endurance higher than  $10^{12}$  cycles [32].

RRAM has attracted interest for the low energy operation, the low cost, the fast write operation and the good scalability. However, the main limits of RRAM are the temporal (cycle-to-cycle) and spatial (device-to-device) variability of the programmed resistance due to the stochastic formation and rupture of the conductive filament in the oxide [33].

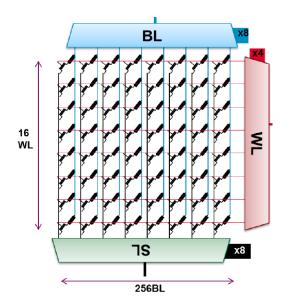

#### 1.1.4 PCM

Phase-change memory (PCM) is a dual terminal memory that exploits the property of phase-change materials to reversibly switch from an amorphous to a crystalline phase. In a PCM device, this transition is obtained by Joule heating through electrical pulses. The crystalline phase is characterized by a low resistivity, while the amorphous phase features a high resistivity. The large resistive contrast between the two phases exceeds 2-3 orders of magnitude and makes the PCMs suitable for multilevel storage. The multilevel capability can be limited by the resistance drift that can be mitigate through material engineering or error correction metrics and architectures [34–36]. PCM high maturity is demonstrated by its manufacturability and reliability in 28 nm technology node for automotive applications [37] and by its commercialization in SCM market, thanks to 3D XPoint technology [38]. Indeed, the excellent scalability, fast read and write time, good endurance and multilevel cell make PCM a good candidate for SCM [7].

PCM will be better described and analyzed in the next chapter.

Fig. 1.8. Position of 3D cross-point memory compared with DRAM and 3D NAND in terms of latency and normalized cost [39].

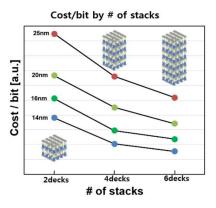

Fig. 1.9. Calculated cost per bit of 3D cross-point memory for scaling and vertical stack-up. [39].

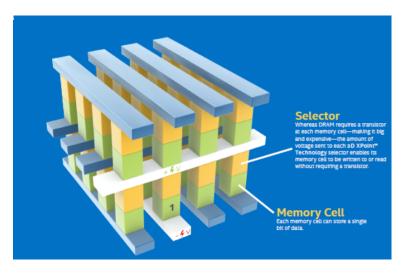

Fig. 1.10. Intel and Micron 3D XPoint technology.

# 1.2 The cross-point architecture: towards a 3D BEOL memory

3D integration is fundamental for boosting the memory density and reducing the cost of SCM architectures. New 3D memory technologies must collocate between DRAM, that is expensive and fast, and NAND Flash, that is cheap but slow, hence should exhibit low latency and cost effectiveness, as indicated in Fig. 1.8. Fig. 1.9 shows how the cost is reduced from both lateral and vertical scaling, assuming that the peripheral circuit is placed completely under the cell array. Without this condition, the number of die per wafer cannot increase [39].

In 2003, the first 3D cross-point (XPoint) memory technology of 512 Mb with 8 layers of vertically stacked memory cells was developed [40, 41]. The memory cell is a poly-silicon based SiO<sub>2</sub> anti-fuse, situated at the intersection between perpendicular word-line and bit-line, which is only programmable once.

A stackable 3D cross-point based on PCM and on an Ovonic Threshold Swith (OTS) selector has been demonstrated in 2009 [42]. Robust isolation of individual PCM cells is ensured by the high resistive amorphous selector. PCMs with OTS are fully stackable over CMOS circuits and the compatibility of PCM with metallization schemes makes feasible the superimposition of multiple layers of cross-point memory arrays. 3D XPoint memory technology was commercialized in 2015. It is 1000 times faster than NAND, 10 times denser than conventional DRAM memory and presents 1000 times greater endurance than NAND. Cells can be addressed individually ensuring faster read and write operations. Therefore, data can be stored close to the processor and accessed at speeds previously impossible for non-volatile storage [43]. The first generation of 3D XPoint memory technology is capable of storing 128 Gb in a die, the second generation has doubled the capacity and future scaling will continue to increase the capacity reducing the cost per bit, while material tuning and circuit design optimization will decrease latency [44].

3D XPoint is exploited in two Intel technologies: Intel Optane Persistent Memory (PMem) and Intel Optane SSDs. Intel Optane PMem is a valid alternative to DRAM

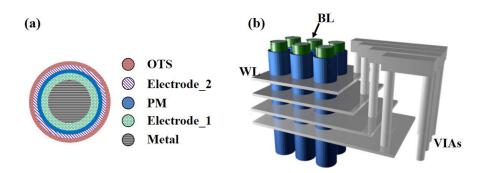

Fig. 1.11. Vertical cross-point architecture. a) Cross section of the bit-line pillar. b) Schematic of the overall vertical cross-point architecture [46].

delivering high capacity at a low cost for rapid data processing, introducing a new category in the memory hierarchy between memory and storage. Intel Optane PMem has two operating modes: Memory Mode and App Direct Mode. In Memory Mode, the amount of volatile memory visible to the operating system is extended without application changes. The CPU uses the DRAM as cache and the Optane persistent memory as addressable main memory, providing larger memory capacity and lower cost than DRAM. In App Direct Mode, the operating system sees Intel Optane PMem and DRAM as two separate entities, and software and application can talk directly to Intel Optane PMem that can act like an SSD with higher endurance and better bandwidth compared to NAND [45]. On the other hand, Intel Optane SSDs consists of a new storage tier between Intel Optane PMem and NAND SSDs. It provides low latency for database applications that require frequent high-speed caching.

However, in 3D XPoint, it is challenging to increase the number of stacked layers, since the amount of lithography and process steps increases linearly with the number of stacked layers, reducing the cost effectiveness of this architecture.

A new proposed architecture is the Vertical XPoint (V-XPoint) that mimics the highly mature 3D NAND fabrication [47]. In V-XPoint, word-line and bit-line are arranged in the lateral and in the vertical directions, as indicated in Fig. [11]. This structure allows reducing the number of patterning steps, improving the cost effectiveness. V-XPoint requires Atomic Layer Deposition (ALD) to ensure conformal film growth over the 3D structure and the research on ALD selectors is still at the beginning [46].

#### **3D** cross-point challenges

In order to achieve a high density in 3D cross-point architectures, word-line and bit-line must be scaled at the same rate as the selector and the memory cell. As Cu wires scale down to a width comparable to the mean free path of Cu, the wire resistivity increases. The resistivity increase can cause degraded write/read margins, reduced speed and substantial energy dissipation of wires. This is a limit on the array size increasing. Possible solutions to overcome the Cu limits may be the use of wires with better conductivity and scalability, such as graphene or carbon nanotubes or memory arrays with smaller partition size [48].

In a cross-point architecture, a half-selected scheme is commonly used, in which the cells along the same word-line and bit-line of the selected cell are biased by a voltage

V/2, in contrast to the selected cell biased at the voltage V. The applied voltage can enable an excessive leakage in the half-selected cells causing sneak paths [49]. Sneak paths are undesired paths for current that act as an unknown parallel resistance to the selected cell resistance narrowing the noise margin and reducing the maximum size of the cross-point array [50]. The choice of an access device with a low leakage current is fundamental to reduce the sneak paths.

### **1.3 3D cross-point selectors**

In a cross-point architecture, the read and write operations must take place in the desired memory cell avoiding disturbing any other cell. In this context, the selector comes to play.

The features that a selector should have are listed below [49, 51]:

- 1. **Two-terminal structure** to not occupy an extra area in the array and ensure the minimal cell size. For this reason, transistors as selectors must be avoided.

- 2. High ON-state current density on the order of several MA/cm<sup>2</sup> to provide enough current to program and erase the memory cell.

- 3. **High non-linearity**, namely the OFF state leakage current must be as low as possible to prevent the leakage through the unselected cells and the associated power consumption. If this condition is satisfied, the maximum array block size can be increased.

- 4. Process compatibility with 3D multilayer stacking: the materials of the selector must be CMOS compatible and the selector must be compatible with the Back-End-of-Line (BEOL) fabrication process to enable the stacking of multiple layers of cross-point arrays. To be compatible with the BEOL, the maximum thermal budget during the fabrication must not exceed 400 °C and the access device must remain functional after 2 hours at 400 °C.

- 5. Voltage compatibility with the memory element to ensure read and write operations in the selected memory cell and low leakage in the unselected cells. Furthermore, the voltage should be compatible with device-to-device variations and changes in the operating temperature.

- 6. Speed, endurance and variability of the access device should be better than those of the memory element to not limit memory chip performance and reliability.

Furthermore, STT-RAM and bipolar RRAM require the current to flow in opposite directions for the programming and erasing operations, in this case, the selector must guarantee bipolar operation.

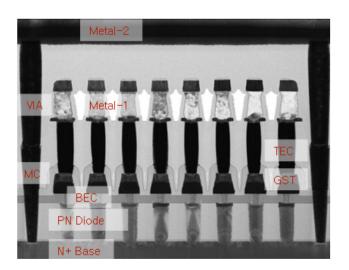

Fig. 1.12. Vertical view of a 512 Mb PRAM array with PN diode selectors 52.

#### Si-based selectors

PN diodes are able to provide enough current for the switching operation of a memory cell minimizing the off-current and ensuring cell area efficiency.

For example, functionality of a 512 Mb PCM array was demonstrated using a vertical PN diode as selector (Fig. 1.12) 52. A poly-Si diode was used in a cross-point with PCMs showing low off-current of 100 A/cm<sup>2</sup> and high on-current of 8 MA/cm<sup>2</sup> that can support PCM programming operation 53. Also a n+/p/n+ vertical junction showed bipolar operation and high switching speed, furthermore the on-voltage can be tuned modifying the p-region doping and its length 54. However, a temperature of 700 °C is required for fabrication making it incompatible with BEOL fabrication process. This is a limit of all Si-based selectors where the dopant activation needs higher temperature not suitable for 400 °C BEOL process and 3D stacking of multiple layers 51.

#### **Oxide-based diodes**

Oxide-based diodes have been proposed as alternative to Si-based diodes since they can be fabricated at BEOL compatible temperatures.

Binary oxide diodes consisting of NiO as p-type semiconductor and TiO<sub>2</sub> as n-type semiconductor have been fabricated below 300 °C combined with oxide-RRAM cells, showing a proper functionality [55]. However, this NiO/TiO<sub>2</sub> diode can provide a maximum current density of  $10^{3}$ A/cm<sup>2</sup>. P-CuO<sub>x</sub>/n-InZnO<sub>x</sub> showed an increased current density of over  $10^{4}$ A/cm<sup>2</sup> and can be easily fabricated at room temperatures [56], although the current density is still not enough high for 3D cross-point architectures. A Ni/TiO<sub>2</sub>/Ni bipolar nonlinear selector has been reported in [57]. It was fabricated by sputtering at 200 °C in series with oxide-RRAM. The Schottky emission over the Ni/TiO<sub>2</sub> barrier allows achieving highly nonlinear characteristics with an ON/OFF ration of six orders of magnitude between 0 and ±2 V. Furthermore, Ni/TiO<sub>2</sub>/Ni demonstrated capable to provide a current density of  $10^{5}$ A/cm<sup>2</sup> and to be fabricated at room temperature in a 8×8 cross-bar array [58].

#### Mixed Ionic-Electron Conduction (MIEC) selectors

Mixed Ionic-Electron Conduction (MIEC) materials conduct both ions and electrons (or holes) and typically contain a large amount of Cu. The Schottky barrier at the MIEC-electrode interfaces suppresses the current flow at low bias. As the bias increases, copper ions and vacancies shift leading to an exponential increase of the current [59]. Selectors based on MIEC materials can be fabricated at BEOL compatible temperature, are scalable, can conduct high currents (>50 MA/cm<sup>2</sup>) and provide a large ON/OFF ratio (>10<sup>7</sup>). This makes MIEC selector interesting for multiple stacking in PCM cross-point arrays [60].

MIEC-based access devices have been integrated with PCM, demonstrating to enable RESET operations at currents higher than 200  $\mu$ A in <15 ns. The devices are still functional if scaled down to a thickness of 11 nm and to <30 nm in lateral size. Despite a leakage increase as the thickness is reduced to 6 nm, the voltage margin improves when the lateral sizes are reduced [61]. Furthermore, large 512 kb arrays with 100% yield have been realized co-integrating PCM and MIEC selectors exhibiting large currents (>200  $\mu$ A), low leakage (<10 pA) and high voltage margin (1.5 V) [62]. Scaling is also beneficial for endurance, indeed an improved endurance in thinner MIEC selectors integrated with PCM has been shown. Endurance can reach 10<sup>8</sup> cycles using 150  $\mu$ A as programming current, but higher currents reduce cycling endurance leading to earlier failures [63].

#### Metal-Insulator transition (MIT) selectors

Some oxides, such as VO<sub>2</sub>, have a metal-insulator transition (MIT) property that can be exploited using these materials as access devices. VO<sub>2</sub> devices show fast switching speed (<20 ns) and high current densities (>10<sup>6</sup>A/cm<sup>2</sup>) [64]. Although VO<sub>2</sub> exhibits an excellent MIT characteristic, its transition temperature of 67 °C [65] makes it unsuitable for applications that need higher operating temperatures [49]. On the contrary, NbO<sub>2</sub> remains stable up to 160 °C. Fast switching speed (22 ns), excellent scalability down to 10 nm and high ON current (>2MA/cm<sup>2</sup>) were observed in NbO<sub>2</sub>-based access devices [66]. However, the leakage current in half-selected and unselected devices is still high, due to the low band-gap of MIT materials [49], [51].

#### **Ovonic Threshold Switch (OTS) selectors**

OTS selectors enabled the commercialization of Intel and Micron 3D XPoint. OTS are based on amorphous chalcogenide materials capable of switching to the crystalline phase reversibly and volatilely. As the voltage across the OTS exceeds a threshold voltage  $(V_{TH})$ , the device switches to the conductive state and, as the current is reduced below a certain value defined as holding current, the OTS switches back to the highly resistive state [67].

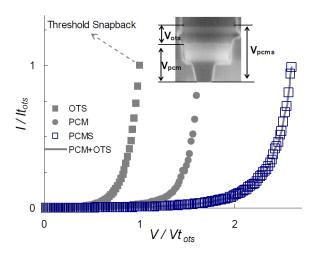

The high ON current, the high selectivity and the compatibility with the BEOL make OTS suitable for 3D integration with PCM 68. The current-voltage (I-V) characteristic of a RESET PCM integrated vertically with an OTS is illustrated in Fig. 1.13:  $V_{TH}$  is equal to the sum of the OTS  $V_{TH}$  and PCM  $V_{TH}$ , since OTS and PCM are connected in series 42. When the PCM is in the crystalline phase,  $V_{TH}$  is that of

Fig. 1.13. I-V characteristic of an OTS, a PCM and an OTS+PCM. The PCM was programmed in the RESET state [42].

the OTS. Hence, this threshold voltage mechanism allows distinguishing the different resistive states of the PCM.

OTS performance depends on the chalcogenide material used. AsTeGeSi shows an ON current higher than 11 MA/cm<sup>2</sup> and an endurance higher than  $10^8$  [69]. Nevertheless, Te-based OTSs exhibit a selectivity lower than  $10^4$  that is insufficient for achieving dense PCM arrays [68]. An OTS based on binary B-Te alloy exhibits high ON/OFF current ratio grater than  $10^5$ , low operating voltage, low leakage, fast switching speed, endurance up to  $10^8$  cycles and a high ON current of 55 MA/cm<sup>2</sup> [70]. Also GeSe OTS showed high drive current of 23 MA/cm<sup>2</sup>, endurance grater than  $10^8$  and tunable turn-on voltage [71]. SET and RESET operations have been demonstrated in AsSeGe selector integrated with PCM. The selector can deliver 7.9 MA/cm<sup>2</sup> and fast speed (10 ns). Moreover, an excellent cycling endurance of  $10^{12}$  is achieved in AsSeGe OTS+PCM [72].

|                       | FeRAM   | STT-RAM | RRAM      | PCM       |

|-----------------------|---------|---------|-----------|-----------|

| Scalability           | Limited | Limited | Promising | Promising |

| Multilevel cell       | Limited | Limited | Medium    | Good      |

| <b>3D</b> Integration | Limited | Medium  | Good      | Good      |

| Write Speed           | High    | High    | Medium    | Medium    |

| Write Power           | Medium  | Medium  | Medium    | High      |

| Retention             | Medium  | Good    | Medium    | Good      |

| Endurance             | Good    | Good    | Limited   | Medium    |

| Variability           | Low     | High    | High      | Medium    |

Table 1.2.

Comparison of emerging NVM technologies for SCM. Adapted from [20]

### **1.4** Summary of the chapter

In this chapter, we discuss the challenges of the traditional memory hierarchy and how they can be overcome by SCM, which goal is to reduce the gap in performances and cost between storage and memory.

Scalability, 3D integration, multilevel cell capability are characteristics required by memory devices to satisfy the high density requirements of SCM applications. Other key features of SCM are low fabrication costs, long data retention, low latency, low power consumption, high endurance and low variability. A comparison of emerging NVMs in terms of these attributes is shown in Table 1.2.

Despite low power and low latency, FeRAM is not indicated for SCM applications due to the poor MLC capability, difficulties in scaling and 3D integration.

Among the described emerging NVM, STT-RAM features the highest endurance. However, maintaining long data retention while achieving competitive speed, endurance, and scalability is challenging.

RRAMs offer the benefit of a simple structure with correlate low cost, however variability and endurance must be improved verifying if aggressive scaling can be supported.

PCM is the most mature among emerging NVM since the multilevel cell capability and good scalability can increase the device density. Latency and endurance can be further improved thanks to material engineering. Power efficiency efforts are ongoing to reduce the power consumption of these memories. For its features and maturity, PCM can be considered the best candidate for SCM.

Indeed, PCM was exploited by Intel and Micron 3D XPoint memory, which is faster than NAND, denser than regular DRAM memory, and offers more endurance than NAND. Moreover, individual cell access provide faster read and write operations.

Read and write operations in a 3D XPoint memory can be realized without disturbing other memory cells thanks to a selector. Different types of selector for 3D architectures have been discussed in this chapter

Si-based selectors require for the fabrication high temperatures incompatible with BEOL process and 3D vertical stacking. However, although oxide-based diodes are compatible with the BEOL fabrication, they can not provide sufficient current density for PCM programming. MIEC selectors offer BEOL compatible temperatures, high ON/OFF ratio, high ON currents and low leakage, however high drive currents reduce the endurance. Among MIT selectors, NbO<sub>2</sub> ensures higher operating temperatures than VO<sub>2</sub> and high ON currents, nevertheless the leakage current is not sufficiently low. The high ON current, high ON/OFF ratio and great endurance of OTS make it suitable for 3D integration with PCM, as confirmed also by the choice to use OTS and PCM in 3D XPoint technology. The research is still active to improve OTS endurance and reduce leakage through material engineering.

## Chapter 2

## **Phase-Change Memory**

In the late 1960s, Ovshinsky discovered a rapid and reversible transition between a highly resistive and a conductive state enabled by electric field in chalcogenide materials [67]. In the '70s, it was proposed to exploit this reversible switching in NVM devices [73], 74. However, the first PCM devices were characterized by high energy consumption due to high programming currents and low speed that prevented their commercialization for long time [75]. After almost three decades, the interest in phase-change technology was renewed: GeSbTe alloys were exploited in optical recording media [76], since these alloys can be switched using laser pulses of short duration. The feasibility of PCM with low energy consumption, high speed and high endurance was demonstrated at the beginning of the second millennium [77, 78]. Read and write operations in memory array are ensured by a selector that must be coupled with the memory cell. BJT was proposed as selector in a 8 Mb array integrated in a 180 nm CMOS process to get high density [79]. Since MOSFET selectors occupy a large area, they cannot be exploited for high density standalone applications, though they can be integrated with few masks into CMOS technology reducing the costs and making them suitable for embedded applications [80]. In 2009, the first 128 Mb array based on a 90 nm PCM technology was commercialized to meet NOR Flash replacement requirements [81]. Finally, a 1 Gb PCM cell array with BJT selector based on a 45 nm technology node was developed 82. At the beginning, PCM development was focused on replacing NOR Flash in cellular phones [75]. This bet turned out wrong, since with smart-phones NAND Flash architecture became dominant due to the high storage capacity demand. PCM prototypes were also realized for SSDs showing improvements in read latency and bandwidth [83]. However, the product was never introduced since density and cost were not still competitive with NAND Flash. Recently PCM entered both embedded and stand alone market. Indeed, ST Microelectronic developed a highly scaled 28 nm embedded PCM that meets automotive reliability criteria [84]. Concerning standalone market, PCM is included in 3D XPoint that has achieved high volume production concretizing the concept of SCM 44.

In recent years, research is working to improve PCM performance on two main fronts [75]:

1. by a scalable cell architecture to minimize the programming current. In fact, PCM working mechanism is based on the ability to convert the current across the device in temperature, but most of the heat generated is lost in the surrounding

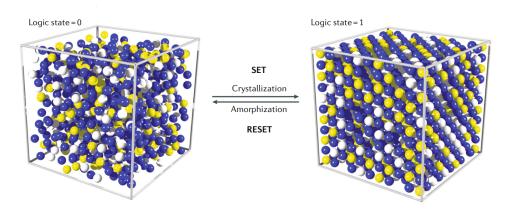

Fig. 2.1. Phase-change transition consequent to SET and RESET operations 85

structure. Therefore, a thermally optimized cell is able to reduce significantly the programming current.

2. by material engineering to tailor PCM properties accordingly to the target applications.

These two subjects will be better discussed later in this chapter.

#### Brief history of phase-change materials for PCM

The first chalcogenide proposed by Ovshinsky was  $Ge_{10}Si_{12}As_{30}Te_{48}$ , but the low speed and low endurance limited its utilization [67]. In the late 1980s, GeTe and GeSbTe compounds in the GeTe-Sb<sub>2</sub>Te<sub>3</sub> tie line, such as  $Ge_2Sb_2Te_5$  and  $Ge_1Sb_2Te_4$ , became popular in optical storage thanks to their fast crystallization. Then, also doped Sb and Sb<sub>2</sub>Te compounds were developed for optical applications, in particular  $Ag_4In_3Sb_{67}Te_{26}$ (AIST) was widely used [85].

In the 2000s, the interest for PCMs was renewed and GeSbTe compounds, in particular  $Ge_2Sb_2Te_5$ , were selected to be integrated in PCM devices thanks to the good cyclability and improved programming speed [85]. However, to make PCM competitive with DRAM and NAND Flash memory technologies, research efforts are required to find the best phase-change materials.

### 2.1 PCM working principle

PCM is a dual terminal resistive memory that exploits the electrical properties of some chalcogenide materials, which are alloys consisting at least of one chemical element in the VI group of the periodic table [87]. These alloys can switch reversibly from an amorphous phase to a crystalline phase: the low-resistance crystalline phase is referred as SET state, while the high-resistance amorphous phase as RESET state (Fig. 2.1). In phase-change materials, this transition occurs thanks to a temperature increase that can be induced optically, like in optical disks, or electrically, like in PCM. After the BEOL fabrication process at 400 °C, the PCM is in the crystalline phase. To bring the cell to the amorphous phase, the temperature must increase above the melting point

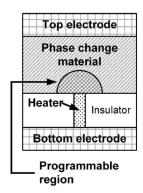

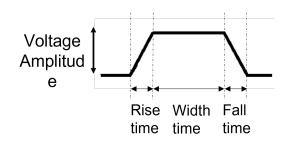

Fig. 2.2. Schematic of a conventional PCM cell, usually referred as mushroom cell [86].

of the phase-change material and then the cell must be quenched rapidly to preserve the disorder typical of the amorphous phase. For the SET operation, the cell must be kept above the crystallization temperature for a time period long enough to crystallize it. Fig. 2.2 shows a typical PCM cell, consisting of a top and a bottom electrode, through which the electrical current flows, the phase change material and the heater, where the heat is generated thanks to Joule effect. The length and the intensity of the program pulse control the local temperature. A short and sufficiently intense program pulse enables the RESET operation. However, the falling edge of the pulse must be fast enough to make effective the RESET operation, otherwise a re-crystallization can be induced. Indeed, the length of the falling edge slows the cooling, favoring the organization of the material in the ordered crystalline phase.

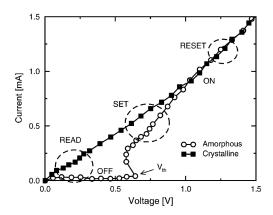

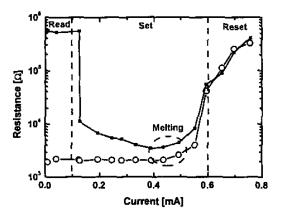

The current-voltage (I-V) curve of a PCM is reported in Fig. 2.3. At low field, crystalline and amorphous phases exhibit a large resistance contrast, in this part of the curve read operation is performed. SET and RESET programming regions can be reached increasing the bias above the switching threshold voltage  $(V_{TH})$ , so that the currents is able to heat the programming region of the cell causing the phase-change [88]. The resistance behavior at different bias is shown in Fig. 2.4. At low currents, the cell resistance state remains the same (READ region). If a device is programmed in

Fig. 2.3. Experimental I-V characteristic of a GST based PCM in the amorphous/RESET and in the crystalline/SET state [88].

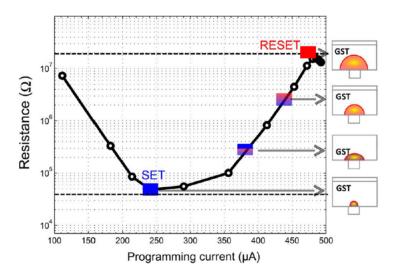

Fig. 2.4. Experimental resistance-current curve of GST PCM programmed in both SET and RESET state [89].

the high resistive state, the resistance drops at higher currents (SET region) and starts to rise when the current is higher enough to generate a rapid cooling of the melted material [89].

### 2.2 Crystallization behavior of phase-change materials

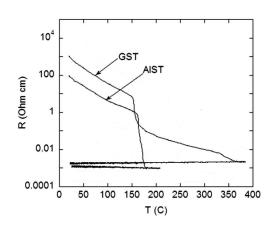

Information about the crystallization behavior of a phase-change material can be extracted from the resistivity as a function of temperature (R-T) characteristic. As shown in Fig. 2.5, amorphous film exhibits a high resistivity that decreases as the temperature increases. The drop in resistivity corresponds to the crystallization temperature that depends on the material. GST shows a more gradual transition to the crystalline phase compared to AIST, in particular GST features two transitions: one from the amorphous to the face-centered cubic phase at 154 °C and the other one from the fcc to the trigonal phase at 348 °C [90]. On the contrary, AIST shows a single steep transition from the amorphous to the trigonal phase.

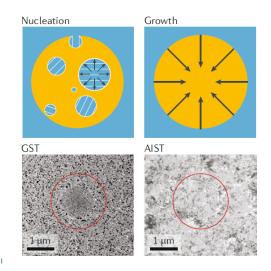

Crystallization of phase-change materials can be either nucleation-driven or growth-driven (Fig. 2.6). For nucleation-driven materials, crystallization occurs through the stochastic formation of crystalline nuclei an their growth [85]. In this case, the crystallization time does not depend on the size of the amorphous mark and the crystallized region is poly-crystalline with grains of different size and orientations.

For growth-driven materials, crystallization starts at the interface between the amorphous mark and the crystalline surrounding creating a single crystallite. The nucleation time is so long that the nucleation of crystalline seeds does not occur during the rapid growth process. In this case, the crystallization time increases as the amorphous size increases [85, 91].

Fig. 2.5. Resistivity as a function of temperature in GST and AIST. Adapted from [90].

Fig. 2.6. Above: schematic of nucleation and growth driven crystallization. Below: Transmission electron microscope (TEM) images showing the crystallized region marked by a red circle in GST and AIST that exhibit respectively a nucleation driven and a growth driven crystallization [85].

Transmission electron microscopy (TEM) analysis evidence that AIST is a growth-driven material, while GST is nucleation-driven [85]. This can explain the different transition from amorphous to crystalline phase in GST and AIST observable in the R-T curve. However, studying the crystallization behavior of phase-change materials, it must be remembered that the nucleation time of a melted-quenched material is half that of an as-deposited material, since in a melted-quenched material atomically ordered clusters already exist reducing the nucleation barrier [91].

# 2.3 Conduction in the crystalline and in the amorphous phase

Investigations on the properties of the band structure can be realized by optical and electrical characterization on thin material films.

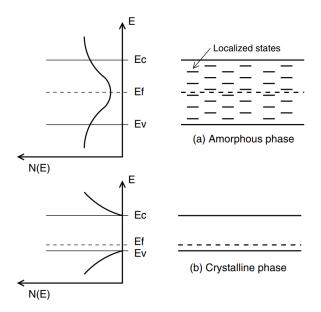

Hard x-ray photoemission spectroscopy (HXPES) is an experimental technique to determine the density of states in the valence band. Commonly, in the crystalline phase the valence band edge is closer to the Fermi level compared to the amorphous phase, since the crystalline phase is highly conductive. In amorphous GST, the band gap is about 0.8 eV, suggesting that it behaves as an intrinsic semiconductor with the Fermi level in the mid gap. In the crystalline fcc GST, the Fermi level situated close to the valence band and the narrow band gap indicates a quasi-metallic conduction. The schematic band structures of crystalline and amorphous phase is represented in Fig. 2.7. Distorted bonds, dangling bonds, wrong bonds (e.g., Ge-Ge bonds in GST) in the amorphous phase constitute defects that result in a large density of localized states in the forbidden gap [93].

Moreover, electrical resistivity measurements as a function of temperature provide information about the band structure. In Fig. 2.5, at temperatures below the crystallization temperature, the resistivity decrease is due to the temperature activation of

Fig. 2.7. Schematic band diagrams and density of states of amorphous (top) and crystalline (bottom).

Fig. 2.8. I-V characteristics for a RESET PCM at increasing temperatures. Inset: Arrhenius plot of the current measured at three values of voltage 92.

Fig. 2.9. Schematic for the trap-limited conduction mechanism with electrons confined by potential barriers at zero bias (a) and after voltage application (b) [92].

transport deriving from thermal generation of carriers from the valence band to the conduction bands of the amorphous semiconductor. The activation energy corresponding to the energy difference between the Fermi level and the valence band, equal to half of the band gap for the amorphous phase, can be estimated from the Arrhenius plot [93]. In the crystalline phase, the smaller slope, that results in a lower activation energy of conduction, indicates a more favorable conduction compared to the amorphous phase.

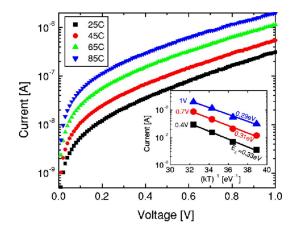

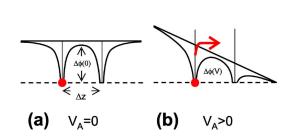

Although thin films investigations provide basic knowledge of the phase-change material, electrical characterization of PCM devices offers more insights on the conduction mechanisms. Fig. 2.8 shows the subthreshold I-V characteristic performed at different temperatures in a GST PCM device programmed in the RESET state. At small voltages below 0.3 V the curve exhibits a linear behavior, while at higher voltages an exponential regime is observed. As the temperature increase, the large activation energy of conduction of the amorphous material causes a strongly increase of the current. The current values were plotted as a function of 1/kT for different voltages in the inset of Fig. 2.8 showing an activation energy of conduction that decreases as the voltage increases. This behavior is observed in materials with a trap-limited conduction and is commonly described as Poole-Frenkel mechanism. According to this mechanism, the conduction is due to electrons thermally emitted hopping between traps. As indicated in Fig. 2.9, the application of an electric field lowers the potential barriers. Since the electron emission depends exponentially on the barrier height, the current *I* can be written as [92]:

$$I \propto e^{\frac{\Delta\Phi(0) - qV_A \Delta z/(2u_a)}{kT}} \tag{2.1}$$

where  $\Delta \Phi(0)$  is the barrier height at zero bias, q is the elementary charge,  $V_A$  is the applied voltage,  $\Delta z$  is the average distance between two traps,  $u_a$  is the thickness of the amorphous material, k is the Boltzmann constant and T is the temperature. Whereas the standard Poole-Frankel model predicts an exponential dependence of I on the square root of the voltage, in eq. 2.1 an approximation valid for small intertrap distance was utilized, assuming that the maximum of the potential barrier lies in the

Fig. 2.10. STS as a function of 1/kT [92].

middle between two traps 92.

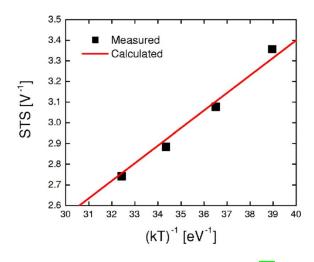

The subthreshold slope (STS) in the exponential regime can be extracted from eq. 2.1

$$STS = \frac{\partial logI}{\partial V} = \frac{q}{kT} \frac{\Delta z}{2u_a}$$

(2.2)

Therefore, STS values can be obtained from the subthreshold I-V characteristic (Fig. 2.8) in the high voltage region. The slope of Fig. 2.2, representing the STS as a function of 1/kT, is useful to calculate  $\Delta z/2u_a$ , i.e. the intertrap distance normalized to the amorphous layer thickness, that allows estimating the degree of disorder in the amorphous phase-change material, or rather, if  $u_a$  is known, the intertrap distance  $\Delta z$ .

### 2.4 The threshold switching

The threshold switching is a critical feature of phase-change materials that arises from a bistable negative differential resistance (NDR) in which two distinct currents can be achieved at a given voltage [93]. Without this mechanism PCM would not be a viable technology, because in the high resistive state extremely high power would be necessary to heat the cell over the crystallization temperature. The threshold switching is reversible since removing the voltage quickly, the cell returns to the high resistance state without memory switching. Memory switching occurs only if the voltage pulse is long enough to organize the material in the crystalline phase bringing the cell in the low-resistance state.

The origin of threshold switching is still debated and has been explained by different models. At the beginning, a thermal model was proposed where the switching phenomenon was due to the thermal breakdown of the amorphous film. As the temperatures rises for Joule effect, the thermal runaway improves the electrical conductivity locally and causes a thermal generation of electrical carriers [94].

In an electronic model, the threshold switching was attributed to a carrier generation mechanism driven by electric field [95].

Fig. 2.11. Resistance as a function of time measured in  $Ge_2Sb_2Te_5$  showing the drift phenomena [98].

Fig. 2.12. Resistance drift for two different read currents 98.

Another electronic model explains the threshold switching with an energy gain of electrons for hopping among traps at high electric field that results in a non-equilibrium configuration of bands with inhomogeneous electric field [96].

In the field-induced nucleation model, the threshold switching is due to a nucleation of a long conductive cylinder. The electric field increase facilitates the nucleation of additional particles making the cylinder longer. However, the conductive embryo disappears if the field is removed too quickly, otherwise the embryo will reach a stable size ensuring the memory switching to the low resitive state [97].

Threshold switching is critical for PCM operation and performances. Indeed, the threshold voltage establishes the voltage ranges for the read and write operations and, if the PCM is integrated with an OTS selector, it defines the ON/OFF ratio.

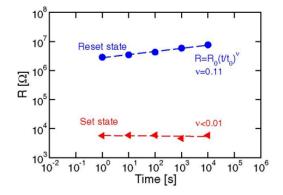

### 2.5 Resistance drift

Resistance drift indicates the increase of the programmed resistance over time due to a structural relaxation of the material, which affects the electrical conduction and the atomic arrangement.

Drift is represented in Fig. 2.3 for both RESET and SET state: SET resistance is stable, while RESET resistance increases according to the following power law:

$$R = R_0 \left(\frac{t}{t_0}\right)^v \tag{2.3}$$

where R is the resistance, t the time,  $R_0$  and  $t_0$  are constants. Although the only state affected by drift is RESET in GST, there are some materials, like Ge-rich GST, where the SET state shows a remarkable drift due to a crystalline disordered phase [99].

Structural relaxation occurs in a disordered phase, where defects of the liquid phase remain in the material after quenching, annihilating these defects. For example, structural relaxation results in fixing dangling bond or wrong bonds. The high temperature accelerates this relaxation process, leading to an increase of the resistance, the STS and the threshold voltage over time [100]. The increase of STS is due to an increase in the average distance between traps linked to the defect annihilation. Moreover, the defect

reduction results in band gap increase, widening the barrier for electrical conduction and leading the increase of the resistance and higher threshold voltage.

The increase of the RESET resistance widens the resistance window and is problematic for multilevel programming, but is not a reliability issue for single level programming, although the increase of the threshold voltage can make difficult the SET operation.

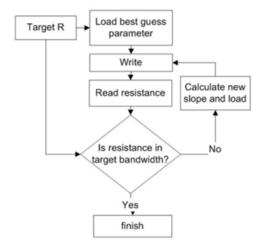

Read and program algorithms can be adopted to mitigate the drift. Indeed, the increase of the read current or of the read voltage leads to a decrease of the resistance drift 101 (Fig. 2.12). Moreover, the material and the device architecture can be engineered in order to reduce the drift. For example, a confined PCM cell with a metallic surfactant layer demonstrates to stabilize the drift, since the metallic layer provides an alternative conductive path during read operations making the cell immune to amorphous instabilities 102.

### **2.6 PCM** architectures

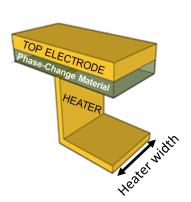

The choice of the ideal cell structure is determined by many factors such as the density of the cell and its scalability, the power consumption and the number of masks required by the cell integration [103]. PCM cell structures can be distinguished in self-heating cells, in which the heat is generated inside the phase-change material, and heater-based cells where the heater element generates the heating.

#### The mushroom cell

A conventional heater-based cell structure is the mushroom cell, where a cylindrical heater made typically with TiN is in contact with a thin film of phase-change material. Since the phase-change material is on top of a flat surface, it can be deposited using a standard physical vapor deposition (PVD) technique. In order to provide thermal insulation during the programming operations, the thermal conductivity must be low enough, while the electrical conductivity must be high enough to avoid adding series resistance. Furthermore, the electrode materials must not chemically interact withe the phase-change material and must be able to withstand the high temperatures during the RESET programming. In the mushroom cell, the RESET current depends on many factors, such as the dimensions, electrical and thermal properties of the bottom electrode and the thermal properties and thickness of the phase-change material [104].

#### The $\mu$ trench structure

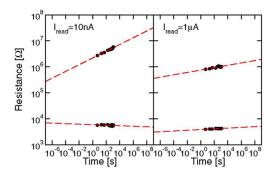

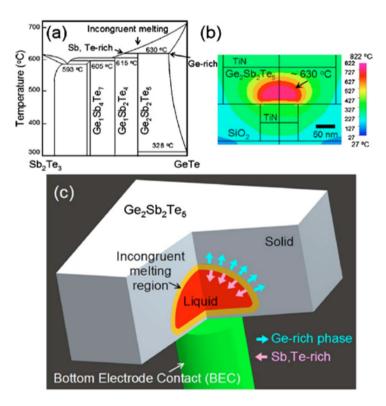

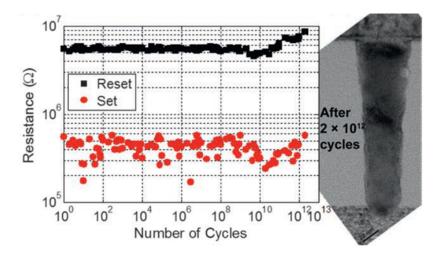

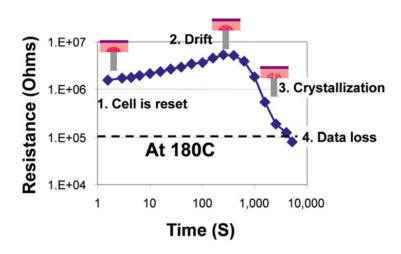

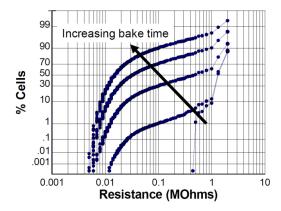

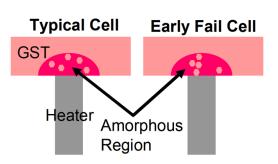

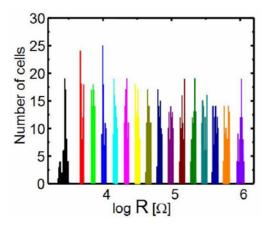

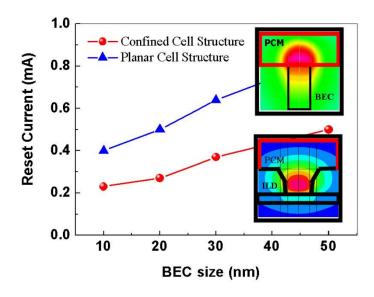

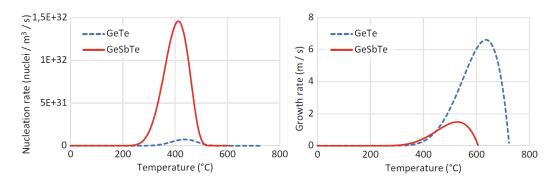

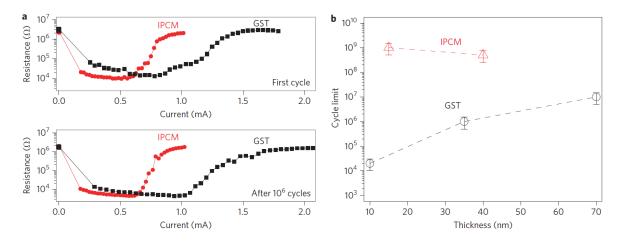

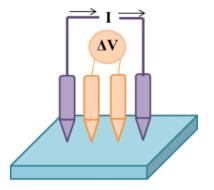

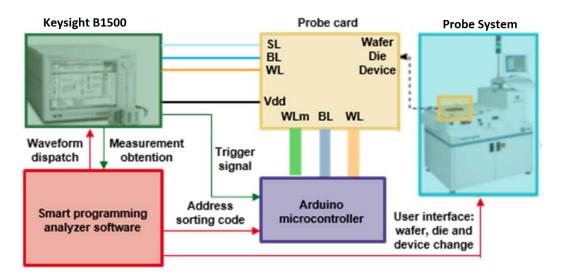

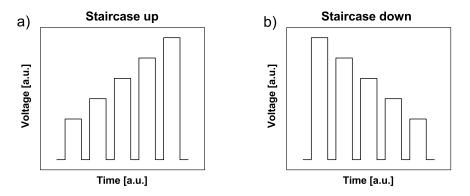

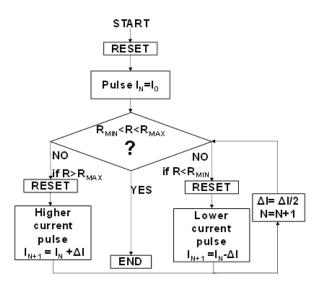

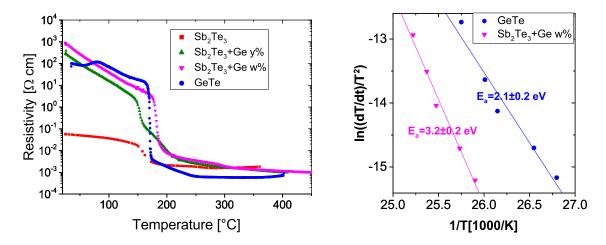

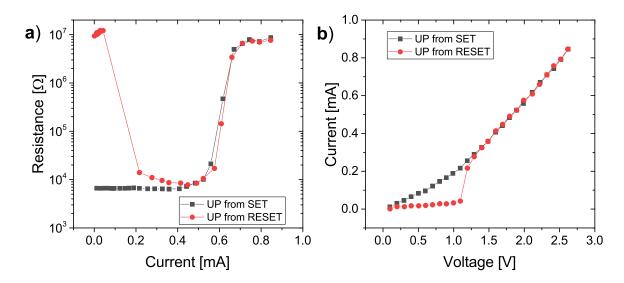

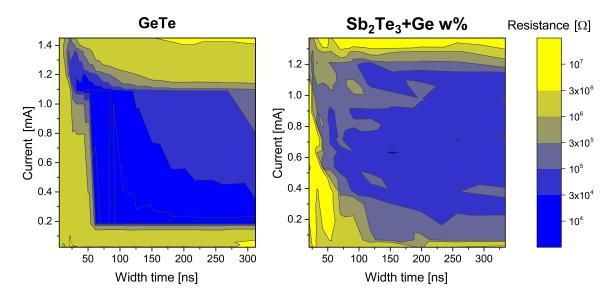

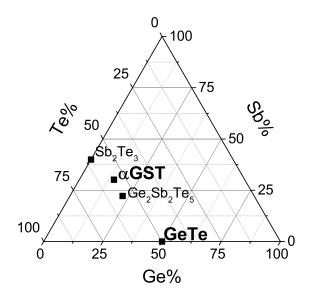

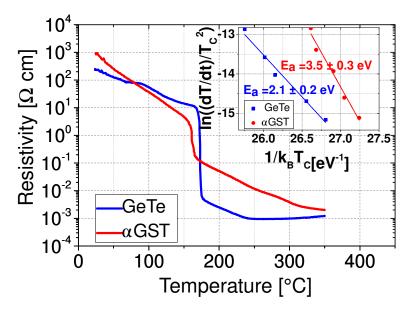

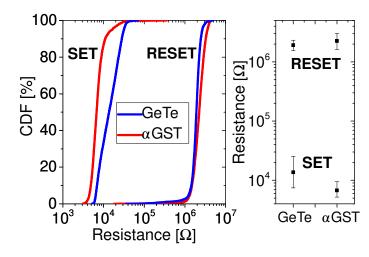

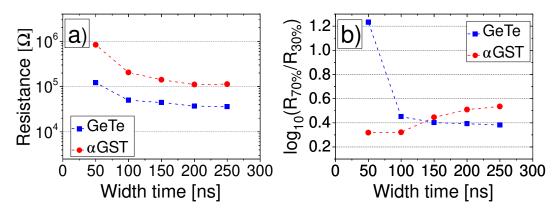

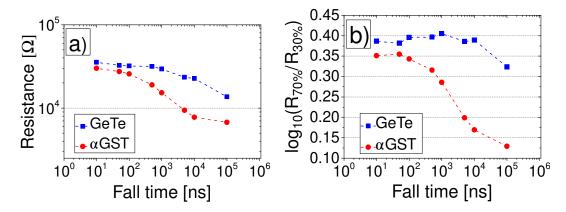

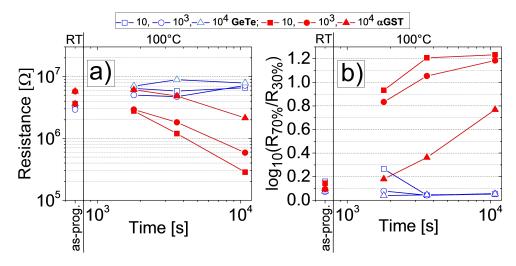

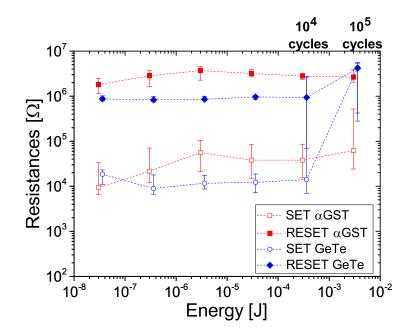

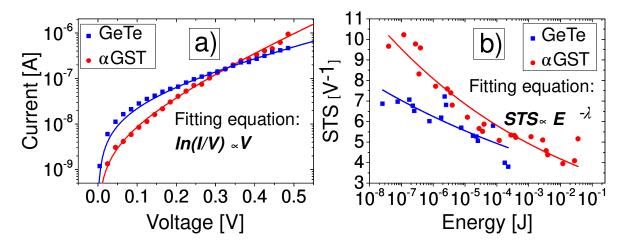

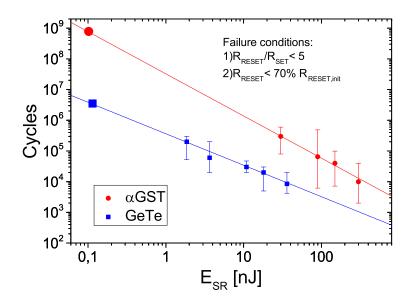

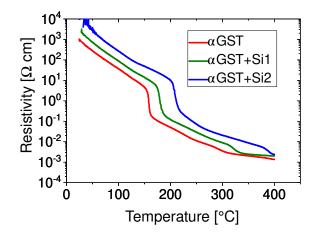

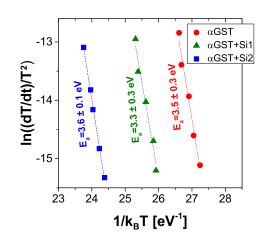

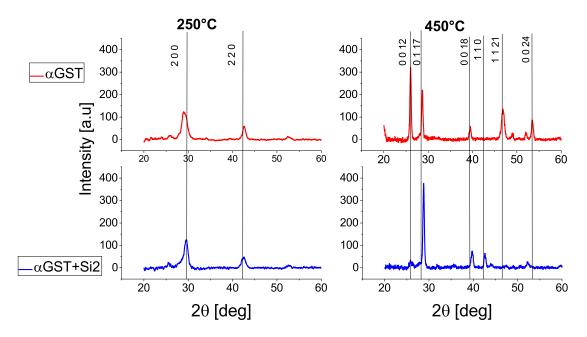

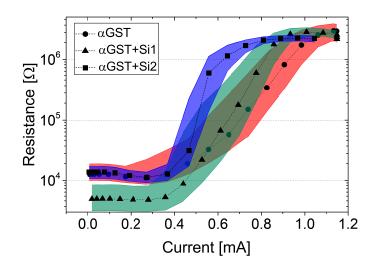

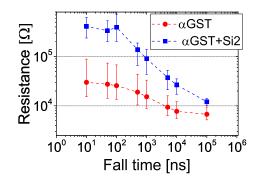

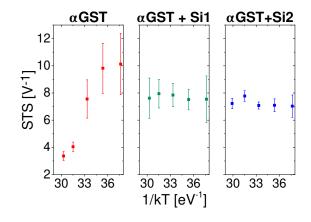

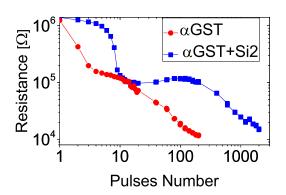

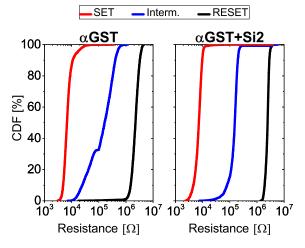

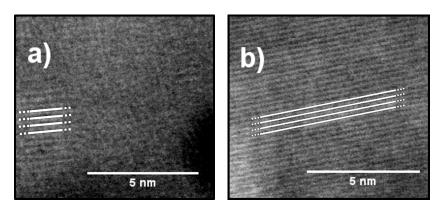

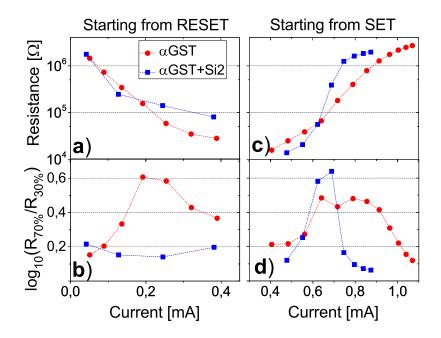

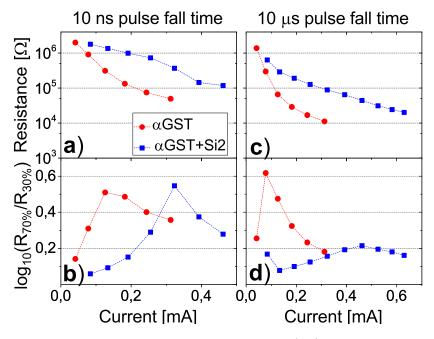

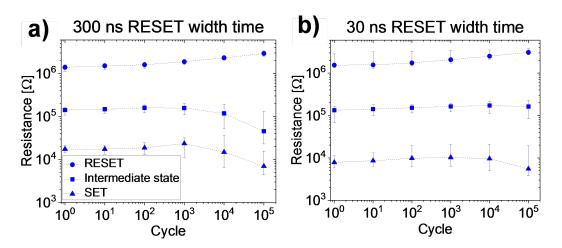

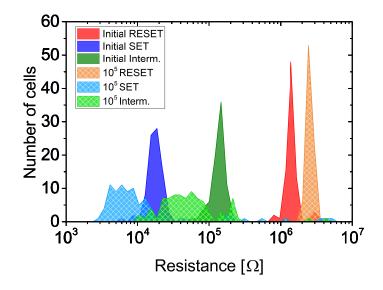

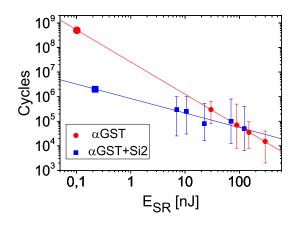

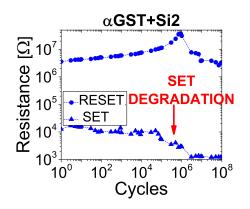

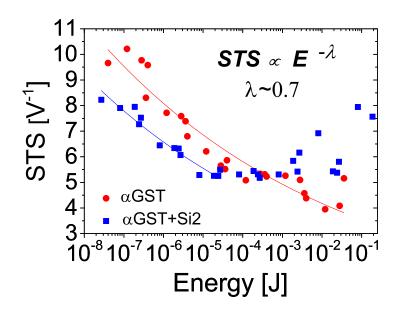

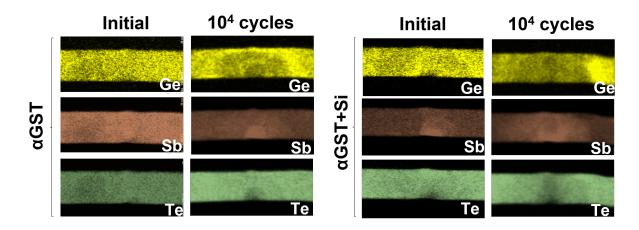

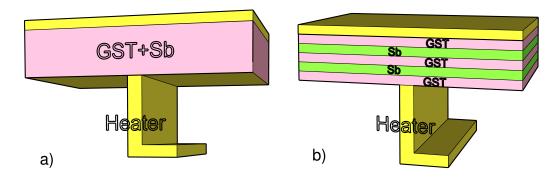

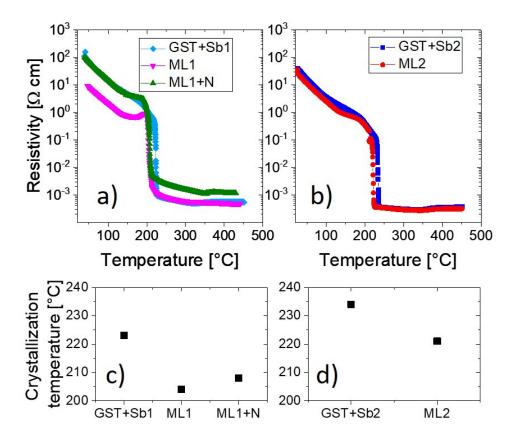

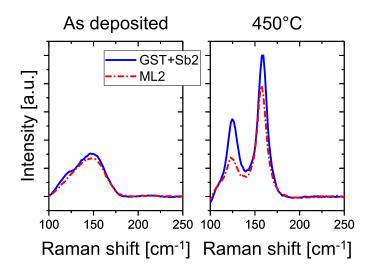

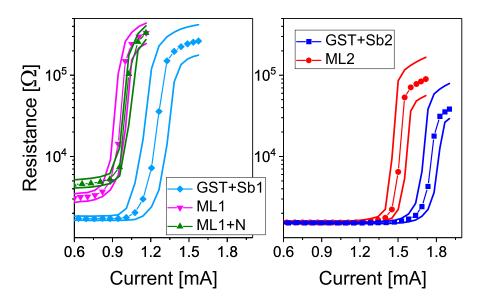

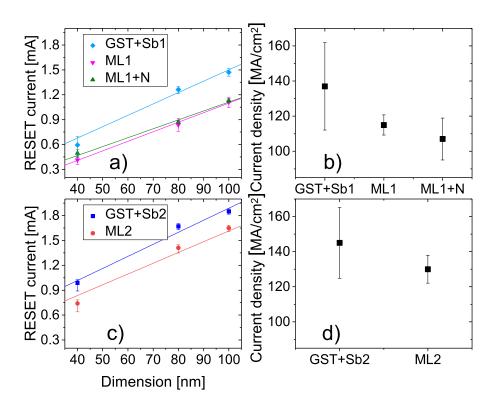

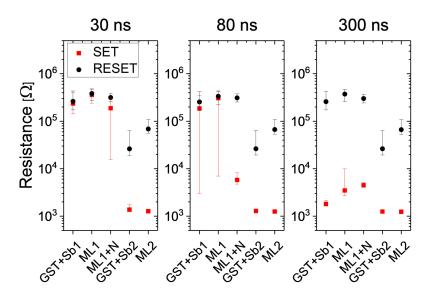

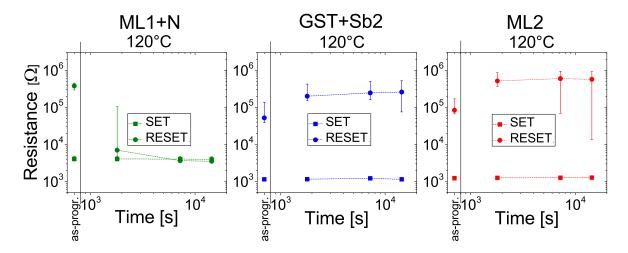

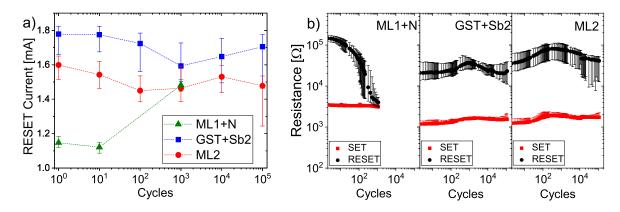

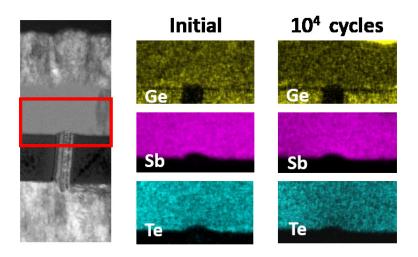

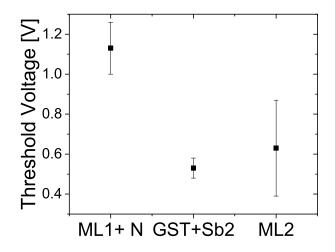

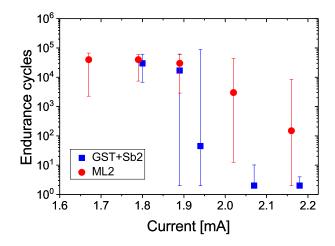

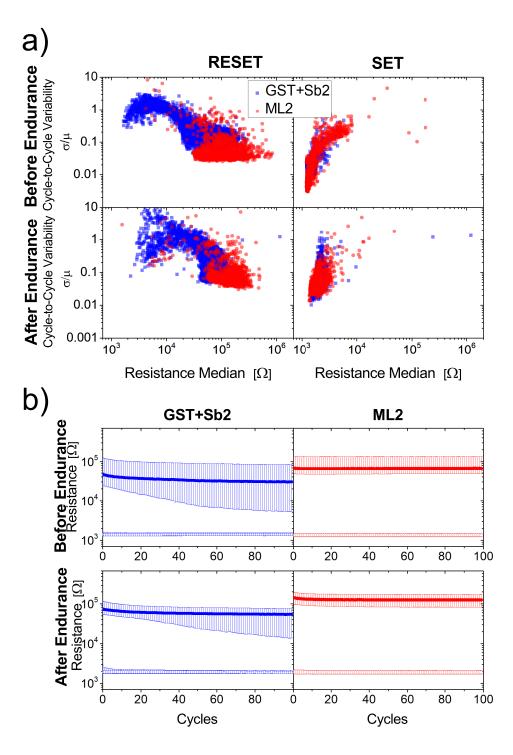

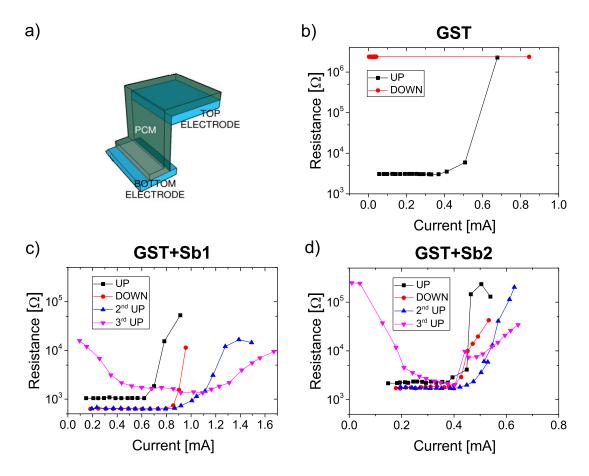

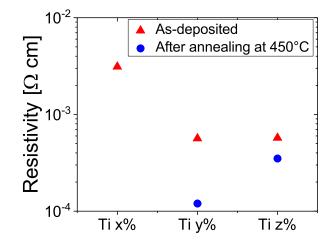

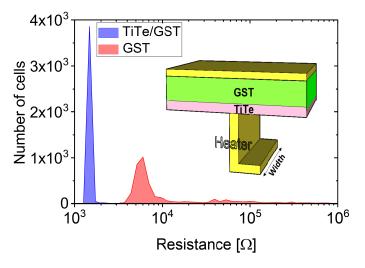

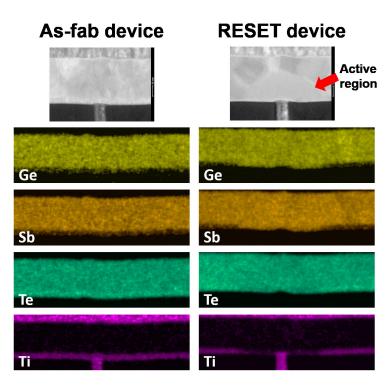

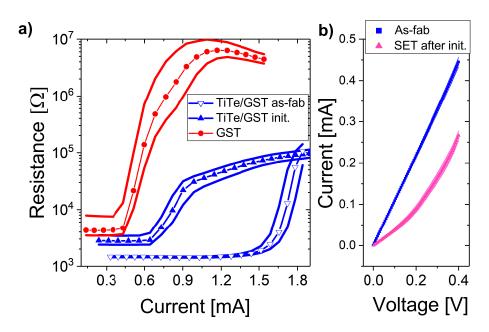

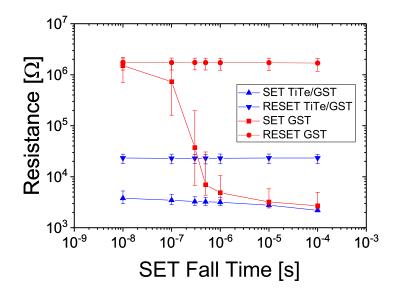

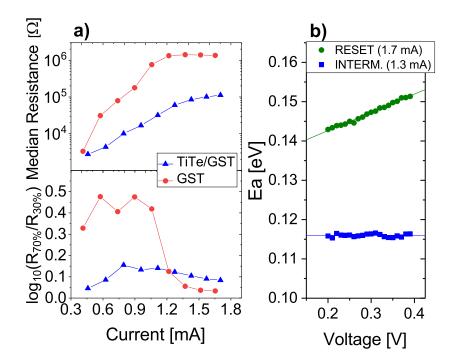

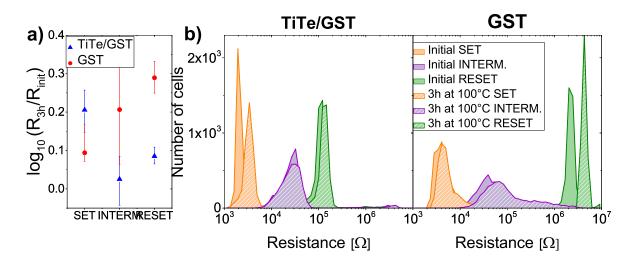

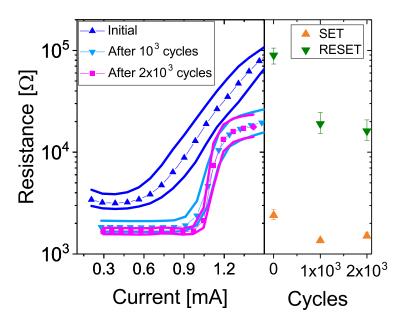

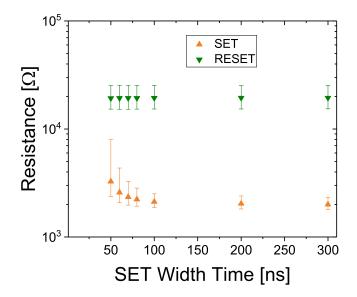

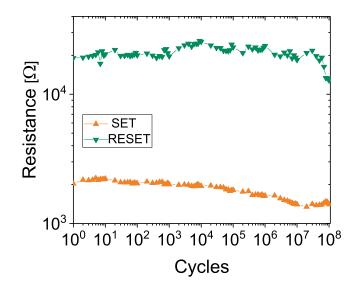

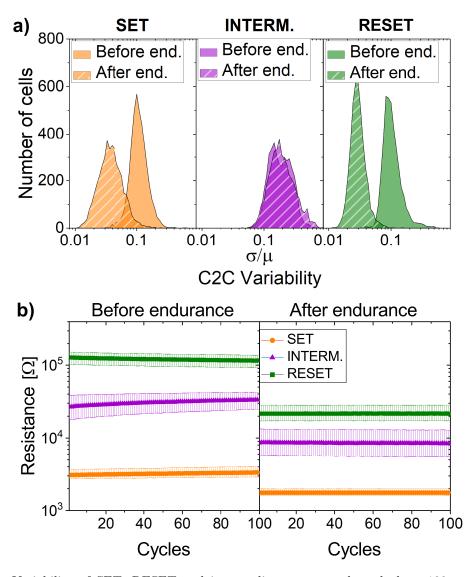

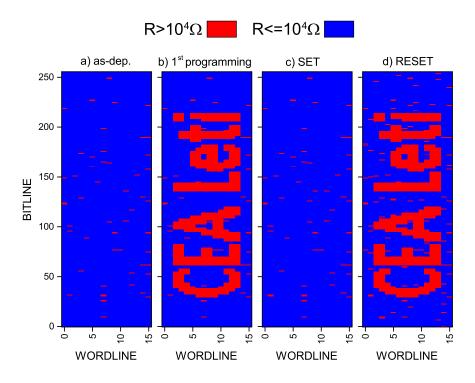

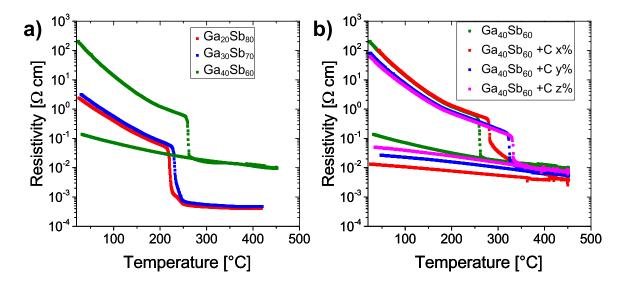

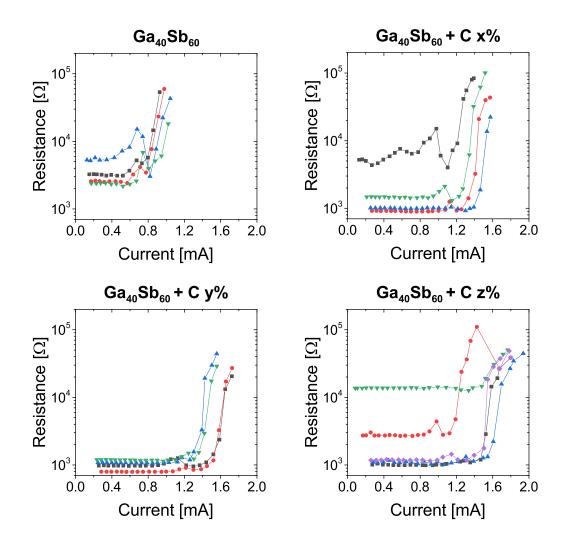

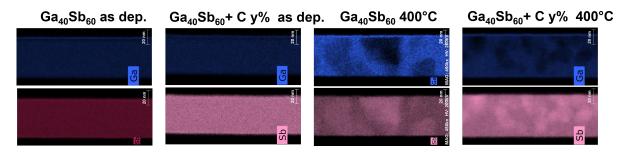

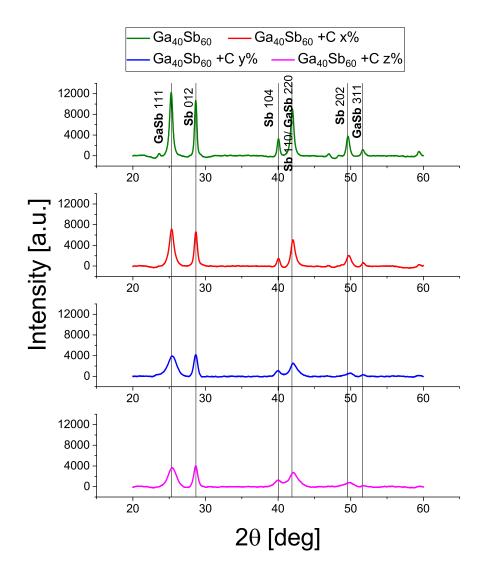

The  $\mu$ trench cell is based on a heater element. In this structure, the contact area between the heater and the phase-change material is defined by the intersection of a thin vertical heater and a trench in which the chalcogenide material is deposited. This expedient allows to keep low programming currents of 600  $\mu$ A maintaining a compact vertical integration demonstrated using a pnp-BJT selector. Furthermore, endurance of 10<sup>11</sup> cycles and data retention of 10 years at 110 °C have been shown [79].