## energy-driven devices and circuit designs for resistive random access memories

Paola Trotti

#### ► To cite this version:

Paola Trotti. energy-driven devices and circuit designs for resistive random access memories. Physics [physics]. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALY073. tel-04053055

### HAL Id: tel-04053055 https://theses.hal.science/tel-04053055v1

Submitted on 31 Mar 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : PHYS - Physique Spécialité : Physique appliquée Unité de recherche : Laboratoire d'Electronique et de Technologie de l'Information (LETI - CEA)

# Dispositifs et circuits à convenance énergétique pour les mémoires résistives

## energy-driven devices and circuit designs for resistive random access memories

Présentée par :

#### Paola TROTTI

Direction de thèse :

Gaël PILLONNET Ingénieur HDR, CEA Centre de Grenoble Gabriel MOLAS CEA SAMI OUKASSI Ingénieur Chercheur, CEA-leti Grenoble Directeur de thèse

Co-encadrant de thèse

Co-encadrant de thèse

#### Rapporteurs :

MARC BOCQUET Professeur des Universités, AIX-MARSEILLE UNIVERSITE ABDELKADER SOUIFI Professeur des Universités, INSA LYON

#### Thèse soutenue publiquement le 8 décembre 2022, devant le jury composé de :

| MARC BOCQUET                                          | Rapporteur     |

|-------------------------------------------------------|----------------|

| Professeur des Universités, AIX-MARSEILLE UNIVERSITE  |                |

| ABDELKADER SOUIFI                                     | Président      |

| Professeur des Universités, INSA LYON                 |                |

| QUENTIN RAFHAY                                        | Examinateur    |

| Maître de conférences HDR, GRENOBLE INP               |                |

| LIONEL TORRES                                         | Examinateur    |

| Professeur des Universités, UNIVERSITE DE MONTPELLIER |                |

|                                                       | Examinatrice   |

| Ingénieur HDR, CEA CENTRE DE GRENOBLE                 | <b>_</b> · · . |

| ILIA VALOV                                            | Examinateur    |

| Docteur en sciences, Forschungszentrum Jülich         |                |

# Energy Driven Devices and Circuit Design for RRAM

Paola Trotti

Picture by Larry O'Connel

#### ABSTRACT

## ENERGY-DRIVEN DEVICES AND CIRCUIT DESIGNS FOR RESISTIVE RANDOM ACCESS MEMORIES

Nowadays, electronic devices are implemented to carry out a wide set of tasks, ranging from high performance processing to low power sensing. Aggressive technological downscaling has allowed to obtain smarter devices, where increased design complexity brings a higher number of functions per chip area, along with faster operational speed and lower power consumption. However, advanced technological nodes have been suffering from architectural limitations, such as the Von Neumann's bottleneck, as well as delay and power loss over interconnections lines. As a results, new solutions are demanded in order to achieve ever increasing performances. To tackle the challenge, the so-called More-than-Moore devices have been emerging, where the hardware architecture as a whole is revisited, for example as in In Memory Computing (IMC) or Near Memory Computing (NMC), where the computation is brought onto, or in close proximity to the memory. This thesis presents alternative solutions to the need of both process miniaturization and better energy efficiency in the field of semiconductor memories. It focuses on emerging Resistive Random Access Memory (RRAM) technology, and consists of two main conceptual parts:

- △ The experimental study on RRAM as energy source, where an architecture able to retain both information and energy is envisaged. Cyclic Voltammetry tests are performed on a wide range of State-Of-the-Art (SOA) devices, evaluating their electrochemical properties. Major traits of RRAM as energy source are outlines and compared to SOA alternatives. Promising energy and power densities are derived, and prospective implementation fields are discussed.

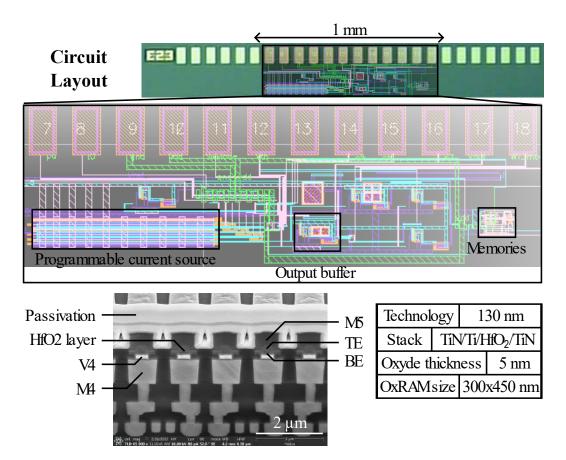

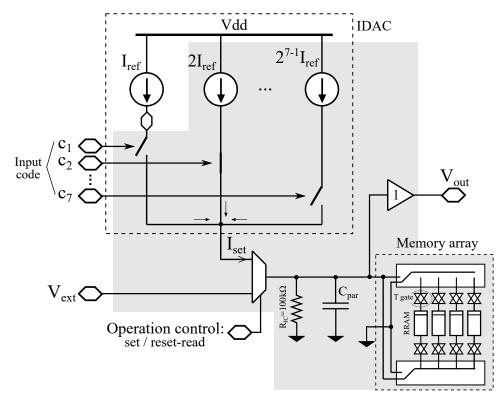

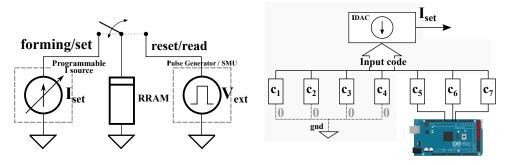

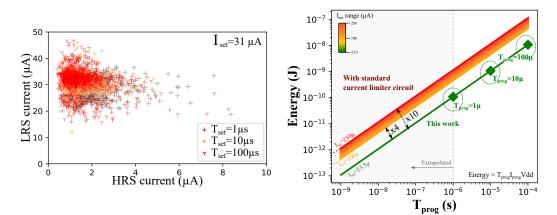

- $\triangle$  Novel, energy-efficient circuit designs for SOA RRAM write/erase operations. Two different approaches are presented: a programming scheme where the set energy is stored on a charged capacitor, and a Current Digital to Analog Converter (IDAC) based architecture. Design details in 130nm CMOS technology are presented, where the memory array is integrated as BEOF process. We deliver proof of concept, and demonstrate that in both cases a clear advantage in terms of energy cost can be achieved over the standard pulsed-voltage method.

**KEYWORDS:** RRAM, Dual-behaviour memory, Energy-efficient memory design, Capacitive Resistive Switching, CQS, DAC based RRAM programming.

#### RÉSUMÉ EN FRANÇAIS

#### DISPOSITIFS ET CIRCUITS À CONVENANCE ÉNERGÉTIQUE POUR LES MÉMOIRES RÉSISTIVES

De nos jours, les appareils électroniques sont mis en œuvre pour effectuer un large éventail de tâches, allant du traitement haute performance à la détection de faible puissance. Une réduction d'échelle technologique agressive a permis d'obtenir des appareils plus intelligents, où la complexité accrue de la conception apporte un plus grand nombre de fonctions par zone de puce, ainsi qu'une vitesse opérationnelle plus rapide et une consommation d'énergie plus faible. Cependant, les nœuds technologiques avancés ont souffert de limitations architecturales, telles que le *Von Neumann Bottleneck*, ainsi que de retards et de pertes de puissance sur les lignes d'interconnexion. En conséquence, de nouvelles solutions sont demandées afin d'atteindre des performances toujours plus élevées. Pour relever le défi, les appareils dits *More-than-Moore* ont émergé, et l'architecture matérielle dans son ensemble a été revisitée, comme avec l'*In Memory Computing (IMC)* ou *Near Memory Computing (NMC)*.

Cette thèse présente des solutions alternatives au besoin de miniaturisation des processus et d'une meilleure efficacité énergétique dans le domaine des mémoires semi-conductrices. Elle se concentre sur la technologie émergente de mémoire vive résistive (RRAM) et se compose de deux parties conceptuelles principales :

- △ L'étude expérimentale sur les RRAM comme source d'énergie, où une architecture capable de retenir à la fois l'information et l'énergie est envisagée. Les tests de Voltammetrie Cyclique sont effectués sur une large gamme de memoires, évaluant leurs propriétés électrochimiques. Les principales caractéristiques des RRAM en tant que source d'énergie sont présentées et comparées aux alternatives. Des densités d'énergie et de puissance prometteuses sont extrapolées et les domaines de mise en œuvre potentiels sont discutés.

- △ Conceptions de circuits économes en énergie pour les opérations d'écriture des memoires RRAM. Deux approches différentes sont présentées : un schéma de programmation où l'énergie est stockée dans un condensateur chargé, et une architecture basée sur un convertisseur digital-analogique en courant (IDAC). Les détails de conception en technologie CMOS 130 nm sont présentés. Dans les deux cas, un avantage clair en termes de coût énergétique peut être obtenu par rapport à la méthode standard de programmation en tension pulsée.

**MOTS-CLÉS:** RRAM, Mémoire à double comportement, conception de mémoire économe en énergie, Memoires Resistives, commutation résistive capacitive, CQS, programmation des RRAM basée sur DAC.

#### ACKNOWLEDGEMENTS

Many people deserve to be thanked for the completion of this thesis work. First of all, my gratitude goes to my thesis director, Gaël Pillonnet, and my supervisors, Gabriel Molas and Sami Oukassi, for the opportunity of conducting my research, and for being a persistent source of support, both technical and moral. I extend my thanks the people in CEA-Leti who actively helped in my work, in particular: Yasser Moursy, Niccolo Castellani, Olivier Billoint, Carlo Cagli, Mathieu Aubras, Larry O'Connell, Gabriele Navarro, Philippe Blaise, Etienne Nowak and Stéphanie Robinet.

I thank my friends, with whom I shared precious moments during this jurney; a special mention goes to Sota Sawaguchi, Leo Laborie, Benjamin Bonnard, Luis Cubero Montealegre, Giusy Lama, Sergio Dominguez and Alessandro Bricalli.

Finally, to my family, whose unwavering support has kept me motivated during the most challenging times.

Paola Trotti October 2022

#### CONTENTS

| I | IN              | FRODUCTION                                                 | 13       |  |  |  |  |

|---|-----------------|------------------------------------------------------------|----------|--|--|--|--|

| 1 | INTRODUCTION    |                                                            |          |  |  |  |  |

|   | 1.1             | Context                                                    | 15<br>15 |  |  |  |  |

|   | 1.2             | Semiconductor Memories                                     | 15       |  |  |  |  |

|   |                 | 1.2.1 The Memory Hierarchy                                 | 16       |  |  |  |  |

|   | 1.3             | Random Access Memories                                     | 18       |  |  |  |  |

|   | 1.4             | Storage Class Memories                                     | 19       |  |  |  |  |

|   | -· <del>-</del> | 1.4.1 Ferroelectric RAM                                    | 20       |  |  |  |  |

|   |                 | 1.4.2 Magnetic RAM                                         | 22       |  |  |  |  |

|   |                 | 1.4.3 PCRAM                                                | 22       |  |  |  |  |

|   | 1 5             | Resistive Random Access Memory                             | 24       |  |  |  |  |

|   | 1.5             | 1.5.1 Types of resistive switching                         |          |  |  |  |  |

|   | 1.6             | Benchmark metrics                                          | 25<br>28 |  |  |  |  |

|   | 1.0             |                                                            |          |  |  |  |  |

|   |                 | 1.6.1 Variability and performance Trade-offs               | 29       |  |  |  |  |

|   | 1.7             | Array structures                                           | 30       |  |  |  |  |

|   |                 | 1.7.1 Transistor-RRAM: 1T1R cell configuration             | 32       |  |  |  |  |

|   |                 | 1.7.2 Selector-RRAM: 1S1R cell configuration               | 34       |  |  |  |  |

|   | -               | 1.7.3 OTS Selectors                                        | 35       |  |  |  |  |

|   | 1.8             | Objective of this Thesis Work                              | 36       |  |  |  |  |

|   | 1.9             | Chapitre 1 - résumé en français                            | 38       |  |  |  |  |

| п | рр              | AM AS ENERGY SOURCE                                        | 20       |  |  |  |  |

|   |                 | RGY STORAGE IN RRAM                                        | 39       |  |  |  |  |

| 2 | ENE<br>2.1      |                                                            | 41       |  |  |  |  |

|   |                 | The interest of RRAM as energy source                      | 41       |  |  |  |  |

|   | 2.2             | A new concept: In-Memory Energy Storage                    | 42       |  |  |  |  |

|   | 2.3             | Experimental devices and methods                           | 44       |  |  |  |  |

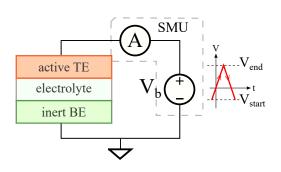

|   |                 | 2.3.1 Electrochemical characterization: Cyclic Voltammetry | 45       |  |  |  |  |

|   | 2.4             | Experimental Results                                       | 46       |  |  |  |  |

|   |                 | 2.4.1 Operation as memory                                  | 46       |  |  |  |  |

|   |                 | 2.4.2 Battery curves: reduction peak                       | 48       |  |  |  |  |

|   |                 | 2.4.3 Impact of voltage, scan rate, area and temperature   | 51       |  |  |  |  |

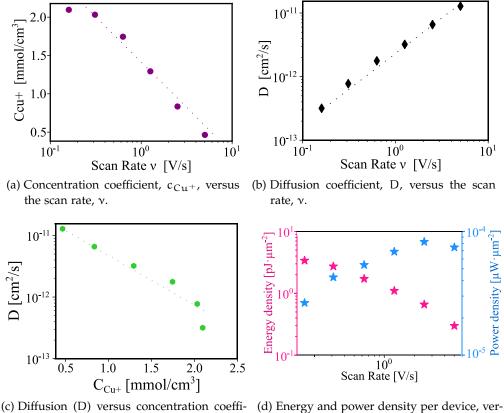

|   | 2.5             | Diffusion and concentration coefficient extrapolation      | 54       |  |  |  |  |

|   | 2.6             | Considerations and perspectives                            | 57       |  |  |  |  |

|   | 2.7             | Conclusions and remarks                                    | 58       |  |  |  |  |

|   | 2.8             | Chapitre 2 - résumé en français                            | 60       |  |  |  |  |

| ш | IN              | FEGRATED CIRCUIT DESIGN                                    | 63       |  |  |  |  |

|   |                 | ACITOR-BASED WRITING PROTOCOL                              | 65       |  |  |  |  |

| 3 |                 |                                                            | -        |  |  |  |  |

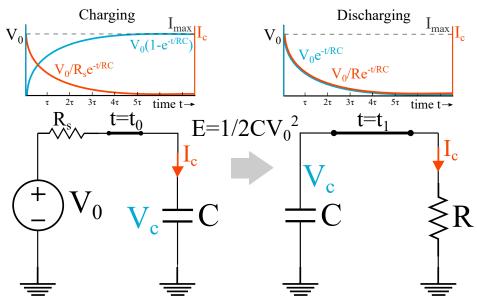

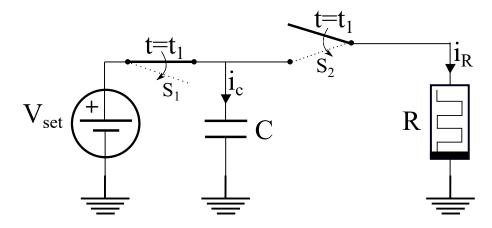

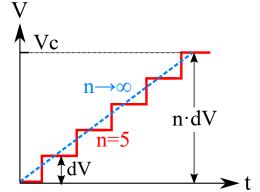

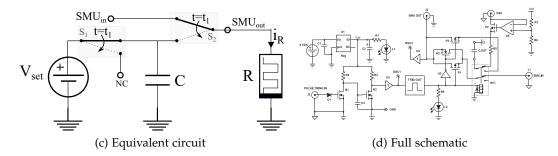

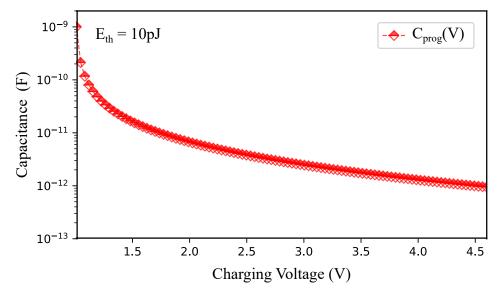

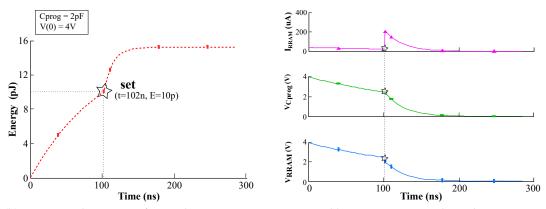

|   | 3.1             | Charge-Based switching concept                             | 65       |  |  |  |  |

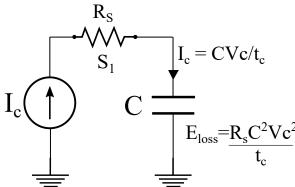

|   | 3.2             | Charging efficiency                                        | 67       |  |  |  |  |

|   | 3.3             | Comparison between CVS and CQS                             | 68       |  |  |  |  |

|   |                 | 3.3.1 Equivalent RRAM circuit for a set process            | 68       |  |  |  |  |

|   |                 | 3.3.2 Model calibration with experimental data             | 69       |  |  |  |  |

|    |             | 3.3.3                                     | SPICE simulation in CVS and CQS                                 | 0     |  |  |  |

|----|-------------|-------------------------------------------|-----------------------------------------------------------------|-------|--|--|--|

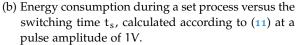

|    | 3.4         | Energy                                    | cost Comparison                                                 | 3     |  |  |  |

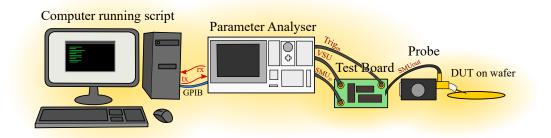

|    | 3.5         | 5 Experimental board for proof of concept |                                                                 |       |  |  |  |

|    | 3.6         |                                           | n considerations and important trade-offs                       | 7     |  |  |  |

|    | -           | 3.6.1                                     | Impact of the programming voltage onto the set switching time 7 |       |  |  |  |

|    |             | 3.6.2                                     | A dynamic RRAM model                                            |       |  |  |  |

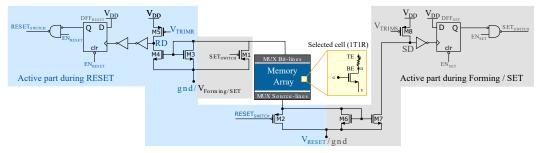

|    |             | 3.6.3                                     | CQS programming integration in a RRAM matrix                    |       |  |  |  |

|    |             | 3.6.4                                     | CQS process integration in 16kb array                           | 1     |  |  |  |

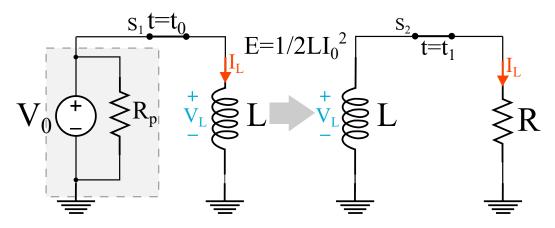

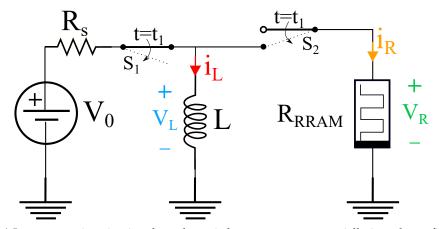

|    | 3.7         | <b>J</b>                                  | l approach: L-based programming                                 |       |  |  |  |

|    | 51          | 3.7.1                                     | Overview of L-based writing process                             | -     |  |  |  |

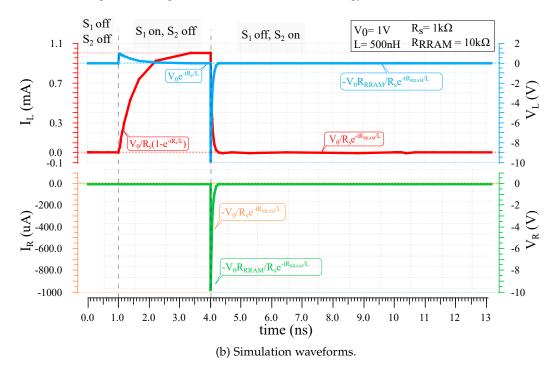

|    | 3.8         | 51                                        | specitive approach: combination of charged capacitor and in-    | т     |  |  |  |

|    | <i>J</i> .e | -                                         | programming                                                     | 6     |  |  |  |

|    | 3.9         |                                           | ary and conclusions                                             |       |  |  |  |

|    | <i></i>     |                                           | tre 3 - résumé en français                                      |       |  |  |  |

|    |             |                                           | IITING, PROGRAMMABLE CURRENT AND VOLTAGE SOURCE                 | 0     |  |  |  |

|    |             |                                           | WRITING 9:                                                      | 1     |  |  |  |

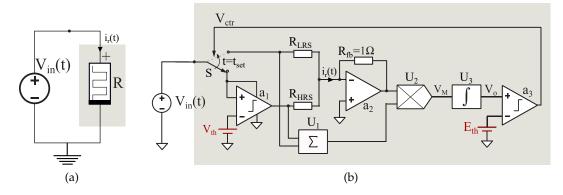

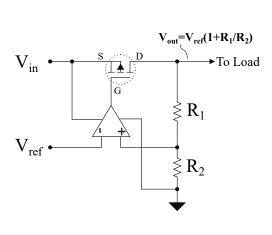

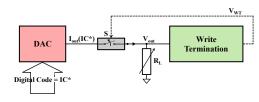

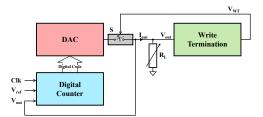

|    | 4.1         |                                           | Termination circuits for RRAM programming                       |       |  |  |  |

|    | 4.1<br>4.2  |                                           | sed Circuit Overview                                            |       |  |  |  |

|    | 4.2         | 4.2.1                                     |                                                                 |       |  |  |  |

|    | 12          |                                           |                                                                 |       |  |  |  |

|    | 4.3         | 4.3.1                                     |                                                                 |       |  |  |  |

|    |             | 4.3.2                                     |                                                                 |       |  |  |  |

|    |             |                                           |                                                                 |       |  |  |  |

|    | 4 4         | 4.3.3<br>Switch                           |                                                                 |       |  |  |  |

|    | 4.4         |                                           |                                                                 |       |  |  |  |

|    |             | 4.4.1                                     |                                                                 |       |  |  |  |

|    |             | 4.4.2                                     |                                                                 |       |  |  |  |

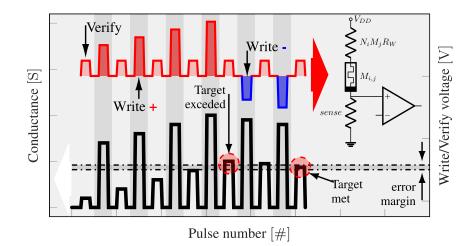

|    |             | 4.4.3                                     | Write and Verify 102                                            |       |  |  |  |

|    |             | 4.4.4<br>Electri                          | Memory Addressing                                               | · · · |  |  |  |

|    | 4.5         |                                           | cal Characterization and Experimental Results                   |       |  |  |  |

|    |             | 4.5.1                                     | Characterization of the Output Analog Buffer 100                |       |  |  |  |

|    |             | 4.5.2                                     | Evaluation of Access Impedances 100                             |       |  |  |  |

|    |             |                                           | Characterization of the I-DAC 107                               |       |  |  |  |

|    | . (         | 4.5.4                                     | Current-based set process                                       |       |  |  |  |

|    | 4.6         | -                                         |                                                                 |       |  |  |  |

|    | 4.7         |                                           |                                                                 |       |  |  |  |

|    |             |                                           | Conclusions 12:                                                 | 1     |  |  |  |

| Ap | PEND        | IX                                        | 12'                                                             | 7     |  |  |  |

|    |             | 4.7.1                                     | Reduction peaks during CV tests                                 |       |  |  |  |

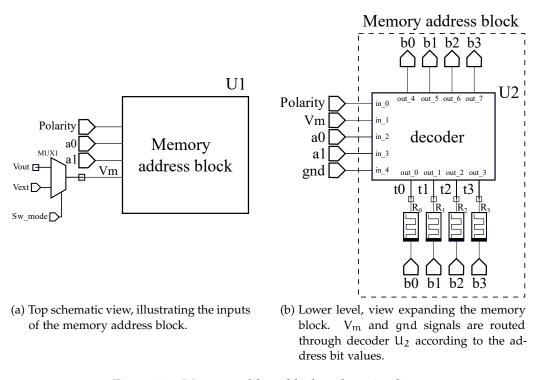

|    |             | 4.7.2                                     | Memory addressing architecture                                  | 8     |  |  |  |

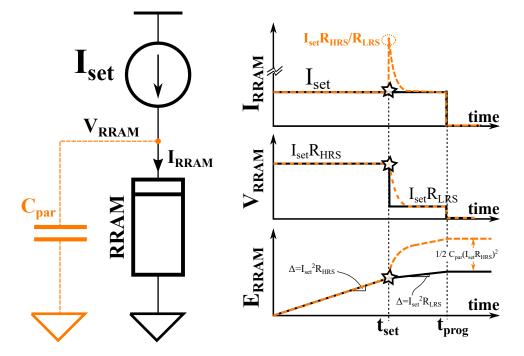

|    |             | 4.7.3                                     | Impact of the parasitic capacitance on a current-driven set     |       |  |  |  |

|    |             |                                           | operation                                                       | 9     |  |  |  |

|    |             | 4.7.4                                     | Evaluation of the parasitic capacitance energy contribution     |       |  |  |  |

|    |             |                                           | during a set process 120                                        | 9     |  |  |  |

|    |             | 4.7.5                                     | Experimental validation of DAC architecture                     | 0     |  |  |  |

|    |             | 4.7.6                                     | Set tests with DAC in Constant Current Source mode 130          | 0     |  |  |  |

| Pu | BLICA       | TIONS                                     | 133                                                             | 3     |  |  |  |

#### BIBLIOGRAPHY

135

#### ACRONYMS

- SOA State Of the Art

- RAM Random Access Memory

- SCM Storage Class Memory

- NVM Non-Volatile Memory

- **RRAM Resistive Random Access Memory**

- CBRAM Conductive Bridge Random Access Memory

- LRS Low Resistive State

- HRS High Resistive State

- DUT Device Under Test

- TEM Transmission Electron Microscopy

- CV Cyclic Voltammetry

- SMU Source Monitor Unit

- CQS Constant Charge Source

- CVS Constant Voltage Source

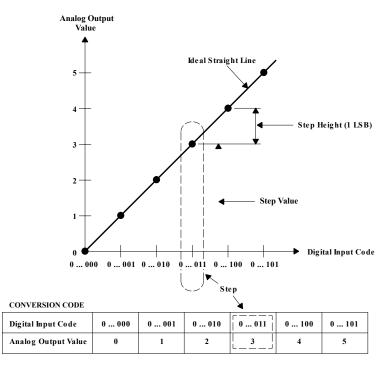

- DAC Digital to Analog Converter

- WT Write Termination

- WV Write Verify

Part I

INTRODUCTION

#### 1.1 CONTEXT

In the past, technological development has been majorly pushed by transistor downscaling [1, 2]; however, as CMOS nodes have advanced, the performance bottleneck has shifted towards interconnects [3–5] and architectures. *The Memory Wall* [6–8] is a well-known problem, where the widening throughput disparity between processor and memory demands a re-visitation of the standard computer architecture. As a result, the so-called *More-than-Moore* devices have been emerging, such as In Memory Computing (IMC) [9–13] or Near Memory Computing (NMC) [8, 14–17], where the computation takes place either onto the memory itself or in its close vicinity.

This chapter gives context to our research, aimed to provide an alternative solution to the need of process miniaturization, reduced latency and better energy efficiency, in the field of semiconductor memories. Various emerging memories are presented, with major focus on Resistive Random Access Memory (RRAM), the technology adopted in our study. Its working mechanism is explained and basic design concepts are illustrated.

#### **1.2 SEMICONDUCTOR MEMORIES**

A computer memory can be defined as a piece of hardware whose task is to retain information, either temporarily of permanently, encoded through binary digits (bits) [18, 19]. It can be further categorized into *main* or *primary*, and *auxiliary* or *secondary* memory; the former generally being responsible of holding data and instructions during a program's execution, while the latter delivers long-term storage [19, 20].

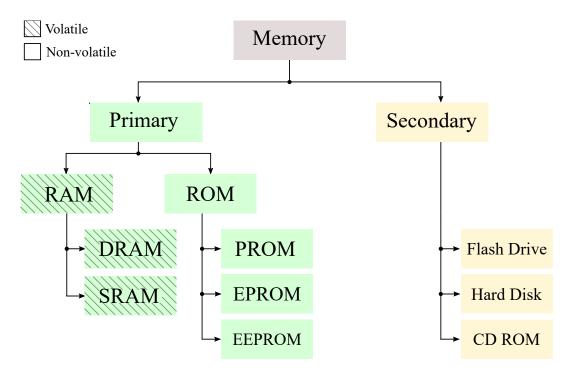

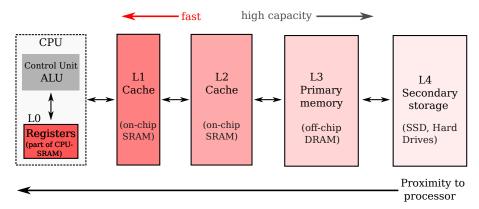

Figure 1 shows a chart reporting the main memory types implemented in today's computer architectures. A further distinction can be made depending on whether the stored data is lost after the system's power off: is this case, the memory is called *volatile*, and *non-volatile* otherwise [18, 19, 21]. Examples of volatile technologies are SRAM (Static Random Access Memory) [22–25] and DRAM (Dynamic Random Access Memory) [22, 26, 27], while Read Only Memories (ROM) [28], Flash [29–31] and Hard Disks [32] are non-volatile.

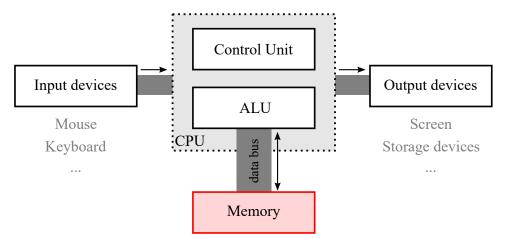

In Figure 2a is reported a schematic view of Von Neumann's architecture [12, 33, 34]: the most largely adapted structure of today's digital computers [9, 34, 35]. At its core there is a Central Processing Unit (CPU), or processor, which executes the instructions that constitute a computer program; it comprises of a Control Unit (CU), which directs the processor operations, as well as an Arithmetic-Logic Unit (ALU), which carries out the actual calculation. The primary memory is highlighted: its role is to supply a program's instructions and data to the CPU, as well as to store the processed data. Hence, the communication between the

Figure 1 – Memory classification: primary and secondary storage, with main SOA technologies. Adapted from [20].

primary memory and the processor is bidirectional, and takes place over the data bus.

#### 1.2.1 The Memory Hierarchy

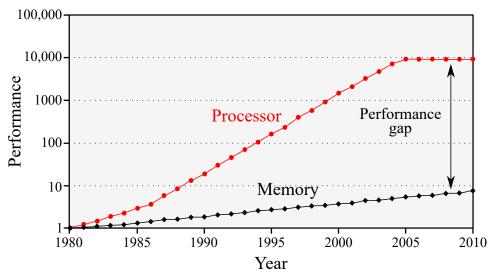

Ideally, the speed at which the processor elaborates the incoming data matches the pace at which the the memory delivers it, so that no time is lost in waiting. However, a widening performance gap has been observed over the years, where the processor throughput<sup>1</sup> has been increasing at a faster pace compared to the memory access time [36]. As a result, the memory latency, i.e. the amount of time that passes between a request for data and the moment the data is available for external use, has become a performance bottleneck [19, 35, 37]. This problem has been known as the *Memory Wall* [6, 7, 38] or the *Von Neumann's bottleneck* [8, 39], and it is illustrated in Figure 2b, which reports the evolution of the processor and primary memory speed over the year.

Recent memory designs have been focusing on reducing power consumption as well as access times; this is due to the fact that enlarged, fast memories will dissipate considerable amount of energy either through dynamic<sup>2</sup> and static losses<sup>3</sup> [7].

The ultimate memory would be fast, cheap, highly scalable, low energy-consuming, and non-volatile. However, in reality these benefits trade with each other; conse-

<sup>1.</sup> In the CPU context, the throughput expresses the number of instructions that can be executed in a time unit.

<sup>2.</sup> Dynamic power is consumed when the memory is written/read.

<sup>3.</sup> Static consumption derives from leakage when the memory is not operated.

(a) Von Neumann's architecture, where the (primary) memory is highlighted. The data bus connects the CPU to the memory, which stores program instructions and data.

(b) The growing gap between the processor and the memory performances. In red, the rate of CPU requests to the memory, while in black, the memory access time. In more recent years, the processor growth tends to flatten, as the path to higher performance started relying on multi-processing, rather than a single processor speed [7]. Redrawn and adapted from [7].

Figure 2

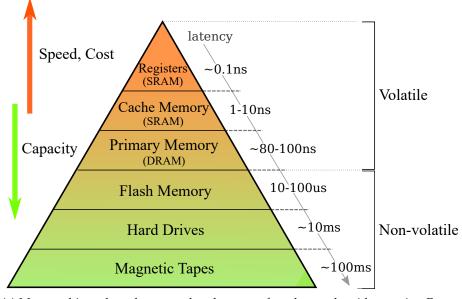

quently, modern computers employ multiple memory units, which differ by technology and architecture, in an effort to shrink the performance disparity between the processor and the memory [18–20]. Figure 3a reports the so-called *Memory Hierarchy* [19, 40], where each layer stands for a different technology: speed and cost decrease towards the bottom, oppositely to capacity. As a general trend, faster memories are smaller and more expensive, whereas slower ones allow larger capacity and are cheaper. Therefore, the technologies that are at the top of the pyramid are used as primary storage and contribute to increase computational performances, while the memories at the bottom are employed for long-term storage. Figure 3b shows a general architectural design, where different memory units are pipelined. The lower the layer index, the lower the latency and size, and the closer the memory is placed to the CPU. This way, the memory wall can be minimized, forming the illusion of an overall fast and large memory, where the speed equals that of the fastest memory, and the capacity that of the largest one.

#### **1.3 RANDOM ACCESS MEMORIES**

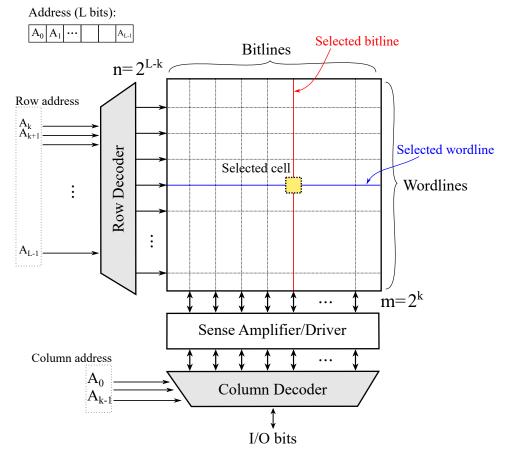

Are called Random Access, those memories whose reading (writing) time does not depend on the physical position of the data stored (to store) [22, 26, 41]. This benefit derives from the layout of Random Access Memory (RAM) systems, which is schematically illustrated in Figure 4. The memory content is stored in a nxm matrix, where n is the number of rows and m the number of columns. At the intersection of each row and column, a memory *cell* stores either a bit or a word<sup>4</sup> of data.

The technical names for the routing rows and columns are, respectively, *word*, and *bit lines*. By selecting, i.e. opportunely biasing, the corresponding word and bit lines, one cell can be accessed at a time. In order to address the whole memory content with the minimum amount of bits, row and column decoders are usually implemented (illustrated in figure); specifically, n lines can be addressed with k bits, so that:

$$k = \log_2(n) \tag{1}$$

Once the voltage across the cell's bit and word lines is appropriate, its content can be read or written. Generally, a low-amplitude voltage is used to probe the cell state, while a relatively high amplitude is required for the write (or programming) operation. The non-selected lines are generally precharged at some fixed voltage, for example Vdd/2, so that no drop is guaranteed to appear across the inactive cells. The sense amplifier/driver amplifies the output swing to rail-to-rail values during a read process, while it buffers the write signal otherwise. The memory cell itself is usually in series with some access element, like a transistor or a diode, so that the leakage current from non-selected data is limited. Further details are given in Section 1.7, which illustrates the architecture of a random access memory array in the context of RRAM.

<sup>4.</sup> The term word indicates a series of bits, commonly one or two bytes (1 bite = 8 bits).

(a) Memory hierarchy, where speed and cost are found to trade with capacity. Faster memories, such as SRAM and DRAM, are generally volatile, while slower and bigger memories, like Flash, are non-volatile. Adapted and redrawn from [40]

(b) Schematic design of the memory organization in a modern digital computer. The memory hierarchy is exploited in order to reduce the memory wall problem, so that faster technologies, which are more frequently accessed, are placed closer to the CPU.

Figure 3 – The Memory Hierarchy

#### 1.4 STORAGE CLASS MEMORIES

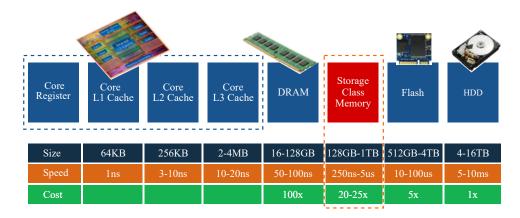

Looking at the memory hierarchy shown in Figure 3a, it can be noticed that there is a relatively large latency, as well as capacity, gap between the primary and the flash memory layer. In order to provide an additional tier for data storage, extensive research has been focusing on emerging memory technologies, whose performances would sit between DRAM and Flash [42–44].

In the literature, they are addressed with the term Non-Volatile Memory (NVM), in virtue of their non-volatility, or Storage Class Memory (SCM) [42–45]. Figure 5a shows how SCM locate in terms of speed, size and cost, with respect to SOA technologies. With storage capability similar to Flash, and access times approaching those of DRAM, at a fraction of its cost, SCM appears as a very promising class

Figure 4 – A general design of a RAM memory array, where row and column decoders process the address bits, in order to grant access to the selected cell. A L-bitlong address is shown: k bits, from  $A_0$  to  $A_{k-1}$ , are dedicated to addressing the bit line, while L – k bits, from  $A_k$  to  $A_{L-1}$ , to the word line.

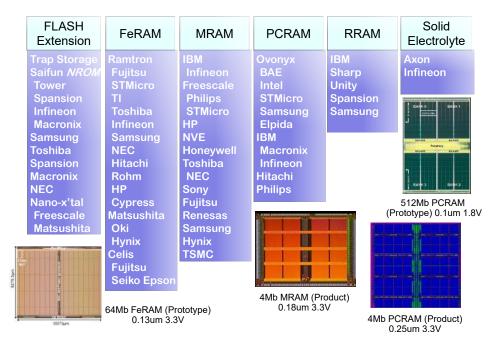

of memories. Indeed, SCM is expected to revolutionize the field, blurring the distinction between memory and storage tasks [40, 42–45]. A multitude of emerging technologies have been intensively researched, both in academia and by the industry. The most widely known are presented in Figure 5b: it can be seen that many semiconductor companies are active in SCM memory development [43].

The physical mechanisms that allow data storage widely vary depending on technology; in the following subsections, an overview is presented for FeRAM, MRAM and PCRAM. RRAM, being the focus of this thesis work, is discussed in larger detail in Section 1.5.

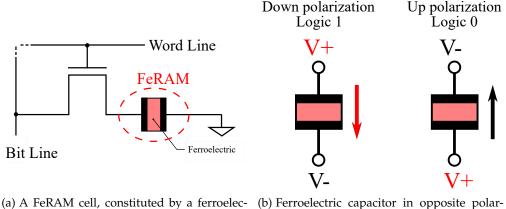

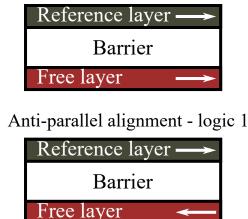

#### 1.4.1 Ferroelectric RAM

Ferroelectric Random Access Memory, or FeRAM in short, stores binary information through the polarization of a thin layer by means of an electric field [46–51]. The cell structure is illustrated in Figure 6a, and resembles DRAM's, where a series transistor is used to gain access to a (ferroelectric) capacitor storing the logic state. Among the metallic plates, a thin ferroelectric layer is located; lead zirconate titanate (PZT) is a popular material choice [43, 44], although most recently

(a) Full memory hierarchy. Storage Class Memories (SCM) fill the gap between DRAM and Flash technologies in term of size, speed and cost. Adapted from [40, 45].

(b) List of main emerging technologies on nowadays market. Under each memory type, the relative major researching companies [43].

Figure 5 – Storage Class Memories: technologies and presence on the market.

hafnium oxide (HfO<sub>2</sub>) has also been considered, thanks to its superior CMOS process compatibility and downscaling potential [51, 52]. By opportunely biasing the capacitor's electrodes, the resulting electric field changes the orientation of the atoms constituting the ferroelectric material, either to "up" or "down" direction, as illustrated in Figure 6b. When a change of orientation occurs, additional charge is induced, thus increasing the device capacitance. Distinct logic states can be associated to each orientation, and a change in polarization, or a lack of one, can be used to read the device state. For example, by applying a write voltage equal to the value required to write a logic 1. If the stored state does not match the polarity of the probing voltage, the polarization is flipped, and a current pulse can be detected as a result over the output line. Its presence, or absence, reveals what the cell state was, although might require rewriting its content as consequence. FeRAM benefits from fast read/write times (~ 50ns) [49], low power consumption, and high number of write/erase cycles (~  $10^{14}$ ), while major downsides are limited scalability and a destructive read process [43, 44, 46, 48, 50].

(a) A FERAM cell, constituted by a ferroelectric capacitor, in series with an access transistor.

Ferroelectric capacitor in opposite polarization state, which translate in binary logic values.

Figure 6 – FeRAM memory.

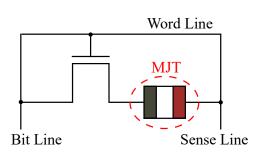

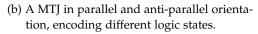

#### 1.4.2 Magnetic RAM

Magnetic Random Access Memory (MRAM), also known as Spin-Transfer Torque RAM (STT-RAM), stores logic states though the orientation of magnetic domains in a thin layer, modulated by means of a spin-polarized current [43, 53]. A MRAM cell is shown in Figure 7: it implements a Magnetic Tunnel Junction (MTJ), which comprises of two ferromagnetic layers separated by a barrier layer. One of the magnetic layers, called reference layer, acts as a permanent magnet showing fixed magnetic direction, while the other's, called free layer, can toggle between parallel or anti-parallel. Depending on the orientation of the free layer, the cell's resistance changes: it is low when they are aligned (parallel direction) and high otherwise (anti-parallel). The cell content can be read by sourcing a non-desruptive DC voltage to measure the cell's resistance [54]. MRAM benefits from low power consumptions, high programming speed, and very high endurance as there is no known wear out mechanism [43, 54]. However, the required write currents can be quite high and thus possibly cause electromigration, especially for more advanced nodes [43, 55].

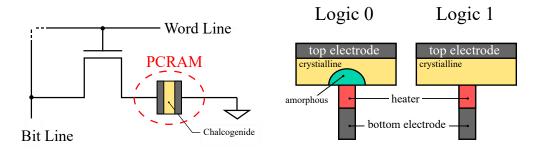

#### 1.4.3 PCRAM

Phase Change Random Access Memory (PCRAM) relies on the state transition of a chalcogenide glass to encode logic values [43, 56]. The cell structure consists on a stack of at least three layers, where the chalcogenide material (a popular choice is  $Ge_2Sb_2Te_5$  [57]) is sandwitched between two access electrodes. Figure 8a shows a typical cell configuration, featuring an access transistor. By heating the glass, through the flow of current over a dedicated heater, a small portion

Parallel alignment- logic 0

(a) A MRAM cell, constituted by a Magnetic Tunnel Junction (MTJ), in series with an access transistor.

Figure 7 – MRAM memory.

can be turned into either an amorphous or crystalline phase (Figure 8b). When the material is in the latter, its electrical resistance is low, as opposed to the amorphous phase; consequently, the two states can be associated to different logic values. The amorphous and crystalline resistances can be several orders of magnitude apart, which is a considerable advantage for the implementation in large arrays, and/or multibit storage. However, PCRAM usually suffers from *resistance drift*, where the amorphous phase resistance tends to decline over time, narrowing the read margin [58]. By sourcing a non-destructive DC voltage while measuring the resulting current, the cell state can be derived. PCRAM offers can endure a high number of write/erase cycles (~  $10^{11}$ ), while the main drawbacks are due to the high amount of current, in the mA range, required for the reset process, to physically melt the chalchogenide. In fact, this implicates relatively high power consumptions and possibly challenging downscaling due to high current densities [43, 56, 57].

(a) A PCRAM cell, in series with an access transistor.

Figure 8 – PCRAM memory.

24

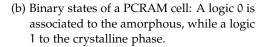

#### 1.5 RESISTIVE RANDOM ACCESS MEMORY

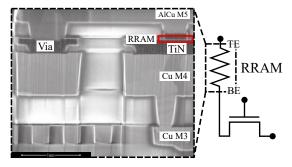

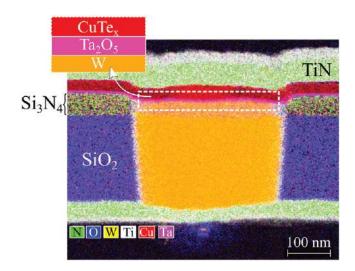

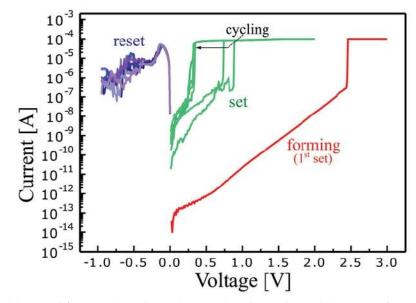

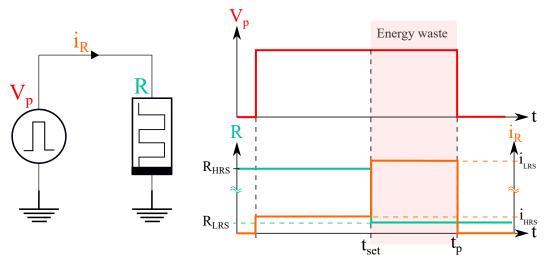

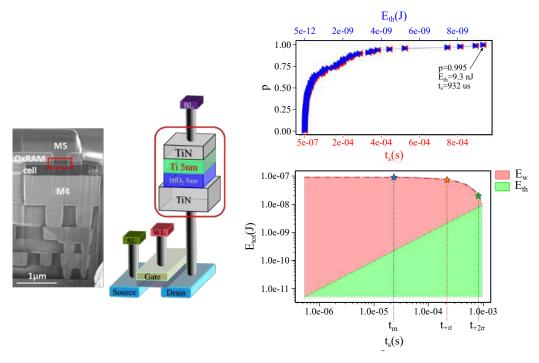

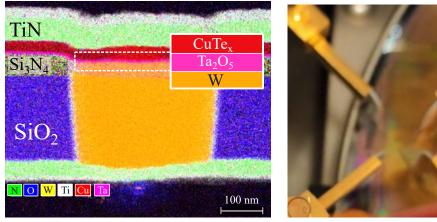

RRAM is an emerging, non-volatile memory technology where a logic state is encoded through a resistance value [59–61]: namely, a High Resistive State (HRS) and a Low Resistive State (LRS), where  $R_{HRS} \gg R_{LRS}$ ,  $R_{HRS}$  being the cell resistance in HRS and  $R_{LRS}$  the resistance in LRS. A Logic 0 is usually associated to the HRS, also called *reset state*, whereas a logic 1 to the LRS, or *set state*. A resistance change can be triggered by opportunely biasing the cell's electrodes: a HRS to LRS transition (i.e. a set process) occurs by posing a set voltage ( $V_{set}$ ) across the cell terminals, while a LRS to HRS (i.e. a reset process) is accomplished by sourcing a reset voltage ( $V_{reset}$ ). A basic representation is illustrated in Figure 9: by supplying the appropriate bias, a thin conductive filament can be formed or dissolved inside the *switching layer*, thus modulating its resistance [59, 62, 63]. Figure 10a shows a Transmission Electron Microscopy (TEM) picture of a RRAM cell in LRS, where a thin filament can be seen bridging the access electrodes.

Figure 9 – Basic structure of a RRAM cell. A thin conductive filament can be formed or dissolved inside the switching layer, representing different logic states.

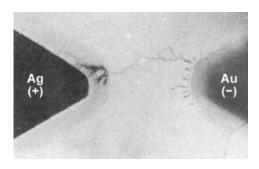

The phenomenon behind the operation of RRAM is known in the literature as *Resistive Switching* effect. Since the late 60s, when it was first reported that oxides can become electrically conductive under the effect of an electric field [62–64], the Resistive Switching effect has been recognized in a large variety of materials. RRAM technology has thus actually been around for several years, despite its role as next-generation memory being relatively recent; technological advantage and material compatibility have allowed the co-integration with the standard CMOS fabrication process, thus making RRAM an attractive technology for today's market [65]. Figure 10b shows a Scanning Electron Microscopy (SEM) picture of a RRAM cell, integrated on top of an underlying access transistor in BEOL.

Nowadays, RRAM represents a competitive alternative in the emerging memory market, exhibiting high programming speed (~ 10ns), fair endurance (~  $10^6$  write/ erase cycles), low power consumption (< 10pJ) and low cost.

ing a conducting filament connecting the electrodes. [66]

(a) TEM picture of a RRAM cell in LRS, show- (b) SEM picture of a RRAM cell, integrated in BEOL on top of an underlying transistor (130nm), between M4 and M5. Adapted from [67].

Figure 10

#### Types of resistive switching 1.5.1

Physically, a HRS to LRS transition is attributed to some sort of soft breakdown process [60, 61, 68] which can thus be made reversible, albeit inescapably damaging the cell over write/erase cycling, and finally limiting its endurance. The first set event a virgin<sup>5</sup> RRAM cell experiences is called *forming* or *electroforming process*, and it requires a voltage amplitude, the *forming voltage*, higher than following set voltages [60, 61, 68].

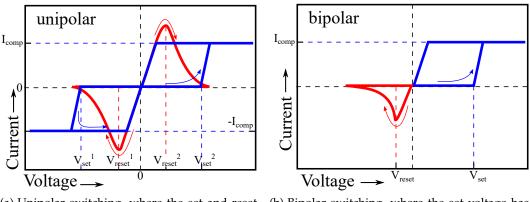

Two main types of switching can be distinguished, depending on the polarity of the set and reset voltages: unipolar and bipolar. The unipolar case is illustrated in Figure 11a: in this situation, the write/erase voltages have the same sign, although the amplitude of the reset voltage is usually lower than the set. The reasoning behind is that Joule heating is identified as the predominant mechanism behind the reset process [68, 69]. The bipolar case is shown in Figure 14b: here, set and reset voltages have opposite sign, due to the fact that the reset operation is attributed to the migration of charged species, although Joule heating can assist the process [68]. Our study focuses on bipolar switching RRAM, namely OxRAM and CBRAM, whose working principle is exposed in further details in the subsequent paragraphs.

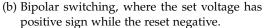

also kown as Valence Change Memory (VCM), OxRAM is a class of OXRAM RRAM that exhibits bipolar resistive switching, whose filament is constituted by oxygen vacancies<sup>6</sup> [60, 61, 66, 68–70]. An OxRAM cell is shown in Figure 12, at point 1: the bottom electrode is made of an electrochemically inert, like Pt or TiN, while the top electrode of an electrochemically active material, such as Ta, Ti, Cu or Hf. The latter allows the formation or redox reactions and ion exchange with the switching layer, which is constituted by some transition metal-oxide, like  $HfO_x$ ,  $TaO_x$  or  $AlO_x$  [66, 69, 70]. A fresh sample is highly resistive, showing a resistance value (IRS resistance) which is usually larger than any subsequent HRS.

<sup>5.</sup> A fresh RRAM cell displays a high resistance, generally much higher than the HRS that achieved after a reset operation. This state is sometimes referred to as Initial Resistive State (IRS).

<sup>6.</sup> A vacancy is a point defect in a crystalline solid, which occurs when an atom is missing from its original lattice site.

(a) Unipolar switching, where the set and reset voltages are either both positive or both negative.

Figure 11 – Unipolar and bipolar resistive switching.

Oxygen vacancies can either be already present inside the switching layer, or later introduced by the forming process [68, 70].

Phase 2 illustrates the forming operation: the appliance of a positive voltage between the electrodes,  $V_{form}$ , results in an electric field inside the switching layer, which ionises some oxygen atoms and pushes them outside the lattice, leaving behind some positively charged oxygen vacancies [69, 70]. The negative charges (oxygen ions) are attracted to the top electrode, where they recombine as oxygen atoms. The vacancies create a conductive path which bridges the electrodes, so that the cell's resistance transits to its LRS (step 3). Phase 4 shows the the reset process, which is triggered under reversed bias.  $V_{reset}$  is a negative voltage that causes the oxygen atoms to ionize back, and recombine with the vacancies constituting the filament. This process interrupts the conductive path, bringing the cell's resistance back to an high value, the HRS. Any subsequent programming operation follows steps 2-5, albeit requiring a lower voltage,  $V_{set} < V_{form}$ , to bring the cell to its LRS.

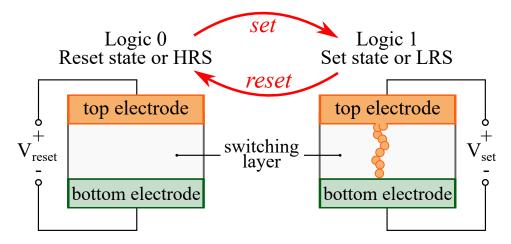

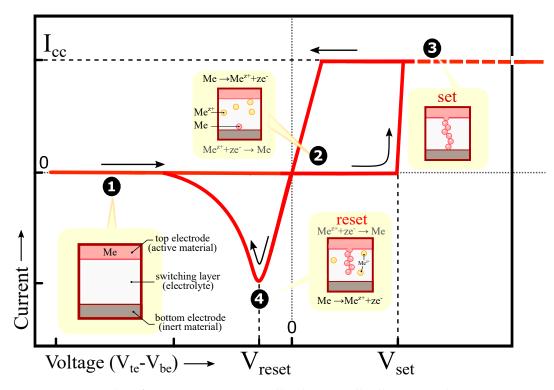

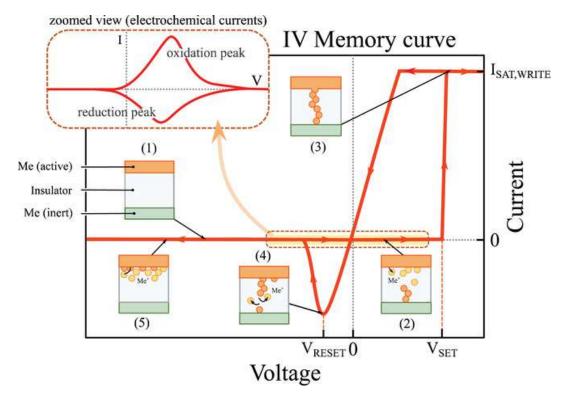

CBRAM Conductive Bridge Random Access Memory (CBRAM) is a bipolar switching class of RRAM, where the filament is build as a result of nanoscale electrochemical reactions [60, 61, 68]. The cell structure resembles a tiny ionic battery [71], where the electrodes are separated by a switching layer which conducts ions from one metal plate to the other, and is thus also called (solid) electrolyte. Figure 13 shows the programming flow of a CBRAM memory cell, reporting on the x-axis the voltage drop from the top to the bottom electrode,  $V_{te} - V_{be}$ , and on the y-axis the current,  $V/R_{cell}$ , where  $R_{cell}$  is the cell resistance. The top electrode is made of some electrochemically active<sup>7</sup> metal Me, for example Cu or Ag, while the bottom is electrochemically inert, like Pt or W. At point 1 of Figure 13, the cell is its Initial Resistive State (IRS), which is highly electrically insulating<sup>8</sup>. Once the voltage across the cell is risen towards positive values, the oxidation of the top electrode

<sup>7.</sup> With electrochemically active, is intended a material which can undergo reduction-oxidation (redox) reactions, usually triggered by the appliance of an external potential. Contrarily, the material is called electrochemically intert.

<sup>8.</sup> Prior to any set event, the range can extend to tens of  $G\Omega$  [60].

Figure 12 – Illustration of the operation of a bipolar OxRAM memory cell.

is triggered (point 2), and some metal atoms constituting the top electrode are ionized into  $Me^{z+}$  cations. In parallel, reduction occurs at the bottom electrode, so that the  $Me^{z+}$  ions lose their charge and revert to metal atoms.

By effect of the electric field inside the electrolyte, the metal ions pile up in filamentary fashion, and eventually short-circuit the cell terminals. Point 3 illustrates the set event, which occurs at voltage  $V_{set}$  and  $R_{cell} = R_{LRS}$ . The current saturates at compliance,  $I_{cc}$ , by effect of some external limiter, like a transistor or a resistor, connected in series with the cell in order to prevent its damage. As the voltage value is hereby varied in order to keep constant the value of the current, the line is dashed. The cell remains in LRS until point 4, where a negative voltage triggers the specular reactions of point 2, so that the filament atoms are ionized away and interrupt the conductive path, rising the cell resistance  $R_{cell}$  to  $R_{HRS}$ . After the electroforming event, some remaining of former filaments generally persist inside the switching layer, causing the HRS resistance to be lower than the IRS of a virgin cell, howbeit resulting much greater than the LRS, until the cell failure eventually occurs.

Figure 13 – I-V plot of a CBRAM memory cell, schematically illustrating the programming flow.

#### **BENCHMARK METRICS** 1.6

This section defines fundamental parameters used to characterize and benchmark memory technologies, in the context of RRAM.

- Cell size: refers to the amount of silicon surface occupied by a memory cell. The lower the cell size, the denser and more area efficient the memory array. The area is usually expressed by means of the technological feature size F, which corresponds to half the pitch of the lowest order metal line<sup>9</sup>. A RRAM cell can potentially be fitted into minimally size metal cross-points, so that its area can be as low as 4F<sup>2</sup>. Section 1.7 gives representation and further explanation on the design of RRAM arrays.

- $\circ$  Window Margin (WM): defined as  $R_{HRS}/R_{LRS}$ , expresses the (resistance) gap between the binary states. In order to evaluate the robustness against technological dispersion, the WM is usually evaluated at the critical tail of the distribution; for example:  $WM(+2\sigma) = R_{HRS}(-2\sigma)/R_{LRS}(+2\sigma)$ . The higher the WM, the more robust the technology against reading errors, facilitating the integration in large arrays.

- Endurance: expresses how many times a cell/array<sup>10</sup> can be successfully programmed, before failure occurs due to accumulated damage brought by

<sup>9.</sup> Metal 1 is the lowest order metal line for a given technology. The minimum pitch, 2F, is defined by the layout design rules.

<sup>10.</sup> When multiple cells are considered, the endurance is expressed along with its statistical dispersion.

previous write/erase processes. In the context of RRAM, it corresponds to the maximum number of set-reset cycles that a memory can withstand, before the HRS collapses onto the LRS (a threshold can be set, for example, at  $WM(+2\sigma) = 10$ ). A well-known failure mechanism is a high current density inside the filament, typically taking place during a set event, which irreversibly damages the cell [68]. To extend RRAM lifetime, a fast-responding current clamp, like a resistor or a transistor, is introduced in series with the cell.

Retention: is the amount of time a memory cell/array maintains the written logic state, before a spontaneous information loss occurs. For non-volatile technologies, a typical target time is 10 years. In the case of RRAM, the problematic state is constituted by the LRS: since, by design, a low amount of atoms are responsible for a dramatic resistance change, limited atomic rearrangement can cause the conductive filament to spontaneously dissolve over time [68]. Retention can be measured by performing a read operation at high temperature (for example 85°C) at regular time intervals, and then projecting the time at which failure occurs to a several-years timescale [68].

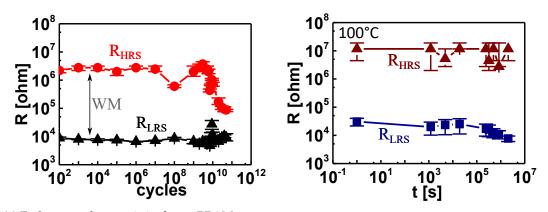

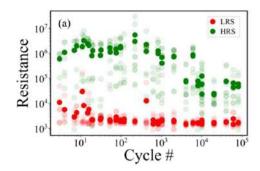

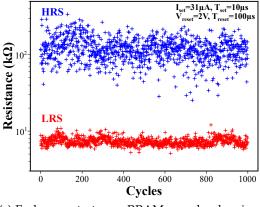

Figure 14 shows experimental endurance (14a) and retention (14b) characteristics for RRAM, where the window margin closure limits the technology performances.

(a) Endurance characteristic for a RRAM array, where the Window Margin (WM) reduces over cycling. (b) Re

(b) Retention characteristic for 10 cells, where the WM slightly reduces over time.

Figure 14 – Endurance and retention characteristics for RRAM, adapted from [72].

In order to give a readable comparison chart, Table 1 reports performance metrics of various State Of the Art (SOA) emerging technologies. [68, 73].

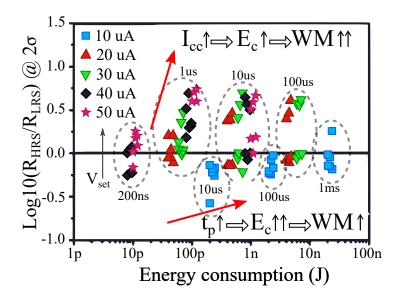

#### 1.6.1 Variability and performance Trade-offs

Ideally, the window margin, endurance and retention should be maximised. However, reported evidence has shown that these parameters are found to trade with each other; for example, a higher WM can be obtained by performing a set event at a higher current compliance, while endurance is degraded [72]. Nonetheless, above some threshold, both endurance and WM result degraded (for example,

| Technology                     | SRAM               | DRAM               | Flash<br>NAND                    | Flash<br>NOR                     | MRAM               | FeRAM            | PCRAM            | RRAM              |

|--------------------------------|--------------------|--------------------|----------------------------------|----------------------------------|--------------------|------------------|------------------|-------------------|

| Non-<br>volatility             | no                 | no                 | yes                              | yes                              | yes                | yes              | yes              | yes               |

| Operating<br>Voltage<br>[V]    | ~ 1                | ~ 1                | ~ 10                             | ~ 10                             | 1-3                | 1-4              | 3-5              | 1-5               |

| Cell size<br>[F <sup>2</sup> ] | > 100              | > 6                | 5                                | 10                               | 6-20               | > 15             | 4-20             | < 4               |

| Write<br>time [ns]             | ~ 1                | ~ 10               | 10 <sup>5</sup> -10 <sup>6</sup> | 10 <sup>4</sup> -10 <sup>6</sup> | ~ 1                | < 50             | ~ 50             | < 10              |

| Read time<br>[ns]              | ~ 1                | 1-10               | 10 <sup>4</sup>                  | ~ 50                             | < 10               | ~ 50             | < 10             | < 10              |

| Retention<br>[time]            | _                  | ~ 60ms             | > 10y                            | > 10y                            | > 10y              | > 10y            | > 10y            | > 10y             |

| Endurance<br>[cycle n.]        | > 10 <sup>16</sup> | > 10 <sup>16</sup> | > 10 <sup>4</sup>                | > 10 <sup>5</sup>                | > 10 <sup>15</sup> | 10 <sup>15</sup> | 10 <sup>11</sup> | > 10 <sup>6</sup> |

| Energy<br>[pJ/bit]             | ~ 10 <sup>-3</sup> | ~ 0.01             | ~ 0.01                           | 100                              | ~ 0.1              | FeRAM            | 10-100           | 1-10              |

Table 1 – Benchmark of main memory technologies.

Nail *et al.* [72] reported  $200\mu$ A to be the max advisable compliance value for their technology). Moreover, endurance and retention are found to trade with each other at a given window margin.

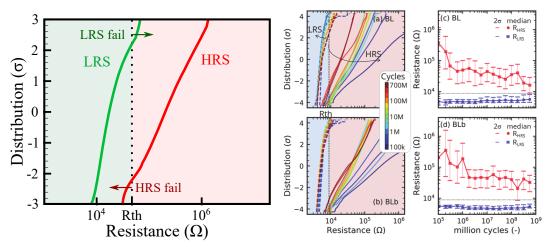

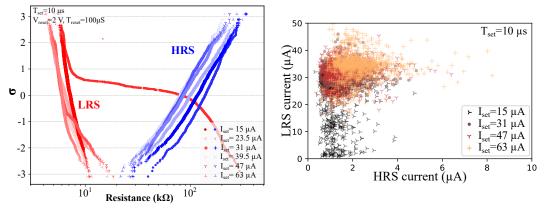

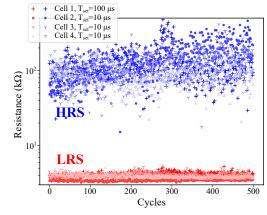

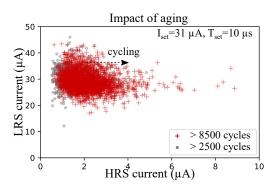

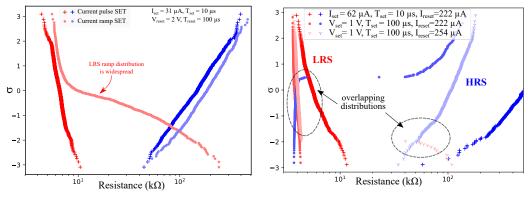

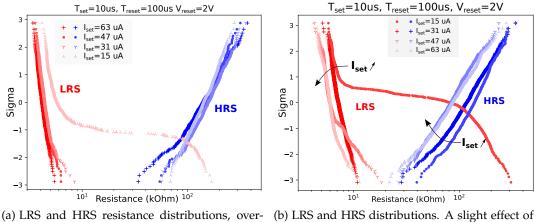

Another important parameter for RRAM is technological variability, intended as the lack of uniformity between LRS and HRS values. Figure 15 shows the problematic: 15a reports the LRS and HRS distribution for 2k samples, while 15b illustrates the evolution of the distribution over cycling. It can be seen that the resistance values vary between different devices as well as programming cycles. Variability is a well known, critical aspect for RRAM, constituting the major hindrance to the implementation of large memory arrays [74–76]. In fact, high statistical variation can result in the overlap of logic values, making the binary states indistinguishable. RRAM is known to be afflicted by both intrinsic and extrinsic varibility [74-78]; while the former results from the stochastic nature of the resistive switching mechanism itself [67, 76, 78], and should be minimized through material engineering, the extrinsic part is caused by erratic programming conditions [79, 80]. Therefore, careful circuit design aimed at reducing the non-uniformity of programming variables (e.g. the wiring voltage/current), has the potential to narrow the resistance distribution [80]. This work tackles the issue of RRAM variability by proposing novel programming circuitries, which are presented in Chapter ?? and Chapter ??: respectively, they rely on a charged capacitor and a Digital to Analog Converter (DAC) to perform the set operation, in order to minimize the writing energy and writing current dispersion.

#### 1.7 ARRAY STRUCTURES

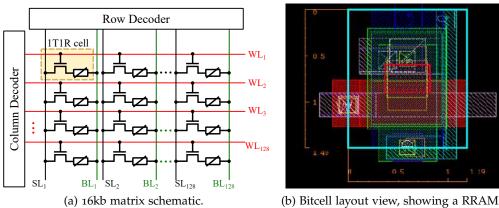

RRAM arrays are arranged in a similar layout to that presented in Section 1.3 for a general RAM memory, where cells are located at the cross-points of horizontal and

which gives rise to fails at the overlapping of the distributions. Adapted from [67]

(a) LRS and HRS device-to-device variability, (b) Cycle-to-cycle variability. As the cycle number increases, the WM closes. [67].

Figure 15 – Variability in RRAM.

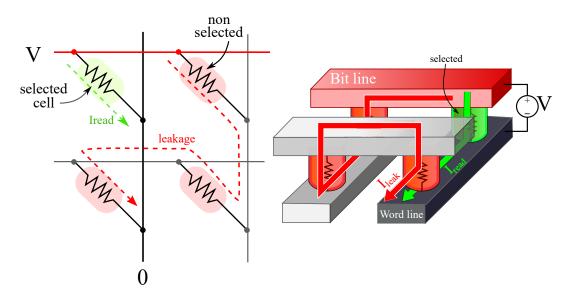

vertical metal lines, the word and bit lines respectively. Each cell is constituted by a RRAM device, storing one bit of information, in series with a selection element, whose impedance is very high when the memory device is not accessed, and low otherwise. The presence of an access element is necessary in RRAM arrays, in order to avoid the programming of non-selected cells, as well as leakage contributions to the output current during the read operation, which might cause readout errors. The phenomenon is known in the literature as sneak paths. Figure 16 illustrates the problematic during a read operation, where a two-terminal crossbar array features cells simply consisting of a RRAM device.

Figure 16 - Sneak paths problem in a selector-less array. Non-selected cells provide an alternative path for current, which results in a leakage contribution at the output.

The selected cell is highlighted in green, and voltage  $V_r$  is posed across its terminals by biasing the corresponding bit and word lines. The output current flowing towards the word line is the sum of the ideal term,  $I_{read}$ , plus a undesired contribution  $I_{leak}$ , which arises by non-selected cells. As a result, the output current is higher than expected <sup>11</sup>, possibly causing the readout circuit to mistakenly interpret the logic state of the selected cell.

The two main SOA cell configurations adopted in order to prevent sneak paths are illustrated in Subsection 1.7.1 and 1.7.2, where, respectively, the selection operation is carried out by a transistor and a volatile RRAM, called as *selector*.

#### 1.7.1 Transistor-RRAM: 1T1R cell configuration

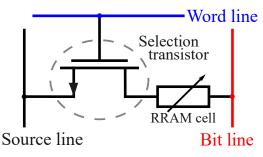

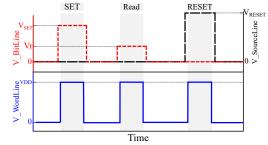

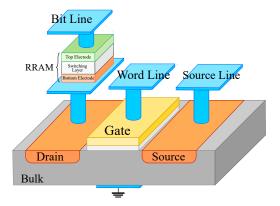

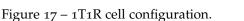

Figure 17a illustrates a popular memory cell topology, known in the literature as one-transistor-one-resistor (1T1R) configuration [81], featuring a MOSFET in series with a RRAM device. Figure 17b shows the corresponding biasing of the metal lines during the set, reset and read operations.

- (a) Memory cell, comprising of a RRAM resistor in series with a NMOS transistor, which acts as selection device.

- (b) Metal lines biasing during the set, read and reset operation of a 1T1R cell, where the transistor (N-MOS) is used as selector.

RRAM

(d) TEM picture of 1T1R cell, where the RRAM is stacked on top of the transistor's drain.

(c) 3D schematic view of the integration process of a 1T1R cell, where the RRAM element is stacked on the drain of the underlying NMOS transistor.

Adapted from [81].

<sup>11.</sup> The lower the impedance of the non-selected cells, the higher the leakage contribution, thus making the presence of sneak paths more critical if the RRAM cells are in LRS.

When the word line voltage,  $V_{WordLine}$ , is high, a conductive channel bridges the drain and source of the access transistor, allowing the voltage difference between the bit and source lines,  $V_{BL} - V_{SL}$ , to drop across the RRAM. The souce line is grounded during the set and read operations, whereas it is positively biased during the reset<sup>12</sup>. This allows to flip the polarity across the RRAM element without implementing negative voltage sources, at the price of a relatively narrowed swing<sup>13</sup>.

The RRAM is generally stacked on top of the transistor during a Back End Of Line (BEOL) process, as illustrated by Figure 17c. The area footprint of a 1T1R cell is 6F<sup>2</sup>: choosing a minimally sized NMOS allows to maximize the integration potential, although awareness to any significant voltage division between the impedance of the transistor and the memory itself is demanded. Figure 17d shows a Transmission Electron Microscopy (TEM) photo of a 1T1R cell, highlighting the front-end transistor and the back-end RRAM.

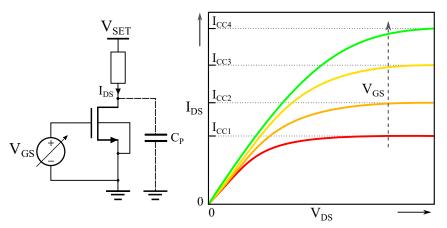

Figure 18 – Equivalent circuit of a 1T1R cell, where the voltage on the gate is varied to obtain different levels of current compliance. Capacitor C<sub>P</sub> represents the parasitic capacitance on the drain, which limits the transistor's frequency response.

As illustrated by Figure 18, the access transistor can be used to clamp the current during the set operation. This is done by opportunely biasing the gate ( $V_{GS}$ ), so that when the transistor enters in saturation, the drain current ( $I_{DS}$ ) equals the desired compliance value. This approach has been largely adapted in the literature [66, 70, 81] due to its simplicity and relative effectiveness; in particular, an integrated transistor offers minimal parasitic capacitance  $C_P$  loading the drain, so that a reduced current overshoot can be obtained when the memory sets (further details on this aspect are given in Chapter ??). However, this method is arguably far from ideal, as technological variability and testing conditions (like temperature) can potentially produce large statistical dispersion in the drain current, especially for smaller nodes. This problematic is further expanded in Chapter ??, where a novel programming circuit is proposed, in order to overcome the dispersion of programming parameters.

<sup>12.</sup> It should be pointed out that, due to its structural symmetry, when the source line is positively biased with respect to the bit line, the drain and source of the transistor are swapped.

<sup>13.</sup> When a NMOS is implemented, the voltage amplitude at the transistor's source must be lower than the gate's by at least a threshold voltage ( $V_{th}$ ) in order to keep the MOS on. Consequently, the amplitude swing is reduced to < 0,  $V_{DD} - V_{th} >$

#### 1.7.2 Selector-RRAM: 1S1R cell configuration

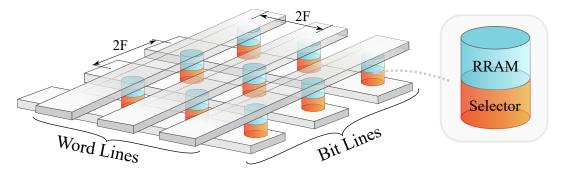

A *selector* is a two-terminal device, which can be put in series to a RRAM cell in order to suppress sneak paths [82, 83]. As a source line is not required, memory arrays can be arranged in *crossbar* topology, which is illustrated in Figure 19. This layout offers high scalability, as the word and bit lines can potentially be minimally spaced (pitch=2F), resulting in a cell area of  $4F^2$  [83].

Figure 19 – Crossbar memory array, where each cell comprises of a RRAM device in series with a selector. If the metal line widths and the spacing between them are designed using minimum feature size (F) the unitary cell footprint results equal to 4F<sup>2</sup>.

The ideal selector resembles a (bidirectional <sup>14</sup>) diode: its resistance should be negligible once enough voltage drops across its terminals, and very high otherwise. It might be assumed that a silicon diode would be a suitable selector: unfortunately, this is not the case, as a p/n junction is produced during front end, while a RRAM in back-end-of the line. Consequently, optimal co-integration with the memory cell would be achievable only by means of some kind of "back-end diode". Different technologies have been emerging, the most promising being Ovonic Threshold Switching (OTS), whose overview is given in Subsection 1.7.3.

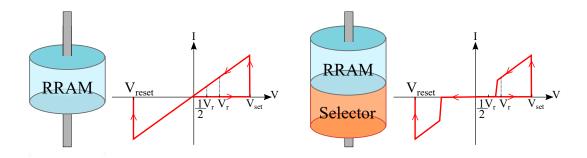

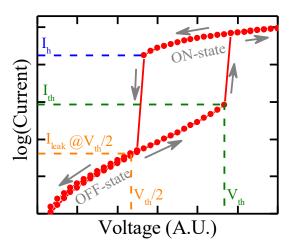

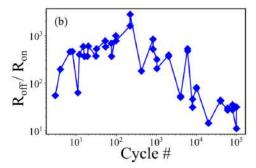

Figure 20a shows the IV curves of a selector-less RRAM (on the left) and a stacked selector-RRAM element (on the right). It can be seen that, when the selector is added, the current across the device remains low until the voltage hits threshold  $\pm V_{\rm th}$ , at which point the selector becomes conductive, and the curve traces that of the single RRAM's. The selector shows low conductivity when the voltage is below  $V_{\rm th}$ , so that the sneak-path effect can be mitigated, preventing programming disturbance and reading errors.

A good selector would offer a high  $R_{off}/R_{on}$  ratio,  $R_{off}$  being its resistance when in insulating state, while  $R_{on}$  the resistance in its conductive state.

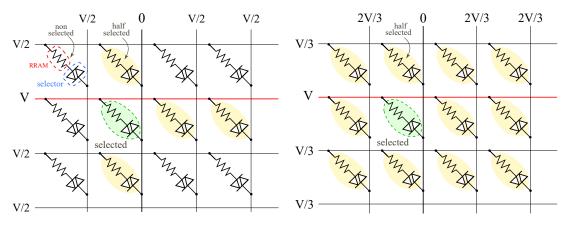

The two most popular biasing schemes, namely the V/2 and V/3 polarization, are illustrated in Figure 20b and Figure 20c, respectively. In either case, the word line of the selected cell is set to write voltage V, while the bit line is at ground. The difference between the schemes lies in how the non-selected lines are biased: according to the V/2 case, any other access line is set to V/2. As a result, the number of half-selected cells, biased at voltage V/2, is  $N_{hs} = n + m - 2$ , while the rest,  $N_{ns} = (n-1)(m-1)$  see no voltage drop.

On the other hand, in the V/3 scheme the non-selected word lines are biased at a

<sup>14.</sup> In the case of a bipolar RRAM.

(a) On the left: I-V characteristic of a RRAM element, on the right: I-V characteristic of the pair selector-RRAM.

(b) Crossbar array in V/2 polarization scheme. The (c) Crossbar array in V/3 polarization scheme. half-selected cells see a voltage drop equal to half of the write voltage.

With exception of the selected cell, the remaining cells are half-selected to a third of the write voltage.

Figure 20 – Operation of the RRAM-selector pair in a memory array.

third of the write voltage, while the non-selected bit lines at two thirds. As a result, more cells are partially selected:  $N_{hs} = nm - 1$ , although the unitary leakage from a non-selected cell (at a given RRAM array) is reduced with respect to the V/2 scheme, as the voltage drop is lessened from V/2 to V/3.

In practice, the optimal biasing scheme should be chosen given the specifics of the memory array at hand, in particular the array size and the device non-linearity [83].

## 1.7.3 OTS Selectors

One of the most promising and intensively researched selector technologies is represented by Ovonic Threshold Switching (OTS) materials, which are based on chalcogenide glasses [84-88].

A typical I-V characteristic is shown in Figure 21: the selector transits from a highly restive (or off) state, to a highly conductive (or on) state, once its voltage and current are greater, respectively, than thresholds V<sub>th</sub> and I<sub>th</sub>. It remains "on", until the current falls below the holding value Ih, at which point the resistance reverts

to a high value. The leakage current,  $I_{leak}$ , is expressed as the current that can be measured when the voltage across the OTS device is equal to  $V_{th}/2$ .

Figure 21 – typical I-V curve of a OTS selector [88]

#### 1.8 OBJECTIVE OF THIS THESIS WORK

In this introductory chapter, the context of this thesis work was given, along with an overview on the main emerging memories in today's market. RRAM, the technology of choice in this study, was presented in larger details, along with some common architectures for the implementation of memory arrays.

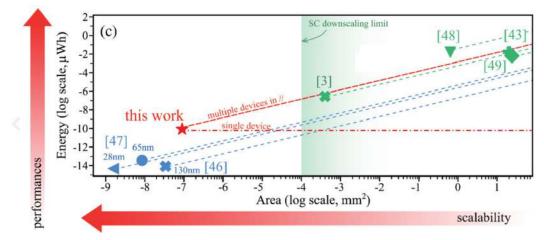

As further discussed in Chapter ??, the motivation behind our study on RRAM is partly rooted in its interest as Storage-Class-Memory, and partly in its potential as a novel type of energy source; the two behaviours are envisioned to coexist, as they share the same, faradaic-based, working mechanism. The attractiveness of a RRAM-based *nanobattery* lies in its high scalability potential, which could be exploited to obtain highly integrable, solid-state energy sources. Moreover, material compatibility with the standard CMOS process would offer the unique advantage of a dual memory/battery device, where the energy could be delivered in close proximity to the target, lowering the power dissipation and delay that occur over standard Power-Delivery-Networks.

In the subsequent chapters, the focus of this manuscript shifts, from device characterization, to integrated circuit design. Chapter ?? and Chapter ?? propose two experimental alternatives, namely a charged-capacitor and Digital-to-Analog Converter (DAC) based programming methods, for setting RRAM. The goal is to reduce both the wide variability which afflicts SOA technologies, and the energy waste that occurs during the set process.

The connecting thread between the diverse parts of this thesis is the research of advanced solutions for a new, energy-efficient, memory technology. As previously presented in this chapter, our quest answers a urgent need in today's semiconductor market, where power consumption and speed are found to trade with each other.

This work is structured in three parts: part i: Introduction (Chapter 1), part ii:

*RRAM as Energy Source* (Chapter 2), and part iii: *Energy-Efficient Design Solutions for RRAM* (Chapters **??** and **??**).

#### INTRODUCTION

## 1.9 CHAPITRE 1 - RÉSUMÉ EN FRANÇAIS

Dans ce chapitre introductif, le contexte de ce travail de thèse a été donné. Les mémoires emergentes non-volatiles devraient révolutionner le domaine des mémoires, offrant des performances qui se situent entre les DRAM et Flash, permettant un stockage de données plus important à une vitesse d'accès et d'écriture plus élevée que les mémoires non volatiles d'aujourd'hui. Après avoir présenté les technologies les plus recherchées (FeRAM, MRAM et PCRAM), les memoires resistives RRAM ont été discutées plus en détail. Les principales mesures de référence (area, Window Margin, Endurance et Retention) ont été présentées et expliquées, et différentes topologies de mémoire ont été comparées. de plus, des typologies d'architecture pour l'intégration de matrices de mémoire à base de RRAM ont été présentées, telles que les schémas 1T1R et 1S1R.

Comme présenté plus en détail au chapitre **??**, la motivation de notre étude sur le RRAM est en partie ancrée dans son intérêt en tant que Storage-Class-Memory, et en partie dans son potentiel en tant que nouveau type de source d'énergie ; les deux comportements sont censés coexister, car ils partagent le même mécanisme de fonctionnement basé sur le faradique que les batteries ioniques.

L'attrait d'une *nanobatterie* à base de RRAM réside dans son fort potentiel d'intégration, qui pourrait être exploité pour obtenir des sources d'énergie à l'état solide hautement intégrables. De plus, la compatibilité matérielle avec le processus CMOS standard offrirait l'avantage unique d'un dispositif à double mémoire/batterie, où l'énergie pourrait être délivrée à proximité de appareil cible, réduisant la dissipation de puissance et le retard qui se produisent sur les réseaux de distribution d'alimentation standard (Power Delivery Networks).

Dans les chapitres suivants, l'objectif de ce manuscrit passe de la caractérisation des dispositifs à la conception de circuits intégrés. Le chapitre ?? et le chapitre ?? proposent deux alternatives expérimentales, basées sur des méthodes de programmation basées sur un condensateur chargé et un convertisseur numériqueanalogique (DAC), pour programmer des RRAM. L'objectif est de réduire à la fois la grande variabilité qui afflige les technologies SOA et le gaspillage d'énergie qui se produit au cours du processus de set.

Part II

RRAM AS ENERGY SOURCE

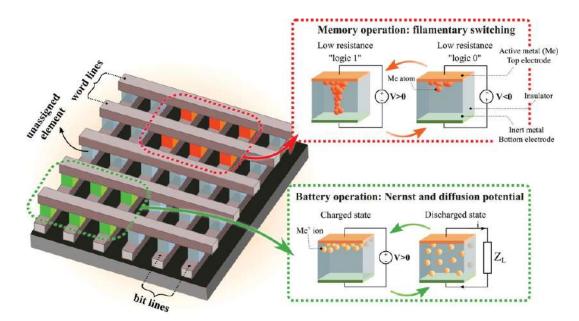

# ENERGY STORAGE IN RRAM

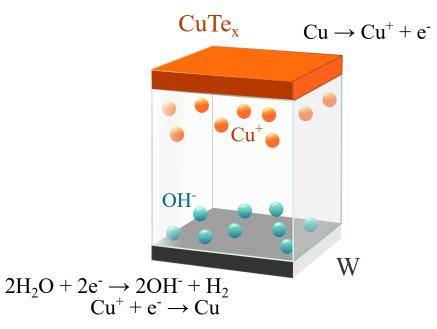

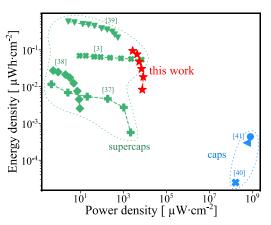

This chapter illustrates the concept of a hybrid dual-behavior device, based on RRAM, for both data retention and energy storage. RRAM as energy storage element is a novel concept, which is grounded on the notion that its working mechanism as memory is based on faradaic reactions, similar to those taking place in ionic batteries. As further expanded by Sections 2.1 and Section 2.2, a RRAM-based battery would offer unique advantages, such as high scalability and CMOS process compatibility, which motivate our study on its feasibility.

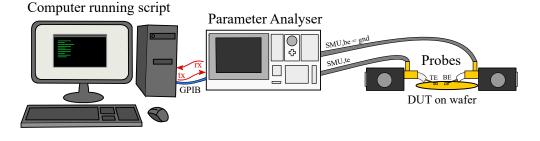

Section 2.3 presents the techniques and instrumentation implemented for the evaluation of energy-storage capability, while Section 2.4 discusses results of various electrochemical characterizations, performed on SOA CBRAM samples. Although far from conventional solid-state battery framework, our results allow us to draw promising preliminary considerations, and express high potential for various standard and emerging applications.

# 2.1 THE INTEREST OF RRAM AS ENERGY SOURCE

Recent advances in fields like artificial intelligence (AI), the internet of things (IoT), virtual reality, and cloud computing have been demanding ever-increasing computational capability. Power-efficient calculation is key in any task implemented on a chip, from high-performance core computing to the edge of IoT. While process miniaturization managed to effectively reduce consumptions in the past [1, 2], its effectiveness has been dropping for recent technological nodes, the overall balance in power cost coming majorly from losses over transmission lines [3–5]. As a result, further downscaling is expected to soon no longer pay off the development investment, and alternative strategies must be considered. This branch of research involves the so-called Moore than More's devices [89].Some attempts to ease consumption rely on on-chip integration of nanoscale energy sources, [90, 91] while others, notably in memory computing (IMC) [9–11, 13], offer a revisited architecture where computation is decentralized. Other research groups proposed the integration of energy sources in close proximity of the memory,[15, 16] or completely integrated within the memory architecture [17].

<sup>6</sup> Our work attempts to tackle the need of energy-efficient computation with a radically different concept, where *dual-behavior* devices are able to store either information or energy, depending on the applied bias. Such capability would be greatly beneficial, allowing localized and high bandwidth energy supply to the processing unit (the memory or a dedicated arithmetic logic unit, ALU). The RRAM samples considered in our study indeed resemble ionic batteries at the nanoscale, providing ground to our inquiry of using these devices as energy sources, other than memory cells [71]. Their operation relies on faradaic processes; therefore, the resulting energy density is expected to well exceed that of electrostatic capacitors, possibly being comparable to supercapacitors [71, 92]. The diameter of the devices under study can range between  $1\mu$ m and  $100\mu$ m, resulting much smaller than the diameter of SOA planar supercapacitors (mm<sup>2</sup>) [71, 91, 92], making such architecture more scalable and granular than any other SOA integrated power source.

Energy storage is achievable when the device is, under a memory point of view, storing a logic 0, and could be accumulated during low logic operation activity for later use, for example, during the most power-hungry phases. These devices would also offer the advantage of placing the battery cell in close proximity to the target, meaning reduced IR drop and voltage undershoot, which develop in a typical inductive-impedance power delivery network (PDN) [93].

Finally, a broad range of applications could be envisioned, each demanding different energy requirements, with widespread specifications. The most suitable target field should be selected taking into account the output voltage, energy, and power delivered by such RRAM-based batteries. Figure 22 provides an outlook on some possible implementations, with some quantified ranges in terms of energy and instantaneous power requirements. The three main eligible domains being energy to memory [94], energy to logic [95], and neuromorphic computing [96–99].

|                                              | Туре              | Energy [pJ] | Voltage [V]      | Power [uW] |

|----------------------------------------------|-------------------|-------------|------------------|------------|

| Energy to memory<br>Cell switching energy    | NAND Flash        | 0.01        | ~20              | 1m         |

|                                              | NOR Flash         | 100         | ~5               | 100        |

|                                              | РСМ               | 100         | 3-5              | 1k         |

|                                              | RRAM              | 1-10        | 2-5              | 100-1k     |

| a a de de                                    | STTRAM            | 0.1         | 1-3              | 10         |

| Energy to logic<br>Min. energy per operation | ARM Cortex M0     | 3 - 6.4     | 0.4 - 0.7        | 0.64 - 240 |

|                                              | ARM Cortex M0+    | 1.1 - 11.7  | 0.19 - 1.2       | 0.4 - 735  |

|                                              | MSP430 compatible | 7           | 0.32 - 0.48      | 56 - 497   |

|                                              | ARM Cortex M3     | 23          | 0.5 - 1          | 23 - 460   |

| , , , , , , , , , , , , , , , , , , ,        |                   |             |                  |            |

| Neuromorphic<br>Energy per synapic event     | SRAM-Based        | 27          | 28nm-compatible  | 63k        |

|                                              | SRAM-Based        | 105         | 14nm-compatible  | -          |

|                                              | RRAM-Based        | N/A         | 40nm-compatible  | 9.9k       |

|                                              | RRAM-Based        | N/A         | 180nm-compatible | 15.8k      |

|                                              | RRAM-Based        | 180         | 130nm-compatible | 1.5k       |

Figure 22 – Estimation of required energy, operating voltage and instantaneous power for various application fields: memory [94], logic [95] and neuromorphic computing [96–99].

## 2.2 A NEW CONCEPT: IN-MEMORY ENERGY STORAGE

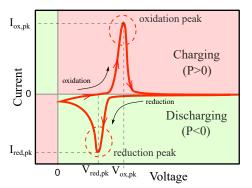

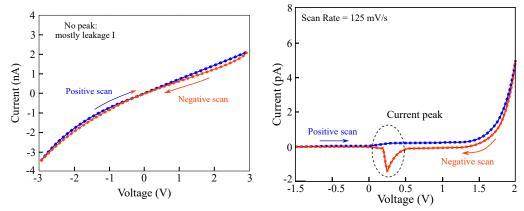

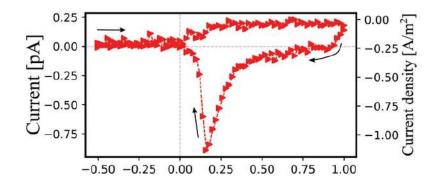

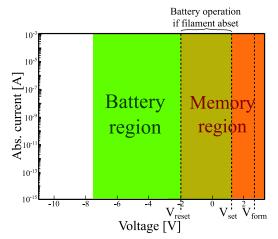

In Chapter i were presented a particular class of RRAM, whose working principle relies on electrochemical reactions: namely, OxRAM and CBRAM. Such devices appear to be the best candidates for energy storage purposes, as their operation as memeories resembles that of ionic batteries. In fact, the cell structure can be seen as a tiny battery, where the top and bottom metal layers constitute the access electrodes, and the (electrically insulating) switching layer is a solid-state electrolyte. Figure 23 reports a schematic illustration of the memory curve of a CBRAM, high-

lighting the electrochemical current contributions for low y values (zoomed view inset). In particular, two peaks are supposed to be revealed: one during the positive voltage scan rate (*oxidation peak*) and one during the negative (*reduction peak*), signalling the saturation of redox products inside the cell's switching layer.

Figure 23 – A typical I–V curve of a RRAM. The memory is, initially (1), in a logic "o" state (highly resistive), and switches to a logic "1" in (3), when the filament bridges the electrodes. The memory goes back to "o" in (4), when the filament dissolves. In the inset, a zoomed view showing the electrochemical currents (redox peaks).

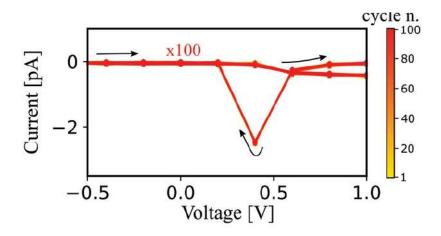

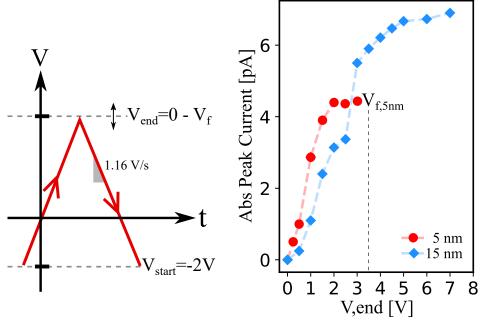

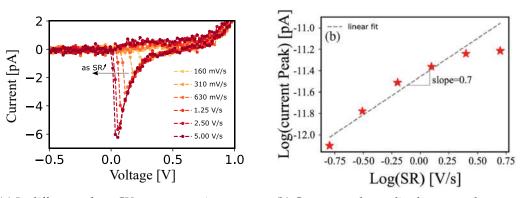

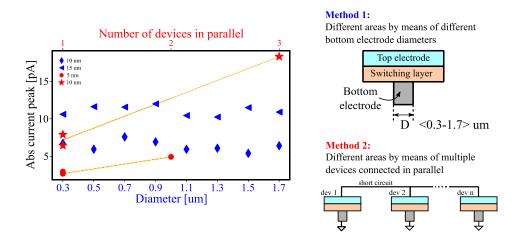

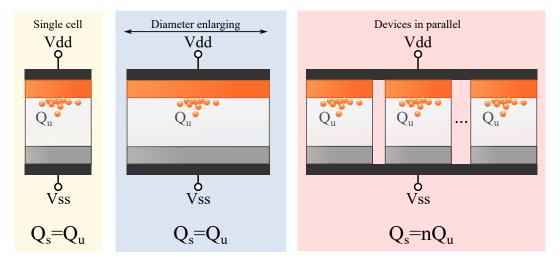

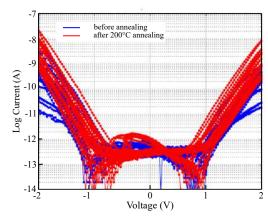

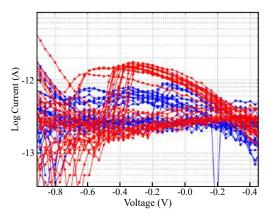

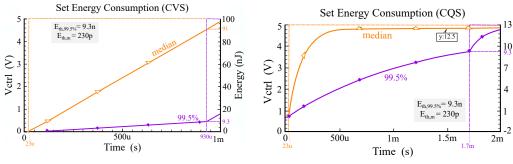

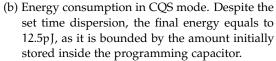

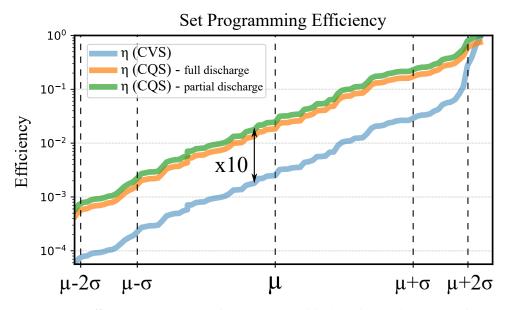

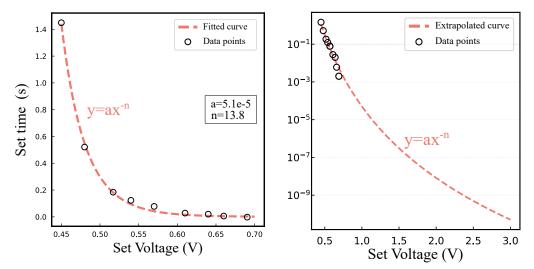

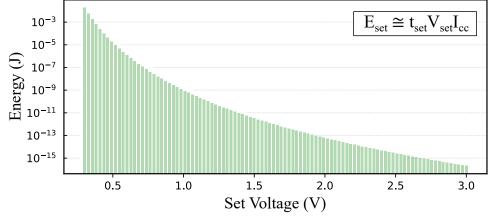

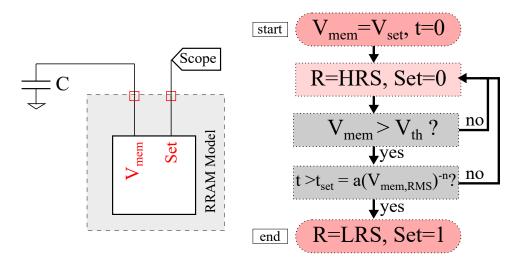

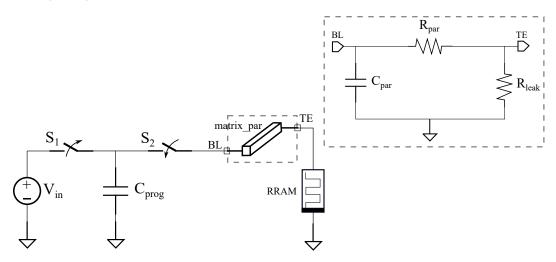

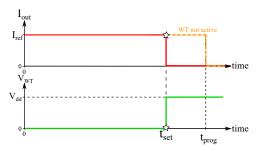

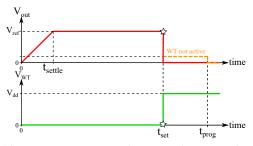

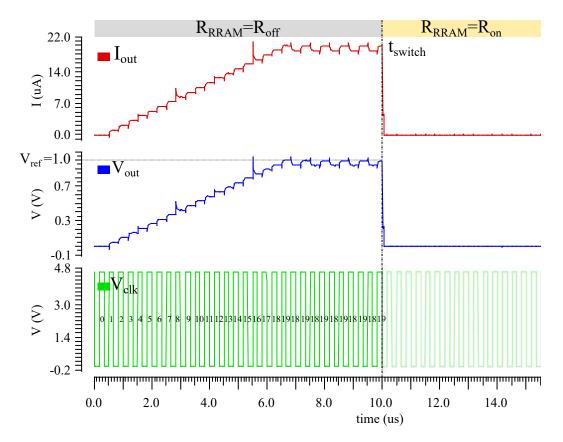

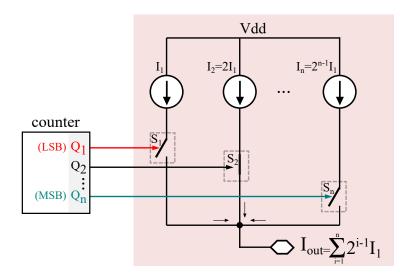

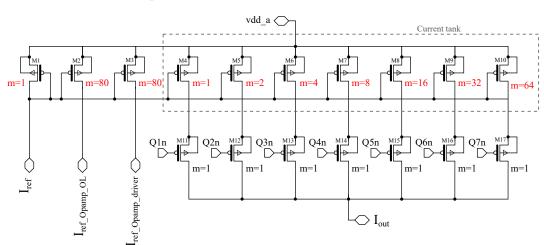

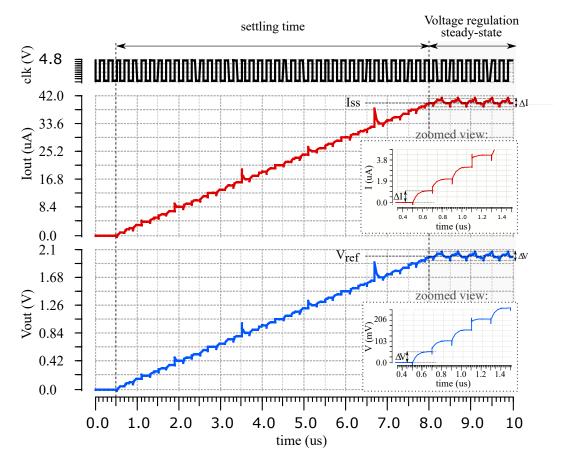

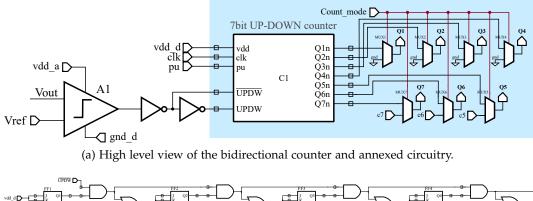

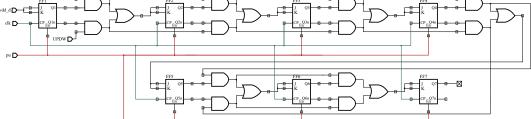

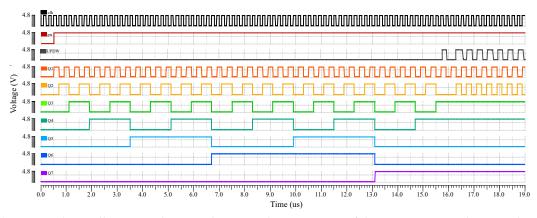

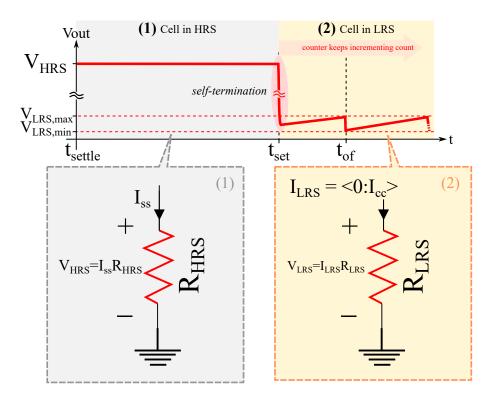

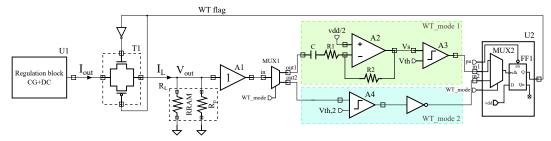

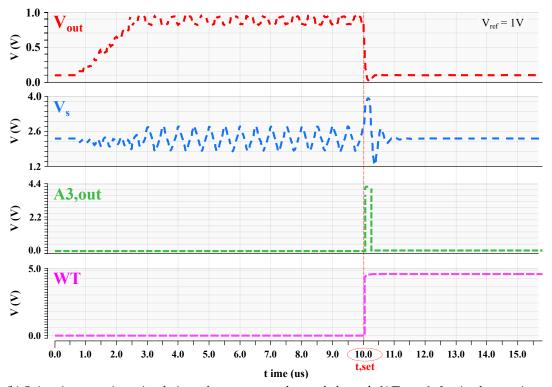

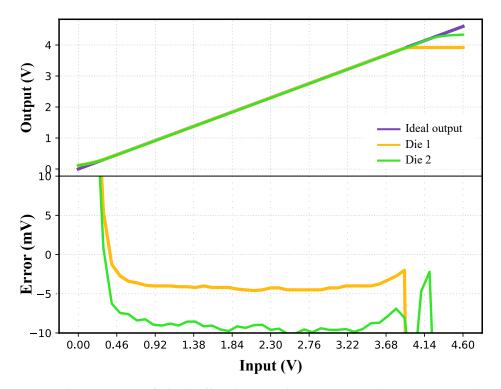

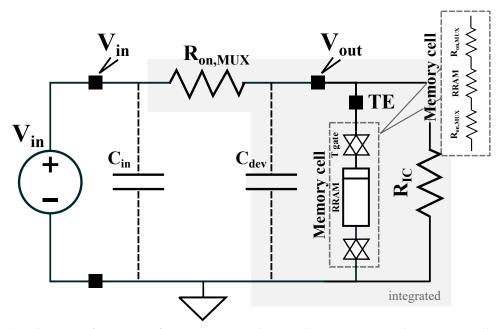

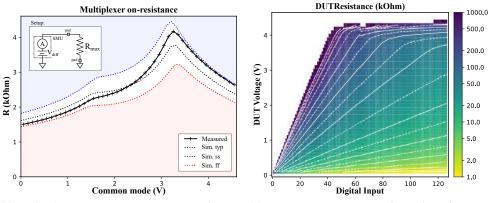

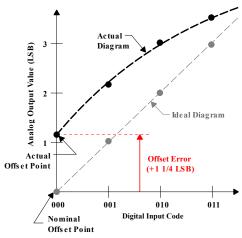

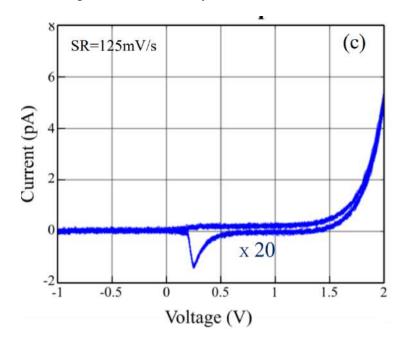

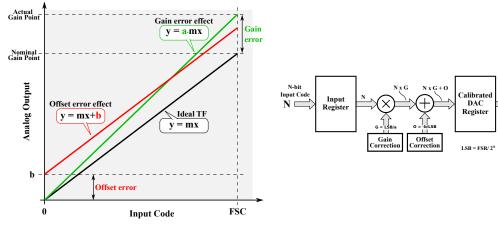

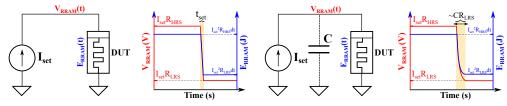

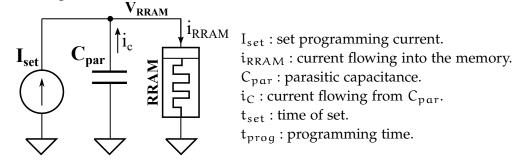

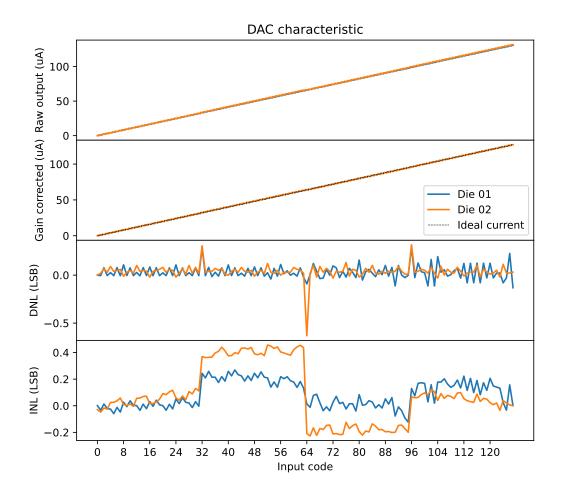

Figure 24 illustrates the envisioned device, where a crossbar-like array integrates elements which can either work as memory or energy storage cells. Sub-arrays are highlighted in green, for cells operating as battery, and in red for those operating as memory. The insets show a schematic of the different operating mechanisms: the *filamentary switching effect* being responsible for nonvolatile information storage, and the *Nernst* and *diffusion* potential for energy supply [60, 68, 100–102].