## Decoupling the optimization space of tensor computation for a better understanding of performance on Intel CPU

Nicolas Tollenaere

#### ▶ To cite this version:

Nicolas Tollenaere. Decoupling the optimization space of tensor computation for a better understanding of performance on Intel CPU. Data Structures and Algorithms [cs.DS]. Université Grenoble Alpes [2020-..], 2022. English. NNT: 2022GRALM045. tel-04068053

## HAL Id: tel-04068053 https://theses.hal.science/tel-04068053

Submitted on 13 Apr 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : MSTII - Mathématiques, Sciences et technologies de l'information, Informatique

Spécialité : Mathématiques et Informatique

Unité de recherche : Laboratoire d'Informatique de Grenoble

Découpler l'espace d'optimisation des calculs de tenseurs pour une meilleure compréhension de la performance sur CPU

Decoupling the optimization space of tensor computation for a better understanding of performance on Intel CPU

Présentée par :

#### **Nicolas TOLLENAERE**

#### Direction de thèse :

Fabrice RASTELLO Directeur de thèse

Directeur de recherche, Université Grenoble Alpes

Guillaume IOOSS Co-encadrant de thèse

Chargé de recherche, INRIA

#### Rapporteurs:

François IRIGOIN

PROFESSEUR, Centre de Recherche en Informatique (CRI) - Mines Paritech

**Brice VIDEAU**

INGENIEUR DOCTEUR, Argonne National Laboratory

#### Thèse soutenue publiquement le 14 décembre 2022, devant le jury composé de :

Fabrice RASTELLO Directeur de thèse

DIRECTEUR DE RECHERCHE, Inria

François IRIGOIN Rapporteur

PROFESSEUR, Centre de Recherche en Informatique (CRI) - Mines

Paritech

Brice VIDEAU Rapporteur

INGENIEUR DOCTEUR, Argonne National Laboratory

Henri-Pierre CHARLES Examinateur

DIRECTEUR DE RECHERCHE, CEA

Michel STEUWER Examinateur

PROFESSEUR ASSOCIE, Université d'Édimbourg

Oleksandr ZINENKO Examinateur

INGENIEUR DOCTEUR, Google Brain

Noël DE PALMA Président

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

#### Invités:

#### Guillaume looss

CHARGE DE RECHERCHE, Inria

# Decoupling the optimization space of tensor computation for a better understanding of performance on Intel CPU

Nicolas Tollenaere

March 14, 2023

# Contents

| 1        | Intr               | roduction                                                    | 1  |  |  |  |

|----------|--------------------|--------------------------------------------------------------|----|--|--|--|

| <b>2</b> | Bac                | kground                                                      | 5  |  |  |  |

|          | 2.1                | Existing tools and related work                              | 5  |  |  |  |

|          |                    | 2.1.1 GotoBLAS/BLIS: a systematic building of efficient ma-  |    |  |  |  |

|          |                    | trix multiplication                                          | 6  |  |  |  |

|          |                    | 2.1.2 Tensorflow                                             | 14 |  |  |  |

|          |                    | 2.1.3 Halide                                                 | 14 |  |  |  |

|          |                    | 2.1.4 Polyhedral tools                                       | 14 |  |  |  |

|          |                    | 2.1.5 MLIR                                                   | 15 |  |  |  |

|          |                    | 2.1.6 BOAST : Source-Source Optimization for optimizing loop |    |  |  |  |

|          |                    | structures                                                   | 15 |  |  |  |

|          |                    | 2.1.7 TVM                                                    | 15 |  |  |  |

|          |                    | 2.1.8 Data-movement modelling: Mopt and Ioopt                | 16 |  |  |  |

|          | 2.2                | Operators                                                    | 17 |  |  |  |

|          |                    | 2.2.1 Tensor Contraction                                     | 17 |  |  |  |

|          |                    | 2.2.2 Convolution                                            | 18 |  |  |  |

|          | 2.3                | Modelization of performance                                  | 20 |  |  |  |

|          | 2.4                | Conclusion                                                   | 21 |  |  |  |

| 3        | Code generation 22 |                                                              |    |  |  |  |

|          | 3.1                | Computation graph                                            | 23 |  |  |  |

|          | 3.2                | Atoms                                                        | 24 |  |  |  |

|          | 3.3                | Examples                                                     | 26 |  |  |  |

|          | 3.4                | Code generation algorithm                                    | 30 |  |  |  |

|          |                    | 3.4.1 Vectorization and Unroll - Generating a basic block    | 30 |  |  |  |

|          |                    | 3.4.2 Tiling loops above the basic block                     | 32 |  |  |  |

|          |                    | 3.4.3 Handling unknown parameters during code generation:    |    |  |  |  |

|          |                    | the Lambda atom                                              | 34 |  |  |  |

|          | 3.5                | Partial Tiles                                                | 36 |  |  |  |

|          | 3.6                | Packing                                                      | 39 |  |  |  |

|          | 3.7                | Work in progress: Parallelism                                | 41 |  |  |  |

|          | 3.8                | Conclusion                                                   | 42 |  |  |  |

| 4 | Exp                  | perimental platform                                               | 43  |  |  |  |

|---|----------------------|-------------------------------------------------------------------|-----|--|--|--|

|   | 4.1                  | General Characteristics of the platform                           | 43  |  |  |  |

|   | 4.2                  | Interface                                                         | 43  |  |  |  |

|   | 4.3                  | Compiler impact                                                   | 45  |  |  |  |

|   | 4.4                  | Performance counters                                              | 47  |  |  |  |

|   | 4.5                  | Semantic Checks                                                   | 47  |  |  |  |

|   | 4.6                  | Performance reproducibility and stability                         | 49  |  |  |  |

|   | 4.7                  | Conclusion                                                        | 50  |  |  |  |

| 5 | Space Exploration 55 |                                                                   |     |  |  |  |

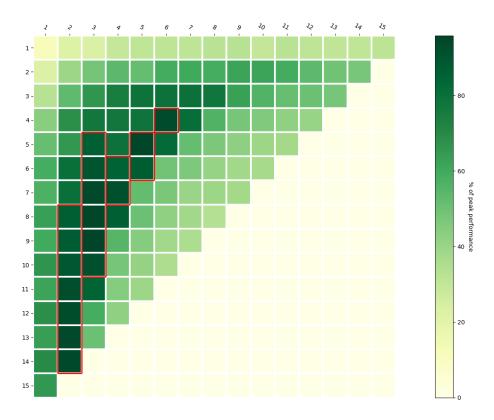

| J | 5.1                  | Quality of a search space                                         | 52  |  |  |  |

|   | 5.2                  | Microkernel selection                                             | 53  |  |  |  |

|   | 5.2                  | Divisibility                                                      | 55  |  |  |  |

|   | 5.5                  | 5.3.1 How to implement a partial tile microkernel                 | 59  |  |  |  |

|   |                      | 5.3.2 Discussion on partial tiles                                 | 61  |  |  |  |

|   |                      | 5.3.3 A case study on small matrix-multiplication                 | 62  |  |  |  |

|   | 5.4                  | Tiling above the microkernel                                      | 63  |  |  |  |

|   | 5.4                  | 5.4.1 On the question of permutation                              | 65  |  |  |  |

|   |                      | 5.4.2 Ioopt                                                       | 65  |  |  |  |

|   |                      | 5.4.3 Model-based filtering                                       | 66  |  |  |  |

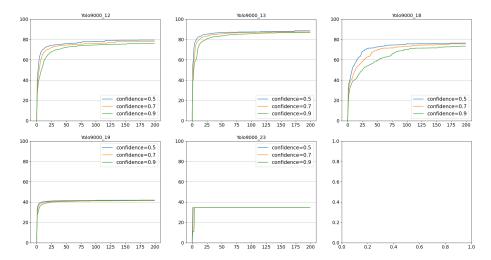

|   |                      | 5.4.4 Tree search                                                 | 70  |  |  |  |

|   |                      | 5.4.5 A baseline better than expected: Random search and met-     | 70  |  |  |  |

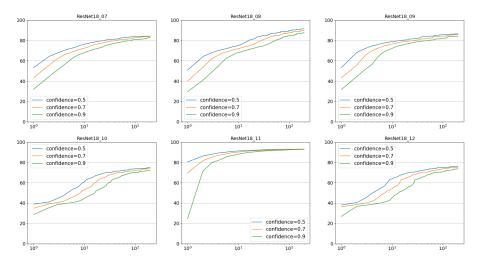

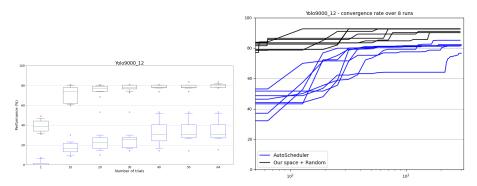

|   |                      | ric evaluation                                                    | 75  |  |  |  |

|   |                      | 5.4.6 Computation of the expect function                          | 76  |  |  |  |

|   | 5.5                  | About layout and packing                                          | 82  |  |  |  |

|   |                      |                                                                   | -   |  |  |  |

|   | 5.6                  | Parallelism                                                       | 82  |  |  |  |

| 6 | Exp                  | perimental results                                                | 84  |  |  |  |

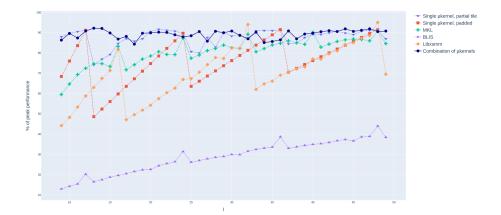

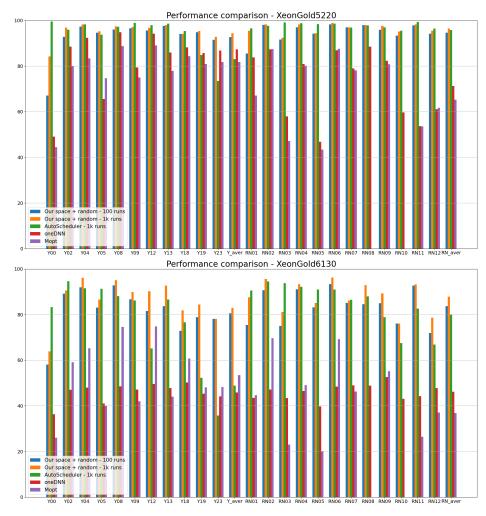

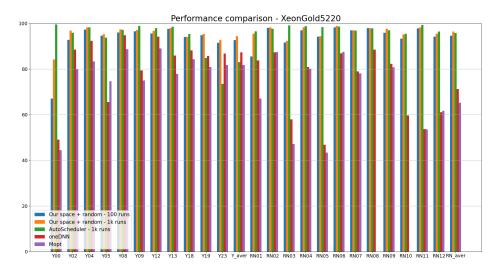

|   | 6.1                  | Performance evaluation - sequential                               | 84  |  |  |  |

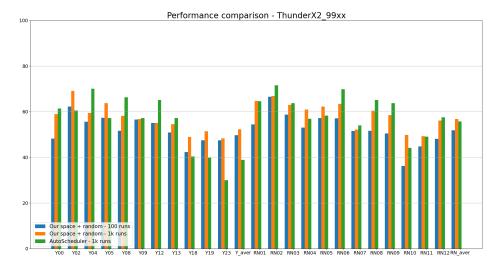

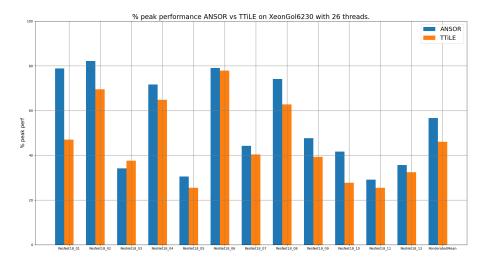

|   | 6.2                  | Performance evaluation - parallel                                 | 86  |  |  |  |

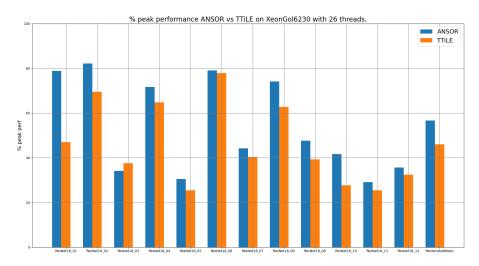

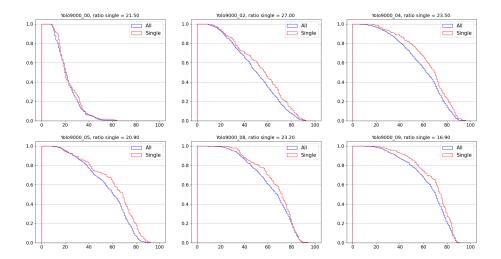

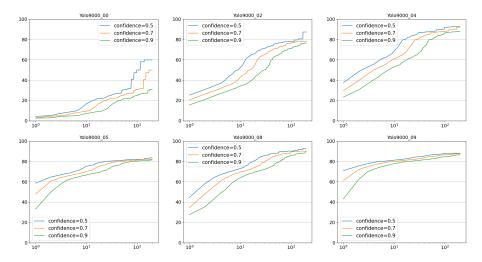

|   |                      | 6.2.1 Random search in parallel                                   | 88  |  |  |  |

|   | 6.3                  | Dissecting performance contributions : Ablation studies           | 91  |  |  |  |

|   | 6.4                  | Evaluation of the combination of microkernels                     | 92  |  |  |  |

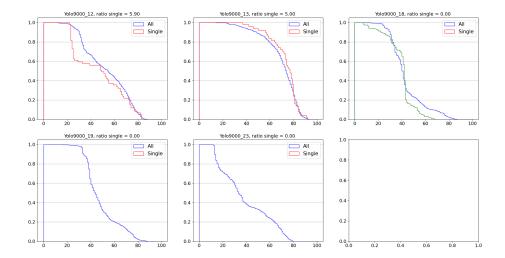

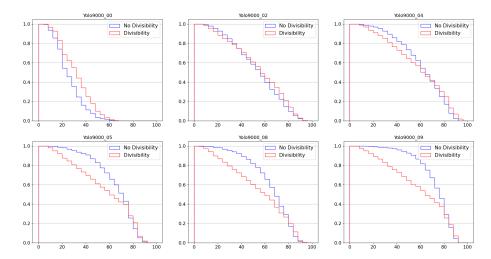

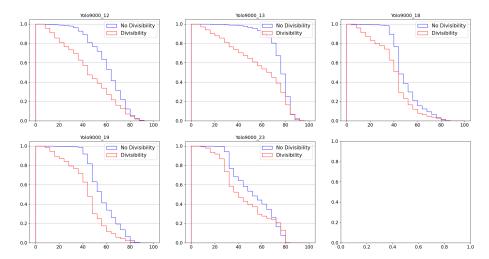

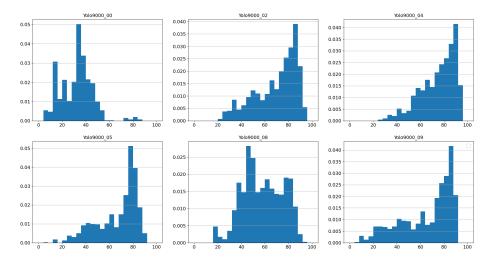

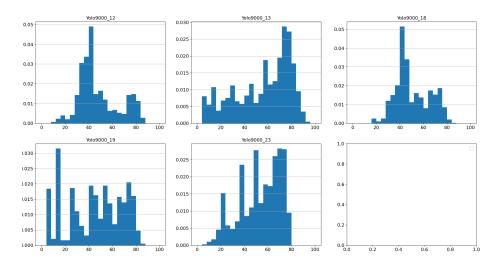

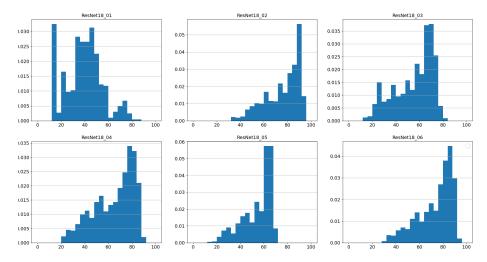

|   | 6.5                  | Evaluation of the divisibility hypothesis above the microkernel . | 93  |  |  |  |

|   | 6.6                  | Future Works                                                      | 96  |  |  |  |

| 7 | Discussion 101       |                                                                   |     |  |  |  |

|   | 7.1                  |                                                                   | 101 |  |  |  |

|   | 7.2                  |                                                                   | 102 |  |  |  |

|   |                      | 7.2.1 Perfectly nested loop and divisibility constraint           |     |  |  |  |

|   |                      | 7.2.2 Random is all you need                                      |     |  |  |  |

|   |                      | 7.2.3 One-shot versus learning                                    |     |  |  |  |

| 8                | Con | clusion and future work 10                                   | 06 |  |  |

|------------------|-----|--------------------------------------------------------------|----|--|--|

|                  | 8.1 | Tensor computation optimizations                             | 06 |  |  |

|                  | 8.2 | Future work                                                  | 08 |  |  |

|                  |     | 8.2.1 Packing and Layout                                     | 08 |  |  |

|                  |     | 8.2.2 Compiler as a language ?                               | 08 |  |  |

|                  |     | 8.2.3 Experimental evaluations                               | 09 |  |  |

| $\mathbf{A}$     | Rés | umé étendu 1                                                 | 10 |  |  |

|                  | A.1 | État de l'art                                                | 10 |  |  |

|                  |     | A.1.1 GotoBLAS/BLIS : construction systématique de multipli- |    |  |  |

|                  |     | cations de matrices efficaces                                | 10 |  |  |

|                  |     | A.1.2 Micronoyau                                             | 10 |  |  |

|                  |     | A.1.3 Tuilage                                                | 11 |  |  |

|                  |     | A.1.4 Multiplication de matrice et convolution               | 12 |  |  |

|                  |     | A.1.5 Autotuning                                             | 13 |  |  |

|                  |     | A.1.6 Autres outils                                          | 13 |  |  |

|                  |     | A.1.7 Quels axes de travail?                                 |    |  |  |

|                  | A.2 | Génération de code                                           | 14 |  |  |

|                  | A.3 | Plateforme expérimentale                                     | 16 |  |  |

|                  | A.4 | Recherche de solutions optimales                             |    |  |  |

|                  | A.5 | Resultats                                                    | 20 |  |  |

|                  | A.6 | Conclusion                                                   | 21 |  |  |

| Bibliography 123 |     |                                                              |    |  |  |

#### Abstract

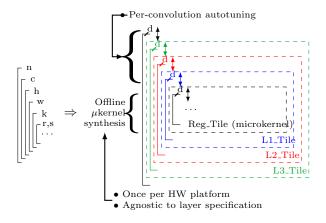

This work focuses on the problem of optimizing a class of programs we call tensor computation, which includes matrix multiplication, tensor contraction (which is a generalization of matrix multiplication), and convolution. One of the key points of our methodology is the use of what we call a *microkernel*, a small optimized block of code that serves as a building block for the whole program. We present a pipeline called TTiLE that automatically generates a specialized code for a given problem size.

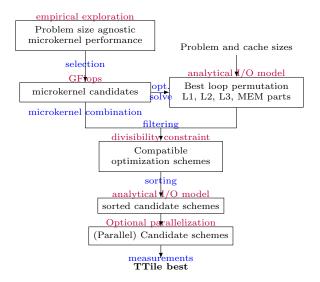

We separate the optimization scheme into two phases: first we select the microkernel with an empiric search. Then we select the outer levels. In this last phase, we leverage some of the work done in performance modelization. This methodology allows us to match the performance of state-of-the-art tools on recent architectures.

To explore our design space and evaluate our search strategy, we crafted a dedicated code generation and evaluation platform.

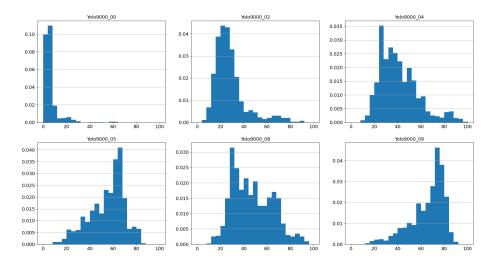

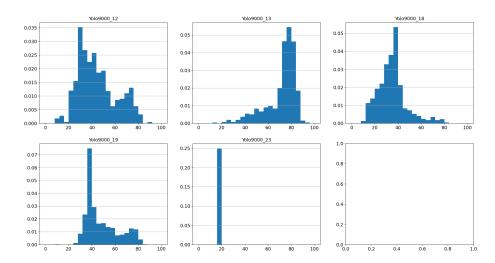

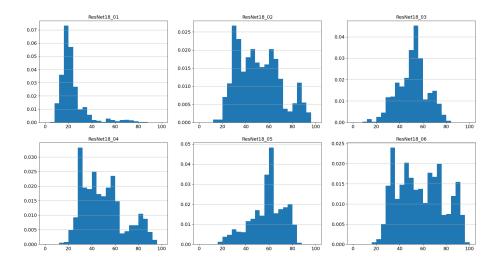

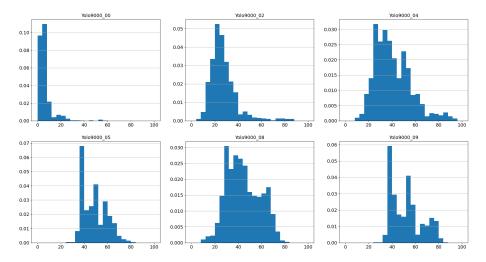

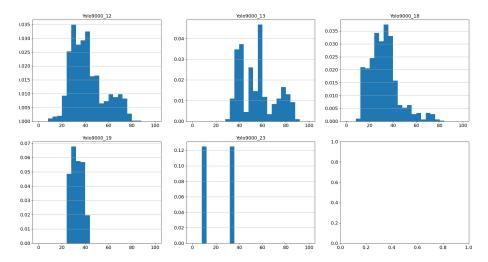

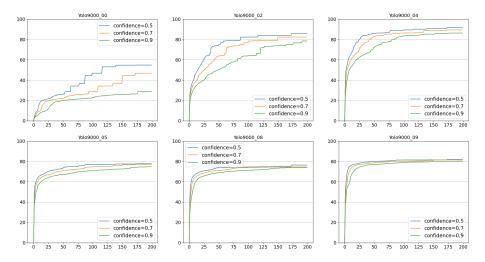

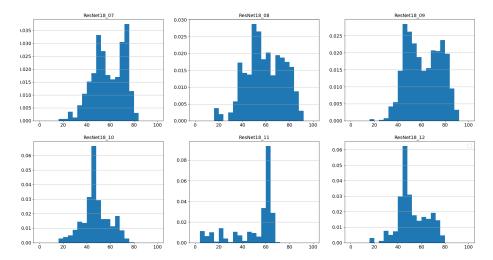

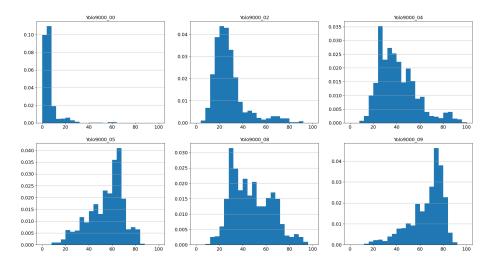

In the process of this exploration, we had to reconsider the way we evaluate a search process. We introduce a clear cut between what we call the *search space* and the *search heuristic*. We characterize a search space by its distribution, which is evaluated empirically by random sampling. This distribution is then used as a baseline - a search heuristic is worth using only if, for the same number of tests, it can converge toward a better candidate than a random search.

This evaluation process allows us to characterize which choices do improve the search by rising the density of good candidates in the space, and which ones do not. Some of the choices we did early in our research, such as generating only perfectly nested or nearly perfectly nested loops, proved to have little to no positive impact on the final performance.

Our results show that the combination of a very straightforward code generation scheme, a restriction to use only selected microkernels at the inner level, and a random search of the outer levels of the loop nest converges very quickly toward candidates that are competitive with the state of the art (mainly AutoTVM/Ansor, but also Halide and OneDNN) on Intel CPU, both in parallel and sequential settings.

The main takeaway of this thesis is the coupling between space definition and exploration. That is, the performance of a given space exploration heuristic (be it guided by a deterministic model, or based on a learning algorithm) strongly depends on the configuration of the space we are looking into. A very loose restriction of a space where a huge proportion of candidates are inadequate imposes the need for a sophisticated search. On the contrary, restricting more tightly the space of possible implementations by constraining some design choices can make even naive search strategies, such as random selection, competitive with more elaborated ones.

#### Résumé

Ce travail se rapporte au problème de l'optimisation d'une classe de programmes que nous appelons Calculs de tenseur et qui inclut les multiplications de matrices, la contraction de tenseur (une généralisation de la multiplication de matrices) et la convolution.

Notre approche s'appuie sur des observations introduites dans GotoBlas et BLIS. Notre méthodologie est basée sur l'utilisation de ce que nous appelons des micro-noyaux. Cela consiste à utiliser un petit morceau de code ultra-optimisé qui sert de brique de base à l'ensemble du programme. Nous présentons un algorithme appelé TTiLE qui génère automatiquement du code spécialisé pour un programme de la classe que nous optimisons et une taille de problème donnée.

Le schéma d'optimisation est séparé en deux phases : nous sélectionnons d'abord le micro-noyau sur la base d'une recherche empirique. Ensuite, nous sélectionnons les niveaux supérieurs du nid de boucle. Dans cette deuxième phase nous tirons parti de l'état de l'art existant en modélisation de performance. Cette méthodologie nous permet de concurrencer les outils les plus récents sur des architectures récentes.

Afin d'explorer l'espace des solutions possibles et d'évaluer notre stratégie de recherche nous avons développé une bibliothèque de génération de code dédiée ainsi qu'une plateforme d'expérimentation.

Au cours de ces travaux, nous avons du reconsidérer la manière dont nous évaluons un processus de recherche. Nous introduisons une distinction nette entre ce que nous appelons l'espace de recherche et l'heuristique de recherche. Nous caractérisons l'espace de recherche par sa distribution. Cette distribution est évaluée empiriquement à l'aide d'un échantillonage aléatoire. Une fois évaluée, nous nous en servons comme d'une référence. Une heuristique est utile uniquement si, pour un nombre d'essai donné, le meilleur résultat obtenu est significativement meilleur que celui qu'on obtiendrait avec une recherche aléatoire.

Ce processus d'évaluation nous permet de caractériser quels choix améliorent réellement l'espace de recherche en augmentant la densité de bons candidats. Certains choix faits tôt dans notre recherche tels que s'astreindre à ne générer que des boucles parfaitement imbriquées se sont révélés n'avoir que peu d'impact.

Nos résultats prouvent que la combinaison d'une génération de code très simple, de la restriction à des micronoyaux sélectionnés au niveau interne et d'une recherche aléatoire pour les niveaux externes du nid de boucles converge très rapidement vers des candidats compétitifs avec l'état de l'art (essentiellement TVM mais aussi Halide et OneDNN) sur des CPU Intel, à la fois en parallèle et en séquentiel. Des expériences préliminaires montrent de bons résultats sur des architectures ARM également.

La leçon prinicipale de cette thèse est le couplage entre la définition de l'espace de recherche et son exploration. Plus précisément, la performance d'une heuristique de recherche (qu'elle soit guidée par un modèle déterministique ou

basée sur un algorithme d'apprentissage) dépend fortement de la configuration de l'espace exploré. Un espace peu contraint où une proportion écrasante de candidats sont mauvais rend nécessaire une exploration puissante. Au contraire, un espace plus contraint où certains choix sont restreints en avance peut rendre des stratégies naïve comme une recherche aléatoire compétitive face à des algorithmes beaucoup plus avancés.

## Chapter 1

## Introduction

Compilation techniques usually care about finding heuristics that would yield the best possible performance for most cases, hiding as much as possible the low level details to final users. This is because the space of possible programs is humongus, so we cannot know in advance which bottlenecks we are going to face. There are other parameters to consider. Depending on the specific usecase, compilation speed, reusability and readability of code can be considered as important or sometimes more important than pure performance. As a result, apart from some simple and well-known optimization such as deadcode elimination or common sub-expression elimination that have been implemented for decades, performance optimization in general-purpose languages and compilers can be considered a lower priority than, say, compilation speed, or language-expressivity. This is not the case we are dealing with though. Some applications are considered worth spending more time, effort and low-level consideration into.

A good example of that is linear algebra. This field of application has led to many researches in the past decades, notably with the BLAS and LAPACK libraries [NVI18] [GVDG08]. This is mostly because an operation such as matrix multiplication is ubiquitous, and because a lot of codebases using matrix multiplication are running for several days. This means that even marginal performance improvements are considered a significant win. In the last decade, the rise of deep learning has further reinforced the importance of linear-algebra super-optimization. Indeed, many layers in a deep neural network are akin to linear-algebra operators, one of them being convolution. This relation between linear algebra and convolution will be made explicit in Section 2.2.2 and is also explained in [ZFL18a]. In a nutshell, a convolution implementation can rely on standard matrix multiplication kernels, modulo some data reshaping, see [CPS06].

There are many ways one can provide highly-optimized operations. These solutions have to make tradeoffs between competing requirements:

- Leverage expert knowledge

- Allow users maximum flexibility

- Portability from one architecture to another

- Minimize engineering costs.

Leveraging expert knowledge means exploiting as much as possible the expertise built over several decades of optimizing linear algebra. Flexibility implies that the user can specify many different kinds of applications, including some that were not anticipated by the vendor. At last, we want to minimize the engineering time we need to spend on hand tuning these applications. At one end of this spectrum, we can find general-purpose language with optimizing compilers. Users are given maximum flexibility but, on the other hand, there is not much high-level information that compilers can exploit and they often have to do pessimistic assumptions to account for edge cases and semantic preservation. As a result, general-purpose compilers need sophisticated heuristics and models to retrieve performance. At the other end, there is the solution of providing a library of hand-tuned routines. In this case, users are constrained by the choices of the vendor and cannot do anything on their own when a particular routine is missing, when their architecture is not supported, or when the implementation does not yield enough performance on their particular setting. However, as library vendors have complete control of the code, they are free to incorporate all the expert knowledge they can into the implementation. This means the engineering cost is high because this work has to be redone for each new operation and each new architecture. Another limitation of this approach is that one can not specialize the code for the problem sizes.

Other solutions try to find some sweet spots between these two extremes. Domain Specific Languages (DSL) are another example of this tradeoff. Instead of providing a full-fledged programming language, vendors provide a dedicated language for the kind of operations they strive to optimize. This allows both to let some degree of flexibility to the user, and to maintain enough invariants so that expert knowledge can be applied without too much effort. DSL can be stand-alone, which allows them to provide custom syntax to their users. One example of this is Halide [RBA+13] or Polymage [MVB15]. They can also be embedded in another language. This is called an embedded domain specific language (EDSL). In the latter case, one can leverage other libraries and tooling available in the embedding language. This also avoids users having to learn a whole new language for the sake of a particular implementation, which can hamper adoption.

My work is focused on the special case of tensor computation, a class of programs that both have applications in a large set of fields, and have nice properties that make optimization somewhat easier. This class of programs includes tensor contraction, matrix multiplications (which is a special case of tensor contraction), and convolutions. Amongst tensor computation, we have put a special effort into convolution, which is a common operation in deep learning and image recognition. Besides being the last "hot stuff" in the compilation and optimization community with articles such as [LXSR+21, CMJ+18] focused on the optimization of this particular operator, convolutions used in practice often exhibit small dimensions which make at least some of the state-of-the-art

optimization schemes inefficient. This is one of the work hypotheses behind my thesis: that at least some of the usual assumptions are invalid in the context of convolution on CPU, and therefore that we can relax these constraints and find another way through.

Nevertheless, this work extends on the principles of BLAS and BLIS libraries (which are described in Chapter 2) and thus contrast with other types of approaches on the matter. Inspirations were taken from many other works such as Telamon [BPP+17], Ioopt [OIT+21] and the place of the final implementation on the previously discussed spectrum (libraries - generic language with compiler) is a matter of discussion. We will see that it leans towards an autotuning solution in some aspects, and on a more "library-like" or maybe DSL-like design in others.

We decompose the problem of building an efficient convolution in two parts: (i) building a space of possible implementations (called a *search space* from now on), (ii) exploring this space to choose one specific implementation. These two phases are coupled in the sense that the search space eliminates implicitly all possible implementations that it does not contain. We will discuss the tradeoff we have to make between allowing a lot of candidates, which implies letting many bad candidates in the space, and building our space in a opiniated manner, which hopefully prunes a lot of bad candidates beforehand and therefore accelerates convergence towards good ones, but makes it easy to miss some good potential candidates.

In this work, we focus on CPU implementation. Nowadays a huge part of the high-computing work is done on GPUs. However, deep learning convolutions are used in two different settings: training, where the network tries to learn to discriminate features from its learning set, and inference, once it has done its training, and applies it to new instances. GPU is mostly used for the training phase, where the goal is to reach the highest possible throughput. When doing inference, CPUs are relevant because the amount of computation and the level of parallelism are lower, and we care more about latency. This is why optimizing convolutions for CPU is an important task.

This document starts with a background chapter that introduces key notions to the design we are going to present. This part will explain concepts such as microkernels or streaming which then act as building blocks for the solutions I have implemented.

A prerequisite to conducting this study was to have an appropriate setting for testing many different code configurations. Thus, a part of my contribution was to design (yet) a(nother) code generation library that would expose all necessary options to twist the code I want to test as needed while being a more lightweight solution than writing C code by hand. The details of this code generation can be found in Chapter 3. The strategy was to start with the simplest code generation that would fit our needs. This code generation was then enriched on the fly with new primitives when they proved useful for performance.

Once this tool was available, the next step was to integrate it into an experimental platform that would measure performance and verify semantic correctness. This is described in Chapter 4.

Then the Chapter 5 describes the optimization process per-se. We will show how we bake our core assumptions into the design of the search space - the space of all possible implementations for the problem size we are dealing with. Then we will discuss different ways we tried to explore this space and the conclusions that arise from it. Chapter 6 presents our results in more details.

This document ends with a discussion on the matter: on a personal level, the way we did our research, which inspirations were used and what could have been done better. The chapter also reflects on the matter of optimizing programs at a higher level.

## Chapter 2

# Background

Since linear algebra optimization has applications in many domains of computing, it has been a research subject for decades. Therefore, many techniques have been explored and we strive to build upon them. The point of this section is to define the key notions that we are going to use through this work, as well as present the state of the art and the different solutions that already exist. A lot of the work done on optimizing linear algebra has been focused on parallelization, either by using multiple cores on the same machine or by relying on a computer cluster. However, our work focuses more on the optimization of linear algebra on a single core.

This optimization relies on well-known optimization techniques such as unrolland-jam, vectorization, exposing instruction-level parallelism, or tiling. One of the most important notions is the definition of a *microkernel* defined in Section 2.1.1. It consists in a small piece of highly-optimized code that serves as a building block. It is central to the way we decouple the problem of building a good implementation for the kind of algorithm we optimize. We also define what is a convolution from an operational point of view, and how the optimization of this operator relates to the general field of matrix multiplication optimization.

## 2.1 Existing tools and related work

As we said, many tools were developed for linear algebra optimization in the last decades. In this section we are going to present a few of them. We start by the most important: GotoBLAS [GG08] (for Basic Linear Algebra Subroutines/BLAS Like Interface Software) [Lou88]. This family of works has helped define some of the concepts we are going to explore in the next sections of this document. Therefore we will spend a lot of time explaining these concepts, especially those of microkernels and hierarchical tiling.

# 2.1.1 GotoBLAS/BLIS: a systematic building of efficient matrix multiplication

We start by describing the BLAS routine. BLAS means Basic Linear Algebra Subroutines and consists of a set of standard interfaces and implementations for some basic linear algebra routines. It dates back as far as 1979 [Lou88]. GotoBLAS [GVDG08] is a specific implementation which settles some of the principles of implementing a high performance matrix multiplication. In 2015, BLIS [VZvdG15] took a look back at these principles and generalized them to provide a library that emphasizes even more portability and reusability. Here we want to give a first intuition of what makes this implementation strategy both efficient and simple.

#### Hierarchical tiling: an overview of the GotoBLAS strategy

As we said, BLAS (Basic Linear Algebra Subprogram) is a specification for a variety of linear algebra low-level routines. As these routines were reimplemented multiple times to take advantage of new architecture designs, this common specification made sure that everyone could rely on the same signatures and still get the benefit of an expert-made implementation.

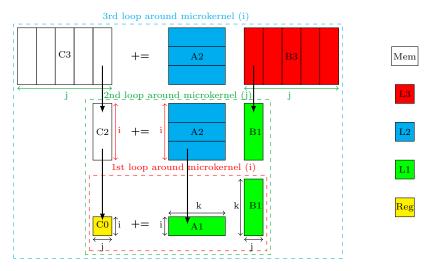

One key point of GotoBLAS implementations is that they rely on a strict separation between the low-level and the higher-level parts of the code. The low-level part is called a *microkernel*. It consists in a fixed-size small subpart of a computation written directly in assembly language. Its design is intended to make the best possible use of the architecture features, such as vector instructions, Instruction level parallelism, or prefetch. We will get back to this design later in Section 2.1.1.

The higher-level part is written in C and makes calls to the microkernels. In GotoBLAS design, it also ensures that data are shaped according to the microkernel requirements. Indeed, a microkernel operates on a fixed-size, contiguous set of subarrays whose layout should match the iteration pattern. That is, accesses inside the microkernel have to be done in a contiguous fashion.

This requirement in turn makes it necessary for the outer-level code to do some reshaping of the data, which consists in reordering and compacting array elements in smaller buffers. This is called *packing* in literature.

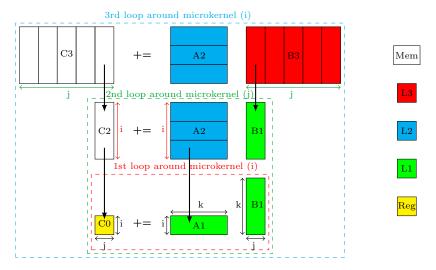

The overall scheme is called hierarchical tiling: it consists essentially in making sure that there is a tile that fits in the cache at every level to exploit data reuse.

In GotoBLAS, packing is done at each level of the cache hierarchy. This means that at each point in the loop nest where the footprint overflows a given cache level, there is a copy/reshuffling that makes sure accesses are done linearly.

BLIS [VZvdG15] is another implementation of BLAS, designed to maximize genericity and code reuse. It does so by providing a set of routines focusing on a kind of polymorphism. Indeed, a typed API allows the user fine-grained control over the dimensionality of computation (pointwise operations on vectors, pointwise operations on matrices, 2d operations...) and the types of matrice elements

Figure 2.1: Naive matrix multiplication

(single or double precision floating point numbers, 32 or 64-bit integers...), and the original layout. This flexibility is not attained by multiple implementations but by adapting dynamically around a bunch of *specialized microkernels*, which is identified as the main performance bottleneck.

#### Microkernel design

In this paragraph, we describe how GotoBLAS has set the design of its micro-kernel and how it is directly guided by micro-architectural considerations.

At the lowest level, performance essentially depends on two parameters: use the full power of vector instruction especially, in our case, single fused multiply-add, and make sure that the core pipeline is full. The second point boils down to two contradictory requirements:

- hide latency by adding enough parallel instructions in the basic block

- minimize spilling, that is, make sure that most data is register-resident

To illustrate that, we present a step-by-step observation to see how to rewrite a naive implementation of a block matrice-multiplication into an efficient one. Recall the definition of a matrice-multiplication - we are using the Einstein's Notation here similarly to  $[RBA^+13]$ :

$$C[i, j] = C[i, j] + A[i, k] * B[k, j]$$

If we were to implement it in a naive way such as in this code:

There would be several problems hindering the performance. Firstly, it is impossible to vectorize this code, as the inner loop is a reduction.

In this setting, vectorizing over a dimension imposes some constraints:

- this dimension should be parallel no data dependencies across iteration over this dimension

- this dimension should be innermost in the layout of all tensors it accesses.

These constraints are not strictly necessary to apply vectorization from a semantic point of view. The first one is too tight: it should be enough to check

```

1 for (int i = 0; i < N - 32; i++) {

2 A[i + 18] = A[i] * B[i];

3 }

```

Figure 2.2: Example of vectorizable loop despite it not being parallel

that there is no dependency from one iteration to another in the same vectorsize frame. For example, assuming a vector size of 16, the loop in Figure 2.2 can be vectorized, even if there is technically a dependency over dimension i.

However, such a dependency could have a performance impact, as we could potentially pay for the latency of a vector instruction if we choose to look for instruction-level parallelism over the same dimension - this is explained later. Moreover, we place ourselves in a setting where all loops are either parallel or reduction loops (simple dependency from an iteration to the previous one). Therefore, it makes sense to tighten our constraints, as such skewed dependencies that would allow vectorization of non-strictly parallel loops never occur.

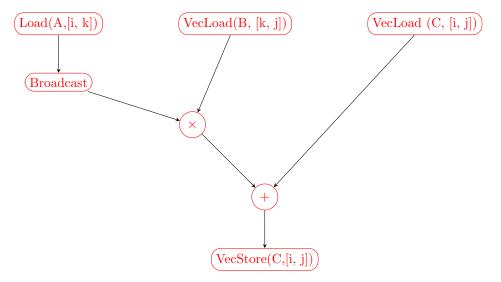

The second constraint can be relaxed if we allow ourselves scatter-gather operations, which consist in building a vector from non-contiguous elements. However, this has a performance cost. When we want to vectorize over a dimension that is not innermost for all tensors accessed, we will rely on packing, which is explained later in Section 2.1.1, which builds a new intermediate tensor with the proper layout.

Given these constraints, to make a naive matrix multiplication efficient, the first major transformation would be to do a loop exchange to bring a vectorizable loop at the inner level. Here we assume a fully permutable computation space where all loop exchanges are semantically valid. Dimensions i or j are the only candidates for vectorization, as k is not a parallel dimension. Either could be vectorized if we make sure that they are the inner dimensions of their respective matrices. This can imply some reshaping of the data in the worst case, but for now, we will assume that j is the inner dimension of both C and B, and is therefore vectorizable. Figure 2.3 shows a vectorized version of the code after permutation.

This is better but still not enough: we still have a cross-iteration dependency over the k loop. Therefore we have to pay for the latency of the fused-multiply-add instruction and we do not take advantage of instruction-level parallelism. Therefore one needs to iterate again over a parallel dimension outer of the stripmined loop. These iterations can be done over either i or j for the same reason as before. The control flow can also hinder the performance, as it makes it harder to fill the pipeline, even if branch-prediction can mitigate this to some degree on modern architectures. This is one the reasons for unrolling loops, the other being that a bigger basic block allows for more registers to be used, thus avoiding anti-dependencies. At low-level, register renaming exploits automatically the fact that there are more physical registers than the logical ones in order to break these anti-dependencies.

Again either i or j can be used. Let us assume we unroll over the i dimension.

```

for (i = 0; i < I; i++) {

\quad \text{for } (\,\mathrm{j}\,0 \,=\, 0\,; \ \mathrm{j}\,0 \,<\, \mathrm{J}\,; \ \mathrm{j}\,0 \,+\!\!=\, \mathrm{VECSIZE}) \ \{\,

for (k = 0; k < K; k++){

3

4

broadcast(v) = [v, v, v, ...]

a_i = broadcast(A[i,k]);

5

// vector loads

\label{eq:c_ij} \begin{array}{ll} c_{\,\text{-}}\mathrm{i}\,\mathrm{j} &=& \mathrm{C}\left[\,\mathrm{i}\,\,,\,\, <\!\mathrm{j}:\mathrm{j+\!VECSIZE}\!>\,\right]; \end{array}

7

8

b_k j = B[k, \langle j: j+VECSIZE \rangle];

9

// vector multiply-add

10

c_{-ij} += a_{-ik} * b_{-kj};

11

// vector store

C[i, < j: j+VECSIZE>] = c_i j;

12

13

14

}

15

```

Figure 2.3: Vectorization on j

This yields the code found in Figure 2.4.

Another subtlety hits here. The line C[i,j]+=A[i,k]\*B[k,j]; hides a series of instructions :

- a read at the address &C[i, j] into a register

- two reads at address &A[i, k] and &B[k, j]

- a multiplication followed by an addition

- a write at the address &C[i, j]

This means that the same memory address (&C[i, j]) will be loaded into a register and then stored back at each iteration of the surrounding k loop. We can avoid this by performing a transformation called scalar promotion, which consists in transforming a slice of the array into a group of variables that can be stored in registers, thus avoiding memory accesses. In this specific case, we use vector registers to do so. This is shown in Figure 2.5.

This basic block was unrolled by a factor of two for the sake of readability but in practice, the unroll factor is usually higher. The value of the unroll factor depends on both the number  $n_r$  of vector registers and the latency l of a multiply-add instruction.

GotoBLAS makes the following design choices about this microkernel: hide latency and avoid spilling entirely. The inner basic block should be unrolled enough to hide the latency, that is, after having issued an instruction *inst* enough instructions that do not depend on *inst* should be issued so that the next instruction that needs the result of *inst* will have its dependencies immediately available. But it should also be small enough so that there is no need for spilling.

This process is described in more detail in [LISQO16]. From these requirements we can derive a formal constraint: Let l be the latency of a float multiply-add instruction,  $n_r$  be the number of vector registers available. Let  $u_i$  the unroll

```

1

for (j0 = 0; j0 < J; j0 += VECSIZE) {

for (k = 0; k < K; k++) {

3

c_{-i\,j} \;=\; C[\,i\;,\; <\!j:j\!+\!\!VECSIZE\!>]\,;

b_k j = B[k, \langle j: j+VECSIZE \rangle];

5

// broadcast(v) = [v, v, v,...]

6

7

a_i = broadcast(A[i,k]);

8

c_i j += a_i k * b_k j;

9

C[i, < j: j+VECSIZE>] = c_i j;

10

11

c_i i j = C[i + 1, < j : j+VECSIZE>];

12

a_i1k = broadcast(A[i + 1,k]);

c_i1j += a_i1k * b_i;

13

C[i + 1, \langle j:j+VECSIZE \rangle] = c_i 1 j;

14

15

16

}

17 }

```

Figure 2.4: Unrolling on i

```

for (i = 0; i < I; i += 2) {

for (j = 0; j < J; j+=VECSIZE) {

2

\begin{array}{l} c_{-}00 \, = \, C[\,i\,, < j\,:\, j \, + \, VECSIZE > ]\,; \\ c_{-}10 \, = \, C[\,i \, + \, 1, < j\,:\, j \, + \, VECSIZE > ]\,; \end{array}

3

4

for (k = 0; k < K; k++) {

5

a_0k = broadcast(A[i, k]);

b_kj = B[k, \langle j:j + VECSIZE \rangle];

7

c_00 + = a_ik * b_kj;

8

9

a_1k = broadcast(A[i +1, k]);

10

c_{-}10 += a_{-}1k * b_{-}kj;

11

\begin{array}{lll} \acute{C}[\;i\; & ,\; <\!j:j{+}VECSIZE>]\; =\; c\, {}_{-}00\;; \\ C[\;i\; +\; 1\; ,\; <\!j:j{+}VECSIZE>]\; =\; c\, {}_{-}10\;; \\ \end{array}

12

13

14

15

}

```

Figure 2.5: Scalar promotion

factor on dimension i, and  $u_j$  the unroll factor on dimension j. We assume that the loop is vectorized on j, which implies that the actual footprint of the basic block over dimension j is  $u_j * VECSIZE$ . We get a pair of inequalities:

$$\begin{cases} u_i * u_j + u_j + 1 \le n_r \\ u_i * u_j \ge l \end{cases}$$

(2.1)

Of course, matrix multiplication is symmetric over matrix A and B and dimensions i and j. Therefore we could choose to vectorize dimension i instead, which would invert  $u_i$  and  $u_j$  in this system. Any choice of factors that verify these constraints is a good candidate for a microkernel. There is no guarantee that this system of inequations has at least a solution, but in practice, all architectures we work on have some. The performance penalty incurred for breaking these constraints is also architecture dependent. For example, the cost of spilling can vary from one machine to another. This will be discussed and evaluated in more detail in Chapter 4.

#### Writing microkernel: a language dilemma

When writing such a low-level piece of code, the question of the most pertinent language to use arises. Microkernels were historically written in assembly language and still are in BLIS. This is in part the reason why they were considered expert-level subjects. Assembly was chosen to put a maximum of control into the hands of the developers. This is reasonable for such sensitive code where anything can hamper performance. However, this choice could be discussed with regard to the capabilities of modern hardware which has many more facilities to transparently hide bottlenecks. For example, while developers and compilers targetting older architectures used to have the burden of accounting for memory access latency and were in charge of scheduling the program accordingly - so that memory accesses are done early enough that they are ready as soon as they are needed - the out-of-order execution implemented by Intel architectures and others can do this scheduling automatically. Hardware prefetching is another strategy that helps amortize latency by speculatively bringing data in the cache before they are explicitly needed, to make them available as soon as possible - assuming the prediction was right and they are indeed accessed soon after. That, along with other similar hardware optimizations, can question the need of programming in assembly, as this choice has impacts such as increasing development cost, hurting portability, and imposing on developer the burden of doing manually tasks otherwise well-handled by compilers such as register allocation and scalar evolution. Maintaining correctness is also a huge challenge.

In contrast, we could choose to write our microkernel directly in C, thus relying on the compiler to do the transformations needed to exploit at least vector instructions. This proved insufficient in practice: the compiler was not able to vectorize the code the way we want it to. This solution also suffers from a lack of portability across compilers and different versions of the same compilers. An alternative is to write most of the code in C with the additional help of

architecture-specific *intrinsics*. Intrinsics are special C functions that map directly to an assembly instruction. This allows forcing the vectorization scheme that yield performance while offloading other tasks such as register allocation or handling induction variables to the compiler. We will discuss the question of the impact of the compiler in more detail in Section 4.6. In conclusion, while this tradeoff was the best we found it is not completely foolproof. It happened that in cases where basic blocks were particularly long (above tens of thousands of lines of code), compilers failed to yield the expected performance, sometimes because of poor register allocation strategy. Nevertheless, it has proven reliable as long as we limit ourselves to smaller generated codes.

#### Outer-level Strategy: Packing and streaming

Implementing a suitable microkernel is not enough. While it accounts for corelevel considerations such as hardware-pipelining (by exposing instruction level parallelism) and register locality, it does not take care of the cache usage. Memory accesses latency can vary from a factor from one to hundreds depending on what level of the hierarchy the address we are accessing is located. Available bandwidth also depends on this level of access. As a reminder, cache policy is the way a given architecture will choose which cache line it is going to evict when new access is made. There are different types of strategies in this regard, the simplest and best-known one being least recently used (LRU) where the cacheline that remained untouched for the longest time is chosen to be evicted. Cache policy is often considered an industrial secret. Moreover, modern architectures incorporate many features such as hardware prefetching, complex cache replacement policies, and others. As a result, predicting cache behavior for a given program is a challenging task. As we will see in Section 5.4.2, it is actually challenging even when simplifying the cache model to the extreme (for example considering we have a perfect control over which cache line will be evicted).

Guiding principles Instead of relying on a specific cache model, BLIS simply assumes that caches work best when they are confronted with the simplest memory access patterns. Their strategy is to make sure the accesses are done in the most regular way possible. In other words, accesses done at one given level of cache should be done as much as possible in a contiguous way. The bet is that cache policies, however complex they are, are more likely to behave smoothly with such nice accesses. This is also an elegant way to retrieve some free portability: while a cache model is most likely tied to a given architecture and can become irrelevant when applied to a new one, this strategy makes as few assumptions as possible and thus can be applied largely.

In practice BLIS achieves this goal in two ways. The first one, called *stream-inq*, consists in, for every level of cache, from the inner level to outer:

1. choosing a tensor

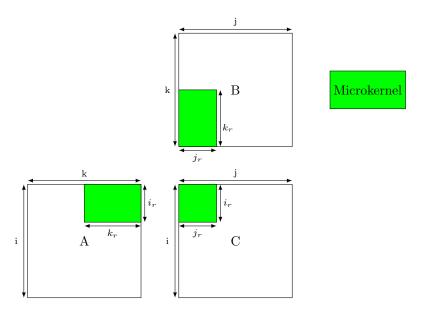

Figure 2.6: GotoBLAS tiling strategy

- 2. tile the code in such a way that the *footprint* of this tensor is close but smaller than the cache capacity of the current level

- 3. maximize reuse over this tensor and only this one

This means that at every level of cache, accesses to all tensor but one will miss. This is illustrated in Figure 2.6 for the first two levels of cache. It is worth noting that the work of Olivry and al. [OIT<sup>+</sup>21] has proven later that it is the right way to optimize the ratio of computation over communication - communication here means the volume of data that is retrieved towards the cache - we will see that in more details in Section 5.4.2.

The other strategy used by BLIS is, again, *packing*. By reshuffling the layout to make it match the iteration pattern, one makes sure that accesses done to a tensor at a given level are contiguous, which makes them hopefully prefetch-friendly and minimizes cache conflicts.

#### **BLIS**: strengths and limitations

Overall, what makes the BLIS approach stands out is that it gives a relatively simple and systematic way to build a high-performance linear algebra kernel. Besides, the separation of the low-level assembly routines and the enclosing code allows for a great composability: the low-level work can be done only once and all other applications can build on it with a high-level API. However, this flexibility comes with a price: it is the responsibility of the outer level of the code to adapt its layout to the requirements of the microkernel. As we said before, this implies data shuffling which can be somewhat awkward, especially since the microkernel size and parameters are not an easy target for transposition routines [SSB17]. This problem is exacerbated when some of the problem dimension sizes

are small, which is often the case when we deal with convolution in real-world Convolutional Neural Networks. Therefore, packing can have a cost that could be avoided otherwise and whose benefits is unclear in terms of performance. Besides, as the microkernel has a fixed size, it does not divide perfectly every possible problem size and thus the library has to do some residual work that can not be handled by the microkernel. Depending on the implementation of the partial tile and the relative size of the problem size and the microkernel, this can also hamper the performance when the partial tile execution becomes dominant.

#### 2.1.2 Tensorflow

Tensorflow [ABC<sup>+</sup>16] is one of the main computation libraries designed for machine learning networks. It exposes a fixed API of operators that let users define a dataflow graph. Contrary to other deep learning libraries such as Caffe [JSD<sup>+</sup>14], dependencies across nodes in this graph can be dynamic and depend on execution time values. As TensorFlow is embedded in several languages such as Python, JavaScript, or C++, In terms of the spectrum of implementation we presented in Section 1, this can be placed somewhere between a library and an embedded domain-specific language. The execution model of TensorFlow relies on calls to specialized linear algebra libraries such as Eigen. This limits both its flexibility and its ability to reach top-level performance, as it can not be specialized to specific problem sizes.

#### 2.1.3 Halide

Halide is a Domain Specific language embedded in C intended to help programmers design image-processing applications. Its main contribution was to decouple the algorithm (that is, the semantic specification) from the schedule - which would correspond to the operational semantic. Indeed, Halide allows users to provide a semantic skeleton that can be later completed by a *schedule* - which can be expressed as a polyhedral mapping from the iteration space to a totally-ordered set. This in turn allows a good encapsulation of the optimized part of the code - users of the library usually only care about the semantics and not about the implementation. [RBA+13]

#### 2.1.4 Polyhedral tools

**Polyhedral compilers** such as Diesel [ERR<sup>+</sup>18], Polly [GGL12], Pluto [BHRS08], PPCG [VCJC<sup>+</sup>13], Tensor Comprehensions, [VZT<sup>+</sup>19], Tiramisu [BRR<sup>+</sup>19] are able to automatically generate multi-level tiled code for affine loop nests. Diesel is a DSL for neural networks. Networks are represented internally as a directed acyclic graph and all operators are optimized together. It can also take problem sizes into account when they are known statically and optionally apply autotuning techniques. Tiramisu also exposes a custom DSL and optimizes both

dense and sparse neural networks and uses an internal polyhedral representation to do so. Contrary to Diesel, it includes a scheduling language that let users specify a particular implementation. Polly is a polyhedral optimizer integrated into LLVM, it can thus be applied to any setting that relies on LLVM. Pluto is a source-to-source compiler that performs automatic tiling and parallelization. PPCG takes a sequential C code as input and generates an equivalent parallel code for CUDA.

These tools deal with a much broader class of programs than us, as we limit ourselves to a small subset of what the polyhedral framework can express. As a result, their performance is usually several factors below what can be achieved with more specialized tools, as it is shown in [Bon20]. This is because some of the lower-level optimization needed are not easily expressed in this framework, even if they significantly outperform general-purpose compilers on naive code.

#### 2.1.5 MLIR

MLIR (Multi-Level IR) [LAB<sup>+</sup>21] is a recent effort to develop an intermediate representation that let users define *dialects* specialized for a given application, such as linear algebra. These dialects aim to bridge the gap between lower-level IR such as LLVM IR and high-level languages. They also strive to be extensible and reusable. Users can define optimization passes at dialect levels that allow to implement a GEMM (general Matrix Multiplication) with the same principles as GotoBLAS, and attain performance close to BLIS level. MLIR tries to leverage some notions from the polyhedral framework to express program transformation easily.

# 2.1.6 BOAST : Source-Source Optimization for optimizing loop structures

BOAST (Bringing Optimization through Automatic Source-to-Source Transformation) [VPG+18] is a tool developed by Videau et al. that, as hinted by its name, performs transformation at the source level to optimize loop-intensive programs. It is embedded in the Ruby programming language and as such qualifies as an embedded domain-specific language. It is a metaprogramming tool that allows users to specify their compute kernel and the way they want it to be optimized in a high-level language. As in AutoTVM, the semantics of the kernel and the optimization are separated. BOAST supports many targets such as OpenCL, CUDA, C or FORTRAN.

#### 2.1.7 TVM

TVM [CMJ<sup>+</sup>18] is a deep learning compiler that exposes a DSL to define custom operators and optimize them with an autotuning framework. It essentially gives up on finding a relevant performance analytical model. The reasoning is that given the size of the optimization space, that depends both on the semantics of the operation we are trying to optimize and microarchitectural choices, and the

fact that we can usually afford a huge training time if needed (these operations are going to run thousands if not millions of times), the problem is suited for machine learning techniques. Therefore, in the fashion of Halide, TVM offers a framework that provides a way to define a custom operator with a special semantic, completed with some primitives that help define a search strategy.

This choice amounts to moving the expertise from the compiler field to the machine learning field. However, this setup still requires some amount of compiler expertise, as defining relevant features is a quite demanding task.

As a platform, TVM provides good mechanisms that allow users to experiment with different strategies.

One of the main limitations of TVM is that they do not build on previous knowledge of optimized kernels. That means that a concept such as a microkernel has to be rediscovered by the search strategy. This in turn implies that many candidates will have to be explored before this knowledge can be rediscovered. Moreover, some degree of expertise at least is still needed to define the features that should be explored. This can cause troubles because one can be tempted to somewhat hardcode aspects that are known beforehand to be useful or to prevent some patterns known to degrade performance.

There is an improvement of TVM called AutoTVM (or Ansor) that we failed to consider properly at first. It somewhat moves toward even more automation as some choices that were hardcoded in TVM are now part of the search space, such as what we call the permutation of dimensions (defined later in Section 5.4. When used properly the results were quite impressive and improved greatly over the basic version. Analyzing these results earlier would have allowed us to improve further our optimization flow but I have to let this for future work. We will detail this part later in Section 5.4.

#### 2.1.8 Data-movement modelling: Mopt and Ioopt

As cache behavior is identified as one of the main parameters that impact performance at outer levels, it makes sense to use a model that predicts this behavior. [DZ03] is a good example of such a model: the reuse distance metrics it tries to estimate is an approximation of the number of accesses that separate two consecutive accesses to the same data.

Mopt [LSV<sup>+</sup>19] and Ioopt [OIT<sup>+</sup>21] are two other similar models. Given a schedule and a cache size, they try to predict, assuming some simplifying hypothesis on cache policy, which amount of data will be loaded towards this cache. In practice, Ioopt can provide both a lower and a higher bound on this metric. These bounds can be tight on favorable cases such as ours. As these models provide a symbolic expression they can be fed into a numerical solver that will attempt to minimize them. This assumes of course that cache effects are the bottleneck of the application, which is false if one does not take care of things such as instruction-level parallelism and vectorization. In consequence, these models can only be used in conjunction with other techniques, such as relying on a microkernel. One of our implementation attempts relies on Ioopt

to choose a tiling scheme, and as such, we describe it in more detail in Section 5.4.

On the other hand, Mopt has a corresponding implementation that exploits its model and therefore qualifies as a competitor.

## 2.2 Operators

Now we are going to define the operators we are striving to optimize. Apart from matrix multiplication we omit for brevity, we will define two of them: convolutions, which we spent most of our time optimizing, and tensor contraction. We will also see how these three operators (matrix multiplication, convolution, and tensor contraction) are actually close in terms of semantic and operational definition. This observation has been done in [ZFL18a] and has a deep consequence on the way we optimize convolution: we follow the principles set on matrix multiplication before.

#### 2.2.1 Tensor Contraction

An interesting operation we will investigate in this work is the tensor contraction, which is a generalization of a matrix multiplication of higher dimensionality. For reasons that also apply in the case of convolution, it can be optimized with the same guiding principles as matrix multiplication. Indeed, tensor contraction is a generalization of matrix multiplication, as we will show with an example.

Here is an example of tensor contraction, again with Einstein's notation:

$$Out[l1, r1, l2] + = Left[l2, k1, k2, l1] \times Right[r1, k2, k1]$$

To show the analogy with matrix multiplication, we can apply the following transpositions (permutation of indices) :

$$\begin{cases} Out[l_{1}, r_{1}, l_{2}] \Rightarrow \widehat{Out}[l_{1}, l_{2}, r_{1}] \\ Left[l_{2}, k_{1}, k_{2}, l_{1}] \Rightarrow \widehat{Left}[l_{1}, l_{2}, k_{1}, k_{2}] \\ Right[r_{1}, k_{2}, k_{1}] \Rightarrow \widehat{Right}[k_{1}, k_{2}, r_{1}] \end{cases}$$

(2.2)

followed by grouping a few dimensions together:

$$\begin{cases} l_1, l_2 \Rightarrow l_1 l_2 \\ k_1, k_2 \Rightarrow k_1 k_2 \end{cases}$$

(2.3)

This yields the following definition:

$$\widehat{Out}[l_1l_2,r_1] + = \widehat{Left}[l_1l_2,k_1k_2] \times \widehat{Right}[k_1k_2,r_1]$$

Which is matrix multiplication. Therefore a tensor contraction is a matrix multiplication modulo some reshaping. It can be implemented by a transposition followed by a call to an optimized matrix multiplication library. This

Figure 2.7: Pseudo-C code for a 2D-convolution

implementation can be improved by trying to do this transposition "on the fly" during the computation.

#### 2.2.2 Convolution

A convolution is an operation commonly used by the deep learning community. Indeed, there is a whole class of deep learning networks called *Convolutional Neural Network* (that we will call CNN from now on) that relies on this specific operation. It is a key part of all modern image recognition tools and is very compute-intensive. As a consequence, they are a major bottleneck of a lot of applications.

In Einstein's notation, a convolution operation is defined as follows:

$$O[b, h, w, k] + = I[b, h + r, w + s, c] \times K[r, s, c, k]$$

h and w are the height and width of the output image, r and s the dimensions of the sliding window, c the number of input channels, k the number of output channels, and b the size of the batch (number of images on which the network is applied in parallel). This notation is a compact way of defining tensor operations. All indices that only appear to the right of the equation are implicitly summed over. Therefore, this is equivalent to the loop nest in Figure 2.7.

Now we are going to dive into the specifics of optimizing a convolution on CPU.

#### Convolution is almost a matrix multiplication

It has been noted in literature that convolution can be viewed as a particular matrix multiplication after some dimension renaming and fusion. This is very similar to what we have shown in the previous section about tensor contraction. If we look at the definition of a matrix multiplication in Einstein's notation:

$$C[i,j] += A[i,k] * B[k,j]$$

And fuse the convolution dimensions in the following way:

$$\begin{cases} b, h, w \Rightarrow bhw \\ r, s, c \Rightarrow rsc \\ k \Rightarrow k \end{cases}$$

(2.4)

We see that our convolution becomes similar to a matrix multiplication:

$$O[bhw, k] + = \hat{I}[bhw, rsc] * K[rsc, k]$$

$\hat{I}$  is the result of applying im2col on tensor I. It is defined as:

$$\hat{I}[b][h][r][w][s][c] = I[b][h+r][w+s][c]$$

This definition makes it obvious that many elements of  $\hat{I}$  are duplicated. While this makes for a bigger footprint, it also greatly simplifies the pattern of accesses.

This reshaping is necessary for the following reasons. As the astute user would have noted, the access function of the input tensor of the convolution is slightly twisted. It turns out that I is not a 5-dimensions tensor, but a 3-dimensions tensor with a non-injective access to dimensions h and w - non-injective in the sense that for example h=0, r=1 and h=1, r=0 actually are the same slice of the tensor. This means that convolution is not strictly equivalent in terms of accesses to a matrix multiplication, and that standard matrix multiplication routines would not be semantically correct if they were applied naively. The consequence is that using a matrix multiplication routine implies a reshaping of the data in the general case - even if a smart dispatch could skip this step when appropriate for example when R=S=1. This reshaping is described in detail in [CPS06].

As a result, some of the first implementations of convolution used to just do the necessary work on input data to make them suitable to a call to a matrix multiplication library, which leverages decades of research and engineering. This is explained in [CPS06].

This reshaping is artificial in the sense that it is justified only by the fact that highly-tuned matrix multiplication libraries pre-exist convolution optimization. Re-using matrix multiplication optimization principles but not code would allow yielding much more performance and this is what has been done in further work such as [ZFL18b].

#### Focusing on Inference

Our work is focused on CPU optimization. In a real-world context, CNN applications use CPU to do inference, whereas the training is done on GPU. For inference, the goal is to reduce the latency of a single application on one input image. This means that we will assume  $a\ batch\ of\ size\ 1$  from now on and that the dimension b will be omitted.

## 2.3 Modelization of performance

Building an optimized program requires some prediction of the way the architecture will behave upon running it. Optimizing compilers incorporate several performance models to guide choices. Some of the approaches we presented could benefit from such a model. Overall, there are several axes along which a model can be placed:

- 1. Quick evaluation how long it takes to compute

- 2. Accuracy of the prediction

- 3. Explainability

- 4. Differentiability

The first one is a matter of *usability*: there is usually no point in having a model if running the model takes more time than running the program it is supposed to evaluate. The second one is how much the model correlates with the actual performance. The third one asks whether we are in a "black-box" approach or if the model tries to have clean, separable components that can be modified independently. The fourth one measures how much this model can be "reversed" if it is possible to use it to guide a search.

It is worth noting that a fully differentiable model can somewhat compensate for a slow execution if it allows to find more quickly an implementation that minimizes the metric given by the model.

The polyhedral world has proposed a few interesting techniques. A noticeable one would be the cost function used by the Pluto Heuristic implemented by Bondhugula and al.[BHRS08]. In this work, a data locality metric is used as a proxy for actual cache performance, in the same spirit as [DZ03] or [SSF+12]. Given a tile size, Pluto aims to minimize the average number of iterations between two consecutive accesses to the same address. It does it by solving for every dimension in the problem an Integer Linear Problem that maximizes data locality (for a certain definition of data locality we will not detail). As a result, the objective function of Pluto is quite good over the explainability and differentiability (it is possible to analytically derive a solution that maximizes the objective). However, the tile sizes have to be chosen manually and it can not account for multiple objectives. Some other works such as this one extend it, but try to optimize both parallelism and data locality.

As we have seen, BLIS chooses to get rid of the use of a model entirely and counts solely on the fact that a smoother pattern of accesses can (hopefully) make the cache behavior nicer.

In general, which search strategy to use and in particular whether using or not a model cannot be decided in isolation, and the tradeoff depends a lot on external constraints. Do we allow ourselves to know the size of the problem and the architecture ahead of time or not? If we want to build a tool that can provide high-performance on problem sizes and architecture that are unknown beforehand, then machine learning tools relying on training are prohibited, and any model can only be used if its cost is amortized in one run by the performance gain. On the contrary, when both problem sizes and architecture are known and available ahead of time, this opens a lot of opportunities, in term of autotuning and model alike. In this work, we mostly assume that both problem sizes and architecture are known ahead of time.

#### 2.4 Conclusion

In this chapters, we presented several things. First the operators we are going to optimize. As we have seen, they are part of the same algorithm family. Having to express this family of related but slightly different specifications motivated us to build an embedded DSL code generation framework we describe in Chapter 3. We also described the state of the art, different kinds of optimization techniques, and different tools that make use of these techniques. This in turn will come into play when we describe our own design choices in our implementation. And of course, our competitors will serve as a baseline for our evaluation in Section 6.

## Chapter 3

# Code generation

To explore a wide range of code variants, having an ergonomic way to design and test new kernels is a requirement. In particular, we want to separate the semantics and schedules of the kernel from the implementation details. Controlling data layout and reshaping is also needed. Such functionalities can be found in other frameworks, such as TVM, as mentioned previously, or Halide [RBA+13]. While Halide has its own syntax and language, TVM is directly embedded in Python. Neither of those, however, provides a sufficient level of control for our needs. Indeed, both are lacking some kind of memory layout specification, and also do not let the user specify some details such as register tiling. We preferred an explicit code generation scheme to template-based or meta-programming approaches. This code generation framework was coded in the OCaml language and benefits from some its advanced typing features.

The *iteration space* is an integer vector, taken by the loop indices enclosing a given computational statement. *Tiling* [RT99, CM95] is a loop transformation that partitions the iteration space into sets, called *tiles* and executed atomically. We only consider programs with rectangular iteration spaces and rectangular tiling. This is explained in more detail in Section 2.1.1. Tiled code has additional loops compared to the original code: loops over tiles, and loops inside a tile. This partitioning allows us to control the amount of data accessed per tile, a.k.a. *footprint*, to make sure it does not exceed a given cache capacity.

Class of programs considered We use lowercase for problem dimensions (i, j, k) for matrice multiplication, i.e. loop iterations, and uppercase to name the (possibly symbolic) upper bound on each dimension (resp. I, J, K), a.k.a. problem size. We also assume that any dimension is either parallel—i and j—or a reduction—k and all dimensions are permutable (loop interchange). While associativity can be used to parallelize a reduction, we do not exploit it.

In the class of computations we consider, a tensor may be accessed multiple times but always with the same subscript expressions, which are affine functions of surrounding loop iterators. For example, tensor A of shape  $\{i, k \mid 0 \le i < I, 0 \le k < K\}$  may be subscripted by [i, k], corresponding to the access function

$(i, j, k \mapsto i, k)$ . We also assume that a loop index cannot appear twice inside an access function: for example E[i, i] is forbidden. These conditions are satisfied by all tensor contractions and convolutions, including strided variants.

In a similar fashion, as Halide [RBA<sup>+</sup>13], our code generation takes two different inputs: the first one is a semantic description of our computation graph. The second is an implementation scheme description that specifies how vectorization, unrolling, tiling, and other implementation choices are done.

## 3.1 Computation graph

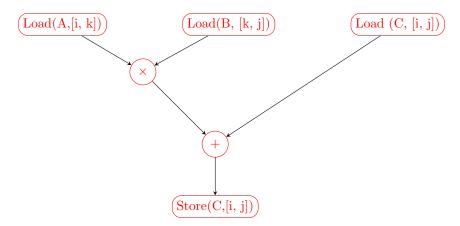

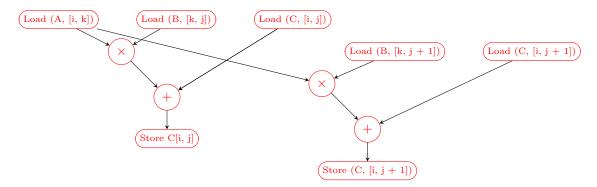

This part of the specification describes the semantics of the program we want to implement. As we said, we assume a rectangular iteration space. We first declare the dimensions we are going to use, then the tensors with their associated dimensions. Then a few primitives are provided such as Load, Store,  $\times$  or + which allow specifying a graph of computation. Input nodes are Load or constants, output nodes are Store and intermediate nodes are arithmetic operations. This specifies a basic block over which all dimensions are iterated implicitly.

**Example** We will now show the canonical example of matrix multiplications. We first declare **three dimensions** i, j, and k and **three tensors** A, B, and C with respectively indexing dimensions (i,k), (k,j), and (i,j):

```

let dim_gen = Dim. fresh_gen ()

let i_dim = dim_gen ~name:"i"

let j_dim = dim_gen ~name:"j"

~name:"k"

let k_dim = dim_gen

let a = Tensor.make

~name:"A"

[i_dim; k_dim]

let b = Tensor.make

~name: "B"

[k_dim; j_dim

let c = Tensor.make ~name:"C"

[i_dim; j_dim]

We define our basic block as follows:

let c_ij = Load (c, [index i_dim; index j_dim])

and a_ik = Load (a, [index i_dim; index k_dim])

and b_k = Load (b, [index k_dim; index j_dim]) in

let contract = Add (c_ij, Mul(a_ik, b_kj)) in

Store (contract, c, [index i_dim; index j_dim])

This reads as:

1. Load C[i,j] into c_{ij};

2. Load A[i, k] into a_{ik};

3. Load B[k,j] into b_{kj};

4. Compute c_{ij} + a_{ik} * b_{kj};

```

5. Store the result into C[i, j].

By default, accesses to tensors are linearized. For example, Load(c, [indexi; indexj]) is translated at code generation time into : C[i\*J+j, with J the size of dimension j. To support the specific access pattern of convolution, an additional ad-hoc constructor is added for tensors. We can "join" two dimensions together inside a tensor :

```

let input = Tensor.make ~name:"Input" [Join(w, r), Join(h, s), c]

Then an access to tensor Input such as: let input_ld = Load(input, [index w, index r, index h, index s, index c] ) will be translated as input[(w+r)*C*(H+S-1)+(h+s)*C+c].

```

#### 3.2 Atoms

Our code generator is driven by a so-called *optimization scheme*. An optimization scheme is a list of *atoms* that describe the layered structure of the generated code, *from the outermost loop inwards*. We first present briefly all of these atoms and their semantics. The next section will illustrate their use by example.

- $R_d$  inserts the outer loop along dimension d. This loop will iterate over the outer-level tiles along d. the problem size D should be divided by the sizes of these tiles. Besides,  $R_d$  may appear at most once for a given dimension d.

- $V_d$  virtually inserts a tile loop with  $T_{v,d}$  where v the vector length then vectorizes it. Vectorization occurs at the innermost level only: there may be at most one  $V_{\bullet}$ .

- $T_{\alpha,d}$  inserts a tile loop along dimension d. It iterates exactly  $\alpha$  times along d. Again,  $\alpha$  must divide the size of the iteration space along d.

- $U_{\alpha,d}$  virtually inserts a tile loop with  $T_{\alpha,d}$  then fully unrolls it (register tile). The divisibility constraint holds.

- $U\lambda_d$  inserts a parametrized unroll: there will be multiple instantiations of this unroll with different values. This atom assumes the use of  $\lambda_{\mathsf{seq}_d}$ .  $[\ell]$  at an outer position.

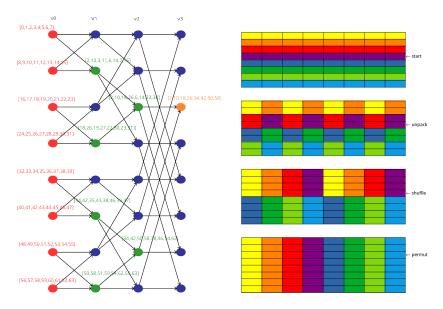

- $\lambda_{\text{seq}_d}$ .  $[\ell]$ , where  $\ell = [(r_i, a_i)]_{1 \leq i < s}$  is a list of  $s \geq 2$  pairs introducing a sequence of s loops of size  $r_i$  along dimension d. Each one iterates over next-level tiles, defining parameter  $\alpha = a_i$  for the atom introducing these tiles. This specifier generates non-perfectly nested tiles, composing

microkernels whose sizes do not individually divide the size of a given dimension. For example, splitting a dimension y of size Y = 34 into two non-equal parts 22 and 12 with  $\ell = [(2,11),(1,12)]$  fulfills the divisibility constraint (no partial tiles) while involving high-performance microkernels of size 11 and 12 along y.

- $\mathsf{Texct}_{\alpha,d}$  inserts a tile loop that has a footprint of exactly  $\alpha$ , regardless of multiplicity. It implies that the inner tile loops on dimension d have a parametrizable size, which is enabled either by the  $\mathsf{Tvar}_{\alpha,d}$  or the  $\mathsf{ExternalCall}_{name,\alpha,d}$  atoms.

- ScalP[ $d_0, d_1, ...$ ] takes all tensor accesses inside the current tile that do not include any dimension in [ $d_0, d_1, ...$ ], and move these accesses out of the loop.

- $\mathsf{Pack}_A$  introduces a temporary buffer that corresponds to the subset of A that is accessed in the inner levels of the loop nest at this level of the scheme.

- $\mathsf{PackT}_A[ell]$  is similar to  $\mathsf{Pack}_A$  but in addition performs a permutation of dimensions over the buffer specified by ell.