# Réalisation et optimisation d'un circuit de récupération d'horloge et de données basé sur le principe de verrouillage par injection d'oscillateur en anneau ciblant les technologies nanométriques et destiné à des applications spatiales

Dorian Vert

### ▶ To cite this version:

Dorian Vert. Réalisation et optimisation d'un circuit de récupération d'horloge et de données basé sur le principe de verrouillage par injection d'oscillateur en anneau ciblant les technologies nanométriques et destiné à des applications spatiales. Electronique. Université de Bordeaux, 2022. Français. NNT: 2022BORD0333. tel-04077562

### HAL Id: tel-04077562 https://theses.hal.science/tel-04077562

Submitted on 21 Apr 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE

### POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

## L'UNIVERSITÉ DE BORDEAUX

# ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ ÉLECTRONIQUE

### Par Dorian VERT

Réalisation et optimisation d'un circuit de récupération d'horloge et de données basé sur le principe de verrouillage par injection d'oscillateur en anneau ciblant les technologies nanométriques et destiné à des applications spatiales

Sous la direction de : Jean-Baptiste BEGUERET

Soutenue le 6 Décembre 2022

### Membres du jury:

M. TARIS Thierry Professeur Université de Bordeaux Président Université de Toulon M. BARTHELEMY Hervé Professeur Rapporteur Professeur Université de Toulouse M. DUBUC David Rapporteur Université de Bordeaux M. BEGUERET Jean-Baptiste Professeur Directeur de thèse M. PIGNOL Michel Ingénieur **CNES** Examinateur Ingénieur Thales Alenia Space M. LEBRE Vincent Examinateur M. MOUTAYE Emmanuel Ingénieur Docteur Thales Alenia Space Invité Mme MALOU Florence Ingénieur **CNES** Invitée

Titre: Réalisation et optimisation d'un circuit de récupération d'horloge et de données basé sur le principe de verrouillage par injection d'oscillateur en anneau ciblant les technologies nanométriques et destiné à des applications spatiales

### Résumé:

L'explosion du trafic des données au sein des systèmes de communication actuels impliquent la nécessité d'optimiser de multiples paramètres tels que le débit, la consommation, l'intégration et le coût. Bien que l'intégration et le coût soient étroitement liés, ceux du débit et de la consommation requièrent quant à eux la définition d'un compromis optimisé.

En effet, cette volonté d'augmentation des débits de fonctionnement conduit intuitivement à une élévation de la consommation. Pour cela, les systèmes de communication numérique à lien série, largement répandus pour les transmissions de données au niveau des systèmes sur puce (SoC), de puce à puce (chip-to-chip), ou encore de carte à carte sont aussi connus sous le nom de Sérialisateur/Désérialisateur (SerDes) et font l'objet de développement de nouvelles architectures optimisées. Ces systèmes, brièvement illustrés dans notre étude, se basent sur l'utilisation d'un émetteur générant les séquences de données, d'un récepteur dont l'objectif est de récupérer correctement celles-ci et d'un canal de liaison reliant ces deux parties. En vue d'effectuer une récupération des données optimale, la présence d'un bloc critique dans la partie réceptrice intitulé circuit de récupération d'horloge et de données (CDR) est requise.

Néanmoins, les pertes introduites par le canal de liaison, le fonctionnement à des débits très élevés exposant les circuits à des interférences inter-symboles, l'environnement et bien d'autres effets constituent ensemble des potentielles sources de dégradations à la réception des données. Dans notre cas, nous nous intéresserons au paramètre de l'environnement auquel est soumis le circuit électronique et plus particulièrement celui du spatial. En effet, les diverses particules radiatives constituent des sources de potentielles dégradations influençant le fonctionnement des circuits électroniques s'étendant du système complet au transistor même.

Dans ce contexte, la conception et l'optimisation d'un circuit de récupération d'horloge et de données fonctionnant à très haut débit (60 Gb/s) et destiné à des applications spatiales est présenté. Afin de remédier aux éventuelles dégradations induites par cet environnement spatial, nous présenterons quelques techniques de durcissement quant à celui-ci. Des efforts d'optimisation en termes d'efficacité énergétique, de densité d'intégration ainsi que de jitter sont adressés par divers moyens tel que le mécanisme de synchronisation par injection. Ce principe accorde une amélioration drastique du bruit de phase et jitter. Bien que la plupart des synthétiseurs de fréquence repose sur l'utilisation d'oscillateur à résonateur LC pour leur supériorité inhérente en termes de bruit de phase, ceux-ci présentent en contrepartie une densité d'intégration bien inférieure à celle de leurs concurrents : les oscillateurs en anneau.

Cette étude s'est déroulée de la façon suivante : un premier circuit type preuve-de-concept en technologie bas coût (180 nm) et ciblant une fréquence de fonctionnement de 3.2 GHz est introduite en vue de valider par mesures l'efficacité de notre architecture. Ces résultats-là s'étant montrés relativement probants, un second circuit s'inspirant du premier, ciblant un très haut débit de fonctionnement (60 Gb/s) et dans une technologie plus agressive (28 nm FDSOI) est ensuite exposé.

Enfin, la fin de ce travail se conclut sur la discussion de quelques perspectives à investiguer en vue d'approfondir l'optimisation de certaines performances.

### Mots clés :

Circuit de récupération d'horloge et de données, Système de communication numérique à lien série, SerDes, Spatial, Verrouillage par injection, oscillateur en anneau.

# Title: Realization and optimization of a Clock and Data Recovery ring oscillator injection-locked based targeting nanometric technologies for space applications

### **Abstract:**

The data traffic exponential growth in actual communication systems requires the optimization of several parameters such as data rate, consumption, area and cost. Although the integration and the cost are closely related, data rate and consumption require the definition of an optimized compromise.

Indeed, these ever-increasing data rates intuitively lead to a consumption increase. To this end, serial link communication systems, widely used in data transmission for Systems on Chip (SoC), chip-to-chip and board-to-board which are also known as Serializer/Deserializer (SerDes) systems result in the development of new optimized architectures. Those systems, briefly introduced in our study, are based on the use of an emitter part for the generation of data patterns, a receiver part for the data recovery and a channel linking them. To get a correct data recovery, the presence of a critical block in the receiver part called clock and data recovery (CDR) circuit is required.

Nevertheless, insertion losses introduced by the channel, high data rates exposing circuits to inter-symbol interferences (*ISI*), the environment and many other parameters represent potential causes of decay for correct recovery data stream. In our case, we will only be interested in the space environment parameter under which our circuit would be exposed. Indeed, various radiative particles establish sources of potential degradations which would impact the correct operation both at system and transistor levels.

In this context, the design and optimization of a clock and data recovery operating at very high rate (60 Gbps) and aiming space applications is presented. In order to rectify possible deteriorations caused by the space environment, we will present some hardening techniques to prevent it. Several endeavors to optimize the power efficiency, the integration density and the jitter are tackled through various ways such as the synchronization by injection-locking. This method allows a drastic enhancement of the phase noise and jitter. Even if most of the frequency synthesizers hinge on the use of LC tank oscillator due to its inherent superiority in terms of phase noise, that one present in return an integration density much lower than its counterpart: the ring oscillator.

This study has been led the following way: a first proof-of-concept circuit in 180 nm technology targeting an operating frequency of 3.2 GHz is introduced for the purpose of the validation of our circuit efficiency by measures. Those results showed satisfying performances. A second circuit inspired from the architecture of the first one and aiming a very high data rate (60 Gbps) in a more recent technology (28 nm FDSOI) is then exposed.

Eventually, the end of this work concludes on the discussion of several prospects to investigate in order to deepen the optimization of some performances to upgrade our full system.

### **Keywords:**

Clock and Data Recovery, Serial link communication systems, SerDes, Space, injection-locking, Ring oscillator.

### Unité de recherche

Université de Bordeaux, Laboratoire IMS, CNRS UMR 5218, Bordeaux INP, 351 cours de la Libération, 33405 Talence

# Table des matières

| 1. Intro | oduction générale                                                 | 20   |

|----------|-------------------------------------------------------------------|------|

| 2. Intro | oduction aux systèmes de récupération d'horloge et de données     | 23   |

| 2.1. In  | ntroduction au contexte                                           | 23   |

| 2.2. O   | Origines, effets et techniques de durcissement aux radiations     | 24   |

| 2.2.1.   |                                                                   |      |

| 2.2.2.   |                                                                   |      |

| 2.2.3.   | _                                                                 |      |

| 2.3. C   | Concepts de bases dans les systèmes de communication              | 30   |

| 2.3.1.   | - · · · · · · · · · · · · · · · · · · ·                           |      |

| 2.3.2.   |                                                                   |      |

| 2.4. T   | ypes de modulation                                                | 33   |

| 2.4.1.   | • •                                                               |      |

| 2.4.2.   |                                                                   |      |

| 2.4.3.   | Duobinary                                                         | 36   |

| 2.5. N   | Tétriques usuelles pour les circuits de communication             | 37   |

| 2.5.1.   |                                                                   |      |

| 2.5.2.   |                                                                   |      |

| 2.5.3.   | Diagramme de l'œil                                                | 41   |

| 2.5.4.   | Taux de Bits Erronés (BER)                                        | 42   |

| 2.6. E   | tat-de-l'art des circuits de récupération d'horloge et de données | 45   |

| 2.6.1.   | Types de CDR                                                      | 46   |

| 2.7. T   | opologies Half & Quarter rate                                     | 50   |

| 2.8. C   | Comparaison des circuits de CDR de l'état-de-l'art                | 50   |

| 2.9. C   | Conclusion du chapitre                                            | 52   |

|          | sibliographie                                                     |      |

| 2.10. D  | ionogi apme                                                       | , 33 |

| 3. Con   | ception des blocs critiques                                       | 58   |

| 3.1. D   | Oélai réglable                                                    | 58   |

| 3.1.1.   |                                                                   |      |

| 3.1.2.   | 1                                                                 |      |

| 3.1.3.   |                                                                   |      |

| 3.2. O   | Oscillateur contrôlé en tension (VCO)                             | 63   |

| 3.2.1.   |                                                                   |      |

| 3.2.2.   | ••                                                                |      |

| 3.2.3.   |                                                                   |      |

| 3.3. O   | Oscillateur verrouillé par injection                              | 69   |

| 3.3.1.   |                                                                   |      |

| 3.3.2.   | Méthodes d'injection                                              |      |

| 3.3.3.     | Bloc d'injection proposé                                 | 74            |

|------------|----------------------------------------------------------|---------------|

| 3.4. Bo    | oucle à verrouillage de phase                            | 76            |

| 3.4.1.     | Principe                                                 |               |

| 3.4.2.     | Caractérisation d'une boucle à verrouillage de phase     | 77            |

| 3.5. Co    | omparateur de phase et filtre de boucle                  | 78            |

| 3.5.1.     | Principe                                                 |               |

| 3.5.2.     | Détermination du filtre de boucle                        |               |

| 3.5.3.     | Types de comparateur phase/fréquence                     |               |

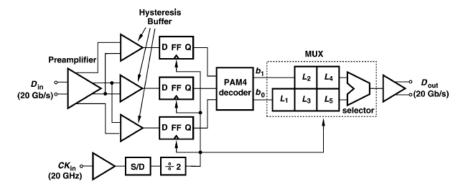

|            | écodeur PAM4                                             |               |

| 3.6.1.     | Principe                                                 |               |

| 3.6.2.     | Types de décodeur PAM4                                   |               |

| 3.6.3.     | Décodeur PAM4 proposé                                    | 83            |

| 3.7. Ré    | écupération de données                                   |               |

| 3.7.1.     | Principe de récupération de données                      |               |

| 3.7.2.     | Types de circuits à récupération de données              |               |

| 3.7.3.     | Bloc de récupération de données proposé                  | 87            |

| 3.8. Co    | onclusion du chapitre                                    | 87            |

| 3.9. Bi    | bliographie                                              | 89            |

|            |                                                          |               |

| 4. Conc    | eption de la preuve-de-concept à 3.2 GHz en technolo     | gie 180 nm 93 |

| 4.1. Vu    | ue d'ensemble de la technologie                          | 93            |

| 4.1.1.     | Technologie 180 nm                                       |               |

| 4.1.2.     | Dimensionnement au niveau transistor                     |               |

| 4.1.3.     | Optimisation au niveau layout                            | 98            |

| 4.2. Os    | scillateur en anneau verrouillé par injection            | 99            |

| 4.2.1.     | Architecture et aperçu de la puce                        | 100           |

| 4.2.2.     | Mesures                                                  | 100           |

| 4.3. Bo    | oucle à verrouillage de phase synchronisée par injection | 108           |

| 4.3.1.     | Architecture et aperçu de la puce                        | 108           |

| 4.3.2.     | Mesures                                                  |               |

| 4.3.3.     | Comparaison à l'état-de-l'art                            | 114           |

| 4.4. Co    | onclusion du chapitre                                    | 117           |

| 4.5. Bi    | bliographie                                              | 118           |

|            |                                                          |               |

| 5. Conc    | eption du circuit de récupération d'horloge et de don    | nées à 60     |

| Gb/s en to | echnologie 28nm FDSOI                                    | 121           |

| 5.1. Vu    | ue d'ensemble de la technologie 28 nm FDSOI              | 121           |

| 5.1.1.     | Front-End Of Line                                        |               |

| 5.1.2.     | Back-End Of Line                                         |               |

| 5.2. M     | éthode de design niveau transistor                       | 123           |

|            | Détermination de la densité de courant optimale          |               |

| 5.2.        | 2. Optimisation layout                                      | 124 |

|-------------|-------------------------------------------------------------|-----|

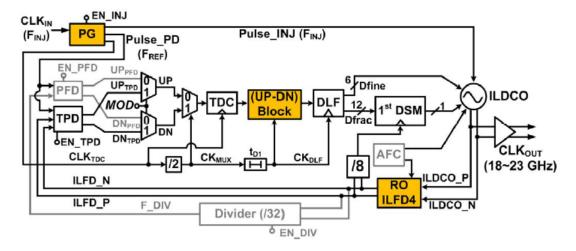

| 5.3.        | Conception Full Rate NRZ CDR                                | 126 |

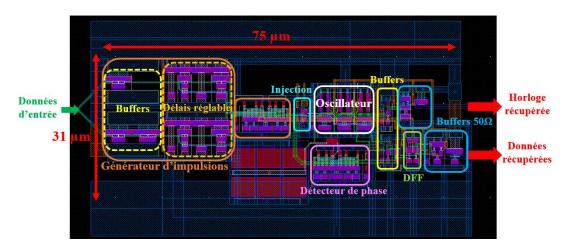

| 5.3.        | 1. Architecture et layout                                   | 126 |

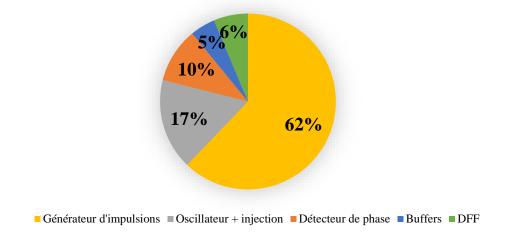

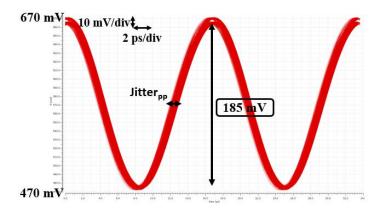

| 5.3.        | 2. Résultats de simulations post-layout                     | 130 |

| 5.3.        | 3. Comparaison à l'état-de-l'art                            | 132 |

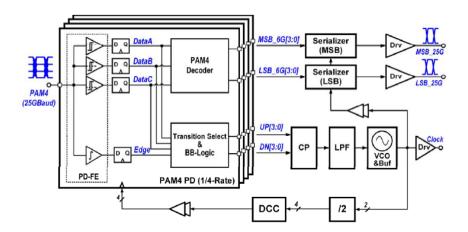

| <b>5.4.</b> | Conception Full Rate PAM4 CDR                               | 134 |

| 5.4.        | 1. Architecture et layout                                   | 134 |

| 5.4.        | 2. Résultats de simulations                                 | 135 |

| 5.4.        | 3. Présentation de l'état-de-l'art des circuits de CDR PAM4 | 136 |

| 5.5.        | Conclusion du chapitre                                      | 138 |

| 5.6.        | Bibliographie                                               | 139 |

| 6. Co       | nclusion générale                                           | 142 |

| 7. Per      | spectives                                                   | 146 |

| 7.1.        | Optimisation de la méthode d'injection                      | 146 |

| 7.2.        | Optimisation de la récupération de données                  | 149 |

| 7.3.        | Optimisation par topologie half/quarter rate                | 150 |

| 7.4.        | Bibliographie                                               | 152 |

# Liste des Tableaux

| Tableau 2-1: Détermination du facteur en fonction du BER requis [28]                    | 41     |

|-----------------------------------------------------------------------------------------|--------|

| Tableau 2-2 : Récapitulatif de l'état-de-l'art des circuits de CDR de modulation PAM4   | et NRZ |

|                                                                                         | 51     |

| Tableau 4-1 : Récapitulatif des performances mesurées de l'oscillateur avec et sans     |        |

| synchronisation par injection                                                           | 108    |

| Tableau 4-2 : Comparaison des performances mesurées de la PLL sans vs avec              |        |

| synchronisation par injection                                                           | 112    |

| Tableau 4-3: Comparaison des performances à l'état-de-l'art                             | 114    |

| Tableau 5-1: Détermination du ratio multiplicateur en fonction du BER requis [6]        | 131    |

| Tableau 5-2 : Comparaison des résultats à l'état-de-l'art des circuits de CDR de modula | tion   |

| NRZ                                                                                     | 133    |

| Tableau 5-3 : Comparaison des circuits de CDR PAM4 de l'état-de-l'art                   | 136    |

# Liste des Figures

| Figure 2-1 : Vue d'ensemble d'un système SerDes                                                 | 23  |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 2-2 : Diagramme en bande des processus physiques lors de l'irradiation d'une structu     | ure |

| MOS [6]                                                                                         |     |

| Figure 2-3: Formation d'un transistor parasite à proximité d'un bec d'oiseau [4]                | 26  |

| Figure 2-4 : Création d'un courant transitoire dans une jonction PN [4]                         |     |

| Figure 2-5 : Effets de funneling sur les technologies Bulk CMOS et Epi CMOS [4]                 |     |

| Figure 2-6: Vue de coupe des technologies (a) Bulk et (b) SOI [8]                               |     |

| Figure 2-7 : Durcissement par découplage résistif [9]                                           |     |

| Figure 2-8 : Durcissement par redondance triple [4]                                             |     |

| Figure 2-9 : Spectres en fréquence du VCO sous radiations (a) sans verrouillage par injecti     |     |

| (b) avec verrouillage par injection                                                             |     |

| Figure 2-10 : Densité de transition faible d'une séquence binaire aléatoire                     | 31  |

| Figure 2-11 : Spectre fréquentiel de données aléatoires [14]                                    |     |

| Figure 2-12 : Chronogrammes de signaux modulés NRZ et RZ [15]                                   |     |

| Figure 2-13 : Comparaison des spectres de modulations (a) NRZ et (b) RZ                         |     |

| Figure 2-14 : Comparaison de la consommation de bande passante d'un signal NRZ vs PAI           |     |

|                                                                                                 |     |

| Figure 2-15 : Comparaison des spectres en puissance d'un signal de modulation NRZ vs            |     |

| PAM4 [16]                                                                                       | 35  |

| Figure 2-16 : Comparaison de la densité spectrale de la modulation NRZ vs Duobinary [20         |     |

| Figure 2-17 : Comparaison des diagrammes de l'œil et spectres respectifs des modulations        | -   |

| NRZ vs PAM4 vs Duobinary [21]                                                                   | 37  |

| Figure 2-18 : Catégories de jitter [27]                                                         |     |

| Figure 2-19 : (a) Représentation temporelle d'une séquence binaire aléatoire et (b) Découpa     |     |

| de cette séquence par segments de temps et diagramme de l'œil résultant de la superpositio      | _   |

| de ces segments                                                                                 |     |

| Figure 2-20 : Diagrammes de l'œil d'un signal de modulation NRZ vs PAM4 [19]                    | 42  |

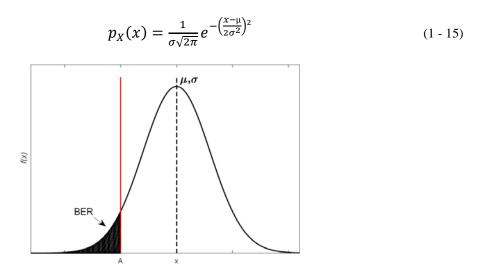

| Figure 2-21 : Distribution aléatoire Gaussienne et BER                                          |     |

| Figure 2-22 : PDF d'un signal PAM4 [19]                                                         | 44  |

| Figure 2-23 : Rôle d'une CDR dans le rééchantillonnage des Données                              |     |

| Figure 2-24 : Schéma bloc du circuit de CDR PAM4 basé sur le principe d'une PLL [31]            |     |

| Figure 2-25: Comparaison d'une structure CDR (a) PLL et (b) DLL [40]                            |     |

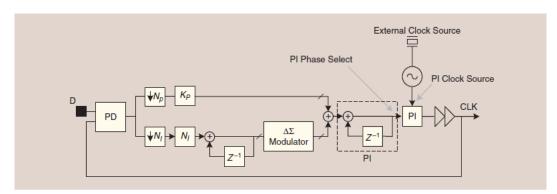

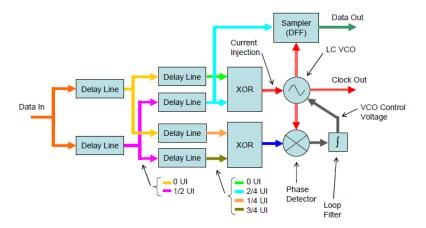

| Figure 2-26 : CDR digitale basé sur le principe d'interpolation de phase [37]                   |     |

| Figure 2-27 : CDR GRO classique [15]                                                            |     |

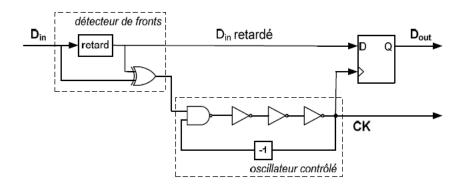

| Figure 2-28 : Exemple d'une CDR ILO [51]                                                        | 50  |

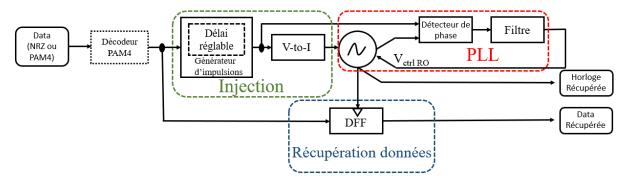

| Figure 3-1 : Schéma bloc de l'architecture générale du circuit                                  |     |

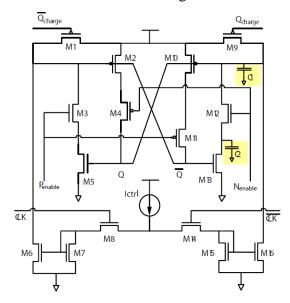

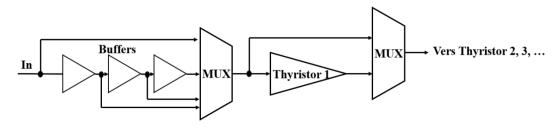

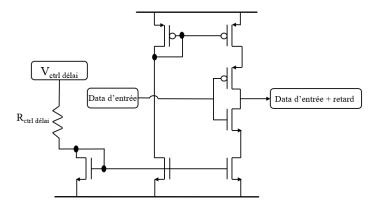

| Figure 3-2 : Cellule de délai CMOS proposée                                                     |     |

| Figure 3-3 : Ligne de délai variable basée sur un CMOS thyristor                                |     |

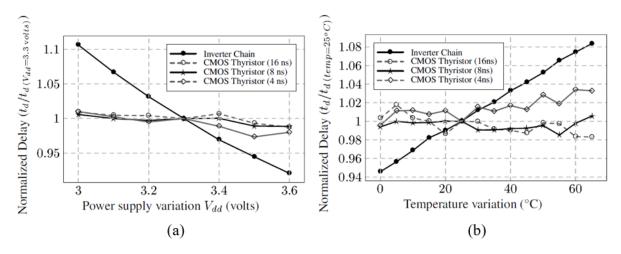

| Figure 3-4 : Comparaison de la variation du délai par rapport à (a) une variation               |     |

| d'alimentation, (b) une variation de la température pour une chaîne d'inverseurs versus         |     |

| thyristors CMOS                                                                                 | 60  |

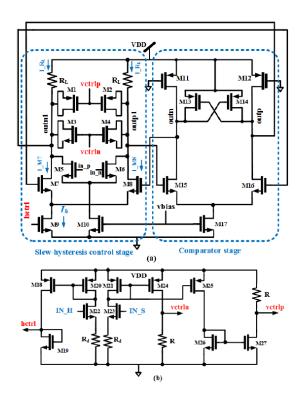

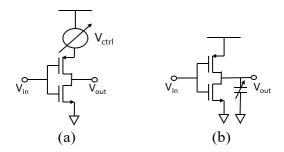

| Figure 3-5 : Cellule HCMLD proposée (a), Contrôle de délai correspondant (b)                    |     |

| Figure 3-6 : Cellule de délai réglable proposée                                                 |     |

| Figure 3-7 : Résultats de simulation pour une variation de délai $0.7V < V_{ctrl délai} < 1.2V$ |     |

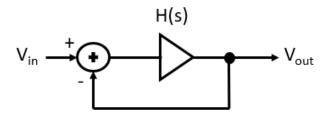

| Figure 3-8 : Système à contreréaction négative                                                  | 63  |

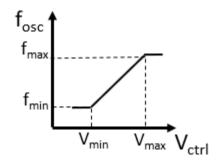

| Figure 3-9 : Allure caractéristique de la fréquence de sortie d'un oscillateur en fonction de s             | a   |

|-------------------------------------------------------------------------------------------------------------|-----|

| tension de contrôle                                                                                         | 64  |

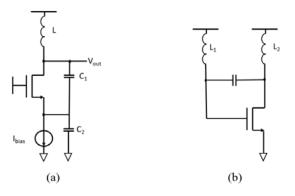

| Figure 3-10 : Oscillateur à résonnateur LC Colpitts (a), Hartley (b)                                        | 64  |

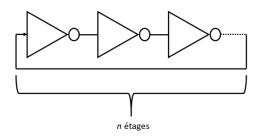

| Figure 3-11 : Exemple d'un oscillateur en anneau à n étages d'inverseurs                                    | 65  |

| Figure 3-12 : Oscillateur en anneau à trois étages                                                          | 65  |

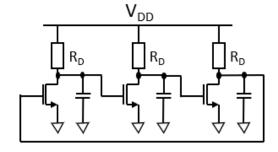

| Figure 3-13 : Méthodes de réglage de la fréquence par variation (a) du gm, (b) du varactor                  | 67  |

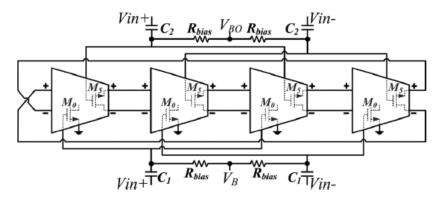

| Figure 3-14 : Architecture complète de l'oscillateur en anneau réalisé                                      | 67  |

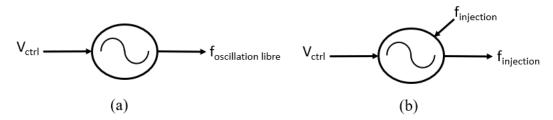

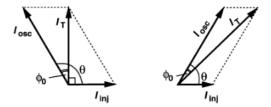

| Figure 3-15 : (a) Oscillateur en oscillation libre, (b) Oscillateur verrouillé par injection                |     |

| Figure 3-16 : (a) Oscillateur à résonnateur LC, (b) Fréquence décalée suite à un décalage de                |     |

| phase, (c) Caractéristiques en boucle ouverte et (d) Décalage de fréquence par injection [7]                |     |

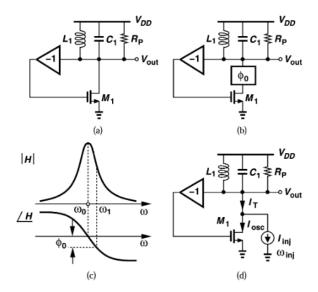

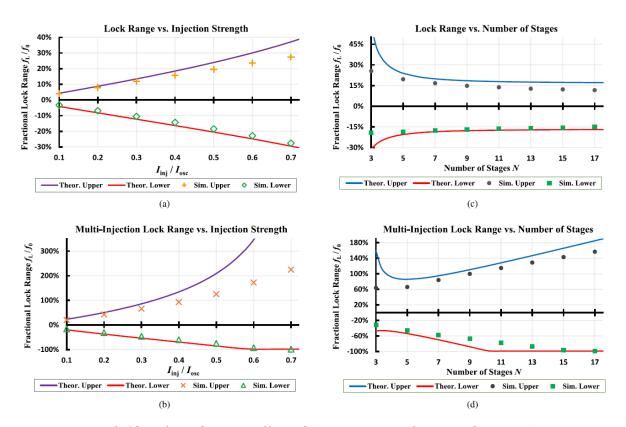

| Figure 3-17 : Différence de phases pour deux valeurs de $\omega inj - \omega 0$ et $I_{inj}$                |     |

| Figure 3-18 : Plage de verrouillage théorique vs simulée pour divers scénarii                               |     |

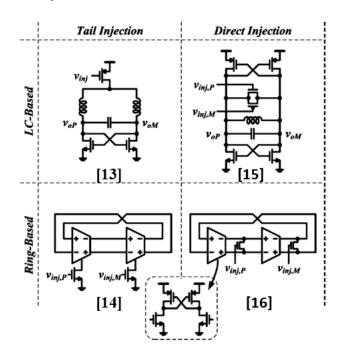

| Figure 3-19 : Différents types de méthodes d'injection selon le type d'oscillateur [12]                     |     |

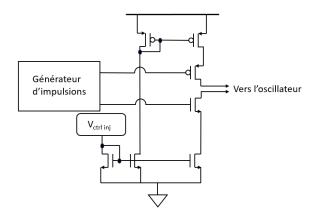

| Figure 3-20 : Oscillateur en anneau verrouillé par injections d'impulsions proposé (PILFM)                  |     |

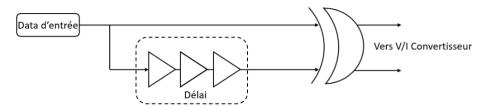

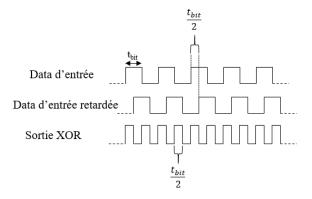

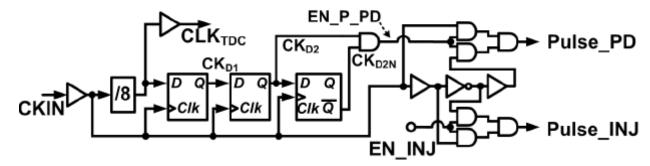

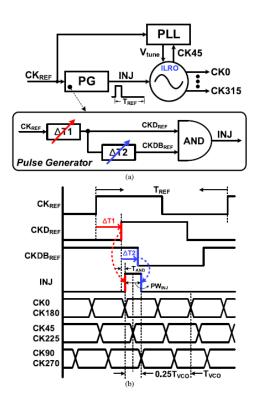

| Figure 3-21 : Générateur d'impulsions proposé                                                               |     |

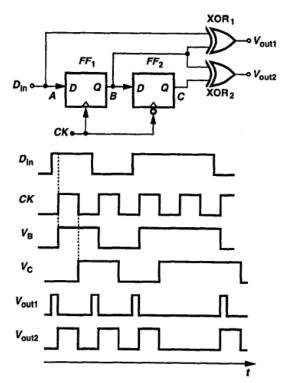

| Figure 3-22 : Chronogramme du générateur d'impulsions                                                       |     |

| Figure 3-23 : Convertisseur de tension en courant réglable                                                  |     |

| Figure 3-24 : Simple boucle à verrouillage de phase                                                         |     |

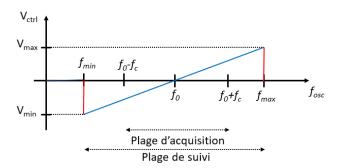

| Figure 3-25 : Illustration de la plage d'acquisition et de suivi de la boucle à verrouillage de             |     |

| phase                                                                                                       |     |

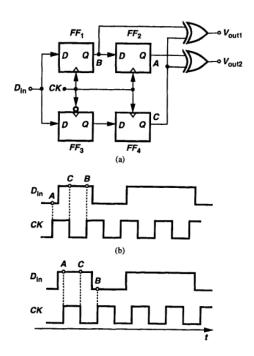

| Figure 3-26 : Comparateur de phase type Alexander                                                           |     |

| Figure 3-27 : Comparateur de phase type Hogge                                                               |     |

| Figure 3-28 : Comparateur de phase XOR différentiel                                                         |     |

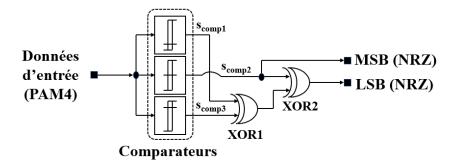

| Figure 3-29 : Bloc de réception PAM4                                                                        |     |

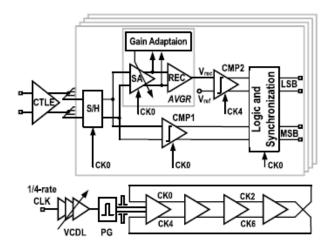

| Figure 3-30 : Décodeur PAM4 basé sur un AVGR                                                                |     |

| Figure 3-31 : Décodeur PAM4 proposé                                                                         |     |

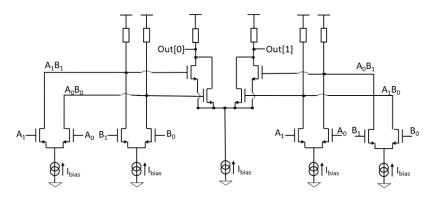

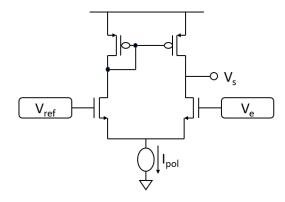

| Figure 3-32 : Comparateur pour décodeur PAM4 proposé                                                        |     |

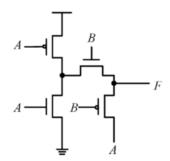

| Figure 3-33 : Porte logique OU Exclusif                                                                     |     |

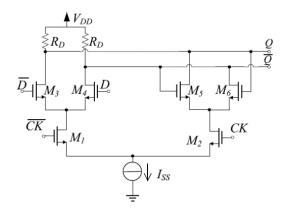

| Figure 3-34 : Bascule D Master/Slave Conventionnelle [34]                                                   |     |

| Figure 3-35 : DFF avec contreréactions positives [35]                                                       |     |

| Figure 3-36 : Diagrammes de l'œil du circuit de CDR : (a) Entrée du Détecteur de Phase avoir                |     |

| DFF en contreréactions et (b) Données récupérées en sortie du système [35]                                  |     |

| Figure 4-1 : Layout d'un transistor unitaire                                                                |     |

| Figure 4-2 : Dépendance de (a) f <sub>t</sub> et (b) f <sub>max</sub> en fonction du nœud technologique [3] |     |

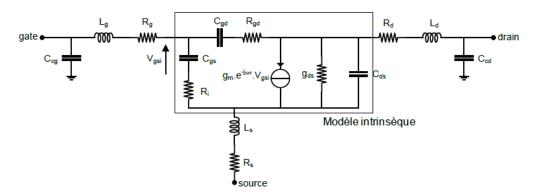

| Figure 4-3 : Schéma petit-signal d'un transistor MOS représenté avec ses parasites                          |     |

| intrinsèques et extrinsèques [4]                                                                            | .95 |

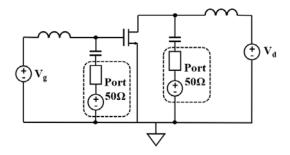

| Figure 4-4 : Schématique du testbench réalisé                                                               |     |

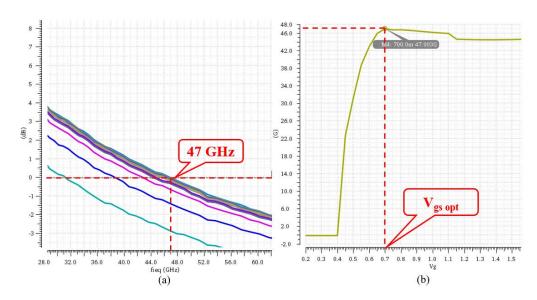

| Figure 4-5 : (a) Estimation de f <sub>t</sub> et (b) détermination de V <sub>gs opt</sub>                   |     |

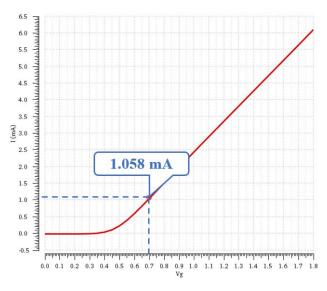

| Figure 4-6 : Détermination de la densité de courant optimale                                                |     |

| Figure 4-7 : Technique de robustesse aux radiations (ELT) d'un inverseur CMOS                               |     |

| Figure 4-8 : Schématique de l'oscillateur en anneau                                                         |     |

| Figure 4-9 : Photographies de la puce du VCO synchronisé par injection                                      |     |

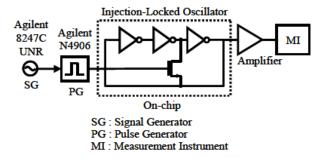

| Figure 4-10 : Synoptique du banc de test de l'oscillateur en anneau non synchronisé                         |     |

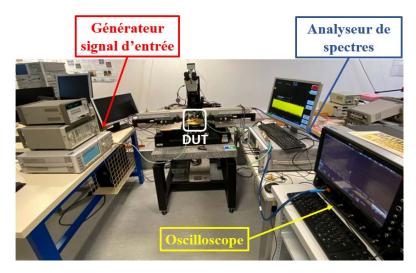

| Figure 4-11: Banc de tests des mesures                                                                      |     |

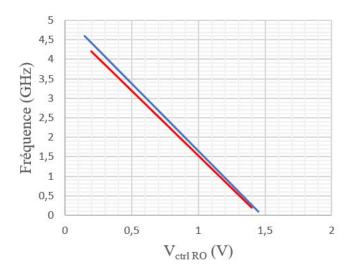

| Figure 4-12 : Comparaison des plages de contrôle : simulée (bleu) et mesurée (rouge)                        |     |

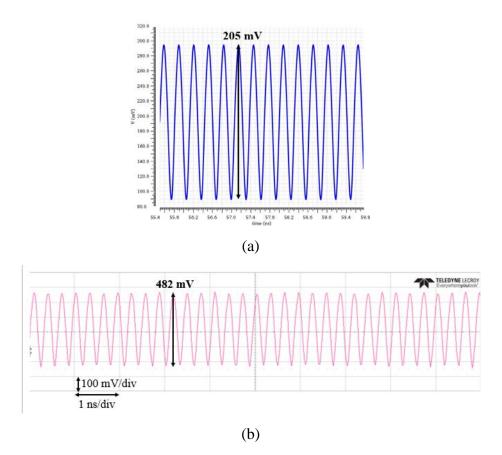

| Figure 4-13 : Allures temporelles du signal de sortie de l'oscillateur non verrouillé oscillant             |     |

|                                                                                                             | 103 |

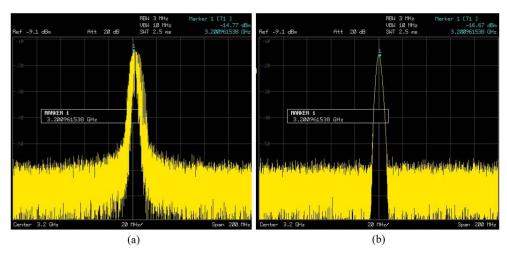

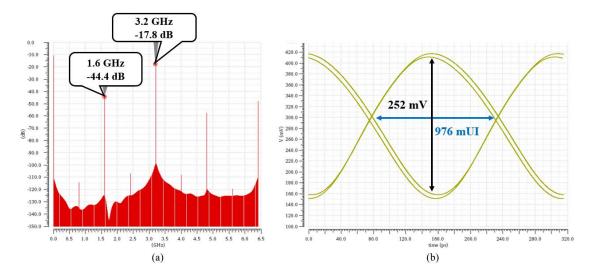

| Figure 4-14 : Comparaison du spectre en fréquence du VCO (a) sans injection et (b) avec           |     |

|---------------------------------------------------------------------------------------------------|-----|

| injection                                                                                         | 103 |

| Figure 4-15 : Bruit de phase de l'oscillateur non synchronisé (a) simulé et (b) mesuré            | 104 |

| Figure 4-16 : Bruit de phase de l'oscillateur injecté (a) simulé et (b) Comparaison du bruit o    | de  |

| phase de l'oscillateur synchronisé mesuré (jaune) vs le signal de référence (vert)                | 106 |

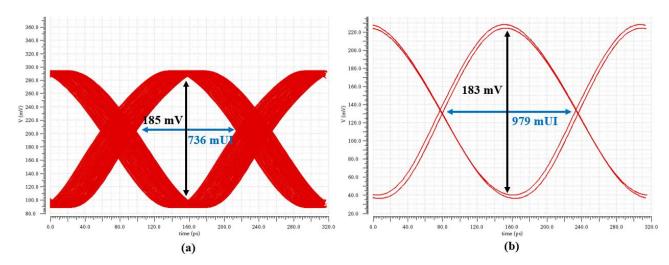

| Figure 4-17 : Résultats de simulation post-layout du diagramme de l'œil de l'oscillateur en       |     |

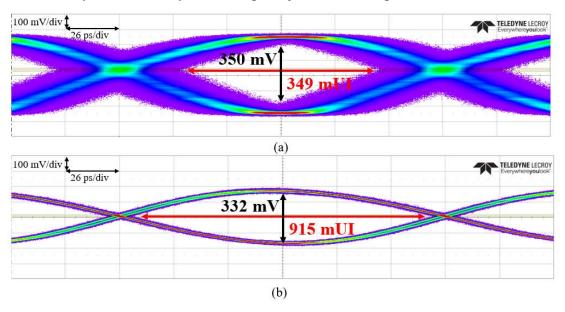

| anneau (a) sans verrouillage par injection et (b) avec verrouillage par injection                 | 107 |

| Figure 4-18 : Mesures des diagrammes de l'œil de l'oscillateur (a) non synchronisé et (b)         |     |

| synchronisé par injection1                                                                        | 107 |

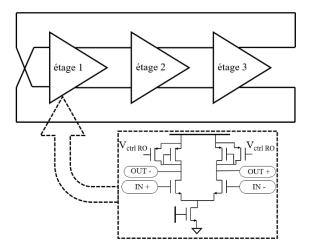

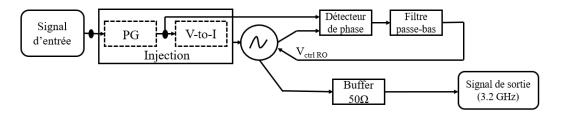

| Figure 4-19 : Synoptique du circuit de la PLL synchronisée par injection                          | 109 |

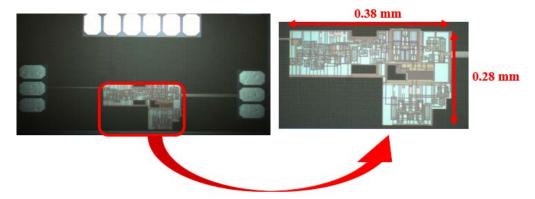

| Figure 4-20: Photographie de la puce de la PLL avec bloc d'injection                              | 109 |

| Figure 4-21 : Comparaison des bruits de phase en bordure inférieure, milieu et supérieure d       | e   |

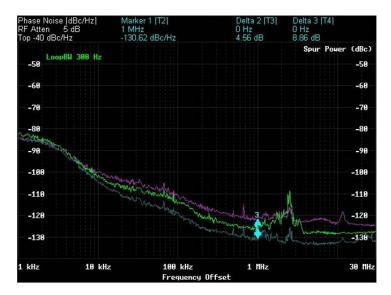

| la PLL synchronisée par injection                                                                 | 110 |

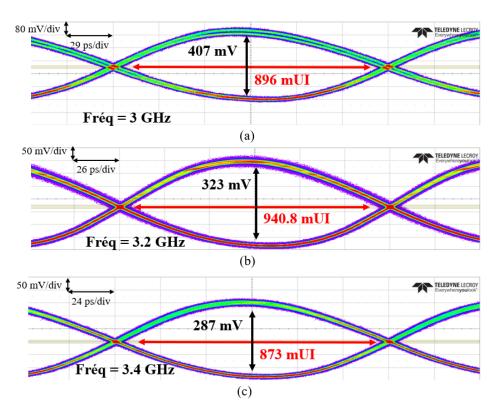

| Figure 4-22 : Résultats de simulation du spectre (a) et diagramme de l'œil (b) de la PLL          |     |

| injectée à 3.2 GHz                                                                                | 111 |

| Figure 4-23 : Comparaison du bruit de phase de la PLL (a) au milieu, (b) en bordure               |     |

| inférieure et (c) en bordure supérieure de la plage de synchronisation                            | 111 |

| Figure 4-24: Bruit de phase de la PLL sans synchronisation par injection à 3.2 GHz                |     |

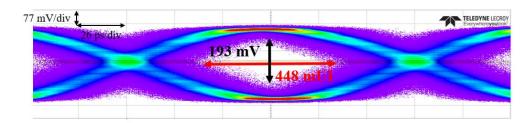

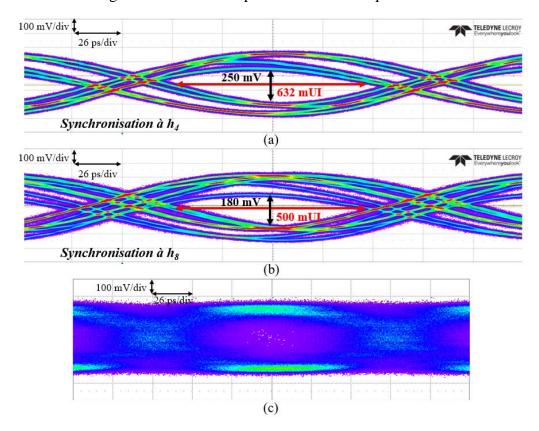

| Figure 4-25 : Diagrammes de l'œil de la PLL (a) synchronisée à l'harmonique 4, (b)                |     |

| synchronisée à l'harmonique 8 et (c) en dehors de la plage de synchronisation                     | 113 |

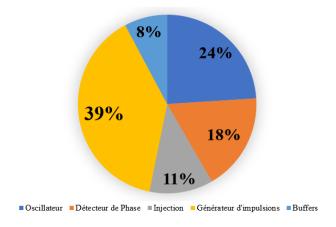

| Figure 4-26 : Diagramme de consommation détaillé de la PLL verrouillée par injection              | 115 |

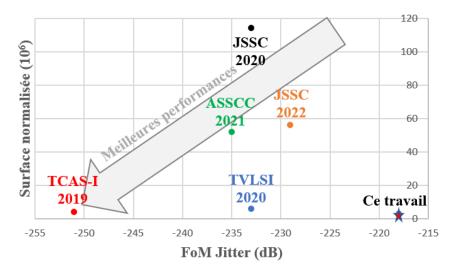

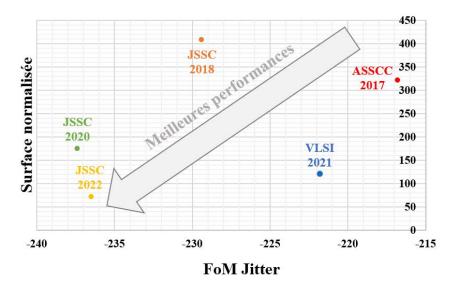

| Figure 4-27 : Comparaison à l'état-de-l'art de la surface normalisée versus FoM Jitter            |     |

| Figure 5-1: Vue de coupe d'un transistor Bulk CMOS et FD SOI [2]                                  |     |

| Figure 5-2 : Variation de $V_t$ en fonction de la polarisation du body bias [1]                   |     |

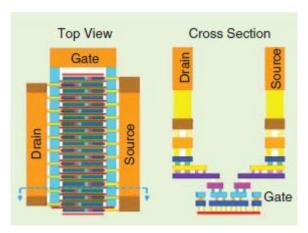

| Figure 5-3: Vues de dessus et de coupe d'un transistor en 28 nm FDSOI                             |     |

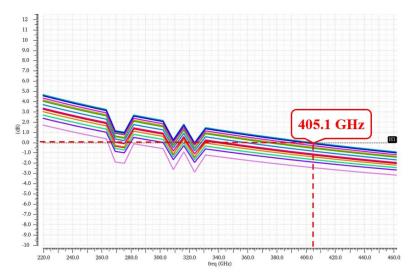

| Figure 5-4 : Estimation de f <sub>t</sub>                                                         |     |

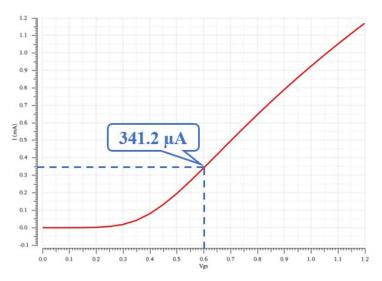

| Figure 5-5 : Détermination du courant de drain (I <sub>d</sub> ) à V <sub>g opt</sub>             |     |

| Figure 5-6 : Exemple d'optimisation de layout avec accès au drain et source par méthode           |     |

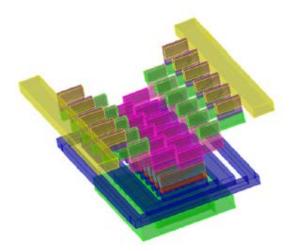

| d'escalier                                                                                        | 125 |

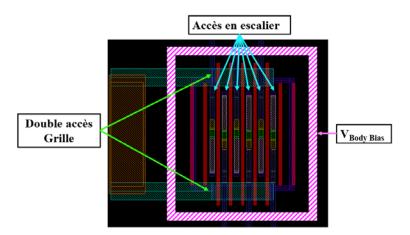

| Figure 5-7 : Layout d'un transistor avec optimisations d'accès en escalier et double accès à l    | la  |

| grille                                                                                            |     |

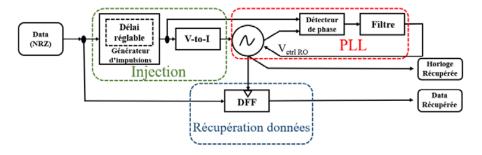

| Figure 5-8 : Synoptique du circuit de CDR réalisé                                                 |     |

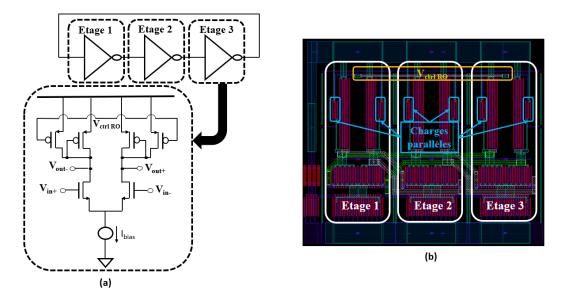

| Figure 5-9 : (a) Schématique et (b) Layout de l'oscillateur en anneau                             |     |

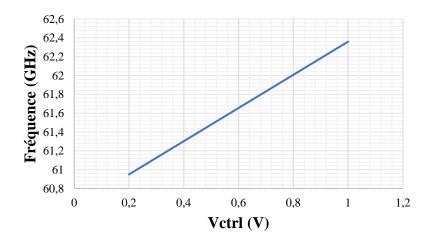

| Figure 5-10 : Plage de contrôle simulée de l'oscillateur en anneau                                |     |

| Figure 5-11 : Comparaison du bruit de phase de l'oscillateur en anneau sans (rouge) vs avec       |     |

| (bleu) synchronisation par injection                                                              |     |

| Figure 5-12: Layout du circuit de CDR de modulation NRZ                                           |     |

| Figure 5-13 : Diagramme de consommation du circuit de CDR de modulation NRZ                       |     |

| Figure 5-14 : Allure temporelle du signal d'horloge récupéré à 60 GHz                             |     |

| Figure 5-15 : Allures temporelles des données d'entrée, des données et horloge récupérées         |     |

| Figure 5-16 : Diagramme de l'œil des Données récupérées (a) avant buffer 50 $\Omega$ et (b) après |     |

| buffer $50 \Omega$                                                                                |     |

| Figure 5-17 : Synoptique de l'architecture complète de la CDR PAM4                                |     |

| Figure 5-18 : Allures temporelles des données d'entées PAM4 et décodage des données MS            |     |

| 1 Iguie 5 16 . Antares temporenes des données d'entées 171114 et décodage des données 1715        |     |

| Figure 5-19 : Comparaison de l'état-de-l'art de la surface normalisée vs FoM Jitter               |     |

| Figure 7-1: Oscillateur en anneau différentiel verrouillé par double injection [1]                |     |

| Figure 7-2 : Schéma-bloc de la PLL entièrement digitale synchronisée par injection         |      |

|--------------------------------------------------------------------------------------------|------|

| sub- harmonique                                                                            | 147  |

| Figure 7-3 : Schématique du générateur d'impulsions proposé                                | 147  |

| Figure 7-4 : Schéma-bloc simplifié (a) et chronogramme associé à la PLL injectée (b) [5] . | 148  |

| Figure 7-5 : Oscillateur verrouillé par injection par couplage électromagnétique           | 149  |

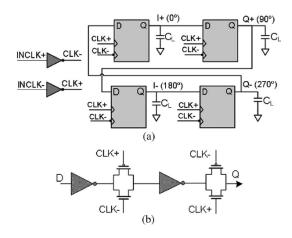

| Figure 7-6 : (a) Génération d'horloge multiphase utilisant quatre DTG-FFs et (b) schéma d' | 'une |

| DTG-FF [8]                                                                                 | 149  |

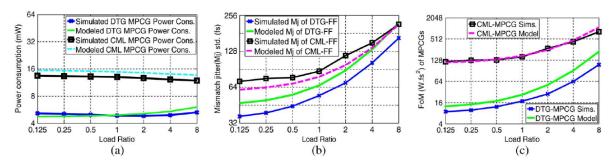

| Figure 7-7 : Consommation de DTG et CML FF, (b) Mismatch Jitter, (c) Figure de Mérite      | de   |

| DTG et CML FF [8]                                                                          | 150  |

### Liste des acronymes

CDR: Clock and Data Recovery

CML: Current-Mode-Logic

CMOS: Complementary Metal Oxide Semiconductor

DFF: Delay Flip Flop

DLL: Delay Locked Loop

DTG: Dynamic Transmission Gate

**ELT**: Enclosed Layout Transistor

FD-SOI: Fully Depleted Silicon On Insulator

FoM: Figure-Of-Merit

ILO: Injection Locked Oscillator

ISI: Interférences Inter-Symboles

LSB: Least Significant Bit

MSB: Most Significant Bit

NRZ: Non-Return-to-Zero

PAM 4 : Pulse Amplitude Modulation 4-levels

PLL: Phase Locked Loop

RX: Reception block

RZ: Return-to-Zero

SEE : Single Event Effect

SerDes: Sérialisateur/Déserialisateur

SET : Single Event Transient

TID: Total Ionizing Dose

TX: Emitter block

VCO: Voltage Controlled Oscillator

XOR: Porte Ou Exclusive

ZCE : Zone de Charge d'Espace

### 1. Introduction générale

L'augmentation continue des débits de données des liaisons numériques en série liée à l'émergence de nouvelles applications conduit à la recherche et au développement de nouvelles méthodes. De nos jours, la majorité des systèmes de communication numérique employés se basent sur des systèmes nommés Sérialisateur/Désérialisateur (SerDes). Ces systèmes, dont les domaines d'utilisation varient des communications des Systèmes sur puce, puce-à-puce, carte-à-carte, etc... ne peuvent opérer efficacement que par la présence d'un bloc crucial situé dans le bloc de réception. Celui-ci consiste à récupérer correctement les séquences de données envoyées depuis l'émetteur. Ce dernier se nomme circuit de récupération d'horloge et de données et fait l'objet de notre centre d'intérêt dans cette étude. Malheureusement, divers parasites intrinsèques et extrinsèques à ce circuit viennent perturber cette récupération et nécessitent d'être traités. Un acteur particulièrement prépondérant est celui de l'environnement.

Le travail de cette thèse s'est donc articulé autour de la conception ainsi que l'optimisation d'un circuit de récupération d'horloge et de données destiné à des applications spatiales. Ce travail s'est concentré sur l'optimisation de trois performances : la consommation, la superficie ainsi que le débit. Cette thèse s'inscrit dans le cadre d'une collaboration entre le Centre National d'Etudes Spatiales (CNES), Thales Alenia Space ainsi que le laboratoire de l'Intégration du Matériau au Système (IMS). Cette étude s'est décomposée en plusieurs parties exposées ciaprès.

Le premier chapitre dresse un état-de-l'art des différents circuits de récupération d'horloge et de données (*CDR*) ciblant des débits très élevés ( $\geq$ 40 Gb/s) en technologie CMOS avancées. Puis, les origines et influences néfastes des particules radiatives sur les circuits électroniques sont introduites en vue de proposer certaines techniques de durcissement quant à celles-ci. Ces diverses solutions ciblent les technologies employées ainsi que les méthodes de conception.

Une discussion concernant les atouts et inconvénients des trois principaux types de modulation de données est également présentée. Un aperçu général destiné à la caractérisation des métriques usuelles dans les circuits de CDR est développé. Les principales sources de bruit existantes au sein des composants électroniques sont également mises en évidence en vue de définir leurs influences sur la dégradation des métriques que constituent jitter et diagramme de l'œil.

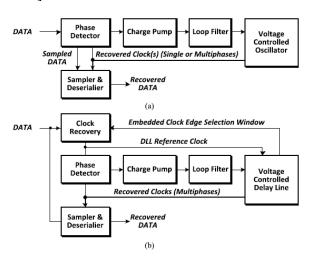

La dernière section se consacre à une étude approfondie de l'état-de-l'art ciblant les circuits de CDR en technologie CMOS et opérant à des débits très élevés (≥40 Gb/s). Les deux principales architectures de CDR sont développées en opposant d'une part les systèmes à contreréaction (dit à boucle fermée) aux systèmes à boucle ouverte d'autre part. Une étude finale comparative conduit à la sélection d'une architecture idéale pour notre cas.

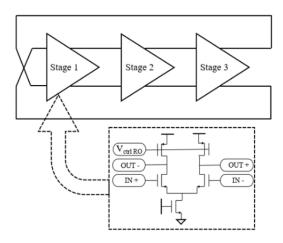

Le second chapitre débute par une présentation de l'architecture générale de la CDR et se poursuit par une présentation détaillée de chacun des sous-blocs la constituant. Un bref état-de-l'art des différents éléments montre les avantages et défauts de chaque topologie dans le but d'en tirer une version optimale pour notre cas. Une analyse théorique du principe de verrouillage par injection sur un oscillateur en anneau est présentée afin d'en déduire les paramètres prépondérants influençant la plage de synchronisation. Différentes méthodes d'injection sont également discutées et comparées.

Ce chapitre se conclut sur une discussion des performances optimisées dans le cas de notre travail, à savoir la consommation et la superficie du circuit tout en ciblant une architecture opérant à très haut débit.

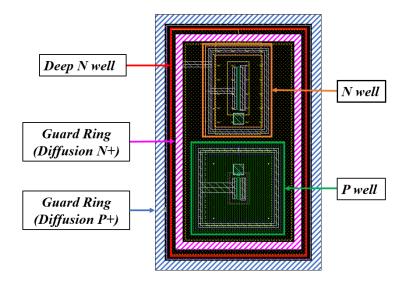

Le chapitre 3 introduit un premier circuit preuve-de-concept en technologie 180 nm ciblant la fréquence de 3.2 GHz. Cette technologie démontre une robustesse quant aux radiations dû à son procédé de fabrication basé sur un triple puit. Ce principe est détaillé de manière plus approfondi par une illustration au niveau layout.

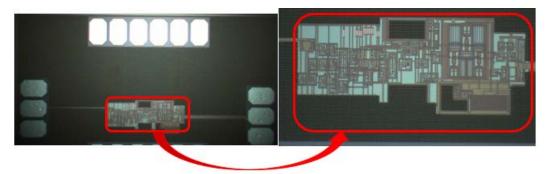

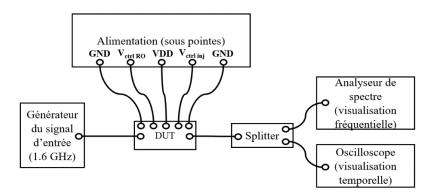

Deux circuits sont présentés et dont les mesures font l'objet de comparaisons avec les résultats de simulation. Le premier est un oscillateur en anneau auquel le mécanisme de verrouillage par injection est appliqué en vue de mettre en avant l'apport bénéfique d'un tel principe sur les performances en jitter et bruit de phase. L'architecture du circuit final, explicité dans le chapitre 4, étant basée sur une boucle verrouillage phase (PLL), le second circuit mesuré correspond à une PLL à laquelle le principe de synchronisation par injection est également appliqué.

Une comparaison avec des architectures fonctionnant dans des plages de fréquence similaires met en exergue des résultats suffisamment probants afin de valider l'architecture. La conclusion de ces résultats met en évidence les optimisations à prévoir pour le dernier circuit.

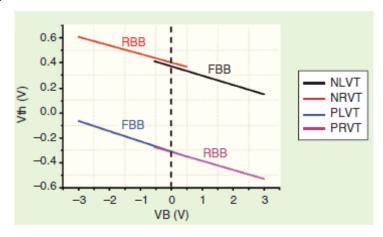

Dans le dernier chapitre figurent deux circuits complets de CDR fonctionnant à très haut débit (60 Gb/s) en technologie 28 nm FDSOI. Ce chapitre débute par une présentation de cette technologie en exposant la différence fondamentale entre les technologies Bulk conventionnelles et de type SOI (*Silicon On Insulator*). Cette partie mentionne également une fonction clé liée à cette technologie permettant en définitive d'optimiser l'efficacité énergétique. Deux nouvelles méthodes au niveau layout sont proposées en vue d'optimiser les  $f_t$  et  $f_{max}$  des transistors.

L'unique différence entre les deux circuits présentés provient du type de modulation des données d'entrées : NRZ (*Non-Return-to-Zero*) pour un cas et PAM4 (*Pulse Amplitude Modulation 4 levels*) pour l'autre. Les résultats exposés dans ce chapitre sont issus de simulations post-layout. Une comparaison de la CDR de type NRZ à un état-de-l'art d'architectures équivalentes est donnée en vue de situer les performances respectives de notre architecture.

Le second circuit est basé sur le même cœur du circuit que le précédent. La seule différence émane de l'ajout d'un sous-bloc situé à l'entrée nommé décodeur PAM4 dont l'objectif est de convertir les données d'entrées en deux signaux de modulation NRZ. Les résultats de simulation ainsi que les difficultés rencontrées lors de la conception de ce décodeur PAM4 sont exposées.

Ce chapitre se conclut sur un résumé ainsi qu'une comparaison des performances obtenues des deux circuits à un état-de-l'art récent de circuit de CDR similaires. Des efforts d'améliorations en comparaison du circuit de preuve-de-concept (chapitre 3) sont aussi énoncés.

Enfin, une conclusion générale récapitule l'ensemble des travaux réalisés au cours de cette thèse et propose l'investigation de quelques pistes de perspectives mélioratives.

# 2. Introduction aux systèmes de récupération d'horloge et de données

### 2.1. Introduction au contexte

La croissance exponentielle des débits de données associée à un souhait de réduction de consommation des systèmes de communication numérique à lien série conduit à la nécessité d'une amélioration drastique de l'efficacité énergétique de ceux-là.

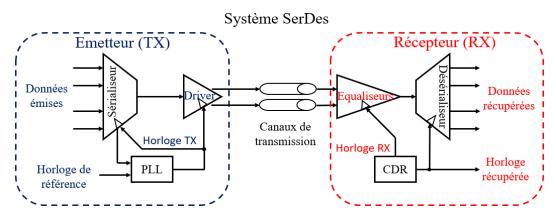

La grande majorité de ces systèmes actuels reposent sur le principe de lien série haut-débit (*HSSL*), aussi appelé système SerDes (Serializer/Deserializer). Trois éléments majeurs composent celui-ci : un émetteur, un canal de transmission ainsi qu'un récepteur [1].

- La partie émettrice (*TX*) sérialise, code et transmet les données au récepteur par le biais de canaux de transmission. Le signal d'horloge de l'émetteur est souvent généré par une boucle à verrouillage de phase (*PLL*).

- Le canal de liaison assure la transmission des données de l'émetteur vers le récepteur. Ceux-là sont à l'origine de pertes, de réflexion ainsi que de distorsion de signal.

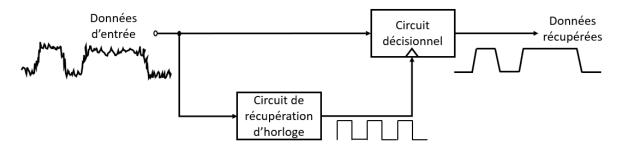

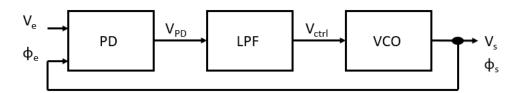

- La partie réceptrice (RX) accomplit l'équalisation, c'est-à-dire la remise en bonne et due forme du signal reçu, mais aussi de la récupération et désérialisation des données. Le signal obtenu à l'entrée du bloc RX étant bien souvent dégradé, il est nécessaire de reconstituer ce signal. Afin de répondre à cela, un rééchantillonnage du signal des données est exécuté par la synchronisation d'un signal d'horloge généré par le bloc un circuit de récupération d'horloge et de données (CDR). Le signal d'horloge n'étant pas transmis depuis la partie émettrice, il est nécessaire de régénérer celui-ci. C'est un des deux objectifs d'un circuit de CDR. Le second consiste à effectuer la récupération des données à l'aide d'un circuit décisionnel.

La figure ci-dessous illustre un système SerDes complet.

Figure 2-1 : Vue d'ensemble d'un système SerDes

Les circuits de récupération d'horloge et de données font partie des circuits les plus complexes à concevoir dans les architectures de transmissions de données [2]. En dehors des paramètres inhérents au circuit tels que les performances sévères en jitter à tenir, ou encore les spécifications liées à la largeur de bande de fonctionnement du circuit, d'autres paramètres tels

que l'efficacité énergétique et la surface occupée constituent un réel challenge à considérer par le concepteur.

Ce premier chapitre s'organise de la façon suivante. Tout d'abord, nous définissons les origines ainsi que les effets des particules radiatives sur les circuits électroniques et proposons ensuite différentes techniques de durcissements face à celles-ci. Puis, nous présentons les concepts basiques dans les systèmes de communications actuels en introduisant les principaux paramètres ainsi que les types de modulation utilisés. Nous poursuivons par une présentation des différentes métriques usuelles dans les systèmes de communication, et plus particulièrement celles liées au circuit de récupération d'horloge et de données. Enfin, nous clôturons ce chapitre par une présentation d'un état-de-l'art récent des circuits de *CDRs* proposant les meilleures performances en termes d'efficacité énergétique et de débit. La conclusion de cette étude mène au choix de l'architecture retenue pour la suite de nos travaux.

### 2.2. Origines, effets et techniques de durcissement aux radiations

L'exposition des circuits électroniques à des environnements radiatifs sévères tels que le nucléaire, le spatial, ... met en évidence la vulnérabilité de ceux-ci. En effet, ces défaillances se traduisent alors par des erreurs pouvant être de nature transitoire voire permanente.

Dans cette partie, nous détaillerons dans un premier temps l'origine de ces particules, leurs influences sur les circuits électroniques et terminerons par des techniques de conception de durcissement aux radiations pour les circuits intégrés.

### 2.2.1. Origines des particules

L'environnement spatial est un milieu dans lequel divers types de rayonnements irradient. Les sources de ces particules proviennent en majorité du Soleil, de la magnétosphère terrestre ou encore de rayonnements cosmiques [3]. On distingue alors des transferts ionisants et non ionisants.

Un transfert non ionisant implique un échange d'énergie par choc avec les atomes du matériau conduisant à des défauts au niveau du réseau cristallin du semi-conducteur, c'est-à-dire en des modifications de ses propriétés électriques [4].

Un transfert ionisant se caractérise par la perdition d'énergie d'une particule, générant ainsi plusieurs paires d'électrons/trous sur sa trajectoire. Ces particules ionisantes sont divisées en deux catégories : les particules légères (protons, électrons, neutrons et particules  $\alpha$ ) et les particules lourdes constituées essentiellement d'ions lourds provenant de vents et éruptions solaires [5]. Ce type de transfert constitue l'impact le plus significatif sur les circuits intégrés destinés à des applications spatiales.

### 2.2.2. Effet des radiations sur les circuits intégrés

Nous pouvons énumérer trois types d'effets de radiations sur les circuits électroniques tels que les mécanismes d'interaction, les effets de Dose ou encore les évènements singuliers.

### Mécanismes d'interaction

Ce type d'interaction correspond à la quantité d'énergie perdue par la particule incidente avec la matière traversée. Une distinction est à prendre en considération suivant la matière avec laquelle la collision a lieu. Cette interaction peut se produire avec un électron, créant alors une paire d'électrons/trous à l'interface du matériau semiconducteur. Une autre interaction avec une particule chargée peut également avoir lieu, conduisant à l'émission de radiations γ. Enfin, une interaction avec un noyau entraine un transfert d'énergie, conduisant potentiellement à l'éjection de celui-ci du réseau cristallin du semiconducteur.

#### Dose

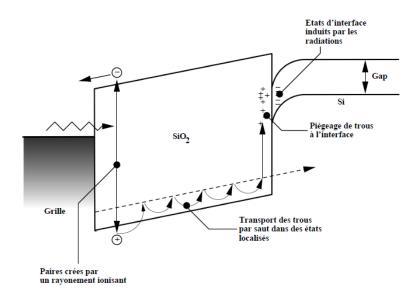

Les effets de Dose représentent la majorité des effets de radiations observables dans les satellites. Ces effets sont issus de l'exposition cumulative des circuits intégrés à des particules radiatives telles que les photons, les ions et les électrons. Cette dose, par interaction avec l'oxyde de Silicium (SiO<sub>2</sub>), crée des paires d'électrons/trous. Une partie de ces paires est à l'origine des effets de dose, se manifestant au niveau des oxydes de grille. L'absorption de cette dose s'exprime en Gray (Gy) ; correspondant à l'absorption d'un Joule par kilogramme de matière [3] et [4].

Deux mécanismes principaux sont à l'œuvre au niveau des oxydes de grille. Le premier est le piégeage d'une partie des trous n'ayant pas été recombinés au niveau de l'interface entre le  $SiO_2$  et le substrat de Silicium. Celui-ci se traduit par une dérive des tensions de seuils  $(V_t)$  des transistors. La figure ci-dessous donne une illustration du piégeage des porteurs à l'interface.

Figure 2-2 : Diagramme en bande des processus physiques lors de l'irradiation d'une structure MOS [6]

Le second mécanisme correspond à la création d'états d'interface entre l'oxyde de grille et le substrat. Cet effet de dose est à l'origine de courants de fuite, d'une augmentation de la consommation et éventuellement d'un blocage de conduction des transistors.

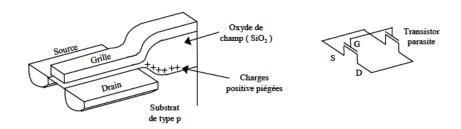

Le phénomène de piégeage des trous peut également être à l'origine de la présence de transistors parasites. La figure ci-dessous expose le phénomène au niveau de la partie de l'oxyde de champ proche d'un transistor, aussi connu comme *bec d'oiseau*.

Figure 2-3 : Formation d'un transistor parasite à proximité d'un bec d'oiseau [4]

Ces transistors parasites créés sont également à l'origine de courants de fuite, induisant le phénomène d'échauffement potentiellement destructif.

### > Evènements singuliers

Bien que l'origine des évènements singuliers soit identique à celle des doses ionisantes (création de paires d'électrons/trous), les conséquences diffèrent. Ces *effets singuliers* se caractérisent par une injection de charge élevée et localisée dans l'espace et le temps.

Nous distinguons différents types d'effets singuliers (SEE : Single Event Effect) : les effets dus à une impulsion transitoire (SET : Single Event Transient) ainsi qu'un changement d'état logique d'une mémoire (SEU : Single Event Upset) pouvant conduire à la destruction du composant par déclenchement d'une structure parasite (SEL : Single Event Latchup) [7]. Les effets singuliers se traduisent par des défaillances temporaires, voire permanentes. Ces effets-là sont classés en deux catégories [3] et [5].

Tout d'abord, les effets irréversibles, c'est-à-dire de type destructif. Différents effets sont répertoriés dans cette catégorie tels que : les *SEL*, les *SES* (Single Event Snapback), *SEGR* (Single Event Gate Rupture), les *SHE* (Single Hard Error), les *SEB* (Single Event Burnout) ou encore les *SEFI* (Single Event Functionnal Interrupt).

Puis, les effets réversibles, qualifiés de non-destructifs correspondant à des aléas logiques. Nous retrouvons parmi ceux-là les *SEU*, les *MBU* (Multiple Bit Upset) et les *SET*.

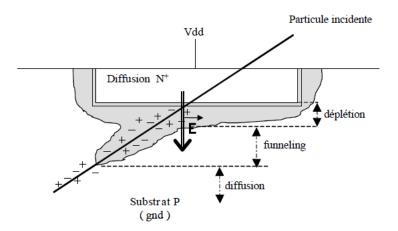

Une particule ionisante heurtant une jonction bloquée de transistor provoquant alors une impulsion de courant constitue un aléa transitoire, nommé *SET*. C'est la durée de cette impulsion transitoire qui détermine si celle-ci se propage au reste du circuit, induisant potentiellement une valeur erronée.

Figure 2-4: Création d'un courant transitoire dans une jonction PN [4]

La figure ci-dessus retrace la trajectoire de la particule ionisante avec les paires électrons/trous générées. Nous pouvons alors observer une extension locale (*funneling*) de la Zone de Charge d'Espace (ZCE). Sous l'action du champ électrique les charges induites sont immédiatement balayées, se traduisant alors par un pic de courant.

### 2.2.3. Conception pour durcissement aux radiations

Les origines et effets de ces radiations ayant été définis, tentons à présent de dresser une liste de techniques permettant de rendre plus robuste ces circuits quant à ces radiations. Nous pouvons distinguer différents types de durcissements, tous adressant des moyens différents.

Nous pouvons dissocier deux approches afin d'améliorer le durcissement d'un circuit aux particules radiatives. La première consiste à durcir physiquement les circuits électroniques par des procédés de fabrication plus complexes que le CMOS standard. La seconde suggère un durcissement des circuits par une évolution des architectures de transistors et des circuits.

### Durcissement par technologie

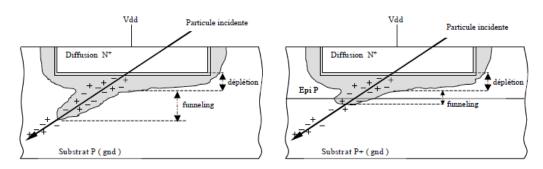

Le durcissement technologique nécessite de recourir à des technologies CMOS plus complexes. En effet, les technologies épitaxiales CMOS ou encore les CMOS SOI suggèrent une robustesse supérieure aux technologies CMOS bulk classiques quant aux radiations. La figure ci-dessous expose une comparaison de l'effet de *funneling* pour une technologie bulk CMOS (gauche) versus une technologie épitaxiale CMOS (droite).

Figure 2-5: Effets de funneling sur les technologies Bulk CMOS et Epi CMOS [4]

Les technologies épitaxiales reposent sur le principe suivant : une couche mince épitaxiée et peu dopée par rapport au substrat plus fortement dopé permet de limiter l'extension de la *ZCE*, réduisant à la fois l'effet de *funneling* ainsi que la charge totale collectée.

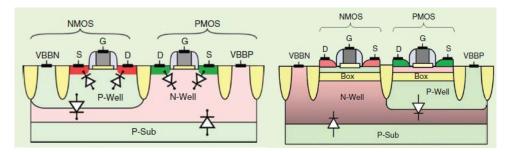

Les technologies CMOS sur isolants (*SOI* : *Silicon On Insulator*) permettent également de réduire cette collecte de charge. La figure 2-6 révèle une vue de coupe d'une technologie bulk et SOI.

Figure 2-6: Vue de coupe des technologies (a) Bulk et (b) SOI [8]

Le terme *FD-SOI* (pour *Fully Depleted SOI*) vient du fait qu'une faible couche de silicium est utilisée pour former un canal. En raison de cette faible couche, aucun dopage de canal n'est nécessaire, rendant le transistor *totalement déplété* (*Fully Depleted*).

La fine couche d'isolant de SiO<sub>2</sub> sur laquelle les transistors sont réalisés accorde une réduction de volume de silicium dans lequel l'irradiation génère les porteurs, améliorant ainsi la robustesse des circuits intégrés aux *SEE*.

### Durcissement par conception

Une seconde méthode basée sur le durcissement par conception existe également. Celle-ci repose sur le principe de redimensionnement des transistors, ou encore de redondances de composants électroniques.

La technique de surdimensionnement des transistors permet une évacuation plus rapide des charges générées et donc un retour plus rapide au potentiel correct. Inclure également des capacités aux nœuds sensibles engendre une augmentation de la charge critique, augmentant alors la charge nécessaire afin de relever des erreurs. Néanmoins, ces approches-ci viennent au détriment d'une diminution de la fréquence de fonctionnement [4].

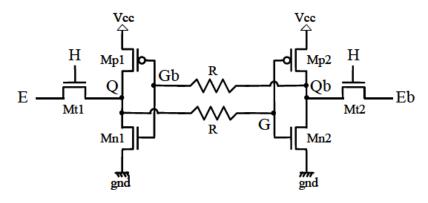

Une méthode nommée durcissement par découplage résistif implique l'utilisation de résistances (R) entre les nœuds dits sensibles Q et Qb ainsi que G et Gb, comme le montre la figure ci-dessous [9].

Figure 2-7 : Durcissement par découplage résistif [9]

Cependant, l'efficacité de cette technique requiert une durée de la perturbation inférieure au temps de réponse, fixé par la constante de temps RC. Cette technique de durcissement soulève deux points critiques. Le premier implique une dégradation du temps de réponse, dû à la volonté de filtrer les perturbations les plus longues. Le second point expose un défaut inhérent à l'architecture. En effet, le recours à l'utilisation de résistances induit une plus grande sensibilité quant aux variations de fabrication et de température.

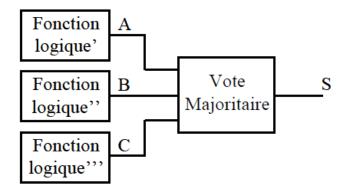

Une technique alternative est basée sur le principe de redondance spatiale. La technique de redondance triple avec vote majoritaire est explicitée ci-après.

Figure 2-8: Durcissement par redondance triple [4]

Le principe est simple. La même fonction logique est répétée trois fois et les sorties de chacune sont ensuite comparées. Le bloc de *Vote Majoritaire* sélectionne alors la réponse majoritaire. Le principal défaut d'une telle technique est la surface requise qui nécessite l'implémentation de trois fois la fonction logique ainsi que d'un bloc de vote majoritaire.

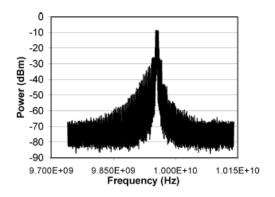

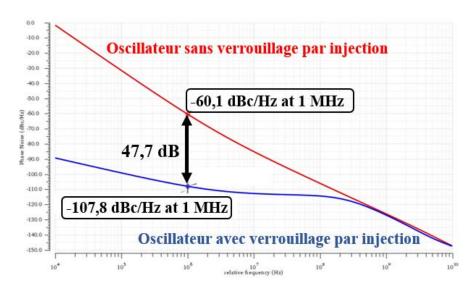

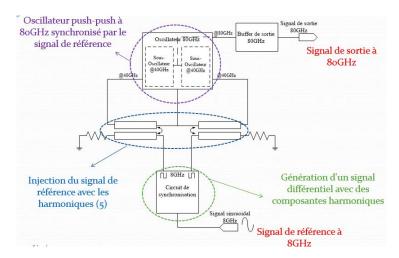

Enfin, une ultime technique de durcissement par conception est proposée par [10] et [11]. Cette technique met en exergue l'influence du verrouillage par injection sur un oscillateur. Le principe de verrouillage par injection sera repris et plus largement discuté dans le chapitre 2.

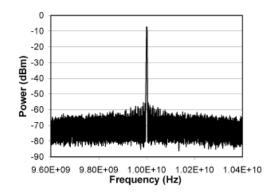

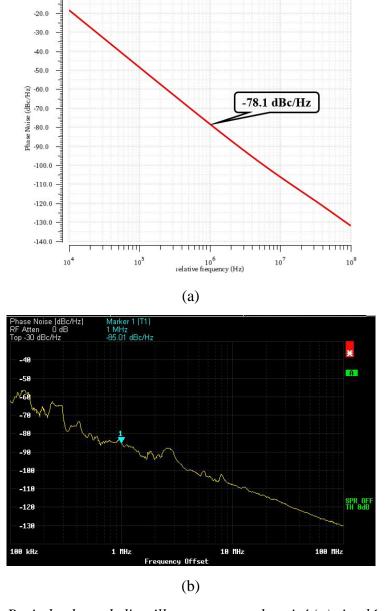

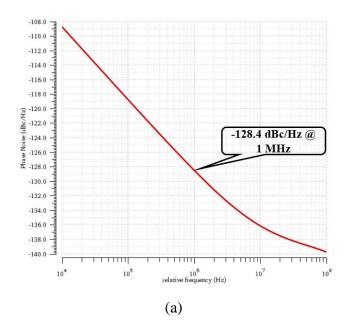

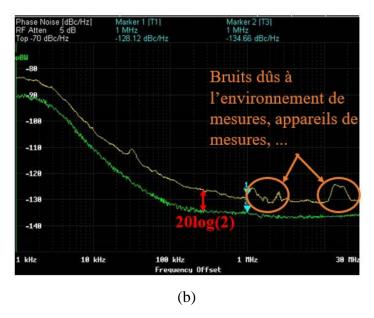

Figure 2-9 : Spectres en fréquence du VCO sous radiations (a) sans verrouillage par injection (b) avec verrouillage par injection

Les résultats des mesures permettent de valider la robustesse de l'oscillateur verrouillé par injection quant aux radiations. Dans le cas où l'oscillateur n'est pas verrouillé par injection (fig. 2-9 (a)), celui-ci se montre bien plus sensible à son environnement en présentant des performances en puissance dégradées autour de la fréquence porteuse. Lorsque celui-ci est synchronisé par injection, une amélioration drastique de la pureté spectrale est alors observable (fig. 2-9 (b)).

### 2.3. Concepts de bases dans les systèmes de communication

Cette partie donne un aperçu général nécessaire à l'analyse et la conception de circuits de récupération d'horloge et de données.

Dans son fonctionnement idéal, l'objectif d'un système de transmission de données à lien série se base sur l'émission d'un signal depuis l'émetteur, la transmission par le biais du canal de liaison afin de l'envoyer vers le récepteur, supposé récupérer le signal initial. Malheureusement, des éléments parasites tels que l'environnement, des variations dues aux procédés de fabrications, à la température, aux appareils de mesures, les pertes et distorsions introduites par le canal de transmission, ... constituent diverses sources de bruit venant alors détériorer le signal récupéré.

Afin de se rapprocher d'un système de transmission de données idéal, Shannon ([12]) propose une théorie. Dans celle-ci, Shannon définit la limite théorique du canal portant l'information, aussi connue sous le nom de capacité du canal (C, en bits/s). Cette capacité du canal est calculée en présence de bruit blanc Gaussien sur le signal et dépend de la bande passante (B) du canal (en Hz) ainsi que du ratio signal-sur-bruit (SNR)  $\frac{s}{N}$ . Son expression est donnée dans l'équation ci-dessous :

$$C = B \log_2\left(1 + \frac{S}{N}\right) \tag{1-1}$$

Cette équation suggère que si le débit d'information (*R*, en bits/s) est inférieur à la capacité du canal (*C*), l'erreur de récupération des données est relativement proche de zéro.

Commençons par introduire quelques applications de standards de communications numérique à lien série.

### 2.3.1. Etat-de-l'art des systèmes de communication numérique à lien série

A l'instar des réseaux sans fil, on distingue les communications filaires par l'utilisation d'une interconnexion physique (câbles, pistes de métallisation, ...) entre l'émetteur et le récepteur. Ce type de liaison filaire existe aussi bien à l'échelle humaine (câble Ethernet, ...) qu'aux circuits intégrés (System On Chip, Chip-to-Chip, ...).

Parmi les liaisons numériques séries les plus connues, nous retrouvons la communication *Universal Serial Bus (USB)* ou encore *Ethernet*. Définie par la norme *Advanced Technology Attachment (ATA)*, le type *USB* permet la connexion de périphériques de stockage avec des PC. Les débits peuvent atteindre jusqu'à environ 4.8 Gb/s avec l'USB 3.0 [13]. A l'heure actuelle, le type de liaison *Ethernet* permet d'atteindre quant à lui jusqu'à 40 Gb/s.

A l'échelle d'une carte électronique, nous différencions les liaisons *I2C* (*Inter Integrated Circuit*) et *SPI* (*Serial Peripheral Interface*) afin d'assurer la communication entre différents éléments. De nos jours, le type *I2C* est généralement implémenté directement dans les microcontrôleurs et propose une fréquence de fonctionnement jusqu'à 5 MHz. Concernant le type *SPI*, celui-ci peut atteindre jusqu'à 20 MHz.

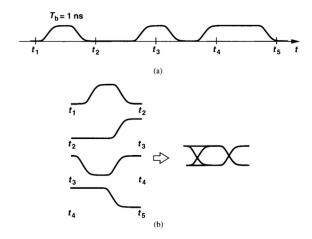

### 2.3.2. Propriétés des données binaires aléatoires

Une séquence binaire aléatoire est constituée d'une suite de 0 et de 1 portant l'information et présente à probabilité égale. On distingue alors le débit de donnée,  $R_b$ , (bit rate) et s'exprime en bit/seconde (bits/s).

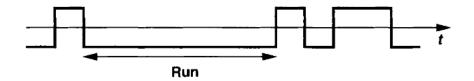

La nature aléatoire des données induit la possibilité que la séquence binaire étudiée présente une longue série de 0 ou de 1. On dit alors que les données montrent une faible *densité de transition*. Ce phénomène crée des difficultés dans la conception de circuits d'émetteurs-récepteurs. Pour cette raison, les standards de communications actuels spécifient également la densité de transition maximale (*maximum run length*). Afin d'éviter des *runlength* trop élevés, des techniques d'encodage sont généralement implémentées dans la partie émettrice du système. Certaines de ces techniques sont introduites ultérieurement.

Figure 2-10 : Densité de transition faible d'une séquence binaire aléatoire

Afin de donner une représentation plus précise concernant la puissance que porte le signal à chaque fréquence, il est intéressant d'étudier celui-ci dans le domaine fréquentiel. Prenons une séquence binaire aléatoire représentée par :

$$x(t) = \sum_{k} b_k p(t - kT_b) \tag{1-2}$$

Avec  $b_k = \pm 1$  et p(t) la forme de l'impulsion. La séquence binaire aléatoire est répétée toutes les périodes de bit  $(T_b)$ .

Reprenons l'équation (1-2) avec p(t) une impulsion rectangulaire large de  $T_b$  secondes et répétées toutes les  $T_b$  secondes. La transformée de Fourier d'un tel signal est égale à :

$$P(f) = T_b \frac{\sin(\pi f T_b)}{\pi f T_b} \tag{1-3}$$

On en déduit le spectre de la séquence aléatoire :

$$S_{x}(f) = T_{b} \left[ \frac{\sin(\pi f T_{b})}{\pi f T_{b}} \right]^{2}$$

$$(1-4)$$

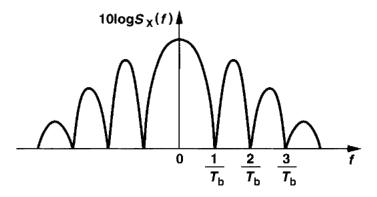

De l'équation (1-4), nous pouvons relever un point essentiel. Lorsque  $f = n/T_b$ ,  $sin(\pi f T_b)$  devient nul, et cela quelle que soit la valeur de n pour tout entier naturel. Les figures ci-dessous donnent les spectres des séquences binaires aléatoires.

Figure 2-11 : Spectre fréquentiel de données aléatoires [14]

L'analyse précédente permet d'en tirer une conclusion importante. Le spectre ne présente aucune puissance aux fréquences égales à  $1/T_b$ ,  $2/T_b$ , ...,  $n/T_b$ . Dans le cas des circuits de récupération d'horloge et de données, cela signifie que ce signal doit être traité afin de générer un signal d'horloge égal au débit des données arrivant en vue d'effectuer une récupération des données correcte.

La prochaine section s'intéresse maintenant aux différents types de modulation de données existants et compare les forces et faiblesses de chacun d'eux.

### 2.4. Types de modulation

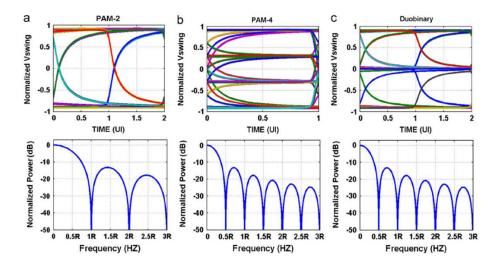

### 2.4.1. NRZ et RZ

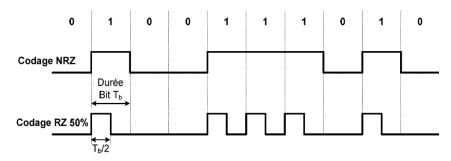

De nos jours, les séquences de données binaires aléatoires reposent en grande partie sur une modulation de type *Non-Return to Zero (NRZ)*. Il est également possible de trouver cette modulation sous le nom de PAM2 (*Pulse Amplitude Modulation 2 Levels*), puisqu'elle correspond à une modulation d'amplitude d'impulsions à deux niveaux. Ce type de modulation de données se distingue du type *RZ (Return to Zero)* qui, contrairement au type NRZ, présente de la puissance au débit des données. Les figures suivantes donnent les chronogrammes (fig. 2-12) et spectres fréquentiels (fig. 2-13) de chacun.

Figure 2-12 : Chronogrammes de signaux modulés NRZ et RZ [15]

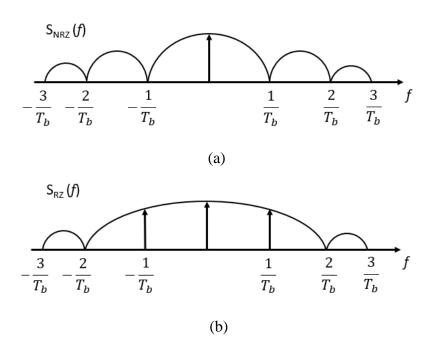

Figure 2-13: Comparaison des spectres de modulations (a) NRZ et (b) RZ

Bien que cet atout facilite la récupération d'horloge, le type RZ révèle par la même occasion un lourd inconvénient. En effet, d'après la figure 2-12, le principe de modulation RZ repose sur la scission de bits en deux parties : la première constitue le bit portant l'information et la seconde est toujours égale à la valeur logique 0. De facto, la bande passante nécessaire pour

faire passer la même quantité d'information est doublée en comparaison d'une modulation type NRZ. Pour cette raison évidente, le type RZ est bien souvent écarté dans les systèmes de communications à haut débit.

La nature aléatoire d'un flux de données constitue une source de difficultés dans les circuits de récupérations d'horloge et de données. En effet, une longue série de bits identiques est à l'origine d'une dérive en fréquence de l'oscillateur, aboutissant alors à de l'accumulation de jitter. Afin de pallier cet aléa, nous distinguons deux principales techniques d'encodage permettent de limiter ces désagréments : le 8B/10B et le Manchester.

### ➤ 8B/10B

Reposant sur l'utilisation d'une table de correspondance, le codage 8B/10B consiste à coder une série de 8 bits en un symbole de transmission de 10 bits. En d'autres termes, sur les 1024 (10 bits) valeurs possibles, seulement 256 (8 bits) valeurs sont retenues. De plus, le *runlength* est limité à 5 bits maximum, signifiant que seules les valeurs comprenant un minimum de quatre transitions d'état logique vers un autre et qui possèdent six valeurs identiques consécutives sont conservées. Cet atout vient au prix d'une réduction d'efficacité de la bande passante de 25% (appelé *overhead*).

### ➤ Manchester

Bien que le codage 8B/10B représente le plus utilisé dans les systèmes de communications actuels, il existe également d'autres technique de codage tel que le *Manchester*, basé sur le codage d'états de base par des transitions et non par des niveaux. Cependant, ce codage-là nécessite une bande passante définie par le débit des données. Dans le cas de notre travail, un signal dont le débit ciblé est de 60 Gb/s requiert alors une bande passante de 60 GHz.

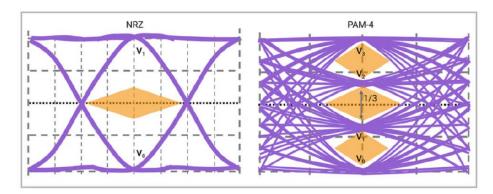

### 2.4.2. PAM4

Récemment, le type de modulation PAM4 (Modulation d'Impulsion à 4 niveaux d'Amplitude) se présente comme une solution alternative au type NRZ. En effet, la contrainte en débit devenant de plus en plus élevée, il devient difficile pour la modulation NRZ de répondre au besoin croissant du débit de données pour une bande passante identique.

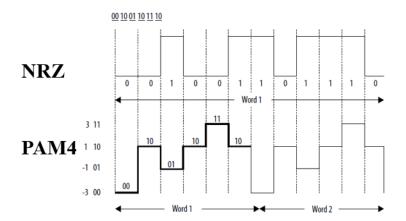

Contrairement au type NRZ, la modulation PAM4 permet d'envoyer deux bits en parallèles. En considérant un bit (0 ou 1) comme un symbole dans le cas d'une modulation NRZ, la modulation PAM4 correspond donc à deux bits par symbole (00, 01, 11 ou 10) [16]. Les Symboles s'expriment en Baud. A titre d'exemple, un signal PAM4 de débit égal à 60 GBaud/S équivaut alors à un signal NRZ de débit de 120 GBaud/S (ou 120 Gb/s). La figure ci-dessous donne une comparaison de la transmission d'un message identique *Word 1* et *Word 2* pour les deux types de modulation NRZ et PAM4.

Figure 2-14: Comparaison de la consommation de bande passante d'un signal NRZ vs PAM4

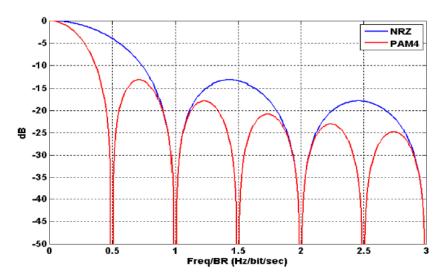

La figure ci-dessous illustre une comparaison des spectres en puissance d'un signal pour les deux types de modulation.

Figure 2-15 : Comparaison des spectres en puissance d'un signal de modulation NRZ vs PAM4 [16]

La figure 2-15 expose l'avantage majeur de la modulation PAM4 : pour une séquence de données identique, deux fois moins de bande passante est nécessaire qu'avec un signal de modulation NRZ.

Dans le cas d'une modulation PAM4, il est possible que deux transitions de bits arrivent au même moment, présageant une possibilité d'obtenir deux erreurs de bits par symbole. Afin de remédier à cela, il est commun de convertir la modulation PAM4 standard en code Gray. Cette conversion permet de réduire la transition à un seul bit par symbole, et donc de diviser par deux le taux de bits erronés (*BER*) [17].

Cependant l'analyse d'un signal de modulation PAM4 amène de nombreux challenges supplémentaires [16]. En effet, les différentes transitions d'amplitudes sont source d'apparition d'Interférences Inter-Symboles (*ISI*), compliquant ainsi la récupération du signal d'horloge.

La comparaison du type de modulation PAM4 vs NRZ étant terminée, définissons maintenant le dernier type de modulation : le Duobinary.

### 2.4.3. Duobinary

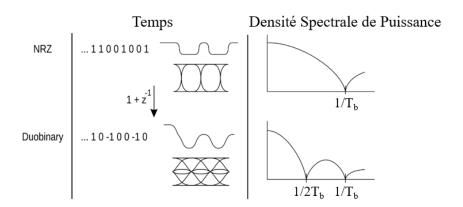

La modulation dite *Duobinary* [18] reprend le principe de la modulation PAM4, c'est-àdire de doubler le débit de données transmis dans la bande passante du canal en comparaison d'une modulation de type NRZ. Cette modulation présente un spectre identique à la modulation de type PAM4.

Ce type de modulation repose sur le principe d'une transformation qui se décompose en deux étapes. La première consiste à précoder la séquence de données binaire en un second signal binaire. Cette transformation est aussi reconnue comme *l'encodage différentiel* [19]. La seconde étape consiste à transformer un signal à deux niveaux en un signal polybinaire à N niveaux  $p_m$ . Cette transformation s'exprime par :

$$p_i = A \sum_{k=0}^{N-2} d_{i-k} \tag{1-5}$$

Avec A une constante et  $d_{i-k}$  le signal binaire converti à l'issu de la première étape.

La modulation *Duobinary* correspond à une modulation polybinaire de trois niveaux. Un symbole *Duobinary* équivaut à une combinaison du bit actuel ainsi que du précédent. Le symbole peut alors prendre trois valeurs respectives parmi les suivantes : +1 (correspondant à 11), 0 (01 ou 10) et enfin -1 (00). Ainsi le débit d'un symbole Duobinary est égal au débit d'un bit NRZ.

Figure 2-16: Comparaison de la densité spectrale de la modulation NRZ vs Duobinary [20]

Comme expliqué précédemment, la modulation *Duobinary* permet de doubler l'efficacité spectrale d'un signal NRZ (comme un signal PAM4). A la différence de la modulation *PAM4*, la modulation *Duobinary* ne présente que trois niveaux, conduisant ainsi à un *SNR* moins dégradé. La figure ci-dessous compare les diagrammes de l'œil et densité spectrale de puissance respectives des trois modulations *NRZ*, *PAM4* et *Duobinary*. Le principe de représentation par diagramme de l'œil présenté de manière plus approfondi ultérieurement.

Figure 2-17 : Comparaison des diagrammes de l'œil et spectres respectifs des modulations NRZ vs PAM4 vs Duobinary [21]

D'après la figure précédente, nous pouvons observer que l'ouverture d'un œil de modulation PAM4 correspond à 33% de l'ouverture d'un œil de modulation NRZ en raison de la division en quatre niveaux de la tension totale. Cette diminution se traduit par une réduction du SNR de la modulation PAM4 comparé au SNR de la modulation NRZ, exprimé par :

$$SNR_{perte} = 20\log_{10}\left(\frac{1}{3}\right) = -9.5dB$$

(1 - 6)

Dans le cadre de cette thèse, nous ne nous préoccuperons pas de la question d'encodage et du type de modulation optimal, ce travail étant réalisé en amont, dans la partie émettrice du circuit. Nous donnerons dans les sous-sections suivantes un état-de-l'art répertoriant les circuits de récupérations d'horloge et de données les plus performants en termes d'efficacité énergétique et de débit.

## 2.5. Métriques usuelles pour les circuits de communication

En dehors de l'analyse de performances communes aux circuits électroniques telles que la consommation, la superficie, la fréquence de fonctionnement, ... des métriques plus spécifiques dédiées à la conception de circuits de récupération d'horloge et de données existent. L'objet de cette section consiste à détailler ces métriques particulières aux circuits de CDR.

Avant d'expliciter celles-ci, déterminons d'abord les diverses sources de bruit présentes au sein des composants électroniques.

#### 2.5.1. Sources de bruit

Le bruit généré par les composants passifs et actifs des circuits représente une source de dégradation du spectre importante. Ces bruits se traduisent par des modulations à la fois sur les amplitudes et les phases générées par les signaux [22-25].

Plusieurs mécanismes de générations de bruit sont répertoriés au sein des composants électroniques. Parmi ceux-là, trois sont majoritaires : le bruit en basse fréquence, aussi appelé bruit en *1/f*, le bruit de grenaille et le bruit thermique.

### **>** *Bruit en (1/f)*

Le bruit en basse fréquence (1/f), est étroitement lié aux mécanismes de piégeages/dépiégeages des électrons aux interfaces. Celui-ci se retrouve essentiellement à l'interface grille-canal des transistors MOS et dépend en grande partie de la technologie utilisée. La densité spectrale de ce bruit est inversement proportionnelle à la fréquence. Son expression est la suivante :

$$S_N(f) = \frac{K}{f^{\alpha}} \tag{1-7}$$

Avec K une constante dépendante de la technologie (géométrie, polarisation et température),  $\alpha$  le coefficient de la pente de la densité de bruit et s'exprime en A<sup>2</sup>/Hz.

#### ➤ Bruit de grenaille

Le second bruit se nomme le bruit de grenaille. Celui-ci est associé à la quantité de courant électrique se situant dans les jonctions semiconductrices. Ce bruit est modélisé par une source de courant placée en parallèle du composant étudié. Sa densité spectrale est quasi-constante et s'exprime en A².

L'expression de celui-ci est la suivante :

$$\overline{i}_N^2 = 2eI\Delta_f \tag{1-8}$$

Avec eI la densité spectrale de puissance de la source de courant modélisée et  $\Delta f$  la bande de fréquences étudiée.

### > Bruit thermique

En dernier lieu, nous retrouvons le bruit thermique. Celui-ci correspond à la génération de bruit par agitation thermique des porteurs de charge, c'est-à-dire les électrons ici. Ce bruit est directement lié à la température dans les conducteurs et semi-conducteurs. Ce bruit s'exprime en Joule (*J*). L'expression de l'énergie moyenne de chaque électron (*E*) se définit par :

$$E = k_B T (1-9)$$

Avec  $k_B$  la constante de Boltzmann égale à 1,3806.10<sup>-23</sup> J/K et T la température absolue en Kelvin. Ce bruit thermique est associé à tous les composants possédant une résistance électrique non nulle et s'exprime en V<sup>2</sup>. La tension moyenne de ce bruit est exprimée par :

$$\overline{v_N^2} = 4k_B T R \Delta f \tag{1-10}$$

Avec R la résistance électrique du dipôle,  $\Delta f$  la largeur de bande de fréquence étudiée et  $\overline{v_N^2}$  le carré de la tension moyenne de bruit.

La densité spectrale de ce bruit étant constante dans le domaine fréquentiel, ce bruit est alors considéré comme un bruit blanc. Afin de limiter au maximum l'influence de ce bruit, il est judicieux de réduire la bande passante des circuits au strict nécessaire.

#### 2.5.2. Jitter

L'analyse du jitter constitue la pierre angulaire des systèmes de communications. Ce dernier correspond au comportement des signaux dans le domaine temporel et permet de dresser les déviations des points de leurs positions optimales. Ce sont ces déviations que l'on nomme *jitter* (ou *gigue*) [26].

Le jitter est un paramètre s'exprimant soit en unité temporelle (ns, ps, fs, ...) soit en unité intervalle (UI). Le terme UI correspond à la proportion du jitter total par le temps bit ( $t_{bit}$ ), et se définit par :

$$Jitter = \frac{TJ}{t_{bit}} \tag{1-11}$$

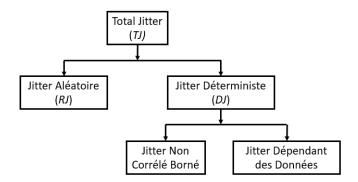

Le Jitter Total (TJ), se décompose en deux catégories de jitter majeurs : le jitter déterministe (DJ) d'une part et le jitter aléatoire (RJ), d'autre part.

Figure 2-18 : Catégories de jitter [27]

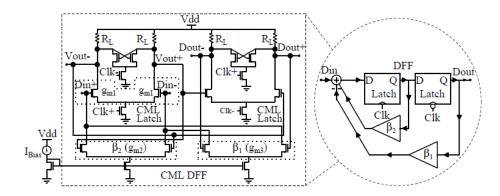

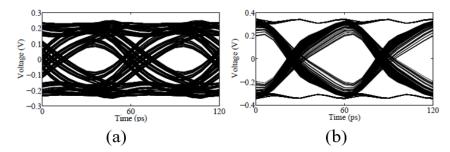

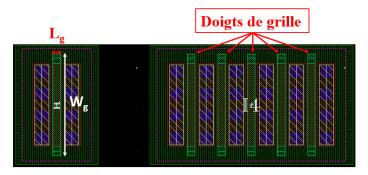

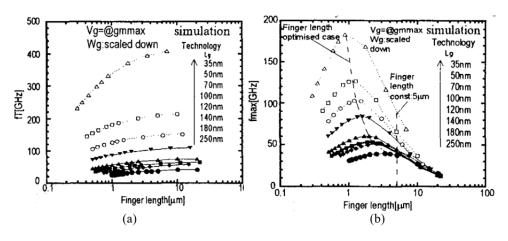

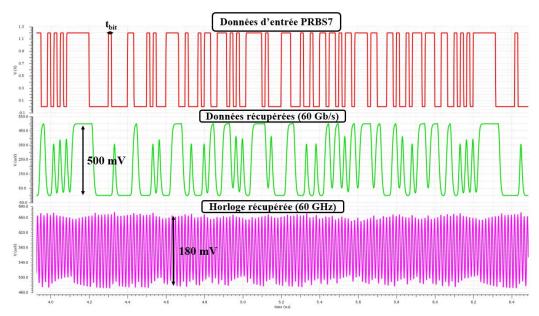

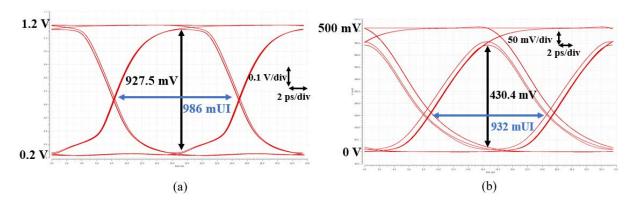

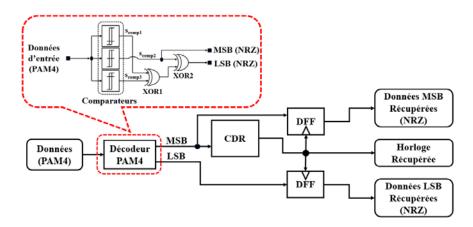

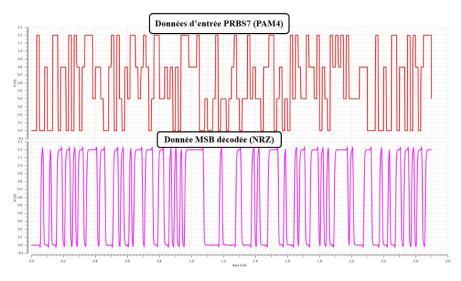

Le *jitter déterministe*, contrairement au jitter aléatoire, se qualifie par des causes spécifiques et reproductibles. Diverses sources de jitter déterministe sont reconnues et incluent *crosstalk*, interférences électromagnétiques, .... Celui-ci peut aussi bien être corrélé ou non au jitter des données.