### Development and evaluation of a new heterojunction bipolar transistor architecture for high-performance and low-cost 55 nm BiCMOS technology

Edoardo Brezza

#### ▶ To cite this version:

Edoardo Brezza. Development and evaluation of a new heterojunction bipolar transistor architecture for high-performance and low-cost 55 nm BiCMOS technology. Micro and nanotechnologies/Microelectronics. Université de Lille, 2022. English. NNT: 2022ULILN032. tel-04086294

#### HAL Id: tel-04086294 https://theses.hal.science/tel-04086294v1

Submitted on 2 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Université de Lille

Ecole Doctorale Sciences de l'Ingénierie et des Systèmes

## THESE

pour l'obtention du grade de Docteur de l'Université de Lille

Specialité: Electronique, Microélectronique, Nanoélectronique et Micro-ondes

par

Edoardo BREZZA

soutenue le 16 décembre 2022 à Grenoble

Development and Evaluation of a New Si/SiGe Heterojunction Bipolar Transistor Architecture for a High-Performance and Low Cost 55 nm BiCMOS technology.

Membres du Jury:

Présidente du Jury Pr. Florence PODEVIN - TIMA UGA Pr. Fabien PASCAL - IES Université de Montpellier Rapporteur Pr. Dimitri LEDERER - UCLouvain Rapporteur Dr. Virginie NODJIADJIM - III-V Lab Examinatrice Pr. Thomas ZIMMER - IMS Bordeaux Examinateur Dr. Pascal CHEVALIER - STMicroelectronics Examinateur Dr. Alexis GAUTHIER - STMicroelectronics Examinateur Pr. Christophe GAQUIERE - IEMN Directeur de Thèse Pr. Associé Nicolas DEFRANCE - IEMN Encadrant invité

# Université de Lille

Ecole Doctorale Sciences de l'Ingénierie et des Systèmes

## THESE

pour l'obtention du grade de Docteur de l'Université de Lille

Specialité: Electronique, Microélectronique, Nanoélectronique et Micro-ondes

par

Edoardo BREZZA

soutenue le 16 décembre 2022 à Grenoble

Développement et Evaluation d'une Nouvelle Architecture de Transistor Bipolaire à Hétérojonction Si/SiGe pour Technologie BiCMOS 55nm Haute-Performance et Faible-Coût

Membres du jury:

Présidente du Jury Pr. Florence PODEVIN - TIMA UGA Pr. Fabien PASCAL - IES Université de Montpellier Rapporteur Rapporteur Pr. Dimitri LEDERER - UCLouvain Dr. Virginie NODJIADJIM - III-V Lab Examinatrice Pr. Thomas ZIMMER - IMS Bordeaux Examinateur Dr. Pascal CHEVALIER - STMicroelectronics Examinateur Dr. Alexis GAUTHIER - STMicroelectronics Examinateur Pr. Christophe GAQUIERE - IEMN Directeur de Thèse Pr. Associé Nicolas DEFRANCE - IEMN Encadrant invité

Les cent-cinquante pages de ce manuscrit ne suffiraient pas à décrire les trois années (et demi) folles et denses pour lesquelles le travail de cette thèse est raison et cadre.

Laissez-moi pour autant utiliser ce petit espace pour rendre honneur à qui fait désormais partie de ma collection de papillons. Ces papillons très chers à moi car trouvés dans mon jardin, ceux qui m'ont permis de fleurir encore et encore dans chaque saison, ceux qui m'ont fait savourer ces timides et fugaces éclaircis de beauté.

Mes remerciements vont à vous.

Aux Rapporteurs et au Jury, qui ont accepté d'évaluer mon travail en lui donnant ainsi cette dignité académique qui me permet d'affirmer que j'ai contribué à étendre la connaissance humaine. Grâce à vous j'accomplis un rêve d'enfance.

A Christophe, qui sans me connaître a choisi de me suivre de loin avec son regard bienveillant et de me diriger jusqu'à la fin de ce parcours. C'est grâce à ta confiance si je suis arrivé ici aujourd'hui.

A Pascal, qui a cru en moi quand encore je ne parlais pas Français et je n'étais qu'un jeune perdu en face au futur. Si aujourd'hui je peux me rapprocher à la table des grands, c'est parce que tu m'as montré ce que ce travail avait à me donner.

A Nicolas, Etienne et ceux que j'ai trouvé en venant à l'IEMN. Lille n'a été qu'une parenthèse, mais vous m'avez donné le plaisir de la découverte humaine et scientifique au même temps.

A Alexis, Victor, Aude et la multitude de personnes que j'ai rencontré à ST et avec lesquelles j'ai partagé quotidiennement ce bout de chemin. Vous avez été mes maîtres, mes copains d'aventure, ma famille. Si ces travaux ont put germer, c'est grâce à vous.

A Paul et Justine, doctorants qui avec moi se sont formés sur ce projet. J'ai aimé chaque table de split, chaque plaque ratée, chaque bière à la Bobine. Vous avez été une inspiration constante.

Aux amis de Grenoble, à ceux de l'Hôtel Grenette, à ceux qui sont partis. Ces nuits fauves ne furent qu'une excuse pour célébrer le feu qui nous brûle dedans. Vous m'avez appris le goût de vivre la vie en chemin, à fond, sans peur. Aux amis du Caffé Schiapparelli. Partis ensemble pour construire notre futur, chacun a enfin entrepris son voyage pour achever les étoiles. Vous m'avez appris à faire les choses sérieusement sans se prendre trop au sérieux. Gaudeamus, igitur !

Aux amis de Casale, aux frères de Asha, à Chiara. Je connais la plupart de vous depuis notre adolescence : regardez comment nous avons grandi ! Vous me rappelez que, peu importe où le vent emportera nos graines, ce seront toujours les racines à nous nourrir. La terre du Monferrato est toujours la plus douce.

A mes parents et à ma famille, qui larmes aux yeux et coeur en fête m'ont vu partir vers une terre étrangere. Vous m'avez bèni avec la faim pour la vie et le soif pour le défi. Si je peux vivre cette drôle de vie, c'est premièrement grâce à vous.

A Antigone, Flora, Nefele, Pandora et toutes les muses sans nom qui ont été croix et délice de mes jours. Vous avez eu mon cœur, mes poèmes, mes nuits. Les fruits les plus amers viennent toujours des plus belles fleurs. N'arrêtez jamais d'être si merveilleuses.

A Vanessa et à ceux qui m'ont offert leur étincelle pour rallumer ma flamme. Un feu qui trop souvent s'est laissé éteindre par le blizzard pendant ces jours sombres et sans issue. Vous me permettez de regarder un peu plus loin quand je ne vois que le noir.

A ceux que je ne peux pas remercier ici, pèlerins de passage dans ma vie qui ont contribué à rendre cette histoire un chef d'œuvre. Si c'est vrai qu'il faut faire sa propre vie comme on fait une oeuvre d'art, vous êtes les diaprures de cette peinture.

Mes chers copains, c'est enfin le moment de se saluer. Le Zéphyr souffle fort et je dois hisser mes voiles pour reprendre mon voyage.

A vous, tous : merci pour les roses, merci pour les épines.

Considerate la vostra semenza: Fatti non foste a viver come bruti Ma per seguir virtute e canoscenza

Considérez la race dont vous êtes, Créés non pas pour vivre comme brutes, Mais pour suivre vertu et connaissance.

Consider the seed that gave you birth: You were not made to live as brutes, But to follow virtue and knowledge.

Dante Alighieri, *La Divina Commedia* Inferno, Canto XXVI, vv.118-120

## Contents

| C  | onten  | nts      | vii                                                                                                                      |  |

|----|--------|----------|--------------------------------------------------------------------------------------------------------------------------|--|

| Li | st of  | Figure   | es xi                                                                                                                    |  |

| Li | st of  | Figure   | es xiv                                                                                                                   |  |

| Li | st of  | Tables   | s xv                                                                                                                     |  |

| Li | st of  | Tables   | xvii                                                                                                                     |  |

| G  | lossai | ry       | xix                                                                                                                      |  |

| Ι  | Intr   | oducti   | on 1                                                                                                                     |  |

|    | 1      | Contex   | $\operatorname{ct}$                                                                                                      |  |

|    | 2      | Figure   | s Of Merit                                                                                                               |  |

|    |        | 2.1      | Voltage references and operating zones                                                                                   |  |

|    |        | 2.2      | Currents and gain                                                                                                        |  |

|    |        | 2.3      | Early voltages                                                                                                           |  |

|    |        | 2.4      | Breakdown voltages                                                                                                       |  |

|    |        | 2.5      | Transit frequency                                                                                                        |  |

|    |        | 2.6      | Maximum oscillation frequency                                                                                            |  |

|    |        | 2.7      | Capacitances and resistances                                                                                             |  |

|    |        | 2.8      | Power behavior at high frequency                                                                                         |  |

|    | 3      | State of | of the art $\ldots \ldots 14$ |  |

|    |        | 3.1      | Global Foundries 15                                                                                                      |  |

|    |        | 3.2      | Infineon                                                                                                                 |  |

|    |        | 3.3      | IHP 16                                                                                                                   |  |

|    |        | 3.4      | NXP                                                                                                                      |  |

|    |        | 3.5      | STMicroelectronics                                                                                                       |  |

|   |     | 3.6     | Tower Se    | emiconductor                                                                            | 19      |

|---|-----|---------|-------------|-----------------------------------------------------------------------------------------|---------|

|   | 4   | From 1  | DPSA-SE     | G to EXBIC architecture: starting point                                                 | 20      |

|   |     | 4.1     |             | Polysilicon Self-Aligned Selective Epitaxial Growt         SEG) architecture            | h<br>20 |

|   |     | 4.2     | Èpitaxia    | l eXtrinsic Base Isolated from the Collector                                            |         |

|   |     |         | (EXBIC      | ) architecture $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$  | 25      |

|   | 5   | Object  | tives of th | nis work                                                                                | 32      |

| Π | Arc | hitectı | ıre revie   | W                                                                                       | 37      |

|   | 1   | Collec  | tor modu    | le                                                                                      | 42      |

|   |     | 1.1     | Ion impl    | antation defects suppression                                                            | 44      |

|   |     |         | 1.1.a       | TCAD simulation of stress distribution in the                                           |         |

|   |     |         |             | substrate                                                                               | 44      |

|   |     |         | 1.1.b       | Silicon testing                                                                         | 45      |

|   |     |         | 1.1.c       | Device functionality                                                                    | 52      |

|   |     | 1.2     | Super Sl    | hallow Trench Isolation (SSTI) design                                                   | 54      |

|   |     |         | 1.2.a       | Ring-shaped SSTI                                                                        | 54      |

|   |     |         | 1.2.b       | Single-trench SSTI                                                                      | 56      |

|   |     |         | 1.2.c       | Electrical characterization of the two SSTI                                             |         |

|   |     |         |             | integrations                                                                            | 58      |

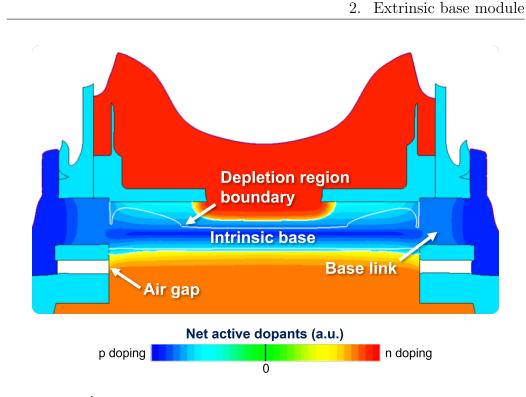

|   | 2   | Extrin  | sic base r  | nodule                                                                                  | 60      |

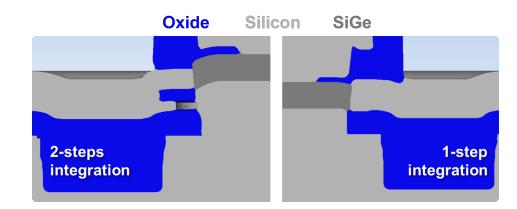

|   |     | 2.1     | 2-step ex   | xtrinsic base integration                                                               | 61      |

|   |     |         | 2.1.a       | Air gaps                                                                                | 61      |

|   |     |         | 2.1.b       | Base link                                                                               | 64      |

|   |     | 2.2     | 1-step ex   | xtrinsic base integration                                                               | 66      |

|   |     |         | 2.2.a       | Air gaps                                                                                | 67      |

|   |     |         | 2.2.b       | Vertical alignment                                                                      | 69      |

|   |     |         | 2.2.c       | Overlay mismatch tolerance                                                              | 70      |

|   |     |         | 2.2.d       | Epitaxial growth parameters                                                             | 71      |

|   |     | 2.3     | Electrica   | al characterization of the two extrinsic base in-                                       |         |

|   |     |         | tegration   | 18                                                                                      | 71      |

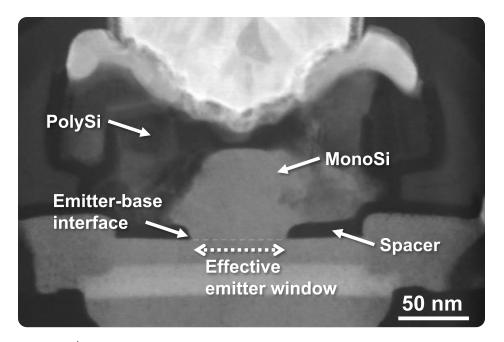

|   | 3   | Emitte  | er module   |                                                                                         | 78      |

|   |     | 3.1     | Emitter-    | base interface cleaning                                                                 | 79      |

|   |     |         | 3.1.a       | Interface impurities                                                                    | 82      |

|   |     |         | 3.1.b       | Emitter resistance measurements                                                         | 88      |

|   | 4   | Archit  | ecture rev  | view conclusion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 90      |

| III          | Elec  | trical optimization 95                                                                                       |  |  |  |  |

|--------------|-------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              | 1     | Collector module                                                                                             |  |  |  |  |

|              |       | 1.1 Resistance reduction                                                                                     |  |  |  |  |

|              |       | 1.1.a Non-product wafer testing 100                                                                          |  |  |  |  |

|              |       | 1.1.b Device testing $\ldots \ldots 103$      |  |  |  |  |

|              |       | 1.2 Base-collector junction tuning                                                                           |  |  |  |  |

|              |       | 1.3 Impact of epitaxial collector thickness variability 108                                                  |  |  |  |  |

|              |       | 1.4 Future studies                                                                                           |  |  |  |  |

|              | 2     | Extrinsic base module                                                                                        |  |  |  |  |

|              |       | 2.1 Extrinsic base thickness                                                                                 |  |  |  |  |

|              |       | 2.2 Germanium percentage                                                                                     |  |  |  |  |

|              |       | 2.3 Boron concentration                                                                                      |  |  |  |  |

|              |       | 2.4 Future studies                                                                                           |  |  |  |  |

|              | 3     | Intrinsic base module                                                                                        |  |  |  |  |

|              |       | 3.1 Boron concentration and doped layer width 127                                                            |  |  |  |  |

|              |       | 3.2 Future studies                                                                                           |  |  |  |  |

|              | 4     | Emitter module                                                                                               |  |  |  |  |

|              |       | 4.1 Spacers sizing $\ldots \ldots 134$ |  |  |  |  |

|              |       | 4.2 Future studies $\ldots \ldots 138$ |  |  |  |  |

|              | 5     | Load-pull measurements                                                                                       |  |  |  |  |

|              | 6     | Optimization conclusion                                                                                      |  |  |  |  |

| IV           | Con   | clusion 151                                                                                                  |  |  |  |  |

| $\mathbf{A}$ | Mod   | leling methods 159                                                                                           |  |  |  |  |

|              | 1     | Current components                                                                                           |  |  |  |  |

|              | 2     | Sheet resistance                                                                                             |  |  |  |  |

|              | 3     | Collector resistance                                                                                         |  |  |  |  |

|              | 4     | Base resistance                                                                                              |  |  |  |  |

| Au           | thor  | s' publications 165                                                                                          |  |  |  |  |

| Bil          | bliog | raphy 167                                                                                                    |  |  |  |  |

## List of Figures

| I.1      | Bardeen, Brattain and Shockley                                     | 2   |

|----------|--------------------------------------------------------------------|-----|

| I.2      | Typical applications of BiCMOS technologies in final devices.[9]   | 4   |

| I.3      | Schematic of an npn transistor with conventional currents and      |     |

|          | voltages                                                           | 6   |

| I.4      | Regions of operation of a bipolar transistor.                      | 6   |

| I.5      | Impact of some current non-idealities on Gummel plot               | 8   |

| I.6      | Schematic representing the impact of junction biasing on de-       |     |

|          | pletion zones.                                                     | 9   |

| I.7      | Published values of $f_T/f_{MAX}$ achieved in the recent years by  |     |

|          |                                                                    | 14  |

| I.8      | Schematic cross section of the BiCMOS platform presented by        |     |

|          | Pekarik et al. [46]                                                | 15  |

| I.9      | TEM cross section of the Elevated Extrinsic Base - Selective       |     |

|          | Epitaxial growth (EBL-SEG) HBT presented by Manger et al.          |     |

|          |                                                                    | 16  |

| I.10     | TEM cross section of the Elevated Extrinsic Base - Non Se-         |     |

|          | lective Epitaxial Growth (EEB - NSEG) HBT presented by             |     |

|          |                                                                    | 17  |

| I.11     | TEM cross section of the Double Polysilicon Self-Aligned-Selective |     |

|          | Epitaxial Growth (DPSA-SEG) presented by Trivedi et al. [61].      | 18  |

| I.12     |                                                                    |     |

|          | Epitaxial Growth (SE-NSEG) HBT architecture presented by           |     |

| Tito     |                                                                    | 19  |

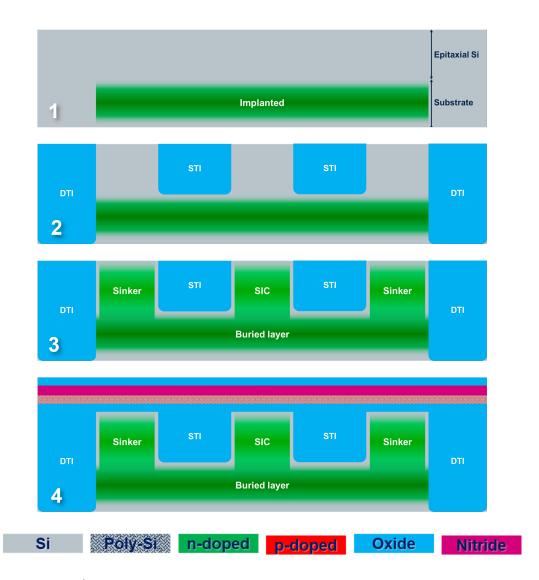

| I.13     | Schematic process flow of a B55 DPSA-SEG. Part 1 Picture           | ~ ~ |

| Tito     |                                                                    | 22  |

| I.13     | 1                                                                  | ~~  |

| <b>T</b> |                                                                    | 23  |

| 1.14     | Comparison between different DPSA-SEG HBT collectors               | 24  |

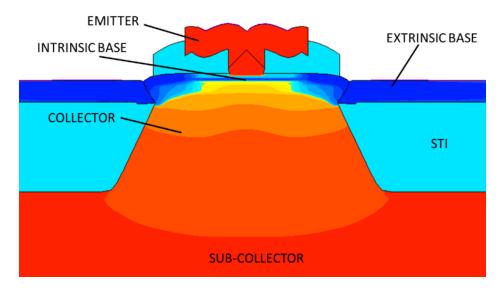

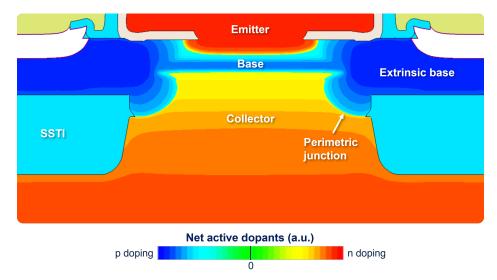

| I.15  | Original EXBIC structure from Technology Computer-Aided<br>Design (TCAD) simulation.                                                                                                  | 25 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

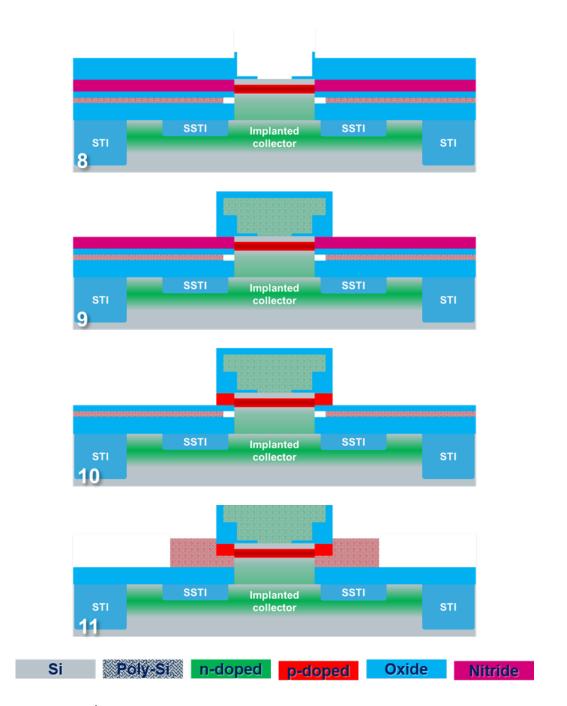

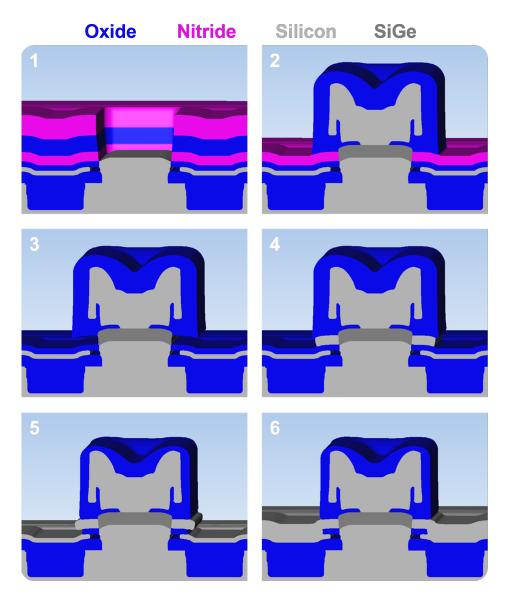

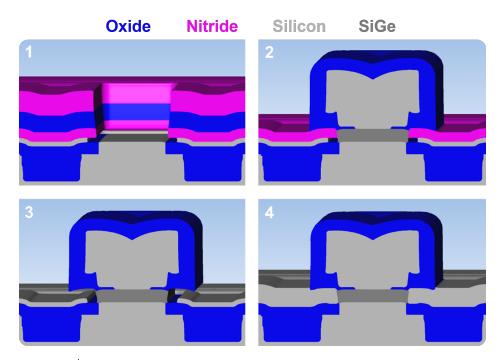

| I.16  | Schematic process flow of a Preliminary EXBIC. Part 1 Pic-<br>ture not to scale.                                                                                                      | 28 |

| I.16  | Schematic process flow of a Preliminary EXBIC. Part 2 Pic-<br>ture not to scale.                                                                                                      | 29 |

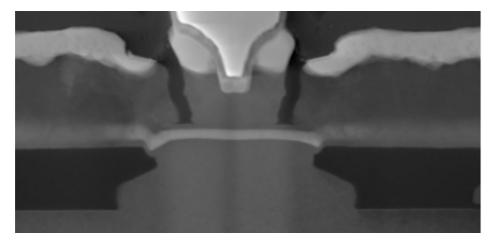

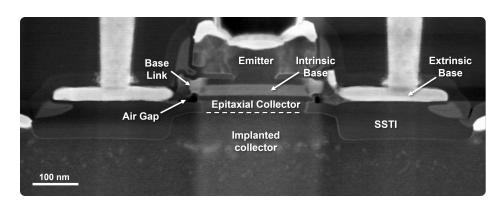

| I.17  | TEM cross-section of an HBT realized with the preliminary<br>EXBIC architecture.                                                                                                      | 30 |

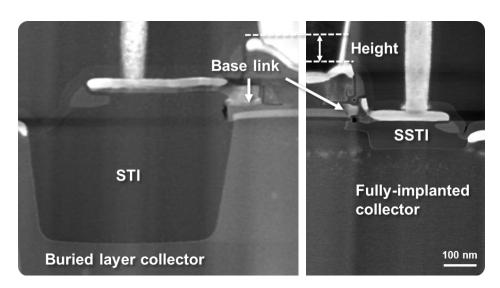

| I.18  | Comparison between TEM cross-sections of B55 DPSA-SEG and POR EXBIC transistors.                                                                                                      | 31 |

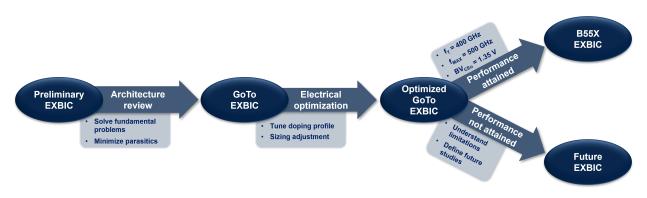

| I.19  | Development process and objectives of this work                                                                                                                                       | 33 |

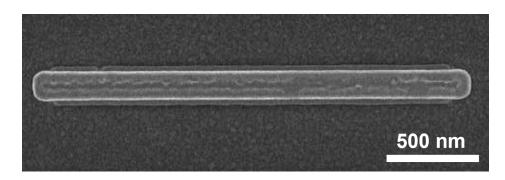

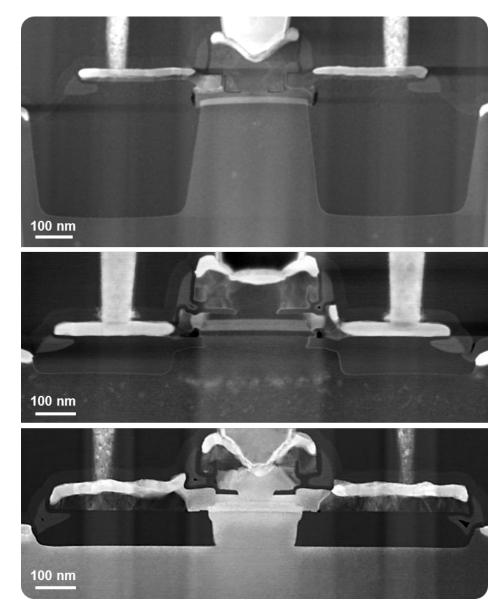

| II.1  | First functional EXBIC HBT                                                                                                                                                            | 39 |

| II.2  | Modules impacted by the architecture review process and rel-<br>ative scopes                                                                                                          | 41 |

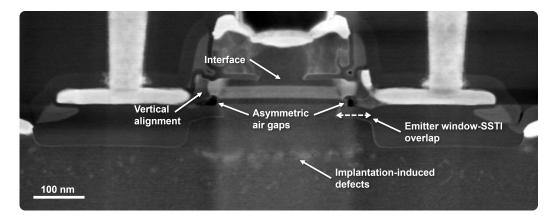

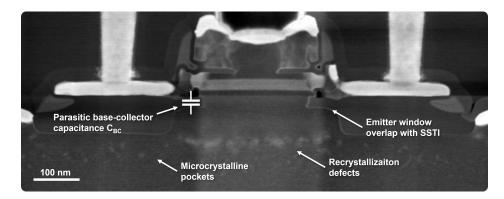

| II.3  | TEM cross-section showing the weak points of the collector in<br>the preliminary EXBIC architecture.                                                                                  | 43 |

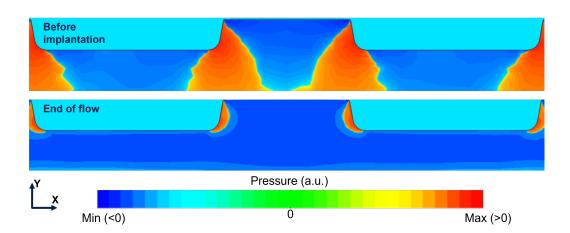

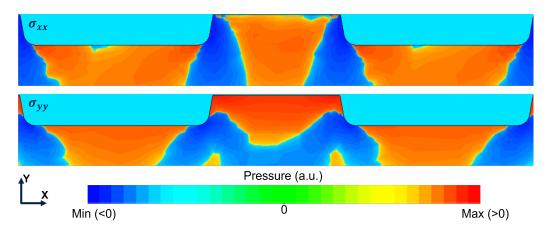

| II.4  | TCAD simulation of a device depicting silicon constraint be-<br>tween SSTIs before implantation and at the end of the pro-<br>duction flow. Normalized values                         | 46 |

| II.5  | TCAD simulation of a device depicting components of silicon<br>constraint between SSTIs before implantation. Normalized<br>values.                                                    | 46 |

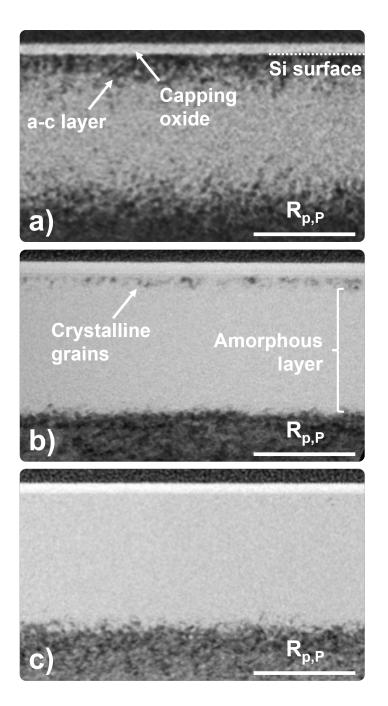

| II.6  | TEM cross-section of Non-Product (NP) wafers after implan-<br>tation with phosphorus doses of a) $P = C/3$ b) $P = C/2$ c)<br>P = C                                                   | 48 |

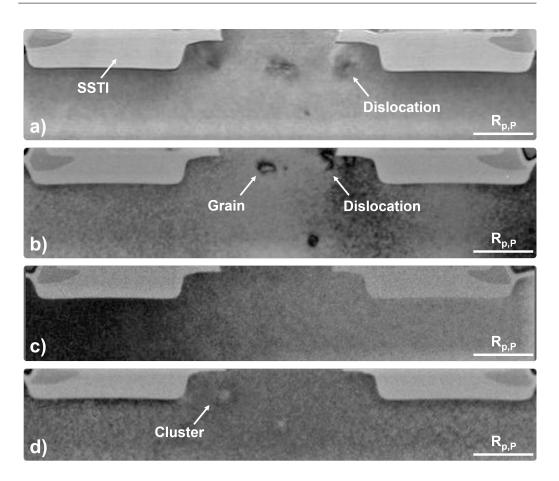

| II.7  | TEM cross-section of patterned wafers implanted with phos-<br>phorus doses of a) $P = C/3$ b) $P = C/2$ c) $P = C$ d) $P = 2C$ .<br>Cuts performed at the end of the production flow. | 50 |

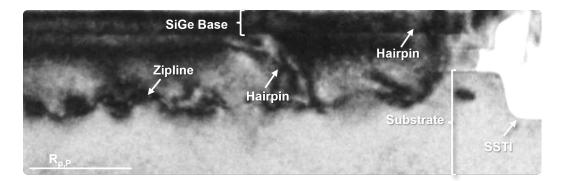

| II.8  | Longitudinal TEM cross-section of a complete device implanted<br>with a phosphorus dose $P = C/2$ .                                                                                   | 50 |

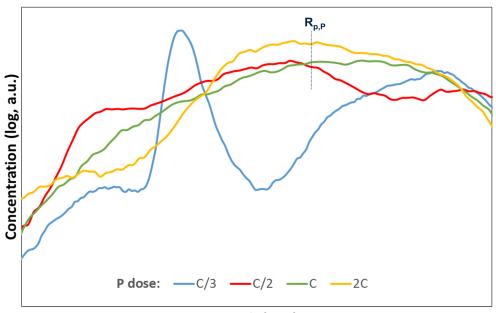

| II.9  | TOF-SIMS profiles of carbon measured on patterned wafers.                                                                                                                             | 51 |

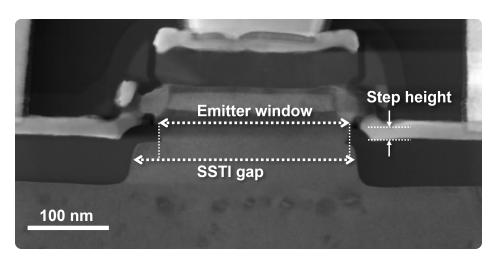

|       | Issues of a ring SSTI                                                                                                                                                                 | 55 |

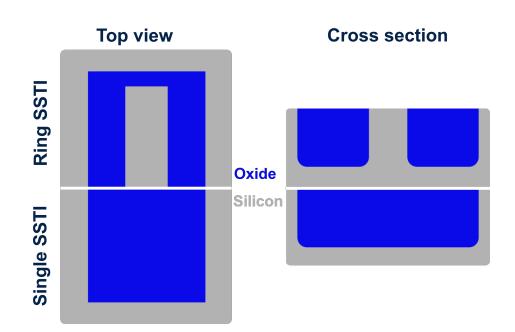

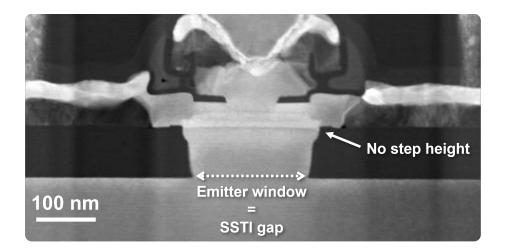

| II.11 | Top view and cross-section schematics comparing the ring and single SSTI integrations after trench filling and planarization.                                                         | 56 |

| II.12 | Advantages of a single SSTI                                                                                                                                                           | 57 |

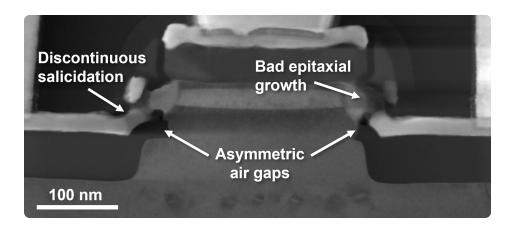

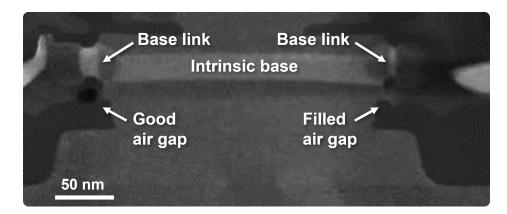

|       | TEM cross-section showing the flaws of the 2-step extrinsic                                                                                                                           |    |

|       | base integration.                                                                                                                                                                     | 60 |

| II.14 Process flow of the 2-step extrinsic base integration simulated                                     |    |

|-----------------------------------------------------------------------------------------------------------|----|

| with Coventor SEMulator 3D                                                                                | 62 |

| II.15 TEM cross section of an HBT presenting both a well-formed                                           |    |

| air gap and a parasitic base-collector junction.                                                          | 63 |

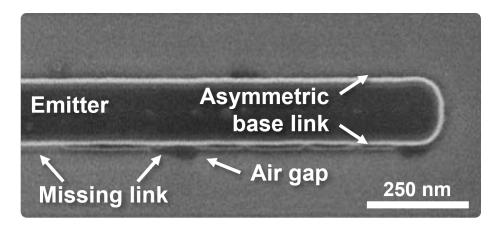

| II.16 SEM top-view picture of an HBT after base link selective epi-                                       |    |

| taxy. Typical defects are highlighted.                                                                    | 64 |

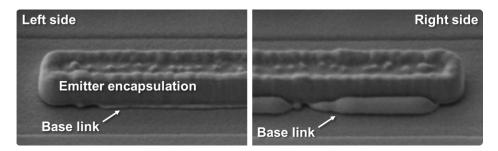

| II.17 Tilted SEM views of the base link on the two sides of an HBT.                                       | 65 |

| II.18 SEM top-view picture of an HBT presenting a uniform base link on the two sides                      | 66 |

| II.19 Process flow of the 1-step extrinsic base integration simulated                                     | 00 |

| - •                                                                                                       | 68 |

|                                                                                                           | 00 |

| II.20 TEM cross-section of the first HBT realized with the 1-step                                         | co |

| extrinsic base integration                                                                                | 68 |

| II.21 Synopsis Sentaurus TCAD simulation of the doping concen-                                            | 60 |

| tration obtained with a heavily-doped extrinsic base.                                                     | 69 |

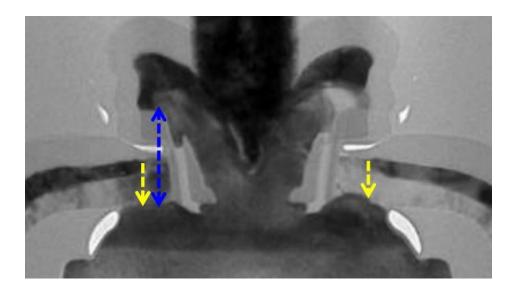

| II.22 Comparison of vertical alignment in the two extrinsic base                                          | -  |

| integrations.                                                                                             | 70 |

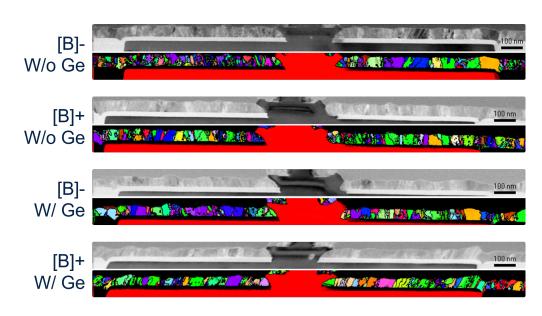

| II.23 TEM cross section and ASTAR grain orientation analysis on                                           |    |

| 1-step extrinsic base realized with four different combinations                                           |    |

| of boron and germanium                                                                                    | 72 |

| II.24 TCAD simulation depicting the depletion regions in a 2-step                                         |    |

| extrinsic base integration                                                                                | 75 |

| II.25 TEM cross-section depicting the main characteristics of the                                         |    |

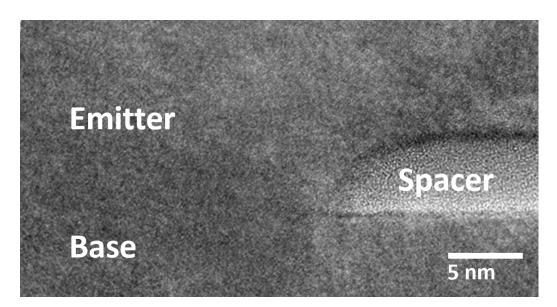

| emitter in an EXBIC HBT                                                                                   | 79 |

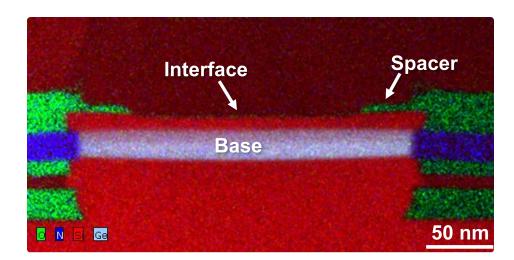

| II.26  TEM + EDX  cross-section highlighting the presence of an in-                                       |    |

| terface at the emitter-base junction. Picture taken after emit-                                           |    |

| ter deposition. $\ldots$ | 80 |

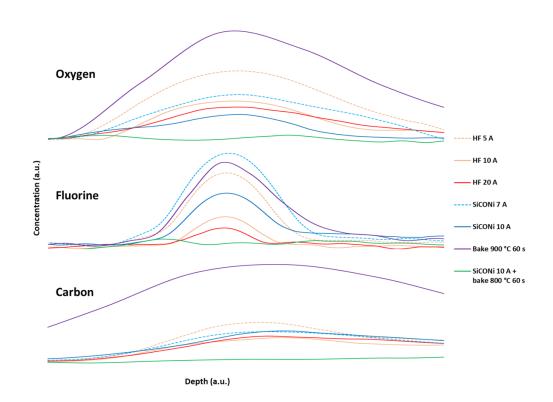

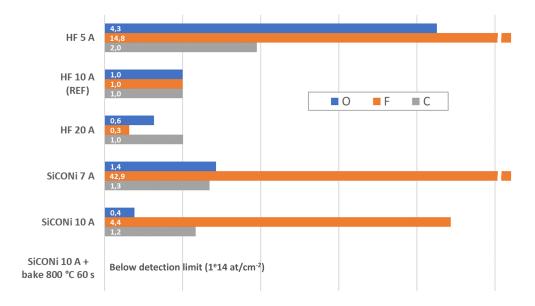

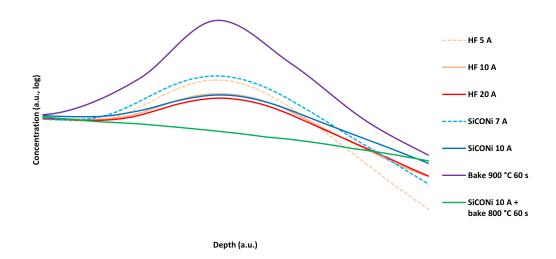

| II.27 TOF-SIMS profiles of oxygen, fluorine and carbon measured in                                        |    |

| a span of 10 nm around the emitter-base interface. Detection                                              |    |

| limit of 1e18 $at/cm^{-3}$ .                                                                              | 82 |

| II.28 Relative total dose of oxygen, fluorine and carbon at the inter-                                    |    |

| face. Integration performed on the curves of figure II.27 over                                            |    |

| the same span. HF 10 A is taken as reference. $\ldots$ $\ldots$ $\ldots$                                  | 83 |

| II.29 TOF-SIMS profiles of arsenic in a span of 10 nm around the                                          |    |

| emitter-base interface.                                                                                   | 84 |

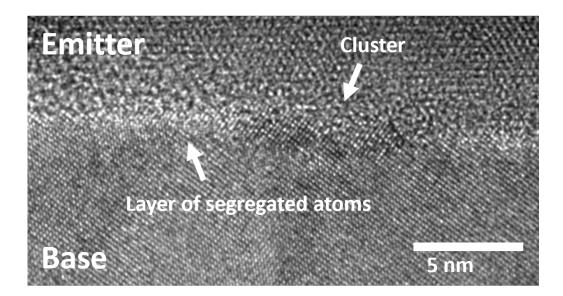

| II.30 HR-TEM of the emitter-base interface of a device treated with                                       |    |

| HF 10 A. A layer of impurities is present all over, with some                                             |    |

| scattered clusters interrupting it. Crystalline orientation of                                            |    |

| the emitter differs from the base.                                                                        | 85 |

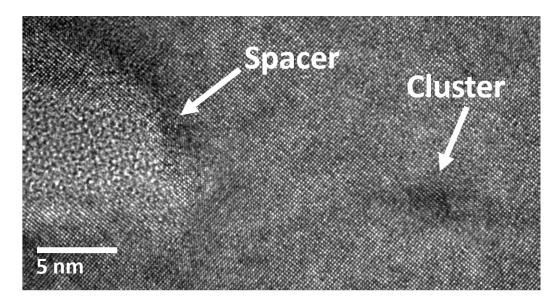

|                                                                                                           |    |

| II.31 HR-TEM of the emitter-base interface of a device treated with                        |

|--------------------------------------------------------------------------------------------|

| Siconi 10 A. Lattice matching between emitter and base is good. 86                         |

| II.32 Detail of a cluster observed at the emitter-base interface of a                      |

| device treated with Siconi 10 A                                                            |

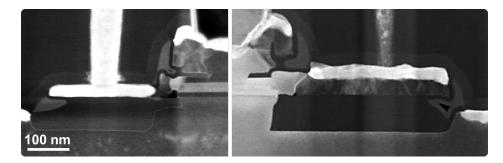

| II.33 TEM cross-sections comparing the preliminary EXBIC archi-                            |

| tecture with the Go To EXBIC architecture                                                  |

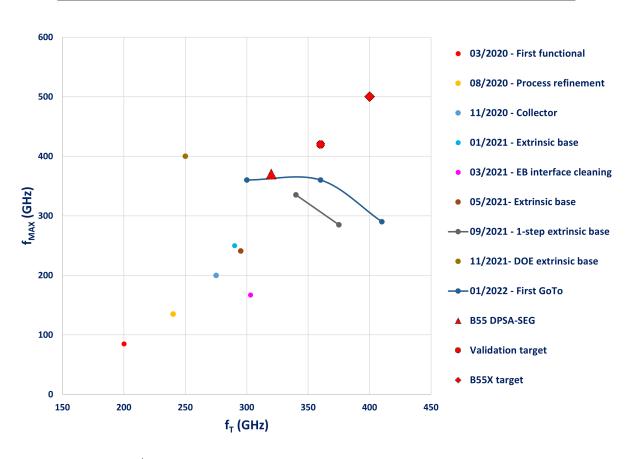

| II.34 $f_T$ and $f_{MAX}$ progression on the lots producing during the                     |

| development of the Go To EXBIC architecture                                                |

|                                                                                            |

| III.1 Modules impacted by the architecture optimization process                            |

| and relative objectives. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $ |

| III.2 TEM cross-section depicting the two main contribution of col-                        |

| lector implantation on device characteristics.                                             |

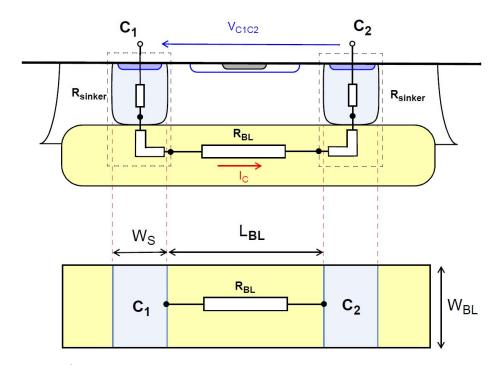

| III.3 Collector resistance $R_C$ components                                                |

| III.4 Sheet resistances measured on plain sheet wafers implanted                           |

| with different carbon energies and phosphorus doses 101                                    |

| III.5 Phosphorus distributions obtained by TOF-SIMS on wafers                              |

| implanted and annealed. Variation of relative phosphorus dose                              |

| and carbon energy                                                                          |

| III.6 Comparison of two transistors featuring different epitaxial col-                     |

| lector thicknesses                                                                         |

| III.7 TEM cross-section highlighting the parameters investigated                           |

| for the 1-step extrinsic base optimization                                                 |

| III.8 TEM cross-section + EDX coloring of two devices obtained                             |

| within the base link thickness study.                                                      |

| III.9 Schematic of the intrinsic base doping profile integrated in the                     |

| EXBIC HBT                                                                                  |

| III.10Boron and germanium profiles in the base obtained by TOF-                            |

| SIMS at the end of the production flow                                                     |

| III.11TEM cross-section of a device obtained within the experiment                         |

| on the effective emitter window variation                                                  |

| III.12Output power $P_{OUT}$ as a function of input absorbed power                         |

| $P_{ABS}$ measured on 0.2×0.5 $\mu m^2$ DPSA-SEG and EXBIC tran-                           |

| sistors                                                                                    |

| III.13Power gain $G_p$ as a function of input absorbed power $P_{ABS}$                     |

| measured on $0.2 \times 0.5 \ \mu m^2$ DPSA-SEG and EXBIC transistors. 142                 |

| III.14Power Added Efficiency $PAE$ as a function of the input ab-                          |

| sorbed power $P_{ABS}$ measured on $0.2 \times 0.5 \ \mu m^2$ DPSA-SEG and                 |

| EXBIC transistors                                                                          |

|                                                                                            |

| III.1 | 5Chronological performance progression of best $f_T/f_{max}$ for<br>each lot produced in the optimization phase                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | Best $f_T/f_{MAX}$ of all the functional lots produced within this<br>work                                                      |

|       | preliminary EXBIC and GoTo EXBIC                                                                                                |

|       | Schematic describing the model used for extracting the sinker and buried layer components of the collector resistance $R_C$ 162 |

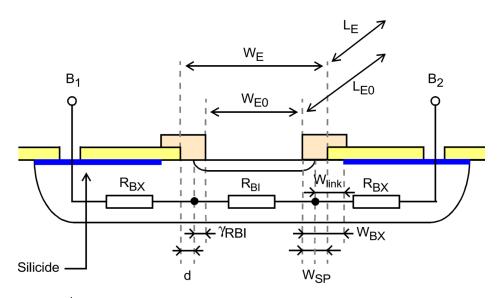

| A.2   | Schematic describing the model used for extracting the base resistance $R_B$ components                                         |

## List of Tables

| I.1         | Comparison of target values defined for main figures of merit.                                                                      | 32         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|------------|

| II.1        | Some Figure Of Merit (FOM)s comparing a B55 DPSA-SEG, one of the first functional EXBIC and the target values for the               |            |

|             | Go To EXBIC architecture integration                                                                                                | 38         |

| II.2        | Average values and relative standard deviation of low, medium<br>and high injection collector currents $I_C$ and correspondent ide- | <b>F</b> 0 |

| TT O        | ality factor $\eta_{I_C}$ for different phosphorus doses                                                                            | 53         |

| II.3        | Figures of merit of two devices integrating respectively a ring-<br>shaped SSTI and a single-trench SSTI.                           | 58         |

| II.4        | Current-related figures of merit measured on two EXBIC HBTs produced with different extrinsic base integrations.                    | 73         |

| II.5        | Perimetric and surfacical component of the base current $I_B$<br>at various injection levels extracted for both integrations of     |            |

|             | extrinsic base                                                                                                                      | 74         |

| II.6        | Junction-related figures of merit measured on HBTs produced                                                                         | 11         |

| 11.0        | with different extrinsic base integrations                                                                                          | 76         |

| II.7        | Parasitics measured on two HBTs produced with different ex-                                                                         |            |

| <b>TT</b> 0 | trinsic base integrations.                                                                                                          | 76         |

| II.8        | Frequencies measured on two HBTs produced with different extrinsic base integrations.                                               | 76         |

| II.9        | Calculated diffusion lengths for a reference concentration of                                                                       |            |

|             | boron $[B] = 1e20 \ cm^{-2}$ .                                                                                                      | 81         |

| II.10       | Average and standard deviation of emitter resistances mea-<br>sured on devices with different emitter-base interface cleaning       |            |

|             | processes                                                                                                                           | 89         |

| III.1       | Resistivity measured on NP and patterned wafers implanted<br>with different carbon energies and phosphorus doses                    | 104        |

| III.2 Currents and related parameters measured on wafers implanted                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| with various phosphorus doses and carbon energies 105                                                                                                         |

| III.3 Junction-related parameters measured on wafers implanted                                                                                                |

| with various phosphorus doses and carbon energies 106                                                                                                         |

| III.4 Resistances measured on wafers implanted with various phos-                                                                                             |

| phorus doses and carbon energies                                                                                                                              |

| III.5 Maximum frequencies measured on wafers implanted with var-                                                                                              |

| ious pho<br>sphorus doses and carbon energies 107 $$                                                                                                          |

| III.6 Current-related figures of merit measured on devices featuring                                                                                          |

| different collector thicknesses                                                                                                                               |

| III.7 Junction-related figures of merit measured on devices featuring                                                                                         |

| different collector thicknesses                                                                                                                               |

| III.8 Parasitics measured on devices featuring different collector                                                                                            |

| thicknesses. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $112$                                                           |

| III.9 Maximum frequencies measured on devices featuring different                                                                                             |

| collector thicknesses. $\ldots \ldots \ldots$ |

| III.10Extrinsic and intrinsic base resistances of devices with different                                                                                      |

| sacrificial nitride thicknesses and contact zone characteristics. 117                                                                                         |

| III.11Electrical figures of merit of devices with different sacrificial                                                                                       |

| nitride thicknesses and contact zone characteristics. $\ldots$ $\ldots$ 119                                                                                   |

| III.12Figures of merit obtained on devices featuring variations of                                                                                            |

| germanium percentage in the extrinsic base. $\ldots \ldots \ldots \ldots 121$                                                                                 |

| III.13Figures of merit obtained ondevices featuring variations of                                                                                             |

| boron concentration in the extrinsic base. $\ldots \ldots \ldots \ldots \ldots 123$                                                                           |

| III.14Current gain and ideality factors for different boron layer thick-                                                                                      |

| nesses and dopant concentrations                                                                                                                              |

| III.15Breakdown and Early voltages for different boron layer thick-                                                                                           |

| nesses and dopant concentrations                                                                                                                              |

| III.16Parasitic resistances for different boron layer thicknesses and                                                                                         |

| dopant concentrations                                                                                                                                         |

| III.17Maximum $f_T$ and $f_{MAX}$ measured on a golden die for different                                                                                      |

| boron layer thicknesses and dopant concentrations 132                                                                                                         |

| III.18Currents and related parameters measured on HBTs featuring                                                                                              |

| different effective emitter window widths                                                                                                                     |

| III.19Junction-related parameters of HBTs featuring different effec-                                                                                          |

| tive emitter window widths                                                                                                                                    |

| III.20Parasitics extracted on HBTs featuring different effective emit-                                                                                        |

| ter window widths. $\ldots \ldots 137$                                                  |

| III.21Transit and maximum oscillation frequencies extracted on HBTs                            |     |

|------------------------------------------------------------------------------------------------|-----|

| featuring different effective emitter window widths 1                                          | .37 |

| III.22Optimal bias and impedance of HBTs featuring different inte-                             |     |

| grations. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ | 40  |

| III.23Results of load-pull measurements on DPSA-SEG and EXBIC                                  |     |

| transistors                                                                                    | 44  |

| III.24Comparison of target values defined for main figures of merit                            |     |

| and the ones obtained on the best silicon produced within this                                 |     |

| work                                                                                           | .47 |

### Glossary

- **BiCMOS** A technology integrating both Bipolar and CMOS transistors in addition to passives devices on the same wafer.

- **BiCMOS055 (B55)** A 55 nm BiCMOS technology developed by STMicroelectronics, basis of the present study.

- **BiCMOS055X (B55X)** A 55 nm BiCMOS technology developed by STMicroelectronics, context in which this study has been conducted.

- **Bipolar Junction Transistor (BJT)** A type of junction transistor which has been dominant in older analogic and digital technologies.

- Buried OXide (BOX) The oxide layer buried into a SOI substrate.

- **Chemical Mechanical Polishing (CMP)** A process used for planarizing and polishing a wafer. It uses mechanical abrasion along with chemical etching, resulting in a very good surface uniformity.

- Chemical Vapour Deposition (CVD) A deposition technique based on the decomposition of a precursor gas on a solid surface and the consequent deposition of the desired material. Many materials can be deposited by this technique.

- **Complementary Metal Oxide Semiconductor (CMOS)** A logic family based on n- and p-type MOSFET devices, dominant in nowadays digital circuits.

- Double-Polysilicon Self-Aligned Selective Epitaxial Growth (DPSA-SEG) A particular Heterojunciton Bipolar Transistor architecure, also used in STMicroelectronics' BiCMOS055 technology.

- End Of Range (EOR) defects Defects generated outside the range amorphized by ion implantation.

- **Epitaxial eXtrinsic Base Isolated from the Collector (EXBIC)** SiGe Heterojunction Bipolar transistor (HBT) architecture, the name stands for stands for Epitaxial eXtrinsic Base isolated from the Collector

- **Extrinsic collector/base** Collector/base portion not directly playing in the transistor effect. These parts are important because they still play a role as parasitics, potentially having a big impact on performance.

- Figure Of Merit (FOM) A numerical quantity based on one or more characteristics of a system or device that represents a measure of efficiency or effectiveness. (Merriam Webster)

- **Front End Of Line (FEOL)** Part of the fabrication of an integrated circuit consisting in the realization of devices on silicon. It includes all fabrication processes up to the contact.

- Go To EXBIC architecture The EXBIC architecture as defined after solving the problems affecting the preliminary EXBIC architecture. Chacteristic features are single SSTI and 1-step extrinsic base epitaxy.

- Heterojunction Bipolar transistor (HBT) An improved version of the BJT based on heterojunctions.

- **Integrated Device Manufacturer (IDM)** A company responsible for all the aspects of the production of an integrated circuit, from design to fabrication.

- **Intrinsic collector/base** Collector/base portion playing a direct role in the transistor effect. It is generally used to refer to the portion close to the p-n junctions and delimited by the emitter window width.

- Metal Oxide Semiconductor Field Effect Transistor (MOSFET) A modern field-effect transistor, dominant in the nowadays digital circuits for its superior performance in this field.

- Non-Product Wafer (NPW) Wafer not integrating any device structure, i.e. with a plain surface

- **Preliminary EXBIC architecture** The EXBIC architecture as it was at the beginning of this work. Chacteristic features are ring SSTI and 2-step extrinsic base epitaxy.

- **Safe Operating Area (SOA)** Biasing limits beyond which the device could face permanent alteration of its characteristics or destruction.

- Selectively Implanted Collector (SIC) A collector implantation circumscribed below the emitter window and used to adjust the base-collector junction in Hig-Speed HBTs.

- Shallow Trench Isolation (STI) Vertical trench with a depth on the order of the hundreds od nanometers, used for electrical isolation between zones.

- Silicon On Insulator (SOI) Particular type of silicon substrate featuring an oxide layer buried below the surface.

- Smith Chart The Smith chart is a convenient way to represent parameters useful for describing the RF behavior of a device on a complex plane, e.g. impedances, reflection coefficients and scattering parameters.

- Super Shallow Trench Isolation (SSTI) Vertical trench with a depth below 150 nm.

- **Technology Computer-Aided Design (TCAD)** Design of semiconductor devices with the help of computer simulations.

- **Tetraethoxysilane (TEOS)** Chemical compound with the formula  $Si(OC_2H_5)_4$  used as a precursor in silicon oxide Chemical Vapour Deposition (CVD).

- **Time Of Flight Secondary Ion Mass Spectroscopy (TOF-SIMS)** Destructive analysis of the atom distribution present in a bulk. Energetic highmass ions are sent to the surface, detaching the bulk atoms; mass spectroscopy allows to identify the detached atoms.

- **Transient Enhanced Diffusion (TED)** Particularly important for Boron and Phosphorus, consists in an enhanced diffusivity when Silicon selfinterstitials are present, generally after ion implantation.

## Chapter I

## Introduction

The tools needed for understanding the present work are here introduced.

This chapter introduces all the concepts needed for understanding this work and its scope. A glimpse to the context that led to the development of BiCMOS technologies opens the discussion.

The principal figures of merit are reviewed.

The state of the art is then examined by discussing the most recent solutions presented by the actors of current BiCMOS developments.

Finally, a focus on Double-Polysilicon Self-Aligned Selective Epitaxial Growth (DPSA-SEG) architecture used for BiCMOS055 technology by STMicroelectronics will pave the way for the introduction of Epitaxial eXtrinsic Base Isolated from the Collector (EXBIC) Heterojunction Bipolar transistor (HBT)s, which makes the object of this study.

#### 1 Context

After its invention in 1948 by John Bardeen, William Shockley and Walter Brattain, the Bipolar Transistor has become a milestone in human history.

Figure I.1 Bardeen, Brattain and Shockley, discoverers of the transistor effect. (Picture by AT&T. Public domain.)

Celebrated with a Nobel prize to its inventors in 1956, it rapidly substituted the thermionic valves thanks to its reduced dimensions and cost in addition to better performances. The invention of dedicated logic families, the amelioration of the production processes and the development of reliable integrated circuits paved the way to modern electronics. In the meanwhile, the advancements in MOSFET technologies made the development of CMOS logic possible, replacing bipolar-based logics thanks to its high noise immunity and low static power.

Nowadays, most electronic circuits are based on CMOS technologies. The virtues that led to the domination of this technology, however, could not face all the strengths of the Bipolar Junction Transistor (BJT), which kept its superiority in high-frequency applications. Indeed, bipolar transistors outperform MOSFETs by a couple of technology nodes when compared on RF capabilities due to the intrinsic limitations of such devices. The necessity

of combining the CMOS logic capabilities with the RF BJT strengths in the same integrated circuit led to the development of BiCMOS technologies.

In order to keep increasing performances whilst being compatible with CMOS-process, the structure of the original bipolar device has been radically changed:

- Bandgap engineering became a new possibility thanks to the development of SiGe alloys fabrication processes. The Heterojunction Bipolar Transistor (HBT) is an improved type of bipolar transistors that uses a graded SiGe profile in the base to overcome its intrinsic gain-bandwidth limitations.

- The original simple planar layout has evolved to more complex and efficient vertical structures. Advancements in production techniques led to structure shrinkage and increase of complexity in order to ensure higher performances and integration density. While old fabrication processes required very simple integrations based on diffusion doping, modern equipments allow to combine ion implantation and in-situ epitaxy doping to obtain very complex and tiny structures.

- The production flow of a full-bipolar integrated circuit has been adapted to the constraints of a modern CMOS-based platform, leading to particular integration choices. The big difference between the fabrication processes of the two kind of devices is a big constraint during development.

Such innovations allowed to increase maximum frequencies from 500 MHz to above 300 GHz in more than 50 years. Device size shrinked from hundreds of  $\mu m$  down to the nanometric scale.

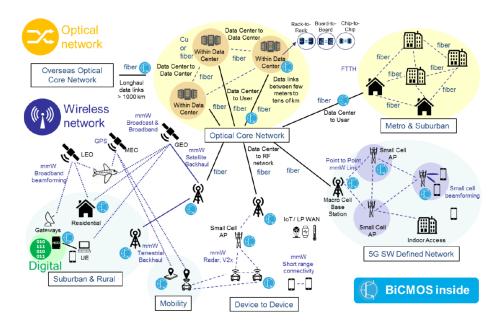

BiCMOS technologies are used nowadays in multiple RF applications where higher performance with respect to pure CMOS technologies has to be combined with smaller cost-per-chip with respect to III-V technologies. Bipolar transistors outperform MOSFET in terms of power amplification, low-frequency noise and reliability. Devices based on III-V semiconductors are capable of reaching much higher performances than HBT but are hindered by wafer size and yield, making them a costly solution not suitable for high-volume production. For all the fields needing high RF performance, mixed-signal capabilities, reduced dimensions, relatively low cost and mass

#### I. Introduction

production, BiCMOS is the technology of choice. Typical commercial applications are optical fiber datacom or wireless networks [66]. Figure I.2 sketches the many systems in which BiCMOS technologies can be found.

Figure I.2 | Typical applications of BiCMOS technologies in final devices.[9]

#### 2 Figures Of Merit

Figures of merit must be defined to evaluate the performance of a device and set a common ground for discussion. The most important parameters for both DC and AC operations will be presented here. HBT theory has been widely treated in literature [1, 10] and will not be repeated here. Since this work is a study on an npn transistor, the following definitions and conventions will be related to this device. More details about some figures of merit will be given in the following chapters when the relative device component will be treated.

#### 2.1 Voltage references and operating zones

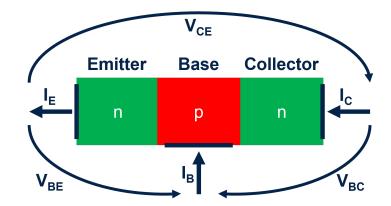

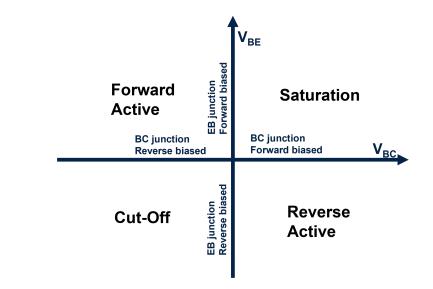

Figure I.3 depicts the naming convention for the electric terminals as well as for currents and bias voltages. Biasing of the two pn junctions regulates carriers flow through the device (Figure I.4) and four regions of operation can be defined:

- Cut-off Each junction is reversely biased and carriers cannot flow through the device.

- Saturation Each junction is forward biased. Net current flow will be directed towards the higher potential terminal.

- Forward active Emitter-base junction is forward biased and base-collector junction is reversely biased. Output emitter current is obtained from the sum of input base and collector currents.

- Reverse active Base-collector junction is forward biased and emitter-base junction is reversely biased. Output collector current is obtained from the sum of input base and emitter currents.

#### 2.2 Currents and gain

Simplified formulas for collector and base current can be obtained with the approximation of abrupt and constant doping profiles and assuming ideal behavior of the device:

$$I_C = \frac{qAD_{nb}n_{i,B}^2}{W_B N_{ab}} exp \frac{qV_{BE}}{k_B T}$$

(I.1a)

I. Introduction

Figure I.3 Schematic of an npn transistor with conventional currents and voltages in forward active region.

Figure I.4 Regions of operation of a bipolar transistor based on junctions biasing.

2. Figures Of Merit

$$I_B = \frac{qAD_{pe}n_{i,E}^2}{W_E N_{de}} exp \frac{qV_{BE}}{k_B T}$$

(I.1b)

Where q is the electron charge; A the junction area; D the diffusivity of electrons (n) or holes (p) in base (b) or emitter (e);  $n_i$ , B the intrinsic carrier density in the base and  $n_i$ , E in the emitter; W the width of base (B) or emitter (E); N the density of donors (d) or acceptors (a) in emitter (e) or base (b);  $V_{BE}$  the base-emitter voltage;  $k_B$  the Boltzmann constant; T the temperature.

The emitter current is related to the other two through a simple equation:

$$I_E = I_B + I_C \tag{I.2}$$

Current gain can be defined in different ways:

$$\alpha = \frac{I_C}{I_E} \tag{I.3a}$$

$$\beta = \frac{I_C}{I_B} \tag{I.3b}$$

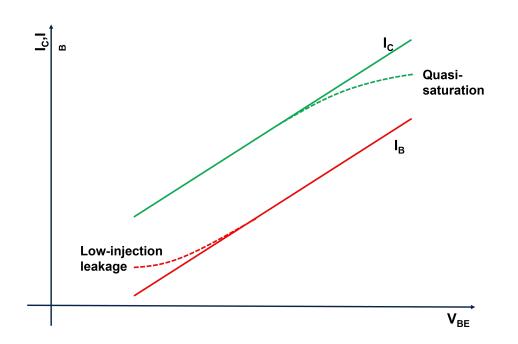

Where  $\alpha$  is the common base current gain and  $\beta$  is the common emitter current gain. Real devices can exhibit current leakages at low injection due to various phenomena inducing carrier generation and recombination. Two figures of merit are introduced to monitor them: collector current ideality factor  $\eta_{I_C}$  and base current ideality factor  $\eta_{I_B}$ . Ideality factors describe the gap between measured current values and those theoretically obtained if currents had a perfectly exponential dependence on junction voltages. An ideality factor of 1 means the device behaves perfectly, while bigger values indicate some non-idealities. Figure I.5 represents the effect of low-injection non-idealities on base current  $I_B$ .

Quasi-saturation is an effect related to collector resistance. When currents grows enough, the voltage drop across the collector resistance becomes large enough to counter the applied base-collector voltage. Consequently, the junction depletion region decreases in size as current increases, widening the neutral base and generating a negative feedback. If the current increases too much, it is also possible that the effective bias on the junction reverses, driving the device into saturation. Figure I.5 shows the impact of quasisaturation on collector current.

Figure I.5 | Impact of some current non-idealities on Gummel plot.

Kirk effect is another phenomenon occurring at high injection. When collector current is high enough, electrons transiting through the device have a non-negligible density when compared with the fixed charges ( $N_A$  in the base,  $N_D$  in the collector). At increasing currents, electrons will start to contribute significantly to junction electrostatics, shifting the depletion regions by acting on electric field. This effect, also known as electric-field screening, is particularly important for the base-collector junction, where the depletion region is progressively pushed out of the base, modifying its effective width. To an extreme point, the base will not be depleted anymore and the transistor will not work as expected.

#### 2.3 Early voltages

Junction bias can have an appreciable impact on depletion regions, indirectly modulating neutral base width. Even if a fixed base width is considered in the current Equation (I.1a), it actually changes depending on the applied  $V_{BE}$ and  $V_{BC}$  voltages. This phenomenon, known as Early effect, can cause an important variation in the device characteristic in the forward active region, implying some difficulties in circuit design. Two figures of merit evaluate the impact of this effect on device behavior: forward Early voltage  $V_{AF}$  and reverse Early voltage  $V_{AR}$ , related to base-collector and emitter-base junctions respectively. High values of Early voltages relate to a base less influenced by biasing and to a more stable collector current as a consequence.

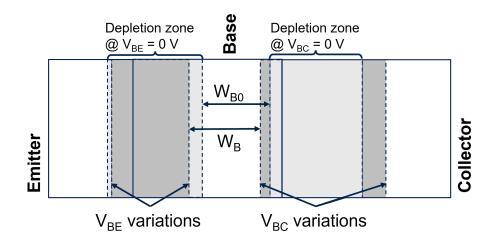

Figure I.6 Schematic representing the impact of junction biasing on depletion zones.  $W_{B0}$  is the neutral base width of an unbiased device;  $W_B$  is the neutral base width of a biased device.

### 2.4 Breakdown voltages

When accelerated to high speeds, an electron acquires enough kinetic energy to ionize an atom by impact. When this occurs within the depletion region of a junction, the electron extracted by ionization can be accelerated by the electric field and ionize another atom. This effect can snowball inducing a cascade of ionizations and creating a massive current typical of the so-called avalanche breakdown. Ionization by impact and the rapid rise in temperature due to the massive current flux can induce permanent alterations of the device. Safe Operating Area (SOA) can be defined from breakdown voltages.

The critical voltage for a reverse-biased pn junction can be expressed as:

$$BV = \frac{\epsilon_0 \epsilon_r E_{crit}^2}{2qN} \tag{I.4}$$

Where  $\epsilon_0$  is the vacuum permittivity;  $\epsilon_r$  is the relative permittivity;  $E_{crit}$  is the critical electric field for attaining impact ionization; N is the dopant concentration. The technological parameter regulating breakdown voltages is constituted by the doping level, posing a constraint on device design.

Three main breakdown voltages can be defined for a BJT (or HBT):

- $BV_{CB0}$  Breakdown voltage measured between base and collector with floating emitter. This value generally depends from base doping.

- $BV_{EB0}$  Breakdown voltage measured between emitter and base with floating collector. Notice that this value is obtained by reverse biasing the junction, i.e. outside the limits of forward active region. This value generally depends from emitter doping.

- $BV_{CE0}$  Breakdown voltage measured between collector and emitter with floating base. Biasing the device in such way reverse biases the basecollector junction, reproducing the same effect observed for  $BV_{CB0}$ . The two figures of merit are related by the equation:

$$BV_{CE0} = \frac{BV_{CB0}}{\sqrt[\gamma]{\beta}} \tag{I.5}$$

Where  $\gamma$  is defined by the breakdown severeness and  $\beta$  is the common emitter current gain. Typical values of  $\gamma$  are between 3 and 6.

#### 2.5 Transit frequency

A way of representing high-frequency behavior of an amplifying device is to define its gain-bandwidth product. The transit frequency  $f_T$  of a transistor is defined as the frequency at which the current gain drops to 1. Such definition is valid for a small-signal current gain  $h_{fe}$  obtained in a common emitter configuration and with a short-circuit load. This is equivalent to having a value  $h_{21} = 0$  dB in the S-matrix representation of the device.

Since the device reaches way higher frequencies than the ones handled by usual measurement equipments, the value of  $f_T$  is extrapolated from measurements performed at lower frequencies on the -20 dB/dec current-gain slope. Once the extrapolation frequency  $f_{extr}$  set, the transit frequency can be obtained:

$$f_T = h_{fe,extr} f_{extr} \tag{I.6}$$

where  $h_{fe,extr}$  is the small-signal common-emitter gain at the extrapolation frequency  $f_{extr}$ .

Transit frequencies reported in this work are normally referring to an extrapolation frequency  $f_{extr}$  of 20 GHz. Tolerance on measured values can go up to 5 % on a well-performed setup.

High-frequency behavior of the bipolar transistor is determined by minority carriers stored in the different parts of the transistor. The capability to remove such carriers determines the speed at which the device can switch and therefore its maximum operating frequency. For an ideal device, the transit time  $\tau_F$  defines such limit. In a real device, parasitics come to play and limit the speed at which excess carriers can be evacuated.

A simple yet fairly complete formula describing the transit frequency is:

$$f_T = \frac{1}{2\pi(\tau_F + (R_E + R_C)C_{BC} + \frac{k_B T}{qI_C}(C_{BE} + C_{BC}))}$$

(I.7)

Where  $\tau_F$  is the electron transit time through the device;  $R_E$  is the emitter resistance;  $R_C$  the collector resistance;  $C_{BC}$  the base-collector capacitance;  $C_{BE}$  the base-emitter capacitance;  $I_C$  the collector current;  $k_B$  the Boltzmann constant; T the temperature; q the electron charge.

Equation (I.7) displays a dependence from the collector current  $I_C$  which minimizes the contribution of some capacitances at high injection.  $f_T$  drops when collector current increases too much because of some limiting phenomena such as quasi-saturation or the Kirk effect.

A common Figure Of Merit (FOM) is  $f_{T,max}$  defined as the maximum value of  $f_T$  attainable for a device. In the following,  $f_T$  will be often used to mean  $f_{T,max}$  for the sake of simplicity. In case of possible confusion, the correct notation will be used.

#### 2.6 Maximum oscillation frequency

Considering power behavior of the transistor, it is also possible to define the maximum oscillation frequency  $f_{MAX}$  as the frequency at which the power (Mason) gain U drops to 1.

Analogously to what seen for the transit frequency,  $f_{MAX}$  is extrapolated from power gain measurements at lower frequencies of the -20 dB/dec power gain slope. Once the extrapolation frequency  $f_{extr}$  set, the transit frequency can be obtained as:

$$f_{MAX} = \sqrt{U} f_{extr} \tag{I.8}$$

where U is the Mason gain at extraction frequency  $f_{extr}$ .

Maximum oscillation frequencies reported in this work are normally referring to an extrapolation frequency  $f_{extr}$  of 20 GHz. Tolerance on measured values can go up to 5 % on a well-performed setup.

A simplified formula for defining such frequency as a function of device parameters is:

$$f_{MAX} \approx \sqrt{\frac{f_T}{8\pi R_B C_{BC}}} \tag{I.9}$$

Where  $f_T$  is the transit frequency;  $R_B$  the base resistance;  $C_{BC}$  the basecollector capacitance.

A common FOM is  $f_{MAX,max}$  defined as the maximum value of  $f_{MAX}$  attainable for a device. In the following,  $f_{MAX}$  will be often used to mean  $f_{MAX,max}$  for the sake of simplicity. In case of possible confusion, the correct notation will be used.

#### 2.7 Capacitances and resistances

As seen in Equation (I.7) and Equation (I.9), parasitics play an important role in limiting the transistor's operation at high frequency. An important part of this work is about minimizing the parasitics to get the maximum out of the device.

Three main resistances can be defined:

- $R_C$  Collector resistance. It is often reported in  $\Omega/sq$ .

- $R_B$  Base resistance. Normally splitted in two components: extrinsic base sheet resistance  $R_{sBX}$  and pinched intrinsic base sheet resistance  $R_{sPBI}$ , reported in  $\Omega/sq$ .

- $R_E$  Emitter resistance. Normally reported in  $\Omega$  or  $\Omega/\mu m^2$

Base and collector resistances are obtained by model extrapolation based on measurements performed on various device geometries, while emitter resistance is obtained by the transconductance method [37]. See Appendix 4 for more details on the extraction techniques of  $R_C$  and  $R_B$ .

Among the capacitances we can list:

$C_{BC}$  Base-collector capacitance. Normally reported in fF.

$C_{BE}$  Base-emitter capacitance. Normally reported in fF.

Capacitances are extracted from S parameters measured on standard  $0.2 \times 5\mu m$  transistors. Reported capacitances are always referring to 0 V junction bias.

#### 2.8 Power behavior at high frequency

Load-pull measurements can be used to define the power behavior of the device at high frequency.

Chosen an extraction frequency  $f_{extr}$ , a cartography on the Smith chart allows to find the optimal load Z.

The power added efficiency PAE is used to express the power effectiveness of the transistor. In practice, it relates the RF increase of signal power with the power consumed for device operation. It is defined as:

$$PAE = \frac{P_{OUT}^{RF} - P_{ABS}^{RF}}{P_{TOTAL}^{DC}} \tag{I.10}$$

where  $P_{OUT}^{RF}$  is the output RF power,  $P_{ABS}^{RF}$  is the absorbed RF power and  $P_{TOTAL}^{DC}$  is the total DC absorbed power required for biasing the device.

PAE is normally expressed in percentage.

The output power at maximum efficiency  $P_{OUT}@PAE_{MAX}$  measures the output power available at maximum efficiency.  $P_{OUT} - 1dB$  is the output power at 1dB compression, setting a soft limit for maximum output power.

The power gain  $G_p$  measured in dB is expressed as:

$$G_p = 10 \cdot log(\frac{P_{OUT}}{P_{ABS}}) \tag{I.11}$$

## 3 State of the art

Many needs require many solutions and each producer of BiCMOS technologies offers its combination both of active and passive components. It is impossible to define which platform is the best since it really depends on customer needs. Specific device performance can be compared from a technical point of view. This section details how each actor is trying to offer the most performing HBT solution for RF applications.

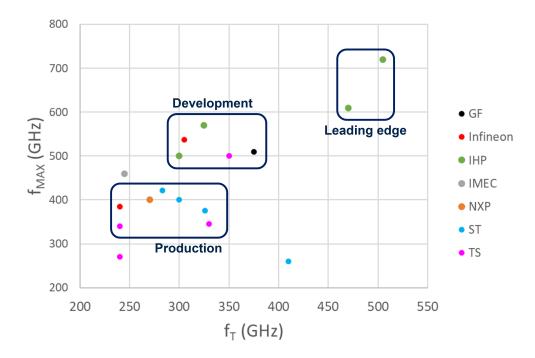

Since HBTs are used in BiCMOS circuits for their RF characteristics,  $f_T$  and  $f_{MAX}$  are quite good parameters for evaluating their performance. Figure I.7 depicts the state of the art obtained from scientific publications of the principal players in the recent years.

Figure I.7 Published values of  $f_T/f_{MAX}$  achieved in the recent years by HBT producers.

Some distinction has to be made on the state of maturity of each result. "Production" solutions are those related to a complete BiCMOS platform and currently sold on the market. This means that a whole set of other active and passive devices are also available for integration on the same die. Transistors appertaining to the "industrial development" category are not necessarily within all the constraints needed for series production but are being developed to be part of it. The present work is meant to establish a new state of the art in this category. "Leading edge" devices are the finest in terms of performance thanks to advanced device design and show the actual known limits for HBT performance.

In the following, the most recent solutions known from each HBT producer will be presented.

#### 3.1 Global Foundries

In 2021, Global Foundries presented a BiCMOS platform based on a 45 nm PD-SOI CMOS node[46]. The HBT realized in this framework could reach an  $f_T$  of 375 GHz and an  $f_{MAX}$  of 510 GHz.

Not many informations are given on the HBT architecture. The collector is realized by opening the SOI BOX to expose the underlying silicon and followed by a typical sequence for realizing a buried doped layer. The rest of the device is obtained with a typical sequence of steps including intrinsic and extrinsic base epitaxy, emitter deposition and patterning with spacer formation. Lateral and vertical scaling allow to suppress parasitic components and optimize the doping profile.

Figure I.8 Schematic cross section of the BiCMOS platform presented by Pekarik et al. [46].

## 3.2 Infineon

The german Integrated Device Manufacturer (IDM) Infineon presented in 2018 its most updated version of the Elevated Base Link - Selective Epitaxial

growth (EBL-SEG) architecture exhibiting  $f_T/f_{MAX} = 305/537$  GHz on a 130 nm CMOS platform[40].

This architecture has been conceived by IHP[21] and then transferred to Infineon's production line[39] for industrialization. Figure I.9 shows a TEM cross-section of the device. EBL-SEG devices rely on a dedicated lateral extrinsic base epitaxy to address the reduction of base resistance  $R_B$  and maximize  $f_{MAX}$ . In practice, the whole intrinsic collector-base-emitter stack is realized before a selective epitaxy is used to laterally contact the base. This sequence allows to heavily dope the extrinsic base without fearing excessive diffusion towards the intrinsic device.

An integration on a smaller 90 nm CMOS platform has been evaluated and should shortly take the place of the current 130 nm one.

Figure I.9 TEM cross section of the Elevated Extrinsic Base - Selective Epitaxial growth (EBL-SEG) HBT presented by Manger et al. [40].

#### 3.3 IHP

The Elevated Extrinsic Base - Non Selective Epitaxial Growth (EEB - NSEG) architecture has been firstly demonstrated by IHP in 2010[53] for the integration on a 130 nm CMOS platform. After some improvements[51], an updated version of the device achieved in 2019 a record performance of  $f_T/f_{MAX} = 470/610 \text{ GHz}[52]$ . This device currently exhibits the maximum reported HBT frequencies on a BiCMOS platform.

A TEM cross-section of the HBT is shown in Figure I.10. This device is based on a non-selective epitaxy covering the whole surface and realizing the intrinsic base the seed layer for the extrinsic base at the same time.

An additional selective epitaxy is used to increase the doping level in the extrinsic base in order to address the base resistance  $R_B$ .

The same research institute presented in 2016 an improved version of this architecture conceived without the constraints of being co-integrated with CMOS devices[31]. The result is an astounding  $f_T/f_{MAX}$  of 505 Ghz and 720 GHz respectively, setting a new peak in HBT performance. Even though this solution is not currently suitable for BiCMOS integration, it raises the known limits for HBTs.

Figure I.10 TEM cross section of the Elevated Extrinsic Base - Non Selective Epitaxial Growth (EEB - NSEG) HBT presented by Rücker et al. [52]

### 3.4 NXP

NXP makes use of the Double Polysilicon Self-Aligned-Selective Epitaxial Growth (DPSA-SEG) architecture for integrating its transistors on a 90 nm CMOS platform. The results presented in 2016 showed an integration achieving  $f_T$  and  $f_{MAX}$  of 270 GHz and 400 GHz respectively [61].

In order to have a high control over the vertical doping profile, this integration minimizes the thermal budget applied to the bipolar transistor by producing it at the end of the production flow, i.e. after the MOSFETS. The collector is doped by the means of a Sub-Isolation Buried Layer (SIBL) to reduce production cost by avoiding the costly epitaxy normally used in DPSA-SEG architectures. Figure I.11 highlights how the device has undergone an aggressive vertical scaling to bring the base contacts closer to the intrinsic base and minimize the  $R_B$  resistance.

Figure I.11 TEM cross section of the Double Polysilicon Self-Aligned-Selective Epitaxial Growth (DPSA-SEG) presented by Trivedi et al. [61].

## 3.5 STMicroelectronics

STMicroelectronics implements its own version of Double Polysilicon Self-Aligned-Selective Epitaxial Growth (DPSA-SEG) transistor. Firstly demonstrated for a 130 nm node on a 200 mm production line with  $f_T/f_{MAX} = 240/270$  GHz by Avenier et al. [3], the architecture has been successively transferred on a 55 nm CMOS node, achieving  $f_T/f_{MAX} = 320/370$  GHz in 2014[7].

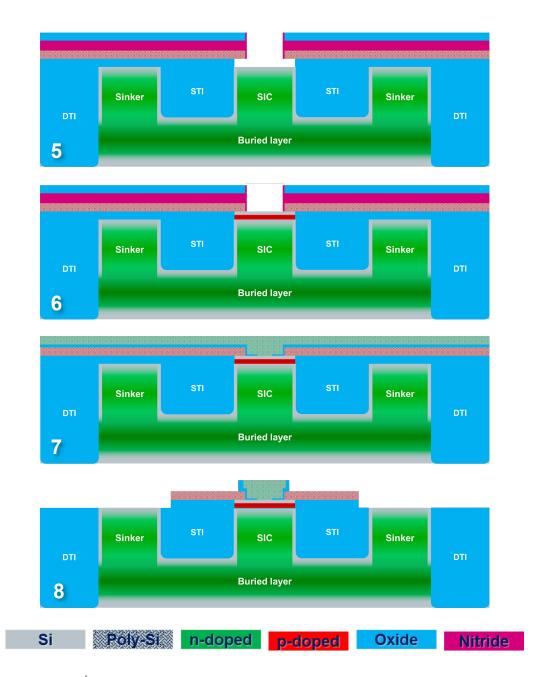

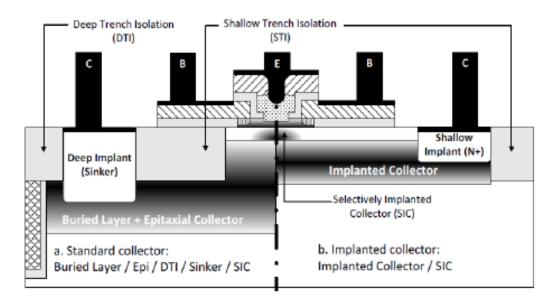

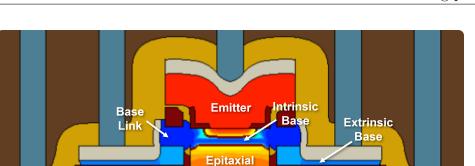

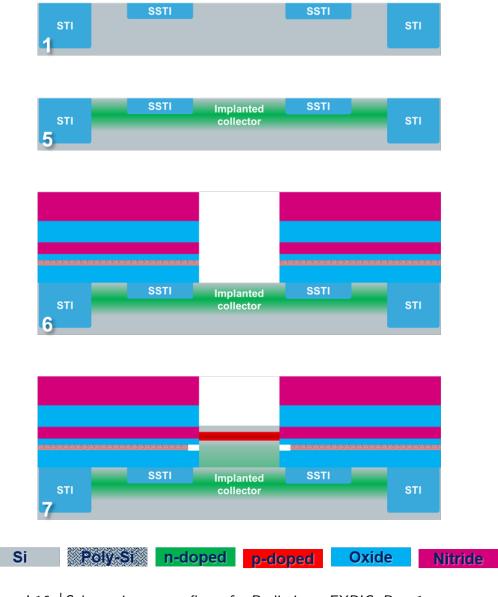

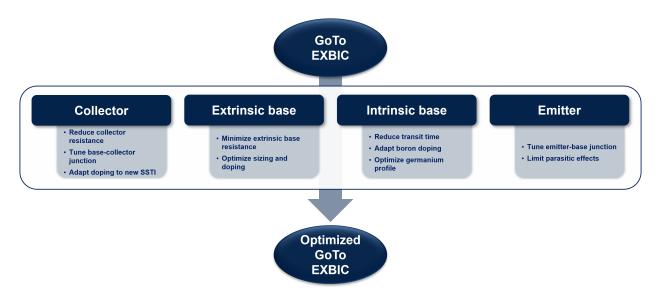

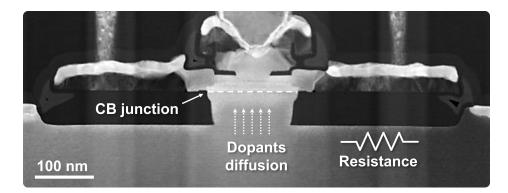

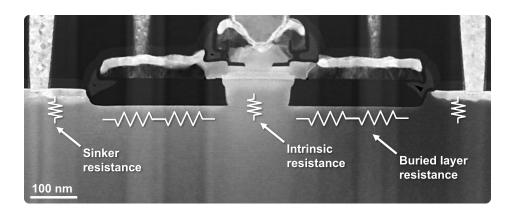

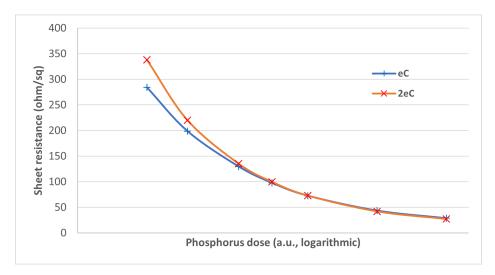

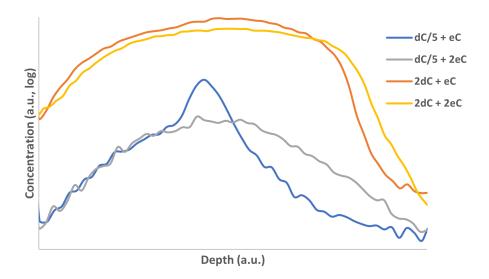

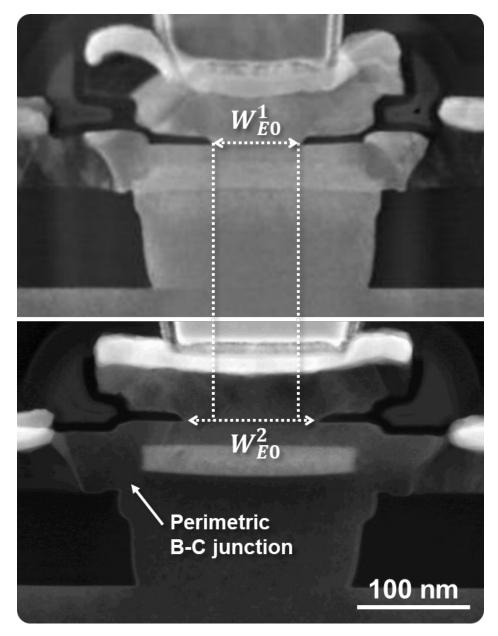

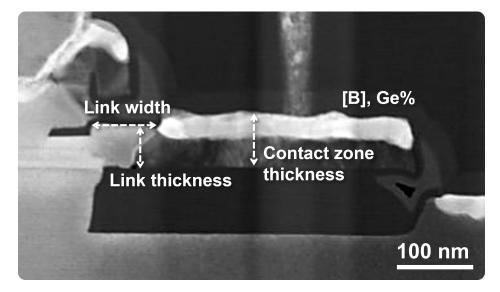

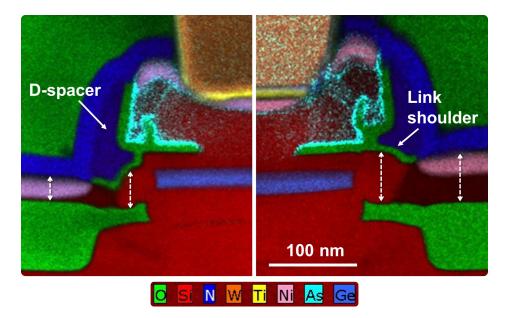

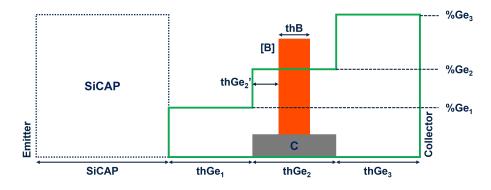

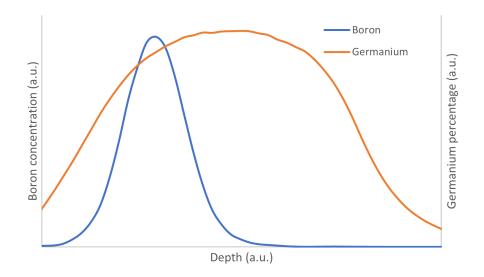

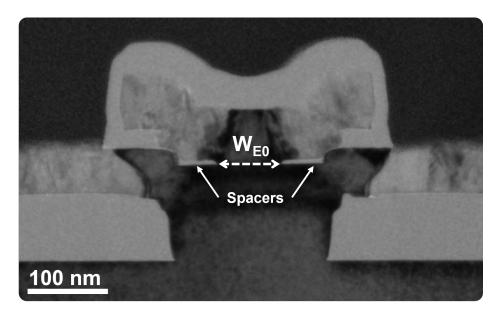

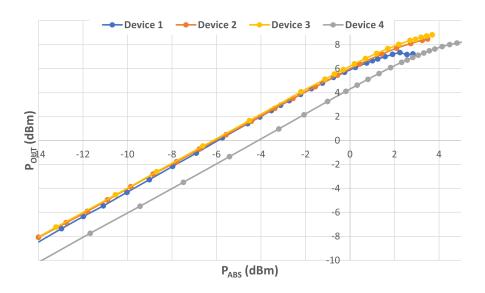

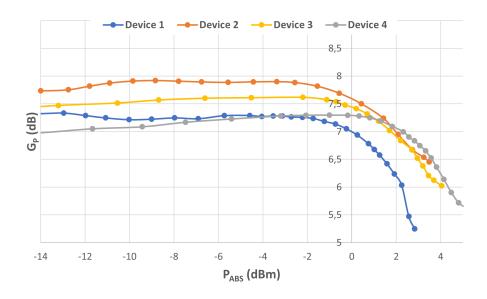

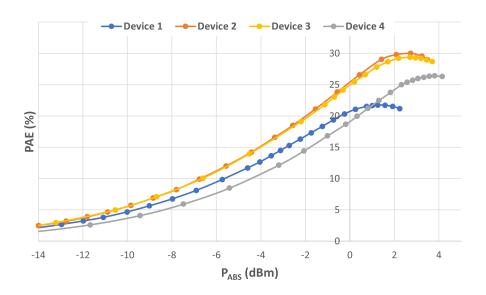

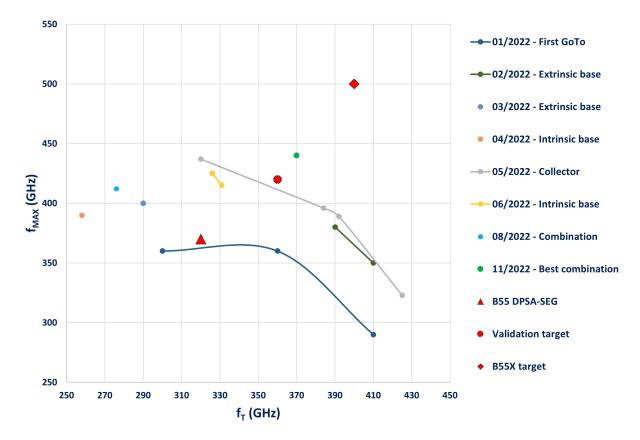

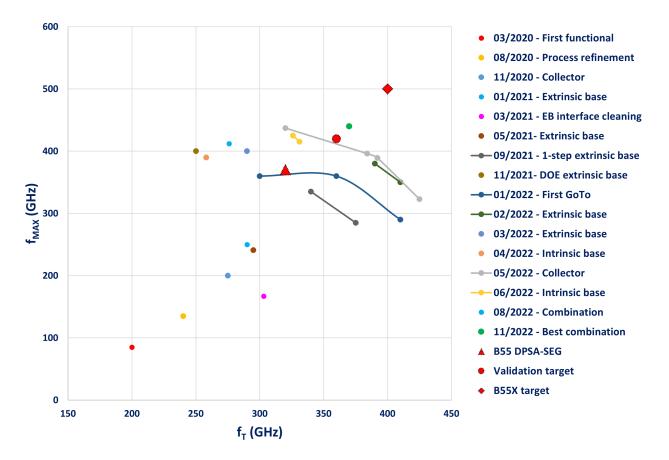

In the years, many studies have worked on improving the performances obtained with this architecture. chevalier2009conventional worked on the maximization of  $f_{MAX}$ , attaining values above 400 GHz. The optimization of thermal budget has shown  $f_T$  values up to 340 GHz [26]. Following studies carried out by Gauthier et al. [22] could further improve  $f_T$  up to 450 GHz, at detriment of  $f_{MAX}$ .