# Development of a dynamic resource allocation controller for partially reconfigurable FPGAs with service guarantee approach

Alexis Duhamel

#### ▶ To cite this version:

Alexis Duhamel. Development of a dynamic resource allocation controller for partially reconfigurable FPGAs with service guarantee approach. Electronics. Nantes Université, 2022. English. NNT: 2022NANU4077. tel-04088507

# $HAL\ Id:\ tel-04088507$ https://theses.hal.science/tel-04088507v1

Submitted on 4 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

#### NANTES UNIVERSITE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: Électronique

Par

# **Alexis DUHAMEL**

Development of a dynamic resource allocation controller for partially reconfigurable FPGAs with service guarantee approach

Thèse présentée et soutenue à Nantes Université, le 7 décembre 2022 Unité de recherche : IETR UMR 6164

#### Rapporteurs avant soutenance:

M. DE LA TORRE Eduardo Associate Professor, Universidad Politécnica de Madrid

M. TESSIER Russell Professor, University of Massachussets

### **Composition du Jury:**

Président : M. VERDIER Francois Professeur, Université Côte d'Azur Examinateurs : M. CHILLET Daniel Professeur, Université de Rennes 1

M. DE LA TORRE Eduardo Associate Professor, Universidad Politécnica de Madrid

M. TESSIER Russel Professor, University of Massachussets

Directeur de thèse : M. PILLEMENT Sébastien Professeur, Nantes Université

Encadrante : Mme. KOUKI Wiem Ingénieure de recherche, Capgemini Engineering, Nantes

# Contents

| Ta           | able  | of Contents                                                  | i   |

|--------------|-------|--------------------------------------------------------------|-----|

| Li           | st of | Figures                                                      | ii  |

| Li           | st of | Tables                                                       | iv  |

| $\mathbf{R}$ | ésum  | né long                                                      | vii |

| 1            | Intr  | $\mathbf{roduction}$                                         | 1   |

|              | 1.1   | Contributions                                                | 2   |

|              | 1.2   | Dissertation organization                                    | 3   |

| 2            | Bac   | ckground and model definition                                | 5   |

|              | 2.1   | Self-reconfigurable system design                            | 6   |

|              |       | 2.1.1 Reconfigurable region definition                       | 6   |

|              |       | 2.1.2 DPR management methodology                             | 8   |

|              |       | 2.1.3 Architecture design for reconfigurable systems         | 11  |

|              |       | 2.1.4 Frameworks and libraries                               | 15  |

|              |       | 2.1.5 Proposed architecture                                  | 26  |

|              | 2.2   | Self-reconfigurable systems management                       | 29  |

|              |       | 2.2.1 Management methodologies                               | 30  |

|              |       | 2.2.2 Mapping and scheduling for self-reconfigurable systems | 33  |

|              |       | 2.2.3 Hybrid methodologies                                   | 42  |

|              | 2.3   | Conclusion                                                   | 43  |

| 3            | Qua   | ality-oriented application management                        | 45  |

|              | 3.1   | Overview                                                     | 46  |

|              | 3.2   | Quality model                                                | 46  |

|              |       | 3.2.1 Execution modes                                        | 46  |

|              |       | 3.2.2 Quality of Experience                                  | 49  |

|              |       | 3.2.3 Quality of Service                                     | 51  |

|              | 3.3   | Hybrid mapping and scheduling management                     | 52  |

|              |       | 3.3.1 Design-time computation                                | 54  |

|              |       | 3.3.2 Run-time computations                                  | 60  |

|              | 3.4   | Experiments                                                  | 68  |

|              |       | 3.4.1 Platform evaluation                                    | 68  |

| i | ii | Cont | ent | 55 |

|---|----|------|-----|----|

|   |    |      |     |    |

| $\mathbf{A}$     | Scie  | ntific communications 14                                    | 5             |

|------------------|-------|-------------------------------------------------------------|---------------|

| Bi               | bliog | raphy 13                                                    | 1             |

| $\mathbf{A}_{]}$ | ppe   | ndices 129                                                  | 9             |

|                  | 5.2   | Future works                                                | 5             |

|                  | 5.1   | Contribution summary                                        |               |

| 5                |       | clusion and discussion 12                                   |               |

| E                | Con   | alusian and discussion                                      | 9             |

|                  | 4.7   | Conclusion                                                  | 1             |

|                  |       | 4.6.2 Experimental results                                  | 6             |

|                  |       | 4.6.1 Experimental setup                                    | 3             |

|                  | 4.6   | Quality-oriented methodology experiments                    | 3             |

|                  |       | 4.5.3 Synthetic workloads                                   | 6             |

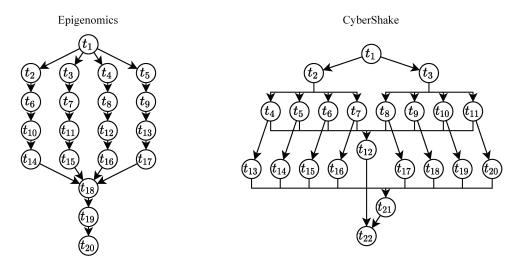

|                  |       | 4.5.2 Real application benchmarks                           | 1             |

|                  |       | 4.5.1 Experimental setup                                    | 0             |

|                  | 4.5   | PF-PEFT performance experiments                             | 9             |

|                  |       | 1                                                           | 7             |

|                  |       |                                                             | 6             |

|                  | 4.4   | Quality-oriented management with runtime scheduling 9       |               |

|                  |       |                                                             | $\frac{1}{2}$ |

|                  |       | 0                                                           | 0             |

|                  | 1.0   | 4.3.1 Reconfiguration tasks                                 |               |

|                  | 4.3   | -                                                           | 7             |

|                  |       | •                                                           | 4             |

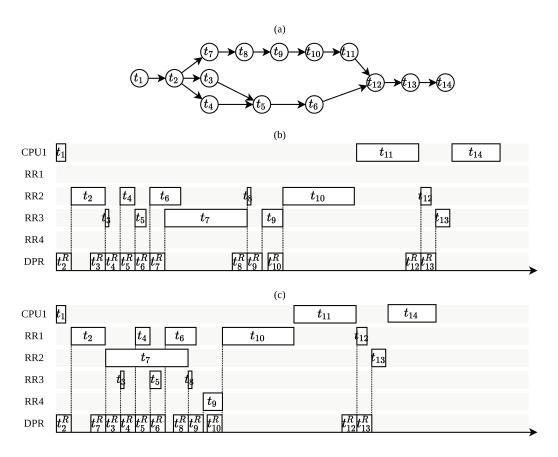

|                  | 4.2   | List-based PEFT scheduling heuristic                        |               |

|                  | 4.1   |                                                             | 0             |

| 4                | 4.1   | time scheduling for self-reconfigurable systems 7  Overview |               |

| 4                | ъ     |                                                             | ^             |

|                  | 3.5   | 0                                                           | 8             |

|                  |       |                                                             | 5             |

|                  |       |                                                             | 2             |

|                  |       | 3.4.2 Simulation environment                                | 1             |

# List of Figures

| 2.1  | Column-based and Region-based reconfigurable regions defini-      |    |

|------|-------------------------------------------------------------------|----|

|      | tion in FPGA matrices                                             | 7  |

| 2.2  | PCAP and ICAP partial bitstream flow                              | 6  |

| 2.3  | The three main RR architecture styles in DPR-capable FPGAs        | 12 |

| 2.4  | Functional abstraction levels                                     | 16 |

| 2.5  | CAP-based hardware preemption example                             | 18 |

| 2.6  | Software delegate thread concept illustration                     | 21 |

| 2.7  | Overview of FUSE's targeted architecture                          | 22 |

| 2.8  | Overview of ReconOS's targeted architecture                       | 24 |

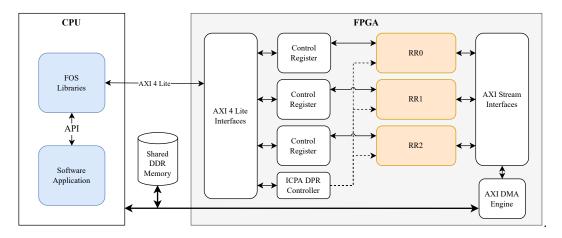

| 2.9  | Overview of FOS' targeted architecture                            | 24 |

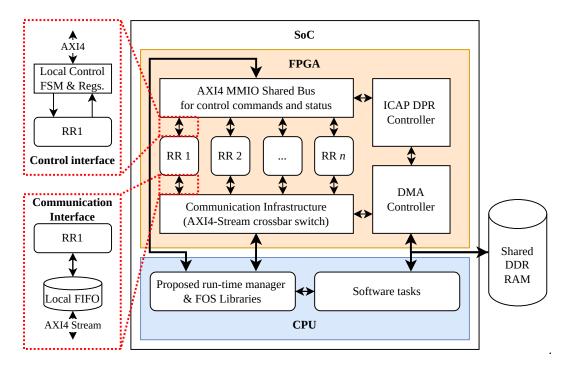

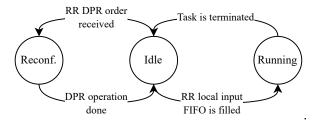

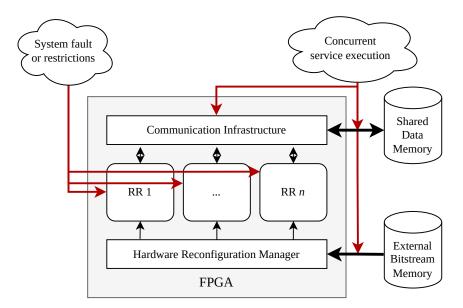

| 2.10 | Overview of the proposed architecture                             | 27 |

| 2.11 | Local control interface FSM                                       | 27 |

| 2.12 | Autonomic quality management                                      | 31 |

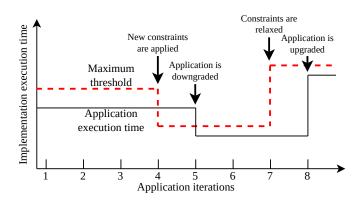

| 2.13 | Roy et al. quality-oriented scheduling principle                  | 32 |

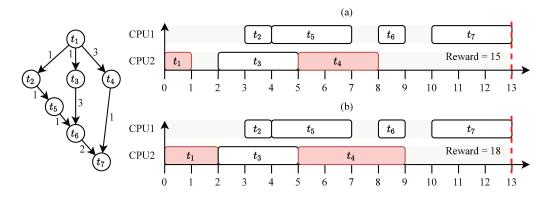

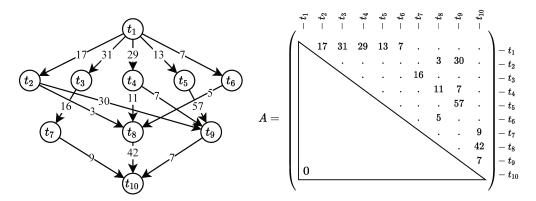

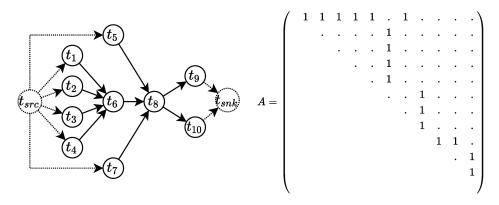

| 2.14 | Canonical application with its adjacency matrix                   | 35 |

| 2.15 | Illustration of the pre-fetch and reuse scheduling techniques     | 39 |

| 2.16 | Critical Path Aware scheduling principle                          | 42 |

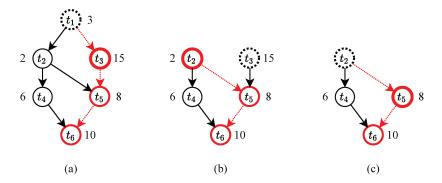

| 3.1  | Task graph representation of the multi-resolution H.264 en-       |    |

|      | coder benchmark with optional filtering and encryption tasks.     | 47 |

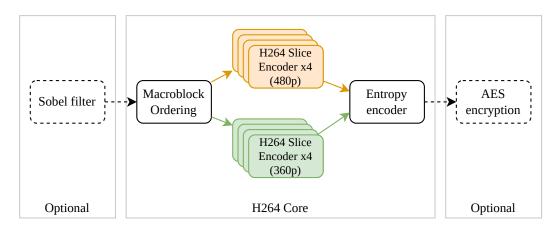

| 3.2  | Overview of the proposed quality-oriented hybrid design-time/run- |    |

|      | time management of self-reconfigurable system                     | 53 |

| 3.3  | Deadline violation due to a task assignment overload on RR1.      | 56 |

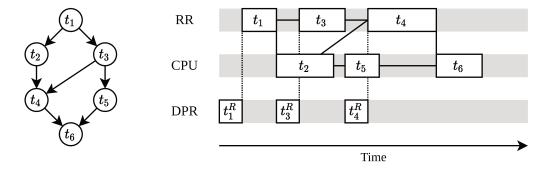

| 3.4  | Schedule of a sample task graph on a RR and a CPU using the       |    |

|      | fixed mapping scheduling heuristic                                | 57 |

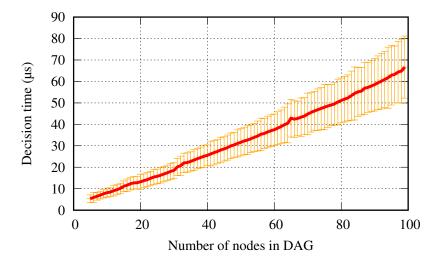

| 3.5  | Scheduling decision time of the fixed mapping ASAP heuristic      |    |

|      | by the number of nodes in the DAG task graph                      | 58 |

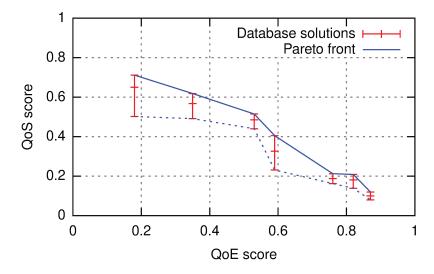

| 3.6  | Database solution space in the QoE-QoS domain                     | 59 |

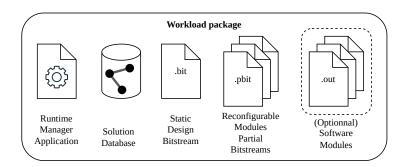

| 3.7  | Content of the run-time workload package                          | 60 |

| 3.8  | Illustration of the potential constraints on FPGA resources       | 62 |

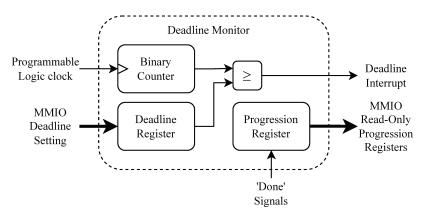

| 3.9  | Hardware programmable deadline monitor                            | 63 |

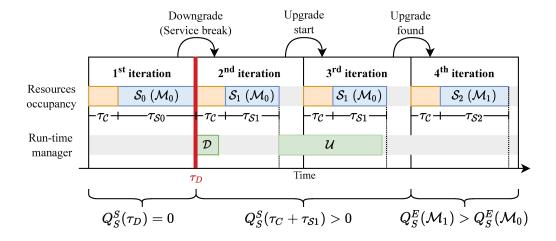

| 3.10 | Illustration of downgrade and upgrade operations in the system    |    |

|      | timeline                                                          | 66 |

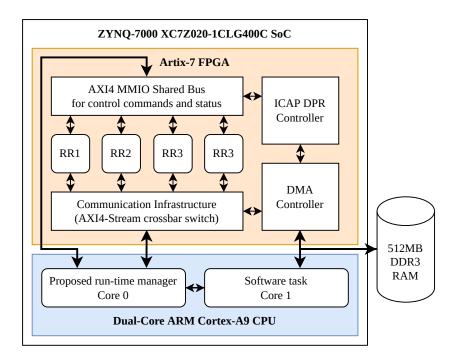

| 3.11 | Considered architecture for the experiments                       | 69 |

| 3 19 | Simulation environment of the run-time manager                    | 71 |

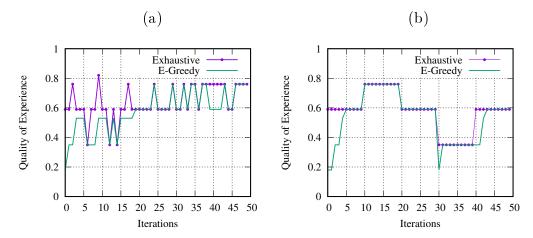

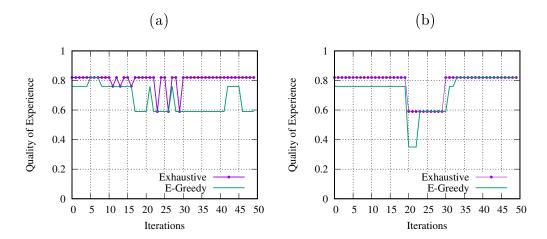

| 3.13 | H.264 QoE score evolution of the greedy-based heuristic on ran-  | _  |

|------|------------------------------------------------------------------|----|

| 0.14 | dom constraints                                                  | 7  |

| 3.14 | H.264 QoE score evolution of the greedy-based heuristic on the   | -  |

| 0.15 | restriction of service scenario.                                 | 7  |

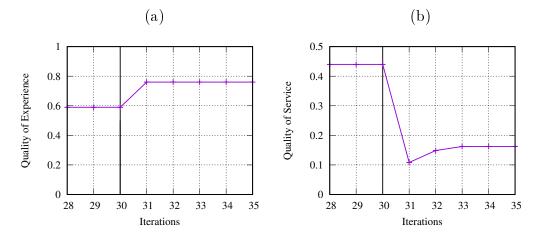

| 3.15 | H.264 QoS score evolution upon application of new constraint     | -  |

|      | levels                                                           | 7  |

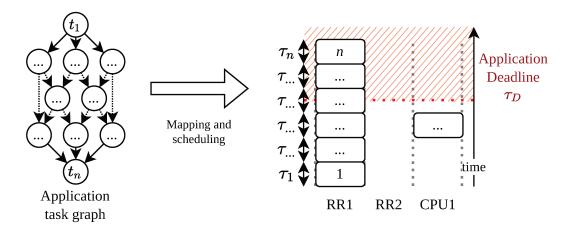

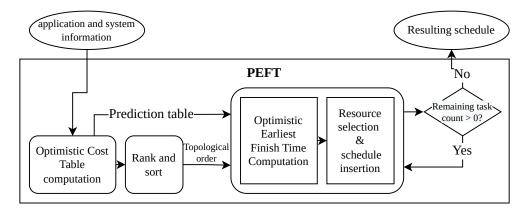

| 4.1  | Overview of the PEFT scheduling heuristic                        | 8  |

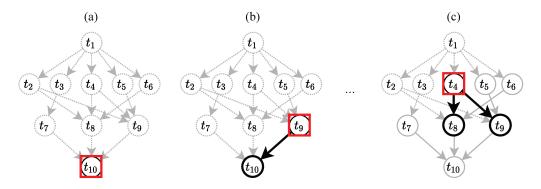

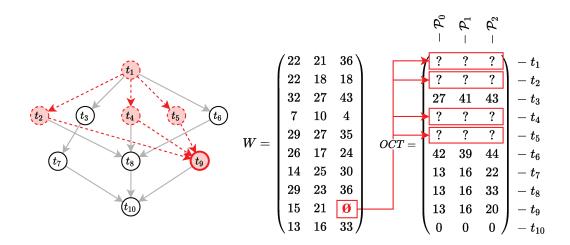

| 4.2  | Example cases of OCT computation                                 | 8  |

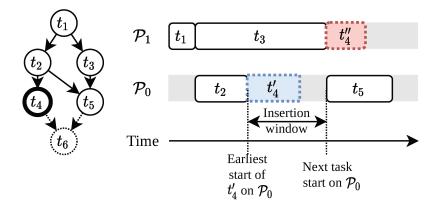

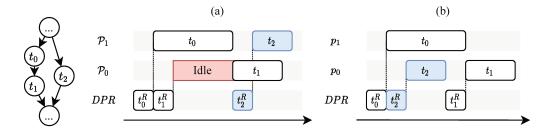

| 4.3  | Illustration of schedule insertion policy                        | 8  |

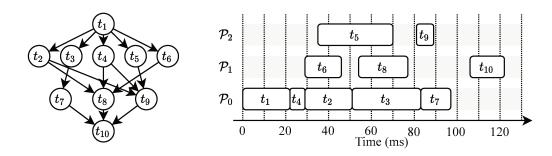

| 4.4  | PEFT schedule of the canonical task graph on three CPU re-       |    |

|      | sources                                                          | 8  |

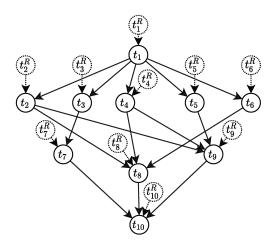

| 4.5  | Canonical task graph with reconfiguration tasks                  | 8  |

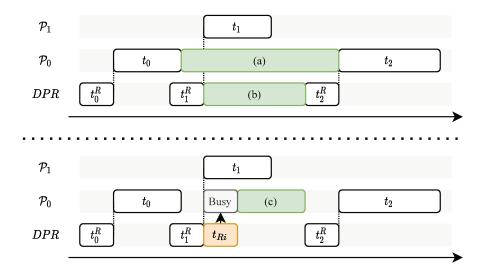

| 4.6  | Illustration of EFT policy with insertion, considering reconfig- |    |

|      | uration tasks                                                    | 8  |

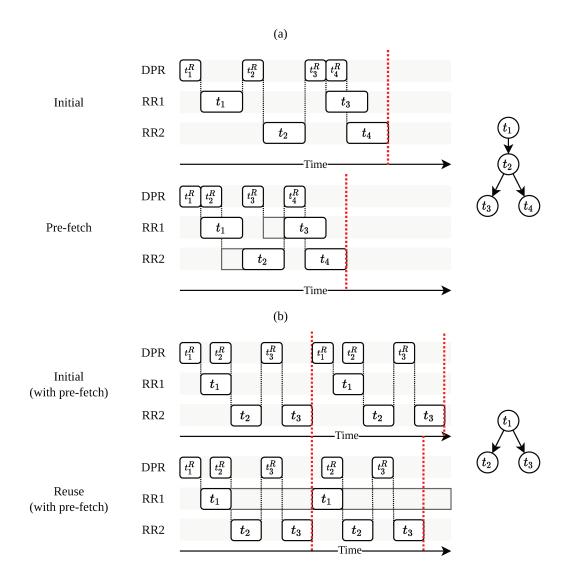

| 4.7  | Illustration of idle task constraint on pre-fetching             | 9  |

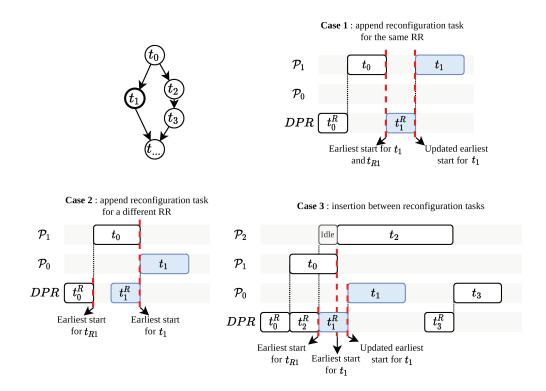

| 4.8  | Just-In-Time bitstream pre-fetching scheduling cases             | 9  |

| 4.9  | Partial OCT computation example                                  | 9  |

| 4.10 | Example of reused task between iterations and execution modes    |    |

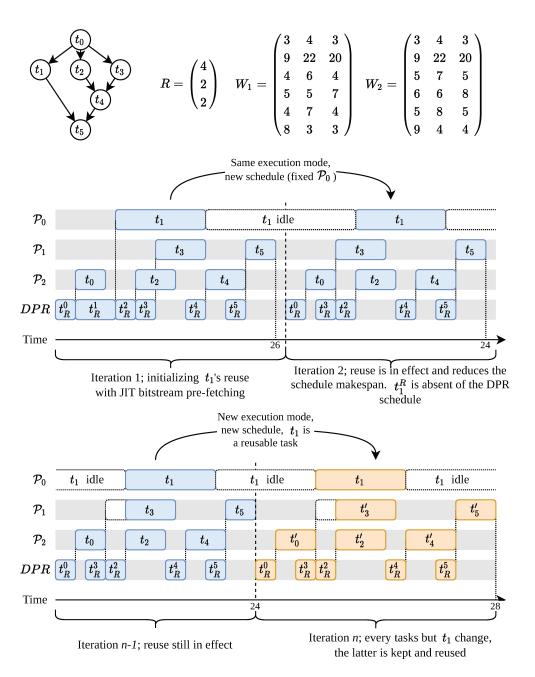

|      | with the schedule-base methodology                               | 9  |

| 4.11 | Illustration of Wide and Tall task graph topologies              | 10 |

| 4.12 | Lane Detection task graph resulting schedules using ASAP PF      |    |

|      | and PF-PEFT                                                      | 10 |

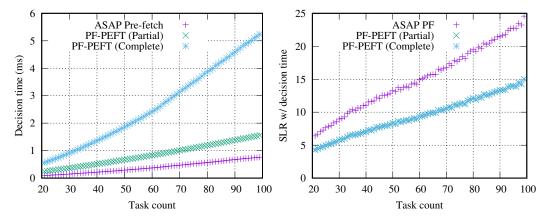

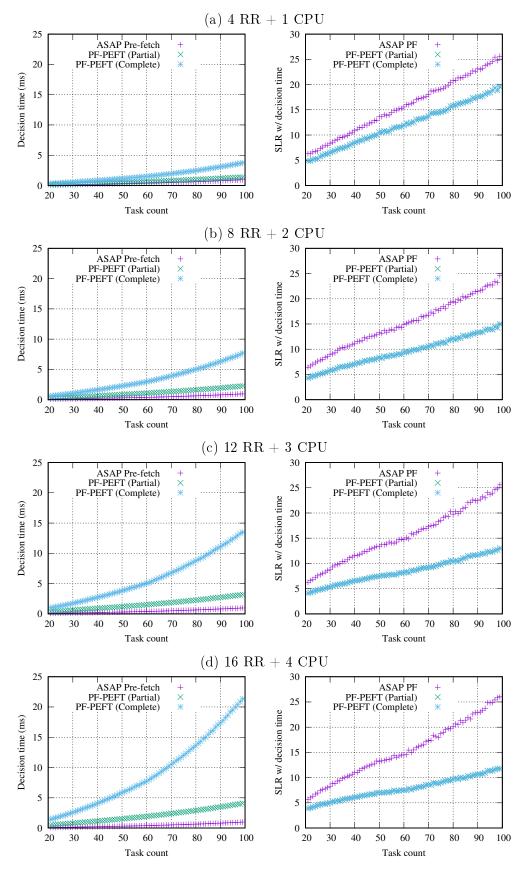

| 4.13 | Random synthetic workload decision times and resulting SLRs      | 10 |

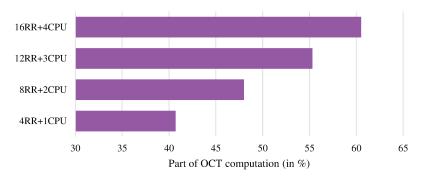

| 4.14 | Part of the decision time spent computing the OCT table when     |    |

|      | OCT reuse is not possible, by system resources composition       | 10 |

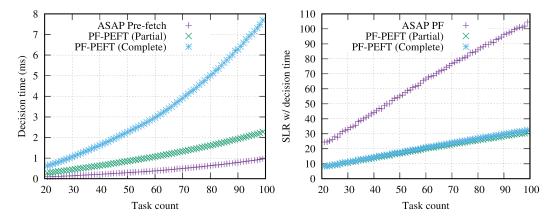

| 4.15 | Random synthetic workload decision times and resulting SLRs,     |    |

|      | longer task computation times                                    | 10 |

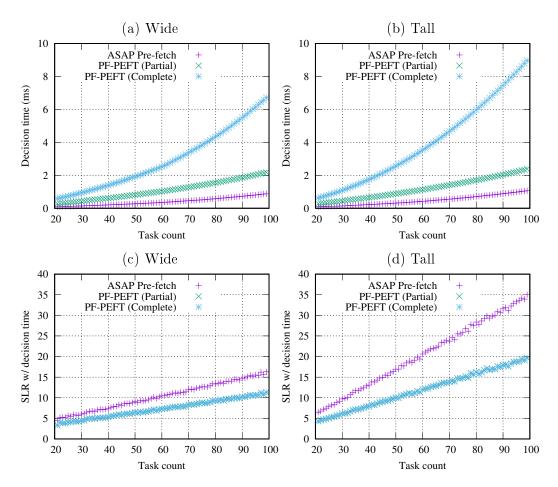

| 4.16 | Comparison of graph topologies impact on SLR and decision        |    |

|      | times                                                            | 11 |

| 4.17 | Platform composition impact on resulting decision times and      |    |

|      | SLRs                                                             | 11 |

|      | Traction control application task graph                          | 11 |

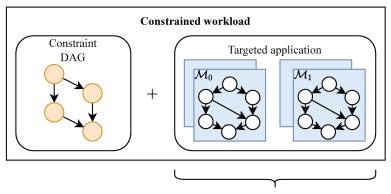

| 4 19 | Constrained workload illustration                                | 11 |

# List of Tables

| 2.1  | Comparison of DPR controllers                                    | 1  |

|------|------------------------------------------------------------------|----|

| 2.2  | Context switching results of CAP-based hardware preemption       |    |

|      | from Happe et al                                                 | 8  |

| 2.3  | Comparison of different frameworks on selected features of in-   |    |

|      | terest                                                           | 5  |

| 2.4  | Self-reconfigurable system resource usage                        | 9  |

| 2.5  | List of system and application parameters                        | 5  |

| 2.6  | Time complexity of popular scheduling policies for heteroge-     |    |

|      | neous computing                                                  | 1  |

| 3.1  | List of quality parameters for the H.264 application             | .8 |

| 3.2  | Definition of the execution modes for the H.264 application 4    | 9  |

| 3.3  | Application execution modes for the H.264 application, sorted    |    |

|      | by increasing quality score $Q_S^E$                              | 0  |

| 3.4  | Number of unrestricted mappings by execution modes for the       |    |

|      | H.264 application                                                | 5  |

| 3.5  | Application execution modes for the H.264 encoder benchmark      |    |

|      | application after the pruning                                    | 0  |

| 3.6  | On-target profiled execution times of extended H.264 applica-    |    |

|      | tion tasks in hardware and software                              | 0  |

| 3.7  | Bitstream size and reconfiguration time by RRs                   | 0  |

| 3.8  | Profiled worst-case delay on the communication interface 7       | 0  |

| 3.9  | Average relative QoE score on 100k iterations                    | 4  |

| 3.10 | Average decision times on 100k iterations                        | 5  |

| 3.11 | Resulting continuity of service execution checks on downgrades 7 | 7  |

| 4.1  | Considered architecture resource compositions                    | 0  |

| 4.2  | Profiled worst-case delay on the communication interface 10      | 1  |

| 4.3  | List of benchmark application topologies                         | 3  |

| 4.4  | On-target scheduling heuristic decision times comparison 10      | 4  |

| 4.5  | Resulting Schedule Length Ratios comparison                      | 4  |

| 4.6  | Traction control execution modes and corresponding QoE values.11 | 4  |

| 4.7  | Resulting average decision times of PF-PEFT based methodol-      |    |

|      | ogy heuristic in constrained workload scenario                   | 6  |

vi List of Tables

| 4.8  | Part of iterations of H.264 Encoder and Traction Control exe- |     |

|------|---------------------------------------------------------------|-----|

|      | cution modes and resulting average QoE score in the workload  |     |

|      | constraint scenario                                           | 117 |

| 4.9  | Resulting decision times of PF-PEFT based methodology heuris- |     |

|      | tic in denied resources scenario                              | 118 |

| 4.10 | Part of iterations of H.264 Encoder and Traction Control ex-  |     |

|      | ecution modes and resulting average QoE score in the denied   |     |

|      | resources scenario                                            | 119 |

| 4 11 | Reusable tasks between execution modes                        | 120 |

# Résumé long

Les Field-Progammable Gate Arrays (FPGAs) reconfigurables dynamiquement présentent une solution prometteuse pour réduire l'empreinte des composants électroniques, leur coût, et leur consommation énergétique. Ce type de système embarqué dit auto-reconfigurable permet le chargement à chaud d'accélérateurs matériels dans des zones dédiées de la matrice FPGA, appelées Régions Reconfigurables (RRs), grâce à la Reconfiguration Dynamique Partielle (RDP). Des architectures FPGAs et des méthodes de gestion d'allocation de ressources dédiées à la RDP ont alors été conçues pour exploiter au mieux cette technique. En particulier, les architectures apportant une couche d'abstraction matérielle sont d'intérêt, car elles simplifient leur utilisation et leur intégration à des systèmes déjà existants.

Les latences introduites par la gestion de ces systèmes, et en particulier des opérations de reconfigurations dynamiques partielles, ne permettent pas d'égaler la performance de plus gros FPGA statiques. Néanmoins, la flexibilité offerte par le chargement à chaud de RRs permet d'exécuter plus de tâches applicatives, sur moins de ressources. Dès lors, la question de la garantie d'exécution de service se pose. La complexité des charges de travail (ou services) à exécuter sur le système se superposant à la complexité de la gestion des RRs justifient le besoin de méthodologies garantissant l'exécution de services.

Ce travail de thèse se concentre sur la gestion sur cible de l'exécution des applications sur systèmes à base de FPGAs reconfigurables dynamiquement avec une approche garantie de service.

Deux principaux verrous technologiques sont identifiés:

• Moduler la complexité de la charge de travail du système à travers une modélisation de la notion de performance et de service. En identifiant les paramètres d'une application impactant la qualité de service perçue, il est possible d'influer sur la prise de décision de la gestion d'allocation de ressources. Cette modulation doit permettre de résoudre le problème de l'allocation des ressources afin de satisfaire un niveau de contraintes de latences sur les différentes ressources du système. En exploitant les invariants face aux paramètres de l'application impactant la qualité, il serait aussi possible de réduire le nombre d'opérations de reconfigurations.

viii Résumé long

• Sur la base des modèles de niveau de service précédents, aborder le problème de l'allocation dynamique des ressources au temps de l'exécution en garantissant l'exécution du service. Si les modèles de qualité de service permettent l'identification d'actions sur les paramètres pour réduire la complexité du service à exécuter, l'application de ces décisions reste un problème conséquent. En particulier, il est nécessaire de bien anticiper les différents temps de reconfiguration et de prendre en compte la disponibilité des différentes ressources du systèmes (RRs et CPUs dans le cas de ressources hétérogènes).

L'aspect garantie de service doit être couvert par un aspect temps réel, i.e. respecter une échéance pour l'exécution de l'application, et d'observer un niveau minimum de qualité du service défini par les concepteurs d'applications. De plus, le temps de décision des algorithmes de gestion d'allocation de ressources doit être pris en compte dans l'échéance de l'application afin que ce mécanisme apparaisse comme transparent pour l'utilisateur.

Pour résoudre la première problématique, nous nous intéressons à la définition de modes d'exécutions basé sur la décomposition en paramètres qualité d'une application. Ces paramètres influent sur la "Qualité d'Éxpérience" (QoE) perçue par l'utilisateur et peut être obtenue par définition mathématique de métriques objectifs (eg: rapport signal à bruit), ou par étude empirique (eg: appréciation de la qualité vidéo). Ainsi, il est possible d'attribuer des scores obtenus par l'étude de cette qualité perçue à plusieurs modes d'exécution d'une même application, définissant par là le mode de qualité dit "optimal", et des modes dégradés.

Puis, un modèle de qualité de l'implémentation de l'application est introduit. L'observation des métriques inhérents à l'exécution d'une application quelconque sur les systèmes auto-reconfigurables à base de FPGA dynamiquement reconfigurables (e.g. taux d'occupation des ressources, consommation énergétique de la puce, ) permet de dresser un modèle de préférence dit "Qualité de Service" (QoS) dépendant de l'objectif du système embarqué (sa mission) et du contexte dans lequel il évolue (son environnement).

La multiplication attendue de ces modes d'exécution dû à l'augmentation du nombre de paramètres qualités est adressée à travers de moyens d'observer le rapport entre qualité d'expérience et de service des modes d'exécution. Ainsi, les concepteurs d'applications peuvent au temps de la conception, déterminer les modes d'exécution pertinents en fonction de la mission et de l'environnement du système embarqué. Cette réduction des modes d'exécution étant

particulièrement importante afin de réduire la complexité des décisions à prendre sur cible.

Après avoir défini ces deux modèles de qualité permettant de qualifier et quantifier le niveau de service perçu par l'utilisateur, et de l'implémentation, nous proposons deux méthodologies de gestion d'allocation des ressources:

• Nous avons dans un premier temps proposé une méthodologie hybride découpée entre temps de la compilation et de l'exécution. Cette méthodo-logie permet d'exécuter une partie des algorithmes de gestion d'allocation de ressources afin de générer un grand nombre de solutions. Ces solutions correspondent à différentes implémentations des différents modes d'exécution de l'application. Ces solutions ainsi pré-générées et pré-évaluées, la problème de la gestion au temps de l'exécution sur cible est réduit à une sélection d'une solution maximisant les métriques de qualités.

Un compromis sur le nombre de solutions pré-évaluées à conserver sur cible doit néanmoins être observé. En effet, le temps passé à chercher une solution dans la base de donnée satisfaisant le niveau de contraintes imposé par l'environnement du système embarqué est lié à la taille (en nombre de solutions) de la base de données. Nous adressons ce compromis en introduisant une méthode permettant, lors de la génération, de ne pas évaluer les solutions d'implémentation d'un mode d'exécution ayant peu ou pas de chance de retourner un niveau de qualité de service suffisant. Puis, une fois les solutions générées, nous proposons une méthode permettant de garder le front de Pareto de l'espace de solution et un nombre de solutions voisines du front.

Une fois sur cible, nous proposons l'utilisation d'une heuristique de recherche rapide qui permet de trouver une solution de la base de solutions satisfaisant les contraintes de l'environnement du système embarqué. Afin de garantir l'exécution du service, cette heuristique améliore incrémentalement la qualité d'expérience afin de réagir au plus vite aux variations de niveaux de contrainte.

Enfin, l'approche proposée a été vérifiée fonctionnellement sur cible Zynq-7000, puis nous avons construit une simulation utilisant des métriques d'une implémentation d'une application d'encodage H.264 sur cette plateforme ainsi que de métriques issus de l'état de l'art. Les résultats obtenus montrent que cette méthode est capable de garantir l'exécution du service, caractérisé par le respect de l'échéance et par un niveau quantifiée

x Résumé long

par le modèle de qualité de service non-nul. En générant des situations de contraintes d'environnement, la simulation montre que notre approche permet de réagir en moins d'une itération et sans couper le service dans 94% des cas. Cette approche est néanmoins moins efficace face aux situations où une ou plusieurs ressources tombent en panne, où elle ne peut garantir l'exécution du service que 62% des cas. L'approche est toutefois capable de maintenir un niveau de qualité d'expérience quantifié allant de 82% à 94% de l'optimal, tout en donnant une réponse sous la milliseconde en moyenne.

• Dans un second temps, nous avons proposé une approche basée sur le calcul d'ordonnancement des tâches de l'application sur les ressources de la cible au temps de l'exécution. Comparativement à la première approche, celle-ci ne nécessite pas le stockage d'une base de données de solution, et a l'avantage d'être déterministe. Un autre compromis se présente alors, car l'exécution d'algorithmes d'ordonnancement est plus long, et leurs temps de décisions évoluent avec le nombre de tâches composant l'application.

Le calcul d'ordonnancement sur cible doit donc être rapide et performant afin d'obtenir une solution permettant l'exécution du service tout en respectant les contraintes. En ce sens, nous avons développé un heuristique d'ordonnancement permettant d'obtenir des solutions au problème d'allocation de ressources. En particulier, cet algorithme prend en compte l'unicité du gestionnaire de reconfiguration et du problème de partage de ressources que cela implique. Ainsi, l'heuristique d'ordonnancement proposé est capable de quérir les bitstreams des modules reconfigurables en avance de phase, pour que la RR assignée à une tâche soit reconfigurée au moment où cette tâche est prête à l'exécution. Cet heuristique est plus performant qu'une approche similaire de l'état de l'art en donnant des solutions dont la durée d'exécution sont plus courtes de 13% environ sur un ensemble de dix applications benchmarks issues de l'état de l'art. De plus, les résultats obtenus sur par génération de graphe de tâches d'applications montrent que bien que la complexité temporelle de évolue quadratiquement avec le nombre de tâches dans l'application, ses performances compensent le temps passé à calculer l'ordonnancement.

Cet heuristique a été utilisé en temps qu'algorithme d'ordonnancement de la solution orientée qualité proposée. Des simulations ont été effectuées sur le même simulateur que la première approche en ciblant l'application H.264 benchmark, ainsi qu'une application de contrôle de traction. Les résultats montrent que cette approche est capable de conserver la continuité de service dans 99% des cas en réponse à des contraintes de l'environnement, et jusqu'à 100% dans le cas de RRs ou CPU restreintes.

En résumé, ce travail de thèse répond au problème de garantie de service en prenant l'angle d'une gestion orientée qualité d'expérience et de service. À l'avenir, des approches statistiques (type scoreboard) ou d'apprentissage permettrai d'identifier des solutions particulières de la méthode hybrides. Elles correspondraient alors des solutions permettant de répondre à des niveaux de contraintes courants, et pourraient être sélectionnées plus fréquemment par la méthodologie afin de réduire le temps de décision. Enfin, l'optimisation énergétique étant une problématique importante de la littérature, l'impact sur la consommation du système dans sa globalité de l'utilisation de la RPD permettrait d'apporter des réponses sur l'intérêt de cette technique pour la réduction de la consommation. Deux axiomes se font alors écho: utiliser une matrice FPGA plus petite permet de réduire consommation en puissance, et la latence introduite par la gestion de l'allocation de ressource rend les petits FPGA reconfigurables dynamiquement plus lent que des plus gros FPGA statiques pour une même application. La réduction en consommation d'énergie reste alors à prouver.

# Acknowledgments

First of all, I would like to express my gratitude toward my supervisor, Professor Sebastien Pillement. He allowed me to pursue this PhD and provided great support throughout this project. I acknowledge his continued assistance and the relevance of his numerous feedbacks have greatly contributed to this work. I would also like to thank my defense committee; professors Daniel Chillet, Eduardo de la Torre, Russel Tessier, and François Verdier, for their efforts and time invested in reviewing my dissertation and attending my defense. I would also like to thank Wiem Kouki, Chabha Hireche, Céline Mayousse and Ahmed Kammoun from Capgemini Engineering's Research & Innovation department for their assistance during those past years.

I express my gratitude toward Sandrine Charlier, Marc Brunet for their administrative and technical assistance, as well as all the members of the IETR laboratory for their engaging discussions. I would like to express heartfelt thanks to all the PhD students and interns with whom I shared a slice of academic life: Safouane Noubir, Quentin Dariol, Guillaume Martin, Antoine Laspeyres, Corentin Darbas, Loreine Makki, May Myat Thu, Tamar Mosiashvili, Mustafa Ibrahim, Reem Ashi, Juliette Pottier, Nolwenn Dreano. Throughout these years, you have all enriched my daily life and made this experience unforgettable.

Finally, I would like to thank Sélèna Marti for keeping faith in my abilities and standing by my side throughout this long journey. I also dedicate this thesis to my parents Valérie and Fabrice Duhamel, and my sisters Clara and Alizée, as an expression of gratitude.

# Introduction

While the number of transistors on chips has effectively doubled for fifty years [1], transistor miniaturization for single-core general-purpose CPUs has slowed down as it became more difficult for the industry. To mitigate these issues and to increase computing performances, a shift has been made toward parallel computing. Using multi-core CPUs or GPUs, applications can be executed faster, but with higher energy consumption and more expensive chips. These are major drawbacks for embedded systems as their batteries have limited energy supply, and the Internet of Things (IoT) tendency shifts toward more computational power on smart devices.

To answer the energy consumption issue, the embedded systems industry has considered Application-Specific Integrated Circuits (ASIC) instead. These chips can be fully customized to meet application and system requirements, achieving the best performance-energy trade-off [2]. However, the high design cost of ASICs can only be compensated by economies of scale. In addition, ASICs cannot execute other workloads than what they have been designed for, which fails to meet the flexibility in usage that embedded systems require.

As an alternative, Field-Programmable Gate Arrays (FPGAs) offer a middle ground between performance, energy efficiency, and flexibility. They have notably been used in the embedded system industry for signal processing [3] and hardware acceleration on satellites [4]. In addition, while they offer high application-specific performance, these chips can be reconfigured to support a broad range of applications, or to mitigate firmware issues with the systems at a distance.

This characteristic can also be exploited to reconfigure only some parts of an FPGA, called Reconfigurable Regions (RRs), through Dynamic Partial Reconfiguration (DPR). Dynamically reconfiguring the FPGA enables the system to change hardware functionality at runtime. This helps reclaim unused parts of an FPGA at a given time in such a way that only what needs to be executed is implemented in the design. Using this technique, designers are virtually capable of executing the same workload on a smaller FPGA chip, in terms of available logic elements. However, this comes at the cost of having to share and manage these regions, which introduces latency. While a fully

static FPGA most likely outperforms dynamically reconfigurable FPGAs due to this latency, DPR can help reduce chip footprint, costs, and power consumption [5].

To benefit from hardware acceleration offered by dynamically reconfigurable FPGAs, there is a need for abstraction layers and software libraries. As a result, new architectural and methodology challenges are introduced to make the most out of dynamically reconfigurable FPGAs. In particular, the savings offered by smaller dynamically reconfigurable FPGAs should not come at the cost of an embedded system becoming unreliable.

Providing accessibility for application designers helps reduce the time to market for embedded systems [6]. To do so, new methodologies aiming to manage dynamically reconfigurable FPGAs should not require deep knowledge of the underlying hardware for the end-users, but still, provide enough control over the architecture.

The environment in which such systems evolve can require reactivity and flexibility, therefore the system must be robust and guarantees the service execution. This means that on top of the targeted applications, additional services can be executed in real-time to react to these events (eg. a drone computing new trajectories to avoid obstacles), or to withstand a system failure (eg: gamma-rays causing errors in satellite applications). In the context of this work, the guarantee of service refers to the execution of a targeted application under a real-time deadline, while maximizing the performance of the application running on the hardware. This is a key factor for industry as it ensures the benefits of using dynamically reconfigurable FPGAs do not come at a loss in reliability, which is critical for embedded systems.

To do so, the dynamic resource allocation problem must be answered to exploit the RRs in a time-multiplexed manner. This allocation must take into account the latencies of DPR operations on the FPGA and must be done at runtime to react to the constraints on the system. In addition, the decision times of this management must be low enough that it doesn't impact negatively the capabilities of the system to withstand the constraints.

### 1.1 Contributions

To solve the challenges of guaranteeing service execution on dynamically reconfigurable FPGAs, we propose:

• A quality model for the guarantee of service characterization: a model of quality is introduced to characterize the level of service of an application running on the hardware. This model is described at the functional level not to introduce extensive design efforts from the application designers. The introduced model of quality is based on the identification of parameters that impact the perceived quality. These parameters can then be tuned at runtime to increase or lower the computeintensiveness of the targeted application.

- Quality-oriented management methodologies: using our model of quality, we introduce both a hybrid design-time/runtime methodology and a runtime scheduling-based methodology to autonomously manage the runtime of a targeted application in such a way that it ensures the respect of its real-time deadline. These methodologies are capable of upgrading and downgrading the modeled quality of the application to maximize its perceived quality. When doing so, they dynamically allocate resources to execute the applications. The runtime complexity of these methodologies is considered as their decision latency impacts the system's performance.

- Fast and efficient runtime scheduling: to increase the adaptability and scalability of the system, we introduce a novel scheduling heuristic to help meet application deadlines. This scheduling heuristic is capable of processing applications described at the functional task level to work with the introduced quality model. Special attention is brought to the management of FPGA dynamic partial reconfiguration management to shorten the obtained schedules.

# 1.2 Dissertation organization

The remainder of this document is organized as follows:

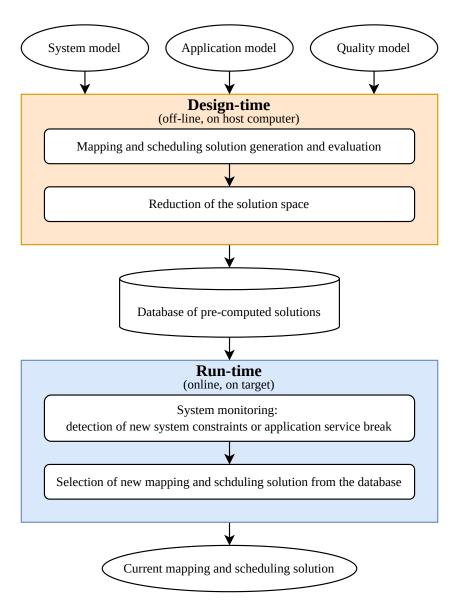

- Chapter 2 introduces the architectural challenges introduced by dynamically reconfigurable FPGAs and describes different approaches of interest from the literature. We compare frameworks and operating system libraries for such systems on key features. In addition, we identify gaps in the literature on the management of dynamically reconfigurable FPGAs with a focus on the guarantee of service and application designer accessibility. Finally, we conclude with the adopted methods and hypotheses made in this thesis and introduce our targeted architecture.

- Chapter 3 introduces our quality model and concept of execution modes of an application. This concept is then applied to a hybrid

design-time/runtime management methodology and illustrated with a H.264 application example. An experimental setup is introduced with emulation of the targeted architecture to introduce constraints on the FPGA and CPU. We then evaluate its performance in terms of perceived quality and guarantee of service, using application duration and time before deadlines as primary metrics.

- Chapter 4 describes and discusses the scheduling heuristic for dynamic resource allocation, which is the second main contribution of this work. We first introduce its prediction capabilities to shorten schedule makespan (or duration), then how the dynamic reconfiguration operations of the FPGA are taken into account. State-of-the-art techniques for management latency minimization are introduced. Its performance is evaluated and compared with another recent approach from the literature, identified in chapter 2. Finally, the heuristic is integrated into the quality-oriented management methodology to increase the guarantee of service.

- Chapter 5 summarizes the contributions of this thesis and discusses obtained results. We also identify future works required to improve the flexibility and performance of our approach.

# Background and model definition

## Contents

| 2.1 | Self- | reconfigurable system design                           | 6  |

|-----|-------|--------------------------------------------------------|----|

|     | 2.1.1 | Reconfigurable region definition                       | 6  |

|     | 2.1.2 | DPR management methodology                             | 8  |

|     | 2.1.3 | Architecture design for reconfigurable systems         | 11 |

|     | 2.1.4 | Frameworks and libraries                               | 15 |

|     | 2.1.5 | Proposed architecture                                  | 26 |

| 2.2 | Self- | reconfigurable systems management                      | 29 |

|     | 2.2.1 | Management methodologies                               | 30 |

|     | 2.2.2 | Mapping and scheduling for self-reconfigurable systems | 33 |

|     | 2.2.3 | Hybrid methodologies                                   | 42 |

| 2.3 | Con   | clusion                                                | 43 |

To save logic elements resources on FPGA matrices and optimize energy consumption of the FPGA, Dynamic Partial Reconfiguration (DPR) has been used in the past to modify the behavior of hardware functionalities during runtime, such as for multi-standard software defined radio [3] and for high performance computing [7, 8]. Over the years, multiple works have been conducted to manage the DPR technique to dynamically reallocate the hardware over time, i.e. in a time-multiplexed way as with threads on a CPU. In this manuscript, we define self-reconfigurable systems as Systems on Chip (SoC) embedding a FPGA matrix capable of performing DPR in order to adapt the hardware accelerators.

This chapter first introduces the self-reconfigurable computing paradigm at large and its associated challenges for FPGA architecture design. Existing architectures are introduced, from which we propose our model. A focus is put on functional abstraction layers for hardware resources. Then, we review existing management methodologies and techniques for self-reconfigurable systems with guarantee of service.

## 2.1 Self-reconfigurable system design

Self-reconfigurable systems rely on the DPR capabilities of their FPGA matrix. To benefit from DPR, Reconfigurable Regions (RRs) must be defined offline when designing the FPGA architecture.

## 2.1.1 Reconfigurable region definition

The two mainstream competing vendors; AMD Xilinx and Intel Altera, propose FPGAs that are capable of performing DPR.

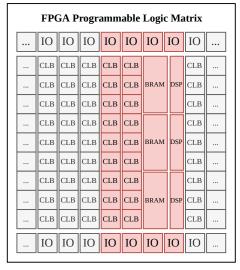

However, a fundamental difference lies in the way RRs are defined in their matrices. Figure 2.1 introduces two ways to define RRs in a FPGA matrix. The column-based definition takes whole columns in the matrix for partial reconfiguration. This was how RRs were defined when DPR was first introduced.

Since then, region-based definition has been introduced to perform DPR in rectangular regions, defined by the coordinates of the logic elements located at the corners of the defined RRs [9, 10]. Region-based definition is more flexible than column-based as it only defines which logic elements are going to be reconfigured, but requires more control.

The literature has mainly focused on Xilinx technologies as they natively support region-based RR definition, whereas Altera still supports column-

Column-based (a)

Region-based (b)

Figure 2.1: Column-based (a) and Region-based (b) Reconfigurable Regions (RRs) definition in FPGA matrices.

based definition. In addition, Xilinx currently offers an on-going support for their DPR design flow [10] and through dedicated software libraries to co-design software and DPR-capable hardware via the Vitis accelerated libraries [11] and the PYNQ project [12].

It has been proven that region-based definition can be used for Altera technologies by masking logic elements that should not be modified [9]. However this adds an additional step when designing with column-based definition.

Therefore in this thesis we will focus on Xilinx technologies and their terminology, yet self-reconfigurable systems using Altera technologies work similarly, this RR definition difference set apart.

To configure the logic elements of a FPGA, a configuration file must be loaded, called bitstream or bit file, in the FPGA's SRAM configuration memory. This read/write memory contains the states of Configurable Logic Blocks (CLBs), Block RAM (BRAMs) and DSP blocks, and the way they are connected to each other to perform a given hardware behavior.

The statically defined RRs can then be filled with hardware accelerators through a bitstream which will configure solely the defined part of the FPGA matrix. Hardware accelerators targeting a specific RR are denoted as Reconfigurable Modules (RMs). After implementation by the toolchain, the obtained configuration file is called partial bitstream, as opposed to the full static bitstream which configures the whole FPGA.

Typically, the configuration bitstreams are stored in an SD card or any read-only memory that's on the board, and are loaded at startup. The CPU of the system is generally used to load the configuration bitstream in the configuration memory through the Configuration Access Port (CAP) of the FPGA. The latter being the only channel with the read/write configuration memory. The Xilinx software development kit makes it possible to perform this operation with the First Stage Boot Loader (FSBL) before loading an Operating System (OS) [13].

Self-reconfigurable systems are still subject to this startup configuration. Whereas the full static bitstream is usually loaded in the configuration memory via the CPU (or JTAG for debugging) once at startup, partial bitstreams can be loaded at runtime via different methods. We'll be referring to any of such methods as DPR management methodology.

## 2.1.2 DPR management methodology

DPR controllers are responsible to manage the DPR process. Performance of this process, in terms of bandwidth, is crucial for self-reconfigurable systems. In practice, faster reconfiguration operations lower the latency overhead when changing the RM in a RR.

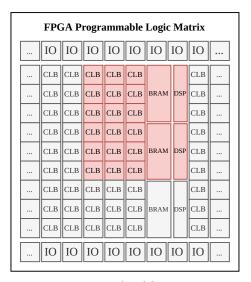

To load the configuration memory with a partial bitstream, two main methods or paths can be used: Processor Configuration Access Port (PCAP) and Internal Configuration Access Port (ICAP). Figure 2.2 illustrates both paths for commonly-used Zynq-7000 device [14].

The PCAP path is the most supported by Xilinx vendor toolchain and devices, notably with the support of dedicated software libraries [12, 15]. When loading a partial bitstream, the CPU sends a request to the Device Configuration (DevC) interface so that its embedded DMA engine fetches the bitstream in the DDR memory. The partial bitstream must have been transferred from local memories to the DDR memory beforehand. The bitstream is sent to the PCAP controller which verifies the integrity and validity of the bitstream. Finally, it is loaded in the configuration memory.

This path provides an easy way to handle DPR operations as it uses the dedicated device configuration interface. This path comes with no additional cost on the designer's side as this interface is already implemented in modern Xilinx SoPCs. However, the provided Python [12] and C [15] libraries suffer from relatively low bandwidth (2.04 and 13.6MBps) compared to other custom PCAP approaches which reach higher bandwidth at 145MBps as in [9]. Such differences can be explained by different DevC interfaces and further library

Figure 2.2: PCAP (left) and ICAP (right) paths for partial bitstream flow. The asterisk between the Multiplexer and PL Configuration Memory boxes indicates presence of another multiplexing step for JTAG PL configuration.

optimizations.

The PCAP path also actively uses the CPU as the latter configures the DevC interface DMA engine so the bitstreams are properly fetched from the memory (DDR or SD card).

The ICAP path is the other main method of performing DPR operations. The main advantages of this reconfiguration path is that they reach higher bandwidth, and free the CPU from the DPR operation. However, it comes at the cost of having dedicated logic within the FPGA matrix to perform the DPR operation.

Xilinx's SoCs allow the static programmable logic to access the ICAP resource. In theory, a static design could fetch a bitstream in DDR memory and reconfigure a RR without using the CPU at all. In practice, the CPU, or a soft processor like the Microblaze, is often used to initiate the DPR process through dedicated libraries.

Coupled with a DMA engine in the FPGA programmable logic, Xilinx's hardware ICAP IP (HWIP) can achieve up to 82MBps bandwidth [16, 17]. Further optimizations on the bitstream fetching part in [17, 18] brings the bandwidth up to 382MBps, which is near the maximum theoretic 400MBps

bandwidth for a 32b data bus at 100MHz.

Thanks to custom designs, works from the literature have achieved higher bandwidth than PCAP approaches. Using on the fly lossless bitstream decompression and ICAP overclocking, other approaches [19, 20, 21] were able to reach bandwidths as high as 1.5GBps. Those approaches store compressed bitstreams and decompress them in the FPGA matrix so there are less data to transfer from the memory.

To the best of our knowledge, the highest bandwidth of 2.2GBps has been achieved by [22] with a custom ICAP design overclocked at 550MHz. Although these approaches impose static design restrictions, authors of these works have made efforts to lower the amount of occupied logic elements to 1K LUTs and FFs on average (approximately 2% of LUTs and 1% of FFs in a ZYNQ-7000 XC7Z020 SoC FPGA) which makes it a relatively good trade-off between bandwidth and implementation cost.

Table 2.1 introduces a comparison of DPR controllers sorted by increasing bandwidth. Because self-reconfigurable systems require prior reconfiguration of RRs, higher bandwidth is crucial to minimize the reconfiguration latency overhead as higher bandwidth leads to lower reconfiguration time.

Spent resources for custom ICAP-based controllers takes between 1.8% to 7.52% of LUTs, and 0.38% to 1.42% of a Xilinx Zynq-7000 Artix-7 XC7Z020 FPGA matrix, which is a popular cost-optimized device. However, among all DPR controller approaches, the ICAP-based DPR controllers have a clear advantage over PCAP-based when it comes to bandwidth. ICAP-based approaches also free up the CPU to run OS services and application-related processes.

In our work, we distinguish two categories of ICAP-based DPR controllers: those who do not impose clock frequency constraints and the others. The first category implies a standard 100MHz clock as it is most often used in FPGA designs, which caps the theoretical bandwidth at 400MBps. In this category, the recent ZYCAP DPR controller [18] is the best trade-off between bandwidth and static implementation cost.

| DPR controller                             | Bandwidth     | Resources usage     | Frequency |  |

|--------------------------------------------|---------------|---------------------|-----------|--|

| DFR controller                             | (MBps)        | (LUTs & FFs)        | (MHz)     |  |

| PCAP controllers                           |               |                     |           |  |

| PCAP Python Overlay [12]                   | 2.04          | -                   | -         |  |

| XilFPGA PCAP C Library [15]                | 13.6          | -                   | -         |  |

| Custom PCAP bit. transfer [9] <sup>1</sup> | 145           | -                   | -         |  |

|                                            | ICAP controll | ers                 |           |  |

| Xilinx HWICAP [16]                         | 19            | 1K LUTs, 0.7K FFs   | 100       |  |

| Xilinx HWICAP (DMA) [16]                   | 67            | 4K LUTs, 6.2K FFs   | 100       |  |

| DMA HWICAP [17]                            | 82            | 4K LUTs, 0.9K FFs   | 121       |  |

| BRAM HWICAP [17]                           | 332           | 1K LUTs, 0.5K FFs   | 121       |  |

| ZYCAP [18]                                 | 382           | 1.1K LUTs, 0.8K FFs | 100       |  |

| FaRM [19]                                  | 800           | 3.2K LUTs, 0.4K FFs | 200       |  |

| uPaRC [20]                                 | 1'433         | 4K LUTs, 1.1 FFs    | 362.5     |  |

| Pham et al. 2 [21]                         | 1'480         | 4.4K LUTs, 1.5 FFs  | 370       |  |

| Hansen et al. <sup>3</sup> [22]            | 2'200         | -                   | 550       |  |

Table 2.1: Comparison of DPR controllers, sorted by bandwidth.

The second category considers DPR controllers that overclocks the ICAP resource. Those approaches make implementation more difficult as timing requirements are harder to meet for the toolchain's place and route steps. Still, those approaches outperform the approaches from the first category with bandwidths up to 5 times higher. In this category, we will consider the profiled bandwidth of the uPaRC DPR controller [20].

## 2.1.3 Architecture design for reconfigurable systems

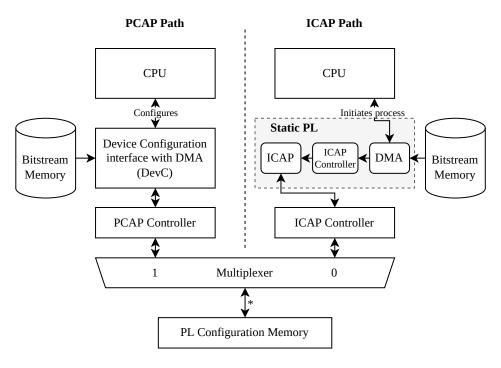

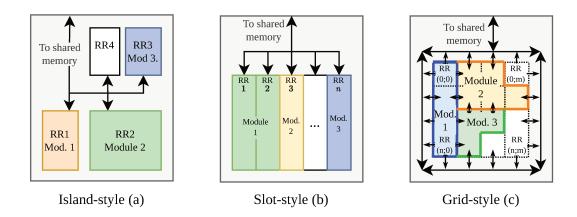

Self-reconfigurable systems can be classified based on their RR architecture style when designing around DPR. Each architecture style comes with their own pros and cons which can make them more suitable to specific paradigm of hardware accelerators (or RM). Three architectures styles cover the majority of DPR approaches: Island, Slots, and Grid styles, as illustrated in Figure 2.3.

<sup>&</sup>lt;sup>1</sup> Authors made use of a custom devC interface.

<sup>&</sup>lt;sup>2</sup> Requires a Microblaze as introduced in [21], but can be modified to use the SoC's ARM CPU instead. Resources given without the Microblaze.

<sup>&</sup>lt;sup>3</sup> Authors did not disclose the resources usage of the full reconfiguration controller.

Figure 2.3: The three main RR architecture styles in DPR-capable FPGAs. Black arrows denote communication channels between RRs and the external shared memory.

In this figure, the FPGA matrix is represented by gray squares which denote the static region, and RRs by colored rectangles inside. The footprint difference of the RRs can be noted, as their number and size respectively increases and shrinks from island style to grid style. This footprint difference is referred to as granularity in the literature [23, 24, 25], and ranges from coarse to fine grain. Coarse-grain defines monolithic accelerators which define RRs in the island styles, while medium-grain refers to functional units which corresponds to slot and grid styles [25].

The fine granularity refers to RRs which comprises just a few specific logic elements to fine-tune parts of the design [25]. However, this granularity fits specific designs and do not focus on supporting a wider range of generic hardware accelerators. For this reason, the fine granularity will not be discussed further in this work.

#### 2.1.3.1 Island style

Island style consists in having few coarse-grain RRs fitting monolithic hardware accelerators (eg: vision application filtering, edge detectors...). A number of works have focused on this style of architecture [24, 26, 23], and it can be considered the most commonly used style.

The communication infrastructures used in these architectures can employ crossbar switches, which have the advantage of low congestion latency. However, crossbar switch resource usage scale exponentially with the number of nodes connected to it [27].

Monolithic accelerators imply that all the dedicated logic elements have to fit inside a single RR. This type of architecture is the easiest to design, as users can make use of High Level Synthesis (HLS) vendor toolchain to rapidly build hardware accelerators to populate the RRs.

Applications can then be described at the functional level to obtain a set of hardware accelerators to speed it up, without much knowledge of the underlying hardware except for what comprises the targeted RRs. This architecture style is often considered high level in comparison to the other styles for this reason.

Because the accelerators are functionally different, their synthesis can result very different number of spent logic elements. Hence the biggest RR in the design has to be at least big enough to fit the largest accelerator. When smaller accelerators are to be implemented, if they are placed in a bigger RR, it causes resource wastage (or resource fragmentation), as the rest of the free logic elements in the targeted RR cannot be used by other accelerators. An island style comprising only RRs of similar logic elements count is considered homogeneous.

Resource fragmentation can be reduced by introducing RRs of different size [24], but this introduces some limitations at runtime as to which accelerator can fit which RR. This hypothesis is called heterogeneous RR size. Using those, it is possible that certain RMs do not fit in all RRs and that execution times of RMs differ between RRs. Having RRs of different size can be beneficial to minimize the reconfiguration latency as the size of partial bitstream files scale with the region footprints, and not with the resource usage in the RR [10].

Finally, this style of architecture gets the most support from Xilinx and Intel as their dedicated toolchain official documentation explicitly supports such architectures [10, 28].

#### 2.1.3.2 Slot style

Slot style architectures tackle the resource fragmentation issue from another point of view. They focus on accelerators that can span one or more RRs, while considering a larger number of fixed size RRs called slots [29]. The medium-grain RRs can fit functional units that may not always correlate to high level functional description as would monolithic accelerators.

This style of architecture usually supports RRs with similar size and logic elements content so that accelerators can be implemented in such a way that they occupy a minimum number of slots to minimize resource fragmentation.

Because the number of considered RRs in the FPGA architecture increases compared to island style, slot style greatly benefits from bitstream relocation [30, 31].

Bitstream relocation consists in taking a RM that targets a given RR i, and relocating it to another RR j. This can be achieved by modifying the configuration header of the bitstream files, which gives information on the localization of a RR in the matrix [10]. Runtime bitstream relocation imposes a latency overhead which in the range of tens of microseconds [31] to milliseconds [30].

However it is paramount that the content (in logic elements) of the original bitstream, and its rectangular shape in the matrix, are exactly identical to the RR that the bitstream is relocated to [31].

This imposes a heavy constraint on the FPGA architecture when defining RRs in the matrix. If slots are too big in proportion of the FPGA matrix, finding similar RRs with the exact logic elements content and shape is harder. This can be less constraining for high-end FPGA chips with Xilinx super logic regions [32, 33] and multi-FPGA reconfigurable systems [33, 34] as they have more resources to partition in slots.

#### 2.1.3.3 Grid style

Finally, grid style further reduces the size of individual RRs. Here, the number of RRs increases significantly as RRs are reduced to a few logic elements organized in a systolic array [35, 36, 37]. Because of the very high number of RRs, grid style architectures rely on dedicated framework to generate flexible partial bitstreams and make extensive use of the bitstream relocation technique [38].

Compared to the other approaches, grid style architectures have the highest flexibility when it comes to implement RRs in the FPGA matrix. Thanks to bitstream relocation, RMs spanning multiple RRs can be moved within the RR grid, and arranged to minimize fragmentation [39, 40].

However, grid style architectures have a bigger static architecture overhead compared to other styles [24]. As shown in Figure 2.3 (c), multiple communication gates between the dynamic and the static region must be defined when designing the architecture. Each gate must be connected to a bigger communication infrastructure so that virtually any combination of RR implementation is valid.

While slot and grid style architectures can minimize dynamic resource fragmentation, the implementation costs brought by the different overlays and frameworks can hinder their adoption by application designers. On the other hand, commercial-off-the-shelf (COTS) accelerators and HLS-built modules can easily be integrated into application designers design flow.

Slot and grid style approaches also require intensive use of runtime bitstream relocation. The latency introduced by bitstream relocation can become problematic to the service execution of real-time applications.

In this work, we believe the island style architectures with coarse-grained RRs of heterogeneous size are a good trade-off between resource fragmentation and ease of use [24].

### 2.1.4 Frameworks and libraries

To make use of the introduced DPR capable island style architectures, works have been focusing on designing dedicated operating system libraries and frameworks. Their goal is to provide software abstraction of dynamically reconfigured accelerators, so that application designers benefit from software flexibility and the computing performance of hardware accelerators. Researchers have then tackled the challenge of building hardware abstraction layers to manage the architecture's RRs efficiently.

In the following sections, we first introduce the different abstraction levels used in the literature, and then introduce the hardware preemption mechanism for the real-time paradigm on self-reconfigurable systems. We then introduce the features of interest when reviewing the existing frameworks and operating system libraries.

#### 2.1.4.1 Abstraction level

Hardware abstraction consists in providing the user with software routines to manage the self-reconfigurable system's FPGA architecture [41]. Choices made on the FPGA architecture and the targeted functional level of abstraction define different approaches.

As the goal is to provide users a generic methodology to implement their accelerated applications, a level of functional abstraction must be chosen. The level of abstraction must reflect the granularity of the FPGA architecture and its specificities.

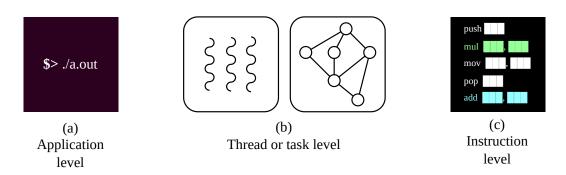

We define 3 main levels of functional abstraction as illustrated Figure 2.4. The application level of abstraction makes the targeted FPGA architecture a black box for the user. By similarities with UNIX systems, the accelerated application is considered holistically as a single process that the user can interact with through a dedicated API.

Figure 2.4: Functional abstraction levels sorted from highest (left) to lowest (right).

This type of approach was first considered in the early stages of reconfigurable computing [42] with applications comprised of a single monolithic accelerators. It is still employed in multi-tenant deployment of FPGA-based accelerators [7], and can also describe recent frameworks that aim to compile software into functional units for grid-style DPR-capable architectures [43]. Application level abstraction is the easiest to comprehend as generating big monolithic accelerators is relatively easy with HLS languages and require no prior knowledge of the underlying architecture. Because this level of abstraction implies the usage of large RRs to fit big accelerators, it mostly relies on island-style coarse-grain architectures and multi-FPGA systems.

The thread or task level of abstraction, cf. Figure 2.4(b), consider a division of the targeted application into accelerated threads or tasks. The resulting partition of the application can then be represented as a task graph, and further parallel or pipeline execution optimization can be introduced at this step [41]. Following this partition of the application, tasks or threads can be identified as best candidates for acceleration and implemented as hardware accelerators. The frameworks and libraries' goals are then to manage those threads and tasks, with respect of the FPGA DPR-capable architecture [44]. Parts that may not benefit much from hardware accelerator, such as purely sequential code or monitoring tasks, can be executed on the self-reconfigurable system's CPU.

Smaller RRs in the architecture can fit with this abstraction level as the application execution is spread across multiple RRs. High performance of the communication infrastructure in terms of high bandwidth and low latency becomes important to maximize application speedup.

Finally, instruction set level of abstraction achieves very low level accelerators description. Its goal is to accelerate the execution of software by accelerating frequent instructions, for RISC-V CPU architecture [45] as a hot

topic example. This last level of abstraction requires application designers to know which instructions, or low-level software routines equivalent, can be accelerated when writing their software programs.

In our works, we focus on the task level of abstraction. Because it relies on a functional level definition, we believe such an abstraction level is suitable to define which parts of the application need to be accelerated.

Additionally, the application level might cause difficulties for guarantee of service execution as the former can lead to high logic element fragmentation because of the coarse-grain island style architecture, resulting in under performing systems. Instruction level on the opposite can help fine-tuning the targeted application's acceleration, but requires a complex framework which end-users can't really tune at run-time for their own goals.

#### 2.1.4.2 Hardware preemption

In a software real-time operating system, task-level preemption momentarily interrupts the execution of a task to free up a CPU core to execute another task. Preemptive multitasking has been used in conjunction with priority-based scheduling to guarantee the execution of higher priority tasks over lower priority ones. Hardware preemption for a self-reconfigurable system aims to bring this feature to preempt hardware accelerators. This feature is interesting for a self-reconfigurable system with guarantee of service as it is notably used in the industry to increase systems reactivity.

To perform any kind of preemption, the system performs a context switch on the task. This context switch consists in three steps: interrupting and saving the task's progress, executing an other task, restoring the preempted task. In software, the task's progress consists of the states of CPU registers, stack pointer and program counter. In hardware however, progress of a task implemented in a RR consists of its FFs and local BRAMs states, plus any processed and unprocessed data that is in the shared DDR memory or still transiting in the communication infrastructure.

To tackle the challenge of hardware preemption, researchers have come up with two main methodologies: Configuration Access Port (CAP)-based and Task-Specific Access Structures (TSAS).

CAP-based methodology consists in using bitstream read back of the configuration memory. This feature allows to extract information on the logic elements states in the FPGA, and can be applied to RRs as well. Then, the partial bitstream which contains the FFs and local memories states can be saved in a local or external memory to be restored later. This idea dates back

as early as 2000 where authors of [46] designed a hardware context switch using this method.

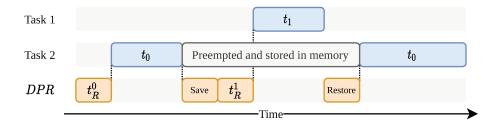

Figure 2.5: CAP-based hardware preemption of Task 1 over Task 0 on a single RR.

Figure 2.5 illustrates CAP-based hardware preemption of a task on a single RR. The DPR schedule shows how the context switch operations can impact the unique ICAP resource usage.

Bitstream size grows with the size of the corresponding RRs, and can reach multiple hundreds of kilobytes. Because local BRAM memories are limited within the FPGA, works have been trying to reduce the amount of extracted data by storing only state information of slices that are used in the RR [47, 48].

Finally, authors of [49] have used the CAP method on a recent framework for preemptive multitasking and disclosed the resulting time spent saving  $(T_{save})$  and restoring  $(T_{restore})$  during a hardware context switch. Obtained results on RR sizes  $S_1$  and  $S_2$  occupying respectively 6% and 2% of a Virtex-6 FPGA are presented in Table 2.2.

Table 2.2: Context switching results of CAP-based hardware preemption on a Xilinx Virtex-6 ML605 board from [49].

|       | FFs in RR | LUTs in RR | Bitstream size (kB) | $T_{save}$ (ms) | $T_{restore} $ (ms) |

|-------|-----------|------------|---------------------|-----------------|---------------------|

| $S_1$ | 17k       | 8.6k       | 741                 | 16.0            | 9.7                 |

| $S_2$ | 5.8k      | 2.9k       | 361                 | 10.3            | 5.5                 |

The approach introduced by authors of [49] get a 30MBps bandwidth for the context switch operation as bitstreams are stored in the shared DDR memory. This bandwidth can be compared with the previously introduced DPR controllers which had up to 382MBps without overclocking the design, even if bandwidth optimizations cannot be applied to both the read and write bandwidth equally [22]. In addition, the saved bitstream can only be restored on the same RR, unless bitstream relocation is involved which also adds latency and require specific architectures.

This highlights the main issue with the CAP-based hardware preemption as it occupies the unique ICAP resource in the FPGA during the context switch operation. It can also be argued that CAP-based methodologies, and their storage size reduction optimization in particular, are technology-dependent. Recently, authors of [50] exposed the bitstream composition and required manipulations to save and restore context on 7-series and Ultrascaleseries Xilinx FPGAs using ICAP read back capabilities, showing this approach can still be applied nowadays.

To mitigate the added occupancy on the ICAP resource, researchers have developed Task-Specific Access Structures (TSAS) methodologies [51, 52, 53, 54]. This type of hardware preemption consists in defining one or multiple task checkpoint(s) within the accelerator description. Different ways to create checkpoints have been studied such as using scan-chains copying the states of LUTs inside the RRs [51, 55], storing the states of specific FFs in a memory-mapped memory [51, 54], and using HLS tools to generate checkpoints [53]. Then, when a hardware task is to be preempted, only the content of those checkpoints is saved and restored, and the remaining uncheckpointed FFs and BRAMs states are dropped.

This type of hardware preemption can also support cross-RR preemption as the content of those checkpoints can be made in a way that they're not dependent on a specific RR. However, checkpoints add extra logic inside the RRs. This logic overhead depends on the used method, and recent approaches [53, 54] disclose up to 7% of LUTs and FFs overhead in RRs while achieving millisecond range context switches.

Finally, authors of [56] study the impact of preemption on priority-based real-time scheduling policies for applications comprised of software and hardware tasks. In this study, authors hypothesize an ideal hardware preemption mechanism with no logic nor time overhead. They compare this ideal preemption with non-preemptive scheduling (Block), and two other scheduling policies (Drop and Rollback). The Drop policy erase any progress made by the hardware task and restarts it from the beginning later on the same RR, while the Rollback policy restarts immediately the task in software after dropping the accelerator.

Comparison on AES encryption and Xvid video codec benchmarks show that whether the tasks were short and frequents, or intermittent and long, the ideal hardware preemption schedule is approximately 10% shorter than the non-preemptive scheduling policies. This paper highlights that latency cost of hardware preemption has to be seriously taken into account as they can quickly outweigh any gains in schedule makespan.

As a conclusion, if hardware preemption has been made possible, the inherent overhead in context switch duration, spent logic elements and design considerations hampers its use. Furthermore, works have shown that non-preemptive scheduling policies can reach similar performance without those limitations. For these reasons, we will not consider hardware preemption as a feature.

#### 2.1.4.3 Features of interest

In this section, we define four features of interests to review frameworks and libraries for self-reconfigurable systems. We focus on approaches that target task-level accelerators in coarse-grained RRs of heterogeneous size organized in island style architectures. We define the following features:

- **POSIX-like API**: Presence of a dedicated API to manage hardware accelerators makes for an easier development on the software side [41]. This API should abstract hardware to hide specific architecture specifications from the application designer.

- RR Point-to-point communication: Data transfer between hard-ware accelerators using DMA access is a major bottleneck [24]. Point-to-point (P2P) communication between RRs within the FPGA helps reducing communication latency and decreases shared memory congestion.

- Standardized RR interfaces: Generic standard interfaces between the dynamic and the static regions helps designing the communication and control infrastructure. These interfaces need to be the same across all RRs so they are abstracted the same way on the software side through the API. In addition, a standard interface helps designing accelerators as designers only have one interface to study.

- Runtime resource management: Computational resources (RRs and CPU) should be managed by the framework, through real-time paradigm, task scheduling or autonomic management. In particular, the system must be resilient to RR unavailability as a result of a failure [4], or additional tasks or services to execute at runtime [57].

#### 2.1.4.4 Related works

Operating System for Reconfigurable Systems (OS4RS) [58] was one of the first OS designed for self-reconfigurable systems. It was built with the Real-

Time Application Interface (RTAI) extension of a Linux kernel. The RTAI API was used to manage hardware accelerator as tasks in a standard real-time system, and RTAI's priority-based scheduler was employed as a mean to manage resources. The OS4RS targeted architecture made use of a standard RR interface to send data packets over a Network on Chip (NoC) which was capable to transfer data between RRs within the FPGA matrix. While its performance and used toolchain are now outdated, OS4RS still constitutes an interesting approach given our selected features of interest.

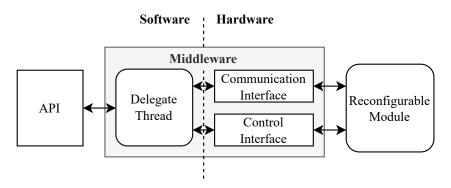

Figure 2.6: Software delegate thread concept enabling data communication and control of a reconfigurable module.

HThreads [59] is to the best of our knowledge the first approach that makes use of a POSIX-like hardware threads model. Hardware threads are abstracted by a software delegate thread, illustrated Figure 2.6, that the dedicated API can interact with as if it was a standard software thread. This concept is an interesting hardware abstraction solution as application designers keep a software stub to manage the hardware accelerator, and actions taken on the delegate thread are reflected to the accelerator. HThreads is based on a Real Time OS (RTOS) kernel that makes use of a priority-based scheduler that is able to manage hardware accelerators. However, while this approach provides an interesting take on POSIX-like API with delegate thread, this approach lacks most of the architectural considerations and offer no runtime management.

The **FOSFOR** project (Flexible Operating System FOr Reconfigurable platform) [60, 61] is an extension of RTEMS (Real-Time Executive for Multiprocessor Systems) for self-reconfigurable systems. Similarly to Hthreads, FOSFOR comprises middle ware to abstract hardware communication. This project's goal was to demonstrate the feasibility of abstracting the hardware accelerators for application designers by using RRs as threads.

FOSFOR's middle ware follows the concept of delegate thread introduced

in Figure 2.6. In FOSFOR, the RRs interface between static and dynamic region consists of a communication and control interface. The communication interface is plugged to a flexible NoC called DRAFT [62]. It is a reconfigurable fat-tree topology network for data flow communication, well adapted for RR to RR communication. The control interface interacts with a dedicated finite state machine located inside the RR that is customized to the accelerator.

The software part of FOSFOR's middle ware is comprised of a custom API to create and manage virtual communication channels. They consist of delegate threads that are software images of the DRAFT configuration.

This work has achieved a speedup up of  $50 \times$  for selected applications, compared to full software RTEMS implementations. However, FOSFOR does not provide any runtime resource management.

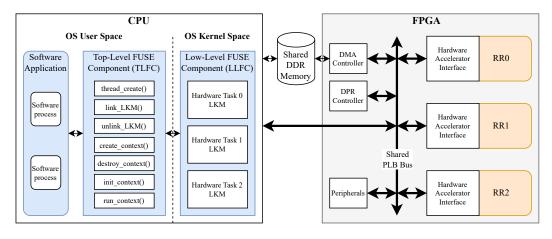

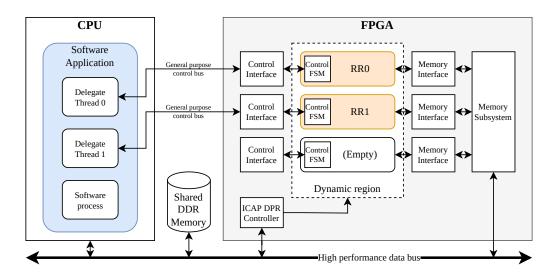

FUSE (Front-end USEr framework) [63] is a framework extending the PetaLinux operating system (now one of Xilinx's tools) with a multi-threaded programming model approach. Its RRs, denoted as hardware threads, don't require a dedicated delegate threads as it was the case in FOSFOR. They instead rely on its software POSIX-like API for RR management. As illustrated in Figure 2.7, this management is done in the CPU from the user space via the Top-Level FUSE Component (TLFC), then handled in the kernel space by the Low-Level FUSE Component (LLFC).

Figure 2.7: Overview of FUSE's targeted architecture [63].

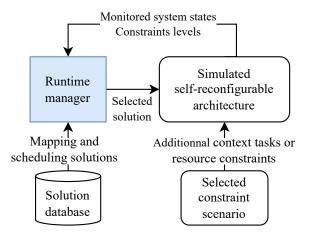

When calling the API from the TLFC to instantiate hardware threads, management of the accelerator is abstracted by the LLFC. The latter is responsible for the management of the RRs and communicates with the FPGA. In the FPGA, each RR has the same hardware accelerator interface with the static region. Data and control communications are differentiated in the interface, and those can either be fully customized or made standard.