# Design of a secure kernel for constrained devices Nicolas Dejon

#### ▶ To cite this version:

Nicolas Dejon. Design of a secure kernel for constrained devices. Embedded Systems. Université de Lille, 2022. English. NNT: 2022ULILB038. tel-04093312

## HAL Id: tel-04093312 https://theses.hal.science/tel-04093312

Submitted on 10 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Université de Lille Orange

École doctorale **Ecole Graduée MADIS-631**Laboratoire **CRIStAL**

Thèse par Nicolas Dejon

Soutenue le 14 décembre 2022

Mémoire présenté en vue de l'obtention du grade de

### Docteur de l'Université de Lille

Discipline **Informatique**Spécialité **Informatique et applications**

# Conception d'un noyau sécurisé pour objets contraints

Thèse dirigée par Gilles Grimaud Directeur de thèse

Julien Cartigny Co-directeur de thèse Chrystel Gaber Co-encadrante

#### Composition du jury

| Rapporteurs        | Didier Donsez  Jean-Pierre Talpin | Professeur des Universités à l'Université de<br>Grenoble-Alpes, LIG<br>Directeur de recherche à l'INRIA Rennes |             |

|--------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|

| Examinateurs       | Romain Rouvoy                     | Professeur des Universités à l'Université de Lille,<br>CRIStAL                                                 | (Président) |

|                    | Marie-Laure Ротет                 | Professeure des Universités à l'Université de<br>Grenoble-Alpes, VERIMAG                                       |             |

|                    | Julien Sopena<br>Patricia Mouy    | Maître de conférences à Sorbonne Université, LIP6<br>Chercheuse-Docteure à l'ANSSI                             |             |

| Invité             | Jean-Philippe Wary                | Responsable de programme de recherche à Orange Innovation                                                      |             |

| Direction de thèse | Gilles Grimaud                    | Professeur des Universités à l'Université de Lille,<br>CRIStAL                                                 |             |

|                    | Chrystel Gaber                    | Ingénieure de Recherche-Docteure à Orange                                                                      |             |

Innovation Caen

|                         |                                                     | Colop                                                          | PHON             |                      |                            |

|-------------------------|-----------------------------------------------------|----------------------------------------------------------------|------------------|----------------------|----------------------------|

| Manuscrit<br>Dejon, cor | de thèse intitulé « Con<br>nposé au moyen du s<br>d | ception d'un noyau<br>ystème de prépara<br>édiée aux thèses pr | tion de document | LATEX et de la class | par Nicolas<br>se yathesis |

|                         |                                                     |                                                                |                  |                      |                            |

|                         |                                                     |                                                                |                  |                      |                            |

|                         |                                                     |                                                                |                  |                      |                            |

|                         |                                                     |                                                                |                  |                      |                            |

|                         |                                                     |                                                                |                  |                      |                            |

|                         |                                                     |                                                                |                  |                      |                            |

## Université de Lille Orange

École doctorale **Ecole Graduée MADIS-631**Laboratoire **CRIStAL**

Thèse par Nicolas Dejon

Soutenue le 14 décembre 2022

Mémoire présenté en vue de l'obtention du grade de

### Docteur de l'Université de Lille

Discipline **Informatique**Spécialité **Informatique et applications**

# Conception d'un noyau sécurisé pour objets contraints

Thèse dirigée par Gilles Grimaud Directeur de thèse

Julien Cartigny Co-directeur de thèse Chrystel Gaber Co-encadrante

#### Composition du jury

| Rapporteurs        | Didier Donsez  Jean-Pierre Talpin | Professeur des Universités à l'Université de<br>Grenoble-Alpes, LIG<br>Directeur de recherche à l'INRIA Rennes |             |

|--------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-------------|

| Examinateurs       | Romain Rouvoy                     | Professeur des Universités à l'Université de Lille,<br>CRIStAL                                                 | (Président) |

|                    | Marie-Laure Ротет                 | Professeure des Universités à l'Université de<br>Grenoble-Alpes, VERIMAG                                       |             |

|                    | Julien Sopena<br>Patricia Mouy    | Maître de conférences à Sorbonne Université, LIP6<br>Chercheuse-Docteure à l'ANSSI                             |             |

| Invité             | Jean-Philippe Wary                | Responsable de programme de recherche à Orange Innovation                                                      |             |

| Direction de thèse | Gilles Grimaud                    | Professeur des Universités à l'Université de Lille,<br>CRIStAL                                                 |             |

|                    | Chrystel Gaber                    | Ingénieure de Recherche-Docteure à Orange                                                                      |             |

Innovation Caen

## Université de Lille Orange

Doctoral School **Ecole Graduée MADIS-631**Laboratory **CRIStAL**

Thesis by Nicolas Dejon

Defended on December 14, 2022

A dissertation submitted in partial fulfillment of the requirements for the degree of

## Doctor of Philosophy of Université de Lille

Academic Field **Computer Science**Specialty (in French) **Informatique et applications**

# Design of a secure kernel for constrained objects

Thesis supervised by Gilles Grimaud Supervisor

Julien Cartigny Co-Supervisor Chrystel Gaber Co-Monitor

#### Committee members

| Referees  | Didier Donsez<br>Jean-Pierre Talpin | Protessor at Université de Grenoble-Alpes, LIG<br>Senior Researcher at INRIA Rennes |         |

|-----------|-------------------------------------|-------------------------------------------------------------------------------------|---------|

| Examiners | Romain Rouvoy                       | Professor at Université de Lille, CRIStAL                                           | (Chair) |

|           | Marie-Laure Ротет                   | Professor at Université de Grenoble-Alpes, VERIMAG                                  |         |

|           | Julien Sopena                       | Associate Professor at Sorbonne Université, LIP6                                    |         |

Patricia Mouy PhD, Researcher at ANSSI

Guest Jean-Philippe Wary Research program director at Orange Innovation

Supervisors Gilles Grimaud Professor at Université de Lille, CRIStAL

Chrystel Gaber PhD, Research engineer at Orange Innovation Caen

| The research leading to these results were funded by ANRT Convention Cifre 2020/0380 and contributed to the TinyPART project funded by the MESRI-BMBF rman-French cybersecurity program under grant agreements n°ANR-20-CYAL-0005 d 16KIS1395K. This thesis reflects only the author's views. ANRT, MESRI and BMBF e not responsible for any use that may be made of the information it contains. |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|            |       | _         | .11   |

|------------|-------|-----------|-------|

| Α          | ma    | tam       | 11.Le |

| <b>4</b> 1 | 11111 | 1 vi II i |       |

A la mémoire de ceux qui m'ont précédé

A mes rêves d'enfant

Parvenu à l'issue de mon doctorat en informatique, et ayant ainsi pratiqué, dans ma quête du savoir, l'exercice d'une recherche scientifique exigeante, en cultivant la rigueur intellectuelle, la réflexivité éthique et dans le respect des principes de l'intégrité scientifique, je m'engage, pour ce qui dépendra de moi, dans la suite de ma carrière professionnelle quel qu'en soit le secteur ou le domaine d'activité, à maintenir une conduite intègre dans mon rapport au savoir, mes méthodes et mes résultats.

Serment doctoral d'intégrité scientifique

With the completion of my doctorate in computer science, in my quest for knowledge, I have carried out demanding research, demonstrated intellectual rigour, ethical reflection, and respect for the principles of research integrity. As I pursue my professional career, whatever my chosen field, I pledge, to the greatest of my ability, to continue to maintain integrity in my relationship to knowledge, in my methods and in my results.

Scientific integrity oath

La chance ne sourit qu'aux esprits bien préparés.

Luck favors the prepared mind.

Louis Pasteur

Si tout est connecté, tout peut être piraté.

If everything is connected, everything can be hacked.

Ursula von der Leyen

Je suis amoureuse d'un OS. I'm in love with an OS.

Film Her / Her movie

L'OS ne fait que mentir. The OS is lying to you.

Chrystel Gaber

Il ne faut jamais sous-estimer le pouvoir du petit canard jaune qui fait oui-oui.

Never under-estimate the power of the small yellow duck nodding his head.

Gilles Grimaud

Abstract xiii

#### Design of a secure kernel for constrained objects

#### Abstract

This thesis invests the field of cybersecurity for small computer systems (embedded systems/connected objects/low-end devices, of type microcontroller) and more precisely aims to bring strong memory isolation guarantees for tasks executing on them.

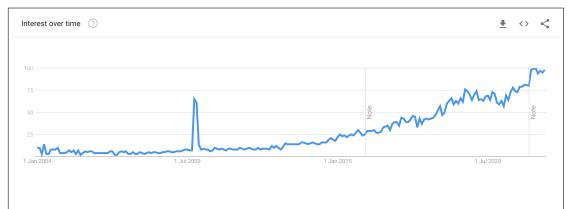

The heterogeneity and strong resource constraints (memory, computing power, energy) of constrained embedded systems require tailored solutions. The embedded software life cycle and the specific hardware platforms challenge us to reconsider the security schemes that leave open memory vulnerability issues, still prevailing today. Furthermore, the risk of vulnerability exploits elevates with the growing number of use cases (smart environments in general) implying increased complexity within these systems and with the burgeoning market of the Internet-of-Things (notably for remote update purposes). As a consequence, cyber attackers can take profit from these vulnerabilities to take remote control of these connected systems in a very scalable way.

In this context, the thesis proposes to design a kernel for constrained objects that is able to bring strong memory isolation guarantees. It studies the blend of high flexibility and strong security for this class of devices with the aim of security-by-design without functional loss. The thesis presents two main contributions dealing with software attacks on memory.

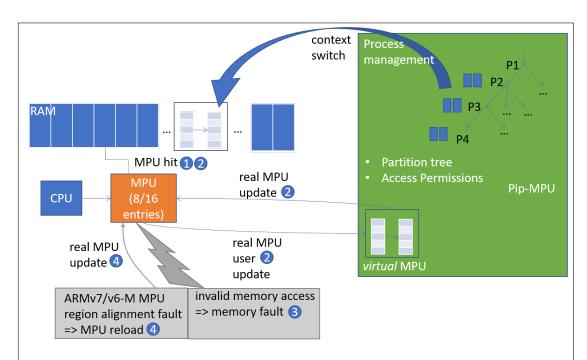

The first contribution is an Operating System (OS) kernel, named Pip-MPU, that offers a hardware-based isolation solution with a degree of flexibility outperforming current solutions. Pip-MPU is adapted from the Pip protokernel initially designed for high-end/general-purpose computers that are provided with more furnished and different hardware platforms than the ones of constrained objects. For that, the designed kernel is a complete refactoring of Pip and offers a security mechanism based on the Memory Protection Unit (MPU), a unit of the processor, which enables hardware-based access control on memory resources. Despite strong limitations due to the limited hardware platform, Pip-MPU is as flexible as its parent project Pip. With a code base size of less than 10 Kb and about 16% extra costs in terms of performance and energy consumption, Pip-MPU reduces the number of privileged operations by 99% and the attack surface of the accessible application memory by 98%.

The second contribution is the demonstration of strong isolation guarantees by the use of formal methods. Several kernel services have been proved against isolation by the use of the Coq Proof Assistant. The proved properties are Pip's security properties that enforce a strict memory isolation security model. To our knowledge, no state-of-the-art solution offering MPU-based isolation has been proved before. We develop novel proof conduct techniques and propose new metrics to follow the proof effort and evaluate the hypotheses supporting the proofs.

All the contributions developed in this thesis are publicly released under open-source licences.

**Keywords:** memory isolation, constrained objects, mpu, formal verification, coq, pip, security-by-design

xiv Abstract

#### Conception d'un noyau sécurisé pour objets contraints

#### Résumé

Cette thèse s'inscrit dans la thématique de la sécurité des petits systèmes informatiques (systèmes embarqués/objets connectés, de type microcontrôleur) et plus précisément vise à apporter des fortes garanties d'isolation mémoire pour les tâches qui s'y exécutent.

L'hétérogénéité et les fortes contraintes en ressources (espace mémoire, puissance de calcul, énergie) nécessitent la mise en place de solutions sur mesure pour les systèmes embarqués contraints. Le cycle de vie des logiciels embarqués et les architectures matérielles spécifiques imposent de repenser la manière de mettre en oeuvre la sécurité qui, encore aujourd'hui, laisse ouvertes des problématiques de vulnérabilité mémoire. De plus, les risques d'exploitation de ces vulnérabilités grandissent avec l'émergence de nouveaux cas d'utilisation (environnements intelligents de manière générale) impliquant des systèmes de plus en plus complexes et l'explosion du nombre de systèmes connectés (notamment pour des besoins de mise à jour à distance). En conséquence, des cyber-attaquants peuvent tirer profit de telles vulnérabilités pour prendre le contrôle à distance de ces systèmes connectés de façon massive.

Dans ce cadre, la thèse propose d'élaborer un noyau destiné aux petits objets qui soit capable d'apporter des garanties fortes d'isolation mémoire. Elle étudie l'association entre flexibilité élevée et forte sécurité au sein d'objets contraints pour une sécurité dès la conception sans perte fonctionnelle. Elle est constituée de deux contributions principales qui répondent aux attaques logicielles sur la mémoire.

La première contribution est un noyau de système d'exploitation, appelé Pip-MPU, qui propose une solution d'isolation ancrée dans le matériel et offrant une flexibilité dépassant les solutions actuelles. Pip-MPU est adapté du protonoyau Pip initialement destiné à des ordinateurs généralistes dotés d'une plateforme matérielle plus fournie et différente de celle des objets contraints. Pour cela, le noyau conçu est une refonte totale de Pip et propose un mécanisme de sécurité basé sur la *Memory Protection Unit (MPU)*, une unité du processeur, qui permet un contrôle d'accès matériel aux ressources. Malgré les fortes limitations imposées par la plateforme matérielle, Pip-MPU est aussi flexible que ce que permet la MMU en termes de sécurité. Du haut de ses 10 Ko de code et 16% de surcoût en termes de performances et de consommation d'énergie, Pip-MPU réduit le nombre d'opérations privilégiées exécutées de 99% et la surface d'attaque de la mémoire accessible depuis l'application de 98%.

La deuxième contribution est l'obtention de garanties fortes de l'isolation par l'usage de méthodes formelles. Plusieurs services du noyau ont été formellement prouvés pour l'isolation à l'aide de l'assistant de preuve Coq. Les propriétés prouvées sont les propriétés de sécurité de Pip imposant son modèle de sécurité d'isolation stricte. A notre connaissance, aucun autre système de l'état de l'art proposant de l'isolation par MPU n'a été formellement prouvé auparavant. Nous développons des nouvelles techniques de conduite de preuve et proposons de nouvelles métriques permettant de suivre l'effort de preuve et d'évaluer les hypothèses soutenant les preuves.

Toutes les contributions de la thèse sont en source ouverte.

**Mots clés :** isolation mémoire, objets contraints, mpu, vérification formelle, coq, pip, sécurisé dès la conception

# Remerciements

Ce document présente des travaux originaux qui n'auraient pas pu voir le jour sans l'implication d'un grand nombre de personnes que je souhaite ici remercier.

Merci à Didier Donsez et Jean-Pierre Talpin, qui m'ont fait l'honneur d'accepter de rapporter ma thèse, ainsi qu'à Marie-Laure Potet, Romain Rouvoy, Julien Sopena et Patricia Mouy pour son examen, et Jean-Philippe Wary, d'avoir accepté de faire partie de mon jury.

Cette thèse n'aurait pas existé sans l'insufflation créatrice et engagée de mes encadrants de thèse Chrystel Gaber et Gilles Grimaud, merci de m'avoir donné la chance de participer à votre vision de recherche. Merci pour votre encadrement bienveillant, pour les années de conseil et d'apprentissage, pour nos discussions, parfois philosophiques, et pour la liberté, l'autonomie et la confiance que vous m'avez accordées pour réaliser mes travaux dans les meilleures dispositions possibles, malgré la distance et la logistique inhérentes à cette thèse.

Un grand merci à mes deux équipes de recherche, à Caen et à Lille, et mes managers, de m'avoir si bien accueilli même pour des séjours (tout le temps) temporaires. Plus que des collègues, j'y ai trouvé des amis. Particulièrement, merci à David et Samuel de l'équipe 2XS de CRIStAL de m'avoir ouvert au monde de la vérification formelle et d'avoir joué les 'petits canards jaunes qui font oui-oui' pour médiatiser mes pensées et me redonner confiance dans mes intuitions. Merci à Clément, Florian (chauffeur privé, conseiller des preuves formelles, et bravo encore pour le karting), Olivier (la force utcéenne), Sofía, mes co-doctorants de Lille, et plus largement toute l'équipe 2XS (merci Thomas pour le piano) pour la chaleureuse ambiance et nos belles conversations autour de (l'ancien) frigo et (l'ancien) canapé. J'aimerais tout particulièrement remercier Narjes, ancienne membre de l'équipe 2XS, pour sa formation expresse de Pip et des preuves réalisée en tout début de thèse. Les travaux que je présente ont mis en musique un grand nombre de ses apprentissages et réalisations. Un grand merci à Damien d'avoir vaillamment repris mes travaux pour en donner la substance prototypique. Un merci particulier à Samuel de l'équipe SASE d'Orange Innovation Caen, et les stagiaires de notre petite équipe Ghilas, Idir, Matthieu et Gregory, d'avoir cogité près de moi et qui m'ont permis de nourrir mon processus de réflexion.

Merci à Orange de m'avoir donné l'opportunité matérielle d'effectuer ma thèse et de m'avoir proposé de continuer un travail de recherche après ma thèse. Orange m'a aussi donné la possibilité de défendre mes travaux dans un concours de vulgarisation au grand public qui me tenait à coeur, je l'en remercie. Merci au laboratoire CRIStAL de l'Université de Lille de m'avoir accueilli et de financer mon déplacement à l'étranger pour présenter mes travaux. J'en profite pour remercier l'ensemble de mes enseignants,

xvi Remerciements

tous domaines confondus, du collage de pastille en maternelle à la rédaction de ce manuscrit, en passant par la musique, le sport, les pompiers et tant d'autres activités qui m'ont forgé, bousculé, étiré toutes ces années. Cette thèse est la quintessence de leur investissement et de la transmission de leur passion, merci.

De plus, ces travaux ont été soutenus, soumis, challengés, améliorés, discutés, présentés, exprimés, développés, démontrés, tissés de nombreuses interactions, durant différents contextes, à travers le temps et l'espace. Merci particulièrement à Guillaume Bouffard, Thomas Létan, Arnaud Fontaine et l'équipe de développement de WooKey de l'ANSSI (Agence Nationale de la Sécurité des Systèmes d'Information). Merci pour tous ces échanges.

Essentiels dans le milieu informatique, peu mis en avant, merci aux développeurs d'outils de développement et d'analyse, IDEs en tout genre, et toutes les communautés derrière qui mettent à disposition leurs compétences, parfois leurs temps de loisir, pour le développement informatique mondial.

Par ailleurs, la thèse est un projet de trois ans, ce qui représente une part de vie qui a été pour ma part densifiée par la crise sanitaire avec la découverte du piano et de l'astronomie, amplifiée par le dynamisme lillois avec la danse, les sorties, les maraudes, bouleversée par les déménagements et la rencontre de cinquantaines de personnes à différents lieux de vie. L'effort de thèse s'appuie sur des fondements humains solides, qui m'ont porté, qui me soutiennent, malgré de nombreuses périodes d'absence pour délivrer ces travaux. Merci à tous mes nombreux amis, vous saurez vous reconnaître, wherever we met, wherever you are, yous qui transformez un jour ordinaire en moments délicieux. Pour cette thèse, j'aimerais particulièrement remercier Charles, fier habitant du Nord, qui m'a offert son canapé pendant plusieurs mois pour y habiter, m'a ouvert à la culture lilloise, et m'a introduit dans de nouveaux cercles amicaux dans une ville que je ne connaissais pas. Du côté de Caen, merci tout particulièrement à Valentin de m'avoir accueilli dans sa ville adoptive avec l'envie de me faire découvrir la région et merci à mon collègue de bureau, Yacine, qui grandit sa thèse en même temps que la mienne tout en partageant et dégageant beaucoup de joie malgré les journées pluvieuses normandes (non ce n'est pas vrai, il fait beau tout le temps ici, si si on me l'a dit).

Enfin, je ne suis que l'enveloppe charnue d'un noyau immuable qui me suit à chaque pas, ma famille. Certaines personnes nous ont quittés, remplacées par les souvenirs et la chaleur du coeur, mais leurs ombres éclairent ma route au quotidien de jour comme de nuit. Tack Mormor för din uppmuntran, för Mexiko resan och alla andra resorna som du hjälpte till med! Pour terminer, merci à ma soeur Chloé, Maman et Papa de ne faiblir jamais et de m'aider à grandir, toujours et encore, avec votre amour et votre soutien indéfectibles, je vous aime.

# Acronyms

```

A \mid C \mid D \mid I \mid J \mid L \mid M \mid O \mid P \mid S \mid T

A

API Application Programming Interface. 64

C

COTS Commercial Off-the-Shelf. 32, 48, 49, 89, 104, 285

CPU Central Processing Unit. 16, 28, 60, 61, 95, 156

D

DMA Direct Memory Access. 185

Ι

IoT Internet of Things. 1, 9, 12, 25, 278, 285, 286

ISA Instruction Set Architecture. 49, 66

J

JCVM JavaCard Virtual Machine. 59, 282

L

LoP Lines of Proof. 181, 207

M

MMU Memory Management Unit. xx, 15, 27, 29, 84, 104, 328

MPU Memory Protection Unit. xx, 3, 15, 27, 29, 48, 49, 104, 107, 328

0

OS Operating System. xi, 281

P

PMP Physical Memory Protection. 79, 82, 108, 300

S

```

xviii Acronyms

**SLOC** Source Lines of Code. 96, 179, 230 **SWaP-C** Space, Weight and Power-Costs. 26, 280

T

**TCB** Trusted Computing Base. 15, 24, 38, 49, 50, 87, 99, 113, 286, 328

# Foreword

"You will learn it later" - said a big sister to her little (too) inquisitive brother on the way to school. One day, he learned that there was no Santa Claus, but kept anyway the gifts he received, including a computer. He learned also, as the years passed, how to conduct mathematical proofs in math class and cool stuff about computers in technology class. In his leisure time, he also learned to break the passwords that restricted his allowed computer time. Unfortunately for him, security increased and there was no more material to show him the way. He faced that human knowledge had frontiers and much more uncertainties than he once thought. Nevertheless, he heard of a profession that regularly crafted new knowledge for others: researchers. That gave him hope to master his computer again one day.

Now, the boy has grown up and does not need to break passwords any longer. However, the world has also changed and the modern Santa Claus is distributing toys embedding computers that can be remotely controlled, with about the same poor security as the boy's first computer. Out in the wild, script kiddies of that time have polished their techniques and take any opportunity to annoy old classmates with much more sophisticated tools. The time has come for the big boy to take a leap of faith in the dark corners of small embedded systems security and make it harder for schoolchildren to hack their toys, if only to help them discover a profession.

# Contents

| Ał | strac                             | et e e e e e e e e e e e e e e e e e e                                                                                              | xiii             |

|----|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Re | emerc                             | iements                                                                                                                             | xv               |

| Ac | rony                              | ms                                                                                                                                  | xvi              |

| Fo | rewo                              | rd                                                                                                                                  | xix              |

| Co | onten                             | ts                                                                                                                                  | XX               |

| Li | st of [                           | Γables                                                                                                                              | xxiv             |

| Li | st of l                           | Figures                                                                                                                             | xxvi             |

| Li | sting                             | S                                                                                                                                   | xxx              |

| G  | Tech<br>Wor                       | l introduction  nnological context                                                                                                  | 1<br>1<br>2<br>3 |

| I  | Con                               | itext                                                                                                                               | 7                |

| 1  | Intr<br>1.1<br>1.2                | oduction Threats and opportunities                                                                                                  | 9<br>10<br>12    |

| 2  |                                   | iminaries                                                                                                                           | 15               |

|    | 2.1                               | Operating systems and kernel                                                                                                        | 16               |

|    | 2.2                               | Security                                                                                                                            | 19               |

|    | 2.3                               | Legacy embedded systems and connected devices                                                                                       | 25               |

|    | <ul><li>2.4</li><li>2.5</li></ul> | Low-end/constrained <i>versus</i> high-end embedded systems Memory Protection Unit (MPU) <i>versus</i> Memory Management Unit (MMU) | 26               |

|    |                                   |                                                                                                                                     | 27               |

| XX |

|----|

|    |

| 3          |             | ent situation in constrained devices - State of the Art                                   | 31       |

|------------|-------------|-------------------------------------------------------------------------------------------|----------|

|            | 3.1 3.2     | Hardware-based isolation solutions                                                        | 32<br>38 |

|            | 3.3         | Problem statement                                                                         | 41       |

|            | 3.4         | Hardware-based solutions in high-end embedded systems                                     | 42       |

|            | J. <b>T</b> | Trandware-based solutions in high-chid embedded systems                                   | 72       |

| 4          | Desi        | ign a secure kernel for constrained devices                                               | 47       |

|            | 4.1         | Thesis                                                                                    | 47       |

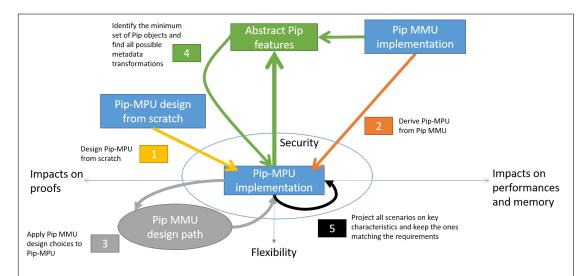

|            | 4.2         | Thesis approach                                                                           | 48       |

|            | 4.3         | Results                                                                                   | 51       |

| II         | Sec         | curity for constrained devices: a flexible and portable memory                            |          |

| isc        |             | on solution based on the Memory Protection Unit (MPU)                                     | 53       |

| Int        | rodu        | ction to Part II                                                                          | 55       |

| 5          | Con         | text                                                                                      | 57       |

|            | 5.1         | Motivations                                                                               | 57       |

|            | 5.2         | Flexibility in MPU-based isolation solutions                                              | 58       |

| 6          | Fran        | nework for secure flexible nested memory spaces using the MPU                             | 63       |

|            | 6.1         | Motivations                                                                               | 64       |

|            | 6.2         | Definitions                                                                               | 64       |

|            | 6.3         | Technical implementation guidelines of the framework                                      | 71       |

|            | 6.4         | Discussion                                                                                | 77       |

|            | 6.5         | Conclusion                                                                                | 82       |

| 7          | Pip-        | MPU, adaptation of the Pip kernel via framework specialisation                            | 83       |

|            | 7.1         | Motivations                                                                               | 84       |

|            | 7.2         | Pip                                                                                       | 84       |

|            | 7.3         | Pip-MPU's requirements                                                                    | 87       |

|            | 7.4         | Pip-MPU design                                                                            | 89       |

|            | 7.5         | Evaluation of Pip-MPU                                                                     | 93       |

|            | 7.6         | Discussion and limitations                                                                | 100      |

|            | 7.7         | Defence against attackers and assumptions                                                 | 103      |

| Re         | view        | of Part II                                                                                | 107      |

|            | Revi        | ew                                                                                        | 107      |

|            | Pers        | pectives                                                                                  | 108      |

|            | Take        | aways                                                                                     | 109      |

| ŢŢŢ        | 11:         | ah agguranga/turraturanthinaga farmal muasf of a leave Warransa                           |          |

| III<br>isc |             | gh-assurance/trustworthiness: formal proof of a kernel's memory on on constrained devices | 111      |

| Int        | rodu        | ction to Part III                                                                         | 113      |

<u>xxii</u> Contents

| 8  | Con                                                                                                        | ext                                                                                                                                                                                                                                                 | 115                                                                |

|----|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | 8.1                                                                                                        | Motivations                                                                                                                                                                                                                                         | 115                                                                |

|    | 8.2                                                                                                        | Background                                                                                                                                                                                                                                          | 116                                                                |

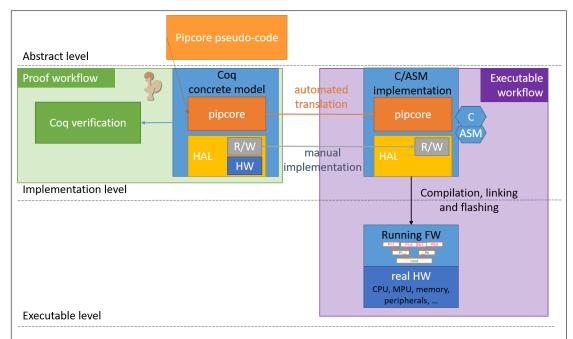

|    | 8.3                                                                                                        | Pip's workflow                                                                                                                                                                                                                                      | 117                                                                |

| 9  | Intu                                                                                                       | ition and formalisation                                                                                                                                                                                                                             | 121                                                                |

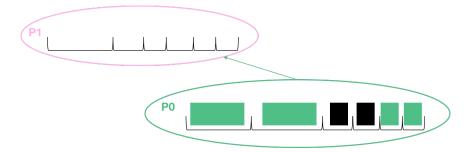

|    | 9.1                                                                                                        | Proof goals                                                                                                                                                                                                                                         | 122                                                                |

|    | 9.2                                                                                                        | Proof methodology                                                                                                                                                                                                                                   | 131                                                                |

|    | 9.3                                                                                                        | Sketch of proof                                                                                                                                                                                                                                     | 132                                                                |

|    | 9.4                                                                                                        | Model and implementation in Coq                                                                                                                                                                                                                     | 138                                                                |

|    | 9.5                                                                                                        | Properties propagation and proof levels                                                                                                                                                                                                             | 146                                                                |

|    | 9.6                                                                                                        | C implementation equivalents                                                                                                                                                                                                                        | 152                                                                |

|    | 9.7                                                                                                        | Discussion and limitations                                                                                                                                                                                                                          | 156                                                                |

|    | 9.8                                                                                                        | Conclusion                                                                                                                                                                                                                                          | 157                                                                |

| 10 | Forn                                                                                                       | nal proof of the security properties                                                                                                                                                                                                                | 159                                                                |

|    | 10.1                                                                                                       | Proof of findBlock                                                                                                                                                                                                                                  | 160                                                                |

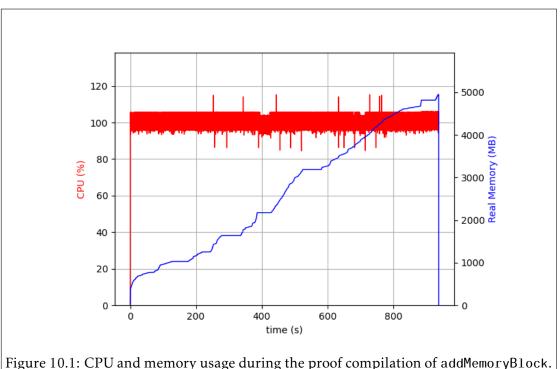

|    | 10.2                                                                                                       | Proof of addMemoryBlock                                                                                                                                                                                                                             | 162                                                                |

|    | 10.3                                                                                                       | Evaluation of Pip-MPU's proof development                                                                                                                                                                                                           | 179                                                                |

|    | 10.4                                                                                                       | Discussion and limitations                                                                                                                                                                                                                          | 182                                                                |

|    | 10.5                                                                                                       | Conclusion                                                                                                                                                                                                                                          | 187                                                                |

| 11 | Proo                                                                                                       | f techniques and evolution of Pip's formal verification process                                                                                                                                                                                     | 189                                                                |

|    | 11.1                                                                                                       | Formalisation                                                                                                                                                                                                                                       | 190                                                                |

|    | 11.2                                                                                                       | Low-level local proofs (HAL)                                                                                                                                                                                                                        | 195                                                                |

|    | 11.3                                                                                                       | High-level local proofs (services)                                                                                                                                                                                                                  | 196                                                                |

|    | 11.4                                                                                                       | Global proof strategy: horizontal and vertical exploration strategies .                                                                                                                                                                             | • • •                                                              |

|    |                                                                                                            |                                                                                                                                                                                                                                                     | 200                                                                |

|    |                                                                                                            |                                                                                                                                                                                                                                                     | <ul><li>200</li><li>201</li></ul>                                  |

|    | 11.5                                                                                                       | Discussion                                                                                                                                                                                                                                          |                                                                    |

| 12 | 11.5<br>11.6                                                                                               | Discussion                                                                                                                                                                                                                                          | 201                                                                |

| 12 | 11.5<br>11.6<br><b>Proo</b>                                                                                | Discussion                                                                                                                                                                                                                                          | 201<br>203                                                         |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1                                                                        | Discussion                                                                                                                                                                                                                                          | <ul><li>201</li><li>203</li><li>205</li></ul>                      |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2                                                                | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206                                           |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3                                                        | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206<br>207                                    |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4                                                | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206<br>207<br>212                             |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5                                        | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206<br>207<br>212<br>225                      |

| 12 | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6                                | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206<br>207<br>212<br>225<br>228               |

|    | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7                        | Discussion Conclusion  f monitoring and proof path Existing proof metrics Code and proof relationship Proof complexity: fine-grained analysis of properties and code elements Proof path best effort strategy Proof dashboard Discussion            | 201<br>203<br>205<br>206<br>207<br>212<br>225<br>228<br>229        |

|    | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7                        | Discussion                                                                                                                                                                                                                                          | 201<br>203<br>205<br>206<br>207<br>212<br>225<br>228<br>229<br>231 |

|    | 11.5<br>11.6<br><b>Proo</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br><b>view</b><br>Revi | Discussion Conclusion  f monitoring and proof path Existing proof metrics Code and proof relationship Proof complexity: fine-grained analysis of properties and code elements Proof path best effort strategy Proof dashboard Discussion Conclusion | 201<br>203<br>205<br>206<br>207<br>212<br>225<br>228<br>229<br>231 |

| <u>Cc</u> | ntent | S                                                                        | xxiii |

|-----------|-------|--------------------------------------------------------------------------|-------|

| Co        | nclus | sion                                                                     | 237   |

|           | Con   | tributions and perspectives                                              | 237   |

|           | Limi  | tations of the approach                                                  | 240   |

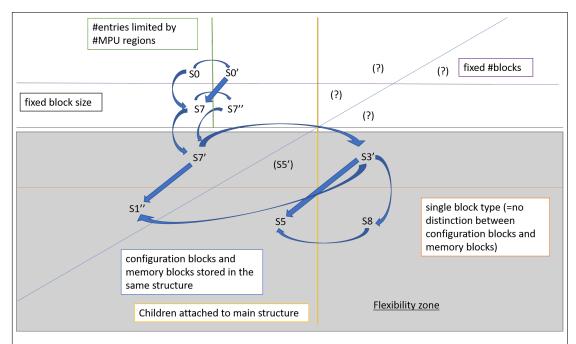

|           | Insig | ghts and learnings on the design of Pip-MPU                              | 241   |

|           | Insig | ghts and learnings on the formal verification of Pip-MPU                 | 253   |

|           | Pers  | onal thoughts                                                            | 260   |

|           | Clos  | ing                                                                      | 262   |

| Bi        | bliog | raphy                                                                    | 263   |

| A         | Rési  | ımé substantiel en français                                              | 277   |

|           | A.1   | Cadriciel MPU pour espaces mémoire imbriqués sécurisés et flexibles      | 287   |

|           | A.2   | Pip-MPU, adaptation du noyau Pip par spécialisation du cadriciel         | 292   |

|           | A.3   | Vérification formelle de la propriété d'isolation de Pip-MPU             | 300   |

|           | A.4   | Techniques de preuves et évolution du processus de vérification formelle | 304   |

|           | A.5   | Suivi du développement de la preuve et optimisation                      | 307   |

|           | A.6   | Conclusion                                                               | 321   |

| In        | dex   |                                                                          | 325   |

| Co        | ntent | ts                                                                       | 327   |

# List of Tables

| 2.1<br>2.2 | Classes of constrained devices (KiB = 1024 bytes) [93]                                                                                                                                                             | 27<br>29 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1        | Hardware-based solutions (OSes/kernels, tools, architectures) classified by isolation guarantees for embedded and general-purpose systems                                                                          | 45       |

| 5.1        | Comparison of compartmentalisation features in MPU-based systems. Pip-MPU is introduced in Chapter 7 as a specialisation of the framework presented in the next Chapter 6                                          | 59       |

| 6.1        | Complexities of the system calls. $s$ is the number of structures in a memory space (expected $\leq$ and $p$ is the number of partitions                                                                           | 76       |

| 7.1        | Complexities of Pip-MPU's memory management system calls. $s$ is the number of structures in a memory space (expected $\leq 8$ ) and $k$ is the number of direct ancestors (expected $\leq 4$ )                    | 90       |

| 7.2        | Comparison of Pip (MMU)'s and Pip-MPU's memory management APIs. Equivalent services are on the same line. Note that Pip-MPU has services that target the current partition. The dashes represent the services that |          |

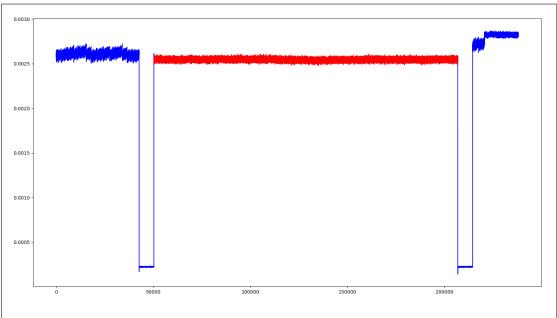

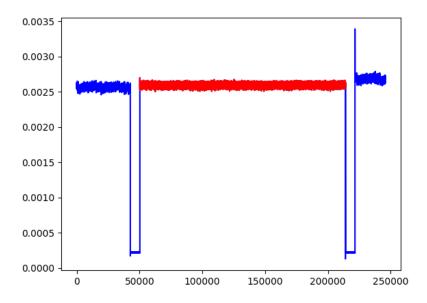

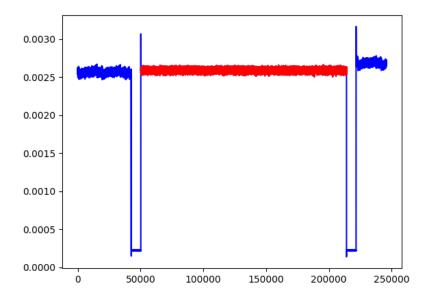

| 7.3        | are not present relative to their counterpart API                                                                                                                                                                  | 92<br>97 |

| 7.4        | Performances comparison (versus baseline). The test application is either executed in the root partition or in the child partition, compared to the                                                                | 71       |

|            | baseline                                                                                                                                                                                                           | 98       |

| 10.1       | Proof status and effort                                                                                                                                                                                            | 180      |

| 12.1       | Effective reusability metric table for Pip-MPU                                                                                                                                                                     | 213      |

| 12.2       | Type changes impacts in Pip-MPU                                                                                                                                                                                    | 215      |

| 12.3       | Field change impacts on Partition Descriptor entry fields in Pip-MPU.                                                                                                                                              | 216      |

|            | Field change impacts on Block entry fields in Pip-MPU                                                                                                                                                              | 217      |

| 12.5       | Field change impacts on Shadow 1 and Shadow Cut entry fields in Pip-                                                                                                                                               | 210      |

| 12.6       | MPU                                                                                                                                                                                                                | 218      |

|            | of Pip-MPU                                                                                                                                                                                                         | 219      |

| 12.7       | Property complexity matrix <i>PCM</i> in Pip-MPU                                                                                                                                                                   | 222      |

|            |                                                                                                                                                                                                                    |          |

List of Tables xxv

|                   | Illustration of the computation of insertNewEntry's proof complexity. Proof path best effort strategy iterations of Algorithm 3 applied to Pip-MPU. Each iteration reveals a new score depending on previously selected                                                                                                         | 224              |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                   | services. The score is given as a tuple: $current\_proof\_effort/next\_proof\_e$ A service is marked with 'o' at the iteration when it is selected. Final service order: [readMPU, findBlock, addMemoryBlock, mapMPU, cutMemoryBlock, mergeMemoryBlocks, createPartition, deletePartition, collect, removeMemoryBlock, prepare] | ef f ort.<br>227 |

| 12.1              | OProof dashboard overview: metrics depending on the granularity                                                                                                                                                                                                                                                                 | 229              |

| A.1<br>A.2<br>A.3 | Classes d'objets contraints (Kio = 1024 octets) [93]                                                                                                                                                                                                                                                                            | 280<br>281       |

| A.4               | garanties d'isolation                                                                                                                                                                                                                                                                                                           | 285              |

| A.5               | Pip-MPU est introduit au Chapitre 7 comme une spécialisation du cadriciel présenté dans le Chapitre 6                                                                                                                                                                                                                           | 288              |

|                   | partition donnée ( $<$ 8) et $k$ est le nombre d'ancêtres de cette partition (attendu $<$ 4)                                                                                                                                                                                                                                    | 294              |

| A.6               | Surcoût de Pip-MPU. Pour mesurer la taille de Pip-MPU et son empreinte mémoire, nous avons utilisé l'option de compilation -0s                                                                                                                                                                                                  | 296              |

| A.7               | Comparaison des performances et de la sécurité par rapport au scénario de référence. L'application est soit exécutée au sein de la partition racine,                                                                                                                                                                            | 200              |

| <b>A</b> O        | soit dans la partition enfant.                                                                                                                                                                                                                                                                                                  | 298              |

| A.8               | Efforts de preuve et statut                                                                                                                                                                                                                                                                                                     | 303<br>312       |

|                   | Réutilisation effective dans Pip-MPU                                                                                                                                                                                                                                                                                            | 312              |

|                   | propriétés de Pip-MPU                                                                                                                                                                                                                                                                                                           | 313              |

|                   | Complexités des propriétés de Pip-MPU                                                                                                                                                                                                                                                                                           | 316              |

|                   | NewEntry                                                                                                                                                                                                                                                                                                                        | 318              |

| A.13              | Itérations de l'Algorithme 4 de sélection du meilleur chemin de preuve par minimisation de l'effort de preuve appliqué à Pip-MPU. Chaque itération donne un nouveau score qui dépend des services sélectionnés précédemment. Le score est donné comme un tuple (ef fort_preuve_courant /                                        |                  |

|                   | ef fort_preuve_suivant). Un service marqué par 'o' dans une itération indique que ce service a été sélectionné à ce moment. L'ordre final des services est : [readMPU, findBlock, addMemoryBlock, mapMPU, cutMemoryBlock, mergeMemoryBlocks, createPartition, deletePartition, collect,                                         |                  |

|                   | removeMemoryBlock, prepare]                                                                                                                                                                                                                                                                                                     | 320              |

# List of Figures

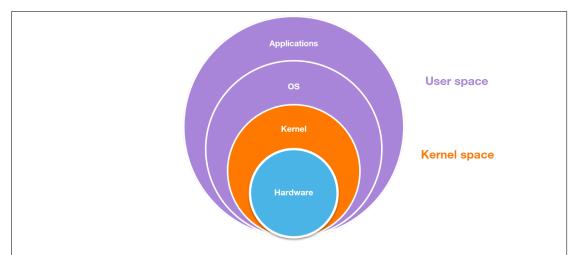

| 2.1        | Typical scheme of hardware and software nesting. The kernel and user spaces are the software layers whereas the hardware is represented here as a general abstraction of the processor, memory and peripherals                                                                                                                                                                                                                                                                                                                                                                  | 17       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

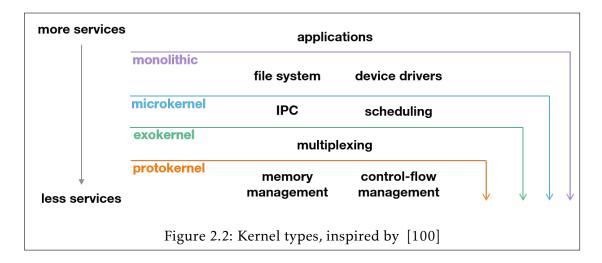

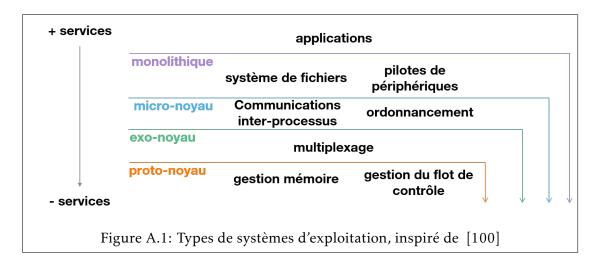

| 2.2        | Kernel types, inspired by [100]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19       |

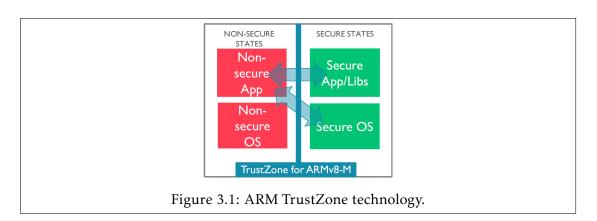

| 3.1<br>3.2 | ARM TrustZone technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33<br>43 |

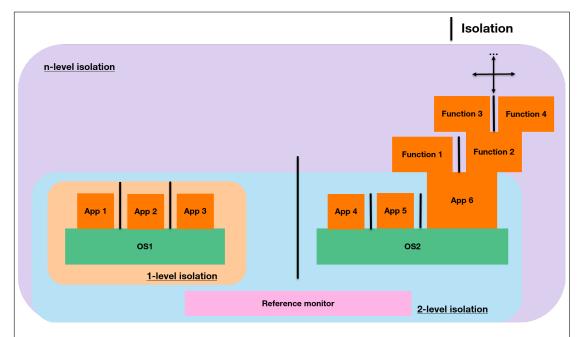

| 5.1        | Example of different levels of isolation. The 1-level isolation typically corresponds to the isolation set up by an OS to isolate applications or processes. The 2-level isolation considers another abstraction level, for example using ARM TrustZone. The n-level isolation do not consider any hardware or software limits on the number of abstraction levels                                                                                                                                                                                                              | 62       |

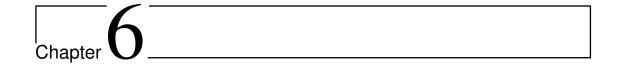

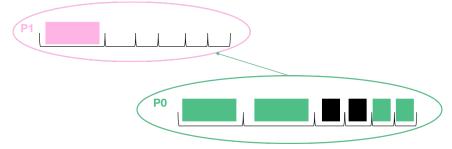

| 6.1        | Example of a cut (1) at an arbitrary <i>cut address</i> followed by a merge (2) within the same memory space P1. The memory space keeps track of the cut by linking the two subblocks (pink arrow). The figure shows the MPU is reconfigured each time there is a mutation in the memory space                                                                                                                                                                                                                                                                                  | 68       |

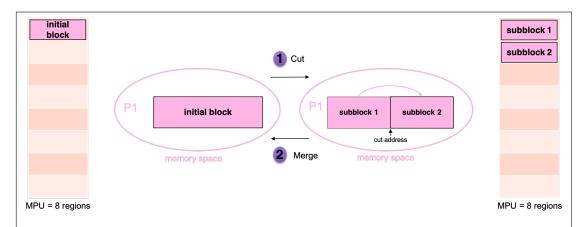

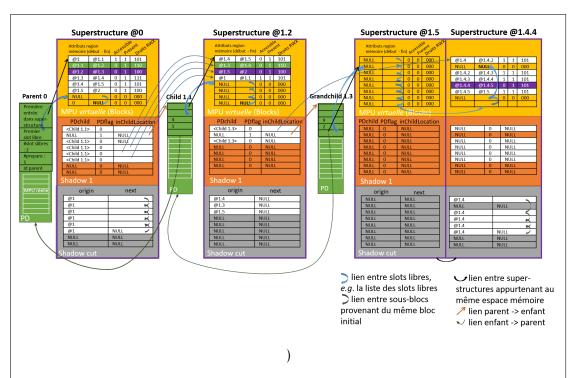

| 6.2        | Relations between and within the structures for the illustrated example memory space @0. The chained blue arrows form the free slots list. The chained grey arrows form the subblocks stemming from the same initial memory block. The chained black arrows form the link between the multiple structures belonging to the same memory space. In particular, memory blocks @1 and @5 are shared respectively with the children 1 and 2, while blocks @3 and @7 are not shared. Furthermore, block @5 has been cut to form the additional subblock @7 as stated in the subblocks |          |

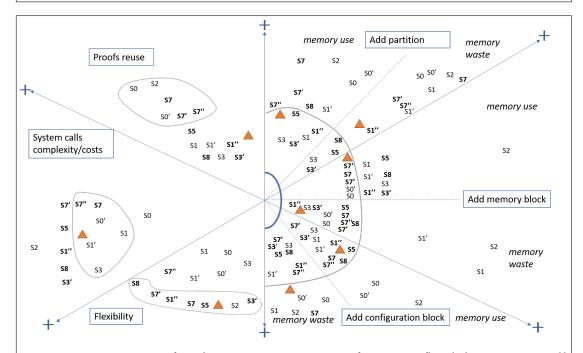

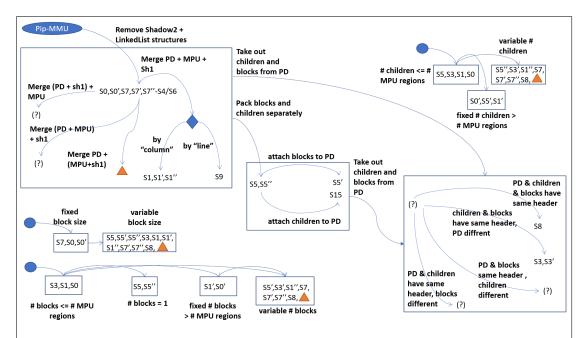

| 6.3        | structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73       |

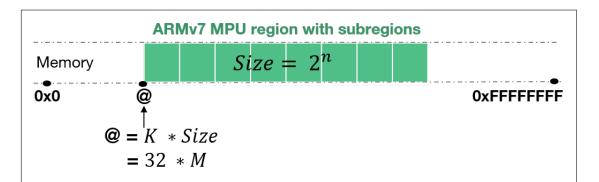

| 0.0        | power-of-two, with $4 < n < 32$ so a minimum region size of 32 bytes. The MPU region's base address is aligned on a multiple of the region's size, with $K, M \in \mathbb{N}$ such as $0 < @ < 4GB$ . There are eight equally-sized MPU subregions in one MPU region, if the feature is enabled, that can be in                                                                                                                                                                                                                                                                 | 0.0      |

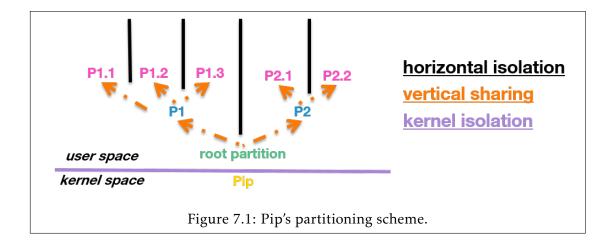

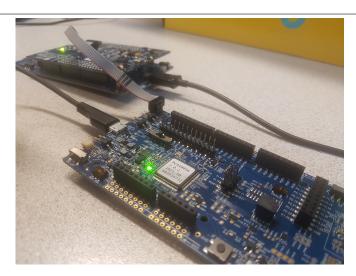

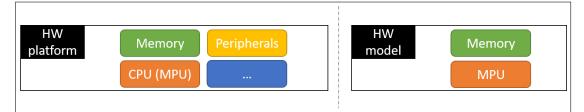

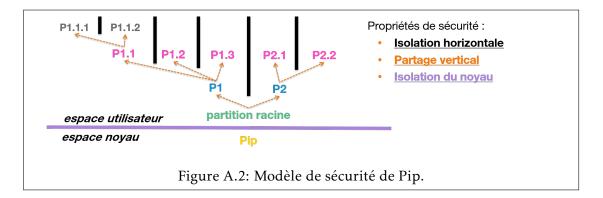

| 7.1        | turn independently enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 80<br>86 |

|            | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

List of Figures xxvii

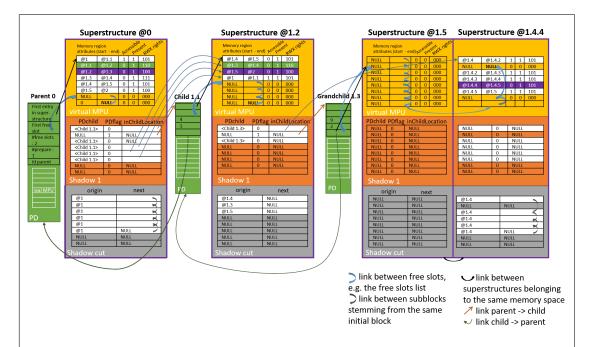

| 7.2 | Example of a parent-child-grandchild relationship viewed from the perspective of the metadata structures. Partition 0 (parent) is parent to partition 1.3 (child of parent 0) which in turn is parent to partition 1.3 (grandchild of parent 0). Green blocks are used as PD structures in their                                                                                                                                                                                                                                                    |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | respective child. Purple blocks are used as superstructures in their respective child or in their own partition (case of grandchild 1.3). The figure                                                                                                                                                                                                                                                                                                                                                                                                |     |

|     | shows that block 1.4 has been cut several times (in blocks 1.4.2, 1.4.3, 1.4.4, and 1.4.5) which implies the original block 1.4 in the ancestors is                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|     | inaccessible. For each memory block in all the partitions, we can observe there is no elevation of access permission rights compared to their original                                                                                                                                                                                                                                                                                                                                                                                              |     |

|     | block, but can only be lowered (like block 1.3). Grandchild 1.3 shows a typical state after a prepare: a new superstructure is initialised out of block 1.4.4 from the same partition 1.3 it is placed at the beginning of                                                                                                                                                                                                                                                                                                                          |     |

|     | block 1.4.4 from the same partition 1.3, it is placed at the beginning of<br>the linked list of all superstructures related to the same partition, the<br>first free slot is the first entry of the new superstructure and all entries                                                                                                                                                                                                                                                                                                              |     |

|     | have the default values except the last entry of the <i>virtual</i> MPU structure that connects with the free slots list with the previous one. Memory block 1 was shared memory between the parent 0 and the child 1.1. In our                                                                                                                                                                                                                                                                                                                     |     |

|     | implementation, we consider a <i>virtual</i> MPU structure of length equal to eight (eight entries). Note the absence of order in the free slots list of grandchild 1.3 which resulted from previous cutand mergeoperations.                                                                                                                                                                                                                                                                                                                        |     |

|     | Note as well the single reference between superstructures 1.5 and 1.4.4 compared to the multiple references in the frameworks between each inner structures.                                                                                                                                                                                                                                                                                                                                                                                        | 94  |