#### Accurate Simulation of Data Movement in Modern Mobile Multicore Systems

Quentin Huppert

#### ▶ To cite this version:

Quentin Huppert. Accurate Simulation of Data Movement in Modern Mobile Multicore Systems. Hardware Architecture [cs.AR]. Université de Montpellier, 2022. English. NNT: 2022UMONS069. tel-04096187

#### HAL Id: tel-04096187 https://theses.hal.science/tel-04096187

Submitted on 12 May 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESIS TO OBTAIN THE DEGREE OF DOCTOR OF THE UNIVERSITY OF MONTPELLIER

In SyAM - Automatic and Microelectronic Systems

Doctoral School: Information, Structures and Systems Sciences (I2S)

Research Unit: LIRMM

# **Accurate Simulation of Data Movement** in Modern Mobile Multicore Systems

Presented by Quentin Huppert December 6, 2022

Under the supervision of Lionel Torres and David Novo

#### In front of the jury composed of:

MUNIER Alix, Professor at Sarbonne University, LIP6

PETROT Frédéric, Professor at University of Grenoble, TIMA

SENTIEYS Olivier, Professor at University of Rennes, IRISA/ENSSAT

CATTHOOR Francky, Professor at KU Leuven, IMEC

TORRES Lionel, Professor at University of Montpellier, LIRMM

Thesis Director

NOVO David, Research Scientist at CNRS, LIRMM

Thesis co-supervisor

#### **Abstract**

Computer system architectures have become increasingly complex. Pushing for better performance and lower energy consumption, they include multiple cores, GPUs, accelerators, and sophisticated memory hierarchies. In this context, computer system simulators play a significant role in the research architecture community. They allow the evaluation of new architecture ideas while being quicker and avoiding the huge costs of manufacturing processes. The simulated architectures are often compared with real state-of-the-art baseline architectures. Thus, the relevance of the conclusions from such simulators is directly related to the faithfulness of the baseline model. We observe that having strong baselines is not a simple task due to the lack of detailed technical information about commercial architectures. In this thesis, we propose a systematic methodology to extract information from real commercial architectures for the calibration of their corresponding simulation models. This methodology is based on handcrafted microbenchmarks that leverage hardware performance counters for non-intrusive monitoring. We instantiate this methodology on two key components of the architecture.

First, we target the different levels of the memory hierarchy. We design the microbenchmarks to produce a signature of the memory system levels. The signature contains parameter values that are important to calibrate a simulation model of the real architecture. We implement the methodology with the gem5 simulator and an ARM Cortex-A53 CPU. Then, we evaluate our methodology with benchmarks from the SPEC CPU2006 suite. The benchmarks are executed on the commercial CPU and gem5 using our calibrated configuration. The results show that our calibration reduces the average and maximum simulation error by 43% and 62%, respectively.

Second, we instantiate the methodology on the data prefetching engine, which is a key component of the memory system that can generate memory requests in parallel to the core. This new instantiation of our methodology results in Pref-X, a framework that enables functional analysis of data prefetching engines in in-order cores. For that, the framework uses memory request sequences to stress the L1 data cache and expose

the changes in L1 cache content. From those changes, Pref-X deduces the functional specifications of the data prefetching engine. Finally, we use the extracted information to build a functional model of the prefetching engine. We apply Pref-X to two in-order ARM CPUs, the Cortex-A7 and the Cortex-A53, and evaluate its accuracy with memory traces extracted from the SPEC CPU2006 suite. We execute the traces on both the commercial CPUs and their corresponding functional models produced by our framework. The results show an average prefetching accuracy of 99.8% and 96.9% for the Cortex-A7 and the Cortex-A53, respectively.

This thesis builds a detailed understanding of how microbenchmarks can be used to improve the modeling accuracy of existing architectures. We believe our methodology has the potential to be applied to other components beyond the ones covered in this manuscript, but that is part of future work. We hope our results will enable the community to use better-calibrated baseline architectures in their simulations.

#### Résumé de la Thèse

Les architectures de systèmes informatiques sont devenues de plus en plus complexes. Dans le but d'améliorer les performances et de réduire la consommation d'énergie, elles comprennent plusieurs CPU, des GPU, des accélérateurs ainsi que des hiérarchies de mémoire sophistiquées. De ce fait, les simulateurs de systèmes informatiques jouent un rôle important dans la communauté des chercheurs. Ils permettent d'évaluer de nouvelles idées d'architecture, de façons plus rapides, tout en évitant les coûts des processus de fabrication.

Les architectures simulées sont souvent comparées à des architectures réelles de l'état de l'art. Ainsi, la pertinence des résultats obtenus depuis un simulateur est directement liée à la fidélité du modèle de référence. Nous observons qu'il n'est pas simple d'avoir des modèles de référence solides, ceci en raison du manque d'informations techniques détaillées des architectures commerciales. Dans le cadre de cette thèse, nous proposons une méthodologie systématique pour extraire des informations depuis des architectures commerciales réelles. Ces informations sont ensuite utilisées afin de calibrer les modèles de référence correspondants. Cette méthodologie est basée sur le design de microbenchmarks et l'utilisation de compteurs de performance qui permettent une mesure non-intrusive du système. Nous appliquons cette méthodologie sur deux composants clés de l'architecture.

Dans un premier temps, nous ciblons les différents niveaux de la hiérarchie de la mémoire. Nous développons des microbenchmarks qui permettent d'extraire une signature caractéristique du système de mémoire. Cette signature contient des valeurs de paramètres importantes que nous utilisons pour la calibration du modèle de référence. Nous implémentons la méthodologie sur le simulateur gem5 et un processeur ARM, le Cortex-A53. Puis, nous évaluons la méthodologie avec des benchmarks de la suite SPEC CPU2006. Ces derniers sont exécutés sur l'architecture ARM et simulés sur gem5 en utilisant notre configuration calibrée. Les résultats montrent que notre calibration réduit l'erreur de simulation moyenne et maximale de 43% et 62%, respectivement.

Dans un second temps, nous appliquons la méthodologie sur le data prefetcher, qui

est un composant clé du système de mémoire. Celui-ci pouvant générer des demandes de mémoire en parallèle du cœur du processeur. Cette nouvelle instance de notre méthodologie donne lieu à Pref-X, un framework permettant l'analyse fonctionnelle des data prefetchers présents dans les coeurs in-order. Pour cela, nous utilisons des séquences de requêtes mémoire pour stresser le data prefetcher et exposer les changements dans le contenu de la cache L1. A partir de ces changements, Pref-X en déduit les spécifications fonctionnelles du data prefetcher qui permettent la construction un modèle fonctionnel. Nous implementons Pref-X à deux processeurs ARM in-order, le Cortex-A7 et le Cortex-A53. Nous évaluons les modèles fonctionnels résultants avec des traces mémoire extraites de la suite SPEC CPU2006. Nous exécutons les traces à la fois sur les CPU commerciaux et sur les modèles fonctionnels produits par notre framework. Les résultats montrent en moyenne une précision des modèles de 99,8% pour le Cortex-A7 et de 96,8% pour le Cortex-A53.

Cette thèse permet de comprendre en détail comment l'utilisation de microbenchmarks permet une amélioration de la précision des modèles de référence au sein des simulateurs. Aussi, nous pensons cette méthodologie est applicable à d'autres éléments de l'architecture, ceci pouvant faire l'objet de travaux futurs. Finalement, ces travaux contribuent à la communauté scientifique en permettant l'utilisation de modèles de référence d'architecture commerciale mieux calibrés.

### Acknowledgements

I would like to thank all the jury members for having evaluated my thesis. I want to thank Professor PETROT Frédéric and Professor SENTIEYS Oliver for having reviewed this manuscript. And, I thank Professor MUNIER Alix for having accepted to be the president of this jury.

I would like to express my gratitude to my thesis director, Professor Lionel Torres for having supervised and advised me during those last three years. I met him during my engineering school years. With his lectures, he showed me the world of computer system architecture and made me want to go deeper into its exploration.

He introduced me to Doctor David Novo who has been my co-supervisor. I especially want to thank him for all the things he has shared with me. His knowledge, experience, and also his own office. This manuscript reflects all the methodologies that he has taught me through those years.

I also want to thank Professor Francky Catthoor for having welcomed me at imec during my engineering school internships. He allowed the collaboration between imec and the university of Montpellier during my thesis.

Thanks to my co-workers who always have been helpful and supportive. Especially during the covid 19 pandemia. I am very grateful to all laboratory members for their kindness and solidarity.

Lastly, thanks to my family and my fiancé for being supportive and understanding all along the challenges of this thesis.

## **List of Figures**

| 2.1 | Memory hierarchy diagram                                                  | 9  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Heterogeneous multi-core architecture of the MediaTek Helio X20           | 11 |

| 2.3 | Virtual to physical address space mapping with memeory management         |    |

|     | unit                                                                      | 13 |

| 2.4 | 4-way associative cache organization                                      | 14 |

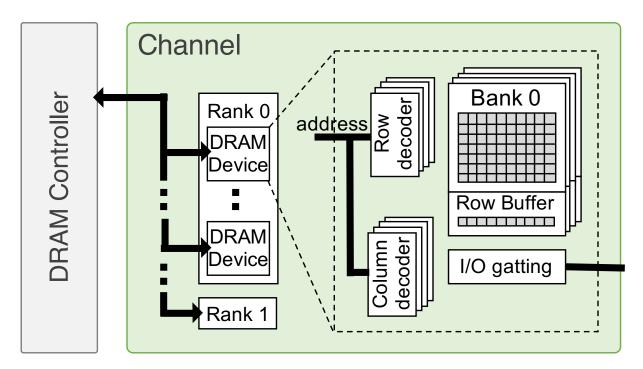

| 2.5 | A DRAM channel architecture                                               | 15 |

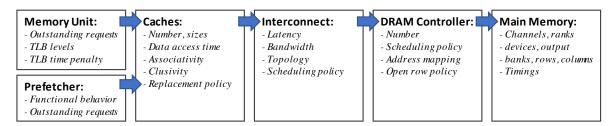

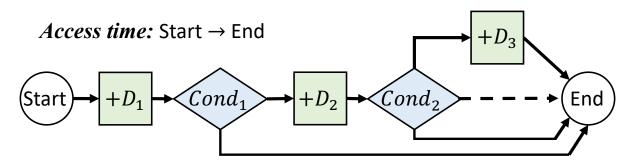

| 4.1 | Memory system component blocks with corresponding generic parameters      | 33 |

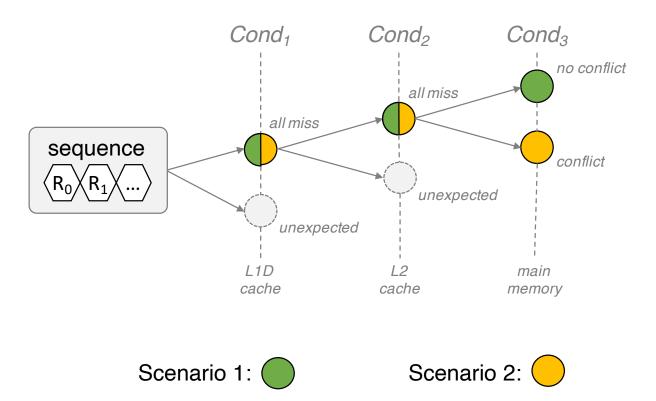

| 4.2 | Running example scenarios and conditions                                  | 37 |

| 4.3 | Running example microbenchmark C-code implementation                      | 40 |

| 4.4 | Measured loop assembly code of the running example microbenchmark.        | 41 |

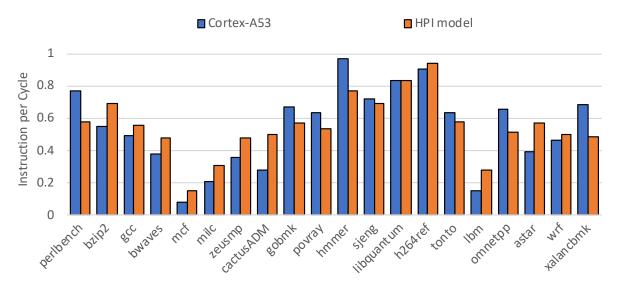

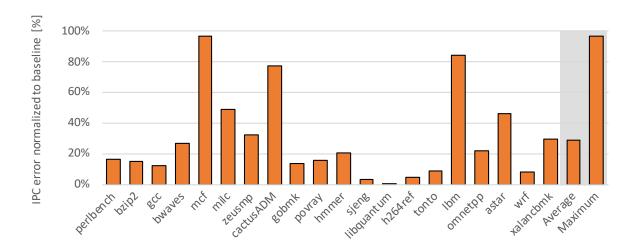

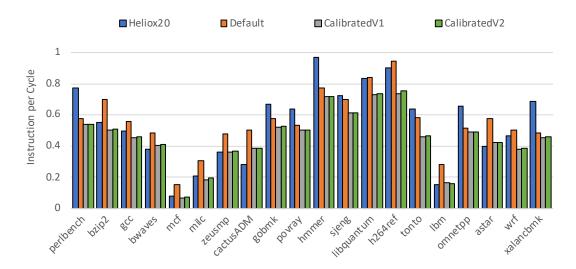

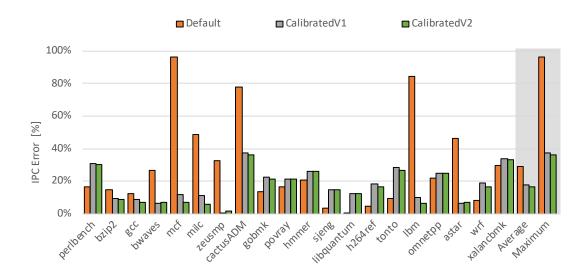

| 5.1 | IPC for the SPEC CPU2006 benchmarks executed on the MediaTek Helio        |    |

|     | X20 architecture and simulated with the default HPI gem5 configuration    |    |

|     | script                                                                    | 47 |

| 5.2 | Absolute IPC error for the SPEC CPU2006 benchmark suite simulated         |    |

|     | with the default HPI gem5 configuration script and normalized by exe-     |    |

|     | cution on the MediaTek Helio X20                                          | 48 |

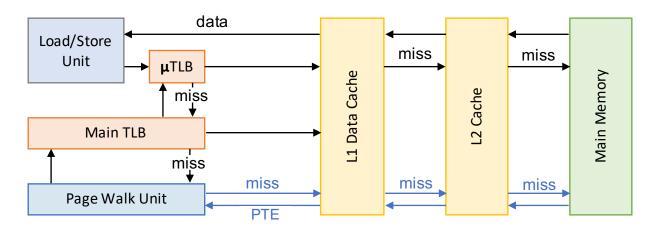

| 5.3 | Reactive memory system template. Translation from virtual addresses       |    |

|     | to physical addresses through multiple TLB levels and the page walk unit. | 49 |

| 5.4 | The delay of a memory request increases as it deepens in the hierarchy    | 50 |

| 5.5 | Gem5 simulated models: CalibratedV1 results from applying our method-     |    |

|     | ology to the on-chip memory system, CalibratedV2 extends the scope to     |    |

|     | the main memory, and Default is the default gem5 model                    | 52 |

| 5.6 | Microbenchmark C code designed to extract memory level signatures         | 55 |

| 5.7 | Microbenchmark pointer chasing implementation                             | 56 |

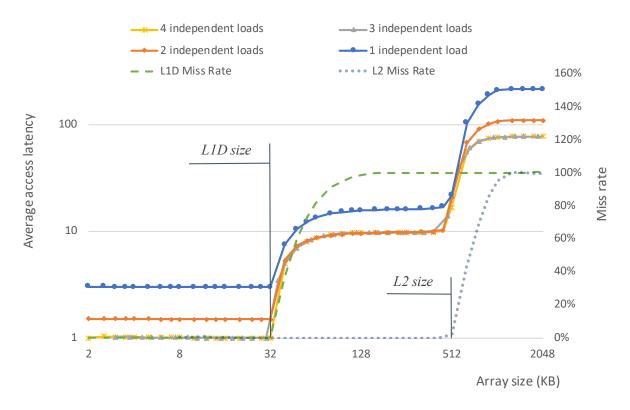

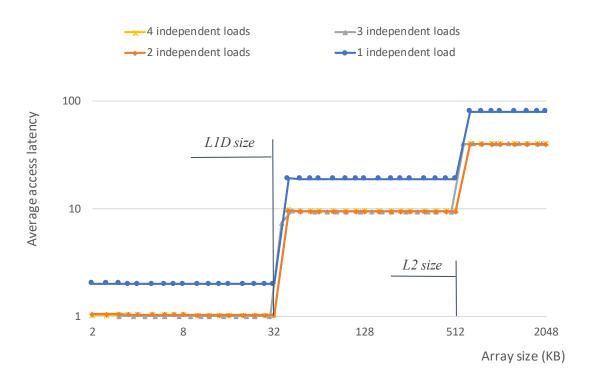

| 5.8 | Results from the execution of the microbenchmark on one Cortex-A53 of     |    |

|     | the MediaTek Helio X20                                                    | 56 |

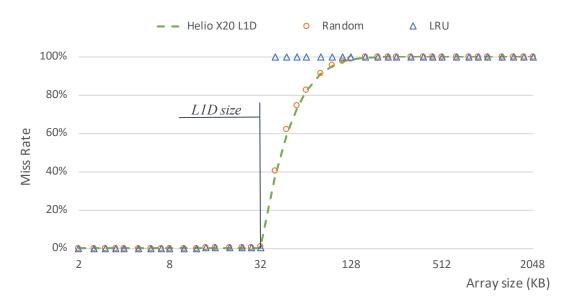

| 5.9 | Miss rate from the L1D of the MediaTek Helio X20 and two cache models     |    |

|     | implementing a Random and a LRU replacement policy. The size and          |    |

|     | the associativity are the same for the three caches                       | 58 |

x List of Figures

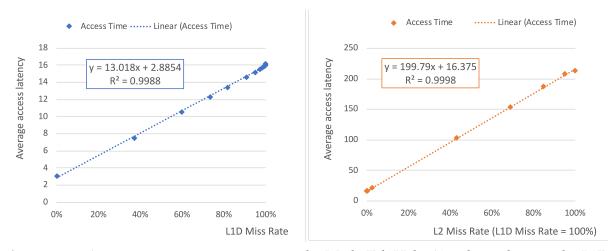

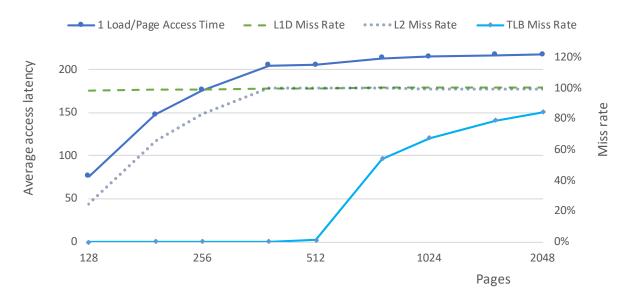

| 5.10 | Average memory access time on the MediaTek Helio X20 depending on the L1D and L2 miss rates | 58 |

|------|---------------------------------------------------------------------------------------------|----|

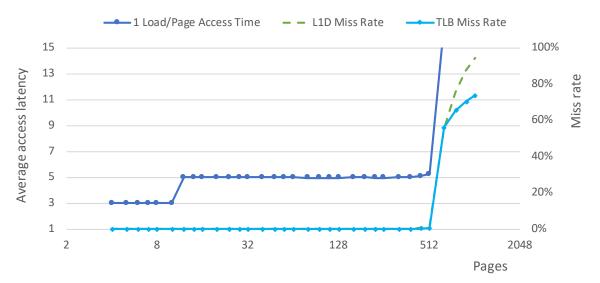

| 5.11 | Average access time depending on the number pages accessed with dif-                        |    |

| 0111 | ferent page-offsets on the MediaTek Helio X20                                               | 59 |

| 5.12 | Average access time depending on the number pages accessed with the                         |    |

|      | same page-offset on the MediaTek Helio X20                                                  | 61 |

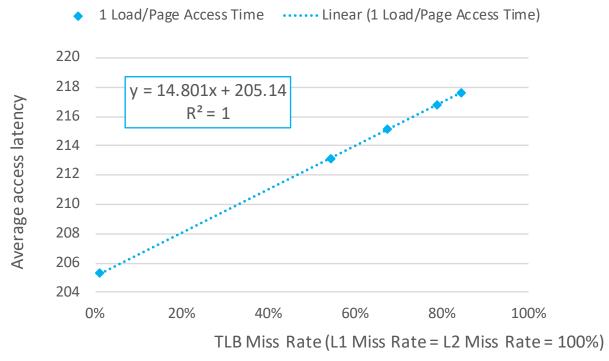

| 5.13 | Average access time on the MediaTek Helio X20 depending on the TLB                          |    |

|      | miss with L1D and L2 miss rates equal to 100%                                               | 61 |

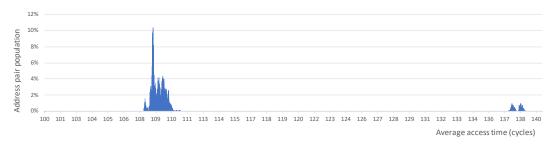

| 5.14 | Average delay distribution of main memory request pairs                                     | 63 |

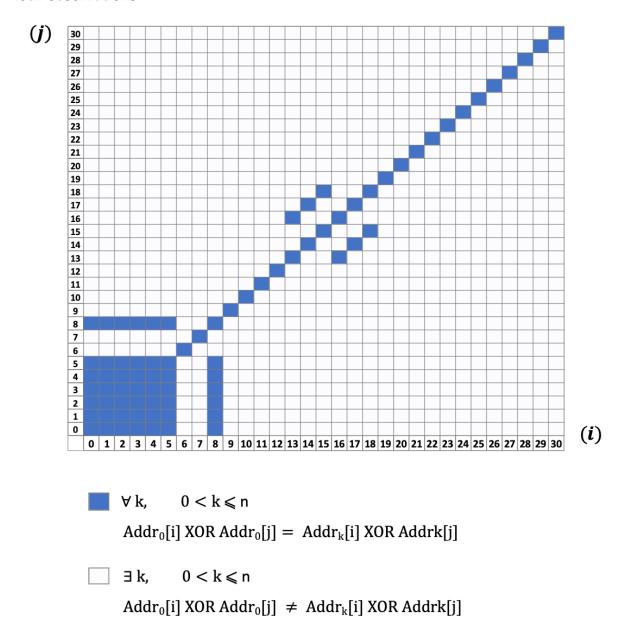

| 5.15 | Similarities between bit $XOR$ combinations of the addresses present in                     |    |

|      | the 138-cycle group of Figure 5.14. Experiments run on the MediaTek                         |    |

|      | Helio X20                                                                                   | 64 |

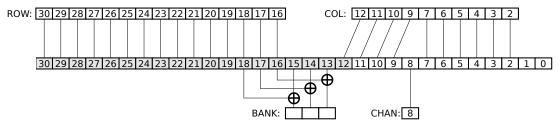

| 5.16 | Helio X20 main memory address mapping                                                       | 65 |

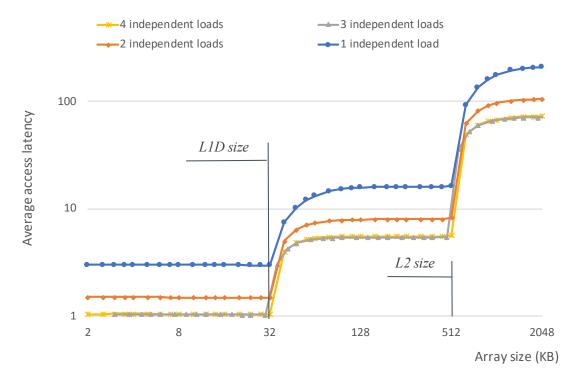

| 5.17 | Memory level signatures on gem5 of the Default HPI model configuration.                     | 67 |

| 5.18 | Memory level signatures on gem5 of the CalibratedV1 HPI model con-                          |    |

|      | figuration                                                                                  | 67 |

| 5.19 | IPC for the SPEC CPU2006 suite executed on the MediaTek Helio X20                           |    |

|      | and simulated on Default, CalibratedV1 and CalibratedV2 gem5 config-                        |    |

|      | urations                                                                                    | 68 |

| 5.20 | Normalized IPC error of the Default, CalibratedV1 and CalibratedV2                          |    |

|      | gem5 configurations with respect to reference hardware, the MediaTek                        |    |

|      | Helio X20                                                                                   | 69 |

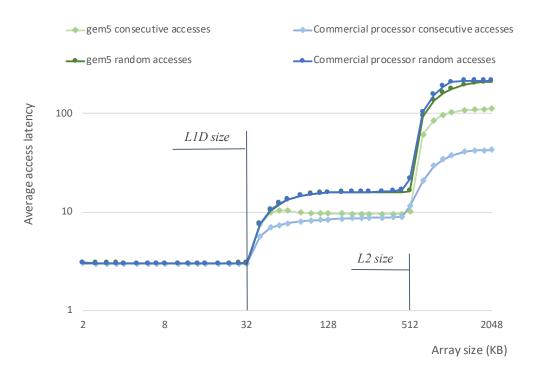

| 6.1  | Microbenchmark results for consecutive and random accesses to the ar-                       |    |

|      | ray, simulated with CalibratedV1 gem5 configuration and executed on                         |    |

|      | oneCortex-A53 of the MediaTek Helio X20 SoC                                                 | 77 |

| 6.2  | Helio X20 main memory address mapping                                                       | 78 |

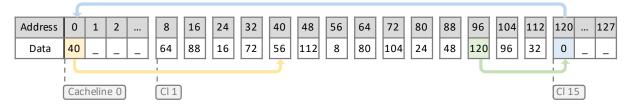

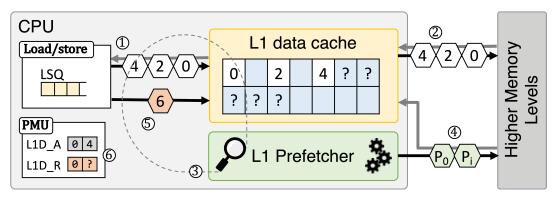

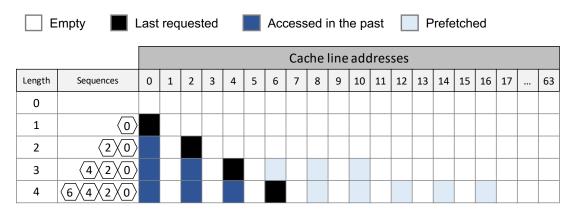

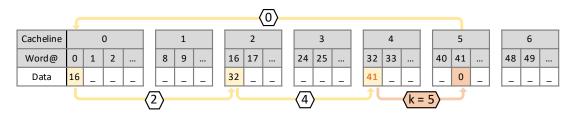

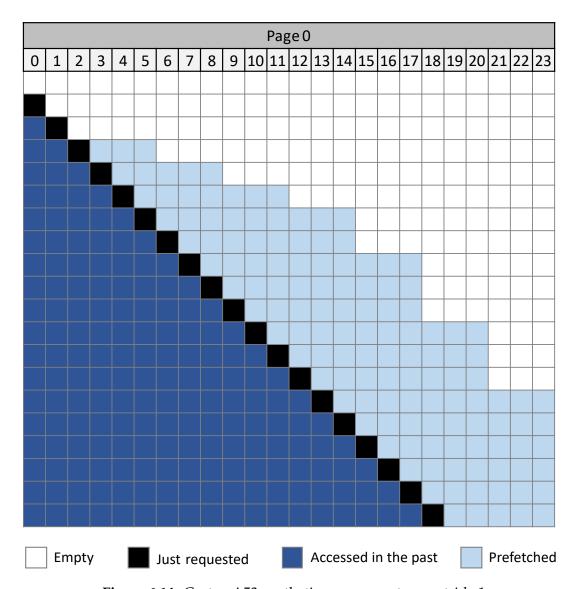

| 6.3  | L1D cache content when accessing memory sequence $(0, 2, 4, 6)$                             | 79 |

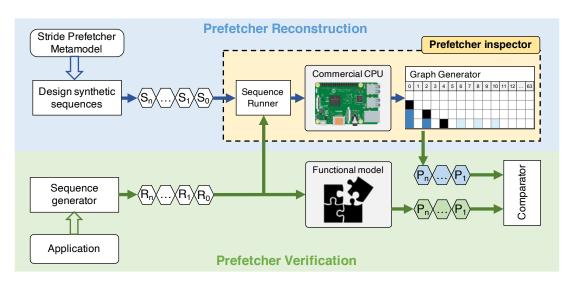

| 6.4  | Pref-X phases illustration                                                                  | 80 |

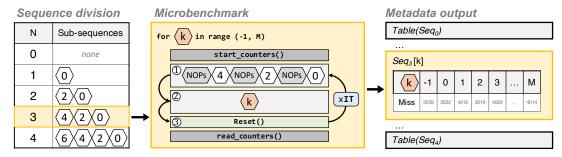

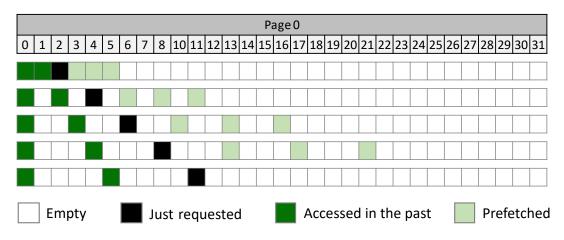

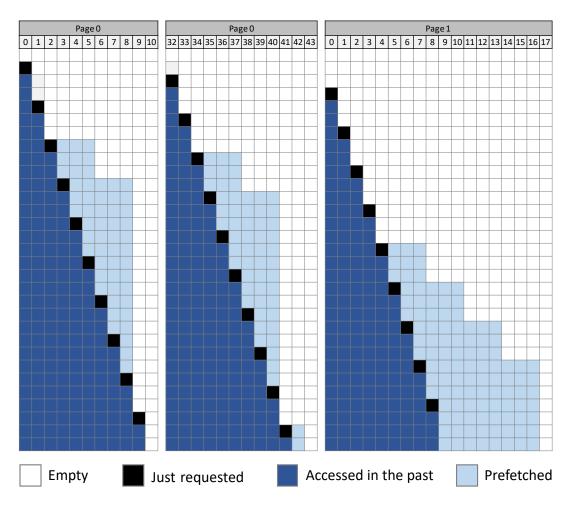

| 6.5  | Prefetcher inspector: sequence runner phases illustration                                   | 82 |

| 6.6  | Sequence runner microbenchmark C code                                                       | 83 |

| 6.7  | Sequence runner pointer chasing for memory sequence $\langle 0, 2, 4 \rangle$ and the       |    |

|      | inspection of the address 5                                                                 | 84 |

| 6.8  | Metadata generated by the sequence runnner, processed by the graph                          |    |

|      | generator                                                                                   | 85 |

| 6.9  | Address mapping L1D of Cortex-A7 and Cortex-A53                                             | 86 |

| 6.10 | Final pointer chasing implementing reset method                                             | 87 |

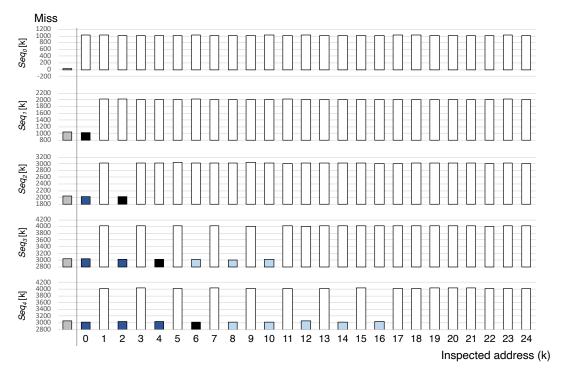

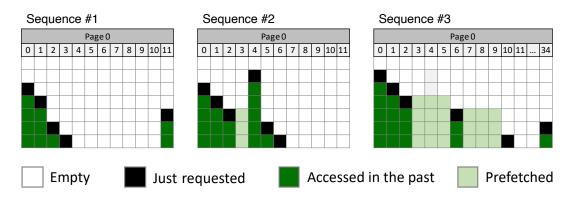

| 6.11 | Cortex-A7 synthetic sequence: stream stride 1                                               | 88 |

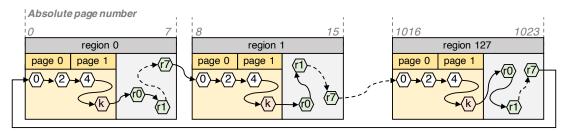

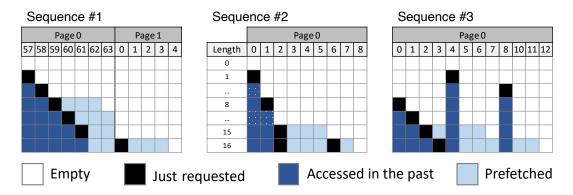

| 6.12 | Cortex-A7 synthetic sequences: #1, #2, and #3.                                              | 88 |

List of Figures xi

| 6.13 | Cortex-A7 synthetic sequence: maximum stride                            | 89 |

|------|-------------------------------------------------------------------------|----|

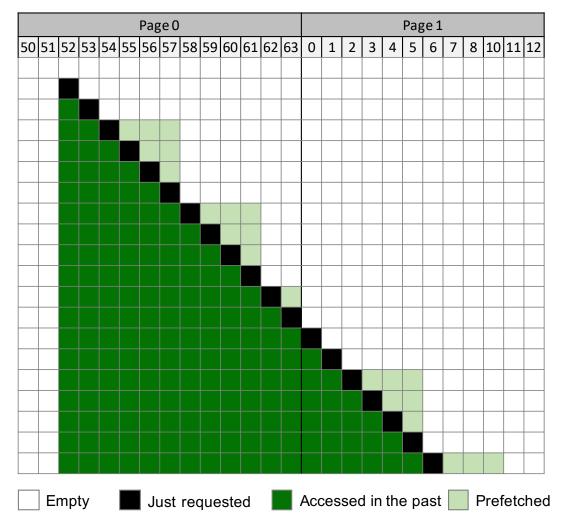

| 6.14 | Cortex-A53 synthetic sequence: stream stride 1                          | 91 |

| 6.15 | Cortex-A53 synthetic sequence: #1, #2, and #3                           | 92 |

| 6.16 | Cortex-A53 synthetic sequence: three interleaved streams                | 93 |

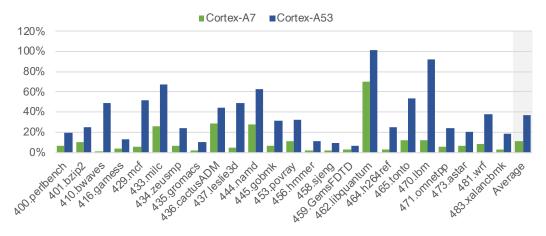

| 6.17 | Prefetcher Intensity of SPEC CPU2006 benchmarks executed on the Cortex- |    |

|      | A7 and Cortex-A53, and simulated on their corresponding functional      |    |

|      | models                                                                  | 95 |

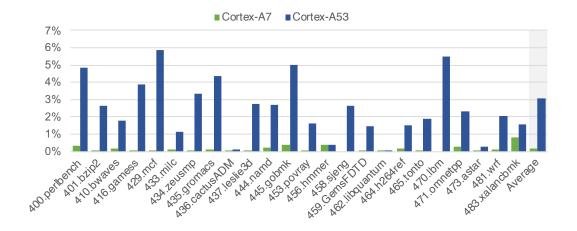

| 6.18 | Normalized modeling error of SPEC CPU2006 benchmarks executed on        |    |

|      | the Cortex-A7 and Cortex-A53, and simulated on their corresponding      |    |

|      | functional models                                                       | 96 |

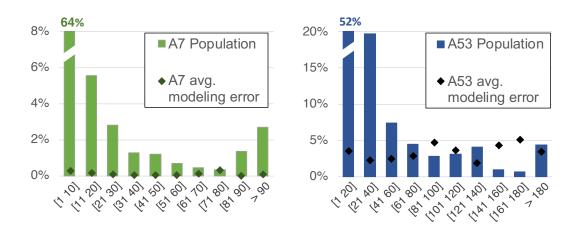

| 6.19 | Memory sequences distribution depending on the number of prefetches     |    |

|      | generated on the Cortex-A7 and Cortex-A53                               | 96 |

### **List of Tables**

| 4.1 | Architecture events monitored with PAPI                          | 39 |

|-----|------------------------------------------------------------------|----|

| 4.2 | Measure time and hardware performance counters outputs from mi-  |    |

|     | crobenchmark execution on Raspberry Pi 3B+                       | 42 |

| 5.1 | List of key parameters with default and calibrated values        | 54 |

| 5.2 | List of Ramulator key parameters                                 | 62 |

| 5.3 | Cumulative simulation time of CalibratedV1 and CalibratedV2 gem5 |    |

|     | configurations                                                   | 69 |

| 6.1 | Comparison of the A7 and the A53 stride prefetchers              | 94 |

### **Contents**

| Li | st of | Figures                                          | ix   |

|----|-------|--------------------------------------------------|------|

| Li | st of | Tables                                           | xiii |

| 1  | Intr  | oduction                                         | 1    |

|    | 1.1   | Context                                          | 2    |

|    | 1.2   | Contributions                                    | 4    |

|    | 1.3   | Outline                                          | 6    |

| 2  | Bac   | kground                                          | 7    |

|    | 2.1   | Memory System                                    | 8    |

|    | 2.2   | Memory Components                                | 11   |

|    | 2.3   | Computer Architecture Simulators                 | 16   |

| 3  | Rela  | ated Work                                        | 19   |

|    | 3.1   | Sources of Error in Simulator Baselines          | 20   |

|    | 3.2   | Simulator Verification                           | 21   |

|    | 3.3   | Dedicated Simulators                             | 22   |

|    | 3.4   | Simulation Time Mitigation Techniques            | 24   |

|    | 3.5   | Remaining Challenges                             | 26   |

|    | 3.6   | Summary                                          | 27   |

| 4  | Mic   | robenchmark-Based Timing Calibration Methodology | 29   |

|    | 4.1   | Motivation                                       | 30   |

|    | 4.2   | Simulator Parameters Identification              | 31   |

|    | 4.3   | Simulator Parameter Discovery                    | 33   |

|    | 4.4   | Implementation of the Running Example            | 38   |

|    | 4.5   | Summary                                          | 42   |

| 5  | Mei   | nory System Timing Calibration                   | 45   |

|    | 5.1   | Background and Motivation                        | 46   |

|    | 5.2   | Methodology Instantiation                        | 48   |

|    | 5.3   | Methodology Implementation                       | 51   |

xvi

|                | 5.4   | Experimental Evaluation         | 66  |

|----------------|-------|---------------------------------|-----|

|                | 5.5   | Summary                         | 71  |

| 6              | Dat   | a Prefetching Functional Model  | 73  |

|                | 6.1   | Background and Motivation       | 74  |

|                | 6.2   | Key Insights                    | 77  |

|                | 6.3   | The Pref-X Framework            | 79  |

|                | 6.4   | Prefetcher Inspector            | 81  |

|                | 6.5   | Implementation                  | 85  |

|                | 6.6   | Evaluation                      | 95  |

|                | 6.7   | Summary                         | 97  |

| 7              | Con   | clusion                         | 99  |

|                | 7.1   | Summary of Key Findings         | 100 |

|                | 7.2   | Recommendations for Future Work | 103 |

|                | 7.3   | Concluding Remarks              | 105 |

| Bi             | bliog | graphy                          | 107 |

| $\mathbf{A}_1$ | ppen  | dix                             | 123 |

### I

### Introduction

Modern computer systems have become increasingly complex. In order to keep improving both performance and energy efficiency, modern computer architectures include multiple processing units such as CPUs, GPUs, or accelerators. All the processing units share the same memory resulting in a meticulously orchestrated hierarchy of distributed private and shared memories. Additionally, the utilization spectrum of computer systems becomes very wide, from very energy-efficient embedded systems to high-performance computing.

#### 1.1 Context

In this section, we present how researchers continue improving modern architecture by exploring new designs of computer architectures. In particular, we see that the memory system is a critical component of the architecture, leading to many specific explorations. We further introduce computer architecture simulators as an alternative to chip manufacturing for architecture exploration. We finally expose simulator drawbacks and limitations, which motive this thesis.

#### 1.1.1 Computer Architecture Exploration

In order to keep improving performance and energy efficiency, researchers continue exploring new designs across all components of the architecture components. Indeed, multiple components other than the CPUs play a significant role in global architecture performance, such as the GPUs or the memory system. The main challenge of such explorations is evaluating new designs' benefits against state-of-the-art references. A straightforward solution would be to conduct the exploration by manufacturing new chips that implement the new design. However, a strong drawback would be the cost of such explorations. Chip manufacturing is a very long and expensive process mainly reserved for commercial platforms. In addition, during architecture exploration, we may evaluate non-existing technologies to identify ideal cases and motivate exploration directions. Also, the monitoring is often limited with actual manufactured chips and can disturb normal behavior.

1.1. *Context* 3

#### 1.1.2 Memory System

The memory system is an essential part of computer system architecture. It provides necessary data around all the processing units present in the architecture. As a result, the memory system significantly impacts global architecture performance. Indeed, a slow reactive memory system can slow down the complete architecture. Additionally, the memory system represents a big part of the system's energy consumption [1]. Consequently, Modern computer architectures implement complex memory organizations, including different memory technologies, layouts, and protocols to keep high performance. Regarding all these aspects, the memory system is a prevalent topic of exploration within the system architect community.

Moreover, emerging non-volatile memory technologies provide new opportunities for memory system improvement [2]. However, those technologies have different technical specifications than existing commercial memory technologies. Thus, the different memory protocols and organizations must be rethought. Many explorations on using such non-volatile technologies have already been done [3, 4, 5]. Nevertheless, some more still need to be made as most of those technologies are not mature yet. They may become even more attractive in the future.

Architecture simulators are essential tools used by academic and industrial researchers to address all these challenges in modern memory systems.

#### 1.1.3 Architecture Simulator

Computer architecture simulators have become an essential tool for computer architecture research [6, 7, 8, 9]. Contrary to chip manufacturing, they allow quick and inexpensive evaluations of new architecture ideas. Computer architecture simulators are already widely used by the research community. For instance, the gem5 simulator [10] has already been cited several thousand times in the last decade. However, computer simulators suffer from drawbacks such as the trade-off between simulation time and model accuracy. The most accurate simulations can achieve very long simulation times. Conversely, the simulation results from an inaccurate model would lead to misleading conclusions [11]. Thus, it is crucial to select an appropriate level of accuracy.

With computer simulators, the evaluation of new ideas is made against a reference baseline model. This baseline model represents a realistic state-of-the-art architecture. A common error with such evaluation is to use a flawed baseline model, which compromises the relevance of evaluation results. However, calibrating a baseline model can be difficult. Indeed, key commercial architecture technical information is often not public, hindering baseline model calibration.

#### 1.1.4 Simulation Verification

To evaluate the accuracy of a simulator, researchers verify them against real architectures. They first calibrate the simulation model before simulating and executing realistic benchmarks on both the simulator and the target. Thus, the simulation error is the difference between the simulator's and target's results. In order to prove the accuracy of the simulator, the simulation error needs to be the lowest. In this way, several works [12, 13, 14] propose verifying the gem5 simulator against architectures. The average error is around 2% within 18%. However, those evaluations cover only a few points of the all gem5 architecture coverage. Moreover, the empirical calibration methods used during those evaluations cannot be generalized to other architectures, limiting the verification of the rest of the architecture coverage. This situation worsens as state-of-the-art architectures keep advancing, making previous evaluations outdated.

#### 1.2 Contributions

In this thesis, we tackle the problem of accurate computer simulations. Specially, we focus on a particular type of error that is recurrent in computer architecture simulators, the flawed calibrations of the simulation baseline. The memory system has a significant role in general, but more importantly, in multicore architectures. Consequently, our goal is to calibrate precisely the memory system of multicore architectures against real state-of-the-art commercial architectures to provide more accurate simulations.

To this end, we propose in this thesis three main contributions that we introduce in the continuation of this section.

#### 1.2.1 Calibration Methodology

The first contribution is a systematic methodology that we propose to calibrate the memory system of a computer architecture simulation. The calibration is made against a real state-of-the-art architecture that we call *target* architecture. The methodology is composed of two phases. We determine the simulator parameters we need to calibrate

1.2. Contributions 5

during the first one. Then, we calibrate them in the second phase of the methodology. For that, we start using first-party documentation. However, as part of the technical information is not public, we propose a method base on handcrafted microbenchmarks and hardware monitoring to extract missing technical information from the target architecture. In parallel, we use a running example to illustrate the different steps throughout the methodology description. This contribution is presented in Chapter 4.

#### 1.2.2 Memory System Simulator Calibration

The second contribution is an instantiation of the proposed methodology on the reactive part of the memory system, i.e., the cache levels and the main memory. We illustrate the path of memory requests through the memory hierarchy and model it as a graph of conditions and delays. We then use it to detail the design of microbenchmarks that we execute to extract technical information from target commercial architectures. We implement the resulting instantiation on the gem5 simulator [10] and one Cortex-A53 of the MediaTek Helio X20 SoC that we select as target state-of-theart architecture [15]. Finally, we evaluate our methodology with benchmarks from the SPEC CPU2006 suite. We execute them on the board to have a reference, and then we simulate them on gem5 using the default and calibrated models to expose our methodology's benefits. This contribution is introduced in Chapter 5.

#### 1.2.3 Analysis of In-Order CPU Data Prefetcher

The last contribution is Pref-X [16], a framework to analyze functional characteristics of data prefetching in commercial in-order cores. Pref-X instantiates the proposed methodology on a commercial data prefetcher engine. It exposes the data prefetching activity by *X-raying* the cache memory content after triggering the data prefetcher. That way, a complete functional data prefetcher model can be extracted from the target commercial architecture. The functional model is verified in a second phase with realistic benchmark memory traces. Finally, we demonstrate the feasibility of this methodology by implementing Pref-X on two ARM in-order cores, the Cortex-A7, and the Cortex-A53. We show a functional accuracy of 99.9% and 96.8% for the Cortex-A7 and the Cortex-A53, respectively. This contribution is described in Chapter 6.

#### 1.3 Outline

We structure this thesis around seven chapters. Chapter 2 introduces relevant background about multicore memory systems. It also introduces two simulators that we further use during evaluations. Chapter 3 discusses related work about computer simulators. E.g., their different categories, their verification or utilization. Chapter 4 introduces our systematic methodology and details the two phases that compose it. Chapter 5 and Chapter 6 present two instances of the methodology on the memory system and the data prefetcher, respectively. Finally, Chapter 7 concludes this thesis by summarizing the key achievements and discussing future work.

# II

# Background

In this chapter, we introduce the main components present in the memory system of modern multicore systems. Also, we present key processes of the memory system, such as data prefetching. Finally, we present the simulators we use to evaluate new architectural ideas and especially new memory architecture designs.

#### 2.1 Memory System

Modern computer architectures are composed of multiple processing units such as CPUs, GPUs, or accelerators. The memory system has the role of providing data and instructions to each processing unit. Consequently, the memory system has a significant impact on global architecture performance [17, 18, 19]. Indeed, a slow data access time or a low memory bandwidth can slow down the whole architecture.

#### 2.1.1 Memory Hierarchy

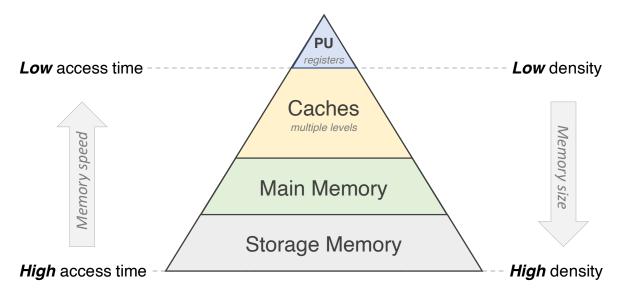

Depending on its organization and technology, memory can have very different characteristics [20, 21, 22], e.g., small and fast, or big and slow. In this way, the memory system is composed of different types of memories. These memories are organized in a hierarchy as illustrated in Figure 2.1. The first level of the hierarchy is the process unit registers. Then there are three different kinds of memories:

- On-chip Caches. The memory caches are small but very fast. They can be private or shared between several processing units. They are divided into different levels that we call L1, L2, and L3. The L1 is the closest memory to the processing unit. The Last Level Cache (LLC) is the farthest memory cache from the processing unit. Additionally, modern heterogeneous SoCs implement System Level Cache (SLC), which is beyond the LLC and shared between all the system components, i.e., CPUs, GPUs, Neural Processing Units (NPUs), and other accelerators. Usually, they are implemented with an SRAM technology. Their sizes go from tens of kilobytes for the L1 to tens of megabytes for the LLC and SLC.

- The main memory is a fundamental element of the memory system, as this memory is shared between all the processing units of the architecture. This memory contains all the data necessary for Operating System (OS) routine and program execution. The main memory is mostly implemented with DRAM technology using standardized interface, e.g., DDR4, LPDDR4. The main memory size goes

from a few gigabytes for embedded systems to hundreds of gigabytes for big servers.

• The storage memory is the largest memory of the memory system but also the slowest. Contrary to the main memory and the caches, the storage memory is Non-Volatile Memory (NVM). Thus, the memory can retain the stored data even without power. The common non-volatile technology used for storage memory is the NAND-Flash. The size of the storage memory is usually at least a few gigabytes. However, the maximum size cannot be defined as we can always increase the size, e.g., plugging a new memory disk or using online storage.

This distribution of technologies in memory hierarchy is also due to other metrics such as the cost per bit or cell endurance. For instance, the L1 cache has high endurance, contrary to the storage memory. Indeed, the L1 cache is more written than the storage memory. In the same way, the cost per bit of the L1 is higher than the storage memory. Thus, the memory hierarchy's purpose is to balance each technology's benefits and drawbacks.

Figure 2.1: Memory hierarchy diagram.

#### 2.1.2 Data Movement

The general purpose of the memory hierarchy is to place *hot* data, i.e., frequently used data, close to the processing units to reduce their access times. For that, the memory hierarchy is based on two principals [20] that characterize data utilization during program execution: First, the temporal locality. If a program uses data once, it is likely to

use it again in a short time. Second, the spatial locality. If a program uses data, it is likely to use its neighbor.

Thus, when a *word* of typically eight bytes is requested by the processing unit, a complete *cache line* of typically sixty-four bytes, including the word's neighbors, is moved to the L1. That way, if the processing unit further requests one of them, the word would already be present in the L1, exploiting both temporal and spatial localities. As the size of the L1 is limited, when the L1 cache is full, one cache line needs to be moved back to a lower level before the L1 receives a new one. The *cache replacement policy* is the set of rules that dictate which address is evicted from the cache. For instance, the Last Recent Used (LRU) cache replacement policy selects the coldest data to evict from the cache.

When a cache line is requested to a cache level, a *cache hit* occurs if the cache line is present in the requested cache. Contrary, a *cache miss* occurs when a requested cache line is missing in the requested cache. Thus, if a memory request causes an L1 cache miss, the request is then sent to the L2 cache, where it can either produce a cache hit or a cache miss. Furthermore, we call *miss* (*hit*) *rate* the ratio of miss (hit) out of the total number of accesses to a specific cache level. This metric is used to measure memory system activity and optimization. During program execution, an ideal case would be an L1 miss rate of 0%. I.e., all the memory requests are issued with the minimum access time.

Finally, the granularity of data transfers between the main and storage memory is a *page* which generally contains four kilobytes. A *page fault* occurs when the requested address is missing in the main memory. In this case, a complex routine is run by the Operating System (OS) to evict one page from the main memory and replace it with the one containing the requested address. This operation is very long (e.g., thousands of CPU cycles) compared to access to the caches or the main memory.

#### 2.1.3 Illustrating Example

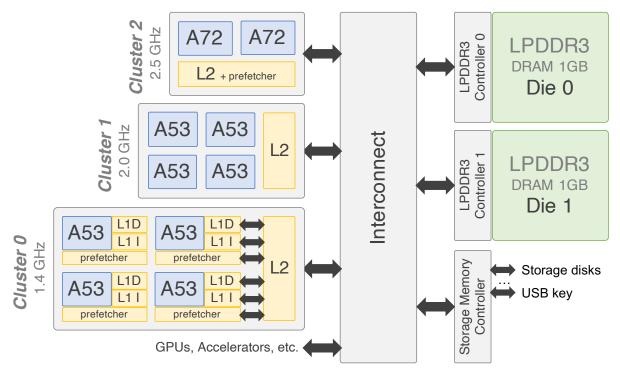

We use an illustrating example to present an existing commercial memory hierarchy. Figure 2.2 shows the architecture of the MediaTek Helio X20 SoC [15]. This commercial platform contains three clusters providing different performance and energy consumption ratios. ARM introduced this organization with the big.LITTLE concept [23]. Clusters 0 and 1 contain four Cortex-A53 each. They are the low and middle-performance clusters. Cluster 2 contains two Cortex-A72. It is a high-performance cluster. All the clusters contain a dedicated L2 cache shared between all the CPUs of the cluster. An

interconnect allows connecting all the processing units, i.e., the clusters, GPUs, and accelerators, to the main and storage memory.

Figure 2.2: Heterogeneous multi-core architecture of the MediaTek Helio X20.

As illustrated with cluster 0, each CPU contains a private L1 cache. This one is separated into two caches: the L1 data (L1D) cache and the L1 instruction (L1I) cache. Thus, at this level of the memory hierarchy, the data and the program instruction are stored in two different memories.

#### 2.2 Memory Components

In this section, we introduce important elements and features of the memory system. We explain what is the virtual address space and how the memory system manages it. Then, we describe the organization of the set-associative caches and the main memory. Finally, we introduce the data prefetching detailing its purpose and main characteristics.

#### 2.2.1 Virtual Space and the Memory Management Unit

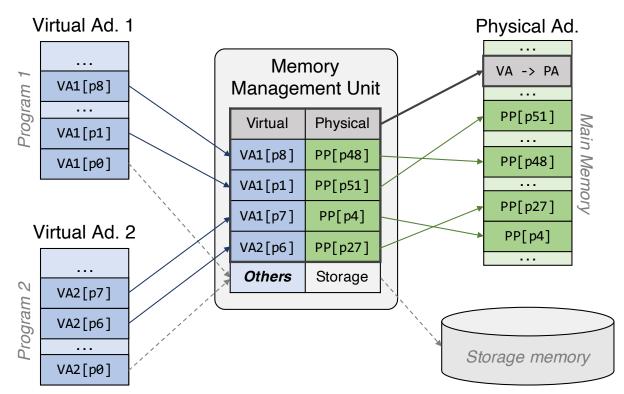

When a program is launched, the OS generates a *virtual* address space, which defines the range of addresses the program can access. Every program has its own virtual

address space. Contrary, the *physical* address space corresponds to real addresses accessible in the main memory. The Memory Management Unit (MMU) is the memory system component mapping virtual addresses to physical addresses. MMU does the translations at the page granularity. That way, it maps virtual pages to physical pages, as illustrated in Figure 2.3. As the main memory size is limited, all the virtual pages are not mapped to physical ones. When a page fault occurs, i.e., a requested virtual address is not present in the main memory, the OS updates the mapping in the MMU, replacing one physical page from the main memory.

This abstraction has multiple benefits.

- 1. It isolates each program from the other, ensuring better security. For instance, malware cannot use another virtual address space. Additionally, the OS randomizes the mapping to prevent malware attacks.

- 2. It prevents programs from dealing with shared memory issues between programs. The OS manages such shared memory portions.

- 3. Contrary to the size of the physical address space, which corresponds to the size of the main memory, the OS can create an infinite number of virtual address spaces.

The MMU stores all *translation* data used to translate virtual addresses in the main memory. However, to avoid accessing the main memory for every memory operation, the MMU contains a Translation Lookaside Buffer (TLB). The TLB can cache a limited number of translation data close to the processing unit. Thus, each processing unit has a TLB to process the address translations. A *TLB miss* occurs when an address translation data is missing in the TLB. In this case, the translation data is requested to the Page Walk Unit (PWU), adding an extra translation delay. Finally, a request is sent to the memory system if the translation data is not present in the PWU.

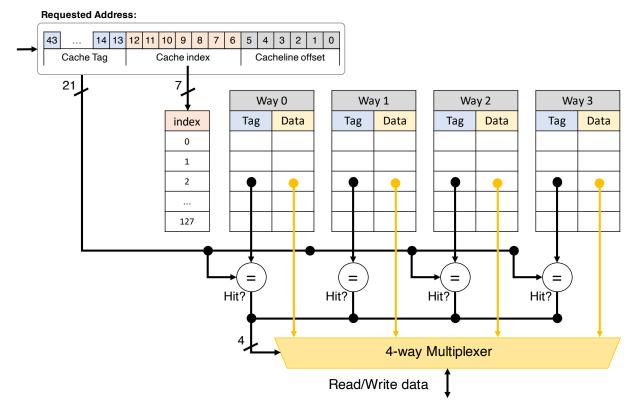

#### 2.2.2 Caches Associativity

The cache memories are the highest levels of the memory hierarchy before the processing unit registers. They usually use the SRAM technology allowing quick read and write operations. The caches contain parts of the main memory data. When requesting an address to a cache, the first step is to check if the address is either present or not in the cache, i.e., if there is either a cache hit or a cache miss. This process can be very long and energy-consuming. Thus, to mitigate this cost, *set-associative* cache limits an address's possible locations in the cache. That way, only the possible locations

Figure 2.3: Virtual to physical address space mapping with memeory management unit.

are checked instead of checking the entire cache, limiting the time and energy cost. A direct-mapping cache limits an address to only one location, allowing the lowest time and energy cost but increasing the cache miss rate. Conversely, a fully-associative cache does not limit any address's location. The cost is very high in this case, with a low cache miss rate. Finally, N-way set-associative cache limits the number of possible locations to N. Depending on the size, the reasonable value of N allows a trade-off between low cost and a low miss rate.

Figure 2.4 illustrates the case of a 4-way set-associative 32KB cache. This organization corresponds to the L1 data cache of one Cortex-A53 [24] present in the MediaTek Helio X20 SoC introduced in the previous Section 2.1.3. The addresses are indexed in the cache using a *tag*, in four arrays, i.e., four ways. The size of one way corresponds to the size of the cache divided by the number of ways. In this case, the size of one way is eight kilobytes corresponding to 128 cache lines.

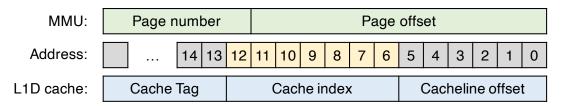

When requesting an address to the cache, the address is first translated into a tag and an index. The six first Last Significant Bits (LSB) correspond to the cache line offset. Then, the seven next bits constitute the index. Finally, the rest of the address represents the tag. To check if the address is present, we check within the four ways at the corresponding index if one of the four tags matches the requested address tag. If one tag matches, there is a cache hit. The last step is to load/write the data from/to the corresponding way.

Figure 2.4: 4-way associative cache organization.

#### 2.2.3 Main Memory Organization

The main memory can implement several organizations [25, 26]. However, the SDRAM organization remains the standard organization using JEDEC interface protocols, such as DDR4 or LPDDR4. Some interfaces, such as HBM [27] or HMC [28] also propose to use 3D stacking implementation.

The main memory organization is divided into multiple channels [29]. Each channel is driven by a dedicated DRAM controller, as illustrated in Figure 2.5. A single channel can contain multiple ranks [30]. Usually, a Dual In-line Memory Module (DIMM) includes one rank in each face. A rank contains multiple DRAM memory devices depending on the device output width. For example, according to the JEDEC standard, a typical rank output width is 64 bits. When using DRAM devices of 8-bit output, a rank is composed of 8 devices. All devices of the same rank execute the same commands from the controller in parallel. Then, the outputs of the devices are concatenated to form the 64-bit rank output.

Furthermore, a DRAM device contains multiple banks. A bank is an array of DRAM cells where one bit is stored as a charge in a capacitor. To read data from a bank, a whole bank row is moved to a row buffer. Then, the right column is read or written using the I/O gatting. The row buffer acts as a cache. Thus, consecutive

memory accesses to the same bank row will be faster than to different banks. A *row buffer hit* occurs when memory access uses a row already present in the row buffer. Conversely, a row buffer *conflict* occurs when memory access requests a different row than the opening one. As the transfer from the bank to the row buffer removes the row data from the bank (i.e., destructive read), we need to write back the opening row to bank, and then transfer the requested row to row buffer to be read. This process is the worst-case scenario.

**Figure 2.5:** *A DRAM channel architecture.*

#### 2.2.4 Data Prefetching

The data prefetching engine is another important component of the memory system. Its role is to monitor the accesses made by the processing unit in order to predict the future necessary addresses. Once the prediction is made, the predicted addresses are prefetched from the lower levels of the memory hierarchy directly to the caches. If the prediction is accurate, data prefetching reduces the cache miss rates and minimizes memory access time, consequently increasing the system performance [31, 32, 33, 34, 35]. Thus, a *prefetch* is a memory request generated by the data prefetching engine.

The data prefetching engine is characterized by two metrics: coverage and accuracy. The coverage defines the number of avoided misses thanks to data prefetching. The accuracy corresponds to the number of useful prefetches, i.e., prefetches that are the

source of cache hits. The coverage and accuracy depend on the prediction process and parameters, such as the number of prefetches generated from one prediction. Ideally, a perfect data prefetcher would have high coverage and high accuracy. However, in reality, a trade-off remains between those two metrics.

For instance, we use only the high confidence degree predictions to get high accuracy but limiting the prefetcher's coverage. Conversely, an aggressive data prefetcher achieves high coverage based on low-quality predictions. However, it pollutes the caches with useless cache lines, degrading the accuracy. Similarly, the number of prefetches generated from one prediction can impact those metrics. For example, the ARM Cortex-A53 exposes several data prefetcher configurations [36] to the firmware. Several parameters, such as the number of outstanding prefetches (from one to eight) or the number of consecutive cache misses triggering data prefetching (between 3 or 4), can also be tuned to obtain different coverage and accuracy values.

#### 2.3 Computer Architecture Simulators

In this section, we introduce two computer architecture simulators, the gem5 simulator and Ramulator, both event-driven open-source simulators. The gem5 simulator is a modular platform that can model a complete computer architecture. Contrary, Ramulator only simulates the main memory allowing faster simulations by abstracting the CPU cores with memory traces.

#### 2.3.1 Gem5

The gem5 simulator comes from merging the M5 [37] and the GEMS [38] simulators. This simulator is very popular in the architecture research community as it has already been cited more than five thousand times. gem5 is a very modular platform that can simulate various ISAs [39]. i.e., Alpha, ARM, SPARC, MIPS, POWER, RISC-V, and x86. It provides a wide range of modules for every element of the architecture. A drawback of its great modularity and accuracy is its long simulation time. Thus, for the same architecture component, gem5 modules provide different levels of accuracy. For instance, a one-core CPU simulation does not need a high-accurate interconnect model, as a single core cannot generate cannot generate enough requests to saturate the interconnect. Conversely, an inaccurate interconnect model can significantly impact the simulation results in the case of multi-core simulation.

One very accurate model available on gem5 is the High Performance In-order (HPI) CPU model [40]. This model is based on the MinorCPU in-order CPU model, which has been tuned by ARM to be representative of a modern ARM in-order 64-bit CPU. This model also includes cache modules and TLB modules, which have also been tuned. Other equivalent computer architecture simulators exist [41, 42, 43, 44, 45, 46]. However, we use gem5 and its HPI model as simulation reference for the rest of this thesis.

#### 2.3.2 Ramulator

Ramulator is an accurate DRAM simulator [30] from SAFARI Research Group at ETH Zurich and Carnegie Mellon University. It supports various DRAM commercial standards such as DDR4, LPDDR4, GDDR5, or WIO2. A few corresponding parameters are available for each standard and can be set up using pre-listed values in the simulator code. Contrary to the high modular gem5 simulator, Ramulator is a memory-dedicated simulator [47, 48, 49, 50, 51]. In this way, it can provide precise and fast main memory simulations. We use it as a DRAM simulator reference in this thesis.

The standard usage mode of Ramulator is the memory trace-driven mode. Ramulator uses memory traces from an input file and simulates the sub-system DRAM controllers plus DRAM memories. Other modes, e.g., the CPU trace-driven mode, which includes a simple CPU model, are also available. Additionally, the gem5 driven mode allows using Ramulator as a module of the gem5 simulator. Thus, gem5 simulates the complete computer architecture but the main memory, i.e., the DRAM controllers and DRAM memories, which Ramulator simulates. For that, Ramulator includes a gem5 wrapper module that links both simulators. Ramulator receives the memory requests from gem5, simulates main memory responses, and sends them back to gem5. This cosimulation of gem5 and Ramulator allows a cycle-accurate simulation of a multicore system including the main memory.

# III

### **Related Work**

Computer architecture simulators have become an essential tool for architecture researchers [6, 7, 8, 9]. They are used to evaluate new architecture ideas and avoid long and expensive manufacturing processes. That way, their reliability is essential for the community. Indeed, we need to guarantee the relevance of our results. Some work already points out that inappropriate use of those simulators may lead to misleading conclusions [11, 6, 52]. Thus, this chapter provides an overview of related work on simulator error sources and mitigation approaches.

#### 3.1 Sources of Error in Simulator Baselines

As discussed in Section 2.3, we use simulators to evaluate novel architectures against a state-of-the-art baseline model. This baseline must represent a real state-of-the-art architecture called the *target* architecture. Thus for a workload, the simulation error is the difference in the metric of interest (e.g., workload execution time) between the execution on the target architecture and the simulation model. There are two sources of error in computer simulations: modeling and parametrization errors.

Computer architecture simulators provide many parameters to configure the simulation model properly. Thus, we tune the simulator parameters to get a model closest to the target architecture. For instance, we set up parameters such as the associativity or size of the L1 data cache. However, due to the lack of information about commercial architectures [7], the simulator may not be appropriately tuned. Consequently, while comparing results from the target architecture and the simulation model, part of the error comes from the fact that the simulator is configured with the wrong parameters. Note that the same simulator can have be more accurate with an adequate parameter configuration. We define this component of the total simulation error as parametrization error.

We define modeling error as the remaining error after removing the parametrization error with an adequate configuration. The modeling error comes from the simulator model accuracy, independently of the parameters. For instance, a simulator can abstract away processes happening in the real architectures, such as main memory bank conflicts (see Section 2.2.3). Thus, even with all the necessary technical information, i.e., removing the parametrization error, it would not be possible to faithfully represent the real target main memory. In this case, we can only reduce the error by extending the simulator with more detailed models (e.g., adding a component that models bank conflicts).

Interestingly, some of the available simulators, such as gem5 and Ramulator, already include very complete and detailed parametric models to cover a wide spectrum of architectures. Hence, in this thesis, we focus on reducing the parametric error as a first necessary step to achieve accurate simulations.

#### 3.2 Simulator Verification

In order to verify the accuracy of simulators, several works evaluate the simulation errors against target architectures [53, 54, 55, 56, 30]. They configure the simulators to get a representative simulation model of the target architecture, i.e., reduce the parametrization error. Then, they use realistic benchmark suites such as SPEC CPU2006 [57] or PARSEC [58] to execute on the target architectures and calibrated simulation model. Different metrics are used to compare the execution and simulation results. Assuming that the simulation model is ideally calibrated, only the modeling error remains. If this one is low enough, the simulator is verified.

## 3.2.1 gem5 Verification

Previous works propose a verification of the gem5 simulator [10]. Endo et al. [12] uses as target architecture the in-order Cortex-A8 [59] and the Out-of-order Cortex-A9 [60]. They compare the execution time of benchmarks from the PARSEC suite against execution on the real target architecture (between 7% and 17% error). Butko et al. [13] use the same target, i.e., the Cortex-A9, but also the Cortex-A7 [61] and the Cortex-A15 [62] present in the ARM big.LITTLE [23] architectures [63]. They measure a mismatch between 1.4% and 17.9% with different benchmarks. In the same way, Gutierrez et al. [14] use the same ARM target architectures but include an OS in the simulation. In order to reduce the error, they disable on both the target and the simulation some components that are not appropriately modeled (e.g., the data prefecher). They finally get an error between 5% and 17% depending on the benchmarks. Akram et al. propose a verification of an X86 architecture [64]. They use the *perf* tool [65] to monitor the target architecture behavior and faithfully configure the simulator (136% remaining error). Then, they reduce the modeling error by modifying the simulator code. For instance, they remap some micro-operations to other functional units. Like that, they reduce the error from 136% to 6%.

#### 3.2.2 X86 Simulator Error Comparison

Akram et al. [8] instead of validating simulators, provide a cross-comparison of multiple simulators: gem5 [10], Multi2sim [45], MARSS×86 [42], PTLsim [66], Sniper [41], and ZSim [43]. After detailing simulator features, they select four of them for a detailed study. They first calibrate them with the same target, Intel's Haswell architecture (core i7-4770). Then, they compare the execution and simulation of SPEC CPU2006 [57] and MiBench [67] realistic benchmark suites. The results show an error of 9.5%, 38.2%, 44.6%, and 47.6% for respectively Sniper [41], PTLsim [66], gem5 [10], and Multi2sim [45]. They use *PAPI* [68] to monitor internal target metrics such as the number of L1 data cache misses and compare them to the simulator results. That way, they expose which parts of the simulators need to be improved, e.g., the branch predictor model. Finally, they conclude that the accuracy of the simulators can significantly change depending on the target architecture. Thus, a verification with one target cannot prove the full simulator's accuracy.

#### 3.3 Dedicated Simulators

The architecture coverage of a simulator defines the range of architecture simulations it can perform. Ideally, a simulator must have the most extensive architecture coverage. However, significant coverage results in a complex parametrizable simulator and very long simulation times. Thus, simulators can limit their coverage to provide accurate simulations while having reasonable simulation times and simulator parametrizable complexity. In this case, we call them dedicated simulators.

The architecture coverage can be described using three dimensions:

- Architecture component. It corresponds to elements of the architecture that the simulator models. For instance, the simulator can model the whole architecture of just one component, such as the main memory.

- Architecture variance. It describes the variations of the same component that the simulator can model. For instance, a CPU can have an x86, RISC-V, alpha, or ARM architecture.

- Simulation metric. It represents the different metrics measured during the simulation. For instance, simulators only measure performance metrics such as IPC while others focus also on energy metrics.

Thus, dedicated simulators limit their architecture coverage. That way, more effort is spent modeling specific parts or features characteristic of the dedicated architectures. Also, as the choice of target architectures is limited, the default baseline model calibration is more likely to fit another target architecture instance that belongs to that restricted domain. Hence, this allows reducing the parametrization error.

#### 3.3.1 Component-Specific Simulators

The first example of component-specific simulators is the GPU simulators [69, 70, 71, 72, 73, 74, 75, 76, 77, 78, 79, 80, 81]. They limit the simulation to one part of the architecture, the GPU, which already includes many processing units and memories. Some simulators, such as ATTILA [76], are very modular, providing a high architecture variance and simulation output. Others like [73, 74, 75], focus on energy consumption. Thus, PowerRed [74] provides details GPU power simulations, including an interconnect power modeling.

Another kind of component-specific simulator focus on memory parts of the architecture [30, 82, 48, 47, 83, 84, 85, 86, 87, 51, 49, 50, 88, 89]. Those simulators allow detailed simulations of the multiple memory components. For instance, Tavakkol et al. propose MQsim [82], an SSD simulator, which they evaluate against four real SSDs (less than 18% error). Kim et al. propose Ramulator [30], which provides highly accurate DRAM models. They verify it by comparing it against RTL simulations of DDR3 commercial Verilog models. Then, they show that it performs 2.5x/3.0x speedup compared to the next fastest simulator [51].

Additionally, we give more examples of component-specific simulators. For instance, accelerator simulator [90, 91, 92], e.g., deep neural network simulations. Or, Network-on-Chip (NoC) simulators [93, 44, 94, 95, 96].

## 3.3.2 ISA-Specific Simulators

Some simulators limit their architecture coverage by fixing the Instruction-Set Architecture (ISA). For instance, x86 architecture simulators [66, 42, 41]. By limiting the ISA, more effort is spent on a dedicated architecture providing better accuracy reducing modeling error. Also, as the choice of target architectures is limited, the default baseline model calibration is more likely to fit another target architecture that belongs to the simulator architecture coverage. Thus the Sniper simulator [41], which is an x86 architecture simulator, provides better accuracy than the modular gem5 simulator on

this particular architecture, as illustrated in Section 3.2.2. In the same way, Bruschi et al. introduce GVSoC [97] dedicated event-driven simulator for RISC-V architectures which is 15% more accurate than gem5.

#### 3.3.3 Metric-Specific Simulators

Dedicated simulators can also limit the architecture coverage by focusing on specific simulation output, such as power consumption. [98, 99, 100, 101, 102, 103] Power consumption is a crucial element of modern architecture. Thus, simulators such as McPAT [98] or eSimu [100] are used to precisely estimate the power consumption of computer architectures. Those simulators also need to be calibrated with target architectures. Thus, Lee et al. propose PowerTrain [101] a McPAT calibration against an ARM Cortex-A15 present in a Samsung SoC, the Exynos 5422. Finally, simulators can be dedicated to other metric such as the system security. Forcioli et al. present a framework based on gem5 to evaluate system security at the architecture level [104].

## 3.4 Simulation Time Mitigation Techniques

The simulation time remains a problem in computer architecture simulation. Thus, this section introduces an overview of some mitigation techniques used to reduce the simulation time. Research still needs to evaluate the necessary accuracy not to simulate unnecessary processes that may slow down the simulation time.

## 3.4.1 Workload Sampling

A fundamental problem with computer architecture simulation is that it is difficult to parallelize in host machines. Indeed, the simulation respects time order execution and intricate dependencies between components. One solution is to sample the simulation, e.g., using a checkpointing method [105], and run the samples in parallel [106]. In order to reduce the noise caused by cold starts, a warmup is added to each sample. Additionally, due to redundant sample behaviors, works [107, 108] propose to select a subset of the samples that already significantly represents the benchmark behavior. For instance, the SimPoint method [108] proposes to use the K-means algorithm and Basic Block Vectors (BBV) to analyze samples and select this kind of subset. The evaluation of the SimPoint methodology shows an extra error of 3%.

#### 3.4.2 Trace-driven Simulator

Another common way to mitigate simulation time is to use traces as input for the simulators, i.e., trace-driven simulators. The traces are prerecorded fixed inputs. For instance, traces can be recorded from memory request addresses. Then, memory trace-driven simulators can directly replay the traces without simulating processing units [30, 82, 48, 47]. Some traces can be more sophisticated and include dependencies such as the elastic traces [109, 110, 111] reproducing an out-of-order CPU execution. However, trace inputs are still different from realistic execution, which includes many dependencies in the program execution flow.

#### 3.4.3 FPGA-Accelerated Simulation

Field-Programmable Gate Array (FPGA) allows fast evaluation of new designs. Thus, several works propose to use them to accelerate the simulation of architecture parts [112, 96, 93, 113, 114, 115, 116, 117]. For instance, Papamichael et al, propose FIST [93] which uses FPGA to emulate NoC designs. That way, they reduce the simulation by 3 to 4 orders of magnitude speedup against software-based NoC simulators. Similarly, simulators propose to simulate complete multicore architecture such as ProtoFlex [114] which achieves an average speedup of 38x compared to Simics [46] software-based simulator. Despite their promising accelerations, FPGA-accelerated simulators have only been successfully employed by those who designed them. They lack the user-friendliness of software simulators. Most previous works focused on efficiently mapping more of the target to a single FPGA. Unfortunately, the resulting multithreaded models became more challenging to implement than the architectures they model, significantly undermining their usability. Some FPGA-based simulators like FireSim [112] mitigate this problem by running full-system simulations on could FPGAs, providing a more user-friendly interface equivalent to software-base simulators.

## 3.4.4 High-Level Simulation

Multiple levels of abstraction exist [118] to model computer architectures. The first is the digital abstraction that interprets the analog signals as digital. The next one is the cycle of abstraction. In this case, the time is no longer continuous but counted using clock cycles. This abstraction is mainly in the computer architecture domain with cycle-accurate simulators, e.g., the gem5 simulator [10] or Ramulator [30]. The

last example of a simulation time mitigation technique is to use a higher abstraction in architecture models [55, 119, 120]. For instance, Genbrugge et al. propose interval simulations [119] instead of cycle-accurate simulations. Analytic models describe intervals between architecture events, such as branch prediction misses or cache misses. By increasing the level of abstraction, they reduce both the development time and the simulation time. Thus, they show a reduction of the simulation time of one order of magnitude for an average extra simulation error of 4.6%. In the same way, many simulators [10, 41, 120, 109] propose different levels of accuracy depending on the experiment's focus to reduce the simulation time. For instance, the gem5 simulator provides multiple in-order CPU models, from the SimpleCPU model, a purely functional in-order CPU model, to the very accurate HPI model described in section 2.3.

## 3.5 Remaining Challenges

This chapter illustrates that simulators are widely used in the architecture research community. Due to the remaining tradeoff between accuracy and simulation time, simulators offer various modeling approaches, e.g., dedicated simulators or simulation time mitigation techniques. Some of the approaches can mitigate the modeling error or, conversely, increase it while reducing the simulation time. Thus, they provide different points on the accuracy versus simulation time Pareto. However, the parametrization error is common to all those simulators and needs to be mitigated following calibration methodologies.

Previous works provide calibrate methods to reduce parametrization error to measure the modeling error against real state-of-the-art architectures. However, those calibrations follow empirical methods, which cover a few targets of the whole simulator architecture coverage and cannot be generalized to others. Moreover, the continuing advancement of state-of-the-art commercial architectures pushes extending the architecture coverage of the simulators, making previous empirical calibration methods outdated.

One presumption with evaluation using computer simulations is that simulators do not need precise calibrations against target architectures as long as the simulation baseline trend is realistic. For instance, multiple memory exploration works [121, 122, 123, 124, 125, 126, 127, 128, 129, 130, 131, 132, 133, 134, 135, 5, 4] use simulators with non-calibrated baseline models to evaluate new memory designs. However, as pointed out by some works [11, 6, 7], this may lead to misleading conclusions, making the simulator calibration a key element of the evaluation.

3.6. *Summary* 27

Consequently, the calibration of the computer architecture simulators remains an important challenge for the community. It remains essential from the verification of simulators to their utilization during new design evaluations. Thus, this thesis proposes a systematic methodology to calibrate computer architecture simulators.

A critical limitation of architecture simulator calibration is the lake of technical information about commercial architectures. Several works [136, 56, 14, 7, 137] propose to use hardware performance monitoring on the target architecture to extract missing technical information necessary for the baseline model calibration. Alves et al. propose dedicated microbenchmarks to evaluate and calibrate specific parts of the SiN-UCA simulator [56]. Other works [138, 139, 140, 140, 139, 138] related to security vulnerabilities propose to use microbenchmarks to discover hidden technical information to exploit the target vulnerability. However, all the proposed methods remain empiric and cannot easily be extended to other architectures. Open-source generic microbenchmarks have been developed to extract technical information from commercial architectures, such as LMbench suite [141] or STREAM [142]. However, they are not part of a complete methodology allowing a direct simulator calibration.

Instead, our methodology describes a complete workflow, including simulator parameters analysis and the detailed design of microbenchmarks used to reveal missing technical information from the target architecture.

## 3.6 Summary

To summarize, this chapter introduces several simulators and how they are verified. Thus, the popular gem5 [10] simulator shows such an average simulation error against ARM commercial architecture under 20%. However, comparison [8] between several simulators [10, 45, 42, 66, 41, 43] shows that the simulation error depends on the targe architecture. In this case, an x86 architecture. Thus, the Sniper simulator [41] shows an average simulation of 9.5%, contrary to the gem5 simulator with 44.6%.

We further see different kinds of simulators. The component-specific simulators allow faster simulation abstraction parts of the architecture. For instance, Ramulator [30] allows faster accurate memory simulation (2.5x/3.0x speedup compared to the next fastest simulator [51]) by abstracting the CPU with memory traces. ISA-specific simulators allow more accurate simulations, as illustrated in the previous paragraph with Sniper [41]. Finally, metric-specific simulators increase simulation accuracy by targeting specific output metrics.

As the simulation time remains an important limitation for simulators, this chapter introduces simulation time mitigation techniques. Thus, workload sampling with the SimPoint method [108] allows a reduction in simulation time and parallelizes it for an average extra error of 3%. Trace-driven simulator abstract processing units by pre-recorded trace files, e.g., illustrated in the previous paragraph with Ramulator. FPGA-accelerated simulations offer good perspectives but are still not modular enough to be widely used. Finally, high-level simulations use higher abstraction-level models to reduce the simulation time. Thus, interval simulations provide speedup the simulation by one order of magnitude for only an average extra error of 4.6%.

As a result, we see that simulator calibration remains a significant problem for all kinds of simulators. The calibration approaches proposed in previous works follow an ad hoc method making them not extendable to other architectures. Hence, this thesis contributes by proposing a systematic calibration methodology.

## IV

# Microbenchmark-Based Timing Calibration Methodology

In this chapter, we propose a methodology to calibrate the memory system of a computer architecture simulation. The methodology is composed of two phases. The first phase consists of determining the different simulator parameters in need of calibration. In the second phase, we then properly calibrate those parameters. To this end, we start by using information from first-party documentation. Then, we design handcrafted microbenchmarks and use hardware performance counters to extract the missing parameter values from the real target state-of-the-art commercial platform.

#### 4.1 Motivation

Computer system simulators [10, 42, 82, 30, 41, 43, 45, 47] are widely used by researchers. They allow quick evaluations of new ideas avoiding long expensive manufacturing processes. Those new ideas are evaluated with respect to state-of-the-art baseline architectures. The choice of a baseline depends on the kind of architecture we target, e.g., low-power mobile architecture or high-performance server architecture. The relevance of the simulated results is directly related to the quality and the choice of that baseline. The use of inaccurate baselines can add unbounded noise to the experimental methodology and lead to erroneous conclusions. Unfortunately, simulation models calibrated with real architectures are rarely available to the research community.

## 4.1.1 Memory System Modeling

The memory system plays a key role in all instruction-processor based compute platforms [1]. A slow data access time directly impacts the instruction execution flow and reduces the whole system performance. This statement is even more true with modern partly heterogeneous multicore architectures which contain many components like cores, GPUs or programmable accelerators that compute data at Gigahertz frequencies. Thus, the data movement in the multiple levels of the memory hierarchy needs to be fast with low access time but also to provide high bandwidth.

Improving the memory system is not an easy task to do due to its high complexity, which includes different components, memory technologies, organizations and access protocols. For example, some new emerging non-volatile memory technologies seem a promising alternative to reduce memory system leakage energy, providing the same or better level of performance [2, 143, 3]. However, those technologies have different technical specifications than the usual memory technologies implemented. This means that

a straightforward replacement is not efficient [144, 145, 146]. Hence, researchers need a complete understanding of all the processes/sub-processes running internally in the memory system. Faithful reference models incorporating all the workload-dependent effects are important for relevant improvement/optimization of the memory system.

#### 4.1.2 Running Example

To illustrate our methodology's different elements, features, and processes, we use a simple running example. We consider a very simple fictional simulator that models the interconnect, DRAM controller, and the main memory as a fixed latency. We use the Broadcom BCM2837B0 SoC present on the Raspberry Pi 3B+ development board [147] as the reference state-of-the-art architecture. This architecture comprises four Cortex-A53 with four individual L1 data caches and one shared L2 cache.

The objective of our methodology is to find the best instantiation of the simulation parameters (e.g., the fixed latency) to produce a calibrated simulation (i.e., a simulation that behaves as close as possible to the reference architecture). Obviously, the quality of the resulting simulation is limited by the level of detail in the simulation model. Nevertheless, our objective is not to question the simulation model but to find the best possible instantiation of its parameters.

## 4.2 Simulator Parameters Identification

In this section, we describe the first phase of the methodology. The purpose of this one is to identify the simulator parameters that we need to calibrate. This process can be very different depending on the kind of simulator we use in the instantiation. The simulator can either model a single memory component (e.g., Ramulator [30]) or a complete architecture (e.g., gem5 [10]). Also, they can be modifiable, modular, or configurable by the user. Even with the same kind of simulator, the parameters may change accordingly to the modeling approach implemented in the simulator. For instance, two different simulators could have different parameters for modeling the same component. Also, due to the complexity of modeling all the processes of real architecture, some processes are modeled in a simpler way or are not modeled at all. The parameters of these simpler models cannot directly be related to a specific architecture feature. For example, we can model the main memory as a simple component with fixed bandwidth and latency. However, as we describe in Section 2.2.3, the main memory is a complex component, including many processes, such as bank conflicts and a

complex scheduling protocol. In this case, a fixed latency has no realistic meaning, but its value may be extrapolated to best match reality.

Frequently, simulators provide different models with different levels of accuracy for the same component. As the trade-off between simulation time and accuracy remains, researchers must properly choose the right ratio to get relevant results with a reasonable simulation time. From the previous example, in case of very low main memory activity during the simulation (e.g., simulating only one core executing a cache-friendly application), using a very accurate main memory model is not relevant. Hence, it does not make sense to needlessly extend the simulation time due to the very low impact of the main memory on key simulation metrics. This example is further detailed in Section 5.4.2.

#### 4.2.1 Generic Parameter Template

To provide flexibility and a high degree of accuracy, simulators have become complex, including hundreds of parameters. Thus, we need to identify the main parameters and understand how they define the behavior of the simulated memory system. For that, we determine the path that a memory request follows inside the simulator memory system from the execution of a memory instruction to the last level of the memory hierarchy.