## Deep Learning Process Integration on Heterogeneous GPU/FPGA Embedded Platforms

Walther Carballo Hernandez

## ▶ To cite this version:

Walther Carballo Hernandez. Deep Learning Process Integration on Heterogeneous GPU/FPGA Embedded Platforms. Embedded Systems. Université Clermont Auvergne, 2022. English. NNT: 2022UCFAC087. tel-04109891

## HAL Id: tel-04109891 https://theses.hal.science/tel-04109891v1

Submitted on 30 May 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

DOCTORAL THESIS

## Deep Learning Process Integration on Heterogeneous GPU/FPGA Embedded Platforms

*Author:* Walther CARBALLO-HERNÁNDEZ *Supervisor:* Prof. François BERRY Prof. Maxime PELCAT

*Reviewers:* Prof. Philippe COUSSY Prof. Alfredo GARDEL VICENTE *Examiners:* Prof. Miguel Octavio ARIAS ESTRADA Prof. Ricardo CARMONA GALÁN Prof. Patrick GIRARD Prof. Paula LÓPEZ MARTÍNEZ

*Defended in public on* November 18, 2022

*A thesis submitted in fulfillment of the requirements for the degree of Docteur de l'Université Clermont Auvergne*

at the

DREAM - Image, Systèmes de Percéption et Robotique (ISPR) Institut Pascal

Numéro National de Thèse (NNT) : 2022UCFAXXXX

### UNIVERSITÉ CLERMONT AUVERGNE Ecole Doctorale des Sciences Pour l'Ingénieur Institut Pascal

## Abstract

#### Deep Learning Process Integration on Heterogeneous GPU/FPGA Embedded Platforms

by Walther CARBALLO-HERNÁNDEZ

Deep Learning (DL) algorithm deployment on *edge devices*, such as Convolutional Neural Network (CNN) inference, has established a high computing demand on devices with limited resources, requiring low execution time and reduced energy consumption. To meet the requirements with such constraints, hardware systems have adopted unconventional processors co-located on the same platform. This architectural *heterogeneity* introduces many challenges in how these processors interact. A well-defined software-hardware co-design environment must be carefully built to ensure a high-performance solution. For this purpose, heterogeneous hardware-awareness must be integrated in the design workflow.

To avoid hardware-agnostic low performance programming, state-of-the-art literature incorporates performance profiling models to aid with partition selection on each accelerator. Subsequently, mathematical optimization techniques benefit from these models to improve workload distribution, specifically tailored for the platform.

This thesis aims to assist the designer by studying the *modeling*, *partitioning* and *optimization* of embedded heterogeneous platforms in the context of CNN computation models. The scope of this dissertation mainly covers the coupling topologies between Graphics Processing Unit (GPU) and Field Programmable Gate Array (FPGA) accelerators in hybrid systems. The opportunities and limitations of hybrid programmable logic and Single-Instruction Multiple-Data (SIMD) architectures are analyzed and discussed.

Keywords: Heterogeneous computing, Embedded design, CNN, GPU, FPGA

### UNIVERSITÉ CLERMONT AUVERGNE Ecole Doctorale des Sciences Pour l'Ingénieur Institut Pascal

## Résumé

#### Intégration des Processus d'Apprentissage Profond sur des Plateformes Hétérogènes Embarquées GPU/FPGA

par Walther CARBALLO-HERNÁNDEZ

Le déploiement d'algorithmes tel que l'inférence de réseaux de neurones convolutifs, impose des temps d'exécution courts et une consommation électrique maîtrisée sur des systèmes embarqués disposant de ressources de calculs limitées. De nouvelles électroniques spécifiques composées de différentes architectures matérielles ont émergé pour répondre à ce type de demande. Ce type d'architecture *hétérogène* impose de nouveaux défis notamment au niveau de l'interaction entre les différentes composantes. Il est alors nécessaire de passer par une étape de co-design matérielle/logicielle décrivant au mieux la plateforme électronique afin d'atteindre un optimum en termes de consommation, latence et vitesse d'exécution.

Pour éviter une conception agnostique du matériel, la littérature de l'état de l'art incorpore des modèles en profilant la performance. Celle-ci, dans l'intention d'aider avec la sélection des partitions sur chaque accélérateur. En suite, des techniques d'optimisation mathématique profitent de ces résultats pour améliorer encore la distribution des tâches de travail spécifiquement adaptées à la plateforme.

Cette thèse cible d'assister le développeur en étudiant le *modelage, partitionnement* et *optimisation* pour les plateformes embarquées hétérogènes dans le contexte des modèles de calcul des CNNs. Le cadre de ce manuscrit couvre principalement des topologies en couplant des accélérateurs GPU et FPGA dans des systèmes hybrides. En se concentrant de cette manière, sur les opportunités et limitations de l'intégration d'architecturelle : logique programmable customisable et SIMD.

Mot clés: Calcul hétérogène, Conception embarquée, Réseau de neurones convolutif, GPU, FPGA

To my parents, my sisters, my brother and all my family

## Acknowledgements

I would like to express my deepest gratitude to my supervisors: Prof. François Berry and Prof. Maxime Pelcat. Without your guidance and expertise this endeavor would not have been possible. Additionally, I will always be extremely grateful for the funding from the European Commission's Marie Skłodowska-Curie Actions and for this international opportunity. My appreciation also goes out to Prof. Ricardo Carmona Galán and the colleagues from the ACHIEVE ITN 2020 consortium who professionally shaped my career.

My recognition extends to the committee members for actively participating in my project and proof-reading my dissertation: to my reviewers Prof. Philippe Coussy and Prof. Alfredo Gardel Vicente and my examiners Prof. Patrick Girard and Prof. Paula López Martínez. I am also indebted with Prof. Miguel Octavio Arias Estrada for his encouragement and motivation in the early steps of my doctoral thesis, being such a model of excellence in research and an integral human being. Thanks also go out to Prof. Shuvra Shikhar Bhattacharyya for your collaboration on the first chapter and academic article of this manuscript.

I would also like to thank my lab friends and work colleagues from DREAM Team and the Institut Pascal: Kamel, Ny Ando, Lobna, Juan, Abiel, Seyfedinne, Anas and Ivan Luca. Special thanks to PhD. Luca Maggiani and PhD. Federico Civerchia from Sma-Rty for leading and helping me during my secondment in Italy. I would like to particularly thank PhD. Jonathan Bonnard, without your help the design of the smart camera (X-MERA) would have simply not seen the light of existence. Thanks for your invaluable encouragement and wise advice. Thank you all for being there and tolerating me in *that* difficult period of time during the development of my thesis.

Most importantly, my family deserves my endless gratitude. My mother, whose eyes closed one last time before the beginning of this project, but who has always being as present as the day I opened mine for the very first time. My father, who has always been my biggest supporter, constantly encouraging me to give the best of me through the wisdom of his words and his advice. To my sisters, Pamela and Yamile, for affectively reminding me how amazing I am, specially when my self doubts clouded my judgement. My brother Carlos, who backed me up on each decision in my life and being there during difficult times. To the friends that I have met on the way around the world these last years. For all these wholesome moments of success with my family and friends, from the deepest and truthful part of my heart, thank you.

## Contents

| 1 | Intr | oduction                                                                    | 1  |

|---|------|-----------------------------------------------------------------------------|----|

|   | 1.1  | Heterogeneous computing                                                     | 1  |

|   | 1.2  | Challenges and problem definition                                           | 4  |

|   | 1.3  | Contributions                                                               | 7  |

|   | 1.4  | Manuscript outline                                                          | 7  |

|   | 1.5  | Publications                                                                | 8  |

|   | 1.6  | Submissions                                                                 | 9  |

| 2 | Flyc | leling: Performance Models for Hardware Acceleration of CNNs through SI     | 11 |

|   | 2.1  | Chapter abstract                                                            | 11 |

|   | 2.2  | Introduction                                                                | 12 |

|   | 2.3  | Related works                                                               | 13 |

|   | 2.4  | Problem definition: Applying Flydeling to CNN KPIs                          | 17 |

|   |      | 2.4.1 Flydel definition and properties                                      | 17 |

|   |      | 2.4.2 Using CNN properties as application activity                          | 19 |

|   |      | 2.4.3 Device Key Performance Indicators ( <i>KPI</i> ) models               | 20 |

|   |      | 2.4.4 Automated model selection with the competitive ensemble modeling      | 22 |

|   |      | 2.4.5 Heterogeneous model definition                                        | 25 |

|   | 2.5  | Flydeling: randomly-excited system identification applied to KPI estimation | 26 |

|   |      | 2.5.1 System identification                                                 | 29 |

|   |      | 2.5.2 Stochastic sequence excitation                                        | 30 |

|   |      | 2.5.3 Linear parametric SI                                                  | 33 |

|   |      | 2.5.4 Non-linear parametric SI                                              | 34 |

|   |      | 2.5.5 Model validation                                                      | 34 |

|   | 2.6  | Flydeling evaluation and results                                            | 35 |

|   |      | 2.6.1 Dataset generation                                                    | 35 |

|   |      | 2.6.2 Resulting experimental models and evaluation                          | 43 |

|   | 2.7  | Conclusions                                                                 | 49 |

| 3 | Het  | erogeneous Partitioning Techniques                                          | 51 |

|   | 3.1  | Chapter abstract                                                            | 51 |

|   | 3.2  | Introduction                                                                | 51 |

|   | 3.3  | CNN partitioning on GPU-FPGA platforms                                      | 53 |

|   | 3.4  | Related works                                                               | 58 |

|   | 3.5  | Problem definition: Heterogeneous partitions                                | 61 |

|   |                                                        | 3.5.1   | Mobile CNN modules: partitioning and scheduling               | 61  |  |

|---|--------------------------------------------------------|---------|---------------------------------------------------------------|-----|--|

|   |                                                        | 3.5.2   | DHM for FPGA synthesis definition                             | 64  |  |

|   |                                                        | 3.5.3   | Inter-device communication modeling                           | 65  |  |

|   |                                                        | 3.5.4   | CUDA microarchitecture comparison of current Nvidia embedded  |     |  |

|   |                                                        |         | GPUs                                                          | 66  |  |

|   | 3.6                                                    | Partiti | on experimental methodology, evaluation and results           | 67  |  |

|   |                                                        | 3.6.1   | Measurement-based performance metrics comparison              | 68  |  |

|   |                                                        | 3.6.2   | Heterogeneous partitioning results                            | 72  |  |

|   | 3.7                                                    | Conclu  | usions                                                        | 77  |  |

| 4 | CNI                                                    | N Mode  | el Partitioning Optimization                                  | 81  |  |

|   | 4.1                                                    | Chapt   | er abstract                                                   | 81  |  |

|   | 4.2                                                    | Introd  | uction                                                        | 82  |  |

|   | 4.3                                                    | Relate  | d Works                                                       | 82  |  |

|   | 4.4                                                    | Flydel  | s as monomials and posynomials formulations                   | 84  |  |

|   | 4.5                                                    | Optim   | ization Problem Formulation                                   | 85  |  |

|   |                                                        | 4.5.1   | GGP Formulation of the Heterogeneous CNN Layer Partitioning . | 85  |  |

|   |                                                        | 4.5.2   | GGP Penalization by Equality Constraints Condensation         | 86  |  |

|   | 4.6                                                    | Experi  | imental results                                               | 87  |  |

|   |                                                        | 4.6.1   | Single layer optimization                                     | 88  |  |

|   |                                                        | 4.6.2   | Full CNN model optimization                                   | 91  |  |

|   | 4.7                                                    | Conclu  | usions                                                        | 99  |  |

| 5 | Con                                                    | clusion | as and discussion                                             | 101 |  |

| A | Con                                                    | vexity, | monomials and posynomials                                     | 103 |  |

|   | A.1                                                    | Conve   | exity definition                                              | 103 |  |

|   | A.2                                                    | Conve   | exity properties                                              | 103 |  |

|   |                                                        | A.2.1   | Summation                                                     | 103 |  |

|   |                                                        | A.2.2   | Scaling                                                       | 104 |  |

|   | A.3                                                    | Posyn   | omial properties                                              | 104 |  |

|   |                                                        | A.3.1   | Summation                                                     | 105 |  |

|   |                                                        | A.3.2   | Product                                                       | 106 |  |

| B | Heterogeneous Smart Camera Architecture Conception 102 |         |                                                               |     |  |

|   | <b>B</b> .1                                            | X-ME    | RA: Co-processor Heterogeneity Integration for smart caMERAs  | 107 |  |

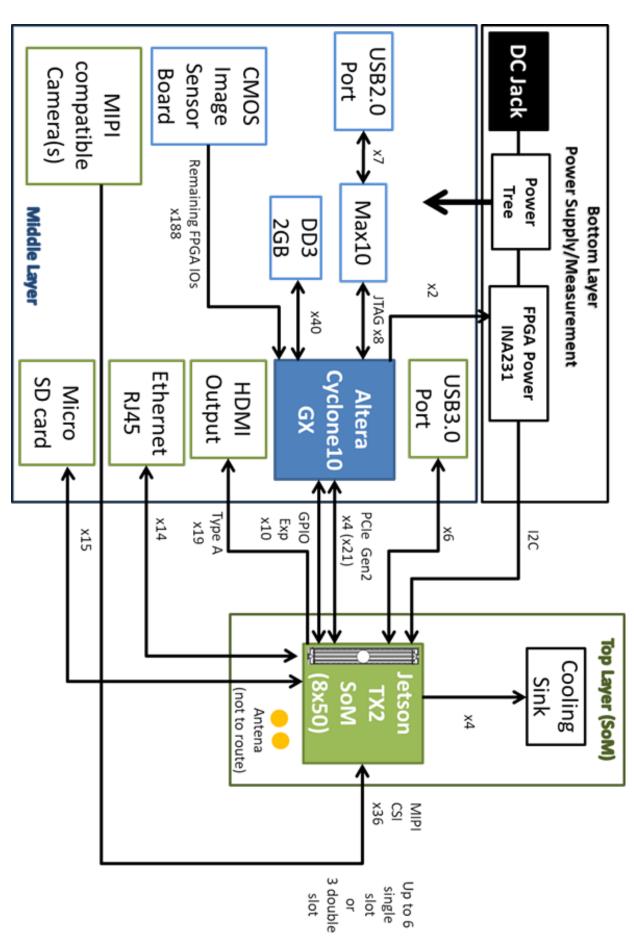

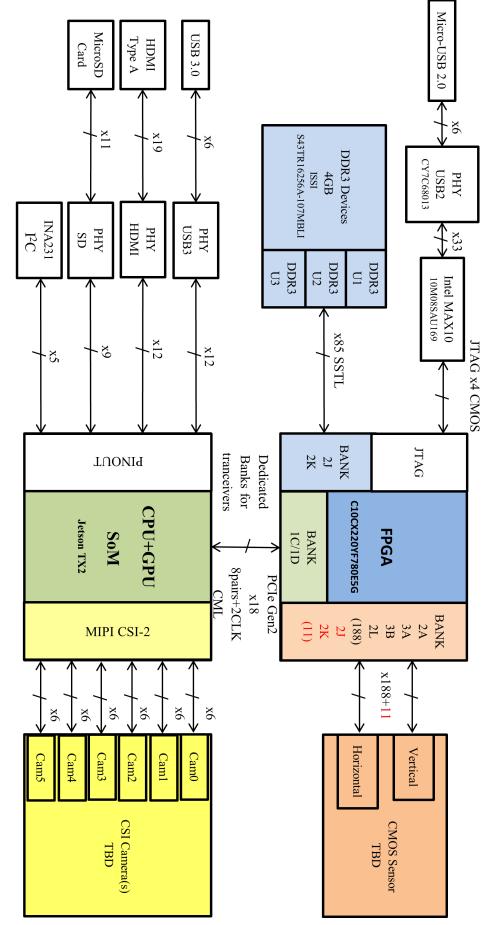

|   |                                                        | B.1.1   | Middle Board (MDB) and Bottom Board (BTB)                     | 108 |  |

|   |                                                        | B.1.2   | Power measurements and PCIe inter-device communication        | 111 |  |

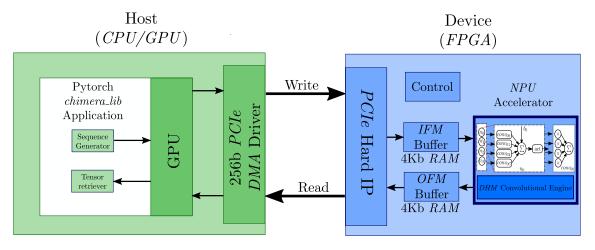

|   | B.2                                                    | Chime   | era library                                                   | 114 |  |

# **List of Figures**

| 1.1 | Generic heterogeneous architecture [Zah17].                                                           | 2  |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 1.2 | Multicore types according to [CMHM10]                                                                 | 3  |

| 1.3 | Some embedded heterogeneous platforms.                                                                | 4  |

| 1.4 | KPI modeling of a heterogeneous platform as system.                                                   | 5  |

| 1.5 | CNN model partitioning and mapping into an embedded heterogeneous                                     |    |

|     | platform with multiple accelerators.                                                                  | 6  |

| 1.6 | Thesis content development flow                                                                       | 7  |

| 2.1 | Flydel models.                                                                                        | 18 |

| 2.2 | Competitive ensemble of single-variable models as weak regressors com-                                |    |

|     | bined to build a multi-variable strong regressor for a performance model.                             | 23 |

| 2.3 | Flydeling methodology. From left to right: Stochastic sequence excitation at                          |    |

|     | data- and structure-level, KPI measurement observations and dataset gen-                              |    |

|     | eration, ensemble modeling for flydel creation and K-fold Cross-Validation.                           | 28 |

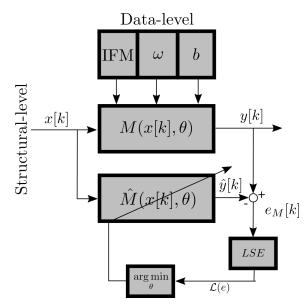

| 2.4 | General SI block diagram. <i>M</i> is the system to be identified by model $\hat{M}$ .                |    |

|     | Values of IFMs, weights ( $\omega$ ) and biases ( <i>b</i> ) are randomized at data-level.            |    |

|     | The CNN activity features $(x[k])$ are randomized at structural-level                                 | 29 |

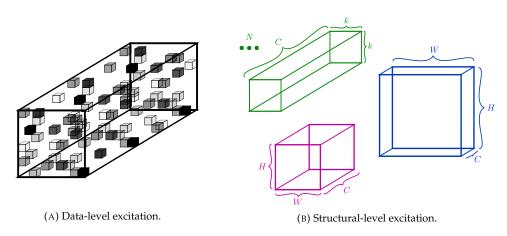

| 2.5 | Stochastic excitation abstraction levels.                                                             | 32 |

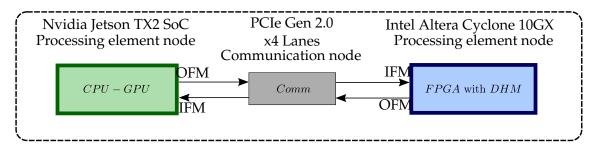

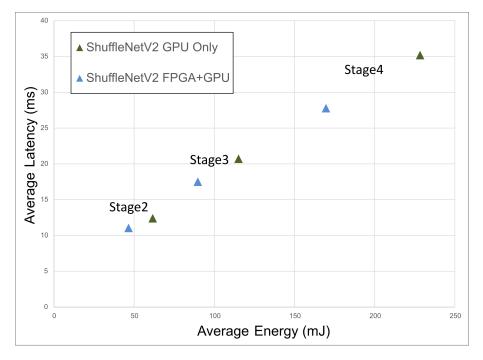

| 2.6 | Architecture model as for the heterogeneous setup with three computing                                |    |

|     | elements: A Nvidia <sup>®</sup> Jetson TX2 <sup>®</sup> CPU-GPU (green) SoC and an Intel <sup>®</sup> |    |

|     | Cyclone10GX FPGA (blue) interconnected through x4 lanes of a PCIe Gen2                                |    |

|     | link (gray). Each processing element and communication node has an IFM                                |    |

|     | and a OFM associated to it required for metric performance measuring on                               |    |

|     | each device. These measurements are used for the flydel data generation                               |    |

|     | and estimation.                                                                                       | 37 |

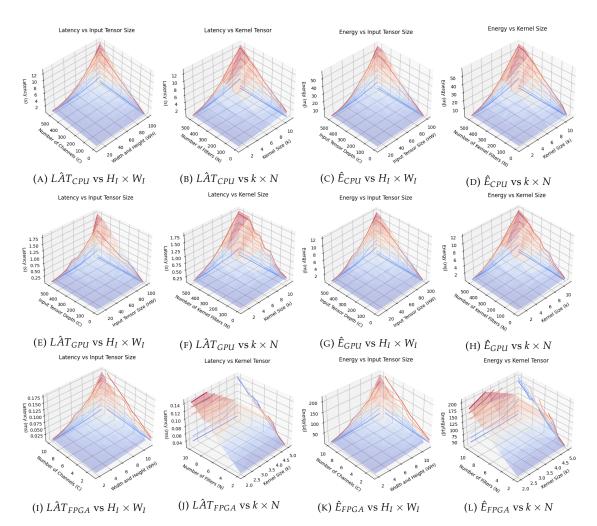

| 2.7 | Average generated subsampled dataset $\mathcal{D}$ on each embedded CPU (top                          |    |

|     | row), GPU (middle row) and FPGA (bottom row) platform by keeping                                      |    |

|     | constant $ \mathcal{X}  - 2$ features for 3D visualization. Each Subfigures row shows                 |    |

|     | latency and energy KPIs on a single device. The contour curves represent                              |    |

|     | the relation between a given KPI and a single feature variable. On Subfig-                            |    |

|     | ures 2.7a, 2.7e, 2.7c and 2.7g; features $k = 11$ and $N = 512$ are kept constant.                    |    |

|     | On Subfigures 2.7b, 2.7f, 2.7d and 2.7h; features $H_I = 100$ , $W_I = 100$ and                       |    |

|     | C = 512 are kept constant. On Subfigures 2.7i and 2.7k, features $k = 5$ and                          |    |

|     | $N = 10$ are constants. Finally, in Subfigures 2.7j and 2.7l, $H_I = 12$ , $W_I = 12$                 |    |

|     | and $C = 10$ are kept constant.                                                                       | 38 |

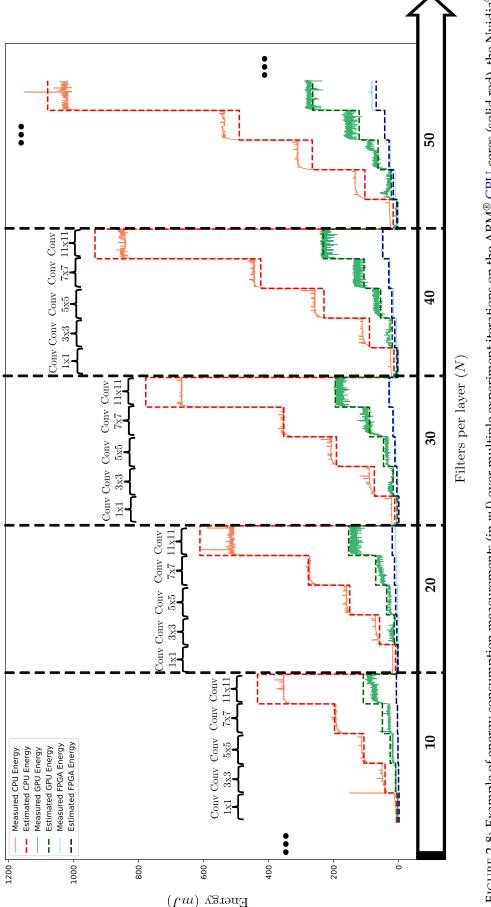

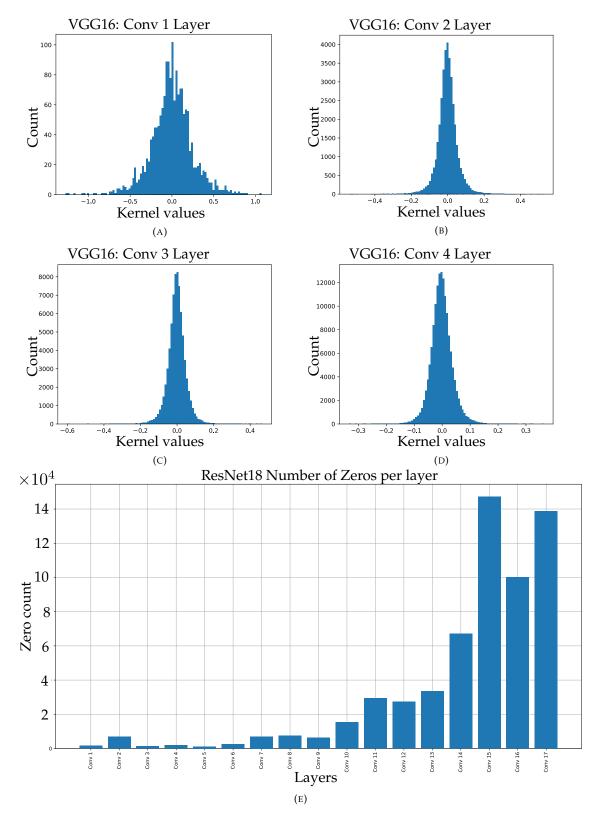

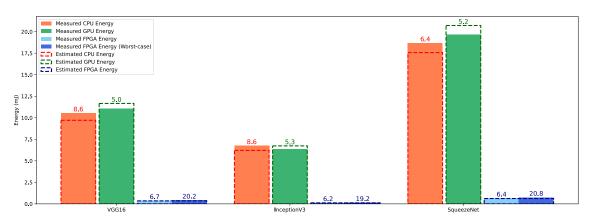

| 2.8  | Example of energy consumption measurements (in <i>mJ</i> ) over multiple experiment iterations on the ARM <sup>®</sup> CPU-cores (solid red), the Nvidia <sup>®</sup> Pascal GPU architecture (solid green) of the Jetson TX2 <sup>®</sup> SoC and the Intel <sup>®</sup> Cyclone $10GX^{®}$ (solid blue). Common convolution filter sizes are iterated 1000 times on a fixed size input tensor ( $32 \times 32 \times 3$ CIFAR-like input image for this example [Kri09]) with a random uniform distribution for the input and a normal distribution for the kernel values. Number of filters <i>N</i> increases progressively over time and the resulting observations are averaged | 41 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

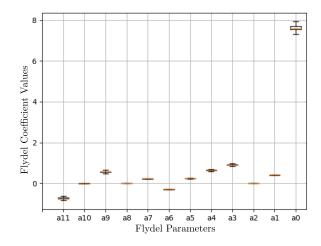

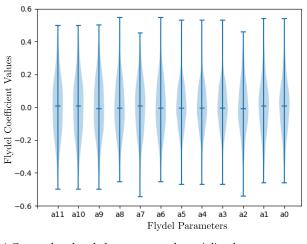

| 2.9  | Obtained parameter distribution using 50 iterations of 10-fold cross-validation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | Weight value distributions of the first four convolutional layers of VGG16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | (2.10a-2.10d). ResNet18 number of zeros per layer 2.10e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47 |

| 2.11 | Comparison of pretrained CNN models energy performance with ImageNet<br>against flydel estimation. On each KPI estimation, the percentage error is<br>shown over each bar.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48 |

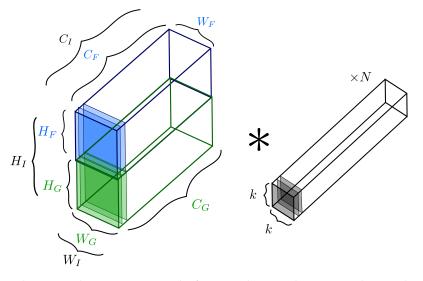

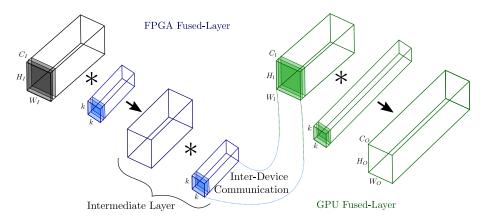

| 3.1  | Tiling on a heterogeneous platform with a single GPU and a single FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 5.1  | with configuration: $H_I = H_G + H_F$ , $W_I = W_F = W_G$ and $C_I = C_G = C_F$ .<br>The blue tensor is the IFM partition mapped on the FPGA. While the green                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | tensor is the IFM partition mapped on the GPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |

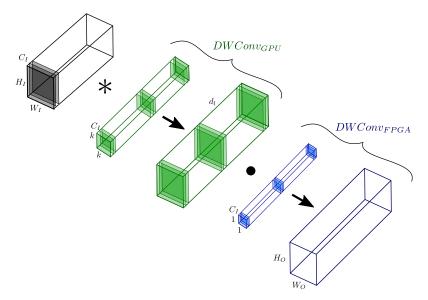

| 3.2  | Heterogeneous Depth-wise convolution example where the $k \times k$ convolu-<br>tion per input channel is executed on the GPU and the Conv1 $\times$ 1 convolu-<br>tion is done on the FPGA. The partition in blue represents the data and task                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | workload on FPGA, while in green the partition on the GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54 |

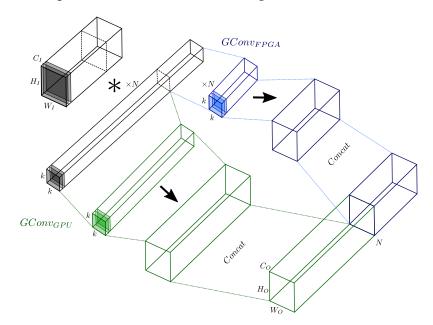

| 3.3  | Heterogeneous Grouped convolution example where the $C_I$ input channels<br>and kernel filters are contiguously and heterogeneously divided on each<br>device. Both resulting partitions are finally concatenated. The partition in<br>blue represents the data and task workload on FPGA, while in green the<br>partition on the GPU.                                                                                                                                                                                                                                                                                                                                                | 55 |

| 3.4  | Heterogeneous Fused layer example where a couple or intermediate layers<br>activity are stored in the internal FPGA RAM memory. Afterwards the<br>output tensor is transferred to the GPU for deeper layers processing. The<br>partition in blue represents the data and task workload on FPGA, while in<br>green the partition on the GPU.                                                                                                                                                                                                                                                                                                                                           | 56 |

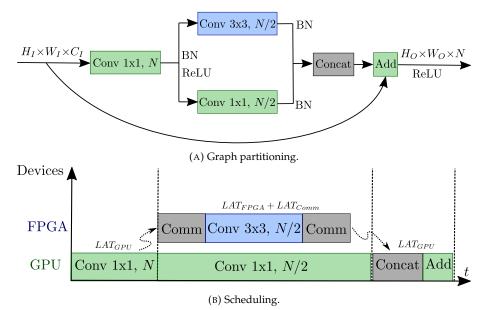

| 3.5  | SqueezeNet's Fire module (a) graph representation and (b) scheduling. The nodes from the graph in blue are scheduled on the FPGA while the ones in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

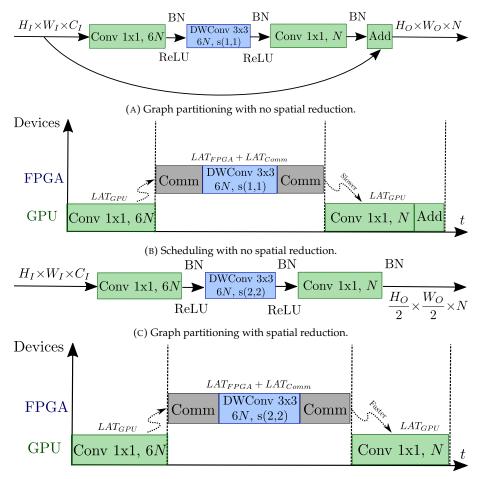

| 3.6  | green are scheduled on the GPU<br>MobileNetv2's Bottleneck module with no spatial reduction (a) graph repre-<br>sentation and (b) scheduling and with spatial reduction (c) graph represen-<br>tation and (d) scheduling. The nodes from the graph in blue are scheduled                                                                                                                                                                                                                                                                                                                                                                                                              | 62 |

|      | on the FPGA while the ones in green are scheduled on the GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

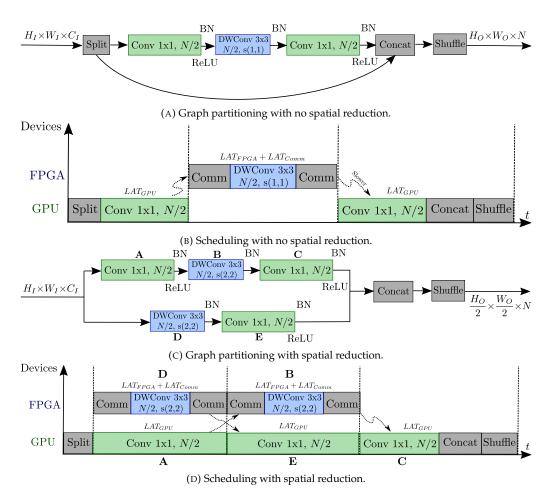

| 3.7  | ShuffleNetv2's Stage module with no spatial reduction (a) graph representa-<br>tion and (b) scheduling and with spatial reduction (c) graph representation<br>and (d) scheduling. The nodes from the graph in blue are scheduled on the                                                                                                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

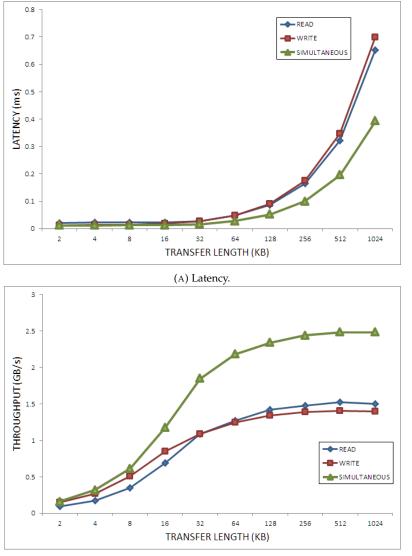

| 3.8  | <ul><li>FPGA while the ones in green are scheduled on the GPU.</li><li>(a) Latency and (b) Throughput in communication using PCIe Gen2 with x4</li><li>lanes over multiple transfer sizes for read, write and simultaneous between</li></ul>                                                                                                                                                                                                                                  | 64 |

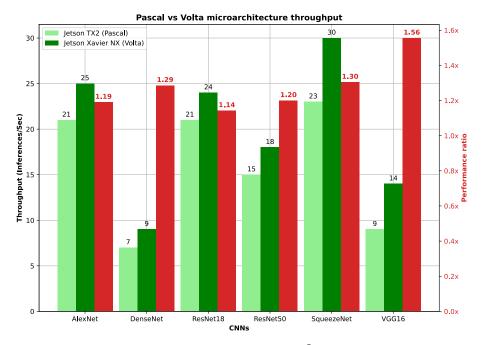

| 3.9  | the Cyclone10GX FPGA and TegraTX2 GPU                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

|      | microarchitecture against Nvidia <sup>®</sup> Jetson Xavier NX with Volta microarchi-<br>tecture over many CNNs, as discussed in [HSKR21]                                                                                                                                                                                                                                                                                                                                     | 68 |

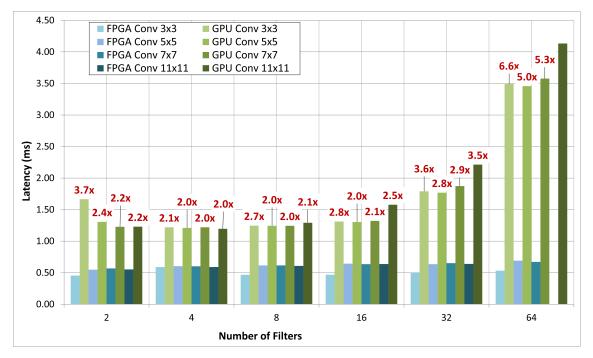

| 3.10 | Latency comparison between multiple convolution function sizes on Cy-<br>clone10GX FPGA (blue) and Jetson TX2 GPU (green) for different CNN<br>layers on an input image of $224 \times 224 \times 3$ . Blue bars represent the layers<br>implemented on the FPGA and the green bars represent the latency on the<br>GPU. Notice that the missing blue bars represent unfeasible tasks to be<br>mapped on more computational intensive task given the logic or memory          | 00 |

| _    | element constrains for the FPGA device.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

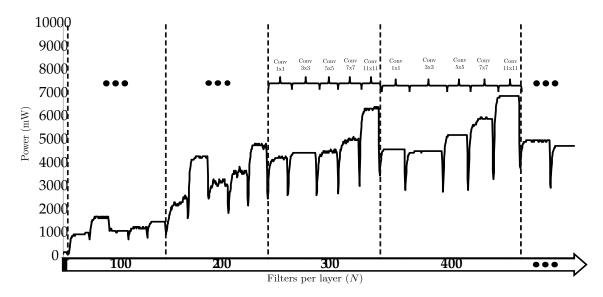

| 3.11 | Power dissipation measurement over multiple experiment iterations on<br>the Nvidia Pascal GPU architecture of the Jetson TX2 SoC. Common con-<br>volution filter sizes are iterated 5000 times on a fixed size input tensor<br>$(224 \times 224 \times N \text{ for this example})$ with a random uniform distribution for the                                                                                                                                                |    |

|      | input and the kernel values. The number of filters <i>N</i> increases progressively over time and the resulting observations are averaged.                                                                                                                                                                                                                                                                                                                                    | 70 |

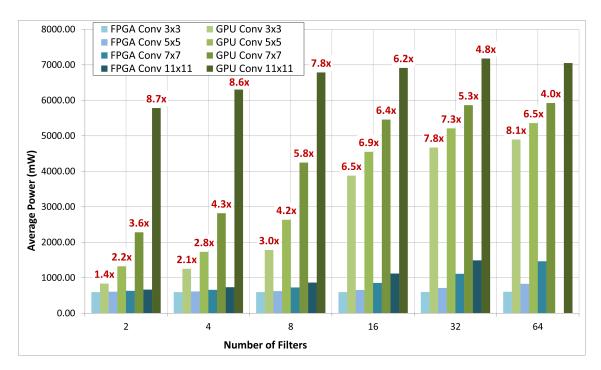

| 3.12 | Average power dissipation comparison between multiple convolution func-<br>tion sizes on Cyclone10GX FPGA (blue) and Tegra TX2 GPU (green) for<br>different CNN layers on an input image of $224 \times 224 \times 3$ . Blue bars repre-<br>sent the layers implemented on the FPGA and the green bars represent the<br>power dissipation on the GPU. Notice that the missing blue bars represent<br>unfeasible tasks to be mapped on more computational intensive task given |    |

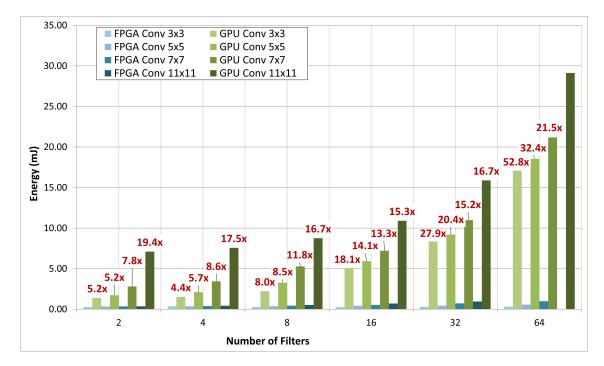

| 3.13 | the logic or memory element constrains for the FPGA device.<br>Energy comparison between multiple convolution function sizes on Cyclone10GX FPGA (blue) and Jetson TX2 GPU (green) for different CNN layers on an input image of $224 \times 224 \times 3$ . Blue bars represent the layers                                                                                                                                                                                   | 71 |

|      | implemented on the FPGA and the green bars represent the energy con-<br>sumption on the GPU. The performance factor in this measure is increased                                                                                                                                                                                                                                                                                                                              |    |

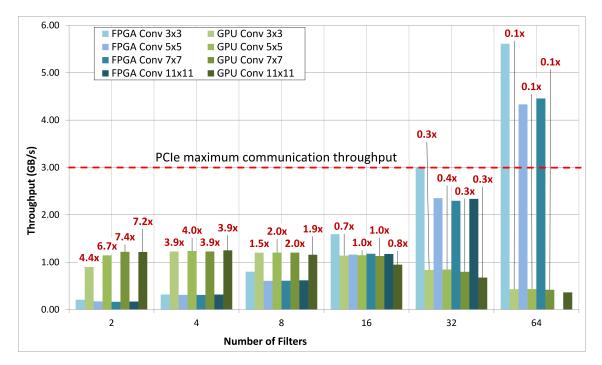

| 3.14 | result of multiplication on both power and latency metrics Throughput comparison between multiple convolution function sizes on Cyclone10GX FPGA (blue) and Jetson TX2 GPU (green) for different CNN layers on an input image of $224 \times 224 \times 3$ . Blue bars represent the layers implemented on the FPGA and the green bars represent the latency on the GPU. The red dashed line represents the maximal theoretical throughput                                    | 72 |

|      | for the PCIe communication lanes.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73 |

$\mathbf{x}\mathbf{v}$

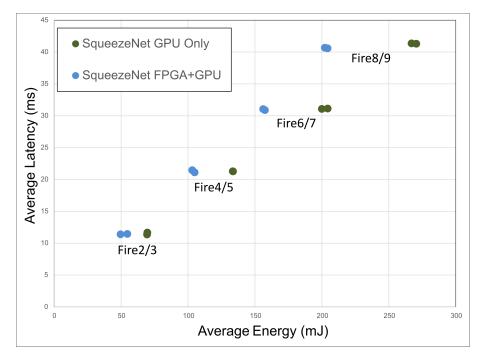

| 3.15        | Average metric performance space of the tested SqueezeNet's modules<br>with different workloads on an homogeneous GPU-only platform (green)<br>and the FPGA-GPU heterogeneous platform (blue). <i>x</i> -axis represents the                                                                                                                                                                                                                                              |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

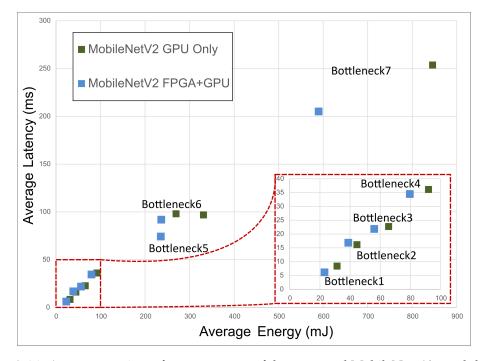

| 3.16        | average energy and <i>y</i> -axis the average latency                                                                                                                                                                                                                                                                                                                                                                                                                     | 74  |

| 3.17        | subfigure highlights the performance of the first four modules in a more detailed way                                                                                                                                                                                                                                                                                                                                                                                     | 75  |

|             | <i>x</i> -axis represents the average energy and <i>y</i> -axis the average latency                                                                                                                                                                                                                                                                                                                                                                                       | 76  |

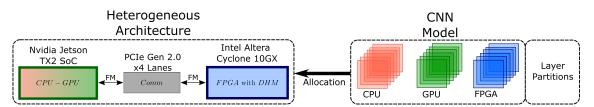

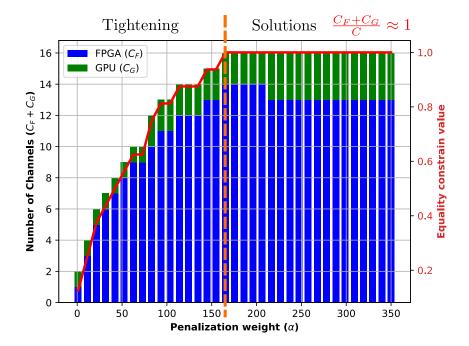

| 4.1<br>4.2  | <b>Setup 1:</b> Single layer setup of a single CNN layer allocation First iterations of a relaxed GGP sequential grouped convolution partitioning of an input tensor with 16 channels ( $C = 16$ ) with an increasing $\alpha$ . The problem is solved as a set of GP problems and he tightening only takes a few iterations (iteration 17 with $\alpha = 170$ ) to find an acceptable solution. Each step is in polynomial time and total optimisation lasts less than a | 88  |

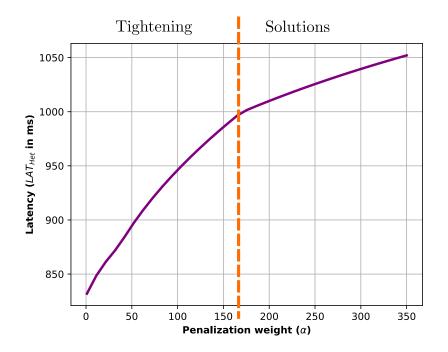

|             | couple of hundred of milliseconds.                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89  |

| 4.3         | Heterogeneous objective function per iteration (without penalization term) from problem in Equation 4.7.                                                                                                                                                                                                                                                                                                                                                                  | 90  |

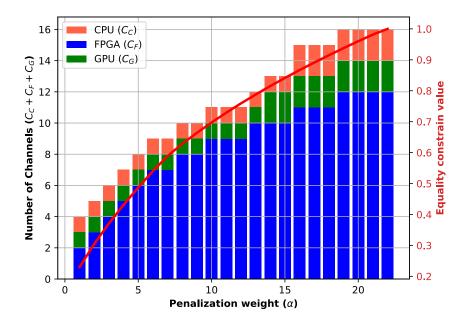

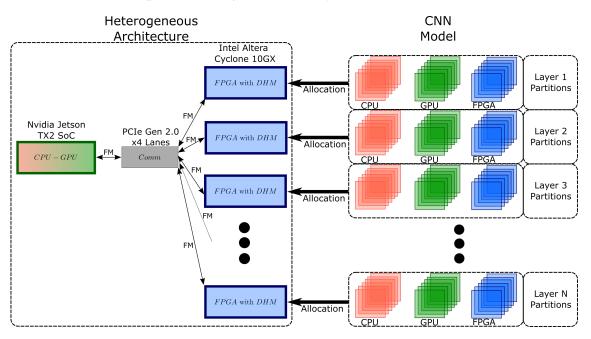

| 4.4         | Relaxed GGP sequential grouped convolution partitioning of an input tensor with 16 channels ( $C = 16$ ) with an increasing $\alpha$ over a CPU-GPU-                                                                                                                                                                                                                                                                                                                      |     |

| 4.5         | FPGA network                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |

|             | cated. The heterogeneous architecture is theoretically simulated.                                                                                                                                                                                                                                                                                                                                                                                                         | 92  |

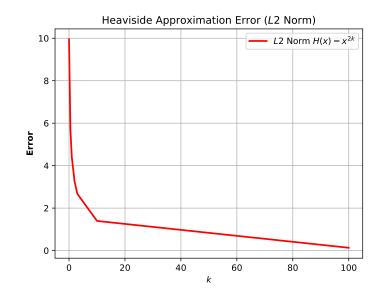

| 4.6         | Communication weight function $S(x) = x^{2k}$ for different values of $k$                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

| 4.7         | Approximation error function based on <i>L</i> 2-Norm                                                                                                                                                                                                                                                                                                                                                                                                                     | 95  |

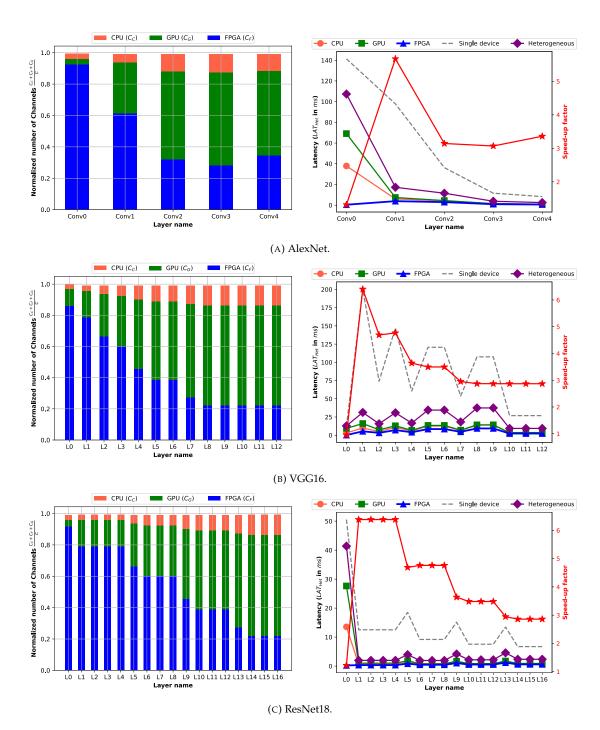

| 4.8         | Resulting GConv channel-wise optimized partitions for AlexNet 4.8a, VGG16 4.8b and ResNet 4.8c.                                                                                                                                                                                                                                                                                                                                                                           | 98  |

| <b>B</b> .1 | X-MERA                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 108 |

| B.2         | X-MERA power supplies, communication interfaces and heterogeneous                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|             | processors synoptic scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                | 110 |

| <b>B.3</b>  | Communication interfaces pinout.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 112 |

| B.4         | FPGA as NPU accelerator using <i>Delirium</i>                                                                                                                                                                                                                                                                                                                                                                                                                             | 115 |

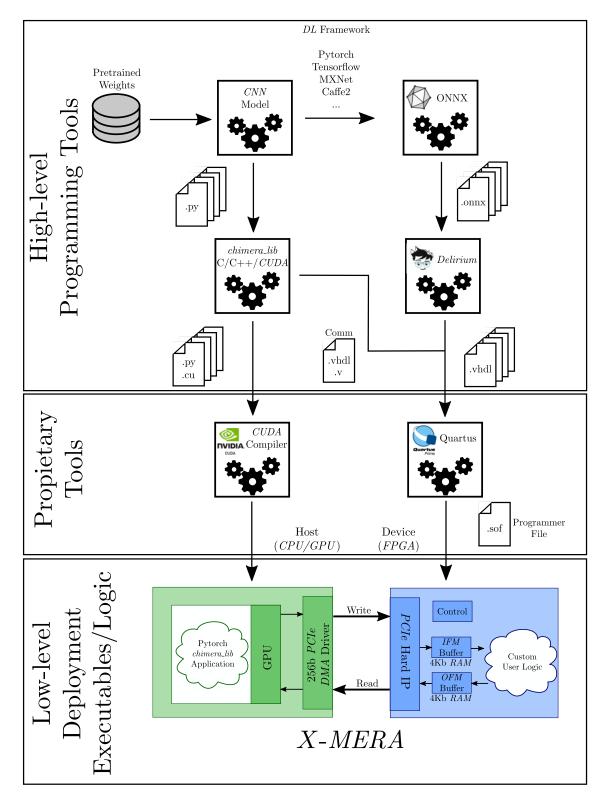

| <b>B.5</b>  | General workflow from high-level programming tools to low-level on-                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|             | device deployment of CNN models with <i>Delirium</i> and <i>"chimera_lib"</i>                                                                                                                                                                                                                                                                                                                                                                                             | 116 |

## **List of Tables**

| 2.1        | Modeling taxonomy according to Pimentel et al. [Pim17] and García-Martin            |     |

|------------|-------------------------------------------------------------------------------------|-----|

|            | et al. [GMRRG19]                                                                    | 17  |

| 2.2        | Flydel curvature, monotonicity and posynomial properties                            | 19  |

| 2.3        | Embedded heterogeneous platform hardware specifications                             | 37  |

| 2.4        | Selected single-feature models per KPI and per device using RMSE as loss            |     |

|            | function with L2 regularization term. $#\theta^*$ is the number of total parameters |     |

|            | chosen for the strong regressor KPI.                                                | 44  |

| 2.5        | Modeling state-of-the-art comparison.                                               | 50  |

| 3.1        | Heterogeneous partitioning methods characteristics                                  | 57  |

| 3.2        | Result comparison of GPU homogeneous vs FPGA-GPU heterogeneous                      |     |

|            | design on ImageNet-like dataset format for several module architectures             |     |

|            | with different parameters configurations.                                           | 78  |

| 3.3        | Energy and latency comparison with state-of-the-art partitioning techniques         |     |

|            | on heterogeneous FPGA-GPU against homogeneous implementations. * In                 |     |

|            | [OHY <sup>+</sup> 18] values were estimated for a single FPGA-GPU pair              | 79  |

| 4.1        | Optimization state-of-the-art comparison.                                           | 100 |

| <b>B.1</b> | X-MERA Intel <sup>®</sup> Cyclone <sup>®</sup> 10 GX FPGA pinout table              | 113 |

## Glossary

- ADC Digital-Analog Converter. 38, 69

- ALM Adaptive Logic Module. 21, 42, 44, 86

- ALUT Adaptive Look-Up Table. 21, 42, 44, 86

- ANN Artificial Neural Network. 15, 17, 19

- ASIC Application Specific Integrated Circuit. 4, 11, 15, 17, 31, 58–60, 81

- **BN** Batch Normalization. 46, 48

- **BNN** Binary Neural Network. 59

- BRAM Block RAM. 21, 50

- **BSP** Bulk Synchronous Programming. 59

- **BTB** BoTtom Board. 108, 109

- BW Bandwidth. 26, 50

- CCR Computation-to-Communication Ratio. 26, 66, 94, 96, 97, 99, 102

- **CNN** Convolutional Neural Network. iii, v, xiii–xvi, 1, 4–8, 11–13, 15–22, 27, 29–33, 35, 37, 39, 42–44, 46, 48–53, 55, 58–61, 63, 65, 67–77, 79, 81–88, 91–93, 95–97, 99, 101, 102, 104, 107, 114–116

- **CPU** Central Processing Unit. xiii, xiv, xvi, 1–3, 7, 11, 12, 14, 15, 17, 30, 35–39, 41, 43, 44, 48–50, 53, 58–61, 69, 77, 81, 84, 88, 90, 91, 96, 97, 99–102, 109, 111, 114

- CUDA Compute Unified Device Architecture. 15, 30, 59, 67, 107, 114

- DHM Direct Hardware Mapping. 35, 39, 42, 43, 46, 48, 51, 52, 61, 65, 67, 68, 70, 73, 77, 84, 92, 101, 102, 115

- DL Deep Learning. iii, 1, 4, 11, 12, 51–53, 61, 65, 67, 77, 82, 101, 107, 115

- DMA Direct Memory Access. 114

- DMU Decision Making Unit. 60

- **DNN** Deep Neural Networks. 83

- **DP** Dynamic Programming. 97, 100

- **DPU** Deep learning Processor Unit. 16, 50

- DRAM Dynamic Random Access Memory. 16, 50

- DSE Design Space Exploration. 4, 7, 13–15, 49, 60, 81, 82, 99, 107

- DSP Digital Signal Processor. 3, 4, 58, 65

- **DT** Decision Tree. 16, 17, 50

- **DVFS** Dynamic Voltage-Frequency Scaling. 60

- FFT Fast-Fourier Transform. 14, 50

- FM Feature Maps. 5, 30, 51, 56, 65, 75, 76, 88, 91, 93, 114

- **FPGA** Field Programmable Gate Array. iii, v, xiii–xvii, 1, 3, 4, 7, 11, 12, 15–17, 21, 30, 31, 35–39, 42–44, 46, 48–56, 58–65, 67–79, 81, 83, 84, 86, 88–92, 96, 97, 99–102, 107–109, 111, 113–115

- **FPS** Frames per Second. 42

- GEMM GEneral Matrix-Multiplication. 14, 50, 59

- **GGP** Generalized Geometric Programming. xvi, 8, 81, 82, 84, 86, 89–97, 99–101

- GP Geometric Programming. xvi, 8, 81, 82, 84–90, 99–101, 105

- **GPU** Graphics Processing Unit. iii, v, xiii–xvii, 1, 3, 4, 7, 11, 12, 15–17, 30, 35–39, 41–45, 48–56, 58, 59, 61–65, 67–79, 81, 83, 84, 86, 88–91, 97, 99–102, 107, 109, 111, 114

- HDL Hardware Description Language. 115

- HLS High-Level Synthesis. 15

- HOG Histogram Oriented Gradient. 59

- HPC High Performance Computing. 4, 52, 53, 59

- IC Integrated Circuit. 38, 69

- **IFM** Input Feature Map. xiii, xiv, 5, 16, 19–21, 24–27, 29, 31–33, 37, 39, 42, 46, 48, 53–55, 59, 65, 69, 70, 72, 73, 75, 76, 79, 88, 89, 93, 114, 115

- ILP Integer Linear Programming. 15, 17, 50, 60, 83, 93, 94, 97, 100

- IoT Internet of Things. 51, 83, 100

- **KPI** Key Performance Indicator. xiii, xiv, xvii, 5–7, 11, 14–18, 20–22, 24, 25, 28, 29, 31–33, 35–38, 40, 42–45, 48–50, 68, 72, 74, 84, 101

- **LAB** Logic Array Block. 21, 42, 44, 86

- LFSR Linear Feedback Shift-Register. 31, 39

- LMA Levenberg-Marquardt Algorithm. 22, 24, 34, 36, 42

- **LP** Linear Programming. 15, 17, 50, 97, 100

- LSE Least Squares Error. 12, 30, 32, 34, 50

- LSM Least Squares Minimization. 34

- LUT Look-Up Table. 59, 65

- MAC Multiply and ACcumulate. 15–17, 30, 50, 64, 99

- MDB MiDdle Board. 108, 109

- MISO Multiple Input Single Output. 34

- ML Machine Learning. 15, 34, 35

- MoA Model of Architecture. 32

- MoC Module-on-Chip. 37, 69

- MVTU Matrix-Vector-Threshold Unit. 59

- NAS Neural Architecture Search. 60, 102

- NCS2 Neural Compute Stick 2. 4

- NNLS Non-Negative Least Squares. 15, 50

- NPU Neural Processing Unit. xvi, 115

- NRMSE Normalized RMSE. 43–45

- OFM Output Feature Map. xiii, 5, 19–21, 25, 32, 37, 55, 62, 65, 72, 93, 114, 115

- **OLS** Ordinary Least Squares. 15, 50

- **PCIe** Peripheral Component Interconnect Express. xiii, xv, 35, 37, 59, 61, 65, 69, 72–74, 108, 109, 111, 114

- PDF Probability Density Function. 35

- PMC Performance Monitoring Counter. 14, 15, 17, 50

- **PRBS** Pseudo-Random Binary Sequence. 31

- RF Random Forest. 15–17, 50

- RFE Response From Excitation. 30

- RL Reinforcement Learning. 102

- RMSE Root Mean Square Error. xvii, 23, 24, 43, 44

- RTL Register Transfer Level. 58

- SDF Synchronous Data Flow. 60

- SI System Identification. xiii, 8, 11–13, 16, 17, 22, 24, 26, 27, 29–31, 34, 35, 37, 46, 49, 101

- SIMD Single-Instruction Multiple-Data. iii, v, 4, 39, 52, 64, 65, 76, 101

- SISO Single Input Single Output. 17, 33

- SoC System-on-Chip. xiii-xv, 36, 37, 41, 69, 70, 77, 84, 102, 111

- SoM System-on-Module. 108, 111

- SVM Support Vector Machine. 15, 17, 34, 59

- TPU Tensor Processing Unit. 4, 58, 102

- U-Core Unconventional Core. 2-4

- VHDL Very High Speed Integrated Circuit (VHSIC) Hardware Description Language. 115

- VPU Vision Processing Unit. 58

## Chapter 1

## Introduction

This first Chapter introduces the main context and ideas of the presented thesis. First, the concept of heterogeneous computing is discussed in the domain of embedded design and the motivation behind it. A plethora of hardware architectures arise from this definition of heterogeneous platforms. A similar phenomenon can be inferred from the software implementation of Deep Learning (DL) models. Thus, this thesis focuses on Central Processing Unit (CPU)-Graphics Processing Unit (GPU)-Field Programmable Gate Array (FPGA) as emerging embedded technologies for DL applications, specifically for Convolutional Neural Network (CNN) models. As a second stage, the challenges evoked from the embedded architecture and algorithmic integration are the central topic of this manuscript. These challenges delimit the scope of this dissertation and establish the problem definition and hypothesis. The contributions are the result of this problem definition, proposing the general and specific objectives to further develop a global methodology. Finally, the manuscript outline is presented to address each individual specific objective. This resulting outline serve as a guide for the thorough content development of the following Chapters.

#### 1.1 Heterogeneous computing

The demand of computing power has not slowed down since the dawn of the computing term itself. As a matter of fact, this demand was already present way before the birth of electronics and even mechanical computers. One can argue, that current processing platforms are only catching up on the most feasible problems that mathematicians, physicians and scientists have already formalized since centuries. Human innovation through technology has allowed to profit from this never-ending progress in a more tangible manner. As a consequence, this pragmatism has led to an environment of problem solving devices adapted not only for high-end computing centers, but also for our daily life. Perpetuating this way, the requirements for more capable processing devices. Nevertheless, as it will be discovered by the reader through this dissertation, this processing scaling is not trivial, nor inconsequential. After the first CPU conception, the most evident step for scaling was to increase the number of cores, giving birth to the concept of *multiprocessor*.

The parallel capabilities and limits of multiple processors against single core processors was first presented by Gene Amdahl and its well-known Amdahl's law [Amd67]. This

work awakened skepticism in the scientific community and extensive discussions between many experts since the early stage of the multiprocessors era [Gus88]. However, a common recurrent topic in these debates is the fraction of parallelism and serial execution found in a given application to benefit from speed-up. The presence of parallelism is a key component for *multiprocessor acceleration* or speed-up on hardware [DRPDDP15]. An *accelerator* is a processing device capable of instruction execution to perform some computation. This software parallelism and hardware acceleration co-dependency must be well described to achieve efficient algorithmic porting into the accelerator architectures. In this manuscript, this is referred as *integration*. To attain this level of efficiency, it is essential to describe the platform in terms of its hardware architecture nature. The first multiprocessor accelerators were considered as *homogeneous*. This is because platforms mostly replicated the same core or processing element with the same architecture capabilities and executing the same instructions. As more and more developers and users made the transition between sequential to parallel programming, newer paradigms were adopted.

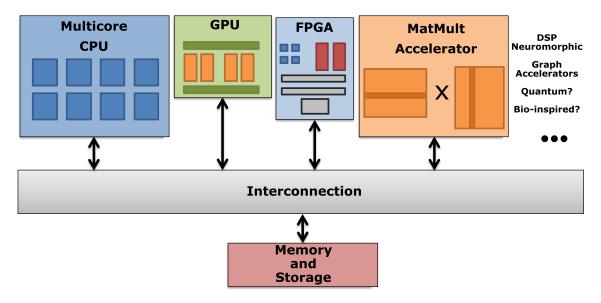

FIGURE 1.1: Generic heterogeneous architecture [Zah17].

*Heterogeneous computing* was introduced to address the *heterogeneity* present in core capabilities or specific ways to handle instructions [Zah17]. However, the term heterogeneity has not a formal nor strict definition. Different levels of heterogeneity can be achieved. Homogeneous multiprocessor architectures can fetch and execute different instructions; like execution synchronization, while the others are fully dedicated to computing. Therefore specializing some cores to an specific task. Another level of heterogeneity could be the type of hardware architectures deployed in our hardware. Heterogeneous architectures can be composed from three main accelerator groups: symmetric, asymmetric and Unconventional Core (U-Core) [CMHM10]. Symmetric cores were the first based on identical core replication, like the first multicore CPUs. Asymmetric focused on specializing some cores to specific tasks or capabilities. Finally, U-Cores cover a wide spectrum of programmable custom-logic devices, highly specialized processors or emerging technologies and how they interact to each other. In this thesis, we focus on the latest one. Figure 1.1

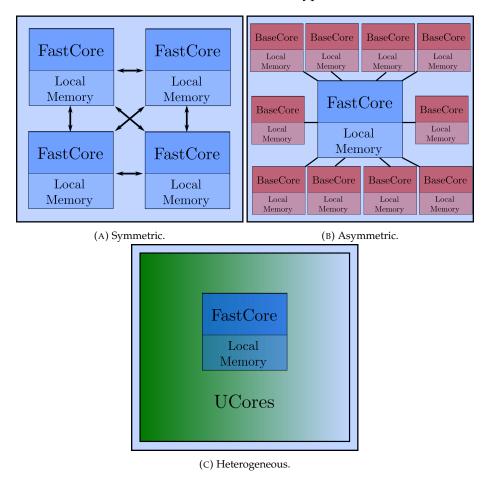

shows a generic heterogeneous architecture incorporating many symmetric or asymmetric accelerators, like: CPUs to U-Cores, like: GPUs, FPGAs, Digital Signal Processors (DSPs), matrix-multiplication accelerators and emerging technologies. However, some heterogeneous architecture include more complex memory models, where heterogeneity is also present in the way these accelerators communicate. For instance, the hybrid accelerator architectures from Figure 1.2 lacks the interconnection from Figure 1.1. Thus, the communication is defined by the neighborhood topology and/or visible memory components on each core. Figure 1.2 shows different multicore accelerator types from [CMHM10]. The arrows represent a dedicated communication link between cores. Fast cores are usually single-core processors to execute sequential instructions with their own resources, like local memory and caches. While the base-core are equivalent to execute parallel portion of instruction execution. Some multicore topologies, like in 1.2a, include a broadcast communication style, where all processor can communicate with each other. While some others have a main sequential processor to orchestrate task execution of similar base cores, as depicted in 1.2b. Finally, in Subfigure 1.2c, a plethora of Ucores are used to deploy parallel execution and communicate directly with the main core. These Ucores may vary in capabilities from each other and include different types of communication links.

FIGURE 1.2: Multicore types according to [CMHM10].

The scope of this dissertation is delimited by the type of U-Cores adopted on the heterogeneous platform architecture. Two individually well-studied accelerators are

explored. On one hand, the GPU is based on core replication with hundreds (embedded), thousands (personal computers) or even tenths or hundred of thousands (data centers) of processing elements. These cores operate in a Single-Instruction Multiple-Data (SIMD) fashion and each core can have a different workload attributed by a scheduler. This is, that they execute the same operation over different data chunks or batches, known as *warps* or *wavefronts*, depending on the vendor. At the other hand, the FPGA takes advantage of its programmable configuration to create custom designs at expense of limited logic and memory resources.

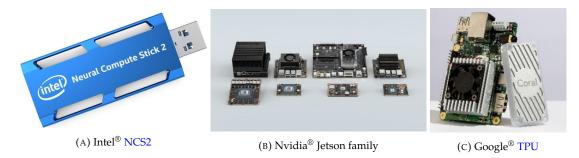

FIGURE 1.3: Some embedded heterogeneous platforms.

These heterogeneous platforms, as depicted in Figure 1.1, are a well-established environment paradigm in High Performance Computing (HPC) data centers since the last decades. This quick adoption has been widely accelerated because of the demand of current DL algorithms  $[TAI^+20]$ . In these specific cases, considerations such as energy consumption, resource utilization or memory transfers; play a lesser role to achieve lower latency and higher throughput. This is however, not the case for *embedded* platforms, where usually a fragile trade-off between system performance, energy efficiency and resource constraints is crucial [HSKR21]. Figure 1.3 shows some embedded heterogeneous platforms with U-Cores. Subfigure 1.3a shows the Intel® Neural Compute Stick 2 (NCS2) [Mov19] with aDSP-GPU microarchitecture. Subfigure 1.3b shows the Nvidia<sup>®</sup> Jetson family of embedded GPUs, which some of them include a dedicated Application Specific Integrated Circuit (ASIC) for DL, named tensor cores. Subfigure 1.3c shows the Google® Tensor Processing Unit (TPU) [JYP<sup>+</sup>17]. With the rise of this new generation of heterogeneous platforms on the edge, a well-defined development ecosystem must be carefully organized to find adequate solutions, this is known as Design Space Exploration (DSE). In the following subsection, the deployment implications of embedded heterogeneous computing for CNN model inference are discussed as motivation behind this manuscript.

### 1.2 Challenges and problem definition

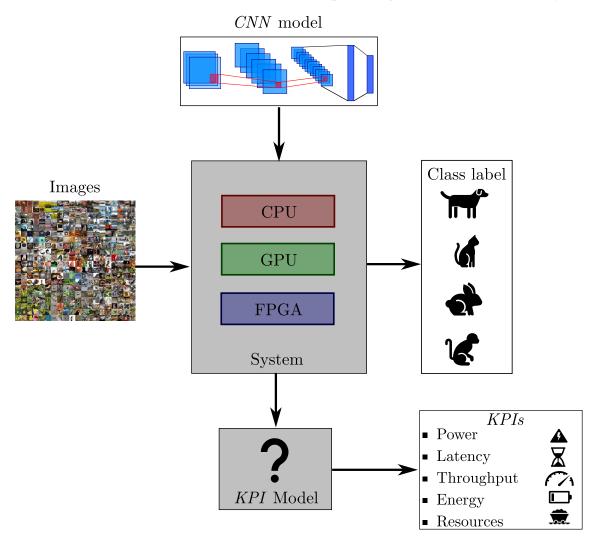

In this thesis, the inference process of CNN models for image classification tasks is studied. In this context, as seen in the upper part of Figure 1.4, a pre-trained CNN model takes as an input an image and it outputs a class label. Once a CNN model is implemented in a hardware platform, also known as the *system*, several computational operations are performed to generate this class label. The required computation has a cost in terms of

time, energy and resources. Such metrics are useful to evaluate the efficiency of a given system, these metrics are commonly known as Key Performance Indicators (KPIs). A KPI is a quantifiable measurement that illustrates the effectiveness of the system towards a specific goal. These KPIs depend on several variables, like the dimensions of the CNN layers, the topology of the network, the internal architecture of the system or the image patterns. Since it is an overwhelming task to control all these variables, it is desired to estimate a *model* from KPI observation from multiple configurations of these CNN layers.

FIGURE 1.4: KPI modeling of a heterogeneous platform as system.

More generally, as it will be slowly introduced during the development of the dissertation, the CNN inference is a computational model that operates over different data workloads called Feature Mapss (FMs), not only images. Each processing block operates over an Input Feature Map (IFM) and produces an Output Feature Map (OFM). The details of these operations are described extensively in the following chapters. Momentarily, it is relevant how these memory transfers are handled and mapped. This is because, from a hardware perspective, memory hierarchy is one of the main challenges and bottlenecks in heterogeneous platforms. Several levels in a memory model like on-chip memory, external memories, local or global memories, shared or private resources; have a direct impact on system performance. The accelerator topology and its interconnection is equally important [Zah17]. Similarly, selecting the distributed workload on a heterogeneous platform is not a simple task. Scheduling relies on data dependency and how each individual accelerator is synchronized. Additionally, some partitions may be well-suited for an specific platform, but quite inefficient on another. This creates a generalization limitation dependant on the specific hardware capabilities. All these challenges become more complex considering the typical embedded design constrains [HBNY19]. Figure 1.5 illustrates the partitioning of a CNN model of computation. Each resulting partition is mapped to an individual accelerator on a custom heterogeneous architecture.

FIGURE 1.5: CNN model partitioning and mapping into an embedded heterogeneous platform with multiple accelerators.

Summarizing, the main challenges covered in this manuscript are listed below:

- Heterogeneous hardware platform performance characterization and evaluation.

- CNN model partitioning, mapping and scheduling.

- Inter-device memory transfers handling.

- Selecting appropriate design solutions considering limited embedded resources.

The following questions are derived from the challenges to guide this thesis and set the contribution basis:

- How to efficiently deploy a CNN topology on a hybrid platform?

- How can a hardware-aware design solution be evaluated?

- Which KPI metrics should be chosen for evaluation?

- Which CNN configuration features should be selected to characterize the heterogeneous platform?

- How to split the CNN model for a better efficiency?

- How to guarantee optimal solutions and time efficiency?

From these questions, a more formal **hypothesis** definition is proposed:

For pretrained CNN model inference, an optimal set of mapped partitions can be obtained from an optimization problem formulation and efficiently deployed on embedded heterogeneous platforms, where each accelerator is analytically characterized and a set of partitioning rules are chosen.

### 1.3 Contributions

The general objective inferred from the hypothesis is *the obtainment and mapping of these optimal accelerated partitions result of the optimization problem*. However, to achieve this goal, three specific tasks must be individually resolved: the *modeling*, the *partitioning* and the *optimization*. The main content development of this thesis is depicted in Figure 1.6.

FIGURE 1.6: Thesis content development flow.

The contribution outcome of the manuscript is enumerated below:

- 1. A methodology to obtain a set of analytical models that describe the hardware KPI efficiency of a heterogeneous platform for CNN workloads.

- Adapting state-of-the-art partitioning, mapping and scheduling techniques to heterogeneous platforms.

- 3. An optimization problem formulation with an optimal solution that can be efficiently solved in terms of time and computational complexity for DSE.

- 4. A software-hardware co-design environment for CNN partition acceleration with high-level abstraction.

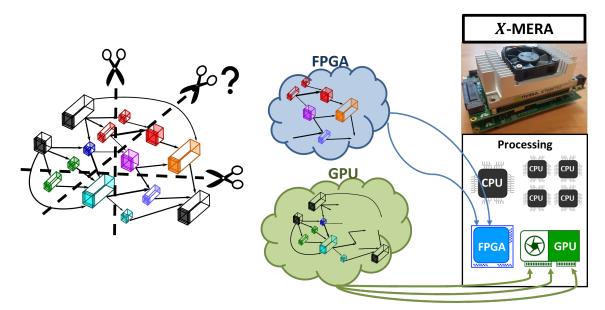

- 5. A smart camera prototype that benefits from the capabilities of a CPU-GPU-FPGA embedded heterogeneous accelerators as test platform. This smart camera is named *X-MERA*.

#### 1.4 Manuscript outline

This first chapter, served as introduction for the main motivation, challenges and contribution of this manuscript. The basis for the content of each chapter has also been established. The following chapters cover the main body and contributions described above. For the next three chapters, an introduction and state-of-the-art related works are presented that set the context and motivation behind each chapter. Additionally, each chapter conclusion sets a transition between the results and their impact for the subsequent chapters. The three main body chapters are briefly described as:

- Chapter 2: This chapter focuses on the heterogeneous hardware architecture characterization through *performance modeling* with analytical mathematical models for CNN layer configurations. The resulting models are the outcome of a methodology inspired from a black-box System Identification (SI) approach with random sequence excitation. The chapter addresses the contribution 1.

- Chapter 3: This chapter covers the mapping and scheduling adapting *heterogeneous partitioning techniques* to the already described hardware models for mobile CNN models from Chapter 2. The experimental results compare the heterogeneous partitioning against homogeneous solutions at a module-level partitioning. The chapter addresses contribution 2.

- Chapter 4: This chapters formalizes the mathematical CNN model partitioning optimization problem. This problem formulation is elaborated in a context for Geometric Programming (GP) and Generalized Geometric Programming (GGP) optimization. This optimization requires some strict specific mathematical formulation, but it offers some convexity and optimal properties. The chapter address contribution 3.

The Chapter 5 further discusses the obtained results of the thesis. Furthermore, an analysis of the possible research exploration paths for this dissertation is studied. These opportunities offer new research question and a new spectrum of hypotheses for embedded heterogeneous platform design. Finally, the Appendix A lists a set of mathematical properties useful for the GGP problem formulation, such as convexity and posynomial preserving operations. This is specially useful for 4. Appendix B describes the hybrid software development environment and the heterogeneous smart camera prototype *X*-MERA used in Chapters 2, 3 and 4. This appendix addresses contributions 4 and 5.

## 1.5 Publications

- Walther Carballo-Hernández, François Berry, Maxime Pelcat, and Miguel Arias-Estrada. Towards embedded heterogeneous FPGA-GPU smart camera architectures for CNN inference. In *Proceedings of the 13th International Conference on Distributed Smart Cameras*. ACM, sep 2019

- Walther Carballo-Hernández, Maxime Pelcat, and François Berry. Why is FPGA-GPU heterogeneity the best option for embedded deep neural networks? *Presented at DATE Friday Workshop on System-level Design Methods for Deep Learning on Heterogeneous Architectures (SLOHA 2021)*, February 2021

### 1.6 Submissions

- Walther Carballo-Hernández, Maxime Pelcat, Shuvra S. Bhattacharyya, Ricardo Carmona Galán, and François Berry. Flydeling: Streamlined performance models for hardware acceleration of CNNs through system identification. Under review for ACM Transactions on Modeling and Performance Evaluation of Computing Systems (ToMPECS), 2022

- Walther Carballo-Hernández, Maxime Pelcat, Ricardo Carmona Galán, and François Berry. A module-level CNN partitioning method for FPGA-GPU heterogeneous acceleration. 2022

## Funding acknowledgements

This project has received funding from the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska-Curie grant agreement No 765866.

## Chapter 2

# Flydeling: Performance Models for Hardware Acceleration of CNNs through SI

#### 2.1 Chapter abstract

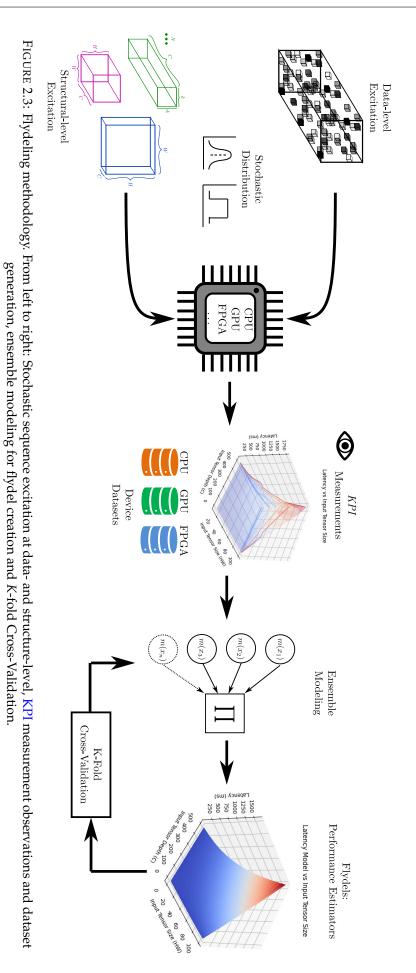

As covered in Chapter 1, DL algorithms, such as CNNs in many near-sensor systems, opens new challenges in terms of energy efficiency and hardware performance. An emerging solution to address these challenges is to use tailored heterogeneous hardware accelerators combining processing elements of different architectural natures such as CPU, GPU, FPGA or ASIC. In order to progress towards heterogeneity, a great asset would be an automated design space exploration tool that chooses, for each accelerated partition of a CNN, the most appropriate architecture. To feed such a design space exploration process, models are required that provide very fast yet precise evaluations of alternative architectures or alternative forms of CNNs. Quick configuration estimation could be achieved with few parameters from representative input sequences. This chapter studies a solution called *flydeling* (as a contraction of flyweight modeling) for obtaining these models by inspiring from the black-box System Identification (SI) domain. We refer to models derived using the proposed approach as *flyweight models* (*flydels*).

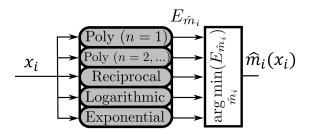

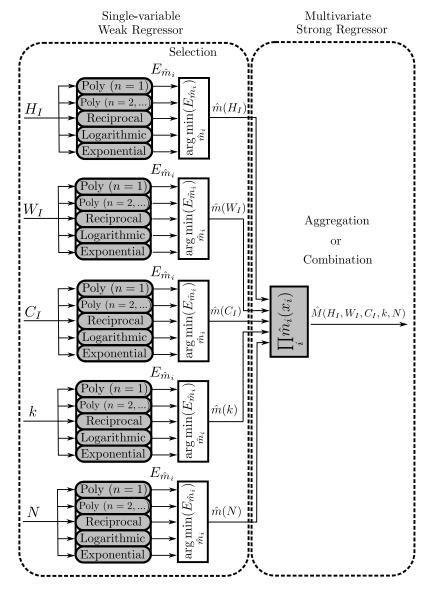

In this chapter, a methodology is proposed to generate these *flydels*, using CNN properties as predictor features together with SI techniques with a stochastic excitation input at a feature map dimensions level. For an embedded CPU-FPGA-GPU heterogeneous platform, it is demonstrated that it is possible to learn these KPIs *flydels* at an early design stage and from high-level application features. For latency, energy and resource utilization, *flydels* obtain estimation errors varying between 5% and 10% with less model parameters compared to state-of-the-art solutions, and are built automatically from platform measurements. A special form of these models (monomial and posynomial forms) are employed in Section 4, in combination with partitioning techniques from Section 3, to characterize heterogeneous platforms.

#### 2.2 Introduction

DL models are increasingly integrated into edge devices for a vast set of applications such as computer vision and speech recognition. To support the strong computing requirements of DL, heterogeneous architectures with application specific acceleration are the dominating solution for edge DL [VGG<sup>+</sup>20, TST<sup>+</sup>19, OHY<sup>+</sup>18], taking over single-processor systems. However, when using traditional programming and hardware description languages, designers are required to build an advanced prototype of their heterogeneous system before obtaining reliable processing performance estimates of their CNN implementation in terms of energy, execution time and resource utilization, given the complexity of such hybrid systems. This constraint leads to a late system performance evaluation and to relatively blind design choices. This drawback is intensified by the demand of efficient and quick comparison between different CNN architectures on constrained platforms.