# Behavioral Analysis and Design of K-Band Low-Phase-Noise Digitally Controlled Oscillators in 22 nm FD-SOI for 76 - 81 GHz Automotive Radars

Zhigang Li

# ► To cite this version:

Zhigang Li. Behavioral Analysis and Design of K-Band Low-Phase-Noise Digitally Controlled Oscillators in 22 nm FD-SOI for 76 - 81 GHz Automotive Radars. Electronics. Université de Poitiers, 2023. English. NNT: 2023POIT2259. tel-04116911

# HAL Id: tel-04116911 https://theses.hal.science/tel-04116911

Submitted on 5 Jun2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE

Pour l'obtention du Grade de

#### DOCTEUR DE L'UNIVERSITE DE POITIERS

(Faculté des Sciences Fondamentales et Appliquées) (Diplôme National - Arrêté du 25 mai 2016)

Ecole Doctorale : Mathématiques, Informatique, Matériaux, Mécanique, Energétique (MIMME)

Secteur de Recherche : Electronique, Microélectronique et Nanoélectronique

Présentée par :

# **ZHIGANG LI**

\*\*\*\*\*

# Behavioral Analysis and Design of K-Band Low-Phase-Noise Digitally Controlled Oscillators in 22 nm FD-SOI for 76 - 81 GHz Automotive Radars

\*\*\*\*\*

Directeur de Thèse : **David Cordeau** Co-Directeur de Thèse : **Jean-Marie Paillot**

\*\*\*\*\*

Soutenue le 05 Mai 2023 Devant la Commission d'Examen

\*\*\*\*\*

# <u>JURY</u>

Rapporteurs :

Yann Deval Philippe Ferrari Professeur à l'Université de Bordeaux Professeur à l'Université de Grenoble Alpes

Examinateurs :

Philippe Descamps Bruno Barelaud Florin Hutu Francis Huin Jean-Marie Paillot David Cordeau Professeur à l'ENSICAEN Professeur à l'Université de Limoges Maître de Conférences à l'INSA Lyon Docteur, Ingénieur à IDDO-IC, Caen Professeur à l'Université de Poitiers Maître de Conférences-HDR à l'Université de Poitiers

# Acknowledgements

This research work was carried out within the framework of a collaboration between the research institute of XLIM (UMR 7252, IUT of Angoulême, University of Poitiers) and the company IDDO-IC. Firstly, I would like to thank Mr. Denis MASLIAH, the founder of IDDO-IC, for welcoming me into his team and for his trust and support.

In particular, I would like to express my sincere thanks to my thesis director, Mr. David Cordeau, Maître de Conference HDR at the University of Poitiers, and co-director, Mr. Jean-Marie Paillot, Professor at the University of Poitiers. Their guidance and support have been the key to all my achievements. Their expertise, patience and encouragement have given me a deeper understanding and higher motivation during my research. Moreover, they always encouraged me to keep exploring and trying. I still remember one time when David told me not to worry that my operations would kill Cadence software. All these were like sparks that helped me to cross one obstacle after another. In addition, I would like to thank them for their precious and valuable feedback and comments that I have greatly benefited from during the process of writing my articles and dissertation.

I would also like to acknowledge Mr. Yann Deval, Professor at the University of Bordeaux; Mr. Philippe Ferrari, Professor at the University of Grenoble Alpes; Mr. Philippe Descamps, Professor at the Ecole Nationale Supérieure d'Ingénieurs de Caen (ENSICAEN); Mr. Bruno Barelaud, Professor at the University of Limoges; Mr. Florin Hutu, Maître de Conférences at the Institut National des Sciences Appliquées de Lyon (INSA Lyon); Mr. Francis Huin, Engineer at the IDDO-IC; whom I am very honored to have as the committee members for my oral defense. I am equally grateful to them for their examinations of my dissertation and for all their valuable comments and suggestions.

Special thanks are given to my dear colleagues from the IDDO-IC, Mr. Sébastien Charpentier, Mr. Matthieu Lecuyer, Mr. Sébastien Vauclair, Mr. Lewis Macdonald and others. Starting from the initial installation and configuration of the PDK to the various details of the circuit design and layout, their constant guidance meant a lot to me. In addition, their selfless care and assistance in my work and life made me feel at home. Of course, I also enjoyed the jokes they occasionally shared, even though some of them were not so funny. My sincere thanks also go to Ms. Emmanuelle Baldinger for helping me with many administrative tasks and keeping me worry-free. Time flies, but the memories

of my time at IDDO-IC will stay with me forever.

I would like to sincerely thank the members of the ReSYST research group, including Mr. Claude Duvanaud, Mr. Smail Bachir, former and current Ph.D. students (Tayeb, Younès, Nuraddeen, Abdulrazaq, Manuel, Bhanu, etc.). I would also like to thank other colleagues and friends, Maxime, Mohamed, Sergueï, Dounia, Baptiste, Georgian, etc. I have to say that they have consistently provided me with invaluable assistance and have supported, encouraged, and accompanied me throughout my academic journey.

Lastly, I would like to thank all my sisters and brothers (Yan Li, Yu Li, Wei Li, Liang Li, Kongliang Liu, Sanqiang Cen, Meng Liu) for their enduring love and encouragement. Especially, I would like to express my deepest appreciation to my lovely parents Zhanguo Li and Xinju Zhang. I will forever be grateful for their unconditional love, their endless sacrifices, and their unwavering faith in me.

Zhigang Li March 2023

# Table of Contents

| Acknowledgements                                      | I    |

|-------------------------------------------------------|------|

| List of Figures                                       | VII  |

| List of Tables                                        | XIII |

| List of Abbreviations                                 | XV   |

| General Introduction                                  | 1 -  |

| CHAPTER I                                             | 3 -  |

| Introduction to Research Work                         | 3 -  |

| I.1. Automotive Radar                                 | 3 -  |

| I.1.1. Radar Fundamentals                             | 3 -  |

| I.1.1.1. Radar-Frequency Bands                        | 5 -  |

| I.1.1.2. Mono-static and Multi-static Radars          | 7 -  |

| I.1.1.3. Radar Equation                               | 8 -  |

| I.1.1.4. Pulsed and Continuous-Wave Radars            | 9 -  |

| I.1.1.5. Transceiver Architectures                    | 12 - |

| I.1.2. Automotive Radar for Autonomous Driving        | 15 - |

| I.1.2.1. SAE Levels of Autonomy                       | 16 - |

| I.1.2.2. Advanced Driver-Assistance System            | 17 - |

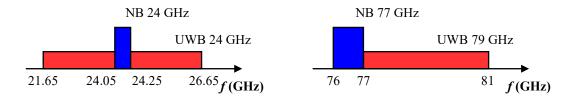

| I.1.2.3. Automotive Radar Frequency Bands             | 19 - |

| I.1.2.4. Automotive Radar Classification              | 20 - |

| I.1.3. Technologies Trends in Automotive Radar        | 22 - |

| I.1.4. Examples of 76 – 81 GHz FMCW Automotive Radars | 25 - |

| I.1.4.1. Academic Works                               | 25 - |

| I.1.4.2. Commercial Works                             | 27 - |

| I.1.4.3. Performance Summary and Comparison           | 30 - |

| I.2. Frequency Synthesizer                            | 31 - |

| I.2.1. Frequency Synthesis Techniques                 | 32 - |

| I.2.2. Phase-Locked Loop Fundamentals                 | 33 - |

| I.2.2.1. PLL Building Blocks                          | 33 - |

| I.2.2.2. PLL Transfer Functions                       | 34 - |

| I.2.2.3. Integer-N PLL and Fractional-N PLL           | 37 - |

| I.2.2.4. Limitations of the Analog CPPLL              | 38 - |

| I.2.3. An Overview of All-Digital Phase-Locked Loop   | 38 - |

| I.2.3.1. ADPLL Basic Principles                       | 39 - |

| I.2.3.2. ADPLL Key Building Blocks                    | 40 - |

|-------------------------------------------------------|------|

| I.2.3.3. Several Representative Examples of ADPLL     | 43 - |

| I.2.3.4. Advantages of the ADPLL                      | 46 - |

| I.3. Oscillators                                      | 48 - |

| I.3.1. Principles of an Oscillator                    | 48 - |

| I.3.1.1. Linear Feedback System                       | 48 - |

| I.3.1.2. Negative Resistance Compensation System      | 49 - |

| I.3.2. Different Types of Oscillators                 | 50 - |

| I.3.2.1. Ring Oscillators                             | 50 - |

| I.3.2.2. Colpitts Oscillator                          | 51 - |

| I.3.2.3. Differential Cross-Coupled Oscillator        | 53 - |

| I.3.3. Phase Noise Analysis of the Oscillators        | 57 - |

| I.3.3.1. Noise Sources                                | 57 - |

| I.3.3.2. Definition of the Phase Noise                | 58 - |

| I.3.3.3. Phase Noise Models                           | 59 - |

| I.4. Conclusion                                       | 64 - |

| I.5. Résumé du Chapitre I                             | 65 - |

| I.6. References                                       | 67 - |

| CHAPTER II                                            | 75 - |

| K-Band Triple-Bank DCO (T-DCO) Design                 | 75 - |

| II.1. Overview of 22FDX Technology                    | 75 - |

| II.1.1. Supported EDA Tools                           | 75 - |

| II.1.2. Preferred Choice for Automotive Radar: FD-SOI | 76 - |

| II.1.3. Device Options in 22FDX Library               | 78 - |

| II.2. Introduction to DCO                             | 81 - |

| II.2.1. From VCO to DCO                               | 81 - |

| II.2.2. Different Types of DCO                        | 84 - |

| II.2.2.1. RO-Based DCO                                | 84 - |

| II.2.2.2. DAC-Based DCO                               | 85 - |

| II.2.2.3. LC-Based DCO                                | 85 - |

| II.3. Development and Research Status                 | 86 - |

| II.3.1. First Multi-Gigahertz DCO for RF Applications | 86 - |

| II.3.2. Overview of Frequency Tuning Techniques       | 90 - |

| II.3.2.1. Mismatched MOS Varactors                    | 90 - |

| II.3.2.2. Switched Capacitors                         | 91 - |

| II.3.2.3. Digital Controlled Artificial Dielectric (DiCAD)                                           | 93 -              |

|------------------------------------------------------------------------------------------------------|-------------------|

| II.3.3. Performances Summary of LC-Based DCOs                                                        | 96 -              |

| II.4. DCOs for FMCW Radars                                                                           | 98 -              |

| II.4.1. Principle of FMCW Radars                                                                     | 98 -              |

| II.4.1.1. Stationary Target Detection                                                                | 99 -              |

| II.4.1.2. Moving Target Detection                                                                    | 101 -             |

| II.4.2. DCO Gain Calibration for Chirp Linearity                                                     | 102 -             |

| II.5. Design and Implementation of a K-Band Low-Phase-Noise T-DCO for 76 -<br>FMCW Automotive Radars | - 81 GHz<br>103 - |

| II.5.1. Introduction                                                                                 | 103 -             |

| II.5.2. K-Band DCO Design Considerations                                                             | 104 -             |

| II.5.2.1. DCO Specifications                                                                         | 104 -             |

| II.5.2.2. Selection of DCO Structures                                                                | 105 -             |

| II.5.2.3. K-Band LC Tank Design Considerations                                                       | 107 -             |

| II.5.2.4. Low Phase Noise Considerations                                                             | 109 -             |

| II.5.3. Circuit Implementation of the Proposed T-DCO                                                 | 110 -             |

| II.5.3.1. Block Diagram of the K-Band T-DCO                                                          | 110 -             |

| II.5.3.2. Parasitic Analysis of MOS Switches                                                         | 112 -             |

| II.5.3.3. 5-Bit Coarse-Tuning Bank                                                                   | 114 -             |

| II.5.3.4. 6-Bit Medium-Tuning Bank                                                                   | 117 -             |

| II.5.3.5. 5-Bit Novel Back-Gate-Based Fine-Tuning Bank                                               | 118 -             |

| II.5.4. Pre-Layout Simulation Results                                                                | 119 -             |

| II.5.4.1. PN Optimization                                                                            | 119 -             |

| II.5.4.2. FMCW Chirp with Frequency Overlap                                                          | 121 -             |

| II.5.5. Post-Layout Simulation Results                                                               | 122 -             |

| II.5.6. Comparative Study                                                                            | 126 -             |

| II.5.7. Summary                                                                                      | 127 -             |

| II.6. Conclusion                                                                                     | 128 -             |

| II.7. Résumé du Chapitre II                                                                          | 129 -             |

| II.8. References                                                                                     | 131 -             |

| CHAPTER III                                                                                          | 137 -             |

| K-Band Dual-Bank DCO (D-DCO) Design                                                                  | 137 -             |

| III.1. Introduction to D-DCO                                                                         | 137 -             |

| III.2. First Version of D-DCO (D-DCO.1)                                                              | 138 -             |

| III.2.1. Circuit Implementation of the Proposed D-DCO.1                                              | 139 -             |

| III.2.1.1. Block Diagram of the K-Band D-DCO.1139                      | 9 - |

|------------------------------------------------------------------------|-----|

| III.2.1.2. 4-Bit Coarse-Tuning Bank 140                                | ) - |

| III.2.1.3. 10-Bit Fine-Tuning Bank 141                                 | 1 - |

| III.2.1.4. LC Resonant Tank 143                                        | 3 - |

| III.2.2. Pre-Layout Simulation Results 144                             | 4 - |

| III.2.2.1. Frequency-Code Characteristic Curves 144                    |     |

| III.2.2.2. PN Performances 146                                         | 5 - |

| III.2.2.3. PVT Variations 149                                          | 9 - |

| III.2.2.4. Overall Performances of the D-DCO.1 150                     | ) - |

| III.2.3. Problems in Post-Layout Simulations 15                        | 1 - |

| III.2.4. Summary 157                                                   | 7 - |

| III.3. Second Version of D-DCO (D-DCO.2) 157                           | 7 - |

| III.3.1. Circuit Implementation of the Proposed D-DCO.2                | 7 - |

| III.3.1.1. Block Diagram of the K-Band D-DCO.2                         | 7 - |

| III.3.1.2. Fine-Tuning Bank Using a Novel Customized MOM Capacitor 159 | 9 - |

| III.3.2. Pre-Layout Simulation Results 16                              | 1 - |

| III.3.3. Post-Layout Simulation Results 163                            | 3 - |

| III.3.4. Comparative Study 166                                         | 5 - |

| III.3.5. Summary 167                                                   | 7 - |

| III.4. Conclusion 168                                                  | 8 - |

| III.5. Résumé du Chapitre III 168                                      | 8 - |

| III.6. References 170                                                  | ) - |

| General Conclusion 171                                                 | 1 - |

| List of Publications 175                                               | 5 - |

| Abstract 177                                                           | 7 - |

| Résumé 178                                                             | 8 - |

# **List of Figures**

| Figure I.1.1 Simplified block diagram of a radar system.                                      |

|-----------------------------------------------------------------------------------------------|

| Figure I.1.2 Atmospheric absorption at altitudes of sea level and 4 km                        |

| Figure I.1.3 Radar configurations. (a) Monostatic. (b) Bistatic                               |

| Figure I.1.4 Range measurement principle of the pulsed radar                                  |

| Figure I.1.5 LFM methods. (a) Linear triangular frequency modulation. (b) Linear              |

| sawtooth frequency modulation. (c) Segmented linear frequency modulation 12 -                 |

| Figure I.1.6 Block diagram of a PLL-based transmitter 13 -                                    |

| Figure I.1.7 Block diagram of a typical superheterodyne receiver 14 -                         |

| Figure I.1.8 Impact of the image frequency on the spectrum of the useful signal 15 -          |

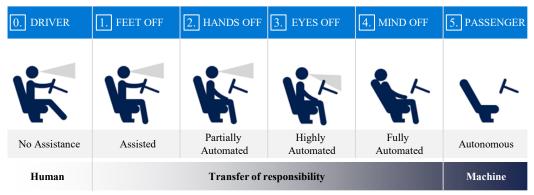

| Figure I.1.9 Five levels of autonomy 16 -                                                     |

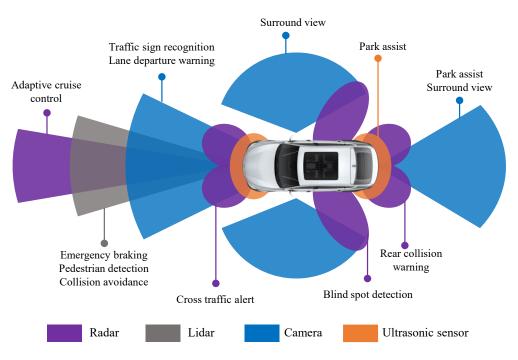

| Figure I.1.10 Typical types of sensors used in ADAS 17 -                                      |

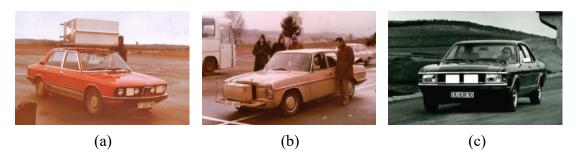

| Figure I.1.11 Early automotive radar systems. (a) 10 GHz radar in the early 1970s. (b)        |

| 16 GHz radar in 1975. (c) 35 GHz radar in 1974 19 -                                           |

| Figure I.1.12 Frequency bands for automotive radars 20 -                                      |

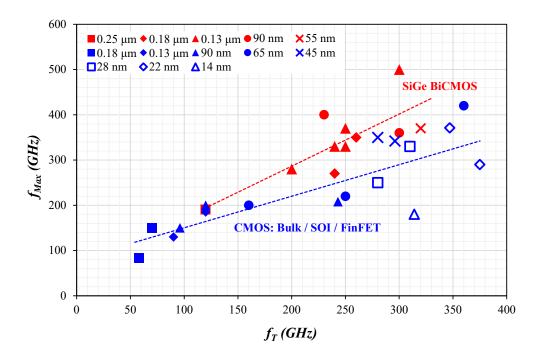

| Figure I.1.13 Comparison of $f_T / f_{max}$ collected from published papers. (a) SiGe BiCMOS. |

| (b) CMOS-Bulk/SOI/FinFET 24 -                                                                 |

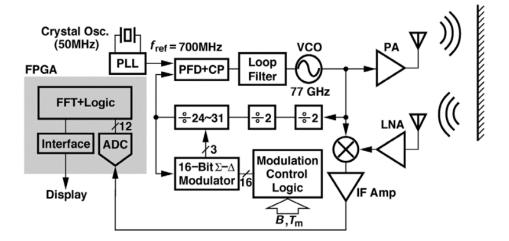

| Figure I.1.14 Schematic of the fully integrated 77 GHz FMCW radar transceiver in 65           |

| nm CMOS technology 25 -                                                                       |

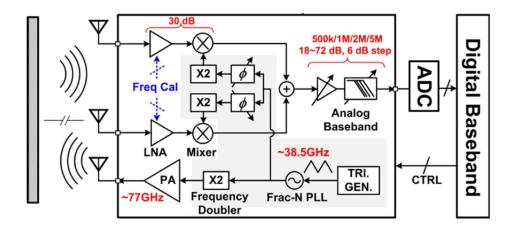

| Figure I.1.15 Schematic of the 77 GHz frequency doubling two-path phased-array                |

| FMCW transceiver for automotive radar 26 -                                                    |

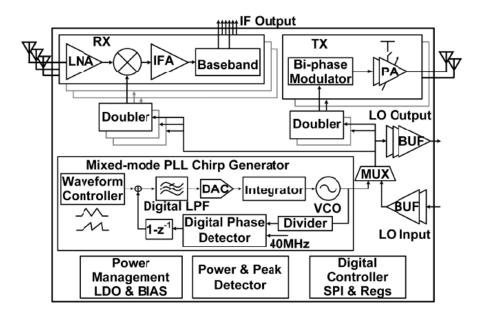

| Figure I.1.16 Schematic of the CMOS 76 – 81 GHz 2-TX 3-RX FMCW radar transceiver              |

| based on mixed-mode PLL chirp generator 27 -                                                  |

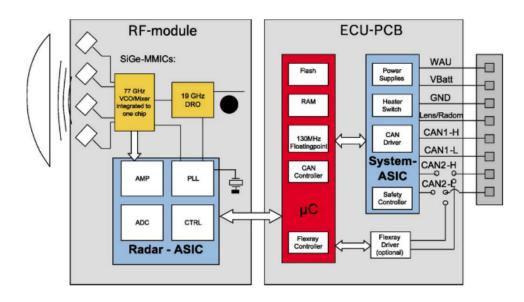

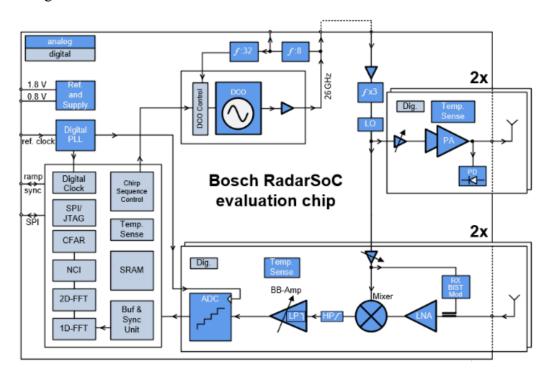

| Figure I.1.17 Schematic of the Bosch's LRR3 system 28 -                                       |

| Figure I.1.18 Schematic of the Denso's LRR system 29 -                                        |

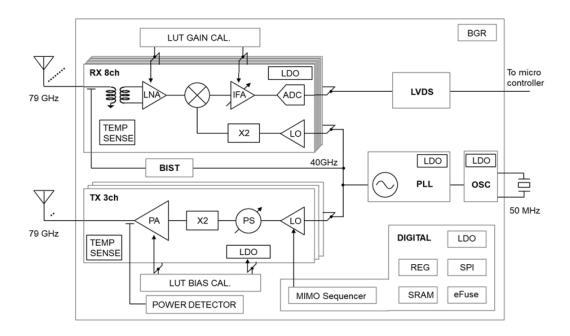

| Figure I.1.19 Schematic of the Bosch's 76 – 81 GHz automotive radar 30 -                      |

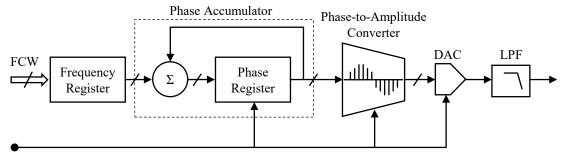

| Figure I.2.1 Simplified block diagram of a DDFS 32 -                                          |

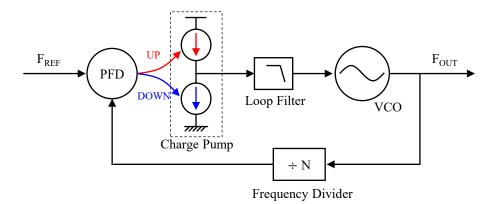

| Figure I.2.2 Simplified block diagram of a typical CPPLL 34 -                                 |

| Figure I.2.3 Linear s-domain model of a typical analog PLL 35 -                               |

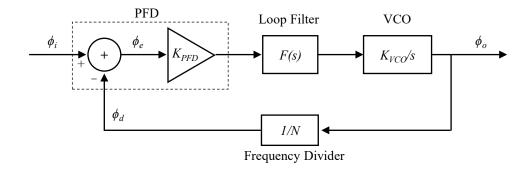

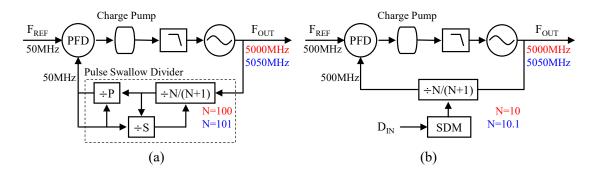

| Figure I.2.4 Step response of the underdamped system. (a) Input step signal. (b) Step         |

| response with different damping factors 37 -                                                  |

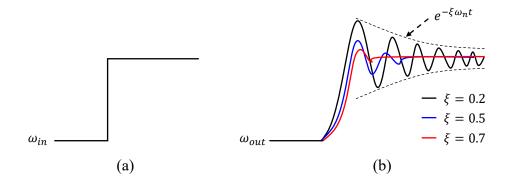

| Figure I.2.5 Block diagrams of (a) integer-N PLL with a pulse swallow frequency divider       |

|                                                                                               |

| and (b) fractional-N PLL with an SDM 37 -                                                    |

|----------------------------------------------------------------------------------------------|

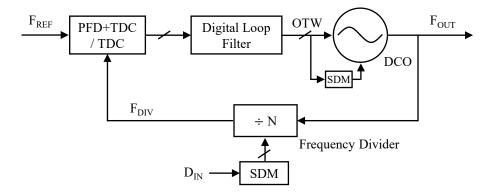

| Figure I.2.6 Simplified block diagram of an ADPLL based on frequency divider 39 -            |

| Figure I.2.7 Simplified block diagram of an ADPLL based on loop counter 40 -                 |

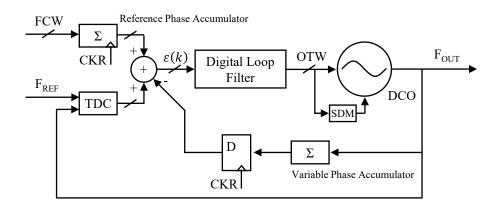

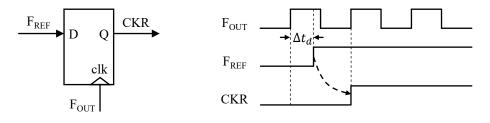

| Figure I.2.8 D flip-flop used for system clock retiming 41 -                                 |

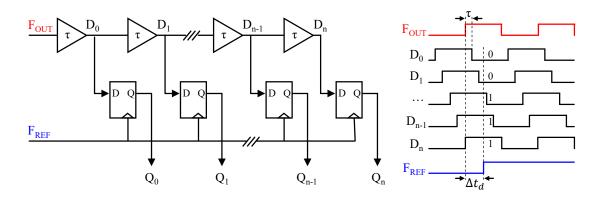

| Figure I.2.9 Classical diagram of the TDC based on an inverter chain 41 -                    |

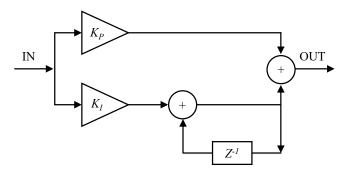

| Figure I.2.10 Discrete z-domain transfer function of the PI loop filter 42 -                 |

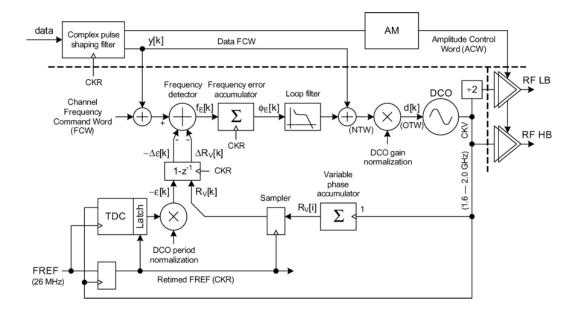

| Figure I.2.11 Schematic of the TI's ADPLL-based transmitter system 43 -                      |

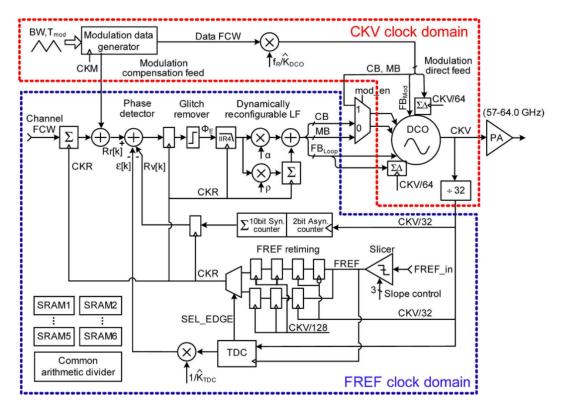

| Figure I.2.12 Schematic of the 60 GHz ADPLL-based FMCW transmitter system 45 -               |

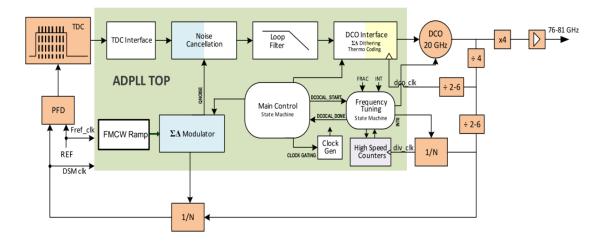

| Figure I.2.13 Schematic of the divider-based ADPLL 46 -                                      |

| Figure I.3.1 Linear positive feedback system for oscillators 49 -                            |

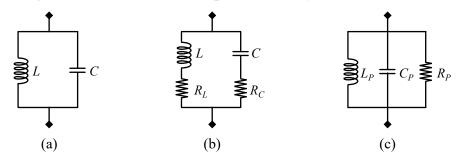

| Figure I.3.2 LC resonant circuit. (a) Ideal parallel LC circuit. (b) Practical parallel LC   |

| circuit. (c) Equivalent parallel RLC circuit 49 -                                            |

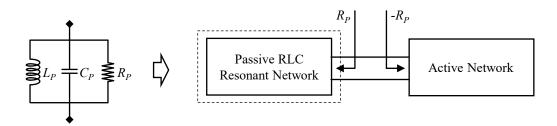

| Figure I.3.3 Negative resistance compensation system for oscillators 50 -                    |

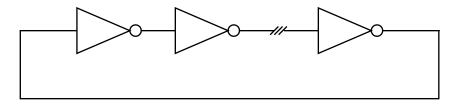

| Figure I.3.4 Ring oscillator based on an inverter chain 51 -                                 |

| Figure I.3.5 (a) Single MOS transistor with feedback applied from drain to source. (b)       |

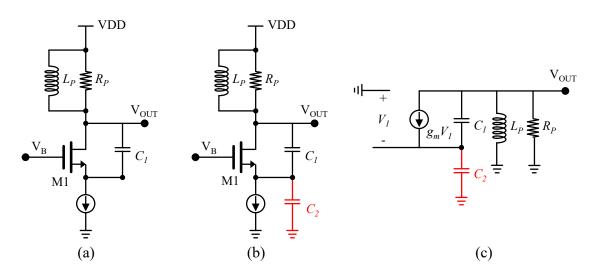

| Colpitts oscillator. (c) Equivalent small-signal model of the Colpitts oscillator 52 -       |

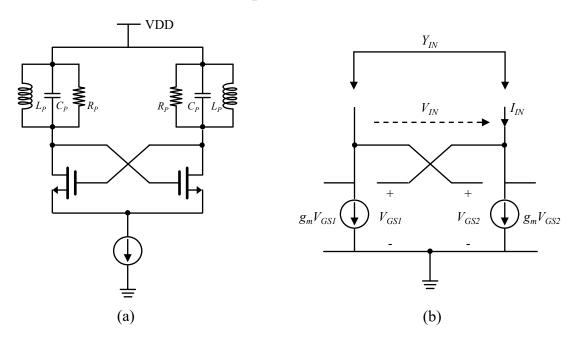

| Figure I.3.6 (a) Simplified schematic of a differential cross-coupled oscillator. (b) Small- |

| signal model of the cross-coupled pair 53 -                                                  |

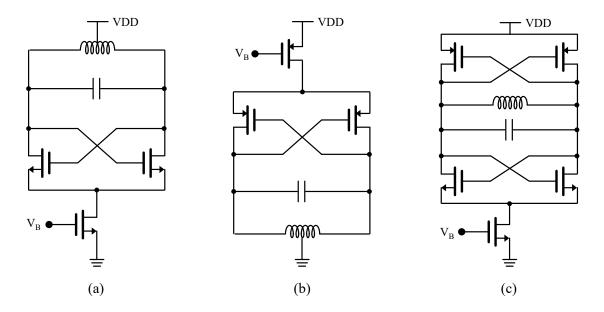

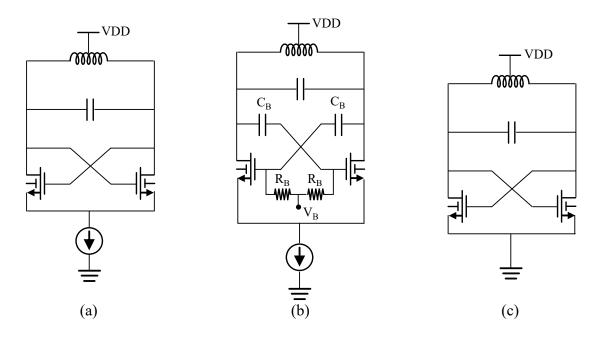

| Figure I.3.7 Cross-coupled oscillators with a tail/top current source. (a) NMOS-only         |

| structure. (b) PMOS-only structure. (c) Complementary structure 55 -                         |

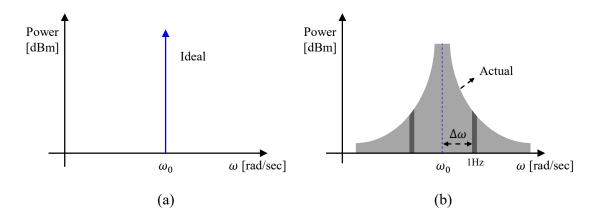

| Figure I.3.8 (a) Ideal power spectral density of oscillators. (b) Actual power spectral      |

| density of oscillators 59 -                                                                  |

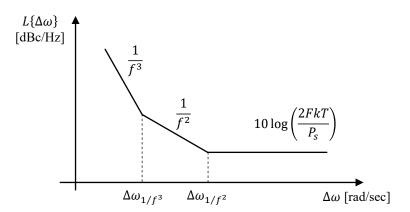

| Figure I.3.9 Typical characteristic curve of oscillators' phase noise 60 -                   |

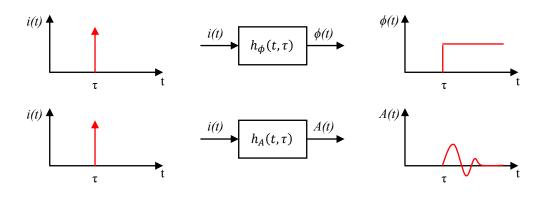

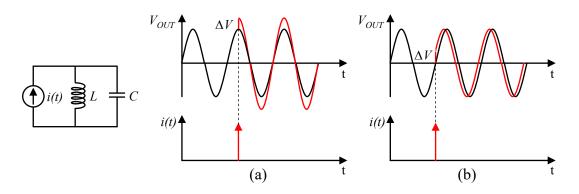

| Figure I.3.10 Phase and amplitude impulse response model                                     |

| Figure I.3.11 (a) Noise impulse injected at the peak. (b) Noise impulse injected at the      |

| zero-crossing point 63 -                                                                     |

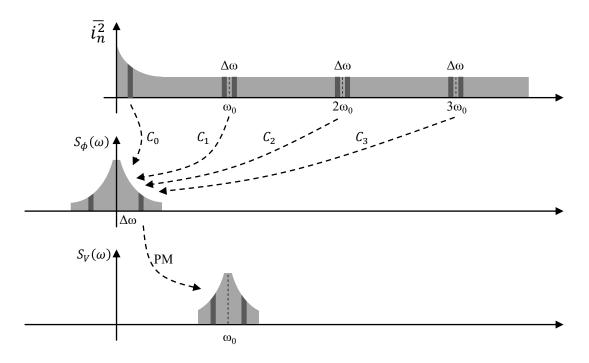

| Figure I.3.12 Conversion of noise to phase fluctuations and phase noise sidebands 64 -       |

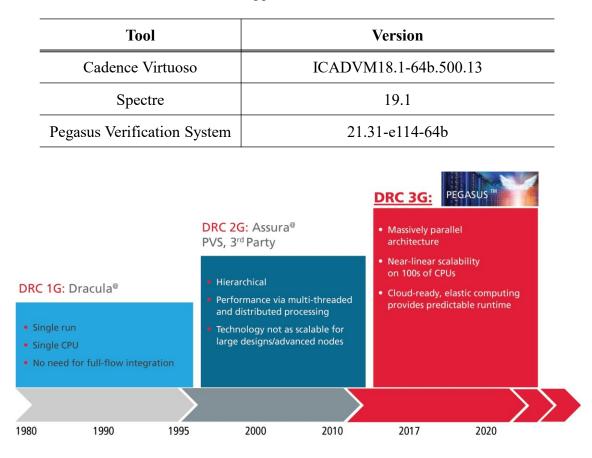

| Figure II.1.1 Third-generation Pegasus Verification System 76 -                              |

| Figure II.1.2 (a) Bulk CMOS versus (b) FD-SOI. (Source: STMicroelectronics) 77 -             |

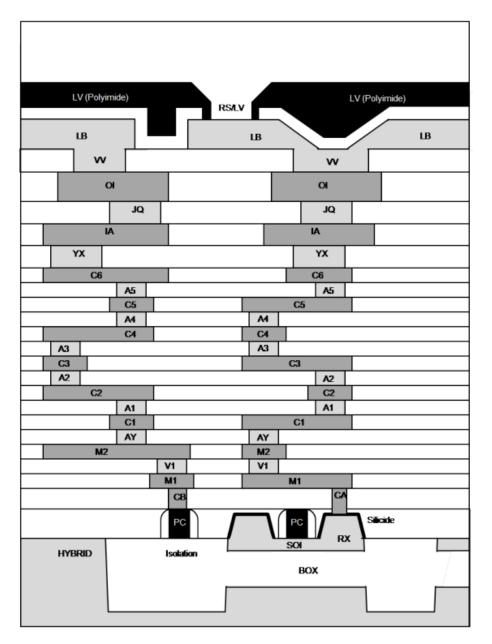

| Figure II.1.3 22FDX cross section example 78 -                                               |

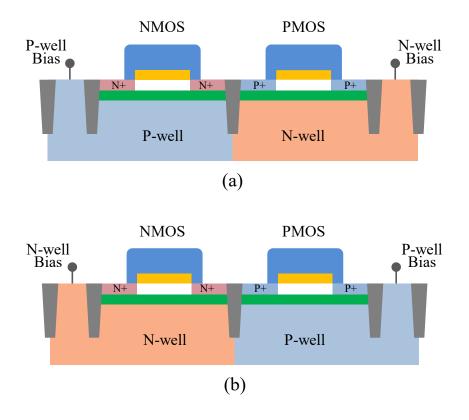

| Figure II.1.4 Cross-section view of (a) conventional well and (b) flipped well 79 -          |

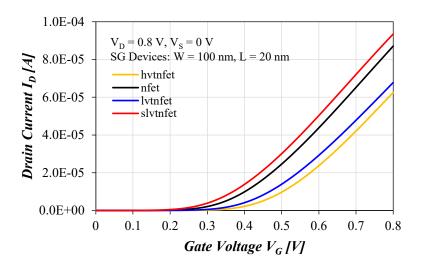

| Figure II.1.5 Threshold voltage for different SG devices 80 -                                |

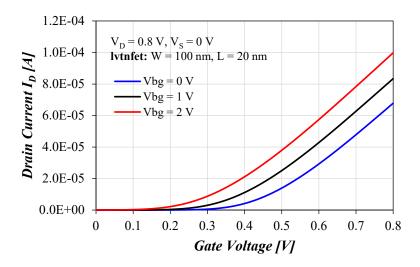

| Figure II.1.6 Threshold voltage for different back-gate voltages 81 -                        |

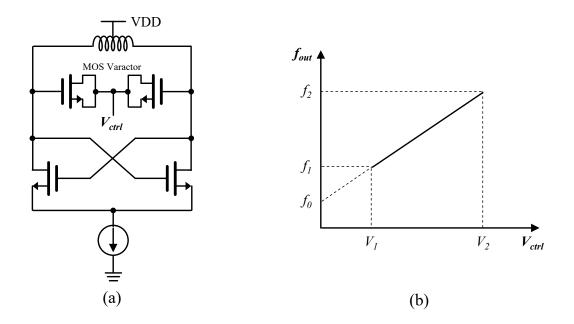

| <b>Figure II.2.1</b> (a) Simplified structure of a typical LC-based VCO using the MOS varactor. |

|-------------------------------------------------------------------------------------------------|

| (b) Frequency-voltage characteristic curve 82 -                                                 |

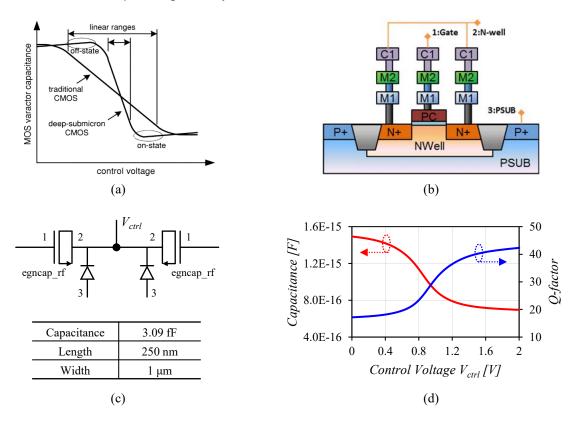

| Figure II.2.2 (a) Idealized C-V curves of a MOS varactor for both a traditional and deep        |

| sub-micrometer CMOS process. (b) Cross-section view of the MOS varactor model. (c)              |

| Differential MOS varactor using the device egncap_rf and its main parameters. (d)               |

| Simulated capacitance and Q-factor versus voltage curves of (c) 83 -                            |

| Figure II.2.3 A conventional RO-based DCO 84 -                                                  |

| Figure II.2.4 RO-based DCO using parallel tri-state inverters 85 -                              |

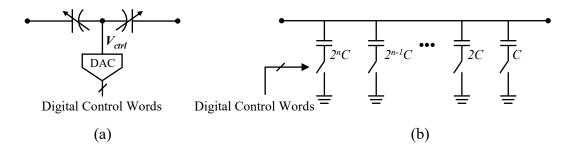

| Figure II.2.5 (a) MOS varactor controlled by the DAC. (b) Binary-weighted switched-             |

| capacitor bank controlled by the digital signal                                                 |

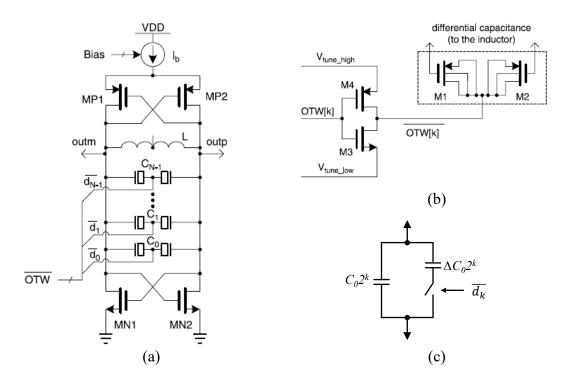

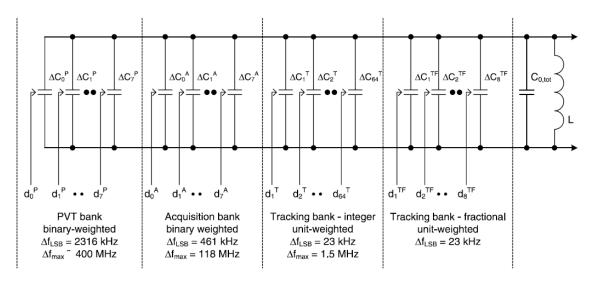

| Figure II.3.1 (a) DCO with discrete tuning controls. (b) Differential PMOS varactor             |

| driven by an inverter. (c) Modeling a binary-weighted switched capacitor 86 -                   |

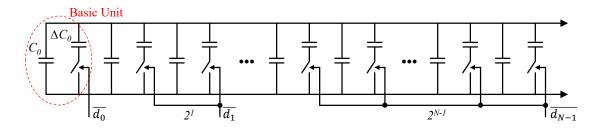

| Figure II.3.2 Binary-weighted switched-capacitor bank of size N 88 -                            |

| Figure II.3.3 LC tank with three-stage switched-capacitor banks 88 -                            |

| Figure II.3.4 (a) Mismatch between two PMOS varactors with different sizes. (b)                 |

| Mismatch between two PMOS varactors with different connections. (c) Mismatch                    |

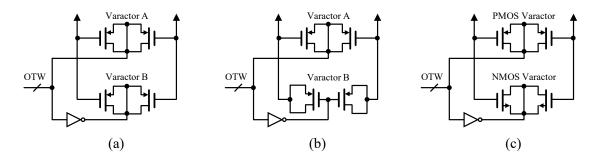

| between a PMOS varactor and a NMOS varactor 90 -                                                |

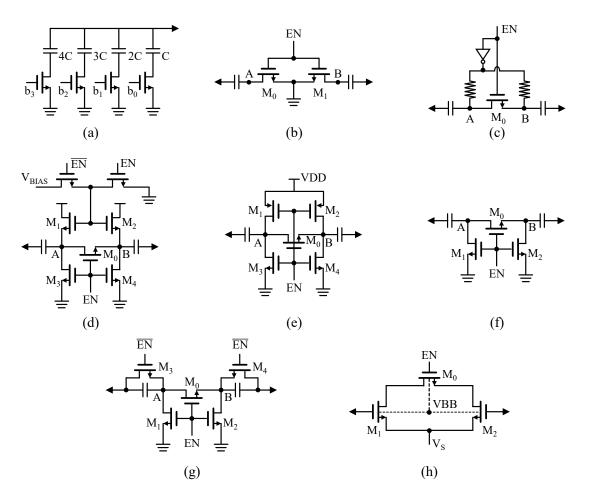

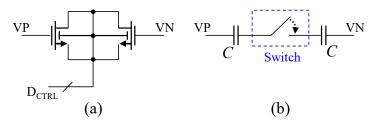

| Figure II.3.5 Common structures of switched capacitors 92 -                                     |

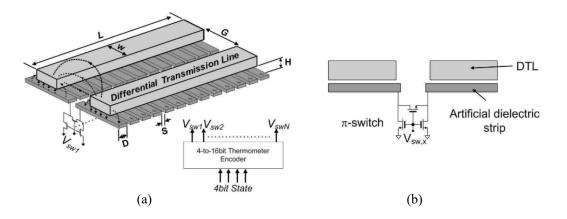

| Figure II.3.6 General DiCAD differential transmission line configuration. (b) Cross-            |

| sectional view of DiCAD differential transmission line strip 94 -                               |

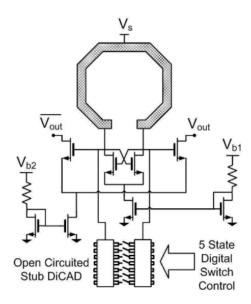

| Figure II.3.7 Schematic of the DiCAD DCO 94 -                                                   |

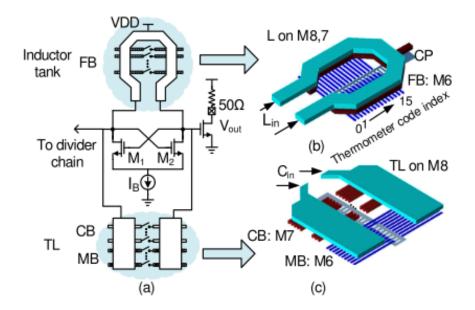

| Figure II.3.8 (a) Schematic of the 60 GHz inductor-based DCO. (b) Inductor-based fine-          |

| tuning bank. (c) Reconfigurable TL for coarse-tuning and medium-tuning                          |

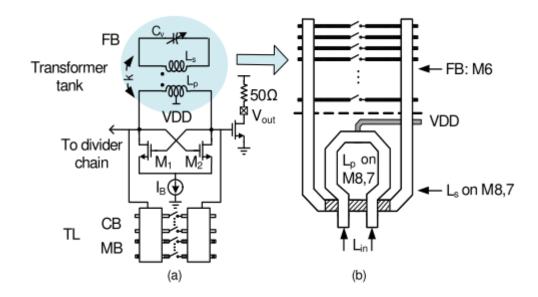

| Figure II.3.9 (a) Schematic of the 60 GHz transformer-based DCO. (b) Transformer-               |

| based fine-tuning bank 96 -                                                                     |

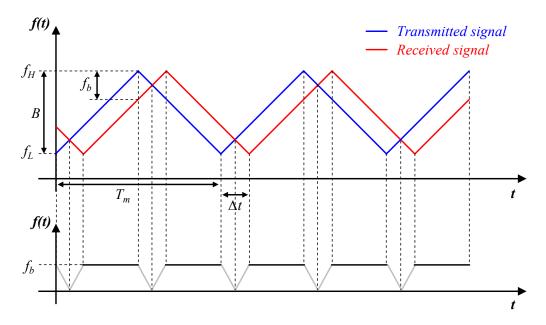

| Figure II.4.1 The principle of FMCW radars with triangular modulation for detecting a           |

| stationary target and the resulting beat signal                                                 |

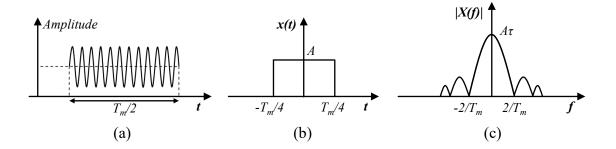

| Figure II.4.2 (a) A solitary rectangular pulse and (b) its spectrum 100 -                       |

| Figure II.4.3 The principle of FMCW radar with triangular modulation for detecting a            |

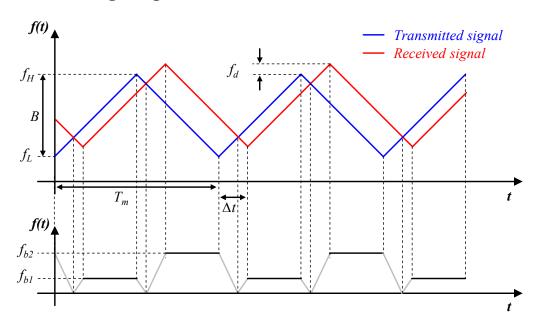

| moving target and the resulting beat signal 101 -                                               |

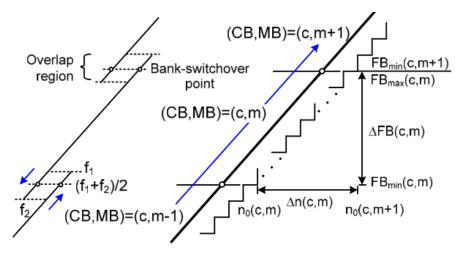

| Figure II.4.4 Gain calibration and linearization technique of multi-bank DCOs 102 -             |

| Figure II.5.1 Commonly used NMOS-only structures of cross-coupled LC DCO. (a)                   |

| Class-B structure. (b) Class-C structure. (c) Class-D structure 106 -                           |

|                                                                                                 |

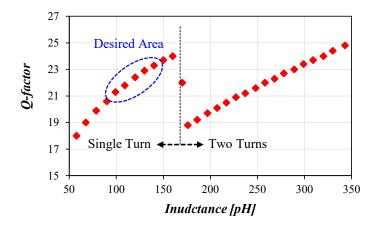

| Figure II.5.2 Typical inductance and Q-factor of a center-tapped inductor at 20 GHz                               |

|-------------------------------------------------------------------------------------------------------------------|

| implemented in the GF' 22 nm FD-SOI process 108 -                                                                 |

| Figure II.5.3 (a) MOS varactor structure commonly used for sub-10 GHz DCOs. (b)                                   |

| Simplified switched-capacitor structure adapted to K-band DCOs 108 -                                              |

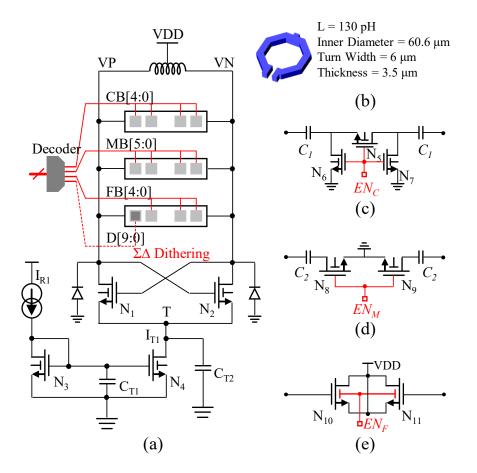

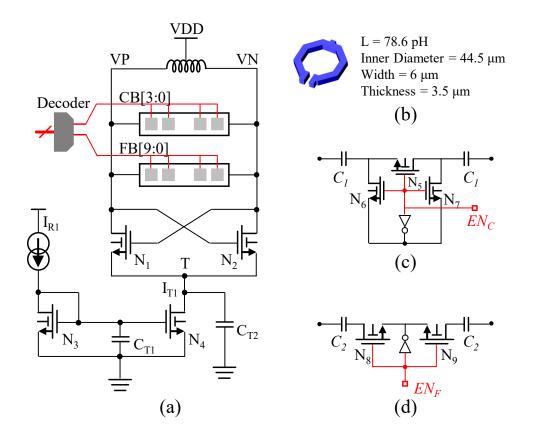

| Figure II.5.4 (a) Block diagram of the proposed T-DCO. (b)Center-tapped inductor and                              |

| its main parameters. (c) Schematic of the coarse-tuning unit. (d) Schematic of the                                |

| medium-tuning unit. (e) Schematic of the fine-tuning unit 110 -                                                   |

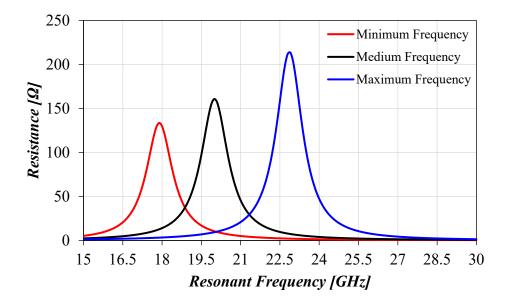

| Figure II.5.5 Real part of the impedance versus the resonant frequency of the LC tank                             |

| 111 -                                                                                                             |

| Figure II.5.6 (a) Pre-layout parasitic model and (b) instance settings for transistors in                         |

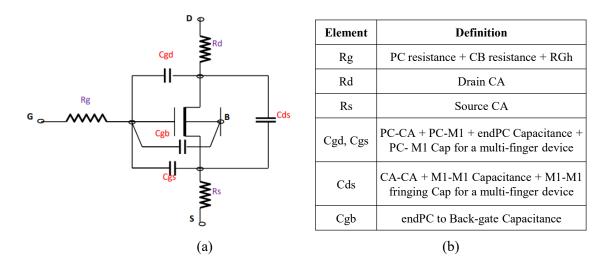

| 22FDX technology 112 -                                                                                            |

| Figure II.5.7 NMOS in N-well (flipped well) with M1 reference plane: (a) cross-section                            |

| view, (b) RF sub-circuit, (c) corresponding labels of the components 113 -                                        |

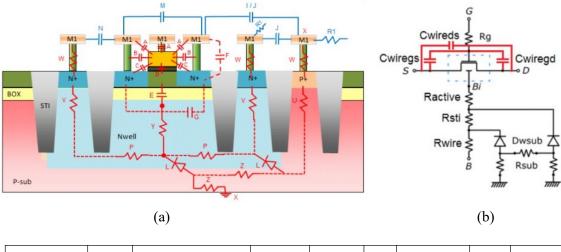

| Figure II.5.8 (a) Typical schematic and (b) truth table of a 3-input 7-output binary-to-                          |

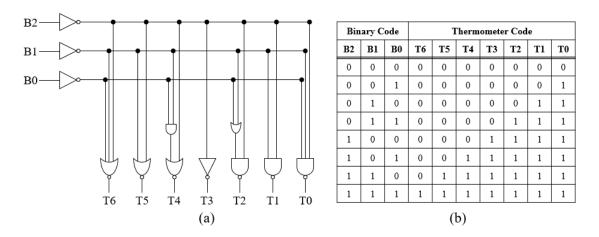

| thermometer decoder 114 -                                                                                         |

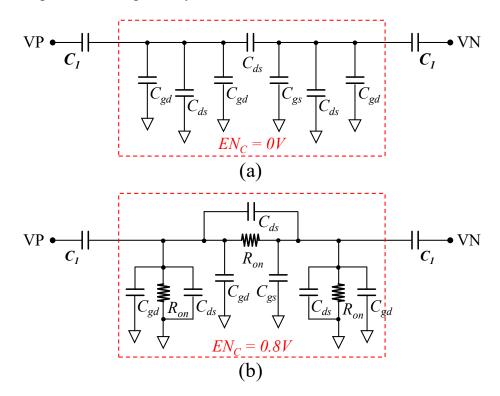

| Figure II.5.9 Equivalent schematic of the coarse-tuning unit: (a) in the OFF-state, (b) in                        |

| the ON-state 115 -                                                                                                |

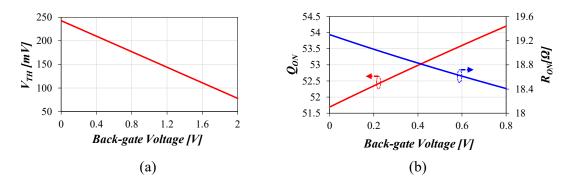

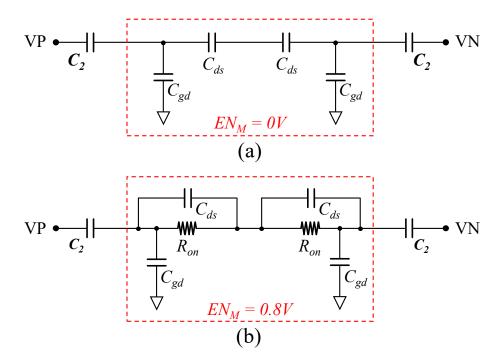

| Figure II.5.10 (a) Threshold voltage $V_{TH}$ of $N_{5\mathchar`-7}$ versus back-gate voltage. (b) $Q_{ON}$ and   |

| R <sub>ON</sub> of the coarse-tuning unit versus back-gate voltage 116 -                                          |

| Figure II.5.11 Equivalent schematic of the medium-tuning unit: (a) in the OFF-state, (b)                          |

| in the ON-state 117 -                                                                                             |

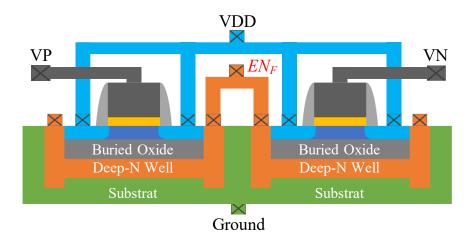

| Figure II.5.12 Cross-section view of the novel fine-tuning unit 119 -                                             |

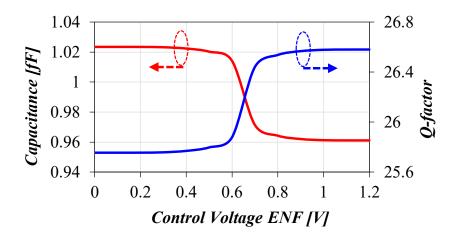

| Figure II.5.13 Capacitance and Q-factor of the proposed fine-tuning unit versus control                           |

| voltage EN <sub>F.</sub> 119 -                                                                                    |

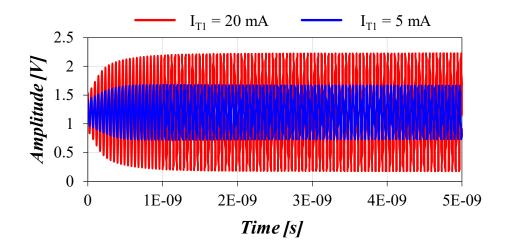

| Figure II.5.14 Output waveforms for tail currents $(I_{T1})$ of 5 mA and 20 mA, respectively.                     |

| Figure II.5.15 Drain-source current (Ids) waveforms of N <sub>1,2</sub> for tail currents (I <sub>T1</sub> ) of 5 |

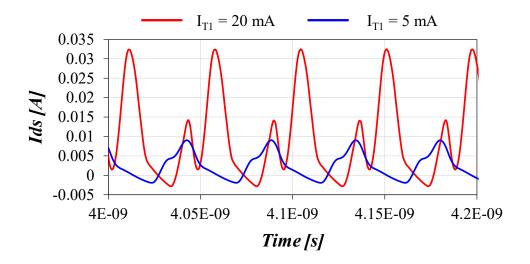

| mA and 20 mA, respectively 121 -                                                                                  |

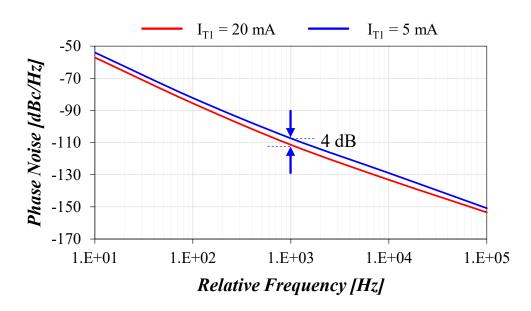

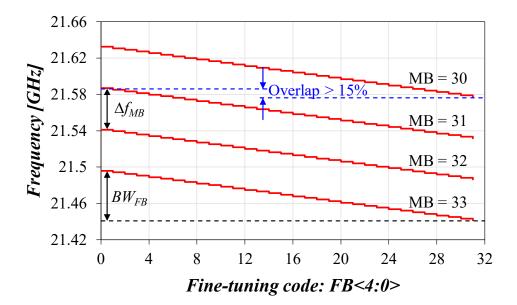

| <b>Figure II.5.16</b> PN performances of the T-DCO for tail currents $(I_{T1})$ of 5 mA and 20 mA,                |

| respectively 121 -                                                                                                |

| Figure II.5.17 Frequency-code characteristics of the medium-tuning bank and the fine-                             |

| tuning bank when $CB = 16$                                                                                        |

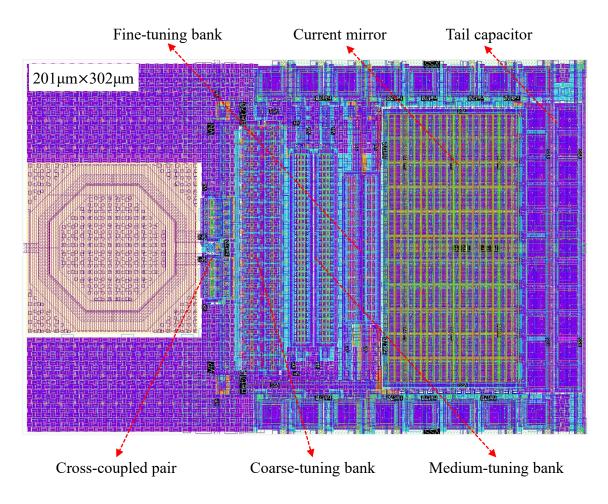

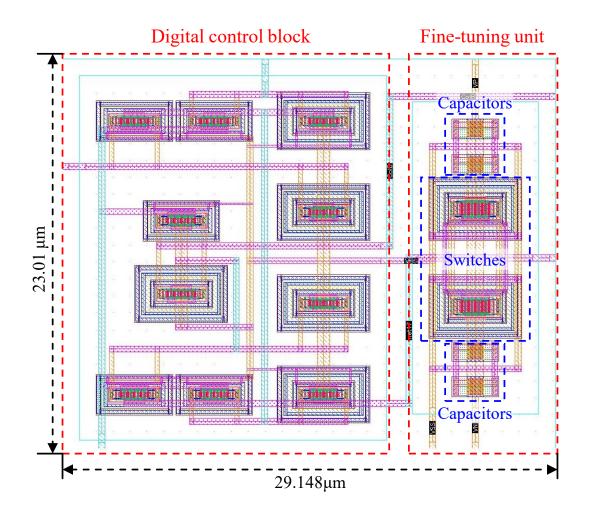

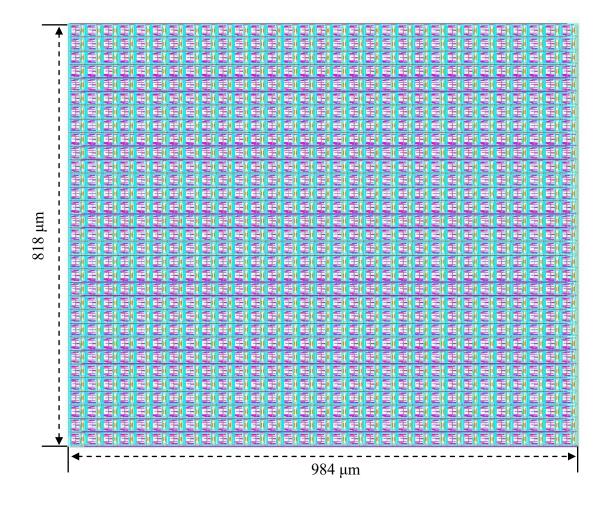

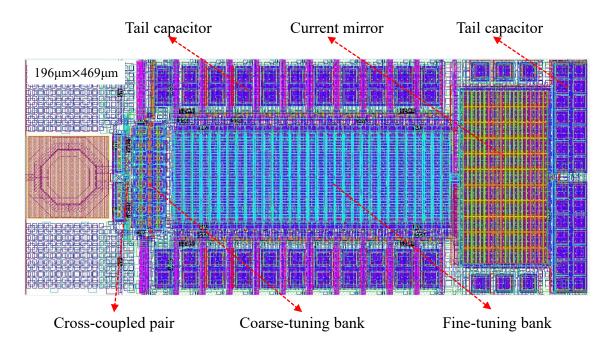

| Figure II.5.18 Top layout view of the proposed T-DCO 123 -                                                        |

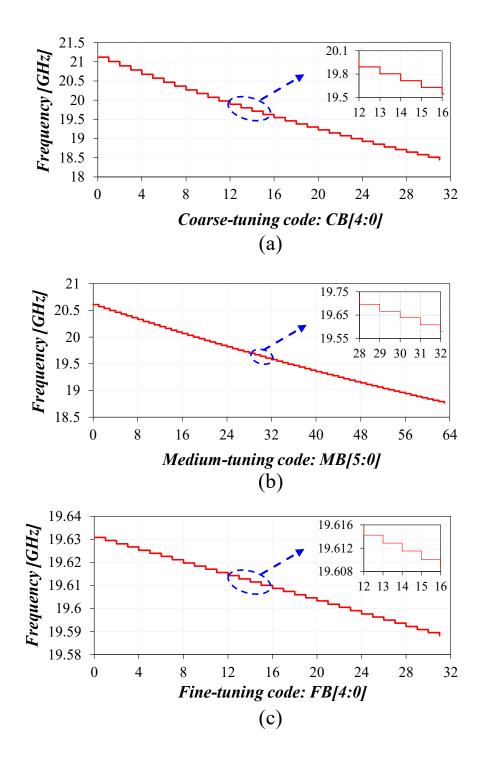

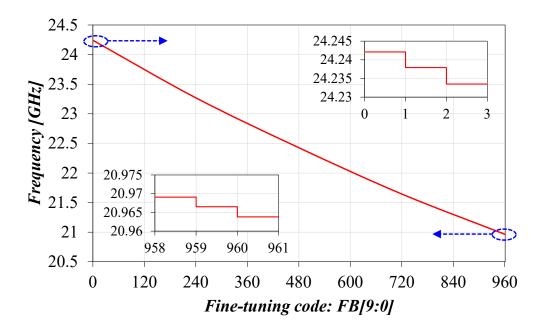

| Figure II.5.19 Frequency-code characteristics of (a) the coarse-tuning bank, (b) the          |

|-----------------------------------------------------------------------------------------------|

| medium-tuning bank and (c) fine-tuning bank 124 -                                             |

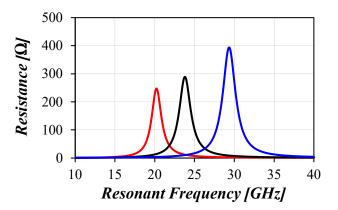

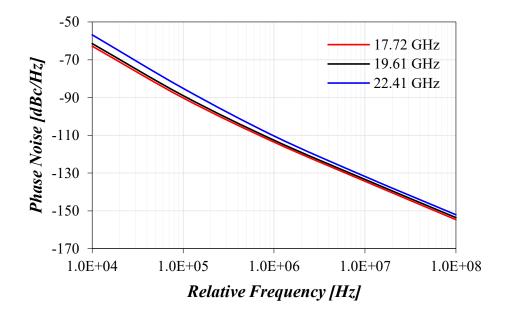

| Figure II.5.20 Simulated phase noise plot at the minimum frequency of 17.72 GHz, the          |

| medium frequency of 19.61 GHz, and the maximum frequency of 22.41 GHz 125 -                   |

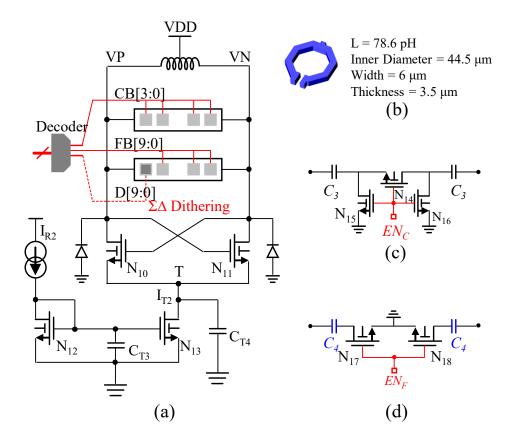

| Figure III.2.1 (a) Block diagram of the proposed D-DCO.1. (b) Center-tapped inductor          |

| and its main parameters. (c) Schematic of the coarse-tuning unit. (d) Schematic of the        |

| fine-tuning unit 139 -                                                                        |

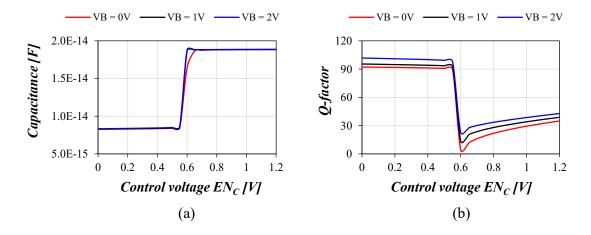

| Figure III.2.2 Pre-layout simulation results of the coarse-tuning unit. (a) Capacitance       |

| values and (b) Q-factor versus control voltage $EN_C$ when the back-gate voltage (VB) is 0    |

| V, 1V, 2V, respectively 140 -                                                                 |

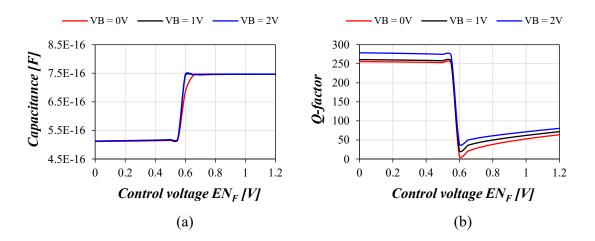

| Figure III.2.3 Pre-layout simulation results of the fine-tuning unit. (a) Capacitance values  |

| and (b) Q-factor versus control voltage $EN_F$ when the back-gate voltage is 0 V, 1V, 2V,     |

| respectively 141 -                                                                            |

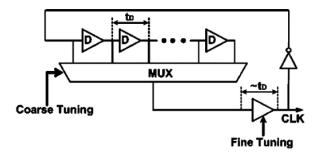

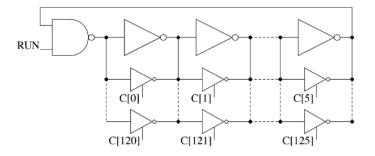

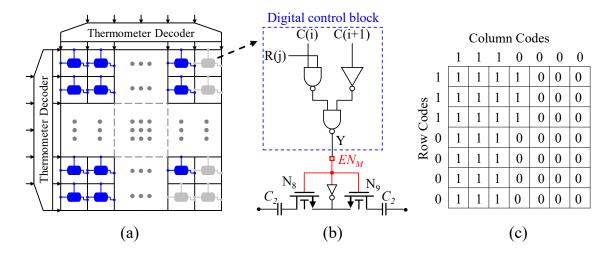

| Figure III.2.4 Schematic of the 10-bit fine-tuning bank 142 -                                 |

| Figure III.2.5 (a) Simplified array control architecture of the fine-tuning bank, (b) digital |

| control block implementation, and (c) example of output logical values 143 -                  |

| Figure III.2.6 Real part of the impedance versus the resonant frequency of the LC tank.       |

| 144 -                                                                                         |

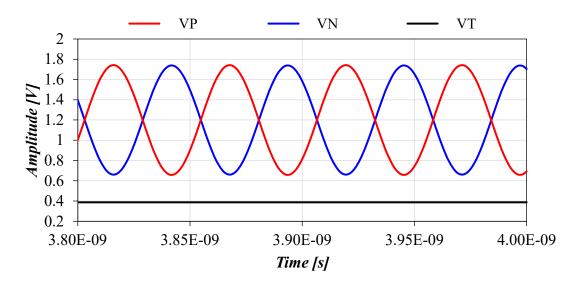

| Figure III.2.7 Output oscillation waveforms of the D-DCO.1 145 -                              |

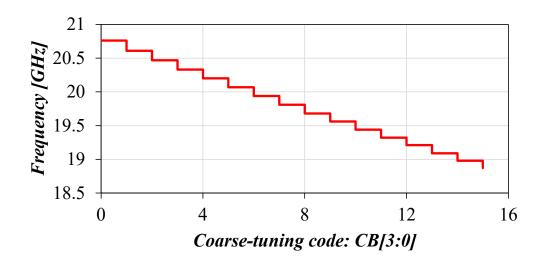

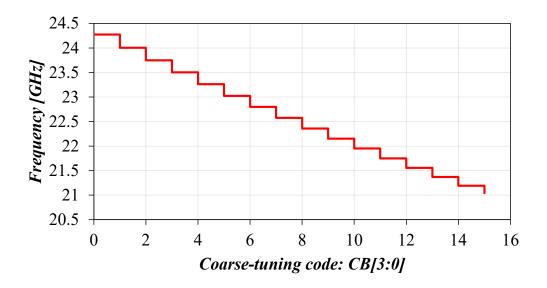

| Figure III.2.8 Frequency-code characteristic of the coarse-tuning bank when the fine-         |

| tuning code is 481 146 -                                                                      |

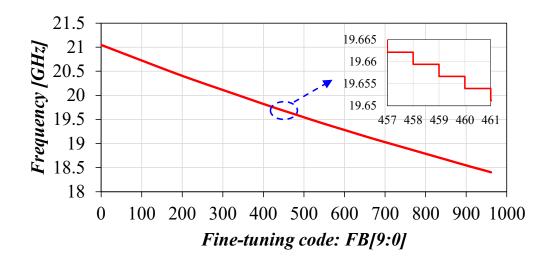

| Figure III.2.9 Frequency-code characteristic of the fine-tuning bank when the coarse-         |

| tuning code is 8 146 -                                                                        |

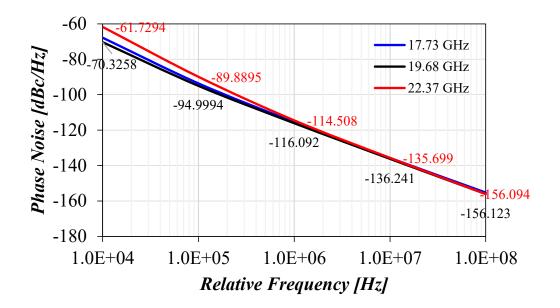

| Figure III.2.10 Pre-layout simulated PN at the minimum frequency of 17.73 GHz, the            |

| medium frequency of 19.68 GHz, and the maximum frequency of 22.37 GHz 147 -                   |

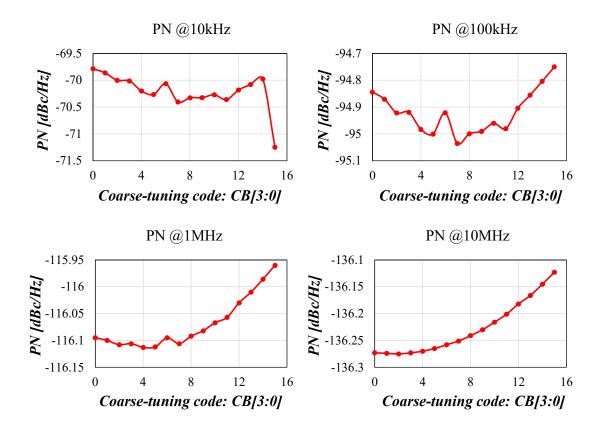

| Figure III.2.11 PN variations versus the coarse-tuning codes                                  |

| Figure III.2.12 PN variations versus the fine-tuning codes 148 -                              |

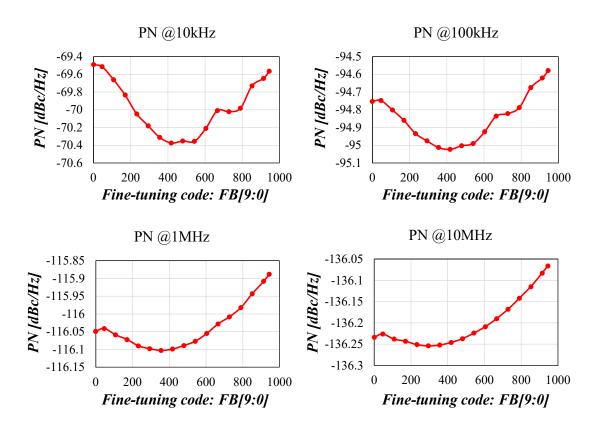

| Figure III.2.13 Frequency and PN variations versus different processes 149 -                  |

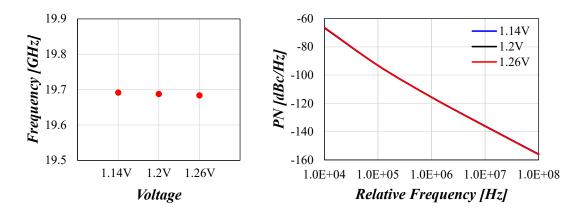

| Figure III.2.14 Frequency and PN variations versus different supply voltages 149 -            |

| Figure III.2.15 Frequency and PN variations versus different temperatures 150 -               |

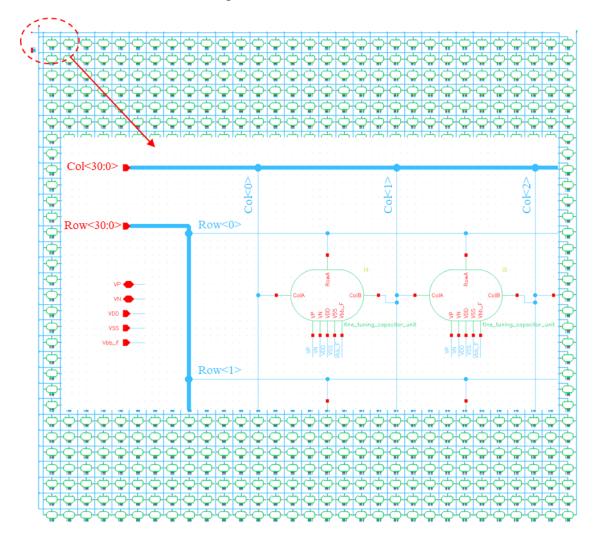

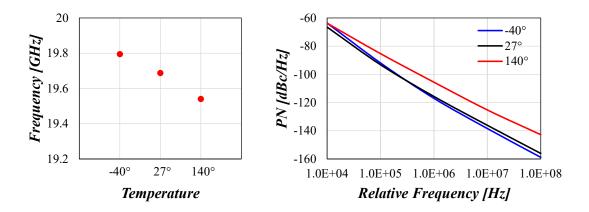

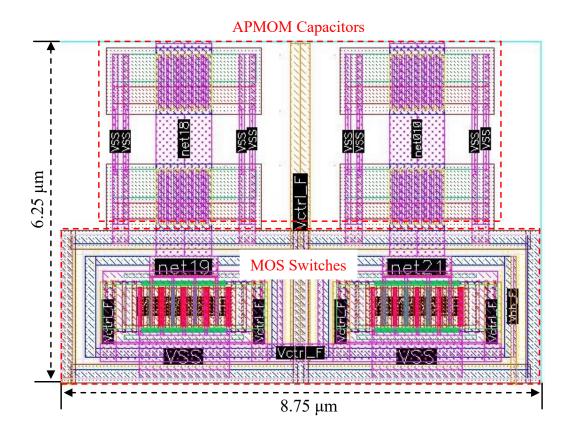

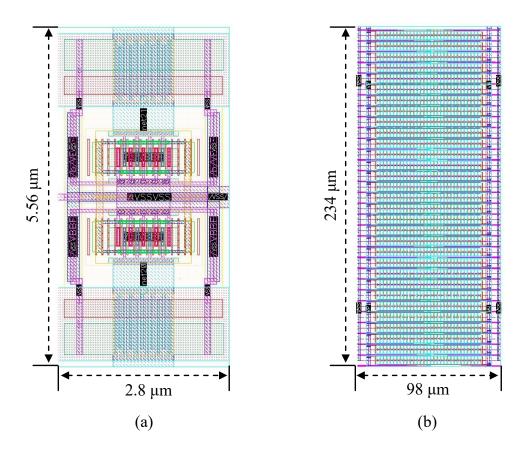

| Figure III.2.16 Layout of a single fine-tuning unit with a digital control block 152 -        |

| Figure III.2.17 Internal connection of partial fine-tuning bank                               |

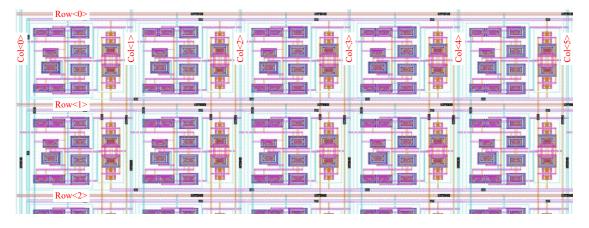

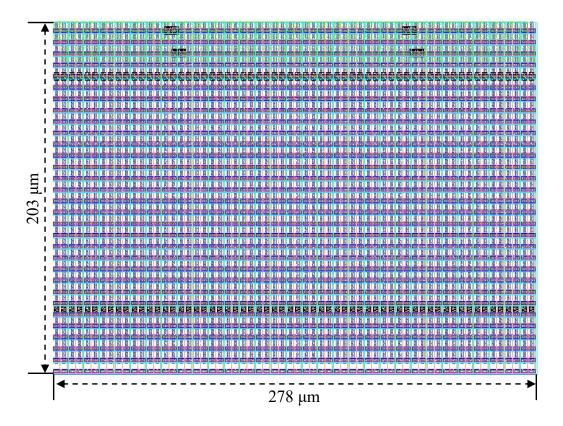

| Figure III.2.18 Layout view of the 10-bit fine-tuning bank 153 -                              |

| Figure III.2.19 New fine-tuning unit without the digital control block 154 -                 |

|----------------------------------------------------------------------------------------------|

| Figure III.2.20 New 10-bit fine-tuning bank without the digital control block 154 -          |

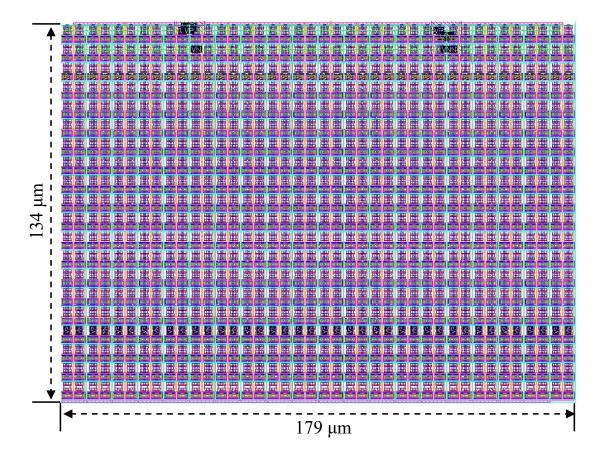

| Figure III.2.21 New resized fine-tuning bank with $20 \times 20$ fine-tuning units 156 -     |

| Figure III.3.1 (a) Block diagram of the proposed D-DCO.2. (b)Center-tapped inductor          |

| and its main parameters. (c) Schematic of the coarse-tuning unit. (d) Schematic of the       |

| fine-tuning unit 158 -                                                                       |

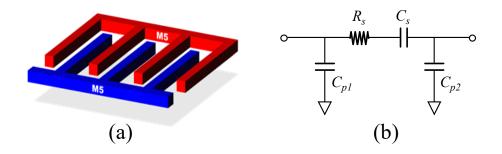

| Figure III.3.2 (a) Structure of the novel customized MOM capacitor. (b) Its equivalent $\pi$ |

| model 160 -                                                                                  |

| Figure III.3.3 (a) New fine-tuning unit with the customized capacitor. (b) New 10-bit        |

| fine-tuning bank 160 -                                                                       |

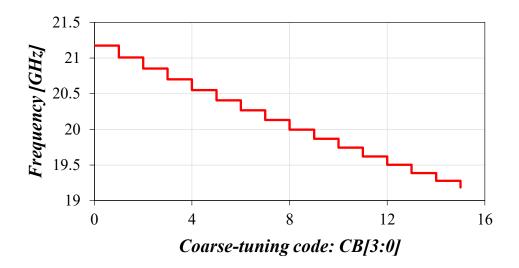

| Figure III.3.4 Frequency-code curve of the coarse-tuning bank when $FB = 481162$ -           |

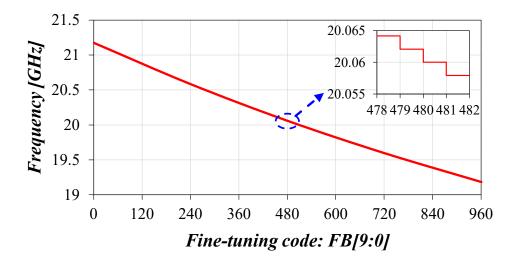

| Figure III.3.5 Frequency-code curve of the fine-tuning bank when $CB = 8$ 162 -              |

| Figure III.3.6 Top layout view of the proposed D-DCO.2 163 -                                 |

| Figure III.3.7 Frequency-code curve of the coarse-tuning bank when $FB = 481164$ -           |

| Figure III.3.8 Frequency-code curve of the fine-tuning bank when $CB = 8$ 164 -              |

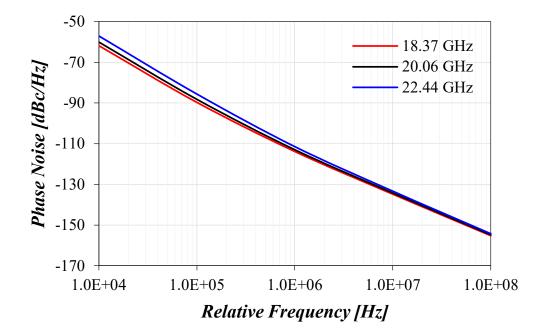

| Figure III.3.9 Simulated phase noise plot at the minimum frequency of 18.37 GHz, the         |

| medium frequency of 20.06 GHz, and the maximum frequency of 22.44 GHz 165 -                  |

|                                                                                              |

# **List of Tables**

| Table I.1.1 Standard radar-frequency letter band nomenclature.         5 -              |

|-----------------------------------------------------------------------------------------|

| Table I.1.2 Comparison of sensors in ADAS.       19 -                                   |

| Table I.1.3 Automotive radar characteristics in 76 – 81 GHz frequency band 21 -         |

| Table I.1.4 Cutoff frequencies for various semiconductor technologies 22 -              |

| Table I.1.5 Performance summary of 76 – 81 GHz automotive radars         31 -           |

| Table II.1.1 Supported EDA Tool Versions.    76 -                                       |

| Table II.1.2 Summary of different devices in the PDK 80 -                               |

| Table II.3.1 Performances summary of LC-based DCOs.         97 -                        |

| Table II.5.1 DCO Specifications.    105 -                                               |

| Table II.5.2 Main parameters of the proposed T-DCO.       111 -                         |

| Table II.5.3 Parasitic capacitances of MOS transistors.         114 -                   |

| Table II.5.4 Post-layout simulated T-DCO performances for the three most                |

| representative PVT configurations 125 -                                                 |

| Table II.5.5 T-DCO performances vs DCO specifications.         126 -                    |

| Table II.5.6 Comparison with state-of-the-art K-band DCOs         127 -                 |

| Table III.2.1 Main parameters of the proposed D-DCO.1         140 -                     |

| Table III.2.2 Truth table of the digital control block.       143 -                     |

| Table III.2.3 DC operating points of the transistors N <sub>1-4</sub> .         144 -   |

| Table III.2.4 D-DCO.1 performances vs DCO specifications         151 -                  |

| Table III.2.5 Post-layout simulation results with RC extraction of the new fine-tuning  |

| unit and the new 10-bit fine-tuning bank with $31 \times 31$ fine-tuning units 155 -    |

| Table III.2.6 Post-layout simulation results of the new resized fine-tuning bank 156 -  |

| Table III.3.1 Main parameters of the proposed D-DCO.2         158 -                     |

| Table III.3.2 DC operating points of the transistors N <sub>10-13</sub> .       - 161 - |

| Table III.3.3 Post-layout simulated D-DCO.2 performances for the three most             |

| representative PVT configurations 165 -                                                 |

| Table III.3.4 D-DCO.2 performances vs DCO specifications.       166 -                   |

| Table III.3.5 Comparison with the state-of-the-art K-band DCOs.         167 -           |

# List of Abbreviations

| ACC    | Adaptive Cruise Control                         |

|--------|-------------------------------------------------|

| ADAS   | Advanced Driver Assistance Systems              |

| ADC    | Analog-to-Digital Converter                     |

| ADPLL  | All-Digital Phase-Locked Loop                   |

| AM     | Amplitude Modulation                            |

| BiCMOS | Bipolar Complementary Metal-Oxide-Semiconductor |

| CMOS   | Complementary Metal-Oxide-Semiconductor         |

| CPPLL  | Charge-Pump Phase-Locked-Loop                   |

| DAC    | Digital-to-Analog Converter                     |

| DCO    | Digitally Controlled Oscillator                 |

| DSP    | Digital Signal Processor                        |

| EDA    | Electronic Design Automation                    |

| FD-SOI | Fully Depleted Silicon-On-Insulator             |

| FinFET | Fin Field-Effect Transistor                     |

| FMCW   | Frequency-Modulated Continuous-Wave             |

| FoM    | Figure-of-Merit                                 |

| FoMT   | Figure-of-Merit including FTR                   |

| FSCW   | Frequency-Stepped Continuous-Wave               |

| FSK    | Frequency Shift-Keying                          |

| FTR    | Frequency-Tuning Range                          |

| GaAs   | Gallium Arsenide                                |

| GaN    | Gallium Nitride                                 |

| HCI    | Hot-Carrier Injection                           |

| HF     | High Frequency                                  |

| IC     | Integrated Circuit                              |

| InP    | Indium Phosphide                                |

| LDO    | Low-dropout Regular                             |

| LFM    | Linear Frequency Modulation                     |

| LNA    | Low-Noise Amplifier                             |

| LPF    | Low-Pass Filter                                 |

| LRR      | Long-Range Radar                        |  |  |  |

|----------|-----------------------------------------|--|--|--|

| MMIC     | Monolithic Microwave Integrated Circuit |  |  |  |

| MRR      | Medium-Range Radar                      |  |  |  |

| OTH      | Over-The-Horizon Radar                  |  |  |  |

| PA       | Power Amplifier                         |  |  |  |

| PCB      | Printed Circuit Board                   |  |  |  |

| PFD      | Phase-Frequency Detector                |  |  |  |

| PLL      | Phase-Locked Loop                       |  |  |  |

| PM       | Phase Modulation                        |  |  |  |

| PN       | Phase Noise                             |  |  |  |

| PVT      | Process, Voltage, and Temperature       |  |  |  |

| Q-factor | Quality factor                          |  |  |  |

| RF       | Radio Frequency                         |  |  |  |

| RO       | Ring Oscillator                         |  |  |  |

| RX       | Receiver                                |  |  |  |

| SDM      | Sigma-Delta Modulator                   |  |  |  |

| SiC      | Silicon-Carbide                         |  |  |  |

| SiGe     | Silicon-Germanium                       |  |  |  |

| SoC      | System-on-Chip                          |  |  |  |

| SRR      | Short-Range Radar                       |  |  |  |

| TDC      | Time-to-Digital Converter               |  |  |  |

| TX       | Transmitter                             |  |  |  |

| UHF      | Ultra-High Frequency                    |  |  |  |

| VCO      | Voltage Controlled Oscillator           |  |  |  |

| VHF      | Very-High Frequency                     |  |  |  |

|          |                                         |  |  |  |

# **General Introduction**

As one of the core sensors for advanced driver assistance systems (ADAS), the automotive radar is becoming mainstream for applications such as obstacle detection and automatic cruise control. Meanwhile, the millimeter-wave (mm-W) band, 76 - 81 GHz, is promised to be a long-term solution for automotive radar development as it allows for a smaller antenna size, uncrowded spectrum, larger bandwidth, etc. In particular, the frequency-modulated continuous-wave (FMCW) automotive radar greatly benefits from the high carrier frequency and the large bandwidth to improve its angular and radial resolution, which is also inseparable from the linear triangular or sawtooth chirp generated by the phase-locked loop (PLL).

However, some bottlenecks of the analog PLL are revealed at deep nanoscale CMOS nodes. For instance, the chip area of PLL does not decrease significantly with process scaling, and it is difficult to migrate it from one process to another, leading to long design cycles and high costs. Based on these facts, implementing PLLs like digital circuits has recently been a hot research topic, i.e., all-digital phase-locked loop (ADPLL). Compared to the analog PLL, the ADPLL shows excellent prospects in terms of low cost, small area, low power consumption, easy integration, and high compatibility with other digital baseband circuits. As one of the essential building blocks of ADPLLs, Digitally Controlled Oscillators (DCO) are employed to generate a periodic waveform with a frequency that can be digitally controlled, making them a versatile and flexible alternative to traditional analog Voltage-Controlled Oscillators (VCO). While numerous DCOs operating at frequencies below 10 GHz have been published so far, reports of those operating above 10 GHz are scarce. There is even less material on the design challenges of K-band DCOs and the solutions to address them.

In such a context, the objective of this thesis is not only to investigate the feasibility of designing a K-band DCO in an advanced 22 nm FD-SOI process, but also the proposed DCOs need to meet stringent specifications to be suitable for 76 - 81 GHz FMCW automotive radars, such as achieving low phase noise, wide tuning range, and high frequency resolution simultaneously, which is quite challenging.

Chapter I aims to comprehensively review the research background related to automotive radars, frequency synthesis techniques, and oscillators. We will begin by presenting an overview of the principles, structures, categories, operating bands, and processes relevant to automotive radars, followed by a brief review of the research conducted on 76 - 81 GHz automotive radars. This will highlight the significant commercial value of this research topic. Next, we will review some common frequency synthesis techniques and emphasize the basic theory and main modules of PLLs and ADPLLs, while also comparing them to show the potential of ADPLLs for future applications. Finally, we will introduce the theory and types of oscillators and conduct a brief analysis of their phase noise performances. These are crucial factors in DCO design and serve as the theoretical foundation for the discussion in later chapters.

In Chapter II, we will begin by briefly introducing GlobalFoundries' 22 nm FD-SOI process, including the flipped well structure, the back-gate biasing technique, and the available components in the library. We will then compare different DCO topologies, focusing on LC-based DCOs, as well as classical frequency tuning techniques. We will also briefly introduce the fundamental theory of FMCW radars and DCO gain calibration for chirp linearity. Our main focus will be on the design and implementation of a K-band low-phase-noise triple-bank DCO (T-DCO) for 76 - 81 GHz automotive radars. We will not only discuss the design difficulties and important considerations, but also provide a theoretical analysis and a detailed presentation of the switched-capacitor structure used, along with a novel back-gate-based fine-tuning structure. Finally, we will compare the post-layout simulation results of the T-DCO with the specifications and other state-of-the-art DCOs to demonstrate the feasibility of designing a K-band DCO in a 22 nm FD-SOI process. This will further solidify the potential of using this process for high-frequency applications such as automotive radars.

In Chapter III, we will first briefly elucidate the frequency overlap problem that arises in a multi-bank DCO, as well as the complex frequency calibration and linearization problems. In order to address these issues at the design level rather than only at the algorithmic level, we will present a new dual-bank DCO (D-DCO) prototype that has seldom been disclosed before. We will describe the circuit implementation in detail, along with the key considerations and design challenges. Finally, we will compare the post-layout simulation results of the D-DCO with the specifications to verify its compliance with the 76 – 81 GHz automotive radar requirements.

# **CHAPTER I**

# **Introduction to Research Work**

This research work aims to design a high-performance digitally controlled oscillator (DCO). It is a core module of an all-digital phase-locked loop (ADPLL) that will be used in 76 - 81 GHz automotive radars. Therefore, this chapter focuses on presenting and reviewing the background in the existing literature related to the research purpose. In Section I.1, we will briefly introduce the development footprint, main architectures and principles of automotive radars. In Section I.2, the fundamentals of frequency synthesizers will be elaborated, followed by an introduction and comparison of PLLs and ADPLLs. In Section I.3, we will mainly present the theory and types of oscillators, and finally their phase noise is analyzed.

# I.1. Automotive Radar

# I.1.1. Radar Fundamentals

Radar is an acronym standing for Radio Detection and Ranging. As the name implies, it uses radio/electromagnetic (EM) waves to detect the targets. The first practical radar was invented by the British physicist Robert Watson-Watt and his team in 1935, and a flying bomber was clearly detected in their experiment. During the World War II, radar was developed explosively in the military field. Today, radar plays an important role in our daily life owing to its wide variety of applications in many fields:

- Military: airborne early warning radar, airborne ground surveillance radar, antiaircraft artillery radar, missile guidance radar, fire control radar;

- Air traffic control and navigation: airport surveillance radar, precision approach;

- Meteorology and geography: weather (rain, fog, snow, hail, etc.) surveillance radar, wind profiling radar, millimeter cloud radar, imaging radar, 3D radar;

- Traffic and road safety: radar speed gun, anti-collision radar, blind-spot detection radar, car parking/reversing radar, automatic cruise control system.

Such diverse applications are inseparable from the inherent properties of the EM waves used in radar. For example, EM waves propagate at the speed of light ( $c = 3 \times 10^8$  m/s) and are highly immune to the environment and weather conditions, making radar capable of rapidly determining the location, speed, orientation, etc., of aircraft, ships or other invisible objects at long distances. In addition, radar often works together with different types of sensors to provide better and more comprehensive performances, among which ultrasonic and optical sensors are commonly used, especially in the automotive industry, which is the theoretical basis for autonomous driving technology.

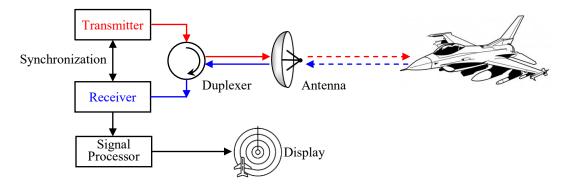

Figure I.1.1 Simplified block diagram of a radar system.

A simplified block diagram of a radar system is shown in Figure I.1.1. Although the details of radar systems are not identical, their sub-modules basically contain a transmitter, an antenna, a receiver, a signal processor and a display. The radio frequency (RF) signal of interest is generated by the transmitter and amplified to a sufficient power level to reach the desired maximum range detection, and then emitted outward to a target through an antenna. Owing to the atmospheric attenuation of signal propagation, a small portion of the signals reflected by the target (also called an echo) can return to the antenna, where they are amplified and demodulated by the receiver. The target characteristics can then be extracted and displayed by processing these received signals. Moreover, it is possible to use a single antenna for both transmission and reception, and the antenna can be switched alternatively between the transmitter and receiver through a duplexer (or circulator). This switching is necessary because it prevents powerful transmit signals from entering the sensitive receiver. Otherwise, the receiver may be damaged or destroyed.

## I.1.1.1. Radar-Frequency Bands

| Band        | Nominal frequency       | Specific frequency ranges for radar based on ITU assignments |                                 |                   |  |

|-------------|-------------------------|--------------------------------------------------------------|---------------------------------|-------------------|--|

| designation | range                   | Region 1                                                     | Region 2                        | Region 3          |  |

| HF          | 3 – 30 MHz              |                                                              |                                 |                   |  |

| VHF         | 30 – 300 MHz            | None                                                         | 138 – 144 MHz                   | 223 – 230 MHz     |  |

|             |                         |                                                              | 216 – 225 MHz                   |                   |  |

| UHF         | 300 – 1000 MHz          | 420 – 450 MHz                                                |                                 |                   |  |

|             | 500 - 1000 WILLZ        | 890 – 942 MHz                                                |                                 |                   |  |

| L           | $1-2 \; GHz$            | 1215 – 1400 MHz                                              |                                 |                   |  |

| S           | 2 – 4 GHz               | 2300 – 2500 MHz                                              |                                 |                   |  |

|             | 2 – 4 GHZ               | $2700-3600 \; \text{MHz}$                                    | 2700 - 3                        | 700 MHz           |  |

| С           | 4 – 8 GHz               | 4200 – 4400 MHz                                              |                                 |                   |  |

|             | 4 – 8 UHZ               | $5250-5850\ MHz$                                             | 5250 - 59                       | 925 MHz           |  |

| Х           | 8 – 12 GHz              | 8.5 . 10.68 GHz                                              |                                 |                   |  |

| Ku          | 12 – 18 GHz             | 13.4 – 14 GHz                                                |                                 |                   |  |

|             |                         |                                                              | $15.4-17.7 \; \mathrm{GHz}$     |                   |  |

| K           | 18 – 27 GHz             | 24.05 – 24.25 GHz                                            | $24.05 - 24.25 \; \mathrm{GHz}$ | 24.05 – 24.25 GHz |  |

|             |                         |                                                              | 24.65 – 24.75 GHz               |                   |  |

| Ka          | $27-40 \; GHz$          | 33.4 – 36 GHz                                                |                                 |                   |  |

| V           | $40-75 \; \mathrm{GHz}$ | 59 – 64 GHz                                                  |                                 |                   |  |

| W           | 75 – 110 GHz            | 76 – 81 GHz                                                  |                                 |                   |  |

|             | 75 – 110 GHZ            | 92 – 100 GHz                                                 |                                 |                   |  |

| mm          | 110 – 300 GHz           | 136 – 148.5 GHz                                              |                                 |                   |  |

|             |                         | 151.5 – 155.5 GHz                                            |                                 |                   |  |

|             |                         | 231.5 – 235 GHz                                              |                                 |                   |  |

|             |                         | 238 – 248 GHz                                                |                                 |                   |  |

| THz         | 300 – 1000 GHz          |                                                              | 300 – 3000 GHz                  |                   |  |

Table I.1.1 Standard radar-frequency letter band nomenclature.

The characteristics and applications of radars are mainly determined by their operating frequencies, and most radar systems have a frequency range from approximately 3 MHz to 300 GHz, which means that the wavelengths of the emitted electromagnetic waves are between 1 mm and 100 m ( $\lambda = c/f$ , where  $\lambda$  is the wavelength, c is the speed of light, and f is the carrier frequency). In order to distinguish such wide radar-frequency bands, radar systems engineers have used band letter designations as a short notation for describing the operating frequencies. The IEEE standard radar-frequency letter band nomenclature is given in Table I.1.1 [I-1]. The band designations mainly include HF, VHF, UHF, L, S, C, X, Ku, K, Ka, V, W, mm, and THz. Moreover, some specific bands are assigned for radar by the International Telecommunication Union (IUT) depending on the regions.

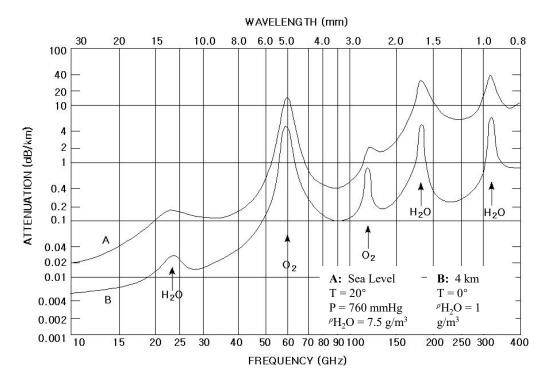

Figure I.1.2 illustrates the atmospheric absorption versus frequency at sea level and 4 km altitude for water density of 7.5 g/m3 and 1 g/m3, respectively [I-2], [I-3]. It should be noted that the major atmospheric constituents absorbing radar energy are oxygen ( $O_2$ ), water ( $H_2O$ ) and other gaseous molecules, the absorption is usually neglected at frequencies of 300 MHz and lower, but becomes increasingly important at mm-Wave frequencies.

Figure I.1.2 Atmospheric absorption at altitudes of sea level and 4 km.

The main factors affecting the choice of the frequency band for radars can be summarized as: usage scenario, antenna size, detection distance, resolution, atmospheric attenuation, available bandwidth, process and cost, and so on [I-4]. Generally, the radars in HF, VHF and UHF bands are commonly used for ultra-long-range detection, such as tracking and searching for satellites and ballistic missiles, because of the low atmospheric attenuation. In addition, radars below 300 MHz can detect targets beyond the horizon using the refractive effect of the ionosphere on electromagnetic waves, known as over-the-horizon radar (OTH). However, the spectrum below 1 GHz is crowded because civil radio communications occupy the channels. The notation L refers to the large antenna or long range. The L-band radars have a relatively wide bandwidth and high emitted power, making them suitable for modern long-range air surveillance up to a range of about 400 km. The notation S means the small antenna or short range. Most land-based and shipborne radars are in this band, where the atmospheric attenuation is higher than in the

L-band, so the radars require a much higher emitted power to achieve long-range detection. Moreover, some special airport surveillance radars also use this band to detect aircraft within 120 km. Most mobile military battlefield and weather radars are based on C-band, allowing for quick installation, good angular accuracy and reasonable resolution.

The radar in Ku and K bands are commonly used as airborne radars, maritime navigation radars and imaging radars (spaceborne or airborne), which have appropriately small antennas and adequate angular accuracy. The high-frequency K and Ka bands are heavily influenced by weather and atmospheric attenuation. Therefore, radars in these bands are suitable for some short-range scenarios such as traffic radars, terrain avoidance and terrain tracking radars. The mm-Wave radars in V, W and mm bands offer a series of advantages in terms of the large spectrum space, low latency time, compact antenna size and high resolution. However, they also suffer from severe atmospheric attenuation, and three attenuation peaks occur at about 60 GHz, 120 GHz and 180 GHz, coinciding with the resonant frequencies of the oxygen and water molecules (Figure I.1.2). Correspondingly, there are some frequency windows between these peaks where the atmospheric attenuation is relatively lower, and most mm-Wave applications are within these windows, such as 76 - 81 GHz automotive radars.

## I.1.1.2. Mono-static and Multi-static Radars

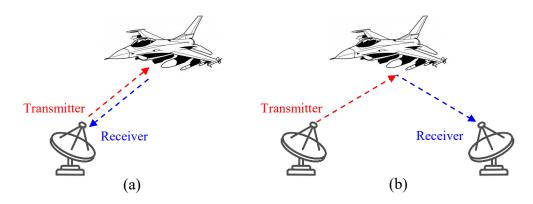

The physical configurations of the antennas can classify the radars into monostatic and multi-static (including bistatic) as shown in Figure I.1.3. A traditional radar in which the transmitting and receiving antennas are located in the same place is referred to as a monostatic radar, regardless of whether single or two antennas are used. A multi-static radar system contains two or more transmitting or receiving antennas, which are all far apart compared to the size of the antennas [I-5].

Figure I.1.3 Radar configurations. (a) Monostatic. (b) Bistatic.

In a monostatic radar system, the time and phase synchronization between transmission and reception can be performed by the same frequency source and clock, resulting in a relatively simple structure. Moreover, for most short-range civil scenarios, the radar size can be petite because of the low emitted power required, such as automotive radars. In military applications, the monostatic radar can also be equipped inside the rocket head to track and attack aircrafts, tanks, etc.

Multi-static radar offers some advantages over monostatic radar in cases where the reflected energy from the target is deficient, such as long-range and weather radars. Furthermore, it allows more comprehensive observations of targets from different transmit-receive pairs, thereby adding potentially valuable information. Hence, it is more likely to detect stealthy objects and less susceptible to interference. However, in such a separated system, a precise standard time reference and complex algorithms are required for synchronization and data processing.

#### I.1.1.3. Radar Equation

The radar equation quantitatively describes the relationship between the radar parameters, the detection distance, and target characteristics [I-6]. Assuming that a target is located at a range of R from the radar,  $P_t$  is the radar transmitted power, and  $G_t$  is the transmit antenna gain, the directional power density  $S_t$  at this target is given by

$$S_1 = \frac{P_t G_t}{4\pi R^2}$$

(I.1.1)

The reflected power  $P_I$  by the target is

$$P_1 = S_1 \cdot \sigma = \frac{P_t G_t \sigma}{4\pi R^2} \tag{I.1.2}$$

where  $\sigma$  is the radar cross section (RCS). A target with a larger RCS means that it is more easily detected. The returned power density  $S_2$  at the radar is given by

$$S_2 = \frac{P_1}{4\pi R^2} = \frac{P_t G_t \sigma}{(4\pi R^2)^2}$$

(I.1.3)

Thus, the total received power  $P_r$  by the radar is

$$P_r = S_2 \cdot A_e \tag{I.1.4}$$

where  $A_e$  is the effective antenna aperture. The relationship between the receive antenna gain  $G_r$ , the wavelength  $\lambda$ , and  $A_e$  can be expressed as

$$G_r = \frac{4\pi A_e}{\lambda^2} \tag{I.1.5}$$

Substituting (I.1.5) into (I.1.4), the total received power  $P_r$  is therefore written as

$$P_r = \frac{P_t G_t G_r \lambda^2 \sigma}{(4\pi)^3 R^4}$$

(I. 1. 6)

If the minimum received power that can be detected by the radar is  $P_{r,min}$ , then the maximum achievable range  $R_{max}$  can be derived as

$$R_{max} = \sqrt[4]{\frac{P_t G_t G_r \lambda^2 \sigma}{(4\pi)^3 P_{r,min}}}$$

(I. 1. 7)

### I.1.1.4. Pulsed and Continuous-Wave Radars

According to the waveform of the radar signal, radar can be classified into pulsed radars and continuous-wave (CW) radars [I-7]-[I-10]. Pulsed radars transmit short and powerful pulses and receive echo signals from the target, which means that the transmission and reception are separated, so pulsed radars can utilize only one antenna. CW radars transmit continuous waves and receive echo signals while transmitting, i.e., transmission and reception are simultaneous, so it requires two independent antennas.

#### I.1.1.4.1. Pulsed Radar

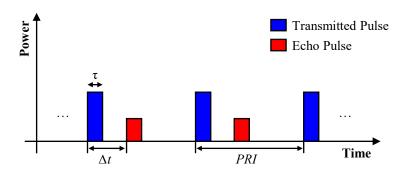

Figure I.1.4 Range measurement principle of the pulsed radar.

The range measurement principle of the pulsed radar is shown in Figure I.1.4. Typically, the transmitter emits a train of rectangular pulses, each pulse has a width  $\tau$  of about 0.1 to 1 microsecond (µs). During this pulse emission, the receiver is isolated from the antenna to protect its sensitive components from the high-power transmit pulse. Once the pulse emission is completed, the receiver is connected to the antenna, enabling it to pick up the reflected echo signals from the target. The distance *R* between the radar and the target can then be measured by simply calculating the round-trip time  $\Delta t$  from the

pulse emission to the reception of its return, which is given by

$$R = \frac{c \cdot \Delta t}{2} \tag{I.1.8}$$

Note that the pulse is emitted periodically with a pulse repetition interval *PRI*, so the pulse repetition frequency *PRF* can be written as

$$PRF = \frac{1}{PRI} \tag{I.1.9}$$

The transmitted duty cycle D represents the ratio between  $\tau$  and PRI and is given by

$$D = \frac{\tau}{PRI} = \tau \cdot PRF \tag{I.1.10}$$

If the transmitted pulse is a square wave, its average power  $P_{av}$  is equal to its peak power  $P_t$  multiplied by its duty cycle D, which can be expressed as:

$$P_{av} = P_t \cdot D = P_t \cdot \tau \cdot PRF \tag{I.1.11}$$

$P_{av}$  is crucial because it determines the potential detectable range of the pulsed radar. To maximize the detection range,  $P_{av}$  can be increased by three means: improving the *PRF*, enlarging  $\tau$ , and increasing  $P_t$ .

In addition, to avoid the range ambiguity, the echo pulse must be received before the next pulse is emitted, which means that the round-trip time  $\Delta t$  of the radar pulse must be less than its *PRI*, and this relation can be defined as

$$\Delta t = \frac{2R}{c} \le PRI \tag{I.1.12}$$

Therefore, the maximum unambiguous range  $R_{max}$  is

$$R_{max} = \frac{c \cdot PRI}{2} = \frac{c}{2PRF} \tag{I.1.13}$$

The minimum detectable range  $R_{min}$  (or blind distance) depends on the radar pulse width  $\tau$ . When the front of the echo pulse reaches the antenna while the radar is still in transmission mode, the round-trip time  $\Delta t$  cannot be determined. Considering the recovery time  $t_r$  of the duplexer,  $R_{min}$  is approximately given by

$$R_{min} \approx \frac{c \cdot (\tau + t_r)}{2} \tag{I.1.14}$$

In the above range measurements, only the amplitude of the echo pulse is employed. In

order to further acquire the velocity of the target  $v_t$ , the frequency of the echo pulse has to be extracted and compared with that of the transmitted pulse, and the resulting frequency difference  $f_d$  is known as a Doppler shift. This coherent radar is also referred to as pulsed Doppler radar, and the relationship between the Doppler frequency shift and the velocity of the target can be expressed as

$$f_d = \frac{2v_t}{\lambda} \tag{I.1.15}$$

where  $\lambda$  is the wavelength of the transmitted pulse.

Another important parameter is the resolution, which represents the capability of the radar to distinguish between two or more adjacent targets, whether in range, angle, or frequency. Let's take the range resolution as an example, if two targets are close enough, their reflected echo pulses will be merged or overlapped, and they will be considered as the same target in the receiver. The minimum resolvable range is defined as the range resolution  $\Delta R$ , which is proportional to the pulse width  $\tau$ . The relationship is

$$\Delta R = \frac{c \cdot \tau}{2} \tag{I.1.16}$$

Therefore, the fine range resolution can be achieved by shortening the pulse. Recall that in this case, the average power (or pulse energy) will be correspondingly decreased, which makes the detection more difficult. To solve this contradiction, pulse compression techniques are used to maintain the pulse energy while providing better range resolution by modulating the amplitude, phase, or frequency of the pulse signal.

Pulsed radars have shown excellent performances in some long-range scenarios such as weather radars, over-the-horizon (OTH) radars, and satellite-based remote sensing radars. However, they are rarely used in short-range scenarios due to their minimum detectable range which is limited by the pulse width and the switching time of the duplexer. Meanwhile, the accurate target localization also requires additional information about the antenna directionality, which further increases the complexity of the system.

#### I.1.1.4.2. Continuous-Wave Radar

Unlike pulsed radar, CW radar continuously transmits EM wave, and its waveform may be considered as a sine wave with constant frequency. The velocity of the target can be measured by Doppler shift, but not the range. Therefore, the EM wave must be modulated so as to obtain the round-trip time for the range determination. There are several ways to modulate a frequency in time, such as linear frequency modulation (LFM), frequency shift-keying (FSK), and frequency-stepped continuous-wave (FSCW) modulation [I-11]. Among them, the LFM method consists in varying the signal frequency linearly with time, and it is the most commonly used method in automotive radars.

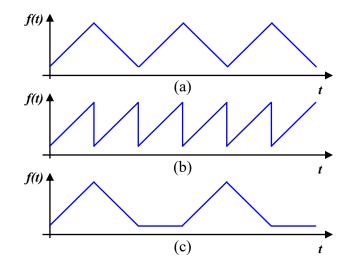

*Figure I.1.5 LFM methods. (a) Linear triangular frequency modulation. (b) Linear sawtooth frequency modulation. (c) Segmented linear frequency modulation.*

Typically, the LFM waveform of a CW radar changes periodically as shown in Figure I.1.5. The frequency f(t) is the instantaneous frequency. Moreover, three LFM methods are widely employed, namely linear triangular frequency modulation, linear sawtooth frequency modulation, and segmented linear frequency modulation. The LFM waveform is often referred to as a chirp because in early radar systems this waveform would produce a chirping sound similar to that made by birds. The term chirp is also used interchangeably with sweep signal. Moreover, CW radars using the frequency modulation method are also known as frequency-modulated continuous-wave (FMCW) radars.

### I.1.1.5. Transceiver Architectures

As the core of wireless communications and radar systems, the transceiver acts as the link between the digital signal processor (DSP) and the RF antenna usually consisting of two or more independent transmitter and receiver chains. The transmitter is used to upconvert a modulated signal to a higher RF signal, which is then amplified to a specific power level to drive the antenna. The receiver is used to filter, amplify and down-convert the received weak signals while suppressing external interferences (e.g., noise, jamming, and clutter). The choice of transceiver architectures is mainly determined by complexity, performance, cost, and power consumption. In the following, we will take a representative PLL-based transmitter and a superheterodyne receiver as examples to briefly elaborate their principles. Another commonly used homodyne architecture will not be presented here, but some details can be found in [I-12], [I-13].

I.1.1.5.1. PLL-Based Transmitter

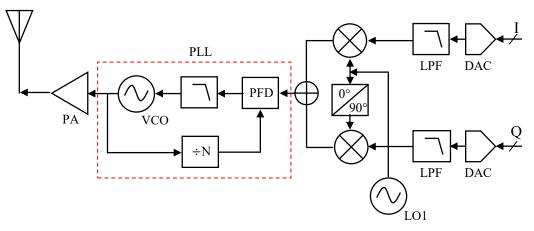

Figure I.1.6 Block diagram of a PLL-based transmitter.

The block diagram of a typical PLL-based transmitter is shown in Figure I.1.6, which is usually employed in FMCW radars. The PLL is followed and modulated by a reference signal from the output of the quadrature I/Q modulator (or a high-precision clock). The out-of-band noise generated by the I/Q modulator can be suppressed if the loop bandwidth of the PLL is appropriately selected, so the output RF filter can be omitted and the output noise of the transmitter at large frequency offsets is mainly determined by the VCO employed [I-14]. Therefore, this architecture permits some advantages such as low phase noise, low power consumption, and high linearity. However, a major challenge is to reduce the lock-in time of the PLL to further lower the power consumption.

Another critical issue is that this architecture is limited to the systems using constant amplitude modulation (AM) because the modulated PLL does not reproduce AM information. The polar modulation architecture can be used to address this issue. For example, the output signal of the modulator is divided into the amplitude and phase components. Phase modulation (PM) is still performed by the PLL, and an additional mixer prior to the PA is added to apply the AM. More details can be found in [I-15].

#### I.1.1.5.2. Superheterodyne Receiver

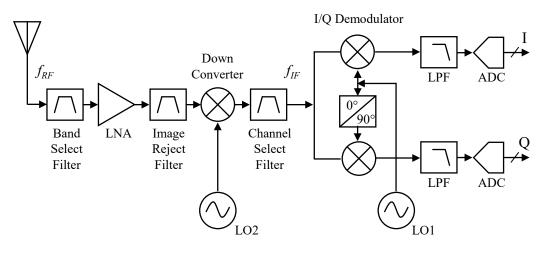

Figure I.1.7 Block diagram of a typical superheterodyne receiver.

The block diagram of a commonly used superheterodyne receiver is shown in Figure I.1.7. Generally, the superheterodyne receiver employs two (or more) stages of downconversion. The RF signal received by the antenna is first filtered by the band-select filter, which allows to select the whole receiver band and to remove unwanted out-of-band interferences. It is then amplified by a low-noise amplifier (LNA) and down-converted to the intermediate frequency (IF) signal by a frequency mixer connected with the RF local oscillator (LO2). The LNA is critical to reach good reception sensitivity. Before and behind the frequency mixer, the image-reject filter and channel-select filter are required to suppress the image frequency and to select the frequency band of the desired channel, respectively. The second down-conversion is performed by the I/Q demodulator and IF local oscillator (LO1), which converts this resulting IF signal to baseband quadrature I and Q signals (i.e., two 90° phase shifted signals). The 90° phase shift is carried out with a polyphase filter or a frequency divider to produce two IF signals with a 90° phase difference. The low-pass filters (LPF) in the I and Q channels are used to filter out the mixing high-frequency components and further attenuate interferences. The analog-todigital converter (ADC) converts the baseband analog signals to digital signals for further processing in the digital signal processor (DSP).

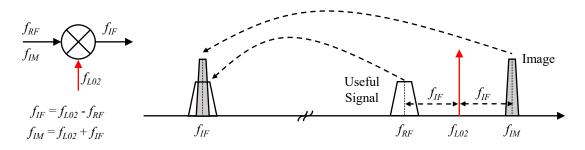

Note that the choice of the IF is critical for the superheterodyne architecture. As depicted in Figure I.1.8, the useful RF signal at frequency  $f_{RF}$  and its undesired image signal at frequency  $f_{IM}$  are symmetrically located above and below the LO2 frequency  $f_{LO2}$ , and they can both be converted to the IF signal at frequency  $f_{IF}$  through the mixing operation. To eliminate this image frequency  $f_{IM}$ , an image-reject filter is necessary to be

placed before the mixer, which has a large attenuation around  $f_{IM}$  and a relatively small loss around  $f_{RF}$ . Since the frequency difference between  $f_{IM}$  and  $f_{RF}$  is  $2f_{IF}$ , a higher IF leads to a better rejection of the image frequency. However, the IF cannot be too high, otherwise the interference nearby the IF is hard to be filtered out by the channel-select filter because of the limitation of its quality factor (*Q*-factor). Therefore, the trade-off between image rejection and channel selection should be well considered when determining the IF. In addition, the image rejection can also be performed by the Hartley and Weaver architectures, the corresponding principles are detailed in [I-16], [I-17].

Figure I.1.8 Impact of the image frequency on the spectrum of the useful signal.

Nevertheless, in superheterodyne receivers, high-performance image-reject filters are still required. Passive filters, such as surface acoustic wave (SAW) or high-order LC filters, are frequently employed. They typically have a large physical size and are difficult to integrate, leading to an increase in design complexity, power consumption, and cost. However, the use of IF and multiple filters in the superheterodyne architecture enables a wide dynamic range of reception and excellent suppression of interference, thus improving its selectivity and sensitivity.

# I.1.2. Automotive Radar for Autonomous Driving

Autonomous driving usually refers to self-driving vehicles that relies on cutting-edge technologies such as powerful processors, multi-purpose sensors and artificial intelligence to travel without any driver manipulation. Such intelligent vehicles can not only improve the travel efficiency by planning routes and times in advance, but also accurately perceive the road conditions and timely react. In addition, they are capable of avoiding road traffic accidents caused by risky behaviors such as drunk, fatigue or distracted driving. According to the World Health Organization (WHO), about 90% of road traffic accidents are caused by human errors, and more than 1.3 million people die and up to 50 million get injured worldwide each year, making them the leading cause of

death among people aged 15 - 29 years [I-18], [I-19]. These numbers are expected to decrease significantly in the near future with the widespread deployment of autonomous driving technology, which will also bring tremendous social and economic benefits.

### I.1.2.1. SAE Levels of Autonomy