## Real-Time implementation of Quasi-Cyclic Short Packet Receiver

Camille Monière

#### ▶ To cite this version:

Camille Monière. Real-Time implementation of Quasi-Cyclic Short Packet Receiver. Electronics. Université de Bretagne Sud, 2023. English. NNT: 2023LORIS650. tel-04117549

## HAL Id: tel-04117549 https://theses.hal.science/tel-04117549

Submitted on 5 Jun 2023

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse de doctorat de

### L'UNIVERSITÉ DE BRETAGNE SUD

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: Électronique

Par

# Camille MONIÈRE

## Implémentation Temps-Réel d'un Récepteur Quasi Cyclic Short Packet

Real-Time implementation of Quasi-Cyclic Short Packet Receiver

Thèse présentée et soutenue à Lorient, le 04/01/2023

Unité de recherches : Lab-STICC — UMR 6285 CNRS, Université de Bretagne Sud

IMS — UMR 5218 CNRS, Bordeaux INP

Thèse Nº: 650

#### Rapporteurs avant soutenance:

Matthieu GAUTIER Maitre de Conférence HDR (Université Rennes 1) Claire GOURSAUD Maitre de Conférence HDR (INRIA, INSA Lyon)

Composition du Jury:

Président : Bertrand GRANADO Professeur des Universités (Sorbonne Université)

Examinateurs: Christophe JEGO Professeur des Universités (IMS, ENSEIRB-MATMECA/Bordeaux INP)

Claire GOURSAUD Maitre de Conférence HDR (INRIA, INSA Lyon) Matthieu GAUTIER Maitre de Conférence HDR (Université Rennes 1)

Dir. de thèse : Emmanuel BOUTILLON Professeur des Universités (Lab-STICC, Université de Bretagne Sud)

Co-Enc. de thèse : Bertrand LE GAL Maitre de Conférence (IMS, ENSEIRB-MATMECA/Bordeaux INP)

Invité(s):

Rémi CHAUVAT Expert Télécommunications Spatiales (KINEIS)

## REMERCIEMENTS

Je tiens à remercier en premier lieu mon directeur de thèse, Emmanuel Boutillon, Professeur à l'Université de Bretagne Sud, ainsi que mon co-encadrant, Bertrand Le Gal, Maitre de Conférences à l'ENSEIRB-MATMECA. Chacun m'a soutenue dans mes initiatives et m'a apporté son expertise. Leur support et leurs conseils ont été d'une grande aide dans le contexte particulier de cette thèse.

Je remercie également Matthieu Gautier et Claire Goursaud, Maitres de Conférences HDR à l'Université de Rennes 1 et à l'IRISA de Lyon respectivement, pour avoir accepté d'être mes rapporteurs de thèse. Leur appréciation du manuscrit a été formatrice, et leurs observations et remarques ont notamment permis d'améliorer et de peaufiner ce manuscrit.

Je tiens à remercier aussi Bertrand Granado et Christophe Jego, Professeurs à l'Université de la Sorbonne et à l'ENSEIRB-MATMECA respectivement, mais aussi Rémi Chauvat, Expert en Télécommunications Spatiales à KINEIS pour avoir accepté de faire partie de mon jury de soutenance de thèse. Leurs questions m'ont offert d'autres perspectives quant à mes travaux.

Je me dois de remercier Cédric Marchand, docteur et ingénieur de recherche au Lab-STICC de Lorient pour l'aide qu'il m'a apporté, notamment autour des codes correcteurs d'erreurs.

De la même façon, je remercie Kassem Saied, docteur de l'Université de Bretagne Sud. Mes travaux et les siens étaient étroitement liés et notre collaboration s'est avérée fructueuse.

Je remercie aussi Hugues Almorin, doctorant à l'Université de Bordeaux. Ses résultats m'ont permis de mieux appréhender certains aspects de mes propres recherches.

Je me dois de citer Bertrand Orvoine, Leonardo M. Obesso et Joseph Jabour pour leurs contributions techniques dans certains de mes programmes, Léa Volpin, que j'ai encadré en tant qu'ingénieure, et aussi tant d'autres, que je ne pourrais citer par manque d'espace.

Enfin, je remercie Virginie Guillet, gestionnaire au Lab-STICC, et Fabienne Prévot, responsable RH à l'IMS de Bordeaux, qui ont garanti le bon déroulement de cette thèse.

# Table of Contents

| A            | Acronyms |                                                                            |           |  |

|--------------|----------|----------------------------------------------------------------------------|-----------|--|

| $\mathbf{G}$ | lossaı   | ry                                                                         | 11        |  |

| Li           | st of    | Figures                                                                    | 15        |  |

| Li           | st of    | Tables                                                                     | 18        |  |

| 1            | Intr     | oduction                                                                   | 19        |  |

|              | 1.1      | Introduction                                                               | 19        |  |

|              | 1.2      | Manuscript outline                                                         | 22        |  |

| <b>2</b>     | Stat     | te of the Art                                                              | <b>25</b> |  |

|              | 2.1      | Internet of Things and associated challenge                                | 25        |  |

|              | 2.2      | Software-defined Radio platforms                                           | 29        |  |

|              | 2.3      | Implementation of digital communication systems                            | 31        |  |

|              | 2.4      | Conclusion                                                                 | 35        |  |

| 3            | Qua      | si-Cyclic Short Packets Communication Chain                                | 37        |  |

|              | 3.1      | Non Binary Error Correction Codes                                          | 38        |  |

|              |          | 3.1.1 Galois Field of order $q - GF(q) \ldots \ldots \ldots \ldots \ldots$ | 39        |  |

|              |          | 3.1.2 Non-Binary Low Density Parity Check                                  | 40        |  |

|              | 3.2      | Cyclic Code Shift Keying                                                   | 41        |  |

|              | 3.3      | QCSP System Model                                                          | 43        |  |

|              |          | 3.3.1 Transmitter                                                          | 43        |  |

|              |          | 3.3.2 Channel model                                                        | 44        |  |

|              |          | 3.3.3 Detection                                                            | 45        |  |

|              |          | 3.3.3.1 Score function                                                     | 45        |  |

|              |          | 3.3.3.2 Search grid                                                        | 47        |  |

|              |          | 3.3.3.3 Performances                                                       | 49        |  |

### TABLE OF CONTENTS

|   |     | 3.3.4                                      | Synchronization                                                           |  |  |  |  |

|---|-----|--------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|   | 3.4 | Concl                                      | asion                                                                     |  |  |  |  |

| 4 | Det | ection                                     | Algorithmic Optimizations 57                                              |  |  |  |  |

|   | 4.1 | Mitiga                                     | ting possible gain instability                                            |  |  |  |  |

|   |     | 4.1.1                                      | Normalization methods                                                     |  |  |  |  |

|   |     | 4.1.2                                      | Complexity estimations                                                    |  |  |  |  |

|   |     | 4.1.3                                      | Impact on detection performances                                          |  |  |  |  |

|   | 4.2 | Time                                       | sliding windows                                                           |  |  |  |  |

|   |     | 4.2.1                                      | Principle                                                                 |  |  |  |  |

|   |     |                                            | Iterative factor precision issue                                          |  |  |  |  |

|   |     |                                            | Architectural variations                                                  |  |  |  |  |

|   |     | 4.2.2                                      | Detection performance and complexity comparisons                          |  |  |  |  |

|   |     |                                            | 4.2.2.1 Impact of $(p_{\omega}, p_{\Delta})$ on detection performances 70 |  |  |  |  |

|   |     |                                            | 4.2.2.2 Computational complexity comparisons 71                           |  |  |  |  |

|   |     | 4.2.3                                      | Software implementation, benchmark, and analysis                          |  |  |  |  |

|   | 4.3 | Concl                                      | asion                                                                     |  |  |  |  |

| 5 | Rea | l-Time                                     | e Implementation 77                                                       |  |  |  |  |

|   | 5.1 | Transı                                     | mission                                                                   |  |  |  |  |

|   |     | 5.1.1                                      | Principles                                                                |  |  |  |  |

|   |     | 5.1.2                                      | Transmitter software implementation                                       |  |  |  |  |

|   |     | 5.1.3                                      | Transmitter hardware implementation                                       |  |  |  |  |

|   | 5.2 | 5.2 Detection $\dots$                      |                                                                           |  |  |  |  |

|   |     | 5.2.1                                      | Critical task identification                                              |  |  |  |  |

|   |     | 5.2.2                                      | Correlator inherent parallelism                                           |  |  |  |  |

|   |     | 5.2.3 Correlator in-depth complexity study |                                                                           |  |  |  |  |

|   |     | 5.2.4                                      | Correlator software implementation                                        |  |  |  |  |

|   |     |                                            | 5.2.4.1 Analysis of the results                                           |  |  |  |  |

|   |     | Correlator hardware implementation         |                                                                           |  |  |  |  |

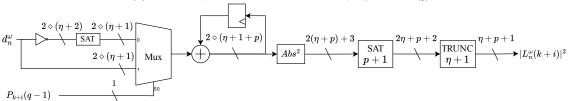

|   |     | 5.2.6                                      | Quantized model of the score processor                                    |  |  |  |  |

|   |     |                                            |                                                                           |  |  |  |  |

|   |     |                                            | 5.2.6.1 Presentation of the quantized model                               |  |  |  |  |

|   |     |                                            | 5.2.6.1 Presentation of the quantized model                               |  |  |  |  |

|   |     |                                            | -                                                                         |  |  |  |  |

| 6                         | Rea            | l-Time Full-Scale Experiments               | 105          |

|---------------------------|----------------|---------------------------------------------|--------------|

|                           | 6.1            | Experimental setup                          | . 105        |

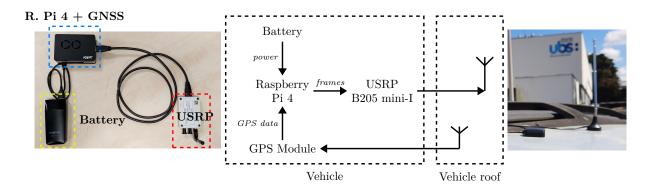

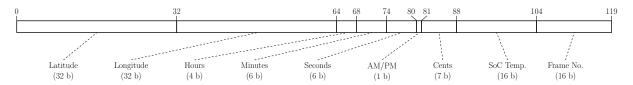

|                           |                | 6.1.1 GNSS-enabled mobile QCSP transmitter  | . 108        |

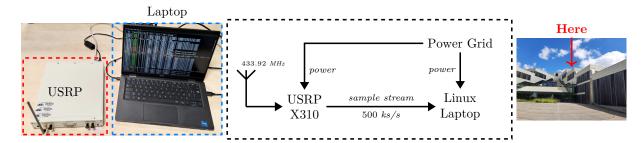

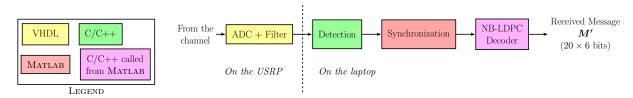

|                           |                | 6.1.2 Real-time QCSP receiver               | . 111        |

|                           |                | 6.1.3 Experimental environment and protocol | . 113        |

|                           | 6.2            | Experimental results analysis               | . 113        |

|                           | 6.3            | Conclusion                                  | . 116        |

| 7                         | <b>Con</b> 7.1 | clusion Synthesis                           | 117<br>. 117 |

|                           | 7.2            | Perspectives                                | . 119        |

| $\mathbf{A}_{\mathbf{J}}$ | ppen           | dices                                       | <b>12</b> 3  |

|                           | A              | Algebraic definitions                       | . 123        |

| Bi                        | bliog          | graphy                                      | 127          |

## ACRONYMS

$\mathcal{P}_{fa}$  probability of False Alarm.

$\mathcal{P}_{md}$  probability of Miss Detection.

**ADC** Analog Digital Converter.

ALU Arithmetic Logic Unit.

**ASIC** Application-Specific Integrated Circuit.

**BPSK** Binary Phase Shift Keying.

**BRAM** Block RAM.

**CAWGN** Complex Additive White Gaussian Noise.

CCSK Cyclic Code Shift Keying.

**CORDIC** COordinate Rotation DIgital Computer.

**CPU** Central Processing Unit.

**CSS** Chirp Spread Spectrum.

CU Correlation Unit.

**DAC** Digital Analog Converter.

**DCS** Digital Communication System.

**DSP** Digital Signal Processor.

**ECC** Error Correction Code.

FCU FFT Correlation Unit.

FF Flip-Flop.

**FFT** Fast Fourier Transform.

**FPGA** Field-Programmable Gate Array.

**GF** Galois Field.

**GNSS** Global Navigation Satellite System.

GPGPU General Purpose Graphical Processing Unit.

**HLS** High-Level Synthesis.

**IFFT** Inverse Fast Fourier Transform.

**IoT** Internet of Things.

**ISA** Instruction Set Architecture.

LDPC Low Density Parity Check.

LLR Log-Likelihood Ratio.

LPWAN Low Power Wide Area Network.

LSB Least Significant Bit.

LUT LookUp Table.

MC Monte-Carlo.

MSB Most Significant Bit.

MT Multithreading.

**NB-ECC** Non Binary Error Correction Codes.

NB-LDPC Non-Binary Low Density Parity Check.

**OM** Overmodulation.

**OSI** Open System Interconnection.

PCM Parity Check Matrix.

PN Pseudo-Noise.

QCSP Quasi-Cyclic Short Packet.

**QPSK** Quadrature Phase Shift Keying.

**RF** Radio-Frequency.

**RFNoC** RF Network-on-Chip.

**ROC** Receiver Operating Characteristic.

SBC Single-Board Computer.

$\mathbf{SdR}$  Software-defined Radio.

${\bf SIMD}\,$  Single Instruction Multiple Data.

${f SNR}$  Signal-to-Noise Ratio.

SoC System on Chip.

**SPU** Score Processing Unit.

$\mathbf{TCU}$  TS Correlation Unit.

$\mathbf{TS}$  Time Sliding.

**UHD** USRP Hardware Driver.

**USRP** Universal Software-define Radio Peripheral.

WSN Wireless Sensor Network.

## GLOSSARY

- Binary Phase Shift Keying Modulation scheme, where "1"-bits are mapped to a high level (e.g. +1) and "0"-bits are mapped to a the opposite level (e.g. -1).

- Chirp Spread Spectrum Modulation scheme, where symbols are mapped to a signal with a particular frequency fingerprint, called a chirp. The key feature of the chirp, is that its frequency fingerprint can be circularly shifted. Each possible shift correspond to a specific symbol.

- **codeword** Output of the channel encoder, that contains the transmitted message and some redundancy. The original message can be retrieved by using the right channel decoder, which can also correct transmission errors in the process.

- Global Navigation Satellite System Regroups all navigation satellite systems. For instance: GPS is the American system, Galileo is the Europen one, GLONASS is Russian and BeiDou is Chinese.

- **ISM radio band** Portion of the radio spectrum reserved internationally for industrial, scientific and medical (ISM) purposes. [...] Despite the intent of the original allocations, in recent years the fastest-growing use of these bands has been for short-range, low power wireless communications systems [1].

- NMEA 0183 NMEA 0183 is a combined electrical and data specification for communication between marine electronics such as echo sounder, sonars, anemometer, gyrocompass, autopilot, GPS receivers and many other types of instruments. It has been defined and is controlled by the National Marine Electronics Association (NMEA). [2].

- **Overmodulation** Added frame-level information, used in the Quasi-Cyclic Short Packet chain to improve synchronization.

- Quadrature Phase Shift Keying Modulation scheme, where the number k from 0 to 3 (2 bits) is mapped to the complex number  $e^{j\frac{(2k+1)\pi}{4}}$ .

Quasi-Cyclic Short Packet The aim of the Quasi-Cyclic Short Packet (QCSP) project is to contribute to the evolution of IoT networks by defining, implementing and testing a new coded modulation scheme dedicated to IoT networks. The "big bet" of the project is to work on the emergence of non-binary codes combined with a Cyclic Code Shift Keying (CCSK) modulation [3].

# LIST OF FIGURES

| 1.1                               | Classical communication chain                                                                                                                                     | 20       |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2                               | Physical layer asynchronous communication chain                                                                                                                   | 21       |

| 1.3                               | OSI Model, with the layer of interest framed in red                                                                                                               | 21       |

| 2.1                               | Different technologies represented in their respective field, depending on<br>the data rates and power consumption involved against the achievable<br>ranges [26] | 27       |

| 2.2                               | Comparisons between a long packet and a short packet, highlighting the                                                                                            | 29       |

| กา                                | major concern the preamble is for short packets                                                                                                                   |          |

| <ul><li>2.3</li><li>2.4</li></ul> | Generic organization of Software-defined Radio (SdR) platforms                                                                                                    | 30<br>33 |

| 3.1                               | Complete QCSP system model                                                                                                                                        | 38       |

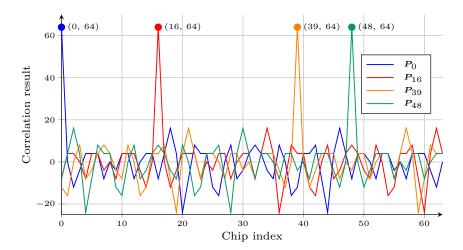

| 3.2                               | Circular correlation results for a given $P_0$ of $q = 64$ chips with four different rotations of itself                                                          | 42       |

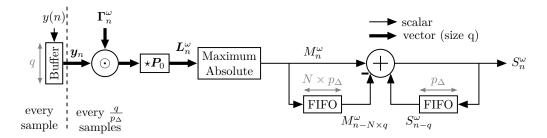

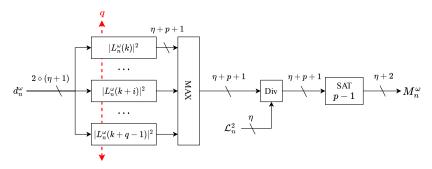

| 3.3                               | Legacy Elementary Score Processing Unit                                                                                                                           | 45       |

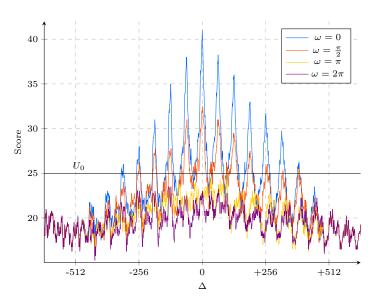

| 3.4                               | Example of score values $S_n^{\omega}$ as a function of the chip offset error $\Delta$ and of                                                                     |          |

|                                   | the residual frequency offset error $\theta - \omega$ at an SNR of -7 dB                                                                                          | 46       |

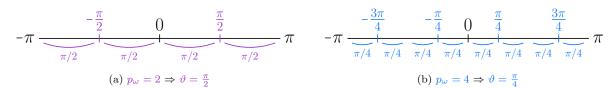

| 3.5                               | Rotation interval division for $p_{\omega} = 2$ and $p_{\omega} = 4$ , $\vartheta$ represented as corre-                                                          |          |

|                                   | sponding arcs                                                                                                                                                     | 47       |

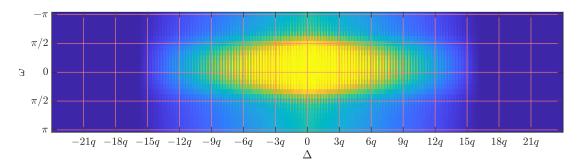

| 3.6                               | Toy example of a search grid (in red) represented on the received score associated to one frame in a noiseless asynchronous channel. The bluer the                |          |

|                                   | color is (resp. the yellower), the lower is the corresponding score (resp. the                                                                                    |          |

|                                   | higher)                                                                                                                                                           | 48       |

| 3.7                               | Complete detection system.                                                                                                                                        | 49       |

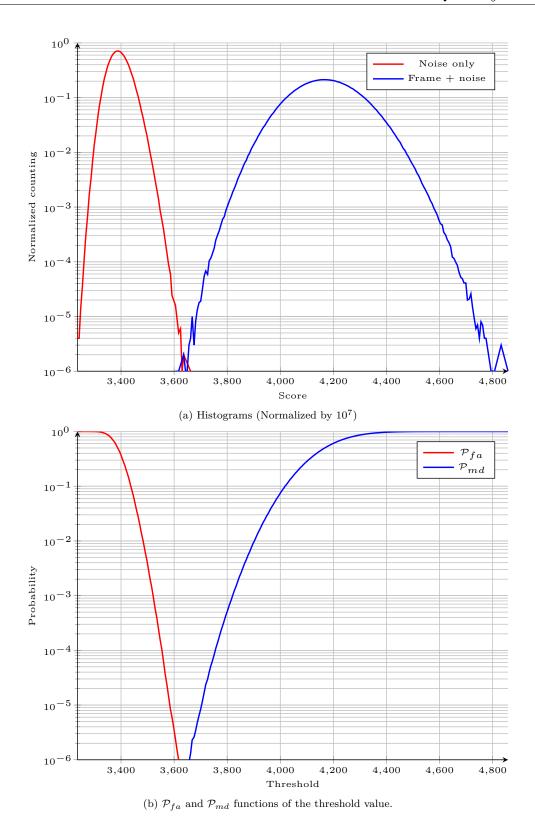

| 3.8                               | Results of $10^7$ MC simulations for $q = 64$ , $N = 60$ , an SNR of $-10$ dB,                                                                                    |          |

| 0.0                               | and over a synchronous channel (i.e. $\Delta = 0$ and $\theta = 0$ )                                                                                              | 51       |

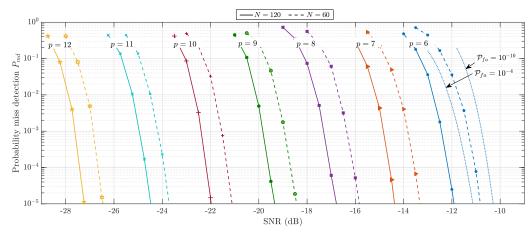

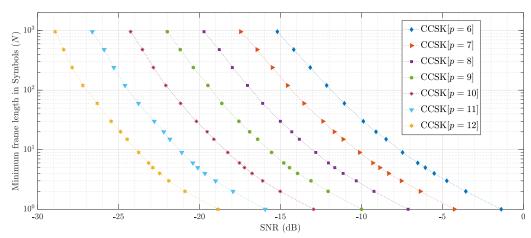

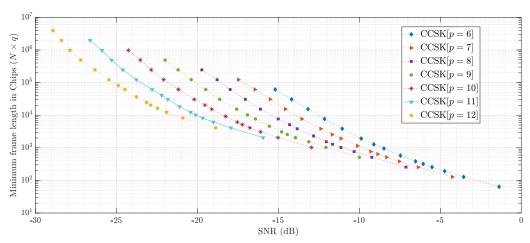

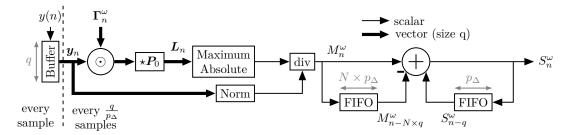

| 3.9                               | Overview of the results presented in [17], showing the impact of $q$ and $N$                                                                                      |          |

|                                   | on the achievable SNR                                                                                                                                             | 52       |

| 4.1 | Score Processing Unit (SPU) robust to an input scaling factor                                                                                                                     | 59  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

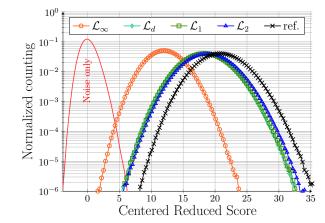

| 4.2 | Effect of the norms $\mathcal{L}_{\infty}$ , $\mathcal{L}_{1}$ , $\mathcal{L}_{d}$ and $\mathcal{L}_{2}$ on detection performances with                                           |     |  |  |

|     | N=60,q=64 and an SNR of $-10$ dB                                                                                                                                                  | 62  |  |  |

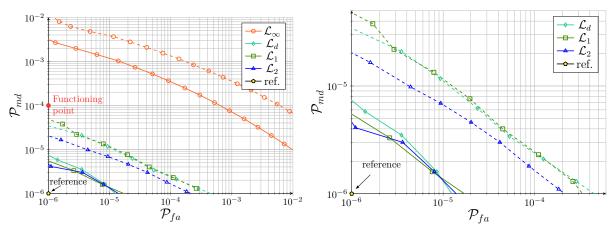

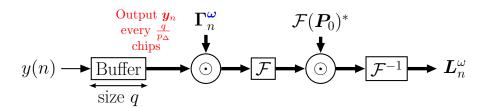

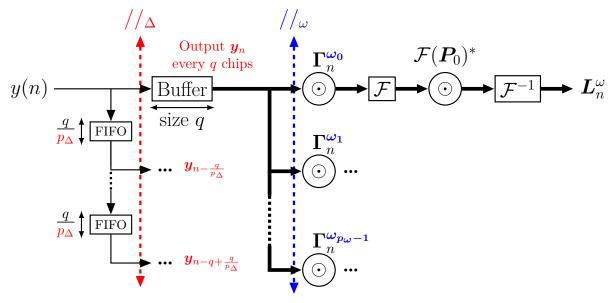

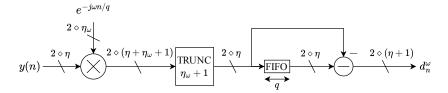

| 4.3 | FFT based correlation possible architecture for a given frequency offset                                                                                                          |     |  |  |

|     | value $\omega$                                                                                                                                                                    | 64  |  |  |

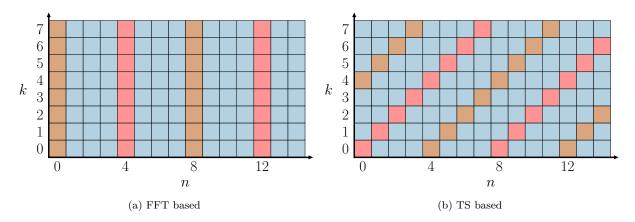

| 4.4 | Comparison between frequency based and time based computation of cor-                                                                                                             |     |  |  |

|     | relations for $q=8$ and $p_{\Delta}=2$ . Red and orange points correspond respec-                                                                                                 |     |  |  |

|     | tively to the output of two distinct SPUs                                                                                                                                         | 66  |  |  |

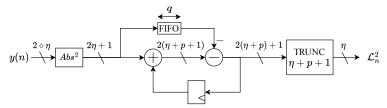

| 4.5 | Time Sliding (TS) correlation possible architectures for a given frequency                                                                                                        |     |  |  |

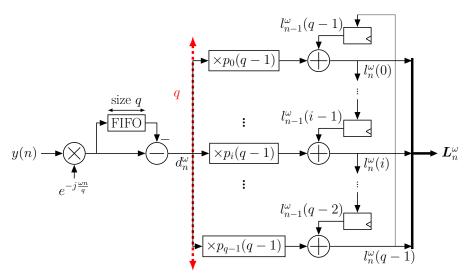

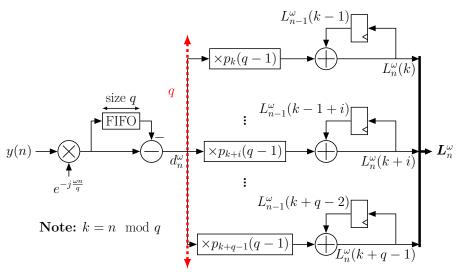

|     | offset value $\omega$                                                                                                                                                             | 69  |  |  |

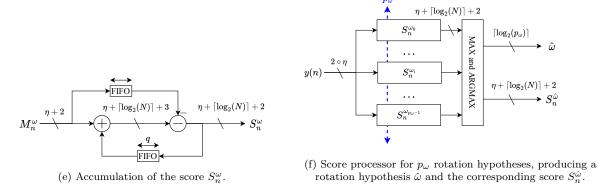

| 4.6 | Resulting ROC curves for frame of $N=60$ symbols, symbols of $q=64$                                                                                                               |     |  |  |

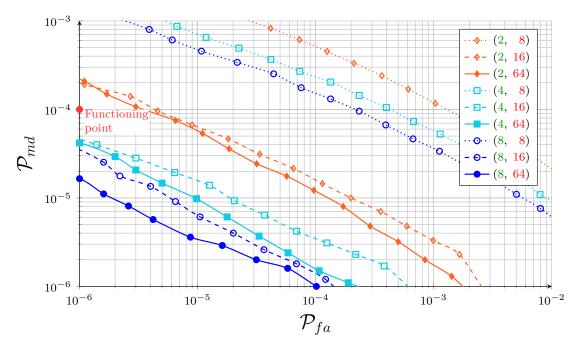

|     | chips, at SNR of -10 dB for several setup of the couple of parameters $(p_{\omega}, p_{\Delta})$ .                                                                                | 70  |  |  |

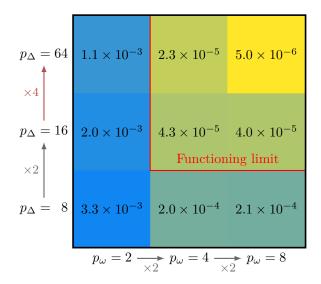

| 4.7 | Impact of the couple $(p_{\omega}, p_{\Delta})$ on $\mathcal{P}_{md}$ for a $\mathcal{P}_{fa} = 10^{-6}$ , represented on a                                                       |     |  |  |

|     | color map. The colder the color is, the higher $\mathcal{P}_{md}$ is (thus, the lower the                                                                                         |     |  |  |

|     | performances are)                                                                                                                                                                 | 71  |  |  |

| 5.1 | Transmitter side of the QCSP chain                                                                                                                                                | 78  |  |  |

| 5.2 | QCSP uncommon functions represented for $q = 4$                                                                                                                                   | 80  |  |  |

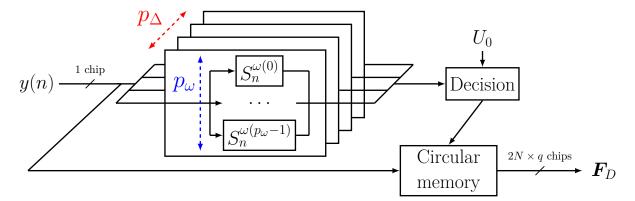

| 5.3 | Detection tasks data flow graph, with associated path stress                                                                                                                      | 86  |  |  |

| 5.4 | The two different correlators represented with their associated $\Delta$ -parallelism                                                                                             |     |  |  |

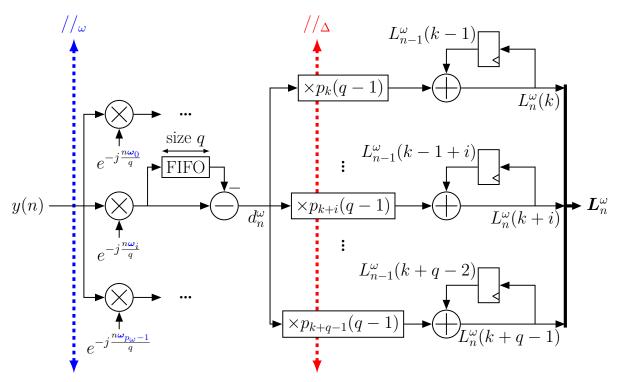

|     | and $\omega$ -parallelism                                                                                                                                                         | 88  |  |  |

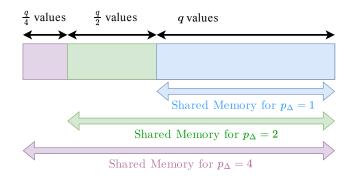

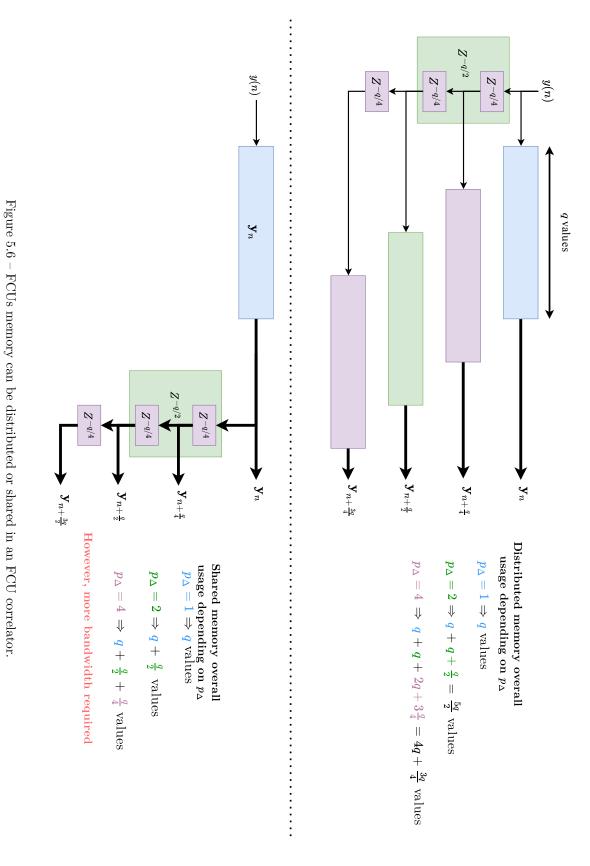

| 5.5 | FCUs shared memory total usage                                                                                                                                                    | 89  |  |  |

| 5.6 | FCUs memory can be distributed or shared in an FCU correlator                                                                                                                     | 90  |  |  |

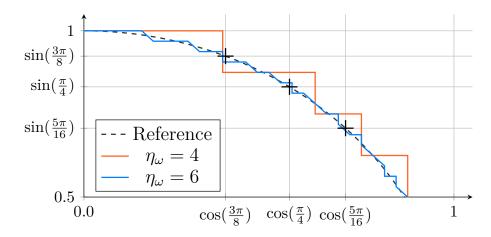

| 5.7 | $\Gamma^{\omega} = \{e^{j\frac{k\omega}{q}}\}_{k \in [0,2qp_{\omega}]-1} \text{ for } q = 64 \text{ and } p_{\omega} = 4, \text{ quantized on } \eta_{\omega} = 4 \text{ and } 6$ |     |  |  |

|     | bits, represented on the north-east quadrant                                                                                                                                      | 99  |  |  |

| 5.8 | Fixed-point model of the QCSP detector, broken down in smaller process-                                                                                                           |     |  |  |

|     | ing blocks, depending on $\eta,$ the input quantization, $p = \log_2(q)$ and $N.~$                                                                                                | 100 |  |  |

| 5.9 | ROC curves for $q=64$ , for various value of $p_{\omega}$ and an SNR of $-9$ dB                                                                                                   | 102 |  |  |

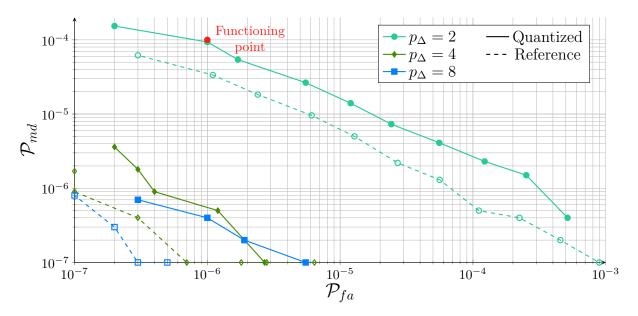

| 6.1 | Complete QCSP communication chain represented with the implementa-                                                                                                                |     |  |  |

|     | tion used, as well as the communication actual settings                                                                                                                           | 107 |  |  |

| 6.2 | Implemented transmitter component diagram                                                                                                                                         | 109 |  |  |

| 6.3 | GNSS module embed into the Raspberry Pi chassis                                                                                                                                   | 109 |  |  |

| 6.4 | Structure of the payload sent over the radio channel                                                                                                                              | 110 |  |  |

| 6.5 | Implemented receiver component diagram                                                                                                                                            | 111 |  |  |

| 6.6 | Languages and platforms involved in the receiver                           |

|-----|----------------------------------------------------------------------------|

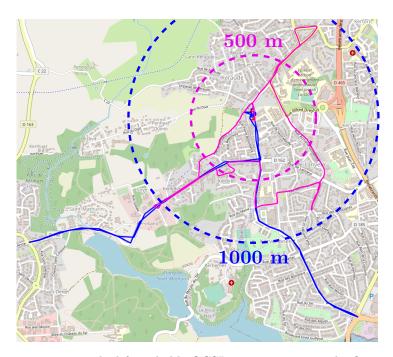

| 6.7 | Maximum ranges reached for reliable QCSP transmissions in the first ex-    |

|     | periment (in blue) and in the second experiment (in magenta), along the    |

|     | tracks followed in each experiment                                         |

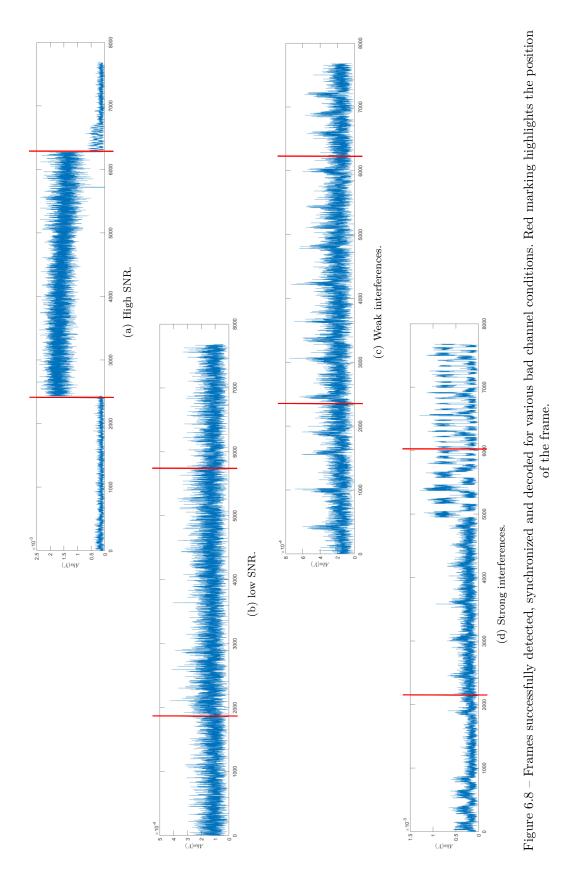

| 6.8 | Frames successfully detected, synchronized and decoded for various bad     |

|     | channel conditions. Red marking highlights the position of the frame $115$ |

| 7.1 | Prospected implementation planning                                         |

# LIST OF TABLES

| 2.1 | Overview of the features offered by three LPWAN technologies, SigFox, LoRa and NB-IoT        | 28  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 3.1 | Different representations of GF(8) elements for $\mathbb{P}_3 = \alpha^3 + \alpha + 1$       | 39  |

| 3.2 | Possible mapping of GF(8) on a generic $\mathbf{P}_0$ , using the natural representa-        |     |

|     | tion of GF symbols defined in Table 3.1                                                      | 41  |

| 4.1 | Computational complexity of each norm in terms of square-roots, multi-                       |     |

|     | plications, additions, and comparisons                                                       | 60  |

| 4.2 | Computational complexity comparison depending on $p_{\Delta}$ value $(p_{\omega} = 1)$ for   |     |

|     | each correlation method                                                                      | 72  |

| 4.3 | Benchmarking platforms technical characteristics                                             | 73  |

| 4.4 | Algorithm benchmarking results depending on the platform used, the val-                      |     |

|     | ues of $(p_{\Delta}, p_{\omega})$ and the correlation method implemented, for $N = 60$ and   |     |

|     | q = 64                                                                                       | 75  |

| 5.1 | Performance of QCSP transmitter software implementation for a payload                        |     |

|     | of 120 bits, $q = 64$ , and $N = 60$                                                         | 81  |

| 5.2 | Targeted FPGA characteristics and price tag                                                  | 83  |

| 5.3 | Performance of QCSP hardware stack on Xilinx FPGA clocked at 100 MHz.                        | 84  |

| 5.4 | Complexity comparison depending on $p_{\Delta}$ and for $p_{\omega} \in [1, 8]$              | 92  |

| 5.5 | Software optimized implementation throughput depending on the platform                       |     |

|     | used, the values of $(p_{\Delta}, p_{\omega})$ and the correlation method used, for $N = 60$ |     |

|     | and $q = 64$                                                                                 | 95  |

| 5.6 | Hardware performance of the detector on a Xilinx Kintex 7 XC7410T                            |     |

|     | clocked at 100 MHz, using floating-point arithmetic if not specified, for                    |     |

|     | $q=64, N=60$ and several values of $p_{\Delta}$ and $p_{\omega}$                             | 97  |

| 5.7 | Hardware performance estimation of the quantized correlators on a Xilinx                     |     |

|     | Kintex 7 XC7410T (speed grade -1) and XC7K325T (speed grade -2), with                        |     |

|     | a working frequency of 100 MHz, for $q = 64$ , and several values of $p_{\omega}$            | 103 |

| 7.1 | Examples of primitive polynomials $\mathbb{P}_p$ for different values of $p$ and the                   |

|-----|--------------------------------------------------------------------------------------------------------|

|     | corresponding order $q=2^p$                                                                            |

| 7.2 | Binary and polynomial representations of GF(8) elements for $\mathbb{P}_3 = \alpha^3 + \alpha + 1.126$ |

# Introduction

#### Foreword

This Ph.D. thesis is a collaborative work between the Université de Bretagne Sud (UBS, France) and the Bordeaux INP institute (France). It has been supervised by Prof. Emmanuel Boutillon and Dr. Bertrand Le Gal. The research leading to these results received funding from the French National Research Agency ANR-19-CE25-0013-01 part of the project entitled Quasi Cyclic Short Packet (QCSP) (website: https://qcsp.univ-ubs.fr/).

### 1.1 Introduction

The demand for interconnected objects, from the simplest *intelligent* thermostat to the most sophisticated autonomous vehicle, has grown exponentially throughout the last decade. The development of this Internet of Things (IoT) has been a strong incentive of innovation, as it allows dreaming of large unsupervised wireless sensor networks. These dense networks are supposed to be composed of low-cost devices, able to operate off-grid, autonomously, and reliably for several years. Thanks to this technology, it may be possible to improve renewable energy production [4], or elaborate a completely autonomous public transportation system [5].

However, with the increasing device density, issues arise. More and more objects need to communicate on the same radio band. The capacity of the channel is limited, thus the question of communication efficiency become increasingly pressing. A naive solution would be to supervise networks, with a human operator or an omniscient scheduler. The problem here is that the first solution would be inefficient in a massively connected network, and that the second one is simply impossible. In addition, since sensor nodes are expected to be used in large number, they must be resource-efficient and energy-efficient, to be in-line with the recent shortages. To tackle this issue, various technologies have emerged, like

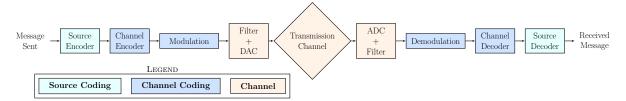

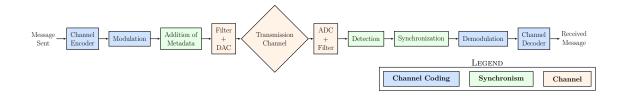

Figure 1.1 – Classical communication chain.

LoRa [6], or ZigBee [7]. However, some paradigms inherited from classical communication contexts and early technologies remains in use despite the drawbacks they come with.

A classical digital communication chain is represented in Fig. 1.1. A certain amount of data, called the message, is first source encoded. This process leverages the knowledge about the source data format to represent it efficiently. It is the case for audio data compression with Free Lossless Audio Compression (FLAC). Another example is the footprint lowering of often-used symbols, like it was done for the Morse code. In this code, the letter E, which was mostly used, was denoted by "." whereas the letter Q, rarely used, was denoted by "--.-".

Then, this binary representation is channel encoded, which consists of adding a reliability to the transmission, often by adding redundancy. The most simple channel coding is the repetition code, where the binary input is just repeated. However, it is highly inefficient in most cases, since the coding rate (the ratio of clear data on the coded data) diminish way faster than the error correcting performance grows. Thus, other correcting codes have been invented, most notably the Low Density Parity Check (LDPC) codes [8], the turbo codes [9] or the polar codes [10].

The output of the channel encoder, called a codeword, is then modulated. This step serves to prepare the binary data to be transmitted through the channel, that is not in the digital world. For radio communications, it is the air. The modulation chosen also has an impact on the signal detection and synchronization capability, and on the sensibility of the signal to events that can appear in the channel, from the simplest additive noise, to more problematic erasures and multi-paths. The next step consists of filtering the digital signal, to prepare to the analog conversion. This filter, coupled with the corresponding optimum filter in reception, helps to maximize the Signal-to-Noise Ratio (SNR). However, a wrong filter choice can increase the sample interference, meaning that consecutive samples could cancel each others. That last step concludes the digital processing in transmission, the signal being then fed to a Digital Analog Converter (DAC). The resulting analog signal is transmitted through a physical channel, which for the IoT, is often the Radio-Frequency

Figure 1.2 – Physical layer asynchronous communication chain.

(RF) channel. In reception, all those steps are done in reverse, using the corresponding filter, demodulator, channel decoder and source decoder.

However, there is an issue with the last presented chain. It assumes the synchronicity of the communication. In reality, the receiver does not know when, nor in which condition the signal will arrive. With the model depicted in Fig. 1.1, it cannot. This is why more accurate models exist, also taking two other steps into account. These steps are the detection of an incoming signal, and the synchronization of a detected signal. An updated model is depicted in Fig. 1.2.

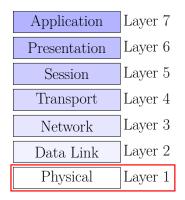

These steps can be addressed in multiple ways, at different levels of the Open System Interconnection (OSI) model (see Fig. 1.3). The current thesis is part of the Quasi-Cyclic Short Packet (QCSP) project. In this project a new innovative waveform is introduced, and proposes a solution at the physical layer, the lowest level of the model.

Historically, the answer to the synchronization problem was to add a level of information shared between the transmitting and the receiving sides. Packets were preceded by a standardized "preamble", which eases the implementation of the detection and synchronization systems, like in 3GPP LTE [11] or Wi-Fi [12]. Indeed, knowing what should be looked up for simplifies the design of the receiving system. In classical contexts, the few

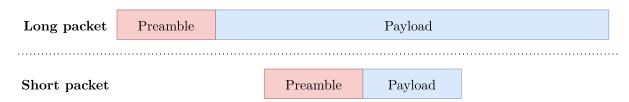

Figure 1.3 – OSI Model, with the layer of interest framed in red.

bytes of the preamble are negligible compared to the kilobytes or megabytes composing the payload. Unfortunately, in the IoT context, the packets sent are often small, from a few bytes to a few hundreds at most [13, 14]. The preamble footprint is not negligible anymore. Worse, Polyanskiy proved that the energy used during its transmission is simply lost from a communication point of view [15]. The bandwidth resource allocated to the preamble transmission is wasted for all other devices that use the same radio band.

The QCSP waveform has been designed specifically to address this issue. It allows detecting and synchronizing short packets at low SNR (lower than -20 dB), without using any preamble [16, 17]. This feature permits saving precious bandwidth resources. The waveform stems from the association of a Cyclic Code Shift Keying (CCSK) modulation and a Non Binary Error Correction Codes (NB-ECC), technologies already in use in the Chinese satellite system [18]. Theoretical results already demonstrated that a probability of Miss Detection ( $\mathcal{P}_{md}$ ) inferior to  $10^{-4}$  is achievable for a probability of False Alarm ( $\mathcal{P}_{fa}$ ) below  $10^{-6}$ . Incidentally, thanks to the lack of preamble, the complexity of the transmitter is reduced, which is logically accompanied by a drop in costs, and a higher energy efficiency. The drawback is a substantial increase in complexity at the receiving side. Although expected, it makes the implementation of a real-time receiver challenging.

The current work aims to study the feasibility of the real-time implementation of the QCSP communication chain. It thrives to propose evolution of the algorithm to improve the detection performances, while increasing the energy efficiency. Besides, several architectural optimizations beneficial to the algorithm-architecture adequacy are presented, for both software and hardware targets. The ultimate goal of the thesis is the implementation of an energy efficient cost constrained QCSP transmitter and of an associated real-time performant receiver. These devices will enable to conduct full-scale experiments that allows validating the waveform in IoT contexts, like those the Low Power Wide Area Networks (LPWANs).

It should be noted that this thesis has taken place in parallel of another, conducted by Dr. K. Saied [17]. His work was focused on the theoretical aspects of the QCSP waveform, yet we fruitfully collaborate with each other on many occasions. We built on each other strengths, the advances of one benefitting the other.

## 1.2 Manuscript outline

The current work is segmented in seven chapters, the first being this introduction.

The second chapter will precise the context of the thesis. It will consist in the definition of the main terms, and the detail of the main challenges. It will also propose a review of the existing optimization and implementation techniques, and how they may be relevant for the current work.

In the third chapter, the complete QCSP communication chain is detailed. The necessary concepts of CCSK modulation scheme and NB-ECC are explicated in the process, as well as their use in the overall algorithm. Both depend on the theory of Galois Fields (GFs), which is thus defined. An overview of the achievable detection performances of the waveform is also provided.

The fourth chapter is dedicated to the improvement made to the detection algorithm, for the purpose of efficiency. Indeed, the algorithm has been fortified, and is now immune to input scaling factors. This feature has been added after evaluating different normalization method from a complexity point of view, but also considering their impact on detection performances. Moreover, a new correlation method based on Time Sliding (TS) windows is presented. The method is demonstrated to be more efficient than the legacy method to compute the correlations crucial to the QCSP detection task. In addition, software simulations and benchmarks supporting this assumption are provided.

Throughout the fifth chapter, the QCSP transmission algorithm and the most critical task of the QCSP receiver, the detection, are analyzed under the prism of efficient implementation. In a first time, the processes involved in the transmission of a frame are detailed and context-aware optimizations are proposed for both CPU and FPGA circuits, enhancing throughput and energy efficiency. Benchmarks and achieved implementation results are presented, validating the relevance of the QCSP chain for use in LPWANs. In a second time, the most critical task of the receiver is defined, to better focus improvement efforts. After demonstrating the criticality of the correlation task inside the detector, the inherent parallelism levels of the algorithm are identified, and presented. As for the transmitting side, an updated complexity review of correlator possible implementations is provided. Indeed, we present how we took advantage of the properties of the QCSP algorithm and the features offered by manycore CPUs and FPGA circuits to reduce the complexity of the correlator. Besides, the superiority of the contributed TS approach is demonstrated, as well as the relevance of the QCSP waveform for IoT context. This is supported by the throughput achieved, and resource utilization of both the software and the hardware real-time implementations. In a third time, a quantized model of the receiver is introduced. It allows reducing yet again the resource footprint of the receiver,

while doubling the throughput. The only downside is a small detection performance toll, that do not prevent the detector to meet the required  $\mathcal{P}_{md} < 10^{-4}$  for a  $\mathcal{P}_{fa} < 10^{-6}$ .

The sixth and penultimate chapter presents the outcome of all the efforts related in the previous chapters: a complete real-time QCSP communication chain. The system is a complex heterogeneous system, yet flexible and modular. It has allowed conducting full scale experiments which permitted to put the waveform to test, and to measure its performances in real case scenarios. Besides, the results of two different experiments are provided.

Finally, the seventh and ultimate chapter concludes this thesis. It summarizes the contributions made throughout the current work, and offers perspectives for future research at short-term and long-term.

# STATE OF THE ART

#### Contents

| 2.1 | Internet of Things and associated challenge     | 25 |

|-----|-------------------------------------------------|----|

| 2.2 | Software-defined Radio platforms                | 29 |

| 2.3 | Implementation of digital communication systems | 31 |

| 2.4 | Conclusion                                      | 35 |

This chapter thrives to introduce the general context in which the current work takes place. To this end, the Internet of Things (IoT) context is presented, with its interests and the associated challenges. Notably, the relevance of short packets, as well as the non effectiveness of preambles for these packets is reviewed.

Then, the advances in Software-defined Radio (SdR) platforms are presented, as well as what they allow. First, we explain what an SdR platforms is, and give example of commonly used devices. Then, the advantages of these platforms are highlighted, and we explain how the current work can benefit from them.

Finally, the challenges related to the implementation of complex digital signal processing systems are highlighted.

### 2.1 Internet of Things and associated challenges

Wireless communication technically already existed in France in the  $18^{th}$  century, with technologies like the Chappe's telegraph [19]. Nowadays, the everlasting increase of popularity of the internet led to the appearance of several digital communication standards. The second generation mobile phone communications (2G) was initially released in the nineties, and nowadays, as of 2022, thirty years later, the fifth generation (5G) is currently in worldwide deployment [20]. The latter represents a considerable leap in

complexity compared to the previous generation, the 4G, also called Long Term Evolution (LTE). In efficiency alone, 5G is expected to perform much better than 4G. The key difference between both generation, is the range of contexts embraced by the generation.

When 4G was mainly focused on human to machine or human to human communications, the 5G aims to enhance these applications, but also enables machine to machine communications. It has boosted the development of IoT applications, that began earlier thanks to technologies such as LoRa and SigFox. It has been a strong incentive for this research field lately [21]. As said in introduction, it is hoped that the development of IoT will bring solution to contemporary issues, like energy and resource shortages. It may help to slow the global warming, which is a threatening reality [22], especially after the COVID-19 outbreak, and the exceptional climatic events of 2022.

The networks involved in the IoT have considerably evolved throughout the years [23]. Nowadays, we can distinguish at least three main use cases.

Safety context — A set of systems that require safety and security cannot be unresponsive. The needs of such systems, like autonomous vehicles, or pilot-less drones, are supposed to be addressed by Ultra Reliable Low Latency Communications (URLLC) subset of the 5G standard [24].

Massively dense context — At the opposite side, massively dense networks of high activity sensor devices, that do not require enhanced reliability, are addressed by massive Machine Type Communications (mMTC) [25], another subset of the 5G standard.

Middle ground — In the between stands the older notion of LPWANs, networks aiming for long range communications, with strong constraints on energy efficiency. For those, latency and throughput are lesser issues, but remains likable features. This is for this context that standards like LoRa and SigFox were developed.

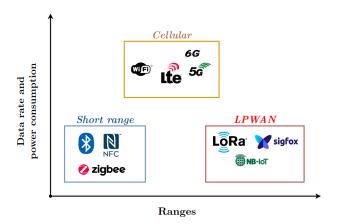

However, since cost and energy efficient implementations are required, the complexity of the algorithms involved in both transmitting and receiving sides can be a bottleneck. As represented in Fig. 2.1, LPWAN tries to achieve transmission ranges superior to cellular technologies, in conjunction with lower power consumption, thus logically for lower data rates.

Wireless Sensor Networks (WSNs) are typical examples of LPWANs. A WSN can represent a large distributed autonomous monitoring system, such as in work reported in [27] that presents ZigBee based network capabilities. The leafs of the network, that are low-end energy constrained sensor nodes, are numerous. They communicate information

Figure 2.1 – Different technologies represented in their respective field, depending on the data rates and power consumption involved against the achievable ranges [26].

to intermediate relay nodes, that themselves transmit data of several sensor nodes to base stations that aggregate the data, to perform actions [28]. This results in a complex meshed network, with several massively interconnected devices. A network like this can be prohibitively expensive, in every sense. To allow such network topology in acceptable costs, the sensor nodes have to be low-cost, thus have to use communication protocols with reduced complexity. That is less true for the relays and the base stations. For them, the priority is real-time performances. However, lower costs and energy sobriety remain sought features. The LPWAN standard [29] define some requirements in terms of efficiency, range and throughput. The battery of LPWAN sensor nodes is assumed to last from a few days to a few years for one full charge. A transmission must be able to reach its recipient for ranges of 1 to 5 km in urban areas at data rates around 100 kb/s, and up to 10 km for lower throughputs. In rural area, this range requirement goes up to 40 km.

Throughout the years, several technologies have been proposed to offer low-complexity energy efficient solutions. For contextualization purpose, three of these technologies are summarized in Table 2.1. They offer different trade-offs, but all have in common a low transmitter complexity.

Another challenge of LPWANs is the coordination of the network [30, 31]. Indeed, there is a massive number of devices, each one may want to transmit data at any in time, and the amount of data cannot be known in advance. In this condition, using a supervised protocol is impossible. Only a random access protocol can sustain the inherent constraints associated to such non-slotted massive ALOHA system [32].

Methods exist on every layer of the OSI model [33], but the best way to reduce energy consumption is to address issues at the lowest level, the physical layer. At this level, the

Table 2.1 – Overview of the features offered by three LPWAN technologies, SigFox, LoRa and NB-IoT.

|                            | SigFox                 | LoRa                   | NB-IoT             |

|----------------------------|------------------------|------------------------|--------------------|

| Modulation                 | BPSK                   | CSS                    | QPSK               |

| Central frequency          | 868 MHz                | 868 MHz                | LTE Bands          |

| ${\bf Bandwidth}$          | $0.1~\mathrm{kHz}$     | $125/250~\mathrm{kHz}$ | $200~\mathrm{kHz}$ |

| Max data rate              | $0.1 \; \mathrm{kb/s}$ | 50  kb/s               | 200  kb/s          |

| Max payload<br>length      | 96 bits                | 1944 bits              | 12.8 kilobits      |

| Urban range                | 10  km                 | $5~\mathrm{km}$        | $1~\mathrm{km}$    |

| Rural range                | $40~\mathrm{km}$       | 20  km                 | 10 km              |

| Interference<br>resilience | very high              | very high              | low                |

| Error correcting code      | none                   | Hamming codes          | Conventional codes |

solution consists on developing methods to detect and synchronize packets reliably at low SNR. The low SNR is a consequence of the lesser quality of the equipments, the low transmission power required by the energy constraints, and of the noise produced by all the other devices trying to independently communicate. The classical way to allow detection and synchronization in an unsupervised network is, as mentioned in the introduction, the use of a pilot, also called a preamble. For instance, in 4G cellular networks, Zadoff-Chu sequences are used [34], due to their excellent correlation properties, and the particularity that two different sequences are near orthogonal. For short, it means that when looking for a specific sequence, one cannot erroneously detect another.

The issue is that in LPWANs, packets sent are, for the most part, short-sized [35], (a few hundreds to a thousand of bits typically). Thus, as represented in Fig. 2.2, while resources allocated to the preamble are negligible in conventional networks, it does not remain true for LPWANs. In current IoT systems, the preamble can represent up to 50% of the data sent [24], i.e. 50% of the bandwidth consumed. In a context where the amount of bandwidth resources is limited, since multiple devices try to access it, this is unacceptable. Moreover, Polyanskiy proved that the energy allocated to detection and synchronization are wasted from the point of view of the overall communication [15], and that preamble-

Figure 2.2 – Comparisons between a long packet and a short packet, highlighting the major concern the preamble is for short packets.

less approach are theoretically possible. Indeed, past the detection and synchronization task, the preamble does not convey any useful information.

Several methods to achieve preamble-less communications are described in the literature. All reported techniques use already present information, and try to use it for detection and synchronization purpose. A classical solution is the use of Error Correction Code (ECC) as a detection marker [36]. However, it has not achieved both low complexity and good detection performances at low SNR. Another common proposition is to superpose an additional frequency information over the payload [37, 38]. This is reminiscent of how "LoRa-like" physical layer works. Nevertheless, this kind of techniques is very sensible to frequency errors, that may arise due to local oscillator inaccuracies or Doppler effect. Some recent work introduced the use of complex modulation schemes [39, 40], but they have not been implemented yet.

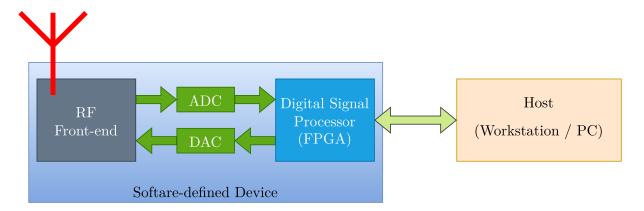

A point all the method related in the literature have in common, is that they must have been prototyped, to validate their performances. A key enabler of the current advances in wireless technologies is the democratization of Software-defined Radio (SdR) platforms. These systems boost research on those topics, by greatly reducing development cycles.

### 2.2 Software-defined Radio platforms

The concept of Software-defined Radio (SdR) platforms has emerged in the late 20<sup>th</sup> [41, 42]. A few years later, the apparition of various SdR devices and their associated platforms in the first decade of the 21<sup>st</sup> century has been a great breakthrough. Indeed, devices like the high-end Universal Software-define Radio Peripheral (USRP) from Ettus Research [43], or low-cost HackRF [44], coupled with the GNU Radio software suite [45][46] have been key enablers for the digital communication progress. Importantly, they successfully combine high versatility and high performance, satisfying the need of an efficient prototyping and fast deployment platform [47–49].

Figure 2.3 – Generic organization of Software-defined Radio (SdR) platforms.

An SdR system is often composed of an Radio-Frequency (RF) frontend associated to a reconfigurable digital processing system, as represented on Fig. 2.3. The reconfigurable system controls the RF frontend, and communicates with a "host" computer. The digital signal processing tasks can then be performed on the host, offering a very high flexibility. This is why SdR platforms are interesting for both research and industrial applications, as one unique physical device can be used to implement radically different protocols. For instance, it has enabled free and open source implementation of the LTE specification, through OpenLTE, and the very complete Open Air Interface (OAI) [50]. This framework allows simulating and even implementing state-of-the-art communication scheme on general purpose processors, sparing precious design time. In the recent years, even General Purpose Graphical Processing Unit (GPGPU) accelerated frameworks are created [51], enabling faster prototyping of complex communication schemes.

Speeding simulations and reducing prototyping times are not the only benefits of SdR advances. Recent platforms can be used to actually implement energy efficient solutions. Indeed, high-end FPGA circuits (like Xilinx Kintex and Zynq 7 in USRPs) can be intentionally oversized, to allow partially or even completely deferring digital processing to the device. Thanks to the seamless integration of GNU Radio with the hardware it targets, real-time SdR-powered LPWAN systems are born, like LoRa [52] and SigFox [53] transceivers.

However, while eased by SdR breakthroughs, the development and the efficient implementation of state-of-the-art digital communication systems remain challenging. That is especially true for LPWANs, since they have to achieve energy efficiency, reasonable data rates, and long range all together. Different ways exist to implement such communication systems, and they all require to work on the algorithm to take advantage of target-specific

features.

## 2.3 Implementation of digital communication systems

While the implementation of digital communication systems has been fastened thanks to SdR platforms like USRPs used conjointly with GNU Radio, special care must be given to the development of the related algorithms. Indeed, real-time efficient radio systems can be implemented using SdR platforms [54]. However, the digital processing involved remains complex. Their implementation thus still requires intensive work in order to minimize algorithm complexity. Algorithms also have to be parallelized and pipelined. It enables to benefit from multicore CPU or FPGA circuit features.

In the late decades, the processing performance of multicore and manycore devices has constantly improved, thanks to clock frequency increases, and to the integration of more and more Instruction Set Architecture (ISA) extensions. Associated with easy-to-use programming models [55–57], it enabled the prototyping and implementation of real-time software communication systems. While an implementation on CPU may not reach the throughputs and energy efficiency achievable with ASICs or FPGA circuits, it provides undeniable advantages. The software implementation flexibility and scalability are much higher, and prototyping time is substantially lower than for its hardware counterparts. Nevertheless, achieving high performances is challenging and requires algorithm parallelization efforts.

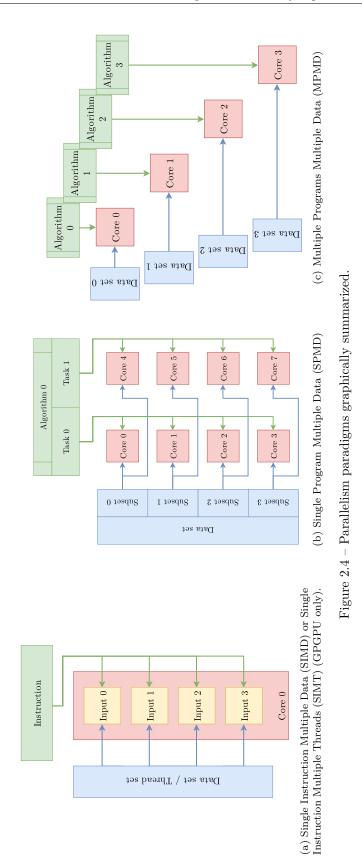

Nowadays, multicore and manycore systems can execute billions of instructions per second. They also offer parallelization opportunities that may help to achieve high throughputs and low latencies. Throughout the years, several programming languages and frameworks appears, to help in taking advantage of those opportunities. However, to actually benefit from them, it requires a substantial amount of developing time. Indeed, parallelization efforts are required to adapt the algorithm to the CPU or GPGPU architecture, and this is rarely addressed during the early stages of digital communication system design. Several types of parallelism exploitable in modern multicore and manycore architectures can help to increase data rates in baseband processing tasks. Based on Flynn's taxonomy [58, 59], we list four of them hereafter, the first three relevant for multicore CPUs and the fourth one more related to manycore GPGPUs. A graphical summary is depicted in Fig. 2.4 after the detailed explanations.

1. Single Instruction Multiple Data (SIMD): The first type of parallelism is

incidentally the one that is involved at the lowest level in processors. Current ARM and Intel architectures include vector instructions [60, 61], that are able to execute 4 to 16 floating-point operations in one clock cycle. It mechanically allows speedup by the same factors. The issue however, is that it requires the possibility for the processing to be described by unique operations on multiple inputs. Besides, to be effective, operands have to be aligned in memory, and the unique operation cannot be performed through independent tasks.

- 2. Single Program Multiple Data (SPMD): The second approach takes advantage of the number of individual physical processor cores. Modern CPUs (Intel Core I7 or ARM Cortex A72) integrate several processor cores, typically 4 to 8 for ARM circuits, and from 10 to 40 for Intel ones. Computing speed can be increased by transforming the execution of an algorithm on a set of data to the execution of n sub-tasks on n subset of data. This can allow to substantially speed up the independent sub-tasks in the algorithm, but not by a factor n. Indeed, since neither the distribution of the task over several processor cores, nor the synchronization of all processor cores after the task completion are instantaneous. Thus, the performance is impacted in accordance to Amdahl's law [62]. To be beneficial, this parallelization paradigm requires startup and data gathering time to be negligible compared to the processing time.

- 3. Multiple Programs Multiple Data (MPMD): Another way to leverage numerous processor cores is to segment the Digital Communication System (DCS), composed of several algorithms, into macro-tasks, as independent of each other as possible. Then, each one of them can be executed on its dedicated core. However, data still have to go through the complete processing pipeline. Consequently, the data rate is limited by the slowest task, incidentally called the bottleneck. A major advantage compared to the second approach though, is that tasks only need to be started and stopped once, minimizing startup and task synchronization times.

- 4. Single Instruction Multiple Threads (SIMT): Massively parallel architectures like those involved in GPGPU excel in performing various calculations simultaneously on different data. The operations executed can slightly diverge, but it may hurt computation speed. Besides, they really shines for large data set, typically of around 64 kB [63], inducing extended latencies. As demonstrated in [64], while achieving honorable performances, they may not be well suited to implement a DCS.

By making use of these parallelization techniques, it has been possible to implement

performant 4G and 5G software chains [50]. Note that it requires the conjoint use of all the paradigms to ensure efficiency [65]. These implementations have even met industry-compliant constraints. Nevertheless, a glimpse to the efforts needed to develop efficient software implementations for various ECC decoders [66–68] allows to measure the non-negligible amount of engineering time and research work needed.

Despite the fact that such software platforms are already been developed and deployed, they require high-end devices to be up to the task [69]. The issue is that the relevant systems require CPUs like Intel Xeon processors, that can consume up to 500 Watts, and cost thousands of euros per unit. Intel themselves recommend the use of (their own) Stratix FPGA devices in order to improve digital processing capabilities of their platforms [70]. Indeed, the superiority of DCS hardware implementations over software implementations in terms of raw throughputs and latency but also of energy efficiency has been highlighted in work presented in [71]. The authors presented hardware ECC decoders achieving energy efficiency  $\approx 30 \times \text{ to} \approx 100 \times \text{ superior}$  to their software counterparts. Undoubtedly, the use of the FPGA circuits available in the SdR platforms boost DCS performances, as it is done in the computer vision domain [72]. However, the design of hardware architecture for reconfigurable targets is a long and difficult process. While implementations for numerous digital processing elements already exist in the literature [11, 73–75], the amount of work needed to actually use them can be substantial. Besides, they have often been optimized for specific use cases, which limits their adaptability. In the worst cases, the lack of flexibility can be an effective barrier to their deployment and to further evolutions.

To mitigate this issue, hardware design methodology has evolved. During the last two decades, High-Level Synthesis (HLS) industrial tools have matured, and are now widely adopted [76–79]. HLS have been developed for several decades now [80, 81], in order to allow the RTL design of digital processing systems from their behavioral descriptions [82]. The way HLS tools work is similar to how a compiler functions. The main difference is that the compiler has to translate the algorithmic description into machine understandable code, suited for a specific architecture. The HLS tool tries to design and generate the architecture that best suits the algorithmic description on the specified target. This allows achieving the high performances of RTL designs, without completely sacrificing flexibility and versatility. However, the procedure realized by the tool is extremely complex. For this procedure to be successful, the behavioral description have to be synthesizable <sup>1</sup>, which requires that the designer has actual knowledge on digital circuit design. Thus, as for

<sup>1.</sup> i.e. understandable by the tool and implementable on the targeted circuits

RTL descriptions, algorithms have to be reformatted to suit hardware implementations. In addition, the description have to be tailored to the tool used, sometimes even to specific versions of a tool. For instance, in less than two years, several breaking changes have been introduced between the version 2019.1 [83] of the Xilinx HLS tool, and the version 2021.1 [84]. Consequently, the performances of the resulting implementation in throughput, latency and energy efficiency, depend on the algorithm itself, and the tool used, but also on the efforts put by the designer [85–89].

Nevertheless, HLS enables the development of hardware implementations in reduced design time, in comparison to RTL-based workflow. Even if achieved performances do not always match those of pure RTL descriptions, this time-saving feature, combined with higher flexibility, scalability and versatility, makes HLS a perfect tool for design exploration and other hardware-related research works. Especially since the democratization of Network-on-Chip systems [90] and their usage in SdR platforms, with frameworks like Ettus Research RF Network-on-Chip (RFNoC) [91].

These design procedures are complementary with multicore and manycore implementations. In an SdR platform, HLS coupled with development interface like RFNoC allow integrating all or part of the digital processing tasks as close to the RF frontend as possible [92].

### 2.4 Conclusion

As stressed out in the current chapter, the design and implementation of Digital Communication System for the IoT are anything but simple processes. The low complexity requirements, and the energy constraints, make achieving standard-compliant throughputs and latencies challenging. To make things worse, by the very nature of LPWANs, the available bandwidth is critically limited. It makes relying on preamble based approach unsustainable. Preamble-less strategies exist but can not trivially achieve acceptable detection and synchronization performances at the low SNR usual for the LPWAN context.

Nevertheless, the impressing development of SdR platforms is a game changer. Coupled with the increasing performances of multicore and manycore systems on one hand, and the maturity of HLS tools on another hand, it has enabled the real-time implementation of solutions to these problems. While design time required by algorithm parallelization and adaptation are still substantial, they are no longer prohibitive.

In the next chapter, the recently introduced Quasi-Cyclic Short Packet (QCSP) wave-

form [16, 17, 93] is presented. This new approach proposes a preamble-less detection and synchronization method, that has been demonstrated to work at low SNR. In the following chapter, the algorithm involved are analyzed and fortified. Moreover, the algorithm is optimized to increase its adequacy to intended targets. In a subsequent chapter, leveraging the parallelism types previously presented, the data rates are improved again. In addition, taking advantage of HLS, hardware specific optimizations and real-time implementations are also presented. A quantization work realized to maximize algorithm hardware adequacy is also related. Finally, a complete real-time QCSP communication system is disclosed, relying heavily on the previous efforts and on the features offered by SdR platforms.

# Quasi-Cyclic Short Packets Communication Chain

## Contents

| 3.1 | Non B  | Binary Error Correction Codes                                                                                                                       |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.1.1  | Galois Field of order $q - GF(q) \dots \dots$ |

|     | 3.1.2  | Non-Binary Low Density Parity Check                                                                                                                 |

| 3.2 | Cyclic | Code Shift Keying                                                                                                                                   |

| 3.3 | QCSP   | System Model                                                                                                                                        |

|     | 3.3.1  | Transmitter                                                                                                                                         |

|     | 3.3.2  | Channel model                                                                                                                                       |

|     | 3.3.3  | Detection                                                                                                                                           |

|     |        | 3.3.3.1 Score function                                                                                                                              |

|     |        | 3.3.3.2 Search grid                                                                                                                                 |

|     |        | 3.3.3.3 Performances                                                                                                                                |

|     | 3.3.4  | Synchronization                                                                                                                                     |

| 3.4 | Conclu | usion                                                                                                                                               |

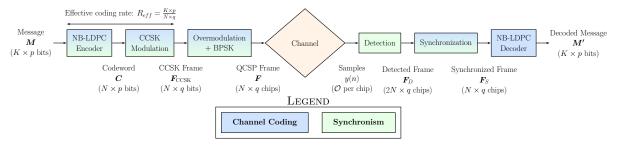

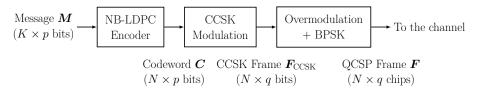

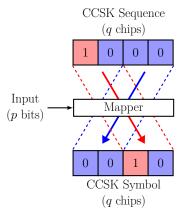

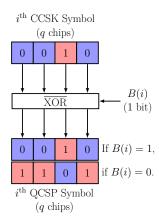

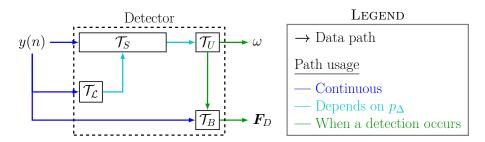

This chapter aims to present the Quasi-Cyclic Short Packet (QCSP) communication chain in details, as depicted in Fig. 3.1. Indeed, understanding the algorithm and its whereabouts is needed in order to measure the requirements of its implementation. The core feature of the QCSP communication chain resides in the association of Non Binary Error Correction Codes (NB-ECC) and Cyclic Code Shift Keying (CCSK). Thus, this chapter begins by giving an overview of both concepts. For NB-ECC, it first summarizes the notion of Galois Fields (GFs), followed by Non-Binary Low Density Parity Check (NB-LDPC) codes, the family of NB-ECC used throughout the thesis. Then it introduces briefly how NB-LDPC codes works, followed by some available decoding methods. For CCSK, it explains how a Pseudo-Noise (PN) is generated and what is its properties, then summarizes the modulation and demodulation processes. It finishes by the presentation of the complete QCSP communication chain, from the transmitter side to the retrieve of the received message. Transmission and detection stages are detailed, and the synchronization and decoding stages are quickly summarized for completeness, since they have not been explored in this work.

# 3.1 Non Binary Error Correction Codes

On any medium, through any channel, exists the risk of an erroneous communication. Whether errors come from a faulty device or a hostile environment does not matter. They must be mitigated. That is the purpose of channel coding, which aims to add redundancy to a payload (i.e. the message to transmit) to make it resilient to a certain amount of errors.

There is a large variety of error correction codes. In this work, the focus has been given to NB-ECC, that exists over GF(q) for q > 2, such that NB-LDPC codes [94], non-binary turbo codes [95], or non-binary polar codes [96]. Non-binary codes have better

Figure 3.1 – Complete QCSP system model.

| Power of $\alpha$ | Index | Polynomial              | Binary | Natural |

|-------------------|-------|-------------------------|--------|---------|

| 0                 | 0     | 0                       | 000    | 0       |

| $lpha^0$          | 1     | 1                       | 001    | 1       |

| $\alpha^1$        | 2     | $\alpha$                | 010    | 2       |

| $\alpha^2$        | 3     | $lpha^2$                | 100    | 4       |

| $lpha^3$          | 4     | $\alpha + 1$            | 011    | 3       |

| $\alpha^4$        | 5     | $\alpha^2 + \alpha$     | 110    | 6       |

| $lpha^5$          | 6     | $\alpha^2 + \alpha + 1$ | 111    | 7       |

| $\alpha^6$        | 7     | $\alpha^2 + 1$          | 101    | 5       |

Table 3.1 – Different representations of GF(8) elements for  $\mathbb{P}_3 = \alpha^3 + \alpha + 1$ .

error correction capabilities that their binary counterparts. These codes have been widely studied in the literature, due to their good performances for short payloads [97]. Moreover, they are highly compatible with high order modulations, since if the modulation order is equal to the one of the code, each symbol can be directly mapped to its modulated version, avoiding binary marginalization [98].

This section first introduces the notion of Galois field. It then briefly presents NB-LDPC codes with some decoding techniques.

# 3.1.1 Galois Field of order q - GF(q)

A Galois Field denoted GF, also called finite field, is a field which contains a finite number of elements. The number of element is called the order of the field. The Galois Field of order q is denoted GF(q).

Because it is a field, multiplication and addition are defined in GF(q) for any order  $q = \kappa^p$ ,  $\forall p \in \mathbb{N}$  and with  $\kappa$  a prime number. Both operations follow mainly the same rules they follow in traditional fields (like in  $\mathbb{R}$ , or in  $\mathbb{C}$ ). Non-zero elements of GF(q) can be represented as power of a primitive element denoted  $\alpha$ , such that the q elements GF(q) can be denoted  $\{0, 1 = \alpha^0, \alpha^1, \dots, \alpha^{q-2}\}$ . In addition, when  $\kappa = 2$ , such that  $q = 2^p$ , elements of GF(q) have a binary representation. These results from the polynomial definitions of GF(q). An example of such representation is given in Table 3.1 for q = 8 and a primitive polynomial  $\mathbb{P}_3 = \alpha^3 + \alpha + 1$ . All necessary mathematic definitions and more in depth explanations can be found in appendix A.

## 3.1.2 Non-Binary Low Density Parity Check