### Development and evaluation of solutions for the protection of DRAM and MRAM memories against Rowhammer attacks

Loïc France

#### ► To cite this version:

Loïc France. Development and evaluation of solutions for the protection of DRAM and MRAM memories against Rowhammer attacks. Cryptography and Security [cs.CR]. Université de Montpellier, 2022. English. NNT: 2022UMONS086. tel-04117848

### HAL Id: tel-04117848 https://theses.hal.science/tel-04117848v1

Submitted on 5 Jun2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THESIS TO OBTAIN THE DEGREE OF DOCTOR OF THE UNIVERSITY OF MONTPELLIER

In SyAM - Automatic and Microelectronic Systems

Doctoral school: Information, Structures and Systems sciences

#### Research Unit: LIRMM

### Development and evaluation of solutions for the protection of DRAM and MRAM memories against Rowhammer attacks

### Presented by Loïc France December 16, 2022

#### Under the supervision of Pascal Benoit and Florent Bruguier

#### **Thesis Committee:**

| Pascal BENOIT , Associate Pro <mark>fessor , University of Montpellie</mark> r      | Thesis Director      |

|-------------------------------------------------------------------------------------|----------------------|

| Florent BRUGUIER,Associa <mark>te Professor,University of Montp</mark> ellier       | Thesis Co-supervisor |

| Jean-Luc DANGER , Profess <mark>or , Telecom-ParisTech</mark>                       | Examiner             |

| Giorgio DI NATALE , Res <mark>earch Director , University of Gre</mark> noble Alpes | Reporter             |

| Guy GOGNIAT, Professor, University of Bretagne Sud                                  | Reporter             |

| Maria MUSHTAQ , Ass <mark>ociate Professor , Telecom-ParisT</mark> ech              | Examiner             |

| David NOVO , Resear <mark>ch Scientist , CNRS</mark>                                | Examiner             |

| Lionel TORRES , Pro <mark>fessor , University of Montpellie</mark> r                | Examiner             |

|                                                                                     |                      |

UNIVERSITÉ DE MONTPELLIER

### Abstract

Modern computer memories have shown reliability issues. The main memory is the target of a security threat called Rowhammer, which takes advantage of cell-to-cell disturbance between DRAM rows to cause bit-flips in adjacent victim cells of repeatedly activated aggressor rows. Moreover, as DRAM manufacturers keep increasing the memory density to improve efficiency and reduce cost, the disturbance between cells gets more important over the years, worsening the threat. The abundant research on this subject led to the development of numerous countermeasures. Each proposal comes with pros and cons in terms of modularity, performance cost, silicon area, and energy overheads, with implementation in software, hardware or both. The development of hardware-based mitigation techniques can be made easier with a computer architecture simulator such as gem5, which facilitates the development of computer architectures that integrate new hardware components with existing and future memories or other elements. However, existing simulators are not suitable for Rowhammer mitigation development, as they cannot simulate memory corruption from Rowhammer attacks, which makes verifying mitigation techniques more difficult.

In this work, we first improve the open-source simulator gem5 to make it a complete tool for Rowhammer mitigation development. We add a memory corruption module that is able to simulate the bit-flips caused by Rowhammer attacks, with various parameters to adapt it to mature and future memories, and utility functions to facilitate the integration and evaluation of mitigation techniques into the architecture. Then, we study how changing the counting granularity of counter-based Rowhammer mitigation proposals could reduce their storage requirements. Some of the most efficient proposals rely on row activation counters, using for example Counting Bloom Filters or the Misra-Gries algorithm. We demonstrate that those proposals can have their storage requirements reduced by 40% to 50% without impacting the protection level, by changing their counting granularity from bank-level to rank-level. Additionally, we propose two new Rowhammer detection mechanisms. We show that by including hardware event counters inside the architecture, a machine-learning algorithm implemented in the hardware can classify traces from these counters to detect Rowhammer attacks. We also propose a new detection mechanism that evaluates the activation frequency of every DRAM row to accurately detect aggressor rows and prevent the corruption, with an adaptive energy consumption. As a line of research, we explore the vulnerabilities of emerging non-volatile memories to variations of the Rowhammer attack. Through power consumption analysis, we retro-engineer the internal architecture of commercial Toggle-MRAM and STT-MRAM to design attacks that are susceptible to produce bit-flips in the memory, and execute these attacks to check if they can corrupt the memory.

### Résumé de la thèse

Les mémoires des ordinateurs modernes sont sujettes à des problèmes de fiabilité. La mémoire principale est la cible d'une attaque appelée Rowhammer, qui exploite les perturbations électriques entre les lignes de la DRAM pour corrompre la donnée stockée dans les cellules voisines de cellules activées fréquemment. De plus, la densité des mémoires augmentant avec l'amélioration des technologies de fabrication pour optimiser l'efficacité et réduire les coûts, les effets des perturbations entre les lignes sont de plus en plus importants, empirant la menace. La recherche abondante sur ce sujet a conduit au développement de nombreuses contremesures. Chaque proposition a ses propres avantages et inconvénients en termes de modularité, d'impact sur les performances, sur la surface de silicium ou la consommation énergétique, avec des implémentations purement logicielles, matérielles ou un mélange des deux. Le développement de contremesures peut être facilité par l'utilisation d'un simulateur d'architecture tel que gem5, qui simplifie l'intégration de nouveaux composants matériels avec différentes technologies de mémoires et de processeurs. Cependant, les simulateurs existants étant incapables de simuler la corruption de la mémoire produite par une attaque Rowhammer, ils ne sont pas appropriés pour le développement de protections contre Rowhammer car ils ne permettent pas de vérifier l'absence de corruption.

Dans un premier temps, nous proposons une amélioration du simulateur ouvert gem5 pour en faire un outil de développement de contremesure contre Rowhammer. Nous y incorporons un simulateur de corruption de mémoire capable de simuler des bit-flips causés par les attaques Rowhammer, configurable en plusieurs points pour l'adapter aux mémoires existantes et futures, et fournissant les fonctions nécessaires à l'intégration et l'évaluation de contremesures dans l'architecture. Dans un deuxième temps, nous étudions comment le changement de granularité de comptage peut réduire les besoins en mémoire de certaines contremesures contre Rowhammer. Parmi les propositions de contremesures les plus efficaces à ce jour, certaines utilisent des compteurs d'activations des lignes de la DRAM, en utilisant par exemple les compteurs à filtre de Bloom ou l'algorithm de Misra-Gries pour réduire les besoins en mémoire. Nous démontrons que ces propositions peuvent avoir leurs besoins en mémoire réduits de 40% à 50% sans impacter le niveau de protection, en modifiant la granularité de comptage du niveau *bank* au niveau *rank* de l'architecture de la DRAM. Dans un troisième temps, nous proposons deux nouveaux mécanismes de détection des attaques Rowhammer. La première proposition utilise un algorithme de machinelearning ainsi que des compteurs d'événements introduits dans l'architecture pour détecter les attaques Rowhammer. La seconde proposition combine le comptage des activations et l'évaluation de la fréquence d'activation de toutes les lignes de la DRAM pour détecter les attaques. Dans un quatrième et dernier temps, nous explorons les vulnérabilités des mémoires émergentes non-volatiles aux variations de l'attaque Rowhammer. En analysant la consommation d'une mémoire externe de technologies Toggle-MRAM et STT-MRAM lors de différentes opérations de lecture et d'écriture, nous reconstituons une partie de l'architecture interne de ces mémoires, afin de concevoir des attaques susceptibles de corrompre les données stockées, puis exécutons ces attaques pour évaluer la vulérabilité de ces mémoires.

### Acknowledgements

This thesis was made possible with the support of many people, which I would like to thank.

Foremost, I want to express my gratitude to my supervisors Pascal Benoit, Florent Bruguier, Maria Mushtaq and David Novo, who all offered assistance in various fields. Their support during those three years has been a major contribution to the success of my thesis. First, my thesis director Pascal Benoit, for his mentorship, scientific support and guidance. The regular meetings we had maintained a productive work throughout the duration of the thesis Then, Florent Bruguier, who brought this thesis subject to me, and was my day-to-day contact to discuss about all aspects of my contributions and publications; Maria Mushtaq, who offered her helped at the beginning of my thesis, participated in the development of my first contribution and continued to follow me to the end of my thesis; and last but not least David Novo, for his listening, scientific knowledge and help on the publications to bring the best out of them.

I am grateful for my PhD student colleagues Theo Soriano and Paul Delestrac with whom I shared the office during this three years and regularly brainstormed on research subjects, and Quentin Huppert for accompanying us through our theses; I also thank my other colleagues Jonathan Miquel, Geoffrey Chancel and Julien Toulemont who shared lunch and coffee breaks with us.

I extend my appreciation to the teachers of my former engineering school Polytech Montpellier, especially Laurent Latorre, Eric Dubreuil and Guy Cathébras, who offered me the possibility to give programming lessons to students, which played an important part of the last three years.

I want to thank former Engineer student Constantin Gaboury for his contribution in the experiments on STT-MRAM memories for his end-of-study project.

I am truly thankful to the reviewers of this manuscript Guy Gogniat and Giorgio Di Natale for the time they took to review my thesis manuscript and their helpful feedback, and all jury members presided by Lionel Torres for their interest in my work, their interesting questions and suggestions. Finally, I express my gratitude to my family and friends who have supported me up to this day, and have without a doubt contributed to this achievement.

The authors acknowledge the support of the French Agence Nationale de la Recherche (ANR), under grant ANR-19-CE39-0008 (project ARCHI-SEC). They also acknowledge the French Ministère des Armées – Agence de l'innovation de défense (AID) under grant ID-UM-2019 65 0036.

### Contents

| Li | List of Figures |         |                                                         |      |

|----|-----------------|---------|---------------------------------------------------------|------|

| Li | st of '         | Tables  |                                                         | xv   |

| Li | st of           | Algori  | thms                                                    | xvii |

| Li | st of           | Acrony  | yms                                                     | xix  |

| 1  | Intr            | oductio | on                                                      | 1    |

|    | 1.1             | Conte   | ext                                                     | 2    |

|    | 1.2             | Contr   | ibution                                                 | 3    |

| 2  | Bac             | kgroun  | ıd                                                      | 5    |

|    | 2.1             | Memo    | ory Architecture and operation                          | 6    |

|    |                 | 2.1.1   | Memory architecture, Core to main memory read operation | 6    |

|    |                 | 2.1.2   | DRAM architecture and operation                         | 7    |

|    | 2.2             | Rowh    | nammer attack                                           | 13   |

|    |                 | 2.2.1   | Cell-to-cell disturbance                                | 13   |

|    |                 | 2.2.2   | Basic exploit                                           | 15   |

|    |                 | 2.2.3   | Exploits in literature                                  | 17   |

|    | 2.3             | Rowh    | nammer countermeasures                                  | 19   |

|    |                 | 2.3.1   | Basic Principles                                        | 19   |

|    |                 | 2.3.2   | Software-based protection                               | 20   |

|    |                 | 2.3.3   | Hardware probabilistic protection                       | 20   |

|    |                 | 2.3.4   | Hardware counter-based protection                       | 21   |

|    |                 | 2.3.5   | Conclusion                                              | 23   |

|    | 2.4             | Concl   | lusion                                                  | 23   |

| 3 | Rov | vhamm    | ner Simulation                                                    | 25 |

|---|-----|----------|-------------------------------------------------------------------|----|

|   | 3.1 | Motiv    | ration                                                            | 26 |

|   | 3.2 | Rowh     | ammer simulation requirements                                     | 28 |

|   | 3.3 | gem5     | and Ramulator                                                     | 31 |

|   | 3.4 | Memo     | ory Corruption simulation                                         | 33 |

|   |     | 3.4.1    | Integration of the memory-corruption module in gem5 and Ra-       |    |

|   |     |          | mulator                                                           | 33 |

|   |     | 3.4.2    | Disturbance and corruption simulation                             | 34 |

|   | 3.5 | Mitiga   | ation integration in gem5                                         | 37 |

|   | 3.6 | Usage    | e, limitations and evaluation                                     | 38 |

|   |     | 3.6.1    | Limitations                                                       | 40 |

|   |     | 3.6.2    | Evaluation                                                        | 41 |

|   | 3.7 | Concl    | usion                                                             | 42 |

| 4 | Cou | inter-ba | ased Rowhammer mitigations improvement                            | 43 |

|   | 4.1 | Motiv    | vation                                                            | 44 |

|   | 4.2 | Bank-    | level and rank-level counting granularity                         | 44 |

|   | 4.3 | Implie   | cation in State-of-the-art mitigation proposals                   | 46 |

|   | 4.4 | Consi    | derations for technology and timings                              | 49 |

|   |     | 4.4.1    | DDR generation parameters                                         | 49 |

|   |     | 4.4.2    | Feasibility - timing considerations                               | 50 |

|   | 4.5 | Concl    | usion                                                             | 51 |

| 5 | Mit | igation  | proposals                                                         | 53 |

|   | 5.1 | Motiv    | vation                                                            | 54 |

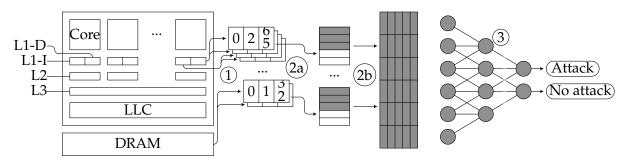

|   | 5.2 | Hardy    | ware counters and machine learning for Rowhammer detection        | 54 |

|   |     | 5.2.1    | Methodology                                                       | 55 |

|   |     | 5.2.2    | Experiments and results                                           | 57 |

|   |     | 5.2.3    | Conclusion                                                        | 60 |

|   | 5.3 | F-Cor    | D: Forgetful Counters for Rowhammer Detection                     | 61 |

|   |     | 5.3.1    | Introduction: Unsynchronised refresh issue for counter-based Row- | •  |

|   |     |          | hammer mitigation                                                 | 61 |

|   |     | 5.3.2    | Tracking frequently-activated rows                                | 62 |

|   |     | 5.3.3   | Detecting attacks                                     | 64  |

|---|-----|---------|-------------------------------------------------------|-----|

|   |     | 5.3.4   | Discretisation                                        | 68  |

|   |     | 5.3.5   | Periodic maintenance                                  | 69  |

|   |     | 5.3.6   | Implementation details                                | 71  |

|   |     | 5.3.7   | Number of entries                                     | 73  |

|   |     | 5.3.8   | Example                                               | 74  |

|   |     | 5.3.9   | Conclusion                                            | 75  |

| 6 | Exp | erimen  | ts on MRAM                                            | 77  |

|   | 6.1 | Motiv   | ation                                                 | 78  |

|   | 6.2 | Attack  | c on a Toggle-MRAM chip                               | 82  |

|   |     | 6.2.1   | Platform Requirements                                 | 82  |

|   |     | 6.2.2   | Test Platform                                         | 83  |

|   |     | 6.2.3   | Reverse-engineering of the memory module architecture | 86  |

|   |     | 6.2.4   | Designing the attack                                  | 88  |

|   |     | 6.2.5   | Results                                               | 90  |

|   | 6.3 | Attack  | c on an STT-MRAM chip                                 | 91  |

|   |     | 6.3.1   | Test Platform                                         | 91  |

|   |     | 6.3.2   | Reverse-engineering of the memory module architecture | 92  |

|   |     | 6.3.3   | Designing the attack                                  | 94  |

|   |     | 6.3.4   | Results                                               | 94  |

|   | 6.4 | Conclu  | usion                                                 | 95  |

| 7 | Con | clusior | n and Perspectives                                    | 97  |

|   | 7.1 | Contri  | ibutions                                              | 98  |

|   |     | 7.1.1   | Rowhammer simulation in gem5                          | 98  |

|   |     | 7.1.2   | Improvement of Rowhammer mitigations                  | 99  |

|   |     | 7.1.3   | Mitigation proposals                                  | 99  |

|   |     | 7.1.4   | Experiments on MRAM                                   | 99  |

|   | 7.2 | Future  | ework                                                 | 100 |

|   | 7.3 | Conclu  | uding remarks                                         | 101 |

|   |     |         |                                                       |     |

### Bibliography

# **List of Figures**

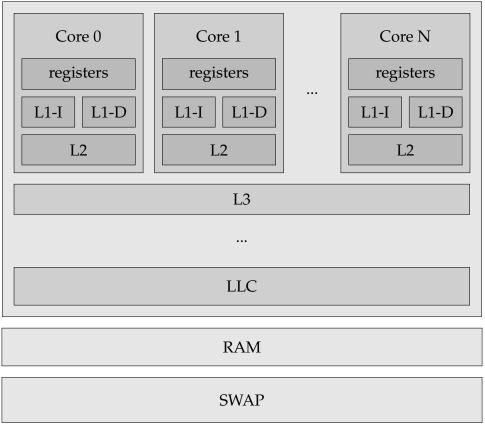

| 2.1  | Memory architecture for run-time data in modern computers            | 7  |

|------|----------------------------------------------------------------------|----|

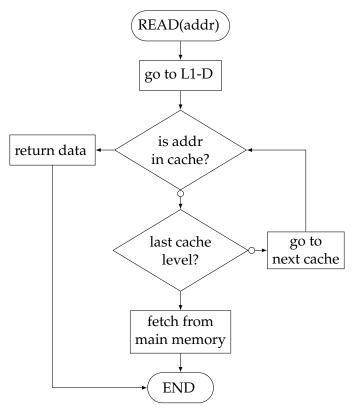

| 2.2  | Read operation flowchart (simplified) from CPU Core to main memory . | 8  |

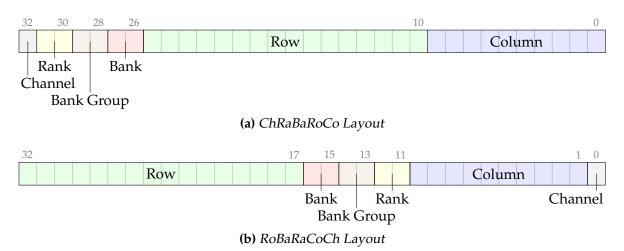

| 2.3  | Address bit layouts                                                  | 8  |

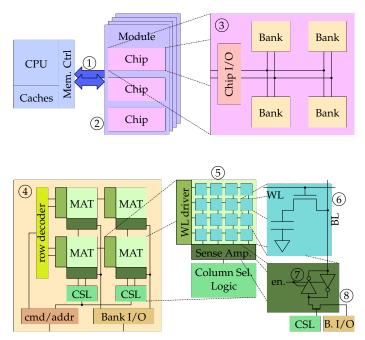

| 2.4  | Processor to DRAM bank architecture                                  | 9  |

| 2.5  | Bank-level states and data-access-related commands                   | 10 |

| 2.6  | ACTIVATE-PRECHARGE cycle                                             | 11 |

| 2.7  | Illustration of DDR timings                                          | 13 |

| 2.8  | Charge trapping and migration to victim memory cells                 | 14 |

| 2.9  | Memory cell capacitor voltage evolution under normal behaviour and   |    |

|      | under disturbance                                                    | 14 |

| 2.10 | Memory bank under attack                                             | 16 |

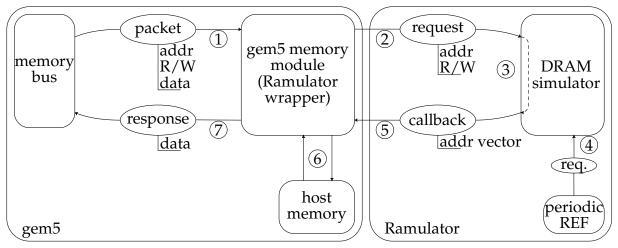

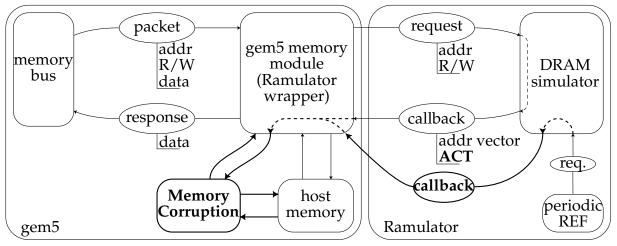

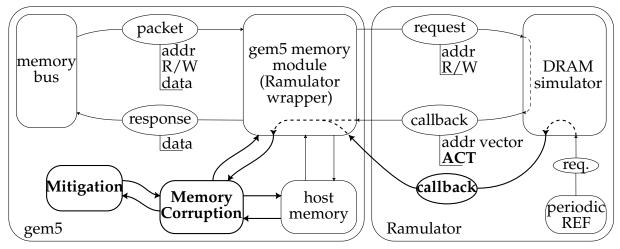

| 3.1  | gem5 and Ramulator memory architecture                               | 32 |

| 3.2  | gem5 and Ramulator memory architecture, with the Memory-Corruption   |    |

|      | module                                                               | 34 |

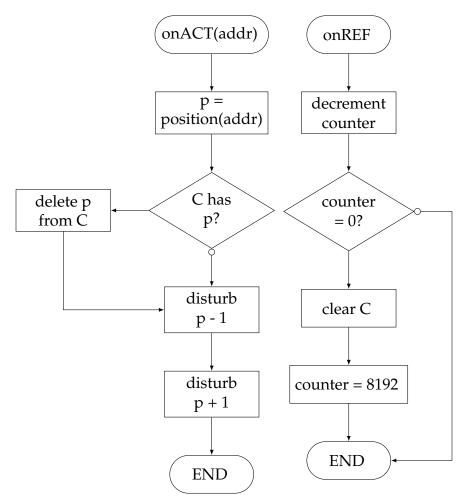

| 3.3  | ACT and REF callback functions                                       | 35 |

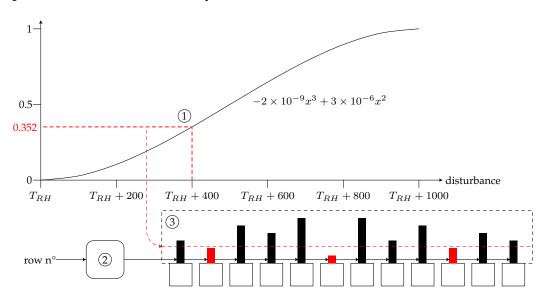

| 3.4  | disturbance simulation                                               | 36 |

| 3.5  | Bit-flip simulation with polynomial equation                         | 37 |

| 3.6  | gem5 and Ramulator memory architecture, with Memory-Corruption       |    |

|      | module and Rowhammer mitigation                                      | 38 |

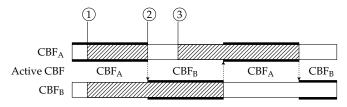

| 4.1  | Alternating CBFs of BlockHammer                                      | 48 |

| 5.1  | Machine Learning detection mechanism integration in computer archi-  |    |

|      | tecture                                                              | 57 |

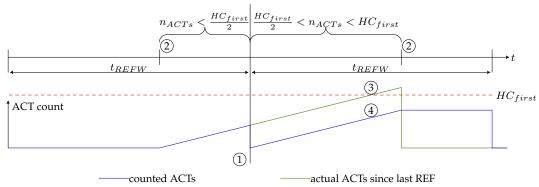

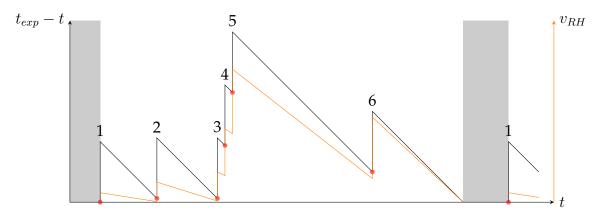

| 5.2  | Counters reset not synchronised with row refresh                     | 62 |

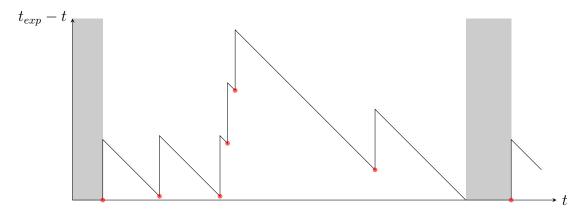

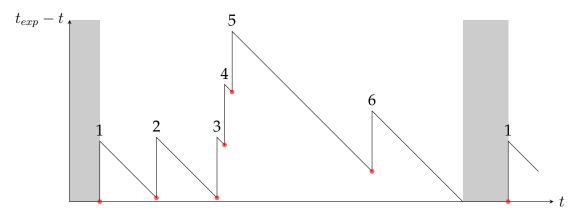

| 5.3  | Evolution of the remaining time for one row in the table             | 64 |

| 5.4  | Evolution of the counter for one row in the table                    | 65 |

| Evolution of the value for one row in the table                       | 66                     |

|-----------------------------------------------------------------------|------------------------|

| Split attack on F-CoRD                                                | 67                     |

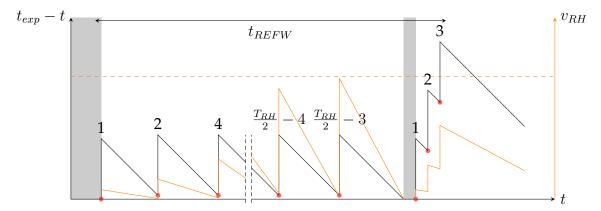

| Slow attack with discrete timings                                     | 69                     |

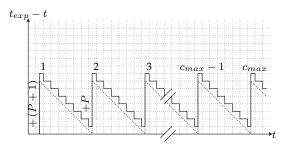

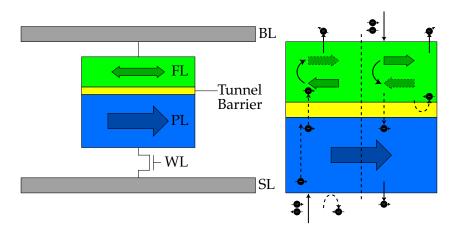

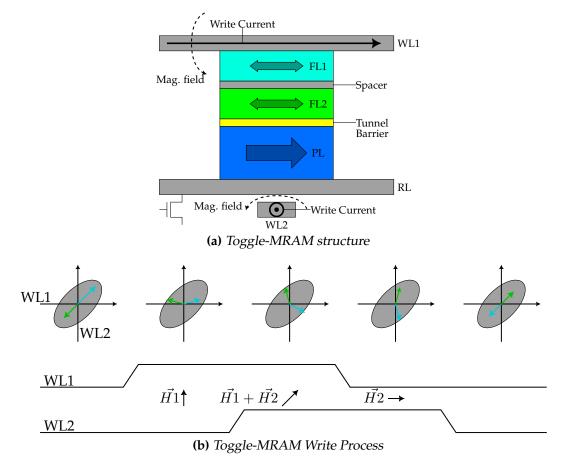

| Bit-cells of Emerging NVMs                                            | 79                     |

| STT-MRAM structure and write process                                  | 80                     |

| Toggle-MRAM structure and write process                               | 80                     |

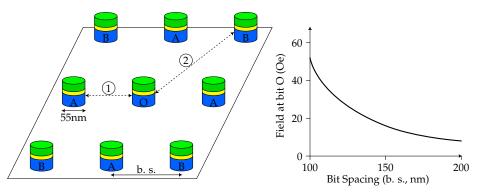

| Cell-to-cell magnetic disturbance on MRAM                             | 81                     |

| Rowhammer effect on STT-MRAM                                          | 82                     |

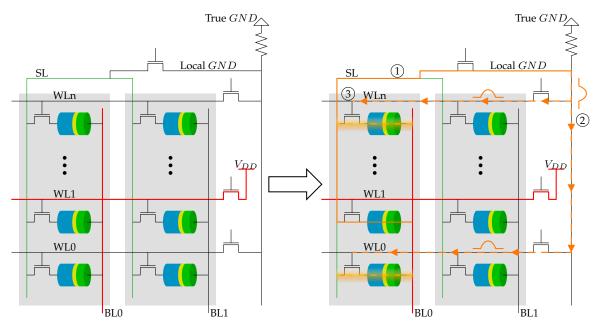

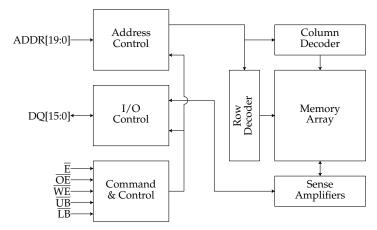

| Simplified architecture of the Toggle-MRAM module                     | 83                     |

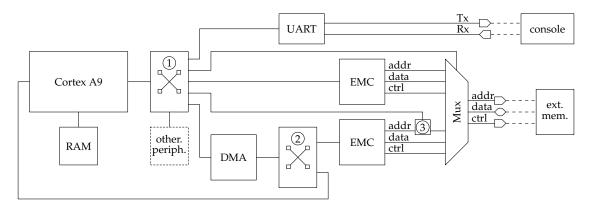

| FPGA-based platform peripherals architecture                          | 84                     |

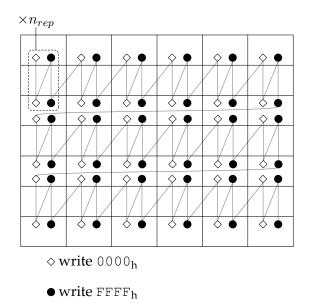

| Attack pattern on Toggle-MRAM                                         | 89                     |

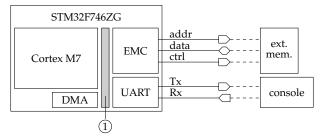

| Microcontroller-based platform architecture                           | 92                     |

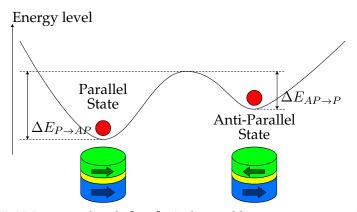

| STT-MRAM energy levels                                                | 93                     |

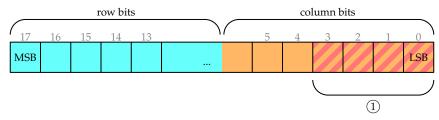

| Hypotyhesis on the order of row and column bits in the address vector |                        |

| of the stt-mram module                                                | 94                     |

|                                                                       | Split attack on F-CoRD |

### List of Tables

| 2.1 | DRAM timing parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Architecture Simulators comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

| 3.2 | DRAM layout configuration example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40 |

| 3.3 | Impact of the Memory-Corruption module (M-C) on simulation perfor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | mance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

| 4.1 | Values of $W_B$ and $W_R$ , number of banks per rank, and theoretical re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | duction of total number of counters, for DDR3, DDR4 and DDR5 (c.f.,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | Table 2.1 page 12).         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | 46 |

| 4.2 | Values of $W_B$ and $W_R$ , number of banks per rank, and theoretical re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | duction of total number of counters, for DDR3, DDR4 and DDR5 (c.f.,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | Table 2.1 page 12).         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | 50 |

| 5.1 | ML models categorisation accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60 |

| 5.2 | minimum table size for the F-CoRD implementationon DDR3, DDR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|     | and DDR5, for a bank-level implementation counting granularity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

| 6.1 | Current consumption of Toggle-MRAM memory module for read oper-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87 |

| 6.2 | Toggle-MRAM deducted address layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87 |

| 6.3 | Current consumption of Toggle-MRAM memory module for write oper-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|     | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88 |

| 6.4 | current measurements during read and write operations on the STT-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | MRAM memory module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93 |

# List of Algorithms

| 1 | F-CoRD global algorithm                            | 72 |

|---|----------------------------------------------------|----|

| 2 | Calculate the required number of entries of F-CoRD | 73 |

| 3 | Attack algorithm on Toggle-MRAM                    | 89 |

## **List of Acronyms**

| ACT   | Activate command              |

|-------|-------------------------------|

| ALU   | Arithmetic Logic Unit         |

| BL    | Bit Line                      |

| CAM   | Content-addressable Memory    |

| CBF   | Counting Bloom Filter         |

| CNN   | Convolutional Neural Network  |

| CSL   | Column Selection Logic        |

| CPU   | Central Processing Unit       |

| DDR   | Double Data Rate (memory)     |

| DIMM  | Dual In-line Memory Module    |

| DMA   | Direct Memory Access          |

| DRAM  | Dynamic Random Access Memory  |

| EMC   | External Memory Controller    |

| FN    | False Negative                |

| FP    | False Positive                |

| FPGA  | Field-Programmable Gate Array |

| HPC   | Hardware Performance Counter  |

| LLC   | Last-Level Cache              |

| LPDDR | Low Power DDR memory          |

| LSTM  | Long Short-Term Memory        |

| MAT   | Memory Array Tile             |

| ML    | Machine Learning              |

| MLP   | Multi-Layer Perceptron        |

| MRAM  | Magnetic Random Access Memory |

| MTJ   | Magnetic Tunnel Junction      |

|       |                               |

| NVM      | Non-Volatile Memory            |

|----------|--------------------------------|

| OS       | Operating System               |

| PRE      | Precharge command              |

| PRNG     | Pseudo-Random Number Generator |

| RAM      | Random Access Memory           |

| RB       | Row Buffer                     |

| REF      | Refresh command                |

| RFM      | Refresh Management command     |

| RTL      | Register-Transfer Level        |

| SA       | Sense Amplifier                |

| STT-MRAM | Spin-Transfer Torque MRAM      |

| WL       | Word Line                      |

# Ι

### Introduction

### Contents

| 1.1 | Context      | 2 |

|-----|--------------|---|

| 1.2 | Contribution | 3 |

### 1.1 Context

Memory is a key component of computing systems. It is used to store the input values, intermediate variables and end results of any program. Over the years, following the Moore's Law, computing systems have become exponentially more powerful, allowing computers to run faster, with an increasing number of more and more complex programs running in parallel. Handling this complexity and speed requires the memory to become faster, with an ever-increasing capacity to store the large quantity of data programs need during run-time. The most popular technology nowadays for the main memory is the Dynamic Random Access Memory (DRAM). This technology uses capacitors to store the data: the charge of each capacitor determines the value of the bit it stores. Again, following the Moore's law, DRAM manufacturers have been able to increase the density of the memory, reducing the production cost per bit and allowing more data to be stored in the same silicon area.

However, as the memories became denser, storage capacitors became smaller, and their maximum capacity reduced. Additionally, physical phenomenon that originally had no consequence on the behaviour of the devices started to cause reliability issues. In 2014, Kim et al. [1] published the first public paper on cell-to-cell disturbance errors caused by DRAM row activations. When a DRAM row is activated, undesired electric communication between adjacent DRAM rows disturb the storage nodes of adjacent rows. Capacitors of victim storage nodes, which by nature already leak charge over time, see their charge reduced by a small amount when disturbed. This additional leakage is not important and do not compromise the data by itself, as capacitors are periodically refreshed to compensate their natural leakage. However, repeated activations of the neighbouring rows can cause this disturbance to progressively empty the victim capacitors, effectively flipping the bits.

The authors showed that this phenomenon can be easily leveraged by a malicious program to mount the Rowhammer attack. Over the next years, several contributions showed that this attack can be improved to cause major issues in modern computers, ranging from discovering encryption keys [2] to remotely disabling systems [3] or performing privilege escalation from web browsers [4]. In the same time, various mit-

igation techniques were proposed by the community or the manufacturers to prevent those attacks from harming the systems. Some proposals are implemented in software, and try to detect the attack processes from their abnormal memory activity; some are implemented in hardware, in the memory controller or in the memory modules, and refresh the potential victim rows before they experience bit-flips; finally, some mitigation proposals are implemented in both hardware and software, detecting potential aggressor rows using hardware components and asking the software to stop or slow down the suspicious processes. In addition to the variety of implementation levels, we see a variety of detection methods. Some proposals exploit the already-implemented Hardware Performance Counters (HPC) to detect suspicious memory activity; some implement row activation counters to detect rows that are activated too many times; some use probabilistic mechanism to prevent aggressor rows to corrupt neighbour rows; finally, some exploit specific mechanisms such as empty "barrier" DRAM rows, or randomly swapped rows to prevent aggressor from corrupting critical data.

However, as DRAM manufacturers continue to increase the storage density, attacks are made easier. The minimum amount of activations to produce a bit-flip has drastically reduced, and it became possible to corrupt rows that are not immediately adjacent to the aggressor rows. Hence, most mitigation proposals become useless against recent attack. Manufacturer's proprietary mitigation techniques are proved to be ineffective, and some proposals incur increasing performance and silicon area overhead to stay effective on more and more vulnerable memories. Therefore, Rowhammer mitigation is still to this day an important issue that requires extensive research.

### **1.2** Contribution

During the development of a Rowhammer mitigation technique, testing on a working system is an important step, that helps optimising the solution and permits the validation against state-of-the-art attacks. However, most proposals require modifications of hardware components, sometimes in the DRAM, and therefore cannot be implemented on existing systems. For our first contribution, we present a simulation tool to develop and validate Rowhammer attacks on a configurable computer architecture. The tool simulates the memory corruption caused by Rowhammer attacks, and provides tools to implement various mitigation techniques.

Counter-based hardware mitigation techniques are among the most efficient Rowhammer mitigation techniques. Most of them are implemented with a bank-level counting granularity, which means that each bank has a dedicated set of counters. However, due to limitation at the rank level, all banks of the memory cannot be accessed at their maximum frequency. For our second contribution, we propose to change the counting granularity of some mitigation proposals to rank level to reduce the required number of counters, ultimately reducing the dedicated memory size by 40% to 50%.

Rowhammer mitigation is still an open research. Numerous mitigation techniques are proposed every year, using different algorithms to detect the attacks while trying to reduce the performance and area overhead to the minimum. For our third contribution, we propose two new detection mechanisms. Machine learning has not been extensively studied as a detection mechanism. In our first proposal, we demonstrate that machine learning can be exploited as a hardware component to detect Rowhammer attacks using counters of specific micro-architecture events. For our second proposal, we describe a new counter-based mitigation technique that uses the activation frequency of each row to detect aggressors.

Recent memory technologies such as the various Magnetic Random Access Memory (MRAM) variants show promising characteristics as DRAM replacements. However, the vulnerability of this new technology has not been extensively studied. Previous studies have shown that these technologies may be vulnerable to cell-to-cell disturbance error. In our last contribution, we try to attack two commercially-available MRAM external memory modules using custom platforms. We show that even if the attacks we try are not able to produce bit-flips in the memory, we can successfully retroengineer some information about the internal structure and behaviour of the memory modules, that could be leveraged to perform side-channel attacks.

# Π

# Background

### Contents

| 2.1 | Memory Architecture and operation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $ |                                                           |    |

|-----|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|----|

|     | 2.1.1                                                                                        | Memory architecture, Core to main memory read operation . | 6  |

|     | 2.1.2                                                                                        | DRAM architecture and operation                           | 7  |

| 2.2 | Rowh                                                                                         | ammer attack                                              | 13 |

|     | 2.2.1                                                                                        | Cell-to-cell disturbance                                  | 13 |

|     | 2.2.2                                                                                        | Basic exploit                                             | 15 |

|     | 2.2.3                                                                                        | Exploits in literature                                    | 17 |

| 2.3 | Rowh                                                                                         | ammer countermeasures                                     | 19 |

|     | 2.3.1                                                                                        | Basic Principles                                          | 19 |

|     | 2.3.2                                                                                        | Software-based protection                                 | 20 |

|     | 2.3.3                                                                                        | Hardware probabilistic protection                         | 20 |

|     | 2.3.4                                                                                        | Hardware counter-based protection                         | 21 |

|     | 2.3.5                                                                                        | Conclusion                                                | 23 |

| 2.4 | Conclu                                                                                       | usion                                                     | 23 |

### 2.1 Memory Architecture and operation

#### 2.1.1 Memory architecture, Core to main memory read operation

In modern computing systems such as consumer computers, memory is a key component. During run-time, the largest portion of the data used by running programs is stored in a Random-Access Memory (RAM). Data transit between the main memory and the processor through multiple cache memory levels, integrated in the processor. These cache memories are faster to access than the main memory, but have much lower capacity. They are organised in levels, typically from L1 to L4. Higher cache levels have more storage capacity, but are slower to access. The cache memories are used to store the most frequently used data. Ideally, the more frequently used are the data, the lower they are stored in the cache levels. While the last levels are global to the processor, each core has its own sets of first level caches (typically L1 and L2). Moreover, the first cache level is split into instructions cache and data cache. Finally, each core has its own register file, which it uses to store data when performing operations on it. Register files have a very low capacity, but are directly connected to the Arithmetic Logic Units (ALU), and therefore provide very low access time. When the registers are needed to store other data, this data is stored back in the address space mapped to the RAM which is external to the processor. When a requested data is not stored in a cache memory, it is fetched from the RAM. When a data is evicted from the cache, it is stored back in the RAM.

If the RAM (or main memory) capacity is not sufficient, a SWAP partition can be used in the hard drive to temporarily store run-time data that is more rarely used. The memory architecture is illustrated in Figure 2.1.

When the core requests some data from the memory, it usually follows the process illustrated in Figure 2.2. The request first goes to the first cache level (L1-I for instructions, or L1-D for other data). If the data is stored in this cache, it is returned. Otherwise, the request goes to the next cache level, on which the same test is performed. If the data is not stored at any level of the cache memories, the request is passed on to the main memory. After fetching from a higher cache level or the main memory, the new

Figure 2.1: Memory architecture for run-time data in modern computers

data can be stored in the current cache, replacing older data following some eviction rules. We call the event of a data found in a cache memory a cache hit, and the data missing in a cache memory a cache miss.

#### 2.1.2 DRAM architecture and operation

In consumer computers, the technology used for the main memory is the Dynamic Random Access Memory (DRAM) technology.

In this memory, the data is addressed using the following architecture levels, from higher to lower: channel, rank, bank group, bank, row and column. Each level has its own bits in the address word, depending on the chosen layout. Two common address layouts, ChRaBaRoCo and RoBaRaCoCh (**Ch**: Channel, **Ra**: Rank, **Ba**: Bank, **Ro**: Row, **Co**: Column, Bank group is omitted), are illustrated in Figure 2.3.

The architecture of a DRAM main memory is illustrated in Figure 2.4. The proces-

Figure 2.2: Read operation flowchart (simplified) from CPU Core to main memory

Figure 2.3: Address bit layouts for a main memory of 2 channels, 4 ranks of DDR4 8Gb x8

sor communicates with the main memory through distinct memory channels ①, each having its own set of command, data and address buses. Multiple memory modules ② (usually Dual In-line Memory Modules, DIMM) can be connected to a single channel. A module includes multiple memory chips ③, grouped in ranks. The command and address buses are common to all chips, but the data bus is split among all the chips of a rank. A memory chip contains several banks ④, grouped in bank groups.

The bank is the smallest structure visible to the memory controller. It is the target

Figure 2.4: Processor to DRAM bank architecture

of all data-access requests. A bank is made of interface ports, drivers to select the row to activate (the row decoder) and the column to read or write on (the column selection logic, CSL), and a set of Memory Array Tiles (MAT) (5).

In a MAT, the bit cells (6) are organised in a matrix, where all cells of a row share a unique wordline (WL), and all cells of a column share a unique bitline (BL). The MAT also contains a WL driver and a set of Sense Amplifiers, which are used to read and write values in cells. A memory cell is the combination of one capacitor and one transistor. The transistor, called access transistor, is driven by the WL of the row. When activated, it connects one end of the capacitor to the BL of the column. The other end of the capacitor is permanently connected to the ground. The charge of this storage capacitor defines the value of the bit stored by the cell.

At one end of the BL is the Sense Amplifier (SA) (7), which is made of two inverters in a cross-coupled configuration. One side is connected to the BL, and when the bit is accessed, the CSL connects the other end of the SA to the bank data I/O (8). The Sense amplifiers are also used to store the last accessed row, therefore the set of Sense amplifiers is also called Row Buffer (RB).

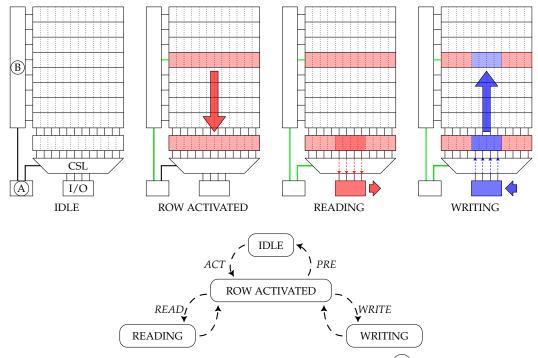

To read or write data in the memory, the target row must be activated to load its content in the RB, before accessing the data in the RB. The PRECHARGED state, AC-

TIVATE, READ and WRITE commands are illustrated in Figure 2.5.

- When no row is loaded in the RB, the bank is in the idle state.

- To load a DRAM row in the RB, the memory controller issues an ACTIVATE command (ACT) to the bank.

- when a row is loaded in the RB, the memory controller can issue READ commands to request data from the RB,

- or WRITE commands to change data in the RB. As the row is still activated, any change on the RB is reflected in the DRAM row.

- When an other row is accessed, the connection between the currently-activated row and the RB must first be closed using the PRECHARGE command (PRE), resetting the bank to the PRECHARGE state.

**Figure 2.5:** Bank-level states and data-access-related commands. (A): cmd/addr decoder, (B): row decoder and WL driver. Changing from IDLE state to ROW ACTIVATED state and back is done using the commands ACT and PRE. commands READ and WRITE temporarily change the state to READING and WRITING, but automatically it changes back to ROW ACTIVATED once the operation is completed.

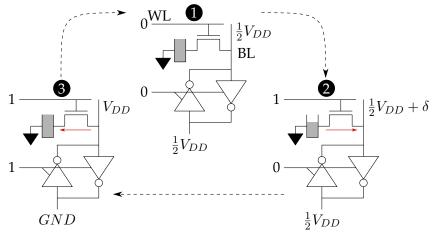

Loading rows in the RB is done using the ACTIVATE-PRECHARGE cycle. On an electrical level, the ACTIVATE-PRECHARGE cycle is illustrated in Figure 2.6.

**Figure 2.6:** ACTIVATE-PRECHARGE cycle. the grey rectangle inside the capacitor represents its charge.

- 1. By default, every bit-cell is in the precharged state ①: the capacitor is fully charged (resp. fully depleted), the WL is lowered, and both ends of the SA, including the BL, are maintained at a voltage of  $\frac{1}{2}V_{DD}$ .

- 2. In order to load the content of the bit in the row buffer, the memory controller issues an ACT to the bank. When the bank receives this command, the appropriate WL is raised, connecting the capacitor of the memory cells in the target row to their BL. Each capacitor and its BL share their charge, raising the voltage of the BL to  $V_{DD} + \delta$  (resp. lowering it to  $V_{DD} \delta$ ) 2. Then, the SA is enabled, detects the voltage difference between its ends, and amplifies it until the BL is at  $V_{DD}$  (resp. *GND*) and the other end of the SA is at *GND* (resp.  $V_{DD}$ ) 3. As the capacitor is still connected to the BL, its charge is restored (resp. depleted) by the voltage change in the BL.

- 3. When writing data in the RB, changing the value in the RB changes the voltage of the BL and therefore the charge of the capacitor, keeping the bit-cell updated with the proper value.

- 4. When the RB is needed to store an other row, the currently-activated row must first be closed. When the bank receives a PRE, the WL of the active row is low-ered, isolating it from the BL. The voltage of both ends of the SA returns to  $\frac{1}{2}V_{DD}$ , and the system returns to the precharged state **1**, ready for the next ACT.

When accessing data, if the targeted row is already loaded in the RB (we call this event a **row hit**), the operation is performed directly on the RB. If an other row is

activated (we call this event a **row conflict**), the bank must precharge the previous row, and activate the target row before returning the data. If no row is currently active in the bank (we call this event a **row miss**), the bank only needs to activate the target row before returning the data.

Capacitors are not perfect charge holders. They leak charge over time. If a memory cell is not accessed (*i.e.*, loaded into the RB) frequently enough to refill the capacitor, the charge will reduce until it goes below the threshold at which it can raise the voltage of the BL when the row is activated. At ambient temperature, most memory cells will lose their data after a few seconds of inactivity. This effect varies from cell to cell, and is inversely proportional to the temperature, so it is lowered in cold environments [5]. To counter this issue and to avoid losing data while the system is running, the memory controller periodically issues REFRESH commands (REF) to the memory. To process this command, the memory banks activate a few rows to refill their storage capacitors.

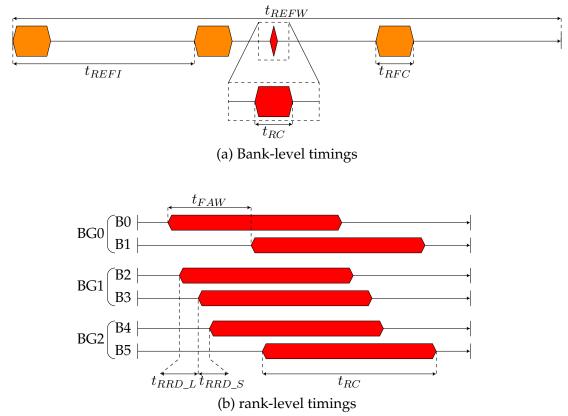

The relevant DRAM timing parameters are illustrated in Figure 2.7 and listed in Table 2.1 for three models of DDR3, DDR4 and DDR5. The minimum interval between two ACTs is defined by  $t_{RC}$ ,  $t_{RRD_L}$  or  $t_{RRD_S}$  if the rows to activate are respectively located in the same bank, in different banks of the same bank group, or in different bank groups. Additionally, a maximum of four ACTs can be issued to a rank every  $t_{FAW}$ . REF commands are issued by the memory controller every  $t_{REFI}$  and last  $t_{RFC}$ . In a cycle of  $t_{REFW}$ , all the rows of the memory are refreshed at least once.

| Name         | Description                               | DDR3    | DDR4    | DDR5  |

|--------------|-------------------------------------------|---------|---------|-------|

| $t_{RC}$     | Same-bank minimum ACT interval            | 48.75ns | 45.8ns  | 46ns  |

| $t_{RRD\_S}$ | Different-Bank-Group minimum ACT interval | 6.25ns  | 3.3ns   | 4ns   |

| $t_{RRD\_L}$ | Same-Bank-Group minimum ACT interval      | -       | 4.9ns   | 5ns   |

| $t_{FAW}$    | Four activate window                      | 30ns    | 21.67ns | 16ns  |

| $t_{REFW}$   | REF window (ms)                           | 64ms    | 64ms    | 32ms  |

| $t_{REFI}$   | REF interval (µs)                         | 7.8µs   | 7.8µs   | 3.9µs |

| $t_{RFC}$    | REF command duration                      | 350ns   | 350ns   | 195ns |

**Table 2.1:** *Relevant timing parameters for a DDR3 1600 8Gb x8 [6], DDR4 2400 8Gb x8 [7], and DDR5 4000 8Gb x8 [8].*

**Figure 2.7:** Illustration of DDR timings. Horizontal axis is time. Coloured sections represent periods when the bank is busy. An orange section represents a bank busy from a REF command. A red section represents the period after an ACT command when the bank cannot be issued an other ACT command. for the rank-level timings (b), 3 bank groups are represented, with 2 banks for each bank group.

### 2.2 Rowhammer attack

### 2.2.1 Cell-to-cell disturbance

As manufacturing processes become more efficient over the years, manufacturers are able to increase the memory density of DRAM chips, resulting in lower production cost, lower energy consumption for the same storage capacity, and higher storage capacity for the same silicon area. However, increasing the density of DRAM banks also results in rows being closer to each other, lower noise margin for bit cells, leading to increased parasitic electrical interactions between nearby bit cells.

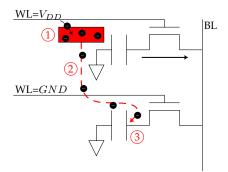

Kim et al. [1] discovered that when a row is activated, the capacitors of adjacent rows experience a small charge leakage, more important than their normal leakage. Multiple causes were considered by the author: electromagnetic coupling had already been proved to cause undesirable interactions between nearby wordlines [9]; bridges could be formed between adjacent wires and/or capacitances to accelerate the charge loss when toggling the WL [10, 11]; toggling a WL repeatedly for long periods of time could permanently damage the row ant its neighbours by hot carrier injection [12], altering the property of access transistors or injecting charges in nearby capacitors. At that time, the author could not determine precisely the main cause of this issue. More recently, Yang et al. [13] demonstrated that the cause of this issue is that when a WL is switched up and down, charge traps located below the WL capture some negative charges, which are emitted in the substrate, then migrate to the nearby capacitors, causing the charge leakage.

**Figure 2.8:** Charge trapping and migration to victim memory cells. When a WL is toggled, charge traps located below the WL (1) capture some negative charges , which are emitted into the substrate (2) and migrate to nearby capacitor (3), reducing the stored charge.

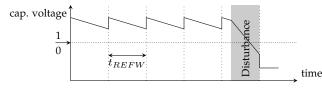

Alone, this issue is not dangerous, as the charge leakage is not important. The next REF or ACT on this row will refill the capacitor. However, if this operation is repeated enough times so that the charge of a capacitor goes below the threshold at which it can raise the BL voltage during an ACT, the bit will be misinterpreted on the next ACT, the charge depleted, resulting in the corruption of the data. The evolution of the charge of the capacitor under normal operation and under disturbance from repeated ACTs on adjacent rows is illustrated Figure 2.9

**Figure 2.9:** Memory cell capacitor voltage evolution under normal behaviour and under disturbance. Stored value starts at 1, and changes to 0 after corruption.

We define the disturbance level of a row as the number of ACTS that have been

issued to its neighbours since the last ACT or REF on it. Bit-flips only appear after the disturbance level reaches a certain value. We call this value the Rowhammer threshold  $(T_{RH})$ . It is primarily defined by the technology: because of smaller capacitors and closer wordlines, denser memories will have a lower  $T_{RH}$  [1, 14]. The value of  $T_{RH}$  has been greatly reduced over the years, getting from 138k ACTs to produce a bit-flip on older DDR3 to 9.6k for recent LPDDR4 [15].

Additionally, multiple factors can influence the effect of cell-to-cell disturbance on bit-flips. While the capacitors can only discharge under the influence of cell-to-cell disturbance, the bit-flip can happen in both directions  $(1 \rightarrow 0 \text{ or } 0 \rightarrow 1)$  depending on how the voltage is interpreted by the logic circuits. However, this direction being determined by the logic circuits, it cannot vary in time for one bit. According to the experiments conducted by Kim et al. in 2020 [15], the data pattern in the memory (*i.e.*, the positions of 1s and 0s in the MAT, *e.g.* row stripes, column stripes, checkerboard) seems to have a very important influence on the presence of bit-flips after an attack. This study shows that the pattern that produces the most bit-flips varies largely across DRAM generations, but does not vary as much across the tested manufacturers.

#### 2.2.2 Basic exploit

Cell-to-cell disturbance can be triggered intentionally and exploited to perform what is called a **RowHammer** (RH) attack. The goal of the aggressor is to ACT the neighbours of a victim rows enough times between two ACTs on the victim in order to flip some bits. Two obstacles arise to perform this attack:

- the row buffer: it contains the last activated row, accessing the row stored in it will trigger a row hit. Row hits must be avoided, as they don't lead to ACTs on the row, and therefore don't disturb the neighbours. The aggressor must use at least two aggressor rows of the same bank to avoid row hits;

- the cache memories: they contain the most frequently-accessed data. Repeatedly accessing the same rows will generate cache hits, and no request will reach the main memory. The aggressor must either bypass the cache [16], or use cache

eviction mechanisms to remove the aggressor rows from the cache memories, using for example cache flush instructions when they are available [1, 17], or cache eviction techniques [4, 18, 19].

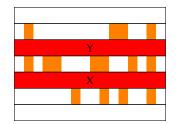

Memory corruption using the RowHammer attack can be performed using the simple x86 assembly loop presented in Listing 2.1 [1]. The positions of the aggressor rows and the victim cells in the DRAM bank attacked by this program is illustrated in Figure 2.10.

```

loop:

mov (X), %eax ; read value from address X

mov (Y), %eax ; read value from address Y

clflush (X) ; evict address X from cache

clflush (Y) ; evict address Y from cache

mfence ; wait for previous instructions to complete

jmp loop ; restart the loop

```

Listing 2.1: Rowhammer loop on x86 system

**Figure 2.10:** Memory bank under attack on rows *X* and *Y*. Aggressor rows are colored in red, and victim cells in orange.

However, the cache cannot be flushed manually by user-level programs on all systems. ARMv7-A processors restricted the cache-managing instructions to privileged programs, and ARMv8-A processors can be configured to restrict their usage by unprivileged programs. Cache-managing instructions are also not available to web pages, as the available instructions are limited by the web browser. In these cases, the aggressor can rely on cache-eviction strategies that exploit the replacement policy of the cache memory to replace the used address with an other data in the caches [4, 18, 20, 3, 21], on the DMA to bypass the cache [16], or on the integrated GPU which has a very simple cache from which it is easy to evict data [19].

Recently, it has been demonstrated that the Rowhammer attack could be escalated beyond immediate neighbours of aggressor rows [15, 22]. The increasing density made

the disturbance reach beyond the immediate neighbours on recent LPDDR4 [15]. But more importantly, a study demonstrated that it was possible to *propagate* the disturbance from the immediate neighbour of an aggressor row to its next neighbour, two rows from the main aggressor [22]. This attack combines many accesses to the main aggressor rows with a few accesses to the secondary aggressors, adjacent of the firsts. It manages to induce bit-flips in the victim rows, immediate neighbours of the secondary aggressor rows, at a distance of two rows from the main aggressors.

#### 2.2.3 Exploits in literature