# Secure Processors with respect to Micro Architectural Attacks

Valentin Martinoli

## ▶ To cite this version:

Valentin Martinoli. Secure Processors with respect to Micro Architectural Attacks. Micro and nanotechnologies/Microelectronics. Universit\'e Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT024. tel-04145576

# HAL Id: tel-04145576 https://theses.hal.science/tel-04145576

Submitted on 29 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Spécialité : Nano électronique et Nano technologies

Unité de recherche : Techniques de l'Informatique et de la Microélectronique pour l'Architecture des

systèmes intégrés

# Processeurs Sécurisés et Attaques de Micro Architecture Secured Processors with respect to Micro Architectural Attacks

Présentée par :

### Valentin MARTINOLI

#### Direction de thèse :

Régis LEVEUGLE Directeur de thèse

Professeur des universités, Grenoble INP, Université Grenoble

Alpes

Yannick TEGLIA Co-encadrant de thèse

Ingénieur Docteur, Thales DIS

## Rapporteurs:

#### **Guy GOGNIAT**

Professeur des universités, Université Bretagne Sud

#### Jean-Max DUTERTRE

Professeur IMT, École Nationale Supérieure des Mines de

Saint-Etienne

#### Thèse soutenue publiquement le 23 mars 2023 devant le jury composé de :

Régis LEVEUGLE Directeur de thèse

Professeur des universités, Grenoble INP, Université Grenoble

Alpes

Guy GOGNIAT Rapporteur

Professeur des universités, Université Bretagne Sud

Jean-Max DUTERTRE Rapporteur

Professeur IMT, École Nationale Supérieure des Mines de

Saint-Etienne

Lorena ANGHEL Présidente / Examinatrice

Professeure des universités, Grenoble INP, Université

Grenoble Alpes

Sébastien PILLEMENT Examinateur

Professeur des universités, Nantes Université

#### Invités:

Yannick TEGLIA

Ingénieur docteur, Thales DIS

Paolo MAISTRI

Chargé de recherche, CNRS

# **Acknowledgements**

Before any further technical development, I would like to start this manuscript by thanking those who guided me, supported me, and taught me a lot during this thesis.

I would like to express my deepest gratitude to my professor and thesis director Régis Leveugle for his invaluable patience and expertise. This endeavor would not have been possible without my thesis co-director Yannick Teglia, who provided intangible support and guidance. I am also extremely grateful to Guy Gogniat and Jean-Max Dutertre who agreed to examine this thesis manuscript. I would like to express my deepest appreciation to my defense committee Lorena Anghel and Sébastien Pillement. Words cannot express my gratitude to Thales DIS and TIMA laboratory for their tangible support. I am deeply indebted to the Université Grenoble Alpes for making this thesis possible.

I am also grateful to Samuel Gröger, Abdellah Bouagoun and Elouan Tourneur who worked in collaboration with me and provided valuable support towards enriching the results of this work. I would like to extend my sincere thanks to my colleague Joseph Gravellier for his advices and his support. Many thanks to Philippe Loubet-Moundi, manager of the Hardware-Lab Team for his feedbacks and suggestions. I would like to acknowledge Jean-Roch Coulon and André Sintzoff for their valuable knowledge and support. I had the pleasure of working with the Hardware Lab Team members who provided me an intangible support throughout my thesis.

# **Table of contents**

| Acknowledg        | gements                                                        | III  |  |  |  |  |

|-------------------|----------------------------------------------------------------|------|--|--|--|--|

| Table of contents |                                                                |      |  |  |  |  |

| Table of Fig      | ures                                                           | IX   |  |  |  |  |

| Table of Tab      | oles                                                           | XI   |  |  |  |  |

| Table of List     | ings                                                           | XII  |  |  |  |  |

| Table of App      | oendices                                                       | XIII |  |  |  |  |

| Résumé éte        | ndu                                                            | XV   |  |  |  |  |

| Introduction      | 1                                                              | 25   |  |  |  |  |

| Chapter 2. E      | Background and State of the Art                                | 29   |  |  |  |  |

| 2.1. Mi           | cro architectural mechanisms involved in the presented attacks | 29   |  |  |  |  |

| 2.1.1.            | Architectural and micro architectural worlds                   | 29   |  |  |  |  |

| 2.1.2.            | Cache memories                                                 | 30   |  |  |  |  |

| 2.1.3.            | Speculative execution                                          | 33   |  |  |  |  |

| 2.2. Mi           | cro architectural covert-channels                              | 36   |  |  |  |  |

| 2.2.1.            | Prime+Probe                                                    | 37   |  |  |  |  |

| 2.2.2.            | Flush+Reload                                                   | 38   |  |  |  |  |

| 2.2.3.            | Flush+Flush                                                    | 39   |  |  |  |  |

| 2.2.4.            | Evict+Time                                                     | 39   |  |  |  |  |

| 2.2.5.            | Prime+Abort                                                    | 40   |  |  |  |  |

| 2.2.6.            | Evict+Reload                                                   | 40   |  |  |  |  |

| 2.2.7.            | The importance of the encoding technique                       | 41   |  |  |  |  |

| 2.3. Ma           | ain micro architectural end-to-end attacks                     | 44   |  |  |  |  |

| 2.3.1.            | Transient-execution attacks                                    | 44   |  |  |  |  |

| 2.3.2.            | Microarchitectural Data Sampling attacks                       | 52   |  |  |  |  |

| 2.4. De           | rived micro architectural attacks                              | 56   |  |  |  |  |

| 2.5. Cla          | ssical timing attacks                                          | 57   |  |  |  |  |

| 2.6. So           | ftware-based Hardware attacks                                  | 58   |  |  |  |  |

| 2.7. Exi          | sting mitigations                                              | 59   |  |  |  |  |

| 2.7.1.            | User-space mitigations                                         | 60   |  |  |  |  |

| 2.7.2.            | Hardware mitigations                                           | 61   |  |  |  |  |

| 2.7.3.            | System-level mitigations                                       | 63   |  |  |  |  |

| 2.8. Dis          | cussion and conclusion                                         | 66   |  |  |  |  |

| Cha    | pter         | 3. Th                                                           | ne case of Intel SGX: the discovery of critical leakages in all high-end CPUs | 67  |  |  |  |  |  |  |  |

|--------|--------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 3      | .1.          | Overview of the SGX technology67                                |                                                                               |     |  |  |  |  |  |  |  |

| 3      | .2.          | A first case-study: Applying Foreshadow to a SGX secure enclave |                                                                               |     |  |  |  |  |  |  |  |

|        | .3.<br>ounte |                                                                 | al software mitigation ideas and robustness evaluation of the e               | _   |  |  |  |  |  |  |  |

|        | 3.3.         | 1.                                                              | Intel proposed mitigations                                                    | 71  |  |  |  |  |  |  |  |

|        | 3.3.         | 2.                                                              | Adding random temporal loops                                                  | 72  |  |  |  |  |  |  |  |

|        | 3.3.         | 3.                                                              | Flushing the cache                                                            | 73  |  |  |  |  |  |  |  |

|        | 3.3.         | 4.                                                              | TSX transactions                                                              | 74  |  |  |  |  |  |  |  |

| 3      | .4.          | Putt                                                            | ting the mitigations to the test on a real use-case                           | 75  |  |  |  |  |  |  |  |

| 3      | .5.          | Con                                                             | clusions and lessons learned                                                  | 77  |  |  |  |  |  |  |  |

| Cha    | pter         | 4. M                                                            | licro architectural vulnerability study of the CVA6 RISC-V core               | 78  |  |  |  |  |  |  |  |

| 4      | .1.          | The                                                             | RISC-V ecosystem                                                              | 78  |  |  |  |  |  |  |  |

| 4      | .2.          | Mot                                                             | tivation for CVA6                                                             | 80  |  |  |  |  |  |  |  |

| 4      | .3.          | Ove                                                             | rview of the CVA6                                                             | 80  |  |  |  |  |  |  |  |

| 4      | .4.          | Thre                                                            | eat Model and Best attack path candidate                                      | 81  |  |  |  |  |  |  |  |

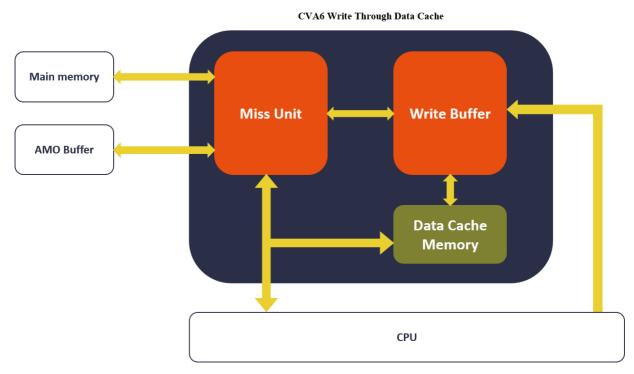

| 4      | .5.          | In-d                                                            | epth micro architectural study of the CVA6 data cache                         | 84  |  |  |  |  |  |  |  |

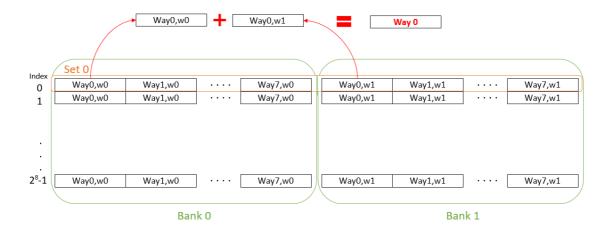

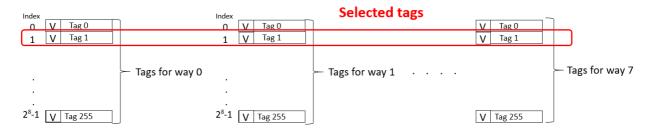

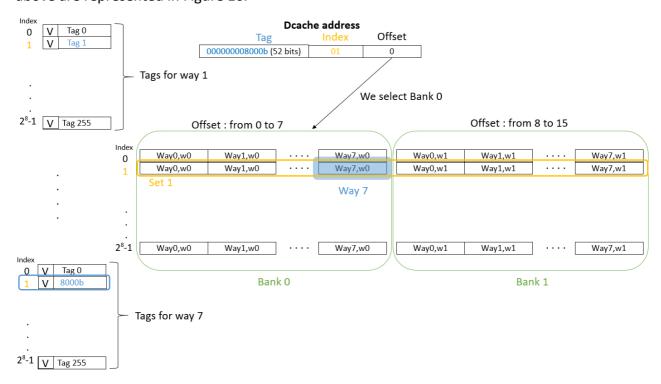

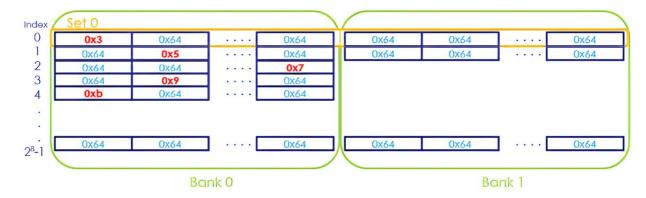

|        | 4.5.         | 1.                                                              | Dimensioning and behavior                                                     | 84  |  |  |  |  |  |  |  |

|        | 4.5.         | 2.                                                              | How addresses can be decomposed to represent the CVA6's data cache            | 85  |  |  |  |  |  |  |  |

|        | 4.5.         | 3.                                                              | CVA6's writing/eviction policies                                              | 86  |  |  |  |  |  |  |  |

|        | 4.5.         | 4.                                                              | The data cache memory's structure                                             | 88  |  |  |  |  |  |  |  |

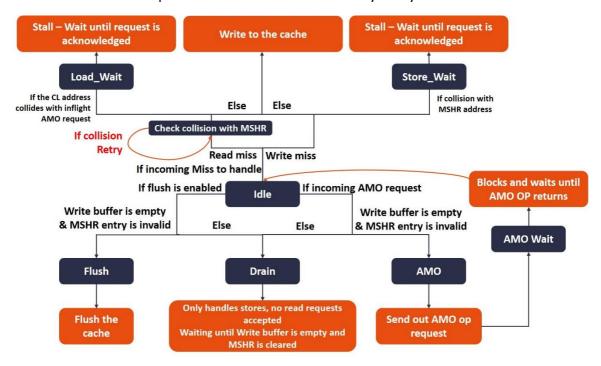

|        | 4.5.         | 5.                                                              | Storing atomic operations in the AMO buffer                                   | 91  |  |  |  |  |  |  |  |

| 4.5.6. |              | 6.                                                              | Introduction to the MSHR                                                      |     |  |  |  |  |  |  |  |

|        | 4.5.         | 7.                                                              | Handling misses and more with the miss unit                                   |     |  |  |  |  |  |  |  |

|        | 4.5.         | 8.                                                              | The write buffer's different usages                                           | 93  |  |  |  |  |  |  |  |

| 4      | .6.          | Con                                                             | clusion and outcomes of the study                                             | 94  |  |  |  |  |  |  |  |

|        | -            |                                                                 | first simulated baremetal Proof-of-Concept of the Prime+Probe covert-core     |     |  |  |  |  |  |  |  |

| 5      | .1.          | Mot                                                             | tivation and objectives of the study                                          | 95  |  |  |  |  |  |  |  |

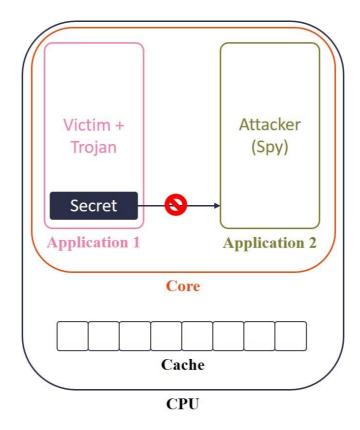

| 5      | .2.          | Thre                                                            | eat model                                                                     | 96  |  |  |  |  |  |  |  |

| 5      | .3.          | Initi                                                           | al version: noiseless and unscheduled                                         | 97  |  |  |  |  |  |  |  |

| 5.3.   |              | 1.                                                              | Code's structure and chosen encoding technique                                | 97  |  |  |  |  |  |  |  |

|        | 5.3.         | 2.                                                              | Data extraction and experimental results                                      | 100 |  |  |  |  |  |  |  |

| 5      | .4.          | Tow                                                             | vards the addition of an OS                                                   | 103 |  |  |  |  |  |  |  |

|        | 5.4.         | 1.                                                              | Impact of a scheduler                                                         | 103 |  |  |  |  |  |  |  |

| 5.4.2. |              | 2.                                                              | Noise generation and effects on the attack                                    |     |  |  |  |  |  |  |  |

|    | 5.4.           | 3.    | Combination of scheduling and noise generation                                               | 106 |  |  |  |  |  |

|----|----------------|-------|----------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

|    | 5.5.           | Disc  | ussion and contributions                                                                     | 108 |  |  |  |  |  |

|    |                |       | A more realistic use-case: targeting cryptographic implementations with COS on an FPGA board |     |  |  |  |  |  |

|    | 6.1.           | Mot   | ivation and objectives of the study                                                          | 110 |  |  |  |  |  |

|    | 6.2.           | Ехре  | erimental setup and tools                                                                    | 111 |  |  |  |  |  |

|    | 6.3.<br>an enc |       | experimentations on information transmission and statistical analysis: defining technique    | _   |  |  |  |  |  |

|    | 6.4.           | First | version of the attack on a simple victim                                                     | 115 |  |  |  |  |  |

|    | 6.5.           | AES   | case-study                                                                                   | 118 |  |  |  |  |  |

|    | 6.5.           | 1.    | Implementation of the Prime+Probe covert-channel                                             | 119 |  |  |  |  |  |

|    | 6.5.           | 2.    | Results obtained and limitations                                                             | 121 |  |  |  |  |  |

|    | 6.5.<br>envi   |       | One more step towards realism: considering a multi-user platform with a nonent               | •   |  |  |  |  |  |

|    | 6.5.           | 4.    | Summary and conclusions on the AES case study                                                | 125 |  |  |  |  |  |

|    | 6.6.           | RSA   | case-study                                                                                   | 125 |  |  |  |  |  |

|    | 6.6.           | 1.    | Implementation similarities and differences with the AES                                     |     |  |  |  |  |  |

|    | 6.6.           | 2.    | Discussion and conclusions on the RSA                                                        |     |  |  |  |  |  |

|    | 6.7.           | Disc  | ussion and limitations                                                                       | 130 |  |  |  |  |  |

|    | •              |       | eneralization of the proposed mitigations towards secure cores with respec                   |     |  |  |  |  |  |

|    | 7.1.<br>condit |       | rards the development of mitigations: study the favorable and unfavoration for an attacker   |     |  |  |  |  |  |

|    | 7.2.<br>data   |       | proposed micro architectural modifications for a secure handling of sensitions               |     |  |  |  |  |  |

|    | 7.3.           | Disc  | ussion and limitations                                                                       | 142 |  |  |  |  |  |

| Со | nclusi         | on ai | nd future works                                                                              | 143 |  |  |  |  |  |

|    | 8.1.           | Sum   | mary of the thesis                                                                           | 143 |  |  |  |  |  |

|    | 8.2.           | Futu  | ure work                                                                                     | 145 |  |  |  |  |  |

|    | 8.2.           | 1.    | Research perspectives                                                                        | 145 |  |  |  |  |  |

|    | 8.2.           | 2.    | Industrial perspectives                                                                      | 146 |  |  |  |  |  |

| Pu | blicati        | ons,  | communications and other contributions                                                       | 147 |  |  |  |  |  |

| Re | ferenc         | es    |                                                                                              | 149 |  |  |  |  |  |

| Αp | pendi          | ces   |                                                                                              | 166 |  |  |  |  |  |

| Ré | sumé.          |       |                                                                                              | 171 |  |  |  |  |  |

|    | -4             |       |                                                                                              | 470 |  |  |  |  |  |

# **Table of Figures**

| Figure 31. Synchronization process for the covert-channel when targeting an AES victim in a                               |

|---------------------------------------------------------------------------------------------------------------------------|

| TEE environment                                                                                                           |

| Figure 32. Synchronization process for the covert-channel when targeting an RSA victim 127                                |

| Figure 33. Illustration of the synchronization issues on an RSA victim128                                                 |

| Figure 34. Illustration of the synchronization with Prime+Probe timing shorter than the                                   |

| handling of a key bit equal to zero129                                                                                    |

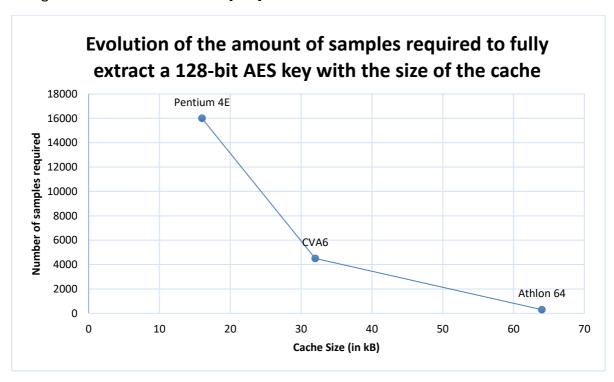

| Figure 35. Evolution of the number of samples required to extract a 128-bit AES key varying with the cache size           |

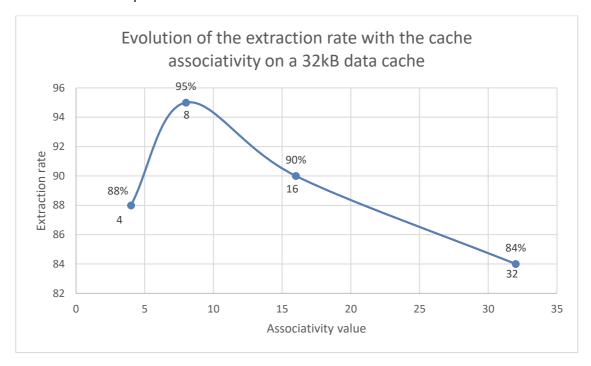

| Figure 36. Evolution of the extraction rate with the cache associativity for a 32kB data cache                            |

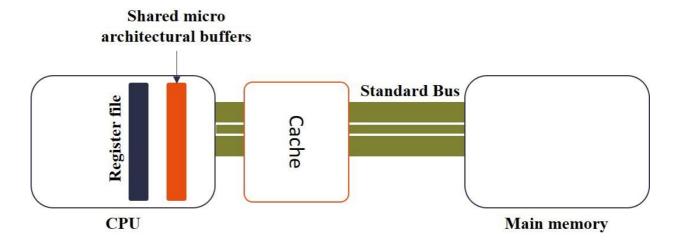

| Figure 37. Schematic representation of the micro architectural memory elements of a typica CPU                            |

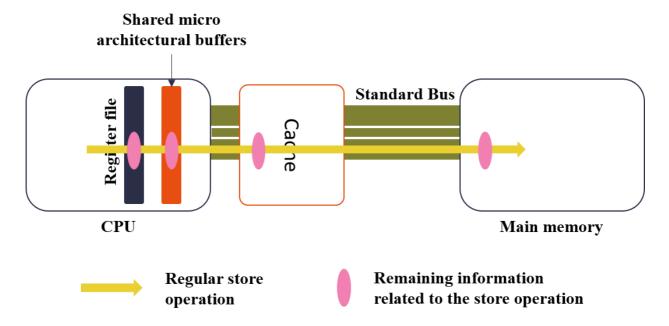

| Figure 38. Schematic representation of potential micro architectural information leakages after a regular store operation |

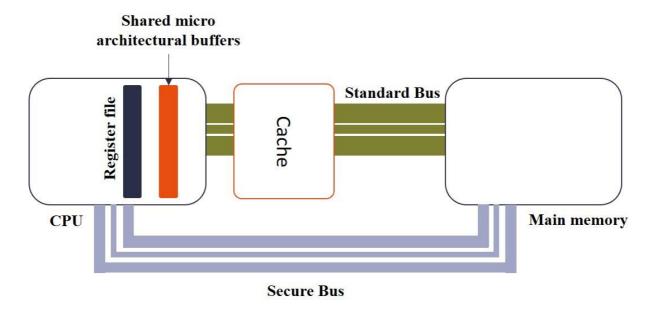

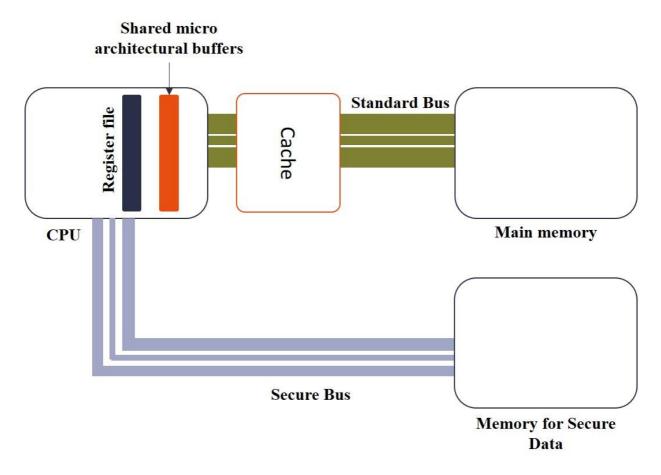

| Figure 39. Schematic representation of a CPU with the proposed micro architectura modification                            |

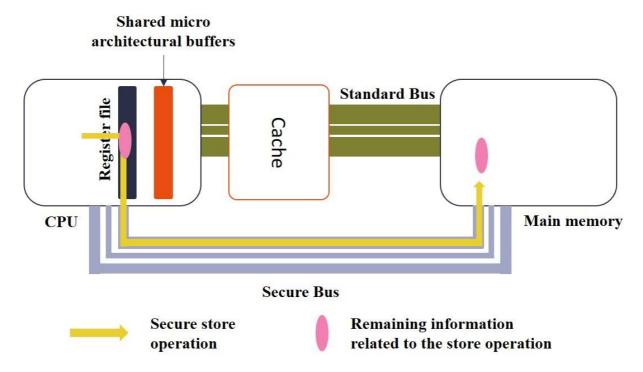

| Figure 40. Schematic representation of the STORE_SEC instruction on CPU using the                                         |

| proposed micro architectural modification140                                                                              |

| Figure 41. Schematic representation of the alternative implementation where a dedicated                                   |

| additional secured memory is added to the CPU141                                                                          |

# **Table of Tables**

| Table                                                                                      | 1.    | Summary     | of  | the    | main     | micro    | architectural   | cache   | covert-channels    | and  | their  |

|--------------------------------------------------------------------------------------------|-------|-------------|-----|--------|----------|----------|-----------------|---------|--------------------|------|--------|

| specif                                                                                     | iciti | es          |     |        |          |          |                 |         |                    |      | 43     |

| Table 4. Table representing the filling of the data cache when allocating an array of 2048 |       |             |     |        |          |          |                 |         |                    |      |        |

| cells                                                                                      |       |             |     |        |          |          |                 |         |                    |      | 86     |

| Table                                                                                      | 5. T  | able repres | ent | ing th | ne diffe | erent st | ates of the byt | es cont | ained in the Write | Buff | er. 94 |

# **Table of Listings**

| Listing 1. Example of Spectre attack leveraging conditional branch                   | 45  |

|--------------------------------------------------------------------------------------|-----|

| Listing 2. Structure of a TSX transaction                                            | 74  |

| Listing 3. Artificial scheduling pseudocode                                          | 98  |

| Listing 4. Pseudocode of an example of the simply scheduled attack                   | 104 |

| Listing 5. Pseudocode for our Prime+Probe micro architectural covert-channel         | 113 |

| Listing 6. Pseudocode for the covert-channel targeting the "Tiny-AES" implementation | 120 |

| Listing 7. Pseudocode of the randomized skeleton of a scheduler                      | 134 |

# **Table of Appendices**

| Appendix 1.   | Main chara | octerist | tics of the $\epsilon$ | existing | micro archited | ctural attacks | and | compa | arison |

|---------------|------------|----------|------------------------|----------|----------------|----------------|-----|-------|--------|

| with related  | attacks    |          |                        |          |                |                |     |       | 166    |

| Appendix 2.   | Overview   | of th    | e existing             | micro    | architectural  | mitigations    | and | their | main   |

| characteristi | cs         |          |                        |          |                |                |     |       | 167    |

# Résumé étendu

#### I. Introduction et contexte

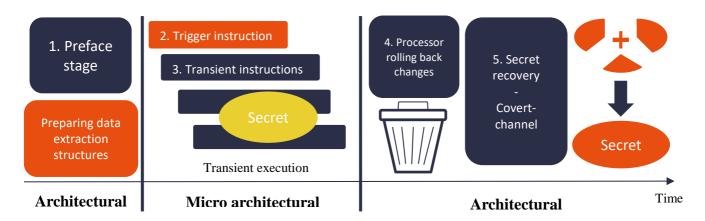

Usuellement, les attaques matérielles sont considérées comme nécessitant un accès physique à la victime. Néanmoins, une classe intermédiaire d'attaques dénommées attaques matérielles à distance est apparue récemment. Ces attaques permettent l'exploitation de failles matérielles via l'utilisation de code, injecté par exemple au travers d'un réseau. Elles ont gagné en importance dans la mesure où les technologies cloud, terreau propice à ce type d'attaques, ne cessent d'évoluer et de se perfectionner. Les attaques matérielles à distance comportent plusieurs sous-catégories, dont les menaces dites micro architecturales. Des publications récentes ont démontré que les ressources matérielles partagées, telles que les caches ou les mémoires tampons internes, peuvent permettre à un attaquant de franchir les limites de sécurité introduites par l'OS ou l'hyperviseur. La première cible de ces attaques dans la littérature a été la technologie SGX d'Intel. L'attaque micro architecturale nommée Foreshadow a permis de franchir l'étanche isolation logicielle introduite par SGX via la création de coffre forts logiciels nommés enclaves. Cette attaque a été le début d'une longue lignée de vulnérabilités. Ces attaques sont basées sur les disparités temporelles observées entre le monde micro architectural et le monde architectural. Le monde micro architectural est interne, invisible, et le programmeur ne peut interagir directement avec ses éléments. Il s'agit d'une implantation spécifique d'un jeu d'instruction donné (exploitant les mémoires caches, les mémoires tampons internes...). Le monde architectural quant à lui correspond à l'ensemble des éléments visibles directement par le développeur par le biais d'un débogueur (les registres banalisés par exemple).

Dans la course aux performances des CPUs, les développeurs n'ont cessé d'ajouter des mécanismes d'optimisation tels que l'exécution dans le désordre ou l'exécution spéculative. Le fonctionnement de ces mécanismes repose sur la présence de ressources matérielles partagées. Cependant, la littérature a démontré que ces ressources peuvent être exploitées afin de récupérer des informations sur les processus qui les partagent. Il s'agit ici du principe fondamental des attaques micro architecturales. Ces attaques sont lancées via du code qui, grâce à une succession judicieuse d'instructions, permet de déclencher les différents mécanismes d'optimisation qui font intervenir les ressources matérielles partagées. Il est ensuite possible de récupérer les données d'un autre processus au sein de ces ressources, puis de les extraire afin de les observer. L'étape d'extraction est une attaque par canal auxiliaire (ou canal caché), et permet de faire transiter l'information du monde micro architectural vers le monde architectural où elle pourra être utilisée. Le canal de communication le plus utilisé dans les attaques micro architecturales est la mémoire cache. Le cache est la ressource matérielle partagée la plus évidente et est présent dans la plupart des CPUs actuels.

Habituellement, les éléments micro architecturaux ne sont pas documentés par les constructeurs. Il s'agit de structures internes que les développeurs n'ont normalement pas besoin de connaître ; elles sont transparentes pour eux. Cependant, des chercheurs ont réussi à les caractériser en construisant des attaques les ciblant. Intel, ARM, AMD, tous les constructeurs sont vulnérables face à ces menaces. Le modèle de sécurité par l'obscurité qui

semblait suffisant n'est plus efficace, même lorsqu'il s'agit de structures profondément enterrées dans le circuit. L'idée à l'origine de ce projet de thèse est donc d'étudier le jeu d'instruction RISC-V comme alternative à Intel, ARM ou AMD en termes de sécurité face aux attaques micro architecturales. Contrairement aux processeurs propriétaires, RISC-V est une initiative ouverte, menant à de nombreuses conceptions de processeurs également ouvertes. Les processeurs RISC-V sont à priori tout aussi vulnérables que les autres face aux attaques micro architecturales et de plus permettent des analyses plus rapides, les codes source de la microarchitecture étant le plus souvent disponibles. Le but ultime de cette étude est d'établir si un modèle de cœur ouvert et résilient, de par son architecture, serait plus efficace que les approches usuelles pour faire face aux attaques micro architecturales. Cette thèse vise à proposer une étude approfondie de l'origine des attaques micro architecturales tout en répliquant certaines d'entre elles sur le cœur RISC-V CVA6. Ces expériences ont pour but de caractériser plus précisément les mécanismes à l'origine des vulnérabilités et d'estimer les avantages et désavantages des approches ouvertes pour un attaquant, ou un développeur tentant de protéger son système.

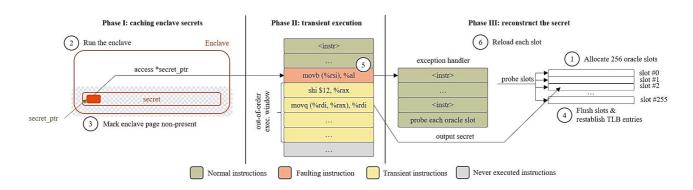

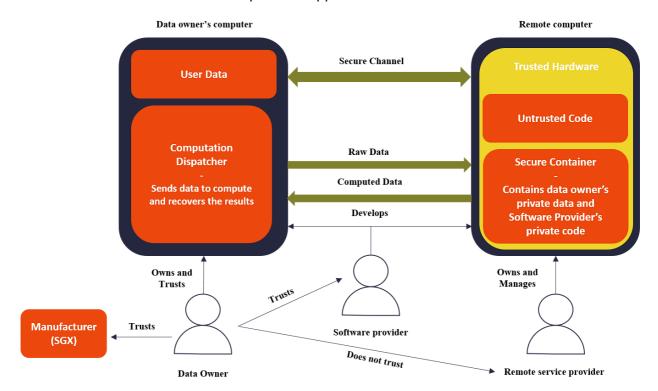

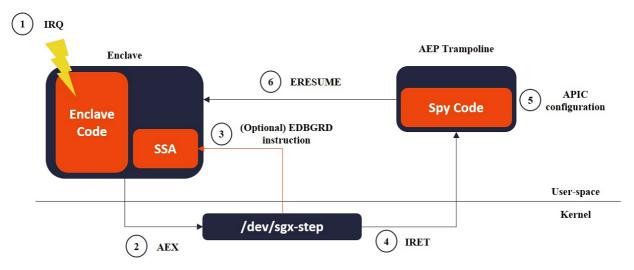

#### II. SGX et la découverte des fuites micro architecturales

Avant d'aborder les processeurs RISC-V, la première étude de cette thèse s'est dirigée vers la technologie SGX d'Intel, et la vulnérabilité Foreshadow. En effet, l'objectif de ces travaux est de constituer une première analyse des attaques de type micro architecturales, ainsi que de déterminer leur dangerosité dans des scénarios d'usages réalistes. L'objectif est également de proposer des premières idées de contre-mesures, notamment au niveau logiciel, afin d'évaluer les possibilités d'endiguer les fuites à moindre coût (et donc en évitant les modifications matérielles). La réplication de l'attaque Foreshadow sur une enclave de test s'est tout d'abord avérée relativement aisée, sur un système de la génération disponible au moment de l'apparition de l'attaque, notamment grâce à l'outil SGX-Step qui permet d'exécuter pas-à-pas des enclaves. A l'issue de cette réplication, il a été décidé d'étudier les possibilités de protections (ou contremesures) au niveau logiciel afin de protéger la victime ciblée par l'attaque Foreshadow telle que répliquée, à savoir un algorithme de chiffrement AES.

Face aux menaces, Intel a proposé plusieurs contremesures. Tout d'abord, la désactivation de l'hyperthreading, bien que coûteuse en termes de performances, a permis de diminuer le risque d'exploitation de ces attaques dans un premier temps. Ensuite, Intel a notamment proposé des mises à jour de micro code, permettant entre autres la vidange des caches au moment des changements de contexte. Ces protections étaient efficaces pour contrer les variantes initiales des attaques Foreshadow et Meltdown. Cependant, elles présentaient d'importants manquements face aux attaques plus récentes, et certaines variantes des attaques existantes.

Face à ce constat, plusieurs propositions de protections supplémentaires au niveau logiciel ont été faites et évaluées dans des contextes semi-réalistes. Nos idées initiales de contremesures comprenaient notamment l'addition de boucles temporelles aléatoires, des vidanges du cache, ainsi que l'utilisation de transactions TSX, permettant l'exécution atomique de sections définies de code. Les vidanges de cache sont basées sur l'idée initiale

d'Intel mais visent à exploiter la présence de l'instruction clflush afin de vidanger le cache après chaque manipulation de données sensibles, et donc plus souvent que la proposition du fondeur. La protection à base de boucles temporelles aléatoires est basée sur des protections traditionnellement utilisées face aux attaques par canaux cachés. Enfin, la contremesure basée sur les transactions TSX permet d'exécuter l'intégralité du contenu d'une enclave de manière atomique. Cela devait endiguer les attaques micro architecturales car toute interruption de la victime, telle qu'une faute de page, interrompt le calcul en cours et remet le système dans son état initial au début de la transaction TSX. Les attaques de type Meltdown ou Foreshadow exploitent les fautes de pages pour déclencher l'utilisation de mécanismes d'optimisation et donc de ressources matérielles partagées. La protection à base de transaction TSX devait donc contrer ce type d'attaques.

Ces contremesures, ainsi que celles proposées par Intel, ont été évaluées sur des algorithmes de chiffrement AES et RSA, sur des machines standards de l'entreprise. Ces ordinateurs contenaient les protections proposées par Intel, à l'exception des défenses matérielles contre les attaques de type Forehsadow. Il a été démontré que l'ensemble des contremesures proposées par Intel ainsi que par les travaux de cette thèse sont efficaces pour empêcher l'exploitation de l'attaque Foreshadow initiale. Cependant, d'autres variantes de l'attaque étaient toujours fonctionnelles, et les attaques les plus récentes telles que LVI (Load Value Injection) passaient au travers des défenses proposées. Tous ces résultats démontrent les limitations des architectures fermées, ainsi que celles des contremesures au niveau logiciel. En effet, pour endiguer les attaques micro architecturales, il est nécessaire d'agir directement à la source de la fuite : au niveau micro architectural.

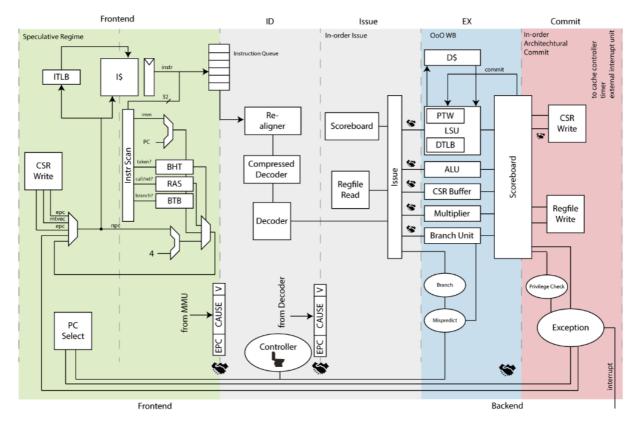

### III. Attaque simulée sans système d'exploitation

L'approche « fermée » proposée par les fondeurs traditionnels ayant atteint ses limites, et l'approche logicielle ayant une efficacité mitigée (notamment face aux attaques récentes), il a été décidé de porter l'étude sur l'initiative RISC-V. En effet, cette initiative étant ouverte, il est possible d'y trouver des projets d'architectures également ouvertes. Dans le cadre de l'étude proposée par ce document, le cœur RISC-V retenu, et qui sera la plateforme dédiée pour toutes les expérimentations décrites, est le cœur CVA6. Ce processeur ouvert a été développé par l'ETH Zurich, pour des objectifs de performance en premier lieu. C'est un cœur simple, sans multi-threading. Il dispose néanmoins de la plupart des mécanismes d'optimisation que l'on trouve sur les cœurs récents tels que la prédiction de branchement ou des caches L1 de données et d'instructions. Le but de l'étude sur CVA6 était dans un premier temps de déterminer son niveau de vulnérabilité face aux attaques micro architecturales.

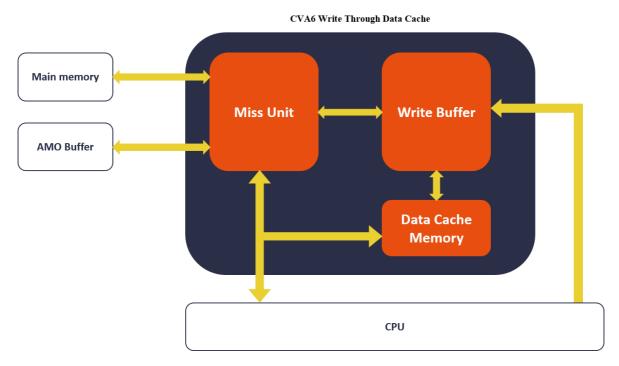

Il a donc été nécessaire de procéder à une analyse détaillée de la micro-architecture du processeur. Le code du cœur est disponible sur GitHub et est majoritairement écrit en System Verilog. Il a d'abord été nécessaire de recenser les différents éléments qui étaient susceptibles de présenter des fuites de types micro architecturales. Plusieurs candidats paraissaient prometteurs, tels que les mémoires caches, les mémoires tampons utiles à la spéculation, et le scoreboard (structure qui réordonnance les instructions avant finalisation de leur exécution au niveau architectural). D'après la littérature et les résultats de cette

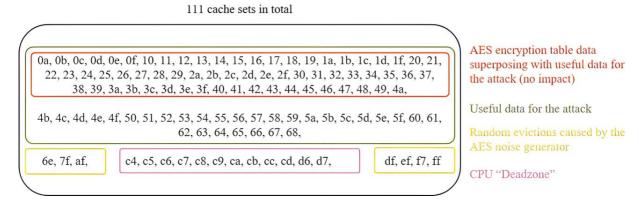

analyse, il a été décidé de se concentrer sur le cache de données. En effet, cette structure avait déjà fait l'objet d'une publication proposant des résultats préliminaires et des bases pour une étude plus approfondie. N. Wistoff et al., de l'ETH Zurich, avaient en effet étudié les possibilités de fuites d'informations au sein du cache de données du CVA6 en utilisant une bibliothèque de vulnérabilités nommée Mastik. Il n'existait toutefois pas à notre connaissance de description fonctionnelle et pratique concernant l'architecture du cache de données du CVA6. Même les documents récemment mis à disposition sur le site du groupe de travail ne détaillent pas cette partie. Une analyse approfondie a donc été réalisée et le résultat de ces efforts de compréhension a été mis sous la forme d'une documentation et partagé avec la communauté.

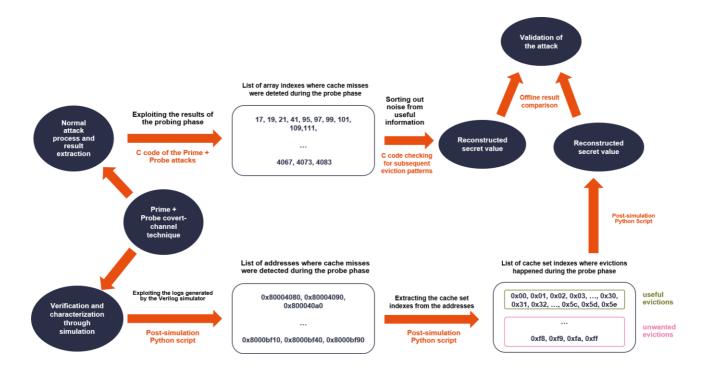

Pour poursuivre notre étude micro architecturale, il a été décidé de procéder à la réplication de l'attaque par canal caché la plus emblématique sur les caches de donnée, l'attaque Prime+Probe. L'un des avantages des approches ouvertes est la libre disposition du code source des processeurs. Il a donc été choisi d'exploiter cette différence en utilisant des outils de simulation afin de répliquer l'attaque. La chaîne de simulation mise à disposition par l'ETH Zurich sur Github a été utilisée. Le simulateur est le logiciel ouvert Verilator, qui est un simulateur précis au cycle d'horloge près. L'attaque Prime+Probe, bien connue dans la littérature, a donc été reproduite en simulation, sans système d'exploitation, sur le processeur CVA6. L'attaque implémentée est capable de récupérer des informations allant en théorie jusqu'à 256 bits en les faisant transiter par le cache de données. Pour des valeurs secrètes exprimées avec 0 à 50 bits, notre implémentation de l'attaque possède un taux de succès de 90%. Ce dernier diminue à 85% pour des valeurs nécessitant entre 51 et 130 bits, pour finir aux alentours de 70% pour un codage sur 131 à 195 bits. Ces valeurs dépendent fortement du scenario matériel et logiciel choisi. Par ailleurs, contrairement à la théorie, il n'a pas été possible d'extraire des valeurs nécessitant plus de 195 bits. En effet, nous avons été confrontés à ce que nous avons nommé la « zone morte ». Cette zone du cache est constamment balayée par le processeur lui-même, et contient des informations telles que des résultats de calculs d'adresses, des adresses intermédiaires, etc. ... Il en résulte que cette zone, comprise entre les sets du cache numéro 196 et 226 (dépendant du scénario logiciel/matériel) n'est pas utilisable pour stocker puis récupérer de l'information dans le cadre d'une attaque micro architecturale. En effet, toute information utile qui serait placée à cet emplacement se verrait expulsée du cache quelques cycles d'horloge plus tard, et serait donc inutilisable.

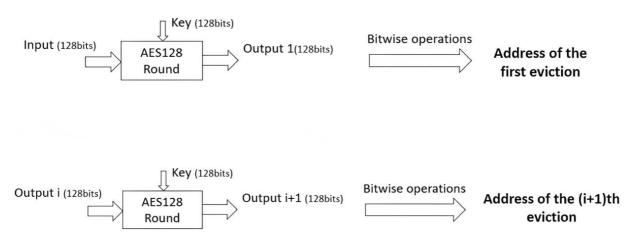

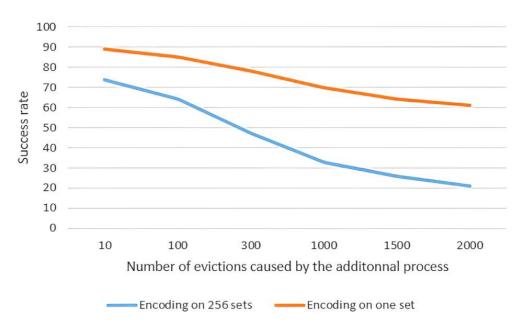

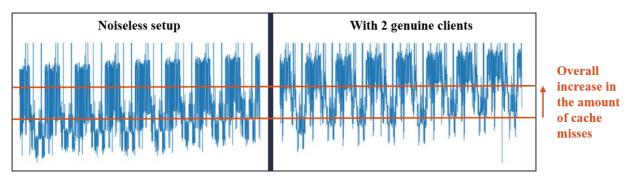

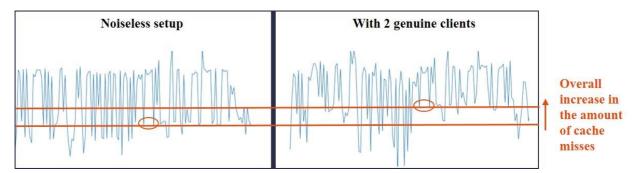

Cette étude sur environnement de simulation sans système d'exploitation a été conclue par certains enrichissements visant à prédire le comportement d'une telle attaque dans le cas de l'ajout d'un système d'exploitation. Pour ce faire, il a été décidé de simuler un système d'exploitation rudimentaire chargé d'un ordonnancement, codé par nos soins. En plus de cela, plusieurs autres processus ont été ajoutés afin de simuler l'activité générée par la présence de processus multiples dans le cadre d'un système d'exploitation complet. Ces processus supplémentaires sont des générateurs aléatoires, basés sur des algorithmes de chiffrement AES. Leur objectif est de produire des expulsions aléatoires au sein du cache de données, afin de perturber autant que possible le processus de l'attaque. Il résulte de cette expérimentation que l'ajout d'un squelette de système d'exploitation pose des problèmes temporels pour l'attaque Prime+Probe. En effet, il est nécessaire que les différentes phases de l'attaque soient suffisamment rapides (i.e., plus rapides que le temps alloué par le

système à chaque processus) afin qu'elles ne soient pas interrompues en plein déroulement, et ainsi perturbées trop fortement pour rester opérationnelles. De plus, l'ajout de processus supplémentaires en parallèle produit comme prévu des remplacements aléatoires dans le cache. Ces derniers compliquent la tâche de l'attaquant qui doit alors procéder à une analyse plus poussée des résultats de l'attaque afin de discriminer l'information utile du bruit ajouté par les perturbateurs. Pour contrer ces perturbations, il est possible de simplifier l'encodage, ou la manière de cacher l'information à l'intérieur du cache de données.

Toute cette étude a permis de mettre en lumière l'avantage que représentent les initiatives ouvertes pour les attaquants. En effet, disposer librement du code permet de faciliter et d'approfondir la phase de compréhension et d'analyse comportementale de l'architecture ciblée. De plus, cela permet également de recourir aux outils de simulation qui, comme démontré, permettent de développer des attaques et de les rejouer avec différentes variantes, sans avoir besoin d'un accès physique à la cible réelle. Toutefois, un effort considérable de compréhension a été nécessaire, dû au manque de documentation de la partie de la microarchitecture exploitée par l'attaque. Rejouer une attaque connue n'est donc pas si simple, même dans le contexte d'une initiative ouverte.

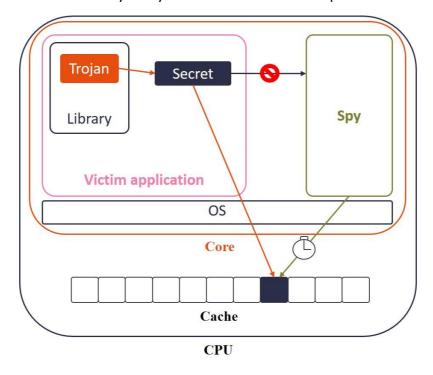

### IV. Attaque sur Linux : vers plus de réalisme

La suite des travaux s'est orientée vers la réplication de la même attaque, Prime+Probe, mais sur un support et accompagnée d'un scénario tous deux plus réalistes. L'objectif est ici de se rapprocher d'un cas d'usage réel du cœur, afin de prouver que l'attaque est dangereuse en pratique. De plus, les éléments méthodologiques sont décrits afin de faciliter la compréhension des différents défis que représente l'implémentation d'une attaque connue sur une nouvelle plateforme et dans un nouveau contexte. Enfin, ce travail permet également une fois abouti d'étudier les possibilités de contremesures lorsqu'un système d'exploitation est présent, et sur une victime plus réaliste. Le cœur CVA6 a donc été instancié sur une carte FPGA Genesys II. Un système d'exploitation Linux a été installé sur le cœur CVA6.

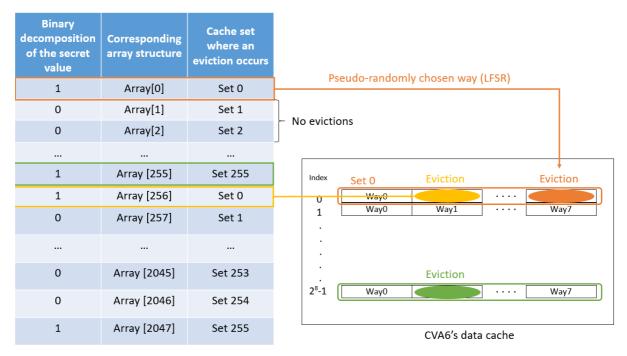

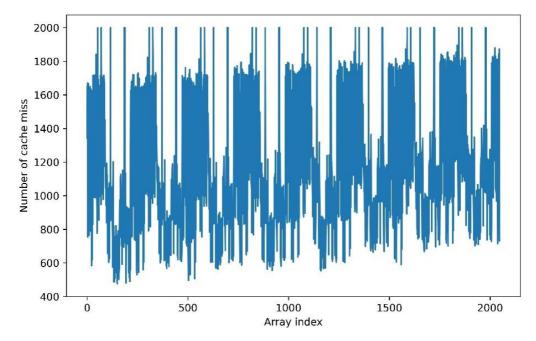

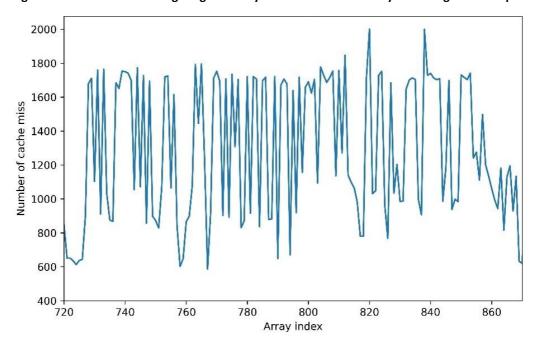

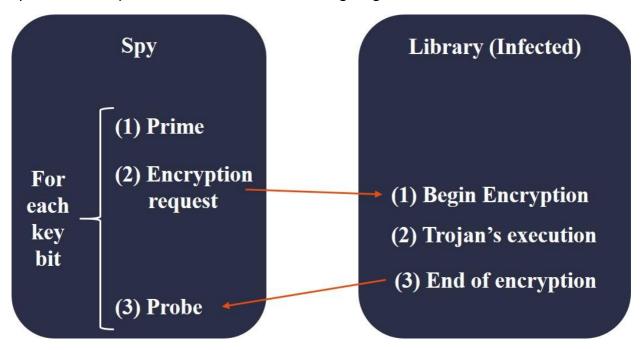

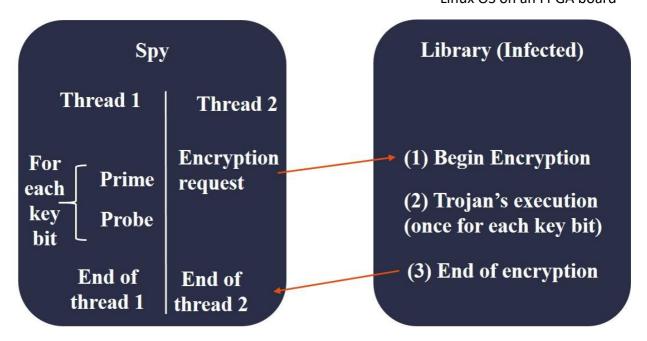

La difficulté principale a dans un premier temps été de définir la méthode d'encodage de l'information. En effet, chaque cache possède une structure ainsi qu'un comportement différents, et nécessite donc la prise en compte de ses caractéristiques pour adapter l'attaque. Ici, le cache de données possède une politique d'éviction pseudo-aléatoire, rendant le travail sur les lignes de caches complexe car les remplacements sont difficiles à prévoir. Il a donc été décidé de travailler sur les sets (ensembles cohérents de lignes de cache). L'idée générale de la méthode employée est de faire correspondre à chacun des sets une valeur binaire. Pour cela, la victime est supposée couplée à un cheval de Troie (Trojan) qui a été inséré par un utilisateur malveillant sans avoir été détecté. Ce Trojan cause des évictions dans les sets du cache d'une manière cohérente au secret à récupérer. Si un bit de la valeur secrète à récupérer est égal à 1, alors le Trojan va causer des évictions à l'intérieur du set correspondant à la position du bit secret à récupérer. Si le bit considéré et valant 1 est le 3ème, alors le Trojan causera des évictions au sein du 3ème set du cache. Si le 4ème bit du secret vaut 0, alors le Trojan ne causera pas d'évictions supplémentaires sur le 4ème set du

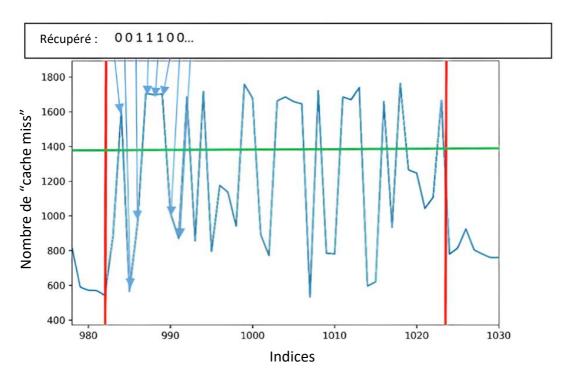

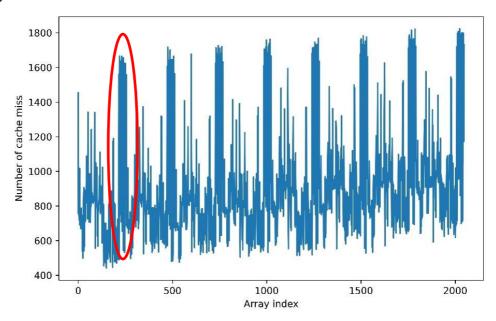

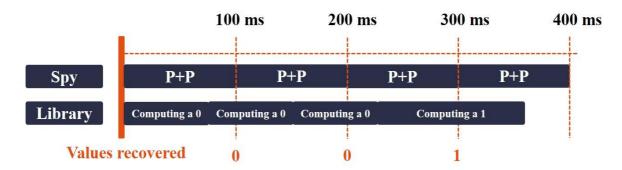

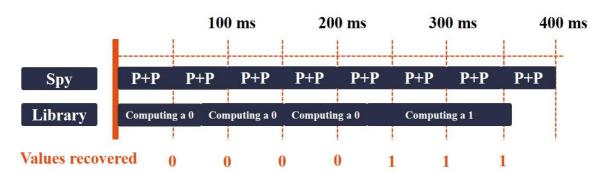

cache. Ainsi, il est possible de relier la quantité de contention au sein des sets du cache à la valeur du secret à récupérer. Ici, nous cherchons à déterminer la valeur de la clé secrète de la victime AES en employant une attaque par canal caché de type Prime+Probe. En utilisant l'encodage décrit ci-dessus, il est possible de reconstruire le secret en observant à posteriori la contention sur chacun des sets du cache. Si un set contient beaucoup de données qui ont été remplacées pendant l'attaque, dans ce cas le cheval de Troie cherche à transmettre un bit égal à 1. Sinon, il s'agit d'un 0. On obtient en sortie des traces dont l'allure est illustrée en figure 1 avec un seul processus exécuté correspondant à une victime simple.

Figure 1. Motif de trace obtenu en résultat de l'attaque Prime+Probe sur une victime simple basée sur une addition dont le résultat constitue le secret.

Sur la figure 1, 2000 échantillons ont été collectés. Les barres rouges délimitent la trace utile, tandis que la verte représente la valeur seuil permettant de discriminer les bits valant 1 de ceux valant 0. Cette expérience a été réalisée à titre de vérification de l'encodage proposé, et permet ainsi d'obtenir des courbes en facilitant la visualisation.

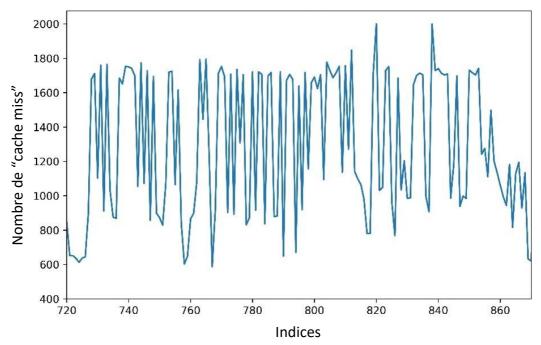

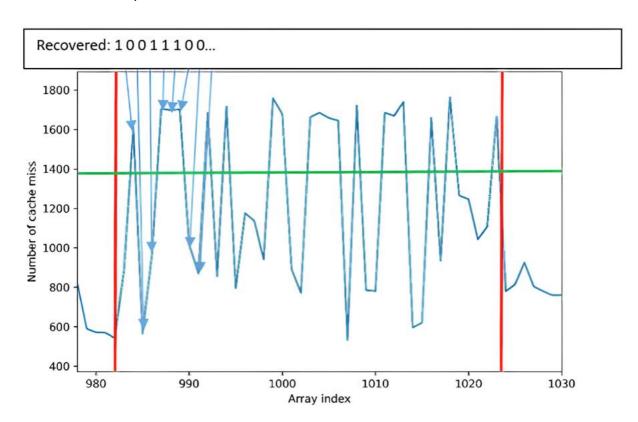

La technique d'encodage proposée ayant été validée par une preuve de concept sur une victime simple de type addition, elle a été appliquée sur une victime plus complexe, un AES. Les traces obtenues lors de l'attaque d'un algorithme de chiffrement AES sont similaires à celles présentées en figure 1, et sont visibles sur la figure 2.

Figure 2. Trace obtenue lors de l'application de l'attaque Prime+Probe sur une victime AES avec 2000 échantillons.

Les résultats de l'implémentation sont satisfaisants ; l'attaque proposée permet de récupérer l'intégralité des 128 bits de clé de l'AES en moins de deux secondes avec un taux d'extraction de 97,6% pour 2000 échantillons. Cela signifie qu'en moyenne 2,4% des bits récupérés sont erronés. De plus, il n'est pas possible d'identifier la position des bits faussés. Cependant, il existe des techniques d'attaques cryptographiques qui permettent de déduire les bits restant d'une clé à partir de bits aléatoires. Il est donc tout à fait envisageable de recourir à ces techniques afin de récupérer les bits restants de la clé. De plus, lorsque l'on considère un nombre d'échantillons supérieur à 3500, on obtient un taux d'extraction égal à 99%, suffisamment élevé pour considérer que l'on récupère l'intégralité de la clé correctement à chaque itération.

De manière analogue à l'étude précédente sans système d'exploitation, des ajouts visant à augmenter le réalisme du scénario ont été proposés. En effet, en parallèle du processus attaquant et du processus victime, ont été implémentés des clients bénins, qui réalisent des chiffrements AES en boucle afin de perturber le processus de l'attaque. Il en résulte que le taux d'extraction de l'attaque diminue. Par exemple, pour 2 clients bénins, le taux d'extraction diminue à 94% pour 2000 échantillons. D'une manière générale, pour contrebalancer la présence de bruit, il est nécessaire de recourir à l'utilisation de plus d'échantillons. Là où l'attaque dans un environnement non bruité pouvait récupérer 95% de la clé en 6 échantillons, il en faut désormais 100 avec deux clients supplémentaires pour conserver le taux de succès à 95%.

## V. Développement et propositions de protections

Les derniers travaux réalisés dans le cadre de la thèse présentée dans ce document concernent les efforts de protection dérivés des études réalisées et décrites dans les sections précédentes.

Une première étude a été menée afin d'analyser l'influence de l'architecture d'un cache spécifique sur la capacité d'un attaquant à en extraire des données utiles dans le cadre d'une attaque par canal caché. Il a été établi que la taille du cache et la valeur de son associativité ont une influence non négligeable sur la capacité d'une attaque à extraire des informations. La taille d'un cache conditionne directement la quantité d'information qu'il sera possible de faire transiter au travers de ce dernier à chaque itération de l'attaque. Cependant, plus le cache sera grand, plus il sera difficile pour l'attaquant et la victime de partager des sets du cache, rendant certaines variantes d'attaques par canal caché plus complexes. D'un autre côté, l'associativité contraint également les attaques. En effet, plus elle est élevée, plus il sera probable que d'autres processus en plus de la victime et de l'attaquant partagent un set du cache. Ainsi, les risques que l'attaque soit perturbée seront plus grands. Par ailleurs, une associativité trop petite signifie également que le nombre de sets dans le cache diminue proportionnellement, réduisant ainsi la capacité de l'attaquant à encoder beaucoup d'information à chaque itération de l'attaque. Il existe donc des structures de cache qui sont moins vulnérables aux attaques par canaux cachés du fait de leur disposition. Les valeurs de la taille ainsi que de l'associativité du cache permettent une première estimation grossière du niveau de fuite d'un cache spécifique avec l'encodage utilisé, et donc conséquemment, de l'importance des efforts qu'il sera nécessaire de déployer afin de les colmater.

Ensuite, la contremesure proposée par N. Wistoff et al. a également été étudiée. En effet, ils implémentent une instruction supplémentaire, nommée fence.t, dont le but est de purger le cache et de provoquer un changement de contexte. Lorsqu'employée correctement par le développeur, cette instruction permet de bloquer la plupart des attaques par canaux cachés exploitant les caches. Elle a été utilisée sur l'implémentation d'attaque évaluée précédemment et s'est avérée efficace, empêchant l'attaque de récupérer la clé secrète de l'AES. L'attaque ne récupère plus que des bits égaux à 0 (correspondant à un manque de contention sur les sets du cache) et son taux de succès est donc de 50% car lié au nombre moyen de bits égaux à 0 dans les clés secrètes aléatoirement générées puis extraites.

Enfin, plusieurs contremesures ont été proposées et étudiées. La protection sous forme de boucles temporelles aléatoires a été implémentée et mise à l'épreuve face à la même attaque que précédemment. Il s'avère que la protection est efficace et perturbe grandement l'attaque en modifiant le comportement temporel de la victime de manière aléatoire. Le taux de récupération de l'attaque est également réduit aux alentours de 50%, prouvant son efficacité. Cependant, cette protection n'est pas viable car trop coûteuse : en moyenne, elle double le temps d'exécution de la victime AES. Il serait donc intéressant de procéder à des études supplémentaires afin de raffiner cette proposition. Une idée similaire serait de modifier le comportement temporel du système d'exploitation. En effet, si chaque processus se voyait attribué un temps d'exécution variable, et généré aléatoirement, cela augmenterait grandement la difficulté de procéder à une attaque par canal caché sur le cache. Aussi bien le comportement de la victime, que celui de l'attaquant, seraient modifiés

constamment et de manière aléatoire. Cette proposition a été étudiée dans le cadre de l'attaque simulée sans système d'exploitation, en modifiant le squelette d'ordonnanceur qui avait été implémenté. Ce dernier attribue alors des temps d'exécution variables et aléatoires à chaque processus au lieu d'attribuer un temps fixe et égal. Cela s'est avéré très efficace pour contrer l'attaque dont le taux de succès a été réduit à 51% dans un environnement sans bruit, puis à 10% lors de l'ajout d'un processus perturbateur générant des évictions pseudo-aléatoires à l'aide d'un AES.

La dernière proposition effectuée dans les travaux de thèse présentés dans ce document concerne une modification de la micro architecture elle-même. Cette proposition concerne le cache de données. Afin de contrer les fuites présentes dans les différents éléments micro architecturaux, l'ajout d'un second bus de données vise à contourner le bus usuel. Lors des calculs qui utilisent des données sensibles, ces dernières transiteraient par le bus sécurisé, qui ne fait pas appel aux différentes mémoires micro architecturales partagées. Ainsi, les données sensibles ne peuvent pas être extraites en utilisant des attaques par canaux cachés sur le cache, ou toute autre mémoire tampon au niveau micro architectural. Afin de déclencher l'utilisation de ce bus de données supplémentaire, il a été envisagé d'ajouter deux instructions au jeu d'instruction; LOAD\_SEC et STORE\_SEC. Cette contremesure n'a pas été implémentée dans le cadre des travaux réalisés, et sa caractérisation pratique est laissée pour des travaux futurs.

## **Chapter 1**

# Introduction

With the fast growth of industries such as embedded systems, Internet of Things, or Cloud Computing, more systems are being connected to networks while cybersecurity is an increasing concern due to the wider range of application domains. To protect these devices, it is necessary to study the different types of attacks they may be confronted with. Historically, attacks have been separated into two main categories: software attacks and hardware attacks. The former require no physical access to the victim device and are leveraged remotely only by running some malicious code on the target [1-3]. The latter often require physical access to the target in order to recover sensitive information or modify the device's behavior [4-6]. Some techniques for hardware attacks enable an attacker to recover information without needing physical contact with the target, but rather being relatively close to it (a few centimeters up to a few meters) by exploiting emissions such as acoustic or electromagnetic signals [7, 8]. Hardware attacks were therefore considered threatening only in use-cases where an attacker could potentially get access to the device, or get close enough to it. However, hardware attacks are not solely limited to attacks requiring physical access to the target. Some techniques that can be carried out remotely have indeed been discovered by P. C. Kocher et al. in 1996 [9]. These attacks lead to considering of a new category of attacks: the remote hardware attacks. These new techniques use software code to exploit hardware leakages remotely, when connections to the networks are available. Since their initial discovery, several types of remote hardware attacks have been disclosed, including micro architectural attacks.

Recent publications have demonstrated that shared hardware resources, such as caches or internal buffers can be leveraged by an attacker to bypass regular security boundaries like memory protection units for instance. Intel's SGX technology [10] has been a recent target of these attacks. The Foreshadow [11] micro architectural attack enables an attacker to bypass the strong software isolation introduced by SGX enclaves. These enclaves can be described as vaults that protect any piece of code or data that is placed within it. No other entity, even with higher privileges like the OS or the hypervisor is capable of accessing the content of an enclave. However, Foreshadow allows bypassing the security barriers and has led to the development of many other micro architectural attacks. These offensive techniques are based on temporal disparities existing between the micro architecture and the architecture of a CPU. The micro architecture is concealed, almost transparent for the programmer. It cannot be interacted with directly. It is the specific hardware implementation of a given instruction set architecture (ISA), typically composed of cache memories, inner buffers, etc. It is opposed to the architecture that can be observed and directly manipulated through a debugger. The architecture contains the standard registers and memories for example.

In the race towards CPU performance, many optimization mechanisms have been added such as out-of-order execution and speculative execution. These mechanisms require the addition of shared hardware mechanisms that have proven to be exploitable by micro architectural attacks. These vulnerabilities can be leveraged by an attacker to recover information about the processes that share these hardware resources. Micro architectural attacks are triggered through software code and do not require a physical access to the target. They take advantage of certain instruction sequences to force the CPU using optimization mechanisms based on shared resources. The attacker can then recover data belonging to another process sharing these hardware memories. The specific action of extracting data is called a covert-channel. Covert-channels transfer the information from the micro architecture (where it cannot be directly retrieved) to the architecture where it can be observed and exploited. Cache memories are the preferred extraction medium, being the largest and most studied shared hardware resources. They are also present in most high-end CPUs.

Traditionally, micro architectural elements are not documented. They are generally transparent for the software developers and thus do not require to be described in details. However, researchers demonstrated that even without documentation, it is possible to characterize these elements and their behavior, while also carrying out an attack targeting them [12]. All the providers are vulnerable to these micro architectural attacks, including Intel, ARM and AMD. This raises the question about the effectiveness of the security model based on obscurity. With the rise of remote hardware attacks, some additional security mechanisms have to be introduced and the development of open cores also raises new questions about the level of risk. The main goal of this thesis work is therefore to study the security level of a CPU core implementing the RISC-V ISA [13], with a focus on micro architectural attacks. RISC-V is an open initiative thus providing the mold for many open CPU architectures. RISC-V cores are as vulnerable as other ones. However, thanks to the availability of their source code, they allow a faster analysis of the micro architectural vulnerabilities. The goal of this work is therefore to study to what extent open architectures are more or less resilient than closed approaches when facing micro architectural threats. This thesis aims at providing an extensive study of the origin of micro architectural attacks while replicating some of them on the CVA6 RISC-V core [14, 15]. These experimentations aim at determining the advantages and disadvantages of open approaches in the case of an attacker, or a developer willing to protect his system.

To reach the proposed objectives, the CVA6 micro architecture has been studied in-depth and the results have paved the way for the implementation works done afterwards. While replicating the attacks, this thesis work proposes a focus on the Prime+Probe cache covert-channel [16] that is one of the most widely used and well-known techniques. This covert-channel has been replicated on the CVA6 core by leveraging one of the advantages of open initiative for an attacker: the possibility to simulate the internal behavior of the core. To study the implications of such a new possibility, the Prime+Probe covert-channel has been implemented on a simulated baremetal version of the CVA6 core. Some mitigation ideas were proposed, and the impact of the addition of mechanisms used by an operating system (OS) has been studied to anticipate the next implementation work. To propose more realistic mitigations and experimental results, the same attack has been developed on an FPGA-instantiated CVA6 with a running Linux OS. This experimentation aimed at providing a more

realistic attack, as well as studying mitigations on a use-case close to real-life. Throughout both implementations, this work also explored the different requirements and considerations to adapt such an attack to a new hardware/software scenario. Moreover, it also studied how specific architectural designs and choices may affect the development of the chosen covert-channel. Finally, once the attacks were functional and characterized indepth, the work focused more on the mitigation aspects. Several different approaches were studied at different levels (user-mode, system, hardware) and new mitigations were proposed and explored.

## This thesis' contributions are the following:

- A state-of-the-art of micro architectural and related attacks and of the existing mitigations to hinder them. Their core principles are explained as to provide a synthetic approach of the global micro architectural panel.

- A demonstration of the limitations of Intel SGX enclave system in real-life scenarios, with the application of micro architectural attacks in realistic use-cases.

- An in-depth study of the CVA6 data cache, its structure, behaviors, and specificities to consider when trying to leverage or mitigate a micro architectural attack on this core

- The development of a simulated baremetal micro architectural covert-channel on a RISC-V core, enabling infinite replaying possibilities for an attacker. The whole methodology to implement such an attack is detailed and the inner mechanisms are studied in depth.

- The development of a more realistic micro architectural covert-channel on a real-life application use-case. This attack targets a cryptographic algorithm running on an FPGA-emulated RISC-V core. Different attack conceptions are detailed and the focus is set on the methodology and its impact on the resulting implementation.

- A proposal of a novel micro architectural structure leading to a stronger resilience with respect to micro architectural attacks by adding a secure bus to the architecture.

#### The rest of this document is organized as follows:

Section 2 provides a detailed background on the main micro architectural concepts to understand the rest of the document, as well as a state-of-the-art related to micro architectural and related threats, and the existing mitigations against them.

Section 3 describes the initial study of the micro architectural vulnerabilities on Intel SGX and concludes on the limitations of "closed" architectures for mitigating these leakages.

Section 4 consists in an extensive analysis of the CVA6 RISC-V core, which is the main support for most of the experimentations carried out in this document. This section emphasizes on the description of the data cache of CVA6 and the chosen attack path.

Section 5 focuses on a first simulated baremetal proof-of-concept implementation of a Prime+Probe micro architectural covert-channel on this RISC-V CPU. This section also elaborates on the effect of perturbations on such an attack, and the methodology to reproduce it with a running OS.

### Introduction | 28

Section 6 proposes a more realistic implementation of the Prime+Probe micro architectural covert-channel on an FPGA-emulated CVA6 core running a Linux OS. This implementation is put to the test by targeting the attack of AES-128 and RSA cryptographic algorithms. This section then draws conclusions on the methodology to protect such algorithms against micro architectural attacks, and potential countermeasures.

Section 7 focuses on the protections analyzed or proposed in the work both at the software and hardware levels.

Section 8 provides conclusive remarks on the work described in this document and research perspectives.

# **Background and State of the Art**

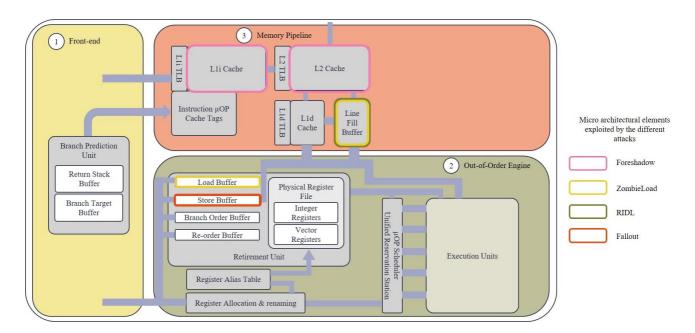

This chapter provides the background knowledge required for understanding the micro architectural information leakages in modern processors. It first provides essential concepts about micro architectural mechanisms that are exploited by the attacks described later in this document. A classification and state-of-the-art on micro architectural covert-channels is then provided. This chapter then details the state-of-the-art and classification on existing micro architectural end-to-end attacks before presenting mitigation techniques. It ends with a general discussion on the conclusions that can be drawn from the existing works in the literature.

# 2.1. Micro architectural mechanisms involved in the presented attacks

Before being able to describe the different information leakage methods that exist at the micro architectural level, it is mandatory to detail several micro architectural notions that are involved in the process of these attacks. The proposed study mainly focuses on cache memories, the behavior of which will be detailed in the next section. Then, an overview of Speculative and Out-of-Order execution will be given, as they are the two most important micro architectural optimization mechanisms involved in the attacks.

### 2.1.1. Architectural and micro architectural worlds

Every recent CPU contains two different worlds that constantly coexist. The first one is the architectural world. It consists in every element that can be seen and explicitly used by the software developer (and/or the development tools) who can modify the data processed in these elements. More specifically, the architectural world consists in the registers, the memories, and every element that can be monitored or modified with a debugger.

The second world is called the micro architecture. This second part of the CPU is more hidden, deeper inside the CPU's construction. The micro architectural world cannot be observed by the developer if the source code of the CPU is not available and it is usually not documented in details by the manufacturer. It is in general not possible to interact with this part of the CPU with a debugger neither to have a deep understanding of its behavior. The micro architectural world is composed of the cache memories, the logical cores, all the internal buffers used for optimization purposes, etc. All of these elements are transparent for the programmer. The micro architecture of a CPU is a specific hardware implementation of computations required to execute the elementary actions defined in a given instruction

set (ISA). Each processor, even based on the same ISA as others, will have a unique micro architecture that will reflect the different technical choices made by the developers.

Architectural and micro architectural views of a CPU may present mismatches. Indeed, the state values and their evolution differ from one world to another. The result of the computation of a given instruction will reside inside micro-architectural elements such as caches and inner buffers of the pipeline before being eventually committed and appear at the architectural level. For this reason, there is an inherent timing discrepancy between the micro architecture and the architecture. Moreover, with some optimization mechanisms detailed below, it is even possible that some content existing inside the micro architecture never gets committed. This content is discarded without having ever existed at the architectural level. The existence of these divergences is the base principle of the micro architectural attacks.

#### 2.1.2. Cache memories

In the race towards performance that exists in CPU designs, memory latency is a main limiting factor. In practice, memory accesses are as slow as several hundreds of CPU clock cycles [17] or even more. One solution to this issue was the introduction of cache memories inside the CPU architectures. Cache memories are smaller and faster memories compared to the main memory. Even if they contain a smaller amount of data, these cache memories can be accessed in a smaller amount of clock cycles. Cache memories can store either data, instructions, or both. Their main objective is to save some data and/or instructions that are most likely to be soon reused so that they can be accessed rapidly. When requesting access to a data or instruction, two possibilities arise: a cache hit or a cache miss. The former consists in requesting information that is already stored in a memory block inside the cache and is therefore accessed rapidly. The latter experiences a slower access time.

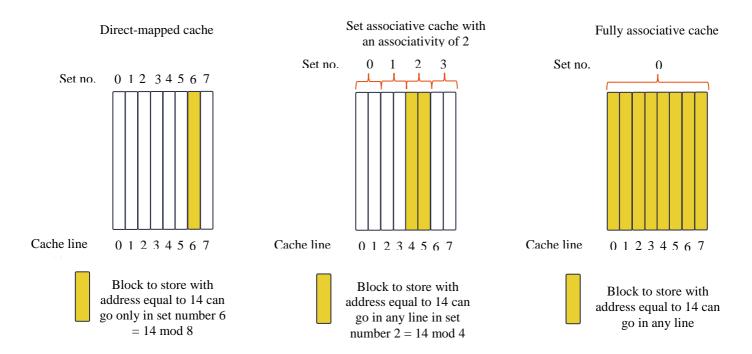

Caches have a specific organization. They are divided into smaller individual memory elements called "cache lines". Each cache line contains several independent elements, either pieces of data or instructions. Some caches are also composed of another subdivision named "sets". These "cache sets" are containing one or more cache lines. The number of cache lines contained in each cache set varies with the cache organization used, as detailed below. Three cache organizations exist:

- 1. In a direct-mapped cache, the element to store is placed inside a definite cache line, based on its address, leaving only a single possibility. In this organization, there are as many cache sets as cache lines. Each set is therefore composed of a single cache line.

- 2. For a fully-associative cache, the element selected can be placed in any cache line. There are no specific restrictions, unlike for the direct-mapped cache. In this organization, there is only a single cache set. This set contains all of the cache lines and represents the whole cache.

- 3. The last cache organization possible is the set-associative cache. In practice, it is a mix of the two previous organizations. When an element to store inside the cache is chosen, its address defines which cache set will be used, similarly to the direct-mapped cache. More specifically, a part of the address is used to calculate an index that refers directly to a given cache set inside the cache organization. Once the index

and thus a cache set are selected, there are still several cache lines to choose from (as many as the cache's associativity). For the cache line, the choice is made by cache policies. The selected element can therefore be stored in any cache line of the selected set. To remember which line has been chosen, a part of the address of the element to store is used as a tag. This tag can be composed of a variable amount of bits (depending on the cache architecture and technical choices) and is stored in a specific array structure, named the tag array. This tag array enables to make a correspondence between an address and the corresponding cache line where it has been stored.

Figure 1 represents each cache organization that has been presented, and provides a simple example on how a given element is placed within each organization.

Figure 1. Representation of the three existing cache organizations and example of placement possibilities for each one

As cache memories have a limited size, it is required to have an eviction policy. This policy determines which cache line to remove when an element needs to be stored in a filled cache. For eviction policies, there are many possible solutions. This type of policy is not needed in a direct-mapped cache and therefore only applies to fully-associative and set-associative organizations. The main policies used to choose which cache line to evict are the following:

Least Recently Used (LRU) evicts the cache line that has been used the least recently. This implies that each cache line contains a supplementary field to store a value reflecting the duration since its last use. This value is incremented for every cache line when there is a cache access, and it is reset to zero for the cache line that is being accessed. Therefore, the cache line with the highest value will be selected for eviction, as it is the least recently accessed one. This policy can be costly especially when there are many cache lines. Indeed, there has to be one counter per line. For this reason, some Pseudo Least-Recently-Used policies tend to simplify the complexity of the LRU policy while having a similar behavior. The main goal of these

policies is to maintain an approximate measurement of each cache line's age rather than their exact value. This implies that the value to be stored inside the register is smaller. Thus, the policy is less costly to implement due to the reduced amount of memory required.

- Random policies can also be used for eviction. They rely on a specific software or hardware element to generate randomness and evict cache lines based on it. There are two types of potential generators: pseudo-random and random generators. The former has a low cost, as it does not require adding some dedicated hardware and solely relies on software algorithms. The resulting pseudo-randomness can be predicted by a motivated attacker however. The latter is based on a hardware random number generator and therefore comes at a much higher cost. The resulting randomness is almost impossible to predict.

- First-in-First-Out (FIFO) policy implies that the cache line to be evicted is the one that has been filled the longest time ago. As opposed to the LRU, this policy does consider the accesses made to the cache lines. Analogously to the case of the LRU, a supplementary field is required in every cache line to keep track of the "age" of each cache line.

Moreover, a policy has to be introduced to determine when to update the main memory when updating an element that already exists inside the cache. This is a writing or coherence policy. These policies are only required in the case of data caches (instruction caches do not need them). There are two main possible writing policies:

- The CPU updates the cache and the main memory synchronously when there is a request to modify the content of the accessed memory block. This is a write through policy.

- The CPU only updates the cache; it writes the data to the main memory only when there is another request to overwrite an attributed cache way that is "dirty", i.e. where values have been modified by the processor. This is done to avoid losing the content previously stored in the data cache, while avoiding too many main memory accesses that are useless for temporary data quickly changed by the processor. It is called a write back policy.

There are also two possible approaches to handle write operations when the data is not already allocated in the data cache:

- Write-allocate consists in writing the data in the cache and then into the main memory

- No-write-allocate consists in writing the memory block only in the main memory and not in the cache. Data is only loaded into the cache on read misses.

In modern processor architectures, high-end CPUs generally embed several cache memories with a specific hierarchy. These cache memories have different sizes, and the smaller is the first one to be used, as it is the fastest. The smallest and fastest cache memory is named the L1 (for level 1) cache. If a request to the L1 cache is a cache miss (i.e. the element requested does not reside inside the L1 cache), then the request is sent to the L2 cache, then to the L3

cache and so on until the main memory is reached. The main memory is always the last one to be used as it is the slowest (but also the biggest). L1 caches are the smallest and fastest caches, and are generally separated into two distinct caches: one for instructions and one for data. L2 caches are bigger and slower and are designed to reduce the impact of L1 cache misses. They are generally unified, meaning that they both contain instructions and data. This depends on the specific application they will be used for however. L1 and L2 caches are generally core-specific, meaning that each physical core has its own L1 and L2 caches. They are still shared among several threads on the same core. This is also application-dependent as in some specific cases, the L1 and L2 caches can be shared among several physical cores. In some architectures, there are also higher level L3 and L4 caches. These caches are even bigger and slower than the L2, but still faster than the main memory. Analogously to the L2 cache, the goal of the L3 and L4 caches is to reduce further the timing penalties of cache misses. These caches, contrarily to the L1 and L2 caches are generally shared among several different physical cores. The combination of all the caches and the main memory composes the memory hierarchy.

### 2.1.3. Speculative execution

Speculative execution is an optimization mechanism aiming at improving CPU performances. The general idea behind this mechanism is to anticipate part of the future computations and perform them in advance and in an optimized way in order to save some precious time. Speculative execution regroups two main inner CPU mechanisms that work together: branch prediction and Out-of-Order execution.

#### 2.1.3.1. Out-of-Order execution

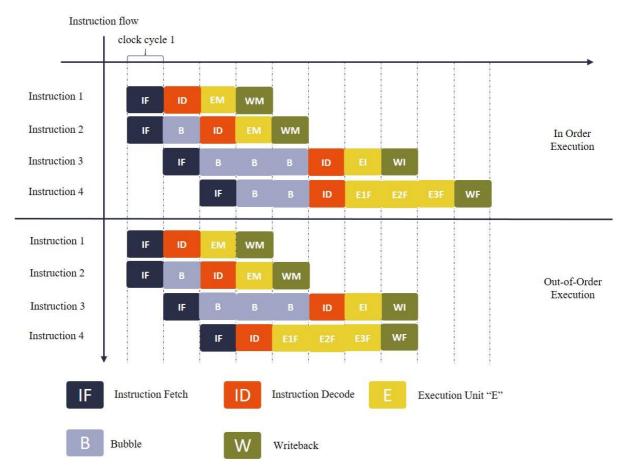

Processor pipelines are composed of several stages (frontend, instruction decode, issue stage, execution stage...). When instructions are issued, the actual computation happens at the execution stage of the pipeline. The execution stage is composed of several execution units, for example a load-store unit (LSU), a multiplier, an arithmetic-logic unit (ALU), etc. These resources are limited and can only be used by a single instruction at a time. The basic method for computing instructions is called "in-order". This means that the instructions are computed and calculated in the same order as they are issued by the programmer's code. Thus, a given instruction cannot be computed before all of the previous ones have been. This has several drawbacks, especially when consecutive instructions require the same execution unit to be computed. This leads to a pipeline stall until the specific execution unit is freed. In order to avoid this type of pipeline stall, and to gain some precious execution time, another method for computing instructions has been developed. "Out-of-Order" execution, as opposed to "in-order" execution, is an optimization mechanism that tends to optimize the usage of the available execution resources. To proceed, it disorganizes the instructions compared to the program semantic. The objective is to compute all the instructions as fast as possible by maximizing the usage of every execution unit available in the pipeline. This results in a much better parallelization of the execution units' usage. However, the instructions are not computed in the order requested by the programmer, as visible in Figure 2. In this figure, the considered CPU is a simple "superscalar" processor. It can read up to two instructions per cycle. We consider three execution units: integer calculations (two stages EI and WI), floating-point calculations (four stages E1F, E2F, E3F and WF) and memory accesses (two stages EM and WM). We also suppose that there is a memorization element in the completion unit, and that there are two writeback entries. We then consider the following simplified assembly pseudo-code:

Load R3

Load R8

Add R3, R8, R3

AddF RF2, RF4, RF6

Figure 2. Schematic representation of the difference between in-order and out-of-order execution

Some instructions that are supposed to be computed after can be computed before another instruction that uses a busy or slow execution unit. To restore the correct flow of instructions, and issue it as requested by the programmer, a specific structure is added to the pipeline. The reorder buffer stores the computed instructions and reorganizes them in the correct order before transmitting them to the commit stage, thus returning the appropriate architectural state requested by the programmer. The reorder buffer is not the only supplementary hardware element that needs to be added in the case of an Out-of-Order CPU. Several tables to memorize the initial program order, intermediary states in case or error and many other elements have to be further implemented. Therefore, Out-of-Order execution is very costly and only added in high-end processors that have strong performance requirements and are not too limited in terms of space or cost.

#### 2.1.3.2. Branch Prediction