# On improving complexity of linearizable and wait-free implementations of concurrent objects by relaxing their specifications.

Adnane Khattabi Riffi

#### ▶ To cite this version:

Adnane Khattabi Riffi. On improving complexity of linearizable and wait-free implementations of concurrent objects by relaxing their specifications.. Computational Complexity [cs.CC]. Université de Bordeaux, 2023. English. NNT: 2023BORD0101. tel-04147099

## HAL Id: tel-04147099 https://theses.hal.science/tel-04147099

Submitted on 30 Jun 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

# ÉCOLE DOCTORALE MATHÉMATIQUES ET INFORMATIQUE

## Par Adnane KHATTABI

Amélioration de Complexité d'Implémentations Linéarisables et Wait-free d'Objets Concurrents en Relaxant leurs Spécifications

Sous la direction de : Colette JOHNEN et Alessia MILANI

Soutenue le 31 mars 2023

#### Membres du jury :

| Mme. Emmanuelle ANCEAUME | Directrice de Recherche | IRISA                    | Rapporteure  |

|--------------------------|-------------------------|--------------------------|--------------|

| M. Achour MOSTEFAOUI     | Professeur              | Université de Nantes     | Rapporteur   |

| M. Nicolas HANUSSE       | Directeur de Recherche  | Université de Bordeaux   | Président    |

| Mme. Janna BURMAN        | Maître de conférences   | Université Paris-Saclay  | Examinatrice |

| Mme. Alessia MILANI      | Professeure             | Aix-Marseille Université | Directrice   |

| Mme. Colette JOHNEN      | Professeure             | Université de Bordeaux   | Directrice   |

### THESIS PRESENTED

## TO OBTAIN THE DEGREE OF

# DOCTOR FROM BORDEAUX UNIVERSITY

# DOCTORAL SCHOOL OF MATHEMATICS AND COMPUTER SCIENCE

### Adnane Khattabi

On Improving the Complexity of Linearizable and Wait-free Implementations of Concurrent Objects by Relaxing their Specifications

Supervisors: Colette Johnen and Alessia Milani

Defended the 31st of March 2023

#### Members of the jury:

| Emmanuelle ANCEAUME | Research Director   | IRISA                    | Reporter   |

|---------------------|---------------------|--------------------------|------------|

| Achour MOSTEFAOUI   | Professor           | Nantes University        | Reporter   |

| Nicolas HANUSSE     | Research Director   | Bordeaux University      | President  |

| Janna BURMAN        | Associate Professor | Paris-Saclay University  | Examinator |

| Alessia MILANI      | Professor           | Aix-Marseille University | Supervisor |

| Colette JOHNEN      | Professor           | Bordeaux University      | Supervisor |

# Amélioration de Complexité d'Implémentations Linéarisables et Wait-free d'Objets Concurrents en Relaxant leurs Spécifications

**Résumé**: Dans un contexte distribué, les différents problèmes de synchronicité entre processus sont modélisés à l'aide d'objets partagés. Lorsqu'un nouvel objet partagé est implémenté, on s'appuie souvent sur des objets de base préexistants. En cherchant à maximiser l'efficacité de ces implémentations, un nouveau domaine de recherche a émergé ces dernières années, centré sur le compromis possible entre la précision d'une implémentation et sa complexité.

Nous étudions dans cette thèse la définition d'objets partagés relaxés où les opérations ont le droit à une certaine marge d'erreur, et comment cela peut améliorer la complexité de leurs implémentations. Nous considérons le cas d'objets partagés connus : counter, max register, et FIFO queue.

Tout d'abord, nous étudions la possibilité d'améliorer la complexité des implémentations relaxées du counter et max register par rapport à leurs implémentations exactes. Dans le modèle de mémoire partagée classique, nous étudions dans quelle mesure permettre aux implémentations linéarisables et wait-free de ces objets de retourner des valeurs approximatives, plutôt que des valeurs précises, peut améliorer leur complexité.

Nous considérons le k-multiplicatif max register et le k-multiplicatif counter, où les opérations de lecture sont autorisées à se tromper d'un facteur multiplicatif de k. Nous présentons une implémentation du k-multiplicatif counter wait-free linéarisable pour  $k \geq n$  avec une complexité de pas amortie constante où n est le nombre de processus. Nous montrons également qu'en bornant l'exécution, nous sommes capables d'implémenter le counter k-multiplicatif pour  $k \geq \sqrt{n}$  d'une manière linéarisable wait-free avec une complexité de pas dans le pire des cas de  $O(\min(\log(\log(m+1)), n))$  où m représente la limite du nombre d'opérations CounterIncrement lors d'une exécution. Les deux implémentations offrent une amélioration exponentielle de la complexité de leurs équivalents exacts dans l'état de l'art.

Ensuite, nous montrons que la relaxation de la sémantique du max register en autorisant l'imprécision d'un facteur multiplicatif constant produit une amélioration exponentielle de la complexité de pas dans le pire des cas pour la variante bornée, et de la complexité de pas amortie pour la variante non bornée.

Afin de mesurer les limites de ces relaxations, nous étudions les bornes inférieures de la complexité du counter et max register k-multiplicatif. Nous obtenons le résultat que lorsque le paramètre d'approximation k ne dépend pas du nombre de processus, assouplir la sémantique du counter en autorisant l'imprécision d'un facteur multiplicatif ne peut asymptotiquement réduire la complexité des pas amortis des compteurs non bornés de plus d'un facteur logarithmique. Nous prouvons également que notre max register k-multiplicatif borné est optimal.

En ce qui concerne la FIFO queue, la conception d'implémentations efficaces wait-free est complexe malgré son utilisation dans de nombreuses applications distribuées. La plupart des implémentations des FIFO queue dans la littérature s'appuient sur des contraintes de concurrence : tous les processus ne sont pas autorisés à exécuter des opérations de Enqueue et de Dequeue.

Dans cette thèse, nous étudions la possibilité d'implémenter la FIFO queue d'une façon wait-free avec une complexité logarithmique dans le pire des cas sans contraintes de concurrence. Par conséquent, nous présentons une implémentation qui prend en charge n enqueuers et k dequeuers où la complexité dans le pire des cas d'une opération Enqueue est en  $O(\log n)$  et où la complexité de l'opération Dequeue dépend du niveau de concurrence et est  $O(k \log n)$  dans le pire des cas.

Nous nous appuyons ensuite sur l'assouplissement de la sémantique de la FIFO queue pour montrer que le fait d'autoriser des opérations Dequeue concurrentes à retourner le même élément engendre une implémentation avec une complexité en  $O(\log n)$  dans le pire des cas

pour les opérations Enqueue et Dequeue.

Mots-clés: objets concurrents, algorithmes distribués, calcul distribué, complexité, tolérance aux pannes

#### On Improving the Complexity of Linearizable and Wait-free Implementations of Concurrent Objects by Relaxing their Specifications

**Abstract:** In a distributed context, the different problems of synchronicity between processes are modeled using shared objects. When a new shared object is implemented, it relies on base objects consisting of preexisting implementations, as building blocks. In seeking to maximize the efficiency of these implementations, a new research field has emerged in recent years, with a focus on the possible trade-off between the accuracy of an implementation and its complexity.

We investigate in this thesis how defining relaxed shared objects where the operations are allowed a certain margin of error can result in improved theoretical complexity results. We consider the case study of well-known shared objects, namely: the counter, max register, and FIFO queue.

First, we study the possible improvement in step complexity of the relaxed implementation of the counter and max register objects compared to their exact implementations. In the classical shared memory model, we investigate the extent to which allowing wait-free linearizable implementations of these objects to return approximate values, rather than accurate ones, may improve their step complexity.

We consider the k-multiplicative-accurate max register and the k-multiplicative-accurate counter, where read operations are allowed to err by a multiplicative factor of k. We give a wait-free linearizable k-multiplicative-accurate counter implementation for  $k \geq n$  with constant amortized step complexity where n is the number of processes. We also show that by bounding the execution, we are able to implement the k-multiplicative-accurate counter for  $k \geq \sqrt{n}$  in a wait-free linearizable manner and with a worst-case step complexity of  $O(min(\log(\log(m+1)), n))$  where m represents the bound on the number of CounterIncrement operations during an execution. Both implementations offer an exponential improvement on the complexities of their exact counterparts in the state of the art.

Then, we show that relaxing the semantics of max registers by allowing inaccuracy of even a constant multiplicative factor yields an exponential improvement in the worst-case step complexity of the bounded variant and in the amortized step complexity of the unbounded one.

For the sake of gauging the limitations of these relaxations, we study the lower bounds of the complexity of the k-multiplicative-accurate counter and max register in both their bounded and unbounded variations. We obtain the result that when the approximation parameter k does not depend on the number of processes, relaxing counter semantics by allowing inaccuracy of a multiplicative factor cannot asymptotically reduce the amortized step complexity of unbounded counters by more than a logarithmic factor. We also prove that our bounded k-multiplicative-accurate max register is optimal and matches the lower bound.

When it comes to the FIFO queue, designing efficient wait-free implementations remains a challenge despite its usage in many distributed applications. Most of the FIFO queue implementations in the literature rely on concurrency constraints: not all processes are allowed to execute either/or Enqueue and Dequeue operations.

In this thesis, we investigate whether it is possible to implement a logarithmic worst-case step complexity wait-free implementation that does not suffer from concurrency constraints.

Therefore, we present a wait-free FIFO queue implementation that supports n enqueuers and k dequeuers where the worst-case step complexity of an Enqueue operation is in  $O(\log n)$  and where the complexity of the Dequeue operation depends on the level of concurrency during the execution and is  $O(k \log n)$  in the worst-case scenario.

We then rely on the relaxation of the FIFO queue semantics to show that allowing concurrent Dequeue operations to retrieve the same element results in an implementation with  $O(\log n)$  worst-case step complexity for both the Enqueue and Dequeue operations.

**Keywords:** concurrent shared objects, distributed algorithms, distributed computing, complexity, fault tolerance

Laboratoire Bordelais de Recherche en Informatique (LaBRI)

UMR 5800, Université de Bordeaux, 33405 Talence, France.

# Acknowledgements

I would like to thank the many people in my life that have supported me throughout the different stages of my thesis and have made it possible for me to reach the other side of the tunnel.

Starting with my supervisors Alessia Milani and Colette Johnen who have been patient and supportive with their guidance even when I found it difficult to look ahead. I also would like to thank the collaborators I had the chance to work with in different capacities namely, Corentin Travers, Danny Hendler, and Jennifer Welch who have helped shape this thesis alongside all the colleagues at the LaBRI who were more than happy to discuss theory or even just hear me rant. Especially, I would like to name Nicolas Hanusse and Pascal Weil, the members of my monitoring committee, and thank them for their encouragement and objective assessment of my thesis throughout the years. I also would like to mention the people I have shared an office with and came to consider friends Yanis, Colleen, Amaury, and many others.

I owe deep gratitude to my close friends whose presence in my life does more than I could ever quantify. Thank you, Marwa, Ghita for the decade-old friendship and your unwavering love and support.

Korlan, who I met the first month of my thesis, and have gone through the entire journey together and I now consider one of my closest friends.

My personal trainer and friend Marc, for inspiring me to live life for myself and teaching me to disconnect and destress during some of the most difficult periods of my thesis.

And the friends that have made an impact on different periods of my life but we have since grown apart, I will always hold love for you.

Finally, to my mom and dad for being an example to me of hard work and dedication no matter what cards you have been dealt in life. I love you and hope you are proud.

To seeing things through.

# Contents

| 1 | Intr | roduction                                                              |

|---|------|------------------------------------------------------------------------|

|   | 1.1  | Overview                                                               |

|   | 1.2  | Model and Preliminaries                                                |

|   |      | 1.2.1 Model                                                            |

|   |      | 1.2.2 Termination Conditions                                           |

|   |      | 1.2.3 Consistency Conditions                                           |

|   |      | 1.2.4 Sequential Specification Relaxations                             |

|   | 1.3  | Related Work and Contributions                                         |

|   |      | 1.3.1 Counter and Max Register                                         |

|   |      | 1.3.2 FIFO Queue                                                       |

|   | 1.4  | Organization                                                           |

| 2 | K-n  | nultiplicative-accurate Counter and Max Register 2                     |

|   | 2.1  | Introduction                                                           |

|   | 2.2  | Unbounded k-multiplicative-accurate Counter                            |

|   |      | 2.2.1 Algorithm Description                                            |

|   |      | 2.2.2 Wait-freedom and Technical Lemmas                                |

|   |      | 2.2.3 Linearizability                                                  |

|   |      | 2.2.4 Complexity Analysis                                              |

|   | 2.3  | Bounded k-multiplicative-accurate Counter                              |

|   |      | 2.3.1 Algorithm Description                                            |

|   |      | 2.3.2 Linearizability                                                  |

|   |      | 2.3.3 Complexity Analysis                                              |

|   | 2.4  | Bounded k-multiplicative-accurate Max Register                         |

|   | 2.5  | Unbounded k-multiplicative-accurate Max Register                       |

|   |      | 2.5.1 Algorithm Description                                            |

|   |      | 2.5.2 Linearizability and Wait-freedom                                 |

|   | 2.6  | Worst-case Step Complexity Lower bound for k-multiplicative-accurate   |

|   |      | m-bounded Max Register and Counter                                     |

|   | 2.7  | Amortized Step Complexity Lower bound for $k$ -multiplicative-accurate |

|   |      | Counter                                                                |

|   | 2.8  | Discussion                                                             |

| 3 | Effi | cient Queue Implementations 6                                          |

|   | 3.1  | Introduction                                                           |

|   | 3.2  | Wait-Free Linearizable Queue                                           |

|   |      | 3.2.1 Inspiration 6                                                    |

| 5.4 | Discui |                                                                           | 0.5         |

|-----|--------|---------------------------------------------------------------------------|-------------|

| 2 / | Discus | ssion                                                                     | 89          |

|     | 3.3.5  | Step Complexity                                                           | 89          |

|     | 3.3.4  | FIFO Queue Specification                                                  | 88          |

|     | 3.3.3  | Set-linearizability                                                       | 84          |

|     | 3.3.2  | Algorithm Properties                                                      | 82          |

|     | 3.3.1  | Algorithm Pseudocode and Description                                      | 80          |

| 3.3 | Set-Li | nearizable Wait-free Queue Algorithm with Multiplicity                    | 80          |

|     | 3.2.4  | Proof                                                                     | 69          |

|     | 3.2.3  | Algorithm Pseudocode                                                      | 65          |

|     | 3.2.2  | Algorithm Overview                                                        | 64          |

|     |        | 3.2.3<br>3.2.4<br>3.3 Set-Li<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5 | 3.2.4 Proof |

# Chapter 1

# Introduction

#### 1.1 Overview

Following the natural evolution of modern hardware architectures into multi-core systems, the issues of synchronicity between different processes became more prevalent. For instance, ensuring the data stored remains consistent for a multi-process system is much more challenging than the case of a single-process environment.

Take, for example, the problem of assigning valid memory addresses for different applications. While the solution for a single-process system consists of simply retrieving the last attributed address and then assigning the next available slot, the problem becomes complex when it requires coordination between multiple processes.

Many fundamental multi-process coordination problems (akin to memory address assignment) can be expressed as *counting problems* [6]. By considering an *abstract data type*, like the *shared counter* in the case of counting problems, it is possible to resolve the synchronicity problems for multiple processes by implementing the data type. This formalism shifts the problems at hand from low-level and architecture-specific to high-level abstract questions.

A shared object is an instance of an abstract data type represented by a domain of possible value and a set of operations that provide the correct behavior of the object when the operations are invoked in a sequential setting. This definition is what we call the sequential specification of the object.

An implementation of a shared object offers the algorithms describing the steps executed by each process when applying an operation on the object being implemented.

Distributed algorithms that implement new shared objects rely on preexisting implementations of common shared objects denoted *base objects* as building blocks because they already solve many of the synchronization problems when considering a distributed execution environment. Relying on base objects also benefits from the *composable* or *local* property of linearizability and wait-freedom; meaning that if all the base objects used in the implementation of a new shared object are linearizable and wait-free, the implemented object is also linearizable and wait-free.

We say that a process takes a *step* during the execution of an operation of an implemented shared object when it executes an operation on a base object. Any computations that are executed locally by the process do not count in the total cost of the algorithm that implements the shared object. An *execution* is the sequence of steps executed by the processes as they follow the algorithms implementing a shared object.

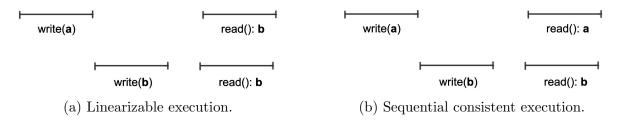

Figure 1.1: Different execution scenarios for a shared register.

Measuring the correctness of an implementation depends on how closely matched the behavior of the operations executed in a concurrent setting, is to the sequential specification of the object. Consistency conditions formalize this distance and can vary by how strictly they relate concurrent executions to the sequential specification. The most common of these conditions is linearizability introduced by Herlihy and Wing [26] such that, roughly speaking, an implementation is linearizable if any execution where operations are executed concurrently is equivalent to a sequential execution where each operation appears to take effect instantly at an instance during the execution of the operation and behave according to the sequential specification of the object.

It has been shown that linearizable implementations are often more costly than implementations with more lenient consistency conditions. For instance, this is the case for *sequential consistency* which requires that the operations appear to take place in an order that reflects the order of operations for each individual process as opposed to linearizability which requires a total order of all operations (Figure 1.1). Different results substantiate the claim by showcasing the cost difference between linearizable and sequential consistent implementations of different shared objects from read/write register, FIFO queue, and stack (Attiya and Welch [11]) to snapshot (Petrin et al. [36]).

The implementation of a shared object is also subject to termination conditions which ensure a certain degree of progress during an execution. To ensure the operations have some guarantee of ending, these conditions are of varying degrees depending on whether the guarantee of progress is only system-wide or if it is process-specific. We consider the strongest of the termination conditions denoted wait-freedom [25] which requires that every operation ends after executing a finite number of steps.

In this thesis, we focus on complexity analysis to measure the efficiency of an implementation of a shared object and how it compares to the state of the art. For a given implementation of a shared object, many variations of the complexity of the operations can be calculated: from space complexity to step complexity and from the worst-case scenario to an overall average. In our analysis, We consider the worst-case step complexity and the amortized step complexity. The worst-case step complexity is defined as the worst-case (over all possible executions) total number of steps taken by an operation. The amortized step complexity is defined as the worst-case average number of steps performed by operations. It measures the performance of an implementation as a whole rather than the performance of individual operations. More precisely, given a finite execution E, an operation Op appears in E if it is invoked in E. We denote by Nsteps(op, E) the number of steps performed by op in E and by Ops(E) the set of operations that appear in E. The amortized step complexity of an implementation A

is then:

$$AmtSteps(A) = \max_{E} \frac{\sum_{op \in Ops(E)} Nsteps(op, E)}{|Ops(E)|}$$

A large portion of the research around shared objects centers around the goal of improving the efficiency of the implementations and reaching the best possible complexities. It is also of high interest to prove *lower bounds* or the limits to how low the complexity of an implementation can get under a specific computational model. For many common shared objects (e.g. *Counter*, *Max Register*, *FIFO queue*, etc.), the aim is to find implementations that match the complexity lower bounds.

For instance, a well-known result by Jayanti, Tan and Toueg [29] proved a linear lower bound in the number of processes n on the worst-case step complexity of a large class of shared objects that includes the counter object. An implementation of a wait-free counter with optimal worst-case step complexity can be constructed easily by using a wait-free atomic snapshot: Each process has a component in the snapshot object, and to increment the counter, a process simply increments its component. To read the counter's value, the process invokes Scan to obtain an atomic view of the snapshot, and returns the sum of all components in the view it obtains. Since wait-free atomic snapshot can be implemented, using reads and writes only, with worst-case step complexity linear in n, e.g. [9], so can counters.

To further optimize beyond this point, different strategies have been conceived to bypass the limitations of a lower bound on shared objects. For instance, by considering bounded executions where the number of operations permitted is restricted to a number m of calls; sub-linear implementations of the counter object have been obtained [5].

More generally, a *bounded* shared object is a variation of a regular object but with a restriction on the number of operations in an execution of the object.

Recently, however, there has been a surge of interest in the relaxation of the sequential specification of different shared objects in order to obtain more efficient implementations. The intuition for these relaxations comes from the disconnect between the strict sequential specification of shared objects and the applicative needs in practical settings.

In many cases, applications can function normally even in the case of some anomalies in data. For instance, in the context of Big Data applications, many popular data platforms including BigQuery [13], Oracle [37], and SQL Server [4] support an approximate form of counting because the real-life applications can tolerate a margin of error and run more efficiently using approximation.

The goal is to be able to implement a shared object in a more efficient manner by allowing operations applied to the object to err to a certain degree defined by the relaxation. This thesis investigates different relaxations of widely used shared objects. And Comparing these relaxed objects to the exact versions, we can gauge the possible optimization of the implementations when applying different relaxations to shared objects.

Specifically, we focus in this thesis on the k-multiplicative-accurate relaxation first introduced in [7] for the counter object. We study the relaxation applied to common shared objects, namely the counter and max register. The relaxed sequential specification of the k-multiplicative-accurate counter allows for the return value of a call to CounterRead to fall within an approximative range of the value returned by the exact counter. Specifically, a call to CounterRead returns x such that  $v/k \le x \le k \cdot v$  where

v is the exact value of the counter. We also study the same k-multiplicative-accurate relaxation applied to the max register. Similarly, an instance of the MaxRead operation returns an approximate value x' within a k multiplicative range of the maximum value v' written to the register (i.e.  $v'/k \le x' \le k \cdot v'$ ).

Following the results on the relaxed versions of the counter and max register, we shift focus to the FIFO queue and consider the relaxation denoted *multiplicity* and introduced in [14] which allows multiple concurrent *Dequeue* operations to return the same element.

In the remainder of this chapter, we present the model of computation considered throughout the thesis and then give a detailed synthesis of our contributions and their position from the standpoint of the state of the art.

#### 1.2 Model and Preliminaries

#### 1.2.1 Model

We consider the standard asynchronous shared memory model with a set  $\mathcal{P}$  of n processes  $p_1, \ldots, p_n$ . Each process  $p_i$  is identified by a unique integer i.

We consider that the processes are prone to crashes. Thus, a process could stop due to a crash at any moment during an execution. In an asynchronous setting, the physical time between two instructions is unknown, making it impossible to know with certainty that another process has crashed. Any distributed algorithm in the asynchronous model must take into consideration the fact that it is impossible to distinguish between the case where a process crashes and the case where it might resume its execution.

In a concurrent setting, the problems of synchronization between processes that arise are modeled using *shared objects*. These objects are defined by a *sequential specification* describing the set of operations that can be invoked on the implemented object as well the correct behavior of the operations in the absence of concurrency.

Formally, a high-level shared object O is a concrete representation of a data type T, composed of a set of states S, a finite set of operations O and a set of transitions  $\sigma$  between states. A transition  $\sigma(s, op(arg)) = (s', res)$  describes the sequential behavior of the object when an instance op of an operation is invoked with the argument arg, causing the object to move from its current state s to a new state s', and resulting in a response res to the operation from the object. We say that op is an update operation if it changes the state of O.

We say that an object or data type is deterministic if the set of transitions  $\sigma$  is a function; meaning that a specific invocation of an operation on the object from a state would always (in any execution) result in the object transitioning to the same new state and having the same response.

To solve a problem in a distributed system is to present a correct implementation of the shared object under a specific model of computation.

Implementation and execution An implementation of a shared object provides a specific data representation for the object from a set of shared base objects, each of which is assigned an initial value; the implementation also provides algorithms for each process in  $\mathcal{P}$  to apply each operation to the object being implemented. To avoid confusion, we

call operations on the base objects *primitives* and reserve the term *operations* for the objects being implemented.

An execution fragment is a (finite or infinite) sequence of steps performed by processes as they follow their algorithms. In each step, a process applies at most a single primitive to a base object (possibly in addition to some local computation). An execution is an execution fragment that starts from the initial configuration. This is a configuration in which all base objects have their initial values and all processes are in their initial states. More generally, at any moment during the execution, the configuration of E represents the state of all the base objects. We say that an operation is complete in an execution, if it returns within this execution. Otherwise, we say that the operation is pending. If an operation  $op_1$  returns before a second operation  $op_2$  is invoked, we say that  $op_1$  is before  $op_2$  in the real-time execution order, and write  $op_1 <_{ro} op_2$ .

A set of primitives is *historyless* if all the nontrivial primitives in the set overwrite each other; we also require that each such primitive overwrites itself. A primitive is *nontrivial* if it may change the value of the base object to which it is applied.

In the shared memory model, the processes communicate with each other by applying *primitives* to *base objects*.

The processes are sequential. Meaning that when executing an operation, a process will execute the instructions in order and is not able to execute them in parallel. Since we consider an asynchronous model, the physical time required for the execution of a step might differ from process to process and from one instance of an operation to another. Therefore, any complexity analysis we present is based on the number of steps executed by a process during an operation.

**Shared objects** In practice, there is no distinction between the shared objects being implemented and the base objects. On a case-by-case basis, the same shared object can play both roles. For instance, it is possible to use a shared counter as a base object for the implementation of a queue, as it is just as possible to have a new implementation of the counter itself.

Aside from the atomic Read/Write registers, the following is an exhaustive list of the shared objects we consider in this thesis:

- Fetch&Inc: the only primitive executed on the Fetch&Inc object, is the identically named primitive Fetch&Inc that increments the value of the object by 1 and returns the value prior to the incrementation.

- **Test&Set:** is set initially to 0, and the first call to the primitive *test&set* changes its value to 1. All instances of *test&set* return the previous value of the object and we consider that it also takes the simple *Read* primitive.

- Swap: takes the primitives Swap and Read, such that an instance Swap(v) writes v to the object and returns its previous value.

- Max register: takes the two primitives ReadMax and WriteMax such that ReadMax returns the maximum value written to the register through the calls to WriteMax.

- Counter: can be incremented by calling the primitive CounterIncrement and a call to CounterRead returns the number of calls to CounterIncrement before it.

- **Snapshot:** defined by the two primitives *Update* and *Scan*. Each process has a corresponding component in the snapshot and is the only one allowed to modify through a call to *Update*. And a process is able to obtain a coherent state of all the components in the snapshot object using the *Scan* primitive.

- CAS: takes the Read primitive as well as the Read-Modify-Write primitive CAS, such that the call CAS(old, new) writes new to the object only if the previous value of the object was old.

- **FIFO queue:** provides the two high-level operations Enqueue and Dequeue. The sequential specification of the queue determines that an instance Enqueue(v) adds the element v at the tail of the queue, while the Dequeue() operation removes the element at the head of the queue and returns its value, if the queue is not empty, otherwise, it returns  $\epsilon$ .

When limiting the available shared base objects to the "weaker" primitives, It is often the case that the implementation of new shared objects proves to be more difficult. For instance, implementations of the FIFO queue without the CAS object are rare and require clever algorithmic ideas. This "synchronization power" that the CAS has over other base objects is a great indicator of the existence of a hierarchy within the set of shared objects.

Consensus number The notion of *consensus number* was introduced by Herlihy in [25] to describe such a hierarchy for shared objects based on their ability to solve the consensus problem for a specific number of processes.

The consensus problem is fundamental in the field of fault-tolerant distributed computing since it models a large set of problems in which processes need to agree on a specific value. The consensus object takes the operation Propose(). When process  $p_i$  executes an instance  $Propose(v_i)$ , it signifies that  $p_i$  is proposing the value  $v_i$  to the consensus. The operation returns the agreed-upon value of the consensus. Formally, any implementation of the consensus object needs to fulfill the following requirements.

**Definition 1.2.1.** Consensus: Let A be an implementation of the consensus object. Let  $Propose(v_i)$  be an instance executed by process  $p_i$  in which  $p_i$  proposes the value  $v_i \in V$  the set of possible values of the consensus object. A satisfies the conditions of safety (validity, agreement) and liveness (termination).

- Validity: If the agreed-upon value is v, a process has invoked Propose(v).

- Agreement: No two processes decide on different values.

- Termination: All non-faulty processes decide on a value.

| Consensus<br>Number | Object                                                                                 |

|---------------------|----------------------------------------------------------------------------------------|

| 1                   | read/write registers                                                                   |

| 2                   | test&set, swap, fetch&add, queue, stack                                                |

|                     |                                                                                        |

| 2n-2                | n-register assignement                                                                 |

|                     |                                                                                        |

| $\infty$            | memory-to-memory move and swap, augmented queue, compare&swap, fetch&cons, sticky byte |

Table 1.1: Examples of consensus numbers of different shared objects (table from [25]).

Herlihy hierarchy The consensus number associated with an object is the number of processes we can solve the consensus problem for, using only the object and Read/Write registers. For instance, the Read/Write registers have a consensus number 1, and the Fetch&Add, Swap and Stack objects all have consensus number 2. We say that the consensus number of an object is infinite if it can solve the consensus problem in an asynchronous system with n processes for any  $n \in \mathcal{N}$ . The CAS object is an example of an object with an infinite consensus number. Table 1.1 taken from [25], gives a more comprehensive list of different shared objects and their consensus number. In [25], it is also shown that given an object T with a consensus number i alongside Read/Write registers, it is impossible to have a wait-free implementation of any object with a consensus number j > i. However, Jayanti argues in [27] that the Herlihy hierarchy is not a robust wait-free hierarchy. Meaning that contrary to what might be assumed, it is possible to implement an object with a consensus number j using a combination of any number of objects with consensus numbers in  $1, \ldots, j-1$ . Meaning that combining weaker shared objects can result in the implementation of stronger ones.

#### 1.2.2 Termination Conditions

An execution is *non-blocking* if the failure or crash of a process does not impede the progression of other processes. An execution is *lock-free* if there is a guarantee of system-wide progression but not necessarily a guarantee for each process to terminate. An execution is *wait-free* [25] if each process completes its operations if it performs a sufficiently large number of steps. We say that an implementation verifies any termination condition if all its executions do as well.

**Definition 1.2.2.** Lock-freedom: Let A be an implementation of a concurrent object O and E an execution of A. E is lock-free if for any operation  $\alpha$  that takes infinite steps in E there exists infinitely many concurrent operations executed by other processes that terminate in a finite number of steps (system-wide progress).

**Definition 1.2.3.** Wait-freedom: Let  $\mathcal{A}$  be an implementation of a concurrent object  $\mathcal{O}$  and  $\mathcal{E}$  an execution of  $\mathcal{A}$ .  $\mathcal{E}$  is wait-free if all operations in  $\mathcal{E}$  terminate in a finite number of steps (per-process progress).

#### 1.2.3 Consistency Conditions

Since shared objects are defined by sequential specifications, we require a means to relate the correct behavior of the object in a concurrent setting to its definition in the absence of concurrency. Consistency conditions define what behaviors are allowed during a concurrent execution.

**Definition 1.2.4.** A consistency condition C is the set of all legal operation sequences of any data type T under C.

#### Linearizability

As one of the most intuitive consistency conditions, *linearizability* is used throughout the literature. Roughly speaking, an execution is *linearizable* [26] if each operation appears to take effect atomically at some point between its invocation and response and behaves according to the sequential specification of the object.

**Definition 1.2.5.** Linearizability: Let A be an implementation of a concurrent object O. An execution E of A is linearizable if there is a sequential execution S of O such that S contains every completed operation of E and might contain some pending operations, and the inputs and outputs of the invocations and responses of the operations in S agree with the inputs and outputs in E and behave according to the sequential specification of O. Furthermore, if two completed operations  $op_1$  and  $op_2$  in E verify  $op_1 <_E op_2$ , then  $op_1$  appears before  $op_2$  in S.

We say that an implementation is linearizable if all its executions are linearizable.

#### Weaker Consistency Conditions

In recent years, the *relaxation* of the implementations of shared objects for the sake of solving scalability issues, has become the focus of many research topics. We present next some of the most common weaker consistency conditions.

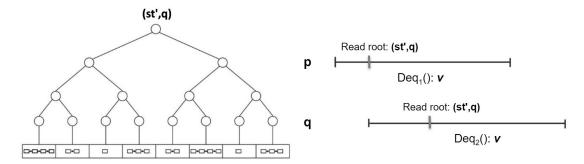

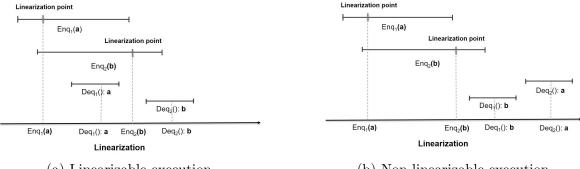

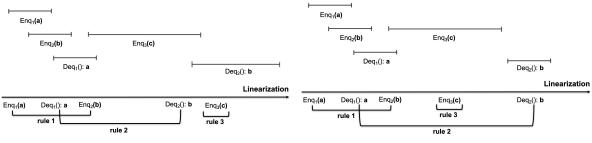

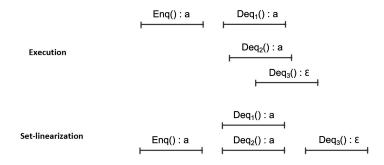

Formally, the set-sequential specification of a shared object differs from its sequential specification in regards to the definition of the transition function  $\sigma$  between states of the object. In the set-sequential specification, instead of taking a single instance op of an operation as a parameter and having a single response res, a transition  $\sigma(s, \mathcal{S}(op)) =$  $(s', \mathcal{S}(res))$  between two states s and s', of the object takes a set of instances  $\mathcal{S}(op) =$  $\{op_1,\ldots,op_i\}$  of operations as a parameter and returns a set of responses  $\mathcal{S}(res)=$  $\{res_1, \ldots, res_i\}$  where each response corresponds to an instance of an operation from the parameter set. An execution E of a concurrent object is set-linearizable if there exists an equivalent set-sequential execution S that contains all the complete operations of E and possibly some pending operations, and the execution S verifies that if an operation op is before another operation op' in E (i.e. op  $\langle E \rangle$  then op is also before op' in S. Figure 1.2 illustrates the differences between a linearization of an exact FIFO queue and a set-linearization of a relaxed FIFO queue where multiple concurrent mathit Dequeue operations are allowed to return the same element. In Figure 1.2a, the linearization defines a sequential total order of all the operations, while in Figure 1.2b, multiple operations have the same linearization point and are executed concurrently in the set-linearization.

**Definition 1.2.6.** Set-linearizability: Let A be an implementation of a concurrent object  $\mathcal{O}$ . An execution E of A is set-linearizable if there is a set-sequential execution E of E such that E contains every completed operation of E and might contain some pending operations, and the inputs and outputs of the invocations and responses of the operations in E agree with the inputs and outputs in E. Furthermore, if two completed operations op<sub>1</sub> and op<sub>2</sub> in E verify op<sub>1</sub> <E op<sub>2</sub>, then op<sub>1</sub> appears before op<sub>2</sub> in E. We say that an implementation is set-linearizable if all its executions are set-linearizable.

Figure 1.2: Example of a linearization of an execution of a FIFO queue and a setlinearization of an execution of a relaxed FIFO queue.

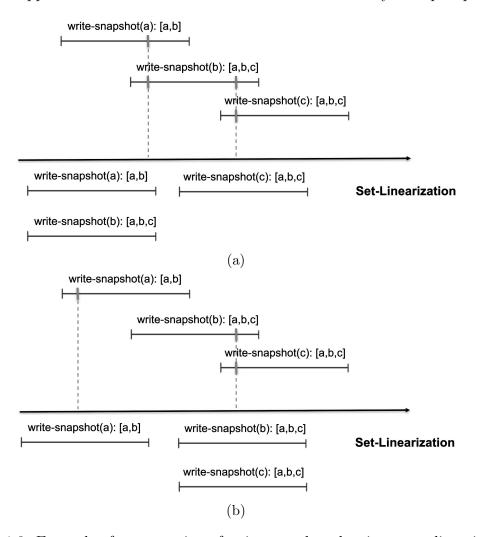

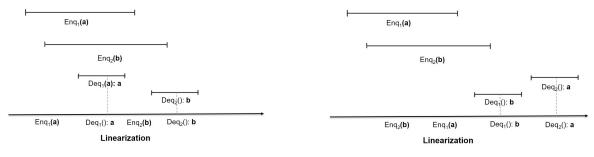

The consistency condition of interval-linearizability is introduced by Castañeda et al. [15] to take into consideration the set of problems in the distributed setting that cannot be represented with a sequential specification of an object. This is the case for the write-snapshot object as observed by Neiger [35]. Differently from the regular snapshot object defined by the two operations Update and Scan, the write-snapshot is defined by a single operation that concatenates the two: when a process invokes the instance write-snapshot(x) to add the value x to the object, the operation returns the state of the object. Neiger notes that it is impossible to represent the write-snapshot using a sequential specification and can only be modeled as a task. The execution in Figure 1.3 illustrates the case where an execution of a write-snapshot is not set-linearizable. No matter where the instance write-snapshot(b) is linearized, the set-linearization obtained has an operation that returns a value that appears to be predicting a future operation.

Hence, the need for a more flexible framework where it is possible to express that an operation happens over an interval of time that can be affected by multiple operations.

Figure 1.3: Example of an execution of write-snapshot that is not set-linearizable.

Formally, in the *interval-sequential specification* of an object, if an operation op is pending in a state q, and the transition  $\sigma$  is applied such that  $\sigma(q, Inv) = (q', Res)$  where Inv is a set of operation invocations and Res is a set of responses; then op might still be pending in q'. Meaning that Res contains the responses of only the operations that are complete in q'.

**Definition 1.2.7.** Interval-linearizability: Let A be an implementation of a concurrent object O. An execution E of A is interval-linearizable if there is an interval-sequential execution S of O such that S contains every completed operation of E and might contain some pending operations, and the inputs and outputs of the invocations and responses of the operations in S agree with the inputs and outputs in E. Furthermore, if two completed operations op<sub>1</sub> and op<sub>2</sub> in E verify op<sub>1</sub>  $<_E$  op<sub>2</sub>, then op<sub>1</sub> appears before op<sub>2</sub> in S.

We say that an implementation is interval-linearizable if all its executions are interval-linearizable.

Other weaker consistency conditions include quasi-linearizability [2], which models legal executions with a distance function from sequential executions. Intermediate value linearizability [39] is defined through linearizability such that a read operation is allowed to return a value that is bounded by two values that are legal under linearizability. And similarly to abstract data type relaxations, some consistency conditions are introduced for specific data structures. For instance local linearizability [20] is defined for container-type data structures like queues and stacks, with a guarantee of a consistent view of the object only at the process level as opposed to regular linearizability which guarantees a consistent view overall (for local-linearizability a projection of the global execution onto a specific process is linearizable).

### 1.2.4 Sequential Specification Relaxations

While considering weaker consistency conditions is one way to implement relaxed shared objects, The second approach that has emerged is the relaxation of the sequential specification of the object.

Henzinger et al. [24] introduced a formal framework for obtaining new data structures by quantitatively relaxing existing ones. Intuitively, the framework defines a distance between sequences of operations such that a sequence that might not be permitted under the sequential specification of the original object, might be allowed for the relaxed version of the object if the sequence is at some distance k from a sequence of operations that is legal. Several authors [43, 31, 38, 45, 41, 42] have used this framework to give different implementations of relaxed data structure types or to study properties of specific relaxations.

The first general relaxation that results from this framework is the Out-of-order relaxation. When applied to an ordered data structured like the queue or stack, this relaxation allows the deleter operation (Dequeue and Pop, respectively), to return an element up to k places out-of-order.

The other generic relaxation presented in [24] is the *stuttering* relaxation. This relaxation allows some update operations to not take effect, meaning that the call to an operation that changes the state of the object "stutters" and does not succeed in modifying the state of the object. For a sequence of operations to be allowed under this relaxation, no more than k consecutive update operations can stutter before an operation succeeds in changing the state of the object.

The k-atomicity relaxation defined in [3], resembles the stuttering relaxation in that it allows read operations to return a "stale" value bounded by the parameter k to limit the number of write operations it can overlook. However, the definition of k-atomicity differs from stuttering in the sense that for the latter, an operation that changes the state of the object might "stutter" and fail to do so, while for the former, the relaxation affects the read operations alone.

Aside from this framework, there have been data type-specific relaxations that are defined with the sequential specification of the object in mind. For instance, Castañeda et al. [14] define a relaxed queue object with *multiplicity*, such that multiple concurrent instances of the *Dequeue* operation are allowed to return the same element in the queue. They also define a relaxation that allows an instance of *Dequeue* to return a special value *weak-empty* when the queue *might* be empty.

#### Relaxation Equivalence

Talmage and Welch show in [43] that in many ways the two approaches of considering weaker consistency conditions and relaxing the object's sequential specification are different ways to specify the same sets of allowed concurrent behaviors of a given shared object. They give in subsequent work [44] equivalent consistency conditions to different abstract data type relaxations, namely k-out-of-order, k-lateness, and k-stuttering. In doing so, they prove that in many cases both relaxing the sequential specification and considering weaker consistency conditions are two equivalent ways to represent the same set of concurrent problems faced when implementing shared data objects. Meaning that it is possible to focus on whichever approach is easier to achieve thanks to this equivalence.

#### 1.3 Related Work and Contributions

In this section, we present the related work to the different problems we investigate in this thesis as well as our contributions. Starting with some lower bounds results justifying the limitations of step complexities of the implementations of the shared objects in the absence of any relaxation of the consistency condition or sequential specification. We then present some relaxations of shared objects with a focus on the objects we are interested in (counter, max register). Finally, we present the general landscape of wait-free FIFO queue implementations.

### 1.3.1 Counter and Max Register

Jayanti, Tan and Toueg [29] show for any deterministic non-blocking n-process implementation I of a shared object in a large set A using a set B of primitives where  $A = \{\text{increment}, \text{ fetch}\&\text{add}, \text{ modulo } \text{k counter (for any } k \geq 2n), \text{ LL/SC bit, k-valued compare}\&\text{swap (for any } k \geq n), \text{ single-writer snapshot} \}$  and  $B = \{\{\text{resettable consensus}\}\}$  (historyless objects such as registers and swap registers), that I has a lower bound for both time and space complexities of n-1. To illustrate the intuition behind this lower bound, take the example of a simple implementation of a counter object for n processes  $p_i$  with  $i \leq n$ . If  $p_n$  executes a Read() operation  $op_n$ , it will need to read a single base object at least to retrieve the value of the counter. However, in the meantime, a different process  $p_l$  could execute an instance of CounterIncrement() to change the value of a base object of the implementation of the counter. This would render the value read by  $p_n$  obsolete and forces it to read another base object. If this scenario occurs for every process  $p_i$  such that  $i \neq n$ , then  $p_n$  will need to read n-1 base objects.

However, this lower bound result does not consider restricted-use objects. And in many cases, there have been implementations of objects that beat the  $\Omega(n)$  lower bound because the executions in the restricted-use context exceed the scope of the proof of the lower bound. For instance, Aspnes, Attiya, and Censor-Hillel [5] show the possibility of implementing exact counting algorithms whose step complexity is sub-linear when the number of operations is bounded. In particular, they presented a wait-free exact counter for which the worst-case step complexities of the *CounterIncrement* and *CounterRead* operations are  $O(min(\log n \log v, n))$  and  $O(min(\log v, n))$ , respectively, where v is the

object's current value. In [5], they also give an implementation of a max register that can write v in  $O(min(\log v, n))$  steps.

For this reason, Aspnes, Censor-Hill, Attiya, and Hendler [7] generalize the lower bound results in [29] to bounded shared objects. More specifically, through this generalization, they propose a new lower bound for both time and space complexities in  $\Omega(min(\log L, n))$  for deterministic implementations from historyless primitives of bounded objects where L is the bound parameter. This lower bound also proved that the m-bounded max register implementation in [5] is optimal.

For shared objects that manipulate numerical values, a natural relaxation might consist of allowing an additive margin of error for the return value of the read operation. This is the case for the k-additive-accurate counter introduced in [5] as a counter for which any CounterRead operation returns a value that is within  $\pm k$  of the number of CounterIncrement operations linearized before it. It is then shown that for any deterministic solo-terminating implementation from atomic registers by n processes of an m-bounded k-additive-accurate counter, there is a CounterRead operation that takes  $min(n-1, \lceil \log m \rceil - \log(\lceil \log m \rceil + k))$  steps. Meaning that allowing the CounterRead operation to have some additive error accounts for the cost of some of the accumulating pending operations. This lower bound is improved in [7], where it is shown that the m-bounded k-additive-accurate counter has a lower bound of  $\Omega(min(\log m - \log k, n))$ .

|                    | Step complexity                    |                                    | Space<br>complexity                  |

|--------------------|------------------------------------|------------------------------------|--------------------------------------|

| max<br>register    | $\Omega(\min(\log m, n))$          | $\Omega(\min(\log m, n))$          | $\Omega(\min(m,n))$                  |

| Counter            | $\Omega(\min(\log m, n))$          | $\Omega(\min(\log m, n))$          | $\Omega(\min(\sqrt{m},n))$           |

| k-additive counter | $\Omega(\min(\log m - \log k, n))$ | $\Omega(\min(\log m - \log k, n))$ | $\Omega(\min(\sqrt{\frac{m}{k}},n))$ |

Figure 1.4: Lower bounds on restricted use objects where m is the maximum value assumed by the object or the bound on the number of operations applied to it, from [7]

The first relaxation we consider is the k-multiplicative-accurate relaxation introduced in [7].

#### Contribution: k-multiplicative-accurate max register

We define the *k-multiplicative-accurate* max register, where the *MaxRead* operation returns an approximate value x' within a k multiplicative range of the maximum value x' written to the register (i.e.  $x'/k \le x' \le k \cdot v'$ ).

we have shown that relaxing the semantics of the bounded max register by allowing inaccuracy of even a constant multiplicative factor yields an exponential improvement in the worst-case step complexity. Then, we present a novel m-bounded k-multiplicative-accurate max register algorithm whose worst-case step complexity matches this lower bound. We then easily "plug-in" our bounded k-multiplicative-accurate max regis-

ter into the construction proposed by Baig et al. [12] to obtain an unbounded k-multiplicative-accurate max register with sub-logarithmic amortized step complexity.

#### Contribution: k-multiplicative-accurate counter

Similarly to the k-multiplicative-accurate max register, reading the of value the k-multiplicative-accurate counter through a call to the operation CounterRead returns an approximation x of the exact value v of the counter by a multiplicative factor of k (i.e.  $v/k < x < k \cdot v$ ).

We implement a wait-free linearizable k-multiplicative-accurate counter for  $k \ge n$  where n is the number of processes, with constant amortized step complexity for executions of arbitrary length. We also give an implementation of the m-bounded variant of the k-multiplicative-accurate counter for  $k \ge \sqrt{n}$  with a worst-case step complexity in  $O(min(\log(\log(m+1)), n))$ .

Then, by extension of the lower bound of Attiya and Hendler, [10], we prove that any implementation of a k-multiplicative-accurate counter from read/write and conditional primitive operations has amortized step complexity of  $\Omega(\log(n/k^2))$ , for  $k \leq \sqrt{n/2}$ . Our results together with the upper and lower bound on exact counting proved in [12] show that when the approximation parameter k does not depend on n, relaxing the counter semantics by allowing a multiplicative error cannot asymptotically reduce the amortized step complexity by more than a logarithmic factor.

We also show a lower bound for unbounded k-multiplicative-accurate counters for the worst-case step complexity in  $\Omega(n)$ . Meaning that the linear lower bound by Jayanti, Tan, and Toueg [29] for exact counters also holds in the case of the k-multiplicative-accurate counters.

## 1.3.2 FIFO Queue

There have been results showing the difficulties of implementing a linearizable wait-free queue because of the "tail chasing" problem. Roughly speaking, the "tail chasing" scenario occurs when a process is trying to retrieve an element from the queue but finds itself unable to return because it is invisible to other processes that keep modifying the state of the queue indefinitely by executing operation sequences that contain element insertions followed by dequeuing elements from the queue.

The difficulty to implement the queue in a wait-free manner is formalized by Attiya, Castañeda, and Hendler [8]. They categorize helping mechanisms into trivial and non-trivial helping. This distinction relies on the definition of  $operation\ valency$  introduced in [22] to describe the possible return values an operation can have. Roughly speaking, an implementation has helping if a process makes another process decide on a return value by executing a specific mechanism. In the case of queues, stacks, and similar data structures, the helping is nontrivial, if the non-decided process is made to return a value different than  $\epsilon$  (the empty state of the object). This often requires delicate communication between the processes to ensure that a value reserved for a specific undecided process is not taken by a process unaware of the helping taking place. The main result from [8] is the distinction between stack and queue implementations: A wait-free queue implementation requires nontrivial helping while a stack can be implemented in a wait-free manner without nontrivial helping [1].

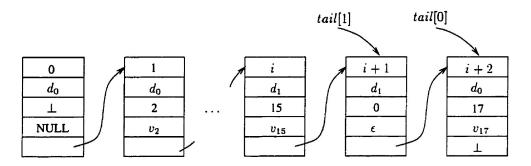

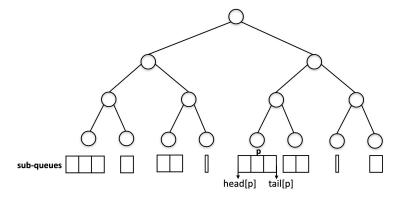

An example of such a helping mechanism is used by Li [33] to implement a waitfree multiple enqueuer 2 dequeuer queue. In this implementation, each instance of the Dequeue operation is represented by a node in a linked list denoted DeqCell. The position of an instance in the list is dictated by a sequence number that defines a total order for the Dequeue operations. In addition to the sequence number of the operation and the id of the process invoking the operation (i.e.  $d_0$  or  $d_1$ ), a node in DeqCell also stores both the index and the value of the element returned by the operation (Figure 1.5).

Figure 1.5: The linked list data structure storing instances of the *Dequeue* operation, from [33].

The Dequeue operation uses a 2-process consensus object to communicate between the two dequeuer processes. They are used to propose the index of the instance of Dequeue that needs to be executed first as well as to agree on its return value. When a process executes an instance of Dequeue, it creates a node in DeqCell with a new sequence number. Then, it verifies that there is no pending Dequeue operation from the other dequeuer process. If there is, the process proposes the index of the pending operation, otherwise, it proposes the index of its own operation. After a response is received from the consensus object, the process executes the corresponding Dequeue operation. By the end of this execution, the process verifies if its own Dequeue operation has been assigned a return value, and returns if it is the case. Otherwise, it repeats the same steps previously executed to help the pending operation, but for the node in DeqCell it created.

A characteristic of the queue implementation by Li [33] is that it only uses primitives with consensus level 2. In fact, it attempts to answer the open question of whether the queue object belongs into *Common2* and is implementable with consensus 2 level primitives only. There exist other implementations based on registers and Common2 objects [17, 16]. However, all these implementations rely on concurrency conditions that limit the number of either enqueuer (e.g. [17, 16]) or dequeuer (e.g. [33]) processes.

Even when considering strong primitives like the CAS primitive, it is often necessary to compromise between the concurrency constraints and the complexity of the wait-free queue implementations.

Using Compare&Swap, some practical wait-free queue implementations that support multiple enqueuers and multiple dequeuers have been proposed [32, 34, 46, 19]. Some of these implementations are wait-free [32, 46, 19]; while some are only lock-free [34]. All these solutions have been evaluated empirically and do not have formal complexity analysis. Nonetheless, the worst-case step complexity of either the Enqueue or

of the *Dequeue* operation is not sublinear.

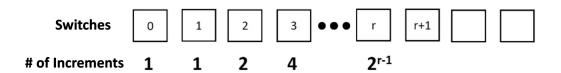

The best-known upper bound for the worst-case step complexity of wait-free queue implementations is given by Khanchandani and Wattenhofer [30]. They present an algorithm in which both the *Enqueue* and *Dequeue* operations take  $O(\sqrt{n})$  steps and require O(nm) registers of  $O(max(\log n, \log m))$  bits, where n is the number of processes and m is the bound on the number of *Enqueue* operations. The previous upper bound prior to their work was in O(n) and relied only on the strong primitive CAS.

Inspired by the algorithm proposed by Ellen et al. [18] to solve the consensus for infinitely many processes in O(1) by combining the functionalities of weak primitives, Khanchandani et al. aimed to show through their implementation, that it is possible to improve the complexity of a shared object implementation by using a combination of strong and weak primitives. For that reason, they introduce the register TH: a new data type that takes two operations half-increment and half-max. This register is composed of two components, i.e. (t,h). A call to half-increment() increments the value of t as long as  $t \leq h$ , and a call to half-max(t) writes the maximum between t and the previous value of t, to t. It is shown that the two operations half-max and half-increment have a consensus number of 1 and 2 respectively. Register TH is used to represent the head and tail of the queue.

In addition to the register TH, they use an array to store the queue elements as well as the data structure counting set they introduce to manage possible concurrency between Enqueue and Dequeue operations. More specifically, the counting set takes the two operations insert() and remove(). An instance insert(x) adds the element x into the set and returns the number of total inserts completed (i.e. it also counts apart from inserting the elements). The call to remove(i) will remove the i-th inserted element to set if and only if this insert was the last one executed by the corresponding process. For the queue implementation, the counting set is needed when there is a call to a Dequeue operation that is concurrent with a pending Enqueue operation which has yet to insert an element into the array.

The counting set has two main functions. First, it defines a global order for all Enqueue operations. An instance of Enqueue(x) invokes insert(x) on the counting set and retrieves the index it uses to insert the element into the array. The second purpose of the counting set consists of ensuring that a fast Dequeue instance that reaches an index of the array that has not been filled yet by a pending Enqueue, is capable of executing a call to remove(i) on the counting set to retrieve the element and return, guaranteeing the wait-freedom of the implementation.

The main difficulty in implementing the counting set object resides in transforming a local value of the counter of Enqueue operations of a single process, into a global index defined for all processes. A log system is used to store information regarding every Enqueue operation in order to compute global indexes. The sublinear complexity is obtained through an optimization of the log by limiting the concurrency during write operations to  $\sqrt{n}$  processes instead of all n processes. Therefore, it seems that this approach of using the counting set is limited by this complexity and may not be easily transferable to implement other shared objects or to investigate logarithmic complexity queue implementations.

To the best of our knowledge, all other wait-free queue implementations with sublinear worst-case step complexity in the literature rely on limiting the number of processes allowed to execute either *Enqueue* of *Dequeue* operations (e.g. [28, 16, 33, 17]). Jayanti

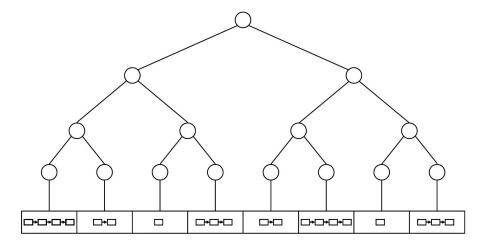

and Petrovic [28], for instance, give an implementation of a queue that supports a single dequeuer process and any number of enqueuers. Their implementation has a worst-case step complexity of  $O(\log n)$  for both Enqueue and Dequeue operations, where n is the number of processes.

#### Contribution: FIFO queue

In this thesis, we were interested in the open question of whether it is possible to have a wait-free queue implementation in logarithmic worst-case step complexity with no concurrency constraints. In particular, we proposed a wait-free FIFO queue implementation that supports n enqueuers and k dequeuers where the worst-case step complexity of an Enqueue operation is in  $O(\log n)$  and of a Dequeue operation is in  $O(k \log n)$ . But then, by considering a relaxation of the FIFO queue where multiple concurrent Dequeue operations are allowed to return the same element, we have shown that it is possible to implement a wait-free FIFO queue with no concurrency constraints in logarithmic step complexity.

We have also investigated the possibility of implementing an exact wait-free FIFO queue using only objects of consensus number 2. As a preliminary approach to solving the question, we limited the execution to 2 processes and presented a wait-free implementation of the FIFO queue based on such objects without relying on universal constructions or on the consensus object which cannot be used to generalize the implementation to more processes without losing the property of having a consensus number 2.

## 1.4 Organization

The thesis is structured as follows. First, we present in Chapter 2 the implementations of both the counter and max register objects under the relaxed semantics of k-multiplicativity. We investigate different variants of these implementations under the properties of wait-freedom and linearizability. Specifically, we present both an unbounded and bounded approximate k-multiplicative-accurate counter and max register implementations. We then present different lower bounds results for these objects: mainly we prove a lower bound on the amortized step complexity for the unbounded k-multiplicative-accurate counter by extension of a lower bound by Attiya and Hendler [10]. Additionally, we give a lower bound for the worst-case step complexity of the m-bounded k-multiplicative-accurate max register and counter objects.

Then, in Chapter 3, we present a wait-free linearizable FIFO queue implementation for n-enqueuer and k-dequeuer processes with a worst-case step complexity of  $O(\log n)$  for the Enqueue operation and  $O(k \log n)$  for the Dequeue operation. Then, we consider the relaxed semantics of the FIFO queue introduced in [14] where multiple concurrent Dequeue operations are allowed to return the same element, denoted multiplicity. We give an implementation of set-linearizable FIFO queue with multiplicity where both the Enqueue and Dequeue operations are in  $O(\log n)$ .

Finally, in Chapter 4 we offer some overall insights on the work in retrospect while discussing possible leads and prospects for future work.

# Chapter 2

# K-multiplicative-accurate Counter and Max Register

#### Abstract

Relaxing the sequential specification of shared objects has been proposed as a promising approach to obtain implementations of shared objects with better complexities.

By considering the case study of two common shared objects: max register and counter, we study the possible improvement in step complexity of their relaxed implementations compared to implementations of the corresponding exact objects. In particular, in the classical shared memory model, we investigate the extent to which allowing wait-free linearizable implementations of these objects to return approximate values, rather than accurate ones, may improve their step complexity.

We consider the k-multiplicative-accurate max register and the k-multiplicative-accurate counter, where read operations are allowed to return an approximate value within a multiplicative factor k of the accurate value (for some  $k \in \mathbb{N}$ ). More specifically, reads are allowed to return an approximate value x of the maximum value v previously written to the max register, or of the number v of increments previously applied to the counter, respectively, such that  $v/k \leq x \leq v \cdot k$ . We provide upper and lower bounds on the complexity of implementing these objects in a wait-free manner in the shared memory model.

We give an implementation of the k-multiplicative-accurate counter that has an exponentially better amortized step complexity than the best implementation of the exact counter in the state of the art when the approximation parameter  $k \geq n$ .

We also implement the k-multiplicative-accurate max register with an exponentially better worst-case step complexity compared to the exact max register implementation.

We give lower bounds on the worst-case step complexity of the bounded variant of both the relaxed counter and max register, as well as a lower bound on the amortized step complexity of the unbounded counter.

An earlier version of this work containing the lower bound results was presented during the 41st IEEE International Conference on Distributed Computing Systems (ICDCS 2021) [23].

### 2.1 Introduction

With the ubiquitousness of multi-core and multi-processor systems, there is a growing need to gain a better understanding of how to implement concurrent objects with improved complexity, while maintaining the natural correctness guarantee provided to programmers by linearizability. Relaxing the sequential specification of linearizable concurrent objects is one promising approach to achieving this [2, 24]. An object's sequential specification defines its correct behavior in sequential executions. Roughly speaking, linearizability [26] guarantees that any concurrent execution is equivalent to a sequential one.

There is empirical evidence that relaxing the sequential specification of some common objects, e.g. queues and counters, yields improved performance of linearizable implementations, e.g [24, 40]. However, the theoretical principles to implement concurrent objects more efficiently by relaxing their sequential specification are not yet clear.

We study relaxed-semantics variants of two well-known concurrent objects – counters and max registers, in the classical shared memory model. In particular, we investigate the extent to which allowing wait-free linearizable implementations of these objects to return approximate values, rather than accurate ones, may improve their step complexity.

A counter is a linearizable object that supports a CounterIncrement operation and a CounterRead operation. The sequential specification of a counter requires that a CounterRead operation returns the number of CounterIncrement operations that precede it. A relaxed variant of the counter is the k-multiplicative-accurate counter, defined by Aspnes, Censor-Hill, Attiya, and Hendler in [7], where a CounterRead operation returns an approximate value x of the number v of CounterIncrement operations that precede it, such that  $v/k \le x \le v \cdot k$  for some parameter k > 0.

A max register r supports a Write(v) operation that writes a non-negative integer v to r and a Read operation that returns the maximum value previously written to r, [7]. We define the k-multiplicative-accurate max register by allowing a Read operation to return an approximate value x of the largest value v written before it, such that  $v/k \le x \le v \cdot k$  for some parameter k > 0.

#### k-multiplicative-accurate counter

To the best of our knowledge, we present the first deterministic approximate counter with constant amortized complexity. More precisely, we present a wait-free linearizable k-multiplicative-accurate counter for  $k \geq n$  where n is the number of processes, with constant amortized step complexity for executions of arbitrary length. Then, by extension of the lower bound of Attiya and Hendler, [10], we prove that any n-process solo-terminating implementation of a k-multiplicative-accurate counter from read/write and conditional primitive operations (including k-word compare-and-swap) has amortized step complexity of  $\Omega(\log(n/k^2))$ , for  $k \leq \sqrt{n/2}$ . Our results together with the upper and lower bound on exact counting provided by Baig et al. in [12], show that when the approximation parameter k does not depend on n, relaxing the counter semantics by allowing a multiplicative error cannot asymptotically reduce the amortized step complexity by more than a logarithmic factor. Table 2.1a compares the amortized

| Unbounded                 | Lower bound                      | Upper bound                     |

|---------------------------|----------------------------------|---------------------------------|

| (Amortized complexity)    | Lower Bound                      |                                 |

| Exact Counter             | $\Omega(\log n)$ [12]            | $O(\log^2 n) \ [12]$            |

| k-multiplicative-accurate | $\Omega(\log n/k^2)$             | O(1)                            |

| Counter                   | $k \le \sqrt{n/2}$ (Section 2.7) | $k \ge n \text{ (Section 2.2)}$ |

(a) Unbounded counter results.

| Bounded (Worst-case complexity) | Lower bound                      | Upper bound                                                         |

|---------------------------------|----------------------------------|---------------------------------------------------------------------|

| Exact Counter                   | $\Omega(\min(\log m, n))$ [5]    | $O(min(\log n \log m, n))$ for Inc $O(min(\log m, n))$ for Read [5] |

| k-multiplicative-accurate       | $\Omega(min(\log(\log_k m), n))$ | $O(min(\log(\log(m+1)), n))$                                        |

| Counter                         | (Section 2.6)                    | $k \ge \sqrt{n+1}$ (Section 2.3)                                    |

(b) Bounded counter results.

Table 2.1: k-multiplicative-accurate counter implementations and lower bounds results (n is the number of processes and m is the bound on the object).

complexity of the implementation of our unbounded k-multiplicative-accurate counter and the lower bound result to the results from [12].

Then, we consider the bounded version of the k-multiplicative accurate counter. More precisely, we give a wait-free linearizable m-bounded k-multiplicative-accurate counter for  $k \geq \sqrt{n+1}$  where n is the number of processes and m is the bound on the number of CounterIncrement operation instances that can be performed on the counter. The implementation has a worst-case step complexity of  $O(min(\log(\log(m+1)), n))$ . We also prove that a lower bound on the worst-case step complexity of obstruction-free implementations of m-bounded k-multiplicative-accurate counters from historyless primitives in  $\Omega(\min(n, \log_2 \log_k m))$ . Meaning that our implementation of the m-bounded k-multiplicative-accurate counter is optimal. This also implies that for unbounded k-multiplicative-accurate counters, the worst-case step complexity is in  $\Omega(n)$ , and we fall back to the linear lower bound by Jayanti, Tan and Toueg [29]. Table 2.1b summarizes the results for the bounded approximate counter and compares them to upper and lower bound results for the exact bounded counter from Aspnes, Attiva and Censor-Hillel [5].

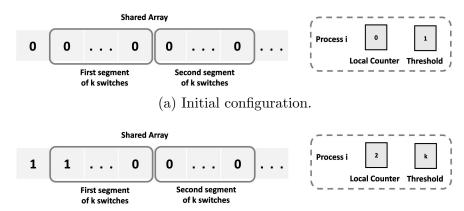

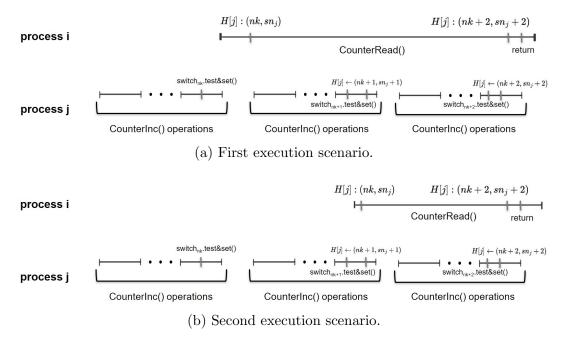

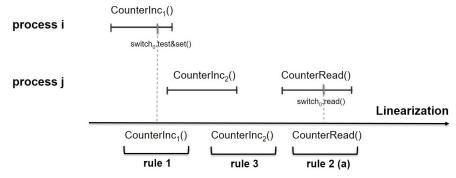

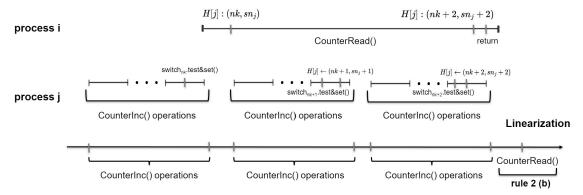

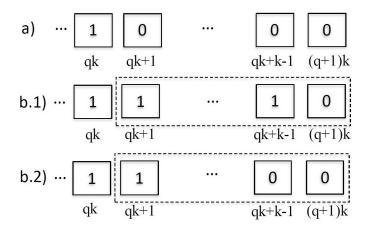

#### k-multiplicative-accurate max register