# Programming and analysis of critical real-time systems Julien Forget

# ▶ To cite this version:

Julien Forget. Programming and analysis of critical real-time systems. Embedded Systems. Université de Lille, 2023. tel-04148643

# HAL Id: tel-04148643 https://theses.hal.science/tel-04148643

Submitted on 3 Jul 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Mémoire d'Habilitation à Diriger des Recherches

Préparé au sein de *l'Université de Lille* Spécialité *Informatique*

Présenté et soutenu par

Julien Forget

Le Lundi 12 Juin 2023

Programming and analysis of critical real-time systems

# Devant le jury composé de :

Sebastian Altmeyer Examinateur Alan Burns Rapporteur Laure Gonnord Examinatrice Giuseppe Lipari Garant

Christine Rochange Rapportrice

Marc Pouzet Président

École doctorale MADIS

# Acknowledgements

I would first like to thank Alan Burns, Marc Pouzet, and Christine Rochange, for reviewing my manuscript. I learnt a lot from their work, I hope they learnt a few things in return reading this document. Many thanks to Sebastian Altmeyer for making the trip from Germany and for our stimulating discussions. My gratitude to Laure Gonnord for her comeback to the source, as well as for her guidance in dire times.

This work would not exist without my collaborators. Frédéric Boniol and Claire Pagetti kindly guided my first steps as a researcher. Emmanuel Grolleau and Pascal Richard helped me unravel the inner workings of the real-time community. Ph.D. students and post-docs have been the main drive for my research activities: many thanks to Antoine Bertout, Andrei Florea, Frédéric Fort, Sandro Grebant, Jordy Ruiz and Rémy Wyss. Our trio with Clément Ballabriga and Giuseppe Lipari was the most stimulating research environment I could have hopped for. A warm thank you to my colleagues from SyCoMoRES, SEAS, and Polytech, for countless scientific and non-scientific discussions, and for being such uniformly caring persons.

To my family, my southwestern second family, my mexican-connection, my adoptive northern family: I am so grateful that you are part of my life.

# **Contents**

| Co | onten | its                                                  |                                                               | iii |  |  |  |  |  |  |  |

|----|-------|------------------------------------------------------|---------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 1  | Ove   | rview                                                |                                                               | 1   |  |  |  |  |  |  |  |

|    | 1.1   | Conte                                                | xt                                                            | 1   |  |  |  |  |  |  |  |

|    | 1.2   | Contributions                                        |                                                               |     |  |  |  |  |  |  |  |

|    |       | 1.2.1                                                | Programming with Prelude                                      | 2   |  |  |  |  |  |  |  |

|    |       | 1.2.2                                                | High-level timing analysis                                    | 3   |  |  |  |  |  |  |  |

|    |       | 1.2.3                                                | Low-level timing analysis                                     | 4   |  |  |  |  |  |  |  |

|    | 1.3   | Readir                                               | ng this document                                              | 4   |  |  |  |  |  |  |  |

| I  | lnt   | troduc                                               | tion                                                          | 7   |  |  |  |  |  |  |  |

| 2  | Bac   | kgroun                                               | d on real-time systems                                        | 9   |  |  |  |  |  |  |  |

|    | 2.1   | Prelud                                               | e, a synchronous data-flow language with real-time primitives | 9   |  |  |  |  |  |  |  |

|    |       | 2.1.1                                                | Informal presentation                                         | 9   |  |  |  |  |  |  |  |

|    |       | 2.1.2                                                | Formal semantics                                              | 13  |  |  |  |  |  |  |  |

|    |       | 2.1.3                                                | Compilation overview                                          | 15  |  |  |  |  |  |  |  |

|    | 2.2   | 2 High-level timing analysis of a real-time task set |                                                               |     |  |  |  |  |  |  |  |

|    |       | 2.2.1                                                | Real-time attributes                                          | 16  |  |  |  |  |  |  |  |

|    |       | 2.2.2                                                | Precedence constraints                                        | 16  |  |  |  |  |  |  |  |

|    |       | 2.2.3                                                | Scheduling                                                    | 18  |  |  |  |  |  |  |  |

|    | 2.3   | Low-le                                               | evel timing analysis of a single task                         | 19  |  |  |  |  |  |  |  |

|    |       | 2.3.1                                                | Control-flow analysis                                         | 19  |  |  |  |  |  |  |  |

|    |       | 2.3.2                                                | Hardware analysis                                             | 20  |  |  |  |  |  |  |  |

|    |       | 2.3.3                                                | Value analysis                                                | 21  |  |  |  |  |  |  |  |

|    |       | 2.3.4                                                | WCET bound computation                                        | 21  |  |  |  |  |  |  |  |

| II | Co    | ntribu                                               | itions                                                        | 23  |  |  |  |  |  |  |  |

| 3  | Pro   | gramm                                                | ing real-time systems with Prelude                            | 25  |  |  |  |  |  |  |  |

|    | 3.1   |                                                      | nentation on multi-core with distributed memory               | 25  |  |  |  |  |  |  |  |

|    |       | 3.1.1                                                | Motivation                                                    | 26  |  |  |  |  |  |  |  |

|    |       | 3.1.2                                                | Model                                                         | 26  |  |  |  |  |  |  |  |

|    |       | 3.1.3                                                | Code generation                                               | 27  |  |  |  |  |  |  |  |

|    |       | 3.1.4                                                | Comparing memory architectures                                | 29  |  |  |  |  |  |  |  |

|    |       | 3.1.5                                                | Related works                                                 | 31  |  |  |  |  |  |  |  |

|    |       | 3.1.6                                                | Conclusion                                                    | 32  |  |  |  |  |  |  |  |

|    | 3.2   | Partial                                              | delays specification                                          | 32  |  |  |  |  |  |  |  |

# **CONTENTS**

|   |     | 3.2.1    | Motivating example                                    |

|---|-----|----------|-------------------------------------------------------|

|   |     | 3.2.2    | Incomplete program specification                      |

|   |     | 3.2.3    | Program concretisation                                |

|   |     | 3.2.4    | Related works                                         |

|   |     | 3.2.5    | Conclusion                                            |

|   | 3.3 |          | mode multi-periodic systems                           |

|   |     | 3.3.1    | Motivating example                                    |

|   |     | 3.3.2    | Language extension                                    |

|   |     | 3.3.3    | Clock calculus                                        |

|   |     | 3.3.4    | Evaluation                                            |

|   |     | 3.3.5    | Related works                                         |

|   |     | 3.3.6    | Conclusion                                            |

|   |     | 3.3.0    | Conclusion                                            |

| 4 | Hig | h-level  | timing analysis 47                                    |

|   | 4.1 | Real-ti  | me scheduling                                         |

|   |     | 4.1.1    | Scheduling tasks with simple precedence constraints   |

|   |     | 4.1.2    | Scheduling tasks with extended precedence constraints |

|   |     | 4.1.3    | Conclusion                                            |

|   | 4.2 | End-to   | end constraints analysis                              |

|   |     | 4.2.1    | Motivating example                                    |

|   |     | 4.2.2    | End-to-end properties definition                      |

|   |     | 4.2.3    | End-to-end properties verification                    |

|   |     | 4.2.4    | Related works                                         |

|   |     | 4.2.5    | Conclusion                                            |

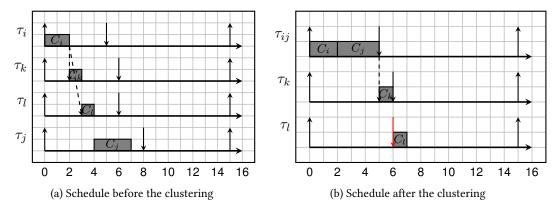

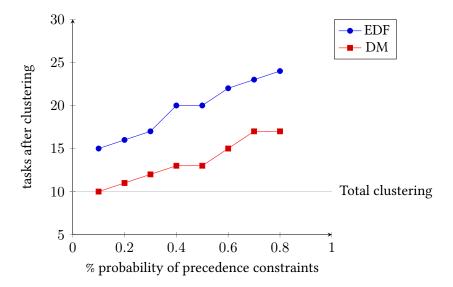

|   | 4.3 | Task c   | lustering                                             |

|   |     | 4.3.1    | Problem definition                                    |

|   |     | 4.3.2    | Guiding principles                                    |

|   |     | 4.3.3    | Independent tasks, uniprocessor                       |

|   |     | 4.3.4    | Dependent tasks, uniprocessor                         |

|   |     | 4.3.5    | Dependent tasks, multiprocessor                       |

|   |     | 4.3.6    | Related works                                         |

|   |     | 4.3.7    | Conclusion                                            |

|   |     | 1.017    | 001101111111111111111111111111111111111               |

| 5 | Low | -level t | timing analysis 71                                    |

|   | 5.1 | Symbo    | olic Worst-Case Execution Time analysis               |

|   |     | 5.1.1    | Control Flow Tree                                     |

|   |     | 5.1.2    | Context-sensitive execution time                      |

|   |     | 5.1.3    | Symbolic computation                                  |

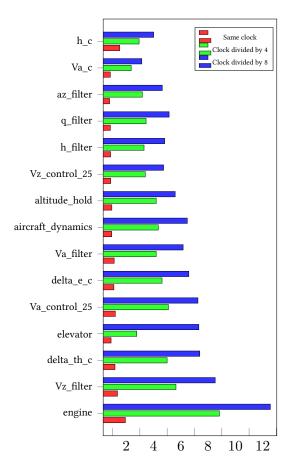

|   |     | 5.1.4    | Experiments                                           |

|   |     | 5.1.5    | Related works                                         |

|   |     | 5.1.6    | Conclusion                                            |

|   | 5.2 | Relatio  | onal abstract interpretation of assembly code         |

|   |     | 5.2.1    | Motivating example                                    |

|   |     | 5.2.2    | Target language                                       |

|   |     | 5.2.3    | The POLYMAP domain                                    |

|   |     | 5.2.4    | Abstract interpretation                               |

|   |     | 525      | Evneriments 80                                        |

# CONTENTS

| 5.2.6 Related works                                    | . 90  |

|--------------------------------------------------------|-------|

| 5.2.7 Conclusion                                       | . 90  |

| III. Dawana atiwas                                     | 02    |

| III Perspectives                                       | 93    |

| 6 Conclusion                                           | 95    |

| 6.1 Summary                                            | . 95  |

| 6.2 Future research projects                           | . 95  |

| 6.2.1 Modular WCET analysis (short term)               | . 95  |

| 6.2.2 Synthesis of Prelude programs (medium term)      | . 96  |

| 6.2.3 Formally verified real-time programs (long term) | . 97  |

|                                                        |       |

| IV Appendices                                          | 99    |

| A Main symbols and acronyms                            | 101   |

| Programming with Prelude                               | . 101 |

| High-level timing analysis                             | . 101 |

| Low-level timing analysis                              |       |

| Bibliography                                           | 105   |

# 1. Overview

This document summarizes my research since my appointment as an associate professor in 2010 at the University of Lille. Since then, I have been doing my research in the CRIStAL laboratory (Centre de Recherche en Informatique, Signal et Automatique de Lille), and I have been teaching at the Polytech Lille engineer school. I was a member of the following research teams, chronologically:

- 1. The DaRT team (until 2011), whose focus was on high performance systems on chip;

- 2. The Émeraude team (until 2021), whose focus was on software systems embedded on heterogeneous hardware platforms;

- 3. The SyCoMoRES team (since 2021), whose focus is on modular analysis and development of real-time systems.

My research as an associate professor concerns the development of real-time systems. I focused on three main topics in this context. First, I studied programming languages dedicated to the development of critical real-time systems, and their compilation. Second, I studied high-level timing analysis of real-time systems modeled as a set of concurrent tasks. Third, I studied low-level timing analysis of the code of a single real-time task. Work presented in this document is the result of my collaborations with several colleagues from CRIStAL, Onera Toulouse, the University of Lyon, and the University of Poitiers.

## 1.1. Context

Real-time systems are computer systems that are required not only to produce the correct output values, as a reaction to the system inputs, but also to produce these values at the correct time. We can distinguish two subclasses of real-time systems: hard real-time systems, where failing to respect some constraints may have catastrophic consequences, and soft real-time systems, where failures only cause a degradation in the quality-of-service of the system. In my work, I focus on hard real-time systems. The flight-control system of an airplane, or the autonomous driving system of a car, are good examples of hard real-time systems.

Real-time systems are a sub-class of *reactive systems*, their behaviour consists in indefinitely repeating the following sequence: wait for inputs from sensors, compute a reaction, send outputs to actuators. At the highest level of abstraction, a real-time system can be represented as a set of concurrent tasks, where each task either senses, computes, or actuates.

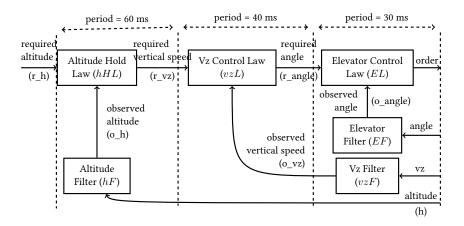

Each task is subject to real-time constraints. *Periodicity constraints* dictate the rate at which tasks must be repeated. *Deadline constraints* are usually derived from periodicity constraints and define the latest date at which each repetition of a task, also called a *job*, must complete. Real-time constraints typically stem from the physical characteristics of the device under control. The rate at which a device must be controlled is upper-bounded by the maximum rate at which the sensors and actuators of the system can operate (e.g. the maximum samples per second of

a LIDAR). It is lower-bounded by the minimum rate required by the control/command laws of the system (e.g. the minimum rate to ensure the stability of an airplane). Since different sensors and actuators have different capabilities, and since the control/command of a system is usually structured as a collaboration of several laws, different tasks of the systems are subject to different real-time constraints. Choosing the actual task rates amounts to a compromise between the quality of the control/command laws and the overall computation demand. Once real-time constraints are set, reacting faster than these constraints usually does not improve the quality of the system. Instead, the main focus of hard real-time systems development is to ensure that the constraints will always be met, so as to ensure the system safety.

# 1.2. Contributions

The programming of hard real-time systems involves several research domains, which are traditionally studied by separate research communities. An important part of my work focuses on the connection between these domains, through the development of the Prelude language and its compiler. This section outlines my contributions and the three main domains they cover.

# 1.2.1. Programming with Prelude

Because real-time systems are critical, development based on formal methods has become popular in this domain. Formal models (e.g. timed-automata [AD94], timed-petri nets [Wan12], or synchronous programs [Ben+03]), provide unambiguous specifications of the system behaviour and enable to mathematically prove safety and security properties for it. Formally defined compilation chains (e.g. synchronous languages compilers [Hal+91; Bou+17]), automate the translation from a high-level formal model to lower-level code, and preserve the semantics of the formal model in the corresponding low-level code. This ensures that the properties proved on the model are still valid in the generated low-level code.

Synchronous languages [Ben+03] have proved successful for the development of critical embedded systems. Their structure is particularly well-adapted to the specification of reactive systems. Their formally defined semantics and compilers improve the system safety and security. However, they traditionally lack primitives to specify real-time constraints. Prelude is a synchronous language dedicated to the programming of real-time systems, which was designed during my Ph.D. thesis. It extends synchronous data-flow languages, such as Lustre [Hal+91], with language constructs to specify real-time constraints. Its compiler generates multi-threaded C code, to be executed by a real-time operating system. This document presents several extensions to my initial work on Prelude. They are summarized below.

**Implementation on multi-core with distributed memory** The Prelude compiler initially generated code for a mono-core hardware platform with the MarteOS operating system [RH01]. It has since then been extended to support several different types of hardware platforms and operating systems. In particular, during the internship of Frédéric Fort, the Prelude compiler was extended to generate code for a multi-core hardware with distributed memory (a larger central memory, along with smaller scratchpad memories for each core), with the Erika real-time operating system<sup>1</sup>.

<sup>1</sup>http://erika.tuxfamily.org/drupal/

**Partial delays specification** In collaboration with colleagues from Onera Toulouse (Frédéric Boniol, Claire Pagetti, Rémy Wyss), the Prelude language was extended to support incomplete specifications. A new operator was introduced to enable to specify communications with flexible non-deterministic communication semantics (either synchronized or not). The compiler then chooses among several possible deterministic implementations, its objective being to satisfy end-to-end latency constraints.

**Multi-mode multi-periodic systems** In the Ph.D. of Frédéric Fort, we extended Prelude to support the programming of multi-mode real-time systems. In such a system, each mode corresponds to a different behaviour, to a different set of computation tasks, with different real-time constraints. The Prelude language and its clock calculus have been extended to support mode automata where tasks of the same mode can have different periodicity constraints.

# 1.2.2. High-level timing analysis

The Prelude compiler translates the input program into a C program structured as a set of concurrent real-time tasks. In order to ensure that the task set will always respect its real-time constraints at run-time, a timing analysis must be performed. This consists of several sub-analyses applied at different abstraction levels. *High-level timing analysis* considers a system modeled as a set of concurrent tasks, where each task is characterized solely by its real-time characteristics. *Low-level timing analysis* focuses on the code executed by one task and mostly abstracts from other tasks. The following contributions to high-level timing analysis are presented in this document.

**Real-time scheduling** Real-time scheduling considers a set of tasks characterized by their periods, deadlines, and worst-case execution time, and ensures that all tasks will meet their deadlines during execution. In collaboration with colleagues from the University of Poitiers (Emmanuel Grolleau, Pascal Richard) and from Onera Toulouse (Frédéric Boniol, Claire Pagetti), we studied the scheduling of dependent tasks, that is to say tasks related by precedence constraints, as it is the case for task sets generated by the Prelude compiler.

**End-to-end constraints analysis** While periodicity and deadline constraints are per-task constraints, end-to-end constraints involve a chain of tasks. For instance, an end-to-end latency constraint imposes an upper-bound to the total delay from the start time of the first task of the chain to the completion time of the last task of the chain. In collaboration with colleagues from Onera Toulouse (Frédéric Boniol, Claire Pagetti, Rémy Wyss), we proposed a general framework for the analysis of such properties.

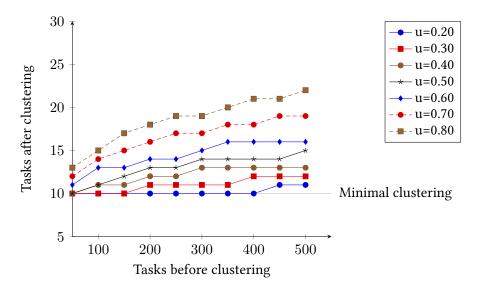

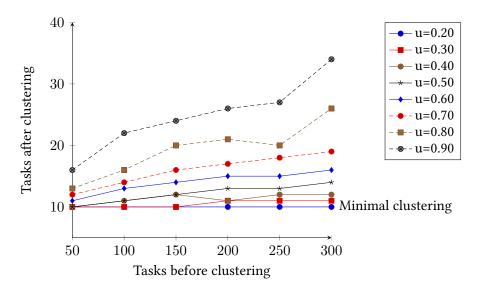

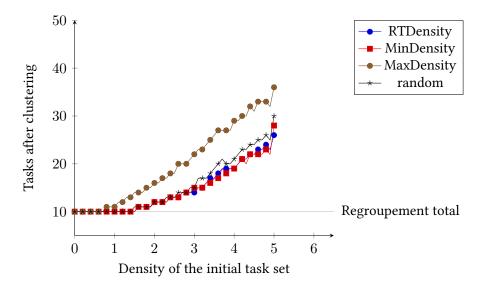

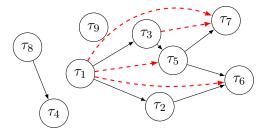

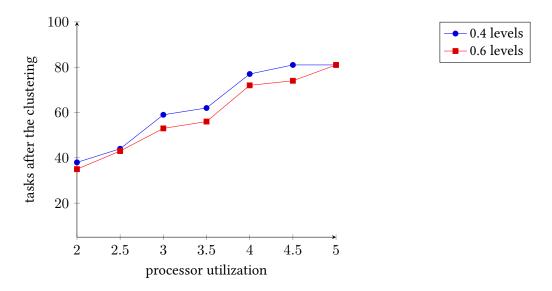

**Task clustering** In a Prelude program, each functionality of the system is implemented as a *node*. The Prelude compiler then translates each node into a separate real-time task. However, for complex industrial systems, mapping each functionality to a different task would produce a large number of tasks, incurring a significant time and memory overhead. In the Ph.D. thesis of Antoine Bertout, we studied the *task clustering* problem, where the objective is to reduce the number of real-time tasks used in the node-to-task mapping, while preserving schedulability.

# 1.2.3. Low-level timing analysis

High-level timing analysis requires as input the Worst-Case Execution Time (WCET) of each task. This information is provided by a low-level timing analysis, which considers the code executed by a single task in order to determine its WCET. WCET analysis is most often performed by static analysis of the task code. Due to the difficulty of the considered problem, WCET computation by static analysis makes simplifications that yield an over-approximated, yet safe, value. Even though the higher-level of abstraction of source code would simplify WCET analysis, compiler optimizations have a huge impact on WCET, and this impact is hard to predict, thus binary code is usually analysed instead. The following contributions to low-level timing analysis are presented in this document.

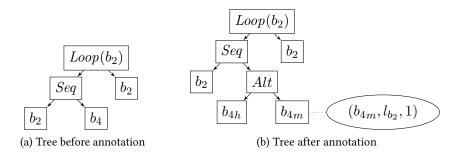

**Symbolic WCET computation** Traditional WCET analysis produces a constant numeric upper-bound to the WCET. Thus, if some parameters of the program change (e.g program inputs, loop bounds, cache size, ...), the analysis must be re-run. An alternative approach is to produce a parametric WCET formula. In collaboration with colleagues from the CRIStAL laboratory (Clément Ballabriga, Giuseppe Lipari), we proposed a new approach to parametric WCET analysis based on symbolic computation. The original motivation of this work was to enable the design of adaptive real-time systems in Prelude: we compute off-line a WCET formula, instantiate the formula on-line, and adapt the system behaviour if the WCET reaches a certain threshold. Such an adaptive behaviour can be specified using the multi-mode extensions of Frédéric Fort.

Relational abstract interpretation of assembly code Abstract interpretation is a static analysis technique that provides a sound over-approximation of the possible behaviours of a program. Relational abstract interpretation establishes relations (e.g. linear relations) between variables of the program under analysis. Abstract interpretation is usually performed on the program source code. Instead, in collaboration with colleagues from the CRIStAL laboratory (Clément Ballabriga, Giuseppe Lipari), and from the University of Lyon (Laure Gonnord), and in particular during the post-doc of Jordy Ruiz, we proposed an abstract interpretation technique for the analysis of assembly code. The original motivation of this work was to establish relations between software parameters appearing in WCET formulae produced by our symbolic WCET analysis.

# 1.3. Reading this document

The structure of this document does not follow the chronology of my research, but instead groups my contributions by research domains: programming real-time systems with Prelude (chapter 3), high-level timing analysis (chapter 4), and low-level timing analysis (chapter 5). The document summarizes the main research results, but it is not a comprehensive presentation of my work. The reader should refer to my cited publications for more details. In particular:

- Proofs and intermediate lemmas are not presented, only the main theorems are provided;

- The presentation of related works is succinct and limited to works that are the most tightly related to my contributions;

- When possible, formal definitions are replaced by illustration through examples.

A *Conclusion* subsection is provided at the end of the presentation of each contribution. It highlights the main contribution, detailing where it was published, collaborations, tutored students, and funded research projects.

Glossaries listing the main symbols and acronyms used in each chapter are provided in the appendix part of this document.

# Part I. Introduction

# 2. Background on real-time systems

This chapter provides a description of the background on which my contributions on real-time systems rely.

The development of hard real-time systems usually involves several development teams, each separately responsible for the development of a subset of the system tasks. These tasks are then assembled together to form the complete system, at which point real-time properties and inter-task communication schemes are integrated. In Section 2.1, I present the Prelude language, which I designed and developed during my Ph.D. thesis for specifying how real-time tasks are integrated together to form a complete real-time system. In Section 2.2, I recall classic definitions and results on real-time task models and their scheduling. In Section 2.3, I provide a short summary on the Worst-Case Execution Time analysis of a task.

# 2.1. Prelude, a synchronous data-flow language with real-time primitives

Prelude builds upon synchronous data-flow languages, such as Lustre [Hal+91]. It inherits their clean and formal semantics, and extends them with language concepts dedicated to the description and management of real-time constraints. This section presents the core language defined during my Ph.D. thesis.

The Prelude compiler translates the input program into a set of concurrent and interdependent C tasks. The compilation process is defined formally, so as to ensure that the program semantics is preserved throughout the compilation (semantics preservation is only proved on paper, not with a proof assistant such as e.g. [Bou+17]). The generated code is independent of the target Operating System. Several options for the compiler back-end have been developed since the initial compiler release, in order to support various types of hardware architectures: single-core, multi-core, centralized memory, as well as distributed memory.

# 2.1.1. Informal presentation

**Data-flow** The data-flow nature of Prelude is reminiscent of Lustre, and illustrated in Figure 2.1. When the program receives new input values, it reacts by computing new output values. Variables and expressions denote infinite sequences of values called *flows*. Figure 2.1 details the values of each flow, for each reaction of the node main.

Computations described in the program *equations* (the let...tel block) are implicitly repeated indefinitely. In the example of Figure 2.1, whenever the program receives new values for the input flows a and b, it computes the new value of output flow o as the sum of the new values of a and b. Note that computation order depends on data-dependencies and on real-time constraints, not on text order (the node body is a set of unordered equations, not of sequential instructions): we need values for variables on the right-hand side of an equation to compute values for variables on the left-hand side. Execution order is determined by the compiler and the scheduler, based on the program data-dependencies and real-time constraints.

#### 2. Background on real-time systems

```

imported node add(a,b:int) returns(o:int) wcet 6;

imported node plus_one(a:int) returns(o:int) wcet 3;

node main(a,b: int)

returns(o, p: int)

let

o=add(a,b);

p=0 fby (plus_one(o));

2

0

4

b

7

1

3

13

17

5

o

2

6

14

```

Figure 2.1.: The data-flow semantics of a Prelude program

Nodes are the structuring unit of the language, much like functions/procedures in procedural languages: a Prelude program consists of a set of nodes that can be instantiated (called) in the equations of other nodes. The *main* node is the entry point of the program, it communicates with the program environment by acquiring its inputs from sensors and applying its outputs on actuators. Because it is designed as an architecture description language, Prelude does not include arithmetic or logic operators. Instead, computations are performed by *imported nodes* (add, plus\_one), whose behaviour is described outside the Prelude program. Imported nodes are the leaves of the nodes hierarchy, which will ultimately be translated into tasks/threads in the generated low-level code.

The program of Figure 2.1 consists of a single non-leaf node (the main node), although there can be several non-leaf nodes in general. This node instantiates two imported nodes (add sums its arguments and plusone adds one to its argument). The program also uses the builtin operator fby, which is the delay operator: the value of expression cst fby e is cst for the first reaction *followed by* the value of e at its previous reaction.

**Synchronous real-time** Real-time constraints can be specified in Prelude as illustrated in Figure 2.2. The programmer either declares the rate of a flow explicitly (c: int rate(40,0)) or lets it be inferred by the compiler. A rate declaration specifies the *period* of a flow along with its *phase*, thus defining the dates at which the flow produces values. In the example, inputs a, b have period 40, while input c has period 20.

Due to the data-flow nature of the language, the execution rate of a node depends on that of its inputs. More precisely, when instantiating an imported node, all its inputs are required to be synchronous, that is to say they must have the same rate. This rate is also the execution rate of the node instance. In the example of Figure 2.2, the execution rate of node instance add in node main is (40,0), because both its inputs have rate (40,0). This is also the rate of its outputs. Trying to apply add to a and c would cause a compilation error, since they do not have the same period: for instance, the value of a cannot be accessed at date 20, while the value of b can.

Worst-case execution times (WCET) are specified in the declaration of imported nodes. The programmer must also specify a WCET for each input (sensor) and output (actuator) of the

```

imported node add(a,b:int) returns(o:int) wcet 6;

imported node plus_one(a:int) returns(o:int) wcet 3;

sensor a wcet 5; sensor b wcet 5; sensor c wcet 4;

actuator o wcet 1; actuator p wcet 1;

node main(a,b: int rate (40,0); c: rate (20,0))

returns(o, p: int)

let

o=add(a,b);

p=0 fby (plus_one(c));

tel

```

| date | 0 | 20 | 40 | 60 | 80 |  |

|------|---|----|----|----|----|--|

| a    | 0 |    | 1  |    | 2  |  |

| b    | 2 |    | 4  |    | 6  |  |

| с    | 1 | 3  | 5  | 7  | 9  |  |

| 0    | 2 |    | 5  |    | 8  |  |

| p    | 0 | 2  | 4  | 6  | 8  |  |

Figure 2.2.: A program with inputs with two different rates

main node. WCETs are only used for the schedulability analysis of the program (see Section 4.1 for details), they are not enforced at execution.

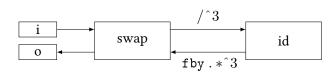

Rate transitions Rate transition operators are used to combine flows that have different rates, as illustrated in Figure 2.3. In expression e\*^k the operator \*^ over-samples expression e, duplicating each value of e k times. Conversely, in e/^k the operator /^ under-samples e, keeping only one out of k successive values of e. In the example, the compiler infers that the rate of swap is (50,0) (because its input i has rate (50,0)), and that the rate of id is (150,0) (because vf has the same rate as swap, and thus vf/^3 has rate (150,0)). Since flow vs has rate (150,0), it is oversampled before being passed as input to swap so as to be synchronous with (i). A delay (fby) is also applied, to avoid overconstraining the deadline of id. Without this delay, id would have to complete no later than the deadline of swap. The imported nodes swap and swap are defined outside Prelude such that swap(i,j) = (j,i), and swap(i,j) = i.

#### 2. Background on real-time systems

```

imported node swap(i, j: int) returns (o, p: int) wcet 10;

imported node id(i: int) returns (o: int) wcet 15;

sensor i wcet 5; actuator o wcet 5;

node sampling(i: rate(50,0)) returns (o)

var vf, vs;

let

(o, vf)=swap(i, (5 fby vs)*^3);

vs=id(vf/^3);

tel

```

| date            | 0 | 50 | 100 | 150 | 200 | 250 | 300 |  |

|-----------------|---|----|-----|-----|-----|-----|-----|--|

| i               | 0 | 1  | 2   | 3   | 4   | 5   | 6   |  |

| $\overline{vf}$ | 0 | 1  | 2   | 3   | 4   | 5   | 6   |  |

| $\overline{vs}$ | 0 |    |     | 3   |     |     | 6   |  |

| 0               | 5 | 5  | 5   | 0   | 0   | 0   | 3   |  |

Figure 2.3.: Rate transition operators

**Phase offsets** The phase of an expression e can be shifted by a fraction q using the construction  $e^{\sim}$ 9. This effectively shifts every value of e by q multiplied by the period of e.

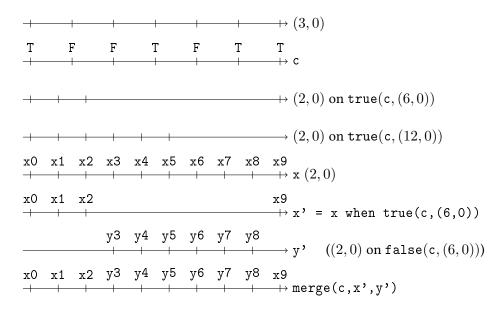

Activation conditions In addition to activation rates (periods and phases), Prelude supports Boolean activation conditions à la Lustre (see Figure 2.4). Expression e when c only keeps the values of e when c is true. Expression merge(c,e1,e2) merges two expressions that have complementary activation conditions: when c is true the expression is equal to e1, when c is false it is equal to e2. For instance, in Figure 2.4, node add is evaluated only if c is true, otherwise plusone is evaluated. Again, because the language is data-flow, the activation condition of an imported node instance is that of its inputs. Note that flows ctrue and cfalse have complementary activation condition, ie either one produces a value or the other does, but not both. They are merged to compute the flow o which always produces values at rate (40,0).

```

imported node add(a,b:int) returns(o:int) wcet 6;

...

node main(a,b: int rate (40,0); c: bool) returns(o: int)

var ctrue, cfalse;

let

ctrue=add(a when c,b when c);

cfalse=plus_one(a whennot c);

o=merge(c,ctrue,cfalse);

tol

```

| date   | 0 | 40 | 80 | 120 | 160 |  |

|--------|---|----|----|-----|-----|--|

| a      | 0 | 1  | 2  | 3   | 4   |  |

| b      | 2 | 4  | 6  | 8   | 10  |  |

| С      | T | T  | F  | Т   | F   |  |

| ctrue  | 2 | 5  |    | 11  |     |  |

| cfalse |   |    | 3  |     | 5   |  |

| 0      | 2 | 5  | 3  | 11  | 5   |  |

|        |   |    |    |     |     |  |

Figure 2.4.: Activation conditions

#### 2.1.2. Formal semantics

The Prelude model of flows and clocks is based on the tagged-signal model [LSV96]. A flow is defined as a set of pairs  $(v_i, t_i)_{i \in \mathbb{N}}$ , where  $v_i$  is a value in some set  $\mathcal{V}$  and the tag  $t_i$  (in  $\mathbb{N}$ ) represents a date associated to  $v_i$ . Tags define the order in which values are produced. Intuitively, the value  $v_i$  is the value carried by the flow in interval  $[t_i, t_{i+1})$ , where  $t_{i+1}$  is the smallest tag in the flow that is greater than  $t_i$ . The clock of a flow is its projection on  $\mathbb{N}$ . Two flows are synchronous iff they have the same clock.

The formal definition of real-time constraints in Prelude relies on a dedicated class of clocks called *Strictly Periodic clocks*, defined as follows:

**Definition 2.1.1** (Strictly Periodic Clock). A strictly periodic clock is denoted as a pair (n, p), with n, p in  $\mathbb{N}$ , and:

- The infinite sequence of tags generated by (n,p), denoted  $(n,p)^{\#}$ , is defined as follows:  $(n,p)^{\#} = \{n * i + p \mid i \in \mathbb{N}\}.$

- $\pi(n,p)=n$  is the *period* and  $\varphi(n,p)=p$  is the *offset* of (n,p).

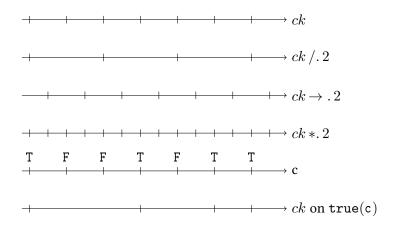

Operators on strictly periodic clocks are illustrated in Figure 2.5. The acceleration (\*,), deceleration (/,), and phase offset ( $\rightarrow$ ), are defined as follows:

**Definition 2.1.2** (Strictly Periodic Clock Operators). Let (n, p) be a strictly periodic clock, and k be in  $\mathbb{N}$ . Then, by definition:

$$(n, p) *. k = (n/k, p)$$

$(n, p) /. k = (n * k, p)$

$(n, p) \rightarrow . k = (n, p + k)$

#### 2. Background on real-time systems

Figure 2.5.: Strictly periodic clocks and clock operations

Prelude combines strictly periodic clocks, which define the activation rate of a flow, with Boolean clocks, which define the activation condition of a flow. To formalise Boolean clocks, we adapt the definition of the clock operator *on* from [CP03] as follows.

**Definition 2.1.3.** Let ck be a clock, c be a flow whose values are of some enumerated type ty, and  $C \in ty$ . Then, by definition:

$$(ck \text{ on } C(c))^{\#} = \{t \mid t \in ck^{\#} \land (C, t) \in c^{\#}\}$$

We will now detail the formal semantics of the language operators. We let  $\hat{s}$  denote the clock of flow s. The term  $\diamond^{\#}(s_0,\ldots,s_n)$  denotes the flow resulting from the application of the operator  $\diamond$  on flows  $s_0,\ldots,s_n$ . The formal semantics of Prelude operators is detailed in Figure 2.6 ( $op_f$  denotes an operator over scalars from the compiler target language). The relation  $x \operatorname{div} y \Leftrightarrow y \operatorname{mod} x = 0$  reads as "x divides y". The denotational semantics of Prelude is rather standard and can be found in [For09].

$$\begin{split} op^\#(s_0,\dots,s_n) &= \{(op_f(v_0,\dots,v_n),t) \mid (v_0,t) \in s_0^\#,\dots,(v_n,t) \in s_n^\#\} \\ & *^{\wedge\#}(s,k) = \{(v,t+i*\pi(\widehat{s})/k) \mid (v,t) \in s^\#,i \in [0..k)\} \\ & /^{\wedge\#}(s,k) = \{(v,t) \mid (v,t) \in s^\# \land (t-\varphi(\widehat{s})) \text{ div } (\pi(\widehat{s})*k)\} \\ & \sim >^\#(s,k) = \{(v,t+k) \mid (v,t) \in s^\#\} \\ & \text{fby}^\#(v,s) &= \{(v,t_0)\} \cup \{(v_i,t_{i+1}) | (v_i,t_i) \in s^\#\} \quad (t_0 \text{ the smallest tag in } s) \\ & \text{when}^\#(s,c,C) &= \{(v,t) \mid (v,t) \in s^\#,t \in (\widehat{s} \text{ on } C(c))^\#\} \\ & \text{merge}^\#(c,s_0,s_1) &= s_0^\# \cup s_1^\# \end{split}$$

Figure 2.6.: Semantics of Prelude operators

Note that the semantics of some operators is well-defined only if the clock of its operands respect some specific clock constraints. For instance, merge# requires flows that do not bear

values at the same dates. Node application requires arguments that are synchronous, i.e. that have the same clock.  $*^{\wedge\#}(s,k)$  is defined iff  $k \operatorname{div} \pi(\widehat{s})$ , etc. The clock calculus (see below) is responsible for checking such clock constraints and inferring the clocks of the program.

# 2.1.3. Compilation overview

The structure of the Prelude compiler follows the classic decomposition into a front-end, which checks the program validity, and a back-end, which translates a valid input program into C code. The front-end starts with a standard syntax analysis, and ML-like type inference [Pie02]. Then it performs two analyses that are specific to synchronous data-flow languages: *clock calculus* and *causality analysis*. The causality analysis checks that the program data-dependencies do form *immediate* cycles (cycles that do not contain at least one delay), its definition is similar to that of Lustre [HRR91]. The clock calculus computes a clock for each element of the program (variables, expressions, etc). In doing so, it verifies that clock synchronization constraints are respected, which ensures that flow values are only accessed at dates at which they are well-defined. The clock calculus is implemented as a type inference system, where the usual types are replaced by clock types, and with some noticeable differences such as subtyping rules, and arithmetic simplifications of periodic clock expressions. For more details, refer to [For+08; For09].

The back-end consists of two steps. First, the program is translated into a  $Task\ Set$  intermediate representation. Basically, each imported node is translated into a real-time task, where periods and offsets are deduced from clocks, while deadlines and WCETs are deduced from the corresponding declarations in the program. In addition, tasks are related by data-dependencies due to the program causality constraints. For instance, Figure 2.7 represents the task graph obtained for the program of Figure 2.3. Boxes represent tasks, edges represent data-dependencies and are annotated with operators that detail how tasks communicate. Tasks i, o and swap have period 50, while task id has period 150. The task relative deadlines are equal to their periods. Data-dependencies have a causal semantics, which means that a task producing data must complete before task(s) consuming this data can start.

Figure 2.7.: Task graph for the program of Figure 2.3

In the second step of the back-end, the task set is translated into C code. This includes a fairly trivial generation of a data-structure describing the characteristics of each task (akin to a Process Control Block). More importantly, a tailor-made communication protocol is generated for each inter-task data-dependency to ensure that task communications respect the synchronous semantics. The code generated for each protocol depends on the operator annotations on the corresponding data-dependency. See [For09] for more details on the compiler back-end.

# 2.2. High-level timing analysis of a real-time task set

The code generated by Prelude is structured as a set of real-time tasks. This section recalls classic definitions for real-time tasks and provides an introduction to real-time scheduling.

#### 2. Background on real-time systems

In the classic model of the real-time scheduling theory [BW01], a real-time task is characterized by its duration (Worst-Case Execution Time), its repetition period, and its deadline (relative to its period). In order to take the functional semantics of the program into account, we also add data-communications to this model. To ensure the functional determinism of the program, we need to control the order in which communicating tasks execute. Typically, data-production must precede data-consumption, so data-communications induce precedence constraints. As a consequence, we consider a *dependent task model*, that is to say tasks whose start time depends on the completion time of other tasks.

For more details on real-time scheduling, the reader unfamiliar with this topic can refer to my introductory course at École Temps Réel 2017 [For17].

## 2.2.1. Real-time attributes

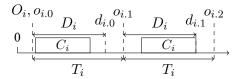

The software architecture of a real-time system can be defined as a set of tasks denoted  $\mathcal{S}=\{\tau_i(O_i,C_i,D_i,T_i)\}_{0\leq i< n}.$   $O_i$  is the first release date of the task  $\tau_i$ , also called *offset* in the literature.  $T_i$  is the *period* of the task and defines the exact duration between two successive releases of the task. We denote  $\tau_{i.k}$  the  $k^{th}$   $(k\geq 0)$  repetition, or job, of  $\tau_i$ . The job  $\tau_{i.k}$  is released at the date  $o_{i.k}=O_i+kT_i$ .  $D_i$  is the relative deadline of the task, every job  $\tau_{i.k}$  must be completed before its absolute deadline  $d_{i.k}=o_{i.k}+D_i$ . We denote  $\mathcal J$  the set of jobs (generated by  $\mathcal S$ ). Finally,  $C_i$  is the worst-case execution time (WCET) of the task and represents the longest possible processing time required to compute a job of  $\tau_i$ . These definitions are illustrated in Figure 2.8. Additionally, we define the *hyperperiod* H of a task set as the least common multiple (lcm) of the task periods.

Figure 2.8.: Real-time attributes

#### 2.2.2. Precedence constraints

Precedence constraints impose constraints on the relative execution order of tasks. In the following, we distinguish simple and extended precedence constraints.

## 2.2.2.1. Simple precedence constraints

Precedence constraints that relate tasks with the same period are called *simple precedence* constraints. They are formalized by a relation  $\to \subseteq \mathcal{S} \times \mathcal{S}$ , where  $\tau_i \to \tau_j$  states that for all  $k \in \mathbb{N}$ ,  $\tau_{i.k}$  must complete before  $\tau_{j.k}$  starts. As such, precedence constraints define a partial order between tasks. We assume that the graph of precedence constraints is acyclic (a Direct Acyclic Graph, or DAG), otherwise the system is not causal, meaning that there exists no execution order that respects all the precedence constraints. We define the predecessors of a task  $\tau_i$  as  $\operatorname{preds}(\tau_i) = \{\tau_j | \tau_j \to \tau_i\}$  and its successors as  $\operatorname{succs}(\tau_i) = \{\tau_j | \tau_i \to \tau_j\}$ . We let  $\tau_i \stackrel{*}{\to} \tau_j$  denote the transitive closure of  $\to$ .

#### 2.2.2.2. Extended precedence constraints

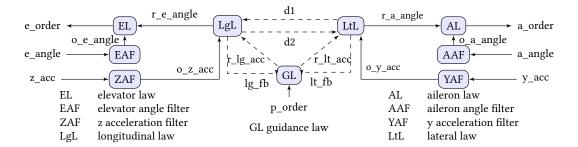

Prelude programs are often made up of several *computation chains*. Tasks within a chain all have the same period, while tasks of different chains may have different periods. The different computation chains eventually join, since they must collaborate to implement the complete system behaviour. Such junctions imply communications between tasks of different periods.

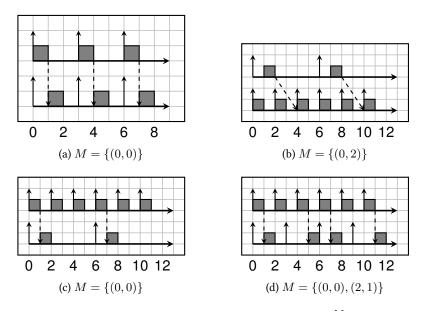

Precedence constraints that relate tasks with different periods are called *extended precedence* constraints. In that case, only a subset of the jobs of the related tasks are concerned by the constraint. We let  $\tau_{i.k} \to \tau_{j.k'}$  denote a precedence constraint from  $\tau_{i.k}$  to  $\tau_{j.k'}$ . We define the predecessors of a job  $\tau_{i.k}$  as  $\operatorname{preds}(\tau_{i.k}) = \{\tau_{j.k'} | \tau_{j.k'} \to \tau_{i.k}\}$  and its successors as  $\operatorname{succs}(\tau_{i.k}) = \{\tau_{j.k'} | \tau_{i.k} \to \tau_{j.k'}\}$ . We use a  $\operatorname{precedence}$  matrix  $M_{i,j} \in \mathcal{M}$  (with  $0 \le i < |\mathcal{S}|, 0 \le j < |\mathcal{S}|$ ), to specify the pairs (p,q) such that  $\tau_{i.p} \to \tau_{j.q}$ . Precedence matrices represent sets of precedence constraints that follow patterns repeated periodically. Let  $\mathbb{N}_{< n}$  denote the set of natural integers strictly smaller than n. Let  $\operatorname{lcm}(n,n')$  denote the least common multiple of n and n'.

**Definition 2.2.1.** Let  $\tau_i$  and  $\tau_j$  be two tasks. Let  $H = lcm(T_i, T_j)$ . A precedence matrix M associated to tasks  $\tau_i$ ,  $\tau_j$ , is such that  $M \subseteq \mathbb{N}_{< H/T_i} \times \mathbb{N}_{< H/T_j}$ , where for all  $(p,q), (p',q') \in M^2$ ,  $p = p' \Rightarrow q = q'$  and  $p' > p \Rightarrow q' \geq q$ . Then,  $\tau_i \xrightarrow{M_{i,j}} \tau_j$  denotes a precedence relation defined as follows:

$$\forall (p,q) \in M^{\omega}, \tau_{i.p} \to \tau_{j.q}$$

with  $M^{\omega} \equiv \{(n,n') | \exists k \in \mathbb{N}, (m,m') \in M, (n,n') = (m,m') + (k\frac{H}{T_i}, k\frac{H}{T_j})$

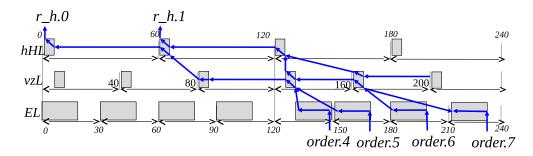

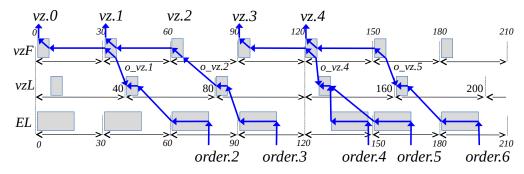

This definition is illustrated in Figure 2.9. Intuitively, M lists all job precedence constraints over one hyperperiod of the related tasks. The pattern is then repeated indefinitely.

Figure 2.9.: Some communication patterns  $(\tau_i \xrightarrow{M} \tau_j)$

# 2.2.3. Scheduling

Real-time scheduling consists in finding an order for the execution of a set of tasks, such that the set of real-time constraints of the tasks is respected. It involves two related parts. First, defining a scheduling policy, that is to say an algorithm whose purpose is to choose which task to execute at each step of the execution. Second, given a scheduling policy, performing a schedulability analysis, prior to execution, to ensure that the task set will respect all its constraints when scheduled with that policy.

In the following, we focus on **preemptive**, **on-line**, **priority-based** scheduling policies. A scheduling policy is *preemptive* if it allows interrupting a job during its execution and resuming it later. With *on-line scheduling*, the scheduler computes the schedule as execution progresses, based on the chosen scheduling policy. Most on-line scheduling policies are *priority-based*, meaning that they only define how to assign priorities to tasks and that the scheduler then always chooses to execute the highest priority task ready for execution. With a *fixed-task priority* scheduling policy, the priority of a task remains unchanged during the whole system execution. With a *fixed-job priority* scheduling policy, the priority can differ between jobs of the same task, but remains unchanged for a given job. Given a priority assignment  $\Phi$ , we define two functions  $s_{S\Phi}, e_{S\Phi}: \mathcal{J} \to \mathbb{N}$ , where  $s_{S\Phi}(\tau_{i.k})$  is the start time and  $e_{S\Phi}(\tau_{i.k})$  is the completion time of  $\tau_{i.k}$  in the schedule produced by this assignment. In the sequel, S and  $\Phi$  are omitted when clear from context. We say that a schedule obtained for a dependent task set under a given priority assignment is *feasible* if it respects all the temporal constraints of the task set and all its job precedence constraints. More formally:

**Definition 2.2.2.** Let  $S = (\{\tau_i\}_{0 \le i < n}, \to)$  be a dependent task set and  $\Phi$  be a priority assignment. Let  $\sigma_{S\Phi}$  be the schedule of S under  $\Phi$ .  $\sigma_{S\Phi}$  is *feasible* if and only if:

$$\begin{cases} \forall \tau_{i.k}, \ e(\tau_{i.k}) \leq d_{i.k} \land s(\tau_{i.k}) \geq o_{i.k} \\ \forall \tau_{i.k} \to \tau_{j.k'}, \ e(\tau_{i.k}) \leq s(\tau_{j.k'}) \end{cases}$$

A task set is *schedulable* by a given scheduling policy if and only if the schedule produced by that policy is feasible. A scheduling policy  $\mathcal{P}$  is *optimal* within a certain class of policies (e.g. the class of fixed-task policies) if the following holds: if a task set is schedulable by some policy of this class, then it is schedulable by  $\mathcal{P}$ .

In monocore<sup>1</sup>, Liu and Layland [LL73] proposed the *rate-monotonic* (RM) fixed-task priority policy, where tasks with a shorter period are affected a higher priority, and the *earliest-deadline-first* (EDF) fixed-job priority policy, where jobs with a shorter absolute deadline are affected a higher priority. RM is optimal within the class of fixed-task priority policies for periodic task sets with  $T_i = D_i$  and  $O_i = 0$ . It can be extended to the *deadline-monotonic* policy (DM) [LW82], to schedule optimally a set of tasks with  $D_i \leq T_i$  and  $O_i = 0$ . For the case where  $O_i \geq 0$ , an optimal algorithm was defined by Audsley in [Aud91]. EDF is optimal within the class of fixed-job priority policies, for jobs with arbitrary offsets and deadlines.

A *schedulability test* determines whether a task set is schedulable with a given scheduling policy. A schedulability test is called *sufficient* if all task sets considered schedulable by the test are indeed schedulable. A schedulability test is called *necessary* if all task sets considered unschedulable by the test are indeed unschedulable. Schedulability tests that are both sufficient and necessary are referred to as *exact*.

<sup>&</sup>lt;sup>1</sup>To avoid overburdening this introduction, multicore scheduling will be discussed later in the document.

# 2.3. Low-level timing analysis of a single task

High-level timing analyses require as input an upper bound to the execution time of each task. Deriving such upper bounds is an undecidable problem in the general case, as it can be reduced to the halting problem. However, programming conventions for real-time systems require the number of iterations of loops and recursions to be explicitly bounded, thus making execution time upper-bounds computable. It remains nevertheless a difficult problem, because it requires to identify the worst case input software-hardware configuration, which leads to the Worst-Case Execution Time (WCET). The software-hardware state space is usually too large to be explored exhaustively, thus WCET analysis produces approximate results. Ideally, a WCET value should be safe, in the sense that it must be greater than all possible execution times of the task, and should also be tight to avoid hardware resource over-provisioning. The right trade-off between safety and tightness depends on the application domain; the critical real-time domain favors safety.

There exists several different approaches to WCET analysis, a survey of which can be found in [Wil+08]. They can be categorized as either *measurement-based*, typically unsafe but less pessimistic and complex, or *static*, typically safe but more pessimistic and complex. As my work targets critical real-time system, in the following I will focus on **static** WCET analysis.

Static analysis can be applied to either source code or binary code. Source code analysis is generally easier, thanks to the higher level of abstraction of the program. However, it requires to make assumptions about the (complex) compiler behaviour, thus machine code analysis is often favored for WCET analysis. In my work, I focus on **machine code** analysis.

Static WCET analysis consists of four main steps. *Control-flow analysis* (CFA) studies the different possible execution paths of the program. *Hardware analysis* determines the execution time of a path on the considered hardware. *Value analysis* studies the values computed by the program, providing information useful both for CFA (e.g. loop bounds) and hardware analysis (e.g. instruction addresses needed for cache analysis). Finally, the *bound computation* puts all information of the previous steps together to estimate a safe over-approximation of the WCET.

# 2.3.1. Control-flow analysis

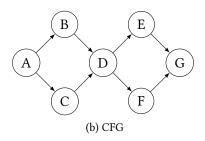

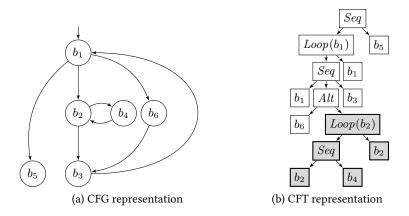

A *Control Flow Graph* (CFG) is the traditional model used to represent the possible execution paths of a machine code program. In a CFG, each node or *basic block* corresponds to a sequence of instructions with no jump or jump target, while edges represent jumps. Figure 2.10 details an example of Arm program, with the corresponding C code as comment for better readability, and the CFG representing it. CFG construction from machine code is a difficult problem, but it is out of the scope of the work presented in this manuscript.

```

0 ...

/* A */

/* A */

str r0, [fp, #-32]

0

2

@ ...

0

/* A */

ldr r3, [fp, #-32]

/* A */

if (n <= 10) /* A */

0

cmp r3, #10

6

bgt .L2

0

/* still A */

Q ...

/* C */

0

}

/* C */

b . L3

0

9

.L2:

0

else {

/* B */

0

10

0 . . .

.L3:

0

}

0

/* D

*/

0 ...

12

/* D */

13

ldr r3, [fp, #-32]

0

if (n <= -1)

/* D */

14

cmp r3, #-1

0

0

/* still D */

bgt .L4

{

15

@ ..

/* F */

0

16

/* F */

17

b . L5

0

.L4:

else {

18

19

0

0

/* E */

.L5:

0

20

21

Q ...

0

/* G */

```

(a) Arm program

Figure 2.10.: Control-flow representation

A CFG represents a superset of the set of paths that are actually feasible in the corresponding program. A path that is structurally feasible in the CFG may be infeasible if we take the semantics of the program into account. For instance, in Figure 2.10, path A.B.D.F.G is structurally feasible in the CFG, but semantically infeasible in the program (n cannot be greater than 10 and smaller than -1).

Control-flow analysis (CFA) provides information on semantically infeasible execution paths, to be combined with the purely structural information provided by the CFG. The more information it can extract, the tighter the WCET bound gets. There exists many CFA approaches, for instance detection of mutually exclusive branch constraints [HW02], detection of infeasible paths across several loop iterations [RCM17], or analysis of loop bounds and their iteration structures [Wil+08].

# 2.3.2. Hardware analysis

In its simplest form, hardware analysis provides the execution time of each instruction of an instruction set on the target hardware. However, on modern hardware the execution time of an instruction can be subject to large variations caused by various optimization components: caches, pipeline, branch prediction, ... Hardware analysis consists of a set of sub-analyses whose objective is to determine the state of the different hardware components at each program point. The execution time of a program instruction is then derived based on the hardware state at that

point.

Hardware analysis is performed on an abstract conservative model of the actual hardware, which means that execution time predicted based on the model is never less than actual execution time on the concrete hardware. As different execution paths may lead to the same program point, the exact hardware state usually cannot be derived. Instead, weaker invariants on it are established, typically using abstract interpretation [CC77]. WCET analysis tools usually include at least hardware analyses for the instruction cache [Fer+99], and the pipeline (e.g. [RS09]).

# 2.3.3. Value analysis

To produce accurate information, CFA and hardware analysis both require information on the values computed by the program. As we analyse machine code, these values are stored in registers or in memory. Value analysis infers properties on the content of processor registers, and memory addresses accessed by the program. Abstract interpretation is a popular approach to value analysis as it provides a safe over-approximation of the possible values computed at each program point. It is most noticeably used to infer loop bounds (e.g. [GEL05]), and to infer instruction addresses (e.g. [The+03]), required for cache analysis.

# 2.3.4. WCET bound computation

The final step of WCET analysis consists in combining information provided by CFA, hardware analysis and value analysis, to compute an upper-bound to the WCET. There are mainly two approaches to WCET bound computation: *tree-based* (also called structure-based), and *implicit-path enumeration* (IPET).

A tree-based approach represents the program to analyse as a tree (akin to an abstract syntax tree), and computes the WCET bound by a recursive evaluation on the tree structure. Essentially:

- The WCET of a sequence of nodes is the sum of the WCET of the nodes;

- The WCET of an alternative between nodes is the maximum of the WCET of the nodes;

- The WCET of a loop multiplies the WCET of the loop body by the loop bound.

For instance, the WCET for the program of Figure 2.10 would be computed as:  $t_A + \max(t_B, t_C) + t_D + \max(t_E, t_F) + t_G$  (where  $t_I$  denotes the WCET of basic block I).

In IPET, the information and constraints provided by CFA, hardware analysis and value analysis, are all combined into a single *Integer Linear Program* (ILP) and the WCET bound is obtained by solving this ILP. Essentially:

- A timing  $t_e$  is associated to each node of the CFG. It is an upper bound to the WCET of the corresponding basic block, inferred by hardware analysis.

- An execution count  $x_e$  is associated to each node and edge of the CFG. It represents the number of execution of the node or edge during a complete program execution;

- The goal function of the ILP is to maximize the term  $\sum_{i \in CFG} x_i * t_i$ , thus obtaining an upper-bound to the WCET.

## 2. Background on real-time systems

Constraints related to the CFG structure are expressed as constraints on execution counts. For instance, for the program of Figure 2.10 the following ILP constraints would be deduced from the CFG:  $x_A = x_G = 1, x_A = x_{A \to B} + x_{A \to C}, x_B = x_{A \to B}, \ldots$  Constraints obtained by CFA or value analysis, are also expressed as constraints on execution counts. For instance, for the previous program, an infeasible path analysis would add the constraint  $x_A = x_B + x_F$ .

IPET has become a popular WCET analysis technique, thanks to its generality; indeed, results of new analyses can easily be integrated as ILP constraints. Its main drawback is its high complexity (potentially exponential in the program size). On the contrary, tree-based approaches have low complexity (a low-degree polynomial in the size of the tree), but struggle to integrate constraints provided by CFA. The popular WCET analysis tools Heptane [HRP17], OTAWA [Bal+10] and AiT [Abs] are currently based on IPET.

# Part II. Contributions

# 3. Programming real-time systems with Prelude

This chapter summarizes my contributions on Prelude that are posterior to my Ph.D. thesis. First, I summarize extensions of the compiler back-end that target multi-core hardware platforms (Section 3.1). Then, I present two extensions to the language definition and to the compiler front-end: the introduction of a new operator to support incomplete specifications (Section 3.2), and support for mode-automata (Section 3.3).

# 3.1. Implementation on multi-core with distributed memory

Over the last decade, the code generation of Prelude has been extended to target several types of hardware platforms and Operating Systems. The available code generation options are summarized in Table 3.1. *Centralized memory* corresponds to a hardware architecture with a large shared memory, and a smaller cache memory for each core. *Distributed memory* corresponds to a hardware architecture with a large shared memory, and a smaller private locally addressable memory for each core (typically a scratchpad memory).

*MarteOS* [RH01] on unicore was the first code generation target, implemented during my Ph.D. thesis. The code generation was then adapted so as to generate OS-independent code. Porting Prelude to a new target OS now only requires to implement a small set of OS-specific functions (task creation, and communication primitives).

SchedMCore [Cor+11], was the first multi-core target. SchedMCore runs on top of an existing Operating System, and allows to run a set of tasks written in C using various real-time multicore scheduling policies (somewhere between a pure simulator and a true hard real-time execution environment).

The code generation was then adapted to enable execution on standard Linux, relying on the SCHED\_DEADLINE scheduling policy and on the ptask API<sup>1</sup> to enforce real-time constraints. Due to unbounded latencies in the Linux kernel, this is not a truly hard real-time port. Nevertheless, it enables easy prototyping and testing of real-time applications.

A distributed memory target was then implemented. This required to significantly extend the code generation, so as to explicitly handle copies between core local memories and the global shared memory. The first port [Pag+18b], referred to as *Sequencer* in Table 3.1, targeted an architecture with no real OS. Instead, the task schedule was generated offline and tasks were executed by a simple sequencer. Finally, we ported code generation to *Erika*, a true real-time Operating System<sup>2</sup>. In the remainder of this section, I present our work on code generation for distributed memory architectures.

<sup>&</sup>lt;sup>1</sup>Ptask is a Periodic Real-Time Task interface to pthreads: https://github.com/glipari/ptask

<sup>&</sup>lt;sup>2</sup>http://erika.tuxfamily.org/drupal/

## 3. Programming real-time systems with Prelude

| OS         | unicore  | multicore | centralized mem. | distributed mem. |

|------------|----------|-----------|------------------|------------------|

| MarteOS    | ✓        |           | ✓                |                  |

| SchedMCore | ✓        | ✓         | ✓                |                  |

| Linux      | ✓        | ✓         | ✓                |                  |

| Sequencer  | ✓        | ✓         |                  | ✓                |

| Erika      | <b>√</b> | <b>√</b>  | <b>√</b>         | <b>√</b>         |

Table 3.1.: Code generation for Prelude on different platforms

#### 3.1.1. Motivation

Implementing real-time tasks on a multi-core platform is hard, mainly because cores share access to a central memory. This leads to contentions, which cause significant execution delays that are hard to predict, because they require to finely analyse task codes, task interferences and the contention resolution mechanisms [PC10].

In order to simplify the analysis of task interferences, the PRedictable Execution Model (PREM) [Pel+11] advocates to decouple communication phases from computation phases. For instance, the AER task model [Dur+14], a declination of the PREM model, splits each task of the system into three phases. The *Acquisition* phase loads task data and instructions from the main memory into the core local memory. Then, the *Execution* phase performs the task computations using only local memory. Finally, the *Restitution* phase copies the results of the E-phase back into the main memory, for use by other tasks. This simplifies timing analysis because: 1) communication phases are clearly identified, so the system scheduler can schedule communications [AP14a; Mai+17] and avoid contentions; 2) worst-case execution time analysis (WCET) of computation phases does not need to take bus contentions into account [Pel+11].

Manually implementing a PREM-compliant program is tedious, unintuitive and error-prone. Instead, we propose an extension of the Prelude compiler that automatically generates PREM-compliant code. The synchronous semantics is close to the PREM model, making the translation into PREM natural. We target a multi-core platform with distributed memory: one shared main memory plus one private scratchpad memory (SPM) for each core. According to a predefined distribution of tasks onto cores, the compiler generates a separate C code for each core. The main advantage of this approach is to simplify the development process, by automating the translation from the high-level specification in Prelude to the low-level implementation in C. In particular, concerns related to task communications become the responsibility of the compiler.

# 3.1.2. Model

First, we define the considered hardware and software model.

# 3.1.2.1. Distributed memory

We consider a multi-core hardware architecture with distributed memory. Each core  $\rho_i$  has access to a global shared memory denoted  $\mathcal{M}_G$  and to a private scratchpad memory denoted  $\mathcal{M}_i$ . We assume a static allocation of code and data to SPMs. Compared to a cache-based architecture, in our case distributed memory is apparent in the program code (local memory is explicitly addressable). Thus, memory transfers between private and global memories are handled by the Prelude compiler. This implies more predictable memory accesses without

| Phase | Dependency                       |

|-------|----------------------------------|

| $E_A$ |                                  |

| $R_A$ | $	au_A  ightarrow 	au_C$         |

| $E_B$ |                                  |

| $R_B$ | $	au_B  ightarrow 	au_C$         |

| $A_C$ | $	au_B 	o 	au_C, 	au_A 	o 	au_C$ |

| $E_C$ | $	au_C  ightarrow 	au_D$         |

| $E_D$ | $	au_C  ightarrow 	au_D$         |

Table 3.2.: Phases and related data-dependencies

overburdening the programmer.

#### 3.1.2.2. Multi-phase tasks

The translation of the Prelude program into a set of real-time tasks remains unchanged compared to previous works. Here, we consider a task set as the starting point for the code generation (for readers unfamiliar with the definition of a real-time task set, see Section 2.2 for more details). Following the AER model of [Dur+14], each task  $\tau_i$  is divided into three phases. In the Acquisition phase  $(A_i)$ , data is copied from  $\mathcal{M}_G$  into  $\mathcal{M}_i$ . The Execution phase  $(E_i)$  then executes using only  $\mathcal{M}_i$ . Finally, in the Restitution phase  $(R_i)$ , the results of the Execution phase are copied back from  $\mathcal{M}_i$  into  $\mathcal{M}_G$ . In our implementation, not all tasks have A and E and R phases. Tasks without incoming data-dependencies, have no A-phase. Tasks without outgoing data-dependencies have no R-phase. Similarly, A/R phases are removed when all predecessors/successors are located on the same processor.

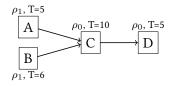

Figure 3.1 shows a simple example, that will be used as an illustration in further sections. The program consists of four tasks/nodes  $(\tau_A, \tau_B, \tau_C, \tau_D)$  distributed on two processors  $(\rho_0, \rho_1)$ . The program is multi-periodic (periods 5, 6, 10). Phases and the data-dependencies they implement are depicted in Table 3.2. For instance,  $\tau_C$  copies both its inputs during  $A_C$ . Since  $\tau_C$  and  $\tau_D$  are colocated (i.e. located on the same core), their data-dependencies are directly handled by  $E_C$  and  $E_D$ . In this example, none of the tasks have three phases.

Figure 3.1.: Running example

# 3.1.3. Code generation

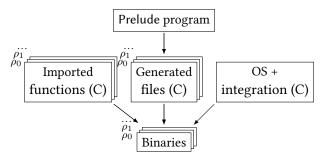

Figure 3.2 details the files involved in the production of an executable for a Prelude program. The Prelude program is compiled into one C file per core and one C file for the global memory  $\mathcal{M}_G$ . The code of each core contains one function per phase allocated to that core, and related communication and synchronisation code (see Figure 3.3 for instance). The  $\mathcal{M}_G$  code contains

data shared for inter-core communication purposes. In addition, the C application contains some code that is not generated by Prelude: 1) for each task, a user-provided imported function, to be executed during the corresponding E-phase; 2) the OS specific code that integrates the generated files into the final application. The compilation of the C code produces one binary per core  $\rho_i$ , to be stored in  $\mathcal{M}_i$ , which contains the instructions and local data of  $\rho_i$ . Shared communication data is stored into  $\mathcal{M}_G$ .

Figure 3.2.: Files involved in the production of the executable code

So as to illustrate the structure of the generated code, Figure 3.3 details the code generated for tasks  $\tau_A$ ,  $\tau_C$ . For each input or output of each task, the compiler allocates a *working variable* in  $\mathcal{M}_i$  that is only accessed by the phases of that task (variables suffixed by \_loc or \_out). It allocates a *communication buffer* for each  $\tau_i \to \tau_j$  (variables suffixed by \_buff). If  $\tau_i$  and  $\tau_j$  are located on the same core, the buffer resides in  $\mathcal{M}_i$  (e.g. C\_D\_buff in  $\mathcal{M}_0$ ), otherwise it resides in  $\mathcal{M}_G$  (e.g. A\_C\_buff).

In the E-phase code, the call to the imported function only operates on working variables (e.g. Line 16). Before this call, we copy input data from communication buffers into working variables. After this call, we copy output data from working variables into communication buffers. For intra-core communications, these copies are directly performed by the E-phase (Line 17). For inter-core communications, they are performed by the A/R-phases (Lines 7 Column 1, and 8 Column 2). We use the OS-specific functions read\_val and wrive\_val to perform copies between  $\mathcal{M}_i$  and  $\mathcal{M}_G$ .

```

1

// core 0

// core 1

void C_A() {

void A_E() {

wait_sem(sem_A_C);

a_{loc} = A();

if (must_wait_B_C())

wait_sem(sem_B_C);

void A R() {

a_loc = read_val(A_C_buff, A_C_idx);

if (must_write_A_C())

8

b_loc = read_val(B_C_buff, B_C_idx);

write_val(A_C_buff, a_loc);

A_C_idx += 1;

if (must_post_A_C())

11

if (must_change_B_C())

post_sem(sem_A_C);

B_C_idx += 1;

12

13

14

void C_E() {

15

c_out = C(a_loc, b_loc);

16

C_D_buff = c_out;

17

post_sem(sem_C_D);

18

```

Figure 3.3.: C code for  $\tau_A$  and  $\tau_C$

| Tubic old size of memories for the experiments |                                 |  |  |  |

|------------------------------------------------|---------------------------------|--|--|--|

| Memory (SPM architecture)                      | Size                            |  |  |  |

| Data SPM                                       | $\rho_0$ : 5kB, $\rho_1$ : 4kB  |  |  |  |

| Instruction SPM                                | $\rho_0$ : 12kB, $\rho_1$ : 8kB |  |  |  |

| Main                                           | 2kB                             |  |  |  |

| Memory (cache architecture)                    | Size                            |  |  |  |

| Data cache                                     | 2kB                             |  |  |  |

| Instruction cache                              | 4kB                             |  |  |  |

| Main                                           | 29kB                            |  |  |  |

Table 3.3.: Size of memories for the experiments

We do not detail here how the Prelude compiler generates the code of the inter-task communication protocols depending on the rate transition operators involved. It remains as detailed in [For09]. To summarize, during that step the compiler determines for each  $\tau_i \to \tau_j$ :

- The size of the communication buffer i\_j\_buff (e.g. C\_D\_buff has size 2);

- A function must\_change\_i\_j, which tells when to change the cell of i\_j\_buff jobs of τ<sub>j</sub> read from (e.g. must\_change\_C\_D always returns true);

- A function must\_write\_i\_j, which tells for each job of τ<sub>i</sub> whether it must write in i\_j\_buff or not (e.g. must\_write\_A\_C alternates between true and false, meaning that only one out of two successive jobs of τ<sub>A</sub> writes in the buffer);

- A function must\_wait\_i\_j, which tells if  $\tau_j$  must wait on the communication semaphore;

- A function must\_post\_i\_j, which tells if  $\tau_i$  must post on the communication semaphore.

# 3.1.4. Comparing memory architectures

The original code generation of Prelude, implemented during my Ph.D. thesis, targets an architecture with centralized memory. As a consequence, we can now use the Prelude compiler, with its new distributed code generation target, to compare the performance of an application on a hardware platform with centralized memory against the same platform with distributed memory instead.

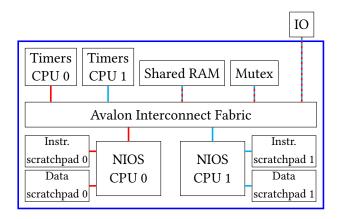

In order to allow the comparison between different hardware architectures, we rely on an FPGA development board, a Cyclone III by Altera with two NIOS-II softcores, depicted in Figure 3.4. The data and instruction ports connect the cores to the Avalon Interconnect Fabric, a crossbar which serves as a hub to access shared resources of the board. Each core has access to a tightly-coupled memory for data and to another for instructions. These memories serve as scratchpad memories ( $\mathcal{M}_i$ ). Processors share access to an on-chip shared RAM ( $\mathcal{M}_G$ ). Finally, processors are also connected through the Avalon to an on-chip mutex (used to implement semaphores), on-board IOs and timers.

In addition to the scratchpad architecture we just detailed, we implement a cache-based architecture on the FPGA. It features a cache for each core, with access performances similar to the scratchpads. The FPGA has tight space limitations, its memory sizes are reported in Table 3.3. Space reserved for SPM in the scratchpad-based architecture is instead reserved for the main memory in the cache-based architecture.

#### 3. Programming real-time systems with Prelude

Figure 3.4.: The hardware design.