# Embracing Imperfections: Hardware-compatible Neural Networks for Neuromorphic Computing

Atreya Majumdar

#### ▶ To cite this version:

Atreya Majumdar. Embracing Imperfections: Hardware-compatible Neural Networks for Neuromorphic Computing. Artificial Intelligence [cs.AI]. Université Paris-Saclay, 2023. English. NNT: 2023UPAST077. tel-04149169

# HAL Id: tel-04149169 https://theses.hal.science/tel-04149169v1

Submitted on 3 Jul 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Embracing Imperfections: Hardware-compatible Neural Networks for Neuromorphic Computing

Accepter les imperfections : réseaux de neurones matériels pour le calcul neuromorphique

### Thèse de doctorat de l'université Paris-Saclay

École doctorale n°575 : Electrical, Optical, Bio-Physics and Engineering (EOBE)

Spécialité de doctorat : Electronique, Photonique et Micro-Nanotechnologies

Graduate School : Sciences de l'ingénierie et des systèmes

Référent : Faculté des Sciences d'Orsay

Thèse préparée au **Centre de Nanosciences et de Nanotechnologies**, (Université Paris-Saclay, CNRS), sous la direction de **Damien QUERLIOZ**, Chargé de recherche au C2N

Thèse soutenue à Paris-Saclay, le 22 mai 2023, par

Atreya MAJUMDAR

#### Composition du jury

Membres du jury avec voix délibérative

Dafiné RAVELOSONA

Directeur de recherche, Université Paris-Saclay

Louis HUTIN

Ingénieur chercheur (HDR) , CEA-LETI

Grenoble, France

Damien DELERUYELLE

Professeur à l'INSA, Lyon, France **Alice MIZRAHI**

Alice WIZK

Ingénieure chercheure, Thales Research and Technology,

France

Luis LÓPEZ DÍAZ

Professeur à la Universidad de Salamanca

Espagne

Jean-Michel PORTAL

Professeur à la Institut Matériaux Microélectronique Nanosciences de Provence (IM2NP) Président

Rapporteur & Examinateur

Rapporteur & Examinateur

Examinatrice

Examinateur

Examinateur

# Ecole Doctorale Physique et ingénierie: Electrons, Photons, Sciences du vivant (EOBE)

**Titre:** Accepter les imperfections: réseaux de neurones matériels pour le calcul neuromorphique **Mots clés:** réseaux de neurones, memristors, apprentissage, neuromorphique, imperfections, Réseaux neuronaux bayésiens

Résumé: Les récents développements en apprentissage profond ont repoussé les limites des possibilités avec de grands modèles de langage présentant des capacités exceptionnelles, des modèles pour la vision par ordinateur et le traitement du langage naturel dépassant les performances humaines. Cependant, ce progrès se fait au détriment d'une consommation d'énergie immense lors de la formation de ces modèles à grande échelle. De ce point de vue, l'avancée n'est pas durable, surtout compte tenu des préoccupations de changement climatique qui planent sur notre époque. L'énormité de la consommation d'énergie peut être attribuée à l'architecture des ordinateurs conventionnels, qui n'est pas optimisée pour la consommation d'énergie pour les applications d'apprentissage profond. D'autre part, le cerveau humain excelle dans cet aspect en effectuant des tâches complexes de reconnaissance de motifs avec un budget énergétique qui est des ordres de magnitude inférieurs à celui de son homologue informatique. La différence découle de la manière fondamentalement différente dont les calculs sont effectués dans le cerveau; pour cette thèse, nous nous concentrons spécifiquement sur l'aspect de la co-localisation du calcul et de la mémoire, qui est présent dans le cerveau humain via les neurones et les synapses. En revanche, dans l'architecture de von Neumann d'un ordinateur moderne, la mémoire et les unités arithmétiques et logiques sont physiquement séparées, et une grande quantité d'énergie est dépensée dans le transfert d'informations entre ces unités. L'informatique en mémoire avec les technologies de mémoire émergentes est une piste prometteuse à cet égard, où la co-localisation de la mémoire et du traitement peut être réalisée, en particulier pour le type de calculs effectués dans les réseaux de neurones. Néanmoins, cette solution présente des défis en termes de performance car ces nouvelles classes de mémoires ont des imperfections différentes. Pour les mises en œuvre conventionnelles de réseaux de neurones avec des mémoires analogiques, ces imperfections peuvent considérablement affecter leurs performances. Le thème central de cette thèse est d'embrasser de telles imperfections pour les réseaux de neurones compatibles avec le matériel. Dans le chapitre 2, nous examinons spécifiquement l'impact de ces non-idéalités dans le contexte de la formation des réseaux de neurones. Nous proposons un modèle de dispositif basé sur la physique pour la mémoire à base d'HfOx qui correspond aux résultats expérimentaux et peut être incorporé dans des cadres d'apprentissage en profondeur. Des simulations de réseaux de neurones binaires avec ce modèle de dispositif montrent que l'apprentissage est possible même sous le bruit et les variabilités intrinsèques à une telle mémoire. Dans le chapitre 3, nous explorons l'impact des imperfections et des contraintes découlant à la fois du niveau de dispositif et de circuit sur la performance d'inférence des réseaux de neurones. Nous démontrons la robustesse des circuits de calcul en mémoire à base d'HfOx qui implémentent des réseaux de neurones binaires face à des contraintes telles que la taille limitée du tableau, l'alimentation électrique irrégulière et la variabilité des dispositifs. Avec le chapitre 4, nous exploitons la stochasticité des nanodispositifs spintroniques, qui est généralement considérée comme une imperfection pour des applications plus conventionnelles. Ce chapitre propose les réseaux de neurones binaires bayésiens qui peuvent être réalisés avec de tels dispositifs. Nous soulignons l'utilité de ces réseaux : l'immunité à la surajustement et la quantification de l'incertitude dans certains scénarios pour une tâche illustrative à deux lunes et un ensemble de données médicales. Les résultats présentés dans cette thèse montrent qu'avec des innovations dans les algorithmes, les circuits et les dispositifs de mémoire, les imperfections peuvent être véritablement embrassées et qu'un avenir conscient de l'énergie et axé sur l'IA peut être envisagé.

# **ÉCOLE DOCTORALE**Physique et ingénierie: Electrons, Photons,

Sciences du vivant (EOBE)

**Title:** Embracing Imperfections: Hardware-compatible Neural Networks for Neuromorphic Computing

**Keywords:** Neural Networks, Memristors, Learning, Neuromorphic, Imperfections, Bayesian Neural Networks

**Abstract:** Recent developments in deep learning have pushed the limits of possibilities with large language models exhibiting outstanding capabilities, models for computer vision, and natural language processing exceeding human-level performance. However, this progress comes at the expense of immense power consumption while training such largescale models. From this perspective, the advance is not sustainable, especially considering the climate change concerns looming over the present day. The enormity of the energy consumption can be attributed to the architecture of conventional computers, which is not optimized for energy consumption for deep learning applications. On the other hand, the human brain excels at this aspect by performing complex pattern recognition tasks with a power budget that is orders of magnitude less than its computing counterpart. The difference arises from the fundamentally different way computation is done in the brain; for this thesis, we specifically focus on the co-location aspect of computing and memory, which is present in the human brain via the neurons and the synapses. In contrast, in the von Neumann architecture of a modern computer, the memory and arithmetic-logic units are physically separated, and a large amount of energy is expended in the shuttling of information between these units. In-memory computing with emerging memory technologies is a promising lead in this regard, where the co-location of memory and processing can be achieved, especially for the type of computations performed in neural networks. Nevertheless, this solution presents challenges in terms of performance as these novel classes of memories have dif-

ferent imperfections. For conventional implementations of neural networks with analog memories, these imperfections can considerably affect their performance. The central theme of this thesis is to embrace such imperfections for hardware-compatible neural networks. In chapter 2, we specifically look at the impact of these non-idealities in the context of training neural networks. We propose a physicsbased device model for HfOx-based memory that matches experimental results and can be incorporated within deep learning frameworks. Simulations of Binarized Neural Networks with this device model show that learning is possible even under noise and variabilities intrinsic to such memory. In chapter 3, we explore the impact of imperfections and constraints arising from both the device and circuit levels on the inference performance of neural networks. We demonstrate the robustness of HfOx-based in-memory computing circuits that implement binarized neural networks to constraints such as limited array size, irregular power supply, and device variability. With chapter 4, we harness the stochasticity of spintronics nanodevices, which is typically considered an imperfection for more conventional applications. This chapter proposes the Bayesian Binary Neural Networks that can be realized with such devices. We highlight the usefulness of such networks: immunity to overfitting and the quantification of uncertainty under some scenarios for an illustrative two moons task and a medical dataset. The results presented in this thesis show that with innovations in algorithms, circuits, and memory devices, imperfections can be truly embraced, and an energy-conscious, Al-driven future can be envisioned.

To the countless researchers, teachers, and students of science and technology whose names have been forgotten by history and will be forgotten.

# Acknowledgements

The first time I visited C2N was on the Good Friday of 2019. I saw the shining building of our lab for the first time amidst large empty areas that were under construction. Over the next three and a half years, I saw how this empty part of the plateau turned into a bustling campus full of institutes, offices, restaurants, and student residences. Over these three and a half years, I also worked on my doctoral research. And research, as it is today, is fundamentally collaborative, where a significant contribution comes from collaborators and colleagues. In that regard, the first person whom I would like to thank is my supervisor Dr. Damien Querlioz. I am truly grateful for your considerate, encouraging, and effective supervision. Discussing research with you has been a fantastic experience, and I would greatly miss our weekly meetings. One of my fondest memories of these years is our discussion in Crete, overlooking the beautiful Mediterranean Sea. Thank you, especially for your support during the lockdown period; it was much less stressful than it could have been due to your constant support.

Also, many thanks to Prof. Damien Deleruyelle, Dr. Louis Hutin, Dr. Dafiné Ravelosona, Prof. Luis López Díaz, Dr. Alice Mizrahi, and Prof. Jean-Michel Portal for accepting to take part in my PhD committee and carefully reviewing this manuscript. Moreover, I found the questions and discussions during my thesis defense exciting and thought-provoking.

The projects done in this thesis were highly collaborative in nature. And as such, it involved the participation of many researchers of diverse backgrounds, and I learned a lot from them. The first project involved collaborating with Dr. Marc Bocquet, and I am grateful to you for your support and prompt response to all my questions. Prof. Jean-Michel Portal has played an instrumental role in the first two of my projects, and my understanding of circuits increased significantly from the discussions with you. For my second project, I particularly collaborated with two fantastic PhD researchers, Dr. Mona Ezzadeen and Fadi Jebali. Mona, I greatly enjoyed the long discussion and brainstorming sessions with you, and I will always cherish the nice publications we produced together. I would like to particularly thank Fadi for his help in making me understand the circuits part of the second project. The third project was a unique experience as I collaborated with brilliant theoretical and experimental physicists. I learned much about Spintronics from Dr. Liza Herrera Diez and Prof. Luis López Díaz. Liza, thank you for being such a joyful and energetic presence in the lab, and I enjoyed our discussions about art and literature. In this project, I also collaborated with the brilliant researcher Djohan Bonnet. One of my favorite scientific moments in the lab was figuring out with you, the correct metrics for the estimation of uncertainty. I thoroughly enjoyed interacting and working with you, and I hope our paths cross again.

The lab is like a second home for researchers, and I was truly blessed to have a beautiful lab. But it's the people of the lab who truly made it feel like home. I feel grateful to have had amazing colleagues throughout my time. Bogdan, it has been fantastic knowing you, and I thank you for your assistance with the initial things at the lab, for inspiring my passion for Deep Learning

and for being a wonderful friend. The pizza dinner at your place was a nice bonding moment for everyone in the group. Thank you, Maxence, for being such a fun and supportive person! You lit up the lab's atmosphere and were a compassionate and supportive friend. I owe many of my accomplishments to Tifenn; thank you for teaching me the ropes of PyTorch and Binarized Neural Networks, which later became the foundations of my PhD thesis. Thank you, Axel, for all your patience and practical help with the first two projects. I loved interacting with such an excellent yet down-to-earth person. Before the pandemic hit us, talking to and working with all four of you was very fun. I missed your presence at the lab quite a lot.

It is not easy acknowledging the contribution of two of my best friends at the lab, Kamel and Xing, just because of the sheer amount of things I need to mention! I have many marvellous memories with both of you- from finishing challenging hikes in the Alpes to swimming in the warm Mediterranean Sea to discussing intense research. Surviving the multiple lockdowns would have been significantly more difficult without your presence. Kamel, thank you for teaching me to play football; you really rekindled my old love. Thank you also for sharing the very *different* kind of humor we possess. It was incredible how sometimes we could read each other's minds. And Xing, you are among the most courageous, smart, and considerate people I have ever met. Your cool, composed, hard-working personality is a massive inspiration for me. I sure hope that we can keep in touch.

Next, I would like to acknowledge the *next generation* of researchers in the group. Clément, thank you for always being there for my circuit-related questions and teaching me much about French culture, especially food. Thank you, Marie, for being such a great friend with whom I could freely discuss research and other fun topics. Your spiritful attitude contributes to the good mood of the group. One of the best memories during my PhD was when you presented a part of my first project! Thank you, Thibaut, for the nice moments at the lab; you were amazing as an officemate. Maryam, it was really fun knowing you and I enjoyed all our interactions. I would like to both thank and wish the very best to Thomas, both Adriens, Theo, and Akib for their contribution to the group and for their upcoming PhD journeys. I hope all of you enjoy your doctoral research days as much as I did in Integnano. I want to thank Bastien for the few days you spent at our lab and became a close colleague. Above all, I believe in all the upcoming projects in the group involving medical datasets, Eq-Prop in hardware, forwardforward algorithm, and the Ising machine. I am looking forward to the published results of those projects. I want to acknowledge Naim for being a cherished friend and allowing me to discuss science and engineering in my mother tongue. The four months you spent at our lab was a very special time for me, and I hope we keep in touch.

I would also like to thank my other friends in Integnano, firstly, Rohit. I shared the most amount of time at the office with you. I appreciate your kind nature, interesting sense of humor, and sharing common love for Biryani at Cafe Sunderban. Tanvi, well, it's also hard to acknowledge you! I got a friend and elder sister in you, which I never imagined I would find in this foreign land. I greatly cherished our discussions about food (although it annoyed Kamel)

ACKNOWLEDGEMENTS vii

and life in Germany. Thank you, Gyan, for being the Dutch friend I was missing from my life after my masters. It was great fun in all our interactions, and I would like to especially thank you for organizing and actively taking part in various group activities. Thank you, Song, for our occasional chats; it was nice to know you. Subhajit, thank you for being a good friend; I appreciate our frank discussions about differences in industry and academia.

I also had the incredible opportunity to befriend others at C2N outside our research group. I met Arup da at the 2019 end-of-year lunch, and since then, you have been such a remarkable presence during the first half of my PhD. I greatly appreciate the hospitality and care that you and Dipanita di showered on me. Thank you, Ritwik da, for help on many fronts; life at the lab would have been very different without you. I will miss the breaks when I can discuss many things at your office. Finally, I thank my closest friend in France, Sukanya. You meant a lot to me, and I will never forget the many experiences we shared. From going for long walks during the depressing lockdowns to cooking sumptuous meals from all over India to sharing happiness, and sadness; you are one of the most precious friends to me whom I got to know in France. I hope we meet in the future very soon.

I also want to thank all the people working at the C2N who contribute to making the lab run smoothly. Many thanks to Christophe Chassat and Alain Péan from IT, Lydia Andalon, Melissa Legendre, Léa Lemmaitre, Sylvie Lamour, and Bernadette Laborde from the administration, Sophie Bouchoule, Emilia Davodeau, and Jean-Christophe Ginefri from the doctoral school. Thanks also to the employees cleaning the lab every morning.

I feel very fortunate to find a family in the Bengali people residing in and around Paris. Centering around our great festival of Durga puja, we formed a close-knit family of people of different ages and backgrounds. Pabitra da and Debasmita di have been like guardians to me with their warm and welcoming presence. I will miss visiting your house in the lovely neighborhoods of Bures-sur-Yvette. I am grateful to Avigyan da and Atreyee di for all the beautiful memories we had together (not to forget the arrival of Arnaa, too!). You seldom find such amazing, kind-hearted people with whom you can connect on many aspects. Thank you for being my favorite people! Rohan da and Soumi di, thank you for being such incredible hosts for me. I loved our discussions at your place about anything and everything about life, people, and ChatGPT! I can't imagine a dull moment when I was in your company, and I would continue to cherish all those moments. Upasika, Anambar da, and Anwesh, how fun of a ride it has been to talk and laugh with you! It was tough saying goodbye to all of you. Sipra mashi, thank you for being such a lively person; I really look up to you in terms of your outlook on life. Performing theatre and other cultural activities with all of you will be some of the most memorable moments of my life. Saheli di, Dibya da, Subrata da, Rajesh da, Sonima di, thank you all for making life on the plateau much more enjoyable in the first half of my PhD. Thank you, Kanka da, for your support; I hope we meet again soon.

I want to end the acknowledgments by first thanking my family. Maa, Baba, bon, bhai, kaka, kamma, and thakun, this would not have been possible without your incredible support and

love. Your sacrifice, advice, and encouragement have been instrumental in completing my doctoral studies. And last but not least, I would like to thank Tista for being an absolutely amazing partner in my PhD journey. Your presence has been like a shelter of warmth and comfort for me, and it goes without saying that this wouldn't have been possible without you. Being a fellow PhD researcher, you truly understood what this journey feels like and stood by me throughout. Thank you for being there, thank you everything.

# **Contents**

| In | Introduction                             |                                                               |                                                 |    |  |  |  |

|----|------------------------------------------|---------------------------------------------------------------|-------------------------------------------------|----|--|--|--|

| 1  | Hardware implementation of deep learning |                                                               |                                                 |    |  |  |  |

|    | 1.1                                      | A brie                                                        | f history of memory and computing               | 8  |  |  |  |

|    |                                          | 1.1.1                                                         | Development of computing                        | 9  |  |  |  |

|    |                                          | 1.1.2                                                         | History of computer memory and storage          | 12 |  |  |  |

|    |                                          | 1.1.3                                                         | Memory in a modern computer                     | 14 |  |  |  |

|    | 1.2                                      | The ri                                                        | se of deep learning                             | 15 |  |  |  |

|    |                                          | 1.2.1                                                         | The rise and fall of AI                         | 15 |  |  |  |

|    |                                          | 1.2.2                                                         | Renaissance of AI: the deep learning revolution | 18 |  |  |  |

|    |                                          | 1.2.3                                                         | Supervised learning                             | 20 |  |  |  |

|    | 1.3                                      | Neuro                                                         | omorphic computing                              | 27 |  |  |  |

|    |                                          | 1.3.1                                                         | Memory requirements of deep learning            | 27 |  |  |  |

|    |                                          | 1.3.2                                                         | Inspiration from the brain                      | 30 |  |  |  |

|    | 1.4                                      | .4 In-memory computing with emerging memory technologies      |                                                 | 32 |  |  |  |

|    |                                          | 1.4.1                                                         | Filling the gap in memory hierarchy             | 32 |  |  |  |

|    |                                          | 1.4.2                                                         | Emerging memory technologies                    | 33 |  |  |  |

|    | 1.5                                      | Hardy                                                         | vare-based neural networks                      | 37 |  |  |  |

|    |                                          | 1.5.1                                                         | Memory architectures                            | 38 |  |  |  |

|    |                                          | 1.5.2                                                         | Neural network dedicated hardware               | 39 |  |  |  |

|    | 1.6                                      | 6 Challenges in learning: imperfections in resistive memories |                                                 | 43 |  |  |  |

|    |                                          | 1.6.1                                                         | Non-linearity and asymmetry                     | 43 |  |  |  |

|    |                                          | 1.6.2                                                         | Intra-device and inter-device variability       | 44 |  |  |  |

| 2  | Lea                                      | rning v                                                       | vith imperfect Resistive RAM                    | 49 |  |  |  |

|    | 2.1                                      | Backg                                                         | ground                                          | 50 |  |  |  |

|    | 2.2                                      | Hafni                                                         | um Oxide ReRAM Technology                       | 53 |  |  |  |

|    |                                          | 2.2.1                                                         | The technology                                  | 53 |  |  |  |

|    |                                          | 2.2.2                                                         | Weak RESET regime                               | 53 |  |  |  |

|    | 2.3                                      | Devic                                                         | e Characterization and Modeling                 | 54 |  |  |  |

|    |                                          | 2.3.1                                                         | Tunneling gan-based model                       | 54 |  |  |  |

CONTENTS

|   |                                                     | 2.3.2  | Mean model                                                            | 55  |

|---|-----------------------------------------------------|--------|-----------------------------------------------------------------------|-----|

|   |                                                     | 2.3.3  | Noise components                                                      | 55  |

|   |                                                     | 2.3.4  | Fitting the parameters                                                | 58  |

|   |                                                     | 2.3.5  | Comparison of experiments and simulation                              | 60  |

|   |                                                     | 2.3.6  | Algorithm for device model                                            | 61  |

|   | 2.4 Implementation within a Deep Learning Framework |        | mentation within a Deep Learning Framework                            | 63  |

|   |                                                     | 2.4.1  | Binarized neural networks                                             | 63  |

|   |                                                     | 2.4.2  | Training in ReRAM-based BNNs                                          | 64  |

|   |                                                     | 2.4.3  | Framework implementation                                              | 65  |

|   |                                                     | 2.4.4  | Algorithm for learning with device model                              | 67  |

|   | 2.5 Neural Network Simulation Results               |        | l Network Simulation Results                                          | 69  |

|   |                                                     | 2.5.1  | The tasks and the architecture                                        | 69  |

|   |                                                     | 2.5.2  | Impact of imperfections                                               | 69  |

|   | 2.6                                                 | Conclu | usion                                                                 | 70  |

| 3 | Imn                                                 | lomont | tation of BNN inference immune to circuit-based constraints           | 71  |

| J | 3.1                                                 |        | ts and Binarized Neural Networks                                      | 72  |

|   | 3.1                                                 |        | Imperfections in inference circuit                                    | 73  |

|   | 3.2                                                 |        | mentation of BNN with ReRAM bridges and capacitive neurons            | 76  |

|   | 3.2                                                 | -      | Circuit                                                               | 76  |

|   |                                                     |        | Measurement of error and error model                                  | 78  |

|   |                                                     |        | Neural network inference                                              | 81  |

|   |                                                     |        | powered memristor-based BNN                                           | 83  |

|   | _                                                   |        | Extreme-edge AI                                                       | 83  |

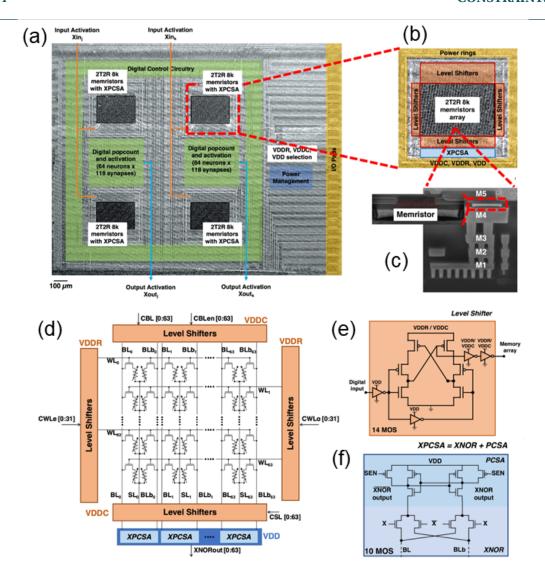

|   |                                                     |        | Circuit                                                               | 83  |

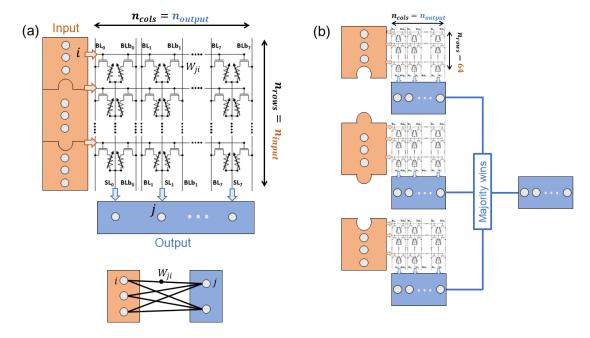

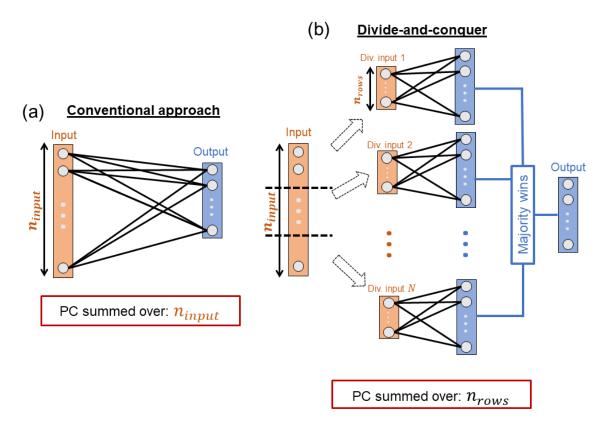

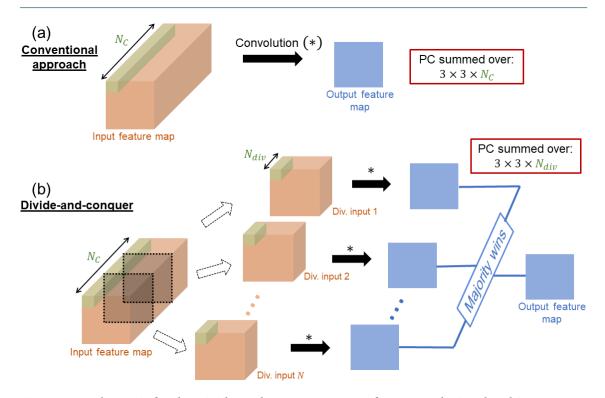

|   |                                                     |        | Divide-and-conquer mapping strategy                                   | 86  |

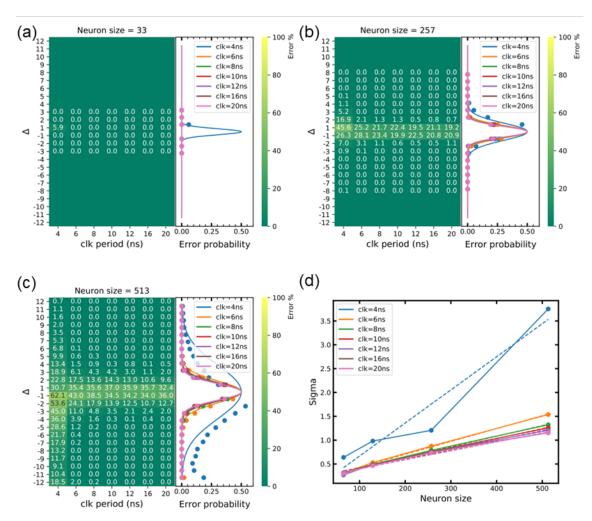

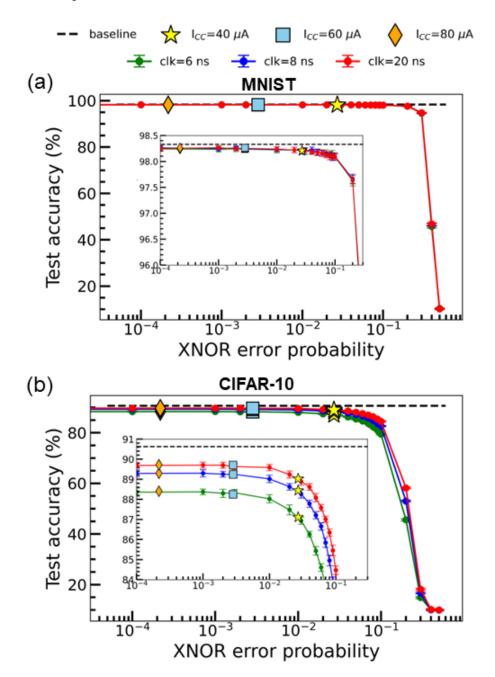

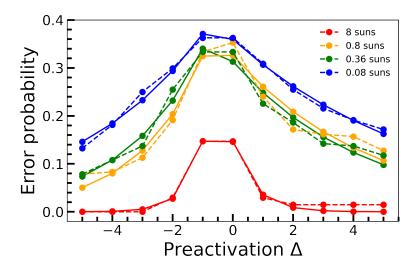

|   |                                                     |        | Error in the circuit inference                                        | 89  |

|   |                                                     |        | Neural network inference                                              | 90  |

|   | 3.4                                                 |        | usion                                                                 | 101 |

|   |                                                     |        |                                                                       |     |

| 4 | Bay                                                 |        | inary neural networks for uncertainty quantification in medical tasks | 103 |

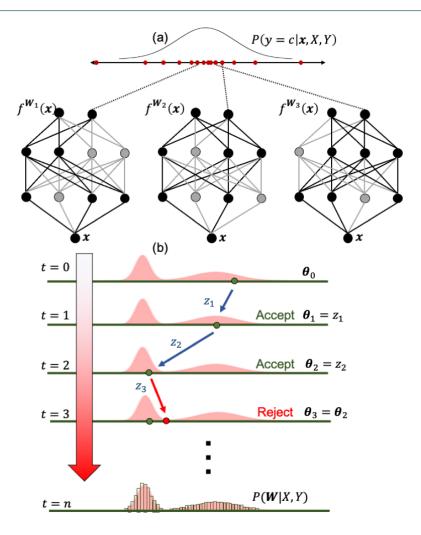

|   | 4.1                                                 |        | etical background                                                     | 104 |

|   |                                                     |        | Bayesian interpretation of probability                                | 104 |

|   |                                                     |        | Bayesian deep learning                                                | 106 |

|   | 4.2                                                 | Memri  | istor-based probabilistic ML                                          | 110 |

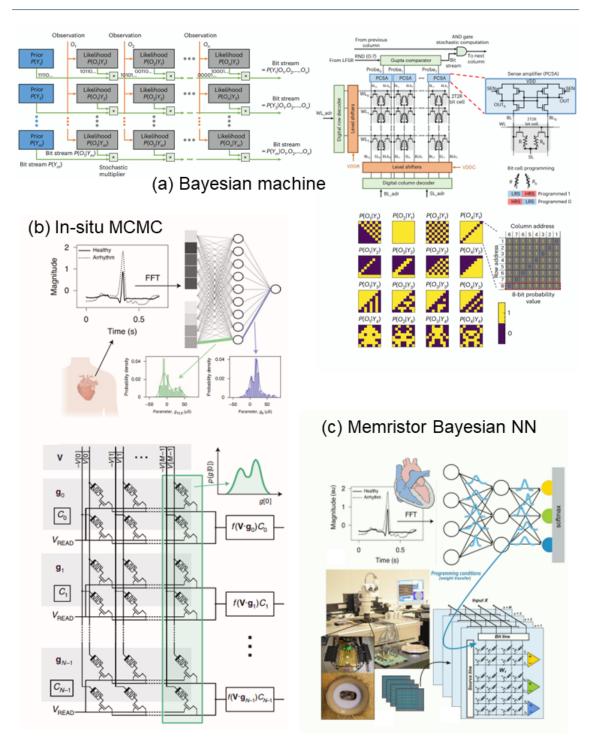

|   |                                                     | 4.2.1  | Bayesian machine                                                      | 111 |

|   |                                                     | 4.2.2  | MCMC on chip                                                          | 111 |

|   |                                                     | 4.2.3  | Bayesian neural network on chip                                       | 111 |

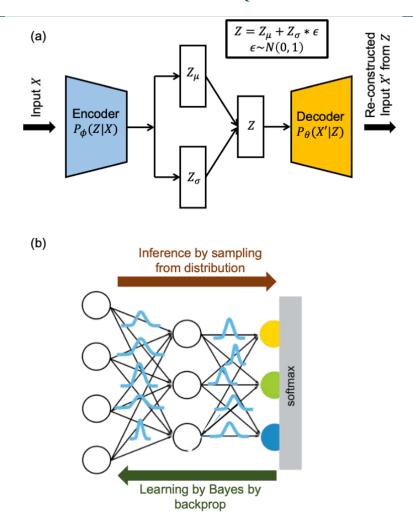

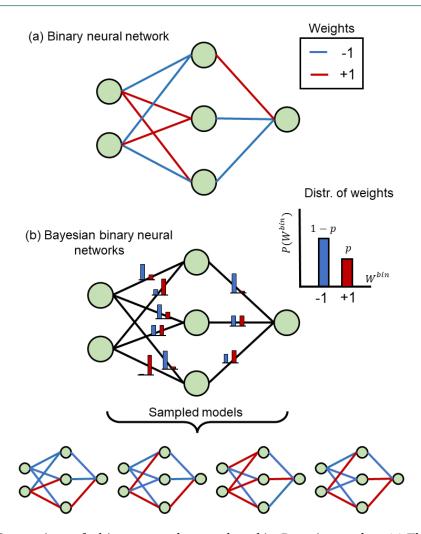

|   | 4.3                                                 | Bayesi | an binary neural networks                                             | 114 |

|   |                                                     | 4.3.1  | Architecture and inference                                            | 114 |

| CONTENTS | xi |

|----------|----|

|          |    |

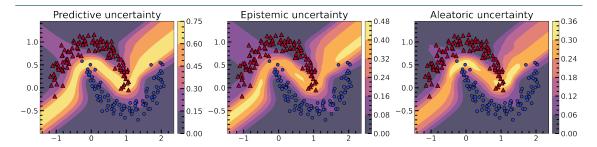

| 4.4                         | Uncer                | tainty quantification                 | 115 |  |  |  |  |  |

|-----------------------------|----------------------|---------------------------------------|-----|--|--|--|--|--|

|                             | 4.4.1                | Safety-critical applications          | 115 |  |  |  |  |  |

|                             | 4.4.2                | Quantification of uncertainty         | 117 |  |  |  |  |  |

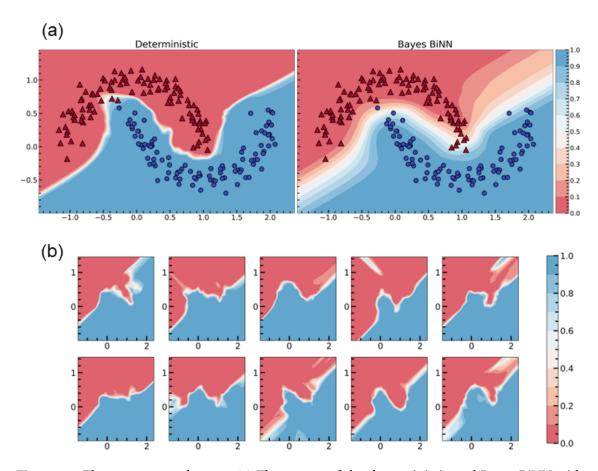

| 4.5                         | Two M                | Ioons dataset                         | 119 |  |  |  |  |  |

|                             | 4.5.1                | The dataset and methods               | 119 |  |  |  |  |  |

|                             | 4.5.2                | Uncertainty quantification            | 121 |  |  |  |  |  |

|                             | 4.5.3                | Impact of dataset size                | 121 |  |  |  |  |  |

|                             | 4.5.4                | Impact of label noise                 | 123 |  |  |  |  |  |

| 4.6                         | Medic                | al task                               | 127 |  |  |  |  |  |

|                             | 4.6.1                | The dataset and methods               | 128 |  |  |  |  |  |

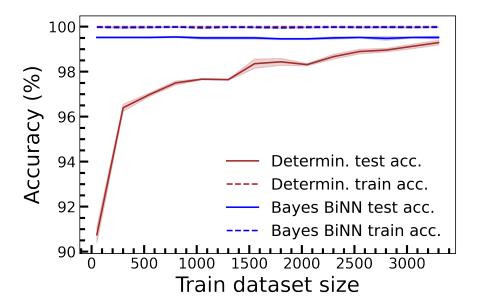

|                             | 4.6.2                | Impact of dataset size                | 128 |  |  |  |  |  |

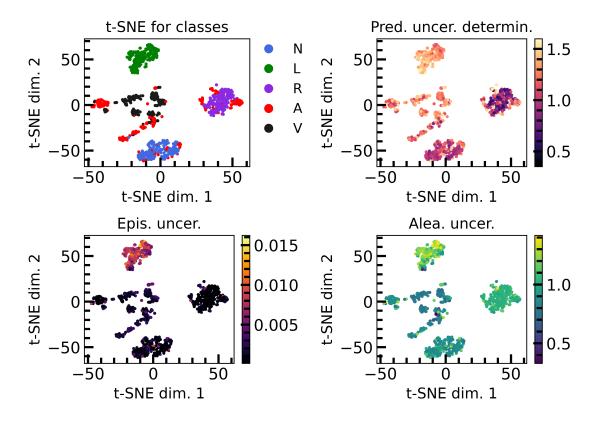

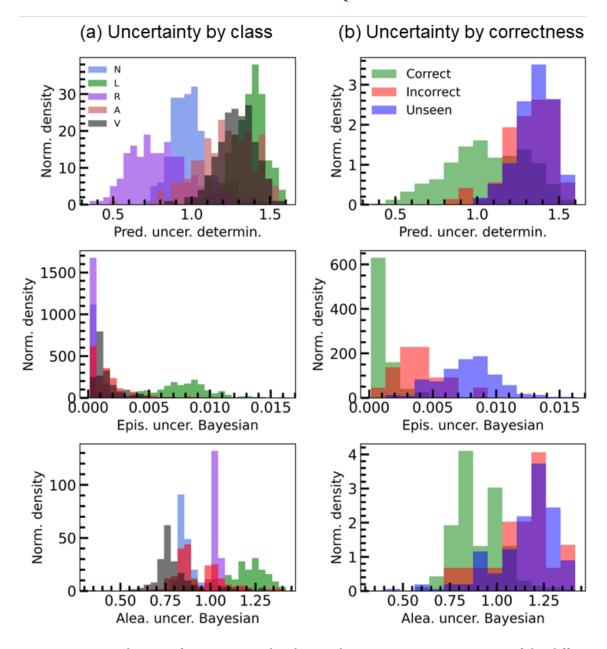

|                             | 4.6.3                | Uncertainty under realistic scenarios | 130 |  |  |  |  |  |

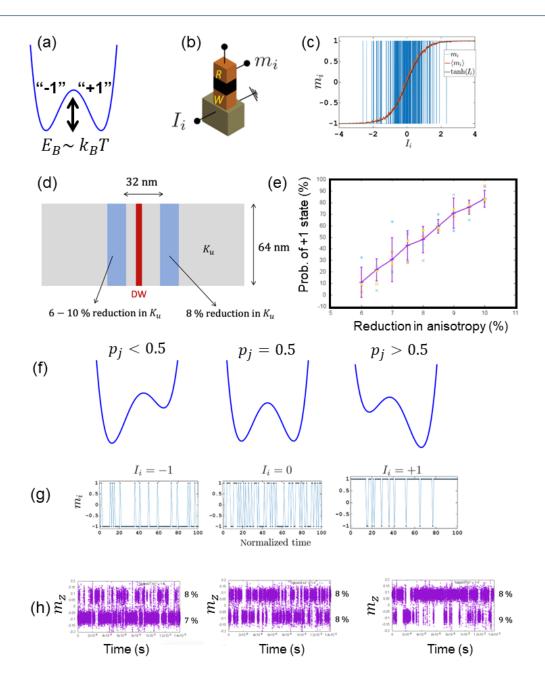

| 4.7                         | Spintr               | onics-based implementation            | 134 |  |  |  |  |  |

|                             | 4.7.1                | Candidate systems                     | 134 |  |  |  |  |  |

|                             | 4.7.2                | Device-based inference simulations    | 137 |  |  |  |  |  |

| 4.8                         | Concl                | usion                                 | 140 |  |  |  |  |  |

| Conclusions and future work |                      |                                       |     |  |  |  |  |  |

| Synthè                      | se (en f             | français)                             | 147 |  |  |  |  |  |

| List of ]                   | List of publications |                                       |     |  |  |  |  |  |

| Trainin                     | Training Bayes BiNN  |                                       |     |  |  |  |  |  |

| Bibliography                |                      |                                       |     |  |  |  |  |  |

**CONTENTS**

# Introduction

"The beginning is the most important part of the work."

Plato

PRESENTLY, we are at a critical juncture where on the one hand, we are experiencing the aggravated effects of climate change. One of the key reasons for this is the emission caused during the generation of electricity from fossil fuels [1]. On the other hand, we are making rapid progress in artificial intelligence (AI), with the large language models already showing preliminary indications resembling artificial general intelligence [2]. The recent progress takes us a step closer to the promises of AI that involve discovering drugs for acute diseases, self-driving cars, and other path-breaking innovations.

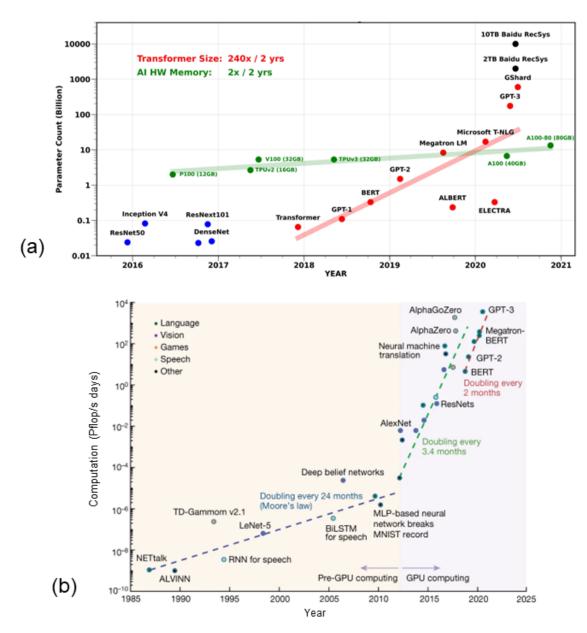

However, there is a cost to this: to develop, train and use the state-of-the-art deep learning models, existing computers expend a lot of energy. This type of computation, typically done in data centers with many Graphics Processing Units and other dedicated accelerators, is not usually optimized for their power consumption. Training a single model consumes more power than the amount consumed by 100 households in the United States in a year [3]. This number would only grow continuously with the ever-increasing model size and computational complexities. The resultant carbon footprint would be humongous, and this development is not sustainable from an environmental point of view.

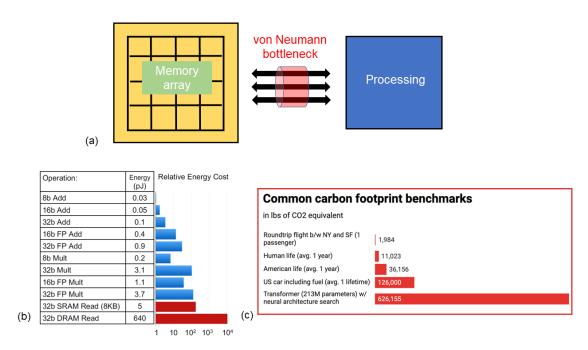

If we consider the computation process at an architectural level, the bottleneck in terms of energy consumption is related to the shuttling of data between the memory and logic units. During the training process of a neural network, three main operations are performed: shuttling data to and from memory and performing multiplication and addition operations in the processing unit. Among these operations, the transmission of information is energetically the most expensive. This computer architecture, called the von Neumann architecture, fundamentally differs from another system adept at pattern recognition tasks: the human brain. It can perform vision, natural language processing, logical deduction, and planning with an energy budget that is orders of magnitude less than what is typically consumed by a modern deep learning model. The brain computes differently: the connectivity is massive with substantial redundancy, the learning rules are local, the information is propagated in electro-chemically induced voltage spikes, and the logic and memory elements are co-located in the form of neurons and synapses. The field of neuromorphic computing aims to emulate or mimic the brain in terms of these aspects to perform more efficient computation. This thesis is about neuromorphic computing with architectural inspiration and attempts to mimic biology from the in-memory or near-memory computing perspective.

In particular, I investigate resistance-based emerging memory technologies for neural networks since they provide a more energy-efficient, CMOS-compatible, non-volatile substrate to perform computation near the memory than their more conventional counterparts (SRAM or DRAM). Low-power, non-volatile memories are well-suited for *edge* applications where power efficiency is prioritized. Additionally, their non-volatile nature is particularly advantageous for equipment that is not constantly used since no power is needed to store a state. Despite such advantages, emerging memories such as oxide-based resistive memories, phase change memories, and magnetic random access memories suffer from imperfections that can dramatically

affect the performance of neural networks. In this thesis, I investigate and present hardware-compatible neural networks which are tolerant to such imperfections to a reasonable extent and can even embrace them for performing computation. I attempt to answer the following questions in the second, third, and fourth chapters.

- Chapter 2 How can we learn with imperfect oxide-based filamentary resistive memory?

- **Chapter 3** What is the impact of errors and constraints arising at the circuit level on the inference of neural networks?

- **Chapter 4** Can we harness the stochastic nature of stochastic devices to perform probabilistic computing? And what additional advantages could it have?

More specifically, in Chapter 1, I lay the foundation of the thesis by elaborating on the background of my research. I start by describing the advancements made in computers and computer memory that subsequently facilitated the development of AI, especially deep learning. I chronicle the rise and fall of AI and the post-2000s resurgence. A detailed description of neural networks in supervised learning follows this. The ever-increasing sizes of models and the associated required computational prowess and their environmental consequences are then discussed. The concept of neuromorphic computing is introduced as a possible solution to this. After that, emerging memory technologies are discussed as the ideal candidates for in-memory computing systems capable of implementing neural networks in hardware. In this context, the different existing ideas about the hardware realization of neural networks are discussed in detail. The chapter concludes with a thorough discussion about imperfections in these kinds of memories, especially those that offer hindrances to learning, such as device-to-device variability, cycle-to-cyle variability, asymmetry, and nonlinearity.

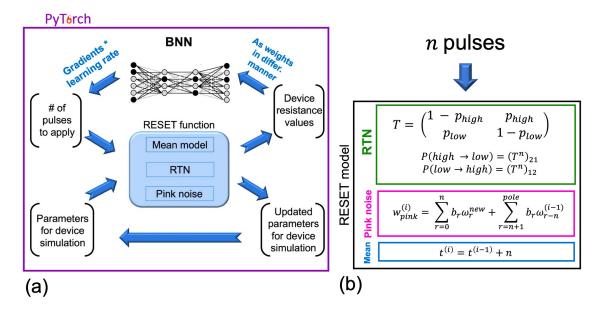

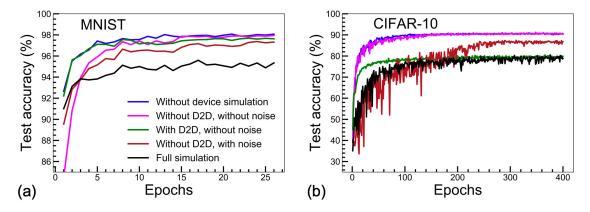

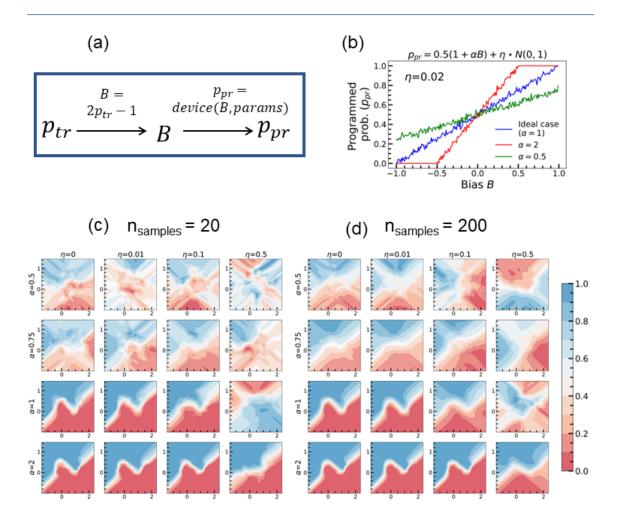

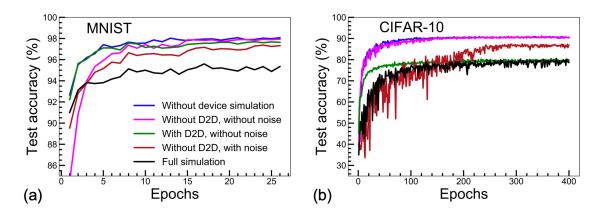

The second chapter is a study done in collaboration with Dr. Marc Bocquet from the Aix-Marseille University that was published in the journal IEEE Transactions on Electron Devices and was also presented at the CVPR 21 (conference on computer vision and pattern recognition) and the Neal 2022 (Göttingen, Germany) conferences, both as posters [4]. This chapter is about implementing learning in the weak RESET regime of HfO<sub>x</sub>-based filamentary resistive RAM using binarized neural networks. I start this chapter by presenting the background of this work, focusing on the importance of on-chip learning and emphasizing the main issues that make it challenging. Next, we introduce the memory technology and detail its co-integration with CMOS and the significance of the weak RESET regime that enhances the endurance of such memory devices, a crucial parameter for on-chip learning. Next, the main focus of this chapter is presented, where I developed a model that considers the different types of variabilities to explain the variation in resistance. Furthermore, I fitted the model to the experimental data and compared the simulations. After this, I describe binarized neural networks as an algorithm suitable for learning with such noisy memory. Then I outline the training process details and illustrate how I incorporated our device model within the PyTorch deep learning framework to simulate learning with these devices. The simulations are done to learn the MNIST

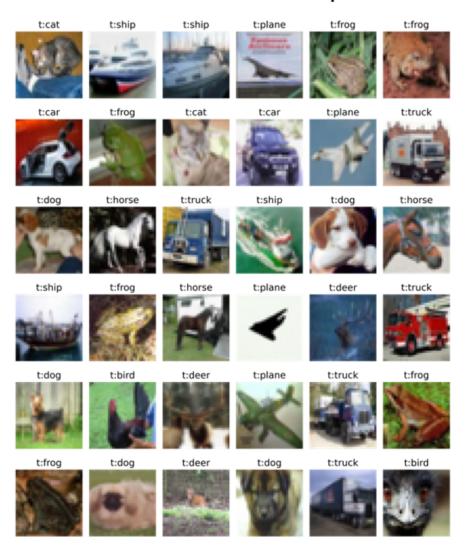

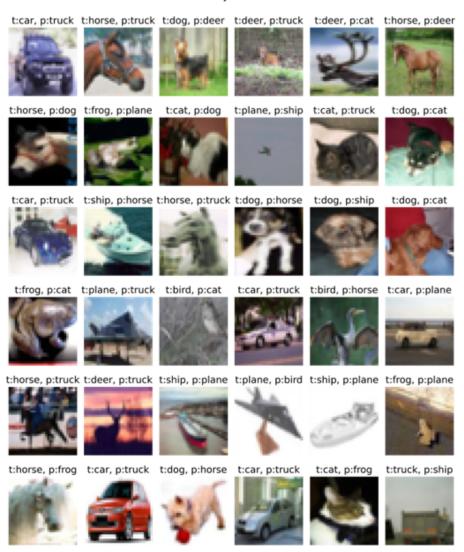

and CIFAR-10 datasets, and the test accuracies exemplify the robustness to different types of imperfections. I conclude the chapter by highlighting how this approach can be generalized to the simulation of other memory technologies.

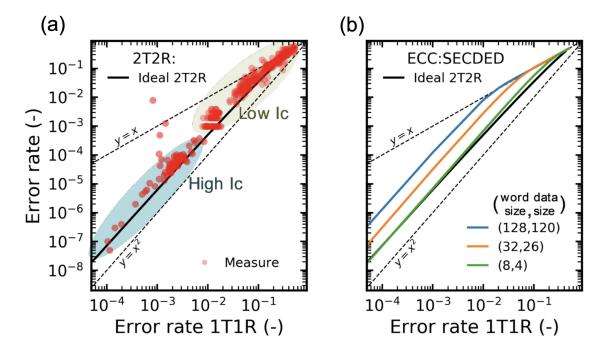

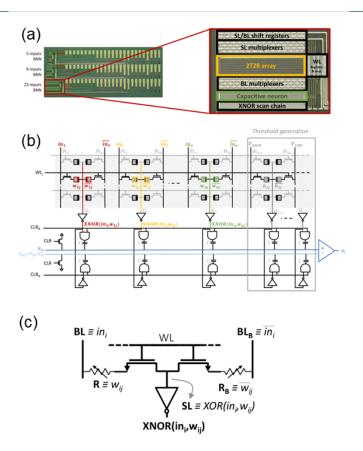

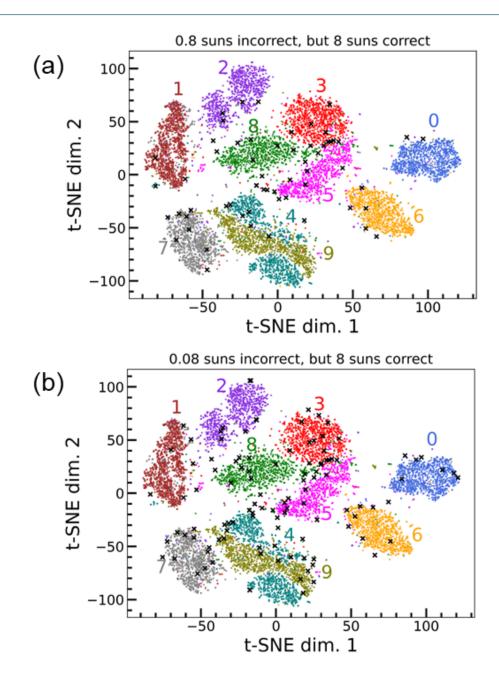

Chapter 3 is about the inference in binarized neural networks with constraints from circuitlevel implementation. This chapter is based on two scientific articles, one is under revision, and the other is under preparation. The first and second studies presented here were done in collaboration with Dr. Mona Ezzadeen and Fadi Jebali from Aix-Marseille University. In the first section of this chapter, I introduce general ideas related to the circuit-based implementation of binarized neural networks and illustrate the significant sources of errors originating from electronic circuits and memories. Next, I present the first study, detailing the circuit used to implement inference in binarized neural networks, the sources of errors, and their analyses. These errors are incorporated into neural network simulations to test how robust the prediction accuracies are to such errors. For the second study, I motivate the scenarios under which this type of circuit could be used: edge applications where the power originates from an energy harvesting system with irregular performance. Then, I present the circuits designed and characterized at the Aix-Marseille University, fabricated in CEA-Leti Grenoble, and present the associated errors and constraints related to the design. Here, I proposed and demonstrated an approach that circumvents array-size-related constraints at the cost of a slight degradation in accuracy. Finally, I use the experimentally characterized error for neural network simulations to show that the binarized neural networks exhibit robust computation even under a low power supply. This chapter highlights the suitability of binarized neural networks for inference, even with different levels of imperfection and constraints, which is especially promising for edge applications.

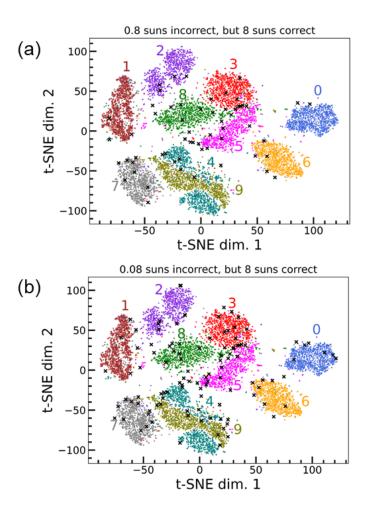

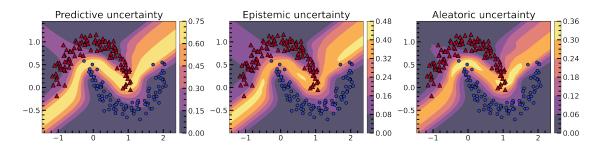

Chapter 4 differs from the earlier two chapters in that it accepts the imperfection and instead utilizes it for computation. In this context, I discuss Bayesian Binary Neural Networks, the probabilistic analog of binary neural networks where only the weights are binarized. This is a study in progress for which we are starting to prepare a manuscript, and it was presented as a poster at the MagnEFi 2022 conference in Crete, Greece. I begin the chapter by reviewing the theory behind probability-based computing, focussing on ideas related to Bayesian deep learning methods. Next, I discuss some recent studies where the concept of probability-based computing has been realized with emerging memory devices. These ideas give us a glimpse at the potential of this computing paradigm. After that, I discuss the Bayesian Binary Neural Networks theory, emphasizing its differences from its deterministic analog. Here, I introduce the idea of quantifying uncertainty, which is one of the main advantages of using Bayesian Neural Networks and is essential for safety-critical applications. I use this type of neural network for a toy example, the two moons dataset, and demonstrate some scenarios under which our neural network provides robustness or more insight than the deterministic network. After this, I utilized this algorithm to learn actual medical tasks, the MIT-BIH dataset for arrhythmia detection, and showcased its unique advantages. Finally, we end this chapter by discussing some

spintronics-based possible systems that could be used for realizing this algorithm and present results related to performing inference with them.

# Chapter 1

# Hardware implementation of deep learning

"If I have seen further, it is by standing on the shoulders of giants."

Sir Isaac NEWTON

THIS CHAPTER serves as a preface to the new ideas and results presented in this thesis. We start by looking back at the past; the historical developments that led to the technology today. After that, the present is discussed: the state-of-the-art and its shortcomings, and from there, the necessity of the research presented in this thesis is motivated.

After discussing the history of computing and memory, it introduces deep learning as a consequence of modern memory-compute capabilities and the abundance of data. Then, it highlights the problems and challenges that deep learning will encounter in the near future and, with this background, introduces brain-inspired or neuromorphic computing. It reviews the development of neuromorphic computing in the light of implementing deep neural networks in hardware with brain-inspired principles that aim to address the energy constraints deep learning faces. Finally, it elaborated on the challenges encompassing the hardware implementation related to the various imperfections present in emerging technologies.

# 1.1 A brief history of memory and computing

The scientific and technological progress of our race is evident from the fact that it took us about 4000 years from the invention of the wheel to the first successful airplane launch, but only just 66 years between the first airplane and the landing on the moon by Neil Armstrong. Many of these advancements were facilitated by the rapid progress made in terms of computing technology; the invention of the modern computer allowed us to automate complicated tasks and do large-scale calculations fast.

The modern computer we use so ubiquitously is the result of technological progress spanning centuries. It required simultaneous developments in multiple fields of science, including physics, mathematics, electronics, and computer science. Each successive generation of computing technology expanded the boundaries of our capabilities, thereby creating newer opportunities that were previously unimaginable. The cyclic nature of the necessity-invention cycle propelled growth at an exponential rate as well as the need for computational power and memory.

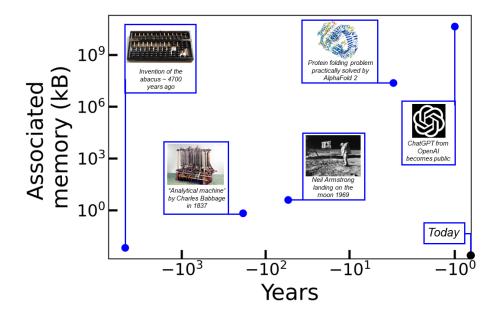

In computing terms, memory refers to the information a certain calculation needs to execute. Fundamentally, a computer is composed of two primary components: the memory unit, which stores information, and the arithmetic-logic unit, which performs operations on that information. The memory required for computation strongly correlates with the task's complexity, as depicted in fig. 1.1. If we focus on some distinct events in the history of human civilization: the invention of the abacus, the conceptualization of the Analytical engine, the first general-purpose computer by Charles Babbage in 1837, the first landing of a human on the moon in 1969, the *solution* of the protein folding problem by the deep learning program AlphaFold 2, and the release of the large language model-based ChatGPT in 2022, we see that the memory associated with each of these developments, as well as the computational needs increase exponentially. Another thing to notice here is that the time difference between such

Figure 1.1: Timescales and the associated memory for some of humanity's most important inventions or events. The Sumerian abacus, considered one of the foremost calculating machines, appears in archaeological evidence as early as 2700 BCE. Charles Babbage invented the Analytical engine, considered the first general-purpose computer, in 1837. In 1969, Neil Armstrong became the first astronaut to land on the moon, embarking upon the Apollo 11 spacecraft, which had the Apollo Guidance Computer as the main computing unit. The 50-year-old protein folding problem, one of the biggest questions in structural biology, was solved by the AlphaFold 2 deep learning algorithm in the year 2022 at the CASP 14 event. In 2022 OpenAI released ChatGPT, an online bot based on the large language model GPT3 that can answer questions from a human prompt. In this figure, the associated memory for the deep learning models has been calculated based on the total number of parameters present, which essentially gives a lower limit on the required memory because training such models requires more memory than just the parameters.

major advances is shortening, signifying the speed of these developments.

With this importance of computer memory in mind, let us look at the historical development of computers and the role memory has played in them.

# 1.1.1 Development of computing

A typical smartphone today can store up to 4 billion bytes of data and can function like a desk-top computer. To understand the root of the invention of such technological components, we turn the pages of history to study the progress made in the early days when the computer had mechanical parts, unlike today.

#### 1.1.1.1 Mechanical calculators

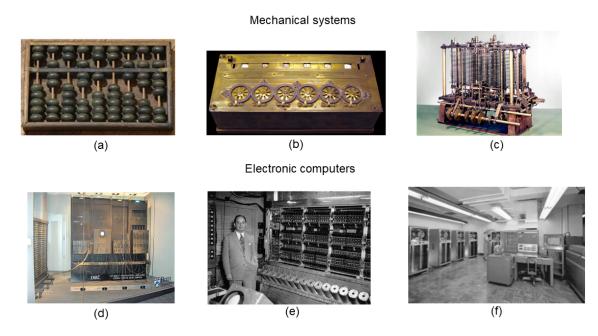

The abacus is the earliest instrument that can be called a calculator or, very broadly, a computer. As shown in fig. 1.2(a), the abacus consists of several movable columns of beads, and a single arrangement of the beads denotes a single number. This device allows for calculations such as addition, subtraction, multiplication, division, and even taking the square or cube root of a number. Such computations are performed by manually moving the beads [5]. Another early prototype of the modern calculator was invented by the French inventor Blaise Pascal in 1643 (fig. 1.2(b)) [6]. The Pascal calculator relied on a set of gears and springs to implement

Figure 1.2: Computers through the ages. (a) An abacus, the first ever calculating device used as early as 2400 BCE by the Babylonians. (b) The Pascal calculator. (c) A model of Charles Babbage's Analytical engine. (d) The ENIAC computer. (e) John von Neumann posing with the EDVAC computer. (f) The IBM 704 mainframe computer occupies a whole room.

simple arithmetic operations on numbers represented by the wheels' position. While these devices are capable of efficiently performing arithmetic operations, they are not programmable, thus rendering them unsuitable for automation purposes. The Jacquard loom machine is one of the earliest examples of an instrument where a textile loom could be programmed to function in a certain way. The machine is essentially a control mechanism for the loom in which a chain of *punched cards* are used as the input for a pattern, and the loom patterns automatically [7].

However, all the aforementioned examples are quite far from modern computers. The first design of a general-purpose computer, albeit mechanical, was proposed by Charles Babbage in 1837, named the Analytical engine (fig 1.2(c)). This was the first computer to have integrated

memory in the form of counter wheels, a dedicated arithmetic logic unit, a control flow that enabled loops and conditional branching, an input system with punched cards, and even a printer for producing the output [8]. After that, there were more instances of mechanical or electro-mechanical computers, but all of them had constraints intrinsic to mechanical systems, like speed issues and mechanical wear-and-tear. Furthermore, these were analog computers and consequently were less robust to noise and inefficient.

#### 1.1.1.2 Electronic computers

It took more than a century after this for the first digital, electronic, programmable computer to emerge. In 1945, the Electronic Numerical Integrator and Computer, or ENIAC, was completed at the United State army's Ballistic Research Laboratory [9]. The construction of this computer, shown in fig. 1.2 (d), was enabled by the developments in electronics in the earlier half of the twentieth century. In particular, the invention of the thermionic vacuum tube paved the way for performing logic efficiently [10]. A technological successor to ENIAC was EDVAC (Electronic Discrete Variable Automatic Computer), which was completed in 1949 at the Moore School of Electrical Engineering in Pennsylvania [11]. The celebrated engineer John von Neumann was involved with this project as a consultant (fig. 1.2(e)), and he proposed in his monograph First Draft of a Report on the EDVAC the architecture-level organization of a computer [12]. This came to be known as the von Neumann architecture, and it represented a computer architecture with several components: a memory unit, an independent arithmetic logic unit, a control unit, and mechanisms for input and output. Later in this chapter, we shall discuss this architecture more in the context of the energy efficiency of a modern computer. The type of internal memory used for these computers were mercury-filled tube-based delay lines, a type of acoustic memory [13].

The next generation of computers was heralded by the invention of the magnetic core memory when Jay Forrester utilized the hysteresis property of magnetic cores. The main advantage of this was that it was truly random access, unlike its predecessors which had a serialized relay of information. The earliest computer to use this was Whirlwind I in 1951 [14], the first computer ever to produce real-time output and function in parallel mode. The year 1954 saw the advent of the first mass-produced computer IBM 704 (fig. 1.2(f)), which was a digital mainframe computer with hardware capable of performing floating-point arithmetic. The following decades saw the development of transistors and integrated circuits, replacing vacuum tubes totally. These rapidly decreased the computer's cost and size and culminated in the invention of the first personal desktop computer, IBM-PC, in 1966 [15, 16].

The history of computers shows us that the advancement of computers didn't happen in a vacuum, and the technological progress of memory devices was closely intertwined with it. With this in mind, let us delve into the history of the development of computer memory itself.

### 1.1.2 History of computer memory and storage

Computer memory is any system or device storing information for immediate computations. Storage memory, on the other hand, refers to the device that can preserve information over a much longer time period and that is not necessary for computations very frequently. For example, in a smartphone, the memory is where the operating system and application software are stored, whereas the storage consists of photos, videos, and documents. Thus, a computer needs a hierarchy of different types of memories to function.

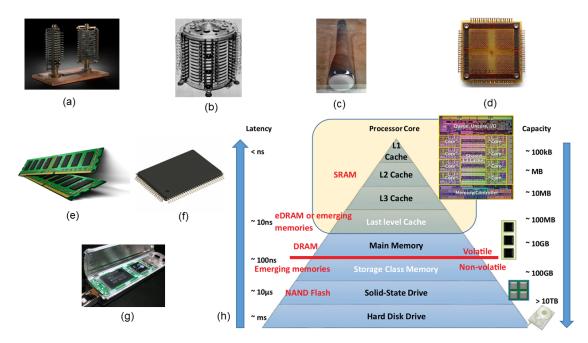

Punched cards can be considered the earliest forms of memory that a computer could use. In these cards, the information was encoded in the form of holes in cards of stiff paper [17]. A typical characteristic of these early forms of memory was the physical state of the device used to encode the information. A fundamental problem with these is that the physical dimension required to represent a single bit of data is quite big, and thus, the access speed is limited by the arrangement of the data. The design of Babbage's Analytical engine used the rotational state of counter wheels (fig. 1.3(a)) for internal memory and punched cards to input information.

Figure 1.3: Memories of yesterdays and today. (a) Counter wheels played the role of main memory in Charles Babbage's proposed Analytical engine. (b) The magnetic drum memory, along with the read-write heads attached to the cylinder. (c) The William-Kilburn tube, which is a modified Cathode ray tube. (d) The magnetic core memory with the toroids is arranged in four grids and connected by wires for reading and writing. The commercially available forms of (e) Dynamic Random Access Memory (DRAM) and (f) Static Random Access Memory (SRAM). (g) NAND Flash memory inside a USB stick. (h) The hierarchy of memory and storage in modern computers (adapted from [18])

As shown in fig. 1.3(b), magnetic drum memory was one of the earliest devices to use mag-

netism to store data. These were large metallic cylinders with ferromagnetic coating on them, and the magnetic polarity of the film represented the data. There were multiple parallel readwrite heads to read and write information from and on the drums as the drum rotated; thus, the access speed was limited by the rotation speed of the drum. Nevertheless, this form of memory was used until as late as the 1960s [19]. An earlier version of this utilized capacitors to achieve the same, but a major drawback was that those needed to be refreshed periodically. A similar memory device is the magnetic tape data storage, which also had a long latency owing to its physical shape but has superior data storage density and endurance (the ability to endure many cycles of switching of memory bits), both of which are important attributes by themselves and are the reasons for its survival even to this day for data archiving.

In the early years of 1940, the success of delay lines in early RADAR systems inspired the development of mercury-based delay lines as a memory device. In this technology, a tube filled with mercury, a quartz transducer, and a receiver comprised a memory device. The transducer was able to produce acoustic waves in the tube, which propagated and were received at the other end. The presence or absence of a wave denoted a bit in such memories, and a single tube typically stored about 1000 bits of data with an access time of just over 200  $\mu$ s [20]. The mercury-tube delay lines were used in the UNIVAC I (Universal Automatic Computer I), which was the successor to the ENIAC, and the first digital general-purpose computer manufactured for business applications [21].

Apart from latency, data storage density, and read and write times, the fashion in which data is accessed is another important metric. Conventionally, there are two different types: sequential access memory (SAM) and random access memory (RAM). In sequential access memories, the data is stored in a sequence, so there's always a substantial time needed to find specific data. On the contrary, RAM enables the access of data in any order. The delay line memories were of the first kind owing to their intrinsic sequential nature and thus were not suitable for situations that necessitated random access. Around the same time, the William-Kilburn tube was also invented as a random access memory. This tube (fig. 1.3(c)) is a customized Cathode ray tube, where the electron beam could create a charge well in the face of this tube, and a read plate was used to sense the absence or presence of that well representing the memory. This was random access since the electron beam could position itself anywhere on the screen quickly, and thus any bit of data could be accessed at a time. This system also required periodic refresh due to the leakage of charge, and the data read was also destructive [22].

The next major development came in the form of magnetic core memories. A single bit of this memory comprised a core, a magnetic toroid with an electric wire connected to it. The current flow magnetized the core, the direction of the magnetization depending upon the direction of the current and encoding a single bit. This state would be preserved even when no current flows through the core, owing to the hysteresis property of ferromagnets. Such cores were arranged in a grid (fig. 1.3 (d)) with wires connected to facilitate the reading, writing, and selection of a single core. The success of this memory can be attributed to its random access

nature, robustness, and the lower access time of 5  $\mu$ s compared to the delay-line memories [14, 19].

### 1.1.3 Memory in a modern computer

Further advancements in computer memory and storage happened hand-in-hand with the progress of transistor technology. The main advantages of transistors are that they are smaller, faster, less power-hungry, and cheaper than the existing solutions of that time. In the year 1966, at the IBM Thomas J. Watson Research Center, the field effect transistor memory or DRAM (dynamic Random Access Memory) was invented. It was built on a semiconductor process with a single silicon transistor and a capacitor in a cell, and the two memory states are represented by the charged or uncharged state of the capacitor. The capacitor circuit element suffers from the leakage of the charge, and hence, this also needs periodic refresh like the Williams tube (fig. 1.3 (e)) [23], from which it derives the 'dynamic' in its name.

Although DRAM is cheap and has a low area overhead, the data access is slower (10-100 ns), which is not desirable in certain cases, like in cache memory or in internal registers. SRAM, or Static Random Access Memory, invented in the early 1970s, is the choice of memory in such cases. A single SRAM cell consists of 6 transistors and hence can have a significantly lower memory density and be more expensive compared to a DRAM which has a single transistor per cell. However, the on-chip location of SRAM, coupled with the fact that it has a small array size with less number of wires and consequently less delay, the memory can be accessed much quicker (a few ns) (fig. 1.3 (f) [18].

Despite the fact that DRAM and SRAM are crucial elements of computer memory, they are volatile; that is, the cell loses its memory when the power supply is turned off and thus cannot be used for storage. Dr. Fujio Masouka, working at Toshiba in the year 1987, invented the Flash memory, a non-volatile, electronically programmable memory [19]. A single cell of such a memory consists of a floating gate transistor, where an additional insulated gate lies between the control gate and the MOSFET channel. The presence or absence of charge in this gate represents the memory states. Since it is electrically insulated, the memory is stored even in the absence of a voltage supply. The NAND flash cell is typically used for storage due to its cheaper cost and high memory density. It is the principal building block for solid-state drives (SSDs), smartphone storage, and USB sticks, as shown in fig. 1.3 (g). Although it is more expensive than the conventional hard-disk drive (HDD), which is magnetic storage with mechanically moving parts, the SSD is faster, smaller, less noisy, more durable, and more energy-efficient.

A computer is a complex device that requires different types of memory storage, each with specific requirements for various applications. The range of storage options spans from the cache memory, which requires speed over size, to the hard disk drive storage, which prioritizes a large size over access speed. Fig. 1.3 (h) details the complete memory hierarchy present in the modern computer that has been discussed in this section. The timescales span from less than a nanosecond to about a couple of milliseconds, and the memory capacity extends from 100s

of kB to more than 10s of TB. Within the extent of these huge time and memory scales, there are gaps that different emerging memory technologies are trying to bridge. We shall discuss such memory later in this chapter. It must be emphasized that the rapid development of transistor technology is enabling the integration of more and more transistors on a single chip, and that, in turn, is giving us access to smaller and more powerful computers. The IBM 704 mainframe computer, with a memory of about 18.4 kB, occupied a whole room, whereas a typical smartphone today has a RAM of 8 GB. Moore's law summarizes this in the form of the statement that the number of transistors on a microchip doubles every two years [24, 25]. Amongst the many benefits that were derived from this, the progress in the field of AI is quite significant.

# 1.2 The rise of deep learning

The exponential development of technology has been driven by the fact that development in a single very important domain affects several others, which continues the same way to produce an avalanche. The huge advancements in computing power, memory capacity, and the availability of an astronomical amount of data have led to the resurgence of deep learning, a special class of artificial intelligence (AI) algorithms.

We start this section with a short history of AI. Then we move on to specifically focus on the resurgence of this field with the support of memory capabilities. Then finally, we discuss the basic ideas behind the deep learning algorithm.

#### 1.2.1 The rise and fall of AI

The modern form of AI that we observe today arose from innovations in different science and technology domains. Algorithmically, the earliest progress could be traced back to the first half of the 19th century when the least square regression and gradient descent methods were formulated, which have been the backbone of the deep learning algorithms, even today [26, 27]. But, it wasn't until the summer of 1956 that the field of AI was formalized at the Dartmouth workshop in the United States of America [28]. Amongst the organizers were John McCarthy, who was the person to coin the term AI to this domain, Nathaniel Rochester, the chief architect of the IBM 701 computer, and Claude Shannon, who is considered the father of information theory. In the conference, topics like creativity, abstraction, computer architecture, computational theory, neural networks, and natural language processing were discussed, which remain relevant even today [29].

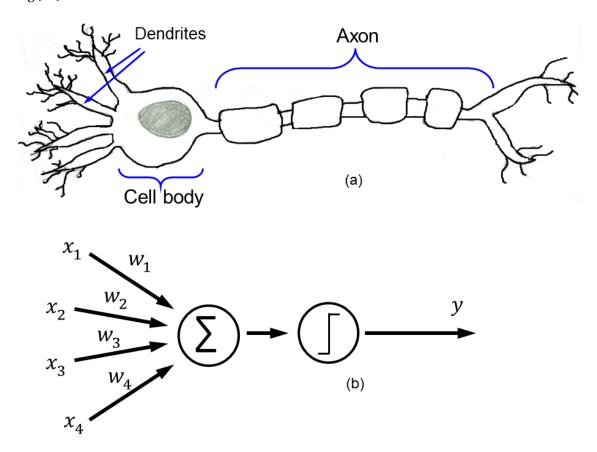

Developments in these aspects were driven mostly by mathematicians and computer scientists, but there was another line of progress that contributed equally. These were attempts by a group of biologists who took inspiration from the nervous system of animals to build *bottom-up* model for intelligence. Warren McCulloch and Walter Pitts proposed a simple model of neurons based on its topology where a single neuron accumulates the inputs that it receives

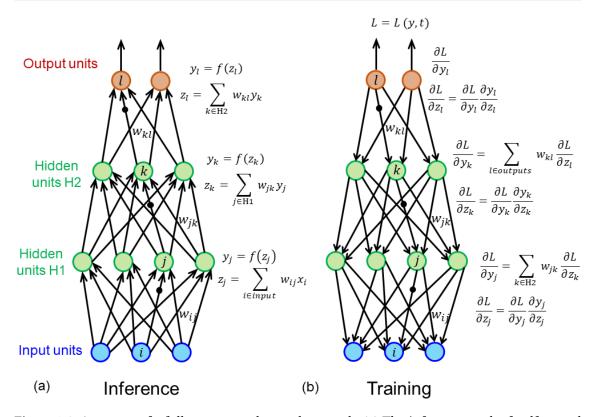

weighted by the synaptic connection strengths and applies a non-linearity to it to produce the output [30]. This model, shown in fig. 1.4, is widely used in neural networks. Biophysicists Alan Hodgkin and Andrew Huxley extended this idea by introducing the concept of dynamics, which, as it turns out, is a crucial aspect of biological neurons [31]. The Canadian neuropsychologist Donald Hebb took this idea of dynamics to suggest a simple learning algorithm based on the temporal correlation of connected neurons, which came to be known as Hebbian learning [32].

Figure 1.4: The analogy between a biological neuron (a) and an artificial neuron (b) as proposed by McCulloch and Pitts. Through their respective synapses, the dendrites bring in electrical voltage pulses to the cell body, where the signal undergoes processing and eventually propagates through the axon onto the next set of neurons. In an artificial neuron, the inputs  $x_1, x_2, x_3, x_4$  are summed up after being weighted up by their respective weights  $w_1, w_2, w_3, w_4$ , and then passed through a non-linear activation function to output y.

The question of having the correct learning rule bugs researchers even today and the bioplausibility of a certain learning rule is often debated. In [30], McCulloch and Pitts discussed ideas that led to the first implementation of a perceptron by Frank Rosenblatt, which is the most rudimentary form of a neural network [33], and the structure is as shown in fig. 1.4(b). It can do a classification or regression task where the N inputs  $x_1, x_2, ..., x_N$  are fed into the

perceptron, where the output y is calculated by taking their linear combination with weights  $w_1, w_2, \dots, w_N$ , and after passing through a non-linear function, which was the Heavyside step function in the original perceptron formulation. The nonlinearity is an important ingredient as a linear setup could learn functions that were linear, which isn't the case most of the time in reality. Learning a good mapping from the input to the output corresponds to learning an appropriate set of  $w_1, w_2, ..., w_N$ , which are referred to as the synaptic parameters because of their functional resemblance to biological synapses. The learning rule for the perceptrons in the simple delta rule is based on the gradient descent algorithm [34]. In this algorithm, a loss metric is defined, which quantifies how far the perceptron is from giving a correct output. Then the parameters are updated in a way that minimizes this metric. This is in contrast to the bio-plausible Hebbian learning and solely depends on the iterative arithmetic updates of the parameters of the system. Although the very first implementation of the perceptron was in software on the IBM 704 computer, eventually, a machine was designed called the Mark I perceptron in 1958. It was connected to 400 photocells in a 20×20 grid, which was then connected to neurons, and the synaptic weights were implemented by potentiometers whose resistance value encoded the weights. The update of the weights was carried out by electrical motors [35]. This physics-based implementation is surprisingly not dissimilar to the hardware implementation of neural networks today, broadly speaking.

This methodology of reducing pattern recognition tasks to simple networks where the output is connected to the input by mathematical operations was termed as *Connectionism*. Initially, the promise behind such an algorithm was huge, and scientists and media alike publicized that general artificial intelligence was just within reach; however, before the 70s, this came to an end. A book called Perceptrons was published in the year 1969, highlighting their severe limitations and criticizing the hyperbolic predictions associated with it [36]. This book What followed was almost two decades worth of disinterest, lack of funding, and research in AI, which is referred to as a period of AI winter [37].

In the 1980s, several developments aroused the interest in AI research anew. In contrast with Connectionism, another AI philosophy relied on symbolic reasoning, such as using decision trees with if-else branchings based on some logic to reproduce intelligence. This gave birth to *expert systems*, a class of computer systems that could emulate the decision-making process in very specific domains [38]. The cause of connectionism was also revived by the physicist John Hopfield in 1982, who proposed Hopfield networks which were a novel, efficient, and biorealistic implementation of neural networks [39]. From the theoretical side, George Cybenko proved the universal approximation theorem, which stated that an artificial neural network (ANN) with a single hidden layer is able to approximate any continuous function for inputs within a specific range of values [40]. A hidden layer in a neural network refers to an additional set of neurons between the inputs and outputs, which aims to learn intermediate values, simplifying the classification task in the successive layer. The deep neural network is a network that has one or more such hidden layers of neurons. David Rumelhart and Geoffrey Hinton

introduced the method of backpropagation as a method to learn the parameter values of such multi-layered networks [41].

Nevertheless, the general interest in ANNs was also short-lived, as, by the beginning of the 90s, many of the new developments failed to offer practical solutions. The expert systems couldn't generalize to other tasks, and it was very hard to manipulate or improve systems based on symbolic computations. However, other machine learning methods like the support vector machine (SVM) or the K-nearest neighbors were extensively used during this time. After this, it would take about two decades for the resurgence of ANNs to take place.

### 1.2.2 Renaissance of AI: the deep learning revolution

The following decades witnessed the sheer dominance of computing power in the context of AI applied to domains where human expertise was considered superior. Riding the wave of Moore's law, computers became powerful in the count of memory as well as processing speed, and a direct result of this could be seen in the defeat of the famous Gary Kasparov to the IBM computer called Deep Blue in a game of chess in the 1997 [42]. Another noteworthy accomplishment of AI during this period included the proof of Robin's conjecture in theoretical computer science by the AI automatic theorem prover known as EQuational Prover in the very same year [43]. In 2005 and 2007, significant demonstrations were made by autonomous vehicles in the DARPA Grand Challenge and DARPA Urban Challenge, respectively [44, 45].

However, these achievements relied on machine learning techniques that were not based on deep learning. The first major breakthrough that ushered in the era of deep learning was when Krizhevsky et al. won the large-scale ImageNet competition in 2012 by a big margin using a Graphics Processing Unit (GPU)-accelerated Convolutional Neural Network (CNN) [46]. What followed was a surge in interest and funding in deep learning algorithms. In 2019, Yann LeCun, Geoffrey Hinton, and Yoshua Bengio were awarded the Turing Award, the highest award in computer sciences. This resurgence could be attributed to three major aspects

- **Big data:** Since the early 2000s, the ubiquity of the internet, the spread of usage of multimedia and social media, along with the advent of new technologies like the Internet of Things, there has been an abundance of data available [47]. This wealth of data, known as Big data, supplied deep learning with information that it could leverage effectively because, as opposed to other machine learning methods, the performance of deep learning scales with the amount of data fed.

- Development of algorithms: Despite the fact that most of the building blocks of the modern deep learning landscape had been around for some time, access to faster computers with bigger memory has facilitated new implementations or the invention of altogether new algorithms. Deep CNNs, Recurrent Neural Networks (RNN), Long short-term memory (LSTM), Transformers, Generative Adversarial Networks (GAN), and Graph Neural Networks (GNN) are some examples of such algorithms which are directed toward

different applications [48–53].

Other than this, different aspects in training were invented which were crucial in the good performance of such networks like the implementation of Batch Normalizations, the Adam optimizer, the cosine annealing learning rate scheduler scheme, etc. [54–56].

• Development of memory and compute: Many of the algorithms listed above date back to the late 1990s, when they failed to perform owing to the mismatch between the required compute/memory and the existing standards. By the early 2010s, computers had grown powerful enough to showcase the effectiveness of these algorithms. A huge part of the computation in neural networks is matrix multiplication. Around the same time, a specialized device emerged that was able to do this specifically very fast in a massively parallel fashion. This device, the Graphics Processing Unit, remains one of the key hardware necessary to perform state-of-the-art deep learning [57]. Presently, more specialized hardware such as the Tensor Processing Unit (TPU) and other accelerators are being developed [58].

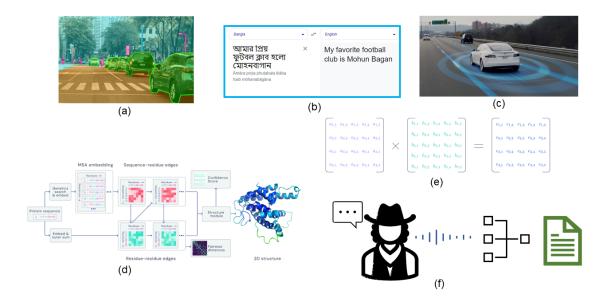

Figure 1.5: A collage of applications of DL today. (a) Image segmentation is a computer vision task where the network learns to separate different components in an image semantically. (b) Google Translate transcribes one language into another using natural language processing. (c) Tesla's autopilot system amounts to international level 2 in terms of vehicle automation. (d) AlphaFold 2 algorithm predicts the 3D crystal structure from the input amino acid sequence. (e) The AlphaTensor algorithm found an efficient way to multiply two matrices that have dimensions larger than 2×2. (f) Speech recognition task: the sound signal is converted to text.

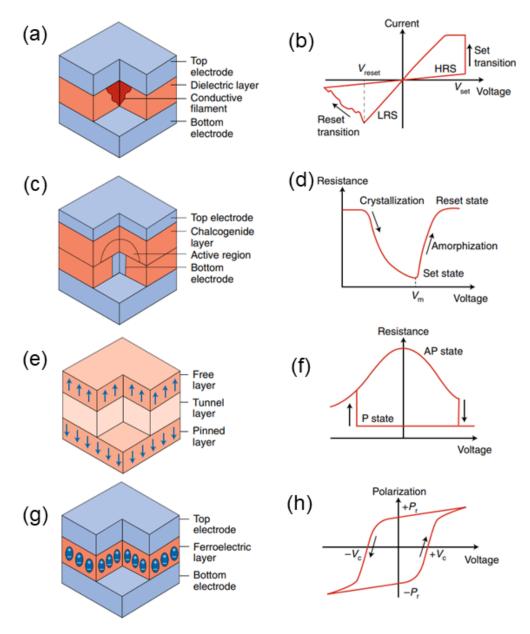

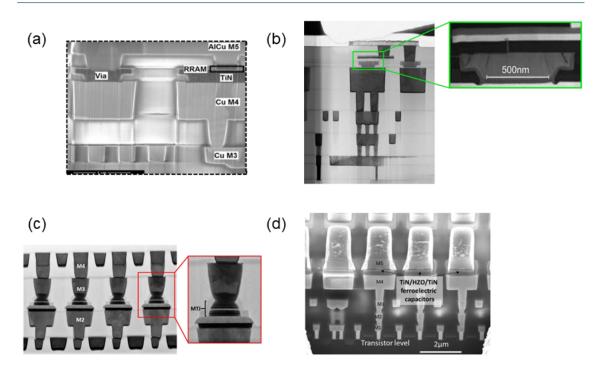

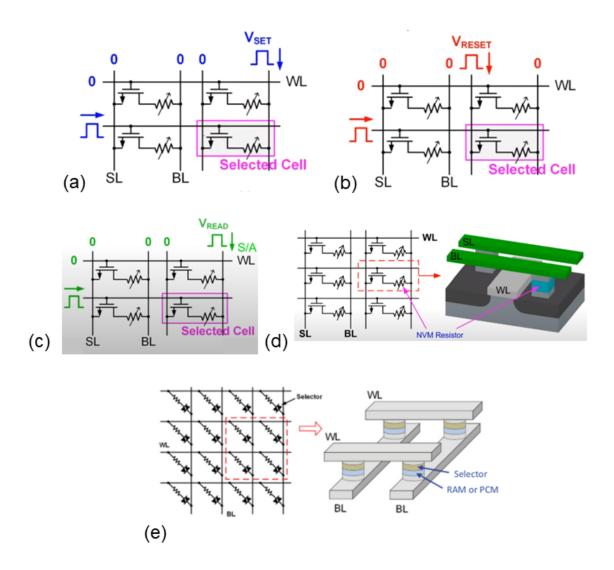

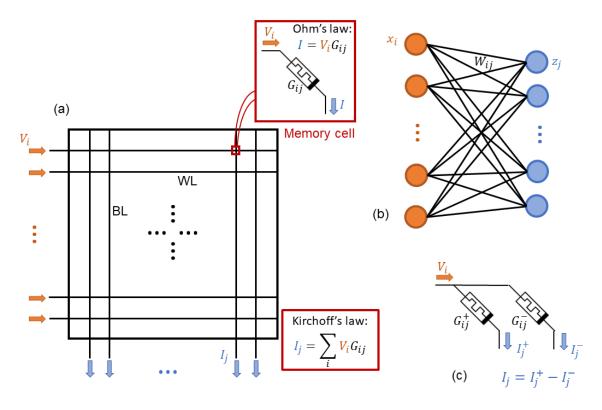

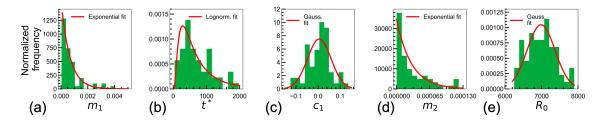

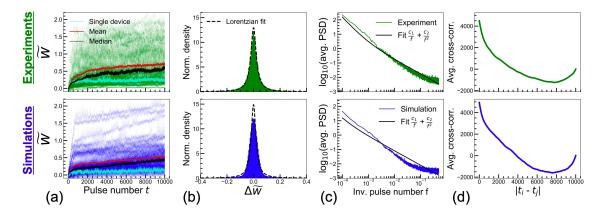

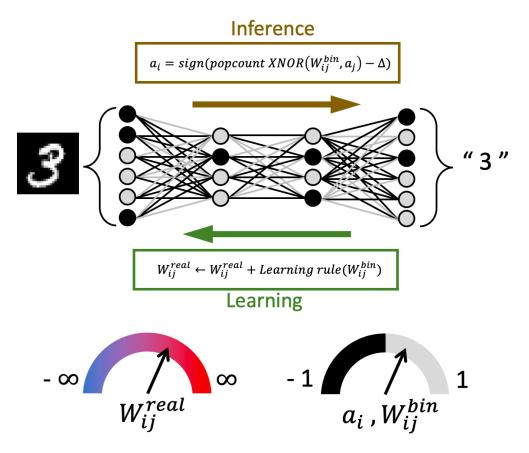

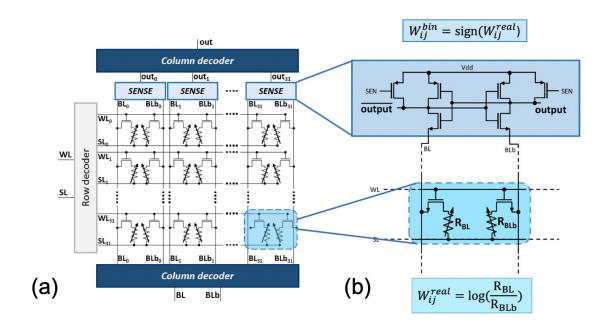

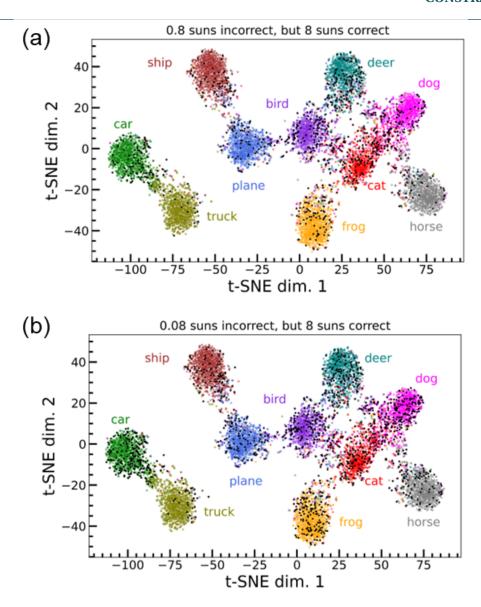

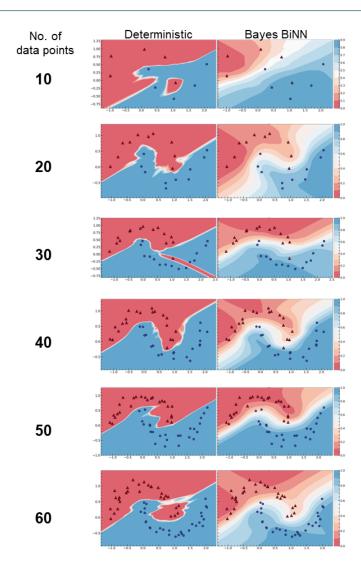

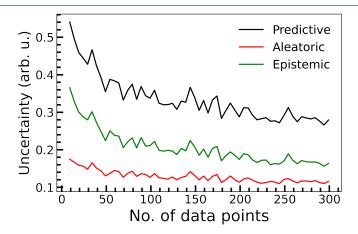

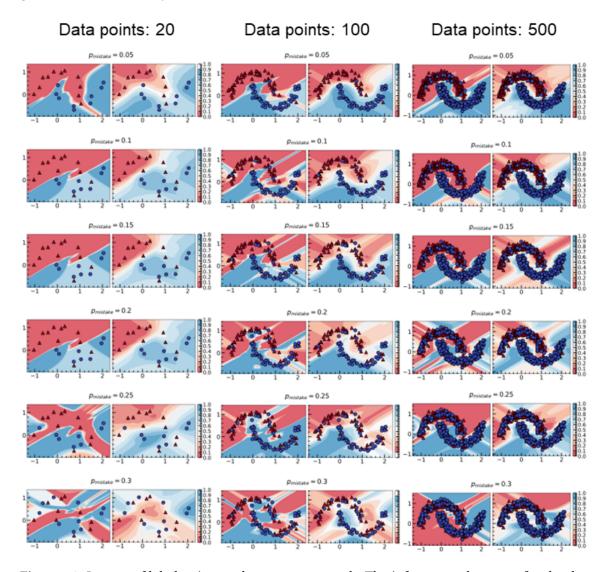

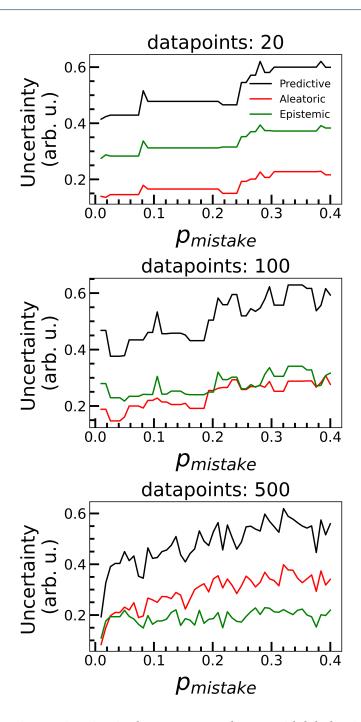

Today, deep learning can be found in a plethora of applications, as shown in fig. 1.5. At