## RF design methodology based on MOS transistors for circuit / technology optimization

Dayana Pino Monroy

#### ► To cite this version:

Dayana Pino Monroy. RF design methodology based on MOS transistors for circuit / technology optimization. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT027. tel-04186861

### HAL Id: tel-04186861 https://theses.hal.science/tel-04186861

Submitted on 24 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. THÈSE

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS) Spécialité : Nano électronique et Nano technologies

Unité de recherche : Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

#### Méthodologie de conception RF à base de transistors MOS pour cooptimisation circuit / technologie

## RF design methodology based on MOS transistors for circuit / technology optimization

Présentée par :

#### **Dayana PINO MONROY**

Direction de thèse :

| Sylvain BOURDEL                                              | Directeur de thèse    |

|--------------------------------------------------------------|-----------------------|

| Enseignant-chercheur Grenoble INP, Université Grenoble Alpes |                       |

| Manuel José BARRAGAN ASIAN                                   | Co-directeur de thèse |

| CHARGE DE RECHERCHE, Université Grenoble Alpes               |                       |

| Phillippe CATHELIN                                           | Co-encadrant de thèse |

| INGENIEUR, STMicroelectronics                                |                       |

| Patrick SCHEER                                               | Co-encadrant de thèse |

| STMiroelectronics                                            |                       |

#### Rapporteurs :

Thierry TARIS PROFESSEUR DES UNIVERSITES, BORDEAUX INP Fernando SILVEIRA PROFESSEUR, Universidad de la República

#### Thèse soutenue publiquement le 30 mars 2023, devant le jury composé de :

| Sylvain BOURDEL<br>PROFESSEUR DES UNIVERSITES, GRENOBLE INP    | Directeur de thèse    |

|----------------------------------------------------------------|-----------------------|

| Thierry TARIS                                                  | Rapporteur            |

| PROFESSEUR DES UNIVERSITES, BORDEAUX INP                       |                       |

| Fernando SILVEIRA                                              | Rapporteur            |

| PROFESSEUR, Universidad de la República                        |                       |

| Manuel BARRAGAN ASIAN                                          | Co-directeur de thèse |

| CHARGE DE RECHERCHE HDR, CNRS DELEGATION ALPES                 | 5 /                   |

|                                                                | Présidente            |

| PROFESSEUR DES UNIVERSITES, GRENOBLE INP                       | F                     |

| Carlos GALUP                                                   | Examinateur           |

| PROFESSEUR, Universidade Federal de Santa Catarina             | Examinateur           |

| Rémy VAUCHE<br>MAITRE DE CONFERENCES, AIX-MARSEILLE UNIVERSITE |                       |

|                                                                |                       |

#### Invités :

Philippe Cathelin INGENIEUR DE RECHERCHE, STMicroelectronics Patrick Scheer INGENIEUR DOCTEUR, STMicroelectronics

PhD Thesis with

Université Grenoble Alpes Ecole Doctorale EEATS Nano électronique et Nano technologies

Dayana Andrea PINO MONROY

# RF design methodology based on MOS transistors for circuit/technology optimization

**PhD defense:** 30<sup>th</sup> March 2023

#### Jury Members

| Mr. Fernando SILVEIRA    | Universidad de la República, Uruguay           | Rapporteur |

|--------------------------|------------------------------------------------|------------|

| Mr. Thierry TARIS        | IMS, Bordeaux-INP                              | Rapporteur |

| Mrs. Florence PODEVIN    | TIMA, Grenoble-INP                             | President  |

| Mr. Carlos GALUP-MONTORO | Universidade Federal de Santa Catarina, Brazil | Examiner   |

| Mr. Rémy VAUCHÉ          | IM2NP, Marseille                               | Examiner   |

| Mr. Sylvain BOURDEL      | TIMA, Grenoble-INP                             | Advisor    |

| Mr. Manuel BARRAGÁN      | TIMA, Grenoble-INP                             | Co-advisor |

| Mr. Philippe CATHELIN    | STMicroelectronics, Crolles                    | Invited    |

| Mr. Patrick SCHEER       | STMicroelectronics, Crolles                    | Invited    |

| Mr. Jean-Michel FOURNIER | Emeritus Professor, Grenoble                   | Invited    |

## Acknowledgments

I would like to express my gratitude to my thesis advisors Sylvain Bourdel, Manuel Barragan, Philippe Cathelin, Patrick Scheer and even if not official, Jean-Michel Fournier for their support and patience guiding me in the development of this thesis work. Thank you for resolving my doubts, giving me advice, and trusting me in the many times that even I doubted myself.

I would like to thank my thesis committee members for their time, their invaluable feedback and the contributions to improve this thesis manuscript.

I would also offer my thanks to Khalil Bouchoucha for all the help and collaboration on the topic of the thesis. Together with him, I want to thank Serge Subias for the realization and measurements of the circuit used for the development of the design methodology presented in this thesis.

I am very grateful for the opportunity to work on this topic in the TIMA Laboratory and STMicroelectronics, this allow me to grow in many ways as a professional, but above all, personally.

I am particularly thankful with my colleagues at STMicroelectronics: Jasmina Antonijevic, Nicolas Pelloux, Raphael Paulin, Patrice Garcia, Clement Charbuillet, Florence Sonnerat and Ophelie Foissey.

I am grateful to the PhD colleagues and friends at STMicroelectronics Crolles for the knowledge exchange, for the discussions in the coffee breaks for the good times and shared laughs. Thanks to Antoine Le Ravallec, David Gaidioz, Robin Benarrouch, Sebastien Sadlo, Guillaume Touchou, Alexander Flete, Thomas Capelli, Romane Dumont, Victor Fioresse, Vincent Gidel, Simon Bouvot, Cybelle Belem Goncalves, David Ouattara, Ioanna Kriekouki, Angel de Dios Gonzalez, Thibaut Despoisse, Raphael Guillaume, Franck Sabatier, Joycelyn Hai, Camille Robert, Soufiane Mourrane, Virgile Colrat and Adrien Verplancke.

Special thanks to all the colleagues and friends at TIMA Laboratory for the good atmosphere, the fun and the multicultural and intellectual discussions. Thanks to Khalil Bouchoucha, Julien Poupon, Imadeddine Bendejeddou, Mohamad El Chaar, Mohammed Tmimi, Marc Margalef Rovira, Renato Feitoza, Jordan Corsi, Sana Ibrahim, Ankush Mamgaim, Manasa Madhvaraj, Ayoub Naoui, Olivier Occello, Sherif Zahran, Hasan Moussa, Fadel Mohsen, William Bontems, Mohammed Wehbi, Diana Kalel and Damiano Zuccala.

My sincere gratitude to the Latino crew and my family in France, Denis Flores, David Ovalle, Enrique Pulido, Ana Bonilla, Carolina Alarcon, Giovani Britton, Daniel Guerrero, Sergio Correa, Carolina Fernandez, Diana Fernandez, Javier Mayen, Armando Garcia, Andrea Zarrate, Louis Genty, Rosa Alvarez Palencia, Tatiana Torres, Sharon Chaves, Daniel Meza, Daniel Rodriguez, Daniela Ramalho, Andres Asprilla, Monica Vallejo, Gonzalo Herrera, Juan Esteban Montoya, Nicolas Magne, Kristel Sanchez and Liset Castro for all your support, love and kindness to me.

Finally, I would like to express how grateful I am to my family for always encouraging me to follow my dreams and support me in every project I undertake. Thanks to my mother, Luz Adriana Monroy, for giving me a great example of what it means to fight for your dreams and to have perseverance to achieve them, for teaching me to be a warrior of life as she is. I am very grateful with my sister, Derly Pino Monroy, who is always there for me whether near or far and who understands me better than anyone else, for being my rock and my fortress. Thanks to my brother, David Pino Monroy, for always making me laugh and cheering me up, for so much fun and love. Thanks to my aunt and my second mother, Dora Ligia Monroy, and to my cousin and sister at heart, Andrea Caro for all the love, kindness, and tenderness.

### Abstract

Thanks to advances in recent technological nodes, the weak and moderate inversion regimes of the MOS transistor become interesting for low power RF circuit design. This work proposes a design-oriented model and an RF design methodology based on the inversion charge of the transistor.

Our proposal considers the most impacting short-channel effects of advanced nanometric CMOS technologies to accurately model the dependence on the drain voltage and to describe correctly not only the I-V curves but also the small signal model of the MOS transistor.

In this regard, firstly a the 7-parameter model has been developed and implemented in Matlab for STMicroelectronics 28nm FD-SOI technology. The feasibility and accuracy of the model have been verified by direct comparison to DC measurements, demonstrating a good agreement for the drain current behavior and its derivatives as a function of the transistor node voltages. Obtained results open the door to estimating the non-linear behavior of the transistor.

Additionally, a parameter extraction methodology is present to estimate the model parameters based on simple simulations (or DC measurement campaigns) proving its accuracy for different channel lengths of the studied technology.

Finally, a simple RF design methodology based on the proposed designoriented model has been proposed for the case study of a resistive feedback LNA. The developed design methodology allows to explore the design space for the selected resistive feedback LNA case study. This exploration allows to determine the best operating point depending on the targeted specifications. The results obtained from the model are compared with simulation results in Cadence and actual probe-station measurements from a fabricated LNA, for a given sizing and biasing of the circuit. Obtained results prove a really good accuracy among the three of them. Furthermore, a really simple study of the LNA performances under the variation of the proposed model parameters is carried out to provide a first glance on the way to circuit/technology co-optimization.

## Table of Contents

| Acknowledg       | jments3                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| Abstract         |                                                                                                                      |

| Table of Co      | ntents6                                                                                                              |

| General Intr     | oduction9                                                                                                            |

| Chapter 1: 0     | Context and State of the Art10                                                                                       |

| 1.1 Inte         | rnet of Things: Towards ultra-low power RF devices                                                                   |

| 1.2 Circ         | cuit design methodologies11                                                                                          |

| 1.2.1            | Circuit design in strong inversion: maximum $f_T$                                                                    |

| 1.2.2            | Circuit design in weak inversion: the interest of the $g_m/I_D$ characteristic 12                                    |

| 1.2.3<br>charact | Circuit design in moderate inversion: recent technologies g <sub>m</sub> .f <sub>T</sub> /l <sub>D</sub><br>reristic |

| 1.2.4            | Circuit design using Figures of Merit14                                                                              |

| 1.2.5            | Design methodologies based on design space exploration16                                                             |

| 1.2.6<br>method  | Limitations of the design-oriented models for circuit design lologies                                                |

| 1.3 Des          | sign-oriented models                                                                                                 |

| 1.3.1            | Analytical models for circuit design                                                                                 |

| 1.3.2            | Evolution of the inversion coefficient-based models24                                                                |

| 1.4 Mot          | ivation25                                                                                                            |

| Chapter 2: I     | Design-oriented 7-Parameter Model26                                                                                  |

| 2.1 3-P          | arameter model: <i>n</i> , $I_{S0}$ , and $V_{T0}$                                                                   |

| 2.1.1            | Description of the 3-parameter model                                                                                 |

| 2.1.2            | Comparison of the 3-parameter model and DC measurements                                                              |

| 2.2 Mo           | deling the carrier mobility reduction and series resistances effects: $	heta$ 30                                     |

| 2.2.1            | Carrier mobility reduction effect                                                                                    |

| 2.2.2            | Series resistances effect                                                                                            |

| 2.2.3            | Model of carrier mobility reduction and series resistances effects 31                                                |

| 2.                                 | 2.4                               | Comparison of the 4-parameter model and DC measurements                                                                                                                   | 32                         |

|------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.3                                | Мо                                | deling the drain-induced barrier lowering effect: $\sigma$                                                                                                                | 32                         |

| 2.                                 | 3.1                               | Drain-induced barrier lowering effect                                                                                                                                     | 32                         |

| 2.                                 | 3.2                               | Comparison of the 5-parameter model and DC measurements                                                                                                                   | 34                         |

| 2.4                                | Мо                                | deling the carrier velocity saturation effect: $\zeta$                                                                                                                    | 34                         |

| 2.                                 | 4.1                               | Carrier velocity saturation effect                                                                                                                                        | 34                         |

| 2.                                 | 4.2                               | Comparison of the 6-parameter model and DC measurements                                                                                                                   | 36                         |

| 2.5                                | Мо                                | deling the channel length modulation: $V_E$                                                                                                                               | 37                         |

| 2.                                 | 5.1                               | Channel Length Modulation effect                                                                                                                                          | 37                         |

| 2.                                 | 5.2                               | Comparison of the 7-parameter model and DC measurements                                                                                                                   | 38                         |

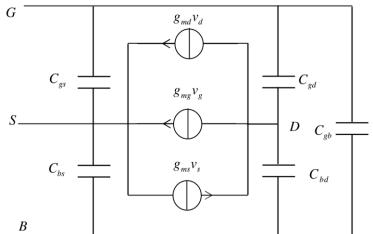

| 2.6                                | Sm                                | all-signal modeling of drain current                                                                                                                                      | 39                         |

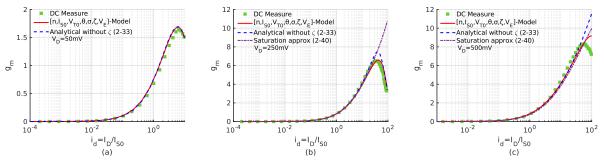

|                                    | 6.1<br>elocity                    | Analytical expressions of the current derivatives in absence of carrier<br>saturation                                                                                     | 40                         |

| 2.                                 | 6.2                               | Analytical expressions of the current derivatives in saturated region                                                                                                     | 41                         |

| 2.                                 | 6.3                               | Numerical approach of the current derivatives                                                                                                                             | 42                         |

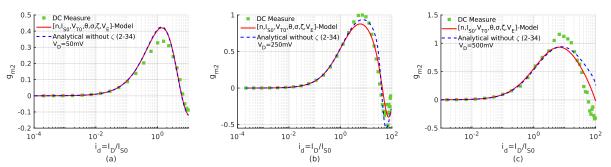

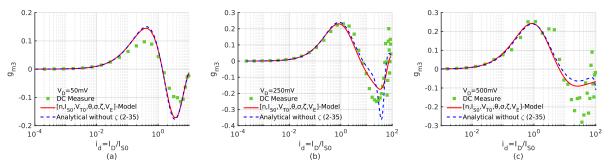

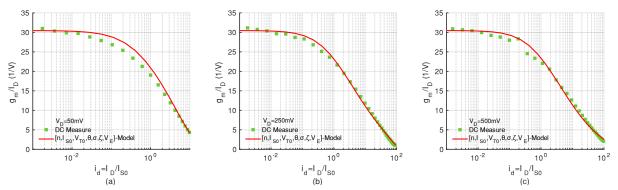

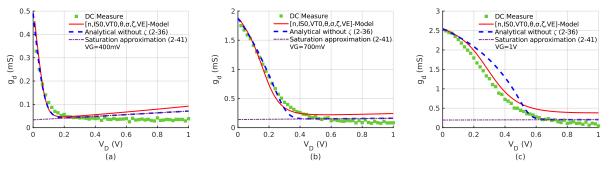

|                                    | 6.4<br>easu                       | Comparison of the derivatives from different approaches and DC rements                                                                                                    | 42                         |

| 2.7                                | Dis                               | cussion on RF modeling                                                                                                                                                    | 45                         |

| 2.8                                | Со                                | nclusion                                                                                                                                                                  | 46                         |

| Chapt                              | er 3: I                           | Parameter Extraction and Consistency of the Proposed Model                                                                                                                | 48                         |

| 3.1                                | Pai                               | ameter extraction                                                                                                                                                         | 48                         |

|                                    |                                   |                                                                                                                                                                           |                            |

| 3.                                 | 1.1                               | Subthreshold slope factor                                                                                                                                                 | 49                         |

|                                    | 1.1<br>1.2                        | Subthreshold slope factor<br>Threshold voltage and specific current                                                                                                       |                            |

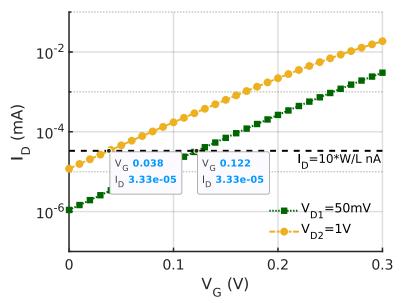

| 3.                                 |                                   |                                                                                                                                                                           | 50                         |

| 3.<br>3.<br>3.                     | 1.2<br>1.3<br>1.4                 | Threshold voltage and specific current                                                                                                                                    | 50<br>52                   |

| 3.<br>3.<br>3.                     | 1.2<br>1.3<br>1.4<br>odula        | Threshold voltage and specific current<br>Drain-induced Barrier Lowering (DIBL)<br>Mobility reduction factor, carrier velocity saturation and Channel Lengt               | 50<br>52<br>h<br>53        |

| 3.<br>3.<br>3.<br>M<br>3.2         | 1.2<br>1.3<br>1.4<br>odula        | Threshold voltage and specific current<br>Drain-induced Barrier Lowering (DIBL)<br>Mobility reduction factor, carrier velocity saturation and Channel Lengt<br>tion (CLM) | 50<br>52<br>h<br>53<br>56  |

| 3.<br>3.<br>3.<br>3.<br>3.2<br>3.2 | 1.2<br>1.3<br>1.4<br>odula<br>Coi | Threshold voltage and specific current<br>Drain-induced Barrier Lowering (DIBL)<br>Mobility reduction factor, carrier velocity saturation and Channel Lengt<br>tion (CLM) | 50<br>52<br>53<br>56<br>56 |

|           | 3.2   | .4    | Relative Error                                                                                 | 59  |

|-----------|-------|-------|------------------------------------------------------------------------------------------------|-----|

| 3.2.5     |       | .5    | Discussion on design-oriented models                                                           | 60  |

| 3.        | 3     | Cor   | nclusions                                                                                      | 62  |

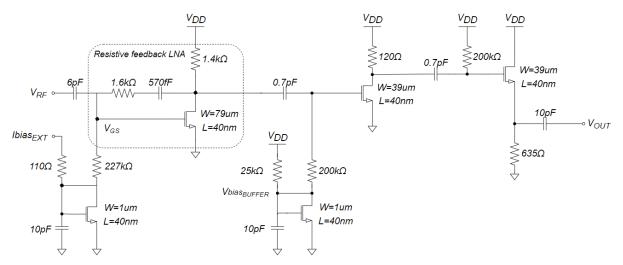

| Cha       | pter  | 4: F  | Resistive Feedback LNA Design based on the 7-Parameter Model                                   | 63  |

| 4.        | 1     | Res   | sistive Feedback LNA                                                                           | 64  |

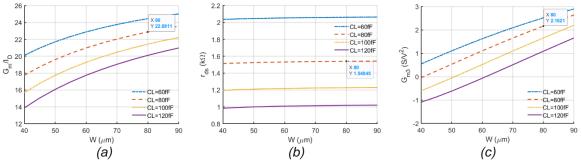

| 4.        | 2     | Exp   | loration of the design space                                                                   | 68  |

|           | 4.2   | .1    | Maximum gain                                                                                   | 69  |

|           | 4.2   | .2    | Operating frequency                                                                            | 70  |

|           | 4.2   | .3    | Design space graphic representation                                                            | 71  |

| 4.        | 3     | Fro   | m design space to practical case                                                               | 78  |

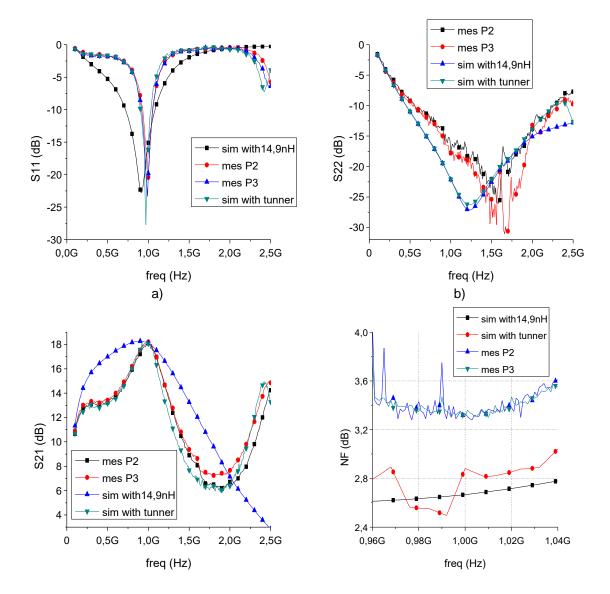

| 4.        | 4     | Sim   | ulation and measurement results                                                                | 79  |

| 4.:<br>pa | -     |       | Iluation of the LNA performances under variation of the proposed mode rs of the MOS transistor |     |

| 4.        | 6     | Cor   | nclusion and perspectives on the design methodology proposition                                | 84  |

| Cha       | pter  | 5: 0  | Conclusions and perspectives                                                                   | 86  |

| 5.        | 1     | Ger   | neral conclusions                                                                              | 86  |

| 5.        | 2     | Per   | spectives                                                                                      | 88  |

| Wor       | 'k sp | oread | ding                                                                                           | 91  |

| Refe      | eren  | ces   |                                                                                                | 93  |

| Арр       | end   | ices  |                                                                                                | 98  |

| A.        | 1     | Dec   | duction of equations and calculation of current derivatives                                    | 98  |

| A.        | 2     | MA    | TLAB codes1                                                                                    | 103 |

| A.        | 3     | Res   | sistive feedback noise factor calculation                                                      | 105 |

## **General Introduction**

The interest in producing low power consumption circuits for radiofrequencies (RF) applications such as Internet of Things (IoT) has led the current CMOS technologies to evolve accordingly to meet the requirements for these standards. This has allowed the transistors in today's technology nodes to have a higher transit frequency ( $f_T$ ) and therefore to operate at weak and moderate inversion regimes.

This has led to the development of design methodologies based on inversion coefficient to be implemented for RF circuit design. However, the simplified models used on these methodologies fail to correctly represent the drain current dependence on  $V_D$  and the short channel effects (SCE) on the most advanced CMOS technologies. As a result, previous design methodologies rely on cumbersome lookup tables to capture the  $V_D$  dependencies and are not able to address the non-linearity behavior of the targeted circuits, mainly dominated by SCEs.

In this thesis work, the aim is then to address the improvement of the RF circuit design methodologies based on the inversion coefficient of the MOS through two main axes connected to each other.

The first one is to work directly on transistor modeling based on its inversion charge to considering the SCE and the dependence on  $V_D$  to accurately reproduce the transistor characteristic I-V curves, but also the partial derivatives of the current.

The second axis is based on implementing this model to improve RF low power circuit design methodologies based on the transistor inversion coefficient in order to consider the modeling of transistor non-linearities within the transistor performance considerations. For this purpose, a specific LNA topology will be used to implement the proposed design methodology.

This document begins by describing the context and the state of the art of both design methodologies for RF circuit applications and design-oriented models in Chapter 1:. In Chapter 2:, the proposed design-oriented model based on the inversion charges of the MOS transistor is described and Chapter 3: presents a methodology to extract the corresponding parameters of the model along with an evaluation of the model robustness for different channel lengths. Chapter 4: presents the design methodology applied to a resistive feedback LNA along with the comparison with respect to the simulation and on-chip measurements of the circuit. Finally, Chapter 5: summarizes the contributions of this work as well as the perspectives for future work on the subject.

9

## Chapter 1: Context and State of the Art

# 1.1 Internet of Things: Towards ultra-low power RF devices

It is a well-known fact that the number of connected devices has increased exponentially and that this number will continue to increase in the coming years. At the moment of writing this manuscript, it has been estimated that there are more than 10 billion IoT (Internet of Things) devices in the world. Reducing the energy consumption of this huge number of devices goes beyond extend the battery life of the device. Actually, it can have a significant impact in the global power consumption with a nonnegligible effect in our society's carbon footprint. For this reason, we must continue to explore how to reduce the energy consumption of electronic devices, reduce their cost and increase their lifetime.

Circuit design for low power RF applications has evolved over the years thanks to advances in technology and also thanks to circuit design methodologies improvement. Advanced technologies and technology node reductions have pushed RF design from the strong inversion regime toward moderate and weak inversion regimes of operation of the MOS transistor, especially because of the  $f_T$  increase but also due also to the decrease of the supply voltages that comes with the shrink of the transistor channel length.

Advances in CAD simulation tools have allowed designers to develop state-ofthe-art devices in nanometric technologies based on accurate and complex compact models. However, the complexity of the CAD models make designers lose a bit of their design intuition and the understanding of the physical effects of the transistor on the circuit performances is lost. On the other hand, analytical methodologies based on traditional piecewise models are not valid anymore due to the physical effects that are now present in the latest technologies.

Design methodologies have then evolved to follow these major technology changes. Most of these new methodologies are based on inversion coefficient approach since it is an accurate and convenient way to describe the MOS behavior in weak and moderate inversion regimes. From basic recommendations on the inversion level up to complex methods based on Look-up Tables (LUTs) and analytical design approaches, many different design strategies have been proposed and will be detailed here. A promising method, that will be privileged in this PhD manuscript, relies on the use of simplified design-oriented charge-based models based on EKV and ACM models. These design-oriented models use a small set of parameters to describe the

MOS behavior and allow to define analytical design methodologies based on physical design equations.

However, current models used for the analytical design methodologies fail to accurately capture non-linearities and  $V_D$  dependency which highly limits their use. This is the reason why there is a need for accurate but simple design-oriented models that helps designers to develop non-linearity-aware design methodologies. This is indeed one of the key objectives of this thesis.

This chapter will expand on the concepts described here and the motivation for this thesis work. Inversion coefficient-based design methodologies will be first studied in the state of the art. Then, design-oriented models will be analyzed in order to set the basis of this work.

### 1.2 Circuit design methodologies

#### 1.2.1 Circuit design in strong inversion: maximum $f_T$

In the 90's with the advance on wireless communications through standards as global system for mobile, GSM, (from 900 to1800 MHz) and the further development of the global positioning system, GPS, (~1100 to 1600 MHz), the demand for RF integrated circuits (RFIC) highly increased. At that time, designers started to use CMOS technologies for radiofrequency (RF) devices. To obtain the best possible frequency response and the best performances that comply with the standards requirements, RF circuits were designed in strong inversion to reach the highest transit frequency,  $f_T$ .

A clear example of this, is the work presented by Shaeffer *et al.* in 1997 [1] with the implementation of an LNA (Low Noise Amplifier) for a GPS receiver operating at 1.5 GHz in 0.6  $\mu$ m technology. Their results demonstrate the interest in using MOS transistors for RF applications and point to future improvements that arrived with the transistor size reduction of the more recent CMOS technologies.

Thanks to the advance of technological nodes, stronger  $f_T$  and lower supply voltage are now possible. With a low voltage supply, the transistor cannot operate in saturation or strong inversion especially for circuits such as a cascode configuration where the supply voltage is divided among several transistors. Hence, transistors have to operate with a  $V_{DS}$  closer to the threshold voltage, pushing the design toward the weak and moderate inversion regimes and in the low saturation region. Fortunately, the increase in  $f_T$  makes possible to operate the transistors at RF frequencies even in weak and moderate inversion regimes.

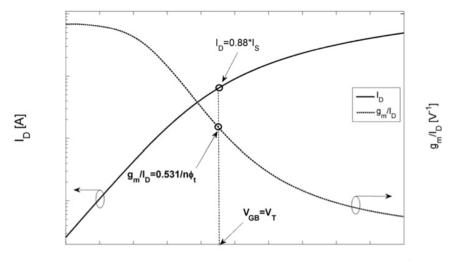

## 1.2.2 Circuit design in weak inversion: the interest of the $g_m/I_D$ characteristic

In 1977, Vittoz and Fellrath in [2], highlighted the interest of weak inversion regime for low-power applications, demonstrating the concept with two different circuits, an amplitude detector and a low-frequency bandpass amplifier.

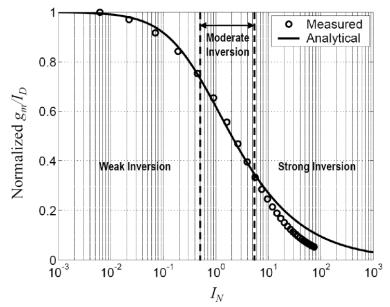

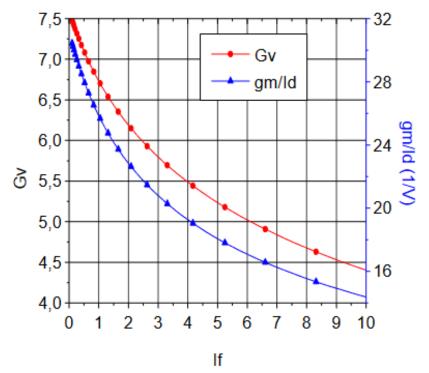

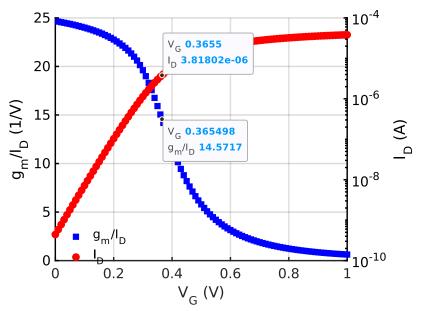

Furthermore, the weak inversion regime keeps high interest for the design of low-power RF circuits, since the maximum of  $g_m/I_D$  is reached in this zone, as illustrated in Figure 1-1. Thus, the trade-off between the intrinsic gain of the transistor, proportional to  $g_m$ , and the power consumption,  $I_D$ , can be optimized.

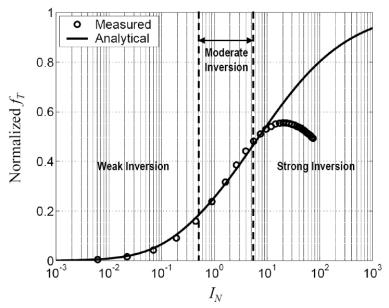

However, working at high  $g_m/I_D$  to improve the energy efficiency of the MOS transistor implies large W to compensate for low  $I_D$  while keeping constant  $g_m$ . Large W leads to large parasitic capacitances which finally reduces the bandwidth of the circuit. This phenomenon is well described in Figure 1-2, where the  $f_T$  of a MOS is plotted as function of the inversion coefficient. This shows that where  $g_m/I_D$  is at its maximum,  $f_T$  is at its minimum, simply justifying why  $g_m/I_D$  design methodologies were only dedicated to low frequency designs up to the early 2010.

Figure 1-1. Normalized g<sub>m</sub>/I<sub>D</sub> characteristic respect to the inversion coefficient [3].

Figure 1-2. Normalized  $f_T$  characteristic respect to the inversion coefficient [3].

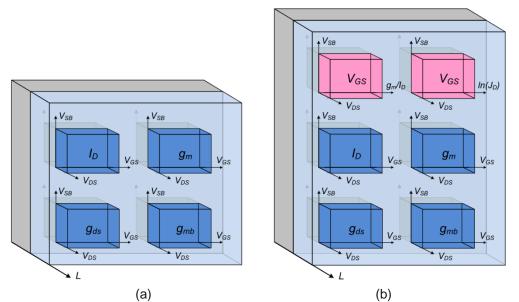

## 1.2.3 Circuit design in moderate inversion: recent technologies $g_m f_T / I_D$ characteristic

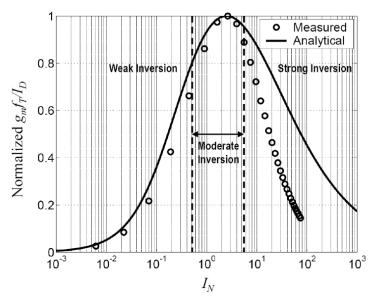

The importance of the transit frequency,  $f_T$ , and the energy efficiency,  $g_m/I_D$ , characteristics for low-power RF circuits has been highlighted in sections 1.2.1 and 1.2.2. In advanced technology nodes with the increase of  $f_T$ , the circuit operation frequency is no more a limitation in the RF domain and lower inversion regime can be considered to save power. Then, a new figure of merit (FoM) becomes interesting for low-power RF domain:  $g_m f_T/I_D$ , it combines the desired operating frequency or frequency band, and a good trade-off between the gain and the power consumption.

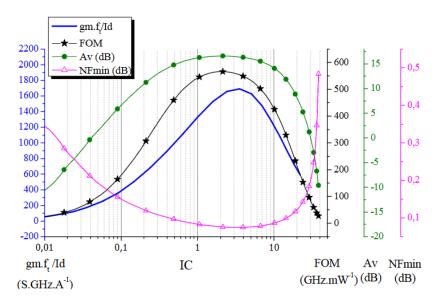

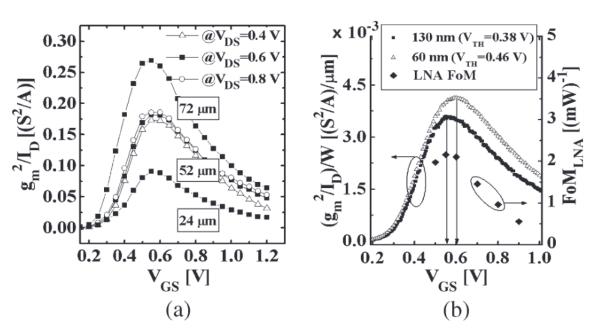

In [3], Shameli and Heydari present an study for a 0.18 µm CMOS technology that leads them to conclude that the moderate inversion is the best operation regime, as the maximum of  $g_m f_T / I_D$  is reached at this regime as illustrated in Figure 1-3. Then, for a given technology, the designer shall investigate which regime give the best  $g_m f_T / I_D$  and then, shall use it for its entire design. As a proof, [4] shown that the typical FoM of a LNA is maximized in the same region as  $g_m f_T / I_D$  as depicted in Figure 1-4.

Figure 1-3. Normalized  $g_{m} f_T / I_D$  characteristic respect to the inversion coefficient [3].

Figure 1-4.  $g_m f_T / I_D$  characteristic used as design metric for an RF LNA in [4] based on the inversion coefficient (IC).

#### 1.2.4 Circuit design using Figures of Merit

To choose an inversion regime better suited to a topology, authors proposed to explore FoMs that are more properly linked to one specific type of block in the RF reception chain. This allows to determine an inversion level not only based on the technological point of view, but also by considering the designed function (LNA, VCO, etc.). To illustrate this, Song *et al.* [5] propose that  $g_m^2/I_D$  can be used as a FoM to optimize the performance of the LNAs, as this characteristic allow to estimate the better

biasing taking into account the noise figure, F, gain, G, and power consumption, P. The article shows that this characteristic follows the same trend that the figure of merit for LNA in (1-1), which is quite traditional because it considers the most critical performances in the design of an LNA.

$$FoM_{LNA} = \frac{G}{(F-1)P} \tag{1-1}$$

Figure 1-5.  $g_m^2/I_D$  and FoM for LNA. a)L=130nm, different widths (24,52,72um) and several VDS, presenting an optimum around  $V_{GS}$ =0.55V. b)Similar trends for both characteristics: FoM for LNA and  $g_m^2/I_D$ , good estimation of corresponding  $V_{GS}$  for the maximum of FoM for the LNA [5].

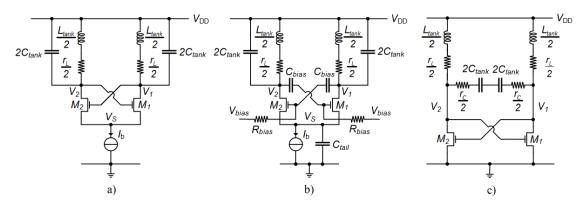

Following the same kind of proposal, in [6], Chicco *et al.* present a FoM to compare different topologies of LC Oscillators based on LUTs with respect to the inversion coefficient, *IC*, to determine in which inversion regime, a certain oscillator class is more performant. In this case the FoM is given by (1-2), considering power consumption,  $P_{DC}$ , and phase noise  $\mathcal{L}(\Delta f)$  depending on *IC*.

$$FoM_{LC\_osc} = \frac{kT}{\mathcal{L}(\Delta f, IC)P_{DC}(IC)} \left(\frac{f_0}{\Delta f}\right)^2$$

(1-2)

The three topologies studied are presented in Figure 1-6, and Figure 1-7 illustrates that the classes B and C reach the maximum FoM in moderate inversion regime, while the class D has its optimum in weak inversion regime.

Figure 1-6. Three topologies of LC oscillators studied in [6]: a) Class-B, b)Class-C, c)Class-D.

Figure 1-7. FoM for LC Oscillators respect to IC [6].

#### 1.2.5 Design methodologies based on design space exploration

FoMs based on the MOS transistor characteristics can be very interesting to make a comparison between different technologies and can give an overview of the inversion regime in which a transistor should operate depending on some characteristics. However, it has been shown that these FoMs are not ideal since they focus on general characteristics and lead to an optimal trade-off. However, they fail to help the designer when particular requirements are targeted. Depending on the specific circuit and its application, the optimum inversion regime will differ from a circuit to another. For this reason, other design methodologies were developed to explore the design space and to find the optimum operating points regarding a specific topology and requirements from particular applications.

In this regard, there are two trends in RF low-power circuit design methodologies. On the one hand, methodologies based on LUTs and on the other hand, methodologies based on design-oriented models leading to a quasi-analytical/ analytical-based design. As will be detailed later, generally the design-oriented model methodology is complemented with the LUTs or with simulation information to provide better results for design.

#### 1.2.5.1 Circuit design based on Look Up Tables

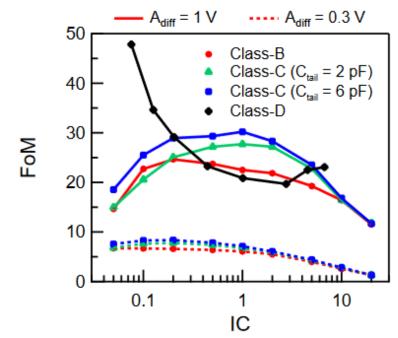

The LUTs are charts where a set of characteristics of the transistor are plotted under the variation of other parameters in the circuit, or design variables such as the size of the transistor or the components that make up the circuit. The LUTs can also contain the circuit performance estimation depending on whether other performance or transistor characteristics are varied. It is essential to remember that the main interest of the LUTs is that it allows a global observation of the design space of the circuit under the variation of different variables.

Figure 1-8. Set of 4D LUTs based on MOS transistor parameters to limit the design space for a given circuit to reach specifications: (a) First proposition (b) Improvement for fastest estimation of the design space [7].

The general concept of the LUTs is illustrated on Figure 1-8(a) where Youssef *et al.* present 4 of the main parameters of the MOS transistor to evaluate several scenarios to design two circuits, a bandgap reference and a folded cascode. However, they added two other parameters (Figure 1-8(b)) to the design space in order to reach

a given set of specifications [7]. This demonstrates that a series of criteria must be taken into account to select the LUTs to be used, without neglecting essential elements for the circuit design to target all specifications, what may not be an obvious task.

The design based on LUTs has proven to be of great interest for the design of all types of circuits as it is found in a whole series of different publications. Here, we will mention only a few that are relevant as they integrate the energy efficiency feature,  $g_m/I_D$ . In [8], Jespers and Murmann present a guide for circuit design based on LUTs for different kind of circuits employing CMOS transistors that allow to obtain results very close to the simulation while dealing with the different trade-offs that occur when designing RF circuits, highlighting furthermore the interest of the  $g_m/I_D$  characteristic.

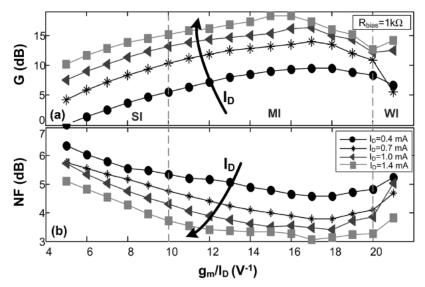

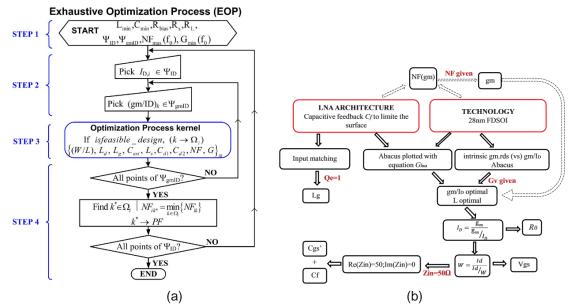

In [9], a design methodology for common source Low Noise Amplifiers (LNAs) is proposed based on the gain, *G*, and noise figure, *NF*, in function of  $g_m/I_D$  to determine the design space for the circuit as illustrated in Figure 1-9. In [10], a similar proposal to determine the sizing and the biasing of a capacitive feedback LNA is presented based on the same performances of gain and noise figure. Behind of the both methods presented in publications [9] and [10], the design methodology applies an algorithm with several loops to optimize and determine of the operating point of the circuit depending on the targeted specifications as depicted in Figure 1-10.

Apart from LNAs, LUT-based design methodologies have been also developed for other circuit families. Thus, an LC VCO is conceived in [11] through an optimization loop based on the characteristics of  $g_m/I_D$  and  $g_{ds}/I_D$  allowing to minimize the phase noise taking into account the constraints of current consumption, output voltage and output amplitude. In [12], the LUTs are used to develop a design methodology for an envelope detector. Here, the second order non-linearities of the transistor are employed for the operation of the circuit demonstrating the interest of LUT approaches for non-linear devices or non-linearity studies. The second derivative divided by the current is used as FoM and a guide to reach the final conditions for the circuit.

Figure 1-9. (a) Gain and (b) Noise Figure based on  $g_m/I_D$  for different drain currents to estimate the design space for common source LNAs at 2.4 GHz [9].

Figure 1-10. Algorithm for sizing and optimization of (a) common source LNA [9] and (b) Capacitive feedback LNA [10].

#### 1.2.5.2 Circuit design based on design-oriented models

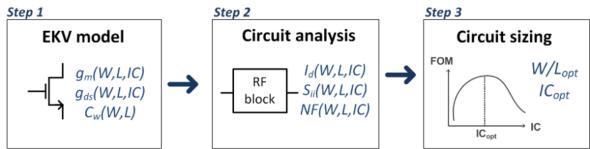

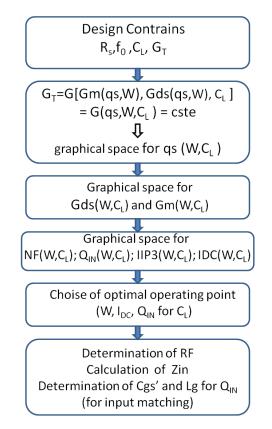

The design-oriented models that are considered in the methodologies explained in this section are based on the inversion level of the transistor as it is of major interest for RF low-power circuit design. A trend in the main algorithm of these design methodologies is noticeable and can be illustrated as shown in Figure 1-11. Firstly, a model based on the inversion coefficient describing the transistor at a technological level is proposed, secondly, an analytical study of the circuit is carried out taking into account the most critical performances and finally, a determination of the transistor size and biasing is done by linking both, the transistor model and the circuit analysis through certain variables such as the width and length of the transistor and the inversion coefficient level, *W*, *L* and *IC* respectively, in this example taken from [13].

Figure 1-11. Design methodologies based on the inversion coefficient-based models [13].

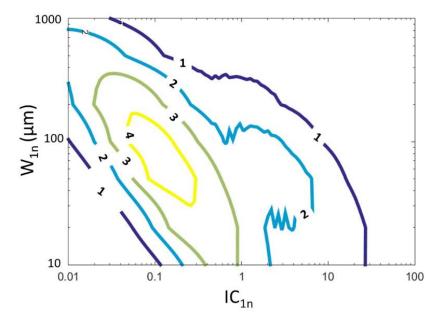

In the case of the LNA presented in [13], an optimum point is found depending on the target application using a single FoM (1-3) that is optimized through the design algorithm. This determines the design space presented in Figure 1-12, where the FoM is plotted as a function of two of the three parameters initially set, *W* and *IC*. In [14], a similar procedure is followed using also EKV model to represent the MOS behavior, what slightly differs from the previous work is simply the FoM (1-4), which, being also for an LNA, takes into account the same criteria, although using the power instead of the current directly.

$$FoM_{LNA[13]} = \frac{BW_{-3dB}G_{\nu}}{I_{total}|F - 1|}$$

(1-3)

$$FoM_{LNA[14]} = \frac{BW_{-3dB}G_{\nu}}{P_{DC}|F-1|}$$

(1-4)

Figure 1-12. Design space for LNA based on FoM with respect to W and IC [13].

The authors in [15] presents a design methodology for a resistive feedback LNA also employing an inversion coefficient-based model (ACM). This design methodology is more focused on achieving the desired performances without necessarily going through a FoM. The proposal consists of expressing the performances as a function of certain metrics of the transistor, for example the gain,  $G_v$ , in function of the  $g_m/I_D$  characteristic or the inversion coefficient,  $i_f$ , as illustrated in Figure 1-13 or the noise figure, NF, in function of  $g_m$ . This methodology allows to reach in a direct way the polarization and sizing of the transistor.

If we take a closer look at what the different publications presented in this section have in common, where various design methods for inductorless LNAs are illustrated, none of them take into account one of the most important metrics of this block for an RF reception chain, the IIP3. The 3<sup>rd</sup> order input intercept point, IIP3, is a fundamental metric to show how linear (or not linear) is the behavior of a circuit. In the case of the LNA, high linearity prevents the generation of undesired signals in the operating frequency band and improve the resilience to interferers and blockers.

Figure 1-13. Gain,  $G_v$ , and energy efficiency factor,  $g_m/I_D$ , in function of the inversion coefficient,  $i_f$  [15].

## 1.2.6 Limitations of the design-oriented models for circuit design methodologies

The design methodologies built from models based on the inversion coefficient are very interesting because they help the designer understand the circuit behavior based on analytical equations. In addition, they provide a powerful tool to easy explore the design space that leads to required specifications taking into account the tradeoffs. However, as highlighted, these methodologies are not suited to non-linear studies. This comes from some limitations in the models used that do not consider nonlinearities that come with short-channel effects (SCEs).

In order to improve the proposals in these design methodologies, it is required to improve the design-oriented models, particularly with the aim of correctly estimating the transistor nonlinearities, to integrate metrics such as the IIP3 in the design of LNAs.

Subsequently, an overview of the models currently used for circuit design for advanced MOS technology nodes and their progress over the last few years is presented.

## 1.3 Design-oriented models

#### 1.3.1 Analytical models for circuit design

Models describing MOS transistor behavior for the most advanced technological nodes can be classified into two families of models: compact models implemented in simulation tools and design-oriented analytical models that are simple enough to be used in hand calculations or can easily be implemented in algorithms to predict the performances of a given circuit. Each of them is presented below and their advantages and drawbacks for RF low power circuit design are briefly summarized.

#### 1.3.1.1 Compact models in CAD tools

Compact models implemented in CAD (Computer-Aided Design) simulation tools are based on the complex semiconductor physics of the MOS transistors, but it also includes certain fitting parameters that allow to bring these models closer to the measurements obtained directly from the implementation of the technology. Making a focus on the chosen technology to carry out this thesis work, the 28nm FD-SOI (Fully depleted silicon on insulator) [16] of STMicroelectronics, it is a very advanced and complex technology that requires models with hundreds of parameters to accurately describe the transistor behavior in simulation tools.

FD-SOI technologies in SPICE simulators and industrial design kits are modeled by BSIM-IMG model [17], [18] but also, by UTSOI2 model [19], [20], which additionally takes into consideration the effects related to the ultrathin body and buried oxide (UTBB). Of course, these models are very accurate in predicting the behavior of a given circuit, but they are difficult to understand at the technological parameter level. Using directly these models in design requires a design approach relying only in simulations that leads to extensive simulation campaigns to properly size and bias transistors in order to comply with a set of given design specifications.

For this reason, it is necessary to use simpler analytical design-oriented models that preserve the physics of the transistor and describe in a more general way its behavior with sufficient accuracy to perform preliminary design studies. Preliminary sizing, either with hand calculations or with rather simple algorithms implemented in a computer, allows the designer to start CAD based optimization with compact models from an operating point that is closer to the optimum, saving a huge simulation time.

#### 1.3.1.2 Analytical models based on the inversion coefficient

In the last few years, design-oriented models based on the transistor inversion level are gaining strength over the conventional piecewise model, as they allow a better approximation to the transistor behavior in advanced technologies, especially in moderate and weak inversion regimes by using a small set of parameters. ACM (Advanced Compact MOSFET) [21]–[24] and EKV (named after its developers' initials: C. C. Enz, F. Krummenacher and E. A. Vittoz) [25]–[29] models are based on inversion charge linearization describing continuously the MOS drain current characteristic as a function of the terminal voltages. The main differences between both models lie in different definitions for the normalization charge and the pinch-off voltage. However, from a designer's point of view, the equations are similar and can be transposed from ACM to EKV or vice versa.

The main advantage of the simplest versions of these models is that by using a small number of parameters, the model is easy to understand and to be used in design methodologies through hand calculations or simple algorithms.

#### 1.3.2 Evolution of the inversion coefficient-based models

Both, the ACM and the EKV models have followed a very similar trajectory in terms of their development. The interested reader is referred to the corresponding books, [23], [24] for ACM and [27] for EKV, for a further explanation of their basis, extensions and even some application cases. However, as far as we are concerned, it is more interesting to start by presenting the basic versions of both models and the evolution that has taken place for their use in more advanced nodes.

The simplest version of the models based on the inversion coefficient have three main parameters as presented by Schneider *et al.* in [30] based on the ACM model or by Jespers *et al.* in [31] based on the basic EKV model, introducing also the first equations describing the harmonic distortion in the transistor, giving a first step towards the estimation of transistor nonlinearities. Up to this point, the modeling of the drain current is independent on the drain voltage, this limitation is considered by Jespers in [31], through calibration curves for two of the three main parameters, which leads to an equivalent LUT to deal with this issue making this solution unpractical for hand calculations with arbitrary transistor biasing.

To go beyond the three-parameter model presented above, several authors consider that one of the main effects to be modeled next is the carrier velocity saturation effect. In [32], Mangla proposes three different ways to model this effect depending on the effective carrier mobility, in the end, most authors who take up this effect in the model tend to take the same approach among the proposed ones.

This fourth parameter integrated in the model is directly related to the carrier mobility saturation effect, but in general, it is also fitted to capture other SCEs presented in saturation and in strong inversion for the MOS transistor operation [28], [33]–[35]. The non-linearity behavior of the transistor is also deduced under the resulting 4-parameter model that may be very useful in many analog and RF design scenarios, as it represents a good trade-off between complexity and accuracy.

However, the simplicity of the model comes at the cost of not describing the linear region and being limited to a fixed value of drain voltage.

Adornes *et al.* proposed very recently (in 2021) [36] a different approach for a 4-parameter inversion coefficient-based model focused on ultra-low voltage applications adding to the basic 3-parameter model a parameter related to the drain induced barrier lowering effect which becomes significant for short-channel devices. This parameter is essential to accurately describe SCEs in weak and moderate inversion regimes of the MOS transistor.

The simple inversion coefficient-based analytical models already proposed until these days are very useful as they are employed for the transistor operation regions for which they have been conceived. Nevertheless, there is still an interest on developing a simple analytical model that describe accurately all the inversion regimes and the operation from linear to saturation regions of the MOS transistor.

#### 1.4 Motivation

Advanced nanometric technologies imposed the need for more accurate but simple analytical models that allow to describe the operation of the MOS transistor in all operation regions (from linear to saturation regions) and all inversion regimes (from weak to strong inversion regimes) that additionally can be implemented in adapted design methodologies for RF low power circuit design.

Two main joint objectives are addressed in this thesis: on the one hand, the development of a design-oriented model for non-linear aware design methodologies and in the second hand, the development of a sizing methodology for a LNA to validate the efficiency of the proposed model in the context of RF design. Concerning the model, the ACM formulation will be chosen as a basis of the work. The basic 3-parameter ACM model will be refined to describe several of the most important SCEs, especially through parameters that have a physical meaning and that are not only based on the optimization or fitting of the device measurements. In addition, it is sought that this model provides modeling features that can be integrated in a design methodology for RF low power circuits, especially integrating metrics such as IIP3, which implies a correct modeling of the transistor non-linear behavior.

## Chapter 2: Design-oriented 7-Parameter Model

The previous chapter has confirmed the need for an improvement in the proposal of design-oriented models, especially for more advance nanometric technologies. Simple models are required that can describe well the MOS transistor behavior from simple but representative parameters that can be used in the early stages of the design, to size the circuit using analytical or algorithm-based methodologies. Of course, the use of comprehensive SPICE models like UTSOI2 [19], [20] is still a fundamental step for design validation.

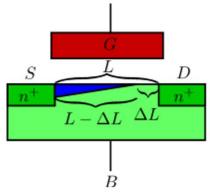

Therefore, taking up the current state of the design-oriented models, basic 3parameter EKV and ACM inversion coefficient-based models [21], [27], although accurate enough for describing a long-channel transistor behavior, are not appropriate for advanced technologies, where short-channel effects (SCEs) dominate the behavior of the transistor. This chapter proposes an all-region, all-regime 7-parameter inversion coefficient-based model that considers the most impacting SCEs present in nanometric technologies, i.e., drain-induced barrier lowering (DIBL), carrier velocity saturation, carrier mobility reduction, and channel length modulation (CLM).

This chapter follows a didactical approach to present the model. As a starting point in our derivation, we first introduce the basic 3-parameter ACM model. This model employs the threshold voltage ( $V_{T0}$ ), the specific current ( $I_{S0}$ ), and the subthreshold slope factor (n) to describe an all-region DC model of a long-channel MOS transistor. Then, SCEs are introduced one by one and incrementally added to the model equations illustrating their effects on the I-V characteristics of the MOS. Comparisons to silicon measurements show the cumulative improvement of the model fitting when introducing each new parameter.

After presenting the DC modeling of the transistor, the small signal modeling is introduced, using first order derivatives of the drain current. Then, high order derivatives are considered to address the description of the transistor nonlinearities. Finally, the perspectives of a complete model considering the high frequency behavior are discussed. Conclusions on the proposed model are drawn at the end of the chapter.

## 2.1 3-Parameter model: *n*, $I_{S0}$ , and $V_{T0}$

#### 2.1.1 Description of the 3-parameter model

ACM and EKV models are inversion charge linearization-based models that describe, continuously, the MOS transistor drain current characteristic as a function of its source, drain, gate, and body voltages. The main differences between ACM and

EKV lie in different definitions for the normalization charge and the pinch-off voltage,  $V_P$ , [24], [28]. However, from a designer's point of view, the equation sets are similar, and the following work can be transposed from ACM to EKV formalism. In the coming discussion, voltages are referred to the body terminal, whose voltage,  $V_{BB}$ , is set to zero. However, the discussion remains valid for any  $V_{BB}$  value knowing that a unique set of parameters must be extracted for every specific value of  $V_{BB}$ .

The cornerstone of ACM and EKV model is that drain current is a function of the forward and reverse currents,  $I_F$  and  $I_R$ . In an ideal MOS, these currents are independent of each other and are a function of the gate ( $V_G$ ), drain ( $V_D$ ), and source voltages ( $V_S$ ) as:  $I_F = I(V_G, V_S)$  and  $I_R = I(V_G, V_D)$ . So,  $I_D$  can be expressed as [24]

$$I_D = I_F - I_R = I_{S0} (i_f - i_r), \qquad (2-1)$$

where,  $i_f = I_F/I_{S0}$ ,  $i_r = I_R/I_{S0}$ , and  $I_{S0}$  is the specific current, defined for the n-channel transistor as

$$I_{S0} = \mu_n C'_{ox} n \frac{U_T^2}{2} \frac{W}{L_{eff}},$$

(2-2)

where,  $\mu_n$  is the electron mobility, W and  $L_{eff}$  are the width and the effective length of the transistor, respectively,  $U_T = kT/q$ , is the thermal voltage,  $C'_{ox} = \varepsilon_{ox}/t_{ox}$ , is the oxide capacitance per unit area, and  $\varepsilon_{ox}$  and  $t_{ox}$  are the permittivity and equivalent thickness of the oxide, respectively.

$i_f$  and  $i_r$  are the inversion coefficients that are directly related to the density of the normalized inversion charges at the source and the drain terminals of the transistor,  $q_s$  and  $q_D$ , respectively. These charges are derived from the source and drain charge densities,  $Q'_{IS}$  and  $Q'_{ID}$ , respectively, as

$$q_{S} = \frac{Q_{IS}'}{Q_{IP}'},$$

(2-3)

$$q_D = \frac{Q'_{ID}}{Q'_{IP}},$$

(2-4)

with,  $Q'_{IP} = -nC'_{ox}U_T$  for the n-channel transistor.

Finally,  $q_S$  and  $q_D$  are related to the inversion coefficients as

$$q_S = \sqrt{1 + i_f} - 1$$

, (2-5)

$$q_D = \sqrt{1 + i_r} - 1 \,. \tag{2-6}$$

Therefore, the normalized drain current can be also expressed as [22]

$$i_d = \frac{I_D}{I_{S0}} = (q_S - q_D)(q_S + q_D + 2).$$

(2-7)

As described in the literature [22], [28], [30], [35], inversion regimes are usually defined as a function of  $i_d$  (or  $IC^1$ ). Indeed, weak inversion corresponds to  $i_d < 0.1$ , moderate inversion to  $0.1 < i_d < 10$ , and strong inversion to  $i_d > 10$ .

In long-channel devices, the use of inversion coefficients  $(i_f \text{ and } i_r)$  is quite convenient since the latter can be easily related to the  $g_m$  transconductance, which is related to most of the circuit performances (gain, noise figure, input impedance, etc.). In a more general context, the use of normalized drain and source charges  $(q_D \text{ and } q_S)$ is preferred since it allows a straightforward introduction of SCEs and simplifies the associated derivations (section 2.6).

The computation of the normalized charges is done as follows. The pinch-off voltage,  $V_P$ , is introduced as the channel to substrate voltage for which the channel charge density is equal to  $Q'_{IP}$ , or,  $Q'_{IS} = Q'_{ID} = Q'_{IP}$ . Then, the threshold voltage,  $V_T$ , is defined as the gate voltage for which  $V_P = 0$  and is linearly approximated by [25]

$$V_P \approx \frac{V_G - V_T}{n}.$$

(2-8)

The pinch-off voltage is then related to the source and drain voltages,  $V_S$  and  $V_D$ , through their corresponding normalized charges as [22]

$$V_P - V_S = U_T(q_S - 1 + ln(q_S)),$$

(2-9)

$$V_P - V_D = U_T(q_D - 1 + \ln(q_D)).$$

(2-10)

(

<sup>&</sup>lt;sup>1</sup> Here, we made a distinction between  $i_d$  and *IC* (Inversion Coefficient) as IC is often referred to an approximation of  $i_d$  in the saturation region of operation [28], [35].

Therefore, the drain to source voltage,  $V_{DS}$ , normalized by  $U_T$  is given by

$$\frac{V_{DS}}{U_T} = q_S - q_D + ln\left(\frac{q_S}{q_D}\right).$$

(2-11)

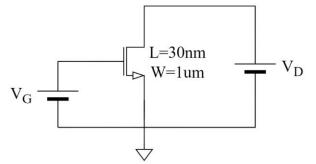

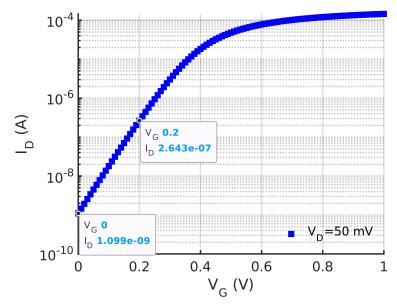

#### 2.1.2 Comparison of the 3-parameter model and DC measurements

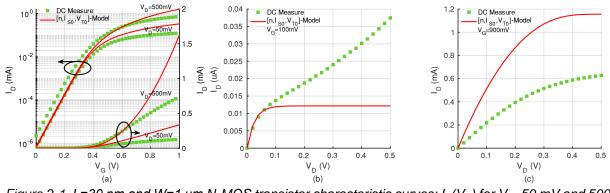

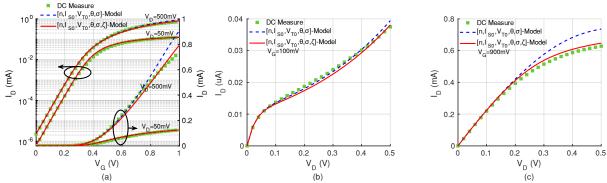

To illustrate the accuracy of the model and the improvements given by the integration of the different parameters modeling SCEs, a comparison is done against the measurements for a 30 nm length and 1  $\mu$ m width n-channel transistor of the 28 nm FD-SOI technology. All model parameters shown in the comparison were extracted following the procedure explained in section 3.1

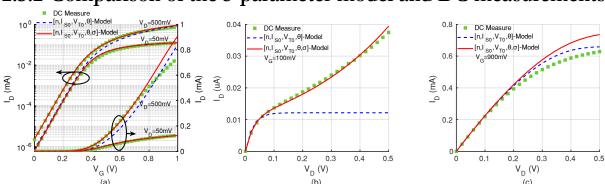

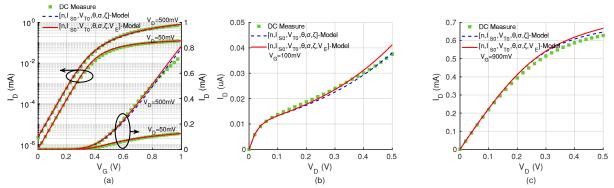

Figure 2-1. L=30 nm and W=1  $\mu$ m N-MOS transistor characteristic curves:  $I_D(V_G)$  for  $V_D=50$  mV and 500 mV in linear (right axis) and in semilogarithmic scale (left axis) (a),  $I_D(V_D)$  for  $V_G=100$  mV (b) and for  $V_G=900$  mV (c): Comparison between measures (green squares) and model based on 3 parameters (solid red line): n=1.377,  $I_{S0}=5.9$   $\mu$ A and  $V_T=380.3$  mV.

Figure 2-1 shows a comparison between the 3-parameter model and some DC measurements. The two main characteristic curves  $I_D(V_G)$  and  $I_D(V_D)$  are presented.

As it can be noticed in the  $I_D(V_G)$  characteristic (Figure 2-1(a)), the model has good accuracy in the weak and moderate inversion regimes of the transistor ( $V_G < 600 \text{ mV}$ ), but presents an overestimation of the drain current in the strong inversion regime also visible in Figure 2-1(c). This can be explained by two short-channel phenomena in strong inversion regime: the apparent reduction of the carrier mobility due to series resistances and the carrier velocity saturation. The first one mainly impacts the triode region ( $V_D = 50 \text{ mV}$ ) and the second one, the saturated region of operation ( $V_D = 500 \text{ mV}$ ).

Besides, the semilogarithmic scale of  $I_D(V_G)$  (Figure 2-1(a)) brings to light two discrepancies with respect to the measured current in saturated region ( $V_D = 500 \ mV$ ) from weak to moderate regime ( $V_G < 500 \ mV$ ). The first one is a difference of the slope, n, and the second one is an underestimation of the drain current. The first discrepancy

can be minimized by slightly adjusting the slope factor, n, to optimize the fit with the measurements [35], noticing that the variation of n with respect to  $V_D$  is small enough to be neglected.

On the contrary, the current increase with  $V_D$  has to be modeled by taking into account two major short-channel effects: the DIBL and the CLM. In the absence of these two effects, the 3-parameter model cannot correctly reproduce the  $I_D(V_D)$  behavior. As shown in Figure 2-1, the current is underestimated in weak inversion while in saturated region it remains constant with  $V_D$ .

In the following subsections, we address the introduction of each of the four above-mentioned physical effects into the transistor model. The discussion starts with the carrier mobility reduction, which has a major impact in linear region in strong inversion regime and continues with the  $V_D$  dependence in saturated region operation.

# 2.2 Modeling the carrier mobility reduction and series resistances effects: $\theta$

#### 2.2.1 Carrier mobility reduction effect

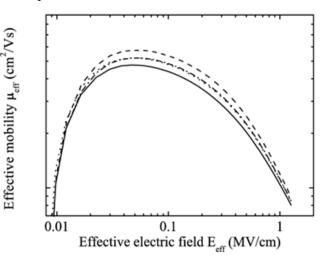

Figure 2-2. Impact of the effective electric field on the effective mobility.

The effective mobility of the carriers in the inversion layer of the MOS transistor depends on several scattering mechanisms causing a complex dependence of the mobility on the transversal and the longitudinal components of the electric field [23], [37]. The first one, related to carrier mobility reduction, is modeled here by  $\theta$ , and the second one by  $\zeta$ , related to the carrier velocity saturation, is described in section 2.4.

As illustrated in Figure 2-2, when a high vertical (or transversal) electric field is applied in the transistor channel, the mobility in the inversion layer near the semiconductor-oxide interface is reduced. This reduction, that leads to an effective

carrier mobility, is mainly due to three mechanisms: Coulomb scattering, photon scattering, and surface roughness scattering [23]. The carrier mobility reduction will cause a decrease of the drain current, especially in strong inversion regime and in linear region.

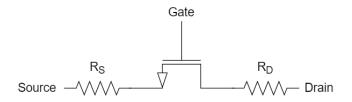

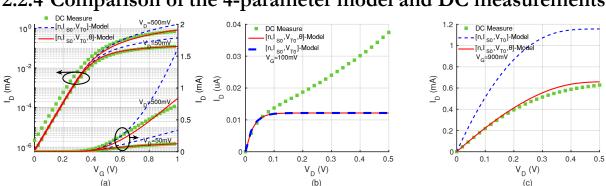

#### 2.2.2 Series resistances effect

The source and drain series resistances cannot be overlooked in short-channel devices. For short-channel transistors, the voltage drop in the source and drain regions becomes important in strong inversion and especially in linear region, where the channel resistance is minimal. In practice, provided that the voltage drops in source and drain regions are small compared to the applied voltages, the series resistances effect can be modeled by just adding an extra contribution to the  $\theta$  parameter. As result, the presence of source and drain series resistances can be described as a further reduction of the apparent carrier mobility [23].

## 2.2.3 Model of carrier mobility reduction and series resistances effects

As explained above, both effects, the carrier mobility reduction and the drain and source series resistances, can be introduced in the drain current expression through a parameter related to the carrier mobility reduction,  $\theta$ , and the average inversion charge,  $(q_s + q_D)/2$ , which represents the vertical field dependence. Hence (2-7) is modified as

$$I_D = I_{S0} \frac{(q_S - q_D)(q_S + q_D + 2)}{1 + \theta \left(\frac{q_S + q_D}{2}\right)}.$$

(2-12)

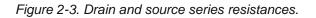

2.2.4 Comparison of the 4-parameter model and DC measurements

Figure 2-4. L=30 nm and W=1  $\mu$ m N-MOS transistor characteristic curves:  $I_D(V_G)$  for  $V_D$ =50 mV and 500 mV in linear (right axis) and in semilogarithmic scale (left axis) (a),  $I_D(V_D)$  for  $V_G$ =100 mV (b) and for  $V_G$ =900 mV (c): Comparison between measures (green squares) model based on 3 parameters (dashed blue line) and on 4 parameters (red solid line): n=1.377,  $I_{S0}$ =5.9  $\mu$ A,  $V_T$ =380.3 mV and  $\theta$ =0.115. Note that for (b) there is no change between models based on 3 and 4 parameters, as the effect of mobility reduction ( $\theta$ ) appears only in strong inversion.

In Figure 2-4(a), the impact of carrier mobility reduction is visible. Compared with the 3-parameter  $(n, I_{S0} \text{ and } V_{T0})$  model presented previously, the fitting with the measurements is better in strong inversion without degrading the behavior at weak and moderate inversion levels in triode region ( $V_D = 50 \text{ mV}$ ), proving that a 4-parameter  $(n, I_{S0}, V_{T0} \text{ and } \theta)$  model could be enough to describe the  $I_D(V_G)$  behavior for a single  $V_D$ . For  $V_D = 500 \text{ mV}$ , the model also improves the estimation of the current in strong inversion, even if the latter is still overestimated.

On the other hand, the underestimation of the drain current in weak inversion as the drain voltage increases (Figure 2-4(a) for  $V_G < 500 \text{ mV}$  and Figure 2-4(b)) remains, due to the DIBL effect, as explained in the next section.

Figure 2-4(b) clearly shows that the carrier mobility reduction ( $\theta$ ) does not have any effect on the current in weak inversion regime. Contrary to this, Figure 2-4(c) depicts the importance of including this effect in the modeling of the strong inversion regime. Unlike other design-oriented analytical models previously proposed [30], [31], the inclusion of  $\theta$  parameter allows to fully model all inversion regimes of operation of the MOS transistor for a given  $V_D$ . As it will be shown later, the  $V_D$  dependence will be further improved thanks to the introduction of additional parameters.

# 2.3 Modeling the drain-induced barrier lowering effect: σ

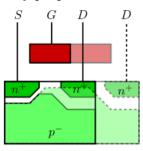

#### 2.3.1 Drain-induced barrier lowering effect

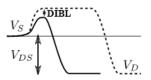

The formation of the conduction channel in long-channel transistors depends mainly on the gate voltage which controls the electric field between the gate and the substrate terminals. However, as the channel length decreases, a drop of the potential barrier at the source side occurs when the drain voltage increases (Figure 2-5). This phenomenon, known as the Drain-Induced Barrier Lowering (DIBL), allows the creation of a conduction channel at a lower gate voltage, which can be interpreted as a reduction of the threshold voltage,  $V_T$  [37].

Figure 2-5. Reduction of the potential barrier for short-channel transistors when applying a  $V_{DS}$  voltage [38].

Introducing the DIBL parameter,  $\sigma$ , this effect is modeled by adding a  $\sigma(V_D + V_S)$  term in the  $V_T$  expression as [24]

$$V_T = V_{T0} - \sigma (V_D + V_S) \,. \tag{2-13}$$

As a consequence, the pinch-off voltage increases and can be expressed from (2-8) as

$$V_P \approx \frac{V_G - V_{T0} + \sigma(V_D + V_S)}{n}$$

. (2-14)

#### 2.3.2 Comparison of the 5-parameter model and DC measurements

Figure 2-6. L=30 nm and W=1  $\mu$ m N-MOS transistor characteristic curves:  $I_D(V_G)$  for  $V_D=50$  mV and 500 mV in linear (right axis) and in semilogarithmic scale (left axis) (a),  $I_D(V_D)$  for  $V_G=100$  mV (b) and for  $V_G=900$  mV (c): Comparison between measures (green squares) model based on 4 parameters (dashed blue line) and on 5 parameters (red solid line): n=1.377,  $I_{S0}=5.9 \ \mu$ A,  $V_{T0}=384.9 \ m$ V,  $\theta=0.115$  and  $\sigma=0.093$

Figure 2-6(a), and (b) show is the importance of DIBL effect to correctly model the drain current in weak and moderate inversion regimes, introducing a dependence on  $V_D$  which was not accounted for in previous analytical models. The remaining drain current overestimation by the model, mainly in strong inversion regime as shown in Figure 2-6(c), is related to carrier velocity saturation effect which will be treated in the next section.

### 2.4 Modeling the carrier velocity saturation effect: $\zeta$

#### 2.4.1 Carrier velocity saturation effect

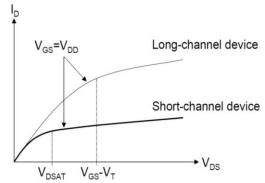

When the longitudinal electric field  $(V_{DS}/L)$  is low enough, as in long-channel transistors for instance, the carrier velocity is proportional to it. Nevertheless, for short-channel devices, the longitudinal electric field is higher and when it increases, the carrier velocity may reach a limit and saturate, leading to a reduced saturation current compared to that of a long-channel device (Figure 2-7). This effect is known as carrier velocity saturation [37].

The carrier velocity saturation effect has already been widely considered in the literature [28], [33]–[35]. In those published models, the carrier velocity saturation parameter is represented by  $\zeta$ , which is defined as

$$\zeta = \frac{\mu_n U_T}{L v_{sat}},\tag{2-15}$$

where,  $v_{sat}$  is the saturation velocity of the carriers. To be more accurate,  $\mu_n$  in (2-15) should be replaced by the effective mobility that includes the effects of the vertical electric field and series resistances presented in section 2.2.2. Keeping here  $\mu_n$  for simplicity purpose will lead to an effective value of  $\zeta$ .

When the carrier velocity saturation is reached, the drain current is given by [23]

$$I_{Dsat} = -W v_{sat} Q'_{IDsat} . (2-16)$$

Or, using the normalized quantities,

$$i_{dsat} = \frac{I_{Dsat}}{I_{S0}} = \frac{2}{\zeta} q_{Dsat}$$

(2-17)

Then, the approximation introduced in [40], considering that the saturation of carrier velocity only occurs at the drain side is made. This assumption simplifies the model equations at the cost of a lower accuracy in the transition from linear to saturated region. With these considerations, the general expression of the drain current (2-12) can still be used to extract  $q_{Dsat}$  value, replacing  $q_D$  by  $q_{Dsat}$ ,

$$i_{dsat} = \frac{2}{\zeta} q_{Dsat} = \frac{(q_S + q_{Dsat} + 2)(q_S - q_{Dsat})}{1 + \theta \left(\frac{q_S + q_{Dsat}}{2}\right)}.$$

(2-18)

Doing so, we obtain the following relation between  $q_s$  and  $q_{Dsat}$ :

$$q_{S} = \frac{\theta}{2\zeta} q_{Dsat} - 1 + \sqrt{1 + q_{Dsat} \left(2 + \frac{2}{\zeta} - \frac{\theta}{\zeta}\right) + q_{Dsat}^{2} \left(1 + \frac{\theta}{\zeta} + \frac{\theta^{2}}{4\zeta^{2}}\right)}.$$

(2-19)

Defining  $V_{DSsat}$  as the drain-to-source voltage for which  $q_D = q_{Dsat}$ , and using (2-11), one obtains [23]

$$\frac{V_{DSsat}}{U_T} = q_S - q_{Dsat} + ln\left(\frac{q_S}{q_{Dsat}}\right).$$

(2-20)

In order to preserve the continuity of the model from linear to saturated region, we can define an effective drain-to-source voltage accounting for the carrier velocity saturation effect,

$$V_{DS}' = \frac{V_{DS}}{\sqrt[4]{1 + \left(\frac{V_{DS}}{V_{DSsat}}\right)^4}}.$$

(2-21)

This formulation, inspired from industry-standard compact models, ensures a smooth behavior of the model around  $V_{DS} = V_{DSsat}$ .

Similarly, one can define an effective drain voltage,

$$V'_{D} = V'_{DS} + V_{S} \,, \tag{2-22}$$

----

and its associated drain charge  $q'_D$ , using (2-10),

$$V_P - V'_D = U_T(q'_D - 1 + \ln(q'_D)).$$

(2-23)

Finally, the drain current expression of (2-12), becomes

$$I_D = I_{S0} \frac{(q_S + q'_D + 2)(q_S - q'_D)}{1 + \theta \left(\frac{q_S + q'_D}{2}\right)}.$$

(2-24)

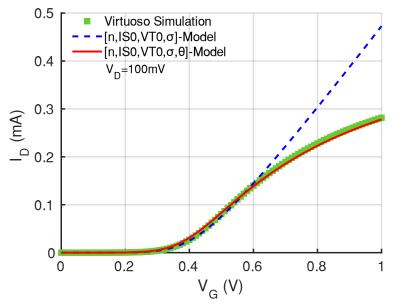

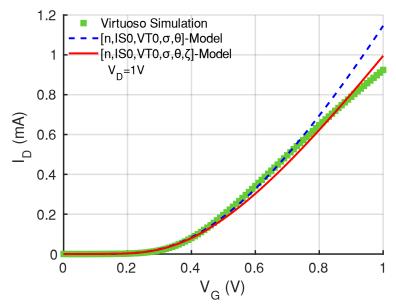

#### 2.4.2 Comparison of the 6-parameter model and DC measurements

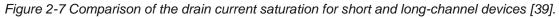

Figure 2-8 illustrates the benefits of introducing the carrier velocity saturation effect in the model through the sixth parameter,  $\zeta$ , especially in strong inversion regime for a transistor in saturated region (Figure 2-8(a) for  $V_D = 500 \text{ mV}$  and Figure 2-8(c)). As expected,  $\zeta$  parameter has no impact in linear regime (Figure 2-8(a) for  $V_D = 50 \text{ mV}$ ).

Figure 2-8. L=30 nm and W=1  $\mu$ m N-MOS transistor characteristic curves:  $I_D(V_G)$  for  $V_D=50$  mV and 500 mV in linear (right axis) and in semilogarithmic scale (left axis) (a),  $I_D(V_D)$  for  $V_G=100$  mV (b) and for  $V_G=900$  mV (c): Comparison between measures (green squares) model based on 5 parameters (dashed blue line) and on 6 parameters (red solid line): n=1.377,  $I_{S0}=5.9$   $\mu$ A,  $V_{T0}=384.9$  mV,  $\theta=0.115$ ,  $\sigma=0.093$  and  $\zeta=0.035$ .

## 2.5 Modeling the channel length modulation: $V_E$

## 2.5.1 Channel Length Modulation effect

The CLM effect occurs when the drain voltage increases after the pinch-off occurrence, creating a depletion region at the drain side which extends towards the source, and thus a reduction of the effective length of the channel by a quantity  $\Delta L$ , which, in turns, increases the current as  $V_D$  increases [37]. Considering this phenomenon in the presented analytical model will add a third effect directly linked to the dependency of the drain current on  $V_D$ .

Figure 2-9. Channel length modulation effect [38].

Taking advantage of the expression of  $\Delta L$  as a function of  $V_D$ , CLM can be accounted for by simply introducing a seventh parameter,  $V_E$ , leading to the following drain current expression:

$$I_D = \left(1 + \frac{V_{DS} - V'_{DS}}{V_E}\right) \frac{I_{S0}(q_S + q'_D + 2)(q_S - q'_D)}{1 + \frac{\theta}{2}(q_S + q'_D)}.$$

(2-25)

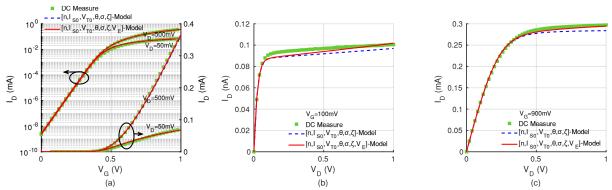

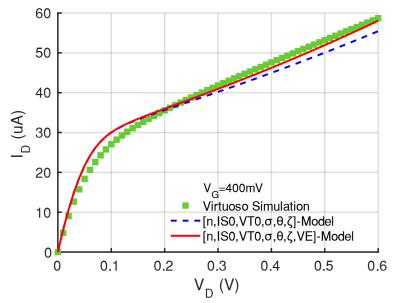

#### 2.5.2 Comparison of the 7-parameter model and DC measurements

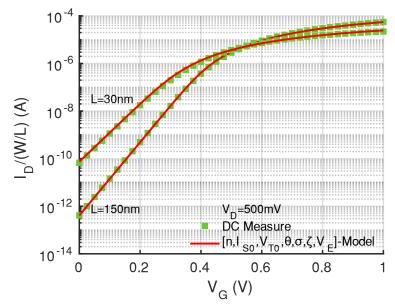

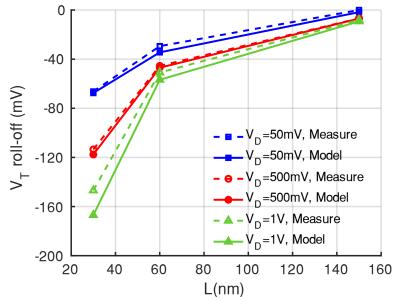

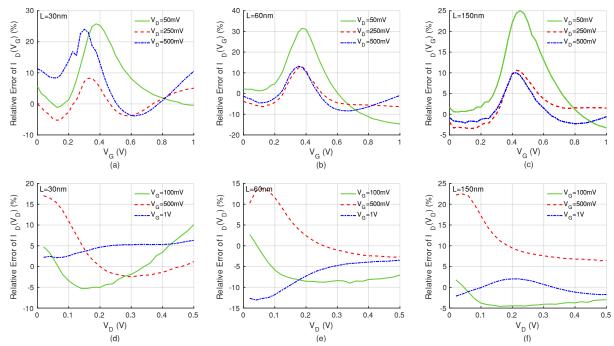

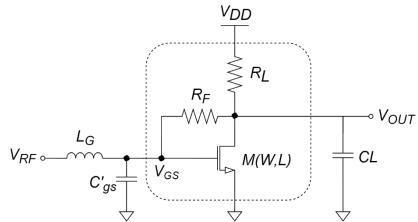

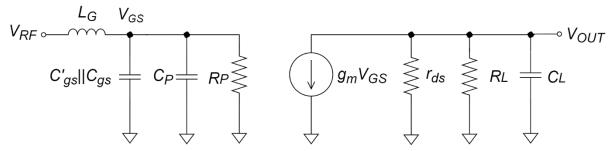

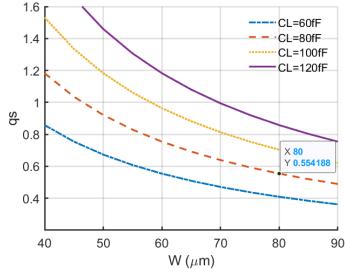

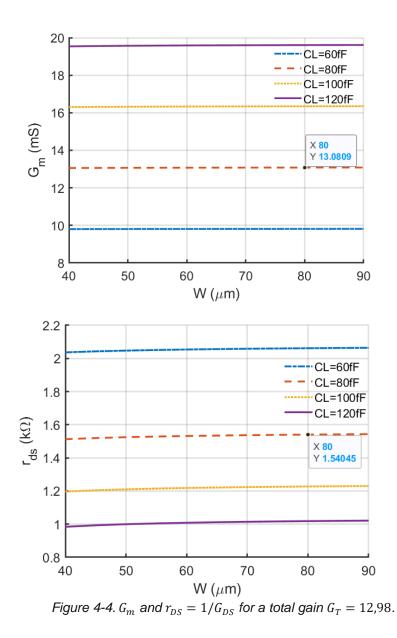

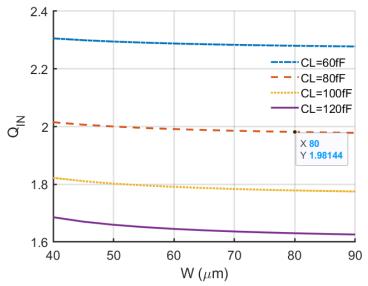

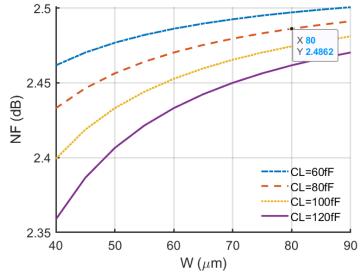

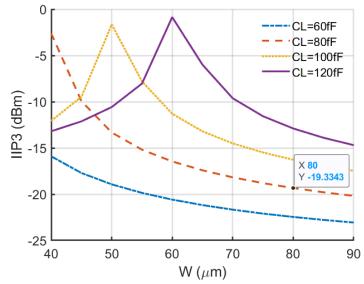

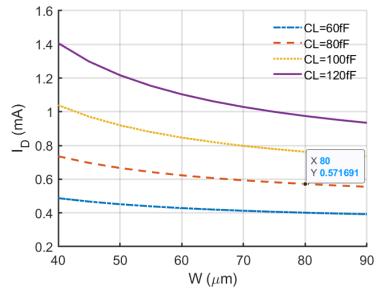

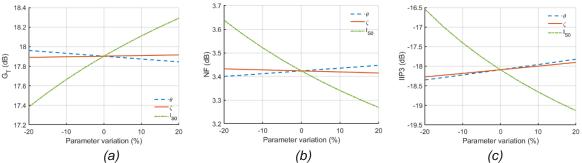

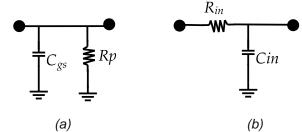

Figure 2-10 illustrates the effect of adding CLM modeling on a 30nm length transistor. As observed in the figure, the difference compared to the 6-parameter model is weak since for this channel length, the DIBL effect is strong and overshadows the CLM one. Hence, it is worth noticing here, that for short-channel devices, the 6-parameter model may be enough to capture the main characteristics of the electrical behavior of such devices.