## Contributions to the scalability of automatic precision tuning

Van-Phu Ha

#### ▶ To cite this version:

Van-Phu Ha. Contributions to the scalability of automatic precision tuning. Other [cs.OH]. Université de Rennes, 2023. English. NNT: 2023URENS007. tel-04189422

### HAL Id: tel-04189422 https://theses.hal.science/tel-04189422v1

Submitted on 28 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE

### L'UNIVERSITÉ DE RENNES

École Doctorale Nº 601 MAthématiques, Télécommunications, Informatique, Signal, Systèmes, Èlectronique Spécialité: Informatique

Par

### Van-Phu HA

### **Contributions to the Scalability of Automatic Precision Tuning**

Thèse présentée et soutenue à IRISA/Inria, le 10/03/2023

Unité de recherche : IRISA/Inria, Rennes

Thèse Nº:

#### Rapporteurs avant soutenance:

Florent de Dinechin Professeur, INSA Lyon

Gabriel Caffarena Professeur, Universidad CEU San Pablo, Madrid

#### **Composition du Jury:**

Président : Daniel Ménard Professeur, INSA Rennes, IETR

Examinateurs: Florent de Dinechin Professeur, INSA Lyon

Gabriel Caffarena Professeur, Universidad CEU San Pablo, Madrid

Fabienne Jézéquel Maître de Conférences HDR, Sorbonne Université, LIP6, Paris

Daniel Ménard Professeur, INSA Rennes, IETR

Dir. de thèse : Olivier Sentieys Professeur, Université de Rennes, Inria, IRISA

### **ACKNOWLEDGEMENT**

In the following lines, I would like to take the opportunity to express my gratitude to everyone who has given their support to me over this research period.

To begin, I would want to express my appreciation to both of my advisers, Prof. Olivier Sentieves and Dr. Tomofumi Yuki, for all of the assistance and support they have consistently provided. In addition to all of the technical advice they have given me, they have consistently kept me inspired and pushed me to push myself and aim for the greatest possible objectives.

I would like to give warm thanks for Prof. Daniel Ménard and Dr. François Charot in the CSI jury. They have been monitoring my research every year and giving me sincere advice that has kept me on the right track in my research and opened up new research directions.

My thanks also go to all the members of the jury, namely Prof. Florent de Dinechin, Prof. Gabriel Caffarena, Mrs. Fabienne Jézéquel, Prof. Daniel Ménard, for giving me the privilege of being a part of the thesis defense and evaluating my work.

My sincere thanks also go to Dr. Hoang Thanh Tung, who provided me with frequent conversation on issues relevant to both study and technology. He has been of great support to me by providing me with astute advice and the best possible direction with regard to new research topics.

I would like to express my gratitude to Silviu-Ioan Filip, who took the time to talk to me about regression technique and was a great assistance to me. Thanks to Nadia Derouault for her administrative support and to Ali Hassan El Moussawi for his support with Gecos tools.

The big thanks go to my colleagues and friends in TARAN team (formerly CAIRN team) at IRISA/Inria Laboratory. They all made the time spent at work enjoyable, with fun or serious conversations, technical or not.

In addition, I feel obligated to acknowledge my close friends Nguyen Khanh Linh, Cong Minh Thanh, and Nguyen Thi Thanh Tam for the valuable time they spent supporting me.

For my family, I would like to express my gratitude to my parents, Ha Hong Thanh and Bui Thi Khe, and the rest of my family for their unwavering love and support throughout my life and academic pursuits. Last but not least, I want to thank my wife, Vu Thi Van Anh, who always encourages me and continuously fills my life with love and happiness.

### **TABLE OF CONTENTS**

| $\mathbf{R}_{0}$ | ésum  | é en f                 | rançais                                                | 8  |

|------------------|-------|------------------------|--------------------------------------------------------|----|

| $\mathbf{Li}$    | st of | acron                  | yms                                                    | 13 |

| Li               | st of | figure                 | es                                                     | 16 |

| Li               | st of | tables                 | 5                                                      | 17 |

| 1                | Intr  | $\operatorname{oduct}$ | ion                                                    | 19 |

|                  | 1.1   | Energ                  | y-Efficient Computing in Post Moore's Law              | 19 |

|                  | 1.2   | Objec                  | tive of Thesis - Application-Level Tuning of Accuracy  | 25 |

|                  | 1.3   | Thesis                 | s Organization                                         | 25 |

|                  | Bibl  | iograpl                | ny                                                     | 27 |

| <b>2</b>         | The   | oretic                 | al Background and Related Work                         | 31 |

|                  | 2.1   | Appro                  | oximate Computing                                      | 31 |

|                  |       | 2.1.1                  | Approximate Computing for Error-Resilient Applications | 32 |

|                  |       | 2.1.2                  | Cross-Layer Approximate Computing Techniques           | 34 |

|                  |       |                        | Approximate Computing at the Software Level            | 34 |

|                  |       |                        | Approximate Computing at the Architecture Level        | 35 |

|                  |       |                        | Approximate Computing at the Hardware Level            | 36 |

|                  | 2.2   | Binar                  | y Arithmetic Number Representations                    | 37 |

|                  |       | 2.2.1                  | Floating-Point Arithmetic                              | 39 |

|                  |       |                        | Floating-Point Exceptions                              | 40 |

|                  |       |                        | Rounding modes                                         | 41 |

|                  |       | 2.2.2                  | Fixed-Point Arithmetic                                 | 41 |

|                  | 2.3   | Fixed                  | -Point Conversion Process                              | 42 |

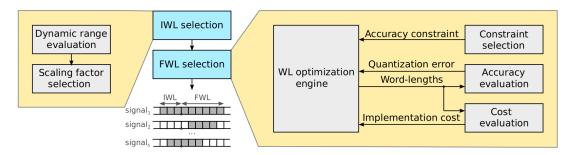

|                  |       | 2.3.1                  | Integer Word Length (IWL) Selection                    | 45 |

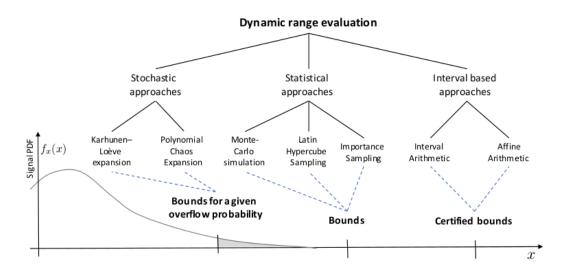

|                  |       |                        | Interval-Based Approaches                              | 46 |

|                  |       |                        | Statistical Approaches                                 | 47 |

|                  |       |                        | Stochastic Approaches                                  | 47 |

|                  |       | 2.3.2                  | Fractional Word Length (FWL) Selection                 | 48 |

|                  |       |                        | Cost Evaluation                                        | 48 |

### TABLE OF CONTENTS

|   |          | Accuracy Evaluation                                                   | 48         |

|---|----------|-----------------------------------------------------------------------|------------|

|   |          | Optimization Approaches                                               | 50         |

|   |          | Brute-force with upper and lower bounds                               | 51         |

|   |          | Heuristics                                                            | 51         |

|   |          | Min+1 bit                                                             | 51         |

|   |          | Max-1 bit                                                             | 52         |

|   |          | Hybrid algorithms                                                     | 52         |

|   |          | Divide-and-conquer approaches                                         | 53         |

|   |          | Analytical approaches                                                 | 54         |

|   | 2.4      | Conclusions                                                           | 55         |

|   | Bibl     | liography                                                             | 56         |

|   | <b>T</b> |                                                                       | o <b>=</b> |

| 3 |          | <b>.</b>                                                              | 6 <b>7</b> |

|   | 3.1      |                                                                       | 67         |

|   | 3.2      |                                                                       | 68         |

|   |          |                                                                       | 68         |

|   | 2.2      |                                                                       | 69<br>70   |

|   | 3.3      | ••                                                                    | 70         |

|   | 3.4      |                                                                       | 73         |

|   |          | · / .                                                                 | 73         |

|   |          |                                                                       | 75         |

|   | 2.5      | ·                                                                     | 75<br>76   |

|   | 3.5      |                                                                       | 76         |

|   |          | 1                                                                     | 76         |

|   |          |                                                                       | 77<br>70   |

|   |          |                                                                       | 78<br>70   |

|   |          |                                                                       | 79<br>70   |

|   |          |                                                                       | 79         |

|   | 2.6      |                                                                       | 84         |

|   | 3.6      |                                                                       | 85<br>86   |

|   | BIDI     | liography                                                             | 86         |

| 4 | Lev      | veraging Bayesian Optimization to Speed Up Automatic Precision Tuning | 89         |

|   | 4.1      | Introduction                                                          | 89         |

|   | 4.2      | Background and Related Work                                           | 91         |

|   |          | 4.2.1 Word-Length Optimization and Classical Approaches               | 91         |

|   |          | 4.2.2 Bayesian Optimization                                           | 92         |

|   | 4.9      | Mativations                                                           | റാ         |

|                           |       | 4.3.1   | Performance Analysis: TPE vs. Tabu                   | . 93  |

|---------------------------|-------|---------|------------------------------------------------------|-------|

|                           |       | 4.3.2   | Initial Combinations of TPE and Tabu                 | . 95  |

|                           | 4.4   | Propo   | sed Hybrid Approach                                  | . 97  |

|                           |       | 4.4.1   | Loss Function                                        | . 97  |

|                           |       | 4.4.2   | Transition Point for Hybrid Approach                 | . 97  |

|                           | 4.5   | Evalua  | ation                                                | . 100 |

|                           |       | 4.5.1   | Experiment setup                                     | . 100 |

|                           |       | 4.5.2   | Performance Evaluation                               | . 101 |

|                           | 4.6   | Conclu  | asion                                                | . 103 |

|                           | Bibl  | iograph | y                                                    | . 104 |

| 5                         | Res   | ource-  | Constrained Word Length Optimization - A New Problem | 107   |

|                           | 5.1   | Introd  | uction                                               | . 107 |

|                           | 5.2   | Relate  | d Work                                               | . 109 |

|                           | 5.3   | Resou   | rce-Constrained WLO                                  | . 110 |

|                           |       | 5.3.1   | Room for Accuracy Improvement Given a Cost Budget    | . 111 |

|                           |       | 5.3.2   | Resource-Constrained WLO as a New Problem            | . 112 |

|                           |       | 5.3.3   | Limitations of Classical WLO Methods                 | . 113 |

|                           | 5.4   | Solvin  | g Resource-Constrained WLO                           | . 113 |

|                           |       | 5.4.1   | Loss Function                                        | . 115 |

|                           |       | 5.4.2   | TPE Algorithm                                        | . 115 |

|                           | 5.5   | Evalua  | ation                                                | . 116 |

|                           |       | 5.5.1   | Experiment setup                                     | . 116 |

|                           |       | 5.5.2   | Performance Evaluation                               | . 118 |

|                           | 5.6   | Conclu  | ısion                                                | . 122 |

|                           | Bibl  | iograph | y                                                    | . 122 |

| 6                         | Con   | clusio  | ns and Perspectives                                  | 125   |

| Li                        | st of | public  | eations                                              | 128   |

| $\mathbf{A}_{]}$          | ppen  | dix A:  | TypeX - An Automatic Float to Fix Conversion toolbox | 131   |

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | dix B:  | An Extension of TypEx in Python                      | 148   |

### RÉSUMÉ EN FRANÇAIS

La consommation d'énergie est l'un des problèmes majeurs de l'informatique aujourd'hui, du calcul haute performance aux systèmes embarqués. Ces dernières années, l'approximation des calculs a reçu un regain d'intérêt pour améliorer l'efficacité énergétique. De nombreuses applications n'exigent pas une précision élevée, et les techniques de calcul approximatif augmentent l'espace de conception en fournissant de nombreux compromis entre la précision, les coûts et les performances. Cette thèse se concentre sur le développement de méthodes pour l'exploration systématique de cet espace de conception, y compris la modélisation de la performance et de la précision et l'automatisation de la conception. Nous utilisons la virgule fixe pour la représentation des données des données et nous optimisons la longueur du mot de chaque données et calcul pour chercher un bon équilibre entre le coût et la précision. Ce problème est appelé Word length Optimization (WLO) ou réglage automatique de la précision. Cette thèse contribue à trois directions de recherche. Premièrement, une méthode est proposée pour améliorer le passage à l'échelle du WLO pour les grandes applications. Pour réduire la complexité exponentielle de la nature de WLO, l'application d'entrée est décomposée en noyaux qui sont ensuite résolus indépendamment. Pour allouer les budgets de réduction de précision à chaque noyau, l'idée principale est de caractériser l'impact de l'approximation de chaque noyau sur la précision et le coût par simulation et régression pour construire les modèles empiriques. La deuxième direction de recherche est un algorithme hybride combinant l'optimisation Bayésienne (BO) et une recherche locale rapide pour accélérer la procédure WLO. Un mécanisme efficace est proposé pour obtenir de bons modèles en peu de temps. La dernière contribution ouvre une nouvelle voie de recherche sur le WLO avec contraintes de ressources. Les approches actuelles résolvent principalement les problèmes de WLO avec une contrainte de qualité (précision). Dans cette étude, un algorithme basé sur l'optimisation bayésienne a été proposé pour maximiser la qualité des calculs sous contrainte d'un budget de coût du matériel.

### Motivations

Alors que nous entrons dans l'ère du "dark silicon", où les avantages de la réduction de la taille des transistors sont limités par la puissance consommée, les scientifiques et les fabricants de puces se trouvent au défi de trouver des solutions alternatives efficaces. Pour l'instant, nous devons concentrer nos efforts sur le développement de technologies à haut rendement énergétique

qui augmentent considérablement les ratios énergie-performance des microprocesseurs tout en réduisant leur surface et leur consommation d'énergie. La demande d'architectures informatiques et d'approches alternatives qui consomment moins d'énergie et génèrent moins de chaleur pousse à réexaminer les microprocesseurs traditionnels.

Ces dernières années, parallèlement aux progrès de l'architecture des calculateurs informatiques, comme les processeurs multi-cœurs ou les systèmes hétérogènes, les informaticiens et les architectes de machines se sont particulièrement intéressés à la modification des méthodes de calcul pour améliorer encore l'efficacité énergétique. Le calcul approximatif (AxC) apparaît comme une solution potentielle pour améliorer les performances et la consommation d'énergie des systèmes embarqués. Le calcul approximatif vise à fournir de bonnes solutions à des problèmes difficiles tout en utilisant beaucoup moins de ressources de traitement que les solutions plus précises. Par exemple, au lieu de chercher la valeur qui fournit le résultat le plus précis, les algorithmes approximatifs prennent une solution acceptable et garantissent un certain seuil d'erreur. Fondamentalement, AxC est conçu pour relaxer les calculs parfaitement précis à un niveau d'inexactitude acceptable pour gagner en performance et/ou réduire la consommation d'énergie. En effet, de nombreux systèmes embarqués ne nécessitent pas une précision (ou exactitude des calculs) élevée, et les concepteurs de matériel recherchent souvent un bon équilibre entre précision, vitesse, énergie et coût en surface. Diverses techniques de calcul approximatif élargissent l'espace de conception en fournissant un autre ensemble de points dans cet espace, permettant de trouver des compromis performance/précision. Aujourd'hui, la communauté des chercheurs et l'industrie déploient des efforts intensifs pour mettre en œuvre les méthodes de calcul approximatif proposées dans des systèmes commerciaux, tels que les plateformes FPGA, ASIC et GPU, afin de réduire la consommation d'énergie et d'améliorer les performances.

L'une des techniques les plus efficaces de l'AxC consiste à réduire la précision de la représentation arithmétique. Les représentations typiques à virgule flottante, telles que *float* (32 bits) et *double* (64 bits), peuvent être remplacées par des formats de données moins précis, tels que l'arithmétique à virgule fixe. De nombreuses techniques de traitement numérique du signal (DSP) utilisant une arithmétique à précision réduite permettent d'augmenter considérablement l'efficacité énergétique en diminuant les coûts de calcul et le stockage des données, tout en maintenant la précision requise du modèle.

Les systèmes embarqués sont plus performants et moins coûteux lorsqu'ils utilisent une arithmétique à précision réduite, mais il n'est pas facile de trouver un bon équilibre entre la perte de précision et l'amélioration de l'efficacité énergétique. L'état actuel de ces techniques consiste à concevoir des moyens d'automatiser l'optimisation de le nombre de bits (aussi longueur des mots) d'une manière qui tire le meilleur parti des avantages de la réduction de la précision des

opérateurs. Ce processus est appelé optimisation de la longueur des mots (WLO pour Word Length Optimization) ou réglage automatique de la précision (Automatic Precision Tuning). Ce processus explore les meilleures longueurs de mots pour les variables d'une application donnée afin de réduire le coût d'implémentation (consommation d'énergie et/ou surface), tout en maintenant la précision à un niveau acceptable malgré la quantification des données. Pour les applications réelles, où de nombreuses variables sont impliquées, cette procédure est confrontée à un problème de passage à l'échelle en raison de l'augmentation exponentielle de la complexité. En réalité, on estime que 25% à 50% du travail de conception est encore consacré à l'obtention d'un choix optimisé de configurations de longueur de mots en virgule fixe.

### Objectifs et contributions

Dans cette thèse, nous nous concentrons sur la modélisation et l'utilisation des approches AxC au niveau logiciel de conception. Cette thèse étudie de nouvelles méthodologies pour l'exploration systématique de l'espace de conception, y compris la modélisation du coût d'implémentation, qualité de service (QoS) et l'automatisation de la conception. Cela nous permet d'accélérer la sélection de la configuration optimale ou quasi-optimale qui (1) réduit le coût (surface et/ou consommation d'énergie) tout en répondant à la précision nécessaire à la sortie de l'application, ou (2) optimise la précision à la sortie de l'application dans un budget de coût. Cette thèse examine la question du WLO sous plusieurs angles, tels que le passage à l'échelle pour des applications larges et l'optimisation sous contrainte de ressources. Dans cette dissertation, trois contributions principales ont été proposées.

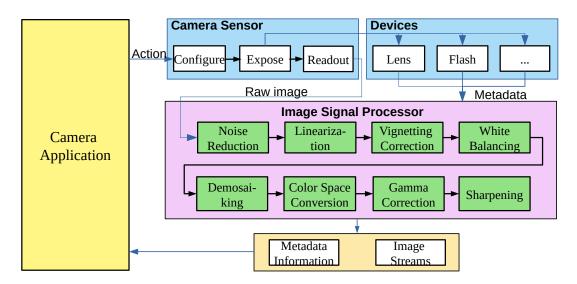

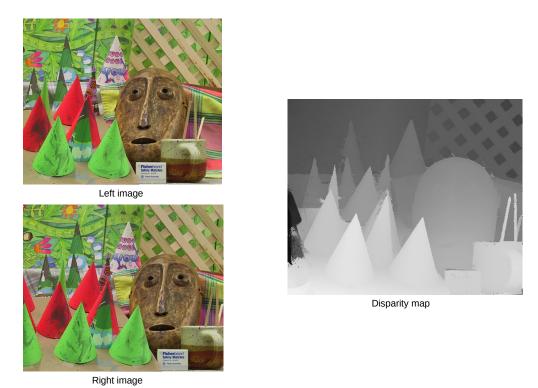

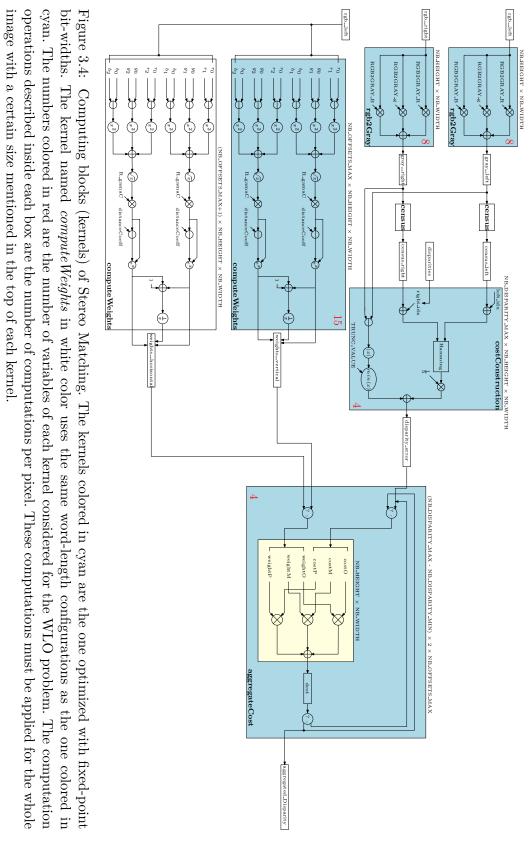

Dans la première contribution, nous proposons une approche pour atteindre une procédure d'optimisation de la longueur des mots (WLO) qui est plus évolutive pour les grands systèmes, et qui utilise des critères de qualité sophistiqués comme la similarité structurelle (SSIM) en traitement d'images. Pour éviter une croissance exponentielle et incontrôlée du temps d'exploration, cette méthode divise l'application d'entrée en noyaux (kernels) plus petits. La question fondamentale qui est étudiée dans cette recherche est le problème de l'allocation des budgets de bruit dus aux calculs aux noyaux individuels qui constituent l'application. Pour ce faire, il est nécessaire de modéliser les interactions entre les différents noyaux. L'idée centrale est d'utiliser la simulation et la régression pour évaluer l'effet de l'approximation de chaque noyau sur la précision ou le coût au niveau global. Notre méthode permet aux techniques de WLO de passer à l'échelle et de trouver de meilleures siolutions pour des applications complexes telles qu'un pipeline de traitement de d'images et la vision stéréo.

La deuxième contribution vise à accélérer le processus WLO et nous proposons une approche

hybride qui combine l'optimisation Bayésienne (BO) avec une recherche locale rapide. Les résultats expérimentaux de ce chapitre fournissent la première preuve que cette combinaison réduit le temps d'exploration. Nous proposons ensuite une nouvelle technique qui permet de trouver automatiquement un point de transition approprié entre les deux algorithmes. Afin d'identifier le moment où il faut passer de la BO à la recherche locale, nous effectuons une analyse statistique de la convergence des modèles probabilistes créés pendant l'optimisation Bayésienne, puis nous formulons une condition d'arrêt. Les résultats expérimentaux montrent que, pour les grands benchmarks utilisés, notre technique peut faire gagner jusqu'à 80% de temps d'exploration.

La dernière contribution s'est concentrée sur un autre aspect de l'optimisation de la longueur des mots qui est affecté par les limitations matérielles. Il est important de noter que la majorité des méthodes de pointe résolvent le problème de WLO sous contrainte de précision. Aucune étude n'a été menée sur la manière d'améliorer la qualité de service (i.e., ici la précision des calculs) tout en maintenant les coûts à un niveau bas. Pour les équipements électroniques à faible puissance ou à faible coût, il s'agit d'un obstacle majeur à l'amélioration des performances des applications. Dans un premier temps, nous démontrons l'importance du problème WLO sous contraintes de ressources, en nous concentrant sur les systèmes à consommation énergétique contrainte. Nous soulignons ensuite la difficulté de choisir un état initial approprié pour les problèmes WLO, inhérente aux méthodes traditionnelles comme la recherche Tabu. Nous proposons d'utiliser une méthode BO/TPE qui incorpore une fonction de perte ajustable. Nos résultats expérimentaux démontrent que notre technique est plus performante que les méthodes de l'état de l'art, WLO uniforme (UWLO) et recherche Tabu. Nous constatons également que la qualité de la solution trouvée par la recherche Tabu dépend fortement du contexte. Notre méthode est la première à s'attaquer au problème du WLO sous contrainte de ressources, et elle sert également de tremplin pour des travaux futurs qui pourraient améliorer le passage à l'échelle et l'optimalité du problème.

### Contenu du manuscrit

La thèse est organisée en six chapitres. L'histoire des ordinateurs est présentée dans le chapitre 1, depuis les premiers jours de la technologie SIlicium jusqu'aux alternatives de la période du *Dark Silicon*. Dans ce chapitre, nous abordons le calcul approximatif, une des technologies émergente de l'ère post loi de Moore. La question de l'optimisation de la longueur des mots est le principal objectif de recherche de cette thèse parmi les méthodologies de calcul approximatif. Le chapitre 2 présente les fondements de l'arithmétique à virgule fixe et à virgule flottante, ainsi que le contexte du problème de l'optimisation de la longueur des mots, suivi d'une étude des

approches récentes utilisées pour résoudre ce problème de WLO. Le chapitre 3 présente notre première contribution visant à améliorer le passage à l'échelle des méthodes d'optimisation WLO pour les larges applications qui utilisent de plus des métriques de qualité complexes, telles que la similarité structurelle (SSIM) en traitement d'images. Le chapitre 4 présente notre deuxième contribution en proposant un algorithme hybride combinant l'optimisation Bayésienne (BO) et une recherche locale rapide pour accélérer la procédure WLO. Le chapitre 5 présente notre troisième contribution qui se concentre sur un autre aspect de l'optimisation de la longueur des mots lorsque des contraintes de ressources matérielles sont considérées. Il s'agit d'un problème critique pour améliorer les performances des applications sur les systèmes électroniques et informatiques dont les budgets d'énergie ou de coût sont limités. Nous proposons un algorithme basé sur BO pour résoudre ce problème. Le chapitre 6 résume les principaux résultats de cette thèse et discute des pistes d'études potentielles pour des travaux ultérieurs.

### LIST OF ACRONYMS

AA Affine arithmetic

AI Artificial intelligence

ASIC Application-specific integrated circuit

AxC Approximate Computing

BER Bit Error Rate

BO Bayesian optimization

CPU Central processing unit

DNN Deep neural network

DSP Digital signal processing

FPGA Field-programmable gate array

FWL Fractional Word Length

GP Gaussian Processes

GPU Graphics processing unit

GWLO Global Word Length Optimization

IC Integrated Circuit

IoT Internet of Things

ISP Image Signal Processor

IT Information Technology

IWL Integer Word Length

LSB Least significant bit

LTI Linear time-invariant system

MC Monte-Carlo

MOSFET Metal-oxide-semiconductor field-effect transistor

MSB Most significant bit MSE Mean Square Error

MWLC Minimum word length configuration MWLO Multiple Word-Length Optimization

NPU Neural processing unit

ODG Objective Degradation Grade

PDF Probability density functions

PSNR Peak signal-to-noise ratio

QoS Quality of service

RAM Random-access memory

SM Stereo Matching SoC System on Chip

$\operatorname{SQNR}$  Signal-to-Quantization-Noise Ratio

SRAM Static random-access memory

SSIM Structural Similarity

TPE Tree-structured Parzen Estimator

UWLO Uniform Word-Length Optimization

WL Word Length

WLO Word Length Optimization

### **LIST OF FIGURES**

| 1.1  | 50 years of microprocessor trend data                                                                                                                         | 21  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | An example of Approximate Computing                                                                                                                           | 23  |

| 1.3  | Cost comparison of various operations                                                                                                                         | 24  |

| 2.1  | Design space with three variables (accuracy, energy consumption and performance)                                                                              | 33  |

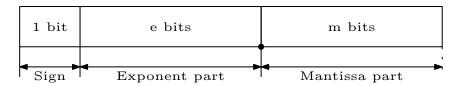

| 2.2  | A number represented in the floating-point format                                                                                                             | 39  |

| 2.3  | A number represented in the fixed-point format                                                                                                                | 42  |

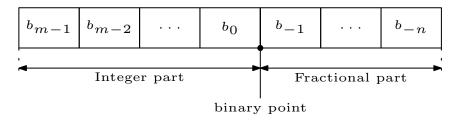

| 2.4  | Floating-point to fixed-point conversion process                                                                                                              | 44  |

| 2.5  | Techniques for assessing dynamic range are categorized into groups                                                                                            | 45  |

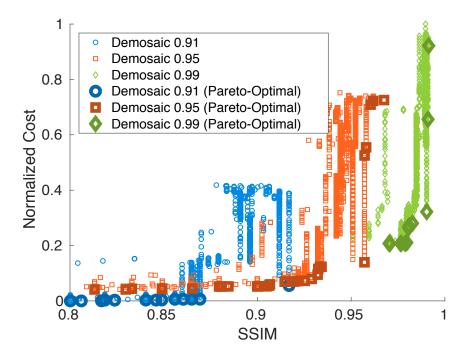

| 3.1  | All explored solutions of three WLO runs for Demosaic                                                                                                         | 74  |

| 3.2  | Image Processing Pipeline used in Smart Phone Camera                                                                                                          | 77  |

| 3.3  | Stereo Matching example                                                                                                                                       | 78  |

| 3.4  | Computing blocks (kernels) of Stereo Matching                                                                                                                 | 80  |

| 3.5  | Two numerical solutions                                                                                                                                       | 81  |

| 3.6  | Two numerical solutions                                                                                                                                       | 82  |

| 3.7  | Two numerical solutions                                                                                                                                       | 83  |

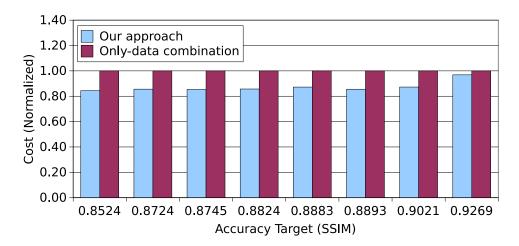

| 3.8  | Comparison of exploration time for ISP and Stereo Matching (SM)                                                                                               | 84  |

| 3.9  | The quality of solutions by our approach compared to the best combination of                                                                                  |     |

|      | the configurations used for accuracy model construction. These results are for ISP                                                                            |     |

|      | with 4 kernels                                                                                                                                                | 85  |

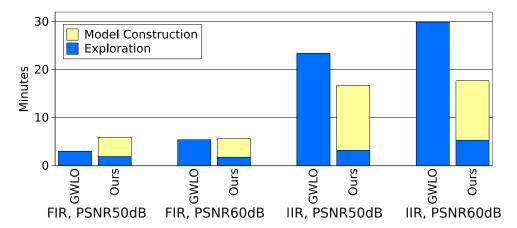

| 3.10 | Comparison of exploration time for filter applications                                                                                                        | 86  |

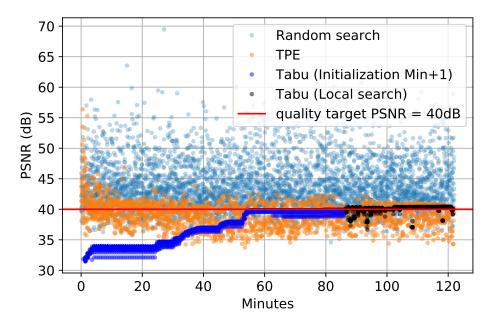

| 4.1  | Search process of Random search, Tabu and TPE                                                                                                                 | 94  |

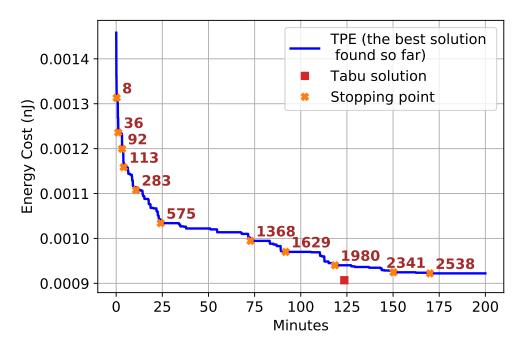

| 4.2  | Manually selected stopping points on the best solution obtained so far by TPE                                                                                 | 95  |

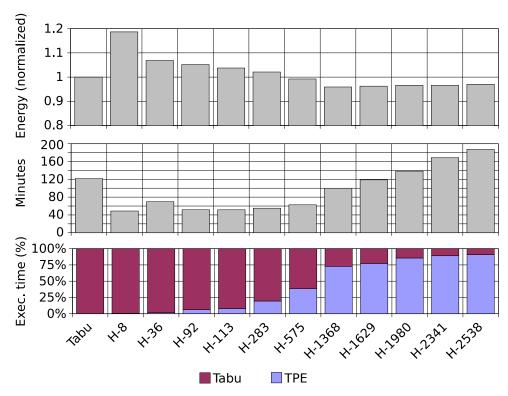

| 4.3  | A comparison in energy cost (top), total exploration time (middle) and separated exploration time (bottom) of Tabu and different combinations between TPE and |     |

|      | Tabu given the selected transition points                                                                                                                     | 96  |

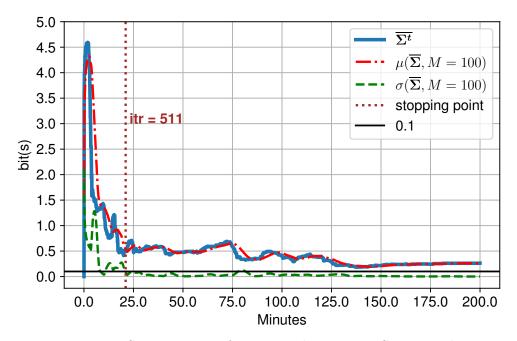

| 4.4  | Stopping point for IIR, quality target PSNR = 40dB                                                                                                            | 99  |

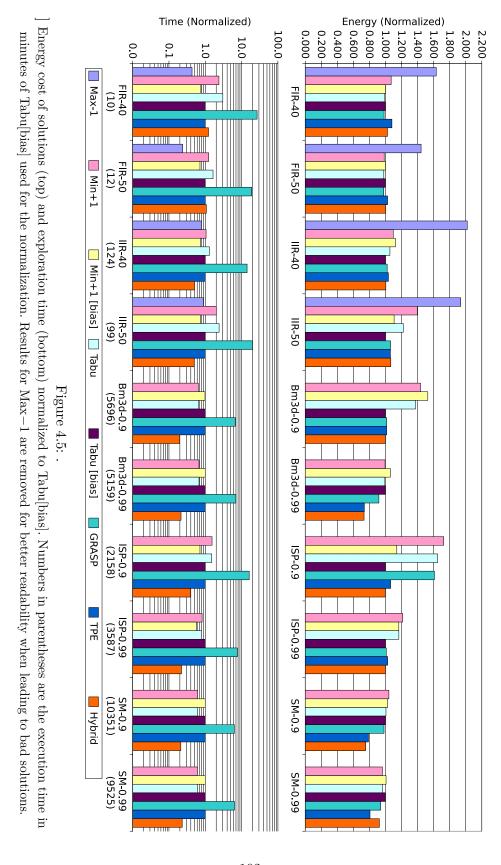

| 4.5  | Energy cost of solutions (top) and exploration time (bottom) normalized to                                                                                    |     |

|      | Tabu[bias                                                                                                                                                     | 102 |

### LIST OF FIGURES

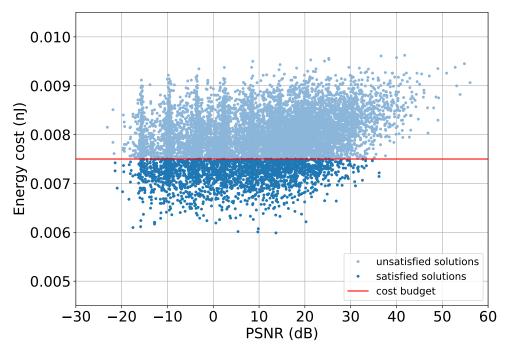

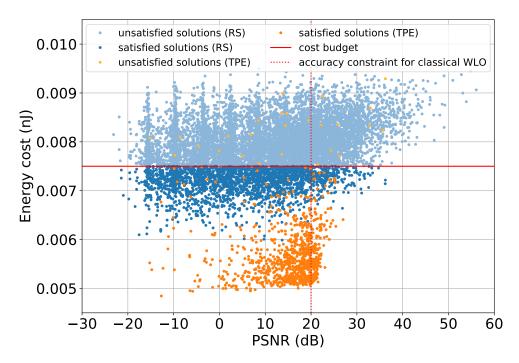

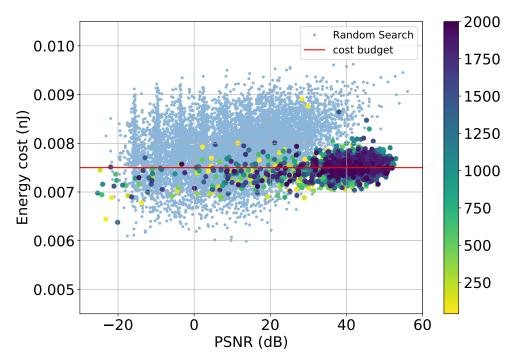

| 5.1 | 10 <sup>5</sup> random solutions as a representative subset of all possible solutions, for the |     |

|-----|------------------------------------------------------------------------------------------------|-----|

|     | FIR filter benchmark. The red line represents an energy budget of 0.0075 $\rm nJ$              | 111 |

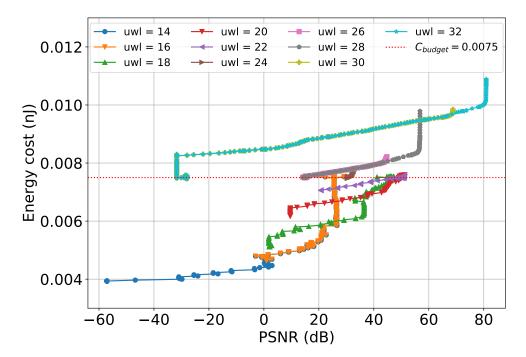

| 5.2 | The classical WLO problem in the context of the cost-constrained WLO problem.                  | 112 |

| 5.3 | Exploration trajectories of Tabu search method with different starting points                  | 114 |

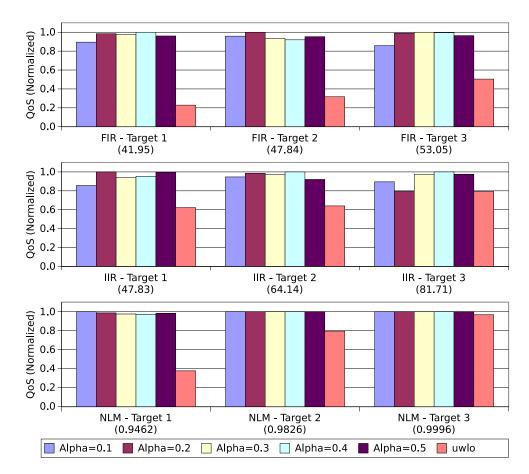

| 5.4 | Performance comparison between our approach and UWLO in terms of quality                       |     |

|     | of results for different benchmarks                                                            | 119 |

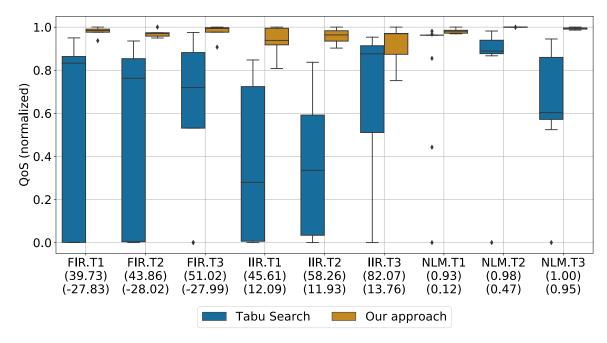

| 5.5 | Comparison of the normalized quality of solutions obtained by Tabu Search and                  |     |

|     | our approach for different benchmarks                                                          | 120 |

| 5.6 | The search direction of our approach compared with the Random Search                           | 121 |

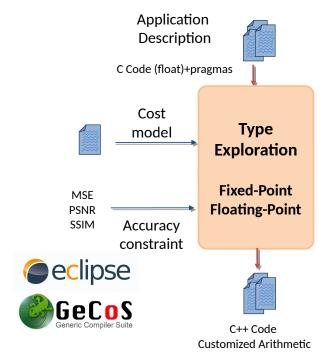

| A.1 | TypEx: a tool for type exploration and automatic floating-point to fixed-point                 |     |

|     | conversion                                                                                     | 131 |

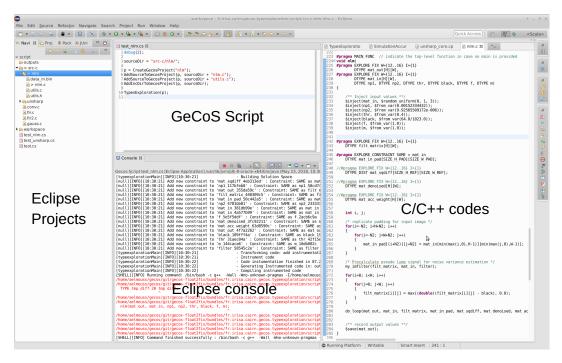

| A.2 | TypEx Tool Screenshot                                                                          | 133 |

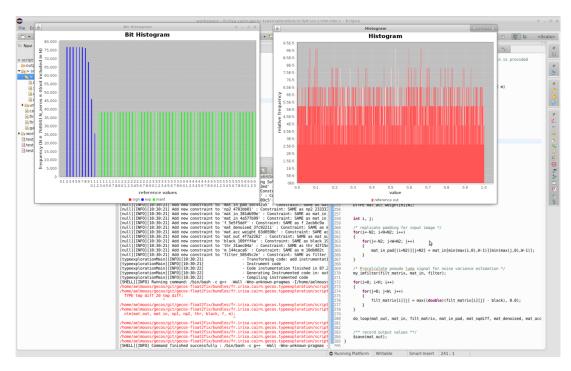

| A.3 | Example of histograms resulting from profiling of data values during exploration               | 134 |

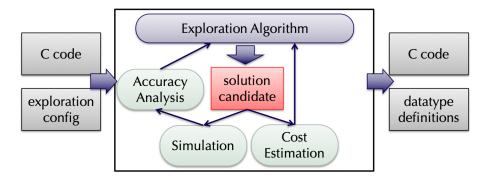

| A.4 | General principle of the exploration algorithm                                                 | 141 |

| A.5 | Example of pruning on a non-local mean (NLM) denoising kernel with two accu-                   |     |

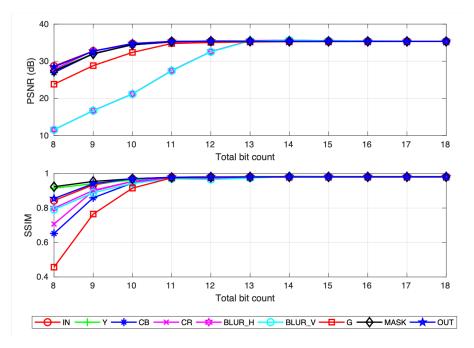

|     | racy metrics (PSNR and SSIM) and nine variables                                                | 142 |

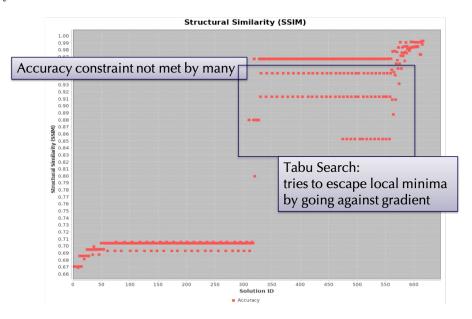

| A.6 | Example of solutions explored by the Tabu search algorithm                                     | 143 |

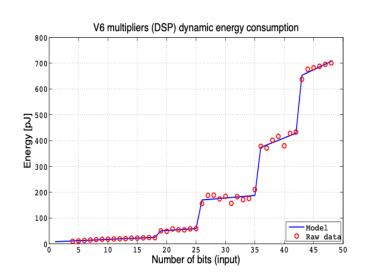

| A.7 | Energy model of multiplier for an FPGA target (Xilinx Virtex6, multipliers im-                 |     |

|     | plemented in DSP blocks) as a function of input wordlength                                     | 145 |

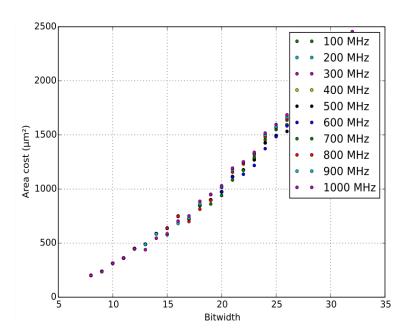

| A.8 | Area model of an adder for a 28nm ASIC technology as a function of input                       |     |

|     | wordlength                                                                                     | 145 |

| B.1 | TypEx on Python repository                                                                     | 149 |

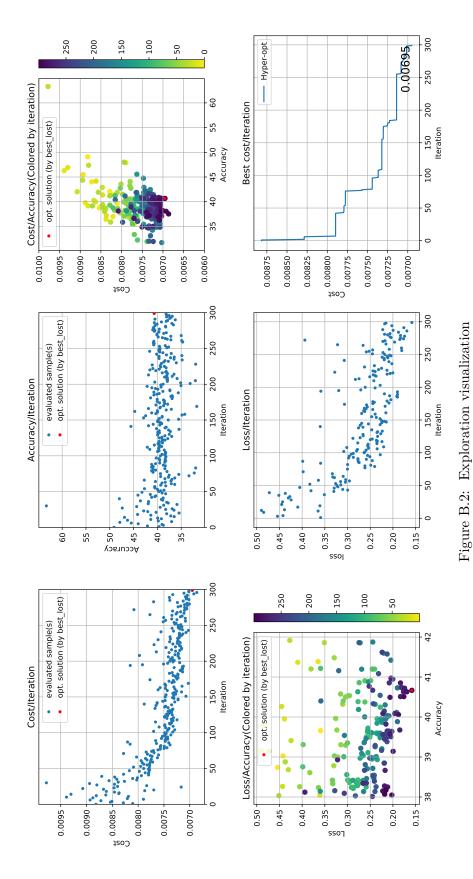

| B.2 | Exploration visualization                                                                      | 153 |

### **LIST OF TABLES**

| 2.1 | IEEE 754 floating-point representation types                                        |

|-----|-------------------------------------------------------------------------------------|

| 3.1 | Comparison of solutions for ISP and Stereo Matching (SM)                            |

| 3.2 | Comparison of solutions for FIR and IIR                                             |

| 5.1 | The benchmarks for the evaluation                                                   |

| 5.2 | Quality improvement of our solutions in percentage compared to UWLO solutions.      |

|     | Given value for each benchmark is the average of those obtained by different values |

|     | of $\alpha$                                                                         |

| 5.3 | Average quality improvement of the solutions provided by our approach over those    |

|     | obtained by Tabu Search (TS). The results are normalized with the range in          |

|     | Figure 5.5                                                                          |

| A.1 | A part of data for the cost model. The data contains the synthesized result of      |

|     | different adders and multipliers (different input/output wordlengths) 144           |

### INTRODUCTION

### 1.1 Energy-Efficient Computing in Post Moore's Law

Information technology is linked to the development of modern society. Electronic computers are now prevalent in many industries, including business, education, entertainment, health, agriculture, and manufacturing industries, contributing to the overall growth in productivity and income. Continued growth in computer performance is the main factor driving innovation in IT. However, this growth is facing difficulties due to a lack of energy. Energy consumption is one of the major issues in computing today, shared by all domains in computer science, from high-performance computing to embedded systems. In particular, we are entering into the dark silicon era, where the benefits of transistor scaling are diminished by the power limitation wall, while the needs of improving the computational performance to address many problems in big data, IoT, Artificial Intelligence, and High Power Computing are a must. This situation poses challenges for scientists and leading chip manufacturing companies to find effective alternative solutions to continue to increase the performance of electronic chips in the dark silicon era.

In 1965, an American engineer, Gordon Moore, made a prediction (the well known Moore's Law), which stated that the number of transistors on a single monolithic chip doubles every two years, though the cost of computers is halved. This means that, every two years, we have a new chip generation with higher speed and performance with lower cost compared to the previous one. So far, Moore's Law has been the fundamental driving force for chip development for more than four decades. Although increasing the number of transistors guarantees performance growth, one of the main challenges of this process comes from the limitation of the power supply to the transistors.

More than three decades since 1971, Dennard's scaling theory, also known as MOSFET scale, is the main driving force behind Moore's law to provide a roadmap for the development of the manufacturing chip industry [1]. According to Dennard's scaling, the power density of transistors will keep to be constant as their dimensions get smaller, which allows chip manufacturers to raise clock frequencies to push the performance of the chips as high as possible without significantly increasing the overall circuit power consumption. In detail, we consider a 2-dimensional transistor. Based on Dennard's scaling rules, with each new generation created, the dimensions

of the transistor, i.e., width and length, are diminished by the factor  $\alpha = \sqrt{2}$ , which allows halving the area of the original transistor, and also means doubling the number of transistors in the same area. Scaling the dimensions with the factor  $\alpha$  results in a reduction in supply voltage and capacitance by about 30% and an increase in input frequency by about 40% [1], which in turn reduces the dynamic power consumption by half, as stated by the following equation representing the dynamic power consumption of a CMOS gate

$$P_{dyn} = a \cdot C \cdot V_{dd}^2 \cdot f. \tag{1.1}$$

where a is the activity of the gate, C its output capacitance representative of the gate area,  $V_{dd}$  its power supply volage, and f its frequency. As a result, the power consumption of the transistors will decline at the same factor as their area reduces. In other words, the power consumption remains the same even if the transistor density doubles each time a new chip generation is created.

#### The Raise of the Dark Silicon Era

However, around 2005, Dennard's scaling law stopped. Although the transistor area continues to shrink by the traditional ratio, i.e. 1/2, to double the number of transistors in the same area, the power per transistor is no longer scaled to the same ratio. The main cause of this change comes from the transistor operating voltages ( $V_{dd}$  and also the transistor threshold voltage  $V_t$ ) not being able to scale to the traditional 1/2 factor, due to the significant increase of leakage current. Indeed, leakage current increases exponentially as the threshold voltage decreases.

Additionally, due to the consequence of downsizing the transistor, leakage is also more likely in smaller devices with thinner dielectrics and shorter channels. In fact, The leakage current is the most important contributor to leakage power. Thus, lowering down the threshold operating voltage contributes to an increase in leakage power, causing an increase in the total power supply. As a consequence of this change, if the proportion of active transistors does not decrease from one technological generation to the next, the power supply needs to be increased to make up the shortfall since it cannot scale with the original rate. The failure of Dennard scaling has ushered in the era of "dark silicon" as known among chip designers. If the scaling rate of power supply for the transistor is less than that of the area, it is possible that not at all of the transistors available as a result of the scaling will be turned on and used. These non-functioning transistors are dark silicon, which accounts for a portion of the chip area. The failure of Dennard Scaling and the opening of the dark silicon era posed many challenges for the computing industry to maintain the advancement of computing performance. The lack of power used to activate all transistors disrupted the effectiveness of the techniques used to improve the performance of single-core microprocessors such as cache management, branch prediction and pipeline tech-

nique. This challenge pushes the semiconductor industry to find alternatives to further increase the performance of chips.

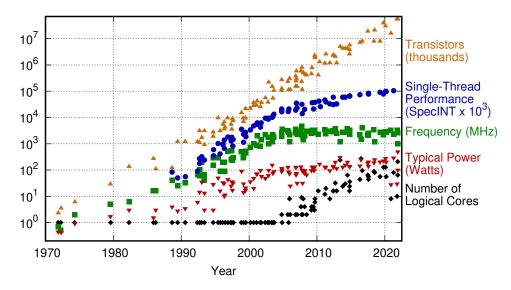

Figure 1.1: 50 years of microprocessor trend data. Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten. New plot and data collected for 2010-2021 by K. Rupp

Indeed, in 2005, the era of multicore began, as shown in Figure 1.1. Some components, like specialized logic and cache memory, contribute to overall integrated circuit (IC) performance while drawing power only when necessary. As a result, the IC industry began focusing on multicore architectures. The idea behind multicore technology is that it allows for parallel computing, which can significantly increase computing performance and efficiency by combining two or more central processing unit (CPU) cores into a single chip. The multicore chips do not necessarily run as fast as the highest performing single-core models, but they improve overall performance by handling more work in parallel. As a result, the heat and power consumption of the system are reduced thanks to managing the leakage power better. A multicore processor's design allows communication across all available cores, ensuring that processing jobs are split and assigned correctly. The processed data from each core is transmitted back to the motherboard via a single common gateway after the task is completed. When compared to a single-core CPU of comparable speed, this strategy considerably improves performance. However, one of the major challenges that are faced by multi-core processors is their memory systems. The execution of a program is often constrained by the memory bottleneck. A multicore system usually uses a 3-level cache structure, including L1, L2 and L3 caches. L1 and L2 are typically private, whereas L3 is the shared memory that synchronizes and facilitates data transmission across cores. When the number of cores increases, the amount of data transferred in L3 caches, buses, and interconnections also increases, resulting in data traffic congestion and performance degradation.

#### **Heterogeneous Computing**

Heterogeneous computing is considered the third age of computing after the single-core and multi-core eras. In addition to breaking Moore's law, it can successfully deal with challenges like energy consumption and scalability to further improve the computing performance. Running some special tasks using GPUs or FPGAs as processing units – or accelerators–, along with standard multicores for general processing, can form heterogeneous systems aimed at speeding up program execution [2]. Indeed, the multi-core architecture is a group of identical single-core processors. This multi-core processor provides the ability to develop and exploit applications for single-cores in a homogeneous manner, which means that the ability to run applications on single cores is identical. However, over the last decade, application domains running on a single processor have become increasingly divergent in terms of functionality and resource requirements, mainly due to the much faster growth in application complexity, which limits the performance of these applications when run on a set of identical cores. In contrast, there is evidence that heterogeneous multi-core architectures are increasingly used to support the efficient processing of computationally demanding applications thanks to significant performance improvements in terms of power consumption and throughput [3, 4, 5]. Besides, heterogeneous multi-cores are perfectly suited for the dark silicon era because only the cores required for a given application must be turned on during program execution, while unused application cores are turned off to save power [6]

#### Approximate Computing is one of the Solutions

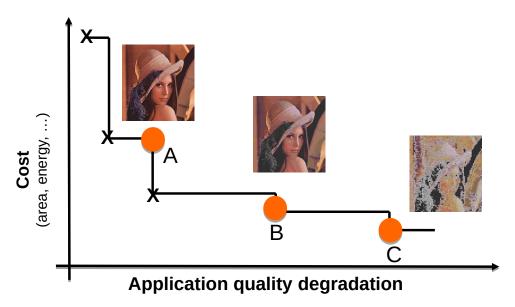

In recent years, along with improvements in computer architecture, computer scientists and leading chip manufacturers have been particularly interested in changing the computing methodology to further improve energy efficiency. Approximate Computing (AxC) methodology emerges as a potential solution to improve performance and energy consumption in embedded systems [7, 8, 9]. Figure 1.2 shows an example of how AxC is used to find a trade-off between the cost and the precision of the representation of an image. The idea behind AxC is to relax the perfectly precise computations to an acceptable level of inaccuracy to gain in performance and/or to reduce energy consumption. This is entirely consistent with the fact that many applications in embedded systems do not require high precision/accuracy, and hardware designers often seek a good balance between accuracy, speed, energy, and area cost. The majority of these applications are not concerned with calculating an exact numerical response. Instead, "correctness" is defined as the ability to provide outcomes that are good enough, or of sufficient quality,

<sup>1.</sup> Precision is defined in this thesis as the number of bits used to represent data.

to provide an acceptable level of user satisfaction [10]. This intuitive insight opens a huge room for researchers and chip makers to rethink computing methodology for most of the computing components that span different layers: application, software, compiler, and hardware levels. Various techniques for approximate computing augment the design space by providing another set of design knobs for performance-accuracy trade-off. Recent methods concentrate on developing systematic procedures for automating the development and compilation of approximation software and hardware. The techniques are designed (1) to provide developers with a better understanding of how approximation hardware and software impact application correctness, and (2) to automate the control of application accuracy, energy consumption, and performance [11].

Figure 1.2: Approximate Computing example: trade off precision for gains in cost (area and/or energy) degradation. The representation A is of great quality but comes at a high cost; the representation B may be of sufficient quality at a reduced cost; and the representation C is of poor quality but has the lowest cost.

#### The Efficiency of Reduced Precision

Reducing precision in arithmetic representation is one of the most effective AxC methods. The standard floating-point representation provides high-precision computations with traditional single (32 bit) and double (64 bit) precision. These data types offer a high degree of accuracy in calculations, but at the expense of long execution time and high energy consumption. In recent applications, particularly in machine learning and deep learning applications, there has been a growing interest in the use of reduced-precision arithmetic. Hardware platforms for training and inference of deep neural networks (DNNs) are shifting towards 8-bit and 16-bit precision and

use fixed-point arithmetic (i.e., integer) with a significant increase in energy efficiency thanks to reducing computational costs and data storage, while ensuring the required accuracy of the model [12, 13, 14].

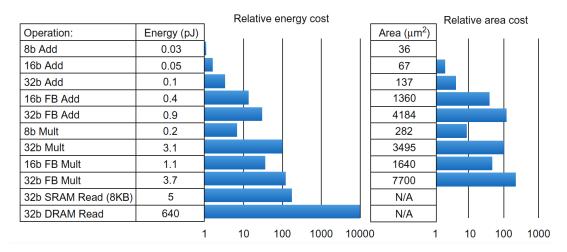

Besides, precision has a close relationship to area and energy consumption. Figure 1.3 [15] compares the energy and area cost of synthesized operators (adders and multipliers) with varying precision (8/16/32 bits) and number representations (float, integer) and memory read operations in SRAM and DRAM. For adders, the cost reduction rate is similar to that of bit-width shrinking. It is worth noting that when reducing the bit-width in multipliers, the cost drops dramatically. Hence, truncating the precision of arithmetic operations creates a new room to further improve energy efficiency.

Figure 1.3: Energy numbers are from Mark Horowitz "Computing's Energy problem (and what we can do about it)", ISSCC 2014 [15]. Area numbers are from synthesized result using Design compiler under TSMC 45nm tech node. FP units used Design Ware Library

Although using reduced-precision arithmetic improves the performance and cost of embedded systems, finding an efficient way to optimize between accuracy loss and energy efficiency improvement is not an easy task. The state of the art focuses on design methodologies to efficiently automate bitwidth assignment to maximize the benefits from reducing the precision of operators. This problem is called **Word-Length Optimization** (WLO) —or **Automatic Precision Tuning**—. Word-length optimization is the process of determining suitable word-lengths for variables of a given algorithm in order to reduce the implementation cost (energy consumption and/or area) while maintaining acceptable accuracy due to data quantization.

### 1.2 Objective of Thesis - Application-Level Tuning of Accuracy

The thesis was initiated as a research direction of the ANR research project named AppRoximaTivE Flexible Circuits and Computing for IoT (ARTEFaCT) under the collaboration of CEA Leti, INRIA, INSA, EPFL and CSEM. The ARTEFaCT project aimed to build on the preliminary results on inexact and exact near-threshold and sub-threshold circuit design to achieve major energy consumption reductions by enabling adaptive accuracy control of applications. ARTEFaCT proposed to address, in a consistent fashion, the entire design stack, from physical hardware design, up to software application analysis, compiler optimizations, and dynamic energy management. Combining sub-near-threshold with inexact circuits on the hardware side and, in addition, extending this with intelligent and adaptive power management on the software side was expected to produce significant results in terms of energy reduction, i.e., at least one order of magnitude, in IoT applications. The project has contributed along three research directions:

- 1. Approximate, ultra low-power circuit design.

- 2. Modeling and analysis of variable levels of computation precision in applications.

- 3. Accuracy-energy trade-offs in software.

The thesis contributes to the third research direction, accuracy-energy trade-offs in software. In this research, we focus on applying AxC techniques at the application level of design. This thesis is about developing methods for systematic exploration of the design space, including implementation cost/quality of service (QoS) modeling and automation of designs. This allows us to speed up the optimal or near-optimal design selection that (1) minimizes cost (area and/or energy consumption) while still satisfying required accuracy at the application output or (2) maximizes the accuracy at the application output under a cost budget. We target emerging System on Chip platforms (Xilinx Zynq or Intel SoC) that feature FPGAs tightly coupled with embedded processors.

This thesis is addressing WLO problem with several aspects including the scalability and resource-constrained optimization. Fixed-point data types are considered for WLO throughout studies in the thesis thanks to the wide use in the implementation of Digital Signal Processing algorithms in ASIC and FPGA platforms.

### 1.3 Thesis Organization

The thesis is organized in six chapters.

This chapter has introduced the historical development of computers, from the beginnings of MOSFET technology when Moore made his prediction about the increase in transistor performance, to the alternatives in Dark Silicon era. In this chapter, we also discussed Approximate

Computing, one of the emerging solutions in the post-Moore's law era. Among approaches in Approximate Computing, the Word Length Optimization problem is the main research objective in this dissertation.

Chapter 2 gives a fundamental background of arithmetic number representations, including Fixed-Point and Floating-Point arithmetic, as well as the context for the Word Length Optimization problem, followed by a survey of recent approaches being used to address WLO.

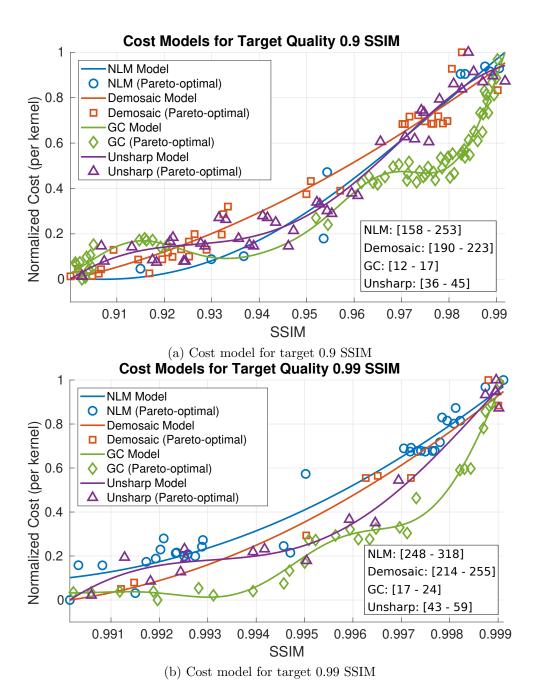

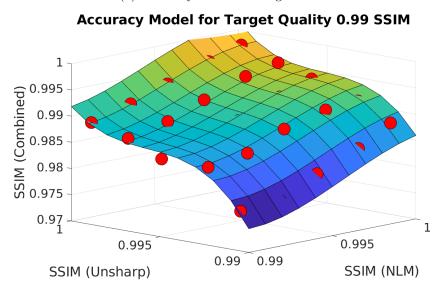

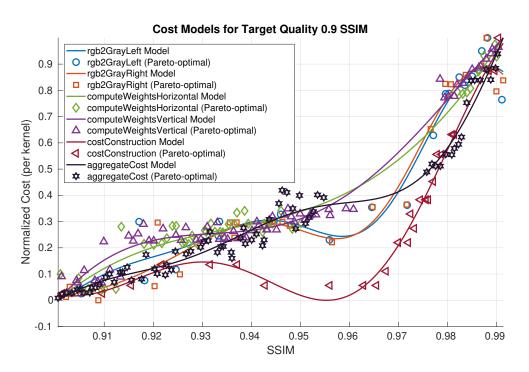

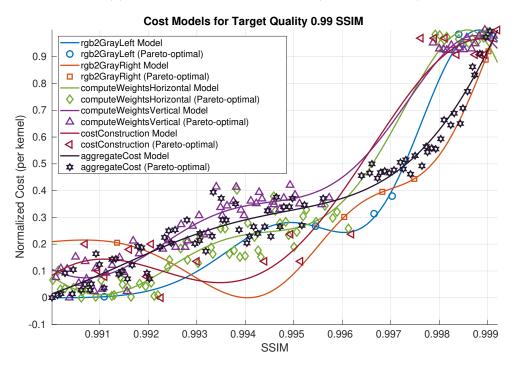

Chapter 3 presents our proposed method to improve the scalability of Word-Length Optimization (WLO) for large applications that use complex quality metrics such as Structural Similarity (SSIM). In this approach, the input application is decomposed into smaller kernels to avoid an uncontrolled explosion of the exploration time, which is known as noise budgeting. The main challenge addressed in this research work is how to allocate noise budgets to each kernel. This requires capturing the interactions across kernels. The main idea is to characterize the impact of approximating each kernel on accuracy/cost through simulation and regression. Our approach improves the scalability while finding better solutions for an Image Signal Processor pipeline.

Chapter 4 presents our proposed hybrid algorithm combining Bayesian Optimization (BO) and a fast local search to speed up the WLO procedure. In this chapter, through experiments, we first show some evidence on how this combination can improve exploration time. Then, we propose an algorithm to automatically determine a reasonable transition point between the two algorithms. By statistically analyzing the convergence of the probabilistic models constructed during BO, we derive a stopping condition that determines when to switch to the local search phase. Experimental results indicate that our algorithm can reduce exploration time by up to 50% - 80% for large benchmarks.

Chapter 5 focuses on another aspect of Word Length Optimization with hardware resource constraints. It is worth noting that state-of-the-art approaches mainly solve WLO given a quality constraint. There is no research on enhancing quality of service under a cost budget. This is a critical problem in improving the performance of applications in electronic devices with a limited energy or cost budget. In this chapter, we first show challenging issues of classical methods in the WLO problem with resource constrains. Then, we propose a Bayesian-Optimization-based algorithm to maximize the accuracy of computations under some cost constraint. Experimental results indicate that our approach outperforms the classical approach in terms of the obtained solution quality.

Chapter 6 summarizes the main results of this thesis and discusses potential next study paths for further work.

### **BIBLIOGRAPHY**

- [1] M. Bohr, "A 30 year retrospective on dennard's mosfet scaling paper," *IEEE Solid-State Circuits Society Newsletter*, vol. 12, no. 1, pp. 11–13, 2007.

- [2] T. Ju, Z. Zhu, Y. Wang, L. Li, and X. Dong, "Thread mapping and parallel optimization for mic heterogeneous parallel systems," in *International Conference on Algorithms and Architectures for Parallel Processing*. Springer, 2014, pp. 300–311.

- [3] T. Mitra, "Heterogeneous multi-core architectures," *Information and Media Technologies*, vol. 10, no. 3, pp. 383–394, 2015.

- [4] D. Shin, J. Lee, J. Lee, J. Lee, and H.-J. Yoo, "Dnpu: An energy-efficient deep-learning processor with heterogeneous multi-core architecture," *IEEE Micro*, vol. 38, no. 5, pp. 85–93, 2018.

- [5] H.-E. Zahaf, G. Lipari, M. Bertogna, and P. Boulet, "The parallel multi-mode digraph task model for energy-aware real-time heterogeneous multi-core systems," *IEEE Transactions* on Computers, vol. 68, no. 10, pp. 1511–1524, 2019.

- [6] J. Carabaño, F. Dios, M. Daneshtalab, and M. Ebrahimi, "An exploration of heterogeneous systems," in 2013 8th international workshop on reconfigurable and communication-centric Systems-on-Chip (ReCoSoC). IEEE, 2013, pp. 1–7.

- [7] M. Baboulin, A. Buttari, J. Dongarra, J. Kurzak, J. Langou, J. Langou, P. Luszczek, and S. Tomov, "Accelerating scientific computations with mixed precision algorithms," Computer Physics Communications, vol. 180, no. 12, pp. 2526–2533, 2009.

- [8] B. Barrois, O. Sentieys, and D. Menard, "The hidden cost of functional approximation against careful data sizing—a case study," in *Design*, Automation & Test in Europe Conference & Exhibition (DATE), 2017. IEEE, 2017, pp. 181–186.

- [9] R. Ragavan, B. Barrois, C. Killian, and O. Sentieys, "Pushing the limits of voltage over-scaling for error-resilient applications," in *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2017. IEEE, 2017, pp. 476–481.

- [10] S. Venkataramani, S. T. Chakradhar, K. Roy, and A. Raghunathan, "Approximate computing and the quest for computing efficiency," in 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC). IEEE, 2015, pp. 1–6.

- [11] A. Filieri, M. Kwiatkowska, S. Misailovic, and T. Mytkowicz, "Approximate and probabilistic computing: Design, coding, verification (dagstuhl seminar 15491)," in *Dagstuhl Reports*, vol. 5, no. 11. Schloss Dagstuhl-Leibniz-Zentrum fuer Informatik, 2016.

- [12] A. Zhou, A. Yao, Y. Guo, L. Xu, and Y. Chen, "Incremental network quantization: Towards lossless cnns with low-precision weights," arXiv preprint arXiv:1702.03044, 2017.

- [13] D. A. Gudovskiy and L. Rigazio, "Shiftcnn: Generalized low-precision architecture for inference of convolutional neural networks," arXiv preprint arXiv:1706.02393, 2017.

- [14] N. Wang, J. Choi, D. Brand, C.-Y. Chen, and K. Gopalakrishnan, "Training deep neural networks with 8-bit floating point numbers," *Advances in neural information processing systems*, vol. 31, 2018.

- [15] M. Horowitz, "1.1 computing's energy problem (and what we can do about it)," in 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC). IEEE, 2014, pp. 10–14.

# THEORETICAL BACKGROUND AND RELATED WORK

In this chapter, we survey and classify recent approximate computing techniques by the level of design. Then, we focus on presenting arithmetic number representations, including Floating-Point (FlP) and Fixed-Point (FxP). After that, we provide the fundamental background and a survey of recent optimization techniques for the Word-Length Optimization (WLO) problem, the central theoretical background of this thesis. The primary optimization approaches are examined and discussed, as well as the advantages and disadvantages of existing approaches. Methods being used to model the cost/accuracy trade-offs during WLO are also discussed in this chapter.

### 2.1 Approximate Computing

Energy consumption is one of the important metrics in designing embedded systems. In many complex systems, such as scientific computing, social networking, and financial analysis. Improving the system performance by adding more features or replacing old functions with more advanced ones, sometimes comes at the cost of increasing the energy supply for the system. Besides, with an increasing amount of data being generated, queried, stored, accessed, and computed by the applications running in these systems, their energy consumption has increased significantly. Considering mobile devices with limited energy budget, such as coin cells or even low-power battery sources, the energy consumption of computer systems becomes a crucial metric.

Approximate Computing (AxC) is an emerging technique in designing embedded systems for energy-efficiency improvement, i.e., enhancing the performance and reducing the area and power consumption. AxC seeks to minimize computing accuracy, in order to achieve large computational performance increase and energy consumption reduction, while ensuring an acceptable quality of service (QoS). Approximate computing provides an alternative paradigm for analyzing large datasets by simulating "what-if" scenarios for entering parameters that capture the necessary trade-off between accuracy and performance. To find the appropriate design that seeks for the golden balance between accuracy and performance, various AxC techniques have been

proposed at various design levels, i.e., system-, algorithmic-, and circuit-level.

Error-tolerant applications relating to human perception and cognition drive the majority of approximate computing. As human beings, our perception and cognition are not perfect, which implies that many computation tasks can be done with certain imperfections or approximations. Multimedia processing, machine learning, signal processing, and scientific computing are examples of such application areas where approximate computing has been used [1]. In recent years, the research focus of the approximate computing community has expanded from fast approximate search algorithms (e.g., low-complexity signal and image processing) to wide applications in big data (e.g., complex analytics in web search, recommendation systems), and real-time/embedded applications (e.g., sensor networks). Numerous of these applications rely on statistical or probabilistic computations, such as the ability to make alternative approximations to better fit the intended goals [1]. These applications aim to provide means for developing such high-level abstractions by formulating approximation problems as parameterized data analysis tasks and proposing concrete methods to solve them. Examples include models for language understanding (such as latent semantic analysis), machine translation, object recognition, medical diagnosis, and DNA sequencing.

However, designing an efficient and accurate approximate computing techniques involves understanding multiple factors, such as the environment conditions, computing load and resource availability. The task of finding an optimal point on the accuracy-performance trade-off axis remains quite challenging in realistic applications. Due to the large number of parameters, it is non-trivial to select an appropriate subset of parameters, and this selection process will be quite time consuming. Hence, it is important to develop effective techniques that speed up the process of selecting the suitable design point.

### 2.1.1 Approximate Computing for Error-Resilient Applications

AxC techniques can be successfully applied to a variety of applications to reduce computational effort thanks to the intrinsic error tolerance properties of those applications. This allows us to simplify the computational elements of the program so that the errors they cause are tolerable. The error tolerance property is defined as the capacity of a program to generate acceptable results despite the fact that some of its underlying computations are faulty or inaccurate [2]. For example, AxC methods can be used in sound and image processing since little sound distortions or slightly discolored pixels go undetected [3]. There are three factors that contribute to the inherent resiliency of applications [2, 4]:

1. The inputs: These applications are designed to handle noisy and redundant input data. For example, the input to the digital image processing algorithms already includes noise or

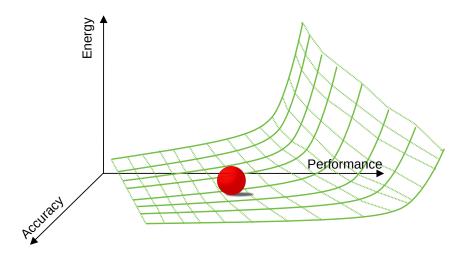

Figure 2.1: An example of design space that depends on three variables (accuracy, energy consumption and performance) for applications designed with AxC techniques. The third dimension, i.e., accuracy, opens a larger room for design optimization to further gains in energy efficiency (i.e., performance per Watt or energy per operations). The red point represents for the design flexibility in three dimensions.

quantization errors that come from digitizing analog data, data being also often sampled with noise.

- 2. The computations: The applications commonly utilize computing techniques like aggregation or iterative refinement to mitigate or repair approximation effects.

- 3. The outputs: The application of the concept that there is no such thing as a "golden" result, but rather a range of acceptable outputs or slight changes in the output that are undetectable by users. For example, a web search system can return similar results. Similarly, due to human limits in perception, occasional frame drops in video applications might go unnoticed.

Thanks to the error-tolerance property of those applications, we can adjust the accuracy of the application in a controlled manner to an acceptable level, which allows us to create a new level of design flexibility, which trade-offs the accuracy with traditional design metrics such as computational performance (number of computational units per second) and implementation cost (area utilization and/or energy consumption) as shown in Figure 2.1.

The use of AxC techniques in embedded system design leads to an optimization problem where the designers need to find a method to select an optimal or near-optimal solution from a design space exploration constructed by a variety of solutions with different parameters (performance, accuracy, and energy). With knowledge about components of the embedded system, the designers can create models that evaluate the interactions among these three parameters and

then formulate the optimization problem constrained by user-defined requirements for performance, energy and accuracy metrics. The optimization problem results in an estimated energy, performance and accuracy that can be compared to the specified constraints, enabling the selection of an optimal (or at least good enough) system design configuration. The selection of the solution using AxC techniques is based on a Pareto optimal design space, which includes a subset of solutions that achieve the highest performance level within a range of accuracy and energy cost. A properly designed AxC technique can improve the energy efficiency of the embedded application. It also helps designers to quickly obtain good design choices and hence reduce the development time, and eventually the time to market of electronic devices.

#### 2.1.2 Cross-Layer Approximate Computing Techniques

Energy consumption is one of key design metrics in battery-operated embedded system. The energy consumption directly relates to dynamic power dissipation  $P_{dyn}$  which is calculated by Equation 1.1 through the product of switching activity factor  $(\alpha)$ , load capacitance  $(C_L)$ , supply voltage  $(V_{dd})$  and clock frequency  $(f_{clk})$ . The reduction in energy consumption is essentially the reduction of individual ingredients Equation 1.1. From that, many AxC techniques were proposed to reduce energy consumption at different layers ranging from algorithm level down to circuit level. In this thesis, we divide techniques into three categories: software, architecture, and hardware. The mentioned methods are the most frequently used approximation approaches in the state of the art. This survey does not include newer or less commonly used methods. It is also worth noting that some methods are shared across layers.

#### Approximate Computing at the Software Level

Some frameworks allow programmers to identify the impact of approximation in specific sections of code, giving them control over the system's accuracy at the software level. Green [5] is a framework that enables programmers to take advantage of AxC in a systematic way, while also ensuring statistical QoS. It allows for complex functions and loops to be approximated. Green develops a model that assesses the impact of approximation on QoS loss, allowing approximation decisions to be made based on the programmer's QoS constraints.

Sampson et al. proposed EnerJ [6] that uses type qualifiers to declare data signals to be expressed in an approximate manner in a system. The storage, computation, and algorithm components utilized for the variables designated with the approximation qualifier can be approximate. The system can ensure that the precise and approximate program components are isolated statically.

Some works [7, 6] use *Loop Perforation*, which systematically skips iterations of the loops without significant quality degradation to reduce the volume of processing in an application. This

can reduce directly the load capacitance that is equivalent to the logic circuit. The consideration of the number representation is also one of efficient approaches to reduce the energy consumption.

Task skipping is an approximation approach that enables code blocks to be skipped based on a specified run-time boolean condition [8]. If a statement block is executed when the runtime boolean condition fails, then the remaining code blocks in that control structure will not be executed. Typically, this method is used for the most computationally demanding portions of the code. In many scenarios, instead of running the loop to its completion, the paradigm may instruct a hardware system to process less data in order to save power and computing time. Some related existing works can be found in [9, 10, 11, 12].

Data sampling [13, 9] is also considered an AxC technique at the software level. This is a method in which the incoming data are not analyzed in their whole, but rather a selection is made before processing. This method decreases the computation complexity, the execution time and the computing power required, while providing acceptable accuracy of the result.

#### Approximate Computing at the Architecture Level

Some works exploit the room for approximation in instruction-set architecture (ISA) [14] and memories [15, 16]. Hadi Esmaeilzadeh et al. [14] proposed ISA extensions that define a set of special instructions that allow the compiler to convey what can be approximated. Truffle, a micro-architecture concept, was suggested to implement the ISA expansions effectively. Dual-voltage operation is the basis of the proposed design, with a high voltage for exact operations and a low voltage for approximate operations. The micro-architecture's reliance on the instruction stream to know whether to employ the low voltage is a significant feature. The paper [17] further proposed a low-power accelerator based on a neural processing unit (NPU) that can perform approximately compute-intensive code segments. The NPU is tightly coupled to the processor pipeline to speedup code regions. It is quicker and more energy efficient to offload approximable code areas to NPUs than to execute the original code.

Sampson et al. [16] proposed techniques that allow applications to approximate data storage, improving the performance, longevity, and density of solid-state memory. There are two mechanisms in operation. The first reduces the amount of programming pulses necessary to write multi-level cells, allowing for mistakes. By transferring approximation data into blocks that have exhausted hardware error correcting capabilities, the second approach reduces wear-out failures and increases memory endurance.

Flikker, an application-level approach for reducing refresh power in DRAM memory, is introduced in [15]. Flikker allows programmers to designate critical and non-critical data in their code, and the runtime system allocates this data to different memory locations. Critical data are updated at the standard refresh rate, whereas non-critical data are renewed at much lower rates. This partitioning saves energy at the expense of a little increase in non-critical data cor-

ruption. As a result, Flikker reveals and exploits a fascinating trade-off between energy usage and hardware accuracy.

#### Approximate Computing at the Hardware Level

Several AxC approaches minimize storage and computation costs by modifying the precision of input or intermediate operands. Many works [18, 19, 20] use low-precision, efficient number representation, such as fixed-point arithmetic, to reduce the energy consumption. These works address the Word Length Optimization (WLO) problem to optimize fixed-point bit-widths of variables in the application to reduce the energy consumption with an acceptable quality at the application output. Indeed, using a shorter fixed-point word-length reduces the switching activity factor and the load capacitance since the operators compute with less bits. The problem of WLO to optimize fixed-point bit-widths of variables in the application is the main objective of this thesis and will be further detailed later in the chapter.

The bfloat16 (Brain Floating-Point) was developed by Google Brain, the company's artificial intelligence research group. Bfloat16 is a shortened version of the 32-bit IEEE 754 single-precision floating-point standard (binary32) designed to speed up machine learning and deep learning tasks. It uses the same 8 exponent bits as the 32-bit floating point standard, but it only supports an 8-bit precision instead of the 24-bit significand of the binary32 format [21]. Experiments conducted by Google have shown that it is feasible to shrink the mantissa as long as it can still represent tiny values closer to zero as part of the summation of minor differences during the training phase. The benefit of this change is the reduction of power consumption and implementation silicon area of the computation operator and memory storage [22]. Bfloat16 is used in Intel AI processors (Nervana NNP-L1000), Intel FPGAs, Google Cloud TPUs, and TensorFlow [21].

Inexact approximate arithmetic operators, such as adders and multipliers, have recently received a lot of attention as a way to enhance speed and energy efficiency with a minimal loss in accuracy for compute-intensive image and video processing and machine learning applications [23, 24, 25, 26]. Exploiting the error-tolerant characteristics of those applications, several approximation methodologies have been proposed for the implementation of inaccurate arithmetic units. Adder and multiplier being the fundamental operations of an arithmetic processor, they are crucial to obtain high performance.

Inexact adder has been explored extensively for approximation computation in order to reduce power consumption and latency [27, 28, 29, 30]. Liang et al. [31] have examined several approximate adders, using different metrics such as error distance (ED), mean error distance

<sup>1.</sup> or bit-width, word-length is also used as a synonym of precision in this thesis

(MED), and normalized error distance (NED), to evaluate approximate and probabilistic adders in approximation computing applications. Existing designs for an approximation multiplier can be divided into truncation and non-truncation methods. For the truncation-based design, the bottom portion of the partial products is eliminated, or the least significant partial products are approximated by a constant [32]. To improve the accuracy of truncated multipliers, many error compensation schemes have been developed [33, 34, 35, 36, 37]. A non-truncation technique assembles an approximate multiplier from approximate circuits [38, 39, 40, 41].