# Improvement of the HVDC converters for grid-connection of remote offshore wind parks: assessment of the potential of new IGCTs

Davin Guedon

# ► To cite this version:

Davin Guedon. Improvement of the HVDC converters for grid-connection of remote offshore wind parks : assessment of the potential of new IGCTs. Electric power. Institut National Polytechnique de Toulouse - INPT, 2022. English. NNT : 2022INPT0005 . tel-04190278

# HAL Id: tel-04190278 https://theses.hal.science/tel-04190278

Submitted on 29 Aug 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Toulouse

# THÈSE

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (Toulouse INP)

Discipline ou spécialité :

Génie Electrique

# Présentée et soutenue par :

M. DAVIN GUEDON le mercredi 2 février 2022

# Titre :

Amélioration des performances des convertisseurs HVDC mis en oeuvre pour le raccordement des parcs éoliens offshore lointains : évaluation du potentiel des nouveaux composants IGCT

# Ecole doctorale :

Génie Electrique, Electronique, Télécommunications (GEETS)

Unité de recherche : Laboratoire Plasma et Conversion d'Energie ( LAPLACE)

# Directeur(s) de Thèse :

M. PHILIPPE LADOUX

# Rapporteurs :

M. CYRIL BUTTAY, INSA LYON M. DRAZEN DUJIC, ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

# Membre(s) du jury :

M. SEDDIK BACHA, INP DE GRENOBLE, Président M. CHRISTIAN WINTER, ABB SEMICONDUCTORS LENZBURG, Invité(e) M. MEHDI KANOUN, EDF ECUELLES, Membre MME MARIE-LAURE LOCATELLI, TOULOUSE INP, Membre M. PHILIPPE LADOUX, TOULOUSE INP, Membre M. SÉBASTIEN CORNET, EDF ECUELLES, Invité(e) M. SÉBASTIEN SANCHEZ, TOULOUSE INP, Membre M. THOMAS STIASNY, ABB SEMICONDUCTORS LENZBURG, Membre

# Acknowledgements

J'ai démarré ma thèse en novembre 2018 au laboratoire LAPLACE, via le dispositif CIFRE, avec l'entreprise EDF. Je tiens à m'adresser aux personnes que j'ai côtoyées durant ma thèse, ponctuellement ou régulièrement, et qui m'ont apporté leur soutien technique et/ou humain.

Je souhaite premièrement remercier mon directeur de thèse, Monsieur Philippe Ladoux, Professeur des Universités à l'INP de Toulouse, de m'avoir accompagné tout au long de cette aventure. Son expérience, ses connaissances et son appétence pour le domaine ont très fortement contribué à la réussite de ma thèse. Je lui dois cette collaboration avec EDF R&D, qui tient ses origines d'une blague que je ne peux malheureusement pas retranscrire ici, et ABB Semiconductors. Je le remercie plus encore pour sa bonne humeur en toutes circonstances, ainsi que pour les expériences sportives et culinaires que nous avons partagées. Merci. Je remercie mon co-encadrant de thèse, Monsieur Sébastien Sanchez, enseignant-chercheur à l'ICAM de Toulouse. J'ai apprécié son engagement durant ces trois années, et l'intérêt immuable qu'il a porté à mes travaux. Sa présence à mes côtés dans les moment importants de la thèse, de Toulouse à Busan en passant par Moret-sur-Loing, a beaucoup compté.

Je tiens à remercier Monsieur Mehdi Kanoun, ingénieur-chercheur à EDF R&D, d'avoir encadré les premiers mois de ma thèse ainsi que mon stage de fin d'études. Il a su m'accompagner dans mes débuts à EDF, malgré la distance. Je le remercie également d'avoir intégré mon jury de thèse. Je veux remercier mon (deuxième) encadrant industriel Monsieur Sébastien Cornet, Chef de Projet Senior à EDF R&D. Ses corrections d'articles et de documents m'ont beaucoup apporté sur le plan technique et professionnel. Son expérience et ses connaissances "des labos" ont été décisives lors de la mise en exploitation du "Power Conversion Lab" (que nous n'avons pas pu appeler "POSEIDON" à mon grand regret). Je remercie Monsieur Thomas Stiasny et Monsieur Christian Winter, de Hitachi Energy, pour la richesse de la collaboration établie avec le laboratoire LAPLACE et EDF R&D. Merci à eux pour le matériel et les données qu'ils ont fournis, pour leur expertise sur l'IGCT, et plus largement pour leur implication dans le projet.

Je souhaite remercier les deux rapporteurs, Monsieur Cyril Buttay, Directeur de Recherche au laboratoire Ampère, et Monsieur Drazen Dujic, Professeur titulaire à l'Ecole Polytechnique Fédérale de Lausanne (EPFL), d'avoir accepté de réviser mon manuscrit de thèse. Je remercie également les membres du jury non cités ailleurs, à savoir Monsieur Seddik Bacha, Professeur des Universités au G2Elab, et Madame Marie-Laure Locatelli, Chargée de Recherche au laboratoire LAPLACE, d'avoir accepté d'évaluer mes travaux de thèse.

Je souhaite remercier Monsieur Jean-Marc Blaquière, ingénieur d'études au laboratoire LAPLACE, pour l'expertise qu'il a apporté à la conception du banc d'essais, pour le temps qu'il y a consacré ainsi que pour son implication globale dans le projet. Merci à Monsieur Didier Flumian, ingénieur au laboratoire LAPLACE, pour son aide précieuse lors des essais ! Je tiens à remercier de manière plus globale le groupe de recherche Convertisseurs Statiques (CS), auprès duquel j'ai appris et évolué.

Je tiens à remercier le bureau E410, entité immobilière du laboratoire LAPLACE, qui a abrité de chaleureux locataires : merci à Andrea Verdicchio de m'avoir initié au café napolitain, et à Kamil Mrozewski de m'avoir préféré à Andrea pour le bureau à côté de la fenêtre (c'est le meilleur). Je veux également remercier Mohsin et Thomas pour les moments que nous avons passés ensemble. Un grand merci au patriarche de ce bureau, Monsieur Joseph Fabre, ancien ingénieur-docteur à la SNCF (et "extérieur émérite" au laboratoire), désormais à la SCLE. J'ai apprécié nos innombrables échanges autour de la machine à café, et nos sorties au-delà du cadre professionnel. Je me dois ici de souligner l'aide précieuse qu'il m'a apportée tout au long de ma thèse. Merci. Je souhaite remercier le bureau de l'Association Des Laplaciens (ADeL) de 2019, à savoir Maxime Bafoil, Yazan, Timothé et Laura. Ils m'ont offert une belle expérience humaine dès ma première année de thèse, et plein de crédits pour l'école doctorale (merci encore Maxime). Je voudrais remercier les autres doctorants dont j'ai croisé le chemin, au laboratoire et ailleurs, en particulier Quentin, Lucille, Youssef, Pawel, Matthieu, Abdulrahman, Grégoire, Daouda, Lucas, Corentin.

Je veux de manière générale remercier l'ensemble du groupe M2A, du département Laboratoire des Matériels Electriques (LME) à EDF R&D, basé aux Renardières. De plus, merci à Monsieur Vincent Vernhes, Chef de Groupe à M2A, pour son professionnalisme et pour sa bienveillance. Je remercie Rafael Coelho-Medeiros, doctorant à M2A, pour ces trois années (et 3 mois) de thèse passées ensemble, malgré la distance. Je tiens à remercier "l'équipe montage" pour son travail, en amont de la mise en exploitation du laboratoire, au hall 400 kV. Je souhaite également remercier Bruno et Laurent pour leur accueil dès mes premiers jours aux Renardières, et pour leur gentillesse. Merci à Edouard de m'avoir fait assister à cet essai !

Enfin et surtout, je veux remercier ma famille pour tout ce qu'elle m'a apporté durant cette période. Merci à Andrea pour son soutien indéfectible, et pour ces trois années de thèse communes. Merci.

# Abstract

For more than a decade, high-voltage direct-current (HVDC) grid-connection of offshore wind farms has intensified. It allows transporting to the mainland power levels around 1 GW, over underwater distances exceeding 50 kilometres. A key issue related to the sizing of HVDC converter-stations, based on MMC (Modular Multilevel Converters), is their efficiency. Only 0.1% of power losses represents several GWh lost for each year of operation of the wind farm.

These power losses are related to the characteristics of the semiconductors used. Today, the IGBT (Insulated-Gate Bipolar Transistor) is the only semiconductor device used in this type of application. Historically, the IGBT has been developed for medium-power industrial applications, and does not appear as the best candidate to realize HVDC systems. On the other hand, the IGCT (Integrated Gate-Commutated Thyristor) has performances and features that seem better adapted, however no HVDC system has been implemented with IGCTs so far.

The aim of this PhD thesis is to optimize the performances of HVDC converters, based on IGCT, as part of the grid-connection of offshore wind farms. This work has been the subject of a collaboration between the LAPLACE Laboratory in Toulouse, Electricité de France Research & Development (EDF R&D), and the semiconductor manufacturer Hitachi ABB Power Grids, Semiconductors.

In a first approach, the static and dynamic characteristics of the IGCTs have been measured experimentally on a double-pulse test bench. Then, an electro-thermal model has been built, in order to determine precisely the power losses in the hundreds of sub-modules present in an MMC arm. This approach has allowed a comparison of different IGCTs, according to their power losses, taking into account the intermittent production of the offshore wind farm.

Following this study based on calculations and simulations, a test bench in steady-state, consisting of two IGCT-based sub-modules connected in a back-to-back configuration, has been designed and implemented to accurately measure on-state and switching losses through dedicated instrumentation. With a working voltage up to 5 kV and currents exceeding 2 kA, 4.5 kV and 10 kV devices have been tested under operating conditions equivalent to those of a 1 GW HVDC station.

The power loss measurements using the calorimetric method have confirmed the validity of the electro-thermal models related to IGCT and its clamp circuit, with an accuracy of about 10%. The waveforms have highlighted larger deviations regarding the switching losses, caused by the stray inductances of connection within the switching cell. The cross-use of electro-thermal models and experimental measurements demonstrates that 4.5 kV IGCTs can allow a significant rise in the power levels of the MMC-based HVDC stations, while 6.5 kV and 10 kV IGCTs are

the most suitable devices for prospective applications, guided by the voltage upgrade of HVDC cables. Soft switching circuits are promising to reduce the volume of the sub-modules, and would be particularly relevant for 6.5 kV and 10 kV devices, whose switching losses are the main limiting factor.

# Résumé de la thèse

Depuis plus d'une dizaine d'années, le raccordement à courant continu haute tension (HVDC) des parcs éoliens en mer s'intensifie. Cela permet de transporter vers le continent des niveaux de puissance avoisinant le GW, sur des distances sous-marines excédant la cinquantaine de kilomètres. Un enjeu clé lié au dimensionnement des stations de conversion HVDC, basées sur des MMC (convertisseurs modulaires multiniveaux), est leur rendement. Rien que 0.1% de pertes représente plusieurs GWh perdus pour chaque année d'exploitation du parc éolien.

Ces pertes sont liées aux caractéristiques des semi-conducteurs utilisés. Aujourd'hui, l'IGBT (transistor bipolaire à grille isolée) est le seul composant utilisé dans ce type d'application. Historiquement, l'IGBT a été développé pour des applications industrielles de moyenne puissance, et ne parait pas a priori bien placé pour réaliser des systèmes HVDC. A contrario, l'IGCT (thyristor intégré commuté par la gâchette) présente quant à lui des performances et des spécificités qui semblent mieux adaptées, néanmoins son usage dans de tels systèmes n'a jamais été considéré.

Le but de cette thèse est d'optimiser le rendement de convertisseurs HVDC à base d'IGCT, dans le cadre du raccordement des parcs éoliens en mer. Ce travail a fait l'objet d'une collaboration entre le Laboratoire LAPLACE à Toulouse, EDF R&D, et le fabricant de semi-conducteurs Hitachi ABB Power Grids, Semiconductors.

Dans un premier temps, les caractéristiques statiques et dynamiques des IGCT ont été relevées expérimentalement sur un banc d'essais impulsionnel. Un modèle électro-thermique a ensuite été élaboré, ceci afin de déterminer avec précision les pertes dans la centaine de sousmodules équipant un bras de MMC. Cette approche a permis de comparer différents IGCT suivant les niveaux de pertes, en prenant en compte l'intermittence de production du parc éolien en mer.

Suite à cette étude basée sur des calculs et des simulations, un banc d'essais en régime permanent, constitué de deux cellules à base d'IGCT mises en opposition, a été conçu et mis en oeuvre afin de mesurer avec précision les pertes en conduction et les pertes par commutation grâce à une instrumentation dédiée. Avec une tension de travail allant jusqu'à 5 kV et des courants dépassant 2 kA, des composants 4.5 kV et 10 kV ont pu été testés dans des conditions de fonctionnement équivalentes à celles d'une station HVDC d'une puissance de 1 GW.

Les mesures de pertes utilisant la méthode calorimétrique ont pu confirmer la validité des modèles électro-thermiques relatifs à IGCT et à son circuit d'aide à la commutation, avec une précision de l'ordre de 10%. Les relevés des formes d'onde ont mis en avant des écarts plus importants concernant les pertes par commutation, causés par les inductances parasites de

connexion au sein de la cellule de commutation. L'utilisation croisée des modèles de pertes et des mesures expérimentales démontre que les IGCT 4.5 kV peuvent permettre une montée en puissance notable des stations HVDC à base de MMC, tandis que les IGCT 6.5 kV et 10 kV sont les plus adaptés pour accompagner la montée en tension des câbles HVDC. Les circuits permettant la commutation douce des composants sont prometteurs afin de réduire le volume des sous-modules, et seraient particulièrement favorables aux composants 6.5 kV et 10 kV, dont les pertes par commutation constituent le principal facteur limitant.

# Résumé de la thèse en français

# Chapitre 1 : Raccordement des parcs éoliens en mer éloignés et composants semi-conducteurs de puissance

Le premier chapitre présente les technologies actuelles et futures du génie électrique, impliquées dans le raccordement des parcs éoliens en mer dits lointains. L'intérêt du transport en haute tension à courant continu (HVDC) est mis en avant, a contrario de la plupart des réseaux terrestres existants, basés sur la haute tension à courant alternatif (HVAC). La technologie HVDC, plus rentable dès lors que la liaison s'étend typiquement sur plus de 50 km, requiert en contrepartie des stations de conversion.

Pour les stations de conversion en question, les topologies du type "convertisseur source de tension" (VSC) sont mises en avant : elles apportent davantage de flexibilité que les traditionnels ponts à thyristors du point de vue du réseau. Le convertisseur modulaire multiniveaux (MMC), utilisé dans des projets industriels depuis plus d'une dizaine d'années, permet de réduire de manière notable l'encombrement du système, et de réduire dans l'ensemble le coût d'installation de la liaison HVDC. Les performances du MMC, incluant le rendement et la fiabilité, ainsi que les coûts d'investissement (CAPEX) et les coûts d'exploitation (OPEX), sont néanmoins très dépendantes des composants semi-conducteurs de puissance utilisés.

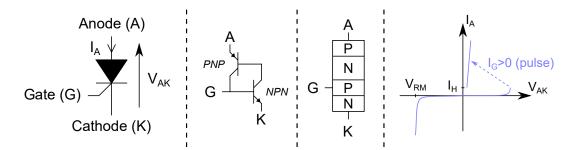

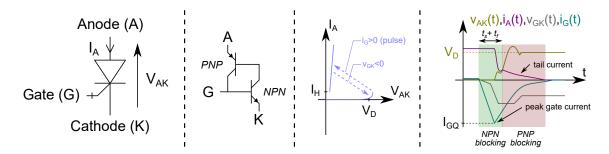

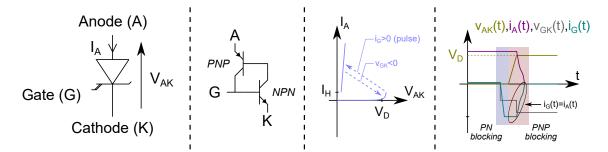

Une étude est donc dédiée à ces semi-conducteurs de puissance. Le composant historiquement utilisé, le thyristor, est introduit, ainsi que sa première déclinaison en composant potentiellement utilisable dans une topologie VSC (le thyristor à extinction par la gâchette, ou thyristor GTO). En parallèle, le développement du transistor bipolaire à grille isolée (IGBT) est présenté, ainsi que ses évolutions afin de répondre aux contraintes de la forte puissance. La genèse du thyristor intégré commuté par la gâchette (IGCT) découle du besoin d'un composant de forte puissance pour les topologies VSC. De ce fait, l'IGCT se veut très performant à basse fréquence de commutation, à fort courant, et peut travailler sous des tensions allant jusqu'à 10 kV.

L'IGCT présente également des propriétés attractives pour le HVDC, notamment sa fiabilité accrue ainsi que son mode de défaillance en court-circuit. Il existe aussi sous forme de composant à conduction inverse, ce qui permet potentiellement d'accroître la compacité de la cellule de commutation.

Le premier chapitre se termine par un bilan des projets de raccordement en HVDC des parcs éoliens, listant les topologies et les technologies utilisées. Cet inventaire montre la prédominance des solutions à base de MMC, avec l'IGBT. Dans le même temps, la montée en puissance attendue de ces liaisons dans les années à venir requiert des calibres en courant et en tension plus importants, que seuls les IGCT sont en mesure de fournir à l'heure actuelle.

# Chapitre 2 : Conception de la liaison haute tension à courant continu (HVDC)

Le deuxième chapitre se concentre sur la conception des stations de conversion HVDC, en intégrant les problématiques liées à la gestion des défauts à l'échelle du convertisseur et de la liaison HVDC. L'utilisation de l'IGCT, en remplacement de l'IGBT, permet d'alléger les sous-modules composant le MMC, grâce à une stratégie de protection alternative en cas de défaut côté DC. En remplacement du circuit d'aide à la commutation traditionnel, dissipant de la puissance, plusieurs autres circuits sont étudiés. Le circuit auxiliaire résonant à pôle commuté (ARCP) apparaît comme prometteur, il permet d'effectuer de la commutation douce avec un petit nombre de composants. Cela induit une réduction des pertes par commutation, ainsi qu'une diminution du volume des composants passifs.

Le dimensionnement des MMC au sein des stations de conversion HVDC constitue un enjeu important. En particulier, les composants passifs influent de manière significative sur le volume (condensateurs), mais également sur l'aire de fonctionnement du convertisseur, sur sa stabilité, ainsi que sur son comportement en cas de défaut (inductances de bras). Le nombre de sous-modules par bras dépend quant à lui du calibre en tension des semi-conducteurs utilisés, et de la tension de la liaison HVDC. La tension nominale des sous-modules,  $V_{SM}$ , est définie pour des IGCT 4.5 kV, 6.5 kV, et 10 kV, en prenant en considération l'influence du rayonnement cosmique ainsi que la température de jonction en fonctionnement.

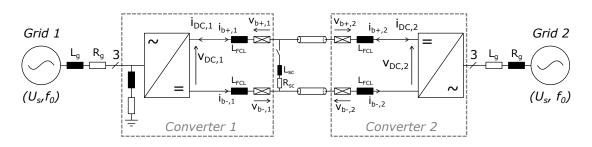

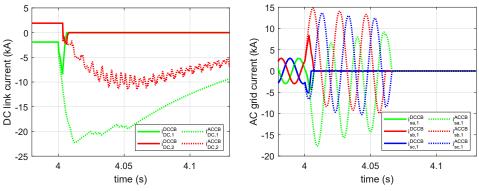

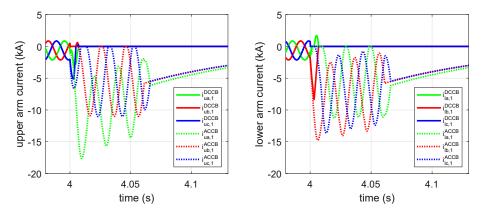

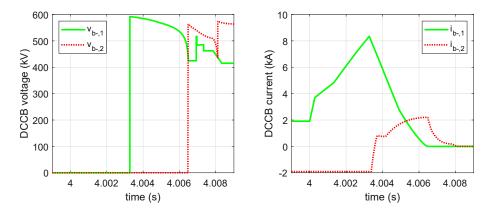

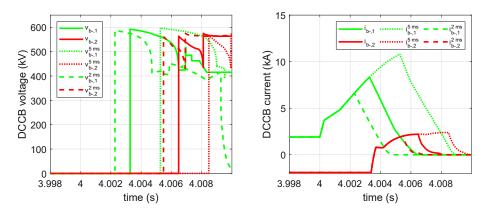

Afin de valider la cohérence des choix effectués, le cas d'un court-circuit franc entre pôles côté DC est simulé, à l'aide d'un modèle complet de la liaison HVDC sous PLECS. En plus des disjoncteurs AC classiquement utilisés, des disjoncteurs DC dits "hybrides" (parties mécanique et statique) sont considérés. Les simulations montrent que les disjoncteurs AC seuls, lents, induisent des courants de défaut pouvant détruire les modules de puissance IGBT traditionnels ainsi que les IGCT à conduction inverse, en l'absence de protections complémentaires au sein des sous-modules. Les IGCT asymétriques, couplés à des diodes discrètes, sont idéaux dans ce cas de figure, afin de simplifier le sous-module. Au contraire, les disjoncteurs DC possèdent une action rapide, de l'ordre de quelques millisecondes. Il en résulte des courants de défaut réduits, et la possibilité d'utiliser des IGCT à conduction inverse, ou des modules de puissance IGBT, avec un degré d'intégration plus important.

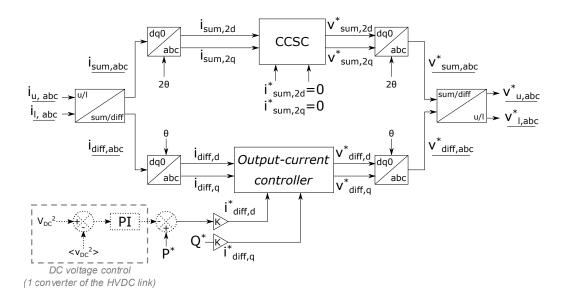

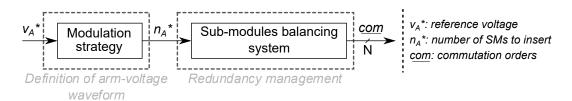

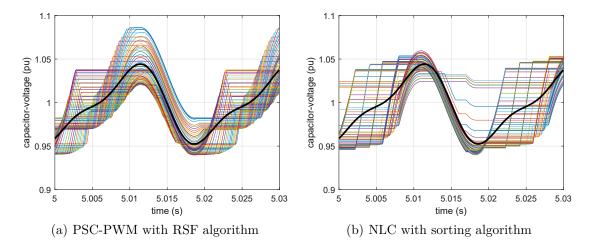

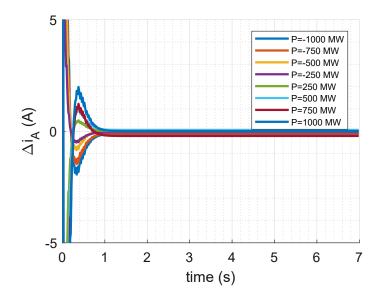

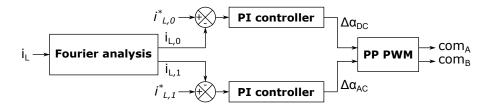

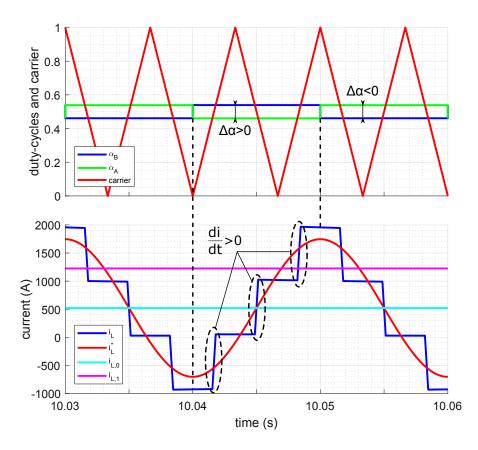

La dernière partie du chapitre se concentre sur la commande du MMC, en intégrant les contraintes liées au HVDC. Le nombre de niveaux important, combiné au besoin de réduire les pertes par commutation des composants semi-conducteurs, conduit à favoriser une commande dite NLC (Nearest-Level Control en anglais). A la NLC s'ajoute un algorithme de tri, chargé d'équilibrer les tensions des centaines de sous-modules de chaque bras, à chaque instant. Dans le cadre de la thèse, un nouvel algorithme de tri, faisant l'objet d'un dépôt de brevet à l'écriture de ces lignes, a été développé afin de faciliter une étude paramétrique. Il permet notamment d'ajuster automatiquement la fréquence de commutation lorsque les conditions de fonctionnement du convertisseur varient.

### Chapitre 3 : Modélisation électro-thermique du convertisseur modulaire multiniveaux (MMC) pour le transport haute tension à courant continu (HVDC)

Le troisième chapitre aborde, avec une approche déductive, la modélisation des stations de conversion HVDC, en vue d'évaluer les pertes des semi-conducteurs de puissance. Un des objectifs clés est de conserver un fort caractère paramétrique, en réduisant le temps de calcul autant que possible. La dépendance thermique, souvent négligée dans la littérature, est intégrée dans l'étude et fait l'objet de multiples discussions.

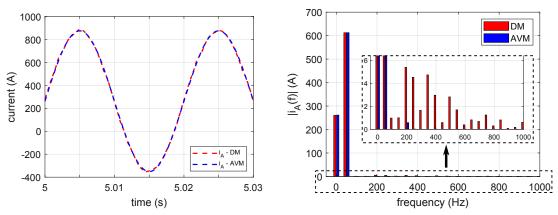

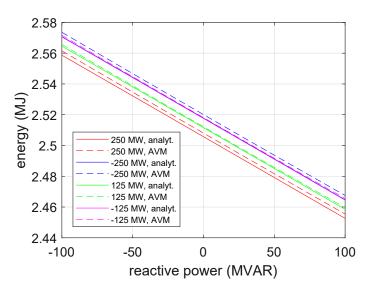

Le point de départ est le modèle complet, dit détaillé, du MMC : il intègre plusieurs milliers de composants discrets. Il est démontré qu'un modèle dit moyenné est plus pertinent pour évaluer les pertes en régime permanent, les formes d'ondes sont reproduites avec précision et le temps de calcul est réduit d'un facteur 40 000.

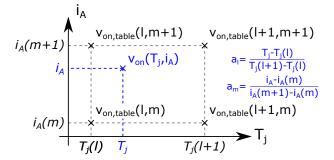

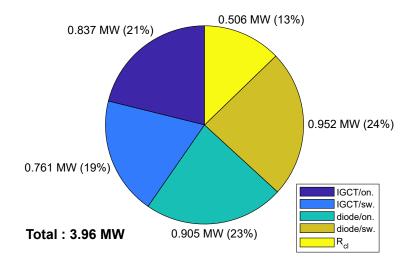

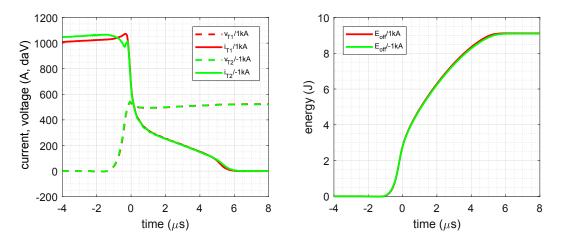

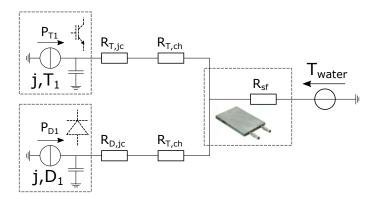

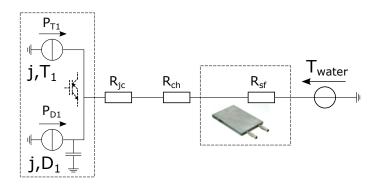

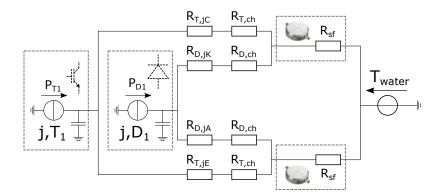

Afin de correctement représenter le couplage électro-thermique impliqué dans l'évaluation des pertes, une série de mesures sur banc d'essai impulsionnel a été effectuée. De multiples IGCT ont ainsi été caractérisés, par Hitachi ABB Power Grids, pour différents courants, tensions et températures de jonction. Ces caractérisations ont permis de constituer des tables de correspondances ("look-up tables" en anglais), facilement exploitables par des logiciels de simulation comme PLECS. Le concept de "bras extérieur" a été introduit : ce dernier est obligatoire afin d'évaluer les pertes, en complément du modèle moyenné. Pour finir, une nouvelle méthode d'évaluation des pertes dans le circuit d'aide à la commutation a été proposée. En se basant sur les formes d'ondes à la commutation, il est possible d'évaluer de manière théoriquement précise les pertes dans la résistance du circuit en question.

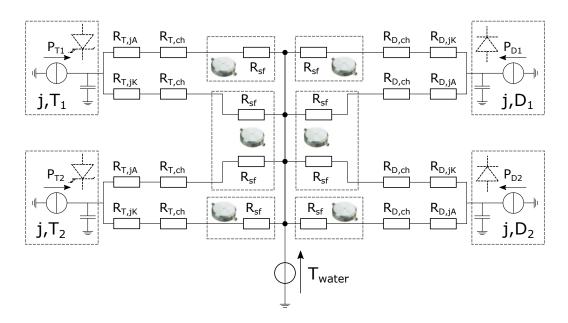

Le modèle conçu souffrait de lacunes sous PLECS, notamment en termes de temps de calcul et de représentation du circuit thermique. Les fonctions liées au modèle moyenné et au "bras extérieur" ont donc été analytiquement implémentées sous MATLAB, afin d'accélérer les calculs. L'outil de simulation développé comprend le chargement des tables de correspondances précédemment établies, permettant de calculer les pertes dans les semi-conducteurs et dans les circuits d'aide à la commutation. Cette transition de PLECS vers MATLAB a également permis d'intégrer un modèle thermique plus précis des IGCT à conduction inverse.

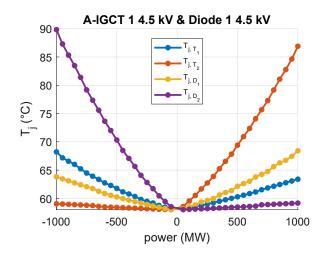

L'outil de simulation mène à l'obtention des résultats voulus 40 fois plus rapidement qu'avec le modèle précédent, soit 30 secondes en moyenne avec un ordinateur de bureau. Les températures de jonction de l'ensemble des semi-conducteurs du convertisseur en régime permanent sont calculées, pour tout point de fonctionnement accessible. Ces développements ouvrent la voie à une étude paramétrique, car l'ensemble des paramètres électriques définissant la liaison HVDC peuvent être modifiés. Dans le même temps, l'influence de grandeurs telles que la température de l'eau de refroidissement, ou le débit d'eau, peut être étudiée. Cette fonctionnalité permet de faire l'interface entre le dimensionnement électrique du convertisseur et le dimensionnement du système de refroidissement de la station de conversion HVDC.

### Chapitre 4 : Analyse des pertes dans les stations de conversion HVDC

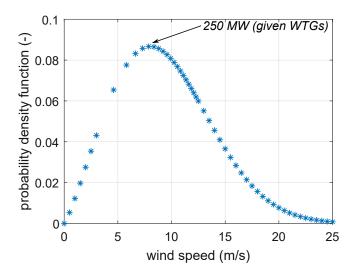

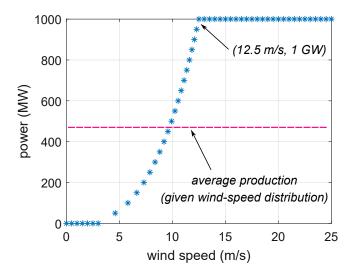

Le quatrième chapitre repose sur les modèles développés dans le troisième chapitre, et utilise les principes de dimensionnement des stations de conversion HVDC du deuxième chapitre. Il y est expliqué que la production d'énergie éolienne est intermittente, puisque la vitesse du vent varie suivant les conditions météorologiques. Cela induit un calcul des pertes non trivial, il est alors proposé de considérer l'ensemble des points de fonctionnement induits par les différentes vitesses de vent, en intégrant les propriétés des turbines éoliennes. Pour cela, une distribution statistique typique des vitesses de vent est considérée. Le calcul des pertes dites "moyennées" est présenté : il s'agit des pertes moyennes observées dans les stations de conversion HVDC, avec une durée de fonctionnement suffisamment longue pour qu'une approche statistique soit applicable.

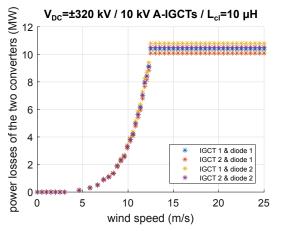

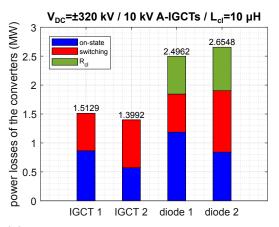

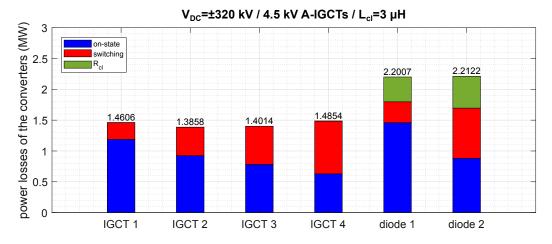

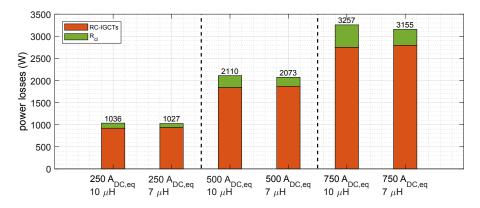

Une première étude comparative est menée entre les composants semi-conducteurs, à tension côté DC fixée à  $\pm 320$  kV. Cette étude montre que les contraintes thermiques sont croissantes avec l'augmentation du calibre en tension des IGCT. L'épaisseur de silicium requise augmente

avec le calibre en tension du composant, ce qui accroît à la fois les pertes en conduction et les pertes par commutation. Ainsi, la température de jonction des IGCT 10 kV dépasse la valeur admissible pour les points de fonctionnement critiques. Les IGCT à conduction inverse 4.5 kV et 6.5 kV s'avèrent quant à eux très performants, ils n'impliquent qu'une faible augmentation des pertes pour un gain significatif en termes de volume, et de coûts d'investissement (CAPEX), par rapport aux IGCT asymétriques 4.5 kV.

En complément de cette étude, une seconde étude comparative est menée à puissance constante et à nombre de sous-modules dans le convertisseur constant. Cela implique que la tension de la liaison HVDC augmente avec le calibre en tension des semi-conducteurs de puissance. Cette approche est pertinente, car elle permet d'envisager l'évolution des stations de conversion HVDC avec des câbles à isolation synthétique (XLPE) 525 kV et 600 kV, qui possèdent à l'heure actuelle des niveaux de maturité technologique (TRL) plus bas que les câbles XLPE 320 kV. Cette seconde étude comparative montre que les IGCT haute tension, c'est-à-dire avec des calibres en tension de 6.5 kV et 10 kV, permettent de réduire les pertes dans les stations de conversion HVDC jusqu'à 10%. Cela montre qu'il est possible de monter la tension de la liaison HVDC, et d'augmenter le rendement de l'installation, tout en évitant d'augmenter le nombre de sous-modules dans les stations de conversion. Cette conclusion est importante, car c'est actuellement un facteur contraignant lors de la conception des stations de conversion HVDC.

La seconde étude comparative met en exergue l'importance des pertes par commutation des IGCT haute tension, ainsi que la part croissante des pertes liées au circuit d'aide à la commutation. Elle fait donc écho à l'étude du deuxième chapitre, portant sur les circuits auxiliaires pour l'IGCT. L'ARCP, permettant de réduire les pertes par commutation des semi-conducteurs sans dissiper d'énergie, présente alors un potentiel accru aux yeux des résultats du quatrième chapitre.

# Chapitre 5 : Réalisation et test de sous-modules à base de thyristors intégrés commutés par la gâchette (IGCT)

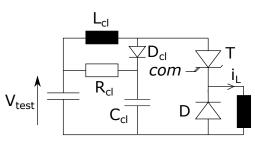

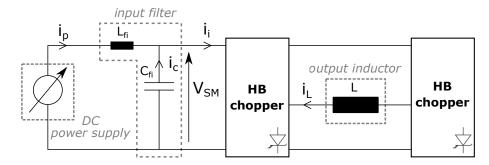

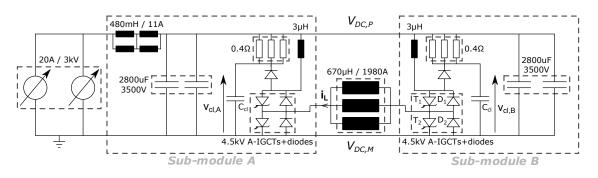

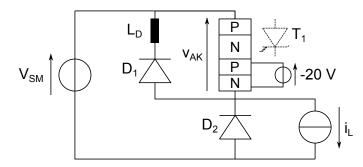

Le but du cinquième chapitre est d'obvier à l'absence de validation expérimentale concernant les résultats du quatrième chapitre. Bien que basés sur des caractérisations expérimentales, les modèles multi-physiques du troisième chapitre reposent sur des hypothèses qui n'ont, jusqu'à ce stade, pas été vérifiées. Reproduire les conditions de fonctionnement des semi-conducteurs de puissance dans un convertisseur 1 GW est a priori complexe et onéreux, à l'échelle d'un laboratoire. Pour pallier cette difficulté, une topologie utilisant le principe de mise en opposition a été considérée : deux sous-modules identiques sont raccordés sur le même bus DC. Une inductance, connectée aux sorties des sous-modules, permet d'assurer une circulation de l'énergie au sein des deux cellules de commutation. De ce fait, une alimentation DC ne fournissant que les pertes du montage est suffisante, ce qui correspond à seulement quelques dizaines de kilowatts.

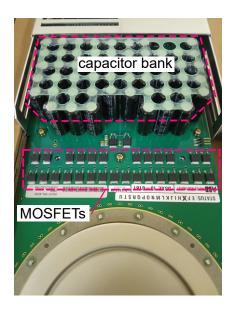

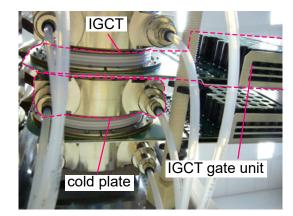

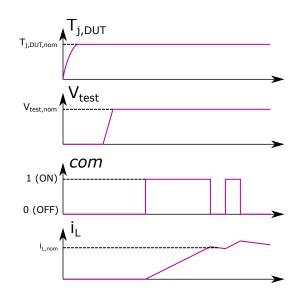

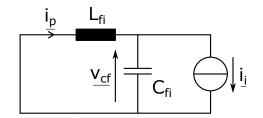

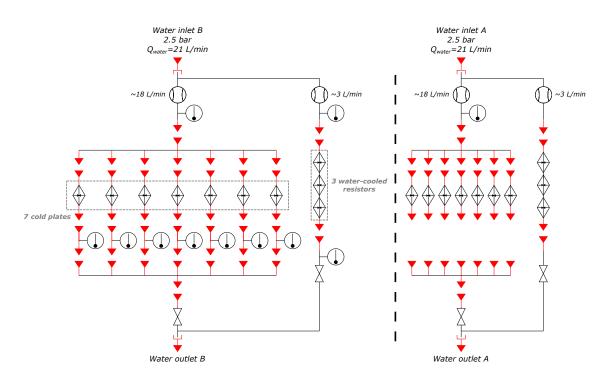

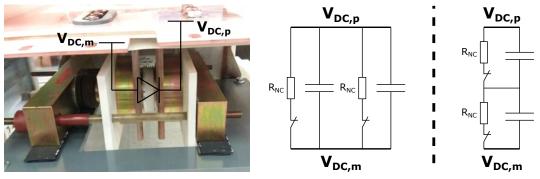

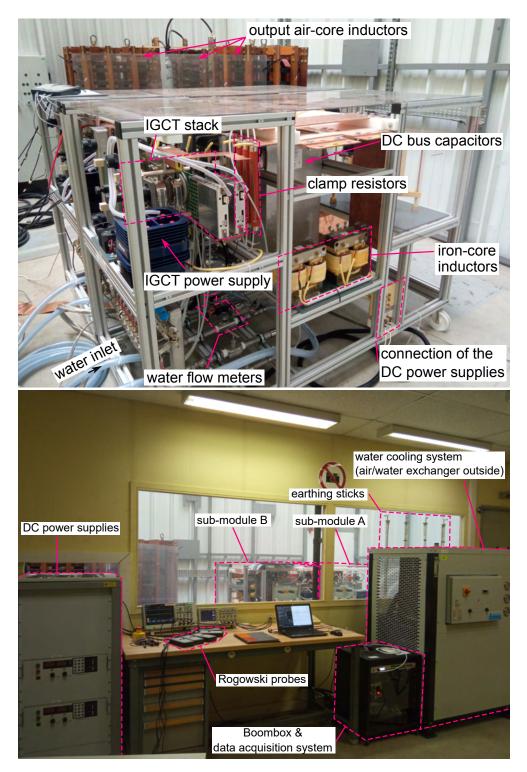

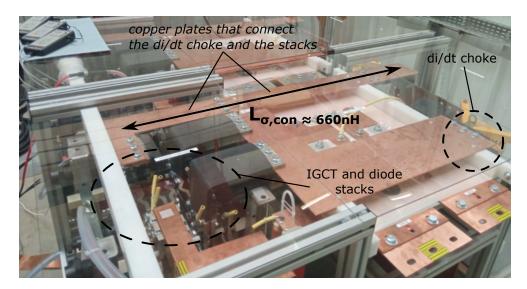

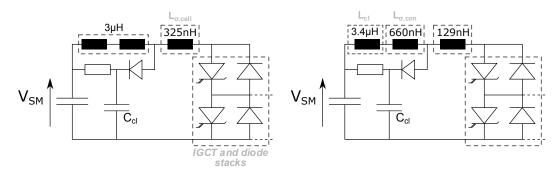

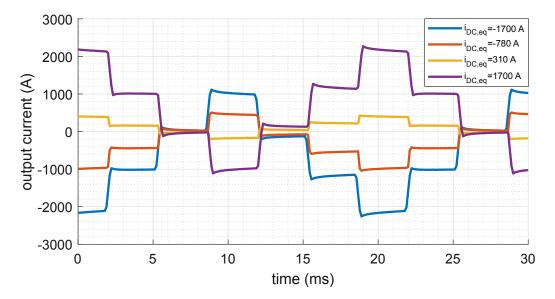

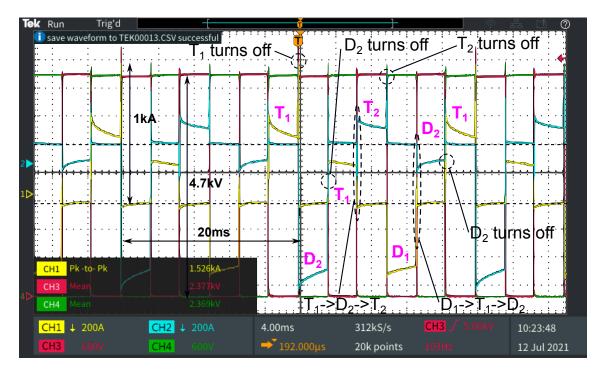

Le banc d'essais a été conçu pour tester des composants semi-conducteurs de puissance allant de 4.5 kV à 10 kV, c'est-à-dire que la tension maximale nécessaire sur le bus DC est de 5 kV. Par équivalence avec le dimensionnement du deuxième chapitre, des courants maximum supérieurs à 2 kA sont attendus en sortie, pour des valeurs efficaces allant jusqu'à 1200 A. Le système de refroidissement, à eau désionisée, est instrumenté afin de mettre en oeuvre une méthode calorimétrique, permettant de déterminer la puissance évacuée par chaque plaque à eau du montage. Des sondes de tension et de courant spécifiques ont été prévues afin d'observer les commutations des IGCT et des diodes, puis de calculer les pertes associées. Les cellules de commutation sont contrôlées par une "Boombox", ce système permet d'implémenter les lois de commande du banc d'essais grâce à une interface MATLAB/SIMULINK, et de facilement analyser les signaux d'entrée/sortie.

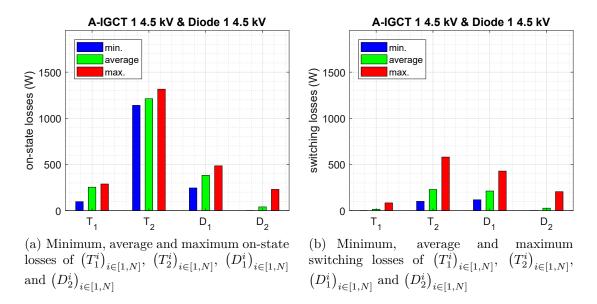

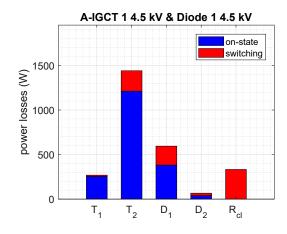

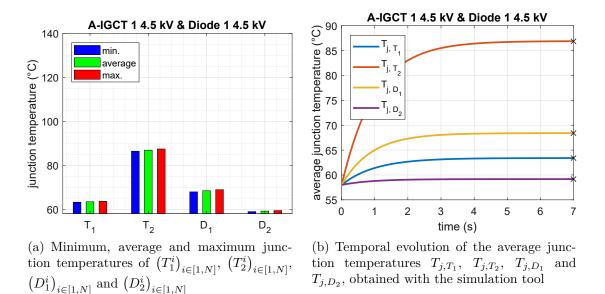

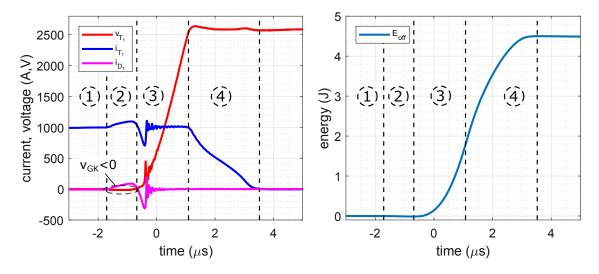

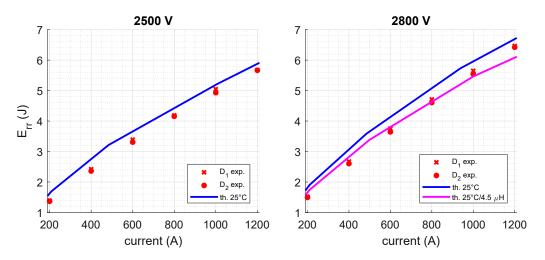

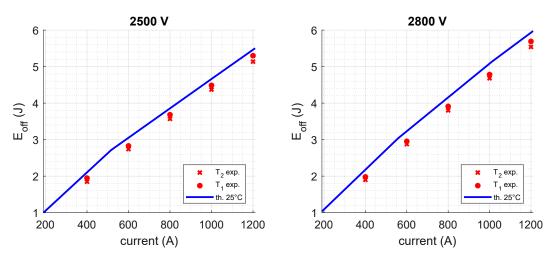

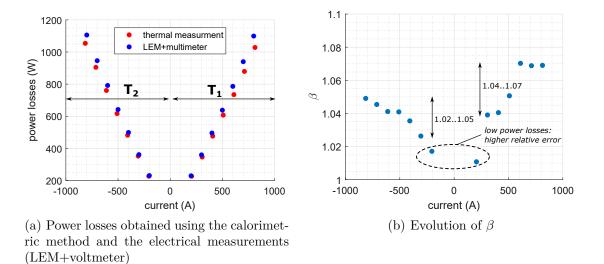

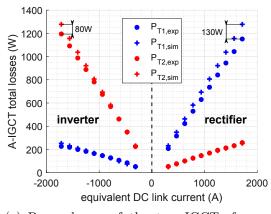

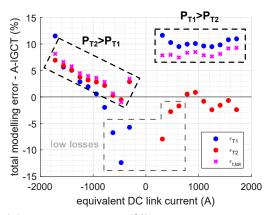

Dans un premier temps, ce sont des composants asymétriques 4.5 kV qui ont été testés. Les résultats expérimentaux ont été comparés aux modèles théoriques, pour un courant de sortie continu, afin de permettre la séparation des pertes en conduction et des pertes par commutation. Il a été observé que les pertes en commutation sont plus faibles que prévu. Cet écart, d'environ 25% pour les diodes et d'environ 15% pour les IGCT, s'explique par les inductances parasites du montage, qui diffèrent du montage où les premiers relevés ont été effectués. L'estimation des pertes en conduction est des pertes dans le circuit d'aide à la commutation s'est révélée précise, avec une erreur relative de l'ordre de 10%. D'après les simulations, pour une température ambiante de 25°C, la température de jonction des semi-conducteurs testés n'a pas dépassé 70°C. Cela démontre que les composants asymétriques 4.5 kV choisis sont des solutions viables, mais également qu'ils sont sollicités bien en-dessous de leur capacité maximale en courant.

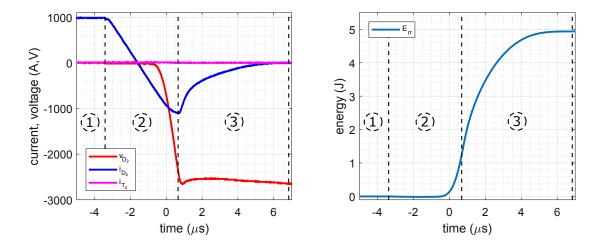

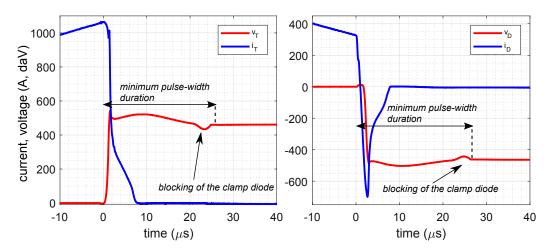

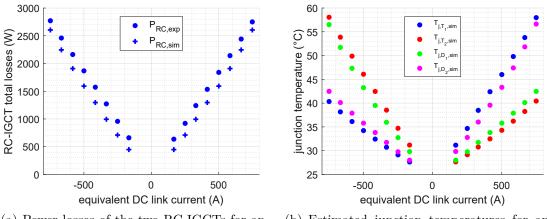

La seconde série d'essais a porté sur des IGCT à conduction inverse (RC-IGCT) 10 kV. Ces RC-IGCT peuvent opérer à une tension nominale de 4700 V; une fréquence de commutation maximale de 150 Hz a été fixée afin de limiter l'influence des pertes par commutation. Le fonctionnement de ces interrupteurs a été testé pour des courants maximum dépassant 1 kA, et des courants efficaces dépassant 500 A, où la forme d'onde d'un courant de bras de MMC a été reproduite aussi fidèlement que possible. La dynamique lors des commutations s'est révélée suffisante pour que ces IGCT soient utilisés dans les stations de conversion étudiées dans le deuxième chapitre. Les modèles électro-thermiques de pertes se sont avérés aussi précis que pour les composants 4.5 kV, démontrant ainsi leur validité pour une large gamme de paramètres. L'étude de la répartition des pertes montre que la réduction de l'inductance de limitation de di/dt, L<sub>cl</sub>, permet de réduire les pertes totales du sous-module. Des circuits permettant la commutation douce seraient donc particulièrement avantageux pour les RC-IGCT 10 kV : ils offriraient une réduction conséquente des pertes pour un volume similaire, voire moins important.

#### Conclusion et perspectives

Cette thèse de doctorat a montré, en se concentrant sur les stations de conversion HVDC et sur les semi-conducteurs de puissance qu'elles contiennent, que des solutions technologiques efficaces et prometteuses existent pour raccorder les parcs éoliens en mer lointains au réseau terrestre. L'IGCT anticipe la tendance actuelle, où les puissances transmises et les tensions de raccordement augmentent, tout en offrant un niveau de pertes réduit. Ces caractéristiques favorisent la réduction progressive du coût moyen de l'énergie (LCOE en anglais) éolienne en mer, ce qui est primordial pour accroître la production d'électricité à base d'énergies renouvelables.

Un état de l'art a été présenté, afin de comprendre les principales thématiques gravitant autour du raccordement des parcs éoliens en mer lointains. Parmi les convertisseurs statiques pour le HVDC, la technologie VSC est apparue comme une solution pertinente. En particulier, le MMC offre de nombreuses caractéristiques pour faciliter le développement des liaisons HVDC dans les zones éloignées ou isolées. L'IGCT présente des performances et des propriétés intéressantes dans le domaine du HVDC : avec des tensions allant jusqu'à 10 kV et des diamètres de wafer entre 4 et 6 pouces, il dépasse les capacités en courant et en tension de l'IGBT.

La conception de la liaison HVDC a été traitée, incluant les deux stations de conversion et les sous-modules qu'elles contiennent. Avec l'IGCT, la stratégie de protection d'un sous-module peut être simplifiée, notamment grâce à son mode de défaillance naturel en court-circuit et à son inductance de limitation de di/dt. L'ARCP, qui vise à remplacer le snubber RCD, est un circuit de commutation douce prometteur avec un volume réduit et une faible complexité. En ce qui concerne la commande du MMC, la NLC est plus appropriée que la MLI (modulation de la largeur d'impulsion) en raison de la largeur d'impulsion minimale qu'elle garantit pour tous les sous-modules. En outre, elle offre davantage de flexibilité pour adapter dynamiquement la fréquence de commutation, et la possibilité de réduire les pertes par commutation grâce à des algorithmes de tri dédiés.

En tenant compte des grandeurs électriques et des propriétés du circuit de refroidissement, un modèle de pertes des composants semi-conducteurs a été proposé. Les étapes successives de simplification du modèle du MMC ont été présentées, orientées vers une réduction du temps de calcul. Une nouvelle approche pour estimer les pertes du snubber RCD a été introduite. Les différents modèles ont été rassemblés dans un outil de simulation unique, mis en oeuvre avec MATLAB. L'outil est capable de fournir toutes les variables de l'espace d'état du convertisseur, y compris les pertes et les températures de jonction de tous les semi-conducteurs, en 30 secondes depuis un ordinateur de bureau.

Une analyse des pertes dans les stations de conversion HVDC a été réalisée, en tenant compte de la production d'énergie intermittente des parcs éoliens en mer. Les IGCT asymétriques 4.5 kV ont montré des pertes et des contraintes thermiques réduites. Les RC-IGCT se sont révélés être un compromis intéressant en termes de rendement, de volume et de coût. Les IGCT 6.5 kV et 10 kV présentent un avantage certain, car ils permettent de réduire le nombre de sous-modules dans les stations de conversion, même si leur potentiel est limité par les pertes par commutation et les pertes du snubber RCD.

Pour finir, une validation expérimentale des modèles électro-thermiques de pertes a été considérée. La tenue en courant des IGCT 4.5 kV, importante, a été confirmée, pour une large plage de fonctionnement, propre aux stations de conversion HVDC. Les pertes ont été mesurées à l'aide de différents instruments et de différentes méthodes. En outre, des protocoles d'étalonnage ont été réalisés pour garantir la précision des résultats. Les erreurs de modélisation concernant les pertes par commutation ont été évaluées, les principaux facteurs les influençant ont été identifiés pour l'IGCT et pour la diode. La précision des modèles de pertes a été validée pour différentes tensions, courants, fréquences de commutation, et une température de jonction variable, en régime permanent. Les RC-IGCTs 10 kV ont dévoilé d'importantes pertes, mais une aire de fonctionnement suffisante pour travailler sous une tension nominale de 4700 V, une fréquence de commutation de 150 Hz, et des courants supérieurs à 500  $A_{\rm rms}/1$  000  $A_{\rm peak}$ .

Plusieurs axes de recherche ont été mis en lumière pour améliorer les performances des sousmodules de MMC. En ce qui concerne le rendement et le volume, la réduction de l'inductance limitant le di/dt est bénéfique : les diodes supportant un di/dt élevé, c'est-à-dire supérieur à 5 kA/ $\mu$ s, sont pertinentes avec l'IGCT. De telles diodes existent déjà en tant que composants discrets, mais leur intégration dans un RC-IGCT contribuerait encore plus à améliorer la compacité du sous-module.

En ce qui concerne les IGCT dits "haute tension", les pertes par commutation et les pertes du snubber RCD contribuent de manière significative aux pertes totales. De plus, l'ARCP étudié est apparu comme une alternative potentielle au snubber RCD traditionnel. Pour un volume et une fiabilité similaires, les pertes par commutation peuvent donc être considérablement réduites, et les pertes du circuit d'aide à la commutation n'existeraient plus avec l'ARCP. Par conséquent, il serait intéressant de tester l'ARCP avec des IGCT 6.5 kV et 10 kV, afin de comparer les deux solutions techniques, et de conclure quant au potentiel des circuits de commutation douce avec des IGCT haute tension.

Les contraintes de volume n'ont pas été prises en compte, puisque les sous-modules assem-

blés ont été spécialement conçus pour la mesure de pertes et les tests en laboratoire, avec la possibilité d'être reconfigurés. La conception d'un sous-module à base d'IGCT, orientée vers des applications industrielles, pourrait dévoiler des avantages supplémentaires par rapport à l'IGBT.

# List of specific acronyms

| A-IGCT        | Asymmetric IGCT                            |

|---------------|--------------------------------------------|

| AAC           | Alternate Arm Converter                    |

| ACCB          | AC Circuit-Breaker                         |

| ARCP          | Auxiliary Resonant Commutated Pole         |

| AVM           | Averaged Model                             |

| CCSC          | Circulating Current Suppression Controller |

| DCCB          | DC Circuit-Breaker                         |

| DM            | Detailed Model                             |

| FIT           | Failure In Time                            |

| HB            | Half-Bridge                                |

| ICCT          | Internal Current Commutation Time          |

| IEGT          | Injection-Enhanced Gate Transistor         |

| IGBT          | Insulated-Gate Bipolar Transistor          |

| IGCT          | Integrated Gate-Commutated Thyristor       |

| LCC           | Line-Commutated Converter                  |

| LCOE          | Levelized Cost Of Energy                   |

| MMC           | Modular Multilevel Converter               |

| MTBF          | Mean Time Between Failures                 |

| MTTF          | Mean Time To Failure                       |

| NLC           | Nearest-Level Control                      |

| PPI           | Press-Pack IGBT                            |

| PSC-PWM       | Phase-Shifted Carrier PWM                  |

| RC-IGCT       | Reverse-Conducting IGCT                    |

| SiC           | Silicon Carbide                            |

| SCFM          | Short-Circuit Failure Mode                 |

| $\mathbf{SM}$ | Sub-Module (elementary brick of a MMC)     |

| SOA           | Safe Operating Area                        |

| TIV           | Transient Interruption Voltage             |

| TSO           | Transmission System Operator               |

| WTG           | Wind Turbine Generator                     |

| XLPE          | Cross-Linked Polyethylene Extruded         |

# Table of contents

$\mathbf{21}$

# General introduction

| 1        | Gri                     | d-conn | ection of wind parks and semiconductors                              | <b>23</b> |

|----------|-------------------------|--------|----------------------------------------------------------------------|-----------|

|          | 1.1                     | HVDO   | C systems for grid-connection of offshore wind parks                 | 23        |

|          |                         | 1.1.1  | Advantages of HVDC over HVAC for cable power transmission            | 23        |

|          |                         | 1.1.2  | HVDC configurations for grid connection of offshore wind parks       | 25        |

|          |                         | 1.1.3  | Grid codes for offshore wind parks                                   | 27        |

|          | 1.2                     | Power  | converters for HVDC power transmission                               | 28        |

|          |                         | 1.2.1  | Line-Commutated Converter (LCC)                                      | 28        |

|          |                         | 1.2.2  | Two-level Voltage-Source Inverter                                    | 28        |

|          |                         | 1.2.3  | Modular Multilevel Converter (MMC)                                   | 29        |

|          |                         | 1.2.4  | Alternate Arm Converter (AAC)                                        | 31        |

|          | 1.3                     | Semic  | onductor devices for HVDC power transmission                         | 32        |

|          |                         | 1.3.1  | Overview of the semiconductor devices for HVDC power transmission    | 32        |

|          |                         | 1.3.2  | Other relevant turn-off devices for present and futures applications | 38        |

|          |                         | 1.3.3  | Integrated Gate-Commutated Thyristor (IGCT)                          | 38        |

|          | 1.4                     | Existi | ng HVDC systems connecting offshore wind-farms                       | 44        |

|          |                         | 1.4.1  | Overview of the existing projects                                    | 44        |

|          |                         | 1.4.2  | Incoming HVDC projects in Europe                                     | 44        |

|          | 1.5                     | Future | e trends and conclusions                                             | 45        |

| <b>2</b> | Design of the HVDC link |        |                                                                      | 47        |

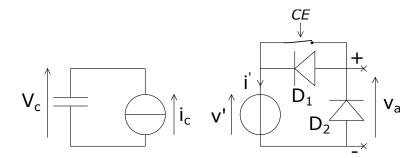

|          | 2.1                     | Desigr | n of the IGCT-based sub-modules                                      | 47        |

|          |                         | 2.1.1  | Selection of the topology                                            | 47        |

|          |                         | 2.1.2  | Sub-module failure, protection and redundancies                      | 48        |

|          |                         | 2.1.3  | Auxiliary circuits for IGCT                                          | 49        |

|          | 2.2                     | Desigr | 1 of the converters                                                  | 55        |

|          |                         | 2.2.1  | Selection of the passive components in an HVDC-MMC                   | 55        |

|          |                         | 2.2.2  | Choice of the number of sub-modules per arm                          | 57        |

|          | 2.3                     | Behav  | iour of the HVDC link during faulty operation                        | 59        |

|          |                         | 2.3.1  | Circuit-breakers and HVDC cables                                     | 59        |

|          |                         | 2.3.2  | Comparison between ACCBs and DCCBs in case of DC fault               | 62        |

|          |                         | 2.3.3  | Influence of the DCCB's Internal Current Commutation Time (ICCT)     | 65        |

|          | 2.4                     | Contro | ol of the converters                                                 | 67        |

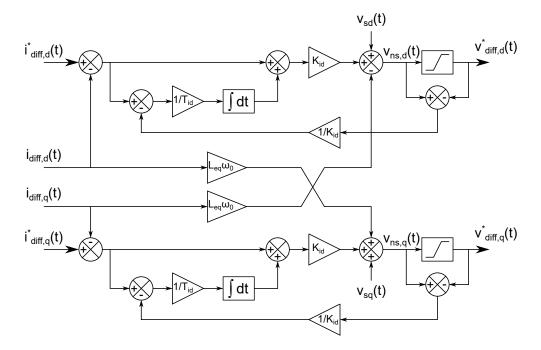

|          |                         | 2.4.1  | Inner control loops                                                  | 67        |

|          |                         | 2.4.2  | Multilevel modulation strategy                                       | 69        |

|          | 2.5                     | Conch  | usion                                                                | 72        |

| 3 | Elec | ctro-thermal modelling of the HVDC-MMC                                                    | <b>73</b> |

|---|------|-------------------------------------------------------------------------------------------|-----------|

|   | 3.1  | Electrical model of the MMC                                                               | 73        |

|   |      | 3.1.1 Detailed model (DM)                                                                 | 73        |

|   |      | 3.1.2 Averaged model (AVM)                                                                | 75        |

|   |      | 3.1.3 Comparison between the DM and the AVM                                               | 76        |

|   | 3.2  | Electro-thermal model of the sub-modules                                                  | 78        |

|   |      | 3.2.1 Measurement of the semiconductors' characteristics                                  | 78        |

|   |      | 3.2.2 Electro-thermal models for the semiconductors                                       | 80        |

|   |      | 3.2.3 External arm for power-loss calculation                                             | 83        |

|   |      | 3.2.4 Clamp circuit and di/dt snubber                                                     | 84        |

|   | 3.3  | Implementation of the model with MATLAB                                                   | 88        |

|   |      | 3.3.1 Motivations                                                                         | 88        |

|   |      | 3.3.2 Simplification of the AVM with analytic expressions                                 | 88        |

|   |      | 3.3.3 Structure of the simulation tool                                                    | 88        |

|   |      | 3.3.4 Performances and validation of the simulation tool                                  | 90        |

|   |      | 3.3.5 Conclusions regarding the simulation tool implemented with MATLAB .                 | 94        |

|   | 3.4  | Conclusion                                                                                | 94        |

|   |      |                                                                                           |           |

| 4 |      | ver-loss analysis in the HVDC converter-stations                                          | 97        |

|   | 4.1  | Modelling of the offshore wind park                                                       | 97        |

|   |      | 4.1.1 Problematic, approach                                                               | 97        |

|   |      | 4.1.2 Statistical distribution of the wind-speeds                                         | 97        |

|   |      | 4.1.3 Wind turbine power curve                                                            | 98        |

|   |      | 4.1.4 Calculation of the averaged power losses                                            | 98        |

|   |      | 4.1.5 Parameters of the converter-stations                                                | 99        |

|   | 4.2  | Power losses of the HVDC stations, $V_{DC}$ fixed                                         |           |

|   |      | 4.2.1 10 kV IGCTs                                                                         |           |

|   |      | 4.2.2 4.5 kV IGCTs                                                                        |           |

|   |      | 4.2.3 6.5 kV RC-IGCT                                                                      |           |

|   | 4.0  | 4.2.4 Summary for constant voltage, $V_{DC} = \pm 320 \text{ kV}$                         |           |

|   | 4.3  | Power losses of the HVDC stations, N=256 sub-modules fixed                                |           |

|   |      | 4.3.1 6.5 kV RC-IGCT                                                                      |           |

|   |      | 4.3.2 10 kV IGCTs                                                                         |           |

|   |      | 4.3.3 Summary for constant number of SMs, $N = 256$                                       |           |

|   | 4.4  | Comparison with other semiconductors, $V_{DC}$ fixed $\ldots \ldots \ldots \ldots \ldots$ |           |

|   |      | 4.4.1 Context and limits                                                                  |           |

|   |      | 4.4.2 Results                                                                             |           |

|   |      | 4.4.3 Conclusions                                                                         |           |

|   | 4.5  | Conclusion of the power-loss analysis                                                     | 111       |

| 5 | Rea  | lization and testing of IGCT-based sub-modules                                            | 113       |

| 0 | 5.1  | Design of the test bench                                                                  |           |

|   | 0.1  | 5.1.1 Constraints, topology and electrical ratings                                        |           |

|   |      | 5.1.2 Measurements                                                                        |           |

|   |      | 5.1.3 Control and protections                                                             |           |

|   |      | 5.1.4 Overview of the test bench                                                          |           |

|   | 5.2  | Power-loss analysis with the 4.5 kV A-IGCTs                                               |           |

|   | 0.4  | 5.2.1 DC output current                                                                   |           |

|   |      | 5.2.1 DC output current                                                                   |           |

|   |      | 5.2.3 MMC-like output current                                                             |           |

|   | 5.3  | Power-loss analysis with the 10 kV RC-IGCTs                                               |           |

|   | 0.0  | 5.3.1 DC output current                                                                   |           |

|   |      | out Do supur varione                                                                      | 100       |

|                                       | F 4            | 5.3.2 MMC-like output current                 |     |  |  |  |  |  |

|---------------------------------------|----------------|-----------------------------------------------|-----|--|--|--|--|--|

|                                       | 5.4            | Conclusion of the experiments                 | 140 |  |  |  |  |  |

| Conclusion and outlook                |                |                                               |     |  |  |  |  |  |

| Bi                                    | Bibliography 1 |                                               |     |  |  |  |  |  |

| $\mathbf{A}$                          | Ana            | lytic expressions of the electrical waveforms | 161 |  |  |  |  |  |

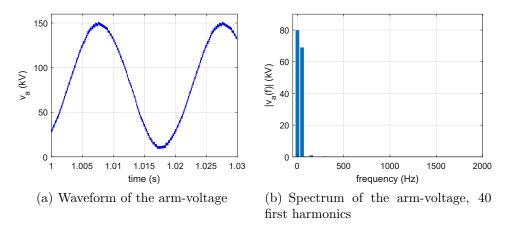

|                                       | A.1            | Arm-voltage $v_u(t)$                          | 161 |  |  |  |  |  |

|                                       |                | DC link current $I_{DC}$                      |     |  |  |  |  |  |

|                                       | A.3            | Arm-energy $E_{cu}(t)$                        | 162 |  |  |  |  |  |

|                                       |                | Average sum capacitor-voltage $v_{cu0}$       |     |  |  |  |  |  |

|                                       | A.5            | Reference arm-voltage $v_{u}^{*}(t)$          | 164 |  |  |  |  |  |

| B Thermal model of PPI, BIGT and IEGT |                |                                               |     |  |  |  |  |  |

|                                       | B.1            | Press-pack IGBT                               | 165 |  |  |  |  |  |

|                                       | B.2            | Bi-mode IGBT                                  | 165 |  |  |  |  |  |

|                                       | B.3            | Injection-enhanced gate transistor            | 166 |  |  |  |  |  |

| $\mathbf{C}$                          | Inst           | ruments, sensors and probes of the test bench | 167 |  |  |  |  |  |

# **General introduction**

Climate imbalance has been a major concern for the last decades, due to human activity and more specifically to the emission of greenhouse gases. Among them, electricity production is regularly pointed out as one of the main sources of carbon dioxide emissions, 31% over the last three decades in the case of the USA, according to the Environmental Protection Agency (EPA). Politically, a step forward has been made to banish fossil fuels from electricity production as much as possible: the European Union plans to install a capacity of 60 GW offshore wind by 2030 [1], whereas the USA targets 110 GW by 2050 [2].

Offshore wind power is especially interesting for many reasons, first of all offshore areas benefit from more important wind-speeds than onshore areas [3][4]. Moreover, it is estimated that the effective available offshore area in Europe could provide about 78% of the total electricity demand in 2030 [5], thanks to wind power. This huge potential of production could drive the energy transition at the scale of a continent.

The distance of a wind-farm to the shore is a key factor: remote offshore areas are larger and they are supposed to provide higher wind-speeds, thus enhancing energy production. Furthermore, the visual impact, often source of critics for wind parks installed close to the shore, could be avoided. In practice, the distance to the shore is limited by the water depth: 60 m is the current maximum, due to the wind turbine foundations [6]. In the meantime, floating wind turbines are emerging, promising the removal of the water depth barrier [7].

The massive offshore energy production, typically up to 1 GW, requires high-voltage direct current (HVDC) transmission to reduce costs; this technology relies on power converters and semiconductor devices. The main concern regarding the whole system is the Levelized Cost Of Energy (LCOE), i.e. the cost of the electricity effectively produced, and averaged over the total duration of operation, as expressed in (1):

$$LCOE = \frac{\text{OPEX+CAPEX}}{\text{raw energy production - energy loss}}$$

(1)

In Europe, LCOE tends to decrease with the rising maturity of the projects, and their associated technologies [8]. The denominator shows that energy loss is a factor which contributes to increase LCOE. Consequently, the efficiency of the conversion system is a critical issue: even with a typical efficiency of 99% per converter-station, the remaining 1% of power losses represent 175 GWh of energy loss per year for the two converter-stations, i.e 8.7 M $\in$  per year for an average electricity price of 50 $\in$ /MWh.

Nowadays, converter-stations are based on modular multilevel converters (MMCs), using thousands of insulated-gate bipolar transistors (IGBT) due to the large number of levels. Then, IGBT's characteristics are of paramount importance to ensure system's availability, reliability and minimum power losses. Historically, IGBT was a medium power device: it has been introduced in the field of HVDC at the end of the 1990s. A new device was emerging during the same period, the integrated gate-commutated thyristor (IGCT). IGCT, an evolution of the Gate Turn-Off thyristor (GTO), benefits from the advantages of thyristor and the turn-off capability of IGBT, with potential benefits in terms of voltage and current ratings, reliability and cost compared to IGBT. For this reason, the use of this device for MMC-HVDC applications is seriously considered.

This PhD thesis has been carried out at the Laboratoire Plasma et Conversion d'énergie (LAPLACE Laboratory) in the Power Converter research group, Toulouse, and at Electricité de France Recherche et Développement (EDF R&D), Les Renardières. A partnership has been made from the beginning of the thesis with Hitachi ABB Power Grids, Semiconductors, to study the applications of IGCT in the field of high-voltage power transmission.

The estimation of the semiconductor power losses is necessary to carry out a relevant study on IGCT in MMC-HVDC applications. Nevertheless, the implementation of fast and accurate simulation models is complex due to the large number of components in a converter-station. Furthermore, the electro-thermal coupling inherent to semiconductor's operation must be considered, since the packaging of the device and the characteristics of the cooling circuit influence the efficiency of the converter-station.

Then, this PhD thesis focuses on the assessment of the potential of new IGCTs for grid connection of remote offshore wind parks, considering the intermittent power production. It aims at studying the main features of IGCTs for HVDC, but also their influence on the converterstations' design. Despite the high level of power of these systems, an experimental approach has been proposed to validate the results obtained with the proposed models. Using the opposition method, the behaviour of IGCT in steady-state, going through the same electrical and thermal stresses as in a real converter-station, has been investigated.

The dissertation has been divided into five chapters: the first chapter presents a state of the art of HVDC technology dedicated to offshore wind-parks, HVDC power converters and high power semiconductor devices. The second chapter deals with the design of the converter-stations for offshore wind applications, including protection aspects from the sub-module to the whole HVDC link.

The third chapter presents the approach to model a MMC sub-module, including electrical and thermal dependencies, to end up with the implementation of a complete simulation tool, fast enough to consider a large number of operating conditions. The fourth chapter is about the power-loss analysis in the two converter-stations of the HVDC link, connecting an offshore wind park, based on the models of the third chapter. Different parametric studies are carried out to compare IGCTs with different voltage ratings, which unavoidably modifies the converterstations' design. Following the power-loss analysis, potential applications for the different IGCTs are proposed.

The fifth and last chapter focuses on the experimental realization of two IGCT-based submodules for MMC, connected in a back-to-back configuration. The power losses are measured with a dedicated instrumentation, allowing a comparison with the power-loss models of the third chapter. Waveforms at the scale of commutation were recorded for different currents, voltages, switching frequencies and different di/dt chokes. Two series of semiconductor devices have been tested, 4.5 kV asymmetric IGCTs with free-wheeling diodes and 10 kV reverse-conducting IGCTs, in realistic steady-state operating conditions.

# Chapter 1

# Grid-connection of remote offshore wind parks and high-power semiconductor devices

This chapter proposes a state of the art of HVDC technologies for cable power transmission, which aims at understanding the benefits and the constraints related to such systems. Then, power converters for HVDC power transmission and high-power semiconductor devices are introduced. A list of the existing projects of HVDC offshore systems has been established in the end of this chapter.

## 1.1 HVDC systems for grid-connection of offshore wind parks

### 1.1.1 Advantages of HVDC over HVAC for cable power transmission

### 1.1.1.1 Transmission capacity

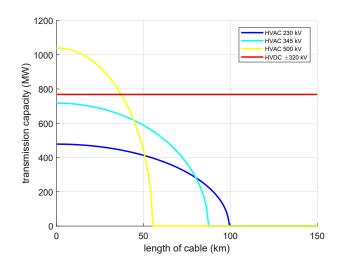

Figure 1.1: Cable transmission capacity for HVAC and HVDC with  $I_{cable, max}=1200$  A

HVAC power transmission has historically spread worldwide. However, it has an unavoidable drawback: cables generate reactive power. Besides, this phenomenon is amplified with the transmission distance. In the case of cable power transmission, the cables generate a significant amount of reactive power, due to the parasitic capacitance between the core and the earthed screen, which increases the Root Mean Square (RMS) currents flowing in them [9]. Considering the thermal limit of the cables, the rise in the transmission distance implies a reduction of the transmission capacity [10]. In order to increase the transmission distance, solutions such as passive reactive power compensation or Flexible AC Transmission Systems (FACTS) can be employed [11]. As a consequence, the transmission distance is a key parameter to consider during the design of HVAC systems.

On the other hand, there is no reactive power involved with DC power transmission, so the transmission capacity is constant with the transmission distance. Figure 1.1 presents the typical evolution of the cable transmission capacity with the length of the cable, it can be observed that HVAC power transmission is seriously penalized beyond 50 km, where capacitive effects are dominant. Consequently, HVDC is an attractive solution for high-power transmission over long distances, either with overheads lines or underground/submarine cables.

#### 1.1.1.2 Technologies of submarine cables

Another important aspect related to power transmission is the technology of the cables. Because of their length and the laying engineering works, they have a consequent influence on the cost of the system.

Mass-impregnated cables Mass-impregnated cables have been used since 1895 in the field of high-voltage systems, with a first application for an HVDC system in 1954 for Gotland I [12]. Its insulation lies in a paper impregnated with a high-viscosity oil, which has proven to be reliable over the past sixty years for HVDC systems. For submarine applications, they also include a steel armour for better mechanical performances. Nowadays, mass-impregnated cables with voltage ratings up to 600 kV and current ratings up to 1800 A are available in Europe [13], leading to a maximum power rating of 2.2 GW per end-station. This technology, though well-established, suffers from some limits such as its weight, in a range of 40-60 kg/m for submarine applications.

**Cross-Linked Polyethylene Extruded (XLPE) HVDC cables** Cross-Linked Polyethylene Extruded (XLPE) HVDC cables have been used for the first time in the Cross-Sound Cable project in 2002 [14], with a voltage rating of 150 kV. This technology is much more recent than mass-impregnated cables in the field of HVDC. An important constraint is that they do not support regular polarity reversal: as a consequence, they are generally not compatible with Current-Source Converters (CSCs). On the other hand, they are suitable for connecting Voltage-Source Converter (VSCs). XLPE insulation leads to lighter cables due to a higher compactness, in a range of 20-35 kg/m [15]. Nevertheless, it remains limited in terms of voltage rating, 320 kV is the maximum for industrialized solutions in the moment [10]. Two times lighter than mass-impregnated cables, it is reported than XLPE cables are also cheaper than mass-impregnated cables [14] in terms of manufacturing, and easier to install [10]. Consequently, they embody a key technology for the development of HVDC offshore converter-stations.

525 kV XLPE cables, already developed by some manufacturers [16][17], must be used in prospective HVDC projects, as they contribute to increase the transmission capacity of the link. A further reduction of manufacturing and installation costs at the scale of the whole system is expected [18]. 600 kV and 640 kV XLPE cables have also been reported [19][20] and are the next milestone.

#### 1.1.1.3 Investments costs for HVAC and HVDC offshore power transmission

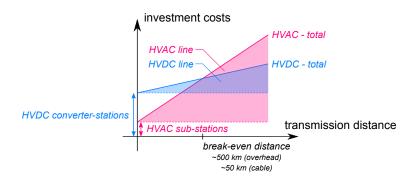

The observations made in 1.1.1.1 and 1.1.1.2 have pointed out that HVDC is clearly favoured when the cable transmission distance increases. Regarding costs, Figure 1.2 presents the typical trade-off in the field of power transmission:

- The cost of HVDC converter-stations is the highest due to the power electronics systems, which makes HVAC power transmission the cheapest for small transmission distances.

- The cost of HVAC power transmission increases faster than with HVDC power transmission. HVAC cables are penalized by the need of three circuits, instead of two circuits compared with HVDC.

Figure 1.2: Relation between cost and distance for high-voltage AC and DC transmission

A so-called critical distance, or break-even distance, is defined as the distance when investment costs are identical for HVDC and HVAC power transmission. Break-even distances between 50 km and 80 km are reported in the literature [9][21][22], for cable power transmission. It explains why HVAC power transmission is preferred when offshore wind-farms are close to the coast, whereas remote offshore wind-farms are most preferably connected using HVDC power transmission, as in the case of many German projects [23].

### 1.1.2 HVDC configurations for grid connection of offshore wind parks

### 1.1.2.1 Connection from the wind turbine generators to the onshore AC grid

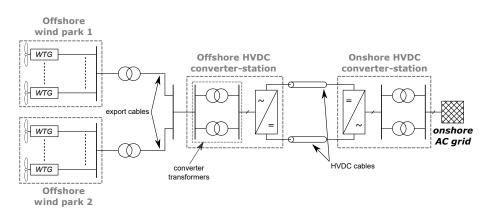

Figure 1.3: Schematic representation of an HVDC grid connection system for offshore wind parks

Figure 1.3 shows a classic configuration to connect one or more wind parks, each composed of several WTGs, to the onshore AC grid [22]. WTGs typically supply power through a 66 kV AC inter-array cable network [6], then the collector networks are connected to collector platforms to step-up the AC voltage, between 132 kV and 220 kV (variable) [6], 155 kV in the case of TenneT (the transmission system operator in Germany and the Netherlands) [24]. Within the offshore HVDC converter-station, the converter transformers increase the AC voltage to reach the nominal input voltage of the rectifier [25]. The offshore converter-station, operating as a rectifier, is connected to HVDC cables ensuring the connection to the onshore HVDC converter-station. The number and the arrangement of collector platforms is chosen to minimize costs, leading to many investigations such as the direct removal of these collector platforms [26], or the use of a DC inter-array collector grid [27][28].

#### 1.1.2.2 Configuration of the main HVDC link

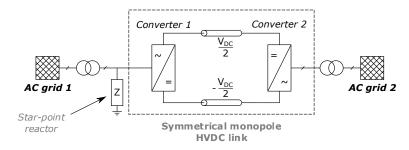

Figure 1.4: Symmetrical monopole configuration for an HVDC link, connecting two AC grids

The HVDC link itself is generally composed of two converter-stations, with a maximum pole-to-ground voltage equal to half the DC link voltage [29]. This configuration is called symmetrical monopole, it provides the maximum DC link voltage with the minimum voltage rating of the cables, as presented in Figure 1.4. Since the maximum transmitted power is restrained by the HVDC cables, a symmetrical monopole link can be doubled to increase the power as in the case of the HVDC links INELFE [21] and Pugalur-Trichur [30]. Special attention must be paid that symmetrical monopole configuration has no natural connection to the ground. Therefore, a star-point reactor, which consists of a high impedance grounding, must be used [31][32][33].

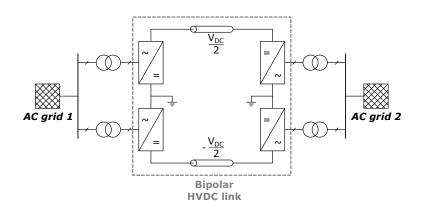

Figure 1.5: Bipolar configuration for an HVDC link, connecting two AC grids

Bipolar systems, as shown in Figure 1.5, are uncommon for offshore installations. They

could be considered in the future as two converters per pole allow redundant operation: even if one converter fails, the HVDC link may remain in operation [34].

27

### 1.1.3 Grid codes for offshore wind parks

Offshore wind-farms, and their grid connection, embody a complex system: to ensure their reliability and their safety, standards are necessary. Besides, standards aim at handling issues of stability and compatibility between the large number of connected systems, which may become more complex with the generalized use of power electronics systems. Transmission system operators (TSOs) are responsible for the establishment of the grid codes, defining a set of rules that connected equipment must follow. Since a TSO is associated to a country or a region, many grid codes with various specifications have appeared. For this reason, the European network of TSOs for electricity (ENTSO-E) also works to the establishment of a grid code, providing common standards within the European Union [33]. As Germany is an European leader in the field of HVDC-connected offshore wind-farms (see 1.4 hereinafter), the grid code of its TSO TenneT is one of the most advanced in this specific domain. ENTSO-E's grid code [35] provides more general requirements that are helpful to analyse the other regional grid codes.

#### 1.1.3.1 Connection point voltage

For TenneT, the AC voltage at the connection point is set to 155 kV. Furthermore, a variation up to  $\pm 10\%$  is requested to comply with voltage stability issues and to facilitate reactive power injection. ENTSO-E has a more generic approach, as it depends on the country. Connection point voltage is generally equal to 380 kV, but a per unit (pu) system is employed. Maximum non-permanent voltage variations go from 0.85 pu to 1.15 pu, including all areas in Europe. This requirement leads to an important constraint for the design of the converter: the nominal AC voltage cannot be delivered at the maximum modulation index m<sub>a</sub>, m<sub>a</sub> must be small enough to benefit from the 15% over-modulation capability aforementioned.

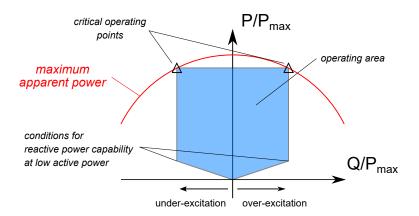

### 1.1.3.2 P-Q profile

The P-Q profile has also a significant influence on the sizing of the converters, as it defines the maximum apparent power. It also affects reactive power exchange capability and thermal stress of the systems as presented in Figure 1.6. The larger the P-Q profile the higher the cost, due to the increase in the initial maximum ratings of the components. In the meantime, the P-Q profile has to be consistent towards grid issues: the growing complexity of grids asks production systems for being flexible, either under-excited or over-excited, at any moment.

Figure 1.6: Generic P-Q profile for a grid-connected power park

Both TenneT's and ENTSO-E's profiles are normalized. TenneT requires a range of  $Q/P_{max}$  equal to 0.7 pu, from -0.3 pu to 0.4 pu, where Q is the reactive power. ENTSO-E's profile is equivalent for the upper limits, with some additional requirements: an inner envelope that can be horizontally translated is defined. Furthermore, the range of reactive powers can be higher for some areas in the European Union: the Nordic area has a maximum range of  $Q/P_{max}$  equal to 0.95 pu, whereas it is only 0.75 pu for continental Europe.

## 1.2 Power converters for HVDC power transmission

### 1.2.1 Line-Commutated Converter (LCC)

The line-commutated converter (LCC) belongs to the category of CSCs: power reversibility is obtained by reversing voltage polarity, while the converter has unidirectional current capability. In 1954 the first commercial HVDC link Gotland I in Sweden, based on this topology, was commissioned [12]. It was able to transfer 30 MW for a rated voltage of  $\pm 150$  kV, between two stations composed of mercury-arc valves, and connected by a 96 km-submarine cable.

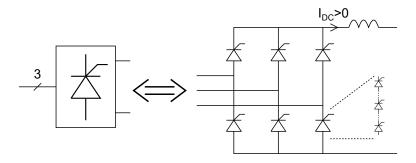

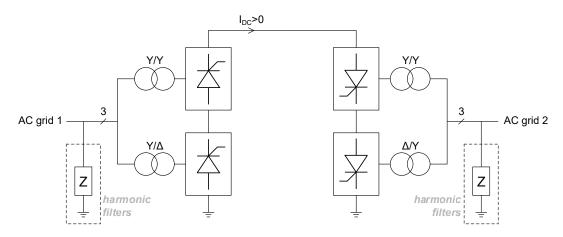

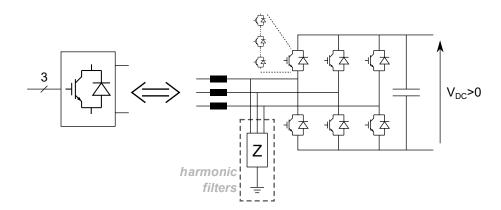

The simplest LCC is a six-pulse unit, as shown in Figure 1.7. Because of the consequent DC link voltage, several thyristors must be series-connected which implies that hundreds of these semiconductor devices are necessary to realize a six-pulse converter unit. To reduce harmonic distortion, twelve-pulse converters are more common as shown in Figure 1.8. Two six-pulse converters are associated and connected to the AC grid through different transformers: a wye-wye transformer keeps the phase-shift constant, whereas a wye-delta or a delta-wye transformer leads to a  $\pm 30^{\circ}$  phase-shift. Converter's operation is adjusted with the firing angle, generally represented by the letter  $\psi$ , which is the turn-on delay angle applied to all thyristors, compared to an operation with diodes.

LCCs have serious drawbacks: due to the transformers and the filters they have a large footprint, which makes their use in specific areas prohibitive. Besides, active and reactive powers cannot be independently fixed, because of the CSC technology. HVDC links using LCCs cannot be connected to AC grids with low short-circuit ratios [36][34], typically inferior to 3 [37]: converter's operation is sensitive to the variations of the AC grid voltages, commutation failures are more likely to happen when the AC grid is weak.

Nowadays, LCCs are used for high-power transmission and ultra HVDC systems, where the DC link voltage reaches  $\pm 800$  kV and even  $\pm 1100$  kV in China, for power ratings of several gigawatts. LCC remains attractive because of its high efficiency, of about 99%. Besides, it is competitive with VSC technology thanks to the use of thyristor, cheaper and more reliable than insulated-gate bipolar transistor (IGBT). Furthermore, LCC is able to handle DC link fault currents before the protections trip [38], limiting potential damage and increasing system's availability.

### 1.2.2 Two-level Voltage-Source Inverter

On the contrary of CSCs, VSCs require power semiconductors with turn-off capability. The appearance of the IGBT in the 1990's has allowed the development of the first commercial HVDC link based on VSC technology, Gotland Light, commissioned in 1999 [39]. With VSC technology, many advantages such as independent control of active and reactive powers, compactness due to capacitive energy storage are brought by the two-level voltage-source inverter [40]. However, it requires a switching frequency of around 2 kHz [41], which severely increases the switching losses compared to a LCC. Besides, tens of IGBTs must be series connected [36], which means that they must commutate exactly at the same moment to ensure a proper sharing of the full

DC link voltage. Figure 1.9 shows a two-level voltage-source inverter. A DC bus capacitor is necessary since the HVDC link must be perceived as a voltage-source by the two converters. Besides, AC filters are mandatory to comply with the harmonic standards. The choice of the switching frequency is a compromise, the higher it is the lower the Total Harmonic Distortion (THD) of the currents, at the price of higher power losses.

Figure 1.7: LCC - six-pulse converter unit

Figure 1.8: HVDC link with twelve-pulse converters, using asymmetrical monopole configuration with ground return

Figure 1.9: Two-level voltage-source inverter: electrical schematic and representation

### 1.2.3 Modular Multilevel Converter (MMC)

Multilevel converters have progressively been introduced in the 1980's (neutral-point clamped converter) and in the 1990's (flying capacitor converter, active neutral-point clamp converter):

they provide many benefits compared to two-level topologies such as lower THD and higher power rating. In the field of HVDC, multilevel topologies are particularly attractive because they allow a division of the DC bus voltage among the semiconductors: the end goal is to avoid series connected devices.

In the beginning, these topologies were only suitable for a few levels: typically, their mechanical assembly becomes too complex beyond fives levels [33]. In the meantime, the number of levels must be large enough to avoid series connection of semiconductor devices. Topologies such as the cascaded H-bridge converter have been proposed, to easily extend the number of levels N. Nevertheless, they require N isolated DC power supplies, which is too expensive at the scale of an HVDC system.

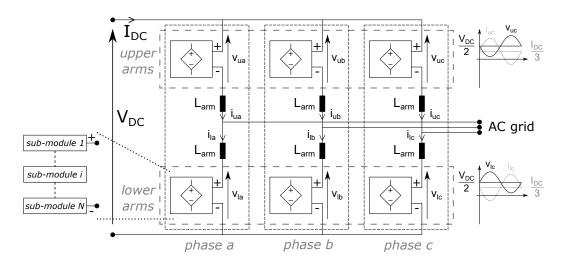

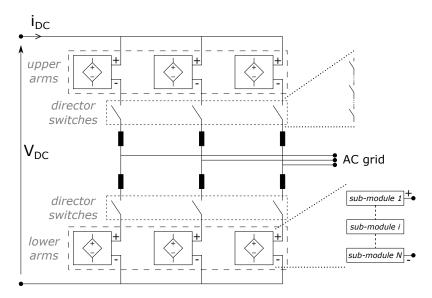

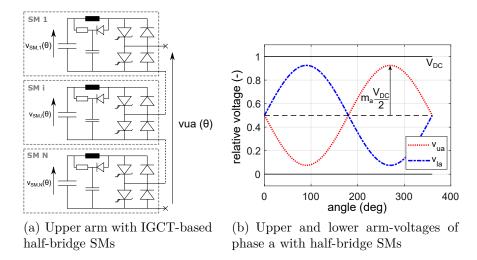

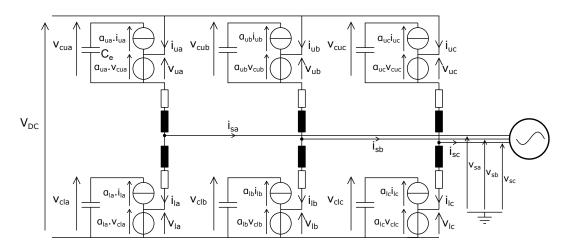

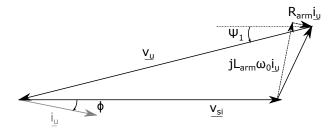

In this context, the introduction of a multilevel and modular solution in the beginning of the 2000's [42] was especially promising. The modular multilevel converter is highly scalable, allows simple mechanical assembly and removes the need for series-connected devices. Figure 1.10 shows the topology: each AC phase is connected to the DC poles by two arms, fitted with inductors to control the arm-currents. An arm is composed of N sub-modules (SMs), where a SM can be considered as an elementary converter with semiconductor devices and at least one capacitor. An arm operates as a controllable voltage-source: the purpose is to reproduce both DC and grid-frequency components inside each phase. Based on Figure 1.10, the following properties can be observed:

- For each phase, the sum of the upper voltage (or current) and the lower voltage (or current) is constant.

- For each phase, the difference of the upper voltage (or current) and the lower voltage (or current) is proportional to the AC grid voltage (or current) of the given phase.

- The sum of the upper/lower voltages/currents is constant, since the sum of the grid-frequency components is null.

Figure 1.10: Modular multilevel converter (MMC): electrical schematic, SMs and simplified arm waveforms

These properties also show that all arm-currents are continuous, which means that high di/dt are removed during normal operation. The large number of levels has many positive consequences: the transition between two successive levels is hardly visible, which means that resulting dv/dt are not problematic. Furthermore, it leads to a THD below international harmonic standards

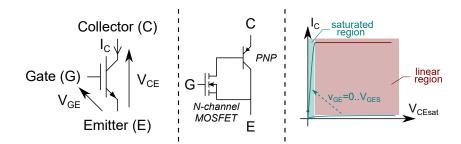

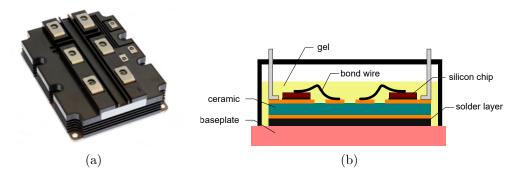

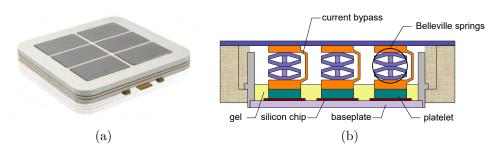

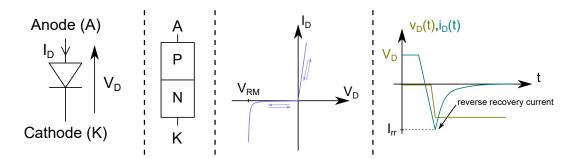

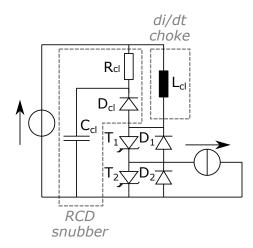

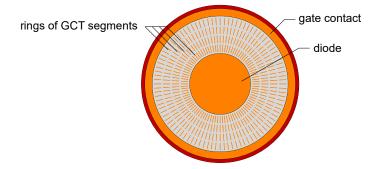

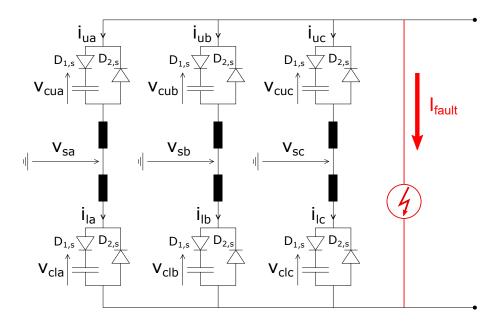

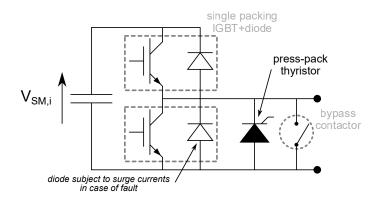

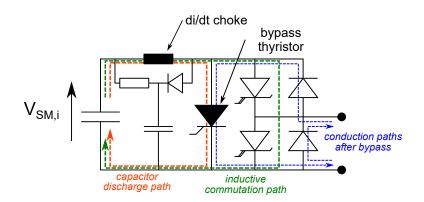

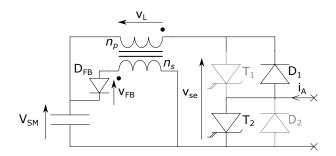

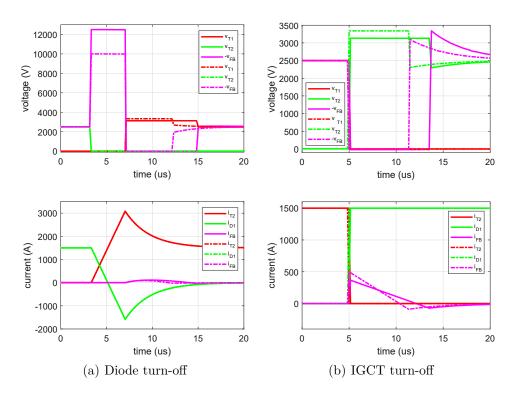

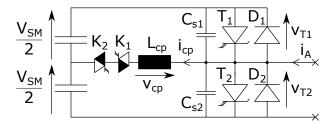

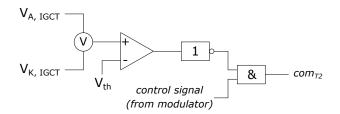

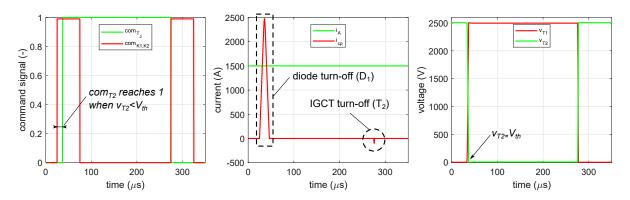

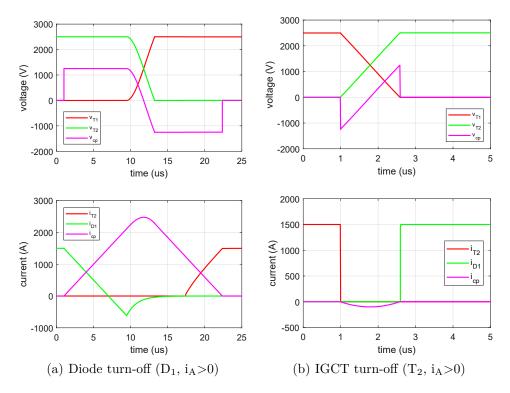

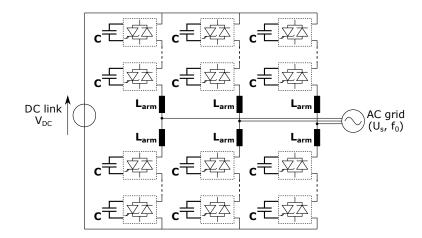

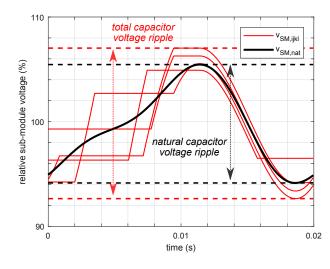

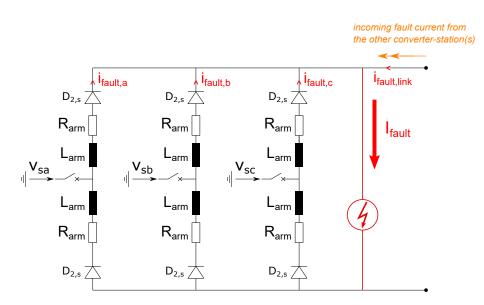

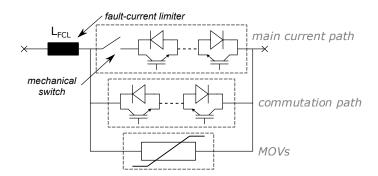

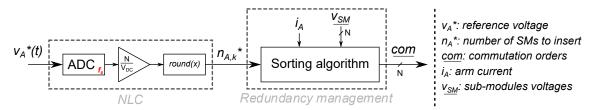

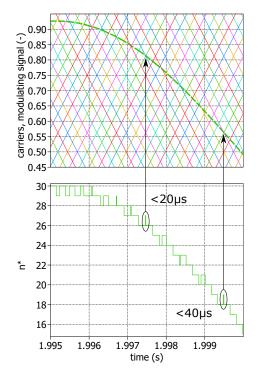

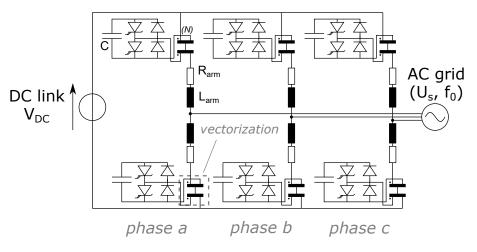

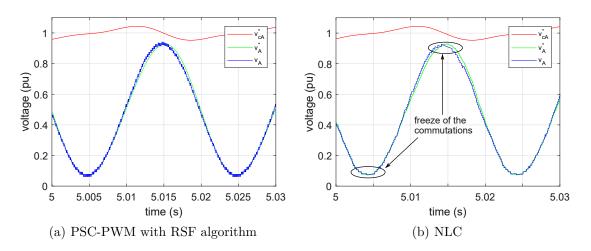

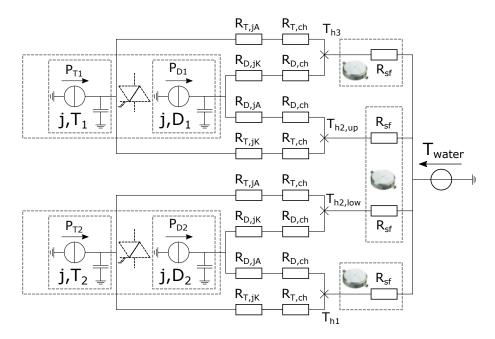

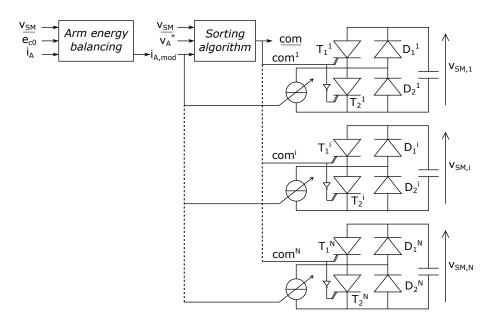

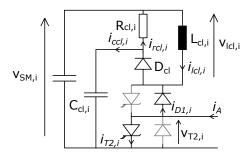

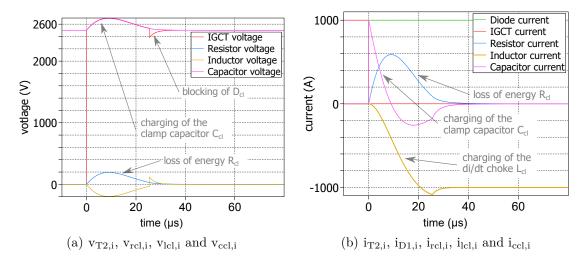

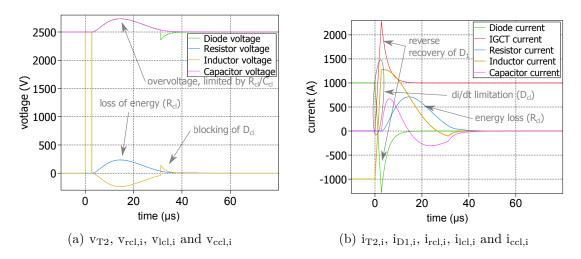

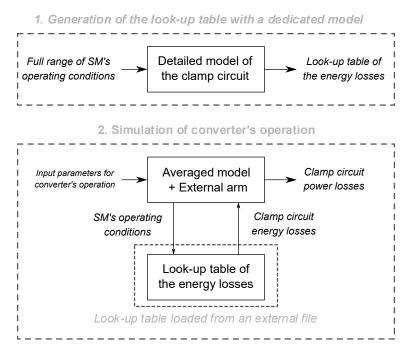

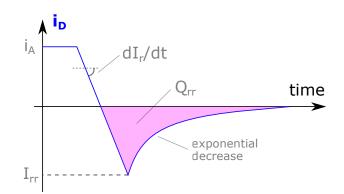

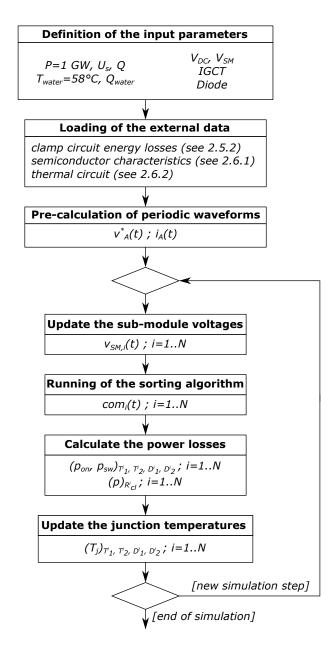

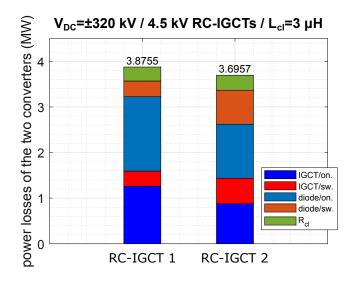

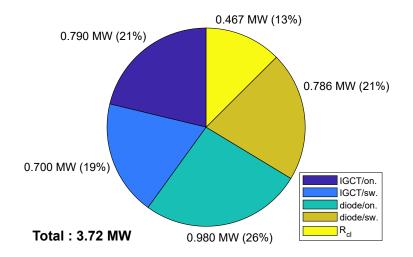

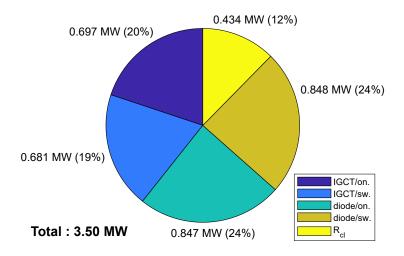

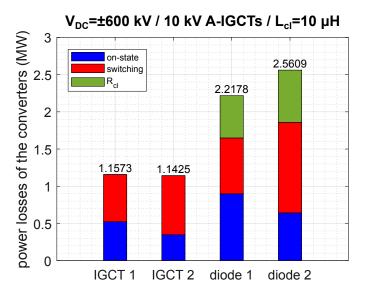

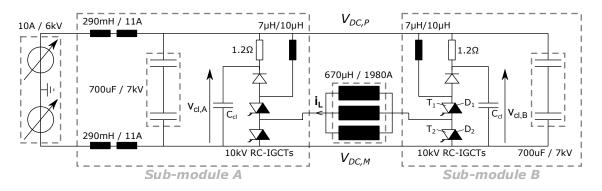

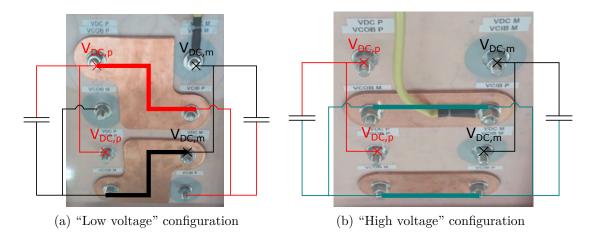

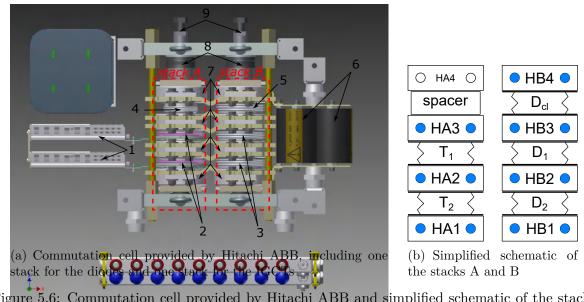

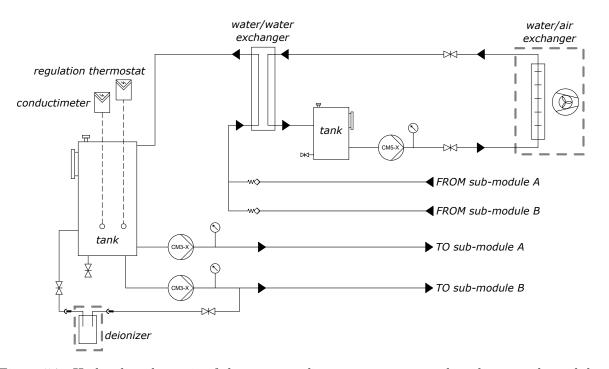

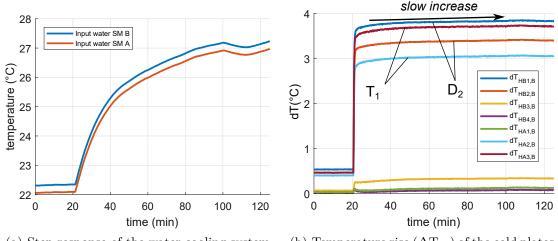

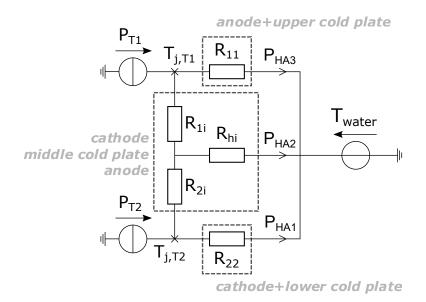

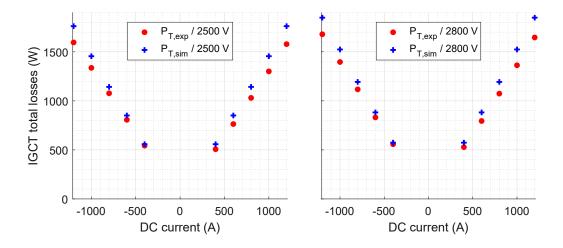

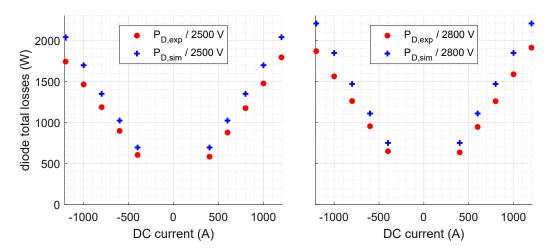

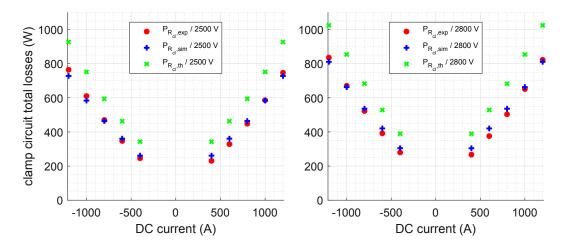

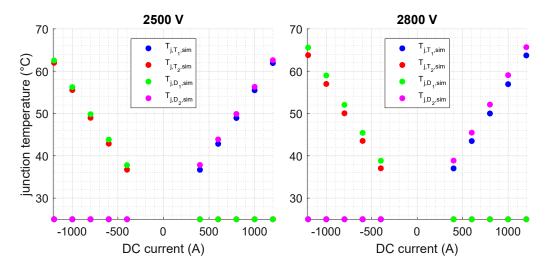

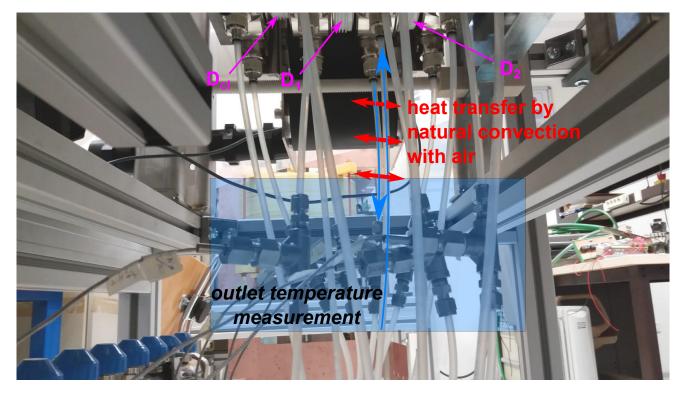

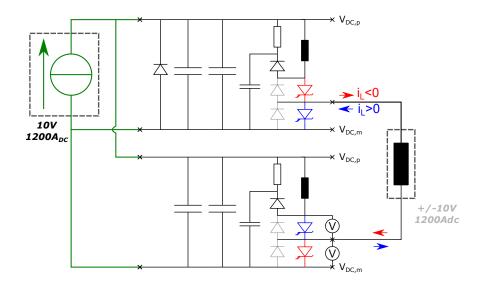

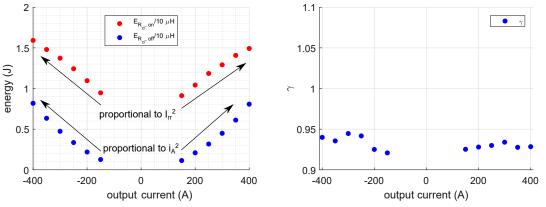

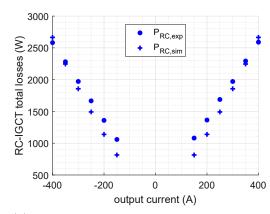

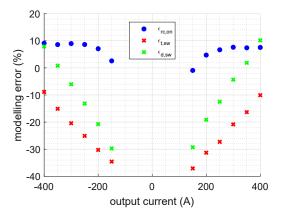

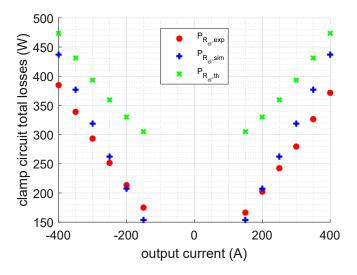

for the AC grid [21][32]. The apparent switching frequency is N times the effective switching frequency, which leads to a switching frequency typically below 200 Hz, i.e. ten times less than in the case of a two-level voltage-source inverter. Then, it automatically reduces converter's power losses, which is a serious drawback of the two-level voltage-source inverter. This observation also unveils that the semiconductor devices must be adapted to low frequency operation, switching performances can be reduced to enhance on-state performances, thus increasing converter's efficiency. This is further discussed in the next chapters.