## Contribution to on-wafer characterization of millimeterwave FD-SOI MOS transistors

Karthi Pradeep

#### ▶ To cite this version:

Karthi Pradeep. Contribution to on-wafer characterization of millimeter- wave FD-SOI MOS transistors. Electronics. Université de Bordeaux, 2023. English. NNT: 2023BORD0164. tel-04197012

## HAL Id: tel-04197012 https://theses.hal.science/tel-04197012v1

Submitted on 5 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# université BORDEAUX

### THÈSE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

## **DOCTEURE DE**

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

SPÉCIALITÉ ÉLECTRONIQUE

### Karthi PRADEEP

### CONTRIBUTION À LA CARACTÉRISATION SUR WAFER DE TRANSISTORS MOS FD-SOI en bande millimétrique

#### CONTRIBUTION TO ON-WAFER CHARACTERIZATION OF MILLIMETER-WAVE FD-SOI MOS TRANSISTORS

Sous la direction de : **Thomas ZIMMER** (co-directeur : **Sébastien FREGONESE**)

Soutenue le 28 Juin 2023

| Membres du jury :                  |                                                 |                       |

|------------------------------------|-------------------------------------------------|-----------------------|

| <b>Prof. DANNEVILLE Francois</b> , | Professeur, Université de Lille                 | Rapporteur            |

| Prof. FERRARI Philippe,            | Professeur, Université de Grenoble-Alpes        | Rapporteur            |

| Dr. MOUNAIX Patrick,               | Directeur de recherche, CNRS, Laboratoire IMS   | President             |

| Dr. DORMIEU Benjamin,              | Ingénieur, STMicroelectronics, Crolles          | Examinateur           |

| Dr. SCHEER Patrick,                | Ingénieur, STMicroelectronics, Crolles          | Examinateur           |

| Dr. FREGONESE Sébastien,           | Chargé de recherche, HDR, CNRS, Laboratoire IMS | Co-directeur de thèse |

| Prof. ZIMMER Thomas,               | Professeur, Université de Bordeaux              | Directeur de thèse    |

| Membre invitée :                   |                                                 |                       |

Maitre de conférences, Université de Bordeaux

Co-encadrante

Université de Bordeaux Laboratoire de l'Intégration du Matériau au Système UMR CNRS 5218, 351 cours de la Libération - Bat A31, 33400 Talence, France

Dr. DENG Marina,

## Abstract - EN

Silicon bipolar and CMOS technologies have been recognized for their abilities in millimeterwave applications, making them good candidates for circuit realization in the THz domain. Among them, the "Fully-Depleted-Silicon-On-Insulator" (FD-SOI) technologies developed from the 28nm node offer promising performances for transition frequencies ( $f_T$ ) and maximum oscillation frequencies ( $f_{MAX}$ ) beyond 300 GHz, and even more for the most advanced nodes. At the same time, the development of millimeter-wave circuits is booming, with realizations at ever higher frequencies, some of which go beyond 100 GHz. To enable the design of circuits operating at millimeter-wave frequencies, an accurate modeling of FD-SOI transistors is essential. Furthermore, it is no longer possible to limit parameter extraction below 110 GHz, and new techniques for obtaining reliable measurements of passive and active devices need to be investigated. In this thesis, we will examine the on-wafer S-parameter characterisation of different passive test structures and MOS transistors in 28nm FD SOI technology from STMicroelectronics, up to 500 GHz.

We will start with an introduction to the measurement equipment usually used for this type of analysis, then move on to the different measurement benches adopted in the IMS laboratory, and finally focus on the calibration and de-embedding techniques. Two different chips were studied. For each chip, we will introduce a new floorplan design and evaluate its ability to limit spurious effects. For our analysis, we will rely on electromagnetic simulations and mixed small signal plus probe model EM simulations, both including the probe models for a closer evaluation of the measurement results under real conditions. Finally, we will present some test structures to evaluate the losses in the lines, the accuracy of the impedance correction methodology and finally the probe-to-probe and probe-to-substrate coupling.

**Keywords:** Characterization, Transmission Lines, THz, Millimeter-Wave, On-Wafer Calibration, MOSFET on FDSOI

## Résumé - FR

Les technologies bipolaires et CMOS sur silicium présentent des aptitudes reconnues pour les applications millimétriques, ce qui font d'elles de bonnes candidates pour la réalisation de circuits dans le domaine du THz. Parmi elles, les technologies « Fully-Depleted-Silicon-On-Insulator » (FD-SOI) développées à partir du nœud 28nm offrent des caractéristiques prometteuses pour un vaste champ d'applications, avec notamment des fréquences de transition,  $f_T$ , et d'oscillation maximum,  $f_{MAX}$ , au-delà de 300 GHz, voire plus encore en ce qui concerne les nœuds les plus avancés. Dans le même temps, le développement de circuits en bande millimétrique est en plein essor, avec des réalisations à des fréquences toujours plus élevées et pour certaines au-delà de 110 GHz. Pour permettre la conception de ces circuits, une modélisation précise des transistors FD-SOI est absolument nécessaire. De plus, il n'est plus possible de limiter l'extraction des paramètres en dessous de 110 GHz, et de nouvelles techniques permettant d'obtenir des mesures fiables de dispositifs passifs et actifs doivent être étudiées. Dans cette thèse, nous examinerons la caractérisation des paramètres S sur silicium (on-wafer) de différentes structures de test passives et des transistors MOS en technologie 28nm FD SOI de STMicroelectronics, jusqu'à 500 GHz.

Nous commencerons par une introduction de l'équipement de mesure habituellement utilisé pour ce type d'analyse, puis nous passerons aux différents bancs de mesure adoptés au laboratoire IMS, et enfin nous nous concentrerons sur les techniques de calibrage et d'épluchage (deembedding). Deux différentes puces ont été étudiées. Pour chaque puce, nous introduirons un nouveau design du floorplan et évaluerons sa capacité à limiter les effets parasites. Pour notre analyse, nous nous appuierons sur des simulations électromagnétiques et des simulations EM mixtes de modèle petit signal + sonde, toutes deux incluant les modèles des sondes pour une évaluation des résultats de mesure plus proche des conditions réelles. Enfin, nous présenterons quelques structures de test pour évaluer les pertes dans les lignes, la précision de la méthodologie de correction d'impédance et finalement le couplage sonde-sonde et sonde-substrat.

**Mots-clés:** Caractérisation, Lignes de transmission, Terahertz, Ondes millimétriques, Calibrage sur silicium, MOSFET sur FDSOI

# Acknowledgements

There have been a lot of people who were part of this thesis directly or directly and I would like to extend my words of gratitude to them.

This CIFRE PhD thesis has been realised in collaboration with the IMS laboratory, University of Bordeaux, and STMicroelectronics, Crolles, and I thank these establishments for giving me the opportunity to work and providing the necessary facilities.

I would like to express my sincere thanks to Prof. Thomas Zimmer, my thesis director for having co-ordinated the progress of my thesis in a well-structured manner for the last 3 years. He has been able to diplomatically and perfectly manage the discussions with all five supervisors who were part of this thesis, and arrive at a unanimous decision that helped the smooth progress of this work. I would also like to thank my thesis co-director, Dr. Sebastien Fregonese, for the very effective technical discussions we have had throughout the course of this thesis. Your suggestions on many simulation problems were very insightful and working with you has taught me to improve my research skills. I also express my heartfelt gratitude to my thesis supervisor, Dr. Marina Deng, for the great amount of time she spent in my office many days, patiently explaining the concepts in simple words and trying to find solutions to the roadblocks in the thesis. I also wish to thank her for all the personal help and support provided during my stay in Bordeaux.

I further extend my deepest gratitude to my industrial supervisor at STMicroelectronics, Dr. Patrick Scheer for having been a source of constant support and guidance all along this PhD, right from the start and even before to prepare for my arrival in France. His comments and suggestions on even the smallest aspect of the work have been instrumental in improving the quality of this thesis. Moreover, his honest feedback has pushed me to perform better every year. My genuine thanks are also due to my industrial supervisor at STMicroelectronics, Dr. Benjamin Dormieu, for always being available for any quick questions or advice all through the tenure of my PhD. A special thanks to Benjamin for the help with all the administrative things during my initial days at ST and also for introducing me to all the ST tools necessary for my thesis work. I also thank all my supervisors for their help during the manuscript preparation that enabled me to complete it in a short time.

I also thank my jury members, Prof. Francois Danneville, Prof. Philippe Ferrari and Dr. Patrick Mounaix for taking the time to review my work and attending my PhD defense.

This work is a result of several and repeated measurement campaigns for which I thank Magali De Matos for her time and expertise. Thanks are also due to Marco for the many technical discussions we had during the first year of my thesis, which served as a great starting point.

Thank you Soumya for being a constant supportive colleague these years, right from arranging my stay upon my arrival to Bordeaux, to finally helping with editing and formatting of my manuscript.

The period of my thesis has enabled me to meet a lot of new people from different parts of the world and make friends, which has been an enriching experience, and I am grateful to each one of you. Thanks to Denis and Sebastien for the cheerful lunch moments in these stressful times, and Andres for your help with Cadence design.

This thesis would not have been possible without the support of my family and I would like to thank each one of them. Thanks to my little brother Krishna for being the reason for my choice of ST for my thesis and for being a source of constant inspiration and support. Thanks to my beloved parents Pradeep and Sheela for always being there for me and keeping me sane. No matter the distance apart, you never failed to make sure I was doing well. My husband Siva also deserves mention for his unwavering support, specifically during these difficult years, and also for his wonderful cooking. Last, but not the least, I thank my little baby Helena for bringing in unmeasurable joy and happiness during the last year of my thesis.

This acknowledgement would not be complete without due mention of Appoopan who taught me to dream big and achieve heights, but couldn't see me embark on this journey of PhD, and Ammamma, who left me halfway without waiting to see me complete this journey. You have given me the best and most memorable childhood memories, which will stay forever with me. This thesis is dedicated to you both and I hope this make you proud of me, wherever you are.

# Contents

| A  | bstrac                                          | ct - EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | i                                                                                                       |

|----|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Re | ésum                                            | é - FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                                                                     |

| A  | cknow                                           | wledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | v                                                                                                       |

| Li | st of I                                         | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                                                                      |

| Li | st of '                                         | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xiii                                                                                                    |

| G  | The                                             | <b>l Introduction</b><br>sis context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>1</b><br>1<br>2                                                                                      |

| 2  | $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6 \\ 1.7$ | kground Theory and Literature Review         28FD-SOI         RF Measurements         Measurement setups         Types of Calibration         Types of De-embedding         Electromagnetic Simulations         Previous works on RF measurements beyond 110 GHz         racterization and EM simulation of Run1 test structures         Test Structure Description         Intrinsic EM Simulations         Transistor characterization procedure and Measurement results         Extraction of Small Signal Equivalent Circuit         Comparison of measurement results with EM simulation and transistor model simulation         Effect of RF probe used for measurement         Drawbacks and limitations of Run1 | <b>5</b><br>8<br>8<br>13<br>18<br>21<br>24<br><b>31</b><br>31<br>35<br>44<br>48<br>52<br>62<br>70<br>71 |

| 3  |                                                 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71<br>73                                                                                                |

|    | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                 | Motivation for Run2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73<br>74<br>79<br>86<br>103                                                                             |

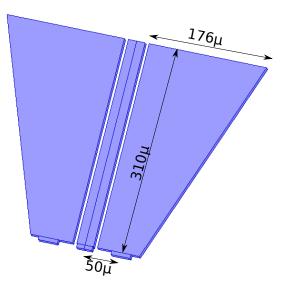

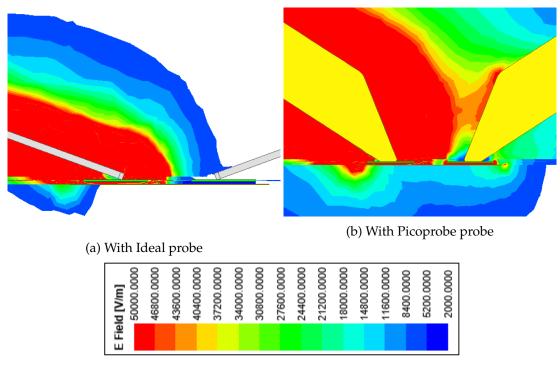

|    | 3.6                                             | Effect of probe geometry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 115                                                                                                     |

| 3.7 Conclusion                    | . 120 |

|-----------------------------------|-------|

| General Conclusion & Perspectives | 121   |

| Author Publication List           | 125   |

| Bibliography                      | 127   |

# **List of Figures**

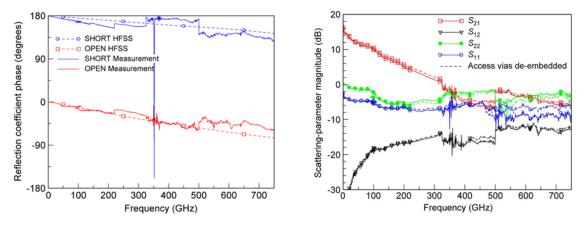

| 1    | NIST (National Institute of Standards and Technologies, USA) measurement of (a) the phase measurement and EM simulation of an open and a short, and (b)       |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the S-parameter magnitude measurement of a transistor up to 750 GHz. [9]                                                                                      | 1  |

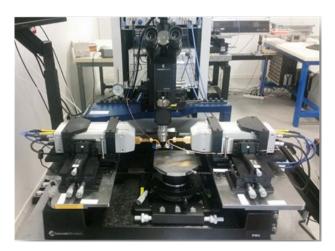

| 2    | Measurement bench of the NANOCOM platform, operating up to 500 GHz                                                                                            | 3  |

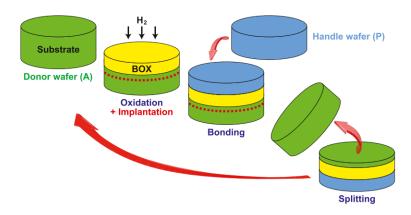

| 1.1  | Smart Cut process for fabrication of SOI wafer [27]                                                                                                           | 5  |

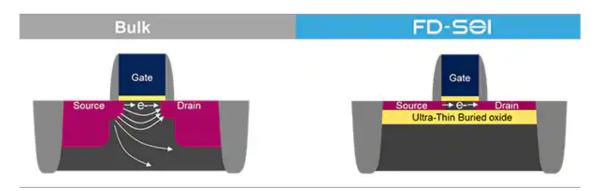

| 1.2  | Bulk CMOS vs FD-SOI (Source: STMicroelectronics)                                                                                                              | 6  |

| 1.3  | Block diagram of VNA S-parameter testset [34]                                                                                                                 | 9  |

| 1.4  | Bias TEE circuit used in VNA [34]                                                                                                                             | 9  |

| 1.5  | Probe station for measurement from 1-110 GHz using N5250A network analyzer                                                                                    | 10 |

| 1.6  | Probe station used for measurements from 140 - 500 GHz                                                                                                        | 11 |

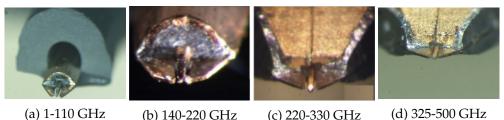

| 1.7  | Photographs of Picoprobes for measurements from 1-500 GHz                                                                                                     | 12 |

| 1.8  | Photograph of Infinity probe for 110 GHz measurements                                                                                                         | 13 |

| 1.9  | SEM image of Infinity XT for 110 GHz measurements                                                                                                             | 13 |

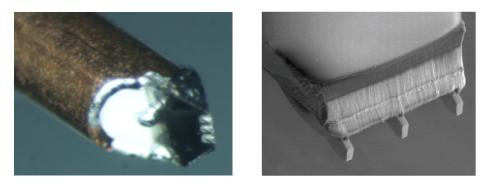

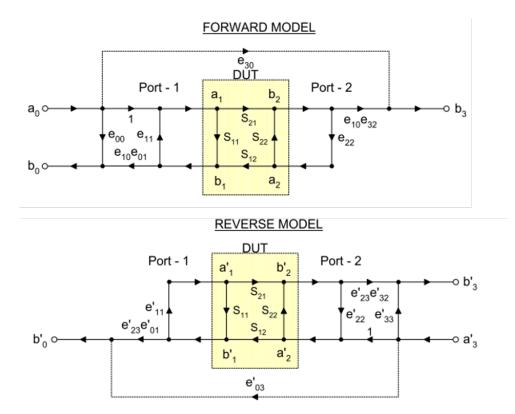

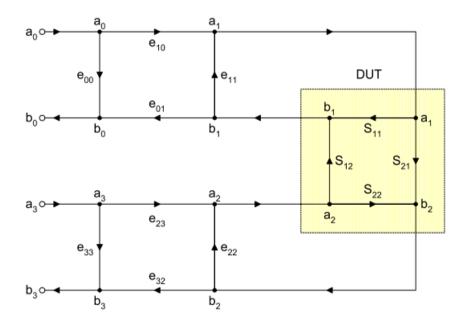

|      | 12-term error model of network analyzer [52]                                                                                                                  | 14 |

| 1.11 | Calibration standards on ISS provided by Cascade Microtech (Form Factor) for                                                                                  |    |

|      | use with Infinity probes [54]                                                                                                                                 | 15 |

| 1.12 | CS-5 Calibration substrate provided by GGB Industries Inc. [55]                                                                                               | 16 |

|      | 8-term error model [52]                                                                                                                                       | 17 |

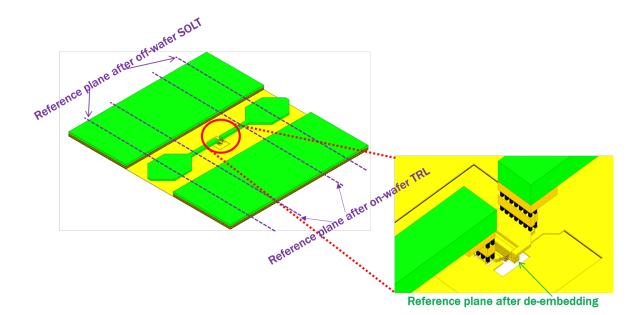

| 1.14 | Figure showing the reference plane after each calibration and after de-embedding                                                                              | 19 |

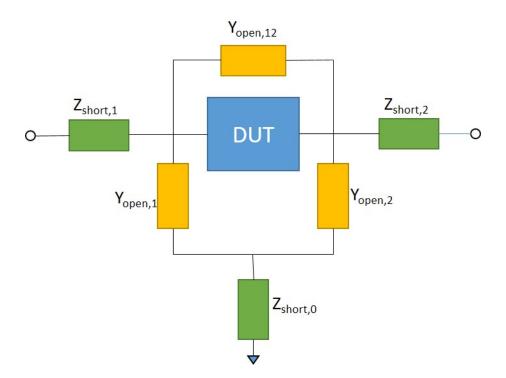

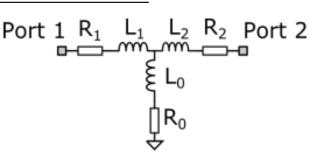

| 1.15 | Lumped model of parasitics to be removed using Short Open de-embedding                                                                                        | 20 |

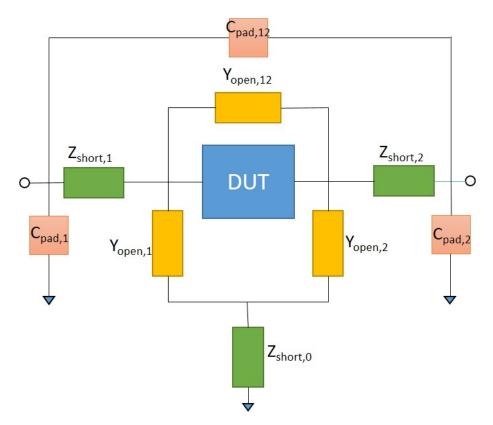

|      | Parasitics model used for Pad Short Open de-embedding                                                                                                         | 21 |

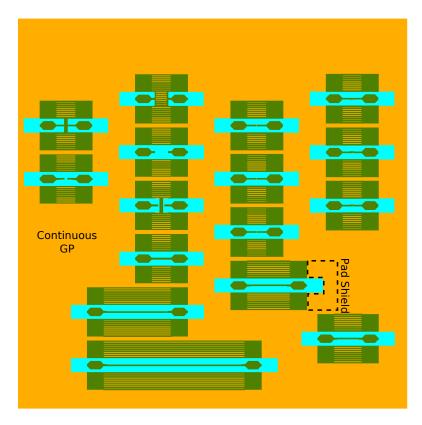

|      | Meshed metal layers of the layout                                                                                                                             | 22 |

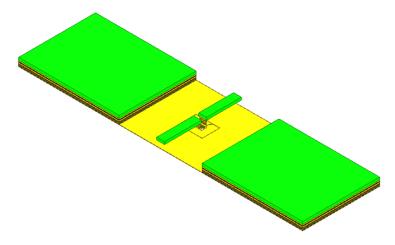

| 1.18 | HFSS model for intrinsic simulation of Transistor Open                                                                                                        | 23 |

| 1.19 | Lumped ports in HFSS for co-simulation of transistor                                                                                                          | 23 |

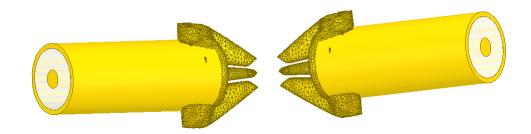

| 1.20 | 3D model of Picoprobe used for EM simulation                                                                                                                  | 24 |

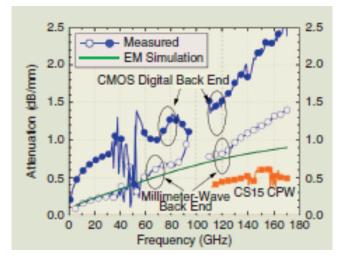

| 1.21 | Measured versus simulated attenuation per mm as a function of frequency for microstrip lines fabricated in digital and mm-wave silicon back-end-of-line, fig- |    |

|      | ure taken from [61]                                                                                                                                           | 26 |

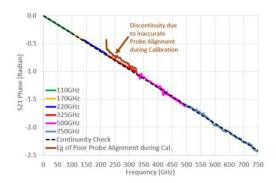

|      | Phase versus Frequency (-0.185 Deg/GHz) for the 0.5ps Line, from [82].                                                                                        | 27 |

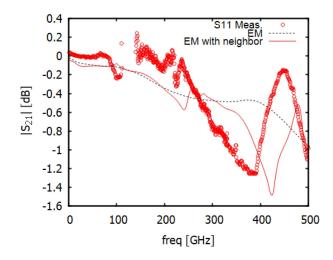

| 1.23 | Magnitude of $S_{21}$ parameter measurements of a line up to 500 GHz showing un-                                                                              |    |

|      | expected behavior: impact of adjacent structures confirmed with EM simulation,                                                                                |    |

|      | from [79]                                                                                                                                                     | 28 |

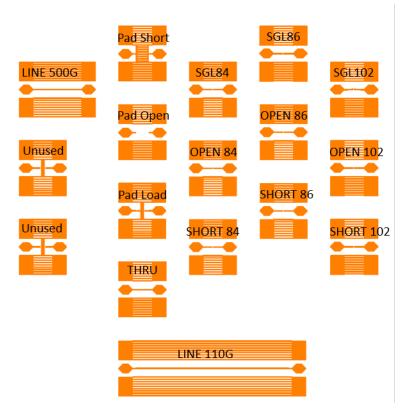

| 2.1  | Top layout of the on-wafer calibration kit.                                                                                                                   | 32 |

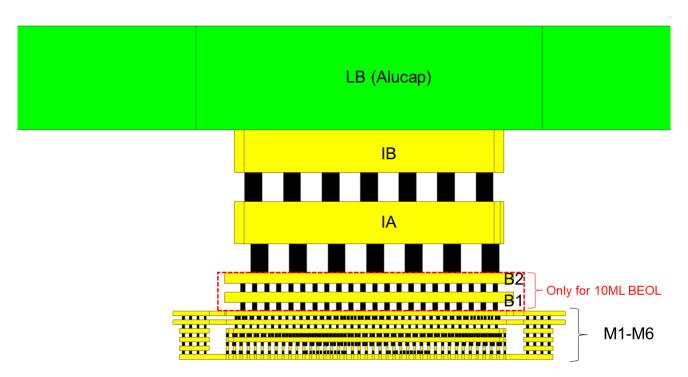

| 2.2  | BEOL of 28 FD-SOI                                                                                                                                             | 32 |

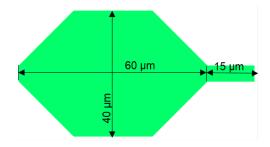

| 2.3  | Dimensions of the RF signal pad                                                                                                                               | 33 |

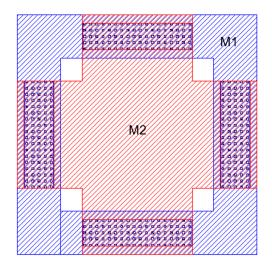

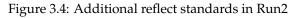

| 2.4  | Ground plane unit cell consisting of M1 and M2                                                                                                                | 33 |

| 2.5  | Top views of test structures                                                                                                                                  | 34 |

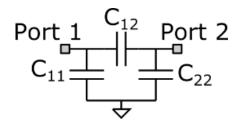

| 2.6  | Equivalent circuit of Transistor Open                                                                                                                         | 35 |

| 2.7  | Equivalent circuit of Transistor Short                                                                                                                        | 35 |

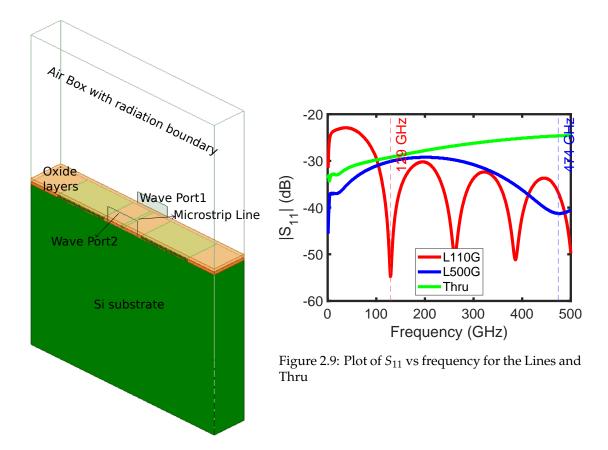

| 2.8   | HFSS model for intrinsic simulation of THRU                                       | 36  |

|-------|-----------------------------------------------------------------------------------|-----|

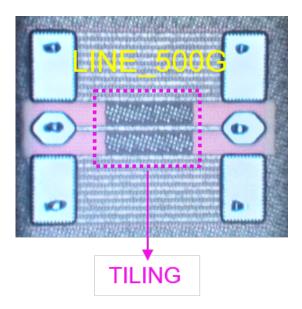

| 2.9   | Plot of $S_{11}$ vs frequency for the Lines and Thru                              | 36  |

| 2.10  | Photograph of the Line_500G. Tiles can be seen in the region within the dotted    |     |

|       | box                                                                               | 37  |

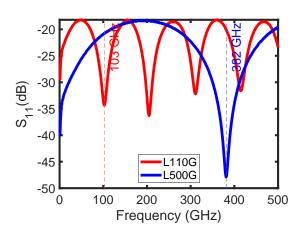

| 2.11  | $S_{11}$ of Line_110G & Line_500G with the hybrid oxide that accounts for tiles   | 37  |

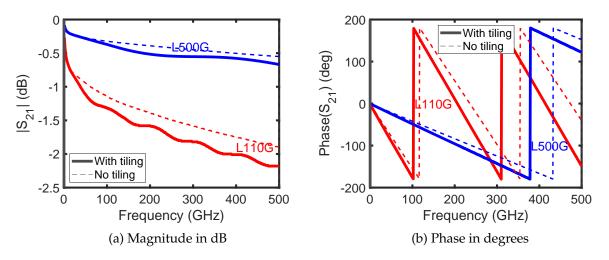

|       | $S_{21}$ of Lines and Thru with (actual case) and without (ideal case) tiling     | 38  |

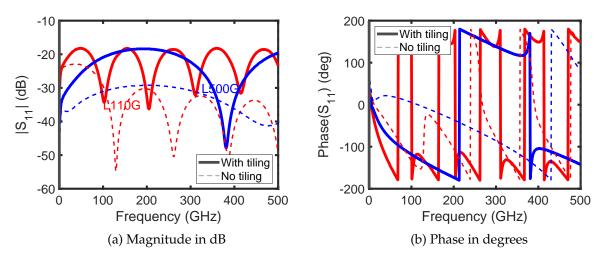

|       | $S_{11}$ of Lines and Thru with (actual case) and without (ideal case) tiling     | 38  |

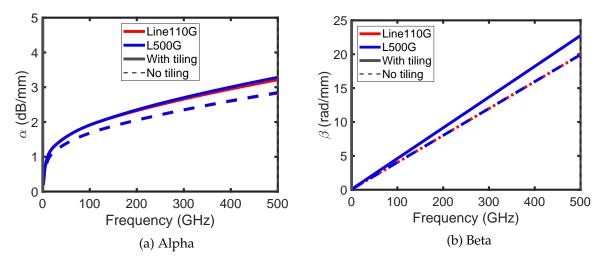

|       | Propagation Constant of Lines                                                     | 39  |

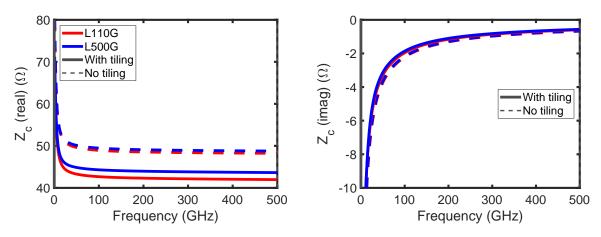

|       | Characteristic impedance of the Lines                                             | 39  |

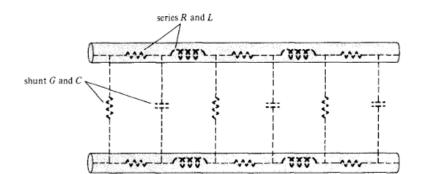

|       | RLCG model of transmission line                                                   | 40  |

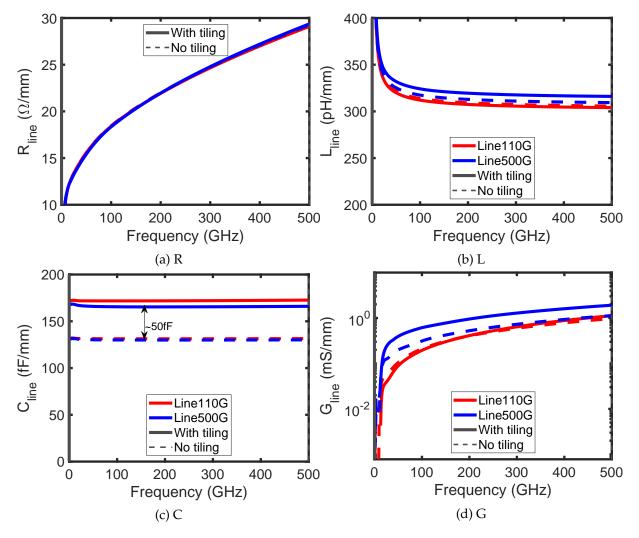

|       | RLCG parameters of Line                                                           | 41  |

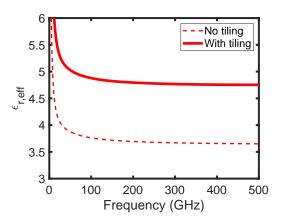

|       | Effective dielectric constant of lines with and without tiling                    | 41  |

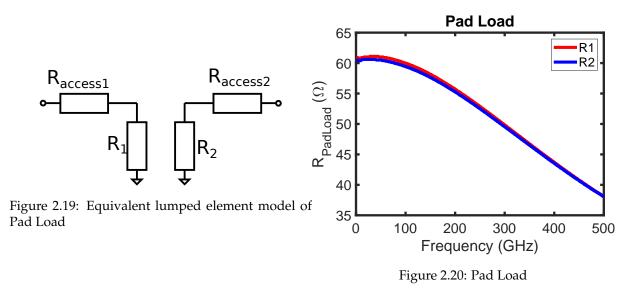

|       | Equivalent lumped element model of Pad Load                                       | 42  |

|       | Pad Load                                                                          | 42  |

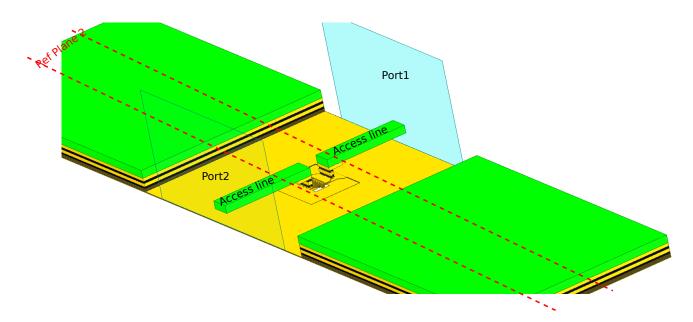

|       | 3D model in HFSS for intrinsic simulation of Transistor Open. Ref Plane 2 corre-  |     |

|       | sponds the reference plane after shifting the TRL calibration plane close the DUT |     |

|       | along the transmission line.                                                      | 43  |

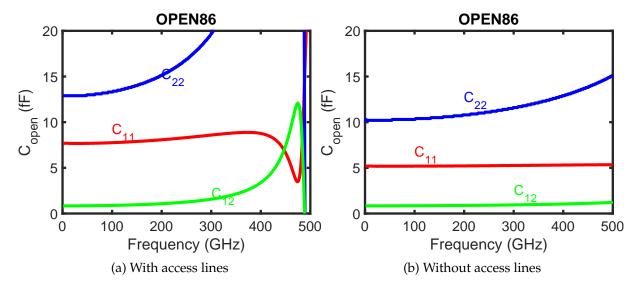

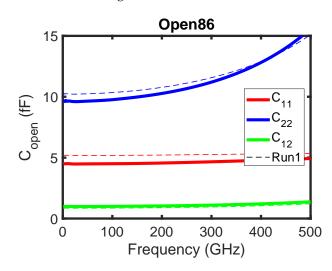

| 2.22  | Equivalent capacitances of Transistor Open extracted from EM simulation           | 43  |

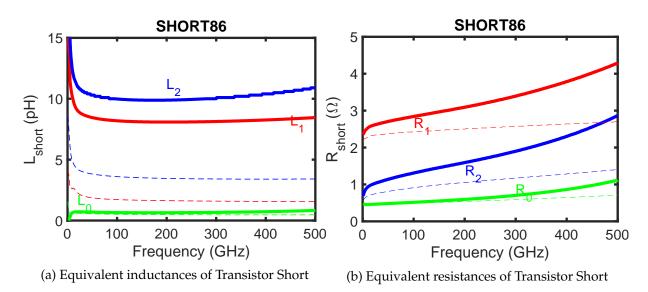

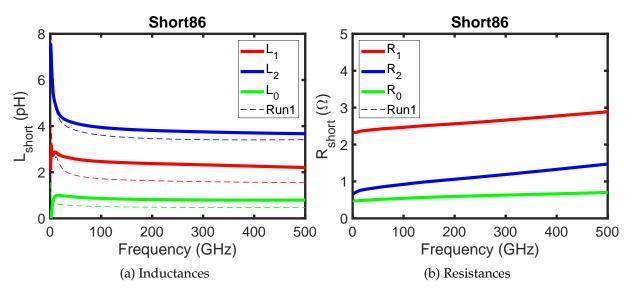

|       | Equivalent lumped elements of Transistor Short extracted from EM simulation       | 10  |

| 2.20  | (solid lines: with access lines; dashed lines: without access lines )             | 44  |

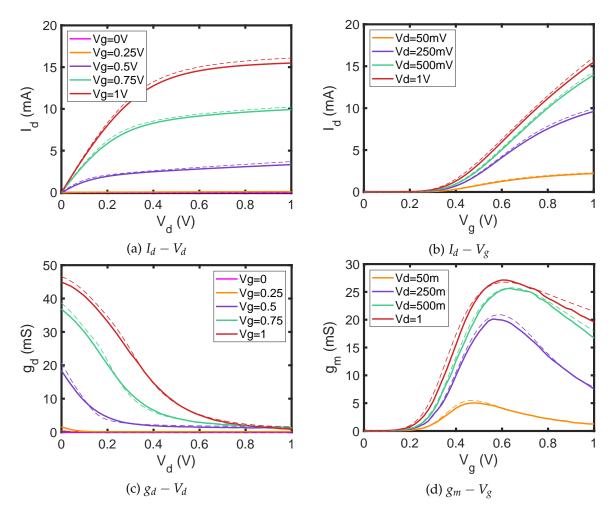

| 2 24  | DC Characteristics of the FD-SOI NMOS transistor (SGL86)                          | 45  |

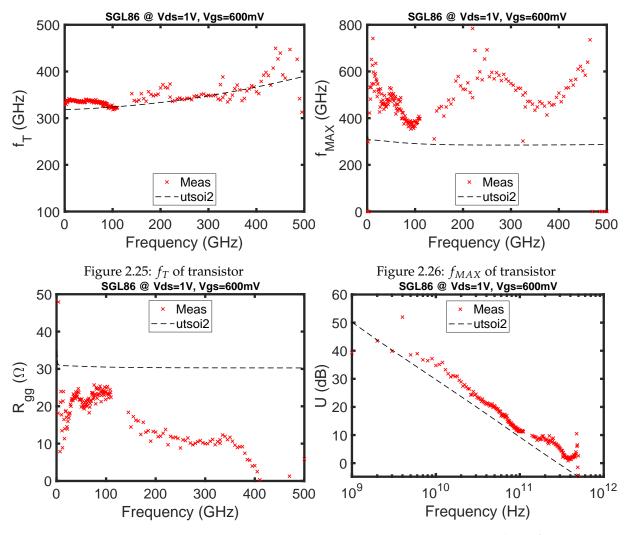

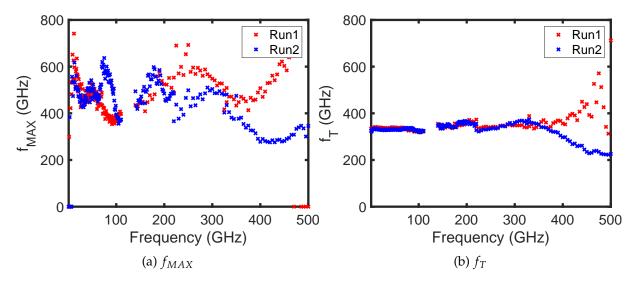

|       | $f_T$ of transistor                                                               | 47  |

|       | $f_{MAX}$ of transistor                                                           | 47  |

|       | Gate resistance of transistor                                                     | 47  |

|       | Mason Gain in dB vs frequency                                                     | 47  |

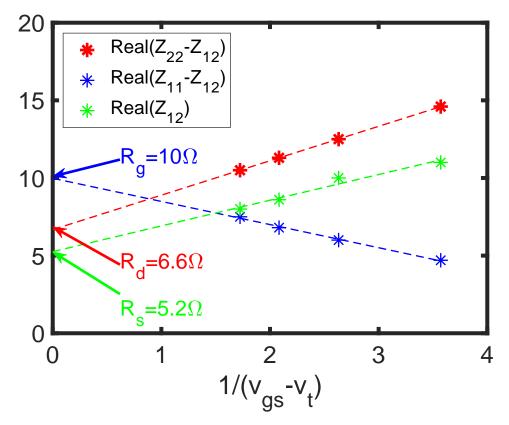

|       | Extraction of extrinsic parameters at 50 GHz for small signal model               | 48  |

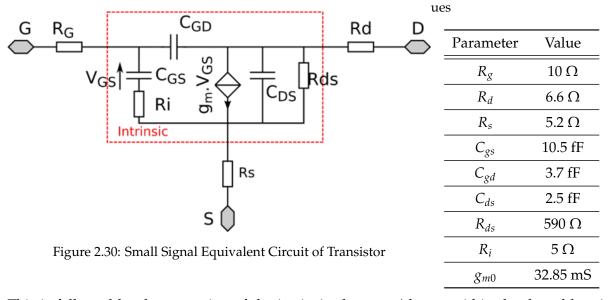

|       | Small Signal Equivalent Circuit of Transistor                                     | 49  |

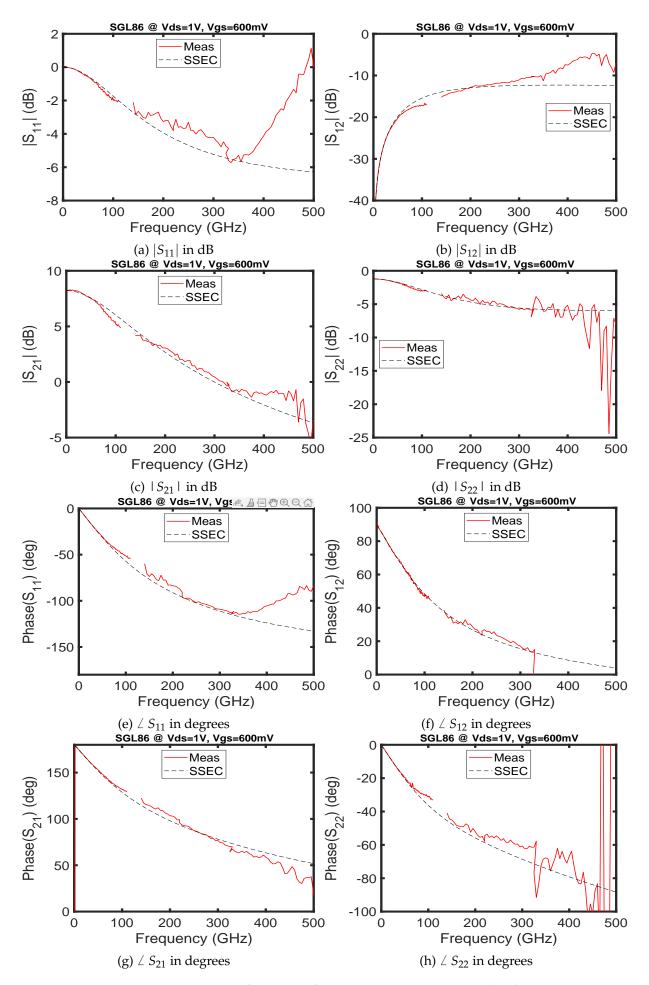

|       | S parameters of transistor from measurements compared to the SSEC                 | 50  |

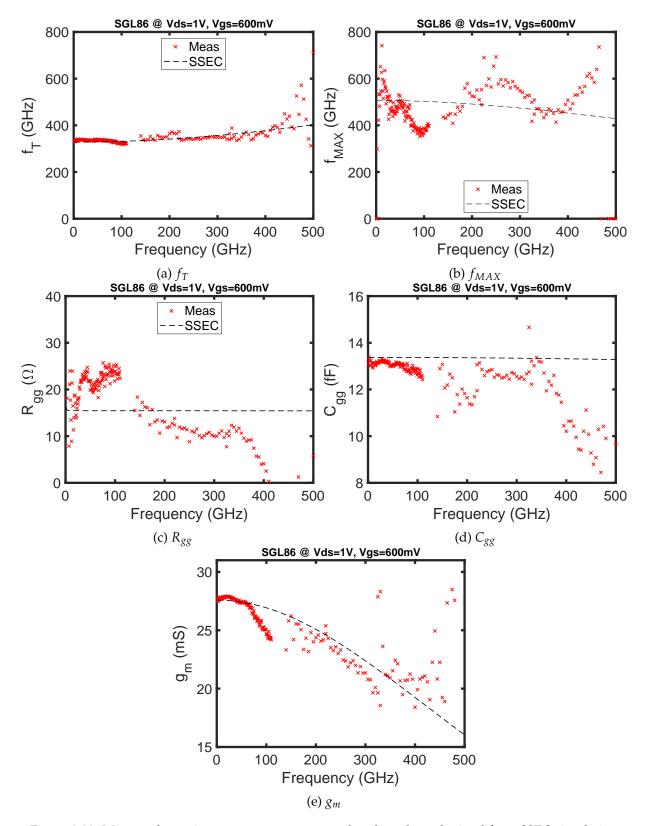

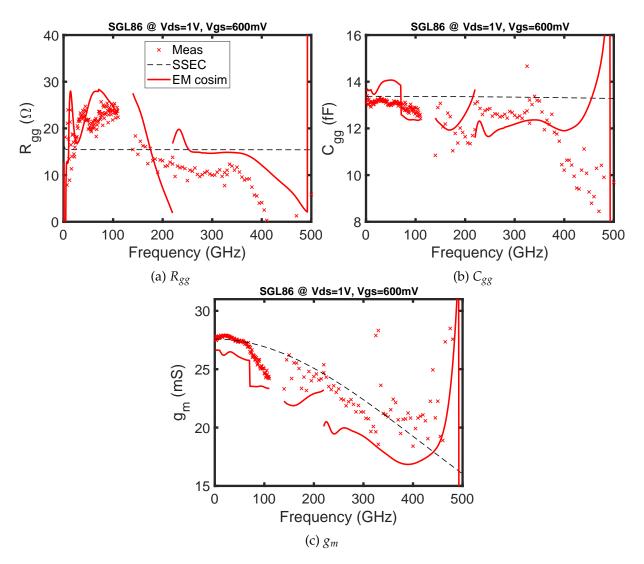

|       | Measured transistor parameters compared to the values obtained from SSEC          | 00  |

| 2.02  | simulation                                                                        | 51  |

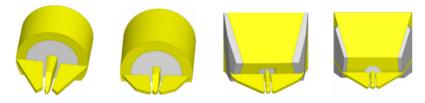

| 2.33  | 3D models of the picoprobe RF probes in each frequency band                       | 52  |

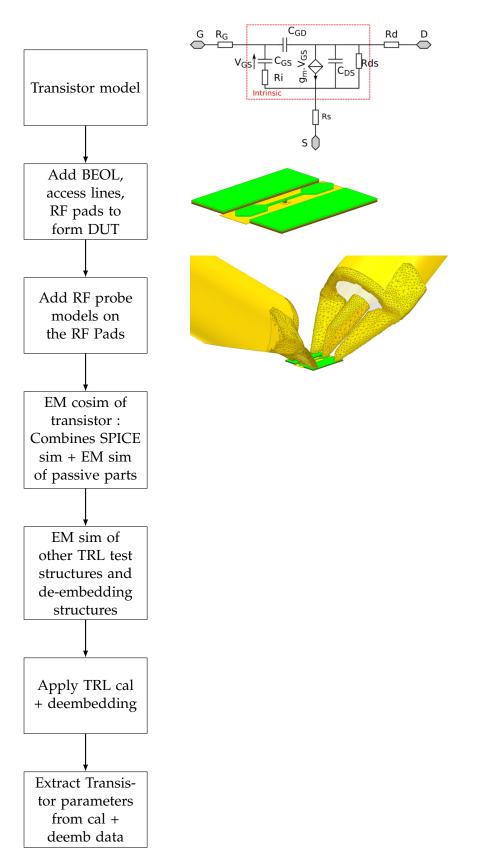

|       | Procedure followed for the EM co-simulation of transistor to simulate the TRL     | 0-  |

|       | calibration                                                                       | 53  |

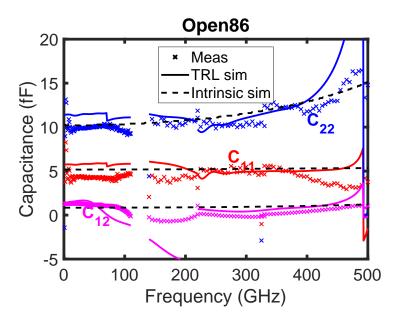

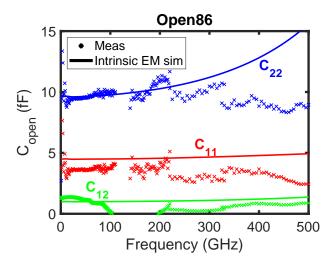

| 2.35  | Capacitances of Transistor Open extracted from EM simulation compared to the      | 00  |

|       | measurements                                                                      | 54  |

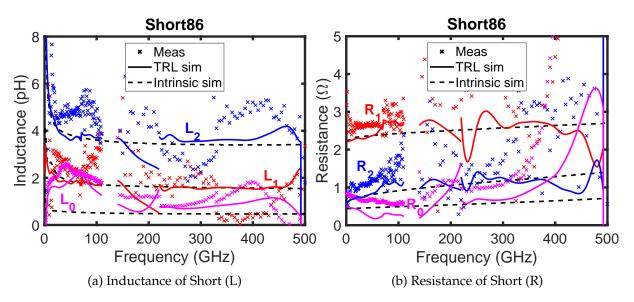

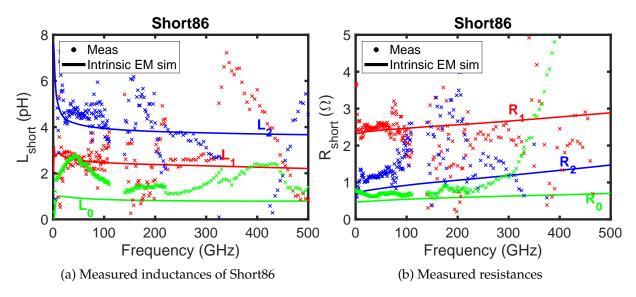

| 2.36  | Results of EM simulation of Transistor Short compared to the measurements         | 55  |

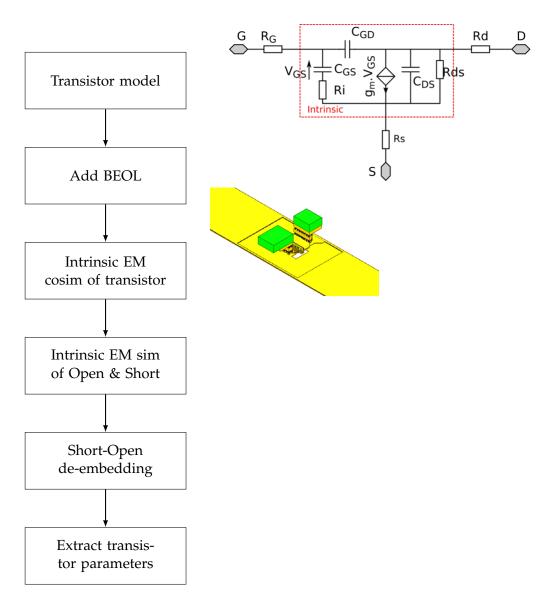

|       | Steps followed for Intrinsic EM Co-simulation                                     | 56  |

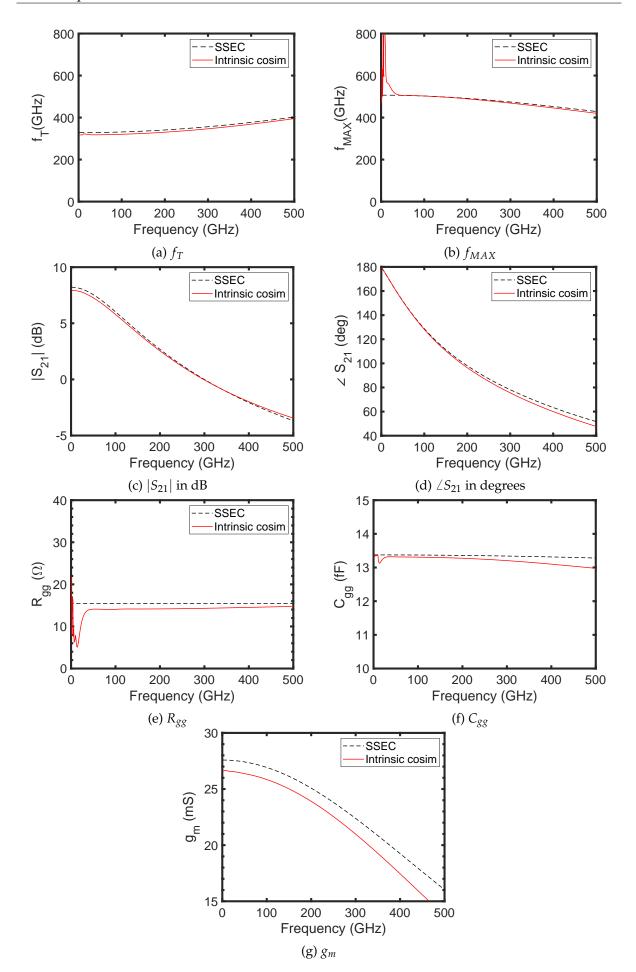

|       | Intrinsic cosimulation of transistor compared with the SSEC to demonstrate the    | 00  |

|       | validity of de-embedding                                                          | 57  |

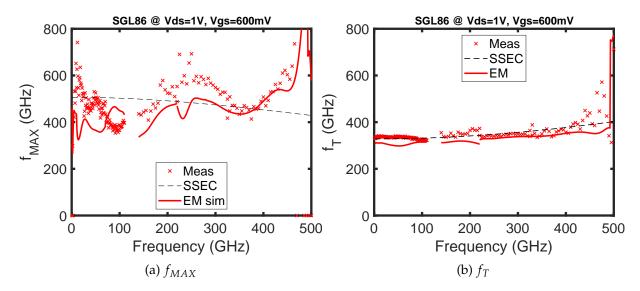

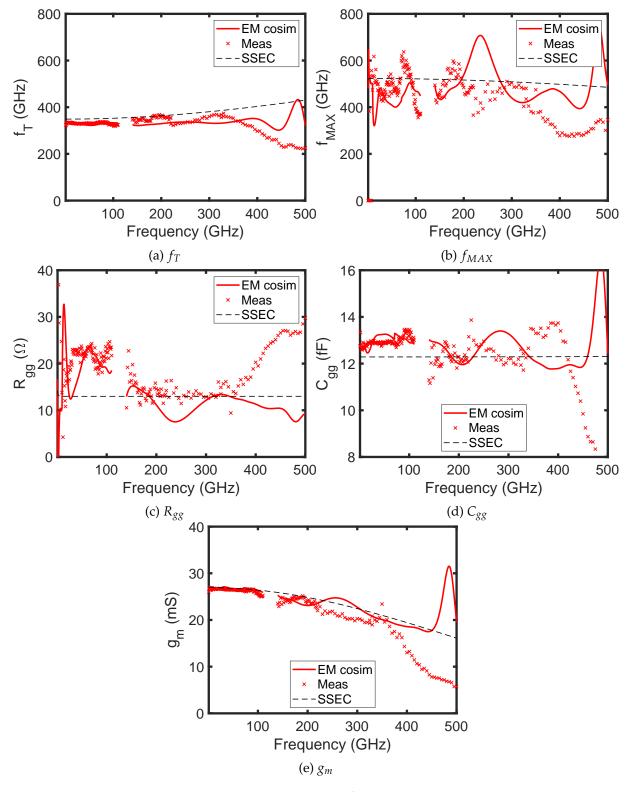

| 2.39  | Transistor RF FoMs from EM cosimulation of TRL calibration compared to the        |     |

| 2.07  | measurement results                                                               | 58  |

| 2.40  | Transistor parameters extracted from EM co-simulation and measurements            | 59  |

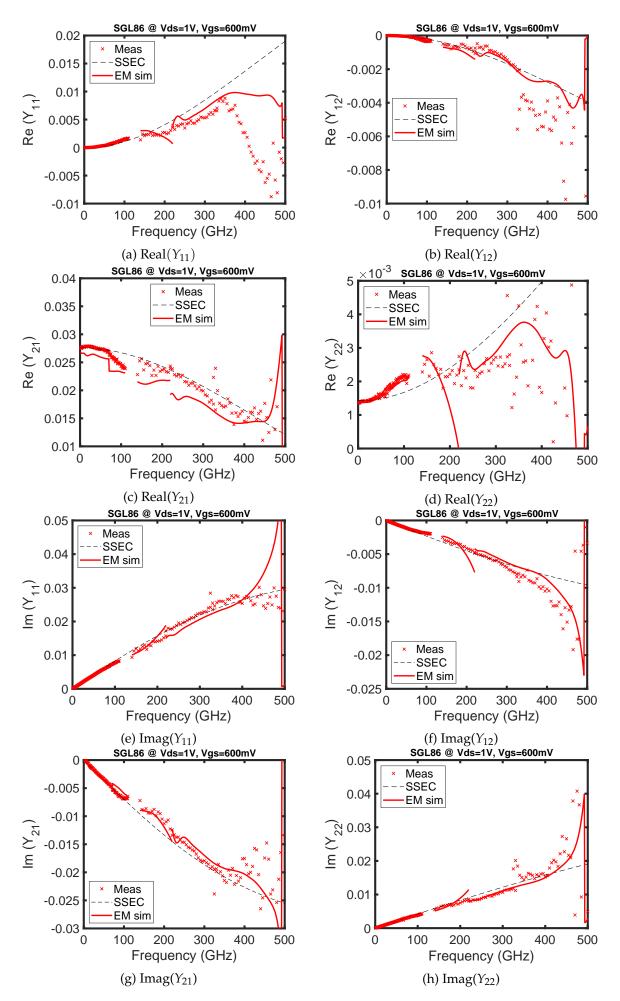

|       | Y parameters of transistor extracted from EM co-simulation and from measure-      | 0,2 |

|       | ments                                                                             | 60  |

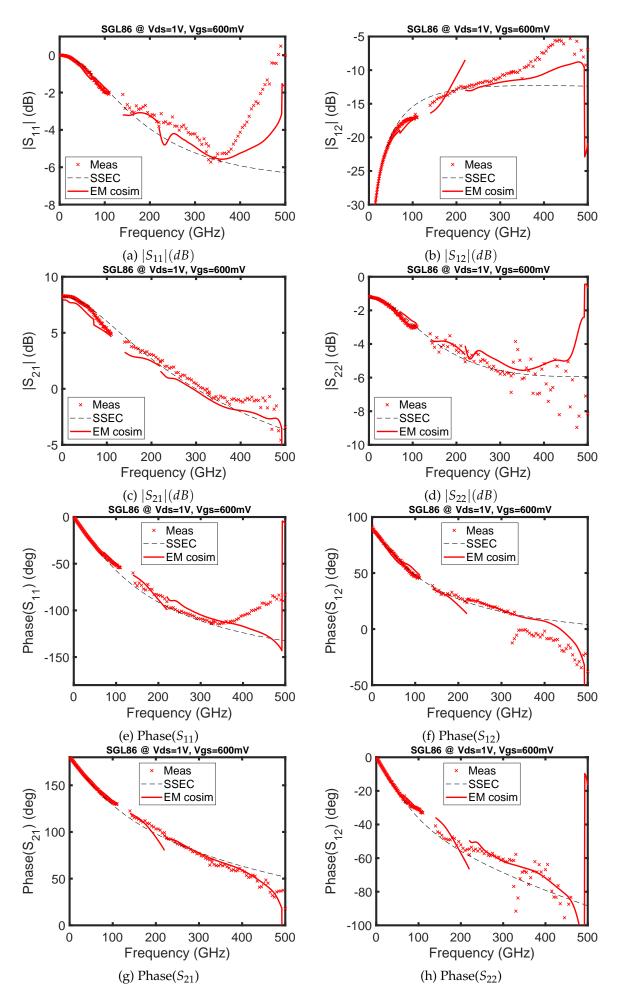

| 2.42  | S parameters of transistor extracted from EM co-simulation and from measure-      | 00  |

|       | ments                                                                             | 61  |

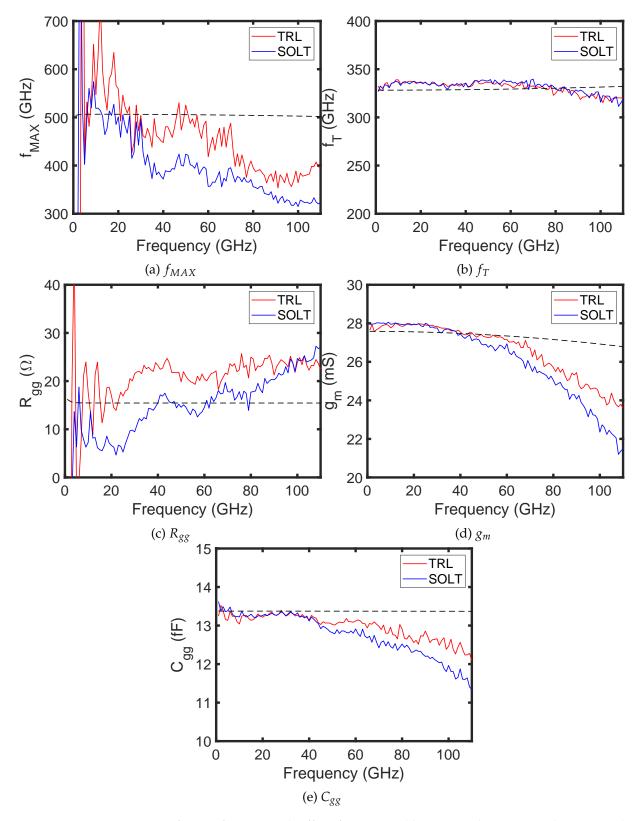

| 2.43  | Comparison of on-wafer TRL with off-wafer SOLT calibration with respect to the    | 01  |

| _, 10 | extracted transistor parameters (The parameters from the small signal model are   |     |

|       | represented using black dotted lines for reference)                               | 63  |

|       |                                                                                   | ~~  |

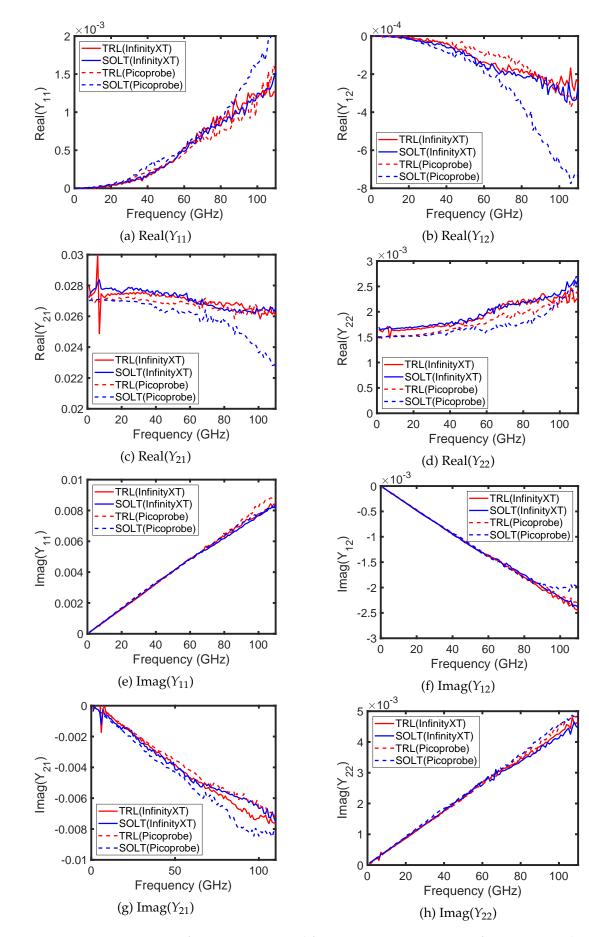

| 2.44  | Comparison of on-wafer TRL with off-wafer SOLT calibration with respect to the                                          |    |

|-------|-------------------------------------------------------------------------------------------------------------------------|----|

|       | Y parameters of the transistor                                                                                          | 64 |

| 2.45  | Capacitances of Transistor Open extracted from measurements using different RF probes and different calibration methods | 65 |

| 2.46  | 1                                                                                                                       | 66 |

|       | Inductances and resistances of Transistor Short extracted from measurements                                             |    |

|       |                                                                                                                         | 67 |

| 2.48  | $S_{21}$ of transistor after calibration & de-embedding using different RF probes and                                   | 68 |

| 2.49  | Transistor Parameters extracted from measurements using different RF probes                                             | 69 |

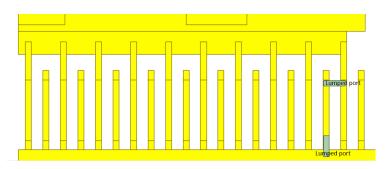

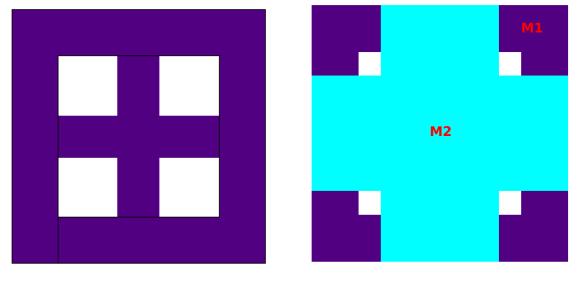

| 3.1   | Layout of Block1 (only top metal is presented)                                                                          | 75 |

| 3.2   | Layout of THRU showing the dummies (the orange color represents the top                                                 | 15 |

| 5.2   |                                                                                                                         | 75 |

| 3.3   |                                                                                                                         | 76 |

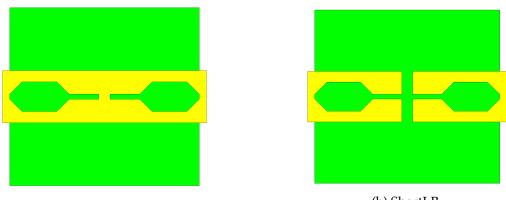

| 3.4   | · ·                                                                                                                     | 77 |

| 3.5   |                                                                                                                         | 77 |

| 3.6   |                                                                                                                         | 77 |

| 3.7   | 0 1                                                                                                                     | 78 |

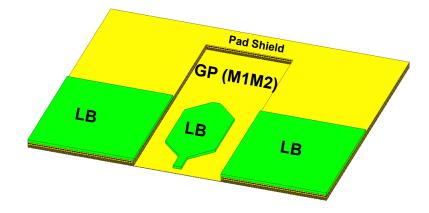

| 3.8   | Cross-sectional view of the Pad Shield around RF pad in Block 4 (green: LB layer,                                       | 70 |

| 5.0   | · · ·                                                                                                                   | 79 |

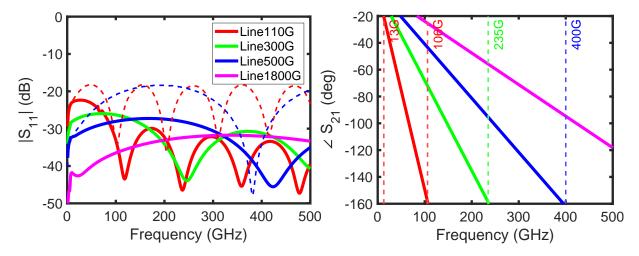

| 3.9   |                                                                                                                         | 80 |

|       |                                                                                                                         | 80 |

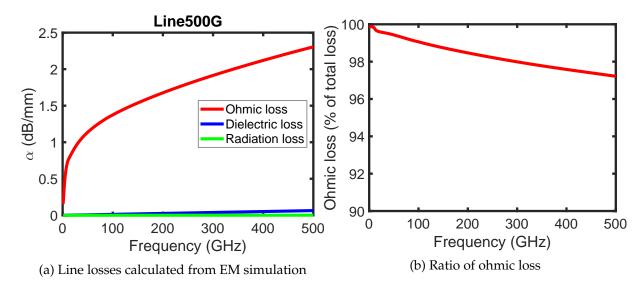

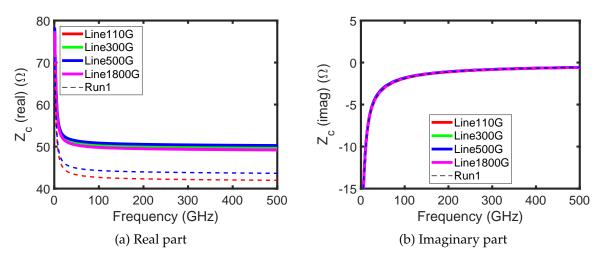

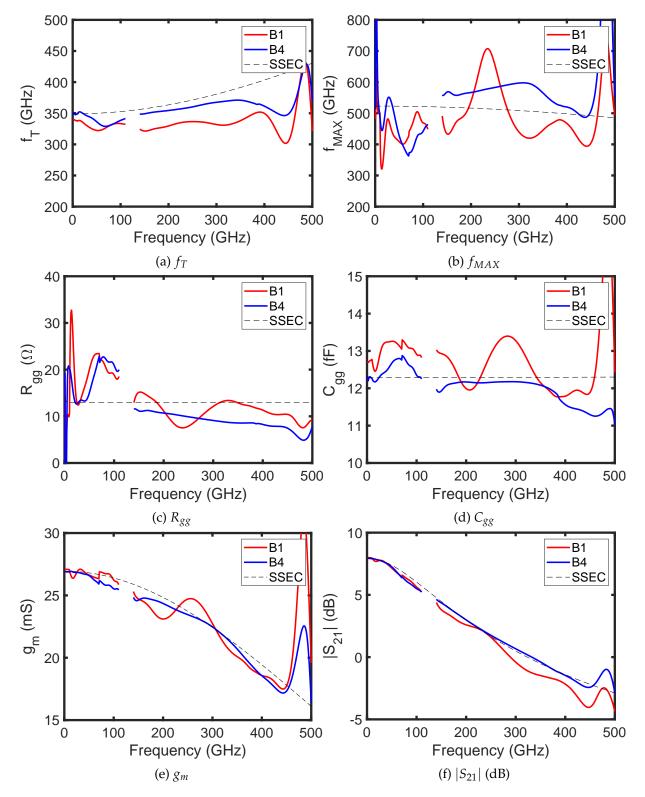

|       | Propagation constant of Lines in Run2 (Run1 lines are shown using dashed lines                                          | 00 |

| 5.11  |                                                                                                                         | 80 |

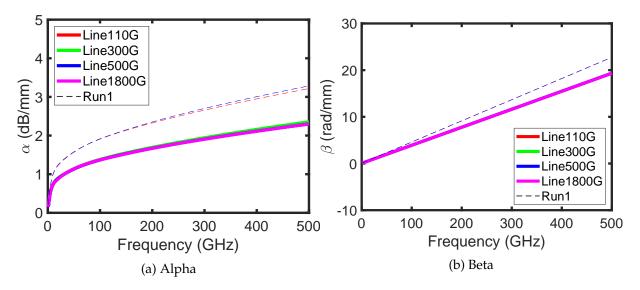

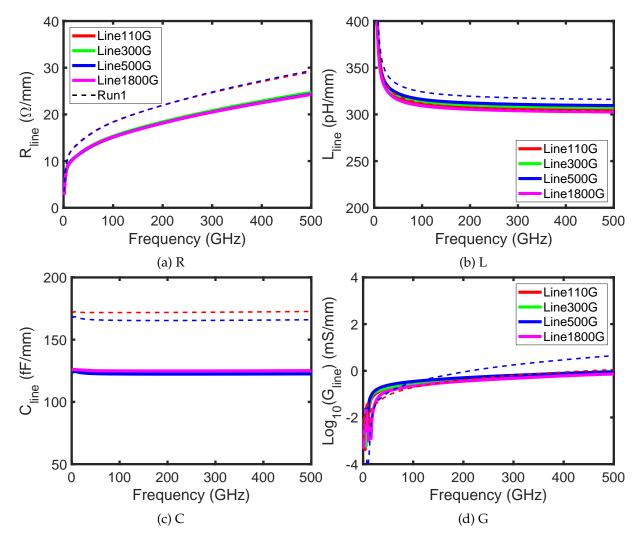

| 312   | RLCG parameters of Line used in Run2 (values from Run1 are plotted with                                                 | 00 |

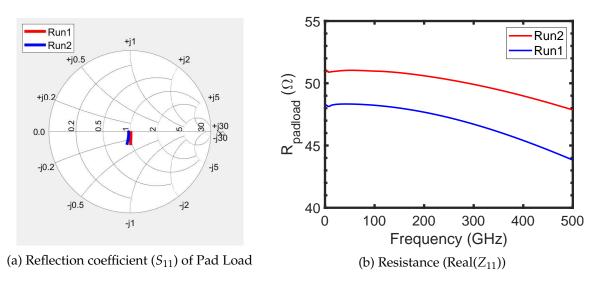

| 5.12  |                                                                                                                         | 81 |

| 3 1 3 |                                                                                                                         | 82 |

|       | 5 I                                                                                                                     | 83 |

|       | -                                                                                                                       | 84 |

|       |                                                                                                                         | 85 |

|       |                                                                                                                         | 85 |

|       |                                                                                                                         | 86 |

|       |                                                                                                                         | 87 |

|       | 1 1                                                                                                                     | 87 |

|       |                                                                                                                         | 87 |

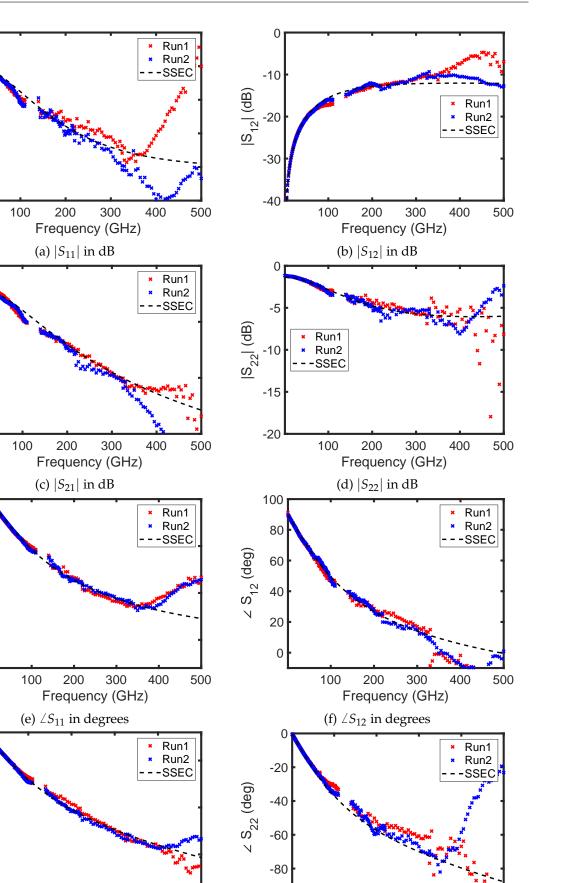

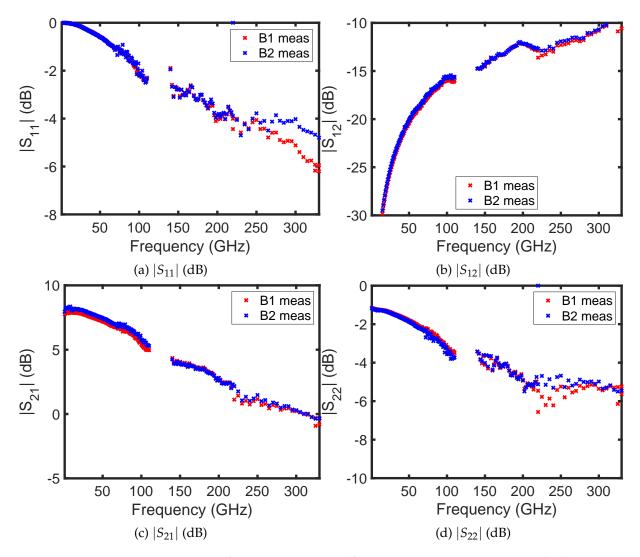

|       | S parameters of transistor extracted from measurements on Run2 compared to                                              | 01 |

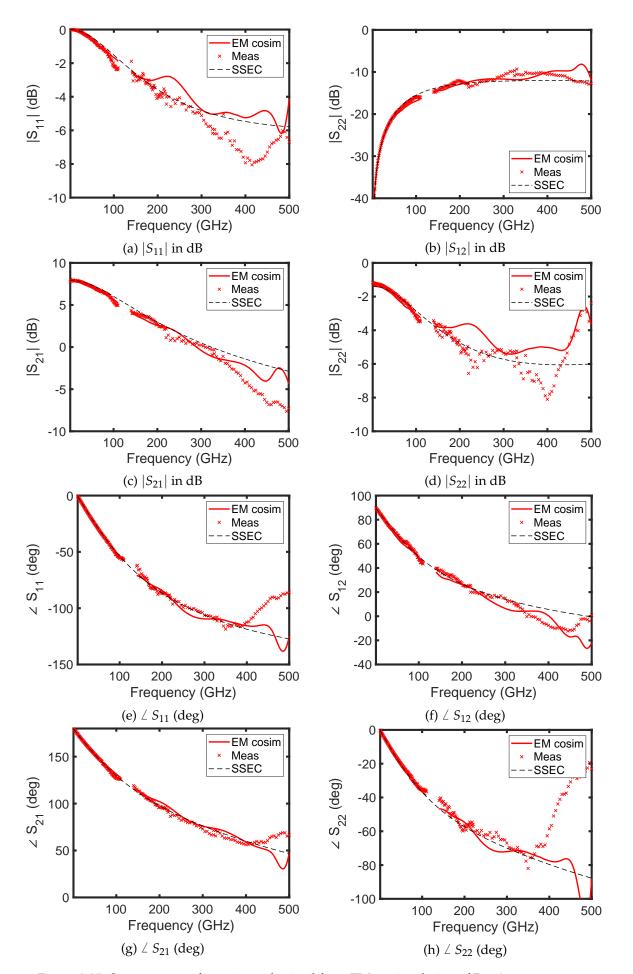

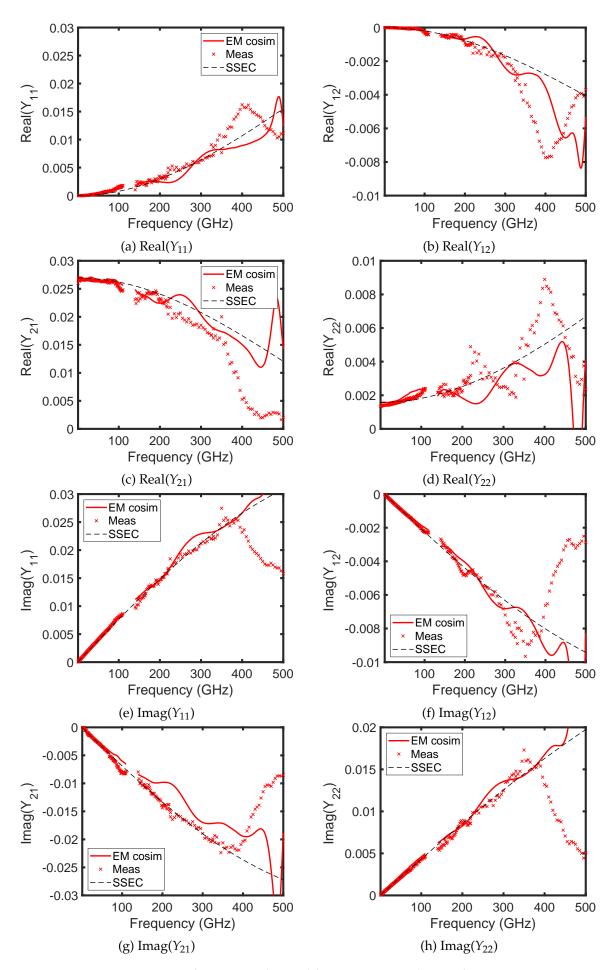

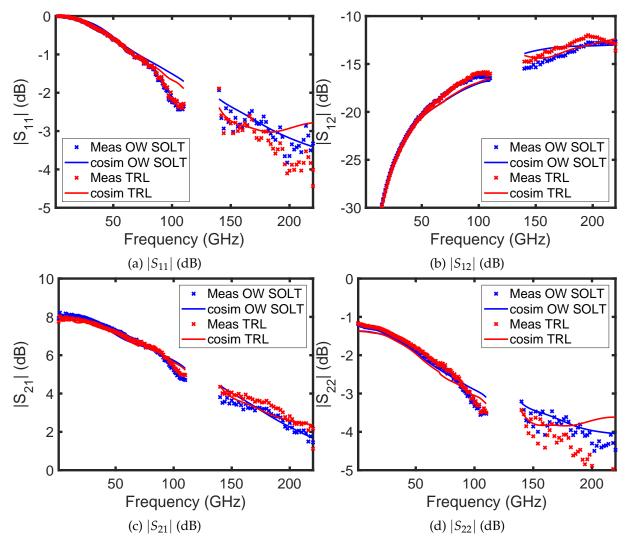

| 0.22  |                                                                                                                         | 89 |

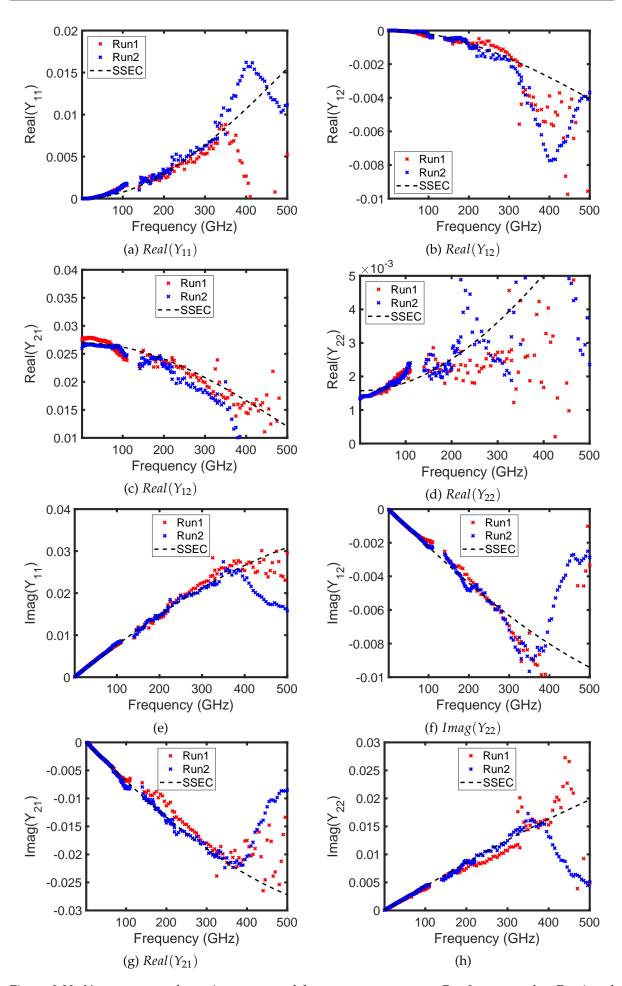

| 2 72  | Y parameters of transistor extracted from measurements on Run2 compared to                                              | 0) |

| 0.20  |                                                                                                                         | 90 |

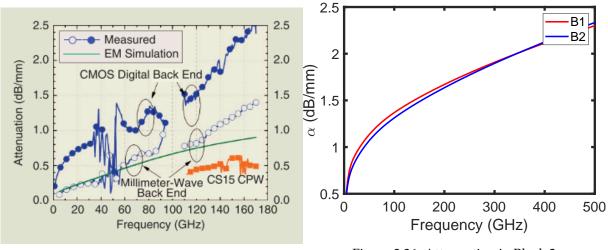

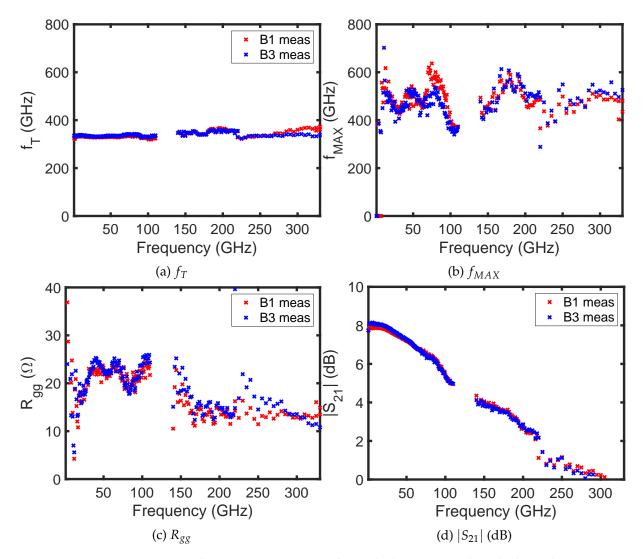

| 3 24  |                                                                                                                         | 92 |

|       | 1                                                                                                                       | 93 |

|       |                                                                                                                         | 94 |

|       | •                                                                                                                       | 95 |

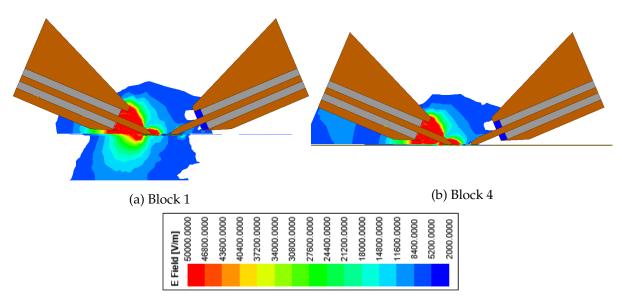

|       | Electric field distribution in Pad Open at 70 GHz when simulated with different                                         | // |

| 0.20  | 1                                                                                                                       | 95 |

| 3 29  | 1                                                                                                                       | 96 |

|       |                                                                                                                         | 97 |

|       |                                                                                                                         | 98 |

| 0.01  | Lin co simulation whither probes. I parameters                                                                          | 20 |

| 3.32 | Transistor parameters extracted using on-wafer SOLT calibration                        | 100 |

|------|----------------------------------------------------------------------------------------|-----|

| 3.33 | On-wafer SOLT: S parameters                                                            | 101 |

| 3.34 | On-wafer SOLT: Y parameters                                                            | 102 |

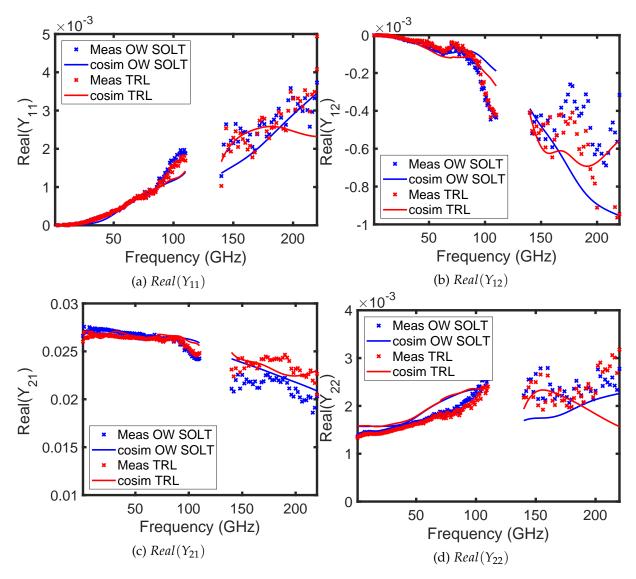

| 3.35 | Attenuation in the lines fabricated using different technologies (reproduced from      |     |

|      | [81])                                                                                  | 104 |

| 3.36 | Attenuation in Block 2 microstrip line obtained from EM simulation (B1 values          |     |

|      | for reference)                                                                         | 104 |

| 3.37 | Transistor parameters extracted from TRL measurements using Block 2                    | 105 |

|      | S-parameters of transistor extracted from TRL measurements using Block 2               | 106 |

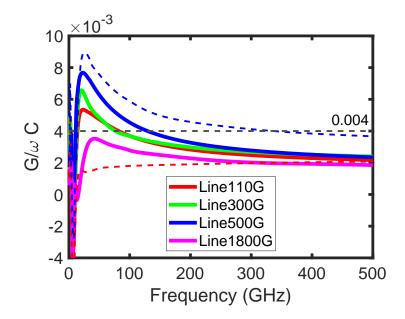

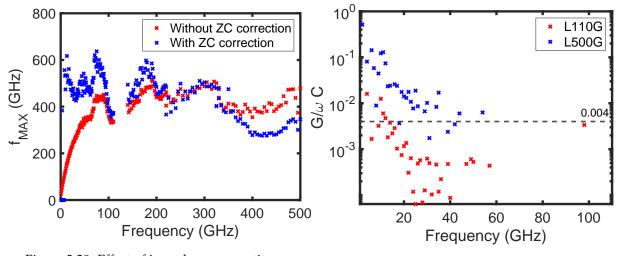

| 3.39 | Effect of impedance correction on extracted $f_{MAX}$                                  | 107 |

|      | Measured value of $G/\omega C$ for the different lines in Block 1                      | 107 |

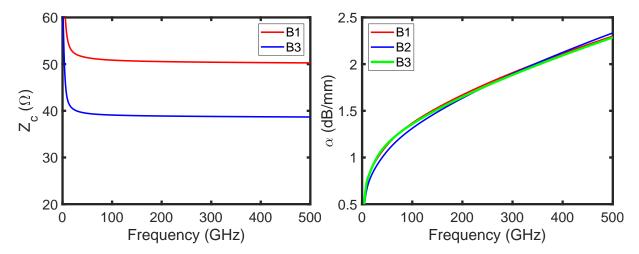

| 3.41 | Characteristic impedance of the lines from Block 3                                     | 108 |

| 3.42 | Attenuation (simulated) in Line_500G from Block 3 as compared to the other             |     |

|      | blocks                                                                                 | 108 |

| 3.43 | Measured transistor parameters from Block 3 compared to Block 1 values                 | 108 |

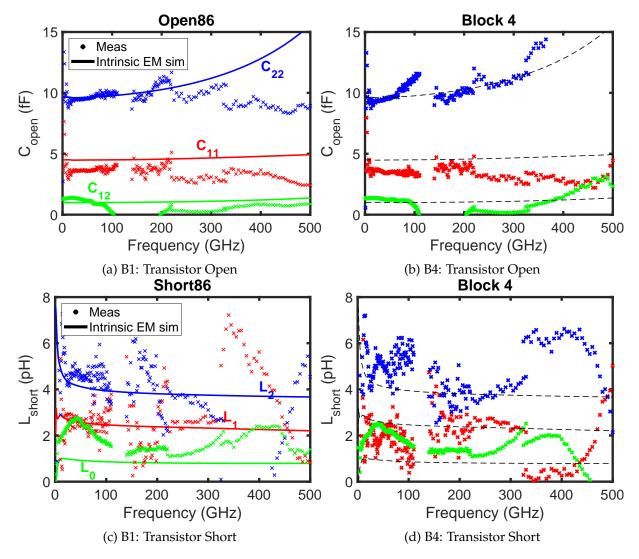

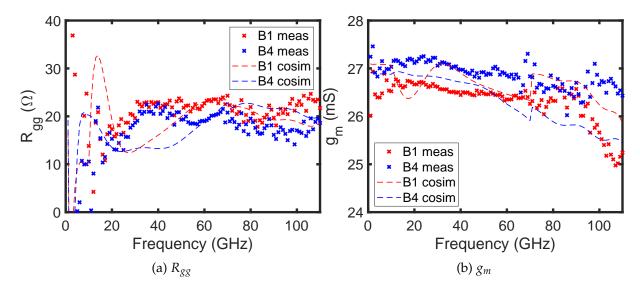

| 3.44 | Comparison of parasitics of Open & Short measured on B1 and B4                         | 110 |

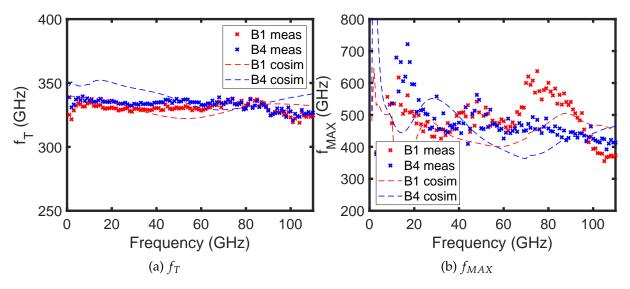

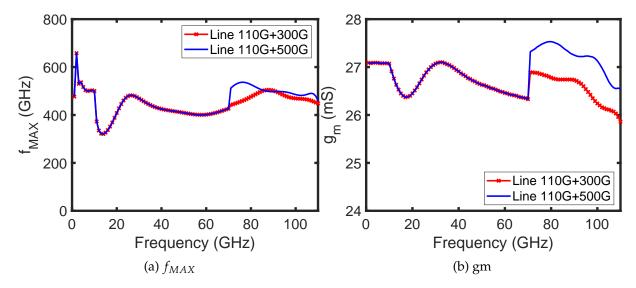

| 3.45 | RF FoMs of transistor from Blocks 1 and 4                                              | 110 |

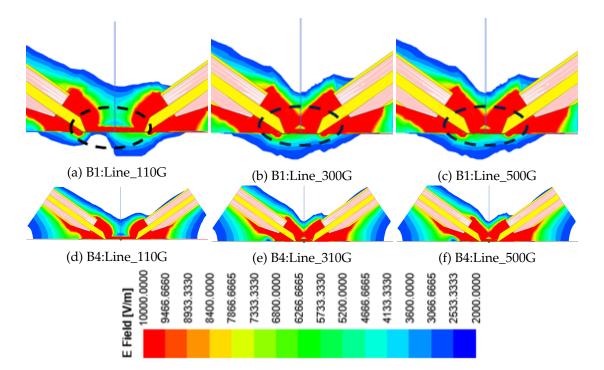

| 3.46 | EM field distribution in the lines at 70 GHz for Block 1 (a to c, without continuous   |     |

|      | ground plane) and Block 4 (d to f, with continuous ground plane)                       | 111 |

| 3.47 | Gate resistance and transconductance of transistor from Blocks 1 and 4                 | 112 |

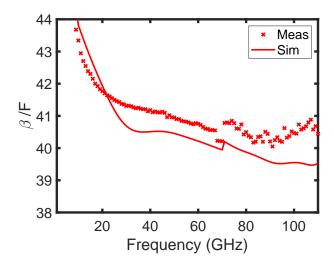

| 3.48 | Normalized Beta extracted from on-wafer TRL calibration on Block1 (measure-            |     |

|      | ment and co-simulation                                                                 | 112 |

| 3.49 | Normalized Beta of each LINE in Block1 after on-wafer TRL calibration (co-             |     |

|      | simulation)                                                                            | 112 |

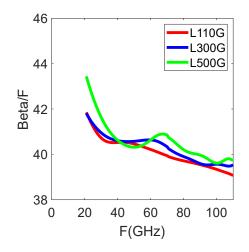

| 3.50 | $f_{MAX}$ and $g_m$ of transistor extracted from TRL calibration (EM simulation) using |     |

|      | different lines after 70 GHz in Block1                                                 | 113 |

| 3.51 | Comparison of transistor parameters from Block 1 (no continuous ground) and            |     |

|      | Block 4 (with continuous ground plane)                                                 |     |

|      | Electric field distribution in Pad Open at 300 GHz                                     |     |

|      | InfinityXT RF Probe                                                                    |     |

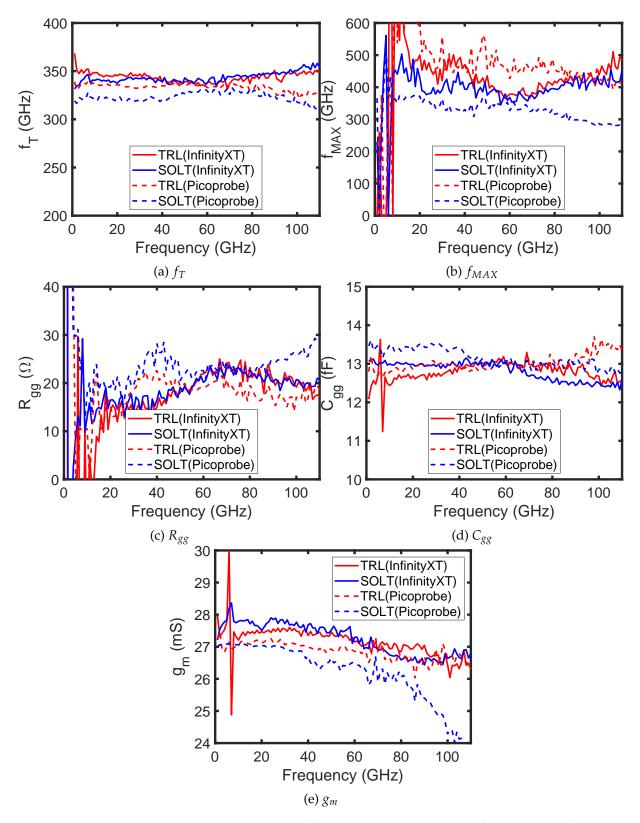

|      | Transistor parameters extracted from measurements using InfinityXT RF probes           | 117 |

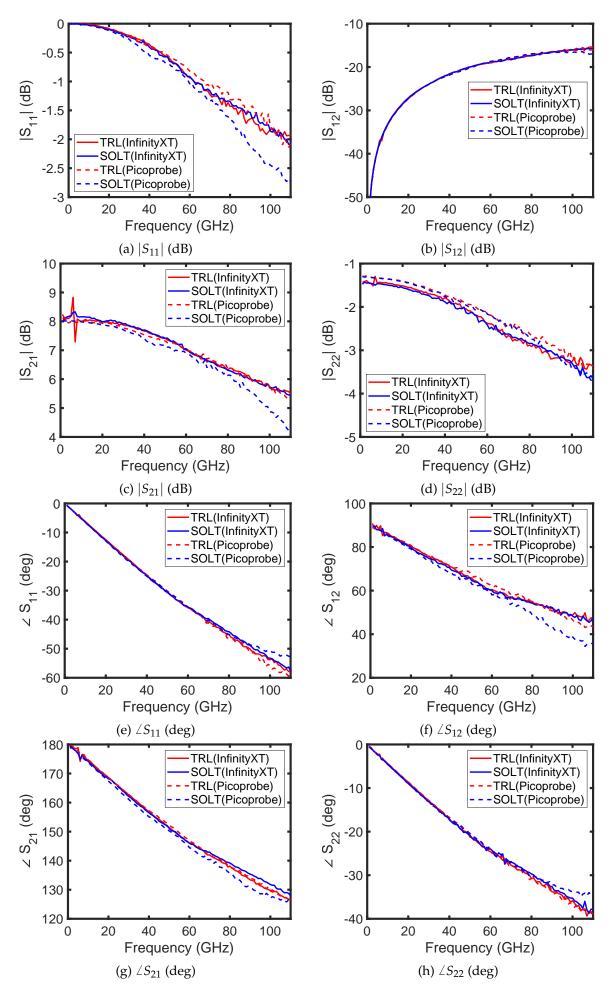

|      | S-parameters of transistor measured using InfinityXT RF probes                         | 118 |

| 3.56 | Y parameters of transistor extracted from measurements using InfinityXT RF             |     |

|      | probes                                                                                 | 119 |

|      |                                                                                        |     |

xii

# List of Tables

| 1.1 | Comparison of FoM of different technologies                                                                                                                     | 7  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Specifications of VNA                                                                                                                                           |    |

| 1.3 | Specifications of Frequency Extenders Used for Measurements                                                                                                     | 12 |

| 1.4 | Comparison of RF Probes                                                                                                                                         | 13 |

| 1.5 | Review of calibration lines realized for the on-wafer calibration structures to use with TRL method, * Inter-probe distance is taken from the middle of the pad |    |

|     | port 1 to the middle of the pad port 2.2 Distance is taken from pad (external                                                                                   |    |

|     | part) structure 1 to pad structure 2 and is defined thanks to a vector, table taken from [79]                                                                   | 25 |

| 2.1 | Frequency limits of the TRL Line standards                                                                                                                      | 34 |

| 2.2 | Transistor geometries on the wafer                                                                                                                              | 35 |

| 2.3 | SSEC parameter values                                                                                                                                           | 49 |

| 3.1 | Specifications of lines used for TRL calibration in Run2                                                                                                        | 76 |

| 3.2 | SSEC parameters from Run2                                                                                                                                       |    |

## **General Introduction**

This thesis aims to establish a high-frequency characterization methodology for advanced MOS transistors, specifically those of the FD-SOI technology from STMicroelectronics. The final goal is to use these characterization results for electrical compact modelling, allowing for precise predictions of electronic system characteristics in the THz frequency range.

#### Thesis context

Silicon bipolar and CMOS technologies have been recognized for their abilities in millimeterwave applications, making them good candidates for circuit realization in the THz domain [1]. Among them, the "Fully-Depleted-Silicon-On-Insulator" (FD-SOI) technologies developed from the 28nm node [2] offer promising performances for transition frequencies ( $f_T$ ) and maximum oscillation frequencies ( $f_{MAX}$ ) beyond 300 GHz [3], and even more for the most advanced nodes [4] [5]. At the same time, the development of millimeter-wave circuits is booming, with realizations at ever higher frequencies, some of which go beyond 100 GHz [6] [7] [8].

To enable the design of circuits operating at millimeter-wave frequencies, an accurate modeling of FD-SOI transistors is essential. The first step has been taken with the development of compact models that can reproduce transistor characteristics in all operating regimes. These models have been validated for RF and millimeter-wave applications, but further development and validation are needed for frequencies beyond 100 GHz to support emerging applications at these frequencies. The main objective of this thesis is to provide reliable measurements in these frequency bands to fulfill this need.

Figure 1: NIST (National Institute of Standards and Technologies, USA) measurement of (a) the phase measurement and EM simulation of an open and a short, and (b) the S-parameter magnitude measurement of a transistor up to 750 GHz. [9]

Currently, the THz domain is seen as a new scientific El Dorado and remains largely unexplored. For several decades, the Sub-THz part of the spectrum (100 GHz to 500 GHz) has only

been used in niche applications and fundamental research. The availability of new semiconductor technologies such as FD-SOI offering components operating close to THz now allows approaching mass markets in areas such as:

- very high-speed and short-distance wireless communications,

- security and anti-collision automotive radars,

- medical and pharmaceutical biology as well as high-resolution imaging.

Currently, "classical" S-parameter measurements are limited to frequencies below 110 GHz, which is insufficient for validating electrical compact models necessary for the design of Sub-THz circuits and systems. Up to 110 GHz, various calibration and de-embedding methods (removal of parasitic elements surrounding the transistor) have been widely studied and published by the scientific community and no longer present major difficulties [10] [11] [12]. However, only few laboratories are equipped with measurement benches up to 220 GHz, or even 325 GHz. Work on the analysis of these measurements is rare [13], and there remain large uncertainties and a need for validation of these measurements through electromagnetic simulation, in particular. Indeed, measurements beyond 110 GHz are performed in multiple bands, each band requiring the use of different millimeter probes and heads. Thus, combining each measurement can introduce discontinuities, as illustrated in Figure 1 (excerpt from [9]). To mitigate these discontinuities, it is possible to use a dedicated calibration kit using inverted microstrip lines, gold contacts, and a dielectric suitable for high frequencies such as benzocyclobutene (BCB). Despite the precautions taken and the experience of the experimenters, the discontinuities remain significant for various reasons:

- calibration error due to poor probe placement, both in terms of contact quality [14] and X or Y position error [15],

- different coupling between the probe and the substrate in each band because each probe has a different geometry [16],

- impact of coupling with neighboring structures [15],

- drift of the measuring instrument during the characterization campaign,

- limitation of the TRL calibration method, which does not take into account cross-talk [17] and which, moreover, varies depending on the probe geometry.

#### Work Description

The description of the thesis project is part of the ongoing research activities carried out by the MODEL team of IMS for many years. The focus of this research is on the development of high-frequency characterization techniques [18] [19] [20] and compact modeling of transistors [21]. It also aligns with the crucial objective of increasing frequency and IMS's participation in the European H2020 projects. The research presented herein is based on state-of-the-art equipment, thanks to the significant investment made by IMS in 2015 and 2018 (>700,000 €) as part of the regional projects SUBTILE and FAST. Moreover, these research activities are carried out in collaboration with STMicroelectronics within the IMS/ST joint laboratory.

The characterization work aims to develop methods for measuring "on-wafer" S-parameters up to 500 GHz, using the measurement bench shown in Figure 2. To make the measurements

Figure 2: Measurement bench of the NANOCOM platform, operating up to 500 GHz.

repeatable and usable for industry, especially for compact modeling of devices, the main challenges are:

- mastering the quality of the contact between the measurement probe and the aluminium contact pad;

- positioning the measurement reference plane as close as possible to the intrinsic region of the transistor;

- quantifying the measurement uncertainty associated with probe positioning errors;

- mitigating the impact of adjacent structures, whose influence increases with frequency [15];

- better understanding and mitigating the signature of parasitic couplings between the probes and the environment of the measured device.

Although some aspects of the research have already been explored and have produced results [15] [20] [22] [23], it is necessary to deepen the ongoing analyses in order to clarify the measurement methodologies and design rules for the test structures to be implemented. Thus, the research work aims to provide answers to essential points in an industrial characterization context, such as:

- the optimal design of test structures to mitigate (or minimize) the effect of probes on the measurement of transistors,

- the benefits of using thick metals and/or large inter-metal thicknesses for test structures, or highly resistive substrates,

- the need (or not) to perform silicon calibration for each measured chip,

- the possibility of eliminating the de-embedding step by using a calibration method that brings the reference planes close to the transistors,

To attain these objectives, a number of topics are addressed during the thesis which are described in detail in three chapters. The chapters are briefly described below.

After a short introduction to the MOS transistors on 28 FD-SOI technology from STMicroelectronics, the first chapter is mainly dedicated to the challenges of RF measurements. First, the available hardware is described including the probe stations and the measurements benches for the four different frequency bands. A focus is given on the probe tips which are different for each frequency band and thus may introduce frequency band specific coupling. Second, the pros and cons of two standard calibration methods (SOLT and TRL) are discussed. Moreover, on-wafer calibration is compared to off-wafer calibration. For on-wafer calibration, TRL is the method of choice. But applying TRL on-wafer calibration implies the need for impedance correction. This topic is also described. In a third part, the different de-embedding procedures are reviewed. In the fourth section, an innovative concept based on electromagnetic simulation is introduced. Indeed, EM simulation allows us to decouple proven phenomena from measurement uncertainties and therefore better understand the effects at play. The simulation methodology used takes into account a part of the measurement system, at least up to the probes, and will clarify one by one each of the points mentioned above, while eliminating the uncertainty associated with the measurement. The first chapter ends with a state-of-the-art section on calibration procedures and de-embedding methodologies of RF transistors in the millimeter wave and sub-millimeter wave frequency ranges.

The second chapter is dedicated to the characterization and EM simulation of the "Run1" test-structures. Indeed, during the thesis work two different Si-hardware with different test-structures have been characterized and designed whereas the design concerns only the second "Run". After a detailed description of the test-structures including layout and cross-section analysis, the intrinsic EM simulation of the test-structures is presented. The issues of the presence of the dummies near the lines is analyzed and its impact on the characteristic impedance investigated. Then, the transistor measurements (DC and RF) are presented. This part is followed by the description of the small-signal equivalent circuit and the extraction procedure of the associated model parameters. A comparison of the small-signal simulation results with respect to measurements up to 500GHz is given. Afterwards, in order to assess possible measurement issues, a comparison of the measurement results are compared to measurements carried out with SOLT calibration. Finally, the effect of the RF probes used for measurement is examined. This chapter ends with an analysis of the drawbacks and limitations of "Run1".

The third chapter is dedicated to the design and analysis of the "Run2" test-structures. As concluded from the previous chapter, the existing "Run1" test structures for on-wafer TRL calibration possess several disadvantages. This has necessitated the development of improved test structures. In this chapter, we present different flavors for the design of the new TRL test structures that can overcome the difficulties encountered previously. Indeed, four different calibration kits have been designed and are explained in detail. To truly assess the intrinsic behavior of the test-structures, an EM simulation is carried out. Afterwards, the measurement results of the transistor are presented and compared to the full EM simulations using the RF probe models. This analysis is completed by adding a comparison with EM simulation with quasi-ideal probes. In order to overcome the inability of TRL to calibrate accurately in the presence of probe coupling (probe-to-probe together with probe-to-substrate), On-wafer SOLT calibration up to 220 GHz has been employed to further improve the accuracy of the calibration. Finally, a detailed comparison is made between the four differently designed calibration kits and the best-in-class kit is designated. The chapter ends with the presentation of very recent results obtained through the use of new probes having a very different probe geometry.

## Chapter 1

# **Background Theory and Literature Review**

#### 1.1 28FD-SOI

As devices are scaled down as per Moore's law, the traditional bulk transistors encounter several limitations, the most important one being the increase in leakage current resulting in higher power consumption [24]. Moreover, from the 40 nm technology node and below, the electrostatic control of the transistor channel becomes more difficult [3]. This has led to the advent of new transistor architectures and new materials that enable further scaling down. Fully Depleted Silicon On Insulator, or FD-SOI, is a planar process technology that is a variant of siliconon-insulator (SOI) technology [25]. The SOI wafer is fabricated using the Smart Cut process, the main steps of which are represented in Fig. 1.1. FD-SOI relies on two primary innovations. First, an ultra-thin layer of insulator, called the buried oxide, is positioned on top of the base silicon. Then, a very thin silicon film implements the transistor channel. As a result of the thin layer, there is no need to dope the channel, thus making the transistor Fully Depleted [26]. In the 28nm node, the transistor has an ultra thin conduction layer (7 nm) on top of a 25 nm insulation layer of buried oxide [7]. This technology is also called Ultra Thin Body and Box (UTBB).

Figure 1.2 shows a comparison of bulk transistor and FD-SOI transistor. In a traditional bulk CMOS transistor, the influence of source and drain junction diodes on the device electrostatic is such that the electrons can move from the source to drain even when the transistor is off,

Figure 1.1: Smart Cut process for fabrication of SOI wafer [27]

Figure 1.2: Bulk CMOS vs FD-SOI (Source: STMicroelectronics)

thereby resulting in a leakage current. In the FD-SOI transistor, most of this leakage is cancelled due to the thin conduction layer and the presence of the buried oxide layer (BOX). Indeed, as a result of the 7nm thickness, the SOI channel presents good Short Channel Effect (SCE) control that allows to decrease the physical gate length down to 24nm while keeping the same leakage as the bulk transistor with a longer gate length [2]. Other advantages of FD-SOI are total dielectric isolation, lower noise variability, and lower parasitic capacitance towards the substrate due to the BOX insulation. Moreover, very fast transistors are possible in this technology due to its deep sub-micron lithography [3].

Another important characteristic of the FD-SOI technology is the possibility of Body Biasing. This is an effective feature that can control the threshold voltage ( $V_t$ ) of the transistor. This is made possible by polarizing the substrate situated below the device. This is similar to the body bias in bulk technologies, the difference being that the threshold voltage variation is limited to a few tens of millivolts in bulk devices, due to the inevitable junction diodes, whereas it can be much larger in FD-SOI. Two types of transistors are available based on their  $V_t$  [28][3],

- RVT are the regular *V<sub>t</sub>* or standard *V<sub>t</sub>* devices. Here *V<sub>t</sub>* modulation through body biasing is possible by applying reverse body biasing (RBB), with the effective magnitude of biasing voltage ranging between 0 and 3V.

- LVT are the low V<sub>t</sub> devices. They are also known as "flipped well" devices, because the NMOS devices lay on a N-type well and PMOS devices lay on a P-type well, which reduces their threshold voltage by roughly 80 mV compared to RVT ones. LVT devices support forward body biasing (FBB) to control the V<sub>t</sub>, with an effective body voltage variation of approximately 0 to 3 V. FBB has the advantage of lowering the V<sub>t</sub>, that enables the transistor to be switched faster. Therefore, LVT devices are used in the design of high speed circuits such as in digital applications for High-Speed Flip-Flops [28].

- Remark: Both body biasing options (RBB and FBB) are available in theory for both flavours (RVT and LVT). The limitation of the biasing range is due to the junction diodes of the wells.

FDSOI transistors obey the same equations as bulk MOSFETs. In strong inversion, the drain current  $I_D$  is [27],

$$I_D = \frac{\mu_{eff} C_{ox} W}{L} \cdot \left( V_{FG} - V_{TF} - \frac{n V_D}{2} \right) V_D \tag{1.1}$$

where,

|                   | $f_T(GHz)$ | $f_{MAX}(GHz)$ |

|-------------------|------------|----------------|

|                   |            | •              |

| 28nm FDSOI [29]   | 310        | 330            |

| 22nm FDSOI [30]   | 332        | 435            |

| 22FFL FinFET [31] | 300        | 450            |

| 28nm HKMG [32]    | 310        | 161            |

| 55nm BiCMOS [33]  | 326        | 375            |

|                   |            |                |

Table 1.1: Comparison of FoM of different technologies

$V_{FG}$  is front gate voltage  $V_D$  is drain voltage  $V_{TF}$  is front channel threshold voltage  $\mu_{eff}$  is effective mobility n is body factor L is effective value of channel length W is effective value of channel width  $C_{ox}$  is the gate-oxide capacitance

At saturation,  $V_D \ge V_{Dsat}$ , then

$$I_{D_{sat}} = \frac{\mu_{eff} C_{ox} W}{L} \cdot \frac{\left(V_{FG} - V_{TF}\right)^2}{2n}, \quad \text{where} \quad V_{Dsat} = \frac{V_{FG} - V_{TF}}{n}$$

(1.2)

In the linear region of operation, equation 1.1 becomes,

$$I_D = \frac{\mu_{eff} C_{ox} W V_D}{L} \cdot (V_{FG} - V_{TF})$$

(1.3)

In subthreshold and linear regions, the current varies exponentially as:

$$I_D = I_0 \exp\left(\frac{q(V_{FG} - V_{TF})}{nkT}\right) = I_0 \exp\left(\frac{2.3(V_{FG} - V_{TF})}{SS}\right)$$

Subthreshold Swing,  $SS = 2.3n(kT/q)$  (1.4)

This work is based on the 28nm FD-SOI technology of STMicroelectronics. This technology enables fast switching in the LVT configuration with FBB. These have a maximum reported values of  $f_T/f_{MAX}$  of 310/330 GHz [29] and find several applications in the RF and millimetre wave frequencies. Table 1.1 makes a comparison of 28 FD-SOI technology with other technology devices in terms of its RF Figure of Merits (FoM).

#### **1.2 RF Measurements**

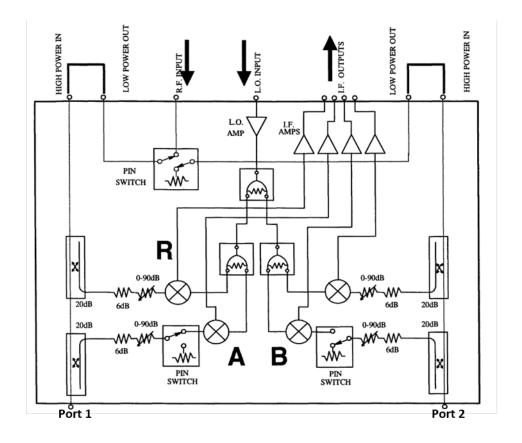

Before digging deeper in the RF measurements domain, a succint review of the basics is presented. RF measurements involve determining the S-parameters of an RF device. This is realised using a Network Analyzer (NWA), also known as Vector Network Analyzer (VNA), which works by measuring the magnitude and phase of the transmitted and reflected power at two ports. A VNA mainly consists of an RF synthesizer, an S-parameter test-set and control and display units. The signal from the synthesizer is fed to the test-set which acquires the incident and reflected power at the Device Under Test (DUT) at both ports. The block diagram of the S-parameter test-set is represented in Fig. 1.3 [34]. The test-set has an RF input receiving signal from the RF synthesizer and a PIN switch that directs the signal to forward or reverse directions. R represents the reference signal, in forward mode (RF input switched to port 1), A the reflected signal at port 1 and B the signal transmitted from port 1 to port 2, where as in reverse mode mode (RF input switched to port 2), B the reflected signal at port 2 and A the signal transmitted from port 2 to port 1. Within the test-set, there are also directional couplers to detect the incident and reflected waves at the DUT. These detected signals are further analyzed by downconverting it to IF signals.

The S-parameter test-set can be of two types: 3-sampler or 4-sampler. Ina 3-sampler VNA, the reflected signal is coupled out before the switch and hence the switching errors are not considered in the calibration. An additional correction step is necessary to account for the switching error. For this, specific measurements are necessary (incident and reflected powers to port 1 and 2). On the other hand, in a 4-sampler VNA, the switching error is eliminated due to the architecture of the test-set. It allows a better calibration , since the reference signals R are taken after the switch. This is significant for frequencies above ~20 GHz [34]. The block diagram in Fig. 1.3 represents a test-set including 4-samplers.

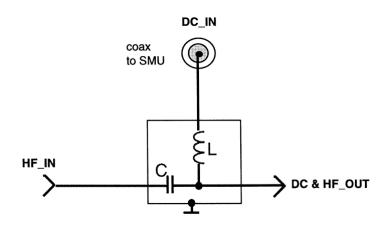

In addition to these, VNAs also include bias TEEs, which set the operating point for the measurement of active components. Bias TEEs are composed of an inductor and a capacitor as shown in Fig. 1.4 [34].

#### 1.3 Measurement setups

In this work, measurements have been performed from 1 GHz to 500 GHz in 4 frequency bands, namely, (i) 1-110 GHz, (ii) 140-220 GHz (iii) 220-330 GHz (iv) 325-500 GHz.

#### **1.3.1** Probe stations

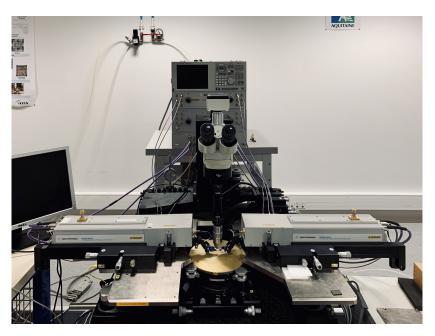

For the measurements in the band 1-110 GHz, the setup consists of the N5250A module (Fig. 1.5) from Agilent Technologies that operates from 10 MHz to 110 GHz [35]. This network analyzer includes the microwave network analyzer E8361A PNA that delivers signals from 10 MHz to 67 GHz, millimetre-wave test heads that provide signals from 67-110 GHz, millimetre-wave test set controller that drives these test heads, the combiner assembly containing the 67 GHz coupler and a combiner that combines the signal from the PNA with that from the mm-wave test heads. Bias tees are added to this for enhanced measurement stability. The specifications of E8361A PNA are given in Table 1.2 [36] [37].

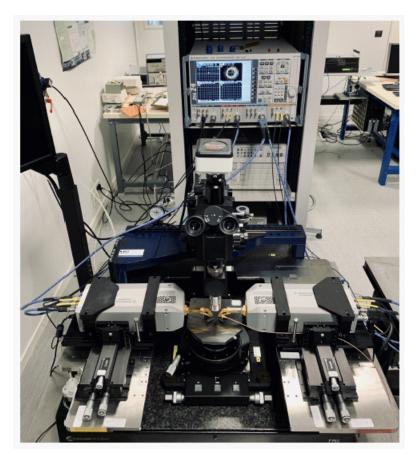

For the higher frequency bands, the Rohde & Schwarz ® ZVA24 VNA [38], which operates from 10 MHz to 24 GHz, is used. The photograph of the probe station is shown in Fig. 1.6

Figure 1.3: Block diagram of VNA S-parameter testset [34]

Figure 1.4: Bias TEE circuit used in VNA [34]

Figure 1.5: Probe station for measurement from 1-110 GHz using N5250A network analyzer

To perform measurements in each band, namely, 140-220 GHz, 220-330 GHz and 325-500 GHz, the frequency extenders ZC220, ZC330 and ZC500 [39] [40] are added respectively to the VNA. The performance specifications of the VNA and frequency extenders are listed in Table 1.2 and Table 1.3. It is observed from Table 1.2 that the ZVA has much better performance, especially regarding the dynamic range which is 30dB higher. This is a tremendous number. The reason is mainly due to the fact that the ZVA has been acquired by the University of Bordeaux in 2015, while the PNA was bought in 2007. That being said, making on-wafer measurement showing a 100dB dynamic range is extremely challenging due to the noise introduced by the on-wafer connections. In the same vein, we recognize superior performance concerning directivity, source match and load match for the ZVA, but these characteristics are directly accounted for in the calibration procedure. The same comment holds for the reflection and transmission tracking. Summing up, the two measurement instruments make it possible to correctly obtain the on-wafer transistor characteristics. There is no fundamental limitation due to the available hardware. Of course, having a state-of-the-art VNA on hand makes for less noisy and smoother measurements, but our somewhat older measuring equipment always gives correct results.

Table 1.3 summarizes the specifications of the frequency extenders used for the measurements. Each frequency range has its own waveguide design due to the different wavelengths. It is observed that the dynamic range, in particular the output power decreases significantly with increasing frequency. For our applications, this is not an issue, as we try to characterize the transistor under small signal operation. Source match and directivity are also decreased, especially compared to the ZVA alone, but as already mentioned, these characteristics are taken into account by the calibration.

#### 1.3.2 Probe types

In the first frequency band of 1-110 GHz, measurements were performed using RF probes from two different manufactures, GGB Industries Inc., and Cascade Microtech Inc. Picoprobe <sup>®</sup> Model 110H RF probes [41] from GGB Industries Inc. operate from DC to 110 GHz with a

Figure 1.6: Probe station used for measurements from 140 - 500 GHz

|                       | E8361A PNA | ZVA24 |

|-----------------------|------------|-------|

| Test Port Connector   | 1.85mm     | 3.5mm |

| Dynamic Range (dB)    | >94        | >125  |

| Directivity (dB)      | >34        | >40   |

| Source Match (dB)     | >34        | >36   |

| Load Match (dB)       | >37        | >40   |

| Reflection Tracking   | <0.09      | <0.1  |

| Transmission Tracking | <0.144     | <0.1  |

Table 1.2: Specifications of VNA

| ZC220              | ZC330                                                                          | ZC500                                                                                                                                                                                                              |  |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 140 to 220 GHz     | 220 to 330 GHz                                                                 | 330 to 500 GHz                                                                                                                                                                                                     |  |

| WM-1296            | WM-864                                                                         | WM-570                                                                                                                                                                                                             |  |

| >100dB, typ. 115dB | >100dB, typ. 115dB                                                             | >85dB, typ. 100dB                                                                                                                                                                                                  |  |

| >-2dBm, typ. +1dBm | >-10dBm, typ7dBm                                                               | >-15dBm, typ11dBm                                                                                                                                                                                                  |  |

| >25dB              | >20dB                                                                          | >20dB                                                                                                                                                                                                              |  |

| >25dB              | >20dB                                                                          | >20dB                                                                                                                                                                                                              |  |

|                    | 140 to 220 GHz<br>WM-1296<br>>100dB, typ. 115dB<br>>-2dBm, typ. +1dBm<br>>25dB | 140 to 220 GHz         220 to 330 GHz           WM-1296         WM-864           >100dB, typ. 115dB         >100dB, typ. 115dB           >-2dBm, typ. +1dBm         >-10dBm, typ7dBm           >25dB         >20dB |  |

Table 1.3: Specifications of Frequency Extenders Used for Measurements

(b) 140-220 GHz (c) 220-330 GHz

Figure 1.7: Photographs of Picoprobes for measurements from 1-500 GHz

maximum insertion loss of 1.5dB. This probe has a coaxial cable design [42]. An insulating layer separates the inner conductor and outer conductor. The miniature coaxial transmission lines having a center conductor diameter of 0.2mm carry signals to and from test instruments. The coaxial cables use a 1mm connector for connection to the instruments at one end. At the other end, the centre conductor extends beyond the cable shield to form a conical point for connection to the RF test pads. For the measurements in this work, two types of GSG (Ground-Signal-Ground) Picoprobes with a pitch of 100 µm and a pitch of 50µm have been utilized. A photograph of the Picoprobe is shown in Fig. 1.7a.

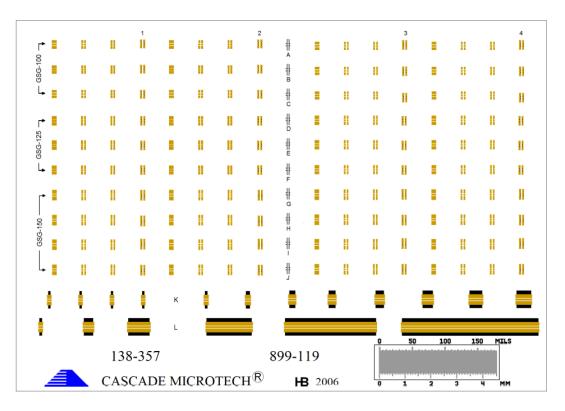

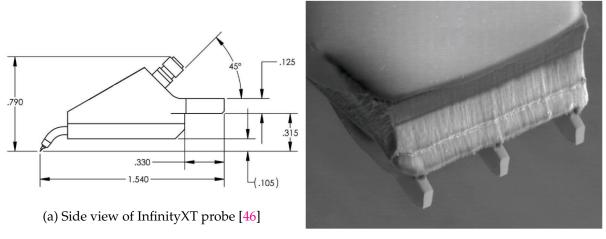

Infinity probes [43] [44] by Cascade Microtech Inc. were also used for measurements in this frequency band (photograph in Fig. 1.8). These probes based on the thin film technology, consists of a microstrip line on a flexible polyimide membrane substrate [45]. The microstrip line transmits the signal from the coaxial conductor to the device through Nickel alloy probe tips. Also used in this band are the improved InfinityXT<sup>™</sup>by Cascade Microtech Inc.[43]. Here only probes with a pitch of 50 µm are available in the lab. These probes having a very different geometry (see Fig. 1.9) as well as a different connection from the coaxial endpoint to the probe tips which greatly influences the EM field. Moreover, these have better tip visibility for enhanced placement accuracy and repeatability [46].

Cascade Microtech also provides Infinity probes [43] [45] in the WR5 (140-220 GHz) frequency band. These waveguide based probes with membrane tips claim to significantly reduce stray fields in the tip area [47]. In fact, waveguide probes support transverse electric (TE) and transverse magnetic (TM) mode of wave propagation, whereas coaxial probes support transverse electromagnetic (TEM) wave propagation mode [48].

In the last two bands (220-330 GHz, 325-500 GHz), Picoprobe RF probes [49] [50] from GGB Industries Inc. were used (Fig. 1.7c and Fig. 1.7d). These have a coaxial design with Beryllium Copper probe tips. Table 1.4 makes a comparison of the different RF probes used for the different frequency ranges. It is observed that for frequencies higher than 220 GHz, probes with 50

Figure 1.8: Photograph of Infinity probe Figure 1.9: SEM image of Infinity XT forfor 110 GHz measurements110 GHz measurements

|                        | Picoprobe110    | Infinity110          | InfinityXT | Infinity220        | Picoprobe330 | Picoprobe500 |

|------------------------|-----------------|----------------------|------------|--------------------|--------------|--------------|

| Frequency (GHz)        | 1-110           | 1-110                | 1-110      | 140-220            | 220-330      | 325-500      |

| Design type            | coaxial         | thin film technology | coaxial    | waveguide          | coaxial      | coaxial      |

| Probe tips             | Berylium-Copper | Nickel alloy         | Rhodium    | thin film membrane | BeCu         | BeCu         |

| Probe pitch ( $\mu$ m) | 100             | 100                  | 50         | 100                | 50           | 50           |

| Insertion loss (dB)    | <1.5            | <1.4                 | <2         | <5.2               | 3            | 4            |

| Return Loss (dB)       | <15             | <20                  | <20        | <13                | 15           | 15           |

Table 1.4: Comparison of RF Probes

$\mu$ m pitch are mandatory. The probe tip material is Beryllium-Copper for the Picoprobe probes whereas for Infinity probes the material is different for each frequency band. Furthermore, it can be said that for higher frequencies the probes get less ideal showing increasing insertion loss and less return loss.

#### **1.4** Types of Calibration

#### 1.4.1 Short-Open-Load-Thru (SOLT) Calibration

The SOLT is a calibration method that uses the 12-term error model. In a three sampler VNA the error model is represented separately for the forward and reverse direction due to the effect of switching. There are 6 terms each in the forward and reverse directions making a total of 12 error terms. The complete error model is shown in Fig. 1.10. The error terms in the forward direction are defined as follows using the notations from [51]:

| $E_{DF}$ | = | $e_{00} = \text{Directivity}$            |

|----------|---|------------------------------------------|

| $E_{SF}$ | = | $e_{11}$ = Source Match                  |

| $E_{RF}$ | = | $(e_{10}e_{01}) = $ Reflection Tracking  |

| $E_{XF}$ | = | $e_{30} = \text{Crosstalk}$              |

| $E_{TF}$ | = | $(e_{10}e_{32}) =$ Transmission Tracking |

| $E_{LF}$ | = | $e_{22} = $ Load Match                   |

Figure 1.10: 12-term error model of network analyzer [52]

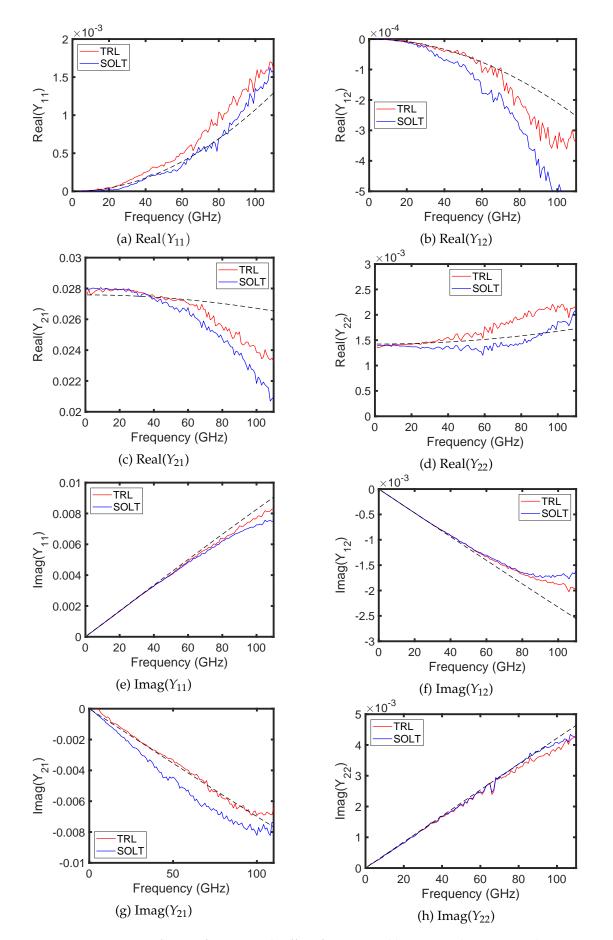

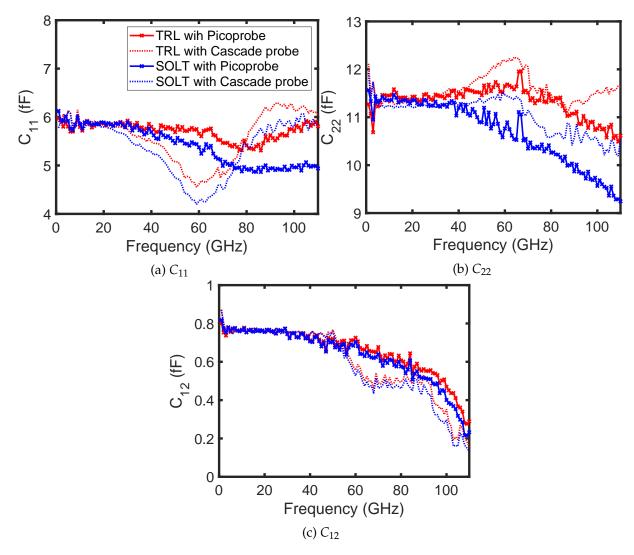

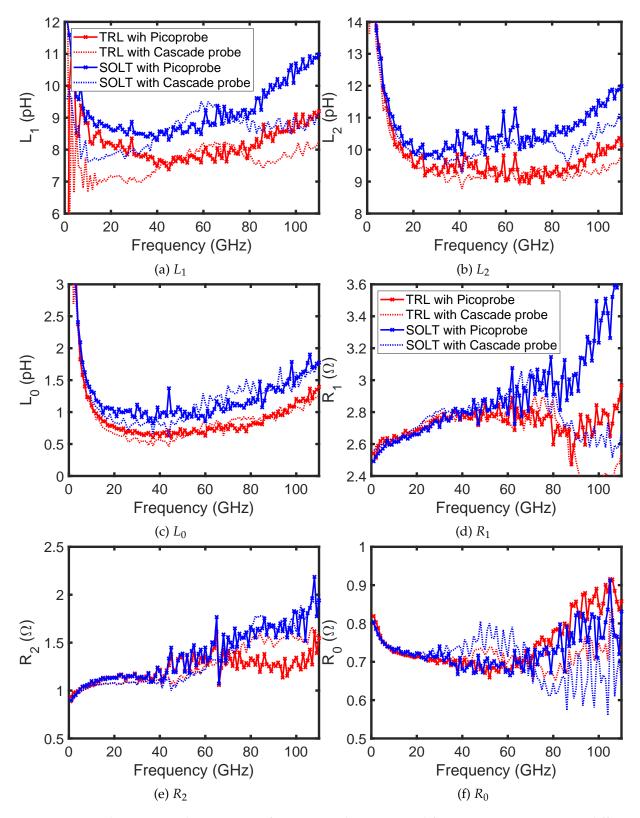

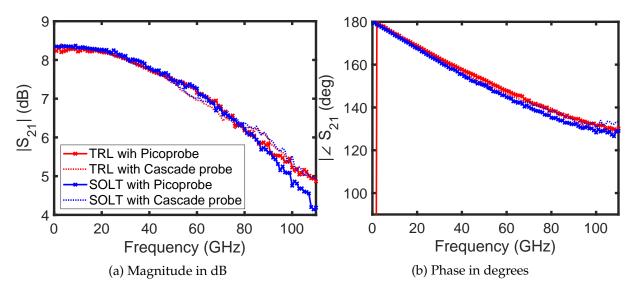

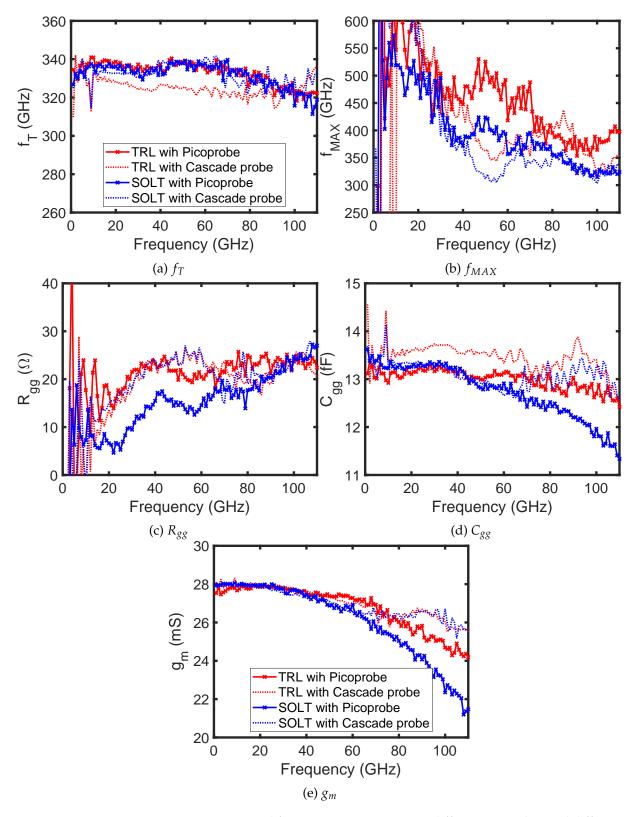

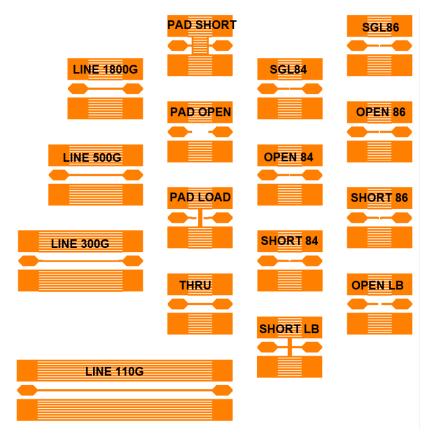

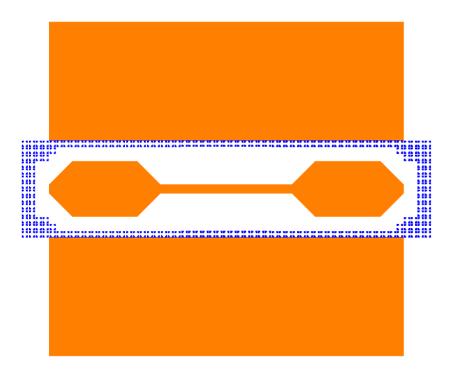

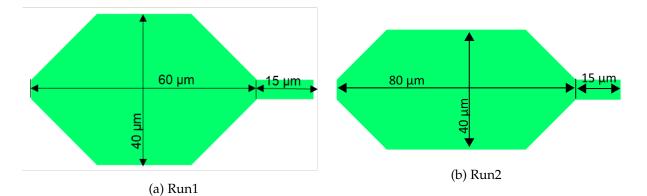

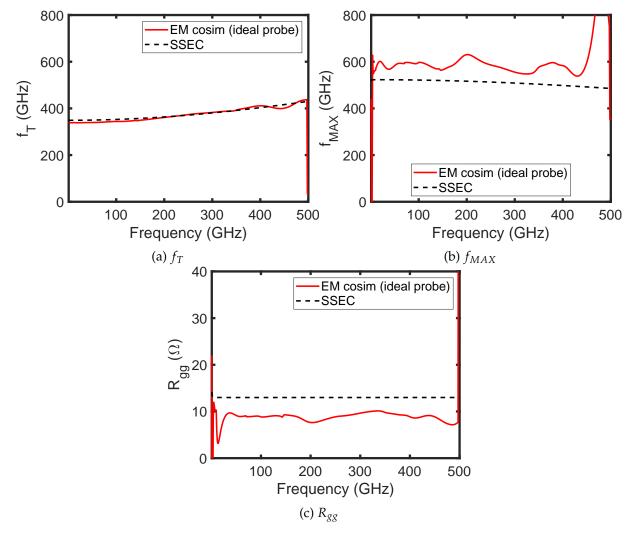

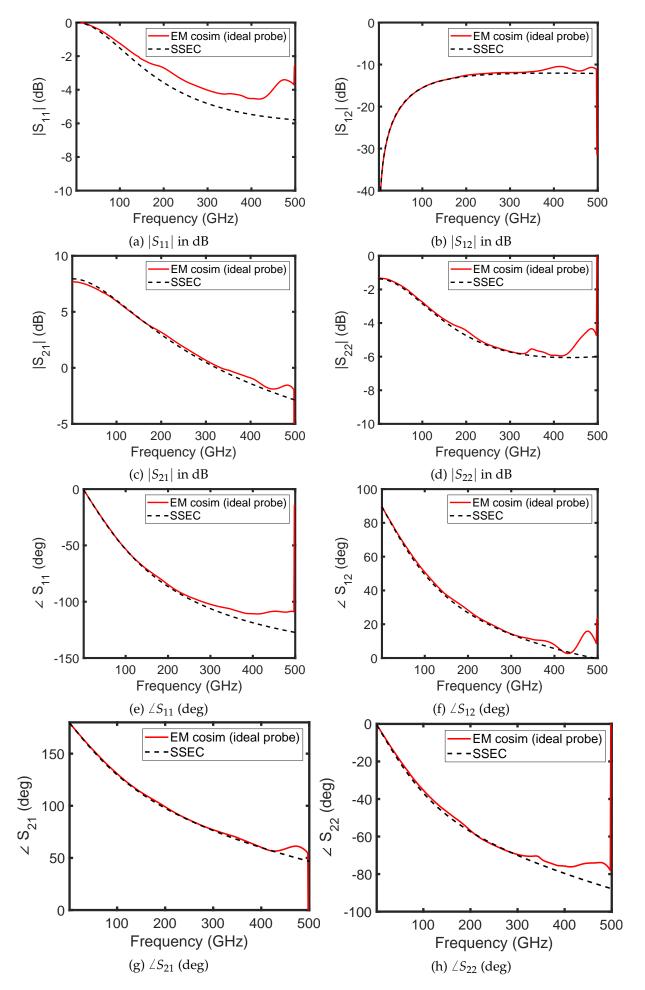

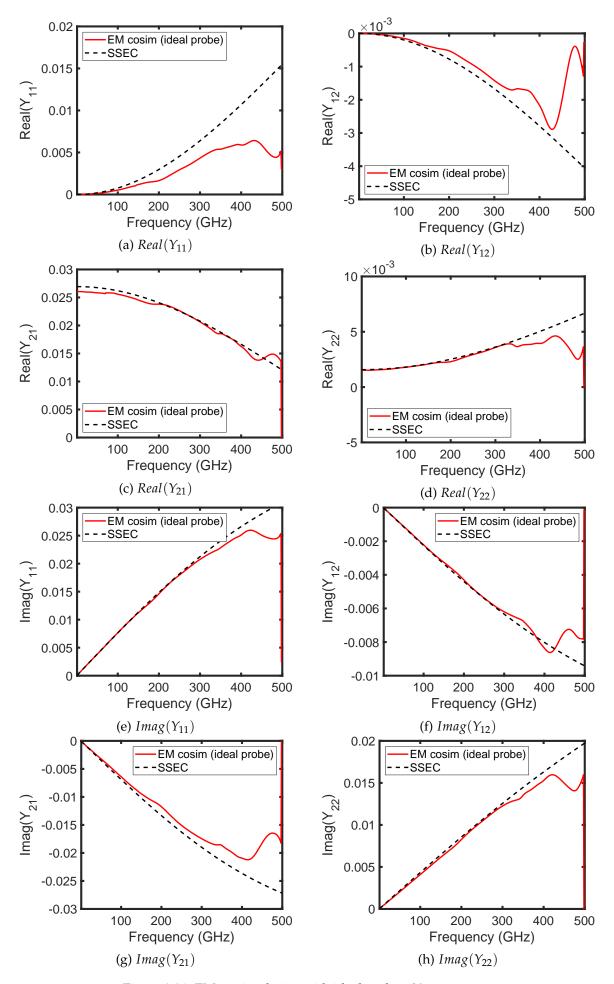

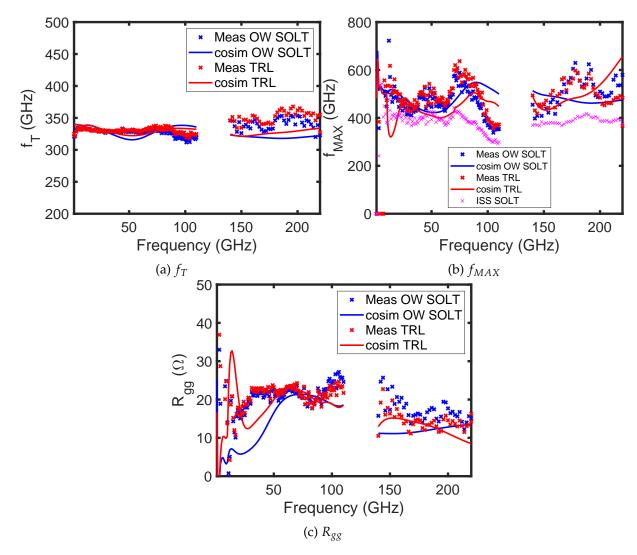

Similarly, we also have another 4 error terms,  $E_{DR}$ ,  $E_{SR}$ ,  $E_{RR}$ ,  $E_{XR}$ ,  $E_{TR}$  and  $E_{LR}$  in the reverse direction.