# Design space exploration of image processing algorithms on FPGAs

Ilias Bournias

# ► To cite this version:

Ilias Bournias. Design space exploration of image processing algorithms on FPGAs. Data Structures and Algorithms [cs.DS]. Sorbonne Université, 2023. English. NNT: 2023SORUS179. tel-04197593

# HAL Id: tel-04197593 https://theses.hal.science/tel-04197593v1

Submitted on 6 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE SORBONNE UNIVERSITÉ

# DESIGN SPACE EXPLORATION OF IMAGE PROCESSING ALGORITHMS ON FPGAS

présentée par ILIAS BOURNIAS

École Doctorale Informatique, Télécommunications et Électronique

réalisée au LIP6

soutenue le

devant le jury composé de :

| М.   | Florent De Dinechin, Professeur, INSA, Lyon, France                           | Rapporteur            |

|------|-------------------------------------------------------------------------------|-----------------------|

| M.   | Steven Derrien, Professeur, Université Rennes 1, Rennes, France               | Rapporteur            |

| Mme. | Fabienne Jézéquiel, Maître de conférences, HDR, LIP6, Paris, France           | Examinateur           |

| M.   | François Berry, Professeur, Université Cl. Auvergne, Clermont-Ferrand, France | Examinateur           |

| M.   | Nicolas Rambaux, Maître de Conférences, Sorbonne Université, Paris, France    | Invité                |

| M.   | Lionel Lacassagne, Professeur, LIP6, Paris, France                            | Co-directeur de Thèse |

| Mme. | Roselyne Chotin, Maître de conférences, HDR, LIP6, Paris, France              | Directrice de Thèse   |

|      |                                                                               |                       |

Ilias Bournias: Design Space Exploration Of Image Processing Algorithms On FPGAs,  $\ensuremath{\mathbb{C}}$  May 2023

To my Family that always supported me

# ABSTRACT

Implementing image processing algorithms for embedded systems is a scientific topic of great importance and many researchers focus their work on this domain. Many trade-offs have to be made in order to fit these algorithms in a specific embedded system and at the same time achieve real time computation and acceptable precision.

In this thesis, we focus on the design space exploration of an optical flow algorithm called Multi-scale Horn and Schunck algorithm in an Arria 10 FPGA. Although we focus on a specific algorithm and a specific device, the exploration we perform and the propositions of this thesis can also be applied to other algorithms and FPGA devices too.

The first thing we explore is the accuracy of the algorithm. We use different floating point formats and we tune different parameters of the algorithm in order to increase the accuracy and at the same time provide an implementation which achieves real time computation. As this algorithm is a multi-rate image processing algorithm, we propose solutions in order to tackle this nature of the algorithm and increase computation throughput. We use pipeline and vectorized architectures in order to further increase the computation speed and we introduce trans-floating computation which enables us to fit more processing elements in our FPGA. We explore how all these solutions affect the resources usage of the FPGA, such as the LUTs, DSPs and Block RAMs utilization. Furthermore, we propose approaches in order to overcome the bottleneck of the external memory bandwidth. Following that, and by taking into account all our propositions, we perform a design space exploration of the algorithm, which helps the optical flow designer to choose among different configurations according to his constraints.

We compare our designs with other state of the art works on optical flow in FPGAs and we show that to the best of our knowledge our fastest design achieves the highest throughput compared to all the rest optical flow designs on single FPGA. At the same time our implementations achieve comparable accuracy of detection.

# RÉSUMÉ

La mise en œuvre d'algorithmes de traitement d'image pour les systèmes embarqués est un sujet scientifique de grande importance et de nombreux chercheurs concentrent leurs travaux sur ce domaine. De nombreux compromis doivent être réalisés afin d'adapter ces algorithmes au système ciblé et obtenir en même temps un calcul en temps réel et une précision acceptable.

Dans cette thèse, nous nous concentrons sur l'exploration de l'espace de conception d'un algorithme de flot optique appelé algorithme de Horn et Schunck multi-échelles dans un FPGA Arria 10. Bien que nous nous concentrions sur un algorithme et une cible spécifiques, l'exploration que nous effectuons et les propositions de cette thèse peuvent élargies à d'autres algorithmes et FPGAs.

La première chose que nous explorons est la précision des calculs. Nous utilisons différents formats de virgule flottante et nous ajustons différents paramètres de l'algorithme afin d'augmenter la précision et en même temps fournir une implémentation qui réalise le calcul en temps réel. Comme cet algorithme est un algorithme de traitement d'images multi-débits, nous proposons des solutions pour augmenter le débit de calcul. Nous utilisons des architectures pipeline et vectorisées afin d'augmenter encore la vitesse de calcul et nous introduisons le calcul trans-flottant qui nous permet d'intégrer plus d'éléments de traitement sur le FPGA. Nous explorons comment toutes ces solutions affectent l'utilisation des ressources du FPGA, telles que l'utilisation des LUTs, des DSPs et des blocs de RAM. De plus, nous proposons des approches afin de surmonter le goulot d'étranglement lié à la bande passante de la mémoire externe. Enfin, en tenant compte de toutes nos propositions, nous effectuons une exploration de l'espace de conception, qui aide le concepteur à implanter l'algorithme de flot optique sur FPGA en choisissant parmi différentes configurations en fonction de ses contraintes.

Nous comparons nos résultats d'implémentations sur FPGA de l'algorithme de flot optique avec d'autres travaux à la pointe du domaine. Ainsi, nous montrons que notre implémentation la plus rapide atteint le débit le plus élevé par rapport à tous les autres travaux portés à notre connaissance et implantés sur un unique FPGA. En même temps, nos implémentations permettent d'obtenir une précision de détection comparable à ces travaux et une utilisation moindre des ressources du FPGA.

# PUBLICATIONS

The following body of work has been published in the course of the thesis at hand:

- I. Bournias, R. Chotin, and L. Lacassagne, "Fpga acceleration of the horn and schunck hierarchical algorithm," in 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021, pp. 1–5. DOI: 10.1109/ISCAS51556.2021.9401068.

- [2] I. Bournias, R. Chotin, and L. Lacassagne, "Using hls for designing a parametric optical flow hierarchical algorithm in fpgas," in 2022 IEEE International Symposium on Circuits and Systems (ISCAS), 2022, pp. 1600–1604. DOI: 10.1109/ISCAS48785. 2022.9937732.

scientia potentia est — Sir Francis Bacon, 1668

# ACKNOWLEDGMENTS

Three and a half wonderful years finally come to an end. It has been a very interesting journey, during which i met some amazing people.

First of all i would like to thank Roselyne. Thanks for guiding me through all these years and supporting me in all the decisions i took. I am really lucky that you were my supervisor as you are a truly wonderful person with endless will for life. The second person I would like to thank is my co-supervisor, Lionel. Lionel transmitted me the passion for research and was always there to help me with any difficulty i faced.

I would like to thank all my friends in the Lab with whom i spent many tremendous moments which i am already missing. Thank you Fedia, Julian, Gabriel, Sarah, Mohamed, Jonathan, Nathan, Thomas, Alan, Maxime, Rieul, Ning, Spyros, Theofilos and Antonis. I would also like to thank my friends, Dimitris, John, George, George and Kyrgiakos from the Fondation Hellenique with whom i spent many hours playing cards and walking around Paris. I will never forget these moments and the time we spent together.

I am very lucky that my sister, my mother and Maria were very patient with me and supported me through all these years. Finally, this thesis is dedicated to my father who led me to the world of engineering. I hope you can see this.

# CONTENTS

| 1 | INT                                 | INTRODUCTION 1                                          |  |  |

|---|-------------------------------------|---------------------------------------------------------|--|--|

|   | 1.1                                 | Context 1                                               |  |  |

|   | 1.2                                 | Contributions 3                                         |  |  |

|   |                                     | 1.2.1 Outline of The Thesis 5                           |  |  |

| 2 | OPTICAL FLOW AND EMBEDDED DEVICES 7 |                                                         |  |  |

|   | 2.1                                 | Optical Flow 7                                          |  |  |

|   | 2.2                                 | Different Optical Flow Algorithms 8                     |  |  |

|   |                                     | 2.2.1 Lukas and Kanade 8                                |  |  |

|   |                                     | 2.2.2 Horn and Schunck 10                               |  |  |

|   |                                     | 2.2.3 Other Optical Flow algorithms 14                  |  |  |

|   |                                     | 2.2.4 Advantages and disadvantages of each algorithm 15 |  |  |

|   | 2.3                                 | Optical Flow In Embedded Devices 15                     |  |  |

|   | 2.4                                 | Different Components of the multi-scale H&S 18          |  |  |

|   | 2.5                                 | Discussion on the state of the art in FPGAs 19          |  |  |

|   | 2.6                                 | Conclusion 20                                           |  |  |

| 3 | ACCURACY 21                         |                                                         |  |  |

|   | 3.1                                 | Evaluation Metrics 22                                   |  |  |

|   |                                     | 3.1.1 Peak Signal to Noise Ratio 22                     |  |  |

|   |                                     | 3.1.2 Average Angular Error 22                          |  |  |

|   |                                     | 3.1.3 Average Endpoint Error 23                         |  |  |

|   |                                     | 3.1.4 Exploration Methodology 23                        |  |  |

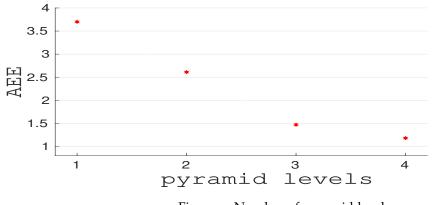

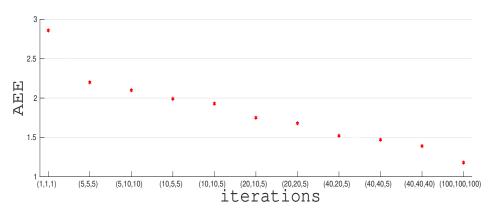

|   | 3.2                                 | Levels of the pyramid and iterations in each level 23   |  |  |

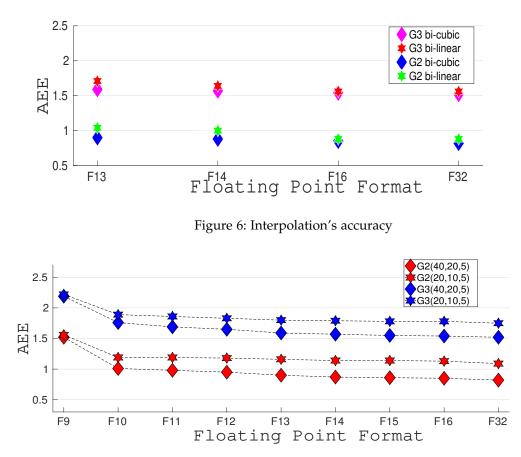

|   | 3.3                                 | Interpolation 25                                        |  |  |

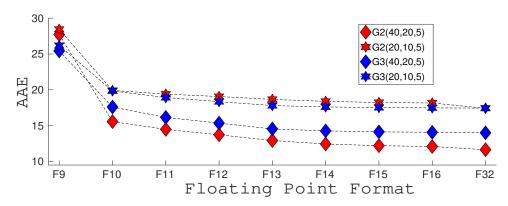

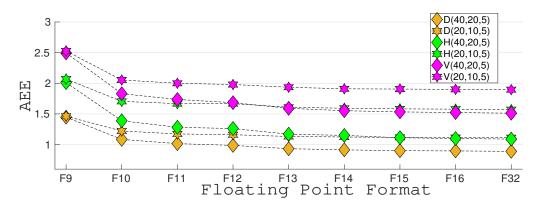

|   | 3.4                                 | Floating point formats 27                               |  |  |

|   | 3.5                                 | Trans-floating formats 30                               |  |  |

|   | 3.6                                 | Comparison with state of the art 30                     |  |  |

|   | 3.7                                 | Conclusions 32                                          |  |  |

| 4 | THR                                 | OUGHPUT 35                                              |  |  |

|   | 4.1                                 | Monoscale Horn and Schunck 35                           |  |  |

|   |                                     | 4.1.1 Pipeline 36                                       |  |  |

|   |                                     | 4.1.2 Vectorization 38                                  |  |  |

|   | 4.2                                 | Warping 38                                              |  |  |

|   | 4.3                                 | Down-sampling 41                                        |  |  |

|   | 4.4                                 | Up-sampling 44                                          |  |  |

|   | 4.5                                 | Multi-Scale H&S 45                                      |  |  |

|   |                                     | 4.5.1 Pipeline and Parallelization 45                   |  |  |

- 4.5.2 Multi-rate Architecture 46

- 4.5.3 Multi-level Architecture 47

- 4.5.4 Computation Time 48

- 4.5.5 Trans-floating architecture 48

- 4.5.6 Computation Time for the Trans-floating architecture 50

- 4.6 Throughput Results and Comparison with State of the Art 50

- 4.6.1 Results of implementation 50

- 4.6.2 Comparison with State of the Art 52

- 4.7 Conclusion 52

- 5 HARDWARE RESOURCES UTILIZATION 55

- 5.1 Mono-scale Horn and Schunck Agorithm 55

- 5.2 Warping 60

- 5.3 Down-sampling 63

- 5.4 Up-sampling 65

- 5.5 Multi-scale H&S algorithm 66

- 5.5.1 Multi-rate Architecture 66

- 5.5.2 Multi-level Architecture 67

- 5.6 Resources Utilization Results and Comparison with state of the Art 68

- 5.6.1 Results of Implementation 69

75

- 5.6.2 Comparison with the state of the art 71

- 5.7 Conclusions 73

- 6 DESIGN SPACE EXPLORATION 75

- 6.1 Methodology

- 6.1.1 Notation 75

- 6.1.2 DSPs Utilization 76

- 6.1.3 Block RAMs 77

- 6.1.4 External memory bandwidth 78

- 6.1.5 Execution Time and Throughput 79

- 6.1.6 Design Space Exploration and OpenCL 79

- 6.2 Results 82

- 6.3 Conclusion 83

- 7 CONCLUSION AND FUTURE WORK 85

- 7.1 Conclusion 85

- 7.2 Future Work 87

BIBLIOGRAPHY 89

# LIST OF FIGURES

| Figure 1  | H&S mono-scale iterative scheme 10                                                 |

|-----------|------------------------------------------------------------------------------------|

| Figure 2  | Pyramid of images 12                                                               |

| Figure 3  | Description of the multi-scale H&S Algorithm 13                                    |

| Figure 4  | Number of pyramid level 24                                                         |

| Figure 5  | Number of iterations in each pyramid level 25                                      |

| Figure 6  | Interpolation's accuracy 26                                                        |

| Figure 7  | AEE for G <sub>3</sub> and G <sub>2</sub> with different Floating Point formats 26 |

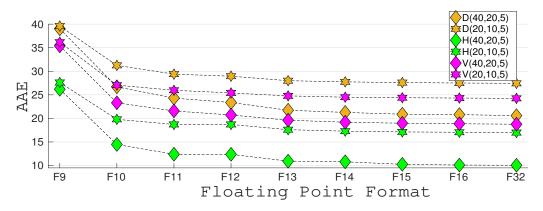

| Figure 8  | AAE for G <sub>3</sub> and G <sub>2</sub> with different Floating Point formats 27 |

| Figure 9  | AEE for H, D and V with different Floating Point formats 27                        |

| Figure 10 | AAE for H, D and V with different Floating Point formats 28                        |

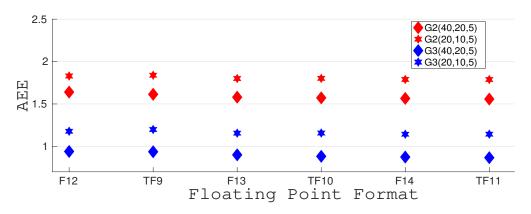

| Figure 11 | AEE for G <sub>3</sub> and G <sub>2</sub> with trans Floating Point format 28      |

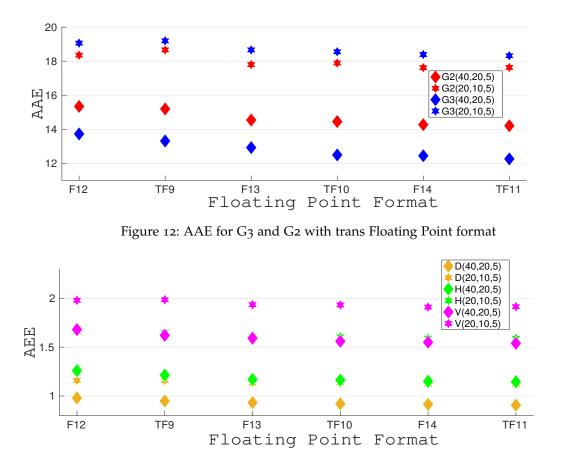

| Figure 12 | AAE for G <sub>3</sub> and G <sub>2</sub> with trans Floating Point format 29      |

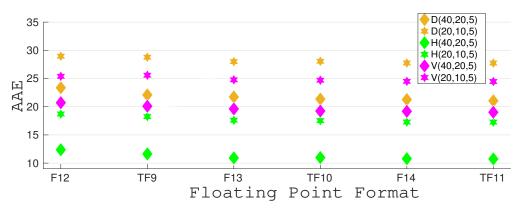

| Figure 13 | AEE for D, H and V with trans Floating Point format 29                             |

| Figure 14 | AAE for D, H and V with trans Floating Point format 30                             |

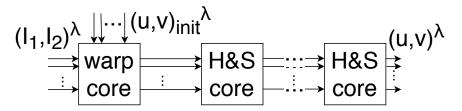

| Figure 15 | Deep Pipeline Architecture 37                                                      |

| Figure 16 | Vectorized Architecture 39                                                         |

| Figure 17 | Interpolation Pattern 40                                                           |

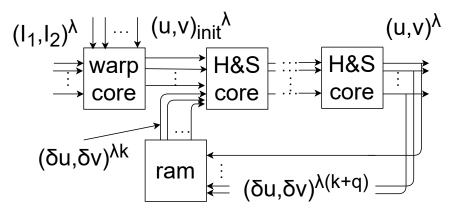

| Figure 18 | Warping Architecture 41                                                            |

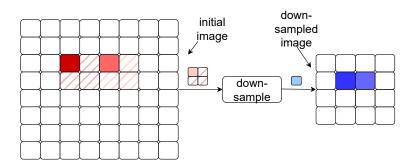

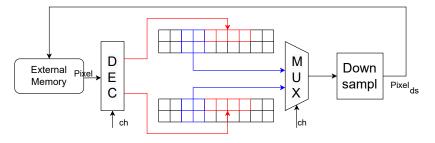

| Figure 19 | Down-Sampling Pattern 42                                                           |

| Figure 20 | Down-sampling 43                                                                   |

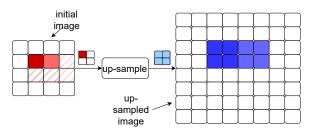

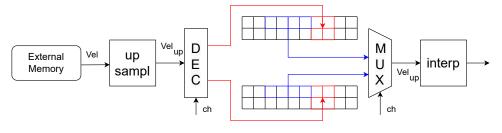

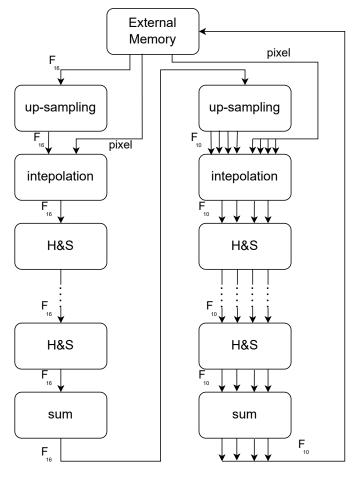

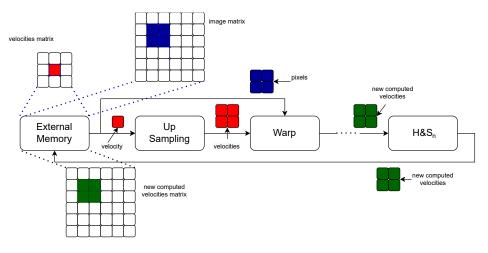

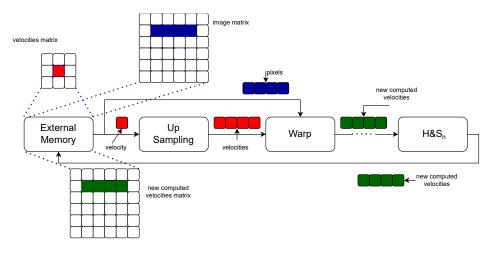

| Figure 21 | Up-Sampling Pattern 44                                                             |

| Figure 22 | Up-sampling 44                                                                     |

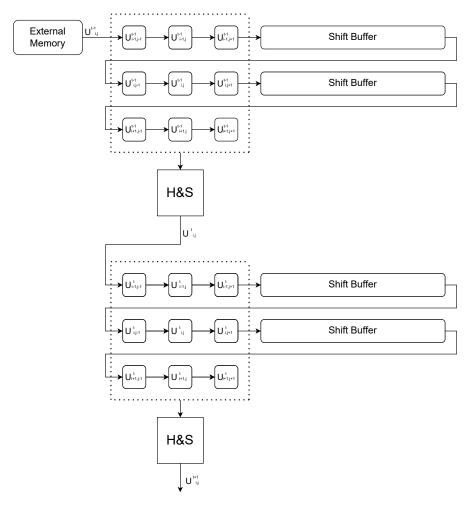

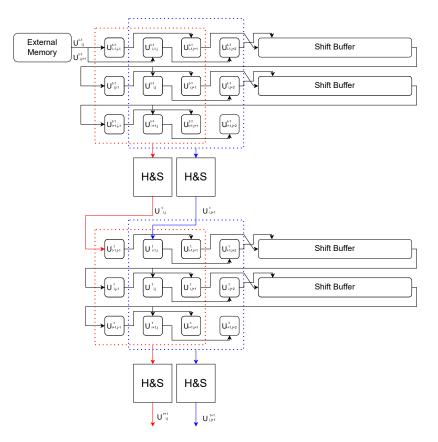

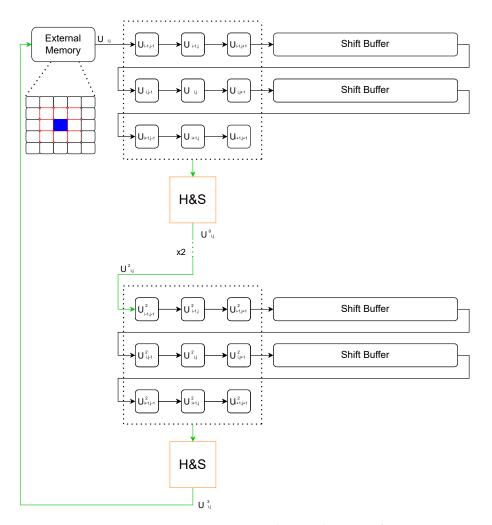

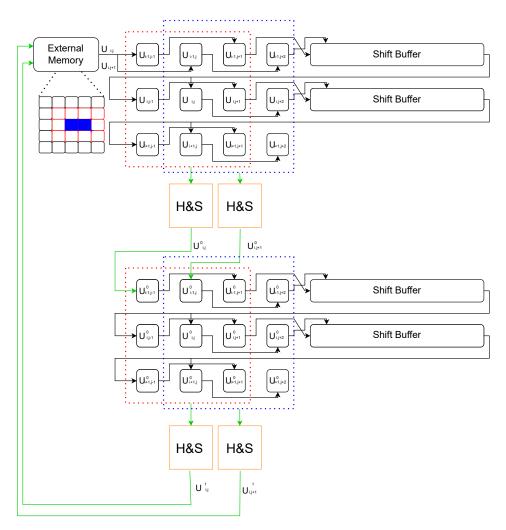

| Figure 23 | Partial pipeline parallel architecture 45                                          |

| Figure 24 | Fully pipeline architecture 46                                                     |

| Figure 25 | Trans-floating architecture 49                                                     |

| Figure 26 | Derivatives Reuse 56                                                               |

| Figure 27 | Deep Pipeline Architecture 57                                                      |

| Figure 28 | Deep Pipeline Architecture for 4 Iterations 58                                     |

| Figure 29 | Vectorized-Deep Pipeline Architecture for 4 Iterations 59                          |

| Figure 30 | Pyramid level implementation of [68] 66                                            |

| Figure 31 | Pyramid level implementation 67                                                    |

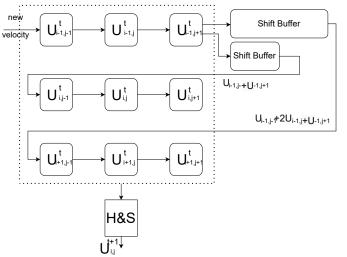

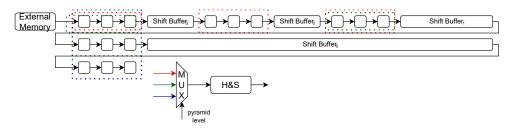

| Figure 32 | Shift Buffers 68                                                                   |

| Figure 33 | Streamed velocities 68                                                             |

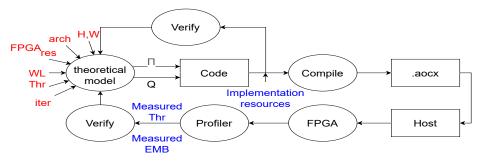

| Figure 34 | Design Space Exploration Steps 80                                                  |

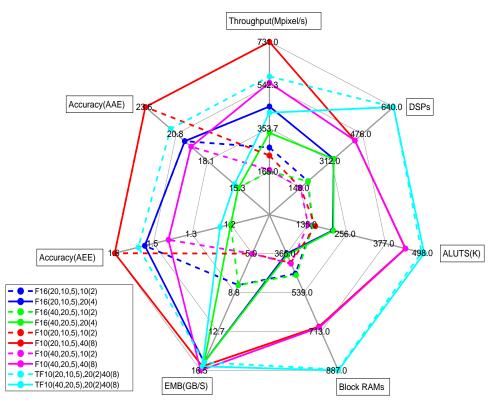

| Figure 35 | Results 81                                                                         |

|           |                                                                                    |

# LIST OF TABLES

| Table 1  | Advantages of the FPGA State of the Art Works 19                      |

|----------|-----------------------------------------------------------------------|

| Table 2  | Comparison with other State of the Art (AAE) 31                       |

| Table 3  | Comparison with other State of the Art (AEE) 32                       |

| Table 4  | Throughput Results with the Same Numeric Format 51                    |

| Table 5  | Throughput Results with the Smaller Numeric Format in level o 51      |

| Table 6  | Comparison with other State of the Art 53                             |

| Table 7  | Mono-scale Core 57                                                    |

| Table 8  | Mono-Scale Architecture 60                                            |

| Table 9  | Mono-Scale Core with Different Floating Point Formats 61              |

| Table 10 | Bi-cubic Interpolation Core with Different Floating Point Formats 62  |

| Table 11 | Bi-linear Interpolation Core with Different Floating Point Formats 62 |

| Table 12 | Down-sampling Core 64                                                 |

| Table 13 | Resources Utilization with $\Pi = 5$ 69                               |

| Table 14 | Resources Utilization with $\Pi$ =10 69                               |

| Table 15 | Resources Utilization with $\Pi = 20$ 70                              |

| Table 16 | Resources Utilization with $\Pi$ =40 70                               |

| Table 17 | Resources With The Smaller Numeric Format in level o 70               |

| Table 18 | Block RAMs usage with different image sizes 71                        |

| Table 19 | Comparison with other State of the Art 72                             |

| Table 20 | Notations for the Theoretical Model I 76                              |

| Table 21 | Notations for the Theoretical Model II 76                             |

|          |                                                                       |

# INTRODUCTION

#### 1.1 CONTEXT

This thesis was conducted in the LIP6 Lab in Sorbonne University of Paris and is a part of the Meteorix project [1]. Meteorix is a university CubeSat mission and its aim is to integrate inside the CubeSat all the materials necessary (such as the cameras, the embedded devices, the algorithms, the memories etc.) for the detection and characterization of meteors. Meteor tracking and characterization requires fast meteor detection algorithms which in the case of the Meteorix project have to be able to fit in embedded systems. Within the LIP6 lab, this thesis was a collaboration between the Analog and Digital Integrated Circuit team (CIAN) and the Hardware and Software for Embedded System team (ALSOC). The activities of the ALSOC team concern methods, algorithms and tools for multiprocessors system on chip design and cots. Such highly integrated multiprocessors architectures are used in embedded applications such as automotive, nomad, audio and video, and telecommunications. The design of these systems requires the development of hardware and software co-design methods. They focus on advanced hardware architecture, communication protocols, embedded operating system, real-time constraints, formal methods for verification systems and optimization of code generation. The research areas of CIAN team focus on designing methods for analog and digital components which are integrated on the same chip (AMS SOC). The main aim is to design generic components that can be adapted for a wide range of applications. Components differ depending upon the nature of the signal to process : signal processors (DSP), digital ASIC, programmable logic component (FPGA), analog circuits, multi-standard RF components and SOC Clocks. The LIP6 laboratory is in charge of the embedded meteor detection and the expertise of the CIAN and ALSOC teams is employed to integrate the algorithms in the CubeSat. To this direction, CPUs [2] and GPUs [3] have been considered so far by the ALSOC team for the optimization of the algorithms . In this thesis, we will focus in FPGAs to make the implementation of the algorithms (specifically the optical flow) that detect the meteors, sustainable in terms of resources utilization and able to compute the required tasks in real time as the CPUs and GPUs implementations are not always able to achieve that. This is the main contribution of the CIAN team.

An essential algorithm which is part of the meteor detection is the optical flow which is used to estimated the pixel movement of two consecutive images [4],[2]. This algorithm is the one which demands the most computation time (over 80% of the total computation time[5]) and it demands special attention in order to be accelerated. Nowadays, neural

#### 2 INTRODUCTION

networks are used widely for optical flow and they achieve the best accuracy compared to all the other algorithms [6],[7]. However, the computation power they demand is way higher than the one embedded devices can offer [8]. Consequently, it is unrealistic to use neural networks for the detection of meteors in small CubeSats as they do not usually carry powerful processing units which require a lot of energy and space to function. By taking that into consideration, in this thesis we turn to a classical optical flow algorithm which with the appropriate handling and optimizations in an FPGA, offers real time computation, competitive accuracy and limited hardware resources consumption.

Nevertheless, optical flow is a vital part of many other computer vision applications in real life. Autonomous driving and vehicle navigation is the kind of algorithms which make a good use of optical flow [9],[10],[11],[12],[13],[14]. For example, when the car is moving along a flat road and the optical axis of the camera is parallel to the ground, the motion field is expected to be almost quadratic and have a specific structure and consequently information about the angular velocity and the speed can be extracted from the flow vectors [10]. Optical flow can be employed to provide strong information for hypothesis generation about the possible presence of cars. Approaching vehicles at an opposite direction produce a diverging flow, which can be quantitatively distinguished from the flow caused by the car ego-motion. In robotics navigation, it is used with the aim of helping solving the obstacle avoidance problem in the ground and in the air. With the vectors, the rotational velocity, translational velocity and terrain information can be estimated separately through the integration of optical flow with inertial, GPS, and range data as thoroughly explained in [13]. Optical flow is a vital algorithm in the biomedical domain too. It has been used to measure the functionality of many body organs with remarkable precision [15],[16],[17][18],[19]. The flow is used for the measurement of organs velocity in centimeter per second in each studied pixel and after that it is visualized as colored vectors superimposed on Magnetic resonance imaging (MRI) images. The measured flow is also used to extract useful biological information for some part detection in the organ which otherwise can not be extracted or even to measure some anomalies in the blood pressure[20],[21],[22],[23]. Moreover, optical flow is used widely in the Defence domain. In video surveillance finding the velocity vectors of the video is of great importance in order to extract useful information [24],[25],[26],[27],[28],[29], [30],[31],[32]. In [25] these vectors are used in the Histograms of Oriented Gradient (HOG) descriptors for captioning the motion information for gesture recognition. In [26] it was used for assessing crowd behaviors from videos in terms of motion pattern and dominant paths. To do that, they rely on the estimation of a collection of sub-affine motion models in the image. In [27] they propose to use optical flow as an igniting point for video recording. As the amount of data when recording for a long time is huge, the velocity vectors can be used to store on the memory data when only movement is happening. In [29], [30] and [28] they use optical flow for video denoising where the flow vectors are used for the detection of the noise

in the image. Finally, optical flow can be used for video indexing [33],[34],[32], restoration of aged videos [35] and aerodynamics or fluid mechanics [36],[37].

A special mention has to be done in the LIP6 lab in Sorbonne University where optical flow is developed for the detection of meteors in the sky and which is also part of the Meteorix Project. Millet [4],[2] in his work is implementing a large image processing pipeline where the dominant part is the optical flow [3], for the flow vectors estimation and in these vectors a component labeling algorithm is applied for the detection of the meteors [38],[39]. With this pipeline which is designed in CPU and GPUs the meteor detection is accomplished with remarkable accuracy.

As in the case of the CubeSat mission project, installing huge computation units in cars, biomedical devices and surveillance cameras for neural networks optical flow computations is not usually feasible. Moreover, the training they require is complex and a massive amount of data which must be also relevant has to be found in order to achieve an effective one. Conventional optical flow algorithms does not suffer from these bottlenecks. They achieve comparable accuracy and they are ideal for embedded devices as they can be massively accelerated. This is why still the conventional optical flow algorithms take the largest piece of the pie in embedded systems and the research done in this domains remains one of the most hot research topics.

The aforementioned applications demand specific constraints in terms of throughput and accuracy [2],[1]. Designing computer vision application for embedded devices is a challenging task and it requires a lot of trade off to be made in order to achieve real time computation and in the same time the hardware to remain low. In FPGAs, the trade off can be made in the arithmetic format used for the representation of the data, in the pipeline and the parallelism with respect to the resources utilization. However, increasing the paralellism might lead to cases where the external memory can not deliver the requested throughput. Thus, we have to take into account that different FPGAs offer different possibilities. It is essential for a design to be scalable in order to fit in different devices and meet certain constraints. In this thesis we offer this possibility which as far as we know is something that is missing from the state of the art.

To sum up, the first challenge that shows up when designing an optical flow algorithm for FPGAs is the accuracy of the detected flow. Increasing the accuracy too much potentially leads to excessive hardware resources utilization. Real time computation also demands careful handling in order to avoid a huge hardware resources utilization. As a result the design has to respect certain constraints, regarding the accuracy of the algorithm, the resources utilization and the computation throughput.

# 1.2 CONTRIBUTIONS

In this thesis we concentrate on the design space exploration of the multi-scale Horn and Schunck algorithm on FPGAs. We will use techniques which are widely used in FPGA

# 4 INTRODUCTION

designing as well as new ones to overcome several bottlenecks. Although we focus on a specific algorithm, the propositions can be used in other image processing algorithms to deal with existing bottlenecks

Our main contributions are:

- One of the most important parts of the algorithm is the accuracy it achieves. Thus, we will explore the pyramid levels and iterations number of the algorithm with the aim of improving the accuracy of the flow detection. We implement two interpolation algorithms and we show the impact they have on the accuracy. Since we talk about embedded designs, we use less bit to decrease the resources utilization to represent the data and keep the accuracy as high as possible. We also use different arithmetic formats in each pyramid level and we observe the drop in accuracy. Thus, we show how all these parameters impact the accuracy.

- Optical flow in real world problems require real time and sometimes higher than real time throughput. Consequently, we explore different techniques to accelerate every part of the algorithm. We make use of previous state of the art techniques such as vectorization and deep pipeline to accelerate the mono-scale kernel. We treat the multi-rate nature of the algorithm more effectively than previous state of the art works by proposing architectures which are friendly to the external memory bus and bandwidth. We use trans-floating point arithmetic and lower precision arithmetic to fit more cores in the design which increases accuracy. We scale up our designs and we show that our fastest FPGA design outperforms in terms of throughput all the previous single FPGA State of The Art designs.

- Although throughput is very important, it usually comes with an excessive cost in hardware. This is not the case in our work as we propose solutions to keep the resource utilization low. Such solutions are the bi-linear interpolation and more important of all, the computation reuse. We focus on inter-iteration computation reuse which to the best of our knowledge, has never been done before in optical flow. We offer a way to use properly the Block RAMs and by using smaller arithmetic formats, the bus of the external memory can be used for increased vectorization.

- After accuracy, throughput and resources usage has been explored, we are performing a design space exploration by taking these three factors into account. We provide the FPGA designer with the ability to choose between different configurations according to his needs and his applications constraints. These configurations vary from small to large architectures which are either accurate or flexible in terms of resources. As far as we know, contrary to all the previous state of the art works in FPGAs, we offer a design which is scalable in terms of throughput, accuracy and resource utilization.

# 1.2.1 Outline of The Thesis

This thesis is composed from 7 chapters including this one.

The second chapter is about an introduction of the optical flow algorithm. A definition is given in the beginning. Following that, several optical flow algorithms are discussed and how they are already implemented by other state of the art works. Their designing advantages and disadvantages are pointed out and it is mentioned why a new optical flow implementation is needed. The multi-scale Horn and Schunck optical flow algorithm, which is used in this thesis, is described and we make an introduction of how a scalable design of this algorithm can solve many existing bottlenecks of other designs. A summary of the strong points of each state of the art work in FPGAs concludes this chapter.

Accuracy is essential in optical flow. Chapter three is devoted in the accuracy. In the beginning, the error metrics that are used for the evaluation are presented. The multi-scale Horn and Schunck is a pyramid design. Thus, an exploration is done regarding the number of the levels of the pyramid and the iterations' numbers in each pyramid level. Bi-linear and bi-cubic interpolation is included in the exploration too. With the aim of reducing the hardware usage, several floating point formats are explored to show their impact in the flow vectors. Trans-floating arithmetic is proposed as an alternative and in the end we do a comparison with the state of the art regarding the accuracy.

Achieving real time computation is very challenging in embedded systems. During the fourth chapter we deal with accelerating the algorithm in terms of throughput. Classic iterative stencil loops techniques are employed to accelerate the mono-scale algorithm. Warping is treated in a way in order not to stall the whole pipeline. The multi-rate nature of the algorithm is mentioned and solutions to overcome the bottlenecks of this kind of algorithms are proposed. Trans-floating point arithmetic format is used to further speed up the computation and finally a comparison with other state of the art works is done regarding the throughput.

Throughput comes with a cost in hardware resources. The resources utilization of the FPGA is a major part in this thesis and chapter five is solely related to this. The resources usage needs of the different components of the algorithm are discussed. Several trade-off are explored concerning the DSPs, logic blocks utilization, Blocks RAMs and the external memory bandwidth. The impact of the different floating point formats in the hardware resources is shown and with the help of trans-floating arithmetic the design is scaled up.

In chapter six all the information are combined in order to perform a design space exploration. This exploration gives the designer the opportunity to tune the design according to his needs. By inserting certain parameters on our model he can choose among different options. Then, we show the results of the exploration.

Finally, in chapter seven a conclusion of our work is done. We point out the strong contributions that this thesis is offering in the state of the art. We discuss the perspectives

# 6 INTRODUCTION

and how our contributions can be employed in other algorithms too. We refer to the future work that can follow as this is an ongoing research.

# OPTICAL FLOW AND EMBEDDED DEVICES

In the introduction it was pointed out, why image processing and especially optical flow computation in real time speed is very important in real life. Furthermore, the context of the thesis and how this thesis contributes in the state of the art was analyzed. In this thesis, optical flow is the kind of algorithm we will concentrate on. As so, we will present the different application domains where optical flow has been used by other state of the art works and why it is considered one of the most important image processing algorithms. The applications vary from the medical world to the autonomous driving and the surveillance systems. Then, we will describe the algorithms that are widely used now. Depending on the algorithm, better accuracy can be accomplished for example with convolution neural networks or in another case reduced computation time and effort with gradient based algorithms. Furthermore, since embedded devices require sophisticated designs we will mention to other recent state of the art implementation in embedded systems. We will refer to their strong parts, their disadvantages and why a new optical flow design in embedded systems is needed. The new algorithm will be presented, its different parts will be analyzed and other state of the art works will be presented which address the same problems. We will mention why our work is needed and where the other works lack in terms of design. Finally, we will sum up the chapter.

# 2.1 OPTICAL FLOW

Image processing is a method to perform some operations on an image, in order to get an enhanced image or to extract some useful information from it. There is a vast variety of image processing algorithms, one of the most hot topics in science. In this thesis we will focus in a family of image processing algorithms called optical flow algorithms.

Optical flow is defined as the motion of each pixel on the whole surface of an image [40]. It often serves as a good approximation of the true physical motion projected onto the image plane. This motion is usually ascribed to the motion of objects in the scene [41]. The notion of optical flow actually refers to the displacement of intensity patterns. It is caused by relative motion between the observer and the objects of the observed scene and it represents motion of intensities in the image plane. In computer vision, optical flow is usually used to detect the displacement of objects. Thus, the variable that we actually want to retrieve with optical flow is the projection on the image plane of the 3D motion in the scene, usually called motion field. A major issue that occurs with optical flow algorithms is that often the intensity changes are not happening due to pixel displacement

### 8 OPTICAL FLOW AND EMBEDDED DEVICES

but because of other disturbing phenomena like lighting changes, reflection effects or modifications of the properties of the objects affecting their light emission or reflectance.

The optical flow methods try to calculate the motion between two image frames which are taken at times t and t+ $\Delta$ t at every pixel position. The equation that describes the optical flow solver is Equation 1. I is the image where the optical flow is performed, x represents the movement in the x axis, y in the y axis, t the time and  $\Delta$ x,  $\Delta$ y and  $\Delta$ t are the partial derivatives of each one of them which are used to detect the movement. These methods are called differential since they are based on local Taylor series approximations of the image signal. That is, they use partial derivatives with respect to the spatial and temporal coordinates.

$$I(x, y, t) = I(x + \Delta x, y + \Delta y, t + \Delta t)$$

<sup>(1)</sup>

#### 2.2 DIFFERENT OPTICAL FLOW ALGORITHMS

# 2.2.1 Lukas and Kanade

# 2.2.1.1 Mono-scale

One of the most famous algorithms that is used for optical flow estimation is the Lucas Kanade mono-scale algorithm (L&K) [42]. This algorithm is a gradient based one. The velocities are computed from the spatial and temporal derivatives of the image's brightness. In order to obtain correct optical flow values using gradient-based optical flow algorithms, certain assumptions have to be met such as the assumption that the flow is not changing a lot between consecutive frames and that the pixel brightness remains the same (const in Equation 2). With these two assumptions Equation 2 derives (t is the time for the first frame while t+1 is the time for the second frame). By taking the partial derivatives of this equation with respect to time (Equations 3, 4), Equation 5 derives.

$$I(x(t), y(t), t) = I(x(t+1), y(t+1), t+1) = const$$

(2)

$$\frac{I(x(t), y(t), t)}{dt} = 0$$

(3)

$$\frac{dI}{dx}\frac{dx}{dt} + \frac{dI}{dy}\frac{dy}{dt} + \frac{dI}{dt} = 0$$

(4)

$$I_x u + I_y v + It = 0 \tag{5}$$

In Equation 5 there are two unknown variables (u,v) but with only one equation to be found. These two variable are the velocity in the x axis (u) and in the y axis (v). For this reason, a method has to be proposed to solve this problem. Lucas and Kanade considered a small neighbourhood of each pixel and they said that inside this neighbourhood, a pixel moves in the same direction as it nearest neighbours. With this assumption from Equation 5 the next step is Equation 6.

$$\begin{bmatrix} I_{x}(p_{1}) & I_{y}(p_{1}) \\ I_{x}(p_{2}) & I_{y}(p_{2}) \\ \vdots & \vdots \\ I_{x}(p_{n}) & I_{y}(p_{n}) \end{bmatrix} \times \begin{bmatrix} u \\ v \end{bmatrix} = (-1) \begin{bmatrix} I_{t}(p_{1}) \\ I_{t}(p_{2}) \\ \vdots \\ I_{t}(p_{n}) \end{bmatrix}$$

(6)

$p_1 \dots p_n$  in 6 are the neighbouring pixels where the assumptions of (L&K) are referred to. Now, there is enough information to estimate the optical flow vectors (u,v).

$$\begin{bmatrix} I_{x}(p_{1}) & I_{y}(p_{1}) \\ I_{x}(p_{2}) & I_{y}(p_{2}) \\ \vdots & \vdots \\ I_{x}(p_{n}) & I_{y}(p_{n}) \end{bmatrix} = A, \begin{bmatrix} u \\ v \end{bmatrix} = d, \begin{bmatrix} I_{t}(p_{1}) \\ I_{t}(p_{2}) \\ \vdots \\ I_{t}(p_{n}) \end{bmatrix} = b$$

$$(7)$$

The notations as shown in Equation 7 are used to form the following optimization problem which is shown in Equation 8.

$$Ad = B \to \min \|Ad - b\|^2 \tag{8}$$

To determine the solution of d, the equation was multiplied by  $A^TW$  on both sides where W is a weight matrix which is usually called a mask of the neighborhood pixels. Thus the final equation where the velocities vectors are estimated is Equation 9. One major drawback of the algorithm is that the invertibility of the matrix  $A_TWA$  does not always guarantee a correct solution

$$(A^{\mathsf{T}}WA)d = A^{\mathsf{T}}Wb \to \begin{bmatrix} u \\ v \end{bmatrix} = (A^{\mathsf{T}}WA)^{-1}A^{\mathsf{T}}Wb$$

(9)

The serious disadvantage from which L&K suffers is that it can only detect small pixel displacements because of the assumptions made.

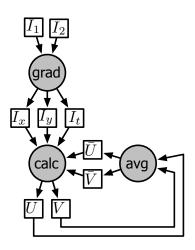

Figure 1: H&S mono-scale iterative scheme

# 2.2.1.2 Multi-scale

The multi-scale L&K method is a solution in order to tackle the bottleneck of the small pixel displacements of the L&K mono-scale algorithm. At first, an image pyramid is constructed for every image, where optical flow is performed. Then, the mono-scale algorithm is applied to every scale and the associated flow vectors are extracted. Since, the pyramid images are down-scaled, the flow vectors of every scale, correspond to larger pixel displacements for the initial image. This way larger pixel displacements are detected. In the end, all the velocity vectors are summed to provide the final velocities [43],[44].

# 2.2.2 Horn and Schunck

#### 2.2.2.1 Mono-scale

The algorithm that we implement and focus in this thesis is the Horn and Schunck (H&S) [45] which is one of the most famous algorithms for optical flow and its scheme is shown in Figure 1. It is also a gradient based algorithm but in contrast to L&K, the global minimum of a function is searched. In [45] an additional assumption was proposed to solve Equation 5 which is that the optical flow should be smooth over the entire image. As a result for every pixel the computed flow in a small neighbourhood is similar. The problem formulation in the case of H&S is described by Equation 10. Parameter  $\alpha$  is a regularization constant. Larger values of  $\alpha$  lead to a smoother flow. Equation 10 can be minimized by solving the associated multi-dimensional Euler–Lagrange equations.

$$\iint [(I_{x}u + I_{y}v + I_{t})^{2} + a^{2}(\|\nabla_{u}^{2}\| + \|\nabla_{v}^{2}\|)]dxdy$$

(10)

By using Cramer's rule the following iterative scheme is derived (Equations 11 and 12) which is used to estimate the optical flow vectors and in Figure 1 is denoted as calc. The mean of the velocities is done with Equations 26 (avg in Figure 1). The derivatives  $I_x$ ,  $I_y$  and  $I_t$  are computed by Equations 13, 14 and 15 (grad in Figure 1).

$$u^{(i)} = \bar{u}^{(i-1)} - I_x \frac{I_x u^{(i-1)} + I_y v^{(i-1)} + I_t}{\alpha^2 + I_x^2 + I_y^2}$$

(11)

$$\nu^{(i)} = \bar{\nu}^{(i-1)} - I_y \frac{I_x u^{(i-1)} + I_y \nu^{(i-1)} + I_t}{\alpha^2 + I_x^2 + I_y^2}$$

(12)

$$I_{x} = \frac{1}{4} (((I_{1}(x + 1, y) - I_{1}(x, y)) + (I_{1}(x + 1, y + 1) - I_{1}(x, y + 1)) + (I_{0}(x + 1, y) - I_{0}(x, y)) + (I_{0}(x + 1, y + 1) - I_{0}(x, y + 1)))$$

(13)

$$I_{y} = \frac{1}{4} (((I_{1}(x, y+1) - I_{1}(x, y)) + (I_{1}(x+1, y+1) - I_{1}(x+1, y)) + (I_{0}(x, y+1) - I_{0}(x, y)) + (I_{0}(x+1, y+1) - I_{0}(x+1, y)))$$

(14)

$$I_{t} = \frac{1}{4} (((I_{1}(x, y) - I_{0}(x, y)) + (I_{1}(x, y + 1) - I_{0}(x, y + 1)) + (I_{1}(x + 1, y) - I_{0}(x + 1, y)) + (I_{1}(x + 1, y + 1) - I_{0}(x + 1, y + 1)))$$

(15)

$$\bar{u} = \frac{1}{12} \begin{pmatrix} 1 & 2 & 1 \\ 2 & 0 & 2 \\ 1 & 2 & 1 \end{pmatrix} * u \qquad \bar{v} = \frac{1}{12} \begin{pmatrix} 1 & 2 & 1 \\ 2 & 0 & 2 \\ 1 & 2 & 1 \end{pmatrix} * v \qquad (16)$$

The advantage of the H&S algorithm is that it yields a high density of flow vectors, i.e. the flow information missing in inner parts of homogeneous objects is filled in from the motion boundaries. On the negative side, it is more sensitive to noise than local methods. TVL1 [46] also belongs in the gradient based algorithm family and it originates from the H&S.

Figure 2: Pyramid of images

#### 2.2.2.2 Multi-scale

Mono-scale optical flow algorithms suffer from limited pixel displacement detection [45]. Nevertheless, many applications such as meteor detection [4] require larger pixel displacement detection and the multi-scale algorithms offer a solution to this problem.

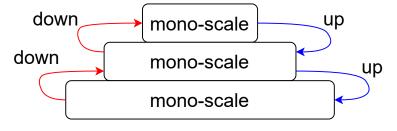

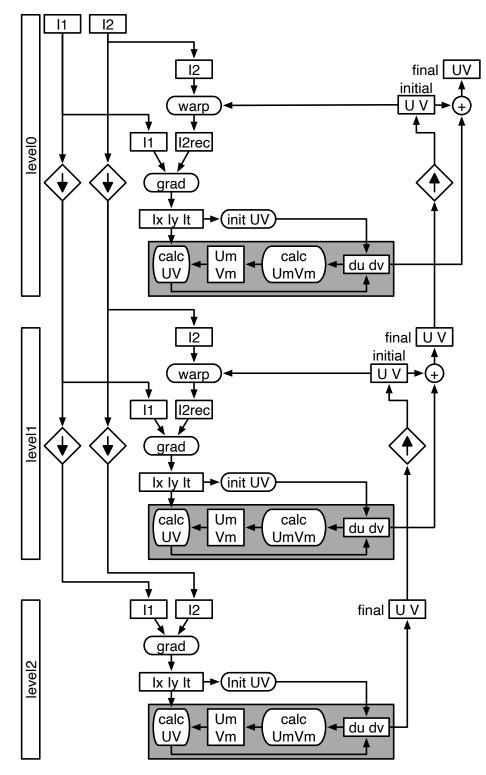

As referred in [45] the mono-scale H&S algorithm is able to detect a flow of one pixel per two consecutive frames. By taking this into account, when down-sampling the image by a specific factor which in our case is 2 and performing the H&S there, the detection might stay the same in this down-sampled scale of the image, but after up-sampling the computed velocities in the initial image size, the displacement is doubled. Considering that, a pyramid of images can be created as shown in Figure 2, whose levels and down-sampling factor can be defined with the aim of increasing the pixel displacement detection.

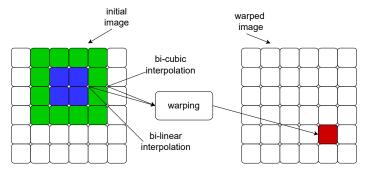

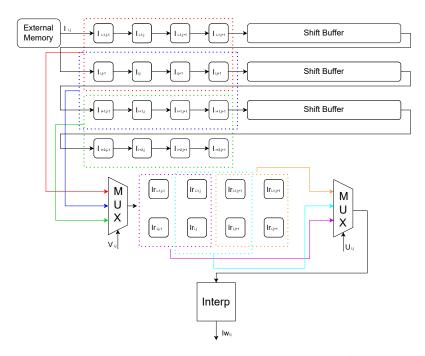

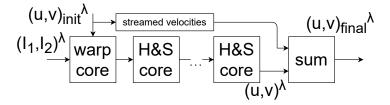

The description of the algorithm is shown in Figure 3. In the beginning, the two consecutive frames are down-sampled in order to create the images of the pyramid. For the down-sampling a five tap Gaussian filter is used. When this procedure has finished, the mono-scale H&S computation is performed iteratively in the smallest image (coarse level of the pyramid). The computed velocities for this level  $((u, v)_{initial}^{\lambda+1})$  of the pyramid are extracted and are up-sampled (up) in order to be used in the next pyramid level. It is of great importance to take into account the motion that was extracted in the previous level, in this level too. Thus, in the beginning of the next level a warping is performed between these pre-computed velocities and the image  $(I_{2rec})$  that will be computed in this level. This is done to compensate the motion because of the previous extracted flow. To implement warping either bi-linear or bi-cubic interpolation is used depending on the accuracy. The same procedure followed in the previous pyramid level is followed in this level too. The only difference is that in the end of the level, the computed velocities from the previous pyramid level and this pyramid level  $((du, dv)_{final}^{\lambda+1})$  have to be accumulated and then up-scaled to be used for the next pyramid warping. In the final pyramid level (fine level) where the initial images are used, the same pattern with the warping and the monoscale kernel is followed. In the end all the velocities from all the levels are accumulated to provide the final computed flow vectors  $((u, v)_{final}^{\lambda+1})$ .

Figure 3: Description of the multi-scale H&S Algorithm

#### 14 OPTICAL FLOW AND EMBEDDED DEVICES

In each pyramid level the displacement detection of pixels is 1. For a three levels pyramid and for a down-sampling factor of 2, the largest total displacement that can be computed is  $\sum_{\lambda=0}^{2} 2^{\lambda} = 7$  pixels. One can choose different down-sampling factors to increase the motion displacement detection but it becomes really complicated for the hardware design [47] and can lead to inaccurate results.

# 2.2.3 Other Optical Flow algorithms

Block methods algorithms are also used for optical flow [48]. There, the operation scheme is based on determining the maximum correlation of a certain area between two frames. The displacement of this area is equivalent to the determined optical flow [43]. The disadvantage of this method is that the analysis is predetermined to characteristic points. This ultimately can lead to sparse flow but with the advantage of being more prone to errors.

In [49] it is analyzed how phase and frequency are used for estimating the velocity flow. There, they make use of the fact that phase is more robust compared to the amplitude with changes in contrast, scale, orientation and speed. For the analysis Gabor filters and Fourier transform is applied in the signals. The biggest disadvantage of this method is the heavy computational effort that has to be performed.

During the last few years neural networks and especially deep neural networks (DNN) are used for the extraction of the optical flow. These approaches excel in the accuracy of the detection but they require sophisticated training and huge computational effort. More precisely in [50] the FlowNet neural network was presented. Convolutional neural networks are known to be very efficient at learning input relations given enough data for training. Thus, in the work of [50] they follow an end to end learning approach to predict optical flow which is to start with a given data set consisting of image pairs and ground truth flows which they use to train their network to predict the x and y flows directly from the images. In order to perform the optical flow they create two separate, yet identical processing streams for the two images and then they combine them at a later stage in the neural network in order to extract the flows. In [6] the new improved version of FLowNet is presented where they solve the problems of small displacements and noisy artifacts in estimated flow fields. They do that by firstly using more sophisticated data sets to train their networks. They introduce a warping operation and show how stacking multiple networks using this operation can significantly improve the results. Finally, they focus in small displacement of pixels by introducing real problem data sets to achieve that. In LiteFlowNet2 and LiteFlowNet3 [51],[52] regularisation is used to reduce the influence of noise and smooth the flow, while conserving the edges. In SpyNet [51],[53] a pyramid of images is used and small sized network for each scale which is trained independently. There, the learned convolution filters appear similar to classical spatio-temporal filters, giving insight into the method and how to improve it. However, since they compute many pyramid scales there is the possibility of loosing objects when the image is down-scaled.

# 2.2.4 Advantages and disadvantages of each algorithm

The neural networks are able to compute the optical flow with the best accuracy compared to all the other state of the art works. The drawback they have, is the enormous computation cost and the very high computation time they require for large images. The same happens with the block matching algorithms, although the accuracy they achieve is lower related to the neural networks. H&S and L&K are ideal for implementing in embedded devices because of their computation patterns. Nevertheless, the accuracy of the mono-scale version is deteriorated compared to other state of the art algorithms. Thus, the multi-scale version is considered which is able to improve drastically the accuracy and detect large pixel movements. The advantage of the H&S algorithm compared to L&K is that it is a 100% dense algorithm which means that the optical flow is detected in the whole image and not locally as in the L&K case.

In the next subsection we will present the state of the art of optical flow in embedded devices.

# 2.3 OPTICAL FLOW IN EMBEDDED DEVICES

Despite the impressive accuracy the DDNs achieve in computing the optical flow, their computations demands make it really challenging to implement in embedded devices. In [6] they implement in the Nvidia GTX 1080 GPU the FlowNet2 and they present a trade off between accuracy and FPS (Frames per Second). The highest FPS they achieve is 123 but for small image sizes and with limited accuracy of detection even in this powerful GPU. A recent work in implementing neural networks for optical flow in FPGAs is presented in [8]. In their work they use a multiplexing binary neural network (BNN) which is less demanding computation wise, instead of a CNN, for pyramidal feature extraction and they make the design independent of the pyramidal level number. They achieve impressive accuracy in the Middlebury data set [54], but there are no information about the resources utilization of the FGPA. The FPS they achieve for the image size they considered is deteriorated compared to other optical flow designs in embedded systems. Furthermore, a correlation is not presented between hardware utilization and throughput to see how it scales.

Many embedded works design the L&K for the optical flow detection. In [55] they use the Nvidia Jetson CPU (only the ARM CPU and not the GPU) to accelerate the L&K. They optimize the throughput with respect to the energy consumption. They also include an implementation on a Nvidia Tegra AGX in order to increase the throughput. Their design which also includes the TVL1 achieves an FPS of 25 for an image size of 960×540 pixel. In [56] they design a multi-scale L&K in a custom processor in the Artix XC7A100T-CSG324 Xilinx FPGA and in an ASIC with a 40 nm CMOS implementation. In order to increase the accuracy they implement a 4 levels pyramid but the FPS they achieve is

only 5 for a 640x480 pixel image. Their design is not scaling for larger images too. In [57] the Texas Instruments C66x, a 10 Watt embedded digital signal processor (DSP) is used for the acceleration of a pyramidal L&K. They perform an exploration concerning the number of cores needed to compute different images sizes and different iterations for a 4 levels pyramid. In [58] they use a CPU-GPU (Core 2 Quad 2.83GHz CPU and an NVidia GeForce GTX285 GPU) for the implementation of the L&K image registration algorithm for 3D computational platform stabilisation. They manage to compute 30 FPS for a 512×512×2 region of interest. In [44] the L&K is again implemented on a Titan GPU for very large image size of 3840x2160 pixels. They achieve real time computation but there are no information about accuracy. [59] design a L&K in a Virtex 6 FPGA. Their work is mainly focused on reducing the demand of external memory bandwidth of the image. They achieve that by compressing the image when they write it to the external memory. Then when they process the image they up-sample it with as much as possible minimum loss of accuracy. They perform an exploration regarding the wordlength of the data but since they use the mono-scale version their accuracy of detection is not very competitive compared to other state of the art works. In their resources utilization there is a slight increase due to the compression of the image. In [60] the authors present a mono and a multi-scale implementation of the L&K algorithm in the Virtex 4 FPGA. They explore different arithmetic formats such as fixed or floating point and they parallelize their code to increase the throughput. They perform warping in each pyramid level which highly reduces their computation speed since they want to make the design to use as less hardware as possible. The final L&K implementation which we will refer to is the one of [61]. They achieve the highest throughput of all the other state of the art works for an image with size 1024x1024 pixels. Their working clock frequency is only 90 MHz which is very impressive. However, they use two FPGAs to make the computation, one for the handling of the inputs and one for the computation of the algorithm. Some parts of the algorithm are also performed in a power PC. That is why we believe they achieve an impressive throughput. Finally, in their work there are no information about the accuracy of their algorithm.

[62] is implementing a hierarchical block matching-based optical flow algorithm in the Virtex 7 FPGA. The accuracy they achieve is higher compared to other state of the art works in FPGAs as they use a multi-scale algorithm. However, the demand of the algorithm is huge in terms of Block RAMs especially when images larger that 640x480 pixel are considered. This happens because they use on-chip memory as blocks where they store the data which they want to process to extract the flow vectors. When the number of blocks is increased with the aim of improving the accuracy of the detection, the throughput is significantly decreased due to the huge computation demand.

A multi-scale, multi-orientation phase based algorithm is employed by [63] on a Virtex 4 FPGA. For the implementation they use various fixed point formats and they warp the images in the different pyramid levels to increase accuracy. They have 4 pyramid levels

and they perform the optical flow in 640x480 pixel images. However, they do not include enough information about accuracy and they do not present how their design scales up in terms of throughput.

Along with L&K, H&S is the most famous algorithm which is implemented widely in embedded devices. [64] designed a mono-scale H&S on the Jetson TK1 board. They applied various optimizations, such as half precision IEEE arithmetic format, SIMD and various pipeline patterns. They tried also different iteration numbers and different image sizes. They achieved 25 frames per second for up to 8Mpix images for 0.35J per image. There were no information provided for the impact of the arithmetic format in the quality of the detection. [3] is using the Jetson AGX Xavier GPU for the implementation and it achieves remarkable throughput for large images by using half precision floating point and an alternative pipeline pattern. [65] is implementing the same algorithm but on an FPGA. The computation time their algorithm needs is very high compared to other state of the art works. They also store the intermediate computed velocities in the Block RAMs which leads to huge cost of on chip memory or the ability to compute only small images. [66] on the other side is able to compute full HD images with a throughput of 283 MPixel/sec. However, it is not using techniques to reduce the resources utilization or to provide a scalable architecture which would fit in a smaller FPGA than the one it is using. There are no information regarding the accuracy achieved too. [67] is implementing exactly the same algorithm and it also achieves impressive throughput compared to other state of the art works. However compared to [66], they deal with the iterations number, the floating or fixed point format and the convergence. Moreover, they claim that in order to detect large pixel displacements they perform the mono-scale algorithm very fast. The last two works are not exploring the trade-offs that have to be made between the external memory bandwidth and the on chip memory. [43] is implementing a multi-scale H&S algorithm on the ZCU 104 platform. The pyramid's levels are two and for the motion compensation the bi-linear interpolation. The throughput they achieve is very high but this comes with an important cost in the DSPs units of the FPGA. They use both vectorization and deep pipeline techniques to accelerate the algorithm. They use fixed point arithmetic and a simple convolution algorithm to down-sample the images. However, since they use two pyramid levels the accuracy is reduced compared to previous state of the art works with more scales. Furhtermore, they perform the interpolation in the end of the pipeline of each pyramid level and then they create the new image for the fine level. This also affects negatively the accuracy. Finally, as all the previous H&S designs in FPGAs they use computation reuse for the derivatives.

In this thesis we will explore and implement the multi-scale H&S algorithm in FPGAs. We believe that since the previous state of the art works focus solely either on the accuracy or the throughput part, there should be a work which would offer a clear trade off between them. The multi-scale H&S is the kind of algorithm which offers this advantage as it can be tuned in many ways.

#### 2.4 DIFFERENT COMPONENTS OF THE MULTI-SCALE H&S

In Figure 3 the different blocks that form the described algorithm in this thesis are presented. The hierarchical H&S algorithm is a multi-rate image processing algorithm [68] which consists different processing units.

The mono-scale H&S kernel is an Iterative Stencil Loop (ISL) algorithm. ISL is a kind of algorithms where a grid is iteratively updated cell by cell according to a multidimensional local fixed input array from the starting grid. Usually, the computation is done for all the cells of the grid for iteration i - 1 before calculating all the cells for iteration i. Instead of doing the computation with all the grid there is a possibility to compute a subset of cells for the grid in iteration i - 1 in order to calculate some adequate cells for the iteration i. Each approach has a different impact in the implementation as we will describe in the next sections.

There are already a lot of works optimizing the above kind of algorithms especially for CPU and GPUs [69]–[74] in terms of parallelism, efficient blocking to reduce memory bandwidth and data locality.

More recently, for FPGAs, there was a great effort to optimize the ISL. These works [66], [67], [75]-[78] take advantage of the deep pipeline approach between consecutive iterations in a similar way as proposed by [79], [80] who also performs the acceleration with the help of OpenCL. Sano [81] in his work combines the deep pipeline and the parallel approaches in multi-FPGA architectures. Zohouri [82], [83] combined temporal and spatial parallelism targeting 2D and 3D iterative stencils in order to deal with different input sizes. In his work, shift registers were used as on-chip buffers to provide the PEs with the adequate data. A similar strategy with [79] was followed by Dest [84] and Chi [85], [86]. Chi proposed a design framework which also solves the problem of halo regions in iterative stencil computations. Nacci [87] followed a different approach compared to the aforementioned works. Instead of doing the computation frame by frame for all the  $c_a$ points of the grid (in a current iteration), he takes advantage of the fact that  $c_a$  need only a neighborhood of  $c_{a-1}$  to be computed. He performs the desired processing by repeatedly applying a cone to portions of the input matrix. In that way he reduces the external memory bandwidth rate with an overhead for on chip memory and computation time. A similar approach was also followed by [88], [89]. Waidyasooriya in his work [90] uses Multi-FPGAs architectures and OpenCL to accelerate Stencil Computation and he also targets very large inputs which he handles with spatial pipelining. Finally, in the work of [91] there is a description of how stencil computation should be handled with high level synthesis tools.

Warping, with the appropriate designing can be considered as a stencil algorithm. The same happens with the down-sampling and the up-sampling core. Still, with the last two algorithms there is a fundamental difference. The input rate of the two algorithms is different from the output rate they produce. This makes them multi-rate algorithms.

| algorithm | Accuracy                                      | Image Size                                                                                                     | throughput                                    | Resources                                     | Tunability                       |

|-----------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|----------------------------------|

| H&S [66]  |                                               | $\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{\sqrt{$ |                                               |                                               | $\checkmark$                     |

|           | NA                                            |                                                                                                                |                                               |                                               |                                  |

| H&S [67]  | $\checkmark$                                  | $\checkmark$                                                                                                   | $\checkmark$                                  | $\checkmark\checkmark$                        | $\checkmark$                     |

| H&S [95]  | $\checkmark$                                  | $\checkmark$                                                                                                   | $\checkmark\checkmark$                        | $\checkmark\checkmark$                        | $\checkmark$                     |

| H&S [96]  | $\checkmark$                                  | $\checkmark$                                                                                                   | $\checkmark\checkmark\checkmark$              | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                     |

| MH&S [43] | $\checkmark\checkmark$                        | $\checkmark$                                                                                                   | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark\checkmark\checkmark$              | $\checkmark\checkmark\checkmark$ |

| L&K [59]  | $\checkmark\checkmark$                        | $\checkmark\checkmark$                                                                                         | $\checkmark\checkmark$                        | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                     |

| L&K [61]  | NA                                            | $\checkmark$                                                                                                   | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                                  | $\checkmark\checkmark$           |

| L&K [97]  | $\checkmark$                                  | $\checkmark\checkmark\checkmark$                                                                               | $\checkmark\checkmark$                        | $\checkmark\checkmark$                        | $\checkmark$                     |

| ML&K [43] | $\checkmark\checkmark$                        | $\checkmark$                                                                                                   | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark\checkmark\checkmark$              | $\checkmark\checkmark$           |

| ML&K [60] | $\checkmark\checkmark$                        | $\checkmark\checkmark$                                                                                         | $\checkmark$                                  | $\checkmark\checkmark$                        | $\checkmark$                     |

| ML&K [43] | $\checkmark\checkmark$                        | $\checkmark$                                                                                                   | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark\checkmark\checkmark$              | $\checkmark\checkmark\checkmark$ |

| MPB [47]  | $\checkmark\checkmark$                        | $\checkmark\checkmark$                                                                                         | $\checkmark$                                  | $\checkmark\checkmark$                        | $\checkmark$                     |

| HBM [62]  | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                                                                                                   | $\checkmark$                                  | $\checkmark\checkmark$                        | $\checkmark$                     |

| DNN [8]   | $\checkmark \checkmark \checkmark \checkmark$ | $\checkmark$                                                                                                   | $\checkmark\checkmark$                        | NA                                            | NA                               |

Table 1: Advantages of the FPGA State of the Art Works

Multi-rate algorithms are widely used in image processing pipelines and a lot of research groups concentrate their efforts on optimizing these kind of algorithms. In [92] [93] [94] they are using static scheduling for accelerating the aforementioned kind of algorithms. Despite the benefits of static scheduling there are no FPGA image processing compilers that can statically schedule realistic size multi-rate applications and they are relying on on the inter-stage FIFO approach which highly increases the usage of Block RAMs and decreases the throughput. There is not also the option of vectorizing the computation with the aim of increasing the throughput. The only work which concentrates on accelerating multi-rate algorithms for FPGAs is the one of [68]. In their work they effectively pipelining stencils with different rates and they try to keep the resources usage low. However, they do not take into account the external memory reads and writes which highly impacts the throughput. They also do not explore the different trade-offs that have to be explored between the external memory interaction and the Block RAMs.

#### 2.5 DISCUSSION ON THE STATE OF THE ART IN FPGAS

Since in this thesis we are designing the optical flow multi H&S in an FPGA, it is important to summarize what other state of the art works are lacking and why our work is essential.

#### 20 OPTICAL FLOW AND EMBEDDED DEVICES

In table 1 we are presenting the strong points of the state of the art FPGA implementations. In this table, we include information about the algorithm used, the image size, the throughput, the FPGA resources utilization and the tunability, meaning from how many options the designer can choose in order to tune the design according to its needs. For example, if there is the option to parallelize the design or to use fewer hardware in order to compute the flow in real time. We grade the strength of each implementation in each domain. We can see from this table that the DNN implementation and the hierarchical block matching implementations achieve the best accuracy detection of the optical flow. Especially the DNN design achieves the highest accuracy between all the state of the art works in the Middlebury data set of images [54]. We also see that the mono-scale H&S designs achieve remarkable throughput but the work of Ishii[61] is achieving the highest throughput among all works for a mono-scale L&K algorithm. Nevertheless he uses two FPGAs for some part of the computation of the algorithm. [43] is implementing multi-scale H&S and L&K algorithms and it performs less iterations in the finest level which highly increases throughput. The gradient based designs are able to compute large images, while this is not the case for HBM and DNNs. Most of the works do not offer tunable designs which can fit to smaller FPGA devices, something we consider very important as with limited resources, still real time processing can be achieved with acceptable accuracy. Finally, it is important to point out, that designs with high accuracy are unable to compute the optical flow with high throughput for large images.

#### 2.6 CONCLUSION

In the beginning of the second chapter of this thesis we have made an introduction to the optical flow algorithms. The definition of the optical flow was given. Different algorithms were presented and the advantages and disadvantages of each one of them were given. Their implementation in embedded devices was discussed and it was pointed out how demanding it is to design effective optical flow algorithms for them. We described the multi-scale H&S algorithm which is the optical flow algorithm we will explore and design in this thesis. The key characteristics of the algorithm were explained and the main challenges that we have to overcome in order to have a sustainable architecture. We referred on how other state of the art works dealt with these challenges and why there is a need for a new FPGA optical flow design dealing with all the factors that impact the design.

In the third chapter we will explore the accuracy of the multi-scale algorithm. We will see why the mono-scale architecture is not enough for detecting the optical flow and how other various factors impact the accuracy. We will use smaller arithmetic formats and we will use a very known sequence of images to evaluate our work.

#### ACCURACY

# 3

An increase in the word length of the data representation usually leads to an improvement in the extracted information from a computer vision algorithm and better precision for the human eye as it is able to detect the difference in accuracy of the pixels of the image. A fundamental part when designing image processing algorithms for embedded applications is the precision of the value representing the pixels of the image compared to a ground truth [54] and it has a key impact on the image quality level which the design achieves [98]. Addressing the issue of accuracy of the observed scene in optical flow is tremendously challenging and it requires careful steps and considerations [99]. Accuracy in optical flow depends on the observed scene, however in any case the accuracy can be augmented with careful handling of certain parameters of the design. In this chapter, an accuracy exploration analysis will be performed regarding the optical flow Hierarchical Horn and Schunck algorithm. Several factors are essential for the tracking of the accuracy in a multi-scale algorithm. Thus, the exploration will include different factors of the algorithm, such as the number of the pyramid levels, the iterations number in each pyramid level and the interpolation algorithm for the warping. As reducing the number of iterations play a significant role in throughput, in this chapter the impact it has in accuracy and convergence will be explored. Embedded applications usually demand the hardware to remain low in order be sustainable in terms of resources usage design. Since we are talking about embedded applications, the impact of reducing the arithmetic format will be explored [100],[101]. Consequently, in this thesis a deep exploration is performed in the multi-scale algorithm concerning the arithmetic formats which to the best of our knowledge has never been done before for a pyramid algorithm. For the exploration results the Arria 10 Han Pilot Platform was used and the components were designed with the help of the FloPoCo library [102]. Since decreasing the data size, decreases the stretching of the external memory bandwidth which potentially leads to higher throughput, the possibility of using smaller arithmetic formats in the last scale of the image which takes the longest time is explored in terms of the accuracy. Finally, a thorough comparison will be made with the state of the art and the most known sequence of images will be used for fair comparisons[54]. The first section will be about the evaluation metrics which are widely used in the literature to compare the different designs[97],[67].

#### 3.1 EVALUATION METRICS

The optical flow is computed between two images. For evaluating the accuracy of the optical flow, it have to be compared with a reference value[98],[103]. However, evaluating the result is subjective, it depends on the observed scene but also on the application where optical flow is used[104],[105]. Nevertheless, by comparing our results with the rest state of the art designs, we can get an idea if our accuracy is acceptable on a very common data set. In order to do a fair comparison of the result with other state of the art works, certain metrics that are used widely will be used in this thesis too.

#### 3.1.1 Peak Signal to Noise Ratio

The Peak Signal to Noise Ratio (PSNR) metric defined by Equation 18, computes the peak signal-to-noise ratio, in decibels, between two images[106],[107]. The higher the PSNR is, the better the quality of the optical flow is. The Maximum Square Error (MSE) [108],[109] which is shown in Equation 17 represents the cumulative squared error between the two images, whereas PSNR represents a measure of the peak error. The lower the value of MSE is, the lower the error is.