# A design space exploration approach to jointly optimize security and schedulability in TSP systems

Ill-Ham Atchadam

# ▶ To cite this version:

Ill-Ham Atchadam. A design space exploration approach to jointly optimize security and schedulability in TSP systems. Software Engineering [cs.SE]. Université de Bretagne occidentale - Brest, 2023. English. NNT: 2023BRES0006. tel-04198835

# HAL Id: tel-04198835 https://theses.hal.science/tel-04198835

Submitted on 7 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

# L'UNIVERSITE DE BRETAGNE OCCIDENTALE

ECOLE DOCTORALE N° 644 Mathématiques et Sciences et Technologies de l'Information et de la Communication en Bretagne Océane Spécialité : Informatique et architectures numériques

# Exploration d'architectures logicielles pour les systèmes critiques partitionnés sécurisés

Thèse présentée et soutenue à Brest, le 12/01/2023 Unité de recherche : Lab-STICC UMR CNRS 6285

#### Rapporteurs avant soutenance :

Liliana CUCU-GROSJEANDirectrice de recherche, INRIAJérôme HUGUESSenior Researcher, Carnegie Mellon University

# **Composition du Jury :**

| Président :<br>Examinateurs : | Emmanuel GROLLEAU<br>Liliana CUCU-GROSJEAN<br>Jérôme HUGUES<br>Antonio CASIMIRO<br>Yvon KERMARREC | Professeur des Universités, ENSMA<br>Directrice de recherche, INRIA<br>Senior Researcher, Carnegie Mellon University<br>Associate Professor, Université de Lisbonne<br>Professeur des Universités, IMT Atlantique |

|-------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Encadrant :                   | Frank SINGHOFF<br>Laurent LEMARCHAND<br>Hai Nam TRAN                                              | Professeur des Universités, Université de Bretagne Occidentale<br>Maître de conférences, Université de Bretagne Occidentale<br>Maître de conférences, Université de Bretagne Occidentale                          |

# Remerciements

Je souhaite exprimer ma gratitude envers tous ceux qui ont contribué à la réalisation de ma thèse.

Tout d'abord, je remercie les membres du jury pour leur temps, leur expertise et leur évaluation minutieuse de mon travail. Je remercie particulièrement Pr. Emmanuel Grolleau pour avoir accepté d'être le président du jury. Je tiens à remercier Dr Liliana Cucu-Grosjean et Senior Researcher Jérôme Hugues pour le temps qu'ils ont consacré à la relecture de ma thèse et leur contribution en tant que rapporteurs. J'exprime également ma gratitude envers Dr. Antonio Casimiro et Pr. Yvon Kermarrec pour avoir accepté d'examiner ma thèse.

Je tiens à exprimer toute ma gratitude et ma reconnaissance envers mon directeur de thèse, Pr. Frank Singhoff, et mes encadrants de thèse, Dr. Laurent Lemarchand et Dr. Hai Nam Tran, pour leur implication, leur patience, leur expertise et leur encouragement constant. Votre investissement personnel, votre expertise et votre soutien ont été inestimables tout au long de ce processus et ont constitué une source de motivation. Je suis reconnaissante de la chance que j'ai eue de travailler avec vous et j'ai énormément appris à vos côtés.

Je remercie tous mes collègues du Lab-STICC et de l'Université de Bretagne Occidentale, en particulier Bismark, Camélia, Grace, Julien, Libey, Morgan, Aymeric, Mayssa et Mourad. Je suis également reconnaissante envers les personnes avec lesquelles j'ai eu l'occasion de travailler : K. Bigou, D. Massé, J. Rivière, V. Marc, S. Rubini, P. Le Parc, et P. Ballet.

Je tiens à remercier tous mes amis qui ont été à mes côtés tout au long de ce parcours, pour leurs conseils et leur soutien moral. En particulier, Camara Sekou Oumar, Bouchra Ettahiri et Bachiratou Sahm pour leur aide lors de la préparation de ma soutenance.

Enfin, je tiens à exprimer ma gratitude envers ma famille pour leur amour indéfectible et leur soutien inconditionnel. En particulier, mes parents, mes frères Manaf et Alim qui n'ont jamais cessé de croire en moi. Vos encouragements et votre soutien moral ont été une source d'inspiration pour moi et m'ont aidé à atteindre ce jalon malgré les défis auxquels j'ai été confrontée.

# Contents

| 1      | Intr | oducti | ion                                                             | 15        |

|--------|------|--------|-----------------------------------------------------------------|-----------|

|        | 1.1  | Introd | uction                                                          | 15        |

|        | 1.2  | Proble | em statement                                                    | 16        |

|        | 1.3  | Contri | ibution                                                         | 17        |

|        |      | 1.3.1  | A PAES based DSE approach for unicore execution plate-<br>forms | 18        |

|        |      | 1.3.2  | Extension of the DSE approach to Multicore execution platforms  | 19        |

|        |      | 1.3.3  | Implementation and evaluations                                  | 19        |

|        | 1.4  | Thesis | organization                                                    | 19        |

| I<br>2 |      | ate of | f art<br>systems                                                | 21 $23$   |

| 4      | 2.1  |        | tions and classification                                        | <b>23</b> |

|        | 2.1  | 2.1.1  | Definitions                                                     | 23        |

|        |      | 2.1.2  | Classification                                                  | 24        |

|        | 2.2  | Real-7 | Fime architecture                                               | 25        |

|        |      | 2.2.1  | Hardware platform                                               | 26        |

|        |      | 2.2.2  | Real-time software application layer                            | 27        |

|        |      | 2.2.3  | Real-time Operating System                                      | 34        |

|        | 2.3  | Real-t | ime scheduling analysis                                         | 37        |

|        |      | 2.3.1  | Feasibility and schedulability                                  | 37        |

|        |      | 2.3.2  | Scheduling analysis methods                                     | 38        |

|        | 2.4  | Conclu | usion                                                           | 41        |

# Contents

| 3 | Hie | rarchical real-time systems                                                  | 43        |

|---|-----|------------------------------------------------------------------------------|-----------|

|   | 3.1 | Definitions and characteristics                                              | 43        |

|   | 3.2 | Resource model                                                               | 46        |

|   |     | 3.2.1 Periodic resource model                                                | 47        |

|   |     | 3.2.2 Bounded delay resource                                                 | 47        |

|   | 3.3 | Time and space partitioning (TSP) and integrated modular avion-<br>ics (IMA) | 48        |

|   | 3.4 | ARINC 653                                                                    | 49        |

|   |     | 3.4.1 Hardware                                                               | 49        |

|   |     | 3.4.2 Software                                                               | 50        |

|   | 3.5 | Examples of hypervisors/operating systems for TSP systems                    | 54        |

|   |     | 3.5.1 PikeOS                                                                 | 54        |

|   |     | 3.5.2 Xtratum [1]                                                            | 56        |

|   |     | 3.5.3 POK                                                                    | 57        |

|   |     | 3.5.4 LynxSecure                                                             | 58        |

|   | 3.6 | Conclusion                                                                   | 58        |

| 4 | Sec | urity                                                                        | 61        |

|   | 4.1 | Security properties                                                          | 61        |

|   | 4.2 | Security models                                                              | 64        |

|   | 4.3 | Security architecture                                                        | 66        |

|   |     | 4.3.1 MILS classification                                                    | 67        |

|   |     | 4.3.2 MILS architecture                                                      | 67        |

|   | 4.4 | Conclusion                                                                   | 70        |

| 5 | Mu  | lti-objective optimization                                                   | <b>71</b> |

|   | 5.1 | Definitions and characteritics                                               | 71        |

|   | 5.2 | Scalarization based multi-objective optimization                             | 74        |

|   |     | 5.2.1 Weighted sum method                                                    | 74        |

|   |     | 5.2.2 $\varepsilon - constraints$ method                                     | 74        |

|   |     | 5.2.3 Goal programming                                                       | 75        |

|   | 5.3 | Direct approaches for multi-objective optimization                           | 76        |

|   |     | 5.3.1 Multi-objective evolutionnary algorithms                               | 77        |

|   | 5.4 | Conclusion                                                                   | 86        |

| Π  | V   | Vork orientations and positioning                                                                              | 87  |

|----|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 6  | Wo  | k orientations and positioning                                                                                 | 89  |

|    | 6.1 | System model, security and schedulability assumptions                                                          | 89  |

|    | 6.2 | Assumptions on security implementation                                                                         | 90  |

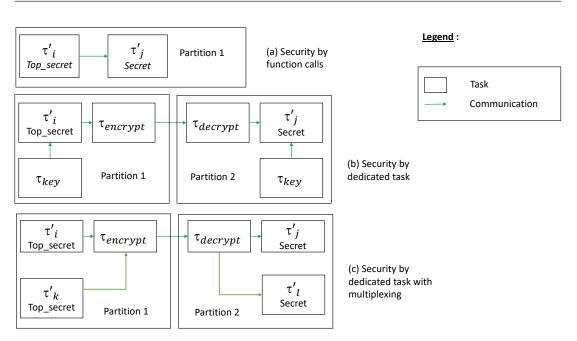

|    |     | 6.2.1 Securing communications through function calls                                                           | 92  |

|    |     | 6.2.2 Securing communications through dedicated tasks                                                          | 93  |

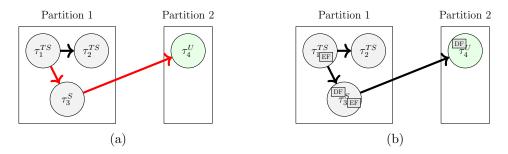

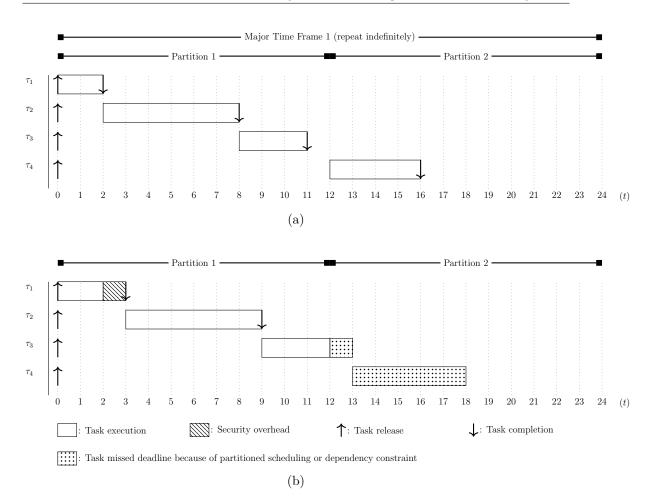

|    | 6.3 | Security and scheduling: trade-off in TSP systems                                                              | 95  |

|    | 6.4 | Related work                                                                                                   | 98  |

|    | 6.5 | Summary of expected contributions                                                                              | 100 |

|    | 6.6 | Conclusion                                                                                                     | 101 |

| II | I   | Contributions 10                                                                                               | 03  |

| 7  | Des | ign space exploration to secure unicore TSP systems 1                                                          | .05 |

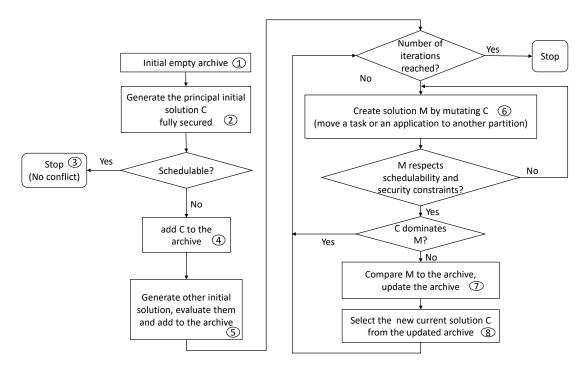

|    | 7.1 | PAES general framework for schedulability and security trade-off . $\ensuremath{1}$                            | 105 |

|    | 7.2 | PAES adaptation to the MOOP of schedulability and security $\ . \ . \ 1$                                       | 107 |

|    |     | 7.2.1 Objective functions and constraints                                                                      | 107 |

|    |     | 7.2.2 Feasibility tests                                                                                        | 109 |

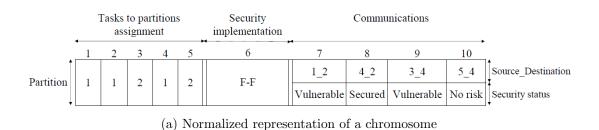

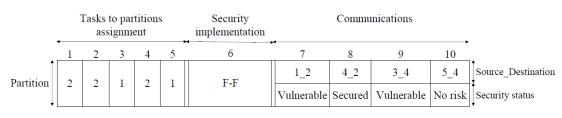

|    |     | 7.2.3 Solutions encoding $\ldots \ldots $       | 110 |

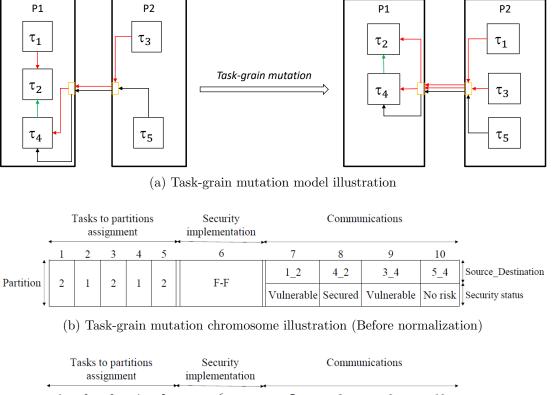

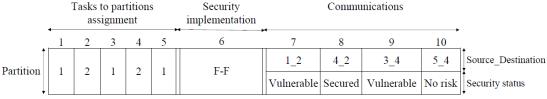

|    |     | 7.2.4 Mutation operator $\ldots \ldots $ | 114 |

|    |     | 7.2.5 Mutation algorithm improvement $\ldots \ldots \ldots \ldots \ldots \ldots 1$                             | 120 |

|    |     | 7.2.6 Initial solutions and archiving process adaptation $\ldots$ 1                                            | 121 |

|    | 7.3 | Conclusion                                                                                                     | 121 |

| 8  | Exp | eriments and evaluations 1                                                                                     | .23 |

|    | 8.1 | Experiment 1: illustration with a flight controller application $1$                                            | 123 |

|    |     | 8.1.1 Conditions of experiment                                                                                 | 124 |

|    |     | 8.1.2 Results                                                                                                  | 125 |

|    | 8.2 | Experiment 2: illustration with a flight controller and JPEG applications                                      | 125 |

|    |     | 8.2.1 Conditions of experiment                                                                                 | 125 |

|    |     | 8.2.2 Results                                                                                                  | 126 |

# Contents

|   | 8.3                | -                                                                                                                | iments 3-6: illustration with a flight controller, multimedia application, CFAR and autopilot applications | 130                                                                                                                                                                    |

|---|--------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

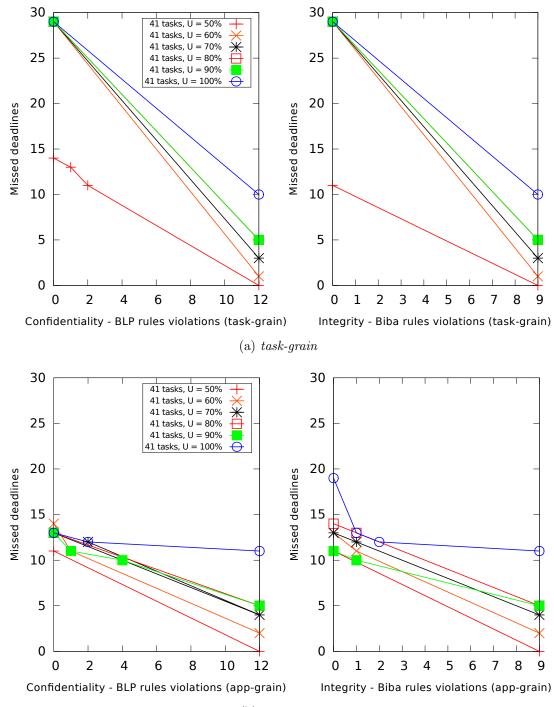

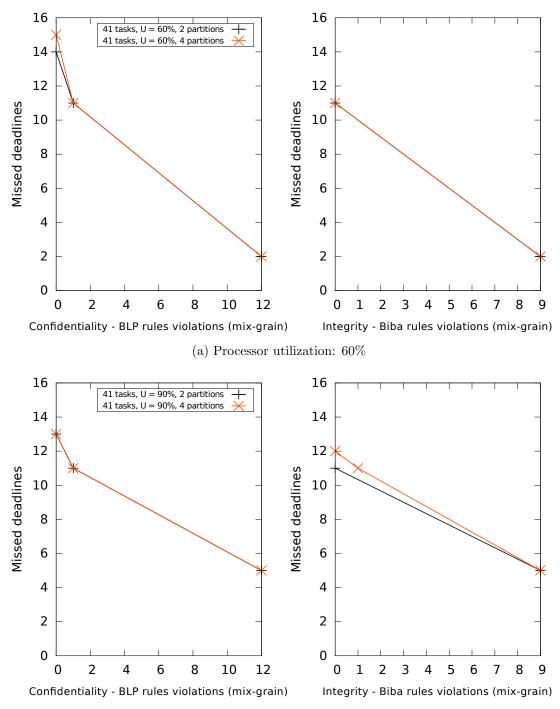

|   |                    | 8.3.1                                                                                                            | Experiment 3: result of PAES when varying processor uti-<br>lization                                       | 131                                                                                                                                                                    |

|   |                    | 8.3.2                                                                                                            | Experiment 4: results of PAES when considering intra-<br>partition communications non-vulnerable           | 133                                                                                                                                                                    |

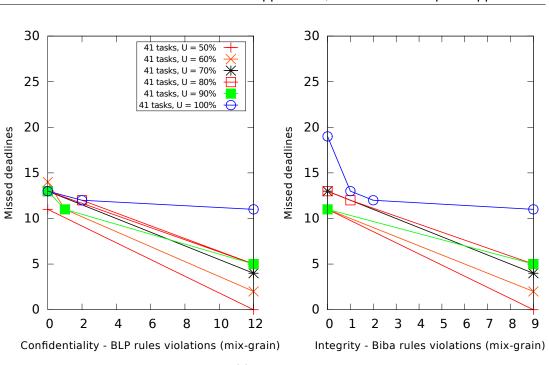

|   |                    | 8.3.3                                                                                                            | Experiment 5: results of PAES with variation of the max-<br>imum number of partitions from 2 to 4          | 135                                                                                                                                                                    |

|   |                    | 8.3.4                                                                                                            | Experiment 6: results of PAES while considering APEX calls execution times given in SFPBench [2]           | 138                                                                                                                                                                    |

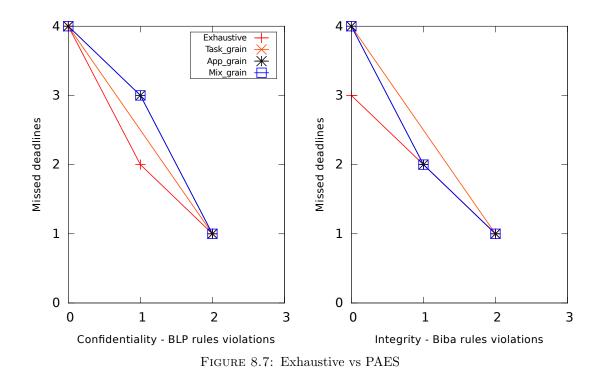

|   | 8.4                | Exper<br>solutio                                                                                                 | iment 7: comparison of our PAES tool results vs. exact<br>ons                                              | 140                                                                                                                                                                    |

|   |                    | 8.4.1                                                                                                            | Conditions of experiment                                                                                   | 140                                                                                                                                                                    |

|   |                    | 8.4.2                                                                                                            | Results                                                                                                    | 141                                                                                                                                                                    |

|   | 8.5                | Concl                                                                                                            | usion                                                                                                      | 142                                                                                                                                                                    |

| _ |                    |                                                                                                                  |                                                                                                            |                                                                                                                                                                        |

| 9 |                    | sign sp<br>tems                                                                                                  | ace exploration for safe and secure Multi-core TSF                                                         |                                                                                                                                                                        |

| 9 |                    | tems                                                                                                             | ace exploration for safe and secure Multi-core TSF round and system model                                  | 145                                                                                                                                                                    |

| 9 | syst               | tems                                                                                                             |                                                                                                            | <b>145</b><br>146                                                                                                                                                      |

| 9 | syst               | t <b>ems</b><br>Backg                                                                                            | round and system model                                                                                     | <ul><li>145</li><li>146</li><li>146</li></ul>                                                                                                                          |

| 9 | syst               | tems<br>Backg<br>9.1.1                                                                                           | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>146</li> <li>147</li> </ol>                                                                                                         |

| 9 | syst               | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3                                                                         | round and system model                                                                                     | <ul><li>145</li><li>146</li><li>146</li><li>147</li><li>148</li></ul>                                                                                                  |

| 9 | syst<br>9.1        | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3                                                                         | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> </ol>                                                                               |

| 9 | syst<br>9.1        | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES                                                                 | round and system model                                                                                     | <ul> <li>145</li> <li>146</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> </ul>                                                                  |

| 9 | syst<br>9.1        | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1                                                        | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> </ol>                                                                  |

| 9 | syst<br>9.1        | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1<br>9.2.2                                               | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> </ol>                                                                  |

| 9 | syst<br>9.1        | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4                             | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> <li>151</li> <li>153</li> </ol>                                        |

| 9 | syst<br>9.1<br>9.2 | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4                             | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> <li>151</li> <li>153</li> <li>154</li> </ol>                           |

| 9 | syst<br>9.1<br>9.2 | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>Test c                   | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> <li>151</li> <li>153</li> <li>154</li> </ol>                           |

| 9 | syst<br>9.1<br>9.2 | tems<br>Backg<br>9.1.1<br>9.1.2<br>9.1.3<br>PAES<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>Test c<br>9.3.1<br>9.3.2 | round and system model                                                                                     | <ol> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>149</li> <li>149</li> <li>150</li> <li>151</li> <li>153</li> <li>154</li> <li>155</li> <li>156</li> </ol> |

| 10 Tool design and implementation                                              | 161 |

|--------------------------------------------------------------------------------|-----|

| 10.1 Cheddar framework                                                         | 161 |

| 10.1.1 Cheddar Architecture Description Language (ADL) $$ .                    | 161 |

| 10.2 Cheddar scheduling analyzer                                               | 168 |

| 10.2.1 Design of a model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 168 |

| 10.2.2 Scheduling simulation                                                   | 168 |

| 10.2.3 Feasibility tests                                                       | 169 |

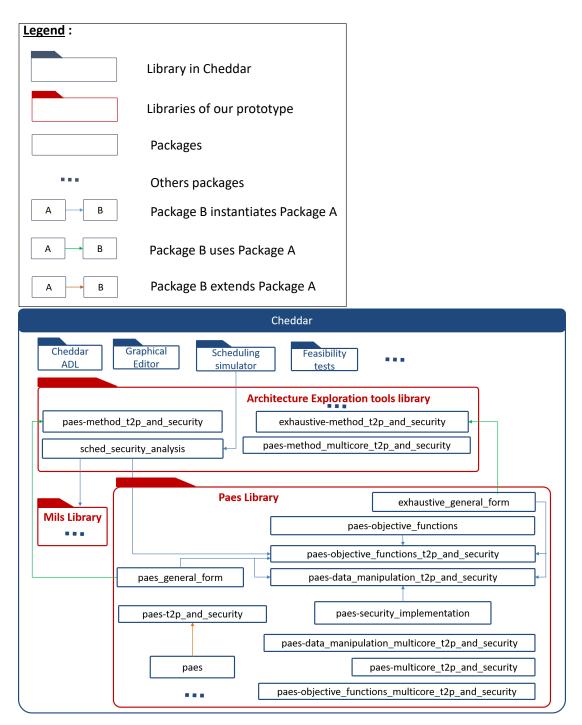

| 10.3 Implementation                                                            | 170 |

| 10.3.1 MILS library                                                            | 172 |

| 10.3.2 PAES library                                                            | 173 |

| 10.3.3 Architecture exploration tools library                                  | 174 |

| 10.4 Conclusion                                                                | 178 |

# IV Conclusion

# 179

| 11 | Con  | clusio | 1                                                                                               | 181 |

|----|------|--------|-------------------------------------------------------------------------------------------------|-----|

|    | 11.1 | Contri | bution summary                                                                                  | 182 |

|    |      | 11.1.1 | PAES adaptation to the MOOP between schedulability and security                                 | 182 |

|    |      | 11.1.2 | Mutation algorithms                                                                             | 182 |

|    |      | 11.1.3 | Mutation algorithm improvement                                                                  | 183 |

|    |      | 11.1.4 | Identification of the key parameters during DSE                                                 | 183 |

|    |      | 11.1.5 | Extensibility of the DSE approach: safe and secure TSP systems on multicore execution platforms | 184 |

|    |      | 11.1.6 | Security architecture modeling and security analysis implementation                             | 184 |

|    | 11.2 | Future | work                                                                                            | 185 |

|    |      | 11.2.1 | Memory protection mechanism                                                                     | 185 |

|    |      | 11.2.2 | Security: investigation of different security models                                            | 185 |

|    |      | 11.2.3 | Schedulability: investigation of different possibilities of major time frame (MAF)              | 185 |

|    |      | 11.2.4 | Conflict between schedulability and security: consideration of the possible overheads           | 186 |

| 11.2.5 | Extension to distributed network platforms | 186 |

|--------|--------------------------------------------|-----|

| 11.2.6 | Finer granularity: functions               | 186 |

# List of Figures

| 2.1 | Task life cycle [3]                                               | 28 |

|-----|-------------------------------------------------------------------|----|

| 2.2 | Illustration of some tasks properties                             | 31 |

| 2.3 | Tasks properties and types illustration with CFAR application [4] | 33 |

| 2.4 | Illustration of a scheduling simulation                           | 41 |

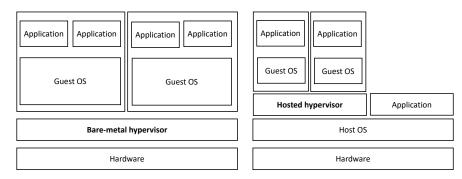

| 3.1 | Bare-metal hypervisor Vs hosted hypervisor                        | 44 |

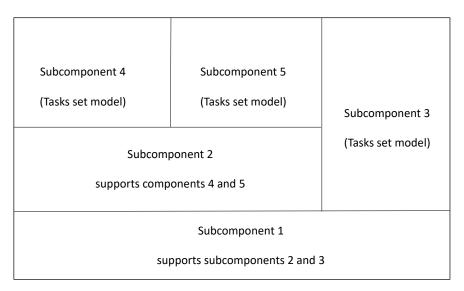

| 3.2 | Hierarchical real-time systems                                    | 45 |

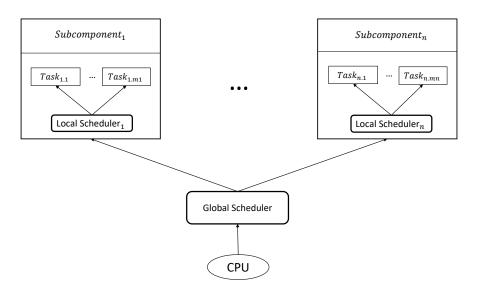

| 3.3 | Hierarchical scheduling framework                                 | 46 |

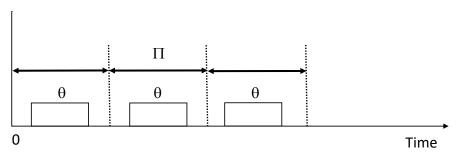

| 3.4 | Periodic resource illustration                                    | 47 |

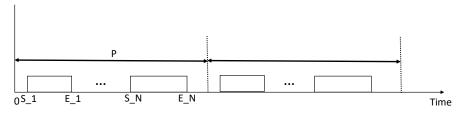

| 3.5 | Bounded delay resource illustration                               | 48 |

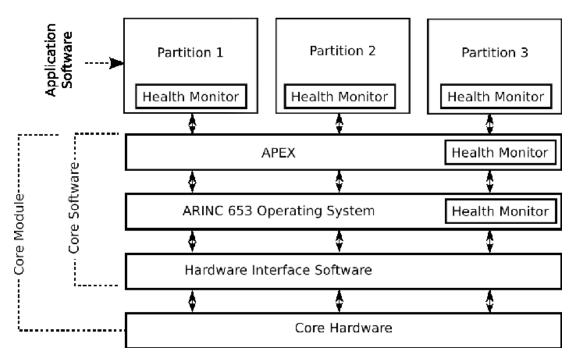

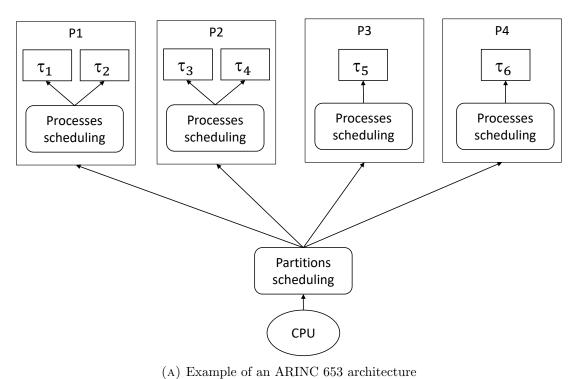

| 3.6 | ARINC 653 architecture [5, 6]                                     | 50 |

| 4.1 | Encryption illustration                                           | 62 |

| 4.2 | HMAC illustration                                                 | 64 |

| 4.3 | Bell-La Padula model illustration [7]                             | 65 |

| 4.4 | Biba model illustration [7]                                       | 66 |

| 4.5 | MILS overview [8]                                                 | 68 |

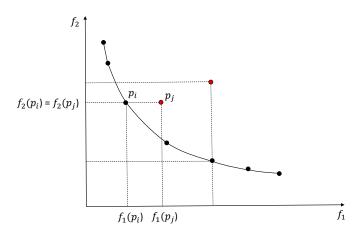

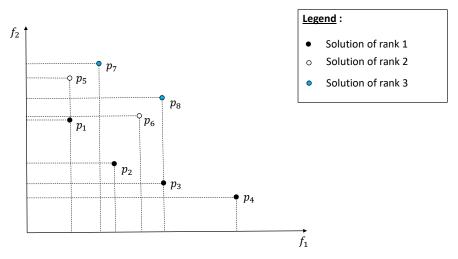

| 5.1 | Illustration of a Pareto front [9]                                | 73 |

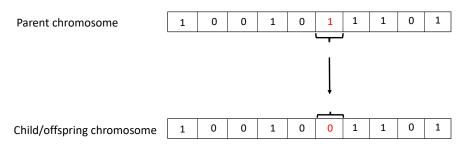

| 5.2 | Illustration of mutation                                          | 77 |

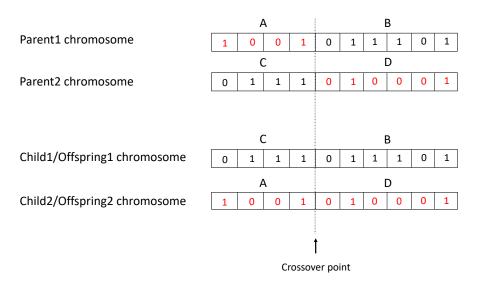

| 5.3 | Illustration of crossover                                         | 78 |

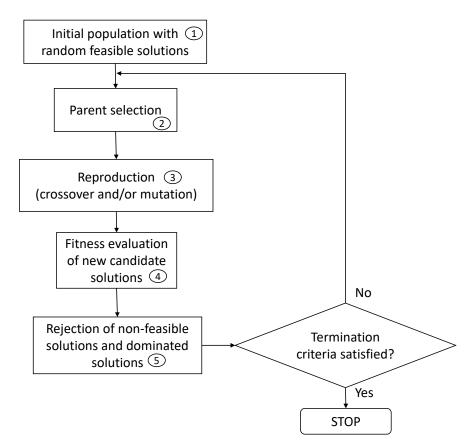

| 5.4 | Multi-objective evolutionnay algorithm                            | 79 |

| 5.5 | NSGA ranking Illustration [10]                                    | 80 |

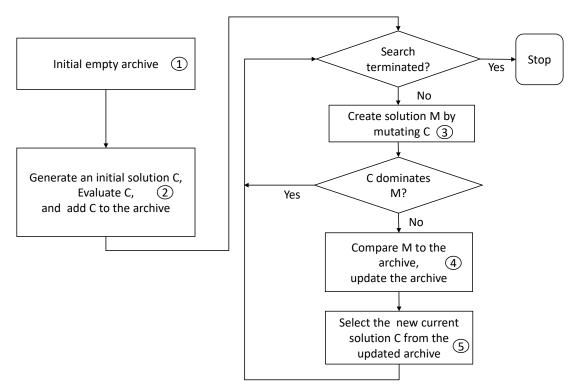

| 5.6 | PAES process                                                      | 82 |

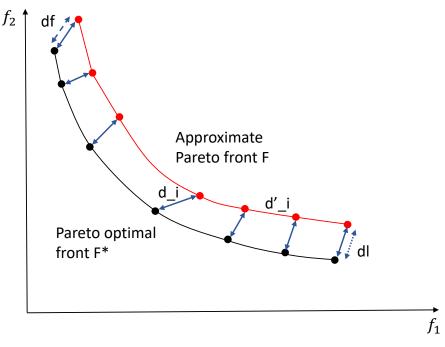

| 5.7 | Convergence and diversity metrics                                 | 84 |

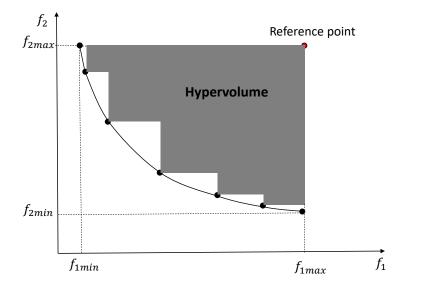

| 5.8 | Hypervolume illustration                                          | 85 |

| 6.1 | Illustration of security implementations                          | 92 |

| 6.2  | Partitioning and communications without/with security functions          | 96  |

|------|--------------------------------------------------------------------------|-----|

| 6.3  | Partitioned scheduling without/with security functions                   | 97  |

| 7.1  | PAES process                                                             | 106 |

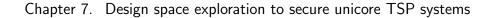

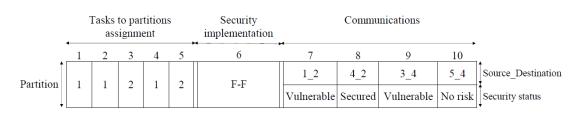

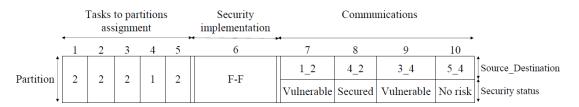

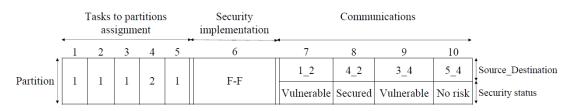

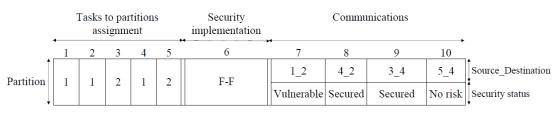

| 7.2  | Example of chromosome                                                    | 112 |

| 7.3  | Model of the illustrated chromosome                                      | 112 |

| 7.4  | Normalization illustration                                               | 114 |

| 7.5  | Task-grain mutation illustration                                         | 115 |

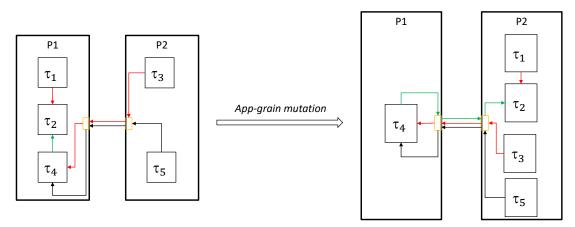

| 7.6  | App-grain mutation illustration                                          | 117 |

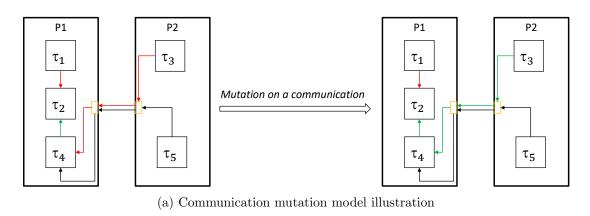

| 7.7  | Communication mutation illustration                                      | 120 |

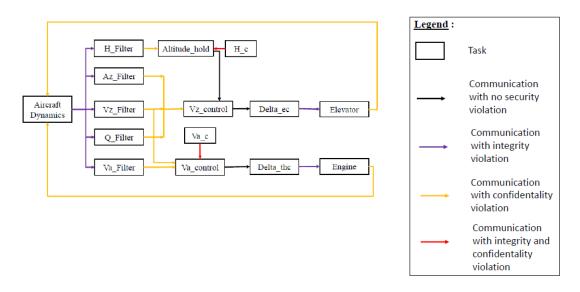

| 8.1  | ROSACE flight controller application                                     | 124 |

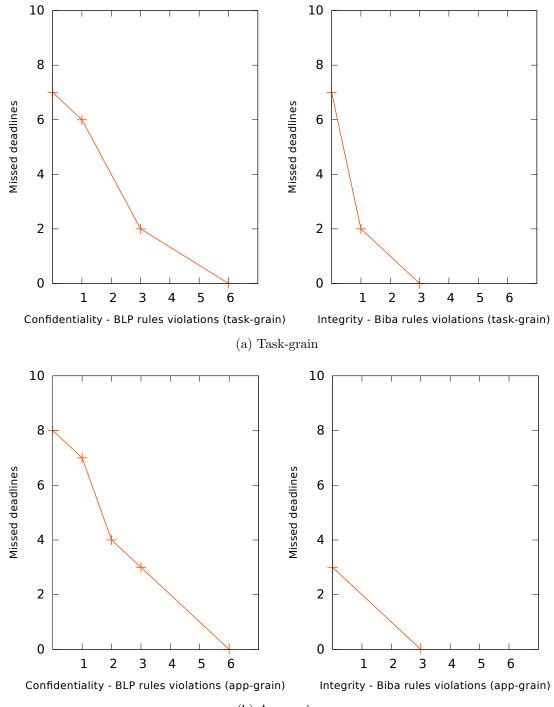

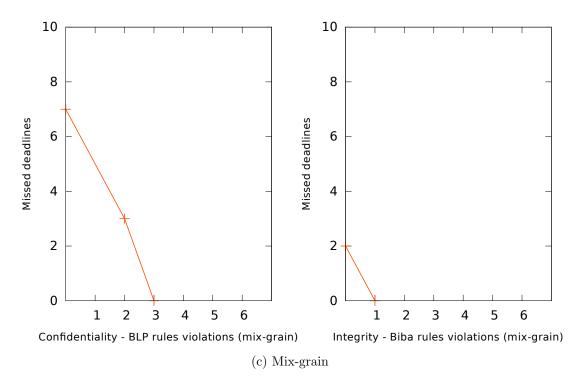

| 8.3  | Schedulability vs. security with ROSACE&JPEG                             | 129 |

| 8.5  | Schedulability vs. security with processor utilization variation $\ .$ . | 133 |

| 8.6  | Schedulability vs. security with variation from 2 to 4 partitions $\ $ . | 137 |

| 8.7  | Exhaustive vs PAES                                                       | 141 |

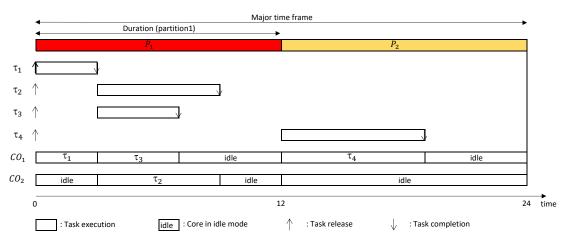

| 9.1  | Example of a multicore TSP system scheduling                             | 147 |

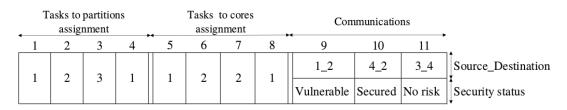

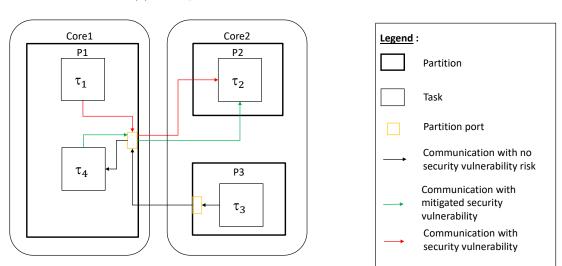

| 9.2  | Illustration of multicore solutions encoding                             | 152 |

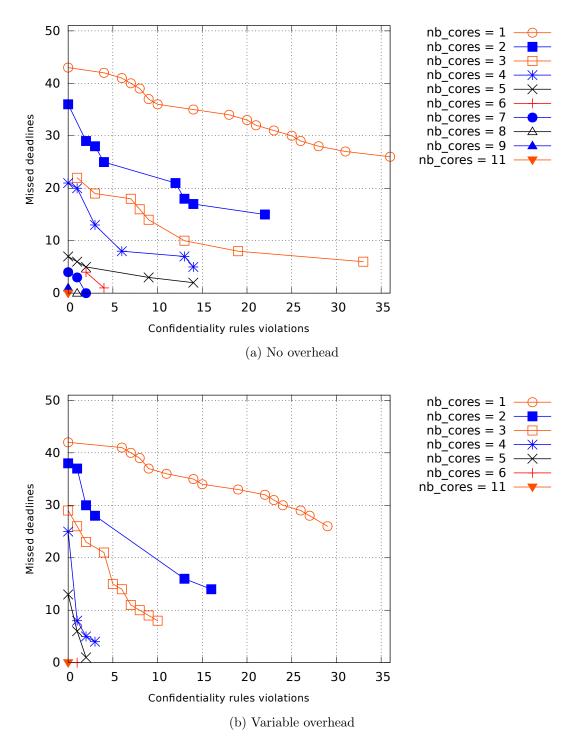

| 9.3  | Schedulability vs. confidentiality                                       | 157 |

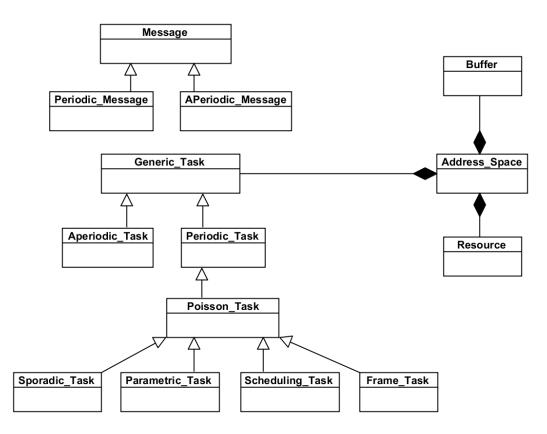

| 10.1 | Software entities in Cheddar ADL [11]                                    | 163 |

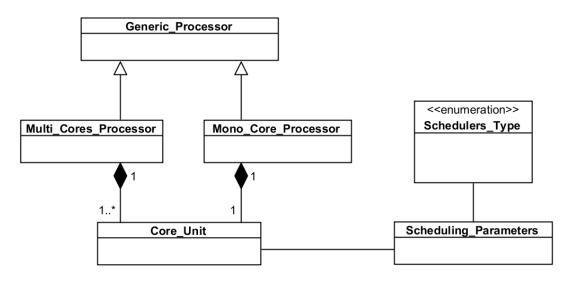

| 10.2 | Hardware entities in Cheddar ADL [11]                                    | 166 |

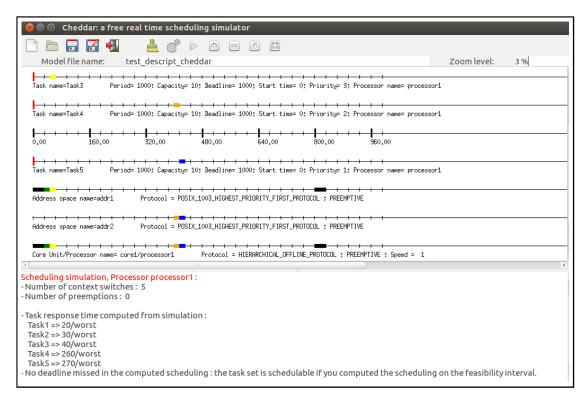

| 10.3 | Cheddar scheduling simulation illustration                               | 169 |

| 10.4 | Cheddar feasibility test illustration                                    | 170 |

| 10.5 | Prototype overview                                                       | 171 |

# List of Tables

| 3.1  | Summary of hypervisors and RTOS for TSP systems                                                                   | 55  |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

| 6.1  | Security implementations considered in this thesis                                                                | 95  |

| 6.2  | Task and partition configuration                                                                                  | 96  |

| 6.3  | Related work                                                                                                      | 98  |

| 7.1  | Communications concerned by security constraints                                                                  | 109 |

| 7.2  | Communications concerned by security objective functions                                                          | 109 |

| 8.1  | Case studies task parameters                                                                                      | 127 |

| 8.2  | DSE with intra-partition communications considered as secured with <i>mix-grain</i> and a maximum of 2 partitions | 134 |

| 8.3  | APEX calls execution times                                                                                        | 139 |

| 8.4  | Schedulability vs. security with SFPBench APEX calls measurements                                                 | 139 |

| 9.1  | Case study task parameters                                                                                        | 154 |

| 10.1 | PAES tool implementation                                                                                          | 175 |

| 10.2 | Exhaustive tool implementation                                                                                    | 176 |

| 10.3 | Scheduing and security analysis                                                                                   | 177 |

# Introduction

# 1.1 Introduction

Real-time systems (RTS) are widely present around us in our daily life. They are widely integrated into devices of different domains from commonly used devices such as cellphones, car navigation, multimedia applications to critical industrial devices such as control command systems in aircraft, automotive systems, and robots. RTS are computing systems whose correctness depends not only on the logical results of the computation but also on the time at which the results are produced [12]. The results processed by RTS must not only be correct but also meet their timing constraints.

An RTS is an application or a set of applications made of tasks that correspond to execution units. Tasks are then subject to timing constraints. In RTS, tasks can be classified based on the criticality of the consequences that may occur if their timing constraints are not respected. Therefore, there are hard deadline tasks and soft deadlines tasks [13, 14]. Hard deadline tasks have stringent timing constraints that must be respected in all situations. Soft deadline tasks are more flexible and tolerate some delay.

With the evolution of technologies, RTS need to integrate more functionalities to satisfy as much as possible the users [15]. Historically in avionic domains, systems have been made based on federated architectures [16] where each function has its own dedicated computing system. In these systems, functions were isolated from each other with limited data exchange. With this architecture, a fault occurring in a function has fewer chances to affect another function on a different computing system. Modern avionics require more services (e.g. entertainment services), safety (e.g. at least a duplication of systems), and smartness (e.g. precise flight management systems, health management systems, smart sensors, and actuators) [15]. This evolution leads to the integration of more functions. Then assigning each function to a dedicated computing system is no longer efficient since it implies an increase in the height, volume, installation, maintenance cost and power consumption of the systems. In [17], the authors shown that avionic software size is multipled by 2 very 4 years. Thus the proposal of integrated modular avionics (IMA) architecture [18] was a solution to the incompatibility of federated systems to the requirements of modern avionic systems. IMA architecture proposes computing resource sharing among different functions instead of dedicating a computing resource to each function as in the federated architecture.

Resource sharing solves the above-mentioned problems raised by the federated architecture, but it comes with some challenges. A fault occurring in a function can easily affect other functions sharing the same computing resource without a proper isolation. Thus, IMA architecture proposed time and space partitioning.

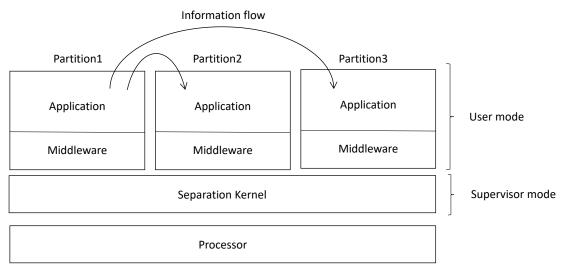

Time and space partitioned (TSP) systems allow the integration of applications with different criticality levels and potentially from different providers on the same shared banalized execution platform. In TSP systems, applications are assigned to partitions [15]. A partition is a logical software unit defining a boundary of isolation. TSP systems guarantee space and timing isolation between partitions. Space isolation may be brought by memory protection between partitions while timing isolation may be enforced by partition scheduling. These features contribute to master the growing complexity both in size and legacy of avionic software.

Although TSP concepts were first adopted by avionic stakeholders with the IMA architecture, they are gaining various domains such as aerospace [19] and railway [20]. For example, due to the similarity between the avionic and spacecraft domain, researchers such as authors of [19] address the integration of TSP in spacecraft. It comes as a solution to the complexity of the spacecraft onboard software due to the increasing number of mission functions implemented in software. In the railway domain, [20] investigates the optimization of partition-based distributed RTS on a real railway signaling application.

# 1.2 Problem statement

In TSP systems, tasks have to be assigned to partitions, their design implies deciding on how to do such assignment. This leads to multiple possibilities of tasks to partitions assignments. The number of options increases exponentially with the number of tasks, and partitions. It is a typical case of combinatorial explosion. Changing the tasks to partitions assignment has an impact on the schedulability of the system. It can make some tasks to miss their deadline. If a hard deadlines task misses its deadline, then the associated tasks to partitions assignment is considered not feasible. Therefore, when designing a TSP system, tasks to partitions assignment and the respect of timing constraints of hard deadline tasks are important challenges to investigate.

As TSP systems may host an increasing number of applications provided by different stakeholders with a significant level of legacy, it then increases the probability of corrupted or malicious software deployment. There exists a multitude of attack and threat models for cyber-physical systems [17, 21]. For example, Man-in-the-Middle attacks [22] can threaten communications in and between partitions. Data can be intercepted during application communications which results in either confidentiality violations by disclosure of sensitive information or integrity violations by data alteration.

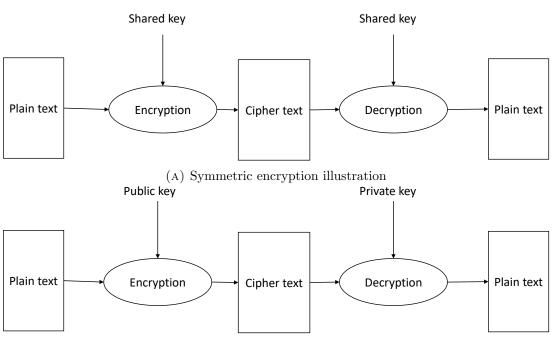

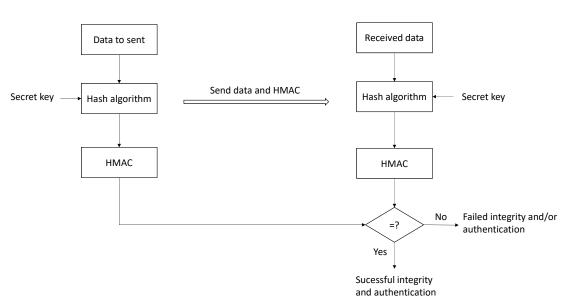

A standard approach to protect against attacks on confidentiality is the use of encryption with a symmetric private key [23]. It guarantees that the content of a message is intelligible only to the actual sender and receiver. To secure the integrity of communications, one can use message by a third party authentication codes (MACs) to make certain that a message has not been tampered and has been sent by the actual sender [22].

However, ensuring data confidentiality and integrity with the use of encryption and MACs incurs a significant computation overhead on banalized hardware. This overhead may impact the system schedulability. We propose that if TSP systems are made of hard deadline and soft deadline tasks, security can be optimized as much as possible by tolerating some missed deadlines of soft deadline tasks. It results in a problem of assigning tasks to partitions while optimizing schedulability and security, which is an NP-hard combinatorial problem with 2 conflicting objective functions: schedulability and security.

# 1.3 Contribution

In this thesis, we investigate the conflict aspect between schedulability and security TSP systems when assigning applications to partitions. Schedulability requires that there is no violation of timing constraints. Enforcing confidentiality and/or integrity of communications between applications introduces overhead and affects schedulability.

We propose a design space exploration process to address the combinatorial problem raised between schedulability and security of TSP systems. Our approach is based on Multi-Objective Evolutionary Algorithms (MOEAs), especially the Pareto Archived Evolution Strategy (PAES) [24] which is a metaheuristic that we have adapted for DSE problems with multiple and conflicting objectives functions. It helps to explore the search space to find an approximate set of optimal solutions in a suitable time for large-scale problems that would be time-consuming with an exact method (i.e. exhaustive method). Our DSE approach proposes to explore the search space of TSP while investigating tasks and partitions assignment and communications security.

# 1.3.1 A PAES based DSE approach for unicore execution plateforms

The PAES is characterized by different operators that have to be defined according to the specific addressed problem. Our approach proposes an adaptation of PAES to jointly investigate schedulability and security.

First, it is important to ensure the feasibility of the proposed solutions. Then feasibility tests are performed to check the validity of the solutions.

Second, in order to find the best solutions, each solution explored has to be evaluated to be compared to others. Evaluations have to be performed to determine the solution's fitness toward the objectives. Feasibility tests and solutions fitness evaluations are performed through analysis. Our analyses are based on schedulability and security analysis. Our schedulability analysis proposes to identify hard and/or soft deadline tasks that missed their deadlines through scheduling simulations proposed in Cheddar [25] an open-source scheduling analyzer. For security analysis, we propose to implement the Bell-La Padulla (BLP) and Biba security rules to identify respectively confidentiality and integrity vulnerabilities. For this purpose, we integrated into the Cheddar tool, the security architecture Multiple Independent Levels of Security (MILS) that helps us to model our TSP systems with the Cheddar tool not only according to scheduling parameters (e.g. worst-case execution time, deadlines of tasks) but also to security parameters (e.g. confidentiality, integrity levels of tasks).

Third, the search space is explored through the generation of candidate solutions. Then is important to define how to proceed with the generation. We propose to explore the design space of TSP systems with different levels of granularity by three mutation algorithms coupled with a multi-objective meta-heuristic.

We assume that applications are composed of tasks. We start by the assignments of tasks to partitions. As this mutation algorithm leads to investigate a large design space, we propose a second mutation algorithm that consists of investigating groups of tasks constituting an application to partitions assignment. This second approach presents a less degree of freedom. We then propose a third mutation algorithm that consists of refining the results obtained at the application level (i.e. second algorithm) by applying on them a mutation algorithm at task granularity (i.e. first algorithm).

With each mutation algorithm, we evaluate four different means to implement security features in TSP systems.

# 1.3.2 Extension of the DSE approach to Multicore execution platforms

We show the extensibility of our DSE by applying it in another context. Then first, we investigate the impact of Multicore execution platforms on safe and secure TSP systems while considering not only tasks to partitions assignment but also tasks to cores assignment.

Indeed, TSP systems are safe from fault propagation from one partition to another through partitioning. However, They are still exposed to failure concerning the availability of tasks and partitions. Safety is a challenge to consider when designing a TSP. It can be addressed through active redundancy which means replication of tasks and partitions. Then as security, safety implies overheads that impact schedulability. Thus we proposed an extension of our DSE approach to Multicore execution platforms well-known to increase computation capability.

Second, we proposed a method to improve the diversity of the proposed solutions by the DSE with each of the three above-mentioned mutation algorithms. We implemented a prototype and performed experiments to show the extensibility of our DSE approach and evaluate the impact of shared hardware resources overheads on our addressed MOOP.

# 1.3.3 Implementation and evaluations

To summarize, we propose a DSE to compute trade-offs between security and schedulability considering four different security implementations in TSP systems. The DSE is computed with three different exploration algorithms (i.e. mutation algorithms) based on a formulation of a multi-objective problem, solved by an adaptation of PAES. The prototype of our DSE is implemented and integrated in the Cheddar tool. This prototype is reusable and extendable to any MOOP.

The security analysis part of this implementation has been integrated into AADL Inspector [26], a commercial scheduling analyzer from Ellidis Technologies.

We run multiple experiments with benchmarks or applications proposed by the community [27, 4, 28, 2, 29, 30, 31, 32] to identify the TSP architecture parameters which impact the trade-off between security and schedulability. They contribute to highlight guidelines that must be considered when designing secure TSP systems. Moreover, the experiments also contribute to evaluate our DSE approach.

# 1.4 Thesis organization

This thesis is organized in 11 chapters.

The chapters 2, 3, 4, and 5 cover the state of the art of this thesis. Chapter 2 presents key knowledge of real-time systems. Chapter 3 discusses the background about hierarchical systems while introducing integrated modular avionics (IMA) [18] concepts such as time and space partitioning. Chapter 4 gives a presentation of security concepts such as security properties, models, and architecture. Chapter 5 presents multi-objective optimization concepts by discussing multi-objective evolutionary algorithms (MOEA).

Chapter 6 depicts the motivations of this thesis. It presents the system model and taken assumptions. It also positions the contributions of the thesis by comparing it with related work.

The contributions are presented in chapters 7, 8, 9, and 10. Chapter 7 presents our DSE approach to investigate the schedulability and security trade-off in TSP systems when considering unicore platforms. Chapter 8 discusses the experiments we performed to evaluate our DSE approach and to identify key parameters that impact the trade-off between security and schedulability. Chapter 9 presents our DSE approach to investigate the impact of multicore platforms on TSP systems while addressing the conflicts between safety, security, and schedulability. It shows the adaptability of our DSE approach to a different context. Chapter 10 presents the implemented prototypes of this thesis. Since they are integrated into the Cheddar scheduling analyzer, the chapter also proposes a presentation of the Cheddar framework.

Finally, a conclusion of the thesis and some directions for future work are given in Chapter 11.

# Part I

# State of art

# Real-time systems

This chapter is dedicated to the background on real-time systems (RTS). First, section 2.1 defines RTS by presenting their characteristics and classifications. Second, section 2.2 presents the architecture of RTS by depicting their hardware platform and their software structure, including the operating system. Third, section 2.3 discusses scheduling analysis and simulation to verify timing constraints. Finally, a conclusion of the chapter is given in section 2.4.

# 2.1 Definitions and classification

In this section, we define RTS, outline the classification and the characteristics of each category.

# 2.1.1 Definitions

Real-time systems are used in several domains such as avionic, space, automotive, and medicine. Applications in these domains may have different functionalities but are all characterized by timing constraints.

**Definition 1.** (*Real-time systems*) A real-time system is defined as a computing system which the correctness depends not only on the logical results of the computation but also on the time at which the results are produced [12].

A peacemaker [33] is an example of a real-time system placed down the heart. It measures the heartbeat and then provides pulsations to slow or accelerate the heart rate in case of an abnormal heartbeat. When the peacemaker receives the information that the heartbeat is lower than normal, it sends electric pulsations to provide acceleration. The peacemakers correctness relies not only on the correctness of the heartbeat measurements but also on the time when the pulsations are sent. It is necessary that the sending of pulsations respects deadlines (i.e. at the right time, neither too early nor too late).

To summarize, a real-time system interacts with its environment by receiving information from the environment, processing them and returning the results that impact the environment while respecting timing constraints called deadlines [34]. Even if the computation results are correct, if the deadlines are not respected, the results can be considered incorrect. The deadlines misses do not lead always to disastrous consequences (e.g. loss of life). The consequences of deadlines misses are various depending on the addressed real-time system. Then real-time systems can be classified depending on the consequences of the deadlines misses.

# 2.1.2 Classification

RTS are classified into different categories. The classification can be made based on the criticality level i.e. the consequences of the missed deadline of the systems [13].

#### 2.1.2.1 Hard real-time system

Hard real-time systems are systems that must imperatively respect their timing constraints [13, 14]. In hard real-time systems, the violations of deadlines have impacts on the system behavior with disastrous consequences. For these systems, the missed deadlines cannot be tolerated. Then a result provided after the expected deadline is considered not correct even if the computation is correct. Heart peacemaker, flight control systems are examples of hard real-time systems.

#### 2.1.2.2 Soft real-time system

Soft real-time systems are systems that can tolerate timing constraints violations without leading to any disaster [13, 14]. Their timing constraints violations do not compromise the global functioning of the system. These systems are more flexible concerning timing constraints. Their deadline violations can lead to the deterioration of the results and system performances (e.g. quality of service [35]) but will not cause catastrophic consequences. Video streaming on internet is an example of soft real-time system.

# 2.1.2.3 Criticality of RTS

There are systems with programs/applications of multiple criticalities. Criticality is a designation of the level of assurance against failure needed for a system component [36]. It can refer to the classification (e.g. hard or soft) of programs/applications according to the consequences of their failures.

Aircraft is an example of a system with multiple criticalities. It contains flight management systems and passenger entertainment systems separated from each other. Flight management systems are hard real-time systems while passenger entertainment systems are soft real-time systems.

We distinguish mixed critical real-time systems and partitioned systems.

• Mixed critical real-time systems: are systems that have two or more distinct levels (for example safety-critical, mission-critical, and low-critical) [36].

A mixed critical real-time system consists of integrating programs/applications of different criticality levels sharing resources together while making adaptations depending on the objectives (e.g. schedulability, security, safety). For example, in the case of schedulability objective, if a high-level task is susceptible to miss its deadline, the access to the resources of a low task can be modified to allow the high task to be executed at the time and to respect its deadline. As an advantage, the mixed critical approach allows better exploitation of the resources, but it is still at the research stage because it is difficult to apply in the industry.

• Partitioned systems are characterized by a necessary separation and independence of programs or applications to ensure that only intended coupling occurs [37].

Each partition hosts programs or applications at the same criticality level. The objective is to limit the propagation of faults (missed deadlines, security attacks, safety failures) from one partition to another. As an inconvenience, it has a high resource requirement since resources have to be dedicated to each partition.

# 2.2 Real-Time architecture

RTS can be seen as layered systems. Most of them are composed of a software application layer deployed on an real-time operating system running on top of a hardware platform. RTS layers are described in the following sections.

# 2.2.1 Hardware platform

The hardware platform is characterized by components such as computing units, cores, networks, memory units.

# 2.2.1.1 Computing units

Many RTS are embedded and then require small computing units with minimum power consumption. There are different categories of hardware platforms depending on the contained components and their interactions.

- Uniprocessor systems: systems based on a single central processing unit (CPU) where the software applications execute. The programs of the applications request and compute concurrently to this computing resources.

- Multi-processor systems: systems that provide two or more central processing units for the execution of the software applications. These CPUs execute programs at the same time while sharing the main memory and the peripherals. There are different types of multi-processing systems depending on how the CPUs are used. Symmetric multiprocessing (SMP) systems are systems where the CPUs used are identicals. There are also Asymmetric multiprocessing (AMP) systems where the used processors are not used equally and may have different roles assigned each.

- Multi-core systems: systems based on single central processing with two or more executing units called cores.

# 2.2.1.2 Memory units

The memory units have many characteristics that should be well study to feet the systems requirements. Among those characteristics, there are power consumption, capacity/size, accessibility to perform for reading and writing operations, cost, etc. Memory is responsible for data and instructions storage. The capacity of storage should fit the needs of the systems. Memory speed is an important characteristic. If this speed is too low as compared to the processor's speed, requests to access data will be too long and lead to more power consumption. Among different existing kinds of memory systems, there are systems with memory partitioned where memory is split into different sections, each assigned to a different program.

# 2.2.2 Real-time software application layer

The software application layer of RTS runs on top of a real-time operating system (RTOS) and is composed of applications. Each application is a set of tasks that interact with each other.

# Definition 2. (Task)

A task is an execution unit of a program and corresponds to a logical unit of computation in a processor [13].

A task is composed of a set of sequentially executed instructions that starts at the release of the task called job.

The software application layer may be composed of tasks that interact with each other. Hardware resources are allocated to tasks based on a multitasking process.

# Definition 3. (Multi-tasking [38])

Multi-tasking is the process of scheduling and switching tasks, making use of the hardware computing, or emulating concurrent processing using the mechanism of the task context switching (defined below).

# Definition 4. (Context switch)

Context switch refers to the switching on the processor from one task to another [39].

The context switch is the process of interrupting a running task and then allocating the processing unit to another task. The state of the interrupted task is saved and the previously saved state of the other task is loaded.

# 2.2.2.1 Task life cycle

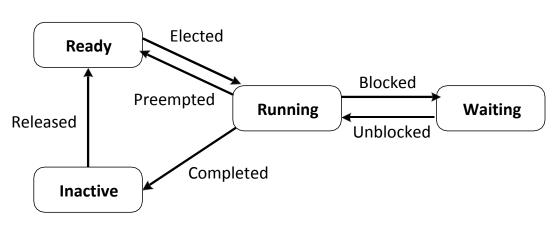

The life cycle of a task is composed of the four states detailed below in figure 2.1: inactive, ready, running and waiting. The switch between the states is handled by the RTOS.

FIGURE 2.1: Task life cycle [3]

- Inactive: the inactive state of a task corresponds to its first state when it is created and its execution has not started yet. Thus the task is waiting for its release that can be activated by an event or message. A task that has completed its execution is also considered in the inactive state.

- Ready: after its release, the task enters its ready state and waits for computing resource assignment. The task waits for its election among the other tasks to be executed on the processor.

- Running: once the task is elected to access the processor for its execution, then it enters the running state and starts its execution. The task has access to all the shared resources. During the execution of a task, preemption may occur meaning another task has been elected to be executed. The current task which is at the running state stops its execution and switches to the ready state.

- Waiting: when a task execution is blocked by the unavailability of a resource (e.g. shared resources) except the processor, it enters the waiting state. As soon as the resource becomes available, the task switches to the running state.

# 2.2.2.2 Task properties

Each task is characterized by a set of properties that help to define its order of priority in the task set, its computational requirements and its timing constraints. This section presents the properties of a task.

# Definition 5. (Offset)

The offset of a task represents the time at which its first request occurs [40].

The offset represents the time at which the first job of a task is released. It is defined to model systems where tasks are not released at the same time. Thus, in those systems, tasks may have different offsets and then the first job of a task can be released later than another task's first job.

### Definition 6. (Execution time)

The execution time of a task is defined as the time spent by the system executing a job of that task using processor resources.

The execution time of a task may vary from a job to another depending on the input data or different behavior of the environment [41]. For example, the changes of the input data may change the execution paths and the number of loop iterations and then lead to different execution times. Some works consider the upper-bound and the lower-bound execution time values respectively called worst-case execution time (WCET) and best-case execution time (BCET).

# Definition 7. (Worst case execution time)

The WCET of a task is the longest execution time of all its jobs [41].

# Definition 8. (Best case execution time)

The BCET of a task is the shortest execution time of all its jobs [41].

Hard real-time systems parameters are always fixed based on a pessimist approach that consists of considering the worst-case situations. They consider the WCET and assume the same execution time for all the jobs of a task. WCET of a task is sometimes referred as the task capacity. This pessimist approach helps to guarantee that the system meets its deadlines [14]. On the contrary, soft realtime systems are not necessarily built under pessimistic assumptions [14] because of their tolerance for deadline misses.

Besides the execution time, each job of task is characterized by its response time.

# Definition 9. (Response time)

The response time of a job of a task is the time between the release of the job and its completion [42].

As for the execution times, the response time of a task varies from a job to another. They are computed based on scheduling analysis methods detailed later in section 2.3.

Upper-bound and lower-bound response time values can be computed and respectively called worst-case response time (WCRT) and best case response time (BCRT).

#### Definition 10. (Worst case response time)

The WCRT of a task is the longest response time of all its jobs [42].

#### Definition 11. (Best case response time)

The BCRT of a task is the shortest response time of all its jobs [42].

We highlight that a task execution time may be smaller than its response time since tasks are not executed immediately after their release. After their release, tasks may also be waiting for the availability of a shared resource or the processor used currently by higher priority tasks.

#### Definition 12. (Priority)

The priority of a task indicates its order of importance for the scheduling among other tasks of the system [13].

Tasks of a system can be ordered based on their priorities that define their order to access the processor. Tasks priorities can be fixed or dynamic depending on the assumed scheduling policy. The task in the ready queue with the highest priority level is usually the elected task to be executed by the processor. In case of preemptive scheduling (detailed in section 2.2.3), when a task is running, it can be suspended by a new ready task with a higher priority level.

#### Definition 13. (Deadline)

The deadline of a task is the maximal allowed response time to the jobs of its task [13].

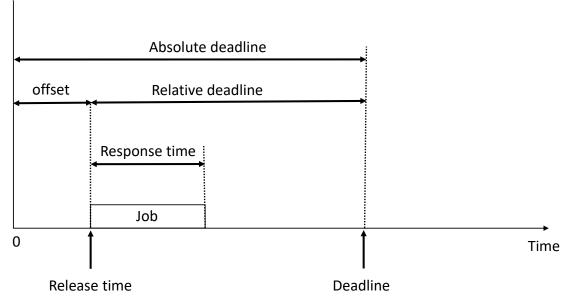

We distinguish relative and absolute deadlines. The relative deadline is relative to the release time of a job in contrary to the absolute deadline. Figure 2.2 shows the difference between relative and absolute deadline of a task and some tasks properties such as release time, response time, deadline.

FIGURE 2.2: Illustration of some tasks properties

Task deadlines can be classified into two categories according to their necessity to be met. There are hard deadlines and soft deadlines.

**Definition 14.** (*Hard deadline*) A hard deadline is a deadline that must imperatively be met, otherwise it can lead to severe damages [13, 14].

**Definition 15.** (Soft deadline) A soft deadline is a deadline that can be missed without compromising the integrity of the system [13]

# 2.2.2.3 Task types

Tasks can be classified based on their release frequency and their activation circumstances (e.g. occurrence of an event). Tasks can be periodic tasks, aperiodic or sporadic.

**Definition 16.** (*Periodic task* [43]) A periodic task is a task that is released at fixed and regular time interval.

A periodic task is released repetitively at a fixed interval time called period. A task that acquires data periodically (e.g. every 1 second) from a sensor is an example of a periodic task.

# Definition 17. (Aperiodic task [44])

An aperiodic task is a task that is not released at a regular time interval, with no minimum interval time between two releases.

Aperiodic tasks are activated by events and the events do not occur at regular intervals. They are usually soft real-time tasks with soft deadlines or no deadlines. It is complex to bound the resource utilization of aperiodic tasks. Thus the feasibility of a system with aperiodic tasks cannot be guaranteed.

Users interactive commands are examples of aperiodic tasks.

# Definition 18. (Sporadic task [44])

A sporadic task is a task that is released with a minimum interval time between two releases.

A sporadic task has a minimum interarrival time (MIT) between two consecutives releases. The MIT of a sporadic task provides a safe upper bound to determine its resource utilization.

A security alert program is an example of a sporadic task. It is a high critical and its releases arrive arbitrary because arrival cannot be predicted.

#### 2.2.2.4 Synchronous and asynchronous tasks

Tasks can also be classified based on their first release. Tasks can be synchronous or asynchronous.

# Definition 19. (Synchronous tasks [45])

Tasks of a system are synchronous if the first jobs of all the tasks are released at the same time.

Synchronous tasks have the same offset. Thus tasks are simultaneously ready to be executed at a given time called critical instant [43].

# Definition 20. (Asynchronous tasks [45])

Tasks of a system are asynchronous if the first jobs of at least two tasks are not released at the same time.

In asynchronous systems, there are at least two tasks with different offsets.

# 2.2.2.5 Tasks dependencies

Tasks can also be classified according to the relationships they have with each other.

**Definition 21.** (*Independent tasks* [13]) An independent task is a task whose progress is not dependent upon the progress of other tasks of the task set.

In a task set with only independent tasks, no task can be blocked by another task.

**Definition 22.** (*Dependent tasks* [13]) A dependent task is a task whose progress is dependent upon the progress of other tasks of the task set.

Dependent tasks are used to force the order in which communicating tasks execute [46]. They can interact in many ways including shared resources and precedence dependencies [13]. It is important to highlight that the competition between tasks to access a processor is not considered as a dependency.

**Definition 23.** (*Precedence dependency* [13]) Task  $\tau_i$  precedes task  $\tau_j$  in the task set, if the task  $\tau_i$  has be executed before task  $\tau_j$ .

By considering two tasks  $\tau_i$  and  $\tau_j$ ,  $\tau_i$  precedes  $\tau_j$  means that the jobs of task  $\tau_i$  have to be executed before the jobs of task  $\tau_j$  start their execution. Precedence dependency can be illustrated by a task  $\tau_j$  waiting for a message or synchronization signal from another task  $\tau_i$ .

**Definition 24.** (Shared resource [13]) A shared resource is a resource accessed by several tasks, in an exclusive manner to enforce data consistency.

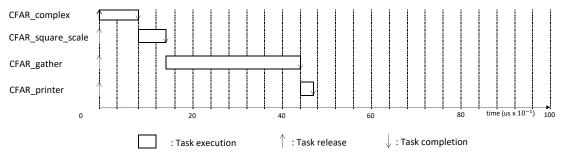

Figure 2.3 shows an example of a real-time system composed of four periodic, synchronous and dependent tasks. This example is inspired from the Constant False Alarm Rate detection (CFAR) application proposed in the benchmark [4]. The boxes represent tasks and the arrows show the precedency dependencies between tasks. For example, the task CFAR\_complex must be executed before task CFAR\_square\_scale. The table in figure 2.3 depicts the properties of each task such as the offset, WCET, priority, deadline, and period.

| CFAR_complex      |                     |        |      |          | Legend : |           |

|-------------------|---------------------|--------|------|----------|----------|-----------|

|                   |                     |        |      |          | Та       | sk        |

| CFAR_square_scale |                     |        |      |          | → De     | ependency |

|                   | Properties<br>Tasks | Offset | WCET | Priority | Deadline | Period    |

| CFAR gather       | CFAR_complex        | 0      | 90   | 1        | 1000     | 1000      |

|                   | CFAR_square_scale   | 0      | 50   | 2        | 1000     | 1000      |

| ↓<br>             | CFAR_gather         | 0      | 340  | 3        | 1000     | 1000      |

| CFAR_printer      | CFAR_printer        | 0      | 30   | 4        | 1000     | 1000      |

FIGURE 2.3: Tasks properties and types illustration with CFAR application [4]

# 2.2.3 Real-time Operating System

An operating system (OS) is a software program that serves as an interface between the software application and the hardware platform by providing services such as memory management, process management, drivers management, communication management, etc.

A real-time operating system (RTOS) is an OS intended for RTS. The guarantee of timing constraints is one of the most significant differences between an RTOS and a general-purpose OS (GPOS) such as Windows, Linux, macOS. FreeR-TOS [47] and RTEMS [48], RTLinux [49], PikeOS [50] are examples of RTOS.

Unlike GPOS, RTOS proposes additional services in order to guarantee systems predictability and timing constraints requirements.

Usually, RTOS support systems with tasks of different priority levels. They guarantee resources access based on tasks priorities. Low priority tasks can then be preempted to allow the execution of high priority tasks. RTOS ensures that whenever a task  $\tau_i$  is running and a higher priority task  $\tau_j$  arrives, the task  $\tau_i$  is automatically interrupted in favor of the execution of  $\tau_j$ .

RTOS proposes specific schedulers responsible of the order of the tasks executions.

# Definition 25. (Scheduler [13])

A scheduler implements an algorithm or a policy for ordering the execution of the tasks on the processor according to some pre-defined criteria.

RTS scheduling is based on the scheduling policies provided by the scheduler.

**Definition 26.** (*Scheduling* [13]) Scheduling is a method by which tasks are given access to computing resources (e.g. processors) based on a predefined scheduling policy.

**Definition 27.** (Scheduling policy or scheduling algorithm [13]) Scheduling policy is the algorithm that defines how tasks have access to computing resources (e.g. processors).

A RTOS may support multiple scheduling policies that can be preemptive and non-preemptive, online and offline, fixed priority and dynamic priority.

**Definition 28.** (*Preemptive scheduling* [13]) A task execution can be arbitrarily suspended and restarted later without affecting the behavior of that task.

For example, a preemption occur if during the execution of a task, comes a higher priority task ready to be executed. In that case, the executing task is preempted in order to allow the execution of the higher priority task. The scheduler suspends an executing task through an interruption mechanism in order to allow another task to be executed. **Definition 29.** (*Non-preemptive scheduling* [13]) A task cannot be suspend during its execution.

In the case of non-preemptive scheduling, once a task gets access to a computing resource (i.e. processor), it cannot be interrupted. Its execution must be completed before the resource access can be given to another task.

**Definition 30.** (*Offline scheduling* [13]) A scheduler is static and offline if all scheduling decisions are made prior to the running of the system.

Offline scheduling is characterized by the definition of all scheduling decisions at compile-time, before the execution of tasks. The scheduling, already confirmed to allow all tasks to meet their deadlines, is specified via a scheduling table. Thus the system will be scheduled based on the scheduling table. It is fully deterministic because all the tasks information such as the list of the tasks and their activation times are predefined in the scheduling table. This method suits well for high critical RTS with high determinism requirements. It also leads to a low runtime overhead since the same scheduling (i.e. specified in the scheduling table) is repeated till the end of the system's running time. The inconvenience of offline scheduling is that it requires complete knowledge of the system's behavior, requirements and environmental situations.

**Definition 31.** (Online scheduling [13]) An online scheduler makes scheduling decisions during the runtime of the system.

In contrary to offline scheduling, the online scheduling is more flexible since the decisions are taken during the runtime. The decisions are based on both tasks characteristics and the current state of the system. Thus, it is less predictable than offline scheduling and may increase significantly the runtime overhead. However, it provides more flexibility such as the possibility to add new entities (e.g. tasks) to the system design.

**Definition 32.** (*Fixed priority scheduling*) In fixed priority scheduling, the priority assignment is done only once and hence the priority of a task will not change with time [51]. Tasks priorities are fixed offline at design [13].

Tasks priorities decide the order in which tasks are executed. They are fixed based on tasks attributes such as periods or deadlines. There are multiple algorithms such as Rate-monotonic and Deadline-monotonic that implemented fixed priority scheduling.

**Definition 33.** (*Rate-Monotonic*) In the Rate Monotonic algorithm (RM), all tasks are allocated a priority according to their periods. The shorter the period the higher their priority [52].

Tasks priorities are inversely proportional to their periods. Tasks with the same period can be resolved in an arbitrary manner [51]. Thus, Rate-Monotonic is devoted to periodic tasks only.

# Definition 34. (Deadline-Monotonic)

In the Deadline-Monotonic (DM), all tasks are allocated a priority according to their relative deadlines. The task with the shortest deadline is assigned the highest priority. The lowest priority is assigned to the longest deadline task [13].

Tasks priorities are inversely proportional to their deadlines. For a system where each task period value is equal to its deadline value, the DM and RM are similar.

**Definition 35.** (*Dynamic priority scheduling*) In dynamic priority scheduling, tasks priorities may change when the system is running [13].

Compared to fixed-priority scheduling, dynamic priority scheduling is more complex since tasks priorities are not static and fixed offline, but can vary during the runtime. This approach leads to an increase of the implementation complexity and the runtime overhead. However, it can allow systems with high processor utilization to become schedulable. The Earliest Deadline First (EDF) and Least Laxity First (LLF) are examples of dynamic priority scheduling.

**Definition 36.** (*Earliest deadline first*) In Earliest Deadline First, the task with the (current) closest deadline is assigned the highest priority in the system and therefore executes [13].

According to EDF, priorities are assigned dynamically and are inversely proportional to the absolute deadlines of the active jobs [53].

**Definition 37.** (Least Laxity First (LLF)) The task which has the least laxity first is assigned the highest priority in the system and is therefore executed [52]. The laxity of a task is defined as the deadline minus remaining computation time [13].

In LLF, the executing task has a constant laxity and will be preempted by a task whose laxity has decreased.

In the case of two tasks  $\tau_1$  and  $\tau_2$  with similar laxities,  $\tau_1$  will run for a short time and then will be preempted by  $\tau_2$  which will also run for a short time and will be preempted by  $\tau_1$ . Thus, when a system has tasks with similar laxities, LLF may lead to thrashing which means the processor spends more time doing context switches than useful work [13].

# 2.3 Real-time scheduling analysis

The scheduling analysis aimed to check the timing constraints of RTS. It mainly consists of feasibility and schedulability tests. This section presents the concepts of feasibility and schedulability in the context of RTS.

# 2.3.1 Feasibility and schedulability

**Definition 38.** (*Feasibility* [13]) *Feasibility is the assessment of a task set to meet all its timing constraints.*

A task set is feasible if there is a scheduling policy guaranteeing that all the timing constraints are met. Thus, for a given system, if all the tasks have all their jobs scheduled without any missed deadline, the system can be qualified as feasible.

**Definition 39.** (*Schedulability* [13]) Schedulability is the assessment of the feasibility of a tasks set under a given scheduling policy.

A task set is schedulable with a particular scheduling policy if none of its tasks will ever miss its deadlines during execution [13]. Feasibility is a broader concept that includes schedulability. It means first, that a schedulable task set is feasible. Second, a feasible task set that is schedulable under a given scheduling policy A, is not necessarily schedulable under another given scheduling policy B.

To assess feasibility or schedulability, we may apply tests.

**Definition 40.** (*Feasibility test* [54]) A feasibility test assesses whether a task set is feasible or not.

**Definition 41.** (Schedulability test [54]) A schedulability test assesses whether a task set is schedulable with a given scheduling policy or not.

Tests that define the feasibility or the schedulability of a task set can be classified into three categories: sufficient, necessary and exact test.