# Lithium-based Nano-ionic Synaptic Transistors For Neuromorphic Computing

Transistors synaptiques nano-ioniques à base de lithium pour le calcul neuromorphique

#### Thèse de doctorat de l'Université Paris-Saclay

École doctorale n° 575 : Electrical, optical bio : physics and engineering (EOBE) Spécialité de doctorat : Electronique et Optoélectronique, Nano- et Microtechnologies Graduate School : Sciences de l'ingénierie et des systèmes . Référent : CentraleSupélec

Thèse préparée dans les unités de recherche Laboratoire de Génie Électrique et Électronique de Paris (Université Paris-Saclay, CentraleSupélec, CNRS) et CEA-LETI, sous la direction de **Olivier SCHNEEGANS**, Chargé de Recherche CNRS, le co-encadrement de **Sami OUKASSI**, Ingénieur R&D CEA-LETI

Thèse soutenue à Paris-Saclay, le 19 décembre 2022, par

# **Ngoc Anh NGUYEN**

### **Composition du Jury**

| <b>Ahmad BSIESY</b><br>Professeur, Grenoble INP - UGA     | Président                |

|-----------------------------------------------------------|--------------------------|

| Fabien ALIBART                                            |                          |

| Chargé de recherche HDR, CNRS, Université Lille<br>(IEMN) | Rapporteur & Examinateur |

| Marc BOCQUET                                              | Rapporteur & Examinateur |

| Professeur, Université Aix-Marseille (IM2NP)              |                          |

| Marie-Paule BESLAND                                       |                          |

| Directrice de Recherche CNRS, Nantes Université           | Examinatrice             |

| (IMN)                                                     |                          |

| Damien QUERLIOZ                                           |                          |

| Chargé de recherche HDR, CNRS, Université                 | Examinateur              |

| Paris-Saclay (C2N)                                        |                          |

| Olivier SCHNEEGANS                                        |                          |

| Chargé de recherche HDR, CNRS, Université                 | Directeur de thèse       |

| Paris-Saclay (GeePs)                                      |                          |

**LHESE DE DOCTORAT**

NNT : 2022UPAST164

#### **DOCTORAL SCHOOL**

Electrical, Optical, Bio: Physics and Engineering (EOBE)

Titre : Transistors synaptiques nano-ioniques à base de lithium pour le calcul neuromorphique

Mots clés : nanoelectronique, calcul neuromorphique, transistors synaptiques, films minces, LiCoO<sub>2</sub>, LiTiO<sub>2</sub>

Résumé : En informatique, l'architecture actuelle de Von Neumann est confrontée à d'importantes difficultés dans la réalisation de tâches cognitives (de reconnaissance ou de classification d'images ou de sons par exemple). Pour surmonter cet obstacle, l'architecture neuromorphique représente une piste prometteuse vers la réalisation de traitements cognitifs performants avec une faible consommation énergétique. La conception de tels systèmes nécessite cependant le développement de synapses artificielles dont le comportement se rapproche de leurs analogues biologiques. À l'heure actuelle, de nombreuses recherches se concentrent sur des nanodispositifs spécifiques (memristors) dont la conductance électrique peut être modulée aisément afin d'émuler le comportement de liaisons synaptiques biologiques. Pour ces composants électroniques, deux configurations sont possibles (à 2 terminaux et à 3 terminaux). Parmi les synapses artificielles à 3 terminaux, les transistors ioniques apparaissent comme de bons candidats potentiels. Leur fonctionnement repose sur un empilement {canal/conducteur ionique} qui permet d'injecter/extraire des ions (via le conducteur ionique) dans la partie active du transistor (le canal), et de moduler ainsi finement la conductance électrique du composant.

universite

PARIS-SACLAY

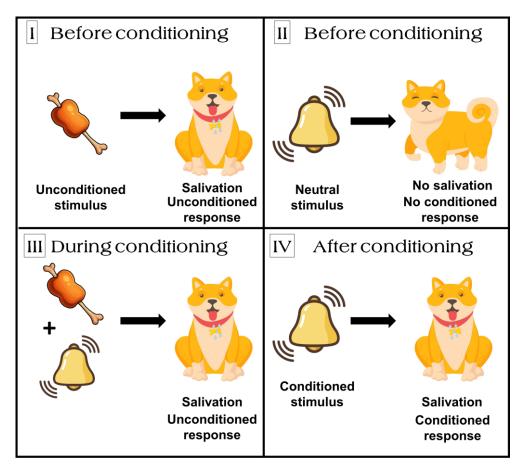

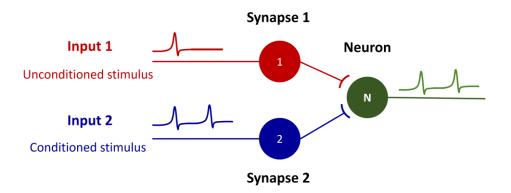

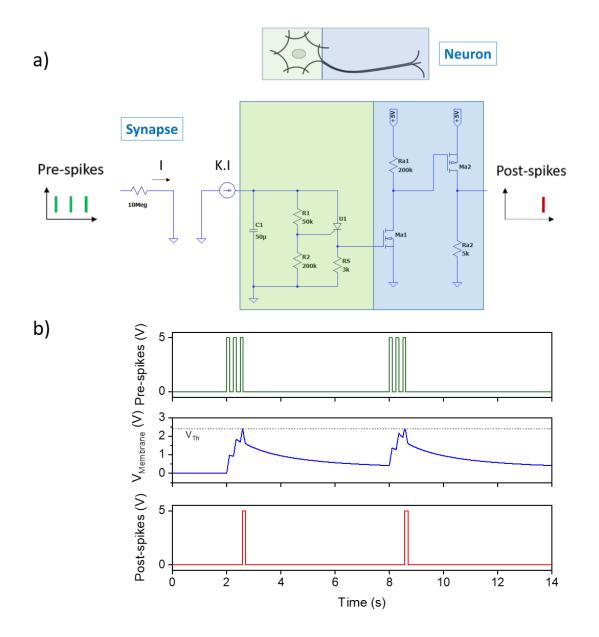

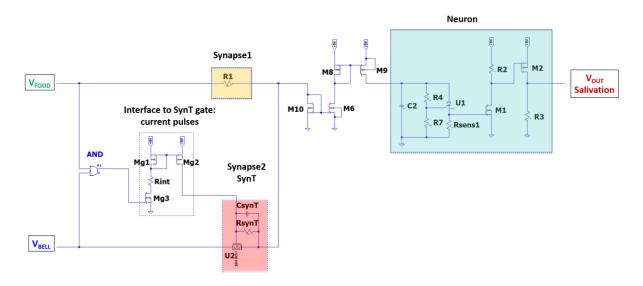

Dans cette thèse, nous explorons de nouveaux types de transistors nano-ioniques pour la réalisation de synapses artificielles. Nous avons d'abord élaboré des transistors synaptiques tout-solide à l'échelle d'un wafer en utilisant des techniques de microfabrication compatibles CMOS : une première génération de composants (deux types d'empilements possibles LiCoO<sub>2</sub>/LiPON, Li<sub>x</sub>TiO<sub>2</sub>/LiPON) a été réalisée. Les propriétés physiques et structurales de tels transistors ont été caractérisées par différentes techniques de microscopie et de spectroscopie (MEB, MET, spectroscopie Raman). Leurs performances en termes de comportement synaptique (modulation de la conductance, stabilité des états, non-linéarité, consommation d'énergie et endurance) ont été démontrées. Une étude électrochimique systématique (focalisée sur le matériau constituant le canal du transistor) a été réalisée, afin de proposer une explication sur l'origine des performances de ces composants. À partir des résultats expérimentaux, des réseaux de calcul neuromorphique (ANNs et SNNs) ont été simulés. En particulier, un réseau de neurones artificiels (ANN : artificial neural network) composés de matrices de transistors synaptiques a été simulé et testé sur différentes tâches de reconnaissance de formes. comportement coanitif Le de conditionnement classique (expérience de Pavlov) a également été simulé, montrant l'applicabilité potentielle de nos transistors synaptiques aux réseaux de neurones à impulsions (SNNs : spiking neural networks). Enfin, diverses approches (nouveaux designs, architectures et matériaux) ont été envisagées pour améliorer encore les performances globales de nos transistors synaptiques, vers une seconde génération de composants.

Title: Lithium-based nano-ionic synaptic transistors for neuromorphic computing

Keywords: nanoelectronics, neuromorphic computing, synaptic transistors, thin films, LiCoO<sub>2</sub>, LiTiO<sub>2</sub>

Abstract: The present Von Neumann computing architecture faces huge problems in achieving complex tasks such as recognition and classification. To overcome such bottleneck, neuromorphic computing represents an innovative and promising architecture towards performing intelligent and energy-efficient computation. The construction of such systems requires however the development of artificial synapses with biorealistic behavior. At present, a high research interest focuses on specific devices (memristors) whose electrical conductance can be tuned to emulate the evolution of biological synaptic weights. Two different device configurations (2-terminal and 3-terminal) are being explored. Among 3-terminal artificial synapses, ion-gated transistors appear as promising candidates. They rely on using an ion conductor as a gate dielectric to intercalate or extract ions into/from the channel layer following electrochemical reactions, thus, modifying the analog conductance states of the transistor.

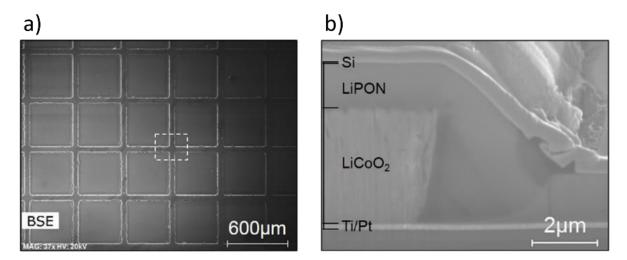

In this thesis, we explored novel nano-ionic transistors as synaptic components. We first managed to elaborate wafer-scale, all-solid-state synaptic transistors using CMOS-compatible microfabrication techniques: a first generation of transistors with two possible gate stacks

(LiCoO<sub>2</sub>/LiPON and Li<sub>x</sub>TiO<sub>2</sub>/LiPON) has been successfully realized. The physical and structural properties of these transistors have been characterized by different microscopy and spectroscopy techniques (SEM, TEM, Raman spectroscopy). Subsequently, synaptic behaviors such as conductance modulation, state retention, nonlinearity, energy consumption, and endurance have been demonstrated. We carried out a systematic electrochemical study (focused on the active channel material), and proposed an explanation on the performance of the synaptic transistors. Furthermore, from the experimental results, neuromorphic computing networks (ANN and SNN) have been simulated. Specifically, neural ANN cores composed of crossbar arrays including our synaptic transistors have been simulated, and tested with different pattern trained. recognition Besides, the tasks. Pavlovian conditioning experiment has been simulated, showing the potential applicability of our synaptic transistors to spiking neural networks (SNN). Finally, various approaches (new designs, architectures, and materials) have been considered improve further the overall transistor to performance, towards a second generation of synaptic transistors.

### ACKNOWLEDGEMENTS

I would like to express my gratitude to all the people who have supported me throughout the three years of my Ph.D. in this part.

First and foremost, I'm deeply indebted to my supervisors, Dr. Sami Oukassi and Dr. Olivier Schneegans. Thank you, Sami, for having always spent at least five minutes of your precious time on me and my problems. Your countless pieces of advice on scientific, technical, and professional aspects were essential to completing this work and my personal growth. Olivier, your supervision style was the warmest I have ever experienced. Weekly discussions with you always brought me lots of motivation and encouragement. Your pedagogical way of teaching and limitless patience helped me a lot in positioning and presenting research findings more efficiently. Your mentorship truly inspired me.

I would also like to show my deep gratitude to Dr. Fabien Alibart and Prof. Marc Bocquet, reviewers of my thesis, for their insightful comments and questions on the scientific content and presentation of my work. I am also very grateful to the committee members: Prof. Ahmad Bsiesy, Dr. Marie-Paule Besland, and Dr. Damien Querlioz, for their constructive suggestions and criticism during the thesis defense.

I would like to extend my sincere thanks to my entire team (LSME and LCRE at Leti-CEA) for your support on different aspects of my work. I very much appreciated the practical career advice from my managers, Dr. Raphael Salot and Dr. Yann Lamy. Thank you, Sylvain and Jouhaiz, for your aid on thin-film deposition. Thanks to Severine, Valentin, Jean-Marc, Jordan, Marjolaine, and Clemence for your assistance in the microfabrication process. Special thanks to Isabelle, Denis, and Anne-Marie, who have supported me in the device and material characterization.

Last but not least, I would like to express my deepest gratitude to my family in Vietnam, especially my mother, Pham Thi Hoa. Her daily care messages motivated me to work harder and be more resilient in this foreign country. I cannot end this part without saying thank you to my girlfriend, Nhat Anh, for her invaluable love and support. Thanks for always believing in me, for the hours of confiding, and the meals with the taste of home.

## **TABLE OF CONTENTS**

| INTRODUCTION                                                                                                                   | 8          |

|--------------------------------------------------------------------------------------------------------------------------------|------------|

| CHAPTER 1: Bibliographical study                                                                                               | 11         |

| CHAPTER 2: Microfabrication techniques of<br>synaptic transistors                                                              | 53         |

| CHAPTER 3: First generation of electrochemical<br>synaptic transistors                                                         | 97         |

| CHAPTER 4: Simulation of neuromorphic computing systems<br>composed of our Li <sub>x</sub> TiO <sub>2</sub> -based transistors | _135       |

| CHAPTER 5: Optimization towards a second generation<br>of synaptic transistors                                                 | 169        |

| CONCLUSIONS AND PERSPECTIVES                                                                                                   | _187       |

| Summary of the thesis in French (5 pages)                                                                                      | 191        |

| Publications during the thesis                                                                                                 | <u>197</u> |

### **INTRODUCTION**

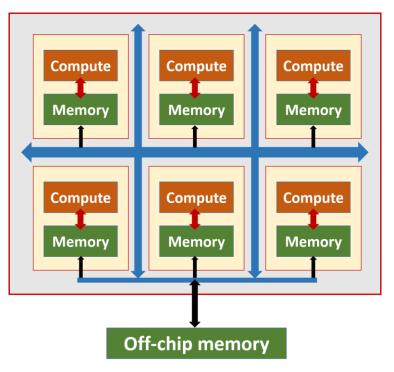

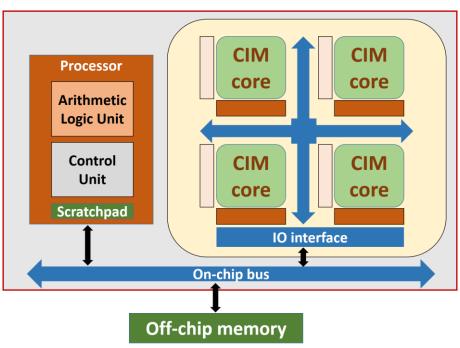

The conventional von Neumann computer plays a critical role in solving problems with different levels of complexity in almost every field of life. However, this computing architecture presents a bottleneck: a significant amount of time and energy are required to transmit data between processors and memory units. This barrier will inevitably limit computational efficiency, especially for solving data-intensive tasks such as pattern recognition, real-time speech, and visual computing. Taking the inspiration from the human brain, neuromorphic computing systems are expected to mitigate the aforementioned limit by performing the computations on the structured memory arrays with massive parallelism.

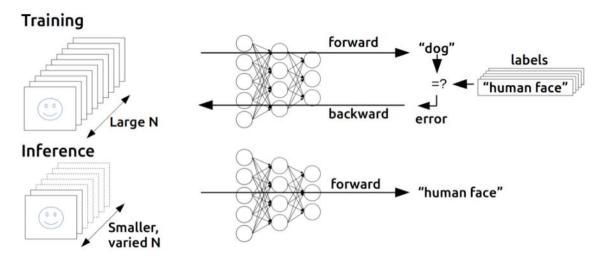

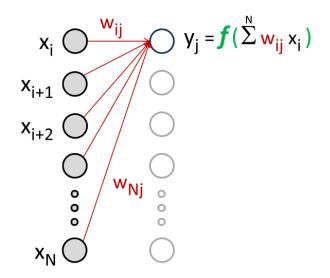

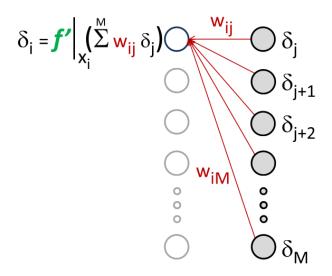

Neuromorphic computing systems are composed of neural networks (representing neurons) connected by artificial synapses. Developing brain-like computers requires artificial synapses that mimic the behaviors of their biological counterparts. Efforts have been made to simulate synaptic functions with CMOS analog circuits. However, they face a critical challenge in large-scale integrations, as tens of components are required to mimic one synapse. This mismatch in efficiency necessitates the search for single electronic devices that can emulate the synaptic functions. In recent years, specific devices (memristors) whose electrical conductance can be tuned to emulate the evolution of biological synaptic weights, have attracted much interest. These components can be subdivided in 2-terminal devices and 3-terminal devices. Each configuration has its own strengths and weaknesses. Specifically, in the 3-terminal configuration, the Write operation (synaptic weight modulation) is decoupled from the Read operation, allowing a better control of conductance tuning.

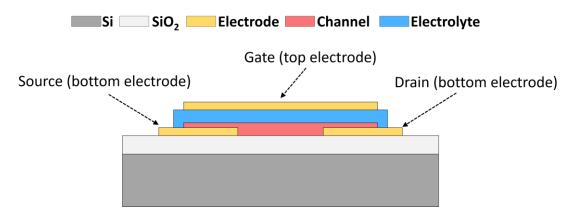

Among 3-terminal artificial synapses, electrochemical synaptic transistors (whose working principle is similar to that of biological synapses) appear as promising candidates. The electrical conductance of the channel is modified upon the intercalation of ions following redox reactions controlled by the gate potential, creating a robust mode of analog weight programming.

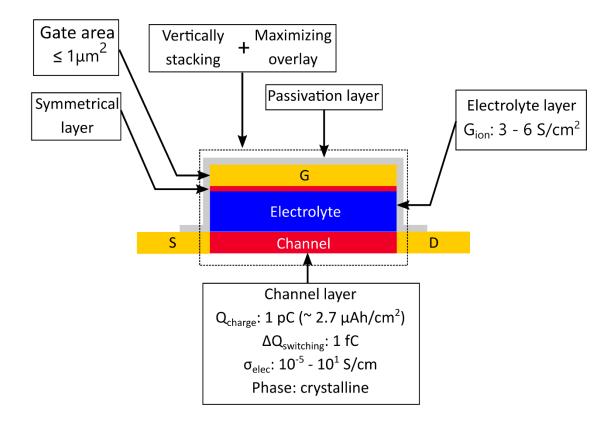

The large-scale integration of the electrochemical synaptic devices at wafer-scale fabrication is inexorable to develop the hardware for neuromorphic computing. There exist devices composed of liquid and polymer electrolytes and manually exfoliated channels, which prohibits however their further integration into dense computing chips. To overcome these drawbacks, the goals of my thesis are to (i) propose innovative solid-state synaptic transistors to optimize the overall performance (ii) elaborate and

characterize such solid-state electrochemical synaptic transistors with CMOS compatible processes, and (iii) demonstrate their required synaptic functionalities. The work in this thesis has been realized with the facilities of Laboratoire Composants pour la RF et l'Energie (LCRE), CEA-LETI, Grenoble and the Laboratoire Génie Électrique et Électronique de Paris (GeePs), Gif sur Yvette.

This dissertation is divided into 5 chapters. In the first chapter, we present a brief review of neuromorphic computing, its motivation, and its emerging artificial synapse solutions with a focus on electrochemical synaptic transistors. A global view of state-of-the-art electrochemical devices and their reported performance parameters is also presented.

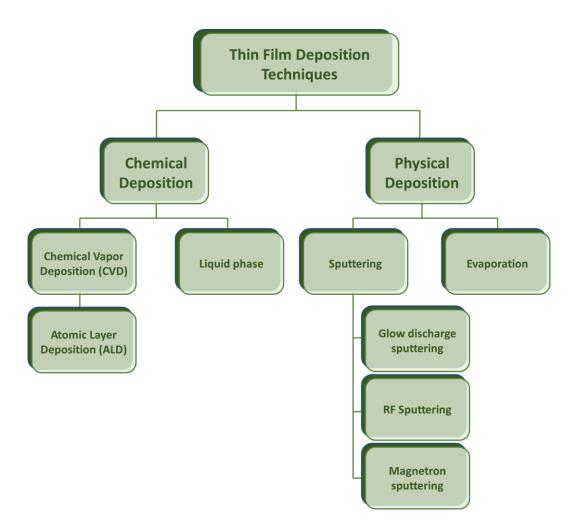

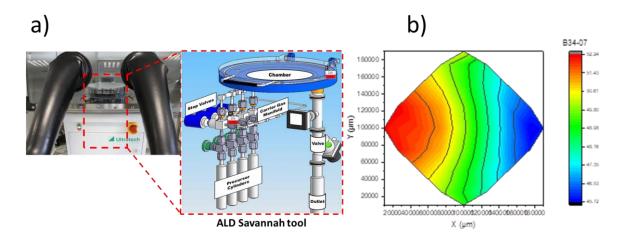

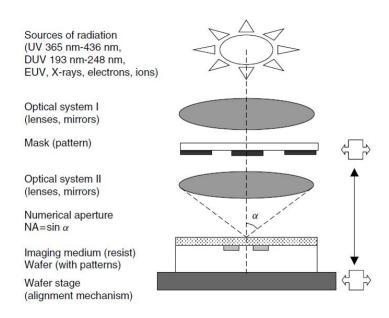

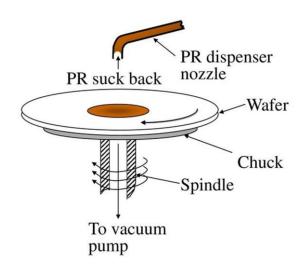

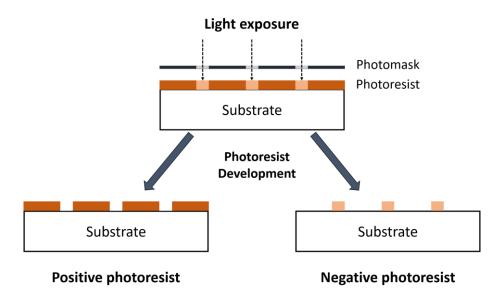

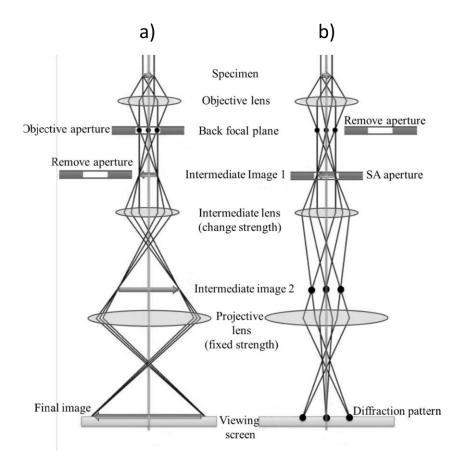

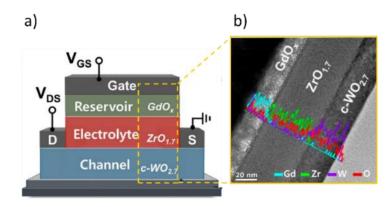

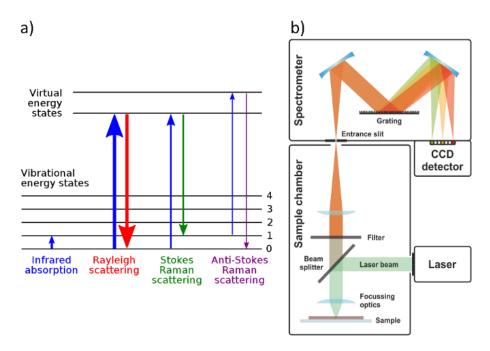

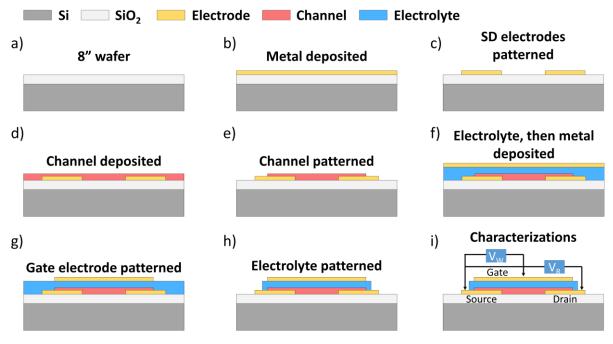

In chapter 2, we will introduce the processes in microfabrication, including thin-film deposition, patterning, and characterization techniques employed in elaborating the electrochemical synaptic transistors in this thesis. The detailed process flow to realize the synaptic transistors based on thin films with the progressive optimization progress is subsequently discussed.

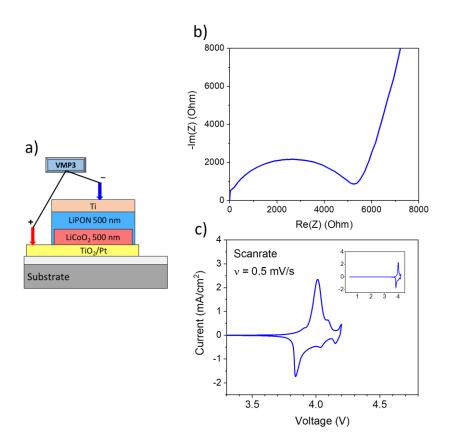

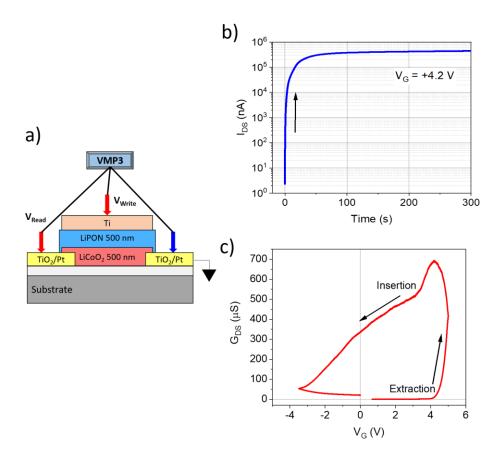

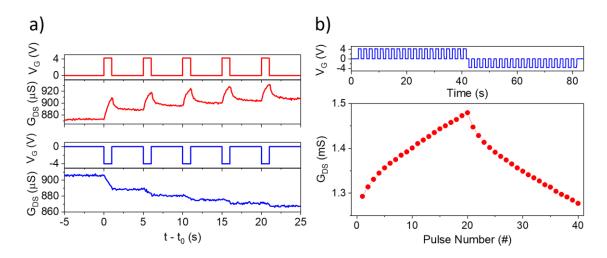

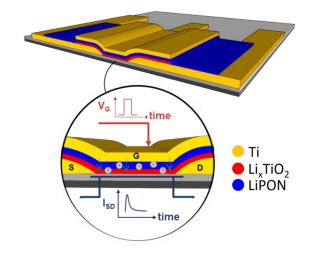

Chapter 3 is dedicated to showing the first functional generation of electrochemical synaptic transistors with two gate stacks:  $LiCoO_2/LiPON$  and  $Li_xTiO_2/LiPON$ . We will first present briefly the properties of the materials composing the transistors. We then investigate the electrochemical and electrical properties of  $LiCoO_2/LiPON$  devices with some preliminary tests. It is followed by a systematic study of  $Li_xTiO_2/LiPON$  systems in which we could demonstrate excellent synaptic behaviors of the electrochemical transistors and their correlation to the electrochemical phenomena.

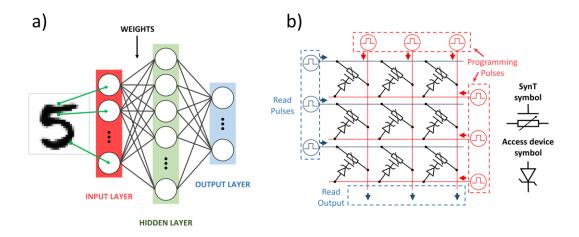

With the results obtained, we initiate in chapter4 the simulation of neuromorphic computing systems which take into account the properties of our synaptic transistors. An Artificial Neural Network (ANN) with analog synaptic transistor crossbar arrays, considering the nonlinearities of realistic devices, is simulated, trained, and tested with the MNIST pattern recognition task. A benchmark among the available artificial synapses is given. In addition, the Pavlovian conditioning experiment is examined with a neural electronic circuit, which includes our synaptic transistor as a learning element: this allows showing the potential applicability of our transistors to spiking neural networks (SNN).

In chapter 5, we will discuss measures to improve further the electrical performance of the synaptic transistors. Feasible approaches come from shrinking both lateral and vertical dimensions of the transistors to facilitate fast, energy-efficient programming pulses and linear, stable analog states. Besides, new ultrathin materials will be considered as an important axe for the next steps.

# CHAPTER I

# **BIBLIOGRAPHICAL STUDY**

## ABSTRACT

The first chapter will be dedicated to introducing the field of neuromorphic computing and neuromorphic hardware. This chapter is divided into 5 main sections. In the first section, we will present the urge to search for and develop a new computing architecture that can help digest the accumulated immense amount of data generated in an energy-efficient way.

Section 2 of this chapter introduces a bio-inspired solution - neuromorphic computing. We will briefly cover the functions of biological synapses and subsequently describe the methods implemented to mimic these brain functionalities using electronic components. With the main arguments of energy and space consumption, we argue the need for emerging synaptic devices to construct novel neuromorphic computing structures.

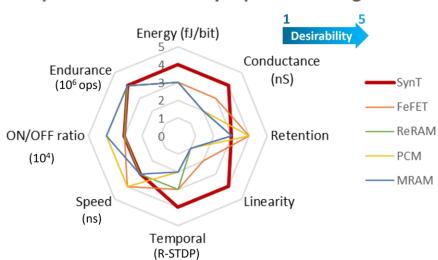

In section 3, we address the types of available electronic solutions for artificial synapses, including two-terminal devices (Resistive random-access memory – ReRAM, Phase-change memory – PCM, and Magnetic random-access memory – MRAM) and three-terminal devices (Ferroelectric field-effect transistor – FeFET and Electrochemical synaptic transistor – SynT). The operation principles of each type of device will be discussed.

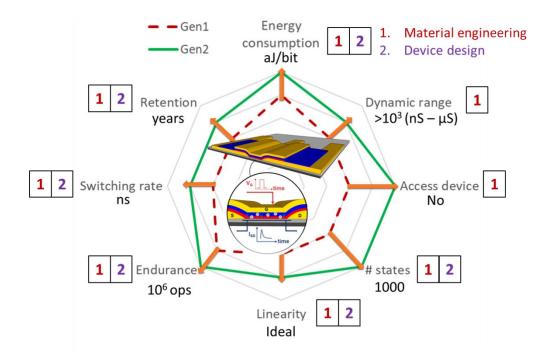

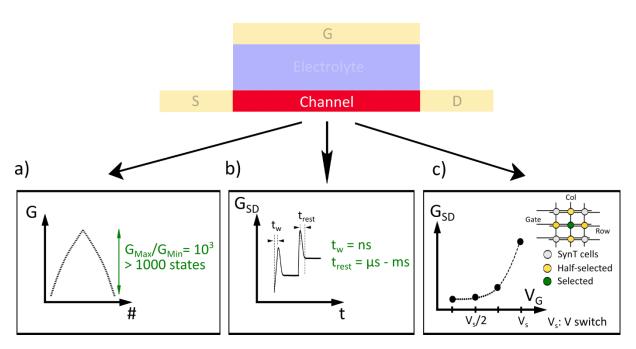

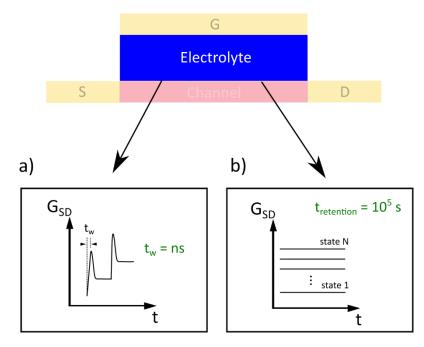

With the similarity to the biological synapses, SynT will be the focus of this thesis and will be explicitly presented in section 4. We first summarize recent works and the trends in the field of electrochemical synaptic transistors. Subsequently, the SynT figures of merit are discussed with methods and examples demonstrated on realistic synaptic transistors, paving the way to systematically characterize future SynTs. In section 5, we will comment on the overall state-of-the-art of the artificial synapses with the input from SynTs and other candidates, and main approaches to improve the performance of these devices. From there, this thesis's outline and scope are presented in section 6.

# Table of Contents

| 1 | THE NEED FOR A NEW COMPUTING PARADIGM |                                                             |    |  |  |  |

|---|---------------------------------------|-------------------------------------------------------------|----|--|--|--|

| 2 | NEU                                   | UROMORPHIC COMPUTING                                        | 17 |  |  |  |

|   | 2.1                                   | Biological synapses                                         | 17 |  |  |  |

|   | 2.2                                   | Neuromorphic computing – the brain emulation using hardware | 19 |  |  |  |

| 3 | THE                                   | E ARTIFICIAL SYNAPSES                                       | 21 |  |  |  |

|   | 3.1                                   | Two-terminal memristive devices                             | 21 |  |  |  |

|   | 3.2                                   | Three-terminal synaptic transistors                         | 22 |  |  |  |

|   | 3.2                                   | 2.1 Ferroelectric field-effect transistor (FeFET)           | 23 |  |  |  |

|   | 3.2                                   | 2.2 Electrochemical Synaptic Transistor (SynT)              | 24 |  |  |  |

| 4 | STA                                   | ATE OF THE ART IN ELECTROCHEMICAL SYNAPTIC TRANSISTORS      | 27 |  |  |  |

|   | 4.1                                   | Summary on the recent works                                 | 27 |  |  |  |

|   | 4.2                                   | Performance parameters of SynTs as artificial synapses      | 32 |  |  |  |

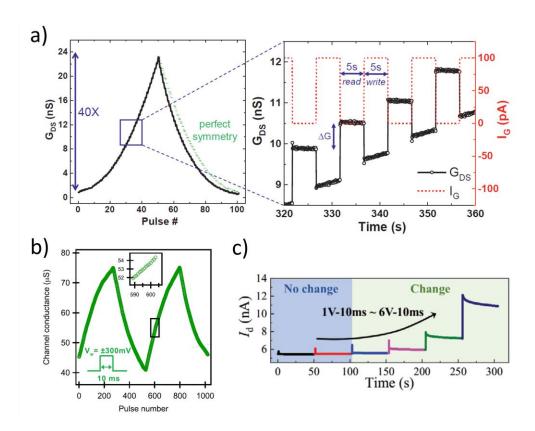

|   | 4.2                                   | 2.1 Conductance modulation                                  | 32 |  |  |  |

|   | 4.2                                   | 2.2 Analog states modulation                                | 35 |  |  |  |

|   | 4.2                                   | 2.3 Write nonlinearity                                      | 37 |  |  |  |

|   | 4.2                                   | 2.4 State retention                                         | 40 |  |  |  |

|   | 4.2                                   | 2.5 Energy consumption                                      | 41 |  |  |  |

|   | 4.2                                   | 2.6 Endurance                                               | 43 |  |  |  |

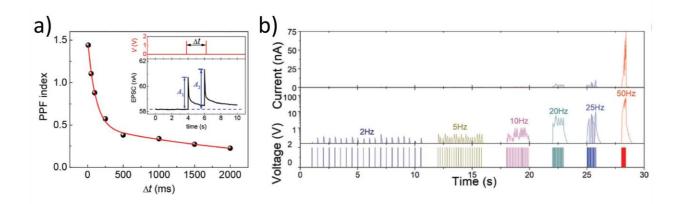

|   | 4.2                                   | 2.7 Temporal dynamics for SNN applications                  | 44 |  |  |  |

| 5 | COI                                   | NCLUSIONS                                                   | 46 |  |  |  |

| 6 | REF                                   | ERENCES                                                     | 49 |  |  |  |

## 1 THE NEED FOR A NEW COMPUTING PARADIGM

Ever since being conceptualized, Artificial Intelligence (AI) has revolutionized the world we are living in a way that no one could imagine. The ability to refine and analyze an enormous amount of datasets and then turn them into fantastic use cases of data that were not previously obvious to the naked eye makes it a genuine game-changer in this "Big Data" era. More and more data is being processed in various fields, such as health, business, and transportation, helping firms make critical data-driven decisions. However, such kind of cognitive operations of AI requires remarkable computing resources, owing to the current constraints posed by the conventional computing hardware platform, namely the termination of Moore's law and the Von Neumann (VN) bottleneck [1].

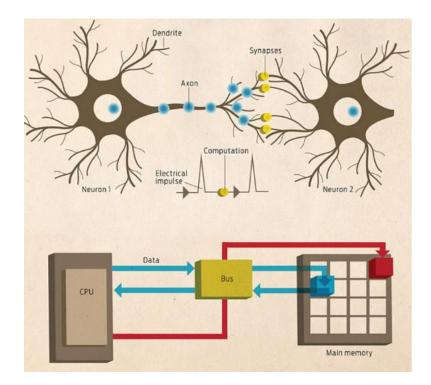

Figure I. 1: Brain versus Computer. (Top) Neurons in human brain are connected via billions of neural connections – synapses, creating a biological computer with energy- and time-efficient computing ability. (Bottom) Conventional computer structure with memory and processing units separated. This structure requires data to be shuttled between the two units and thus, the data latency is unavoidable [2].

Over the past few decades, together with the rapid evolution of micro-fabrication technology, computer chips' performances have been pushed to the edge. They could no

longer be appropriately described by the prediction of Moore in 1965 [3]. As the miniaturization continues, the transistors will eventually reach their atomic limits, which results in critical problems concerning current leakage, overheating, and thus, limiting the processing power of the nano-chips. For these reasons, it is complicated and extremely costly to ensure the ideal functionality across billions of devices. On the other hand, VN architecture implies the usage of a shared data bus between program and data memories, therefore, prohibiting the parallelism of instruction processing. Since the central processing unit (CPU) speed and memory size have increased much faster than the throughput between them, the bottleneck has become an increasingly severe problem with every new generation of CPU. As a result, to accelerate the development of AI, extensive research efforts have been made to optimize an alternative brain-inspired computing paradigm that is both energy and time-efficient – the neuromorphic computing systems (Figure I. 1).

The human brain exhibits an appealing Non-Von Neumann (Non-VN) computing paradigm for future computing systems that can complement or even replace the current VN architecture. Characterized by its massively parallel architecture connecting numerous lowpower computing elements (neurons) and adaptive memory elements (synapses), the brain can outperform modern processors on many cognitive tasks involving unstructured data classification and pattern recognition. Neuromorphic computing is an active multidisciplinary branch of research, combining physics, nanoelectronics, nanomaterials, neuroscience, and computer science. It serves the purpose of building and developing the materials, devices, and systems that closely mimic the human brain, targeting a new generation computing system that inherits the parallelism and low power operation of the mammalian nervous system.

By far, there are two main approaches to realizing brain-like computing, namely software simulation and hardware implementation. However, current software simulation often requires a huge amount of energy consumption and great physical space. For example, IBM's Blue Gene supercomputer is used for executing software simulations consuming roughly 10 MW of power [4]. Moreover, the software in digital computation performs calculations in series, and for these reasons, it is not suitable to mimic the parallelism of neural networks effectively. Such problems could be addressed if we can actualize a massively parallel neural network at a hardware level [5]. Hardware implementation aims to construct artificial neuron networks by using electronic devices. Since synapses are the functional connections of neurons and serve as the basic units of computing and learning, designing physical synaptic devices that exhibit synaptic behaviors is the key step to build brain-like computers. To achieve this, artificial neural networks (ANNs) have been developed and successfully applied in various fields. Despite the fact that these recent favorable outcomes in neuromorphic computing [6]–[8], the hardware implementation of these ANNs has been hindered by the fact that multiple CMOS transistors are required to mimic the behaviors of

the analog synapses. Furthermore, their energy consumption is much higher than the biological synapses to perform the same tasks [9]. Non-volatile electronic memory devices, including memristors and synaptic transistors, are rising as promising technologies to complement the conventional Si CMOS systems with a better energy and space tradeoff.

### 2 NEUROMORPHIC COMPUTING

#### 2.1 Biological synapses

The human brain is by far the most efficient computing system, which is not very surprising as it is the result of millions of years of evolution. The brain combines various types of cells, but the primary functional unit is a cell called a neuron. These neurons are responsible for generating and analyzing signals that control our emotions, memories, movements, thinking, and feelings; these are the traits that make us humans. A human brain contains approximately 10<sup>11</sup> neurons [10]. Each of them is made up of a cell body called soma, an axon, and multiple dendrites. Axon carries information from soma to a junction, where it is collected by dendrites of other neurons. The intersection is called a synapse, and the strength of the synapse (synaptic weight) decides the connection strength between two neurons, which can be altered by neural activities. This process is known as synaptic plasticity and is believed to be the backbone of human learning ability.

The synaptic inputs picked up by the dendrites of other neurons are then integrated by their own cells, encoded in the form of action potentials, and distributed to even more neurons from their axon terminals. Typically, each neuron is connected with about 10<sup>4</sup> other neurons, resulting in a large number (about 10<sup>15</sup>) of biological synapses in the human brain. With its high energy efficiency, the consumes averagely around 20 W of power for its functioning [11], yielding an energy consumption of approximately 1–10 fJ per synaptic event.

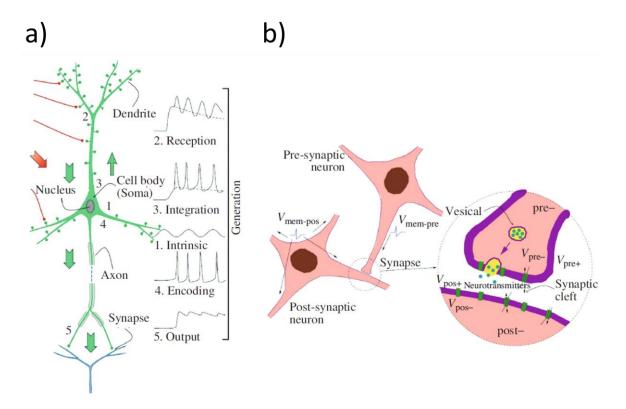

Various neuron interactions should be taken into consideration to understand how a neuron works. Each neuron carries out five essential functions as described in Figure I. 2.a: (1) Generate intrinsic membrane activity in the neuron; (2) Receive synaptic inputs in dendrites; (3) Combine synaptic inputs with the intrinsic membrane activity; (4) Generate outputs in the form of action potentials; (5) Distribute the outputs from axon terminals [12].

There are two fundamental types of synapses: electrical and chemical. Electrical synapses mainly exist in invertebrates – animals lacking a backbone, while chemical synapses are found in humans and other vertebrates. We will only focus on the chemical synapses in this study. The chemical synapse between two neurons is illustrated in Figure I. 2.b. At these synapses, information transfer from one neuron to another occurs through the release of neurotransmitters by one neuron (pre-synaptic neuron) and the detection of the neurotransmitters by an adjacent neuron (post-synaptic neuron).

*Figure I. 2: Schematic of neurons and chemical synapses. a. Different functional regions of a neuron. b. A synaptic connection between a pre-synaptic neuron and a post-synaptic neuron [13].*

The synaptic plasticity shown by chemical synapses is one of the most important neurochemical foundations of learning and memory in the brain. Chemical synapses consist of two types: excitatory or inhibitory [13]. In the brain, the synapse receptors for glutamate neurotransmitters are typically excitatory, whereas the receptors for GABA (Gamma-Aminobutyric acid) neurotransmitters are generally inhibitory. An excitatory receptor results in an Excitatory Postsynaptic Potential (EPSP) and drives the postsynaptic neuron closer to the depolarization threshold, which makes the cell "fire" an action potential. An inhibitory receptor results in an Inhibitory Postsynaptic Potential (IPSP) and drives the postsynaptic neuron further from the depolarization threshold. Axon terminals from many neurons can connect to a given neuron and release a variety of neurotransmitters, which impinge on excitatory and inhibitory receptors to produce EPSPs and IPSPs.

The postsynaptic neuron behaves like a tiny computer, integrating all the EPSPs and IPSPs, which later determines whether it will "fire" or not. When a neuron fires, the resulting action potential travels towards the synaptic cleft through its axon. The arrival of the action potential at the axon terminal results in the merging of neurotransmitter vesicles with the presynaptic membrane, and a subsequent release of the neurotransmitters into the synaptic cleft. The neurotransmitter diffuses through the synaptic cleft, binds to and activates a

receptor in the postsynaptic membrane, modifying the plasticity of the connection, i.e., the synaptic weight. In the learning phase, these synaptic weights are updated in an analog and parallel fashion based on multiple learning rules [13].

#### 2.2 Neuromorphic computing – the brain emulation using hardware

Modern computers are more capable of the enormous amount of information storage as well as fast numerical computation than that of human brains. Still, even the biggest and fastest supercomputers in the world cannot match the overall processing power of the human mind in performing cognitive and adaptive tasks, such as pattern recognition, perception, motor control, flexibility, and learning [14].

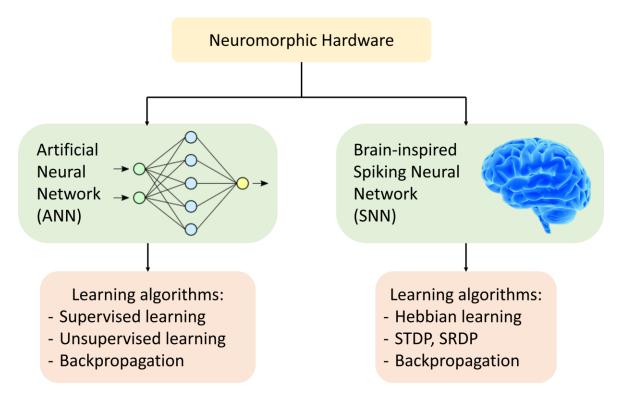

Due to these fantastic capabilities of the brain, it is very appealing to study its structure and working mechanisms in order to mimic it using electronic circuits. The study of the brain and its inspiration in developing computing systems has led to a new form of computer architecture, known as neuromorphic architecture. This field combines knowledge from multidisciplines in order to design artificial neural systems. The physical architecture, design principles, and computing algorithms of artificial systems are based on those of biological systems (Figure I. 3) [15], [16].

Although the behavior and connections between neurons can be partially simulated on a Von Neumann-architecture computer, such a system will consume excessive power, for example "MilkyWay-2" supercomputer [17] consumes a normal power of 20 MW compared to 20 W ultralow consumption of the human brain on real time processing tasks [18]. Furthermore, such a computing system is not capable of exploiting the architecture of the brain due to the fundamental differences between these two systems. As a result, a race is on to develop new types of devices and hardware architectures that can better resemble biointelligent systems at the physical level, and thus more efficiently emulate the brain at the functional level. For instance, the so-called neuromorphic circuit is built from devices that behave like neurons, transmitting and responding to information sent in the form of spikes rather than continuously varying voltages. Carver Mead, dating back to 1980s, first developed the concept of neuromorphic engineering. Mead described it as "using VLSI systems containing electronic analog circuits to mimic neurobiological architectures present in the nervous system [19]."

Figure I. 3: Neuromorphic hardware can be implemented via both artificial neural networks (ANNs) and brain-inspired neural networks. These two approaches rely on a different set of algorithms and learning rules, e.g. the backpropagation algorithm in ANNs, or the temporal dynamics in brain-inspired SNN concepts.

As the brain consumes extremely low energy, the first crucial step in realizing these hardware systems is to achieve a suitable device that can function as a synapse with low power consumption and desired plasticity. Accordingly, researchers have explored a variety of device systems with programmable conductance, also known as synaptic devices.

### **3** THE ARTIFICIAL SYNAPSES

In 1971, Chua first proposed the concept of memristor (memristive device) [20], which was defined as a two-terminal system with resistive switching (RS) effect that could demonstrate a variable and non-volatile resistance depending on the history of applied voltage and current. Later in 2008, the HP lab realized a device that has characteristics that described by Chua [21]. With this progress, huge research attention was dragged into developing and optimizing neuromorphic computing systems with memristors as the primary functional units [22]–[24] as well as the post-CMOS memory components themselves. Over the years, many types of memristive devices were developed for the artificial synapse application, including two-terminal devices (e.g. resistive random-access memory (ReRAM) [25], [26], phase-change memory (PCM) [27], magnetoresistive random-access memory (MRAM) [28]), and three-terminal devices (e.g. ferroelectric field-effect transistor (FeFET) [29], and electrochemical synaptic transistors (SynT) [30], [31]).

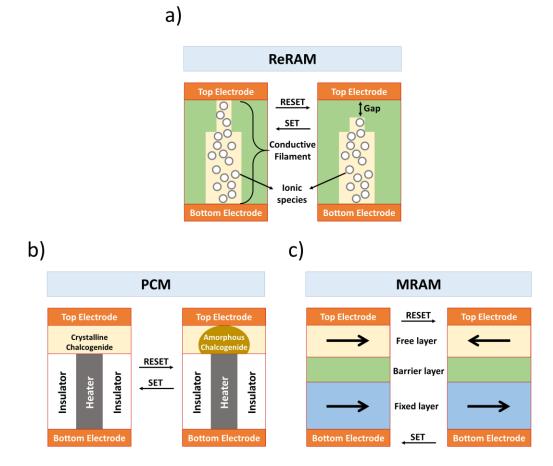

#### 3.1 Two-terminal memristive devices

Memristors usually have a simple metal/insulator/metal structure (see Figure I. 4) [32]. ReRAM memristors are two-terminal resistance switches that can retain their internal resistance states depending on the history of applied voltages/currents [33]. Based on the filament (conducting bridge) rupture mechanism, there are two types of memristive devices, namely, drift and diffusive memristors. PCM devices rely on the resistivity difference between two phases of a chalcogenide material (phase change material): the crystalline phase with low electrical resistivity and the amorphous phase with high electrical resistivity [34]. PCM devices are currently among the most mature devices for artificial synapses [35].

Spintronics-based MRAM consists of a tunneling oxide layer sandwiched by two metallic ferromagnetic layers: the free layer and the pinned layer. This structure is also called a magnetic tunnel junction (MTJ) [36]. The spin polarization of the pinned layer is fixed in a specific direction, while the free layer magnetization can be altered using an external current or magnetic field. Depending on whether the magnetization directions in the two layers are parallel or not, devices can exhibit a high resistance (opposite or antiparallel) state or a low resistance (parallel) state. The artificial synapses built on two-terminal devices have several advantages, such as low power consumption, simple device structure, small cell size, and easy large-scale integration with crossbar structure. However, the device variability and operation instability of the two-terminal synaptic devices may hinder their further applications in advanced artificial intelligent systems [37].

Figure I. 4: Memristor devices. a) Resistive random access memory (ReRAM). b) Phase change memory (PCM). c) Magnetoresistive random access memory (MRAM).

#### 3.2 Three-terminal synaptic transistors

By adding a third terminal to these devices, quite a several problems are mitigated. In comparison with two-terminal synaptic devices, three or multi-terminal synaptic transistors have the advantages of excellent stability, relatively controllable testing parameters, and robust operation mechanism [38]. Through proper material selection and structural design, transistors can convert external stimuli (light, pressure, temperature, etc.) into the electrical signal, which provides the possibility to achieve artificial synapses that can directly respond to the external environment. In addition, synergistic control of one device can be easily implemented in a transistor-based artificial synapse, which opens up the possibility of developing stable neuron networks with significantly fewer neural elements. More importantly, signal transmission and self-learning can be performed simultaneously in multi-terminal transistor-based artificial synapses. Therefore, transistors may be more suitable for simulating synaptic functions than other types of devices, especially for simulating concurrent

learning and dendrites integration that require a multi-terminal operation. In this section, the working mechanisms of the main synaptic transistor types, FeFET and SynT, are discussed with the focus on the central theme of the thesis as electrolyte-gated electrochemical synaptic transistors. A State-of-the-art review will follow to highlight the trends in this topic.

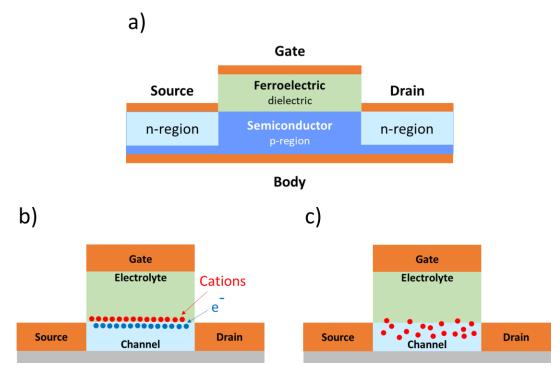

*Figure I. 5: Synaptic transistors: a) Ferroelectric field-effect transistor (FeFET). b) Electric double-layer electrochemical transistor. c) Ion intercalation electrochemical transistor [39].*

#### 3.2.1 Ferroelectric field-effect transistor (FeFET)

FeFETs have been actively studied for practical nonvolatile memory applications due to their non-destructive readout, low power consumption, and high operating speed. The ferroelectric insulator layer, whose polarization states are spontaneous, is the main component of this technology. Upon gating, the carrier concentration of FeFETs can be precisely and gradually modulated by changing the polarization state of ferroelectric materials [29]. For traditional memory applications, the ferroelectric insulator switches between two polarization states representing two digital states of the memory. Recently, FeFETs have attracted considerable attention as a promising platform for mimicking biological synapses thanks to the excellent multi-domain polarization switching capability of ferroelectric materials, which can be used to obtain multilevel FeFET channel conductance. The multilevel channel conductance of FeFETs can be utilized to record synaptic weight. A general schematic of a FeFET is shown in Figure I. 5. [40].

Ferroelectric synaptic transistors show some promising features, such as high stability, large ON/OFF ratio, fast programming operations, as well as fewer variations in the weight update curve [41]. However, they also suffer from scaling issues as floating-gate synaptic transistors because of their similar charge-based memory characteristics. In addition, they have difficulties implementing excellent short-term synaptic plasticity. Therefore, further research focused on addressing these limitations of FeFET-based synaptic devices is urgent.

#### 3.2.2 Electrochemical Synaptic Transistor (SynT)

An additional gate terminal and an ion-conducting electrolyte layer surrounding the channel material constitute the gate-stack of an electrochemical synaptic transistor. The ions inside the electrolyte could be driven toward and even into the channel material, leading to its conductance change. Such ionic dynamics much resemble the pre-synapse process emits synaptic transmitters, which then move across the synaptic cleft, pass the ion channels on the post-synapse, and finally enhance the post-synapse signal. There are two types of working mechanisms in SynTs: electric double-layer formation and ion intercalation.

#### 3.2.2.1 Electric double-layer formation

A constant gate voltage or a low-frequency gate pulse would drive the ions with opposite charges, e.g., cations, toward the channel material surface, leading to a cation accumulation. According to Electrostatics, such an accumulation would also call for a thin layer of electrons inside the channel material, near the material surface Figure I. 5.b. The cations and electron layer would form an ultra-thin capacitor, which is named the electric double-layer capacitor (EDLC). The ion-induced electron layer also functions as a conductive layer, which would significantly improve the conductance of the channel material, leading to the resistance change of the channel material. By engineering the intensity of the gate pulse, the ion density, and the type of ion inside the electrolyte, the formation of the EDL could be changed, which provides an approach to tuning the temporal behaviors of the channel conductance.

EDL-based devices possess many advantages compared to other mainstream mechanisms. The most important one is the extremely large electric field formed between the double layers, which can easily be more than 10 MV/cm due to the extremely short distance

between the two electrical layers. Such a strong electric field can hardly be achieved in conventional solid-state capacitors due to the dielectric breakdown or tunneling. It can lead to better gate control in artificial neuromorphic devices. In other words, the device can work at lower operation voltage compared to conventional devices. Moreover, in most cases, the electrolyte is only conductive to specific types of ions and is insulating to electrons. Hence, there only exists a very low leakage current between the resistive switching material and the controlling terminal. As a result, devices based on EDL formation can often work at a voltage lower than 0.3 V and possess energy consumption as low as 1.23 fJ/spike [33]. Moreover, after the controlling voltage is removed, the ions accumulated on the resistive material surface spontaneously diffuse back into the electrolyte and are re-distributed uniformly from a few milliseconds to a few seconds. This phenomenon leads to a significant current drop from the stimulated state to the original state, which can be read out by the source and drain terminals and greatly resembles the short-term plasticity inside biological systems.

#### 3.2.2.2 Ion intercalation

Another phenomenon that takes place inside electrochemical transistor systems is ion intercalation. The mobile ions in the electrolyte would migrate into the target material under the influence of the gate voltage following electrochemical redox reactions. As a result, the electrical property of the channel layer changes, see Figure I. 5.c. The intercalation effect has been widely studied in electrode materials used for battery cells, with LiCoO<sub>2</sub> and graphene nanosheets being the few types that have been thoroughly studied. Hence, for some layered structure materials, such as WSe<sub>2</sub>, MoS<sub>2</sub>, graphene, and some sub-stoichiometric salts, ions can get into the crystal structure and get stored inside the channel materials. Recent research studies have showed that intercalations inside neuromorphic devices are of two main types, namely electronic redistribution [30], [42] and phase transition of channel materials [43] induced by intercalation of external mobile ions.

Unlike the devices based on EDL, the intercalated ions could remain inside the channel materials even after the controlling voltage is removed, leading to a constant memory effect. By repeatedly applying voltage pulses to the gate relative to the open-circuit voltage (OCV) of the vertical cell, relatively the same amount of ions would be intercalated into the channel material, leading to a linear increase in channel conductance. The OCV measured from Gate-Source electrodes indicates the ionic concentration of the mobile ions inside the channel. Therefore, by controlling the gradual increase of this quantity, one can monitor the conductance change of the channel with precision. With the amount of inserted ions being controlled to the minimum, one can program analog conductance states with a large number of conductance states and small energy consumption of femto-Joule or less per WRITE action,

which is comparable to the biological synapses' operations. These features of ion intercalation SynTs indicate a great fit for bio-inspired computing applications such as artificial neural network (ANN), in which these transistors are the constituting elements.

Furthermore, desirable synaptic functions have been demonstrated with ion intercalation types of electrochemical synaptic transistors, such as short-term plasticity (LTP), long-term plasticity (LTP), spiking-time dependent plasticity (STDP), and spiking-rate dependent plasticity (SRDP) [31], [44]. The listed functions are the requirements for the next generation of the neural networks inspired by the biological nervous system, spiking neural network (SNN). They employ spiking neurons as computational units that process information with the timing of spikes. Therefore, SNNs provide the potential for spatiotemporal information processing with high time and energy efficiency.

# 4 STATE OF THE ART IN ELECTROCHEMICAL SYNAPTIC TRANSISTORS

#### 4.1 Summary on the recent works

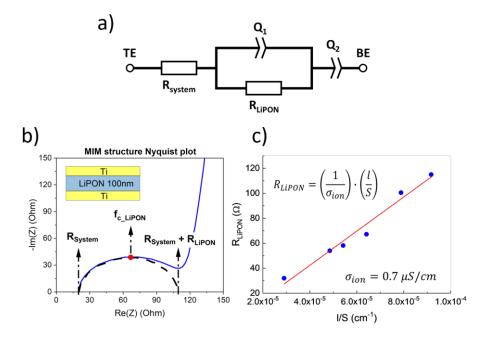

Electrochemical synaptic transistors have attracted much attention from researchers as a great candidate for artificial synapses, and this device will be my main subject throughout this thesis. Two types of electrolytes are used in these devices: ionic liquid (IL) and solid-state electrolytes. ILs have been widely studied for the use of electrolyte gating to induce extremely large modulations in the carrier densities at the interfaces and also a faster switching speed compared to solid-state electrolytes [45]. However, this electrolyte's main drawbacks are environmental dependence, e.g., humidity and unscalability [31]. In fact, from a technological point of view, it is challenging to incorporate liquid phase and environmental factors in the devices. Therefore, an all-solid-state electrolyte-gated transistor has a great potential for becoming the best candidate for a synaptic transistor with the application of neuromorphic computing. In this section, I will present some selected progress in the field of synaptic transistors. Table 1 will sum up the characterizations of the devices.

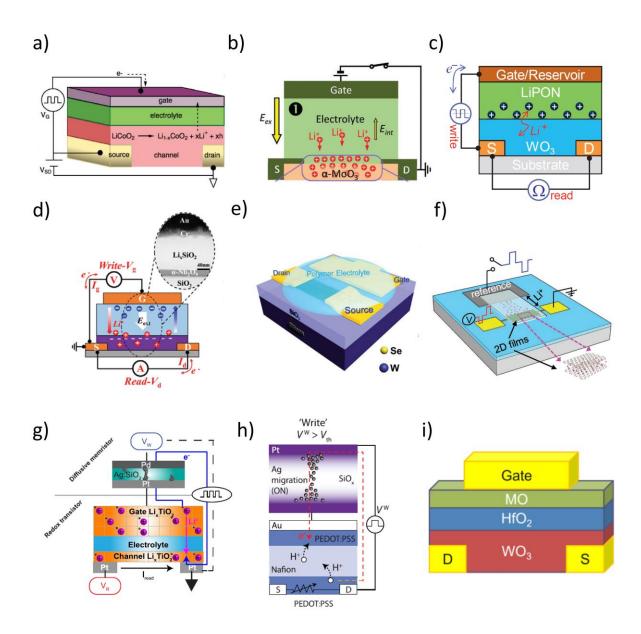

Among the current ions used for modulating the synaptic strength in the electrolytegated transistors, such as Oxygen O<sup>2-</sup> and protons H<sup>+</sup>, Lithium ions Li<sup>+</sup> show their merits in such tasks. Lithium-ion-based devices possess high reversibility and ultra-high stability of Li<sup>+</sup> ion under electrolyte gating. Fuller and coworkers demonstrated the modulation of the conductivity of the LiCoO<sub>2</sub> channel by intercalating (de-intercalating) Li<sup>+</sup> via LiPON electrolyte in their Li-ion synaptic transistor for analog computation (LISTA) (see Figure I. 6.a) [30]. LiCoO<sub>2</sub> is well-known for its reliability and endurance in electrochemical cycling. The removal of Li oxidizes  $Co^{3+}$  to  $Co^{4+}$  and generates positively charged polarons. As the fraction x in  $Li_{1-x}CoO_2$ is varied from 0 to 0.5, the material undergoes an insulator to metal transition, and this process is highly reversible. The LiPON electrolyte was chosen for its scalability, approximately down to 20nm in thickness, high ionic mobility (1.2  $\times$  10<sup>-6</sup> S/cm), and low electronic conductivity (8  $\times$  10<sup>-14</sup> S/cm) at room temperature. This pair of materials is also well studied in the field of all-solid-state micro-batteries. The electrical measurements of LISTA have shown promising characteristics of a synaptic transistor. It possesses a very dynamic conductance range in the order of micro Siemens, from 180 - 220 µS, with 200 nonvolatile states on average. In addition, high linearity, good endurance and low noise weight updates have been demonstrated. Achieving all this at a small cost of a few femto-Joule or even less

has been very promising and a driving factor toward brain-inspired energy-efficient neuromorphic computing.

Yang and *et al.* exploited the stacked structure of  $\alpha$ -MoO<sub>3</sub> to illustrate short/long-term plasticity (STP/LTP) with very low channel conductance (Figure I. 6.b) [31].  $\alpha$ -MoO<sub>3</sub> is a layered 2D material allowing the reversible intercalation of Lithium via a Faradaic reaction involving the reduction/oxidation of Mo ions. This process tunes the oxide electrical properties with minimal structural changes compared to that of the filament formation of memristors. The short and long-term plasticity, bidirectional analog, and near-symmetric weight update between LTP and LTD have been shown with ultralow channel conductance values (<75 nS) and picojoules operation energy. These traits are essential for high-energy efficiency. Another promising technology involving 2D van der Waals layered crystals, or quasi-2D transition metal-oxide whose properties can be tuned with ion gating has been shown to exhibit both STP and LTP owning to high-frequency gating. This phenomenon is accounted by the lithium-ion intercalation into the channel that yields a nonvolatile state before they can diffuse back into the electrolyte (volatile behavior).

At the device level, synapses are still implemented by dozens of digital complementary metal-oxide-semiconductor (CMOS) devices in today's artificial neural networks. Thus, developing synaptic elements with CMOS-friendly materials is highly desirable. Tang *et al.* presented an Electro-Chemical Random-Access Memory (ECRAM) employing the reversible Li-ion intercalation in the Tungsten oxide WO<sub>3</sub> channel via LiPON solid-state electrolyte (Figure I. 6.c) [46]. This nonvolatile transistor can have more than 1000 stable conductance levels, prolonged retention of programmed states, and high-speed writing at 5 ns. All of these characteristics are notably demonstrated at under 100 fJ. Li and colleagues show a high-performance,  $\alpha$ -Nb<sub>2</sub>O<sub>5</sub>-based single transistors and system (Figure I.6.d) [44]. The devices exhibit quasi-linear update, good endurance (10<sup>6</sup>) and retention, a high switching speed of 100 ns, ultralow readout conductance (<100 nS), and ultralow areal switching energy density (20 fJ/µm<sup>2</sup>). The prominent analog switching performance is leveraged for hardware implementation of an SNN with the capability of spatiotemporal information processing, where spike sequences with different timings are able to be efficiently learned and recognized by a 32x32 crossbar array.

Figure I. 6: Recent electrochemical synaptic transistors. a) E. J. Fuller's SynT in 2017, composing of LiCoO<sub>2</sub> channel and LiPON electrolyte films [30]. b) C-S Yang's SynT in 2018, composing of  $\alpha$ -MoO<sub>3</sub> channel and PEO:LiClO<sub>4</sub> polymer electrolyte films [31]. c) J. Tang's SynT in 2018, composing of WO<sub>3</sub> channel and LiPON electrolyte films [46]. d) Li's SynT in 2020, composing of  $\alpha$ -Nb<sub>2</sub>O<sub>5</sub> channel and LixSiO<sub>2</sub> electrolyte films [44]. e) J. Zhu's SynT in 2018, composing of 2D WSe<sub>2</sub> channel and PEO:LiClO<sub>4</sub> polymer electrolyte films [48]. g) Y. Li's 1S1T in 2019, composing of a memristive Pd/Ag:SiO<sub>2</sub>/Pt selector, anatase-phase LixTiO<sub>2</sub> channel and PEO:LiClO<sub>4</sub> polymer electrolyte films [48]. g) Y. Li's 1S1T in 2019, composing of a memristive films [49]. h) E. J. Fuller's 1S1T in 2019, composing of a CBM Pt/Ag/SiO<sub>x</sub>N<sub>y</sub>/Ag/Pt selector, PEDOT:PSS polymer channel and Nafion polymer electrolyte films [50]. i) . S. Kim's selectorless SynT in 2019, composing of WO<sub>3</sub> channel and HfO<sub>2</sub> electrolyte films [51].

Novel approaches involving two-dimensional (2D) materials have demonstrated high performance of synaptic functions based on the exotic physics of these layered materials and the potential for further scaling for synaptic devices. Zhu et al. presented an ionic-gatingmodulated synaptic transistor in which the channel is made-up of a 2D van der Waals layered crystal such as WSe<sub>2</sub>, NiPS<sub>3</sub>, and FePSe<sub>3</sub> (Figure I. 6.e) [47]. These devices have shown almost linear potentiation and depression with multiple conductance states (<200 nonvolatile states), as well as very low energy consumption of 30 fJ per spike. However, a challenge with this device might stem from its tiny conductance change (approximately 300 pS), which is too subtle for realistic measurements and applications. In 2017, Sharbati and colleagues realized an energy-efficient electrochemical transistor with a layered Graphene channel (Figure I. 6.f) [48]. While the electrochemical behaviors of graphite with Li ions have been thoroughly characterized since this material has already been widely used as an anode in Li-ion batteries, Li ions also have been reported to have an unusually high diffusion coefficient  $(7 \times 10^{-5} \text{ cm}^2 \text{s}^{-1})$ in bilayer graphene at room temperature. This combination has resulted in a well-performed transistor with linear, precise, and reversible conductance change, together with scalability in switching speed and operation energy. However, devices based on low-dimensional materials show certain integration issues due to the immature deposition techniques. Thus, they are unsuitable for the further development of neural networks composed of a large number of synaptic components.

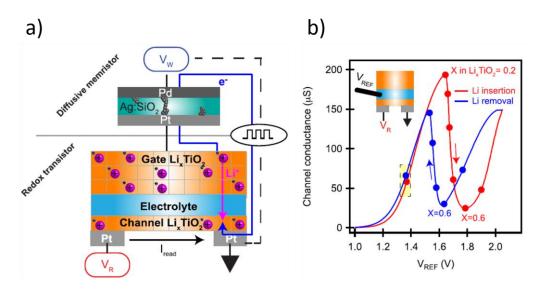

Another recent concept that has caught the attention of researchers is combining an additional two-terminal memristive device connected in series with the gate of the synaptic transistor. This memristor acts as a switch to selectively program the transistor and prevent further unattended conductance changes through the gate [52]. Li et al. demonstrated a cell, i.e., 1 selector & 1 transistor, in which they utilized a two-terminal low-voltage threshold switch based on Ag filament formation (Figure I. 6.g) [49]. Concerning the transistor, they used a stack of LiTiO<sub>2</sub>/LiClO<sub>4</sub>:PEO/LiTiO<sub>2</sub> to reduce the built-in open-circuit voltage. Because of this combination, they were able to demonstrate linear potentiation and depression of the channel conductance in more than 250 states with long retention. In addition to those, the write noise can be as low as 200 mV, corresponding to roughly 0.3 fJ per weight update. Similarly, Fuller and colleagues realized a 1S1T cell with the same memristor, but proton (H<sup>+</sup>) was utilized instead of Li<sup>+</sup> ion (Figure I. 6 h) [50]. Another design worth mentioning in this section is the selector-free synaptic transistor presented by Kim et al. in his 2019 paper (Figure I. 6.i) [51]. Their idea is to create an additional oxide layer between the gate electrode and the electrolyte. This layer generates a supplementary nonlinearity in the IV characteristic that can act as a transistor threshold switch. Even though clear evidence behind this phenomenon was not provided in the article, the "selector-free" approach will gradually be a requirement for fully developed synaptic transistor technology.

| Chara                               | Devices                                                                                                                                                                                                                                                                                                                                                                                 | <b>a</b> [30]                                                                                                                        | <b>b</b> [31]                                                                                                                                                                                       | <b>c</b> [46]                                                                                                 | <b>d</b> [44]                                                                                                                                                                            | <b>e</b> [47]                                                                                                                                                          | <b>f</b> [48]                                                                                                                     | <b>g</b> [49]                                                                                                                                                                                                                                                          | <b>h</b> [50]                                                                                                                  | i[51]                                                             |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Mobi                                | ile Ion                                                                                                                                                                                                                                                                                                                                                                                 | Li+                                                                                                                                  | Li+                                                                                                                                                                                                 | Li+                                                                                                           | Li+                                                                                                                                                                                      | Li+                                                                                                                                                                    | Li+                                                                                                                               | Li+                                                                                                                                                                                                                                                                    | H+                                                                                                                             | Li+                                                               |

| Chai                                | nnel                                                                                                                                                                                                                                                                                                                                                                                    | Li <sub>1-x</sub> CoO <sub>2</sub>                                                                                                   | α-MoO <sub>3</sub>                                                                                                                                                                                  | WO <sub>3</sub>                                                                                               | α-Nb <sub>2</sub> O <sub>5</sub>                                                                                                                                                         | WSe <sub>2</sub>                                                                                                                                                       | Graphene                                                                                                                          | Li <sub>1-x</sub> TiO <sub>2</sub>                                                                                                                                                                                                                                     | PEDOT:PSS                                                                                                                      | WO <sub>3</sub>                                                   |

| Dimensions                          |                                                                                                                                                                                                                                                                                                                                                                                         | SD: Pt<br>Gate: Si<br>Electrolyte :<br>LiPON 400<br>nm<br>Channel :<br>Li <sub>x</sub> CoO <sub>2</sub><br>120nm thick<br>2µm length | SD and Gate:<br>Cr/Au<br>60/5 nm<br><u>Electrolyte</u> :<br>PEO:LiClO <sub>4</sub><br><u>Channel</u> : α-<br>MoO <sub>3</sub><br>16.8 - 28 nm<br>thick (12-20<br>layers)<br>7µm length<br>4µm width | Electrolyte:<br>LiPON<br><u>Channel</u> : WO <sub>3</sub><br>0.3-10-80 μm<br>length<br>0.3-60-<br>100μm width | <u>SD:</u> TiN 40<br>nm <u>Gate</u> :<br>Cr/Au<br><u>Electrolyte</u> :<br>Li <sub>x</sub> SiO <sub>2</sub> 80 nm<br><u>Channel</u> : α-<br>Nb <sub>2</sub> O <sub>5</sub> 20 nm<br>thick | <u>Gate</u> : Pd/Au<br>50/10nm<br><u>Electrolyte</u> :<br>PEO:LiClO <sub>4</sub><br><u>Channel</u> :<br>WSe <sub>2</sub><br>(5 – 48layers)<br>1 μm length<br>3μm width | Electrodes:<br>Cu<br>80nm<br>Electrolyte:<br>PEO:LiClO₄<br>Channel:<br>Graphene<br>3 – 20 nm<br>thick<br>15µm length<br>4µm width | $\frac{\text{SD:}}{\text{SD:}} \text{Pt}$ (50nm)<br><u>Gate</u> : Li <sub>x</sub> TiO <sub>2</sub><br>(90nm)<br><u>Electrolyte</u> :<br>PEO:LiCIO <sub>4</sub><br><u>Channel</u> :<br>Li <sub>x</sub> TiO <sub>2</sub> 8μm<br>thick<br>200 μm<br>length<br>10 μm width | Electrodes:<br>Ti/Au 5/100<br>nm<br>Electrolyte:<br>Nafion<br>Channel:<br>PEI/PEDOT:PS<br>S<br>125 μm<br>length<br>45 μm width | <u>Channel:</u><br>WO₃<br>W/L from<br>100/100<br>µm to<br>10/4 µm |

| Physical characterizations          |                                                                                                                                                                                                                                                                                                                                                                                         | SEM                                                                                                                                  | AFM                                                                                                                                                                                                 | TEM                                                                                                           | TEM, SIMS,<br>GIXRD, AFM,<br>XPS                                                                                                                                                         | FIB-HRTEM,<br>SAED, AFM                                                                                                                                                | Optical<br>imaging,<br>Raman Spec                                                                                                 | Optical<br>imaging,<br>SEM                                                                                                                                                                                                                                             | -                                                                                                                              | TEM                                                               |

| Electrical<br>Characte<br>rizations | Conductance range : $G_{SD}$ or I = f(V) using gate sweep (V <sub>G</sub> or I <sub>G</sub> )         Number of states: $G_{SD} = f(pulse number)$ for one cycle.         Linearity: $\Delta G = f(G_0)$ , $G = f(pulse number)$ for one cycle         Retention: G or I = f(t)         Endurance: cycling cycles         Energy consumption: $\Delta G = f(t_w)$ , E = f(channel area) |                                                                                                                                      |                                                                                                                                                                                                     |                                                                                                               |                                                                                                                                                                                          |                                                                                                                                                                        |                                                                                                                                   |                                                                                                                                                                                                                                                                        |                                                                                                                                |                                                                   |

|                                     | Unique                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                    | C = f(Freq)<br>STDP                                                                                                                                                                                 | -                                                                                                             | STDP                                                                                                                                                                                     | SRDP, STDP                                                                                                                                                             | STDP                                                                                                                              | -                                                                                                                                                                                                                                                                      | -                                                                                                                              | -                                                                 |

### Table 1: Summary of current SynTs' device characterizations (Figure I. 6)

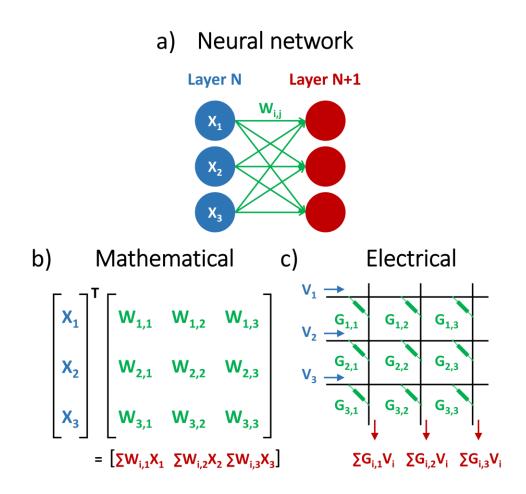

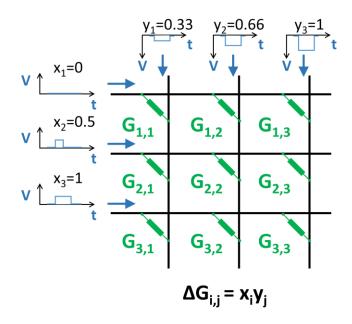

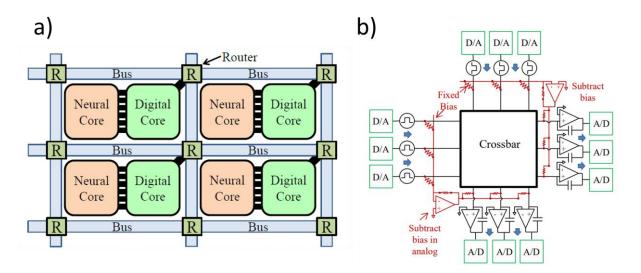

#### 4.2 Performance parameters of SynTs as artificial synapses

The non-volatile synaptic transistors are developed for constructing novel neuromorphic computing architectures to achieve memory density, energy efficiency, and massive parallelism for data-centric tasks. Crossbar arrays built from SynTs reduce the computing cost by alleviating the need to shuttle data from memory storage to the central processing unit. To do so, the connected SynTs, in the role of artificial synapses, act as an embedded memory by storing information in a non-volatile manner in their channels' conductance. Subsequently, the crossbar systems perform neural computing operations such as vector-matrix multiplication and parallel weight updates. For SynTs to become good candidates for artificial synapses, they must meet some electrical characteristics, such as conductance modulation with linear and symmetric profile, analog state retention, endurance, and low energy consumption per operation. I will discuss these figures of merit in detail in the following subsections.

#### 4.2.1 Conductance modulation

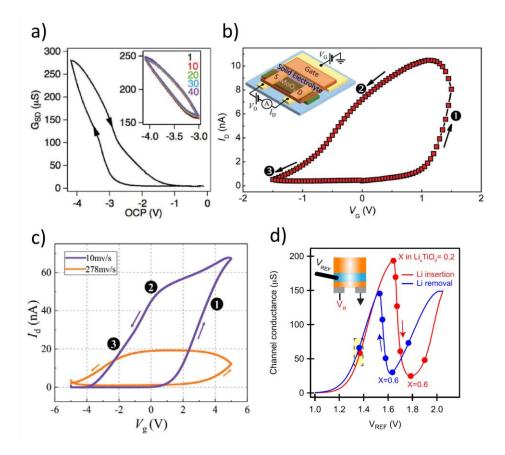

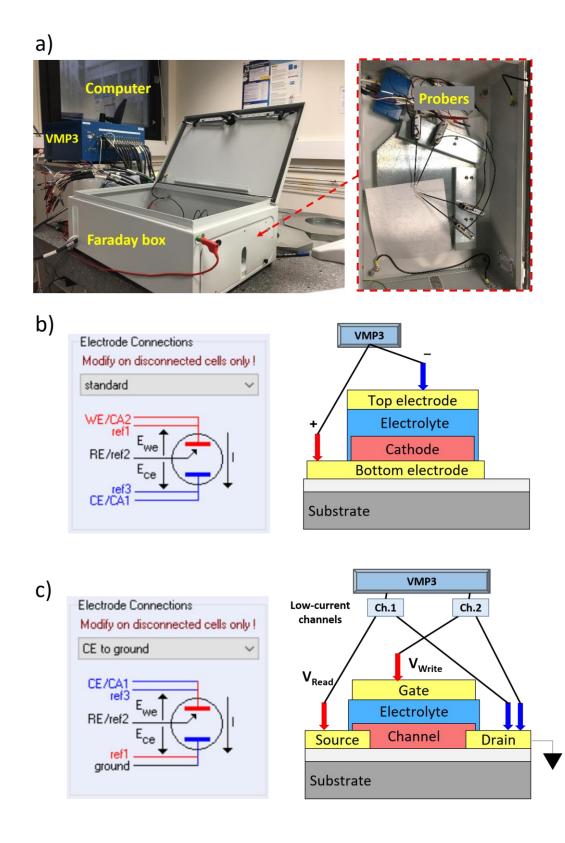

When studying SynT, the most important figure of merit is the hysteresis change of channel conductance, between the lowest conductance to the highest conductance (see Figure I. 7). The source electrode is grounded to measure this, and a linearly ramped voltage is applied on Gate-Source (GS) electrodes while recording the current flowing through Drain-Source (DS) electrodes. Observing this bidirectional change of the DS conductance is considered proof of the concept of electrochemical synaptic transistors. The scan speed (scan rate) is of great importance in determining the conductance modulation of the SynTs. The scan rate signifies how fast the applied potential is linearly varied. It is often presented in the unit of [V/s] or constant Gate current [A] by controlling an unchanged current flowing out of the electrodes.

The electrical property of the channel layer is modified upon the change of its ion content via the charge (ion extraction) and discharge (ion insertion) processes. Fuller *et al.* demonstrate the change of Li<sub>1-x</sub>CoO<sub>2</sub> conductivity by monitoring the gate current to be  $|I_G| = 350$  nA for a full charge-discharge cycle and record the DS conductance (Figure I. 7.a) [30]. When the gate voltage (Open circuit potential – OCP) decreases from 0 V to -4.2 V (the charge process), the conductance of the channel increases from 4.5 to 270 µS. The discharge process drives the conductance back to the initial low conductance state and the gate voltage from - 4.2 V to 0 V. To avoid the saturation region, where the modulation of the conductance is low under the sweep of gate voltage, a voltage window of [-4.1 V, -3.0 V] is selected. The shown

profiles of cycles 1, 10, 20, 30, and 40 on this voltage window on the inset prove that these bidirectional scans are stable.

Figure I. 7: Conductance modulation of channel layer under Gate voltage sweeps. a)  $Li_xCoO_2$  channel SynT works in the range of under 300  $\mu$ S [30]. b)  $\alpha$ -MoO<sub>3</sub> channel SynT works in the range of under 240 nS [31]. c)  $\alpha$ -Nb<sub>2</sub>O<sub>5</sub> channel SynT works in the range under 700 nS or 200 nS depending on the sweep rate [44]. d) Anatase  $Li_xTiO_2$  channel SynT works in the range of under 200  $\mu$ S [49].

A similar hysteresis conductance curve was also demonstrated on an  $\alpha$ -MoO<sub>3</sub>-based SynT (Figure I. 7.b) [31]. The voltage window used for this scan is from -1.5 V to 1.5 V at 20 mV/s. Lithium (Li<sup>+</sup>) ions intercalate into the 2D  $\alpha$ -MoO<sub>3</sub> film and induce an important high/low conductance ratio of 17 at V<sub>G</sub> = 0 V. As we can observe from the curve, there is no significant change in DS current until the V<sub>G</sub> reaches 1 V. This is explained by the accumulation of mobile Li ions on the topmost layer of the  $\alpha$ -MoO<sub>3</sub> nanosheets before actually intercalating into the lattice of the channel with the increase of Gate potential. In contrast to the rapid increase of I<sub>DS</sub> from the forward scan, the decrease of channel conductivity under Li extraction is rather steady from the high conductance to the initial low conductance. This gradual decline of conductance can be explained by the fact that Lithiated  $\alpha$ -MoO<sub>3</sub> (Li<sub>x</sub>MoO<sub>3</sub>) is thermodynamically stable, and a high negative Gate voltage is required to extract all the

inserted Li ions. The difference in dynamics between forward and reversed scans creates the large hysteresis curve as observed.

Intercalation processes of mobile ions into various types of channel material have different timescales, and these timescales of the experiment are determined by scan rate. Li *et al.* show the bidirectional curves at different 2 scan rates of 10 mV/s and 278 mV/s with their  $\alpha$ -Nb<sub>2</sub>O<sub>5</sub>-based SynT (Figure I. 7.c) [44]. The V<sub>G</sub> is swept from –5 to 5 V, creating a counter-clockwise loop with a large high/low current ratio. It is clear from graph that with smaller scan rate (10 mV/s) the ratio of high/low conductance is 3.5 times higher than that of higher scan rate (278 mV/s). This explains the fact that with slow scan rates, Li ions have more time to intercalate into  $\alpha$ -Nb<sub>2</sub>O<sub>5</sub>, and thus the modulation of electrical property is of higher importance. However, one should keep in mind that the scan rates partially represent the realistic resistive switching speed of SynTs. Therefore, we have to select carefully a balanced trade-off between a high ON/OFF ratio and fast switching devices.

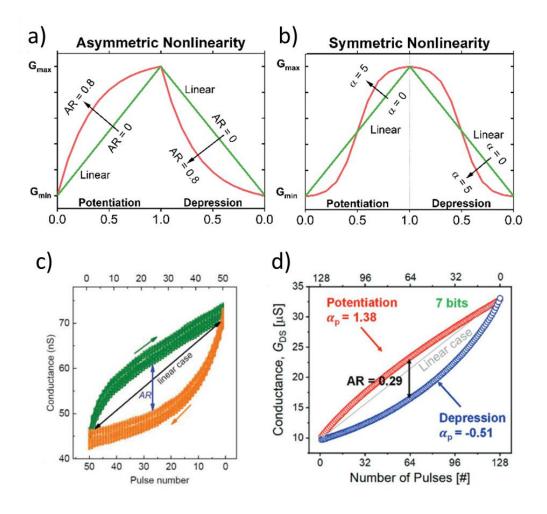

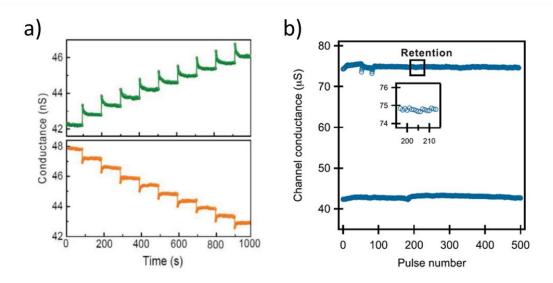

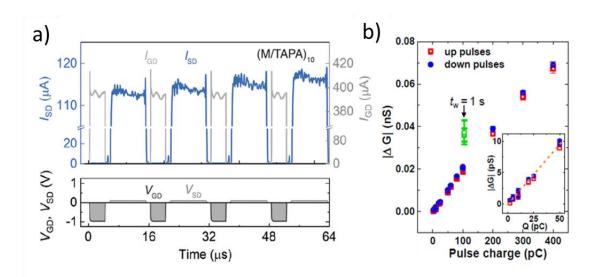

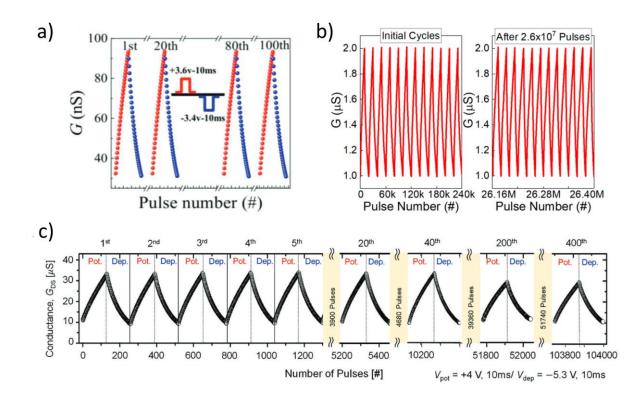

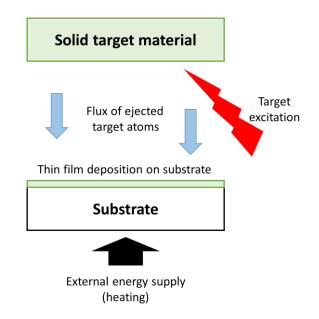

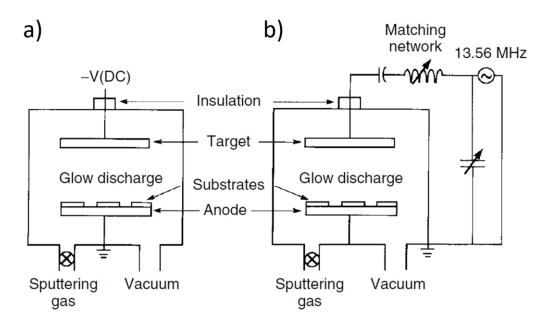

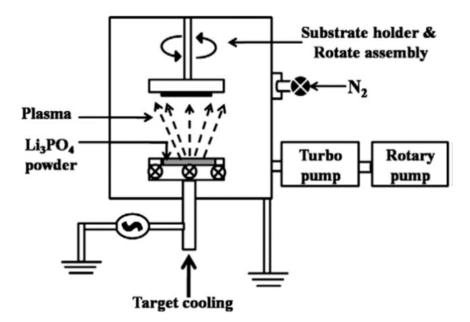

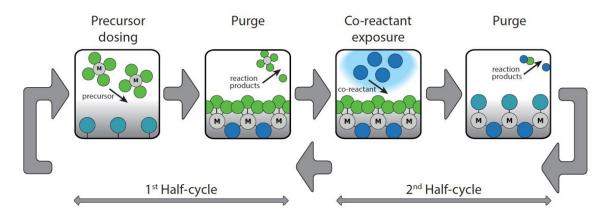

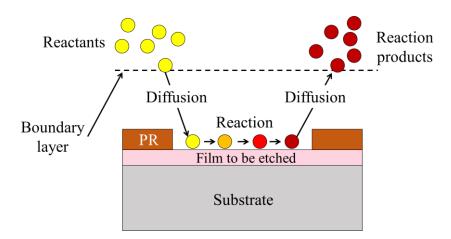

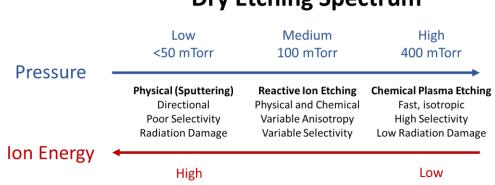

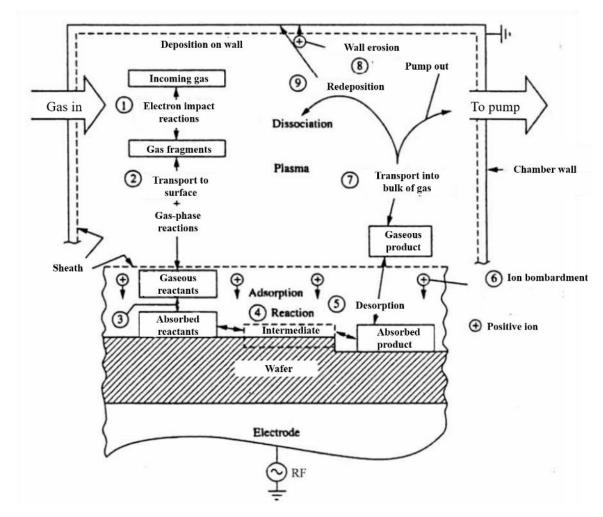

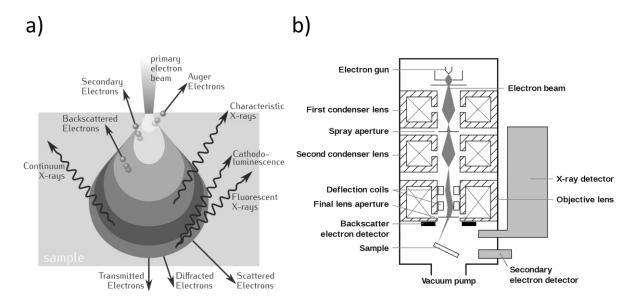

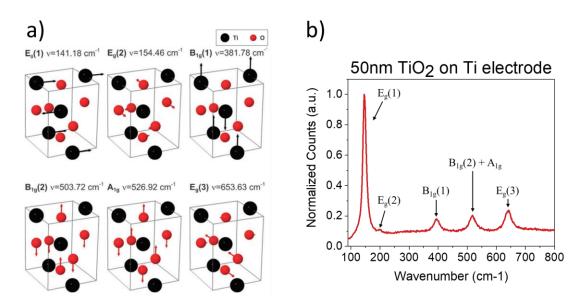

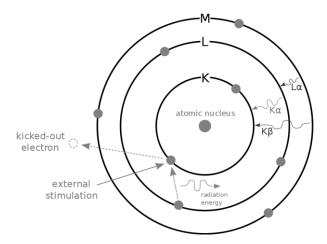

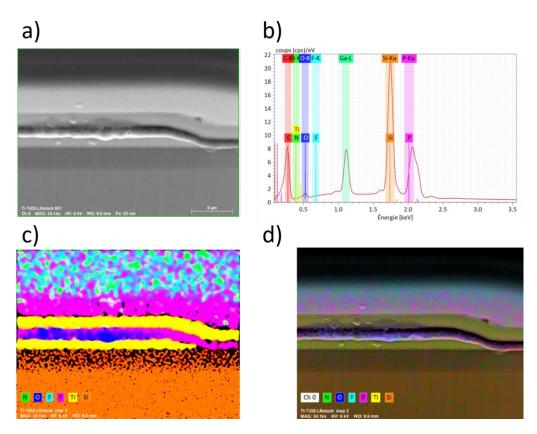

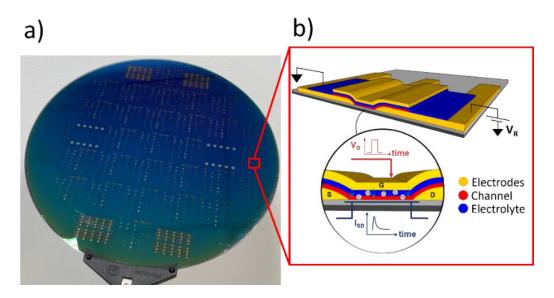

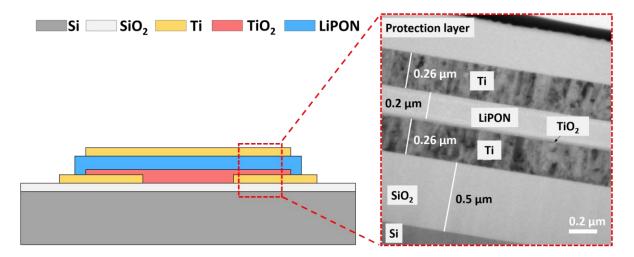

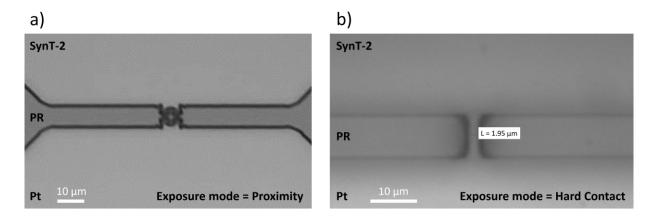

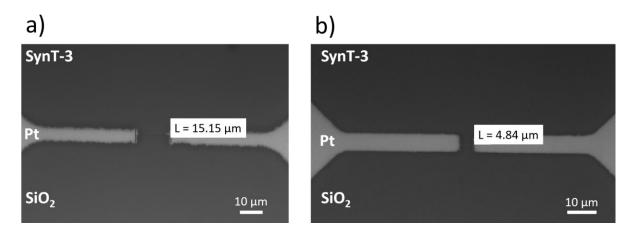

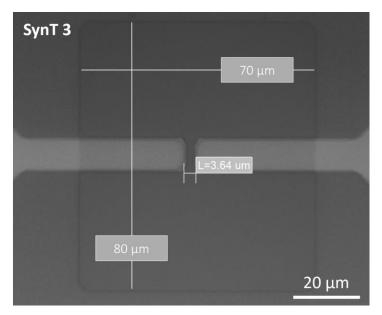

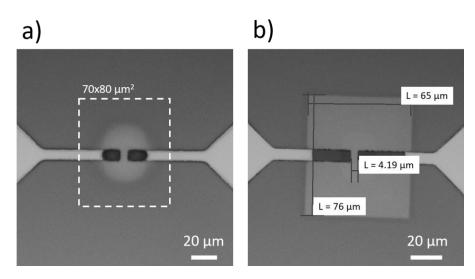

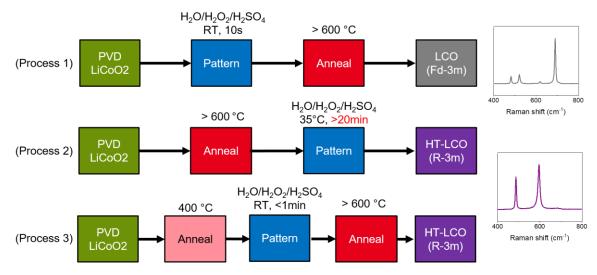

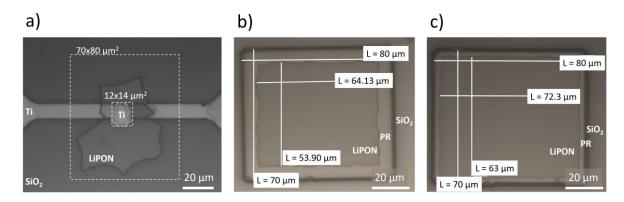

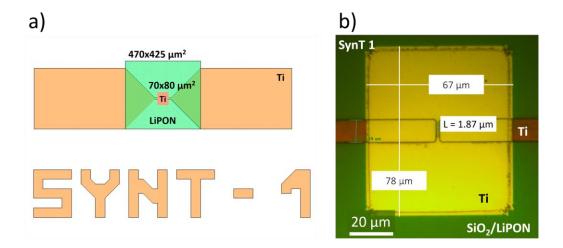

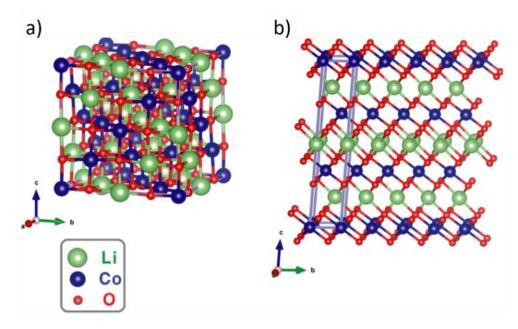

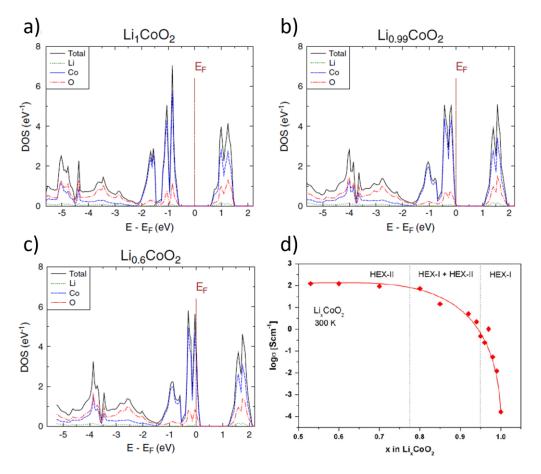

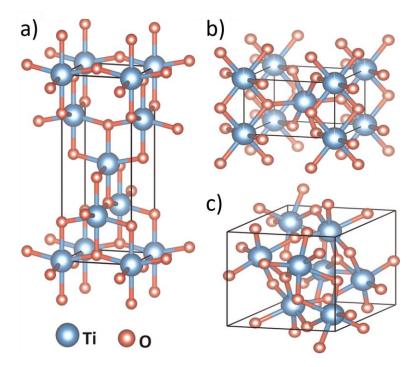

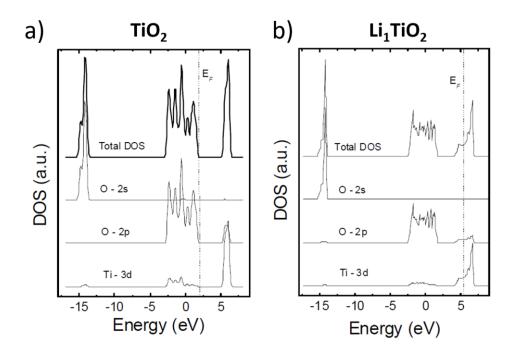

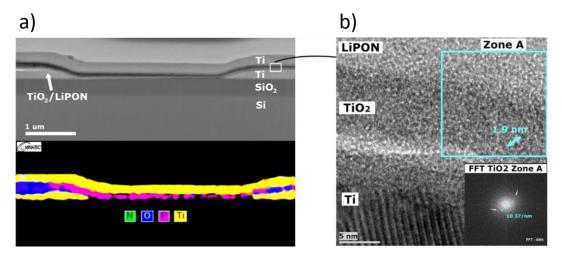

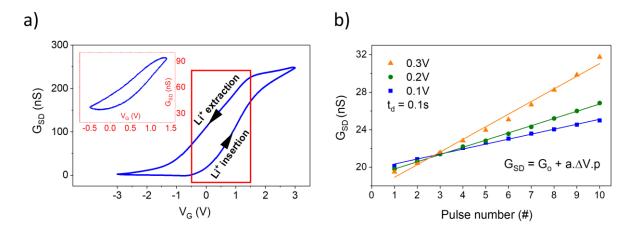

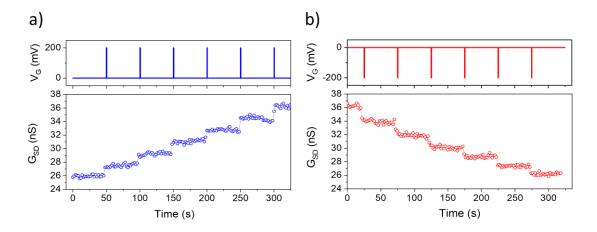

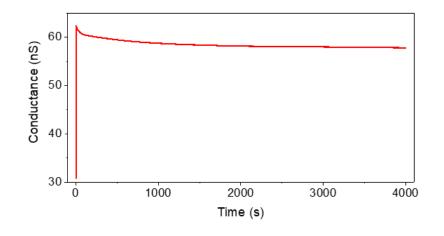

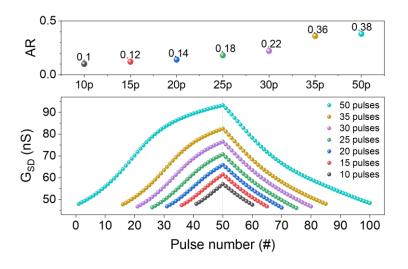

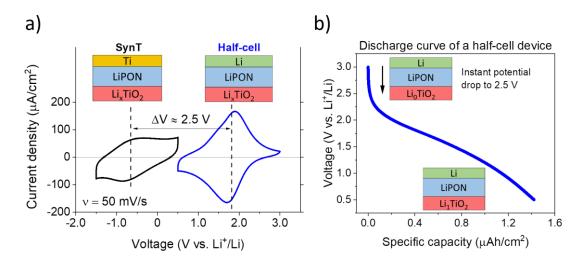

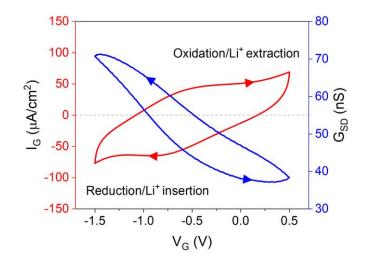

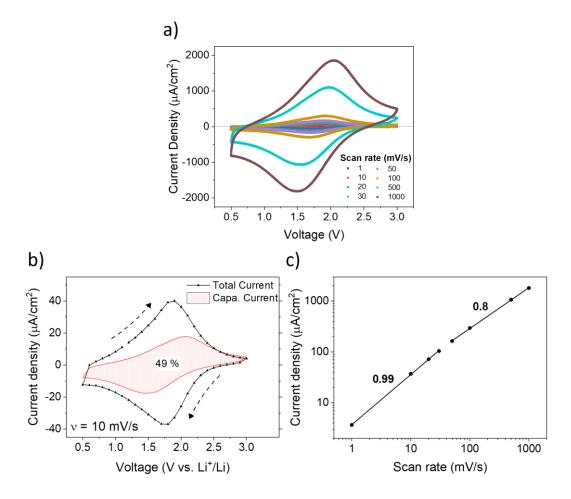

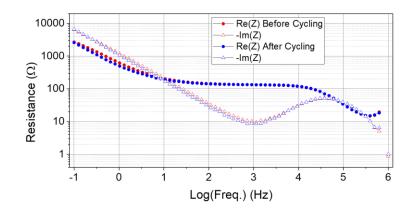

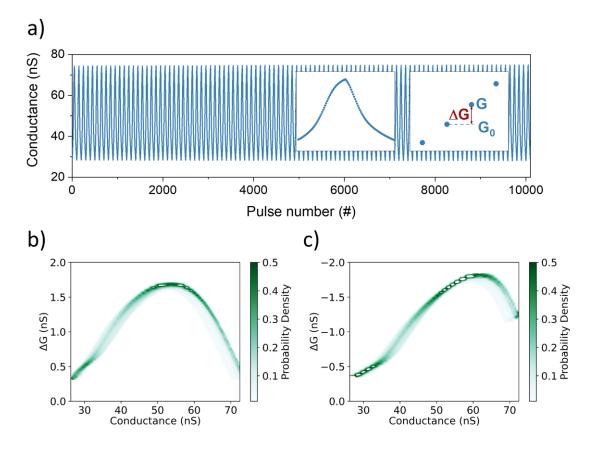

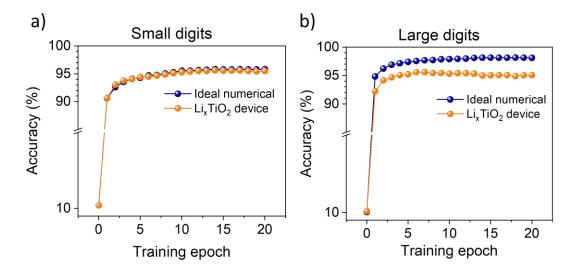

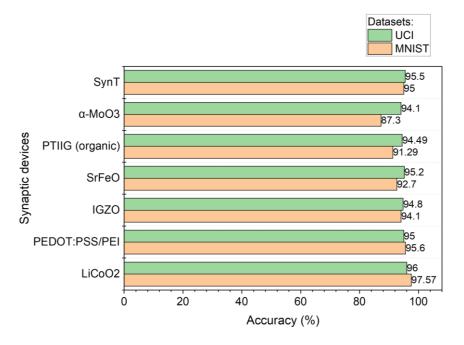

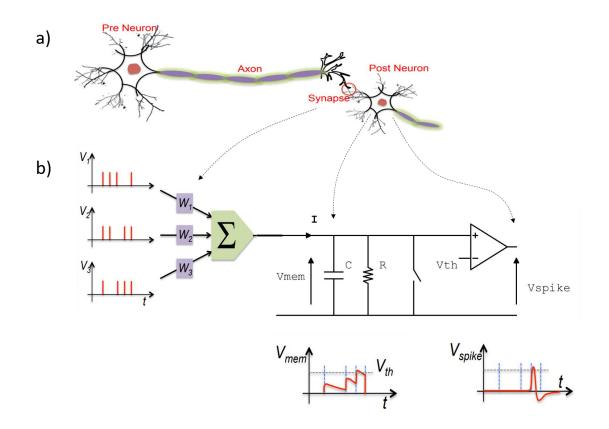

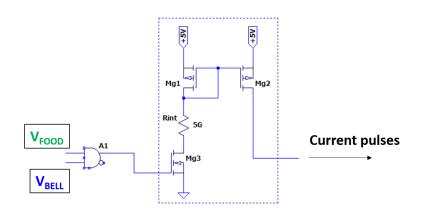

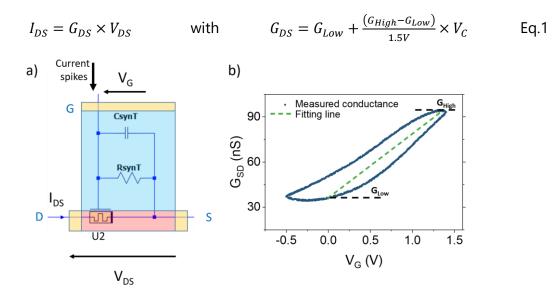

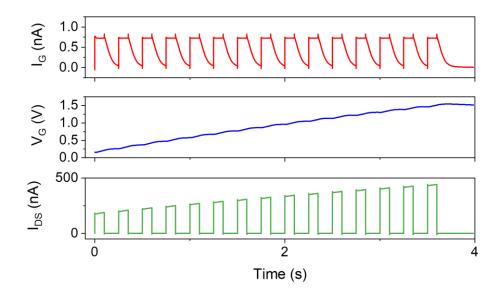

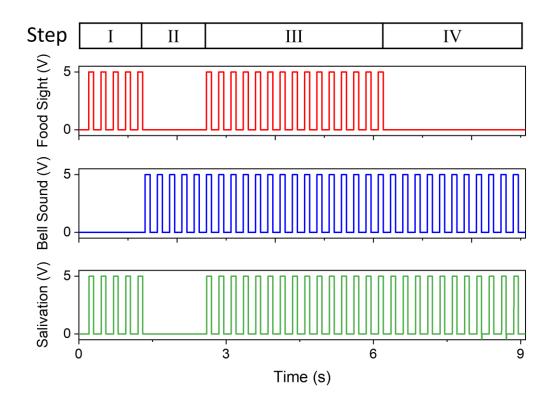

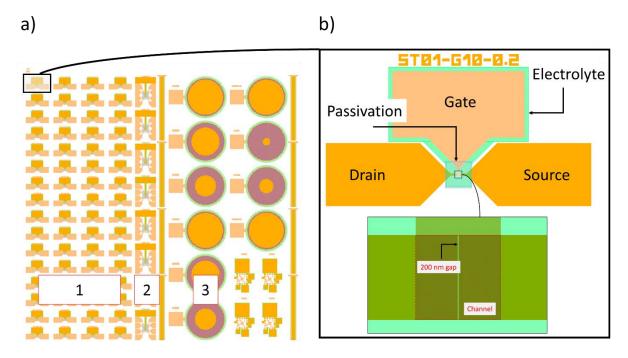

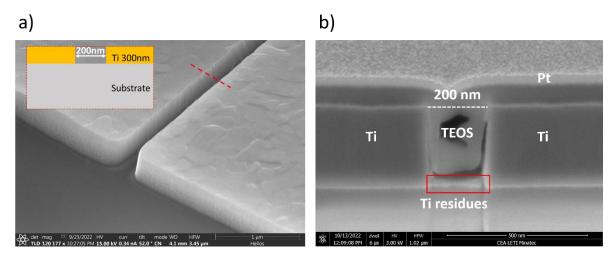

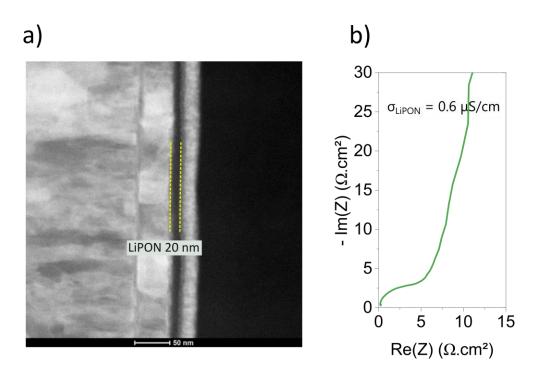

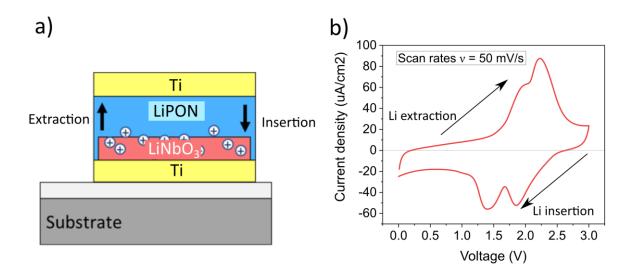

With the help of a reference electrode (REF), monitoring how channel conductance is modified under the intercalation of ions is possible using the voltage sweep method. Li *et al.* show how the anatase phase  $Li_xTiO_2$  channel layer changes its conductance by electrochemically inset and remove Li ions using  $Li_{0.7}FePO_4$  reference (Figure I. 7.d) [49]. The controlled charge and discharge constant current is 1 nA. Here, higher  $V_{REF}$  means that the channel  $Li_xTiO_2$  is more reduced or more Li ions are inserted, and vice versa. The conductance of the anatase  $Li_xTiO_2$  film increases significantly with x in  $Li_xTiO_2$  rising from 0 to 0.2 by enhancing the Ohmic contact between DS electrodes and channel layer, before dropping sharply with x being from 0.2 to 0.6. This drop is associated with an anatase-to-Li-titanate phase transition. As more ions are intercalated into the structure, the re-increase of channel's conductance is observed. The reversed scan shows the same pattern but with a smaller amplitude and a hysteresis, as seen previously in other electrochemical systems. The operating region for this  $Li_xTiO_2$ -based device is between x = 0 and x = 0.65 for linearity reason.