### Experimental and simulation study of GaN device size limitations for high efficiency power converters

Florian Rigaud-Minet

### ▶ To cite this version:

Florian Rigaud-Minet. Experimental and simulation study of GaN device size limitations for high efficiency power converters. Electronics. INSA de Lyon, 2023. English. NNT: 2023ISAL0021. tel-04213673

### HAL Id: tel-04213673 https://theses.hal.science/tel-04213673

Submitted on 21 Sep 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº d'ordre NNT : 2023ISAL0021

### THESE de DOCTORAT DE L'UNIVERSITE DE LYON opérée au sein de

Laboratoire AMPERE et CEA LETI

### **Ecole Doctorale** N° ED160 **Electrotechnique Electronique Automatique**

### **Spécialité/ discipline de doctorat** : Electronique, micro et nanoélectronique, optique et laser

Soutenue publiquement le 20/03/2023, par : Florian RIGAUD-MINET

## Experimental and Simulation Study of GaN Device Size Limitations for High-Efficiency Power Converters

Devant le jury composé de :

MENEGHINI, Matteo, Professeur, Padova University MORANCHO, Frédéric, Professeur, LAAS-CNRS

PLANSON, Dominique, Professeur, Laboratoire AMPERE MOREL, Hervé, Directeur de Recherche, Laboratoire AMPERE BUCKLEY, Julien, Docteur, CEA-LETI

Présidente

Rapporteur Rapporteur

Directeur de thèse Co-encadrant Co-encadrant

### Département FEDORA – INSA Lyon - Ecoles Doctorales

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                                            | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIMIE    | CHIMIE DE LYON<br>https://www.edchimie-lyon.fr<br>Sec. : Renée EL MELHEM<br>Bât. Blaise PASCAL, 3e étage<br>secretariat@edchimie-lyon.fr                                                                                   | M. Stéphane DANIELE<br>C2P2-CPE LYON-UMR 5265<br>Bâtiment F308, BP 2077<br>43 Boulevard du 11 novembre 1918<br>69616 Villeurbanne<br>directeur@edchimie-lyon.fr                                                                                                                                                  |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE,<br>AUTOMATIQUE<br>https://edeea.universite-lyon.fr<br>Sec. : Stéphanie CAUVIN<br>Bâtiment Direction INSA Lyon<br>Tél : 04.72.43.71.70<br>secretariat.edeea@insa-lyon.fr                    | M. Philippe DELACHARTRE<br>INSA LYON<br>Laboratoire CREATIS<br>Bâtiment Blaise Pascal, 7 avenue Jean Capelle<br>69621 Villeurbanne CEDEX<br>Tél : 04.72.43.88.63<br>philippe.delachartre@insa-lyon.fr                                                                                                            |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME,<br>MICROBIOLOGIE, MODÉLISATION<br>http://e2m2.universite-lyon.fr<br>Sec. : Bénédicte LANZA<br>Bât. Atrium, UCB Lyon 1<br>Tél : 04.72.44.83.62<br>secretariat.e2m2@univ-lyon1.fr                     | Mme Sandrine CHARLES<br>Université Claude Bernard Lyon 1<br>UFR Biosciences<br>Bâtiment Mendel<br>43, boulevard du 11 Novembre 1918<br>69622 Villeurbanne CEDEX<br>sandrine.charles@univ-lyon1.fr                                                                                                                |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ<br>http://ediss.universite-lyon.fr<br>Sec. : Bénédicte LANZA<br>Bât. Atrium, UCB Lyon 1<br>Tél : 04.72.44.83.62<br>secretariat.ediss@univ-lyon1.fr                                       | Mme Sylvie RICARD-BLUM<br>Institut de Chimie et Biochimie Moléculaires et Supramoléculaires<br>(ICBMS) - UMR 5246 CNRS - Université Lyon 1<br>Bâtiment Raulin - 2ème étage Nord<br>43 Boulevard du 11 novembre 1918<br>69622 Villeurbanne Cedex<br>Tél : +33(0)4 72 44 82 32<br>sylvie.ricard-blum@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES<br>http://edinfomaths.universite-lyon.fr<br>Sec. : Renée EL MELHEM<br>Bât. Blaise PASCAL, 3e étage<br>Tél : 04.72.43.80.46<br>infomaths@univ-lyon1.fr                                        | M. Hamamache KHEDDOUCI<br>Université Claude Bernard Lyon 1<br>Bât. Nautibus<br>43, Boulevard du 11 novembre 1918<br>69 622 Villeurbanne Cedex France<br>Tél : 04.72.44.83.69<br>hamamache.kheddouci@univ-lyon1.fr                                                                                                |

| Matériaux | MATÉRIAUX DE LYON<br>http://ed34.universite-lyon.fr<br>Sec. : Yann DE ORDENANA<br>Tél : 04.72.18.62.44<br>yann.de-ordenana@ec-lyon.fr                                                                                      | M. Stéphane BENAYOUN<br>Ecole Centrale de Lyon<br>Laboratoire LTDS<br>36 avenue Guy de Collongue<br>69134 Ecully CEDEX<br>Tél : 04.72.18.64.37<br>stephane.benayoun@ec-lyon.fr                                                                                                                                   |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE,<br>GÉNIE CIVIL, ACOUSTIQUE<br>http://edmega.universite-lyon.fr<br>Sec. : Stéphanie CAUVIN<br>Tél : 04.72.43.71.70<br>Bâtiment Direction INSA Lyon<br>mega@insa-lyon.fr                             | M. Jocelyn BONJOUR<br>INSA Lyon<br>Laboratoire CETHIL<br>Bâtiment Sadi-Carnot<br>9, rue de la Physique<br>69621 Villeurbanne CEDEX<br>jocelyn.bonjour@insa-lyon.fr                                                                                                                                               |

| ScSo      | ScSo*<br>https://edsciencessociales.universite-lyon.fr<br>Sec. : Mélina FAVETON<br>INSA : J.Y. TOUSSAINT<br>Tél : 04.78.69.77.79<br>melina.faveton@univ-lyon2.fr<br>Géographie, Aménagement, Urbanisme, Archéologie, Scier | M. Christian MONTES<br>Université Lumière Lyon 2<br>86 Rue Pasteur<br>69365 Lyon CEDEX 07<br>christian.montes@univ-lyon2.fr                                                                                                                                                                                      |

Cette thèse est accessible à l'adresse : https://theses.insa-lyon.fr/publication/2023ISAL0021/these.pdf © [F. Rigaud-Minet], [2023], INSA Lyon, tous droits réservés

| DEPARTEMENT FEDORA         |  |  |  |

|----------------------------|--|--|--|

| FORMATION PAR LA RECHERCHE |  |  |  |

| ET ÉTUDES DOCTORALES       |  |  |  |

| Bâtiment INSA direction    |  |  |  |

Année universitaire 2019-2020

#### ECOLES DOCTORALES – DISCIPLINES A REMPLIR LORS DE VOTRE INSCRIPTION

| Doctorant :<br>Nom : <u>RIGAUD-MINET</u> | Prénom : FLORTAN   | <u>Signature :</u> | erfaile   |

|------------------------------------------|--------------------|--------------------|-----------|

| Directeur de thèse :<br>Nom :            | Prénom : Doninique | <u>Signature :</u> | D. Paulon |

#### UNE SEULE DISCIPLINE POSSIBLE, à choisir parmi la liste suivante :

| ECOLES DOCTORALES<br>n° code national                                                                                                    | DISCIPLINES                                                                                                                                                                                                                                                          | Cocher la case<br>correspondante |

|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ED CHIMIE DE LYON                                                                                                                        | Chimie                                                                                                                                                                                                                                                               |                                  |

| (Chimie, Procédés, Environnement)                                                                                                        | Procédés                                                                                                                                                                                                                                                             |                                  |

| EDA206                                                                                                                                   | Environnement                                                                                                                                                                                                                                                        |                                  |

| HISTOIRE, GEOGRAPHIE, AMENAGEMENT, URBANISME,<br>ARCHEOLOGIE, SCIENCE POLITIQUE, SOCIOLOGIE,<br><u>ANTHROPOLOGIE</u><br>(ScSo)<br>EDA483 | Géographie – Aménagement - Urbanisme                                                                                                                                                                                                                                 |                                  |

| ELECTRONIQUE, ELECTROTECHNIQUE, AUTOMATIQUE                                                                                              | Automatique                                                                                                                                                                                                                                                          |                                  |

|                                                                                                                                          | Génie Electrique                                                                                                                                                                                                                                                     |                                  |

| (E.E.A.)                                                                                                                                 | Electronique, micro et nanoélectronique, optique et laser                                                                                                                                                                                                            | ×                                |

| EDA160                                                                                                                                   | Ingénieric pour le vivant                                                                                                                                                                                                                                            |                                  |

|                                                                                                                                          | Traitement du Signal et de l'Image                                                                                                                                                                                                                                   |                                  |

| EVOLUTION, ECOSYSTEMES, MICROBIOLOGIE,<br>MODELISATION<br>(E2M2)<br>EDA 341                                                              | Paléoenvironnements et évolution<br>Micro-organismes, interactions, infections<br>Biologie Evolutive, Biologie des Populations, écophysiologie<br>Biomath-Bioinfo-Génomique évolutive<br>Ecologie des communautés, fonctionnement des écosystèmes,<br>écotoxicologie |                                  |

| INFORMATIQUE ET MATHEMATIQUES DE LYON<br>(InfoMaths)<br>EDA 512                                                                          | Informatique<br>Informatique et applications<br>Mathématiques et applications<br>Génie Industriel                                                                                                                                                                    |                                  |

| INTERDISCIPLINAIRE SCIENCES-SANTE                                                                                                        | Biochimie<br>Physiologie                                                                                                                                                                                                                                             |                                  |

| (EDISS)<br>EDA205                                                                                                                        | Ingénierie biomédicale                                                                                                                                                                                                                                               |                                  |

| ED MATERIAUX DE LYON                                                                                                                     |                                                                                                                                                                                                                                                                      |                                  |

| EDA 034                                                                                                                                  | Matériaux                                                                                                                                                                                                                                                            | 0                                |

| <u>MEGA DE LYON</u><br>(MECANIQUE, ENERGETIQUE, GENIE CIVIL, ACOUSTIQUE)                                                                 | Mécanique des Fluides<br>Génie Mécanique                                                                                                                                                                                                                             | <br>,                            |

|                                                                                                                                          | Biomécanique                                                                                                                                                                                                                                                         |                                  |

| (MEGA)                                                                                                                                   | Thermique Energétique                                                                                                                                                                                                                                                |                                  |

| EDA162                                                                                                                                   | Génie Civil<br>Acoustique                                                                                                                                                                                                                                            |                                  |

Département de la Formation par la Recherche et des Études Doctorales (**FEDORA**)

Bâtiment INSA direction, 1<sup>er</sup> étage 37, av. J. Capelle 69621 Villeurbanne Cédex <u>fedora@insa-lyon.fr</u>

Référence : TH0957\_RIGAUD-MINET

L'INSA Lyon a mis en place une procédure de contrôle systématique via un outil de détection de similitudes (logiciel Compilatio). Après le dépôt du manuscrit de thèse, celui-ci est analysé par l'outil. Pour tout taux de similarité supérieur à 10%, le manuscrit est vérifié par l'équipe de FEDORA. Il s'agit notamment d'exclure les auto-citations, à condition qu'elles soient correctement référencées avec citation expresse dans le manuscrit.

Par ce document, il est attesté que ce manuscrit, dans la forme communiquée par la personne doctorante à l'INSA Lyon, satisfait aux exigences de l'Etablissement concernant le taux maximal de similitude admissible.

INSA LYON

**Campus LyonTech La Doua** 20, avenue Albert Einstein - 69621 Villeurbanne cedex - France Tél. +33 (0)4 72 43 83 83 - Fax +33 (0)4 72 43 85 00

Cette thèse est accessible à l'adresse : https://theses.insa-lyon.fr/publication/2023ISAL0021/these.pdf © [F. Rigaud-Minet], [2023], INSA Lyon, tous droits réservés

« Crystals are like people: it is the defects in them which tend to make them interesting » Sir Colin Humphreys

# Acknowledgments

These three years of PhD were the opportunity to learn various and interesting things. I wish to express my sincere gratitude to the people who help me going through this experience built at CEA LETI and at Ampere Laboratory.

• Firstly, I would like to express my deepest gratitude to my three supervisors for this unique opportunity as well as mentoring me over these three years:

I would like to sincerely thank <u>Dr. Julien Buckley</u> (CEA LETI) for his constant support, his careful advice and for the fruitful discussions we had as well as and his guidance for the development of this scientific work. Also for having trust in me for the realization of this thesis.

I would like to sincerely thank <u>Prof. Dominique Planson & Dr. Hervé Morel</u> (Ampere Laboratory), for their strong support, their precious advice and for sharing their huge scientific experience.

- Secondly, I would like to thank Prof. Frédéric Morancho (LAAS-CNRS) and Prof. Matteo Meneghini (Padova university) for taking seriously the heavy task of being rapporteurs. Prof. Nathalie Labat (IMS-Bordeaux), to be part of the PhD committee. Thank you for your precious time and consideration.

- Thirdly, I would like to specially thank the people who technically contributed to the realization of this thesis and without whom this thesis wouldn't had the same flavor:

- Dr. René Escoffier (CEA LETI) for the multiple advice for the packaging, dicing step and device modeling,

- Pascal Bevilacqua (Ampere Laboratory) for the realization of electronic boards as well as the Human-machine interface used in the electric bench developed in this PhD,

- Dr. Christophe Raynaud (Ampere Laboratory) for running and helping me analyzing DLTFS measurements,

- Denis Blachier (CEA LETI) for performing the Lock-in Thermography observations,

- David Bouchu & Dr. Stephane Moreau (CEA LETI) for performing the FIB-SEM observations and for the failure analysis discussions,

- Pierre Francois (CEA LETI) for performing the SIMS measurements,

- Thierry Flahaut & Nadine David (CEA LETI) for wafer dicing,

- Jean-Paul Caillaba & Sarah Soulie (SynergieCAD) for the transistor packaging,

- Loris Pace & Matthieu Beley (Ampere Laboratory) for their guidance in the use of VNA,

- Emmanuel Marcault & Mathieu Gavelle (CEA Tech Occitanie) for providing the excellent DFN socket used in the electrical bench.

I want to kindly thank the power, characterization, process (epitaxy, etching ...) and simulation CEA laboratories and Ampere Laboratory teams for their contributions to this thesis and for the memorable moments during coffee breaks and after-works. Finally, I would like to thank my family, my friends and my girlfriend for supporting me during these demanding years.

I wish you all the best!!!

vi

# Outline

| Acknowledgments                                                                                  | vi        |

|--------------------------------------------------------------------------------------------------|-----------|

| Outline                                                                                          | vi        |

| Acronyms                                                                                         | xiv       |

| General Introduction                                                                             | 1         |

| Context                                                                                          | 1         |

| Objectives and Thesis Organization                                                               | 3         |

| Chapter I AlGaN/GaN-on-Silicon Devices for Power Electronics, State-<br>and Scaling Perspectives |           |

| I.1 Gallium Nitride: From the Raw Material to its Applications                                   | 8         |

| I.1.a Gallium Nitride: A Wide Band Gap Material                                                  | 8         |

| I.1.a.i Wide Band Gap Semiconductors                                                             | 8         |

| I.1.a.ii The Crystalline Properties of Gallium Nitride                                           | 11        |

| I.1.a.iii The Polarization Properties of Gallium Nitride                                         | 14        |

| I.1.b Gallium Nitride: A Material Used to Make Power Devices                                     | 19        |

| I.1.b.i Power Devices with GaN                                                                   | 19        |

| I.1.b.ii The Specificity of Lateral AlGaN/GaN-on-Si Power Devices                                | 26        |

| I.1.c Gallium Nitride: From the Power Device Performances to its Application                     | 1s30      |

| I.1.c.i Transistor Hard and Soft Switching                                                       |           |

| I.1.c.ii A Wide Range of Applications for GaN transistors                                        |           |

| I.1.d Summary                                                                                    |           |

| I.2 Device Architecture to Improve the Breakdown Voltage and Method to                           | Study the |

| Electric Field                                                                                   | 37        |

| I.2.a Device Architecture Improvements for High Breakdown Voltage                                | 37        |

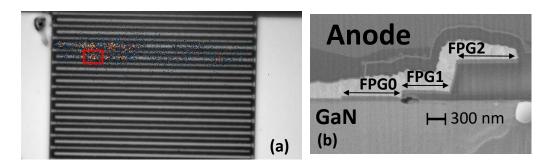

| I.2.a.i The Field Plates                                                                         |           |

| I.2.a.ii The Low Conductive Layer                                                                | 40        |

| I.2.a.iii The Polarization Super Junction                                                        | 41        |

| I.2.a.iv The Epitaxial Layers Engineering                                                        | 42        |

| I.2.a.v The Substrate Removal                                                                    | 43        |

| I.2.b Method to Probe the Electric Field                                                         | 44        |

|                                                                                                  |           |

| I.3 State-of-the-Art of the Switching Loss Measurement Techniques                                                       |

|-------------------------------------------------------------------------------------------------------------------------|

| I.3.a Different Switching Loss Origins45                                                                                |

| I.3.b Different Setups for Loss Extraction                                                                              |

| I.3.b.i Double Pulse Test (DPT)46<br>I.3.b.ii Calorimetric Measurement Test47                                           |

| I.3.b.iii Opposition Test Method                                                                                        |

| I.3.b.iv Indirect Measurement Method                                                                                    |

| I.3.b.v Analytical Model                                                                                                |

| I.3.b.vi Summary                                                                                                        |

| I.3.c Different Loss Extraction                                                                                         |

| Conclusion                                                                                                              |

| Chapter II Experimental Study of the High Voltage Limitations of AlGaN/GaN-on-Si Schottky Barrier Diode                 |

| II.1 Breakdown Analysis in AlGaN/GaN Devices for Power Electronics                                                      |

| II.1.a Literature Review: AlGaN/GaN Power Devices Lateral Breakdown Analysis57                                          |

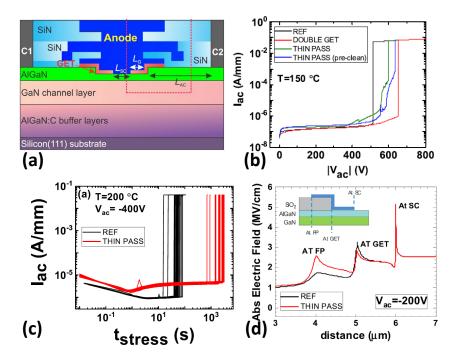

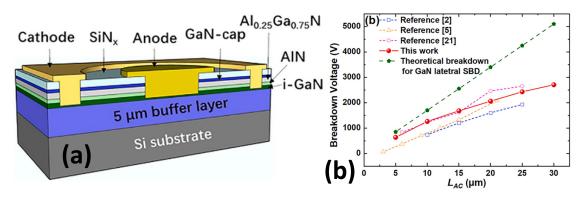

| II.1.a.i AlGaN/GaN Schottky Diodes Lateral Breakdown Analysis                                                           |

| II.1.a.ii Complementary Techniques and Studies in Breakdown Analysis of AlGaN/GaN<br>High Electron Mobility Transistors |

| II.1.a.iii Summary67                                                                                                    |

| II.1.b Literature Review: Vertical Breakdown Mechanisms                                                                 |

| II.1.b.i Literature Hypothesis                                                                                          |

| II.1.b.ii Main Identified Dependence71                                                                                  |

| II.2 The Identification of the Two Breakdown Modes by the Substrate Connection                                          |

| Dependence on the Breakdown Voltage                                                                                     |

| II.2.a Experimental Protocol                                                                                            |

| II.2.a.i Samples Description                                                                                            |

| II.2.a.ii Electrical Characterization Procedure                                                                         |

| II.2.b Experimental Results                                                                                             |

| II.2.b.i Diodes Leakage Trends and Contributions                                                                        |

| II.2.b.ii Breakdown Voltage Extraction in the Different Configurations as a Function of the Anode-to-Cathode Distance   |

| II.3 Device Limitations with a Floating Substrate                                                                       |

vii

| II.3.a Me     | ethod Description and Experimental Presentation                         | 81      |

|---------------|-------------------------------------------------------------------------|---------|

| II.3.a.i      | Method Description                                                      | 81      |

| II.3.a.ii     | Experimental Presentation                                               | 82      |

| II.3.b Exp    | perimental Results                                                      | 86      |

| II.3.b.i      | Long Anode-to-Cathode Distance Devices                                  | 86      |

| II.3.b.ii     | Short Anode-to-Cathode Distance Devices                                 | 89      |

| II.3.b.iii    | Summary                                                                 | 94      |

| II.4 Device   | E Limitations with Grounded Substrate                                   | 96      |

| II.4.a Me     | thod Description                                                        | 96      |

| II.4.b Exp    | perimental Results                                                      | 97      |

| II.4.b.i      | General Trends                                                          | 97      |

| II.4.b.ii     | Failure Analysis for Every Identified Categories                        |         |

| II.4.b.iii    | Summary                                                                 | 103     |

| Conclusion    |                                                                         | 104     |

|               | proving the AlGaN/GaN Schottky Diode TCAD Modeling Bas<br>Measurements  |         |

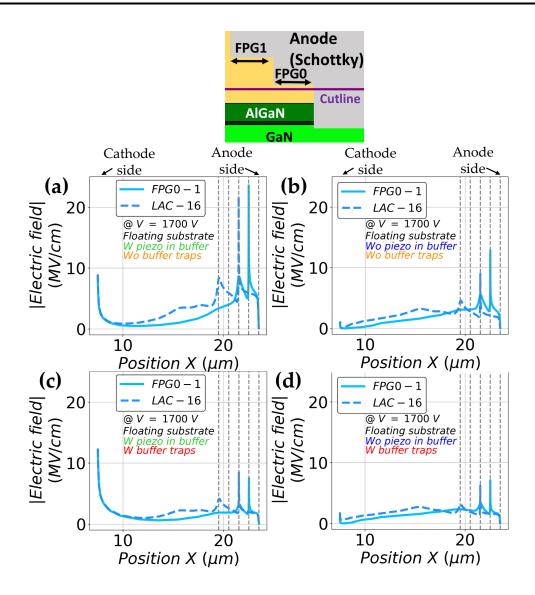

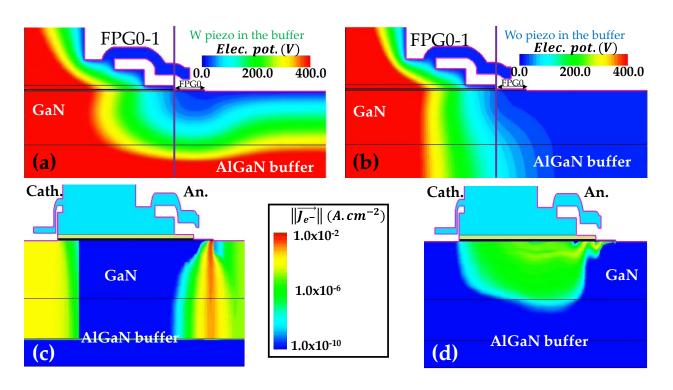

| III.1 State-o | of-the-Art Approach Limits and Proposed Method Description              | 108     |

| III.1.a Lin   | nit of the Approach Present in the Literature to Simulate the Electric  | c Field |

| Distribution  | n in AlGaN/GaN Lateral Power Devices                                    | 108     |

| III.1.a.i     | Two-Dimensional Analytical Model                                        | 108     |

| III.1.a.ii    | Technology Computer Aided Design (TCAD)                                 | 109     |

| III.1.b Pro   | posed Method to Probe the Different Contribution of Buffer Traps on the | Device  |

| Characterist  | tics                                                                    | 112     |

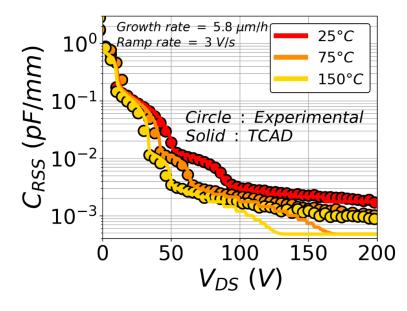

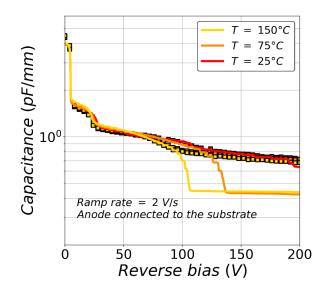

| III.2 Modeli  | ing of the Capacitive 2DEG Depletion Control                            | 117     |

| III.2.a Buf   | ffer Layers Affecting the Capacitance Dependence at First Order         | 117     |

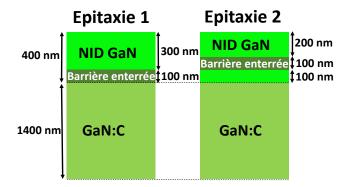

| III.2.a.i     | Sample and Method Presentation                                          | 117     |

| III.2.a.ii    | Impact of the Substrate Presence                                        | 120     |

| III.2.a.iii   | Impact of the Piezoelectric Model Activation in the Buffer Layers       | 120     |

| III.2.a.iv    | Impact of the Back Barrier Presence                                     |         |

| III.2.a.v     | Discrepancy between the Electric field Distribution and the Experi-     | imental |

|               | vn Measurements                                                         |         |

| III.2.b Buf   | ffer Traps Impact on the Capacitive Temperature Dependence              |         |

|               |                                                                         | viii    |

| Diode and E               | Sample Presentation and Preliminary Study       125         Experimental Study       128         TCAD Qualitative Simulation Study of Buffer Traps       130         TCAD Fit on the Experimental Data and the Possible Interpretations       136         VGa-(ON)x Hypothesis Verification       138         Dementation of Deep Acceptor Traps in the Simulated AlGaN/GaN Schottky       141 |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 145                       | Charge Movement Modeling Through Vertical Current Temperature Dependence                                                                                                                                                                                                                                                                                                                       |

|                           | rent Status on the Vertical Current Knowledge and the Different Reported<br>fechanisms                                                                                                                                                                                                                                                                                                         |

| 1                         |                                                                                                                                                                                                                                                                                                                                                                                                |

| III.3.a.i                 | Current Status on the Vertical Current Knowledge                                                                                                                                                                                                                                                                                                                                               |

| III.3.a.ii                | Ohmic Conduction                                                                                                                                                                                                                                                                                                                                                                               |

| III.3.a.iii<br>III.3.a.iv | Recombination Limited Transport                                                                                                                                                                                                                                                                                                                                                                |

| III.3.a.iv<br>III.3.a.v   | Space Charge Limited Current149Hopping Versus Poole Frenkel Mechanisms150                                                                                                                                                                                                                                                                                                                      |

| III.3.a.v<br>III.3.a.vi   | Summary of the Bulk Transport Mechanisms                                                                                                                                                                                                                                                                                                                                                       |

|                           | berimental Analysis and Interpretation of the Vertical Current Temperature                                                                                                                                                                                                                                                                                                                     |

| _                         |                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                         |                                                                                                                                                                                                                                                                                                                                                                                                |

| III.3.b.i<br>III.3.b.ii   | Preliminary Experimental Studies                                                                                                                                                                                                                                                                                                                                                               |

| III.3.b.iii               | Fitting Parameter Interpretation                                                                                                                                                                                                                                                                                                                                                               |

| III.3.b.iv                | Summary                                                                                                                                                                                                                                                                                                                                                                                        |

|                           | AD Simulation and Modeling Study to Reproduce the Experimental Trend 163                                                                                                                                                                                                                                                                                                                       |

| III.3.c.i                 | Simulated Structure Presentation                                                                                                                                                                                                                                                                                                                                                               |

| III.3.c.ii                | Simulation Results                                                                                                                                                                                                                                                                                                                                                                             |

| III.3.c.iii               | Discussion                                                                                                                                                                                                                                                                                                                                                                                     |

| III.3.d Sur               | nmary                                                                                                                                                                                                                                                                                                                                                                                          |

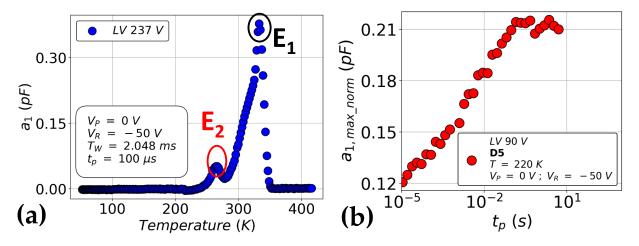

| III.4 Capacit             | tance Deep Level Transient Fourier Spectroscopy (C-DLTFS) of Schottky                                                                                                                                                                                                                                                                                                                          |

| AlGaN/GaN-o               | n-Si Schottky Diode170                                                                                                                                                                                                                                                                                                                                                                         |

| III.4.a San               | nples and Characterization Setup Presentation170                                                                                                                                                                                                                                                                                                                                               |

| III.4.b Exp               | perimental Results172                                                                                                                                                                                                                                                                                                                                                                          |

ix

| III.4.b.i Arrhenius Plot                                                                                            | 172             |

|---------------------------------------------------------------------------------------------------------------------|-----------------|

| III.4.b.ii Filling Pulse Width Dependence                                                                           |                 |

| III.4.c Discussion on the Possible Trap Origins                                                                     | 175             |

| Conclusion                                                                                                          | 179             |

| Chapter IV Evaluation of AlGaN/GaN Fully-Recessed MOS-HEMT Losses                                                   |                 |

| IV.1 State-of-the-Art of E-mode Transistor Switching Losses                                                         |                 |

| IV.1.a Simulation Approach                                                                                          |                 |

| IV.1.b Experimental Approach                                                                                        |                 |

| IV.1.b.i Analytical Design Rules of Hard Switching Losses (versus Te<br>State Blocking Voltage or ON-State Current) |                 |

| IV.1.b.ii Blocking Time Impact before Switching Event                                                               |                 |

| IV.1.b.iii External Gate Resistance Impact                                                                          |                 |

| IV.1.b.iv On-state Gate Driving Voltage Impact                                                                      |                 |

| IV.1.b.v Comparison between Power Transistor Technologies                                                           |                 |

| IV.1.c Mixed Approach                                                                                               |                 |

| IV.1.d Summary                                                                                                      | 190             |

| IV.2 Experimental and Simulation Study of Hard Switching Performance                                                | of E-mode Power |

| Transistors                                                                                                         | 191             |

| IV.2.a Methodology and Experimental/Simulation Tools Description                                                    | 191             |

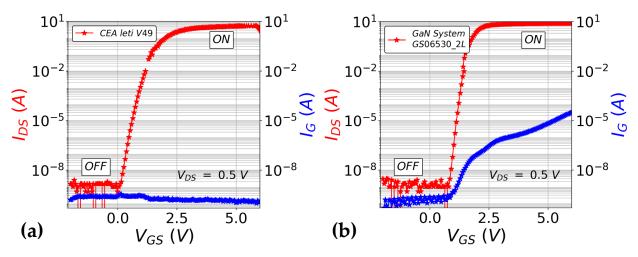

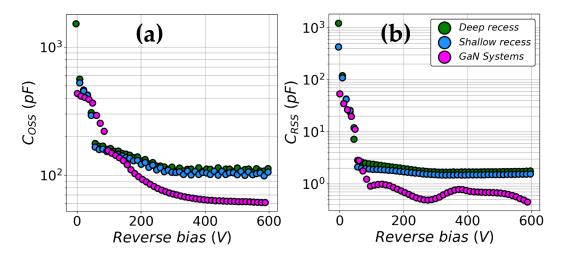

| IV.2.a.i Sample Description                                                                                         | 191             |

| IV.2.a.ii Methodology Description                                                                                   |                 |

| IV.2.a.iii Experimental Circuit Description                                                                         | 194             |

| IV.2.a.iv LTSpice Simulation Presentation                                                                           |                 |

| IV.2.b Results                                                                                                      |                 |

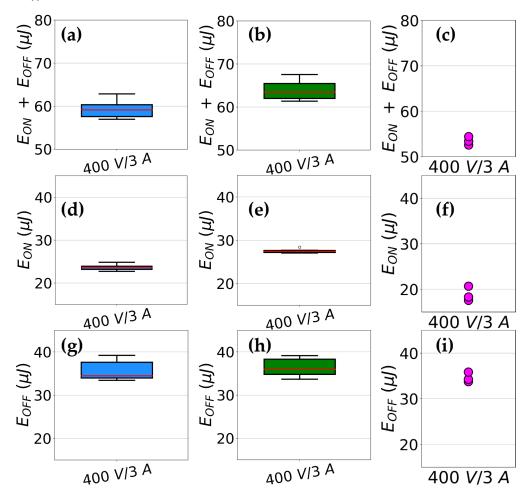

| IV.2.b.i Impact of the Recess Depth on E-Mode 650 V/30 A MOS-H<br>Hard-Switching Losses                             |                 |

| IV.2.b.ii E-mode 650 V/1 A Transistor Switching Loss Analysis                                                       |                 |

| Conclusion                                                                                                          |                 |

| General Conclusion                                                                                                  |                 |

| Summary, Results and Scientific Contributions                                                                       |                 |

| Limitations of the presented studies and perspectives                                                               |                 |

| I                                                                                                                   | X               |

|         | A : Time Dependent Dielectric Breakdown: From the Physical Origin to the l Analysis                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Physics of Time Dependent Dielectric Breakdowns I                                                                                                                         |

| A.2     | Weibull Statistics to Study the Time Dependent Dielectric BreakdownII                                                                                                     |

|         | B : Electrical and Physical Failure Analysis TechniquesIV<br>Lock-in Thermography (LiT) [249], [445]IV                                                                    |

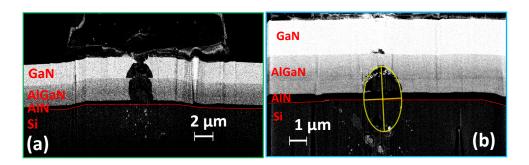

| B.2     | Focused Ion Beam Scanning Electron Microscopy (FIB-SEM) VII                                                                                                               |

| Tempera | C : Perimeter Versus Surface Contribution in the Vertical Leakage<br>ture Dependence Through an AlGaN-on-Si EpitaxyIX<br>Normalisation Trials Varying Contact DiametersIX |

| C.2     | Verification that the Perimeter Contribution in the Ohmic Regime Follows the Same                                                                                         |

| Temper  | ature Dependence than the Analytical FitX                                                                                                                                 |

| C.2.a   | Method DescriptionXI                                                                                                                                                      |

| C.2.b   | Results                                                                                                                                                                   |

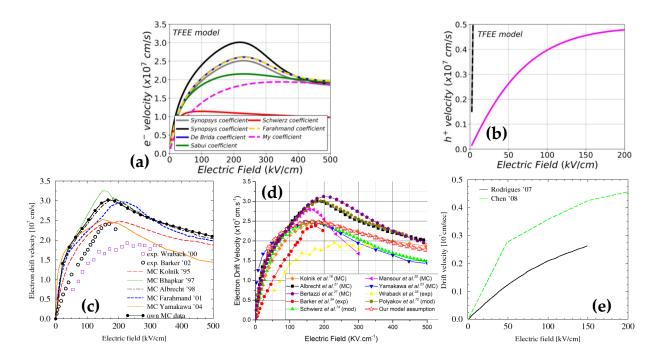

| Through | D : Mobility Model in the Bulk Material for the Study of the Vertical Current<br>the Epitaxy                                                                              |

| D.1.a   |                                                                                                                                                                           |

| D.1.b   |                                                                                                                                                                           |

| D.1.c   | High-Electric Field Dependent ModelXV                                                                                                                                     |

| D.2     | Model Choice and Parameters' DeterminationXVI                                                                                                                             |

| D.2.a   | Model Chosen for GaN bulkXVI                                                                                                                                              |

| D.2.b   | Model for the Other MaterialsXX                                                                                                                                           |

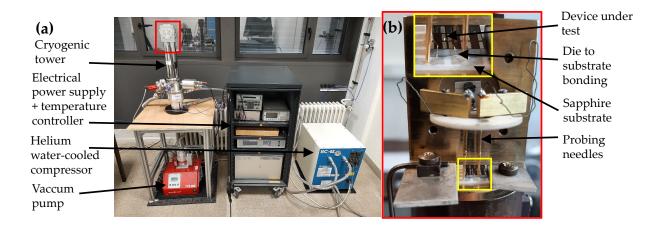

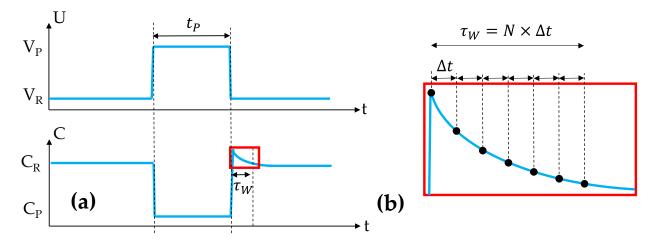

|         | E : Deep Level Transient Fourier Spectroscopy (DLTFS)XXI<br>Experimental SetupXXI                                                                                         |

| E.2     | Different Electrical MeasurementsXXIII                                                                                                                                    |

| E.2.a   | Temperature Scans/ Filling Pulse ScansXXIII                                                                                                                               |

| E.2.b   | Arrhenius PlotXXIV                                                                                                                                                        |

xi

|            | : Double Source Test Complementary Information                      |               |

|------------|---------------------------------------------------------------------|---------------|

| F.1 Ele    | ectrical Circuit                                                    | XXVII         |

| F.1.a      | Circuit Presentation and Elements                                   | XXVII         |

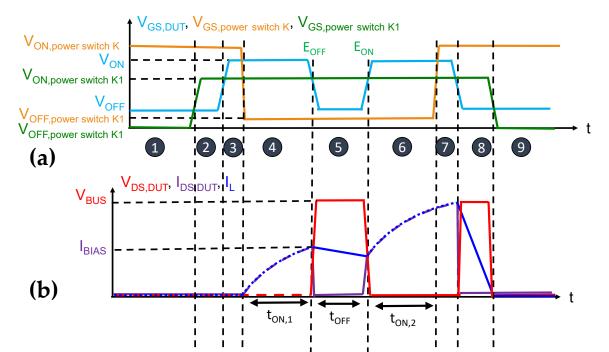

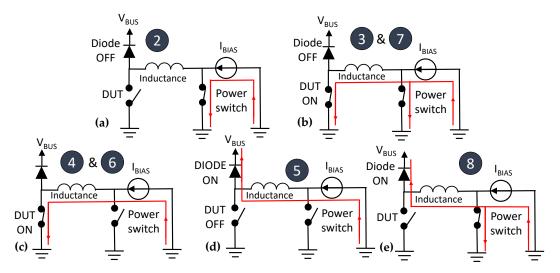

| F.1.b      | Circuit Functioning and Typical Waveforms                           | XXIX          |

| F.1.c      | The Probes Choice Justification                                     | XXXI          |

| F.2 Cir    | rcuit modeling for LTSpice Simulations                              | XXXIII        |

| F.2.a      | Electrical Model                                                    | XXXIII        |

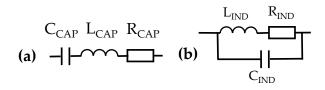

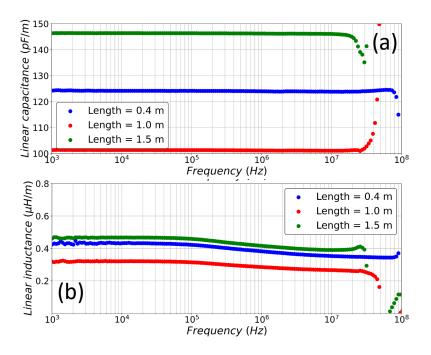

| F.2.a      | .1st Non-Ideal Inductance and Capacitors                            | XXXIII        |

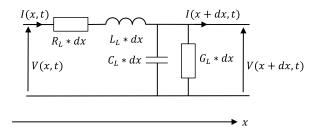

| F.2.a      | .2nd Lossy Transmission Line                                        | XXXIV         |

| F.2.b      | Model Fitting                                                       | XXXVII        |

| F.3 Pro    | obes' Propagation Time Compensation                                 | XL            |

| F.3.a      | Current Probe                                                       | XL            |

| F.3.b      | Voltage Probes                                                      | XLI           |

| F.4 Te     | chnology Comparison with GaN Systems p-GaN gate                     | XLI           |

| Annexe G   | : Transistor LTSpice Model                                          | XLIV          |

| G.1 Ele    | ectrical Model                                                      | XLIV          |

| G.1.a      | Model Presentation                                                  | XLIV          |

| G.1.b      | Model Parameter Differences Between the Model Calibrated for Dee    | p and Shallow |

| Recess     | Transistors                                                         | XLVIII        |

| G.2 Th     | nermal Model                                                        | XLIX          |

| G.2.a      | Model Presentation                                                  | XLIX          |

| G.2.b      | Negligible Self-Heating Effect During a Single Hard-Switching Event | tL            |

| Résumé été | endu (français)                                                     | A             |

|            | hy                                                                  |               |

|            | Bibliography:                                                       |               |

xiii

### Acronyms

2DEG 2-Dimensional Electron Gas 2DHG 2-Dimensional Hole Gas 3DHG 3-Dimensional Hole Gas AC Alternating Current ADC Analog to Digital Converter ALD Atomic Layer Deposition ALE Atomic Layer Etching AlN Aluminium Nitride **BB** Back Barrier BEOL Back-End Of Line BJT Bipolar Junction Transistor BV Breakdown Voltage CCD Charge Coupled Device CCM Continous Current Mode CEA Commissariat à l'Energie Atomique et aux énergies alternatives CL CathodoLuminescence CMOS Complementary Metal Oxide Semiconductor CTE Coefficient of Thermal Expension **CVS** Constant Voltage Stress DAB Dual Active Bridge DC Direct Current DFN Dual Flat No Leads DH-HEMT Double Heterojunction High Electron Mobility Transistor DLTFS Deep Level Transient Fourier Spectroscopy DLTS Deep Level Transient Spectroscopy **DPT** Double Pulse Test DST Double Source Test DUT Device Under Test EL ElectroLuminescance EMC *ElectroMagnetic Coupling* EMMI Emission Microscopy ESB Energy Selective Backscattered ESD ElectroStatic Discharge FEM Finite Element Method FEOL Front-End Of Line FIB Focused Ion Beam FIB-SEM Focused Ion Beam-Scanning Electron Microscopy FOM Figure Of Merit

FP LMTO Full Potential-Linear Muffin-Tin Orbital Ga Gallium Ga<sub>2</sub>O<sub>3</sub> Gallium Oxide GaN Gallium Nitride GaN:C Carbon doped Gallium Nitride GET Gate Edge Terminaison GIT Gate Injection Transistor **GR** Growth Rate HAADF High-Angle Annular Dark Field HBT Heterojunction Bipolar Transistor HD-GIT Hybrid Drain-Gate Injection Transistor HERA DLTS High Energy Resolution Analysis Deep Level Transient Spectroscopy HFET Heterojunction Field Effect Transistors HVPE Hybride Vapor Phase Epitaxy HVSMU High-Voltage Source Measurement Unit IGBT Isolated Gate Bipolar Transistor IMS Insulator Metal Substrate INES Institut National de l'Énergie Solaire InGaAs Indium Gallium Arsenide InSb Indium Antimonide LCL Low Conductive Layer LEM Light Emission Microscopy LETI Laboratoire d'Electronique et de Technologie de l'Information LiDAR Light Detection And Ranging LiT Lock-in Thermography MBE Molecular Beam Epitaxy MEA More Electric Aircraft MFCMU Multi-Frequency Capacitance Measurement Unit MIS Metal Insulator Semiconductor MOS Metal Oxide Semiconductor MOSFET Metal Oxide Semiconductor Field Effect Transistor MOVPE Metal Organic Vapor Phase Epitaxy N Nitrogen NH<sub>3</sub> Ammonia NNH Nearest Neighbor Hopping OBC On Board Charger PCB Printed Circuit Board PEM Photon Emission Microscopy PF Poole Frenkel PFC Power Factor Correction PL PhotoLuminescence PLC Power Line Cycle

XV

**PSJ** Polarization Super Junction PVD Physical Vapor Deposition PWM Pulse Width Modulation ReSurf Reduced Surface electric field **RF** Radio Frequency **RMBE** Reactive Molecular Beam Epitaxy **RR** Ramp Rate RTA Rapid Thermal Annealing SBD Schottky Barrier Diode SCLC Space Charge Limited Current SEM Scanning Electron Microscopy SiC Silicon Carbide SIMS Secondary Ion Mass Spectroscopy SiN Silicon Nitride SiO<sub>2</sub> Silicon Dioxide SJ Super Junction SL Super Lattice SMU Source Measure Unit SOA Safe Operation Area SRL Strain Relief Layer SSPC Steady-State PhotoCapacitance STEM Scanning Transmission Electron Microscopy TCAD Technology Computer Aided Design TDDB Time Dependent Dielectric Breakdown **TEM** Transmission Electron Microscopy TFEE TransFerred Electron Effect TIM Thermal Infrared Microscopy TMAl TrimethylAluminium TMGa TrimethylGallium UID Unintentionally Doped GaN UID-GaN Unintentionnally Doped Gallium Nitride VNA Vectorial Network Analyzer VRH Variable Range Hopping WBG Wide Band Gap XPS X-rays Photoelectron Spectrometry ZVS Zero Voltage Switch

# General Introduction

### Context

Nowadays the astonishing rise of electrification in our society creates a huge demand for technologies related to power conversion systems (example: laptop or cell phone chargers, electric vehicle chargers, *etc*). This is bringing a lot of opportunities for research and development centers such as the Commissariat à l'Energie Atomique et aux énergies alternatives (CEA) and especially the Laboratoire d'Electronique et de Technologie de l'Information (LETI) as well as academic laboratories such as Ampère Laboratory to develop highly efficient electrical systems.

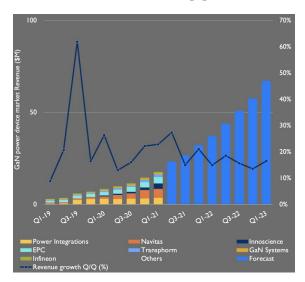

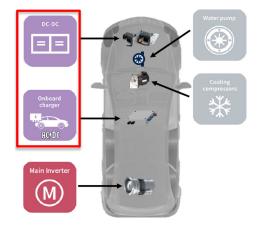

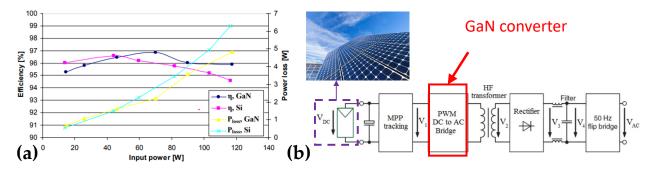

The mainstream silicon technology reveals its limits for certain applications especially in power electronics. Gallium Nitride (GaN) based Heterojunction Field Effect Transistors (HFET) have managed to enter the power semiconductor device market for several years now. Discrete devices are currently available in the 100-900 V and range and from few amperes to 100 A [1], [2]. Its revenue is more than 10M dollars for three years (the main players being: EPC<sup>TM</sup>, Infineon<sup>TM</sup> (Panasonic<sup>TM</sup>), Innoscience<sup>TM</sup>, GaN Systems<sup>TM</sup>, Navitas<sup>TM</sup>, Power Integrations<sup>TM</sup>, Transphorm<sup>TM</sup> and STMicroelectronics<sup>TM</sup>) as shown in **Figure 1** with more than 10% quarter to quarter growth. The latest data report a 2021 revenue of 126M dollars [3].

**Figure 1:** GaN power device revenue from 2019 to Q1-2021 and its forecast for the end of 2021, 2022 and the beginning of 2023 [4].

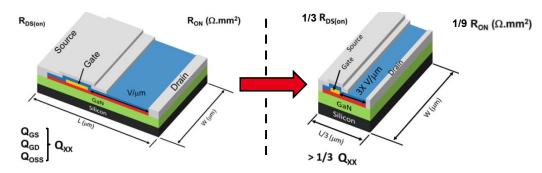

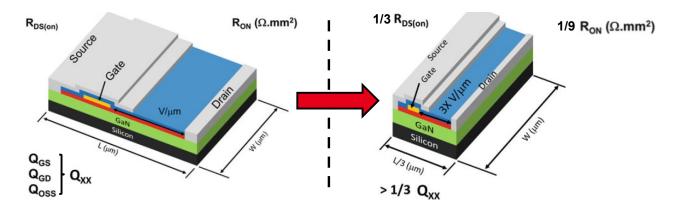

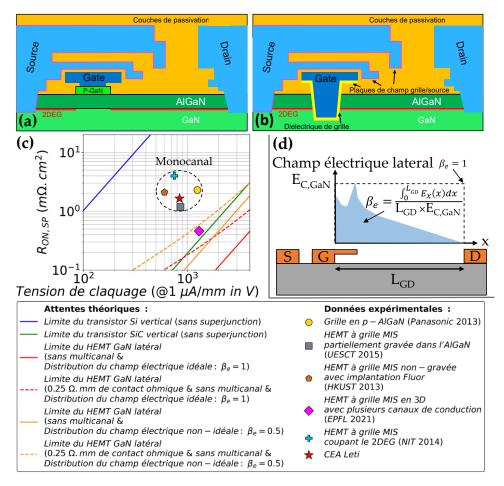

Nevertheless, these GaN-based power switches have not reached their theoretical maximum performance in conduction and during switching. The device length scaling may help in reaching these limits according to Johan T. Strydom in the book of Meneghesso *et al.* [5, pp. 145–148] as illustrated in **Figure 2**, for the following reasons:

- The static on-state resistance<sup>1</sup> ( $R_{DS,ON}$  in Figure 2) is decreased. This is interesting to lower the conduction losses. In addition, the specific on-state resistance ( $R_{ON} = R_{DS,ON} \times A$  in Figure 2) is expected to be even more reduced with the downsized wafer area required to build the transistor,

- The transistor-related charges (Q<sub>XX</sub> in Figure 2) are decreased (divided by three when the length is divided by three in Figure 2). This would lower the switching time (switching speed increased) and therefore the switching losses.

Both allow improving the efficiency of the power converter (ex: chargers) in which they are used. Nevertheless, this approach is limited by:

- The possible reduction of the breakdown voltage in blocking mode with the expected increase of the lateral electric field at a given bias (multiplied by three "3× V/µm" when the length is divided by three in Figure 2),

- The switching speed increase because the parasitic elements perturbation on the switching waveform will be enhanced. This may alter the switching stability.

**Figure 2:** Effect overview of the GaN transistor length scaling down on its relevant electrical properties (adapted from [5, p. 146]).

<sup>&</sup>lt;sup>1</sup> This is different from the dynamic on-state resistance (non-permanent on-state resistance increase after having been stressed in the off-state [6]. Nowadays, some manufacturers report "current-collapse-free" devices [7]. However, to be accurate, it concerns applications in the 100 kHz range because systems were limited to an accurate acquisition after some microseconds [8]. For applications above the MHz range, multiple pulse fast acquisition system was shown to be required for the characterization of GaN technology enabling the observation of the potential limits of these "current-collapse free" devices with respect to more conventional GaN devices for soft-switching applications [9].

### **Objectives and Thesis Organization**

To surpass the possible scaling limitations presented before, the purpose of this PhD is to provide a better understanding:

- On the device electric field distribution in blocking mode,

- On the **transistor hard switching losses**.

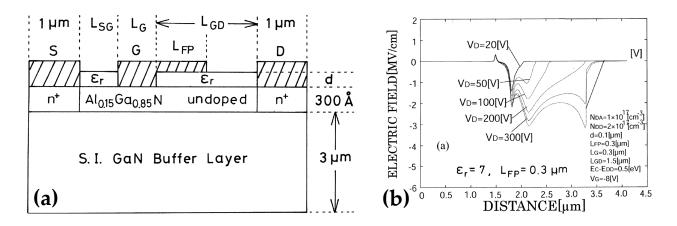

With these targets in mind, <u>Chapter 1</u> is first intended to provide basic knowledge on the AlGaN/GaN lateral power devices from the material properties to its applications. On the one hand, it highlights the interesting material properties that initiated the research and development on this material: the GaN high critical electric field (for high voltage applications) as well as its piezoelectric properties (responsible for the formation of a high electron mobility two-dimensional electron gas used for the low on-state resistance). And on the other hand, the technology developed at CEA LETI will be introduced emphasizing the current technological challenges (normally-off operation, low leakage level, *etc*) as well as a comparison of this technologies (silicon and silicon carbide). After that, a focus on the electric field management will be performed with on the one side the engineering elements allowing to improve the breakdown voltage and on the other side the different methods proposed to probe and study it. A dedicated focus on the switching loss measurement techniques will be presented with a proper definition of the different types of losses and the measurement and extraction methods of the state-of-the-art.

As for the rest of this manuscript, it follows different problematics stated below:

What is currently limiting the device breakdown voltage?

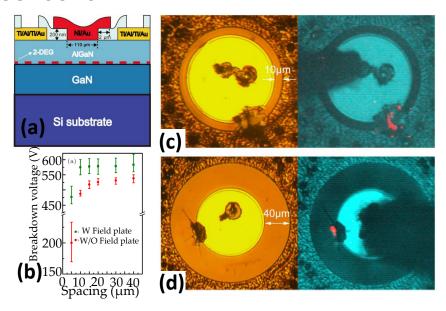

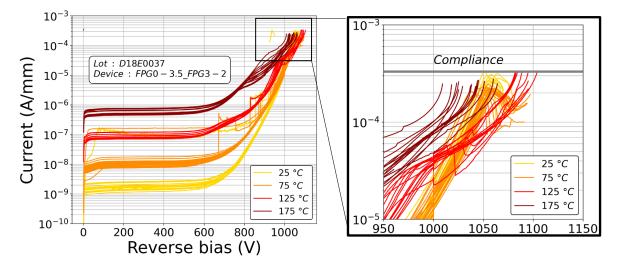

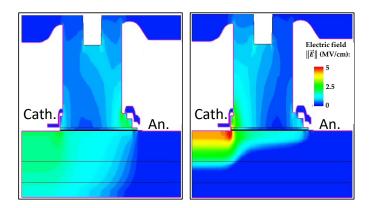

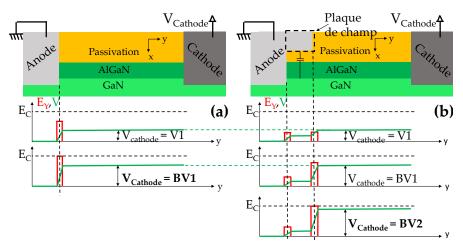

<u>Chapter 2</u> is intended to address this question on the 650 V/6 A AlGaN/GaN-on-Si Schottky barrier diode manufactured at CEA LETI. To do so, the breakdown mechanisms as well as the techniques to identify them reported in the AlGaN/GaN power device literature will be presented. This part will be followed by the general identification of the different breakdown mechanisms in the studied devices will be introduced especially by connecting the substrate to the anode or not. Then the breakdown location will be investigated in both breakdown modes (vertical and lateral). This will be realized by analyzing the dependency of the breakdown voltage with respect to 3

temperature, layout and epitaxy and also by means of a failure and physical analysis (Lock-in thermography and Focused ion beam scanning electron microscopy). This study will be used as a reference for the electric field simulation study proposed in the <u>Chapter 3</u> in addition to proposing possible layout and epitaxial optimization for the breakdown voltage.

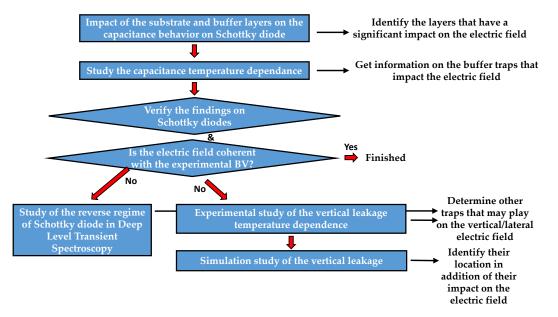

Is the Technology Computer-Aided Design (TCAD) modeling proposed in the literature sufficient enough to reproduce the current experimental breakdown voltage? What are the missing elements? Which electrical characterizations would allow their calibration?

<u>Chapter 3</u> is intended to develop the TCAD modeling of AlGaN/GaN-on-Si Schottky barrier diodes fabricated at CEA LETI to be able to get a representative image of the experimental electric field. To do so, limits of the state-of-the-art approach will be reported before describing the methodology adopted in this thesis to deal with the modeling of buffer traps. Based on capacitance-temperature measurements and TCAD analysis, deep acceptor traps present in the buffer layers are identified based on their electrical properties. After that, a study performed on the experimental vertical current temperature dependence will be presented, highlighting the impact of some donor traps on the vertical conduction which plays a role in the electric field distribution. Finally, Deep Level Transient Fourier Spectroscopy (DLTFS) allowing to probe traps near the anode will be presented before summarizing the different obtained results.

What are the impacts of the transistor layout and process parameter that may be changed due to the scaling down on the switching losses?

<u>Chapter 4</u> is dedicated to the study of the 650 V rated AlGaN/GaN-on-Si power transistors switching losses. In this chapter, the layout (gate, gate to drain and field plates length) and process parameters (gate recess depth) dependencies will be studied. Indeed, these parameters may be changed in the device length scaling down. This can provide scaling guidelines to optimize the switching losses. Coupled with well-calibrated TCAD simulation deck allowing to reproduce static on and off experimental measurements (as developed in <u>Chapter 3</u>), it would ease the device design. Thus a state-of-the-art of the switching loss-oriented studies performed in the literature will be presented to situate the following studies. Switching losses of 650 V/30 A transistors with two different gate recess depths will be compared and analyzed to understand the origin of the switching loss differences thanks to LTSpice simulations mainly and TCAD simulations. Finally, the layout limitation of the scaled 650 V/1 A transistors will be enhanced as well as some observations on the hard switching performance.

# Chapter I AlGaN/GaN-on-Silicon Devices for Power Electronics, State-of-the-Art and Scaling Perspectives

This chapter explains the technical reasons for the astonishing growth of GaN power devices on the market. The current limitations in terms of electric field management will be emphasized with the different proposed solutions to tackle the problem. After that, key knowledge will be given to understand switching losses.

### Outline

| Chapter I AlGaN/GaN-on-Silicon Devices for Power Electronics, State-of-the-Art   |

|----------------------------------------------------------------------------------|

| and Scaling Perspectives                                                         |

| I.1 Gallium Nitride: From the Raw Material to its Applications                   |

| I.1.a Gallium Nitride: A Wide Band Gap Material8                                 |

| I.1.a.i Wide Band Gap Semiconductors                                             |

| I.1.a.ii The Crystalline Properties of Gallium Nitride11                         |

| I.1.a.iii The Polarization Properties of Gallium Nitride14                       |

| I.1.b Gallium Nitride: A Material Used to Make Power Devices19                   |

| I.1.b.i Power Devices with GaN19                                                 |

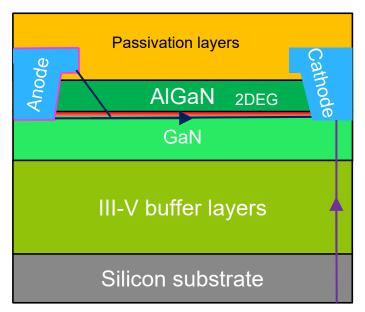

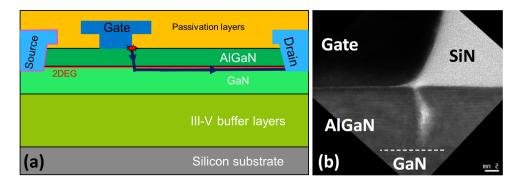

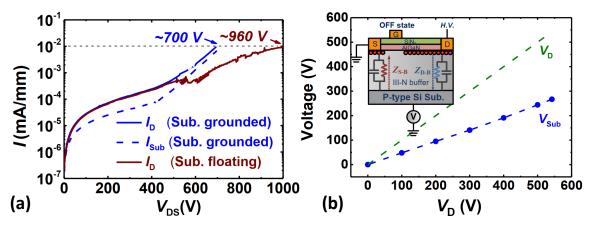

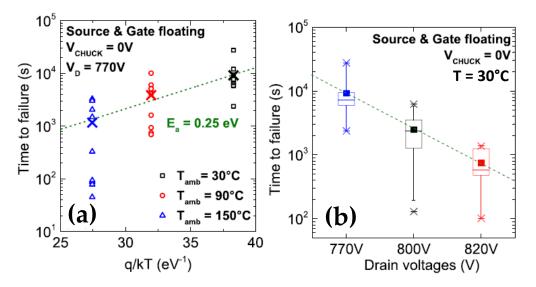

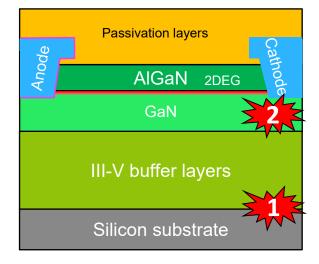

| I.1.b.ii The Specificity of Lateral AlGaN/GaN-on-Si Power Devices                |

| I.1.c Gallium Nitride: From the Power Device Performances to its Applications    |

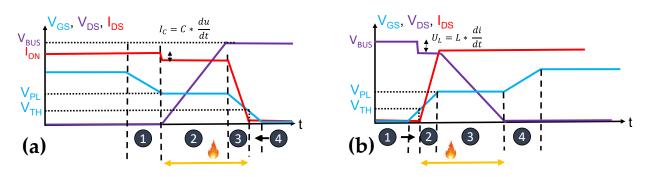

| I.1.c.i Transistor Hard and Soft Switching                                       |

| I.1.c.ii A Wide Range of Applications for GaN transistors                        |

| I.1.d Summary                                                                    |

| I.2 Device Architecture to Improve the Breakdown Voltage and Method to Study the |

| Electric Field                                                                   |

| I.2.a Device Architecture Improvements for High Breakdown Voltage                |

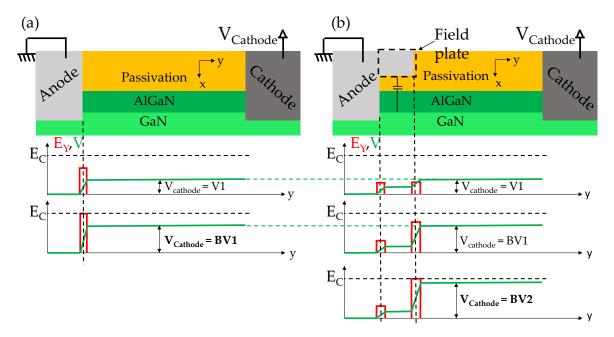

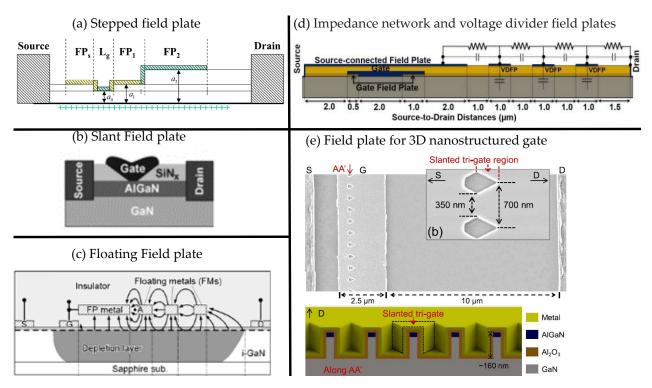

| I.2.a.i The Field Plates                                                         |

| I.2.a.ii The Low Conductive Layer40                                              |

| 6                                                                                |

| I.2.a.iii    | The Polarization Super Junction                        | 41 |

|--------------|--------------------------------------------------------|----|

| I.2.a.iv     | The Epitaxial Layers Engineering                       | 42 |

| I.2.a.v      | The Substrate Removal                                  | 43 |

| I.2.b Met    | thod to Probe the Electric Field                       | 44 |

| I.3 State-of | f-the-Art of the Switching Loss Measurement Techniques | 45 |

| I.3.a Dif    | ferent Switching Loss Origins                          | 45 |

| I.3.b Dif    | ferent Setups for Loss Extraction                      | 46 |

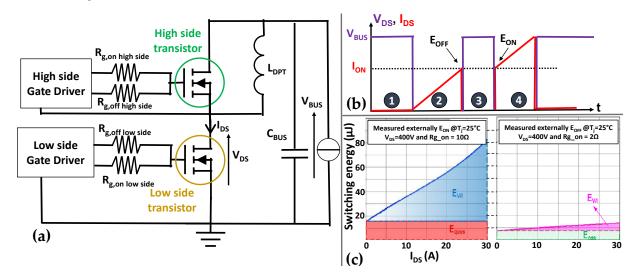

| I.3.b.i D    | Oouble Pulse Test (DPT)                                | 46 |

| I.3.b.ii     | Calorimetric Measurement Test                          | 47 |

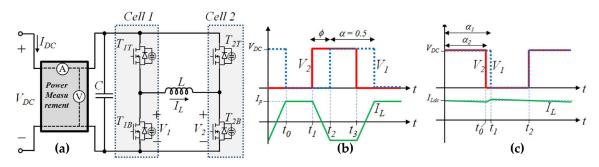

| I.3.b.iii    | Opposition Test Method                                 | 48 |

| I.3.b.iv     | Indirect Measurement Method                            | 48 |

| I.3.b.v      | Analytical Model                                       | 49 |

| I.3.b.vi     | Summary                                                | 49 |

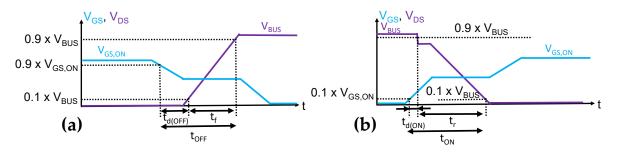

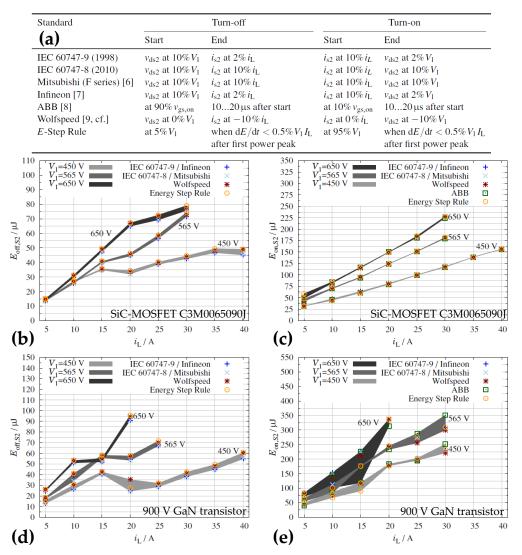

| I.3.c Dif    | ferent Loss Extraction                                 | 50 |

| Conclusion   |                                                        | 52 |

# I.1 Gallium Nitride: From the Raw Material to its Applications

In this subsection, a description of GaN-based technology is presented from the raw material properties to its final applications in power converters passing by device properties.

### I.1.a Gallium Nitride: A Wide Band Gap Material

In the first part, Gallium Nitride material properties will be presented. Its belonging to the wide band gap semiconductor category (material prone to extend the limits of silicon power electronics devices) will be firstly introduced. Secondly, its specific crystalline structure, the doping impurities and the crystal imperfections of the material used for power devices will be detailed. Thirdly, its piezoelectric properties allowing to obtain a 2-Dimensional Electron Gas (2DEG) will be presented as well as its interesting electronic transport properties.

### I.1.a.i Wide Band Gap Semiconductors

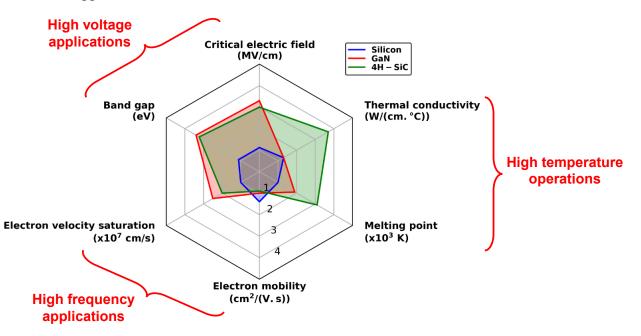

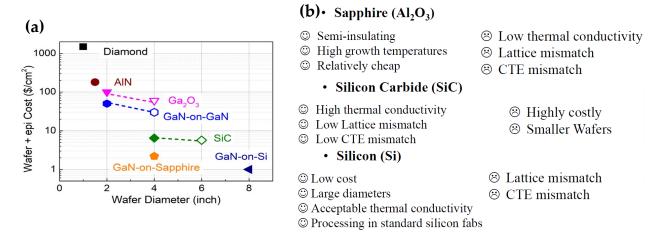

Wide Band Gap (WBG) semiconductors are considered to have properties that are very interesting for power electronics. They are characterized by their larger band gap with respect to the silicon (Silicon Carbide (4H-SiC): 3.23 eV [10]; Gallium Nitride (2H-GaN): 3.4 eV [10]; Gallium Oxide (Ga<sub>2</sub>O<sub>3</sub>): 4.8-4.9 eV [11]; Aluminum Nitride (AlN): 6.2 eV [10]; Diamond: 5.46-5.6 eV [12]). Their properties are compared with respect to the Silicon for three different categories of applications as represented in the radar chart of **Figure 3**:

- I High-voltage properties:

- Band gap E<sub>G</sub>: energy difference between the minimum of the conduction band and the maximum of the valence band in the Brillouin zone. It is important for high voltage applications because the critical electric field is related to this quantity as exposed in Equation 1. For power electronics, this is also interesting because the higher the band gap the higher the energy enabling the thermal generation of carriers. The latter lead to unwanted leakage at high temperature, therefore WBG semiconductors exhibit lower leakage at high temperature. Finally, having a high band gap make the semiconductor less sensitive to irradiation for a certain energy range. This is useful in harsh environments (nuclear power plants, spatial). The 3.4 eV (at room temperature since it slightly decreases with temperature according to the relation given in the book of

Levinshtein *et al.* [10]) of GaN is superior to the value of SiC or Si as shown in Figure 3 which makes it suitable for high-voltage applications.

$$E_C \propto E_G^{\gamma}$$

**Equation 1:** Critical electric field relation with the band gap [13], [14] ( $E_c$ : critical electric field;  $E_G$ : band gap;  $\gamma$ : power coefficient (state-of-the-art value: 1.83 [13])).

- <u>Critical electric field E<sub>C</sub></u>: It is the maximum electric field the material can withstand without irreversible damage. As expected, in accordance with Equation 1, GaN has a higher critical electric field (3.3 MV/cm in Figure 3) with respect to Si and SiC.

- I High-temperature properties:

- <u>Thermal conductivity k</u>: It represents the ability of a material to conduct heat. It is especially interesting to limit self-heating thus preventing performance limitations and reliability issues in high-power-density and high-temperature applications. In **Figure 3**, it can be seen that this is not the main asset of GaN but rather that of SiC.

- <u>Melting point T<sub>C</sub></u>: Temperature above which the material melts. Again, the parameter is higher for SiC, which makes this material very interesting for high-temperature applications.

**Figure 3:** Bulk material properties at 300 K (room temperature): the most common wide band gap semiconductors (SiC, GaN) compared to the widely used silicon (based on [10]).

<sup>9</sup>

- I High-frequency properties:

- <u>Electron mobility μn</u>: It is the ability for the electron to move inside the crystal under a certain electric field. It can be drastically reduced by either crystalline defects, temperature (phonon-electron interactions), the presence of other carriers or impurities. In Figure 3, it can be seen that this is not the main asset of either GaN or SiC since their mobility reaches 1000 cm²/(V.s) whereas the silicon one approaches 1500 cm²/(V.s). Nevertheless, as it will be described later on, lateral GaN devices benefit from the high mobility (close to 2000 cm²/(V.s) [15]) of a 2-Dimensional Electron Gas (2DEG).

- Electron velocity saturation v<sub>sat</sub>: It is the maximum electron speed reached under high electric field. According to Equation 2 exposed in the paper of Marino *et al.* [16], having a large saturation velocity induces a large device cut-off frequency. This simple approach has to be nuanced with more recent formula in the paper of Kwak *et al.* [17] (Equation 3) in which the contribution of access resistance and parasitic capacitance limits the cut-off frequency. This formula is closer to the real device than one based on material properties.

$$f_T = \frac{v_{sat}}{2 \times \pi \times L_G}$$

**Equation 2:** Cut-off frequency in the paper of Marino *et al.* ( $f_T$ : cut-off frequency;  $v_{sat}$ : velocity saturation;  $L_G$ : gate length) [16].

$$f_T = \frac{g_m}{2 \times \pi \times (C_{GS} + C_{GD})}$$

**Equation 3:** Cut-off frequency in the paper of Kwak *et al.* ( $f_T$ : cut-off frequency;  $g_m$ : transconductance;  $C_{GS}$ : gate-to-source capacitance;  $C_{GD}$ : gate-to-drain capacitance) [17].

The material properties comparison is useful to target the possible application range of these wide band gap semiconductors. This is especially done using Figure Of Merit (FOM) proposed by Baliga *et al.* [18] (indication for low-frequency power switching applications) and Johnson *et al.* [19] (indication for high-power applications at high frequency) as summarized in the paper of Islam *et al.* [20]. However, it is still limited to material. More elements are required to verify if the material can be effectively used for power devices such as the capability of making low resistive ohmic contacts, the capability of growing or depositing a dielectric layer with a good interface quality and the capability to modulate the conductivity of the material with doping impurities. Moreover, its commercialization depends also on the overall cost (raw material cost and fabrication cost which include the wafer size) of the device as well as the device performances which may differ with the type of device: vertical or lateral.

Cette thèse est accessible à l'adresse : https://theses.insa-lyon.fr/publication/2023ISAL0021/these.pdf © [F. Rigaud-Minet], [2023], INSA Lyon, tous droits réservés

### I.1.a.ii The Crystalline Properties of Gallium Nitride

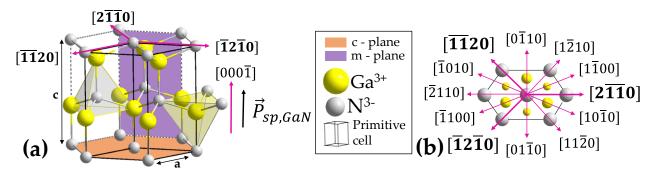

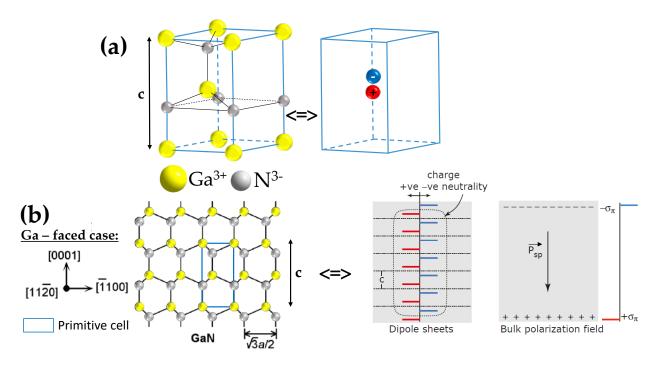

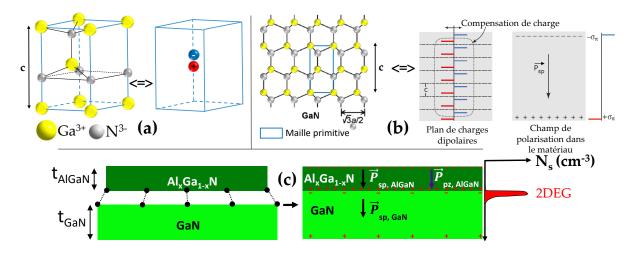

GaN is a III-V semiconductor. This means that it is made of atoms from the third column in Mendeleev's Periodic Table: Gallium (Ga) and atoms from the fifth columns: Nitrogen (N). It was for the first time epitaxially grown on a sapphire substrate in 1969 by Maruska *et al.* [21] using Hybride Vapor Phase Epitaxy (HVPE). The grown crystal had a hexagonal (Wurtzite) lattice as in GaN devices nowadays and as illustrated in **Figure 4**. However, it must be mentioned that another crystalline structure exists: cubic (Zinc Blend) structure. It is thermodynamically metastable whereas the wurtzite structure is mechanically and thermally more stable [22] and it does not exhibit spontaneous piezoelectric properties mandatory for the 2DEG formation (I.1.a.iii).

#### † The GaN Wurtzite (2H) lattice

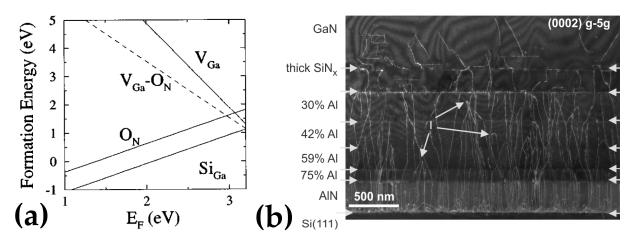

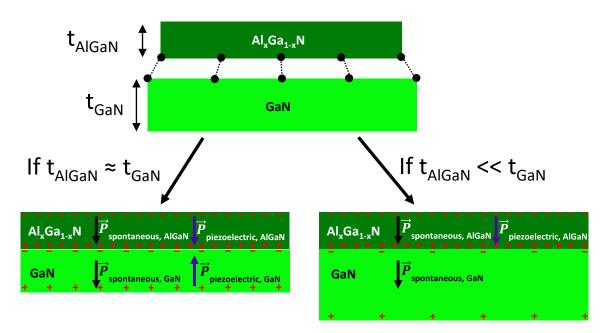

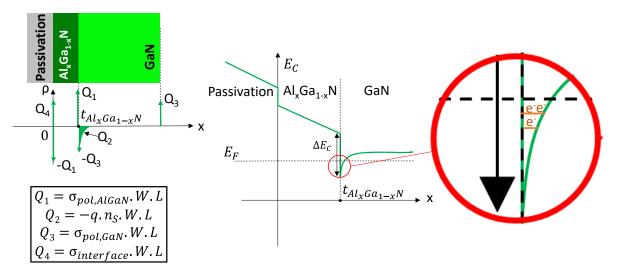

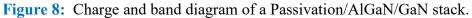

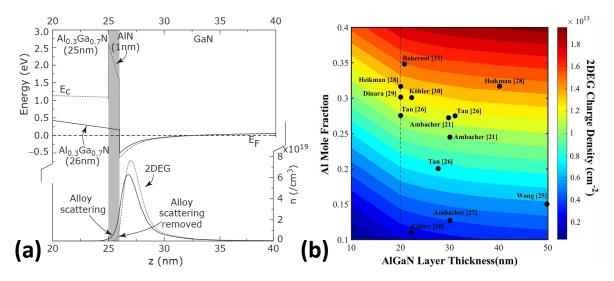

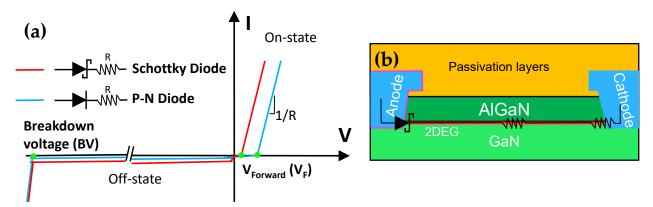

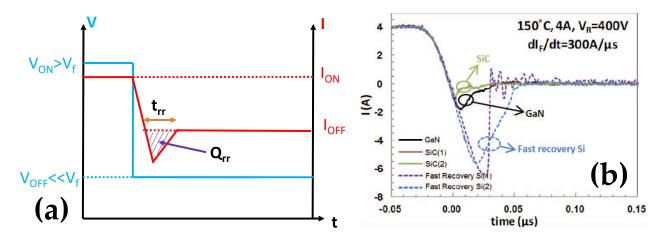

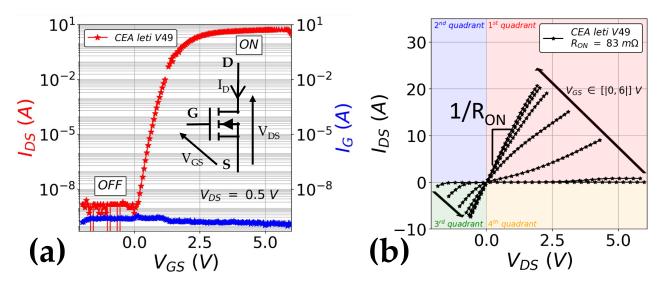

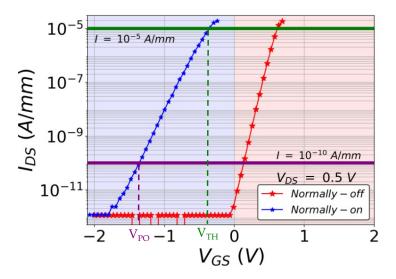

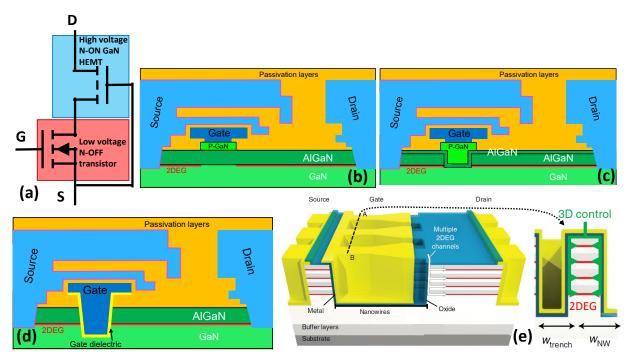

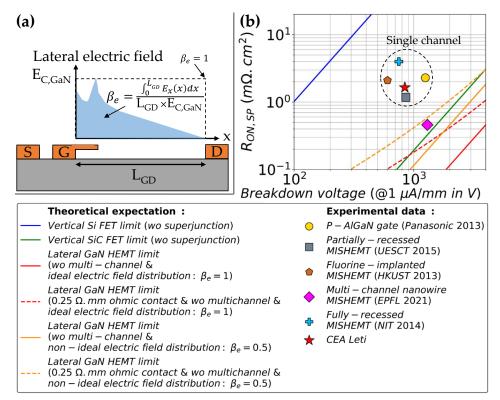

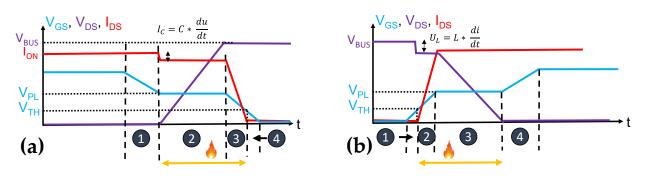

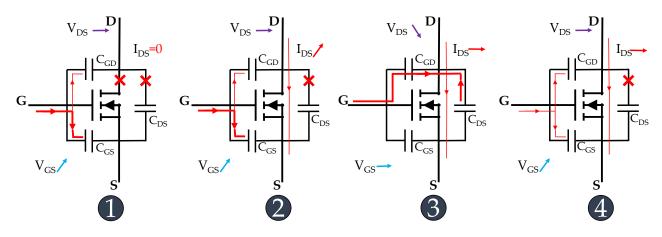

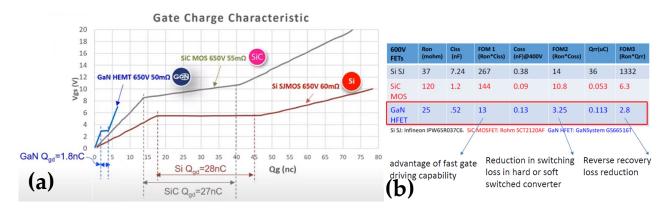

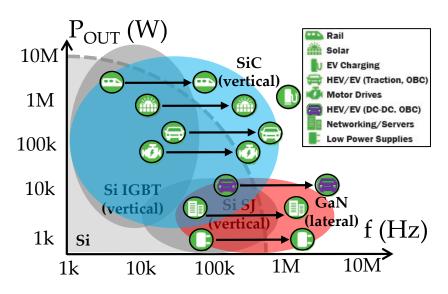

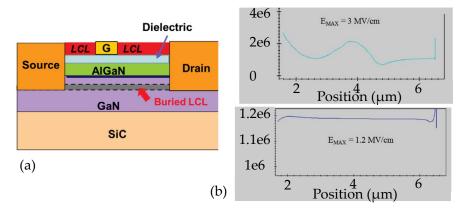

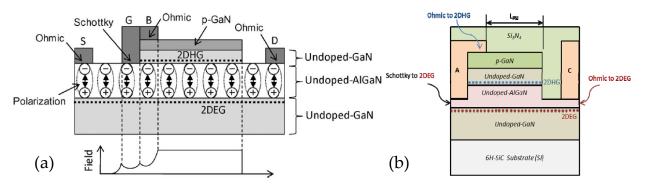

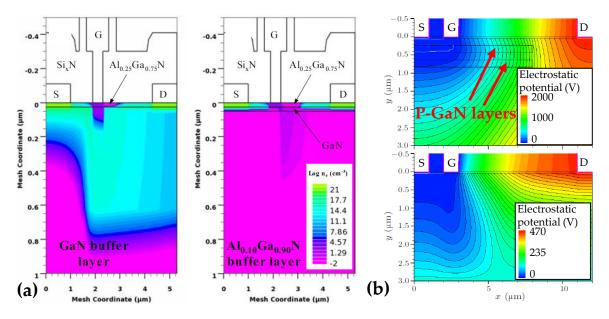

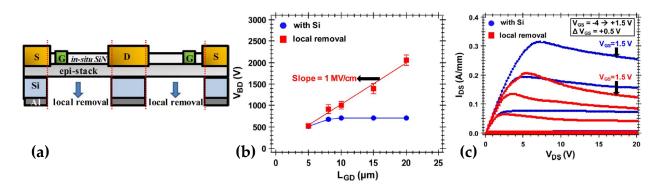

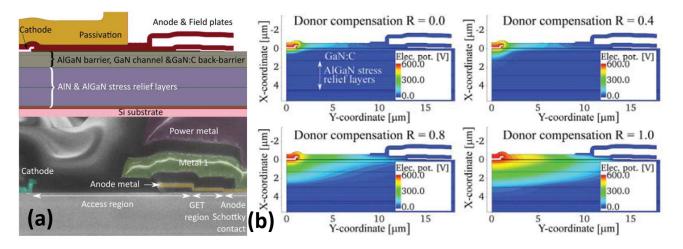

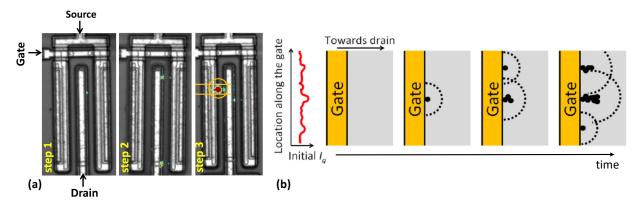

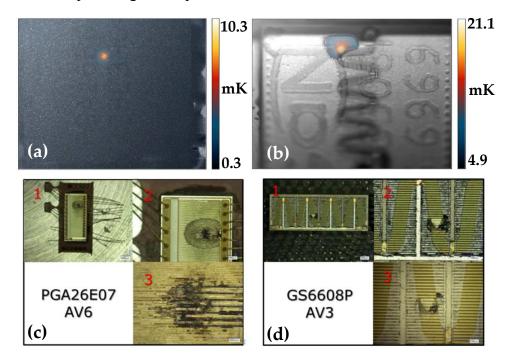

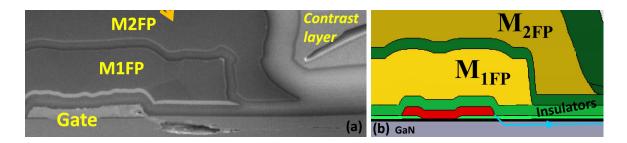

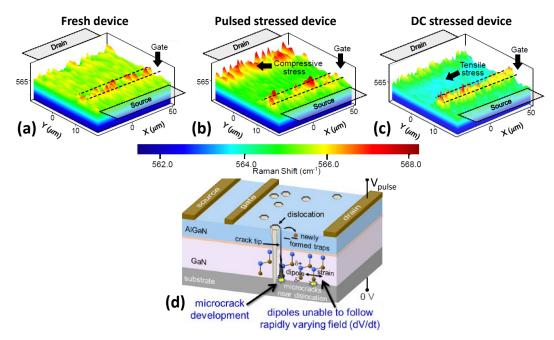

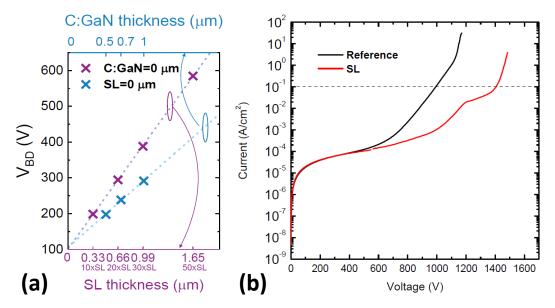

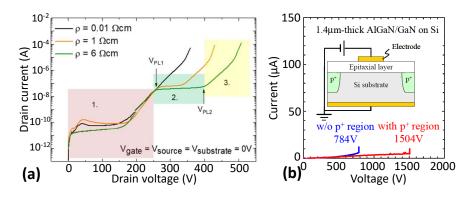

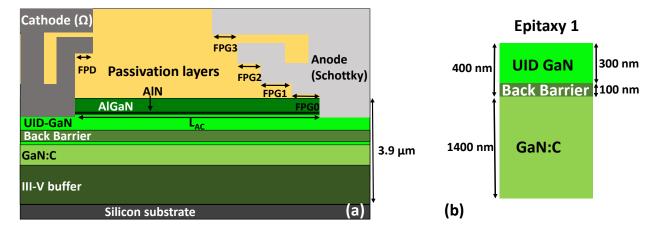

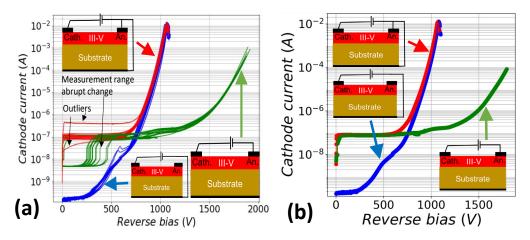

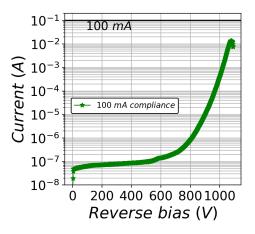

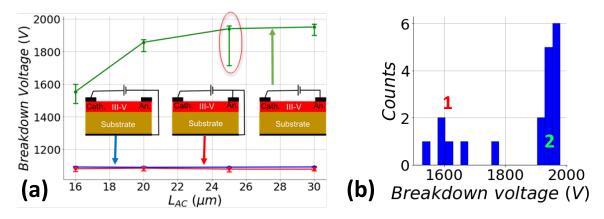

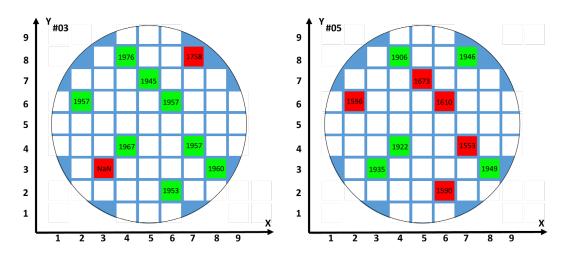

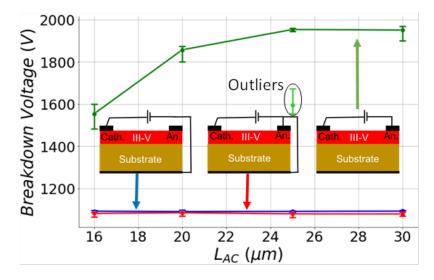

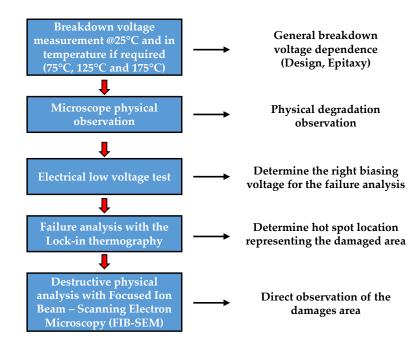

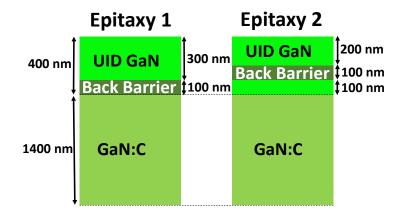

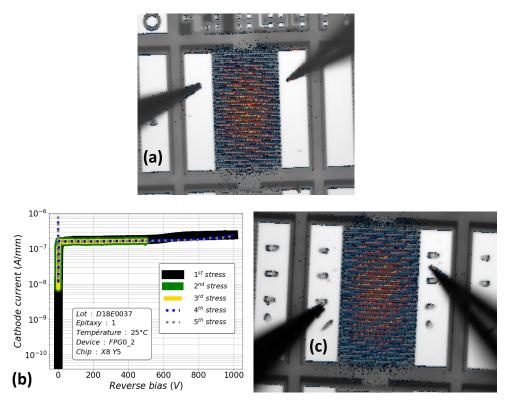

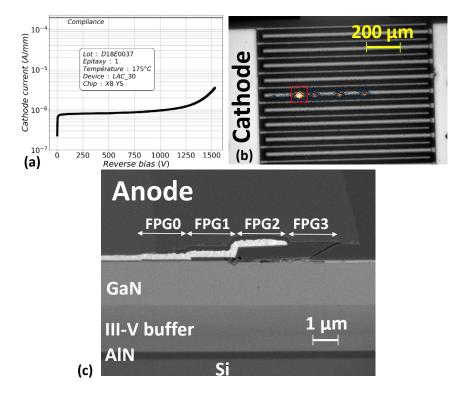

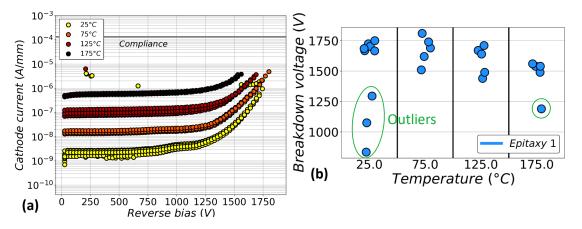

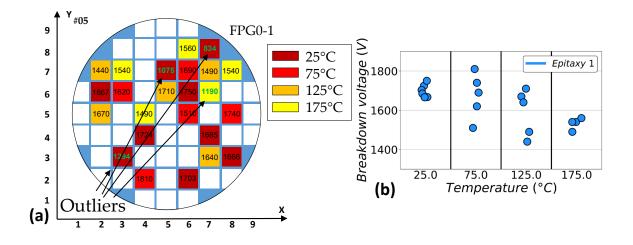

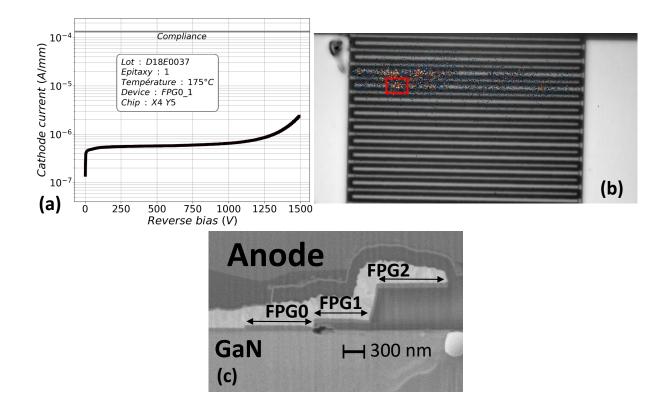

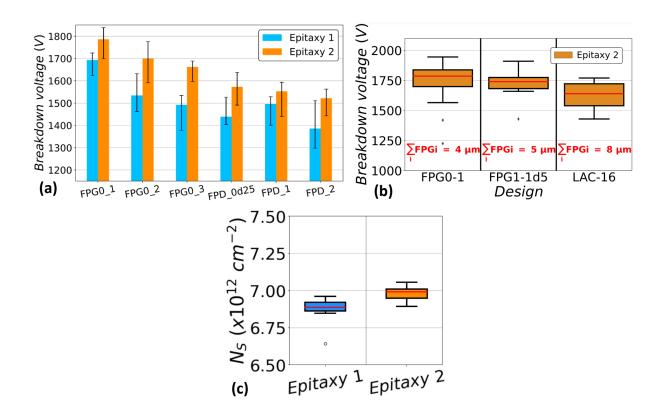

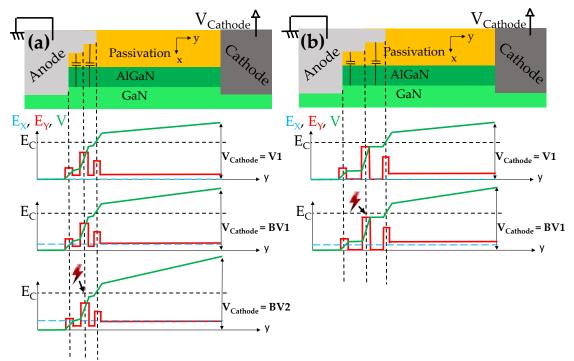

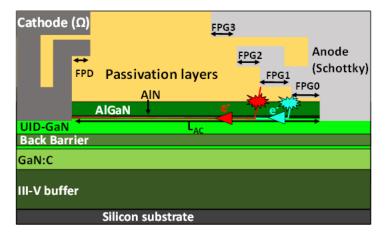

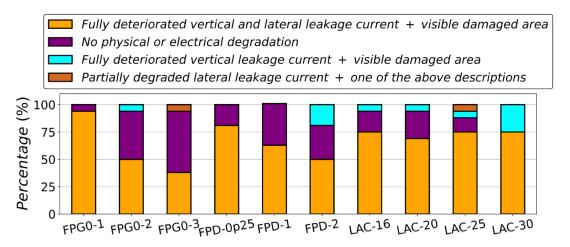

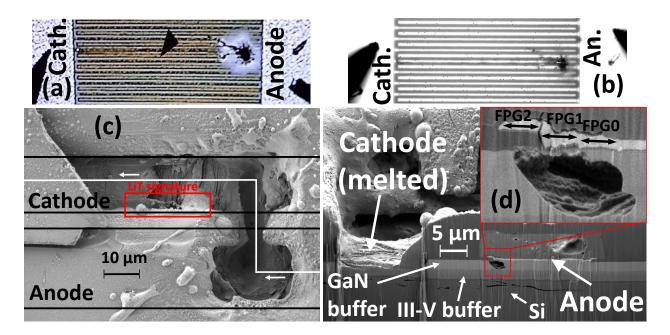

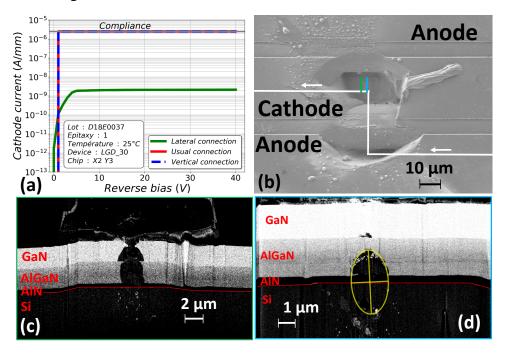

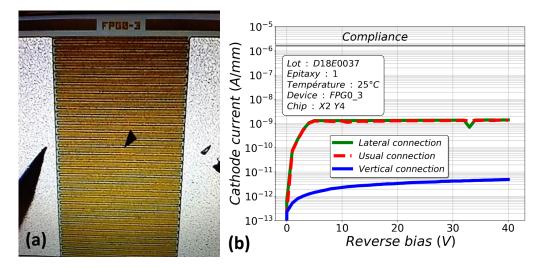

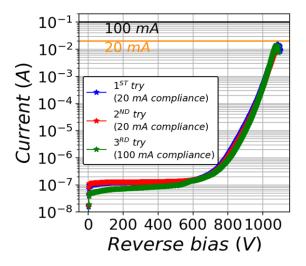

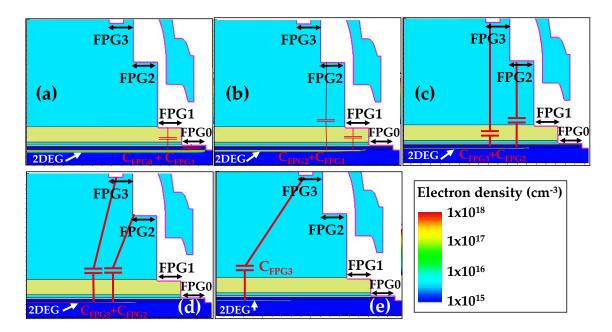

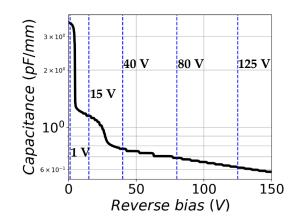

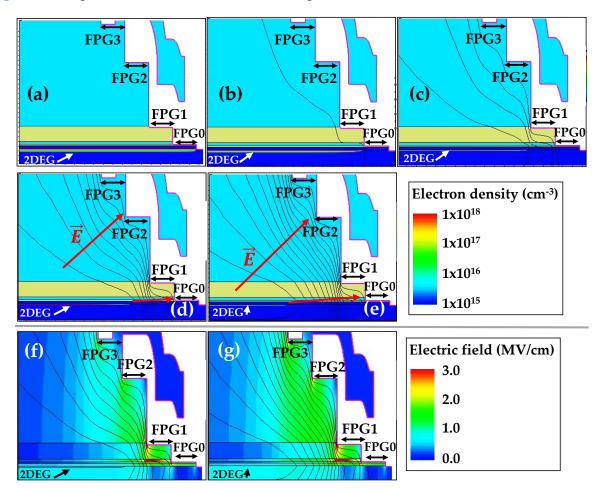

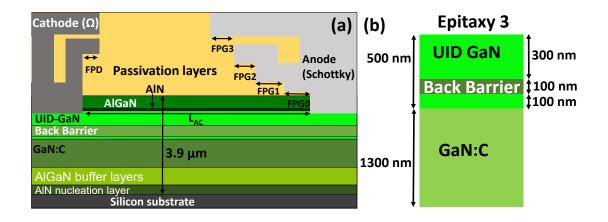

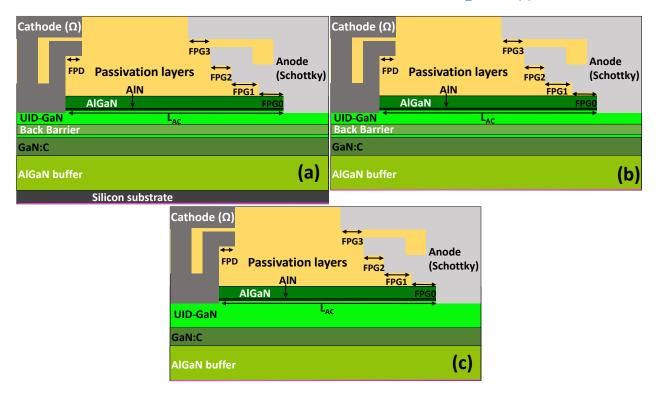

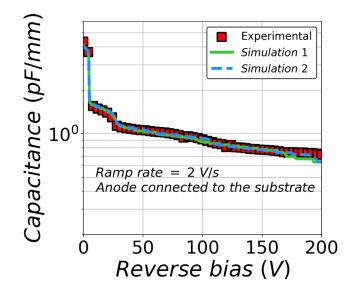

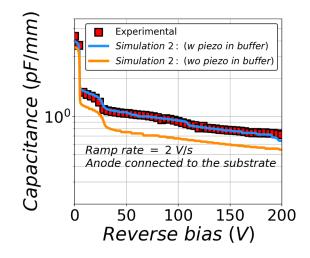

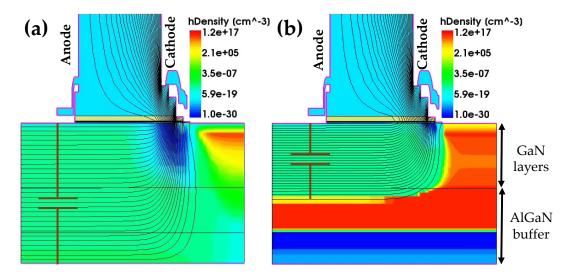

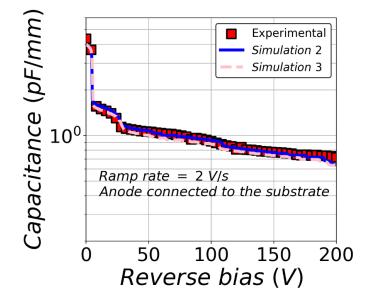

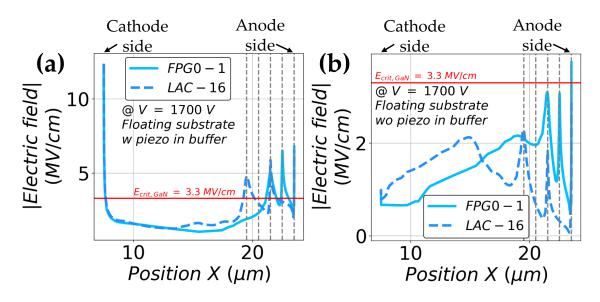

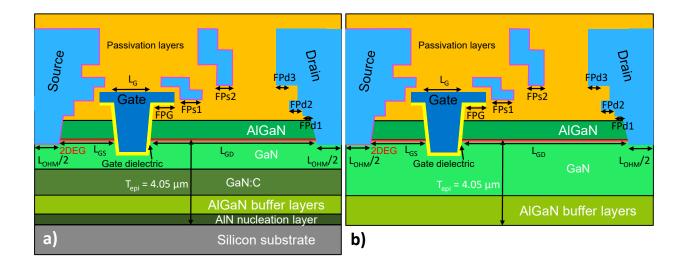

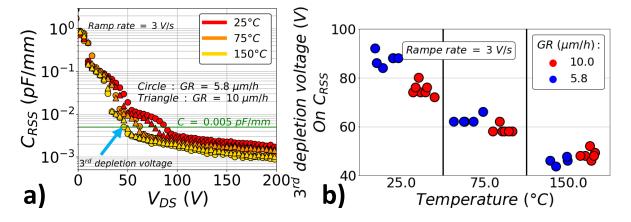

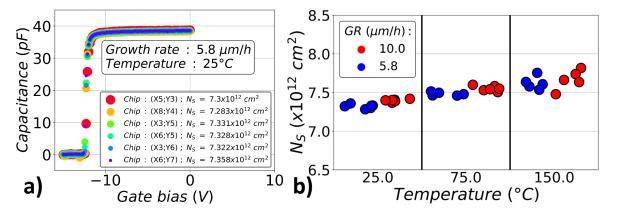

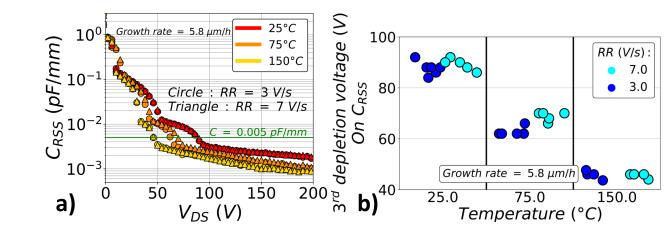

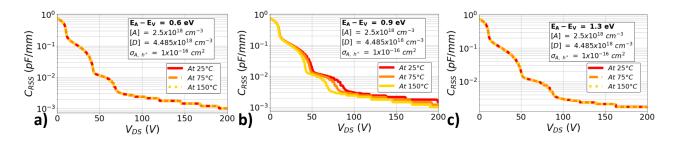

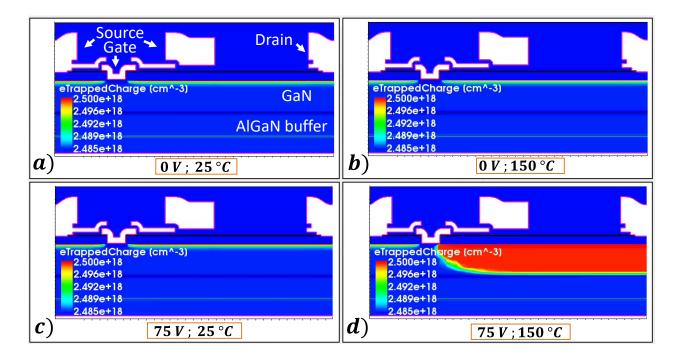

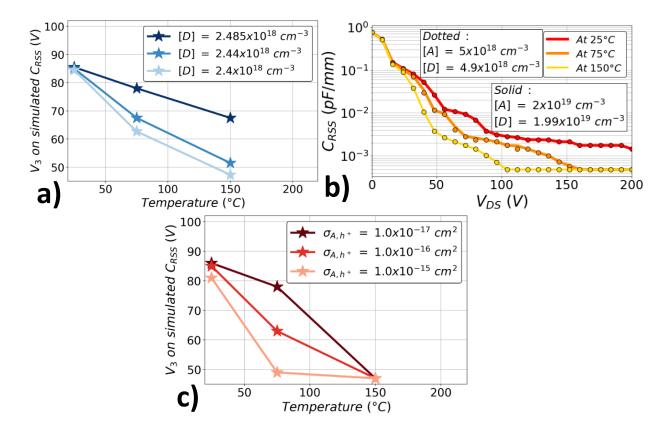

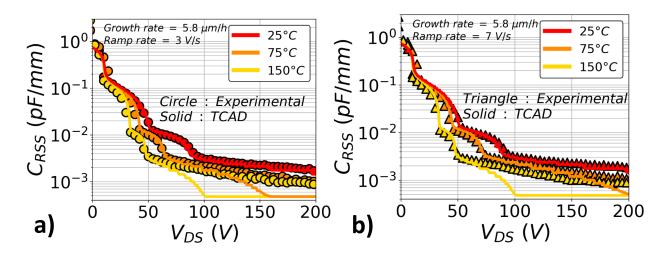

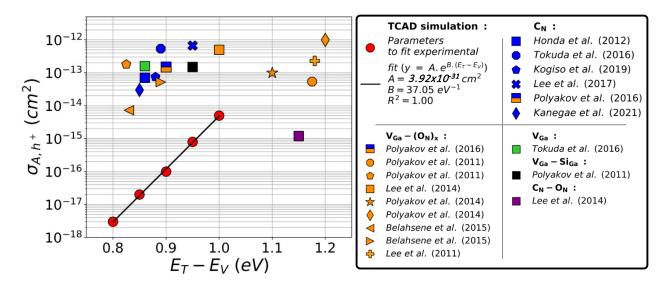

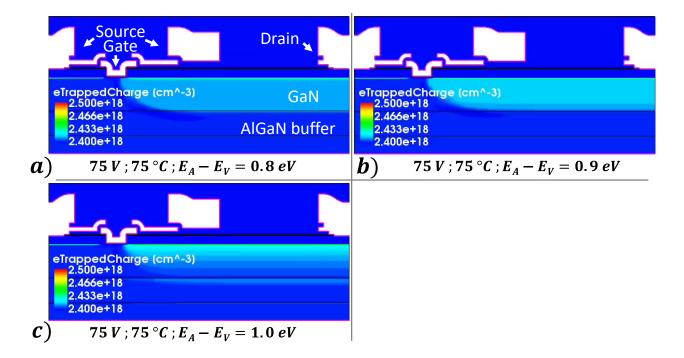

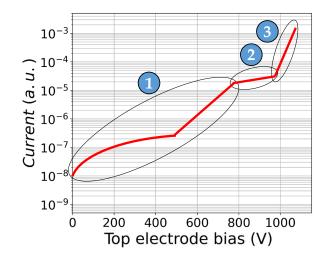

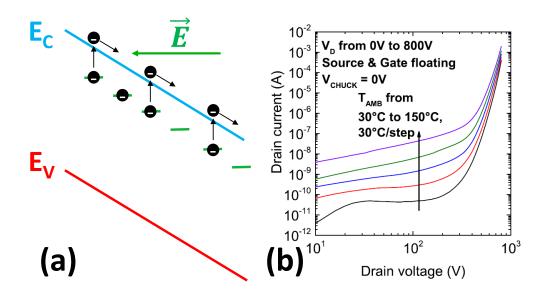

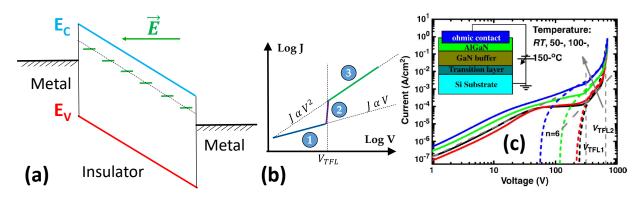

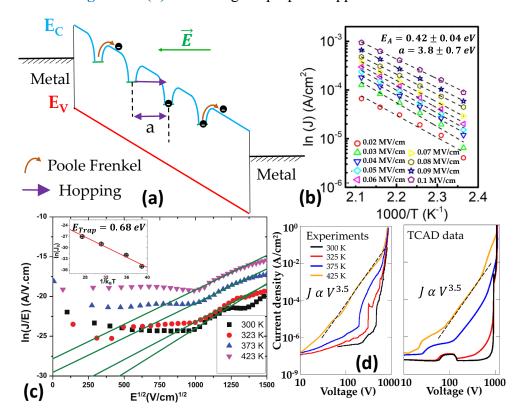

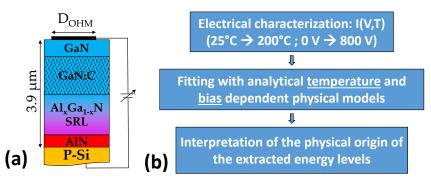

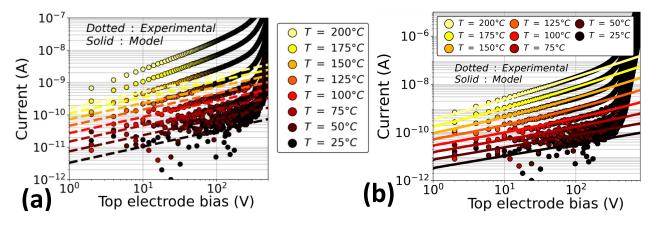

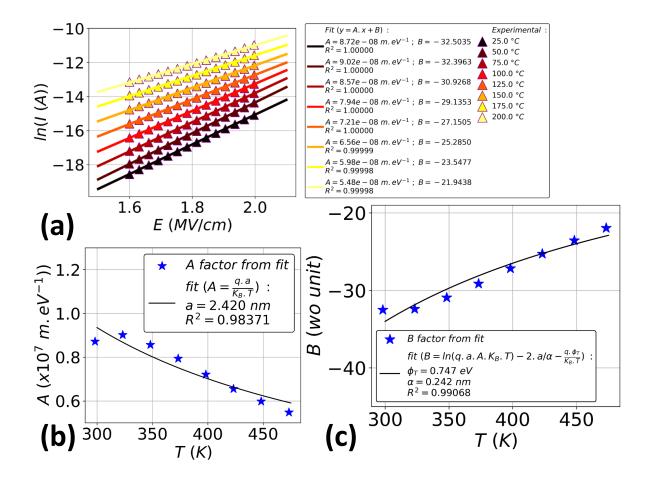

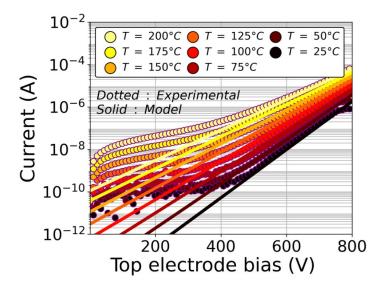

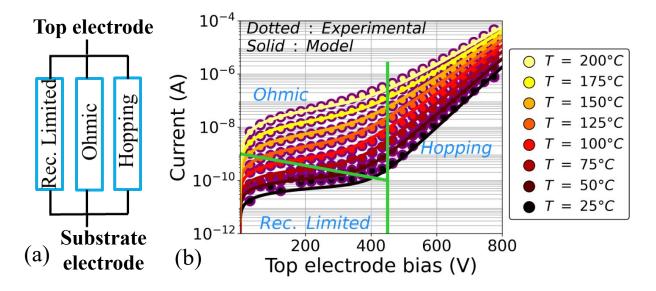

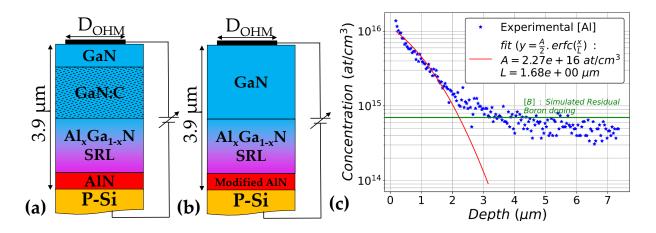

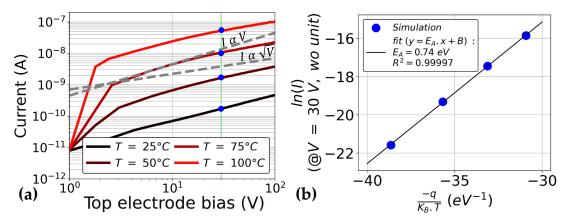

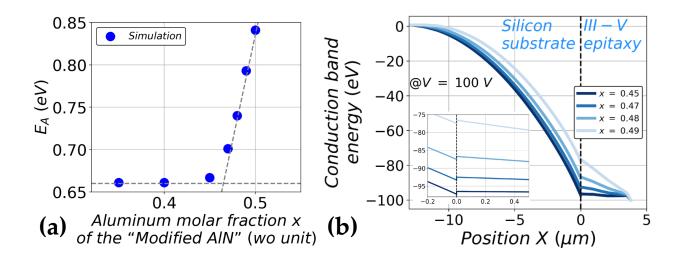

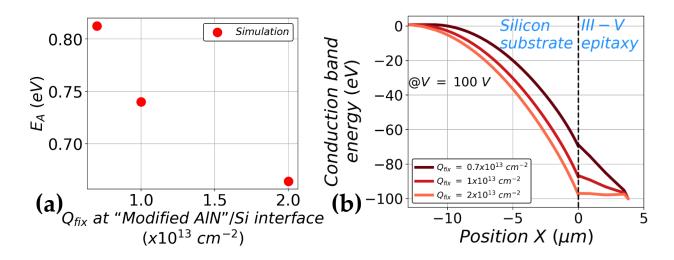

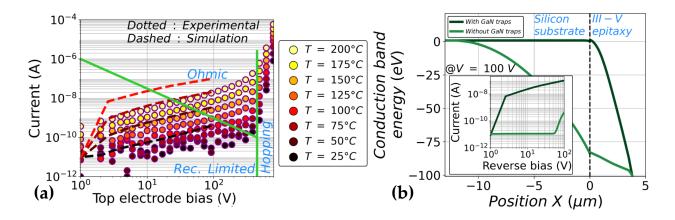

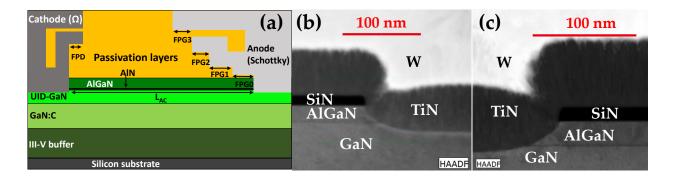

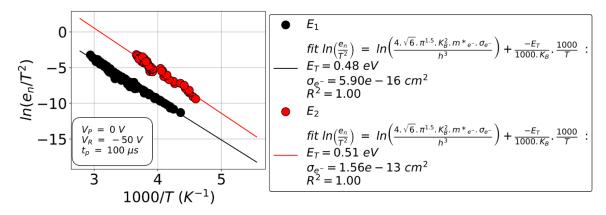

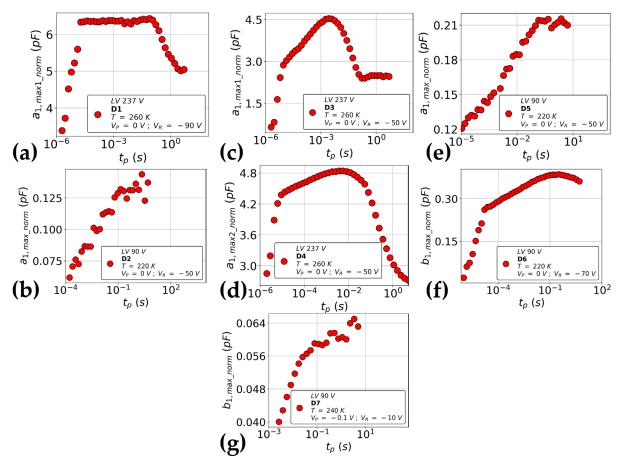

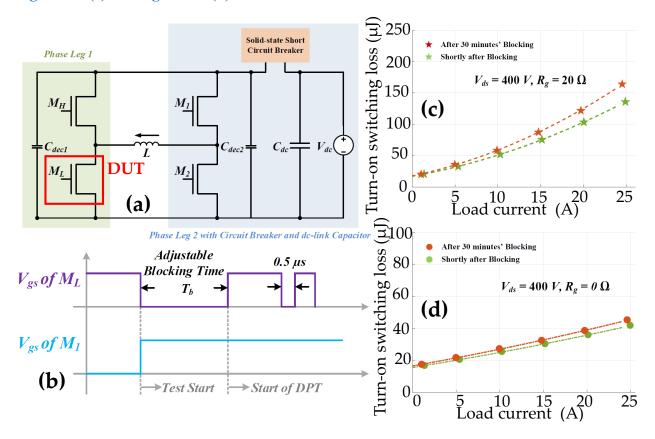

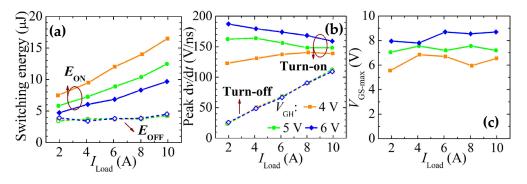

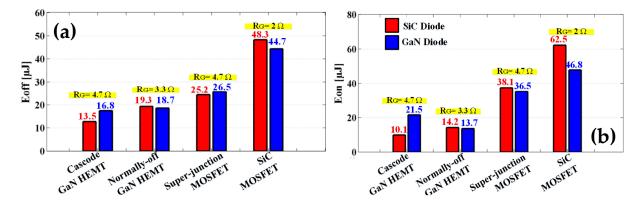

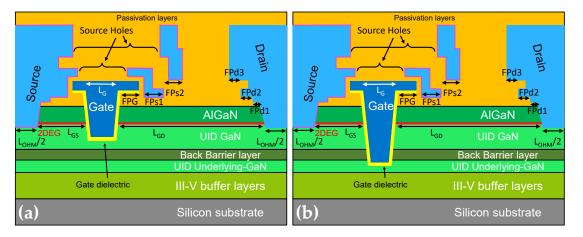

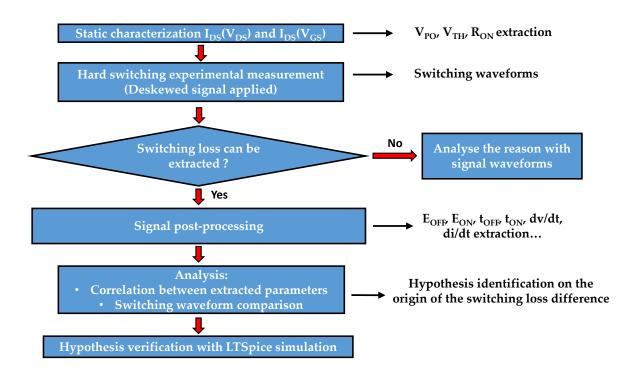

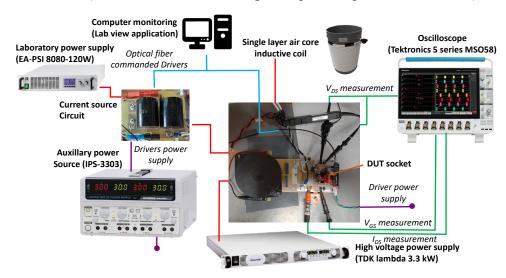

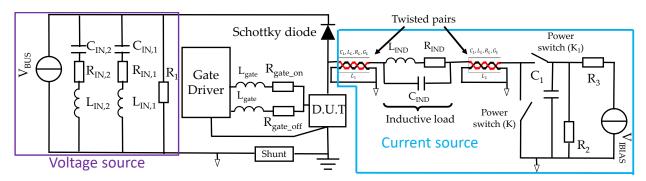

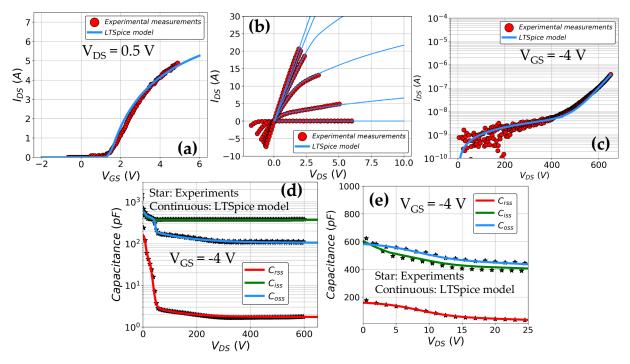

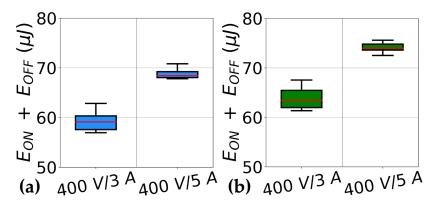

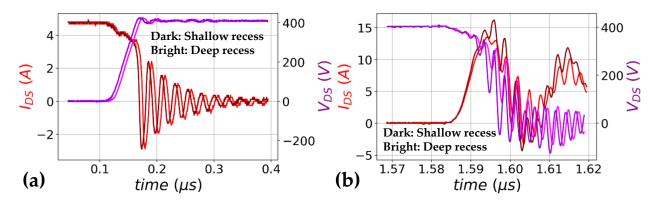

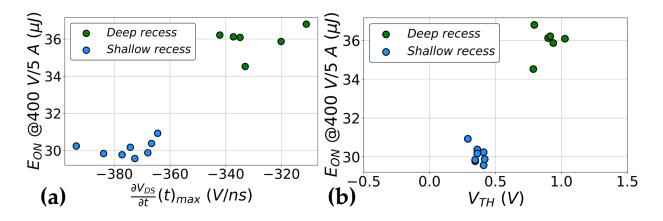

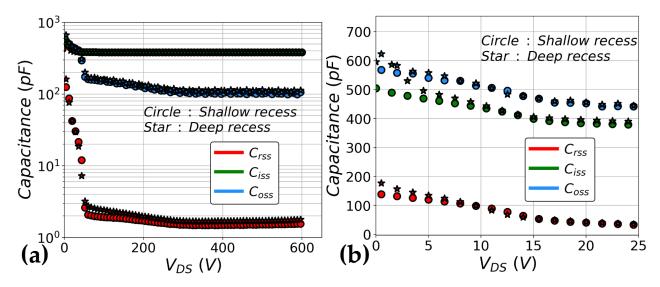

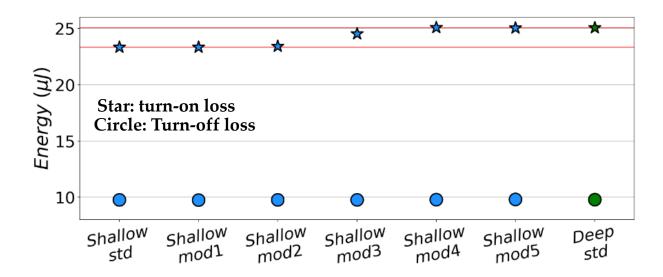

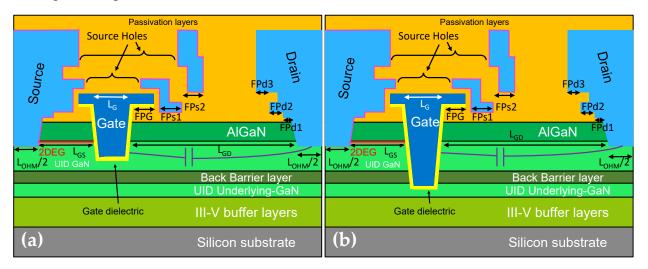

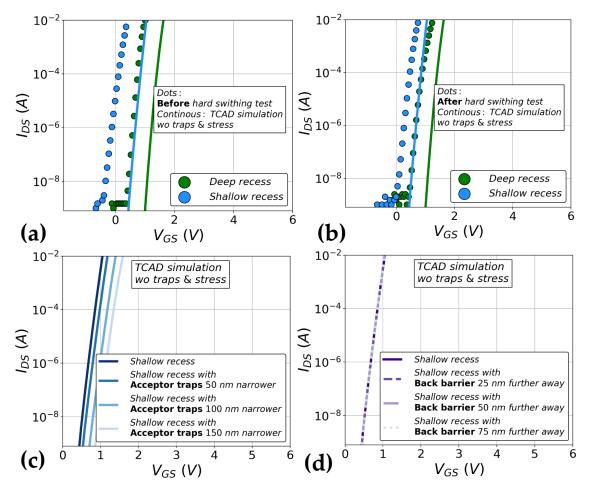

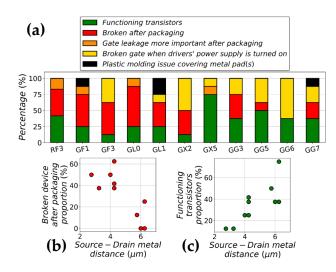

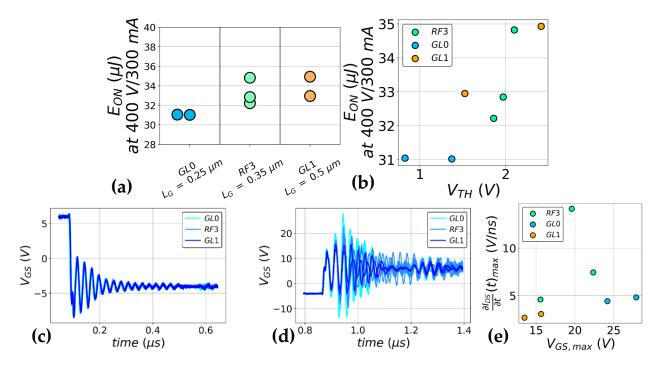

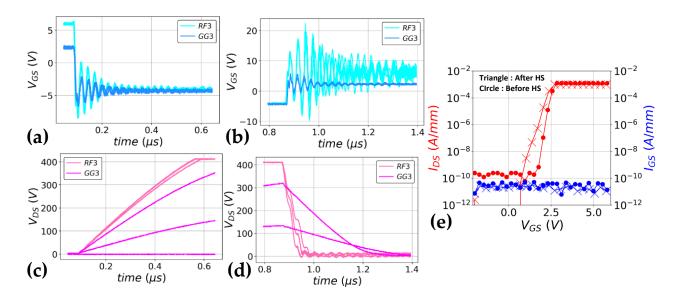

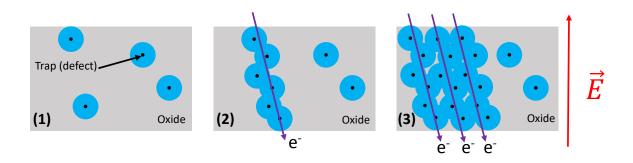

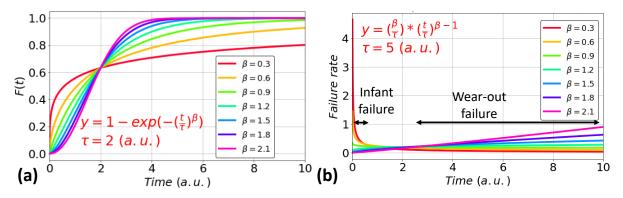

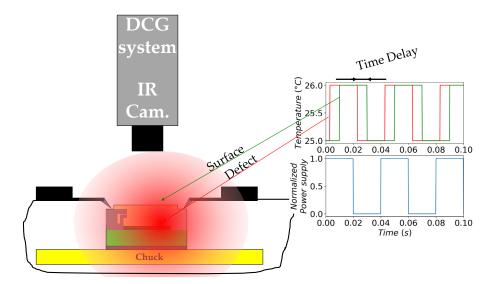

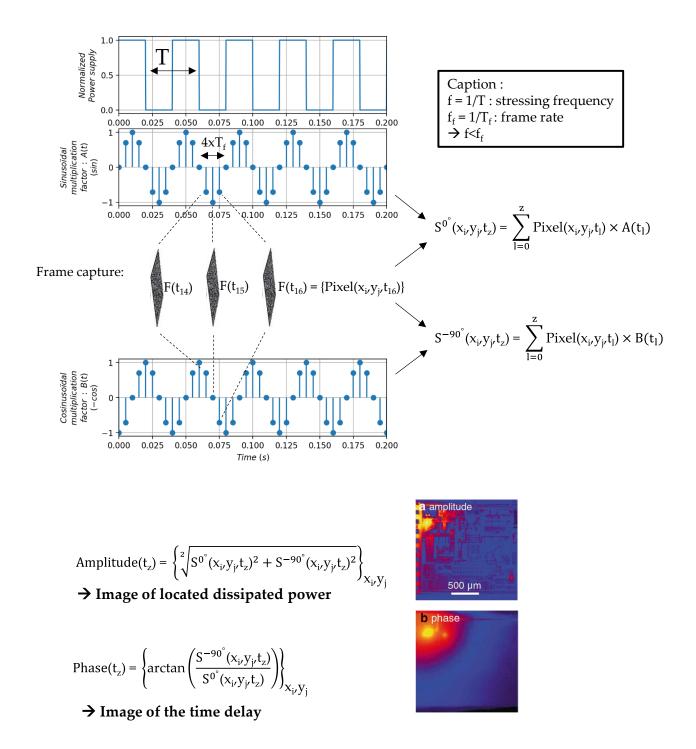

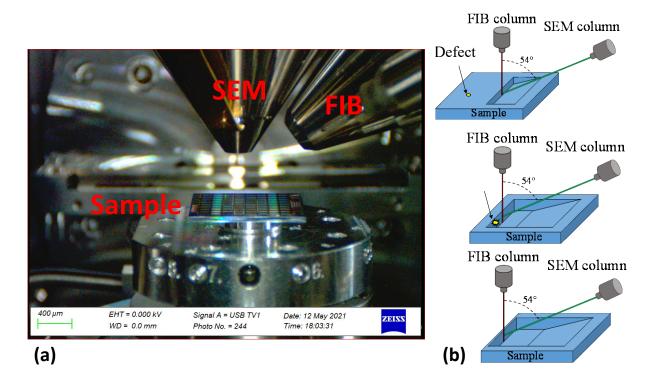

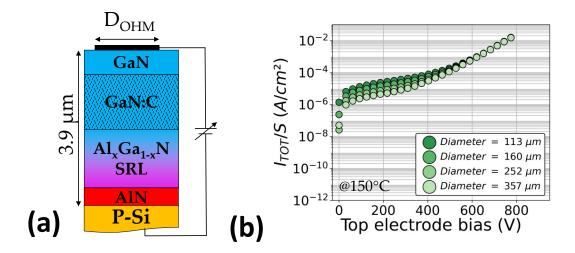

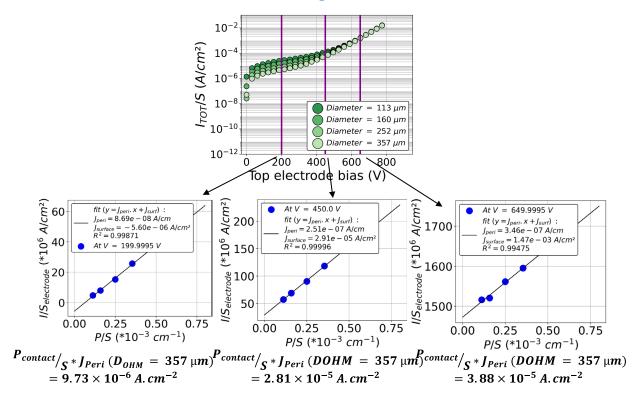

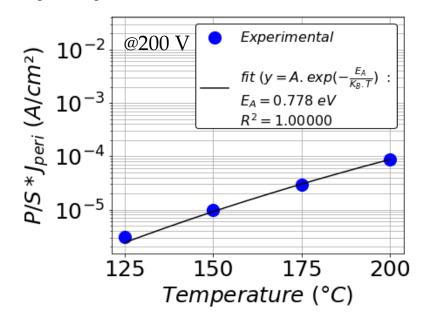

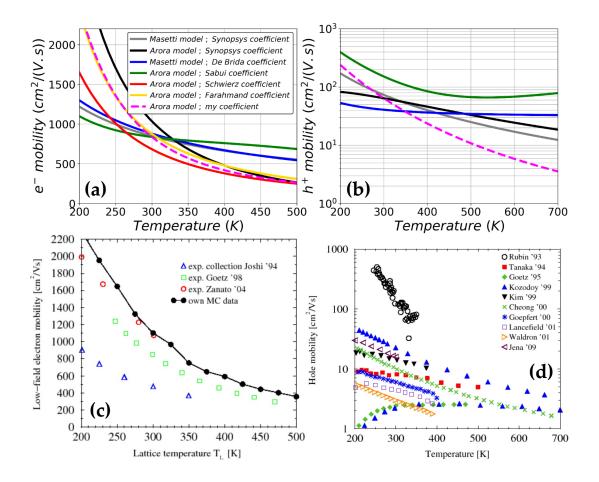

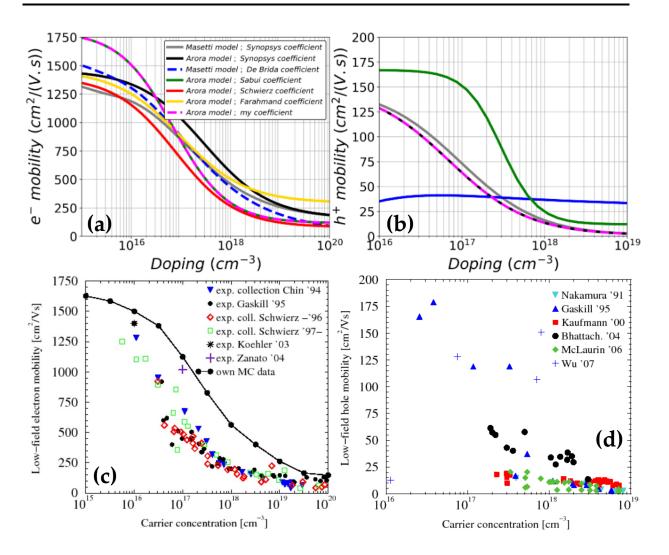

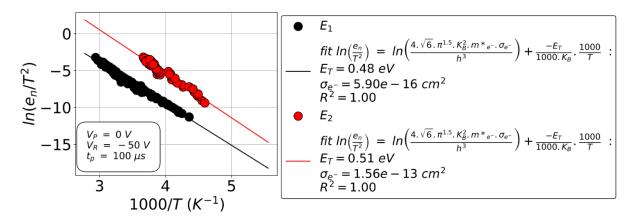

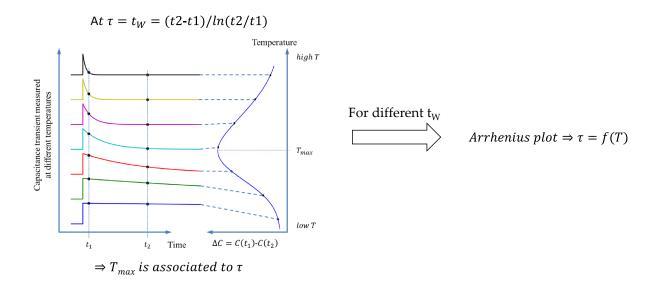

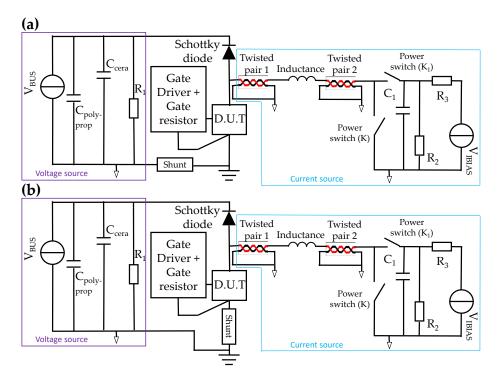

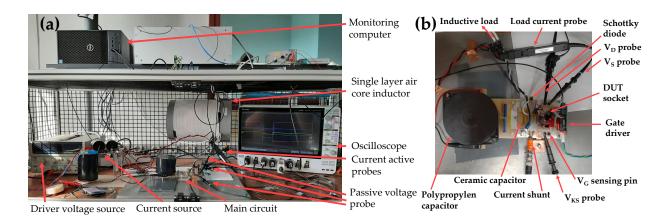

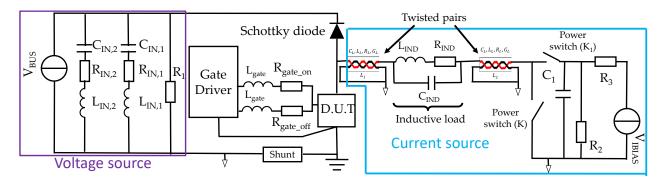

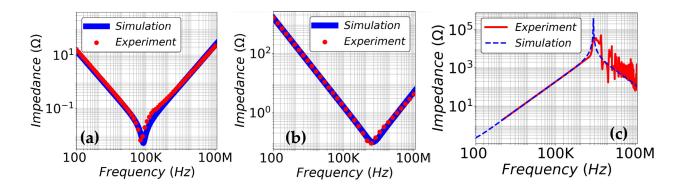

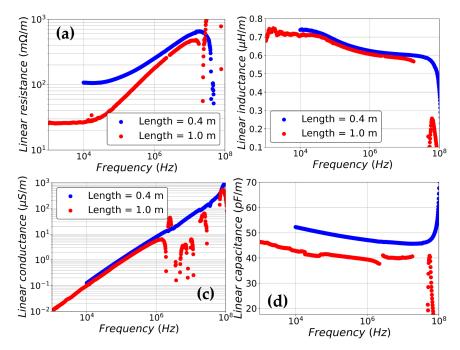

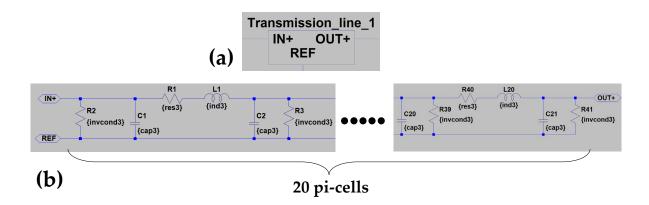

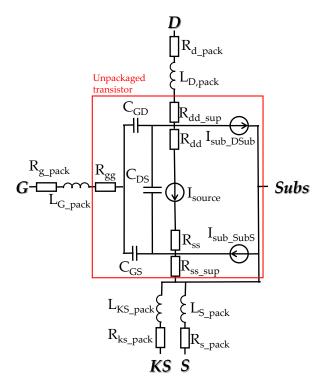

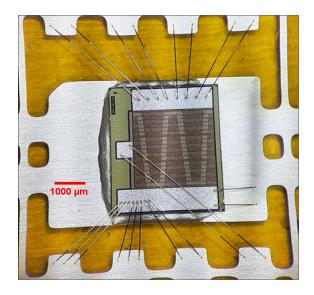

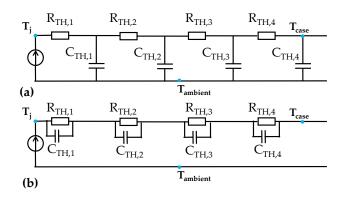

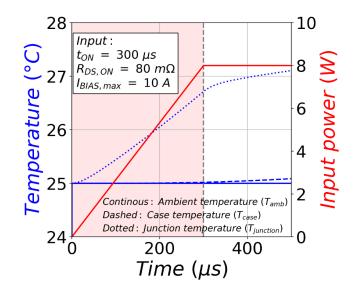

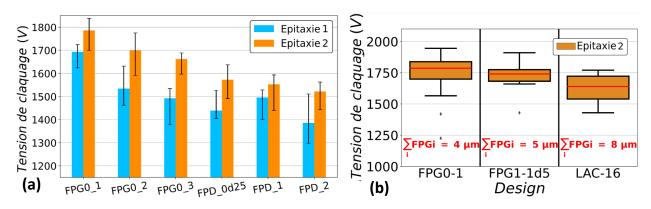

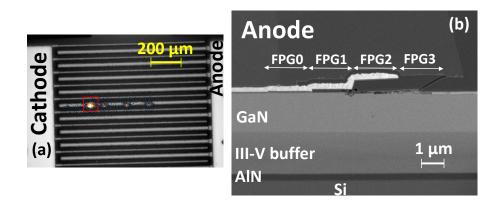

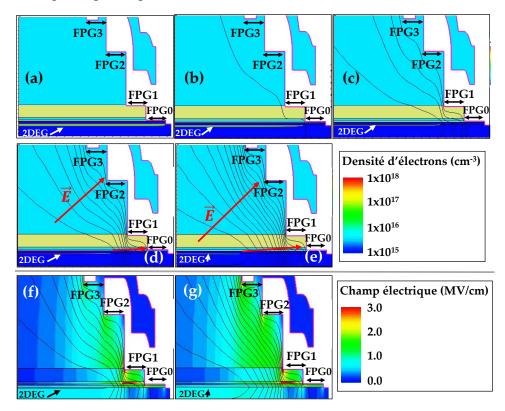

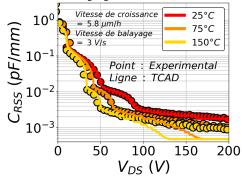

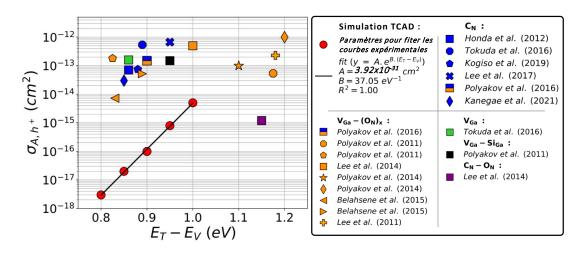

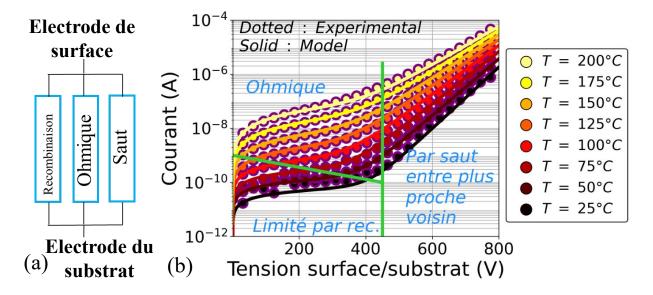

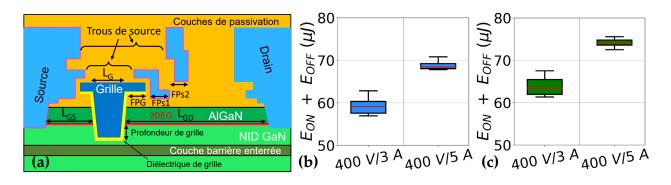

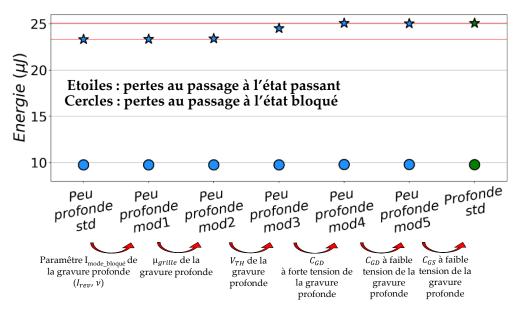

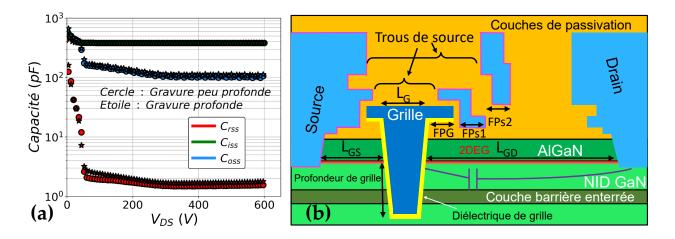

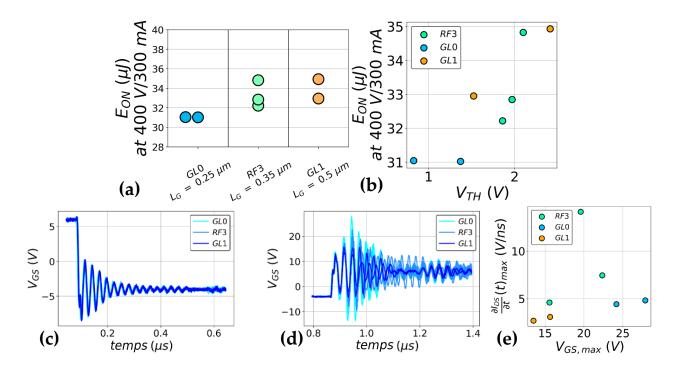

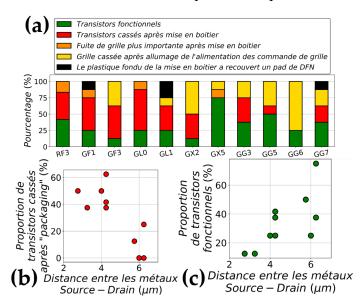

As shown in **Figure 4**, this crystalline structure is obtained by the interception of two hexagonal close-packed sub-lattices of Gallium and Nitrogen respectively having the same vertical axis (c-axis). This vertical axis is also the growth axis of lateral power devices to get the piezoelectric effect required to form the 2DEG. Moreover, two growth directions can be distinguished: N-faced growth directed by the  $[000\overline{1}]$  crystal vector as illustrated in **Figure 4(a)** for which the growth direction is the same as that of the spontaneous polarization vector and Ga-faced growth directed by the [0001] crystal for which the growth direction is opposite as that of the spontaneous polarization vector. Commercialized lateral power AlGaN/GaN devices and the devices studied in this manuscript use Ga-faced growth. The crystal parameters (a = 3.189 Å & c = 5.185 Å) were found using X-ray analysis by the Debye-Scherrer technique [21].