# Recognition of objects to grasp and Neuro-Prosthesis control

Attila Fejer

#### ▶ To cite this version:

Attila Fejer. Recognition of objects to grasp and Neuro-Prosthesis control. Machine Learning [cs.LG]. Université de Bordeaux; Pázmány Péter katolikus egyetem (Budapest; 1992-..), 2022. English. NNT: 2022BORD0301. tel-04213879

### HAL Id: tel-04213879 https://theses.hal.science/tel-04213879

Submitted on 21 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# DUAL DEGREE THESIS PRESENTED TO OBTAIN THE DEGREE OF

# DOCTOR OF PHILOSOPHY OF THE PÁZMÁNY PÉTER CATHOLIC UNIVERSITY

### AND

### THE UNIVERSITY OF BORDEAUX

ROSKA TAMÁS DOCTORAL SCHOOL OF SCIENCES AND TECHNOLOGY

DOCTORAL SCHOOL OF MATHEMATICS AND COMPUTER SCIENCE

SPECIALTY: COMPUTER SCIENCE

by

## Attila FEJÉR

## Recognition of objects to grasp and Neuro-Prosthesis control

Date of the defence: 25/11/2022

Before the review panel composed of:

| Jenny      | Benois-Pineau | Pr. | LaBRI, Université de Bordeaux         | Co-director of the thesis |

|------------|---------------|-----|---------------------------------------|---------------------------|

| Péter      | SZOLGAY       | Pr. | Pázmány Péter Catholic University     | Co-director of the thesis |

| Aymar      | DE RUGY       | Dr. | INCIA, Université de Bordeaux         | Examiner                  |

| Christophe | GARCIA        | Pr. | INSA de Lyon                          | Reviewer                  |

| Alexandre  | Benoit        | Pr. | University of Monblanc-Pays de Savoie | Examiner                  |

| László     | Czúni         | Dr. | Pannon University                     | Reviewer                  |

| Zsolt      | Vörösházi     | Dr. | Pannon University                     | Examiner                  |

| Janka      | Hatvani       | Dr. | Pázmány Péter Catholic University     | Examiner                  |

|            |               |     |                                       |                           |

The jury is chaired by: Pr. Alexandre BENOIT

#### Title

Recognition of objects to grasp and Neuro-Prosthesis control

#### Abstract

The goal of the present PhD research is to provide assistance to upper-limb amputees wearing robotic prosthetic arms. Classical myoelectric control of neuro-prostheses is limited in case of severe amputation. Computer vision approach and gaze information can provide a valuable indication for prosthetic arm control identifying and localizing an object to grasp.

The prosthetic arm controlling mechanism has to be wearable, fast enough for real-time processing, and mobile. Thus we propose an embedded Hardware-Software FPGA implementation of the gaze-driven object recognition method with a Gaze-Driven CNN developed for natural cluttered video scenes.

To achieve the research goal, we propose different algorithmic solutions adapted to FPGA. The whole embedded system allows for recognition and localization of the object-to-grasp in the 3D space.

To decide which block in the whole algorithmic chain needs to be accelerated on FPGA, and which can be processed by an embedded CPU, we first conduct complexity analysis in terms of computational time for the hybridization choices.

The acquisition device is Tobii eye-tracker glasses which the amputee is supposed to wear in an ergonomic scenario of vision-assisted neuroprosthetic control. Due to the distractors, filtering of gaze points with motion compensation from the past to the present frame is needed. To do this, the Scale Invariant Feature Transform (SIFT) keypoints are extracted in every frame and serve for homography estimation between frames. However, our measurements show that SIFT computational time is too high using just an embedded CPU. So we adopted a SIFT keypoint extractor to an FPGA having proposed a simplified SIFT extractor due to the FPGA resource restrictions. Our solution was compared to the fully SW implemented OpenSIFT. The experiments show that the two implementations yield practically the same result. Our implementation can process a 480px x 480 px image at 135 frames/second on the Xilinx ZCU 102 FPGA board.

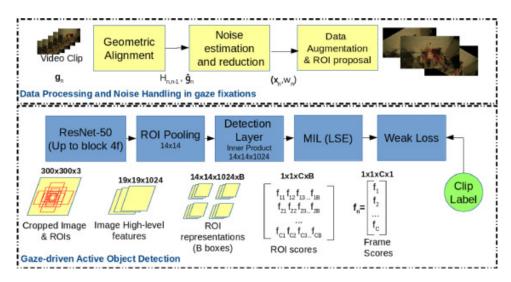

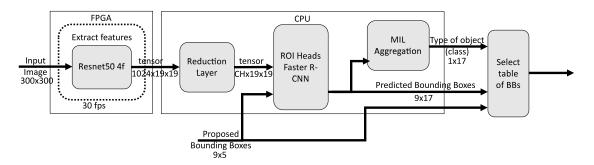

To eliminate the outlier gaze points corresponding to distractors which are projected to the current frame with the estimated homography, DBScan clustering is used. The fixated gaze point on the object to grasp is predicted with the Kernel Density Estimation. The estimated gaze point and the current frame are the input of the Gaze Driven CNN. Its goal is to recognize the object and precisely localize it in the video frame. The original CPU implementation of it contains three modules: Resnet50, Faster R-CNN and Multiple Instance Learning. Our Complexity analysis shows that the Resnet50 computational time is too high for the embedded CPU. Gaze-Driven CNN FPGA optimized version is thus built in the following modules: the Resnet50 (FPGA), which extracts the features from a frame, the Reduction

layer (CPU) to simplify the feature tensor, the Faster R-CNN (CPU) to estimate the grasped object location, and the Multiple Instance Learning (CPU) to predict the grasped object type. The FPGA accelerated Resnet50 can process more than 30 fps on ZCU102.

The depth is estimated based on the plane equation of the 3 closest gaze points to the current frame gaze point.

To validate our approach we have conducted our experiments on a real-world Open Source cluttered Grasping-in-the-Wild (GITW) dataset recorded in kitchens. The subjects are grasping common objects such as a pan, a bowl, etc. The dataset contains 16 different objects in 7 kitchens and 404 egocentric videos.

Our experiments show that the proposed hybrid solution allows achieving 8.5 fps frame rate without losing the accuracy of the original CPU implemented approach. Further acceleration by pipelining is achievable and remains in the perspective of the present work.

#### Keywords

deep learning, FPGA, Object Recognition

iv Attila Fejér

#### Titre

Reconnaissance des objets à saisir et contrôle d'un bras robotique pour l'assistance aux porteurs des neuro-prothèses

#### Résumé

L'objectif de la recherche doctorale est de fournir une assistance aux amputés des membres supérieurs portant des prothèses robotisés. Le contrôle myoélectrique classique des neuro-prothèses est limité en cas d'amputation sévère. L'approche de la vision par ordinateur et les informations sur le regard peuvent fournir une indication pour le contrôle de la prothèse en identifiant et en localisant un objet à saisir.

L'outil de contrôle doit être portable, suffisamment rapide pour un traitement en temps réel, et mobile. Nous proposons donc une implémentation matérielle et logicielle FPGA de la méthode de reconnaissance d'objets, avec un CNN guidé par le regard, développée pour les scènes vidéo naturelles encombrées.

Pour atteindre l'objectif de recherche, nous proposons différentes solutions algorithmiques adaptées au FPGA. L'ensemble du système embarqué permet la reconnaissance et la localisation de l'objet à saisir dans l'espace 3D.

Pour décider quel bloc de la chaîne algorithmique doit être accéléré sur FPGA, et lequel reste sur le CPU embarqué, nous effectuons d'abord une analyse de complexité en temps de calcul.

Le dispositif d'acquisition est constitué des lunettes eye-tracker Tobii que l'amputé est censé porter dans un scénario ergonomique de contrôle neuroprothétique assisté par la vision. En raison des distracteurs, il est nécessaire de filtrer les points de regard avec une compensation de mouvement des images antérieures à l'image courante. Pour ce faire, les points clés SIFT (Scale Invariant Feature Transform) sont extraits dans chaque image et servent à l'estimation de l'homographie entre les images. Cependant, nos mesures montrent que le temps de calcul de SIFT est trop élevé sur le CPU embarqué. Nous avons donc adapté un extracteur de points clés SIFT sur un FPGA en proposant un algorithme simplifié en raison des restrictions de ressources du FPGA. Notre solution a été comparée à l'implémentation entièrement logicielle d'OpenSIFT. Les expériences montrent que les deux implémentations donnent pratiquement le même résultat. Notre implémentation peut traiter une image de 480 px x 480 px à 135 images/seconde sur la carte FPGA Xilinx ZCU 102.

Pour éliminer les points de regard aberrants correspondant aux distracteurs, le clustering des points (DBScan) est appliqué. Le point de fixation du regard sur l'objet à saisir est prédit à l'aide de l'estimateur à noyau. Le point de regard estimé et l'image courante constituent l'entrée du CNN piloté par le regard. Son objectif est de reconnaître l'objet et de le localiser précisément dans l'image vidéo. L'implémentation originale du CPU contient trois modules : Resnet50, Faster R-CNN et Multiple Instance Learning. Notre analyse de la complexité montre que le temps de calcul de Resnet50 est trop élevé pour le CPU embarqué. La version FPGA optimisée du CNN est donc construite dans les modules suivants : le Resnet50

(FPGA), qui extrait les caractéristiques d'une image, la couche de réduction (CPU) pour simplifier le tenseur de caractéristiques, le Faster R-CNN (CPU) pour estimer la localisation de l'objet, et le Multiple Instance Learning (CPU) pour prédire le type d'objet saisi. Le Resnet50 accéléré par FPGA peut traiter plus de 30 images par seconde sur ZCU102.

La profondeur est estimée sur la base de l'équation du plan des 3 points de regard les plus proches du point de regard de l'image actuelle.

Pour valider notre approche, nous avons mené nos expériences sur un ensemble de données Open Source, Grasping-in-the-Wild (GITW), enregistrées dans des cuisines. Le jeu de données contient 16 objets différents dans 7 cuisines et 404 vidéos égocentriques.

Nos expériences montrent que la solution hybride proposée permet d'atteindre une fréquence d'images de 8,5 fps sans perdre la précision de l'approche originale implémentée sur CPU. Une accélération supplémentaire par pipelining est réalisable et reste dans la perspective du présent travail.

#### Mots-clés

l'apprentissage en profondeur, FPGA, reconnaissance d'objet

vi Attila Fejér

# Table of contents

| Li           | st of                 | Figures                                                         | 1  |

|--------------|-----------------------|-----------------------------------------------------------------|----|

| Li           | st of                 | Tables                                                          | 3  |

| $\mathbf{A}$ | ckno                  | wledgements                                                     | 7  |

| Li           | $\mathbf{st}$ of      | acronyms                                                        | 9  |

| Sı           | ımm                   | ary of the PhD dissertation in English                          | 13 |

| $\mathbf{R}$ | ésum                  | né de la thèse de doctorat en français                          | 18 |

| 1            | Intı                  | roduction                                                       | 24 |

| <b>2</b>     | Sta                   | te-of-the-Art in visual scene analysis for neuroprostheses con- |    |

|              | $\operatorname{trol}$ | s and FPGA implementation                                       | 28 |

|              | 2.1                   | Introduction                                                    | 28 |

|              | 2.2                   | Neuroprosthesis control based on visual and gaze information    | 30 |

|              | 2.3                   | Object recognition in visual scenes                             | 34 |

|              | 2.4                   | FPGA implementation of visual scenes analysis methods           | 37 |

|              | 2.5                   | Comparing different hardware for an embedded system from com-   |    |

|              |                       | puter vision point of view                                      | 44 |

|              | 2.6                   | Existing hybrid HW/SW solutions on FPGA                         | 45 |

|              | 27                    | Conclusion                                                      | 17 |

| 3 | Ana  | alysis of object-to-grasp recognition in view of FPGA based im- |     |

|---|------|-----------------------------------------------------------------|-----|

|   | plei | mentation                                                       | 50  |

|   | 3.1  | Introduction                                                    | 50  |

|   | 3.2  | Visual servoing of upper-limb prosthesis scenario               | 52  |

|   | 3.3  | Object-to-grasp recognition approach                            | 53  |

|   | 3.4  | Target FPGA board                                               | 64  |

|   | 3.5  | Critical analysis of computation complexity                     | 74  |

|   | 3.6  | Conclusion                                                      | 81  |

| 4 | Hyl  | brid solutions for SIFT detector implementation                 | 83  |

|   | 4.1  | Introduction                                                    | 83  |

|   | 4.2  | Base-Line SIFT algorithm                                        | 84  |

|   | 4.3  | Hybrid SIFT implementation                                      | 90  |

|   | 4.4  | Experiments and results                                         | 97  |

|   | 4.5  | Conclusion                                                      | 110 |

| 5 | Opt  | timized implementations of preprocessing steps                  | 111 |

|   | 5.1  | Introduction                                                    | 111 |

|   | 5.2  | Gaze point alignment                                            | 112 |

|   | 5.3  | Gaze point noise reduction                                      | 118 |

|   | 5.4  | Depth estimation                                                | 122 |

|   | 5.5  | Results                                                         | 125 |

|   | 5.6  | Conclusion                                                      | 132 |

| 6 | Hyl  | brid solutions for object recognition with Gaze-Driven CNN      | 134 |

|   | 6.1  | Introduction                                                    | 134 |

|   | 6.2  | Gaze-Driven CNN implementation                                  | 135 |

|   | 6.3  | Results                                                         | 140 |

viii Attila Fejér

#### TABLE OF CONTENTS

|              | 6.4   | Conclusion                       | . 147 |

|--------------|-------|----------------------------------|-------|

| 7            | Con   | nclusion                         | 149   |

|              | 7.1   | New scientific results           | . 149 |

|              | 7.2   | Perspectives                     | . 153 |

| Bi           | bliog | graphy                           | 155   |

| $\mathbf{A}$ | Pub   | olications related to the thesis | 173   |

|              | A.1   | Journal publications             | . 173 |

|              | A.2   | Conference publications          | 173   |

# List of Figures

| 2.1 | The bimodal information architecture (Fukuda et al., 2021)           | 32 |

|-----|----------------------------------------------------------------------|----|

| 2.2 | Example of the residual block in the ResNet                          | 34 |

| 3.1 | Example of the Tobii 2 glass camera usage                            | 52 |

| 3.2 | The prosthetic arm visually guided system                            | 54 |

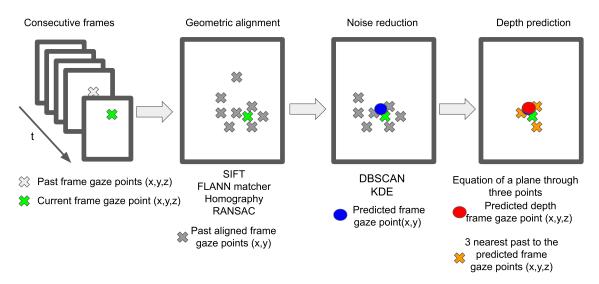

| 3.3 | Gaze-driven CNN for object recognition. Upper part: Preprocessing    |    |

|     | pipeline. Lower part: the Gaze Driven CNN on object proposals        |    |

|     | (González-Díaz et al., 2019)                                         | 56 |

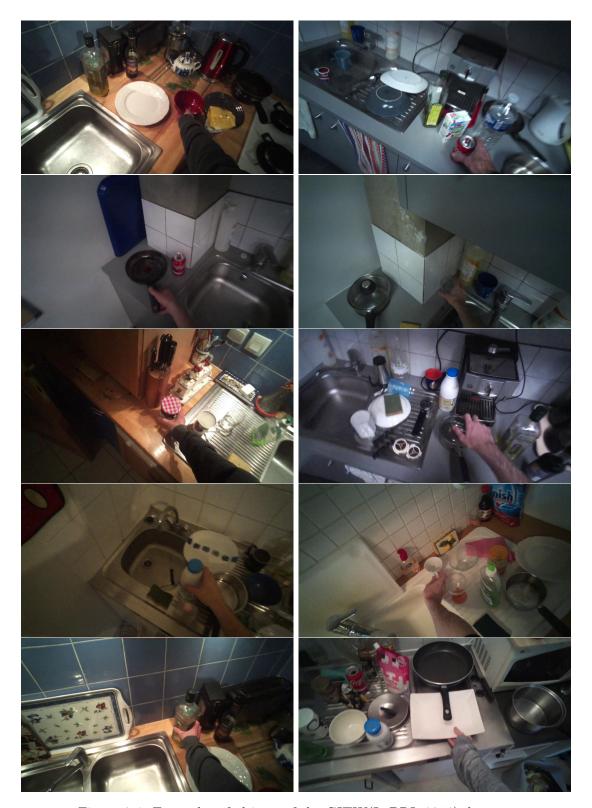

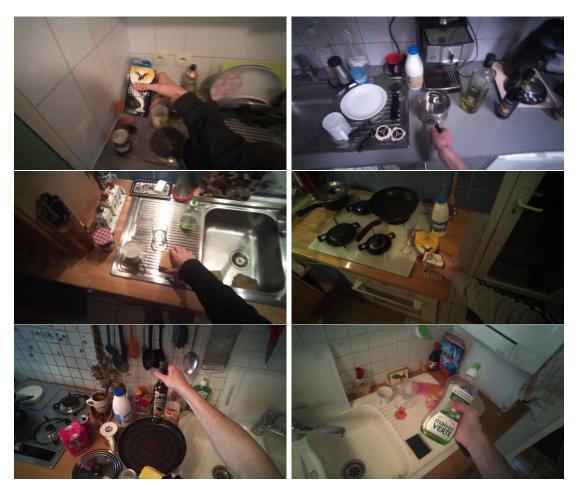

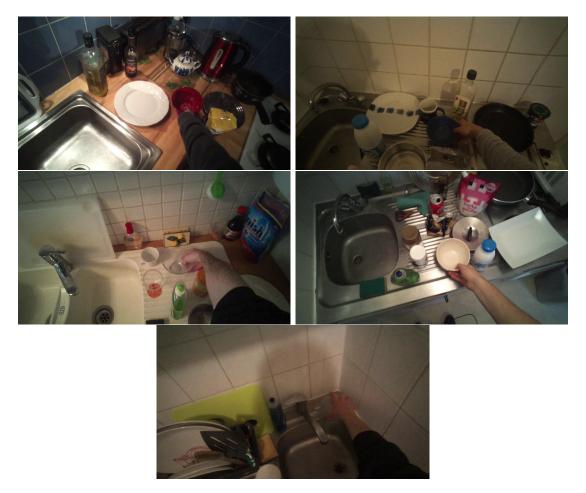

| 3.4 | Examples of objects of the GITW(LaBRI, 2016) dataset                 | 60 |

| 3.4 | Example object of the GITW LaBRI (2016) dataset                      | 61 |

| 3.5 | Example of the Bowl subset. It contains different bowls in different |    |

|     | kitchens                                                             | 63 |

| 3.6 | Example of non-cluttered and cluttered environment                   | 64 |

| 3.7 | Basic FPGA architecture                                              | 64 |

| 3.8 | Vitis AI quantization process Xilinx (2022c)                         | 74 |

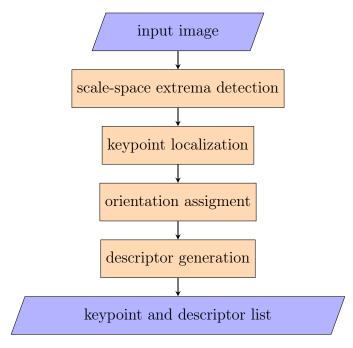

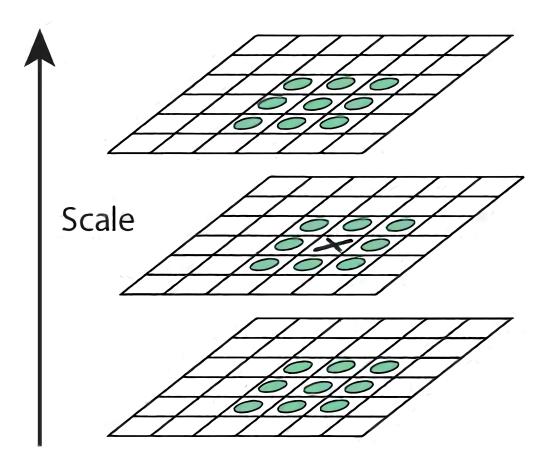

| 4.1 | The main steps of the SIFT(Lowe, 2004) algorithm                     | 85 |

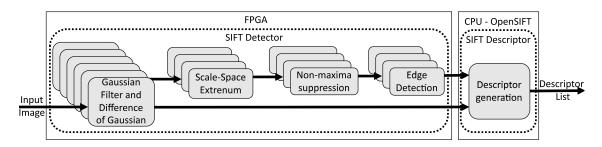

| 4.2 | The block diagram of our proposed architecture. The SIFT detector    |    |

|     | part contains the GFDG computation, SSE, NMS and Edge Detection      |    |

|     | modules. The SIFT descriptor part contains the orientation assign-   |    |

|     | ment and other descriptor computation steps                          | 91 |

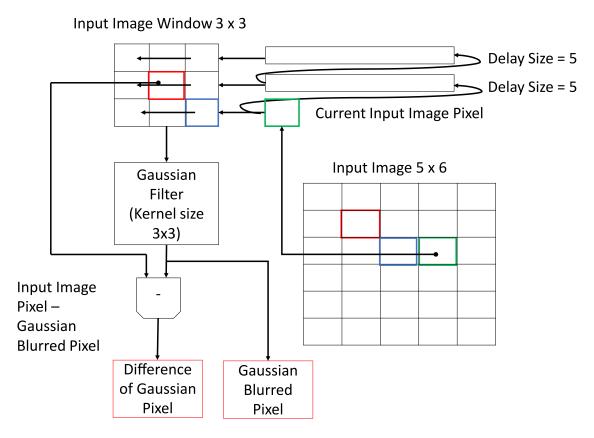

| 4.3 | Gaussian Filtering and Difference of Gaussians computation (GFDG).        |

|-----|---------------------------------------------------------------------------|

|     | The red rectangle is the current computed pixel. The green rectangle      |

|     | is the current input pixel from the input stream. Neighbours of the       |

|     | currently computed pixel are stored in the input image window. Two        |

|     | lines of the most recently used pixels are stored in the "temporary row   |

|     | delay arrays". Gaussian blurred image and the Difference of Gaussian      |

|     | image are the outputs of the module                                       |

| 4.4 | Calculate the local extremas in one scale (Lowe, 2004) 94                 |

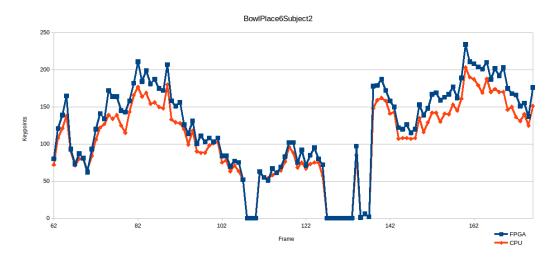

| 4.5 | Comparison between the OpenSIFT (Hess, 2010) and the FPGA im-             |

|     | plementation detected keypoints. Y-axis is the number of the ex-          |

|     | tracted keypoints, X-axis is the frame number. FPGA-detected key-         |

|     | points are in blue, CPU-detected keypoints are in red                     |

| 4.6 | Visual comparison of detected sets of keypoints. On the left: Open-       |

|     | SIFT (Hess, 2010) extracted keypoints. On the right: the FPGA             |

|     | result                                                                    |

| 5.1 | Example of bowl place 4 subject 2 gaze point alignment. The points        |

|     | are the gaze points                                                       |

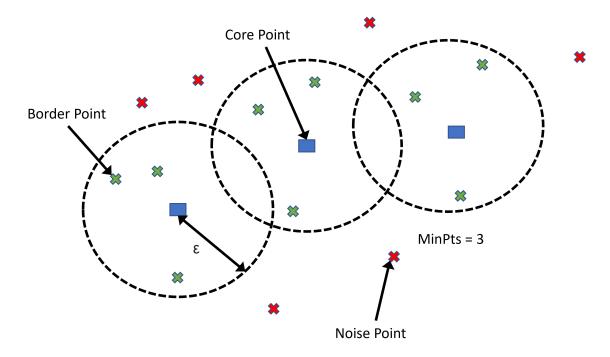

| 5.2 | Chain of the DBSCAN algorithm. The two parameters are the $\epsilon$ and  |

|     | the minPts                                                                |

| 5.3 | Bowl Place 5 Subject 2 DBSCAN parameters: $\epsilon = 0.01, min\_samples$ |

|     | = 3, good gaze points colour blue, outlier gaze points: green 121         |

| 5.4 | Example of bowl place 4 subject 2 KDE gaze point estimation. The          |

|     | points are the gaze points and the white point is the estimated gaze      |

|     | point                                                                     |

| 5.5 | Depth estimation chain                                                    |

|     |                                                                           |

#### LIST OF FIGURES

| 6.1 | Gaze-driven, object-recognition CNN, where $CH$ is the number of                |

|-----|---------------------------------------------------------------------------------|

|     | output channels of the Reduction Layer                                          |

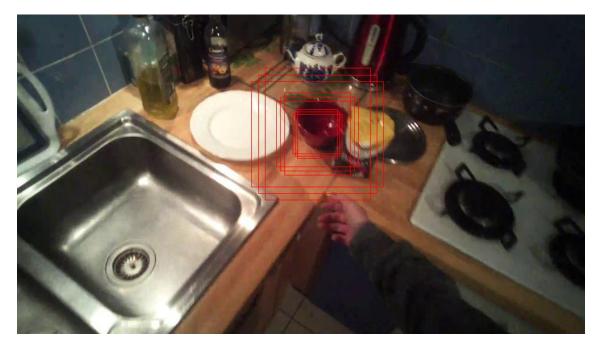

| 6.2 | Example of "Bowl place 1, subject 1", (GITW) generated bounding                 |

|     | box. The bounding boxes are generated around the red bowl 137                   |

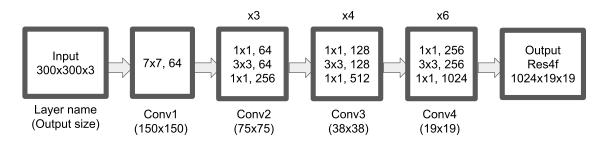

| 6.3 | ${\rm ResNet50~res4f}$ architecture, shown with the residual units, the size of |

|     | the filters and the outputs of each convolutional layer. Downsampling           |

|     | is performed by $conv2_1$ , $conv3_1$ , and $conv4_1$ with a stride of 2 137    |

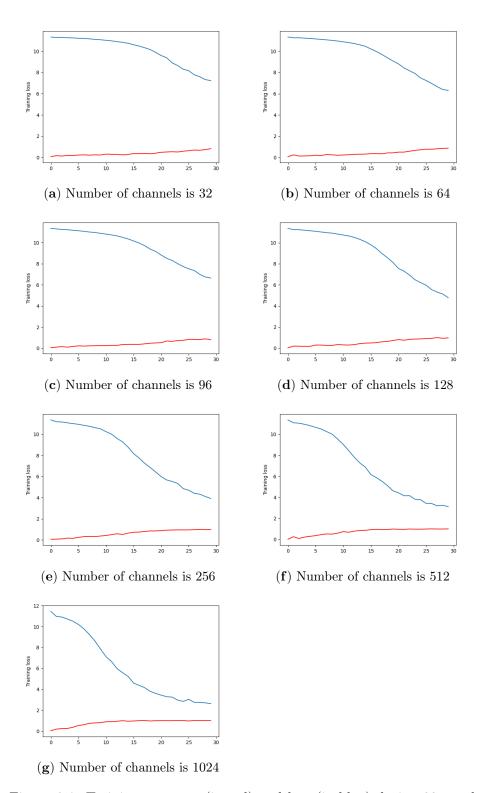

| 6.4 | Training accuracy (in red) and loss (in blue) during 30 epochs with             |

|     | different number of channels due to Reduction Laver                             |

# List of Tables

| 3.1 | Bowl subdataset overview                                             | 62  |

|-----|----------------------------------------------------------------------|-----|

| 3.2 | Xilinx Zynq UltraScale+ ZCU102 programmable logic resources          | 66  |

| 3.3 | The average computational time measurement of the whole system on    |     |

|     | a regular computer and an embedded system. The goal is a system      |     |

|     | which can process a frame less than 100ms and each module maxi-      |     |

|     | mum computation time should be less than 40ms. The SIFT, KDE         |     |

|     | estimation, ResNet50, and the Faster R-CNN computation times are     |     |

|     | too high for real-time processing.                                   | 76  |

| 3.4 | Hybridization of preliminary steps in the pipeline, which contains   |     |

|     | two main blocks: Gaze Point Alignment Block and Gaze Point Noise     |     |

|     | Reduction Block and its submodules                                   | 80  |

| 3.5 | Hybridization of the gaze-driven CNN                                 | 80  |

| 4.1 | The default parameter list in experiments                            | 101 |

| 4.2 | Comparison of the number of keypoints in case of OpenSIFT (CPU)(Hess | ,   |

|     | 2010) and our FPGA implementations. P is the Precision and R is      |     |

|     | the Recall                                                           | 102 |

| 4.3 | The average recall in case of different NMS threshold values. The    |     |

|     | red column is when the NMS threshold was set to 0.01. The average    |     |

|     | recall is higher than 0.9 when the threshold is 0.01                 | 104 |

| 4.4 | The average precision in case of the different NMS threshold values.             |

|-----|----------------------------------------------------------------------------------|

|     | The red column is when the NMS threshold was set to 0.01. The                    |

|     | average precision is higher than 0.81 when the threshold 0.01 104                |

| 4.5 | The average number of KPs extracted in case of different NMS thresh-             |

|     | old values. The red column shows when the NMS threshold is set to                |

|     | 0.01. The number of extracted KPs are computed just using the first              |

|     | octave of the Gaussian pyramids                                                  |

| 4.6 | 1octave resource usages on Xilinx ZCU102 FPGA Board from Vivado                  |

|     | $2018.3$ (Xilinx, $2018\mathrm{b})$ when the default parameters in Table 4.1 has |

|     | been used                                                                        |

| 4.7 | Resource usage estimation of the main modules of the system based                |

|     | on the Vivado HLS report                                                         |

| 4.8 | Comparison of SIFT keypoint extraction in different platforms. The               |

|     | Intel Xeon E5-2620 and ARM Cortex-A53 are used the OpenSIFT<br>(Hess, $$         |

|     | 2010) to extract the keypoint. The Xilinx UltraScale+ ZCU102 are                 |

|     | used our FPGA implementation to extract the keypoint. All three                  |

|     | platform which used OpenSIFT are used with the default parameters                |

|     | (Table 4.1). On the CMOS Vision Sensor, only the time for Gaussian               |

|     | Pyramid calculation is reported. In the case of NVIDIA Jetson TX                 |

|     | 2 the computation time is based on the report of da Costa Barreiros              |

|     | (2020)                                                                           |

| 4.9 | Comparison of our work with different FPGA implementations 110                   |

| 5.1 | Comparison between the Intel i5 7300HQ and the Xilinx ZCU102                     |

|     | ARM CORTEX A53 in the whole gaze alignment chain 127                             |

|     |                                                                                  |

| 5.2 | Comparison in processing time of kernel density estimation module                       |

|-----|-----------------------------------------------------------------------------------------|

|     | between the Intel i5 7300<br>HQ and the Xilinx ZCU102 ARM CORTEX                        |

|     | A53                                                                                     |

| 5.3 | Average computational time of the KDE after 100 iterations on the                       |

|     | Xilinx ZCU 102 Embedded ARM CPU. The gaze points number is                              |

|     | 10 and the size of the area is given                                                    |

| 5.4 | DBSCAN without setting the gaze point maximum number to 10 130                          |

| 5.5 | DBSCAN with gaze point maximum number set to 10 130                                     |

| 5.6 | $\mathrm{KDE} + \mathrm{DBSCAN}$ with removed outliers (Gaze Points area size ${<}4900$ |

|     | px), DBSCAN parameters: $\epsilon$ =0.05, $min\_samples$ =5 131                         |

| 6.1 | Measurements of the gaze-driven, object-recognition CNN in the In-                      |

|     | tel i5 7300 CPU. The first column contains the reaming number of                        |

|     | channels after the Reduction Layer. Each column shows the elapsed                       |

|     | time during the computation in milliseconds                                             |

| 6.2 | Measurements of the gaze-driven, object-recognition CNN in the ARM                      |

|     | A53 CPU. The first column contains the remaining number of the                          |

|     | channels after the Reduction Layer. Each column shows the elapsed                       |

|     | time during the computation in milliseconds                                             |

| 6.3 | The results of the training and testing after 30 epochs                                 |

| 6.4 | Comparison of different object recognition CNNs. All the measure-                       |

|     | ments were taken by Vitis AI 1.4. The gaze-driven, object-recognition                   |

|     | CNN used 128 channels in the Reduction Layer                                            |

| 6.5 | The average computational time measurement of the whole system                          |

|     | on different hardware. The ResNet50 number of channels is 128 146                       |

## Acknowledgements

This thesis was facilitated by the co-tutelle agreement between the Pázmány Péter Catholic University of Budapest and the University of Bordeaux – in particular with Laboratoire Bordelais de Recherche en Informatique (LaBRI).

I think doing a PhD alone is impossible, and I am lucky because I have met the right people who helped me during this period.

I would like to thank my supervisors Jenny Benois-Pineau, Péter Szolgay, Aymar de Rugy and Zoltán Nagy.

I have learnt a lot from Zoltán Nagy about the developing an algorithm on FPGA. He also helped me with teaching, and he gave me insightful tips on writing scientific papers. He was available at any time and answered all my questions I had during my Phd journey.

I am extremely thankful that I had the opportunity to do my PhD studies at the University of Bordeaux with Jenny Benois-Pineau. She made my last few years easier by not only guiding through my studies but also helping me with my integration in Bordeaux. She helped me writing the conference and journal papers, while also was available in times where I had difficulties and i required some help.

Aymar de Rugy helped me with his expert knowledge about the neuroprosthetic arm and reviewed my English in the scientific papers.

Péter Szolgay gave me many insightful tips on how to organize my time when I am writing a scientific paper. He also helped me to earn scholarships during my Phd.

I acknowledge a grant from the Institut Français en Hongrie.

I am grateful for the help of both doctoral schools, the Roska Tamás Doctoral School and the École doctorale Mathématiques et informatique de l'université de Bordeaux. I would like to thank to Tivadarné Vida (Katinka néni) the help of the administrative tasks.

I appreciate the scientific remarks of my thesis follow-up committee Pascal Desbarats and Akka Zemmari.

Big thanks to my friends and collages in LaBRI, Association de la Formation Doctorale d'Informatique de Bordeaux, and Pázmány Péter Catholic University, with whom I work, drink coffee and tea, talk and discuss things in the kitchen, travel, and helping me during the COVID-19 situation, present with, and made my PhD experience rewarding: Pierre-Etienne Martin, Dániel Hajtó, Miklós Tóth, András Attila Sulyok, Zoltán Horváth, János Vincze, Thinhinane Yebda, Thi Trang Ngo, Karim Adherhal, Karim Alami, Soumyajit Paul, Varun Ramanathan, Sougata Bosa, Tidiane Sylla, Abdennour Rachedi, Badreddine Yacine Yacheur, Miltiadis Poursanidis.

I would like to say a big thank you to Dániel Hajtó for being my friend and for his patience to explain me things, travelling with me, and share his opinion with me.

Also, thanks to My Family for encouraging me and believing me throughout my university study period even in the darkest times. Special thanks to My Brother Andris who helped me endlessly correct my grammatical mistakes and my baroquestyle sentences.

# List of acronyms

AR augmented reality 29, 32, 33

**AXI** Advanced eXtensible Interface 68–70

**BB** bounding box 3, 35, 54, 55, 57, 58, 62, 75, 76, 122, 131–133, 135–137, 139, 140, 146, 147, 150, 151

**BRAM** block RAM 66, 69, 106, 107, 152

BRIEF Binary Robust Independent Elementary Feature 33, 40

CNN convolutional neural network 1, 3, 4, 6, 17, 23, 26, 27, 31, 32, 34, 35, 37, 44, 45, 48, 49, 51, 55, 56, 58, 78–80, 110, 111, 133–136, 142, 143, 145, 147, 149, 150

**DBSCAN** Density-Based Spatial Clustering of Applications with Noise 2, 6, 78, 112, 118–121, 125, 129–133, 146

**DNN** deep neural network 24, 26

**DoG** Difference of Gaussians 41, 86, 87, 91, 92, 94–97

DSP digital signal processing 65, 66, 106, 107, 152

**ED** Edge Detection 1, 90, 91, 106, 107

EMG electromyographic 24, 31–33

**FF** flip-flop 65, 66, 106, 107, 152

FINN Framework for Fast, Scalable Binarized Neural Network Inference 30, 37, 38

**FLANN** Fast Library for Approximate Nearest Neighbours 27, 33, 76, 112, 114, 116, 125, 126, 132, 146

**FP** Feautre Pyramid 139

**FPGA** Field-Programmable Gate Array 1, 2, 4, 5, 7, 17, 22, 23, 25–27, 30, 37–40, 42–49, 51, 64–67, 71, 72, 77–81, 83, 84, 89, 90, 92, 95, 96, 98–103, 106–110, 132, 133, 135, 142, 146–153

FPN Feature Pyramid Network 139

**fps** frames per second 41–43, 53, 55, 61, 75, 110, 126, 128, 129, 132, 133, 141, 142, 145–148, 150, 151

**GFDG** Gaussian Filtering and Difference of Gaussians computation 1, 2, 90–94, 98, 106, 107

**GITW** Grasping In The Wild 1, 36, 48, 51, 58, 60–62, 81, 90, 97, 115, 130–132, 141, 145

**GP** gaze point 6, 78, 130–132

HW/SW hardware/software 46, 47, 77, 89, 90, 110, 152

**IP** intellectual property 68–70, 72, 73, 106

**KDE** Kernel Density Estimation 2, 4, 6, 27, 56, 75–78, 80, 112, 118, 119, 121, 122, 125, 128, 129, 131–133, 145, 146

**KP** keypoint 2, 4, 5, 26, 27, 40, 41, 43, 48, 75, 77, 78, 83, 85–88, 90, 94–97, 99–103, 105, 108, 110–113, 116, 125–127, 132, 151–153

LaBRI Laboratoire Bordelais de Recherche en Informatique 7, 8, 26, 150

**LUT** lookup table 65, 66, 69, 106, 107, 152

mAP mean average precision 36, 48

MIL Multiple Instance Learning 27, 58, 75, 76, 80, 135, 137, 140, 146, 147, 150

MPSoC multiprocessor system on a chip 45, 65–67, 73, 81

ms millisecond 4, 6, 25, 32, 41, 43, 55, 75–77, 90, 114, 127–129, 131, 132, 142, 143, 146, 148, 151, 152, 154

MSE mean squared error 50

mW milliwatt 107, 108

NMS Non-maximum Supression 1, 4, 5, 89–91, 95, 101–107, 152

ORB Oriented FAST and Rotated BRIEF 33, 40, 48, 83

**PL** programmable logic 4, 66, 67, 69, 71, 81

**PS** processing system 66, 67, 69, 80, 81

**R-CNN** Region-based Convolutional Neural Network 4, 27, 30, 34–36, 48, 55, 57, 72, 75–77, 80, 81, 134–137, 139, 140, 146, 147, 150, 151

RANSAC RANdom SAmple Consensus 33, 42, 112, 117, 132

**ResNet** Residual Network 1, 3, 4, 6, 27, 30, 34–36, 48, 57, 72, 73, 75–77, 80, 135–138, 142, 146, 147, 150, 151

**RL** Reduction Layer 3, 6, 27, 80, 135, 136, 138, 139, 142–147, 150, 151

**ROI** region of interest 57, 136, 139, 142, 143

RTL register-transfer level 67–70, 81

SIFT Scale-Invariant Feature Transform 1, 4, 5, 17, 23, 26, 27, 37, 40–43, 48, 63, 75–78, 80, 81, 83–85, 87–91, 95–97, 99, 100, 103, 106–114, 125–127, 132, 133, 146, 149–153

**SoC** system on chip 44, 45, 70–72

**SOTA** state-of-the-art 25, 26, 28, 30, 34, 109, 145

SSD Single-Stage Object Detection 30, 34, 36, 48, 72, 73, 134, 145

SSE Scale-Space Extrema Search 1, 90–92, 106, 107

SURF Speeded-Up Robust Features 40, 48, 83

VGG Visual Geometry Group 30, 34–36, 48, 72, 73

VR virtual reality 29–31, 33

VTA Versatile Tensor Accelerator 30, 37, 39

W Watt 41, 67, 75, 77, 107, 108, 110, 146, 153

**YOLO** You Only Look Once 30, 34, 36, 48, 72, 134, 145

# Summary of the PhD dissertation in English

Today, the use of a prosthetic arm has become an accessible and convenient tool for people who have lost their upper limbs due to an unfortunate accident. Technological advancements lead to the development of more comfortable and suitable prosthetic, making the user life easier and more convenient. Our vision is to further enhance the quality of arm prosthetic using visual information which aids its performance tackling everyday problems. In order to keep the lightweight of this system, our visual controlling mechanism must be suitable to wear and allow real-time processing while it should not limit the mobility of the artificial limb. Carefully examining these requirements, we have decided to develop the controlling mechanism in FPGA. This is an open problem and there are intensive research activities in this area.

The visual control program was proposed in previous works of LABRI and has several individual parts. It works on a regular computer. Our goal is to accelerate those algorithms to achieve the real-time processing speed.

It is a complex computer vision, image processing and a robotic problem, because we have to find the object, which the user wants to grasp. This part is the computer vision and image processing task. We also want to control the robotic arm to help the user to grasp this object, which is the robotic problem.

In this dissertation, we discuss the State-of-the-art methods (SOTA) of the visual-guided neuroprostheses control, the object recognition and the FPGA im-

plementation of visual scenes analysis methods. Thus, our system is compared to other SOTA solutions.

Hence, we propose a visual guided system to help control a neuroprosthesis arm.

The Tobii eye-tracker camera is the acquisition device. The user can wear this camera as a glass. The device can record an egocentric view video. The recorded video resolution is Full HD ( $1920 \times 1080$ ) with 25 fps. It can also record the user gaze fixations showing the location of the user' gaze looking in a frame, and the distance between the object of interest and the camera in millimeter precision.

"Grasping-in-the-wild" dataset developed in LABRI was used in our research. This dataset contains real-world video recordings in different kitchens, so the recordings vary. It is an Open dataset freely available for research at Nakala CNRS server. The videos are recorded in an egocentric view when a user is grasping a kitchen equipment. There are 16 different kinds kitchen equipment/objects in this dataset such as bowl, can of coke, milk bottle, and so on. The dataset contains 404 videos with the average duration around 10 seconds. The videos have different complexity from the computer vision point of view, but all remain "natural" and thus complex for an automatic analysis. The environment can be cluttered, because there are multiple objects in a real-world kitchen. Thus, the equipment can be transparent, such as a glass or bottle. The dataset contains the egocentric view videos and the user gaze fixation coordinates.

Our experiments show that a pure software implementation of algorithms is not fast enough to control a neuroprosthetic arm in real time. An ideal solution for this problem should be able to process the data in real-time. The power consumption of the device has to be very low, as the user has to wear it during his natural activities. The Field-Programmable Gate Arrays (FPGA) satisfy those requirements.

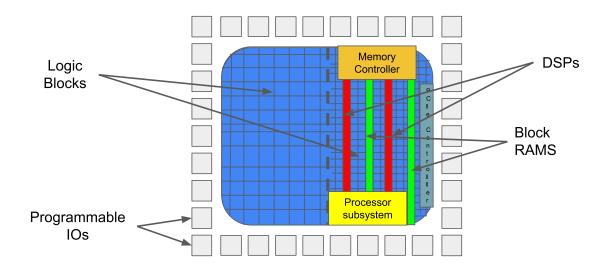

The Xilinx Zyng UltraScale+ MPSoC ZCU102 board has been chosen as a target

development device. This board is ideal to accelerate computer vision algorithms.

The XCZU9EG FPGA device on the ZCU102 board has a Processing System (PS) and a Programmable Logic (PL) part. The PS part has a quad-core ARM Cortex-A53, dual-core Cortex-R5F real-time processors, and a Mali-400 MP2 graphics processing unit. The Cortex-A53 is an Application Processing Unit (APU) to run OS and general purpose applications. The ZCU102 has a Zynq UltraScale+XCZU9EG-2FFVB1156 MPSoC chip. The Cortex-A53 is an ARM v8 architecture-based 64-bit quad-core multiprocessing CPU. The Cortex-R5 is a Real-time Processing Unit (RPU) and is based on an ARM v7 architecture 32-bit RPU with a dedicated tightly coupled memory (TCM). The Mali-400 is a graphics processing unit with pixel and geometry processor and 64 KB L2 cache.

PL resources of ZCU102 are the following: it has 912 Block RAM (BRAM), 548160 flip-flops (FF), 2520 digital signal processing (DSP) units, and 274080 Look-up tables (LUT).

To control a prosthetic arm for the amputees, we proposed a hybrid hardware-software solution. The system main components are the following: Recording the frames and gaze points with Tobii eye-tracker, gaze points alignment, gaze points noise reduction, bounding boxes generation around the noise reduced gaze points, object detection with the Gaze Driven CNN. More information about each component could be found in the next paragraphs.

The Tobii eye-tracker records the user gaze points and an egocentric video.

User gaze points can contain noise due to the distractors and microsaccades. Thus we wish to collect amm the gaze points in the current frame and estimate the smooth position of the gaze fixation in the current video frame. Thus the next step is the gaze points alignment. We wish to perform it with a homography model; The latter can be built by matching characteristic points of the visual scene. Thus, first

we need to extract the Scale-Invariant Feature Transform (SIFT) keypoints of every consecutive frames in a temporal window we wish to use for estimation of smoothed gaze point position in the current frame. Our measurements show that SIFT Lowe (2004) was one of the slowest parts of our method for the experimental system.

Having the SIFT keypoints the next step is the FLANN matching. There is a reference image which we compare the reference image-10, reference image-..., reference image-1 images and put them in the same plane. After that we can compute the homography matrix with matched key-points, and project all the gaze points from the temporal window in the current video frame.

In the gaze-point noise reduction, the goal is to filter out the outlier gaze points. The outlier gaze points may be caused by the saccades, and the head movements, when the user tries to find to object or get distracted during the process of grasping. The DBScan clustering removes the outlier gaze points and the Kernel Density Estimation (KDE) uses the remained aligned gaze points and estimate the smoothed location of the gaze point.

Bounding boxes are then generated around the estimated gaze point. The classification of these bounding boxes accordingly to our object taxonomy will give a precised location of the object-to-grasp and its type. There are 9 bounding boxes generated with different scales and sizes where the center point is the estimated gaze point.

The Gaze Driven CNN is predicting the object type and the object location. Inputs of this CNN are the nine bounding boxes and the current video frame.

The object type is necessary. Indeed, in grasping process, it is important to know the shape and the surface quality of the object. In our current work we have not studied the palm opening control as a function of the object shape, but prepared a good basis for this next step of the prosthesis control.

To summarize, in this PhD research, we have developed a full solution for object recognition with Deep NNs in ego-centered video on a hybrid architecture using FPGA. The solution is guided by gaze fixation recordings from the eye-tracker and is designed for visual servoing of the upper limb neuroprostethic arms. In the following, we summarize the contributions.

My scientific results are two-fold:

- 1. I developed a hybrid solution: FPGA-CPU for object recognition in egocentered video by a Gaze-Driven CNN.

- 2. As a re-usable part of it I have implemented, on FPGA, a new SIFT detector for pre-processing of gaze data, namely their alignment in the current video frame.

# Résumé de la thèse de doctorat en français

Aujourd'hui, l'utilisation d'un bras prothétique est devenue un outil accessible et pratique pour les personnes qui ont perdu leurs membres supérieurs à la suite d'un accident malheureux. Les progrès technologiques conduisent au développement de prothèses plus confortables et plus adaptées, rendant la vie de l'utilisateur plus facile et plus pratique. Notre vision est d'améliorer encore la qualité des prothèses de bras en utilisant des informations visuelles qui aident leurs performances à résoudre les problèmes quotidiens. Afin de conserver la légèreté de ce système, notre mécanisme de contrôle visuel doit être adapté au port et permettre un traitement en temps réel, sans pour autant limiter la mobilité du membre artificiel. En examinant attentivement ces exigences, nous avons décidé de développer le mécanisme de contrôle en FPGA. Il s'agit d'un problème ouvert et unhe recherche intense est menée dans ce domaine.

Une approche de contrôle visuel a été proposé dans des travaux précédents du LABRI. Elle comporte plusieurs étapes. L'implantationfonctionne sur le CPU/GPU d'un ordinateur banalisé. Notre objectif est d'accélérer ces algorithmes pour atteindre la vitesse de traitement en temps réel.

C'est un problème complexe de vision par ordinateur, de traitement d'image et de robotique, car nous devons reconnaître et localiser dans la vidéo, l'objet que l'utilisateur veut saisir. Cette partie est la tâche de vision par ordinateur et de

traitement d'image. Nous voulons également contrôler le bras robotique pour aider l'utilisateur à saisir cet objet, ce qui constitue le problème robotique.

Dans cette thèse, nous discutons des méthodes de l'état de l'art (SOTA) du contrôle des neuroprothèses guidées visuellement, de la reconnaissance des objets et de l'implémentation FPGA des méthodes d'analyse des scènes visuelles. Ainsi, notre système est comparé à d'autres solutions SOTA.

Nous proposons donc un système à guidage visuel pour aider à contrôler un bras robothique de neuroprothèse.

La caméra de l'eye-tracker Tobii est le dispositif d'acquisition. L'utilisateur peut porter cette caméra sur les lunettes. L'appareil peut enregistrer une vidéo en vue égocentrique. La résolution vidéo enregistrée est Full HD (1920 × 1080) avec 25 fps. Il peut également enregistrer les fixations du regard de l'utilisateur en montrant l'emplacement du regard de l'utilisateur dans l'image vidéo, et la distance entre l'objet d'intérêt et la caméra avec la précision millimétrique.

Le jeu de données "Grasping-in-the-wild" développé au LABRI a été utilisé dans notre recherche. Ce jeu de données contient des enregistrements vidéo des scènes réelles dans différentes cuisines, les enregistrements varient. Il s'agit d'un jeu de données ouvert disponible librement pour la recherche sur le serveur Nakala du CNRS. Les vidéos sont enregistrées dans une vue égocentrique lorsqu'un utilisateur saisit un ustensile de cuisine. Il y a 16 différents types d'ustensiles/objets de cuisine dans ce jeu de données, comme un bol, une canette de coca, une bouteille de lait, etc. L'ensemble de données contient 404 vidéos d'une durée moyenne d'environ 10 secondes. Les vidéos ont une complexité différente du point de vue de la vision par ordinateur, mais toutes restent "naturelles" et donc complexes pour une analyse automatique. L'environnement peut être encombré, car il y a de multiples objets dans une cuisine dnas la vie quotidienne. Ainsi, l'obet peut être transparent, comme un

verre ou une bouteille. Le jeu de données contient les vidéos de la vue égocentrique et les coordonnées de fixation du regard de l'utilisateur.

Nos expériences montrent qu'une implémentation purement logicielle des algorithmes n'est pas assez rapide pour contrôler un bras neuroprothétique en temps réel. Une solution idéale pour ce problème devrait être capable de traiter les données en temps réel. La consommation d'énergie du dispositif doit être très faible, car l'utilisateur doit le porter pendant ses activités naturelles. Les réseaux de portes programmables en champ (FPGA) répondent à ces exigences. La carte Xilinx Zynq UltraScale+ MPSoC ZCU102 a été choisie comme dispositif de développement cible. Cette carte est idéale pour accélérer les algorithmes de vision par ordinateur.

Le FPGA XCZU9EG de la carte ZCU102 comporte un système de traitement (PS) et une partie logique programmable (PL). La partie PS comprend un processeur quadricœur Arm Cortex-A53, des processeurs en temps réel Cortex-R5F à double cœur et une unité de traitement graphique Mali-400 MP2. Le Cortex-A53 est une unité de traitement d'application (APU) pour exécuter le système d'exploitation et les applications générales. Le ZCU102 est équipé d'une puce MPSoC Zynq Ultra-Scale+ XCZU9EG-2FFVB1156. Le Cortex-A53 est un processeur multiprocesseur quadricœur 64 bits basé sur l'architecture ARM v8. Le Cortex-R5 est une unité de traitement en temps réel (RPU) et est basé sur une architecture ARM v7 RPU 32-bit avec une mémoire dédiée à couplage serré (TCM). Le Mali-400 est une unité de traitement graphique avec un processeur de pixels et de géométrie et un cache L2 de 64 Ko.

Les ressources PL du ZCU102 sont les suivantes : il dispose de 912 Block RAM (BRAM), 548160 flip-flops (FF), 2520 unités de traitement numérique du signal (DSP) et 274080 Look-up tables (LUT).

Pour contrôler un bras prothétique pour les amputés, nous avons proposé une

solution hybride matériel-logiciel. Les principaux composants du système sont les suivants: Enregistrement des images et des points de regard avec l'eye-tracker Tobii, alignement des points de regard, réduction du bruit des points de regard, génération de boîtes de délimitation autour des points de regard réduits en bruit, détection d'objets avec le Gaze Driven CNN. De plus amples informations sur chaque composant sont disponibles dans les paragraphes suivants.

L'eye-tracker Tobii enregistre les points de regard de l'utilisateur et une vidéo égocentrique.

Les points de regard de l'utilisateur peuvent contenir du bruit dû aux distracteurs et aux microsaccades. Nous souhaitons donc collecter tous les points de regard dans l'image actuelle et estimer la position lissée de la fixation du regard dans l'image vidéo actuelle. L'étape suivante est donc l'alignement des points de regard. Nous souhaitons l'effectuer à l'aide d'un modèle d'homographie ; ce dernier peut être estimé en faisant correspondre des points caractéristiques de la scène visuelle. Ainsi, nous devons d'abord extraire les points caractéristiques SIFT (Scale-Invariant Feature Transform) de chaque image consécutive dans une fenêtre temporelle que nous souhaitons utiliser pour estimer la position du point de regard dans l'image actuelle. Nos mesures montrent que la transformation SIFT est l'une des parties les plus lentes de notre méthode pour le système expérimental. Après avoir obtenu les points clés SIFT, l'étape suivante est la correspondance FLANN. Il y a une image de référence que nous comparons avec l'image de référence-10, l'image de référence-...., l'image de référence-1 et nous les porjetons dans le même plan. Ensuite, nous pouvons calculer la matrice d'homographie avec les points caractéristiques appariés, et projeter toutes les fixations de regard de la fenêtre temporelle dans l'image vidéo actuelle.

Dans la réduction du bruit des points de regard, l'objectif est de filtrer les points

de regard aberrants. Les points de regard aberrants peuvent être causés par les saccades et les mouvements de la tête, lorsque l'utilisateur essaie de trouver un objet ou est distrait pendant le processus de saisie. Le l'algorithme de clustering DBScan élimine les points de regard aberrants. Ensuite l'estimation de la densité par une méthode à noayaux(KDE) utilise les points de regard alignés et estime l'emplacement lissé du point de regard dasn l'image courante.

Des boîtes englobantes sont ensuite générées autour du point de regard estimé. La classification de ces boîtes englobantes selon notre taxonomie d'objets donnera une localisation précise de l'objet à saisir et de son type. Neuf boîtes englobantes sont générées à différentes échelles et tailles, le point central étant le point de regard estimé.

Le CNN piloté par le regard prédit le type et la localisation de l'objet. Les entrées de ce CNN sont les neuf boîtes englobantes et l'image vidéo actuelle.

Le type d'objet est nécessaire. En effet, dans le processus de préhension, il est important de connaître la forme et la qualité de la surface de l'objet. Dans notre travail actuel, nous n'avons pas étudié le contrôle de l'ouverture de la paume en fonction de la forme de l'objet, mais nous avons préparé une bonne base pour cette prochaine étape du contrôle de la prothèse.

Pour résumer, dans cette recherche doctorale, nous avons implementé, sur une architecture hybride qui comprend les FPGA, une solution complète pour la reconnaissance d'objets avec des réseaux profonds dans une vidéo égocentrée. La solution est guidée par les enregistrements de fixation du regard de l'eye-tracker et est conçue pour l'asservissement visuel des bras neuroprosthiques des membres supérieurs. Dans ce qui suit, nous résumons les contributions de notre travail.

Mes résultats scientifiques sont de deux ordres :

• 1. J'ai développé une solution hybride : FPGA-CPU - pour la reconnaissance

d'objets dans une vidéo égocentrique par un CNN guidé par le regard.

• 2. Comme partie réutilisable, j'ai implémenté, sur FPGA, un nouveau détecteur SIFT pour le prétraitement des données du regard, à savoir leur alignement dans l'image vidéo courante.

# Chapter 1

## Introduction

One of the problems assistive robotics addresses is the production of upper limb prostheses for amputees. Despite great progress in upper limb bionic prostheses, allowing for object-of-interest reaching and grasping, the key remaining issues relate to their control by the operator. To overcome the limitations of traditional control solely based on the electromyographic (EMG) activity of the remaining muscles, promising alternatives consider hybrid systems combining noninvasive motion capture and vision control mentioned in Kanishka Madusanka et al. (2017); Mick et al. (2021). They include camera vision modules that allow for recognition of the subject's intention to grasp an object and assist visual control of prosthetic arms for object reaching and grasping (Han et al., 2020).

The computer vision algorithms which are implemented in these systems comprise the latest object recognition approaches, such as deep neural network (DNN) classifiers and regressors (González-Díaz et al., 2019).

Despite the fact that the visual servoing of robotic arms has been a highly researched area (Hussein, 2015), the application to arm neuroprostheses implies supplementary constraints. The whole control device has to be lightweight and worn by the subject. Hence, it is necessary first to minimize the equipment and second to propose efficient, lightweight solutions for visual scene analysis by the camera worn by the subject. So it has to be a wearable device.

Real-time performance is also a mandatory requirement for our target application (Mick et al., 2019, 2021). As the fastest visuomotor response to a perturbation takes about 90 ms (Scott, 2016), and feedback delays of 100 ms or more are known to deteriorate the performance of online feedback control (Miall et Jackson, 2006). Therefore, computation time should remain as low as possible, and below 100 ms.

Field-Programmable Gate Array (FPGA) do fulfil those requirements, because they are lightweight, mobile, and also efficient accelerators for computer vision algorithms (Qasaimeh et al., 2019; Yu et al., 2020).

When speaking about the state-of-the-art (SOTA) family of computer vision algorithms allowing for object recognition and localisation, we have to remember that our environment is very much cluttered and various objects are present in it. In such real-world scenarios, we cannot reasonably hope that the SOTA object detection algorithm could perform well to identify the object-to-grasp. They are usually designed for much less cluttered scenes. External information is needed. The most natural way to introduce this information into prosthesis control consists in measuring user's intention by external tools and incorporating these measures into artificial vision approach to recognize and localize the object to grasp in the visual scene. A natural way to do it consists in measuring visual intention of the amputee with an eye-tracker (Mick et al., 2021). In this case, the gaze fixations on the images of a video recorded with scene view camera could guide the whole recognition system towards the object to recognize and localize.

Nevertheless, as shown in de San Roman et al. (2017), this information is noisy. First of all, when the person realises an initial visual search for object, gaze fixations are scattered in the scene, then some highly contracted visual distractors can disturb the subject in his visual search for the object. Hence, these information has to be

filtered from the past (initial observation) - to the current moment, estimating the gaze fixation on the object-to-grasp.

Filtering of gaze points with motion compensation from the past to the present frame is needed. To do this, the Scale-Invariant Feature Transform (SIFT) (Lowe, 2004) keypoints can be extracted in the images to compute the global motion model after matching of keypoints, to collect all gaze points in the current frame. This redundant information can then be used to estimate a smooth position of a gaze fixation in the current frame. Hence, in our work, we study and propose a solution for SIFT detector implementation on FPGA.

The most efficient solution for object recognition and localisation of it in the frames of video scene are convolutional neural network (CNN)s or recently proposed transformers such as Deformable Transformer for End-to-End Object detection (DETR) (Zhu et al., 2021). In our case, for object detection and localization we adapt and implement in hybrid FPGA - embedded CPU solution the gaze-driven DNN approach, previously developed in software in González-Díaz et al. (2019).

We present our work in the following chapters of the manuscript.

Chapter 2 contains the state-of-the-art (SOTA) in our problem, namely the Neuroprosthesis control, the object recognition and the FPGA implementation of visual scenes analysis methods.

Chapter 3 is devoted to the analysis of the algorithm developed in LaBRI for Object-to-grasp recognition (González-Díaz et al., 2019; Buzási, 2018; Poursanidis et al., 2020), which we have adapted for FPGA implementation (Fejér et al., 2019, 2021a,b, 2022). We supply the complexity analysis in terms of computational time for the hybridization choices.

Chapter 4 presents our solution for SIFT characteristic point detection (Lowe, 2004) on FPGA. We first detail the regular SIFT algorithm and its software im-

plementation reported by Hess (2010). Then we analyse the constraints for its implementation on FPGA and possible available solutions. Finally, we present our solution of accelerated SIFT approach adapted for FPGA implementation (Fejér et al., 2021a).

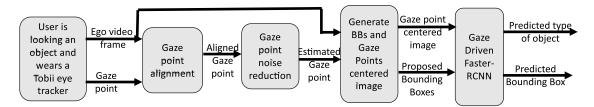

Chapter 5 contains the preprocessing steps of the Gaze-Driven CNN(González-Díaz et al., 2019). The preprocessing process has two steps: the gaze point alignment and the gaze point noise reduction. The gaze point alignment step contains the SIFT point extraction, the keypoint matching with the FLANN matcher (Muja et Lowe, 2009), and the homography estimation. The gaze point noise reduction has two steps: clustering the gaze points and elimination of the outliers, and the Kernel Density Estimation (KDE) (Pedregosa et al., 2011) estimation of the smoothed position of the gaze point in the current frame.

Chapter 6 presents the Gaze-Driven CNN originally proposed for computation on CPU (González-Díaz et al., 2019) and its FPGA optimized implementation (Fejér et al., 2022). The Gaze-Driven CNN FPGA optimized version (Fejér et al., 2022) is built in the following modules: the ResNet50 (He et al., 2016) which extracts the features from a frame, the Reduction Layer to change the size of the input layer of further network to a smaller one, the Faster R-CNN (Girshick, 2015) to estimate the grasped object location, and the Multiple Instance Learning (Amores, 2013) to predict the grasped object type.

Chapter 7 provides a conclusion of this research and outlines its perspectives.

## Chapter 2

State-of-the-Art in visual scene analysis for neuroprostheses controls and FPGA implementation

### 2.1 Introduction

The neuroprosthetic arm is a great tool for helping disabled people who lost their arm due to a disease, an accident, or war injury. However, those robotic arms could be expensive and uncomfortable for the wearer. Nowadays, an intensive research is being conducted on how to achieve an affordable and comfortable, wearable robotic prosthetic arms.

In this Chapter 2 we first review the available methods for controlling a neuroprosthetic arm such as myoelectric control with elements of vision. Then we present an overview of the state-of-the-art for object recognition in visual scenes targeted to our application. Finally, we analyse the FPGA-based implementations of visual scene analysis methods as our goal is to propose such methods for prostheses control on hybrid architectures.

The researchers in assistive robotics and re-habilitation medicine state such as

Parker et al. (2006) that the myoelectric control only has its limitations. First of all the information measured as electrical signals of muscles is noisy and difficult to interpret. Second, the remaining muscles are not necessary the muscles which should control the missing joints. Some solutions have been proposed studying the co-contraction mechanisms in Parker et al. (2006), but this control remains quite sequential and unnatural. The behaviour pattern is difficult to learn by the amputee. Finally, the neuroprostheses with myoelectrical control could be invasive. Some of them require a surgery called "osseointegration" whereas the other surgery is the "targeted muscle re-innervation" (Farina et al., 2021). The latter improves the myoelectric control as it allows for activation of the nerve which controlled the missing muscles. But even in the case of myoelectric control of prostheses, with surface myo-sensors on the remaining part of the arm, that is without the surgery, they are not very comfortable for the amputees. They also do not ensure a perfect recording of myoelectric signals to control the artificial arm (Mereu et al., 2021).

The virtual reality (VR) (Karrenbach et al., 2022; Mick et al., 2021) and augmented reality (AR) (Shi et al., 2022b,a) have been already used for training amputees for neuroprosthesis control. The solutions based on deep learning (Karrenbach et al., 2022) or the regular feature extraction algorithms (Krausz et al., 2020) have been proposed. The AR can be used in the future for the prosthesis control, helping the amputee to select a good movement pattern to grasp an object. The AR or mixed vision-perception and myoelectrical control require understanding of the natural visual scene the amputee faces and, specifically, recognition and localization in it of the object that the person wishes to grasp;

In our case, it is important to know the type of the object and the location of the object in an image. The type is important because every object has a different shape, which requires a different grasp type. The location and distance are also important

for servoing the prosthetic arm. There are several methods for object recognition based on deep learning. For feature extracting there are VGGnet (Simonyan et Zisserman, 2015), Mobilnet (Howard et al., 2017), or ResNet (He et al., 2016). Faster R-CNN Ren et al. (2017) can use those feature extractors to recognize the object. There are also reviewed other object recognition methods such as Single-Stage Object Detection (SSD) (Liu et al., 2016) and YOLO (Redmon et al., 2016).

The developed device has to be wearable. This means that it has to be lightweight, and the device has to be portable, which means that it has to have low power consumption. FPGA has fulfilled those requirements, and it is also a powerful platform because there are methods to accelerate the algorithm. To accelerate a deep learning algorithm for a FPGA different tools are available: Vitis AI (Kathail, 2020), Apache TVM VTA (Moreau et al., 2019), Brevitas (Pappalardo, 2021), and FINN (Umuroglu et al., 2017). In the last part of Chapter 2 the different FPGA deep learning accelerators are reviewed and compared to each other.

# 2.2 Neuroprosthesis control based on visual and gaze information

Neuroprostethis control with visual and gaze information is a quickly developing research area. In this section, we will give a brief overview of the SOTA approaches. Karrenbach et al. (2022) implemented a data-driven predictive control strategy in object grasping tasks performed in virtual reality for wrist prediction to improve the performance of basic prostheses. Their method has two phases: in the first phase, data was captured for pregrasp hand poses, stopping at the point of contact to collect only relevant data for training. A set of eye-tracked gaze and hand kinematic data from a subject during an object reaching task in a virtual environment was

generated. The generated dataset is used during their CNN training. In the second phase, they implemented a user study with a full pick-and-place task to emulate a real use case and investigate the amount of compensation and effort that the user required in virtual reality. The evaluation was that the wrist prediction model was implemented in a virtual prosthesis and compared to a wrist-locked prosthesis. This method leads to a decrease in compensatory movement in the shoulder, as well as to a decrease in task completion time.

Mouchoux et al. (2021) developed a man-machine interface that endows a myoelectric prosthesis (MYO) with artificial perception, estimation of user intention, and intelligent control (MYO-PACE) to continuously support the user with automation while preparing the prosthesis for grasping. The Creative SR300 camera is on the glasses, which provides the camera looking the same scene as the user. It simultaneously acquires colour and depth (RGB-D) images at a resolution of  $1920 \times 1080$ pixels and  $640 \times 480$  pixels. Their method uses sEMG signals and Creative SR300 frames and depths to predict the right movements of the prosthetic arm and wrist. Mouchoux et al. (2021) system integrates a classification-based myoelectric control (MYO; implements the Linear Discriminant Analysis algorithm (LDA) (Englehart et Hudgins, 2003)) with a novel interface for comprehensive artificial exterior and proprioception and autonomous adaptive prosthesis control (PACE). Mouchoux et al. (2021) demonstrate that the implementation of advanced perception, context interpretation, and autonomous decision-making into active prostheses improves control dexterity. Moreover, it also effectively supports the user by speeding up the pre-shaping phase of the movement and decreasing muscle use.

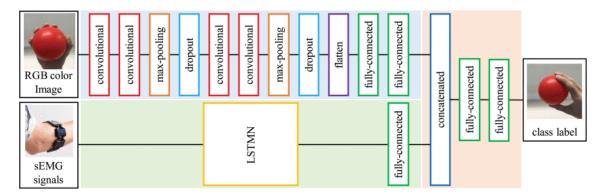

Fukuda et al. (2021) proposed a novel control scheme for a vision-based prosthetic hand, which fuses bimodal information to achieve human-like hand movements. Their methods combine the sEMG signals and the visual information of the object

Figure 2.1: The bimodal information architecture (Fukuda et al., 2021).

to achieve control. It uses a deep convolutional network for servoing. In both the training and the recognition phase, the network uses the sEMG signals and the visual information of the object, called bimodal information. Fukuda et al. (2021) deep learning network has 3 subnetworks as a CNN for the frame input and an LSTMN for the sEMG signals and those are concatenated in the connection network and the result of this network is a class label. They assume only 1 object exists in a frame during the measurements. The camera (Microsoft LifeCam Studio for Business) is mounted on the prosthetic arm.

Shi et al. (2022b) designed a prosthetic arm control system based on eye-tracking. Their system is called i-MYO, and it uses EMG signals and the AR information from Microsoft HoloLens 2. The Microsoft HoloLens 2 is an AR helmet. The user wears this AR helmet and can switch the type of grasp with his eyes. It has 6 different grasp types: Cylindrical, Spherical, Tripod, Pinch, Lateral, and Hook. The user has to look at the selected grasp type for 200 ms. This grasp-type switching is called i-GSI (Shi et al., 2022a). After the selection, the system is used the EMG signals to get the intention of the user to control the prosthetic hand opening or closing.

Krausz et al. (2020) made a system for controlling a prosthetic arm which fused EMG and gaze data predict the desired end-point for full arm prosthesis, which could drive the forward motion of individual joints. The image processing algorithms

have been used to resolve the concurrent head motion in gaze tracking. The image is processed from the front-facing camera to project the gaze position into a global 2D space (using the first recorded frame as a reference). The ORB (Rublee et al., 2011) features and the BRIEF (Calonder et al., 2010) descriptors are extracted in each image, and the extracted descriptors are matched with the FLANN-based matcher (Muja et Lowe, 2009) in all consecutive frame pairs. Then RANSAC (Fischler et Bolles, 1981) was used to estimate the homography transformation matrix to project each pixel from the head-frame to the global frame, and produce gaze coordinates independent of head motions and solely dependent on the distance between targets in the global frame. This gaze fixations result has been fused with the EMG data using a Kalman filter (Kalman, 1960).

Mick et al. (2021) proposed a system which fuses the myoelectric and kinematic information with the gaze information. The gaze tracked information is good to get contextual information about the target's location and orientation. To do that they are using computer vision algorithm such as Neural network. Mick et al. (2021) also used virtual reality. They are created in a virtual environment which was scaled to match the real-world dimensions. The subjects used HTC Vive Pro virtual reality headset and HTC Vive Tracker motion tracker. The subject's goal is to grasp and move a bottle.

The problem with VR (Karrenbach et al., 2022; Mick et al., 2021)) and AR (Shi et al., 2022b,a) based solution is that it could cause visual fatigue and motion sickness as mentioned by Chang et al. (2020); Park et al. (2014); Lambooij et al. (2009). The symptoms include but are not limited to eye fatigue, disorientation, and nausea. Today is a big research area to solve the caused problems of the VR and AR (Kramida, 2016), however it is still an open question. So VR and AR are not good for real clinical research which is available in the outside world, but

it is good for getting proper data for the training (Mick et al., 2021). In the real-world environment, the visual scene analysis tools have to be sufficiently advanced to recognize and localize, in a cluttered environment, the object the prosthesis wearer needs to grasp. In the follow-up of this chapter we will review popular methods from the state-of-the-art (SOTA) for object recognition.

### 2.3 Object recognition in visual scenes

In recent years, in the field of computer vision, the most popular algorithms for object detection are deep convolutional neural network, such as Fast Region-based Convolutional Neural Network (R-CNN) (Ren et al., 2017), You Only Look Once (YOLO) (Redmon et al., 2016), and Single-Stage Object Detection (SSD) (Liu et al., 2016). These detectors are based on deep Residual Network (ResNet) (He et al., 2016), Visual Geometry Group Net (VGGnet) (Simonyan et Zisserman, 2015), Alexnet (Krizhevsky et al., 2017), MobileNet (Howard et al., 2017), GoogleNet (Szegedy et al., 2015) and on older Alexnet (Krizhevsky et al., 2017).

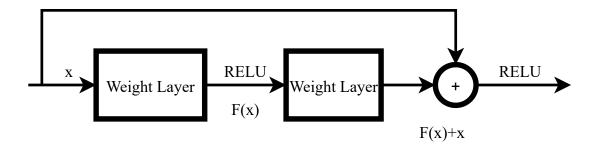

ResNet (He et al., 2016) was proposed by He et al. and uses residual blocks, which are illustrated in Figure 2.2.

Figure 2.2: Example of the residual block in the ResNet.

Its principle is based on the optimizing a residual mapping instead of direct mapping.

# 2. State-of-the-Art in visual scene analysis for neuroprostheses controls and FPGA implementation

Let us denote the desired underlying mapping as H(x). Then the new mapping F(x) is introduced as

$$F(x) := H(x) - x$$

where we let the non-linear stacked layer fit F(x). The original mapping is recast into F(x) + x. It is easier to optimize the residual mapping than to optimize the original mapping. F(x) + x can be realized by feedforward neural networks with shortcut connections, as illustrated in Figure 2.2. Shortcut connections can skip one or more layers. In ResNet (He et al., 2016), the outputs of the shortcut connections are simply added to the outputs of the stacked layer.

The computational cost of ResNet (He et al., 2016) is high, which makes realtime implementation difficult. However, there are methods that can accelerate the computational speed.

VGGNet (Simonyan et Zisserman, 2015) is a simple deep convolutional neural network, where depth refers to the number of layers. The VGG-16 consists of 13 convolutional layers and 3 fully connected layers. The convolutional layers are simple because they use only  $3 \times 3$  filters and pooling layers. This architecture has become popular in image classification problems.

Faster R-CNN was proposed by Ren et al. (2017). This architecture has gained popularity among object detection algorithms. Faster R-CNN (Ren et al., 2017) is composed of the following four parts:

- feature extraction module; this can be a VGGnet (Simonyan et Zisserman, 2015), Mobilenet (Howard et al., 2017), or ResNet (He et al., 2016);

- region proposal module to generate the bounding boxes around the object;

- classification layer to detect the class of the object—for example, cat, dog, etc.;

regression layer to make the prediction more precise.

The computational speed of the network depends on the feature extraction module and the size of the region proposal module.

Both SSD (Liu et al., 2016) and YOLO (Redmon et al., 2016) are single-stage detectors. They are significantly faster than two-stage detectors (region-based methods), such as Faster R-CNN (Ren et al., 2017). However, in cases when the objects have not so much variability, neither interclass nor intraclass Faster R-CNN (Ren et al., 2017) is a well-suited network. In our problem, we are interested in naturally cluttered home environments, where the subject intends to grasp an object, such as in kitchens. The vision analysis system we propose has to be designed to recognise objects to grasp in the video, similar to the Grasping In The Wild (GITW) dataset (LaBRI, 2016). This dataset was recorded in natural environments by several healthy volunteers and made publicly available on the CNRS NAKALA platform. The objects here, seen from the glass-mounted camera, are quite small. Their surface merely represents 10% of the whole video frame. For more information on this dataset, see Chapter 3.3.2. Hence, Faster R-CNN (Ren et al., 2017) is a better choice than the SSD (Liu et al., 2016) and YOLO (Redmon et al., 2016). This is due to the fact that Faster R-CNN (Ren et al., 2017) achieves higher mean average precision (mAP) than them, as reported by Huang et al. (2017) for small objects.

The original Faster R-CNN (Ren et al., 2017) uses VGGnet (Simonyan et Zisserman, 2015) as a feature extractor. However, the mAP is higher when ResNet (He et al., 2016) is used as a backbone (Redmon et Farhadi, 2016). When the object is small, the mAP of the backbone with ResNet (He et al., 2016) is higher than the backbone with MobileNet (Howard et al., 2017), as reported in Huang et al. (2017).

# 2.4 FPGA implementation of visual scenes analysis methods

There are several possible ways to accelerate an algorithm, as described in Fejér et al. (2019). In our case, the FPGA was chosen in the interest of developing a lightweight and portable device (Fejér et al., 2021b). In the first part of the section, the different CNN accelerations on the FPGA are discussed. These approaches have been implemented as tools available today to accelerate a network on different FPGAs.

The second part of this section is about the acceleration of the SIFT (Lowe, 2004) algorithm on different hardware architectures. The main parameters of various architectures will be discussed from the point of view of the wearable device.

#### 2.4.1 CNN acceleration on FPGA

If speaking of one of possible realistic scenarios for a prosthetic arm control, the DNN for object detection and recognition can be trained off-line. The real-time constraints are imposed only at the inference stage. Neural network inference can be very efficiently accelerated on Field-Programmable Gate Array (FPGA). The most important frameworks and development environments are Vitis AI (Kathail, 2020), Apache TVM Versatile Tensor Accelerator (VTA) (Moreau et al., 2019), Brevitas (Pappalardo, 2021), and FINN (Umuroglu et al., 2017).

Due to large computing and memory bandwidth requirements, deep neural networks are trained on high-performance workstations, computing clusters, or GPUs using floating-point numbers. The memory access pattern of the inference step of a trained network is different, offering more data reuse and requiring smaller memory bandwidth. It makes FPGAs a versatile platform for acceleration. Computing with floating-point numbers is a resource-intensive process for FPGA in terms of digital signal processing (DSP) slices and logic resource usage. Memory bandwidth, required to load 32-bit floating point state values and weights, can be still high compared to the capabilities of low-power FPGA devices. Additionally, a significant amount of memory is required for buffering state values and partial results in the on-chip memory of the FPGA. One possible solution would consist of using the industry-standard bfloat, 16-bit, floating-point representation, which can improve the inference speed of an FPGA. Observations show (Umuroglu et al., 2017) that the value of weights, state values, and partial results during the computation usually fall in a relatively small range and the 8-bit exponent range of the bfloat type is practically never used. If the range of values during the computation is known in advance, then fixed-point numbers can be used. One of the major application areas of FPGAs is signal processing; therefore, DSP slices are designed for fast, fixed-point Multiply-ACcumulate (MAC) or Multiply-ADD (MADD) operations, which can be utilized during neural network inference.

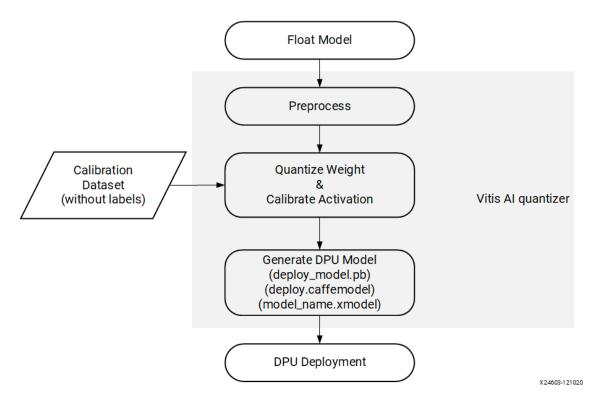

Converting a neural network model trained with floating-point numbers to a fixed-point FPGA-based implementation usually requires an additional step, called quantization. Here, a small training set is used to determine the fixed-point weights and optimize the position of the radix point in each stage of the computation. The common bit width for quantization is 16 or 8 bits, where the accuracy of the network is slightly reduced. In some cases, even a binary representation is possible (Umuroglu et al., 2017), eliminating all multiplications from the computation, which makes FPGA implementation very efficient while the accuracy is decreased slightly.

For latency-sensitive applications, this fixed-point model can be implemented on a streaming architecture, such as FINN (Umuroglu et al., 2017), where layers of