### Modular Avionics Software Integration on Multi-Core COTS: certification-Compliant Methodology and Timing Analysis Metrics for Legacy Software Reuse in Modern Aerospace Systems

Soukayna Raja M'Sirdi

#### ▶ To cite this version:

Soukayna Raja M'Sirdi. Modular Avionics Software Integration on Multi-Core COTS : certification-Compliant Methodology and Timing Analysis Metrics for Legacy Software Reuse in Modern Aerospace Systems. Other [cs.OH]. Institut National Polytechnique de Toulouse - INPT, 2017. English. NNT : 2017INPT0039 . tel-04222367

### HAL Id: tel-04222367 https://theses.hal.science/tel-04222367v1

Submitted on 29 Sep 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Toulouse

En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

Discipline ou spécialité :

Sureté de Logiciel et Calcul à Haute Performance

#### Présentée et soutenue par :

Mme SOUKAYNA RAJA MSIRDI le mercredi 5 juillet 2017

Titre :

Modular Avionics Software Integration on Multi-Core COTS: Certification-Compliant Methodology and Timing Analysis Metrics for Legacy Software Reuse in Modern Aerospace Systems

Ecole doctorale :

Mathématiques, Informatique, Télécommunications de Toulouse (MITT)

Unité de recherche : Institut de Recherche en Informatique de Toulouse (I.R.I.T.)

#### Directeurs de Thèse :

M. YAMINE AIT AMEUR M. MARC PANTEL

Rapporteurs :

Mme ISABELLE PUAUT, UNIVERSITE RENNES 1 M. PASCAL RICHARD, ENSMA POITIERS

#### Membres du jury :

Mme CHRISTINE ROCHANGE, UNIVERSITE TOULOUSE 3, Présidente M. FREDERIC BONIOL, ONERA TOULOUSE, Membre M. MARC PANTEL, INP TOULOUSE, Membre Mme CLAIRE MAIZA, UNIVERSITE GRENOBLE ALPES, Membre M. SEBASTIAN ALTMEYER, UNIVERSITE D'AMSTERDAM, Membre "Libérée, délivréééééée..." – Elsa, La Reine des Neiges

"Let it go, let it gooooo" – Elsa,  $\mathit{Frozen}$

## Contents

| 1 | Inti | roduction 4                                          | 9        |

|---|------|------------------------------------------------------|----------|

|   | 1.1  | Motivations                                          | 19       |

|   | 1.2  | Contributions                                        | 52       |

|   | 1.3  | Thesis Outline                                       | 56       |

| 2 | Bac  | kground 5                                            | 57       |

|   | 2.1  | Terminology                                          | 57       |

|   | 2.2  | IMA Systems in the Aerospace Industry                | 59       |

|   | 2.3  | Safety and Certification Regulations                 | 52       |

|   | 2.4  | WCET Analysis                                        | 64       |

|   | 2.5  | Response Time Analysis                               | 58       |

|   | 2.6  | Summary                                              | 72       |

| 3 | Sta  | te of the Art 7                                      | 3        |

|   | 3.1  | Overview                                             | 73       |

|   | 3.2  | Execution Models                                     | 73       |

|   | 3.3  | Dedicated Designs                                    | 74       |

|   | 3.4  | Software-Based Resource Access Monitoring Approaches | 76       |

|   | 3.5  | Mixed Criticality Approaches                         | 78       |

|   | 3.6  | Hierarchical Scheduling Considerations               | 30       |

|   | 3.7  | Multicore Scheduling Approaches                      | 32       |

|   | 3.8  | Non-Intrusive Static Timing Analysis Techniques      | 33       |

|   | 3.9  | Summary and Conclusions                              | 35       |

| 4 | Inte | egration Strategies Overview and System Model        | <b>9</b> |

|   | 4.1  | Assumptions                                          | 39       |

|   | 4.2  | Proposed Integration Strategies                      | 93       |

|   |      | 4.2.1 Brief Overview                                 | 93       |

|   |      | 4.2.2 One-to-All Integration Strategy                | 94       |

|   |      | 4.2.3 One-to-One Integration Strategy                | 96       |

|   |      | 4.2.4 Comparison of the Two Strategies               | 97       |

|   | 4.3  |                                                      | 99       |

|   | 4.4  | Hardware Architecture Model                          | 1        |

|   | 4.5  | Constraint Programming                               | 6        |

|   |      | 4.5.1 Allocation Constraints                         | 7        |

|   |      | 4.5.2 Scheduling Constraints                         |          |

|   |      | 4.5.3 Why Constraint Programming                     | 9        |

|   | 4.6  | Discussions                                          |          |

|   | 4.7  | Summary                                              | 22       |

| 5 | $\mathbf{M}\mathbf{u}$                                                                                | lticore Timing Analyses                            | <b>123</b>                                                         |

|---|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|

|   | 5.1                                                                                                   | Tasks WCRTs and WCETs Computation                  | 123                                                                |

|   |                                                                                                       | 5.1.1 Tasks WCRTs and Allocation                   | 123                                                                |

|   |                                                                                                       | 5.1.2 Task Instances WCETs and Schedule Generation | 126                                                                |

|   | 5.2                                                                                                   | Multicore Interference Computation                 | 129                                                                |

|   | 5.3                                                                                                   | Partitions CPU Time Budgets Computation            |                                                                    |

|   | 5.4                                                                                                   | Allocation and Timing-Related Verification         | 140                                                                |

|   | 5.5                                                                                                   | Scheduling and Timing-Related Verification         | 143                                                                |

|   | 5.6                                                                                                   | Discussions                                        | 146                                                                |

|   | 5.7                                                                                                   | Summary                                            | 147                                                                |

| 6 | IM                                                                                                    | A System Integration                               | 149                                                                |

|   | 6.1                                                                                                   | One-to-All Integration Strategy                    | 149                                                                |

|   | 6.2                                                                                                   | One-to-One Integration Strategy                    | 163                                                                |

|   | 6.3                                                                                                   | Discussions                                        |                                                                    |

|   | 6.4                                                                                                   | Summary                                            | 170                                                                |

|   |                                                                                                       |                                                    |                                                                    |

| 7 | Eva                                                                                                   | luation Results                                    | 171                                                                |

| 7 | <b>Eva</b><br>7.1                                                                                     | luation Results Software Case Study Generation     |                                                                    |

| 7 |                                                                                                       |                                                    | 172                                                                |

| 7 | 7.1                                                                                                   | Software Case Study Generation                     | 172<br>174<br>178                                                  |

| 7 | $7.1 \\ 7.2$                                                                                          | Software Case Study Generation                     | 172<br>174<br>178                                                  |

| 7 | $7.1 \\ 7.2 \\ 7.3$                                                                                   | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192                                    |

| 7 | $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6$                                                              | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192                                    |

| 7 | <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>                           | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194                             |

| 8 | <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ol> | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194                             |

|   | <ol> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>7.7</li> </ol> | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194<br>197<br><b>199</b>        |

|   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Sum</b>                                           | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194<br>197<br><b>199</b>        |

|   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Sun</b><br>8.1                                    | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194<br>197<br><b>199</b><br>201 |

|   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Sun</b><br>8.1<br>8.2<br>8.3                      | Software Case Study Generation                     | 172<br>174<br>178<br>186<br>192<br>194<br>197<br><b>199</b><br>201 |

# List of Figures

| $\frac{1}{2}$       | Stratégie d'Intégration "One-to-All"                                                                                                                         | $\begin{array}{c} 40\\ 42 \end{array}$ |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

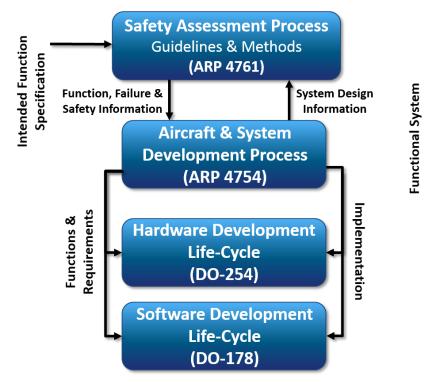

| $2.1 \\ 2.2 \\ 2.3$ | Relations Between Avionics Certification Guidelines Documents [11]                                                                                           | 63<br>65<br>66                         |

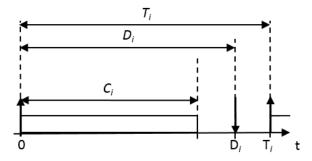

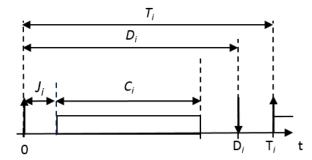

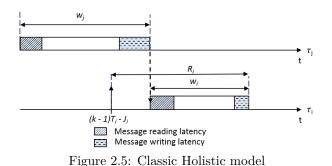

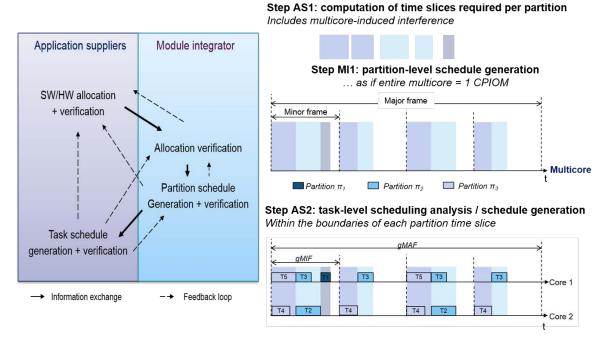

| $2.4 \\ 2.5$        | Tasks Defined with Jitters upon First Activation       Classic Holistic model                                                                                | 71<br>71                               |

| 3.1                 | Summary of the State of the Art                                                                                                                              | 86                                     |

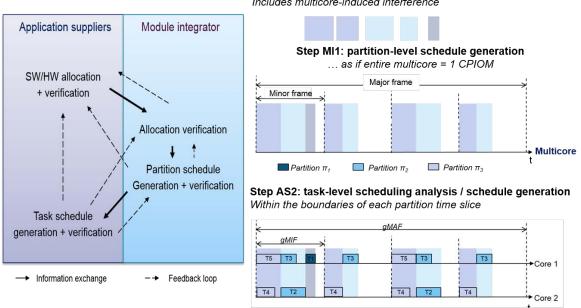

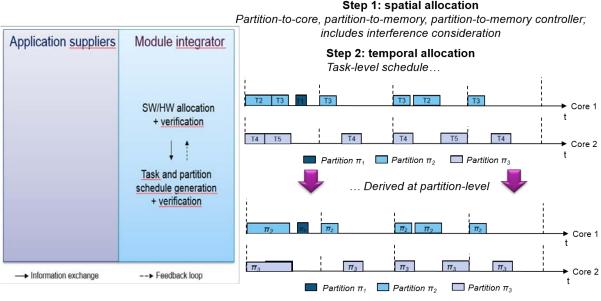

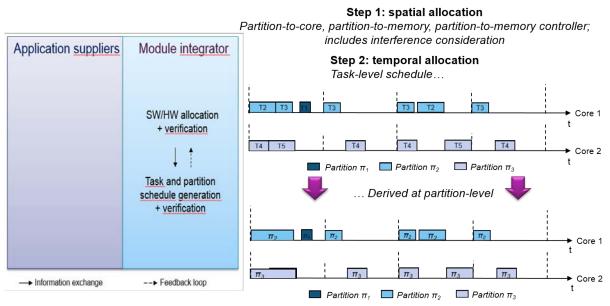

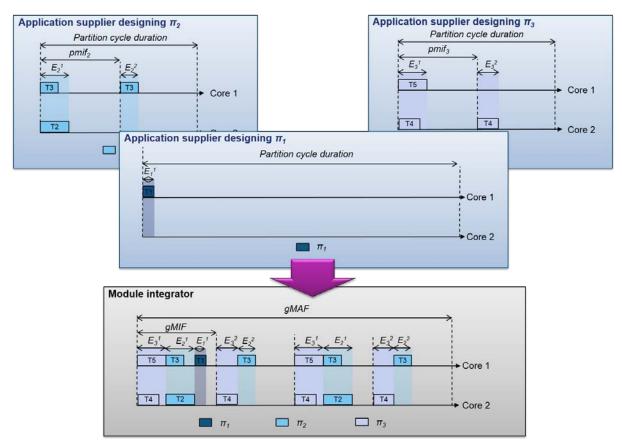

| 4.1                 | Overview of the One-to-All Integration Strategy                                                                                                              |                                        |

| 4.2                 | Overview of the One-to-One Integration Strategy                                                                                                              |                                        |

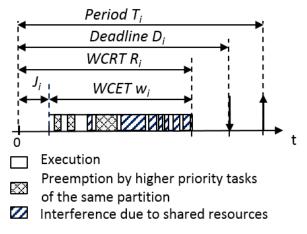

| 4.3                 | Task Model for the Allocation Problem                                                                                                                        |                                        |

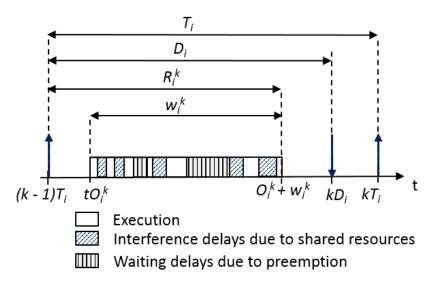

| 4.4                 | Task Model for the Scheduling Problem                                                                                                                        | 101                                    |

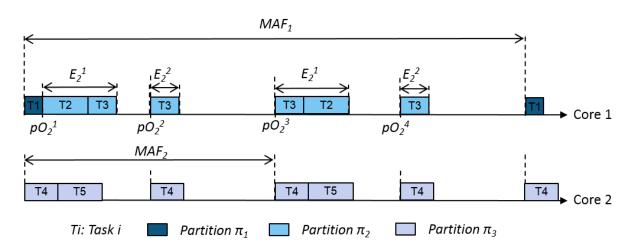

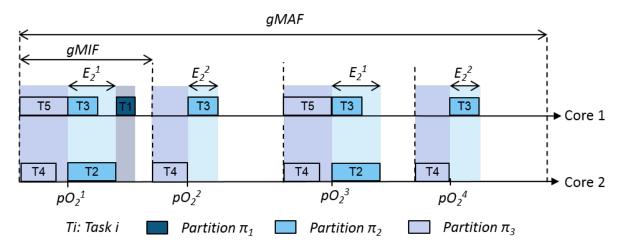

| $4.5 \\ 4.6$        | Example of MAF Schedule Resulting from the One-to-One Integration Strategy .<br>Example of MAF Schedule Resulting from the One-to-All Integration Strategy . | 104<br>104                             |

| 4.0<br>4.7          | System Schedule Generation using each Partition CPU Time Budgets (One-to-All                                                                                 | 104                                    |

| 4.1                 | Integration Strategy)                                                                                                                                        | 105                                    |

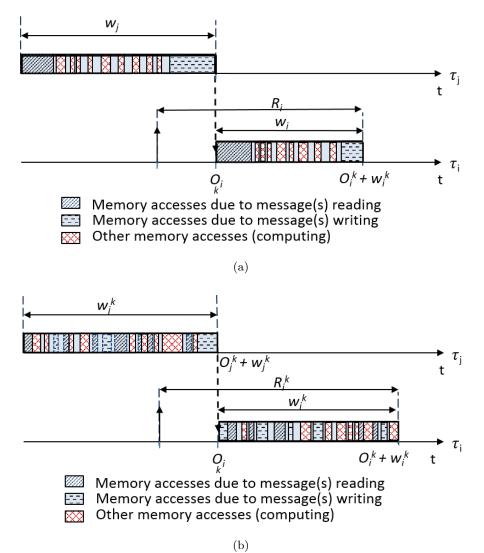

| 4.8                 | Representing Messages as Memory Accesses in Tasks Response Times: (4.8a) when using the classic holistic model versus (4.8b) when using the model proposed   | 100                                    |

|                     | in this thesis                                                                                                                                               | 109                                    |

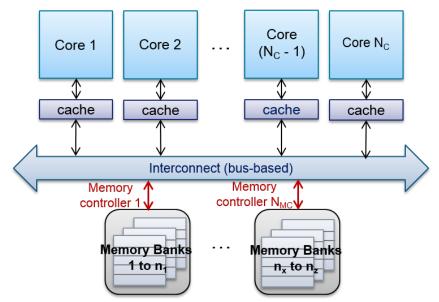

| 4.9                 | Multicore Hardware Architecture Model                                                                                                                        | 112                                    |

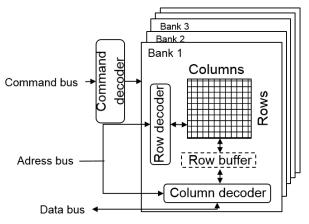

| 4.10                | Model of Memory Banks                                                                                                                                        | 113                                    |

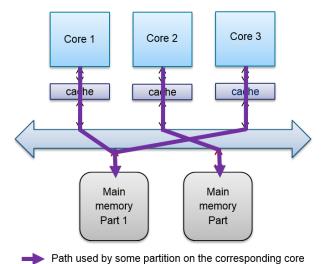

| 4.11                | Example of Memory Path Sharing Scenario                                                                                                                      | 114                                    |

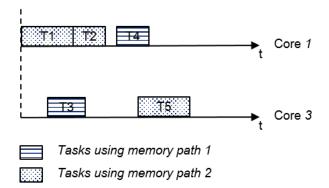

| 4.12                | Core-Level Path Sharing and Runtime Interference                                                                                                             | 115                                    |

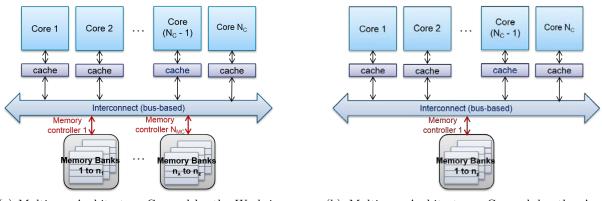

| 5.1                 | Multicore Architectures                                                                                                                                      | 130                                    |

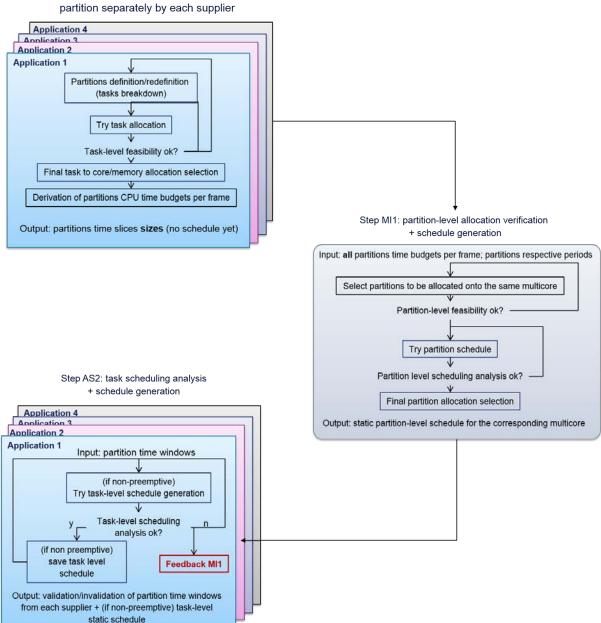

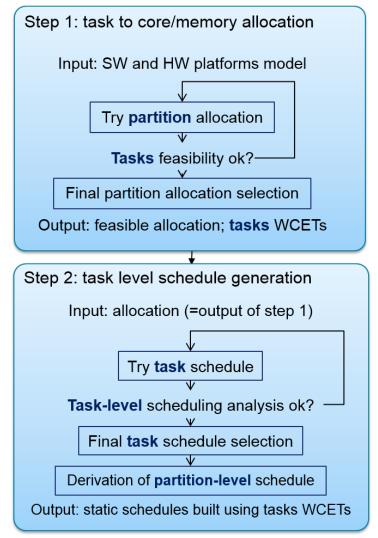

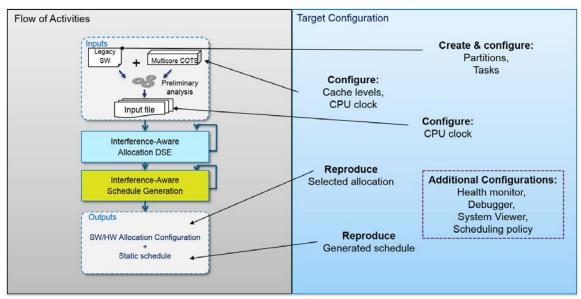

| 6.1                 | Steps of the One-to-All Integration Strategy                                                                                                                 | 150                                    |

| 6.2                 | Steps of the One-to-One Integration Strategy                                                                                                                 |                                        |

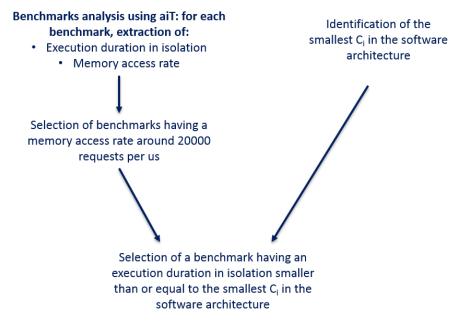

| 7.1                 | Benchmark Selection Process [9]                                                                                                                              | 173                                    |

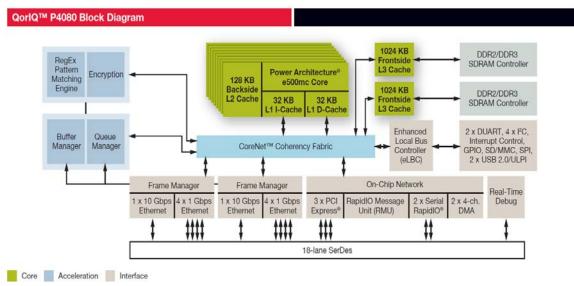

| 7.2                 | Block Diagram of the Freescale/NXP QorIQ P4080 Processor [9]                                                                                                 | 176                                    |

| 7.3                 | Target Configuration                                                                                                                                         | 179                                    |

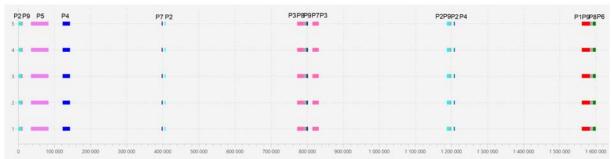

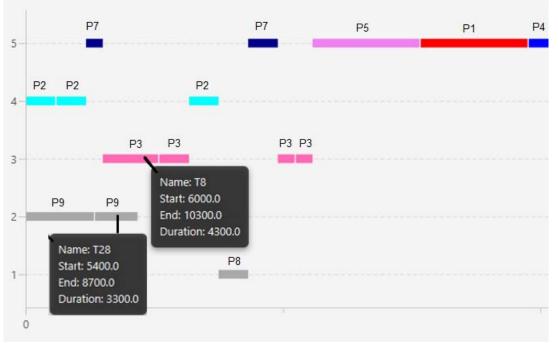

| 7.4                 | Schedule Resulting from Applying the One-to-One Integration Strategy to Inte-                                                                                |                                        |

|                     | grate the SW Case Study on Five Cores of the P4080                                                                                                           | 180                                    |

| 7.5                 | Schedule Resulting from Applying the One-to-All Integration Strategy to Inte-                                                                                |                                        |

|                     | grate the SW Case Study on Five Cores of the P4080                                                                                                           | 181                                    |

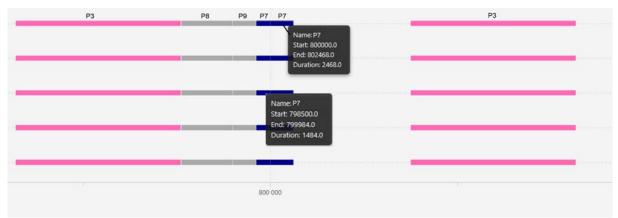

| 7.6                 | Parallel Execution of Non-Interfering Tasks                                                                                                                  | 181                                    |

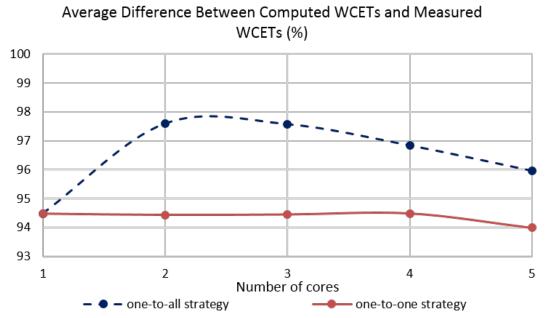

| 7.7                 | Comparison of the Observed Difference between Computed WCETs and the Re-                                                                                     | 100                                    |

|                     | spective Maximum Measured ETs in each Strategy                                                                                                               | 182                                    |

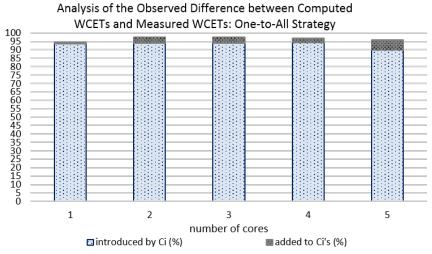

| 7.8                 | Average Difference between Computed WCETs and Measured WCETs in the                                                                                          | 100                                    |

|                     | One-to-All Strategy                                                                                                                                          | 183                                    |

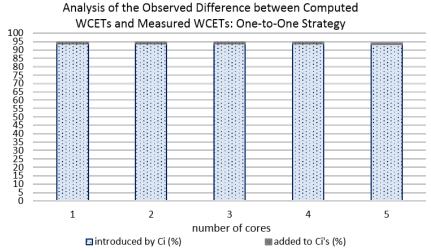

| 7.9  | Average Difference between Computed WCETs and Measured WCETs in the                |    |

|------|------------------------------------------------------------------------------------|----|

|      | One-to-One Strategy                                                                | 83 |

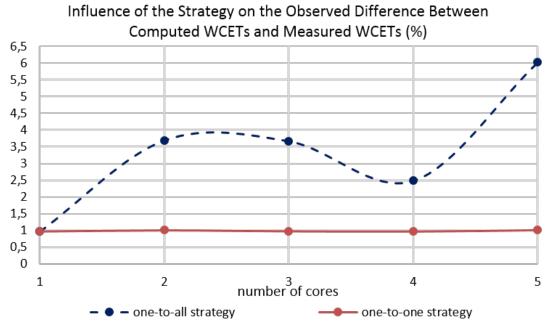

| 7.10 | Pessimism Percentage due to the Timing Analysis Independently from the Pes-        |    |

|      | simism resulting from the Preliminary – Single-Core – Analysis                     | 84 |

| 7.11 | Parallel Execution of Non-Interfering Tasks                                        | 86 |

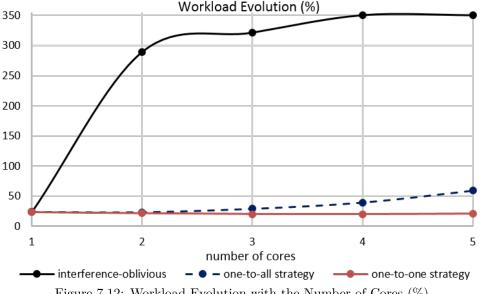

| 7.12 | Workload Evolution with the Number of Cores $(\%)$                                 | 88 |

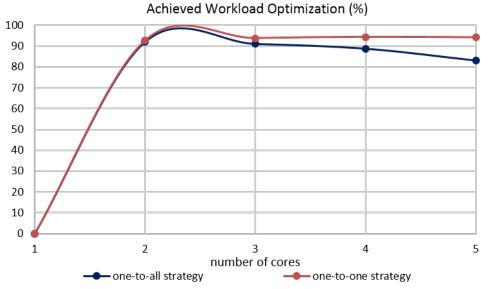

| 7.13 | Achieved Workload Optimization compared to the Classic Integration Strategy (%)1   | 89 |

| 7.14 | Evolution of the Number of Variables and Constraints for the Allocation Search . 1 | 91 |

| 7.15 | Evolution of the Number of Variables and Constraints for the Schedule Generation 1 | 92 |

## List of Tables

| 2.1 | Design Assurance Levels (DALs) as Defined in $[10, 11, 139, 140]$                                                                                   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | Comparison of the two Proposed Integration Strategies                                                                                               |

| 7.2 | Data used for the Software Case Study175L1 Cache Model (Identical for both Data and Instruction L1 Caches)177Data used for the Main Memory Model177 |

| 9.1 | Standard DRAM Parameters                                                                                                                            |

"The greatest enemy of knowledge is not ignorance, it is the illusion of knowledge" – Stephen Hawking

### Acknowledgments

Creating a PhD contract is no piece of cake. It involves submitting an idea to the hierarchy, writing a subject and carefully choosing an academic environment that is relevant to the PhD. For me, it meant coming to a new city, and sacrificing personal paths that were laid out in front of me to shape my future. When starting a PhD involves such sacrifices, you better make your PhD worth it to compensate the personal pain by great work and professional perspectives.

This PhD has been the best, but also the worst thing that has happened to me so far. I even contracted serious back problems during that same period, which lightened once the PhD was over. I always thought the PhD would be the last guided, schooling environment before entering the workforce and all the challenges it brings. I was wrong. But I needed it. These three years of PhD have been a mix of technical research, social conventions learning, a bit of politics and diplomacy sensitization, along with psychological analysis of all the kinds of personalities that may exist in the world. I started as a weak student, lacking confidence, way too naive and gullible. I came out of it focused and more efficient, always true to myself and others.

I would like to thank Yamine Ait Ameur for agreeing to be the PhD director.

I would like to thank Wenceslas Godard for taking me as a 6-month intern, and then offering me the position for this PhD contract, which he initiated. Thank you for letting me write the PhD subject. Thank you for all the space and autonomy you have given me, and for always letting me decide what to do and how to react when my work was challenged. It allowed me to stay focused and find my way out of the biggest challenges encountered, would it be about technical difficulties, but also political, socially tough situations. You thus helped shape my own contributions but also my own character along the way.

I would like to thank Marc Pantel for saying yes to the proposition of Wenceslas of being the academic environment for this PhD, although Marc admitted later that the PhD was not in his field of study. Thank you for giving me enough autonomy to find information and contact relevant people myself. Thank you for your peculiar sense of humor too, including during meetings where you would make funny statements and propose a new challenge to take on every now and then. I eventually understood that you wanted me to not restrict myself to the sole role of student, but also take the lead, be my own safety net and scope-guard, and only rely on solid studies to prove my points to you during technical meetings.

Last but not least, I would like to thank both Wenceslas and Marc for offering me the best gift supervisors could ever offer to their PhD student: the surprise news that you have both been pushing for my PhD contributions to be reused in a multipartner industrial research project. There is no better proof of you being convinced by my work than such a great news.

Now, I would like to actually thank Stephan Stilkerich for his guidance and support which took different shapes over the years, for instance by providing advice on the manuscript breakdown, PhD title, etc. but also the industrial contacts that turned out to play an essential role in the test environment of this thesis. Without you, I would probably not have enough results to defend right now.

I would like to thank every contact I had at Absint, Freescale, and Wind River Inc. for helping me with tools usage and for being interested in my work. Thank you for your patience, especially Stefan Harwarth from Wind River, for always supporting me whenever I asked for an umpteenth free license extension to perform my tests on a real platform.

I would like to thank Isabelle Puaut and Pascal Richard for agreeing to review the manuscript and approve it for defense. I would like to thank Sebastian Altmeyer, Frederic Boniol, Claire Maiza and Christine Rochange as well for agreeing to be part of my jury and for the rewarding appreciation they delivered at the end of the defense. Special thank you to Stephan Stilkerich again, who could not make it for the defense and sacrificed himself off the jury so that I could defend in July rather than having to find a time slot matching every jury member in September, which can be very complex when it involves professors.

I would like to thank my friends from Paris for supporting me despite the distance. I would also like to thank all the friends I made during conferences and kept in touch with. I am grateful for your support, your advice but also all the fun we had after the lecture sessions of the conferences. I would also like to thank the PhD students with whom I briefly shared an office in the first year of my PhD, and in general other students and fellow researchers with which I shared some inspirational talks over a coffee.

I cannot thank enough everyone at Airbus Operations who accepted to join for questioning sessions from time to time, and provided me with all the information I needed to shape my contributions until it fit their industrial environment. I owe you the relevance of my PhD contributions.

In the same line of idea I will always remain grateful to Björn Lisper for inviting me to join the TACLe (Timing Analysis at Code Level) COST Action after I submitted my very first paper to a workshop he was chairing. You provided me with the environment I needed to get in touch with the biggest researchers and contributors of the real-time community, but also to attend technical meetings to remain up to date with the state of the art at no cost. This all was essential in the context of my PhD, and it meant a lot to me. Special thank you to my father for explaining to me what a COST Action was back then, and for encouraging me to join it. In general thank you to every member of the action with which I had the pleasure to interact with; for your advice, encouragement, but also kindness and the fun we had during conferences.

I would like to thank everyone at Airbus Group Innovations, where I spent almost all my time. Let's not forget the German side as well, for the team that welcomed me is dispatched between France and Germany. Thank you to any colleague that got interested in my work, and always took some time to discuss with me whenever they visited Toulouse for some other reason. I will not state any name by fear of forgetting anyone, but I believe they will recognize themselves. In general, thank you to every person at Airbus Group Innovations, Airbus Operations and Airbus Defense and Space who accepted to proofread my manuscript sometimes more than once, and who granted me their friendship; thank you for listening to me and supporting me whenever I took a hit I was not prepared for, and for always getting me back on my feet.

I would like to thank my several osteopaths for getting me back on my feet too, literally this time, more than once in three years.

Finally, I would like to thank my family for always supporting me through these hard times. I am still amazed that each and everyone of you made it to the defense, although it was not that simple at first. Including little Lilia, aged 7 months when attending my defense; you probably did not understand much, let alone remember it, but you were a delight to everyone and I very much appreciated your presence. Thank you for clearing your busy schedule of kindergarten workshops and toys reviewing committees, just to come to my defense.

To finish, a special thank you to my mother who took care of everything for the defense celebration, and who was even more stressed out than me at my defense. And a special thank you to my father who may even be happier than me over my doctors degree. Thank you for letting me handle everything, and refrain from asking questions even though you quickly sensed that something was seriously wrong with my PhD environment. I appreciated your patient supervising, and all the advice you gave me as a professor yourself. "The best way out is always through" – Robert Frost

## Acronyms

| AMP:   | Assymmetric Multiprocessing               |

|--------|-------------------------------------------|

| ARINC: | Aeronautical Radio, Incorporated          |

| ARP:   | Aerospace Recommended Practice            |

| ASIC:  | Application-Specific Integrated Circuit   |

| COTS:  | Component Off-The-Shelf                   |

| CP:    | Constraint Programming                    |

| CPIOM: | Core Processing and Input/Output Module   |

| DAL:   | Design Assurance Level                    |

| DDR:   | Double Data Rate                          |

| DRAM:  | Dynamic Random Access Memory              |

| EASA:  | European Aviation Safety Agency           |

| EDF :  | Earliest Deadline First                   |

| FAA:   | Federal Aviation Administration           |

| FAR:   | Federal Aviation Requirements             |

| GCD:   | Greatest Common Divider                   |

| IMA:   | Integrated Modular Avionics               |

| I/O:   | Inputs/Outputs                            |

| JAR:   | Joint Aviation Requirements               |

| JEDEC: | Joint Electron Device Engineering Council |

| LCM:   | Least Common Multiple                     |

| LRU    | Line Replaceable Unit                     |

| MAF:   | MAjor time Frame                          |

| MIF:   | MInor time Frame                          |

| NUMA:  | Non Uniform Memory Access                 |

| PMC:   | Performance Monitoring Counter            |

| RM:    | Rate Monotonic                            |

| RTA:   | Response Time Analysis                    |

| SMP:   | Symmetric Multiprocessing                 |

| SWaP:  | Size, Weight and Power                    |

| TSP:   | Time and Space Partitioning               |

| UMA:   | Uniform Memory Access                     |

| WCRT:  | Worst-Case Response Time                  |

| WCET:  | Worst-Case Execution Time                 |

# Symbols

| 4                      |                                                                             |

|------------------------|-----------------------------------------------------------------------------|

| $A_p$                  | function computing the maximum number of requests generated by core         |

|                        | p depending on the considered time interval                                 |

| $a_{ij}$               | general term of the matrix defining the partition-to-core allocation in the |

|                        | one-to-one integration strategy                                             |

| AS                     | set of suppliers responsible for the design of the applications integrated  |

|                        | onto the same multicore platform                                            |

| $c2mc_{ij}$            | general term of the matrix specifying the core-to-memory controller – also  |

|                        | referred to as core-to-memory path – allocation in the hardware platform    |

| $cacheLat_p$           | core $p$ L1 cache access latency                                            |

| $cacheSize_p$          | size of the L1 cache of core $p$                                            |

| $C_i$                  | vector gathering the execution durations in isolation of $\tau_i$           |

|                        | depending on the core on which it is executed                               |

| $C_i^p$                | $k^{th}$ execution duration in isolation of $\tau_i$ when running on core p |

| $coreAff_{ij}$         | general term of the matrix defining the partition-to-core affinities        |

| 05                     | for a given software and hardware platforms in the                          |

|                        | one-to-one integration strategy                                             |

| coreExcl <sub>ij</sub> | general term of the matrix defining the task-to-core exclusion constraints  |

| 55                     | for a given software and hardware platforms in the one-to-one integration   |

|                        | strategy                                                                    |

| $Clk_p$                | clock frequency of core p                                                   |

| $\frac{Clk}{Clk}$      | core clock frequency whenever all cores are defined with the same value of  |

|                        | clock frequency                                                             |

| $C_{SW_p}$             | upper-bound of the context switch overhead of the core $p$                  |

| $C_{SW}$               | context switch overhead whenever all cores have the same value of context   |

| 5.00                   | switch overhead upper-bound                                                 |

| $D_i$                  | deadline of $\tau_i$                                                        |

| $d_{INT}$              | function computing, for a given task, its WCET and maximum                  |

|                        | number of memory access requests per execution, an upper-bound              |

|                        | of the maximum total latency suffered by the task from the moment           |

|                        | the corresponding memory access requests are issued by the corresponding    |

|                        | core, to the moment they are serviced by the interconnect                   |

|                        | and transmitted to the corresponding memory controller                      |

| d <sub>RAM</sub>       | function computing, for a given task, its WCET and maximum                  |

|                        | number of memory access requests per execution, an upper-bound              |

|                        | of the maximum total latency suffered by the task from                      |

|                        | the moment the corresponding memory access requests are transmitted to      |

|                        | the corresponding memory controller, to the moment when the                 |

|                        | requests are serviced                                                       |

| $d_{RAM_{method_1}}$   | definition of function $d_{RAM}$ using a first computational method         |

| $method_1$             | (see chapter 5) $a_{RAM}$ using a met comparational method                  |

| draw                   | definition of function $d_{RAM}$ using a second computational method        |

| $d_{RAM_{method_2}}$   | (see chapter 5) (see chapter 5)                                             |

| DRAMSIZE               | total size of the main memory                                               |

| DIAMOILE               | total size of the main memory                                               |

| $E_i^k$                  | upper-bound of the maximum total CPU time budget required by the tasks                     |

|--------------------------|--------------------------------------------------------------------------------------------|

|                          | of $\pi_i$ for their respective executions in the $k^{th}$ window of $\pi_i$               |

| gMAF                     | MAjor time Frame in the one-to-all integration strategy                                    |

| gMIF                     | MInor time Frame in the one-to-all integration strategy                                    |

| $H_i$                    | vector gathering the maximum number of requests to the main memory                         |

|                          | $\tau_i$ can generate in one execution                                                     |

| ~                        | depending on the core on which it is executed                                              |

| $H_i^p$                  | maximum number of requests to the main memory $\tau_i$ can generate in                     |

|                          | one execution when running on core $p$                                                     |

| $hp(\tau_i)$             | set of tasks having an equal or higher priority than the priority of $\tau_i$              |

| $ipc_{ij}$               | general term of the matrix specifying inter-partition communications<br>between partitions |

| $isPreemptive_i$         | boolean parameter defining whether tasks of $\pi_i$ are all preemptive or                  |

| _                        | non-preemptive                                                                             |

| $isSharingMS_{pq}$       | in the one-to-one integration strategy, general term of                                    |

| 11                       | the matrix identifying couples of cores $(p,q)$ of the multicore platform                  |

|                          | which contain tasks or partitions that share access to at                                  |

|                          | least one memory controller                                                                |

| $isSharingMS_{pqj}$      | in the one-to-all integration strategy, and for a                                          |

| 5                        | given partition $\pi_i$ , general term of the matrix identifying                           |

|                          | couples of cores $(p,q)$ of the multicore platform which contain tasks                     |

|                          | of $\pi_i$ that share access to at least one                                               |

|                          | memory controller                                                                          |

| $JD_p^{inter}$           | inter-bank interference a task located on core $p$ can                                     |

| P                        | suffer during its execution in the one-to-one                                              |

|                          | integration strategy in the second computational method                                    |

| $JD_p^{intra}$           | intra-bank interference a task located on core $p$ can                                     |

| p                        | suffer during its execution in the one-to-one                                              |

|                          | integration strategy in the second computational method                                    |

| $JD_{pj}^{inter}$        | inter-bank interference a task of $\pi_j$ located on core p can                            |

| pj                       | suffer during its execution in the one-to-all                                              |

|                          | integration strategy                                                                       |

| $JD_{pj}^{intra}$        | intra-bank interference a task of $\pi_i$ located on core $p$ can                          |

| $o D_{pj}$               | suffer during its execution in the one-to-all                                              |

|                          | integration strategy                                                                       |

| $J_i$                    | jitter upon first activation of $\tau_i$                                                   |

| $\frac{v_i}{L}$          | row-conflict service time                                                                  |

| $\frac{L}{latest_i^k}$   | jitter upon activation of the $k^{th}$ CPU time window of $\pi_i$                          |

| •                        | latency corresponding to one main memory request traversing the                            |

| $l_{bus}$                | interconnect                                                                               |

| l <sub>max</sub>         | maximum memory request service latency, corresponding to the                               |

| °max                     | worst-case scenario (row conflict, etc.)                                                   |

| MAF <sub>p</sub>         | MAjor time Frame on core $p$ in the one-to-one integration strategy                        |

| $\frac{mAP_p}{mcSize_i}$ | total size of the main memory area accessible from the memory                              |

|                          | controller $i$                                                                             |

| MIF <sub>p</sub>         | MInor time Frame on core $p$ in the one-to-one integration strategy                        |

| *                        | general term of the matrix specifying message-based communications                         |

| $msg_{ij}$               | between tasks                                                                              |

| na··                     | general term of the matrix defining the task-to-core allocation in the                     |

| $na_{ij}$                |                                                                                            |

|                          | one-to-all integration strategy                                                            |

| $nbActiv_i$                 | total number of executions of $\tau_i$ in one MAF                                                               |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

| $nbCacheLines_p$            | number of cache lines of the L1 cache of core $p$                                                               |

| $nbWindows_i$               | total number of CPU time windows reserved for $\pi_i$ in one MAF                                                |

| N <sub>C</sub>              | number of cores available on the multicore platform and considered                                              |

|                             | for active usage at runtime                                                                                     |

| $nFrames_i$                 | total number of frames in the partition cycle of $\pi_i$                                                        |

| nFrames                     | total number of frames in the MAF                                                                               |

| $N_{MC}$                    | total number of memory controllers – also referred to as memory                                                 |

|                             | paths – available in the hardware platform                                                                      |

| $N_T$                       | total number of tasks integrated onto the same multicore platform                                               |

| $N_{T_{as_a}}$              | total number of tasks developed by supplier $as_a$                                                              |

| $N_P$                       | total number of partitions integrated onto the same multicore platform                                          |

| $N_{P_{asa}}$               | total number of partitions developed by supplier $as_a$                                                         |

| $overlapping_{ijkl}$        | general term of the matrix identifying couples of task instances                                                |

| ·                           | $(\tau_i^k, \tau_j^l)$ scheduled at least partially in parallel on different cores                              |

|                             | of the multicore platform                                                                                       |

| $p2mc_{ij}$                 | general term of the matrix defining the partition-to-memory                                                     |

| U U                         | controller – also referred to as partition-to-memory path – in                                                  |

|                             | the one-to-one integration strategy                                                                             |

| $\mathcal{P}^{as_a}$        | set of partitions of all applications integrated onto the same                                                  |

|                             | multicore platform                                                                                              |

| PART <sub>ij</sub>          | general term of the matrix defining the task-to-partition allocation                                            |

| $\pi_i$                     | $i^{th}$ partition of the software platform, i e partition which identifier is $i$                              |

| $\frac{1}{P_i}$             | period of repetition of $\pi_i$                                                                                 |

| $\frac{i}{pid_i}$           | identifier of the partition to which $\tau_i$ belongs                                                           |

| $\frac{P_{i}}{pO_{i}^{k}}$  | start date of the $k^{th}$ time window of $\pi_i$                                                               |

| $\frac{1}{pPrec_{ij}}$      | general term of the matrix specifying inter-partition                                                           |

| 1 1 1 1 1 1                 | precedence relations and/or partitions ordering preferences of system                                           |

|                             | designers and integrators to be enforced in the partition-level schedule                                        |

| $pRam_i^p$                  | size of memory space reserved for $\pi_i$ in the main memory area                                               |

| 1 1                         | accessible from the $p^{th}$ memory controller                                                                  |

| $prec_{ij}$                 | general term of the matrix specifying inter-task precedence relations                                           |

| $\frac{prio_i}{prio_i}$     | priority of $\tau_i$                                                                                            |

| $\frac{\frac{1}{R_i}}{R_i}$ | worst-case response time (WCRT) of $\tau_i$ computed during the                                                 |

| - 01                        | schedulability analysis                                                                                         |

| $R_i^k$                     | WCRT of $\tau_i^k$                                                                                              |

| $\frac{R_i}{RD_p^{inter}}$  | inter-bank interference a task located on core $p$ can suffer during                                            |

| p                           | its execution in the one-to-one integration strategy                                                            |

|                             | in the first computational method                                                                               |

| $RD_p^{intra}$              | intra-bank interference a task located on core $p$ can suffer during                                            |

| $hD_p$                      |                                                                                                                 |

|                             | its execution in the one-to-one integration strategy                                                            |

| Dinter                      | in the first computational method inter bank interference a task of $\pi$ located on each on some number during |

| $RD_{pj}^{inter}$           | inter-bank interference a task of $\pi_j$ located on core p can suffer during                                   |

|                             | its execution in the one-to-all integration strategy                                                            |

| DDintra                     | in the first computational method                                                                               |

| $RD_{pj}^{intra}$           | intra-bank interference a task of $\pi_j$ located on core $p$ can suffer during                                 |

|                             | its execution in the one-to-one integration strategy                                                            |

|                             | in the first computational method                                                                               |

| reorder                                                                 | delay suffered by a memory request due to the reordering effect            |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|

| $shared_{pq}$                                                           | general term of the matrix defining whether cores $p$ and $q$ share        |

|                                                                         | access to some main memory area in the one-to-one integration              |

|                                                                         | strategy                                                                   |

| $shared_{pqj}$                                                          | general term of the matrix defining whether, for a given partition         |

|                                                                         | $\pi_j$ , cores p and q schedule tasks of $\pi_j$ that share access to     |

|                                                                         | some main memory area in the one-to-all integration strategy               |

| $t2mc_{ij}$                                                             | general term of the matrix defining the task-to-memory controller – also   |

|                                                                         | referred to as task-to-memory path – in the one-to-all integration         |

|                                                                         | strategy                                                                   |

| $	au_i$                                                                 | $i^{th}$ task of the considered task set, i e task which identifier is $i$ |

| $\frac{ \begin{matrix} \tau_i \\ \tau_i^k \\ \mathcal{T} \end{matrix} $ | $k^{th}$ execution instance of $\tau_i$                                    |

| $\mathcal{T}$                                                           | set of tasks of all applications integrated onto the same multicore        |

|                                                                         | platform                                                                   |

| $\mathcal{T}^{as_a}$                                                    | set of tasks of all applications designed by supplier $as_a$               |

| $T_i$                                                                   | period of repetition of $\tau_i$                                           |

| $taskCoreAff_{ij}$                                                      | general term of the matrix defining the task-to-core affinities for a      |

|                                                                         | given software and hardware platforms in the one-to-all                    |

|                                                                         | integration strategy                                                       |

| $taskCoreExcl_{ij}$                                                     | general term of the matrix defining the task-to-core exclusion             |

|                                                                         | constraints for a given software and hardware platforms in the             |

|                                                                         | one-to-all integration strategy                                            |

| $tO_i^k$                                                                | start date of the execution of $\tau_i^k$                                  |

| $tRam_i$                                                                | memory footprint of $\tau_i$                                               |

| $u_i$                                                                   | utilization ratio of $\tau_i$ , also referred to as workload of $\tau_i$   |

| $w_i$                                                                   | worst-case execution time (WCET) of $\tau_i$                               |

| $w_i^k$                                                                 | WCET of $\tau_i^k$                                                         |

| W(t)                                                                    | workload of a processing resource in a time interval $[0, t[$              |

### Résumé

Les contentions apparaissant au niveau des ressources partagées par les coeurs d'un multicoeur sont problématiques pour les systèmes temps réel critiques. C'est en particulier le cas pour l'industrie aérospatiale, où il est impératif d'assurer un comportement temporel sain de tout système, et ce en avance de phase dans le cycle de développement. Etre capable de prédire le respect de toutes les échéances temporelles d'un système dans n'importe quelle situation pouvant être rencontrée en temps-réel dans l'environnement du système sous étude est indispensable pour obtenir les accréditations délivrées par les autorités de certification au niveau logiciel.

Le but de cette thèse est de proposer une approche pour le portage d'applications IMA (Avionique Modulaire Intégrée) préexistantes sur plateforme multicoeur, et ce sans modification majeure tant au niveau logiciel que matériel. L'objectif final de la thèse est de proposer une approche qui respecte les objectifs de certification appliqués au développement de calculateurs logiciels; cela implique aussi bien les contraintes de certification incrémentale, que le respect des concepts clés de l'IMA, à savoir le partitionnement spatial et temporel des applications intégrées sur le même module multicoeur.

Cette thèse intervient dans le cadre d'un contrat CIFRE (Contrat de d'Initiation à la Formation à la Recherche en Entreprise), à la demande d'Airbus Group Innovations Toulouse. Ainsi, une volonté additionnelle aux objectifs de la thèse et d'importance majeure est celle de suivre le plus possible les process intervenant dans les cycles de développement de logiciel IMA tels qu'ils existent aujourd'hui chez Airbus, pour des calculateurs basés single-core. Si l'on propose une méthodologie d'intégration multicoeur qui possède un maximum de similitudes avec le process d'intégration actuelle, cela augmente les chances des contributions de cette thèse d'être exploités en entreprise dans les plus brefs délais, l'effort à fournir pour proposer une nouvelle façon de travailler à des centaines de personnes expérimentées et habituées aux process existants depuis un certain nombre d'années étant généralement significatif. Il est notamment plus facile de convaincre des personnes de passer à une nouvelle méthodologie si l'effort d'adaptation est moindre, c'est-à-dire si les étapes impliquées dans la nouvelle méthodologie ne sont pas très différents de celles dans l'ancienne méthodologie. De plus, l'efficacité de la nouvelle approche est plus facile à prouver si l'approche ressemble aux process actuels, dont l'efficacité pour obtenir l'accord des autorités de certification n'étant en général plus à prouver.

Enfin, un objectif secondaire de la thèse est de chercher à optimiser au maximum les architectures intégrées résultant de l'étape d'intégration logicielle/matérielle. Si possible, une ou plusieurs des étapes de la méthodologie d'intégration multicoeur devraient être automatisées, de manière à accélérer les études de choix d'architecture tout en orientant la sélection finale vers des conceptions optimisant les critères de performance les plus pertinents pour l'industrie aérospatiale. L'automatisation permet également la réduction du temps et effort à fournir pour les tests et vérifications impliqués dans le cycle d'intégration, et ainsi de réduire le time-tomarket du système avionique complet.

Cette thèse propose deux méthodologies complètes pour l'intégration IMA sur COTS (Component Off the Shelf, ou composant sur étagère) multicoeur. Toutes deux offrent des avantages différents et s'utilisent dans des situations complémentaires. Au final, il s'avèrera que les méthodologies proposées dépassent le cadre fixé originellement dans cette thèse: elle peuvent s'utiliser dans le cadre de développement de nouveau logiciel, qu'il soit IMA ou non, tant que l'architecture visée est basée sur des multicoeurs.

L'une des deux méthodologies, appelée "one-to-all integration strategy", correspond à la situation où, à un instant donné, tous les coeurs sont utilisés au service d'une seule et même partition. Cette stratégie respecte tous les objectifs de certification, y compris le développement, la vérification et certification incrémentale, mais aussi le partitionnement robuste (spatio-temporel) des applications. La stratégie "one-to-one" reste pertinente pour tous les niveaux de criticité logicielle, y compris pour les applications DAL A (le plus haut niveau de criticité). Pour ces raisons, la stratégie "one-to-one" peut être vue comme la stratégie ayant le plus de chance d'être exploitée par l'industrie aérospatiale à l'issue de cette thèse.

La seconde stratégie, nommée "one-to-one integration strategy" correspond à la situation où chaque coeur du multicoeur a son propre schedule et ordonnance son lot de partitions indépendamment. Elle peut être utilisée pour des applications IMA jusqu'au niveau de criticité DAL C, pour une application multipartitions jusqu'au DAL A, ou encore pour tout logiciel temps-réel critique non IMA.

Les deux méthodologies d'intégration proposées sont qualifiées de "complètes" car elles contiennent:

- Une analyse temporelle statique qui borne les interférences inter-coeurs et permet de dériver des bornes supérieures de WCETs de manière fiable;

- Une formulation de problème de programmation par contraintes (PPC) pour l'allocation automatique et optimisée de logiciel sur matériel; la configuration résultante est correcte par construction car le problème de PPC exprimé exploite l'analyse temporelle mentionnée précédemment pour effectuer une vérification temporelle sur chaque configuration testée.

- Une formulation de problème de PPC pour la génération d'ordonnancement automatique et optimisé; la configuration résultante est correcte par construction car le processus exploite l'analyse temporelle mentionnée précédemment pour effectuer une vérification temporelle sur chaque configuration testée.

### Abstract

Interference in multicores is undesirable for hard real-time systems, especially in the aerospace industry for which it is mandatory to ensure beforehand timing correctness and deadline enforcement in a system runtime behavior, to be granted acceptance by certification authorities.

The goal of this thesis is to propose an approach for multi-core integration of legacy Integrated Modular Avionics (IMA) software, without any hardware nor software modification, and which complies as much as possible to current, incremental certification and IMA key concepts such as robust time and space partitioning. The motivation of this thesis, supported by Airbus Group Innovations as an industrial PhD contract, is to stick as much as possible to the current IMA software integration process to maximize the chances of having avionics industries apply the contributions of this thesis to their future systems. Another reason is that the current process has long been proven efficient on aerospace systems currently in usage. A third motivation is to minimize the extra effort needed to provide certification authorities with timing-related verification information required when seeking approval. As a secondary goal, depending on the possibilities, the contributions should offer design optimization features, and help reduce the time-to-market by automating some steps of the design and verification process.

This thesis proposes two complete methodologies for IMA integration on multi-core Components Off The Shelf (COTS). Each of them offers different advantages and has different drawbacks, and therefore each of them may correspond to its own, complementary situations. One of the two proposed strategies fits all avionics and certification requirements of incremental verification and robust partitioning, and can therefore be used for applications with the highest criticality level, also referred to as Design Assurance Level (DAL) A. The other strategy proposed in this thesis offers maximum Size, Weight and Power (SWaP) optimization, and fits either up to DAL C applications, multipartition applications or even non-IMA applications.

The methodologies are said to be "complete" because this thesis provides all necessary techniques to go through all steps of the software integration process. More specifically, this includes for each strategy:

- Static timing analysis metrics for safely upper-bounding inter-core interference, and deriving safe WCET upper-bounds for each task. Both feasibility and schedulability analysis are considered in this thesis for multicore-based IMA systems.

- A Constraint Programming (CP) formulation of the software/hardware allocation problem for multicore-based IMA systems. Proposing a CP formulation enables the automation of the design space exploration and allocation configuration. The allocation selected at the end of the CP solving process is correct by construction since the CP problem embraces one of the proposed timing analysis mentioned earlier.

- A CP formulation of the schedule generation for multicore-based IMA systems. As for the allocation, proposing a CP formulation enables the automation of the design space exploration and schedule generation process. The schedule generated at the end of the CP solving process is correct by construction since the CP problem embraces the proposed timing analysis mentioned earlier.

## Résumé Etendu

#### Motivations

Pour les systèmes temps-réel dur, il est tout aussi important d'obtenir des résultats exacts, que de les obtenir à temps. En particulier pour les systèmes avioniques, des résultats corrects obtenus en retard, soit après l'échéance qui a été défini pour le calcul de ces résultats, peuvent conduire à un dysfonctionnement majeur au niveau du système avion complet, avec des conséquences graves telles que la mort des passagers de l'avion et la perte de l'avion.

Pour que ce genre de situation ne se produise jamais, les systèmes avioniques font l'objet d'un cycle de conception et de vérification strictement réglementé, couplé à un processus de certification strict avant d'être jugés opérationnels puis commercialisés. Par exemple, en ce qui concerne les logiciels critiques embarqués dans un système avionique, chaque opération de logiciel doit être analysée au moment du design afin de dériver un majorant supérieur des temps d'exécution pire cas (aussi notés WCET, pour Worst Case Execution Time) de chaque traitement défini dans le logiciel, de manière à pouvoir vérifier la validité des échéances associées, configurer en avance de phase le plan d'ordonnancement, i.e. les enchaînements des traitements logiciels dans le temps, et vérifier que toutes les échéances seront toujours respectées à l'exécution pendant tout le temps de vol de l'avion. Une fois que le résultat d'une telle vérification montre le respect de toutes les échéances, le résultat et le processus de vérification lui-même peuvent être montrés aux autorités de certification comme justification d'un comportement temps-réel sain, prouvé en avance de phase.

La certification d'un avion est cruciale pour sa commercialisation. Au niveau logiciel, elle implique un respect d'un certain nombre d'objectifs définis par les autorités. Chercher à réspecter ces objectifs et le prouver représentent une part importante de l'effort de conception et vérification dans le cycle de vie d'un logiciel avionique, afin d'assurer sa conformité aux réglementations de certification. Cela s'applique non pas seulement au logiciel, mais à tout sous-système constituant l'avion. Chaque fois qu'une modification est effectuée sur une partie d'un système avionique, toutes les parties de ce système qui sont impactées par les modifications doivent être re-vérifiées, et leur conformité à la réglementation de certification à nouveau prouvée.

Une manière efficace d'essayer de réduire le temps et les efforts passés à gérer des modifications de conception consiste à adopter une approche de conception modulaire et indépendante. Par exemple, l'ensemble des logiciels intégrés dans un système avionique représentent plusieurs applications qui ne sont pas nécessairement développées par le même fournisseur. D'un autre côté, chaque application est développée indépendamment l'une de l'autre, peu importe le fournisseur, pour des raisons de sécurité. Cela permet également de s'assurer que chaque application peut être analysée indépendamment l'une de l'autre, de sorte que la modification d'une fonction n'ait aucun impact sur les autres fonctions. En tant que tel, seules les fonctions modifiées devront être ré-vérifiées; Le processus de développement, de vérification et de certification permettant ce genre d'indépendance est dit *incremental* [172].

En plus de la certification incrémentale, l'architecture IMA (Avionique Modulaire Intégrée) [1] favorise la modularité des systèmes avioniques. Dans les architectures IMA, une application logicielle est divisée en sous-éléments exécutés strictement indépendamment les uns des autres à l'exécution, ce qui assure une isolation temporelle et spatiale de ces sous-éléments entre eux. Une telle séparation est souvent appelée *partitionnement robuste*.

En résumé, les concepts de certification incrémentale et d'architecture IMA assurent la modularité d'un système avionique, et nécessitent une stratégie de vérification qui conserve l'esprit de séparation et isolation des applications et sous-élements des applications. Chaque fournisseur d'application décide comment découper une application en sous-éléments indépendants. Pour cette raison, les fournisseurs d'applications discutent avec les concepteurs de l'avion en cours de développement; la connaissance et l'expérience des fournisseurs d'applications et des concepteurs de systèmes avioniques sont essentielles pour certifier les systèmes avioniques.

Tout logiciel est exécuté sur une plateforme matérielle sur laquelle un processeur au moins est présent. En règle général pour des systèmes aussi critiques que les systèmes aérospatiaux, la tendance est d'exploiter des processeurs sortis sur le marché depuis déjà quelques années, dont les processeurs précédents de la meêm famille ont en général un historique d'utilisation dans l'industrie aérospatiale conséquent, mais surtout qui sont jugés suffisamment fiables par des concepteurs de systèmes experts dans le domaine de l'embarqué temps-réel critique.

La motivation principale d'un tel choix est de pouvoir compter sur des plateformes électroniques qui ont eu le temps d'être testée de manière approfondie, et qui se sont avérées compatibles avec toutes les exigences des systèmes avioniques dans lesquels elles ont été exploitées. Une autre motivation est de faciliter la conception des futurs systèmes avioniques, car il est plus facile de réutiliser une plateforme matérielle dont les caractéristiques temps-réel et comportementales sont bien connues par expérience du fait de son utilisation dans un programme avion antérieur.

Jusqu'à présent, les plateformes matérielles embarquées dans les systèmes avioniques ne contiennent que des processeurs monocoeur. Depuis quelques années, les processeurs multicoeur - jusqu'à 8 ou 16 coeurs sur une même puce - et manycore - des centaines de coeurs sur une puce organisée en plusieurs tuiles et reliées par un réseau sur puce – ont fait leur apparition sur le marché de l'électronique. Chaque coeur supplémentaire sur une puce permet d'augmenter le nombre d'instructions logicielles traitées à un instant donné, améliorant ainsi les performances du système concerné. En l'occurrence, les derniers ordinateurs et téléphones mobiles proposés au grand public ont pu bénéficier d'un gain de performance significatif en embarquant de telles architectures. Le marché de l'électronique évoluant à une très grande vitesse, il suffit de six mois depuis la sortie d'un composant électronique sur le marché pour que celui-ci devienne obsolète. C'est le cas pour les processeurs; en particulier, maintenant que les fondeurs de processeur ont trouvé comment intégrer plus d'un coeur à une puce de processeur, les architectures monocoeur ne vont plus être poursuivies. Cela constitue un problème pour l'industrie avionique, dont tous les systèmes, les études de comportement temporel, l'expérience passée, repose sur l'utilisation de processeurs monocoeurs. Les systèmes aérospatiaux en général ne représentent pas une part de marché assez intéressante pour les fabricants de processeurs pour que ces derniers acceptent de poursuivre la production de processeurs monocoeurs exploités dans les systèmes avioniques. Par conséquent, l'industrie aérospatiale n'a guère d'autre choix que de s'adapter à l'évolution du marché électronique, et ainsi de passer à des architectures multi- ou manycoeurs.

Dans la mesure où le nombre d'applications logicielles, et plus généralement le nombre de lignes de code embarquées dans un avion augmente au fil des programmes, l'avènement des multimanycoeurs peut s'avérer bénéfique pour l'industrie avionique. En effet, une unique plateforme multicoeur pourrait potentiellement remplacer autant de plateformes monocoeurs qu'il n'y a de coeurs dans le multicoeur exploité. Cela permettrait de réduire le poids et volume total de l'avion, sans compter le nombre de câbles à embarquer pour relier l'ensemble des plateformes embarquées, et le besoin en énergie nécessaire pour alimenter toutes ces plateformes matérielles tout le long de la mise en service de l'avion.

Cependant, passer au multicoeur dans les systèmes avioniques soulève un certain nombre de challenges [109]. En particulier, l'ensemble des procédures et standards intervenant dans les différentes phases de développement d'un calculateur embarqué doivent auparavant être mises à jour car elles sont adaptées aux architectures monocoeur et ne permettent pas de couvrir les cas multicoeurs, où plus d'un traitement logiciel est exécuté à chaque instant. En particulier, la vérification du bon comportement temporel et la preuve du respect des objectifs de certification associés sont plus complexes à mettre en oeuvre. L'utilisation d'un multicoeur dans un avion, avec plus d'un coeur exécutant des traitements applicatifs à chaque instant, ne sera pas possible tant que ces points ne seront pas réglés au préalable.

Un exemple concret de standard devant être mise à jour pour inclure le cas multicoeur est le standard définissant la manière dont un logiciel IMA doit s'interfacer avec toute plateforme matérielle sur laquelle il s'exécutera. En particulier, la mise à jour de ce standard devra prendre en considération l'indépendance des applications s'exécutant en simultané sur des coeurs différents, malgré le partage de ressources matérielles entre les coeurs d'un même processeur. Cela représente un challenge significatif. En effet, en raison des accès simultanés aux ressources partagées à l'intérieur de la puce multicœur qui se produisent au moment de l'exécution, l'isolement temporel est difficile à réaliser au moment de l'exécution sur une plateforme multicoeur.

De manière générale, toutes les activités d'analyse et de vérification habituellement menées dans un cycle de conception de logiciel temps-réel embarqué doivent être mises à jour avec des outils et des techniques capables d'analyser des plateformes multicœurs. Les interférences inter-core au moment de l'exécution doivent être majorées en toute sécurité lors de l'analyse des temps d'exécution pire cas des traitements logiciels, afin de pouvoir configurer en toute sécurité en avance le comportement d'exécution du système au moment du design. C'est seulement après de telles mises à jour que les concepteurs de systèmes seraient en mesure d'utiliser correctement les plates-formes multicœurs pour les systèmes aérospatiaux, mais aussi de pouvoir petit à petit reconstruire les connaissances et le savoir-faire nécessaires pour maîtriser les systèmes avioniques multicœurs pour faciliter la réutilisation de plateformes similaires dans les programmes suivants.

L'apparition d'interférence inter-coeur à l'exécution pose problème à la vérification du comportement temporel d'un logiciel, principalement en raison du manque actuel d'outils ou de techniques permettant de produire un majorant des WCET de tâches exécutées dans un environement multicoeur [171]. Les demandes simultanées d'accès aux ressources générées par chaque coeur provoquent des délais d'attente d'accès aux ressources qui viennent s'ajouter au temps d'exécution du code associé à chaque tâche. Ces délais supplémentaires augmentent les temps d'exécution des tâches de manière plus ou moins significative suivant le multicoeur et le logiciel considéré. Le niveau de complexité de l'analyse à mener d'une part, et le couplage du partage des ressources dans les multicoeurs d'autre part, sont tels que l'analyse temporelle devient intractable, sinon trop pessimiste lorsqu'on essaie de réutiliser les techniques monocoeur actuelles en modélisant un environnement multicoeur. D'autant plus qu'il est encore impossible de modéliser une architecture multicoeur avec autant de précision qu'une architecture monocoeur même si on parvient à maîtriser la complexité des couplages impliqués par l'architecture. En effet, le manque d'information de conception par souci de protection d'IP par les fabricants de processeur, rendent la tâche encore plus délicate. Il ne suffit pas de trouver une technique d'analyse temporelle multicoeur; il faut aussi pouvoir contourner le manque d'information sur certaines ressources partagées à l'origine de délais d'interférence, comme les bus d'interconnexion entre les coeurs et les périphériques du processeur par exemple.

Aujourd'hui, il n'existe aucune solution pour l'analyse exhaustive de WCET sur multicoeur. Sans une telle solution, les contentions au niveau des ressources partagées ne peuvent pas être modélisées et majorées de manière absolue, de sorte qu'il n'y a aucun moyen de configurer à l'avance un plan d'ordonnancement dont on puisse apporter la preuve que toutes les échéances du système seront toujours respectées à l'exécution. Un tel manque de techniques d'analyse met en péril l'exploitation de platesformes multicoeur dans les systèmes aérospatiaux, ce qui en fait l'un des sujets de recherche les plus étudiés, dans le milieu académique mais aussi dans l'industrie aérospatiale et automobile. [90, 129, 119, 66, 64].

La littérature est pleine de diverses propositions pour aborder les problèmes posés par le multicoeur [64]:

- Certains travaux proposent de nouvelles couches middleware pour surveiller tous les accès aux ressources matérielles partagées, afin d'imposer des comportements d'exécution déterministes en éliminant les interférences inter-core à l'exécution [46];

- D'autres travaux proposent de nouvelles architectures multicoeur dédiées dans lesquelles chaque coeur possèderait ses propres ressources privées [7, 181, 149];

- Des travaux similaires se focalisent sur l'implémentation de composants hardware permettant de contrôler le partage de ressources, en espérant voir ces composants intégrés aux futures générations de COTS multicoeurs [111, 130, 170];