## Efficient Hardware-aware Neural Architecture Search for Edge Computing

Hadjer Benmeziane

## ▶ To cite this version:

Hadjer Benmeziane. Efficient Hardware-aware Neural Architecture Search for Edge Computing. Machine Learning [cs.LG]. Université Polytechnique Hauts-de-France, 2023. English. NNT: 2023UPHF0022. tel-04224035

## HAL Id: tel-04224035 https://theses.hal.science/tel-04224035v1

Submitted on 1 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Thèse de doctorat

## Pour obtenir le grade de Docteur de

## I'UNIVERSITE POLYTECHNIQUE HAUTS-DE-FRANCE

## et de l'INSA HAUTS-DE-FRANCE

Discipline, spécialité selon la liste des spécialités pour lesquelles l'Ecole Doctorale est accréditée :

### Intelligence Artificielle et Systèmes Embarqués

#### Présentée et soutenue par Hadjer Benmeziane

Le 30/08/2023, à Valenciennes

Ecole doctorale :

Ecole Doctorale Polytechnique Hauts-de-France (ED PHF n°635)

#### Unité de recherche :

Laboratoire d'Automatique, de Mécanique et d'Informatique Industrielles et Humaines (UMR CNRS 8201)

## Optimisation Automatique des Applications d'Apprentissage Profond sur Plateformes Matérielles Edges

## Président de jury

• Cucu-Grosjean, Liliana. Directrice de recherche. INRIA, Rocquencourt, France.

### JURY

#### Rapporteurs

- Sassatelli, Gilles. Directeur de recherche. CNRS, LIRMM, Univ Montpellier.

- Shafique, Muhamed. Professeur. New-York University, Abu-Dhabi.

#### Examinateurs

• Cucu-Grosjean, Liliana. Directrice de recherche. INRIA, Rocquencourt, France.

#### Invités

• Meyer, Brett. Assistant Professeur. Department of Electrical and Computer Engineering McGill University.

#### Thesis director

• Niar, Smail, Professeur, UPHF, CNRS, UMR 8201 - LAMIH, F-59313 Valenciennes, France.

#### Thesis co-director :

• El Maghraoui, Kaoutar. Principal Research Scientist. IBM T. J. Watson Research Center, Yorktown Heights, NY 10598, USA.

#### Co-supervisor :

• Ouarnoughi, Hamza. Professeur. UPHF, CNRS, UMR 8201 - LAMIH, F-59313 Valenciennes, France.

## **PhD Thesis**

## Submitted for the degree of Doctor of Philosophy from

## UNIVERSITE POLYTECHNIQUE HAUTS-DE-FRANCE

## and INSA HAUTS-DE-FRANCE

Subject :

Artificial Intelligence and Embedded Systems

Presented and defended by Hadjer Benmeziane.

## On 30/08/2023, LAMIH

**Doctoral school :** Doctoral School Polytechnique Hauts-de-France (ED PHF n°635)

Research unit :

Laboratory of Industrial and Human Automation control Mechanical engineering and Computer science (LAMIH – UMR CNRS 8201)

## Efficient Hardware-aware Neural Architecture Search for Edge Computing

## President of jury

• Cucu-Grosjean, Liliana. Research Director. INRIA, Rocquencourt, France.

## JURY

#### Reviewers

- Sassatelli, Gilles. Research Director. CNRS, LIRMM, Univ Montpellier.

- Shafique, Muhamed. Professor. New-York University, Abu-Dhabi.

#### Examiners

• Cucu-Grosjean, Liliana. Research Director. INRIA, Rocquencourt, France.

#### Invitee

• Assistant Professor. Department of Electrical and Computer Engineering McGill University.

#### **Thesis director**

• Niar, Smail, Professor, UPHF, CNRS, UMR 8201 - LAMIH, F-59313 Valenciennes, France.

#### Thesis co-director :

• El Maghraoui, Kaoutar. Principal Research Scientist. IBM T. J. Watson Research Center, Yorktown Heights, NY 10598, USA.

#### Co-supervisor :

• Ouarnoughi, Hamza. Professor. UPHF, CNRS, UMR 8201 - LAMIH, F-59313 Valenciennes, France.

Π

## Abstract

It is widely anticipated that inference models based on Deep Neural Networks (DNN) will be actively employed in many edge platforms due to several compelling reasons. Firstly, DNNs have demonstrated exceptional performance in various fields such as computer vision, natural language processing, and speech synthesis. Their ability to extract meaningful features from large datasets enables them to achieve high levels of accuracy and predictive power, making them indispensable for a wide range of tasks. Secondly, deploying DNN-based inference models directly on edge platforms offers several advantages. For instance, executing the inference process locally on edge devices, reduces the reliance on cloud-based computing, thereby minimizing network latency and ensuring real-time responsiveness. This is particularly crucial for timesensitive applications, such as autonomous vehicles, smart surveillance systems, and Internet of Things (IoT) devices, where rapid decision-making is paramount. Furthermore, employing DNN inference at the edge enhances privacy and security. By keeping sensitive data within the edge device's local environment instead of transmitting it to external servers, the risk of data breaches and privacy violations is significantly reduced. This is of utmost importance in scenarios involving personal data, healthcare information, or confidential business data, where preserving privacy and data sovereignty is imperative.

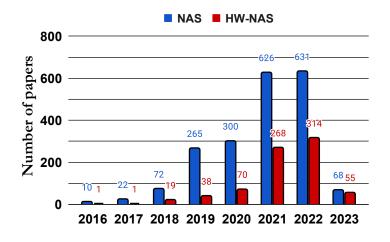

However, edge platforms often operate under resource-constrained environments, characterized by limited computational power, energy constraints, and intermittent connectivity. DNN models are increasingly larger, making them unfit for such platforms. This has promoted research in automatically designing neural architectures through search for such devices. This method is called Hardware-aware Neural Architecture Search (HW-NAS). Such optimization can lead to reduced energy consumption, lower inference latency, and overall improved performance on edge platforms. HW-NAS is the cornerstone of this thesis. HW-NAS can provide both efficient and accurate, customized models for the target platform. This thesis aims at accelerating and generalizing HW-NAS applicability to many platforms and multiple tasks.

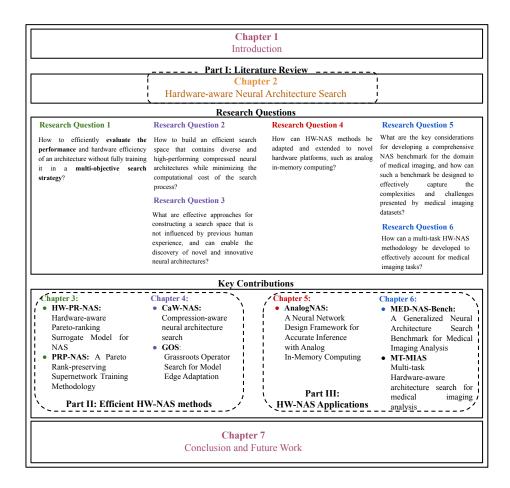

This work introduces innovative solutions to rapidly estimate the efficiency of DNNs for a target HW platform. Our proposed HW-NAS approach encompasses multi-objective optimization techniques, significantly accelerating the search process within sxccupernetwork-based and cell-based search spaces. Within the multi-objective context of HW-NAS, conflicting objectives, such as task-specific performance (e.g., accuracy) and hardware efficiency (e.g., latency and energy consumption), need to be optimized simultaneously. To address this challenge, we define a novel Pareto rank target, leveraging diverse surrogate models employed in HW-NAS. By incorporating multiple objectives and Pareto optimization principles, our approach enables the exploration of trade-offs between task-specific performance and hardware efficiency, ultimately facilitating the identification of superior neural architectures.

We also investigate the human bias induced by current search spaces and propose a non-restrictive search space to find novel operators tailored to a target hardware platform. These methods were validated on image classification benchmarks. We then show how to apply HW-NAS for novel hardware architectures, namely analog in-memory computing hardware.

Finally, we construct a medical imaging NAS benchmark that includes architectures for 11 tasks, including their performance, latency, and energy consumption on several devices, and propose a new HW-NAS approach that, not only includes accuracy and latency as objectives, but also looks for a generalizable architecture that can be fine-tuned for unseen medical tasks.

**Keywords** Neural Architecture Search, Hardware constraints, Optimization, Edge AI

## Résumé

Les modèles d'inférence basés sur les réseaux neuronaux profonds (eng, Deep Neural Networks (DNN)) sont largement utilisés dans de nombreuses platesformes de périphérie pour plusieurs raisons. Premièrement, les DNN ont démontré des performances exceptionnelles dans divers domaines tels que la vision par ordinateur, le traitement du langage naturel et la synthèse vocale. Leur capacité à extraire des caractéristiques significatives à partir de grands ensembles de données leur permet d'atteindre des niveaux jamais atteints de précision et de puissance prédictive, ce qui les rend indispensables pour une large gamme d'applications. Deuxièmement, le déploiement de ces modèles directement sur les plateformes de périphérie offre plusieurs avantages. L'exécution du processus d'inférence localement sur les dispositifs de périphérie réduit la dépendance à l'égard du calcul basé sur le cloud, réduisant ainsi la latence du réseau et garantissant une réactivité en temps réel.

Cependant, les plateformes de périphérie fonctionnent souvent dans des environnements contraints en ressources, caractérisés par une puissance de calcul limitée, des contraintes énergétiques et une connectivité intermittente. Les modèles DNN ne sont par défaut pas adaptés à de telles plateformes. Cela a encouragé la recherche sur la conception automatique d'architectures neuronales adaptées à ces dispositifs. Cette méthode est appelée recherche d'architecture neuronale à contraintes matérielles (eng, Hardware-aware Neural Architecture Search, HW-NAS). HW-NAS est la pierre angulaire de cette thèse. HW-NAS peut fournir des modèles à la fois efficaces et précis. Cette thèse vise à accélérer et à généraliser l'applicabilité de HW-NAS à de nombreuses plateformes et à plusieurs tâches. Ce travail de thèse propose des solutions novatrices pour estimer rapidement l'efficacité d'un DNN déployé sur une plateforme matérielle cible. Notre approche HW-NAS englobe des techniques d'optimisation multi-objectifs, ce qui accélère considérablement le processus de recherche à la fois dans les espaces de recherche basés sur les supernetworks et sur les cellules. Dans le contexte multi-objectif de HW-NAS, des objectifs conflictuels, tels que les performances spécifiques à la tâche (par exemple, la précision) et l'efficacité matérielle (par exemple, la latence et la consommation d'énergie), doivent être optimisés simultanément. Pour relever ce défi, nous définissons un nouvel objectif de rang de Pareto. En incorporant des objectifs multiples et des principes d'optimisation de Pareto, notre approche permet l'exploration des compromis entre les performances spécifiques à la tâche et l'efficacité matérielle. Nous examinons également le biais humain induit par les espaces de recherche actuels et proposons un espace de recherche non restrictif pour trouver de nouveaux opérateurs adaptés à une plate-forme matérielle cible. Ces méthodes ont été validées sur des référentiels de classification d'images.

Dans la seconde partie de la thèse, nous montrons l'utilité de nos méthodes dans des scénarios réels. Premièrement, comment appliquer HW-NAS à de nouvelles plateformes matérielles, notamment les matériels de calcul analogiques en mémoire (eng, in-memory analog devices). Nous avons proposé un HW-NAS dédié à ces plateformes, et nous déduisons les charactérstiques qui différent un réseaux de neuronnes déployé sur ces plateformes, d'un autre déployé sur des plateformes classiques.

Enfin, nous construisons une référence de recherche d'architectures neuronales pour l'imagerie médicale qui inclut des architectures pour 11 tâches, notamment la detection de tumeurs, la segmentation du foie et l'estimation du volume de l'hippocampe. En utilisant cette référence, nous proposons un nouveau HW-NAS qui inclut non seulement l'exactitude et la latence en tant qu'objectifs, mais cherche également une architecture généralisable qui peut être affinée pour de nouvelles tâches médicales.

Mots clés apprentissage profond, optimisation, contraintes matérielles

III

## Acknowledgments

First and foremost, I would like to thank my thesis director Prof. Smail Niar and my supervisor Prof. Hamza Ouarnoughi at Université Polytechnique des Hauts-de-France. The unique research opportunity they provided has been transformative for my academic journey. With their combined expertise, I navigated the complexities of this thesis, and I deeply value the trust they placed in my abilities and the guidance they offered.

I would also like to extend my profound gratitude to my thesis co-director, Dr. Kaoutar El Maghraoui from IBM T.J Watson. Kaoutar has been more than just a supervisor; she has been a mentor in the truest sense of the word. Her guidance, patience, and dedication have been pivotal in shaping my research perspective. I am especially thankful for the invaluable opportunity she provided by allowing me to intern at IBM. The hours she invested in mentoring me, coupled with the hands-on experience at IBM, have enriched my academic journey and provided me with insights that I will carry with me throughout my career.

Heartfelt appreciation is extended to the esteemed jury members for their invaluable time and dedication in accepting, meticulously reading, and offering constructive feedback on this work.

I am grateful to the many researchers I met during my thesis work. I've collaborated with academics from different backgrounds. At present, I'd like to highlight the following co-authors and/or scientists that reviewed my papers and helped me improve them: Irem Boybat, Abu Sebastian, Manuel Le Gallo, Malte J. Rasch, Corey Lammie, Hsinyu Tsai, Ramachandran Muralidhar, Halima Bouzidi, Lotfi Abdelkrim Mecharbat, Ozcan Ozturk, Amine Ziad Ounnoughene, Imane Hamzaoui, Younes Bouhadjar, Abderaouf Gacem, Afaf Alloulal, Mufida Miratul, Rihab Balti and Meyssa Zouambi.

Last, but certainly not least, I would like to thank my family. Their unwavering support, endless patience, and boundless love have been the pillars upon which I leaned throughout this journey. To my parents, whose sacrifices and teachings have shaped who I am today, I owe a debt of gratitude that words can hardly express. They instilled in me the values and skills to live independently, always grounded by unwavering principles and beliefs that they imparted. To my siblings, for their constant encouragement and belief in my abilities, even more than me. While this achievement is a significant milestone, I recognize it as just the beginning of my research journey. Thank you all for being the foundation upon which I build my future endeavors.

## List of Publications Included in this Thesis

This thesis contains a number of original research articles which have been published during my PhD candidature. These papers have been slightly modified to improve readability and cohesion in the form of a thesis document. In this Section, a list of publications included in this thesis is presented.

### - A Comprehensive Survey on Hardware-aware Neural Architecture Search

[1] Hadjer Benmeziane, Kaoutar El Maghraoui, Hamza Ouarnoughi, Sma¨ıl Niar, Martin Wistuba, and Naigang Wang. A comprehensive survey on hardware-aware neural architecture search. CoRR, abs/2101.09336, 2021.

[2] Hadjer Benmeziane, Kaoutar El Maghraoui, Hamza Ouarnoughi, Smail Niar, Martin Wistuba, and Naigang Wang. Hardware-aware neural architecture search: Survey and taxonomy. In Proceedings of the Thirtieth International Joint Conference on Artificial Intelligence, IJCAI-21, pages 4322–4329, 8 2021.

Location in thesis: Chapter 2

### - Accelerating Neural Architecture Search with Rank-Preserving Surrogate Models

[3] Hadjer Benmeziane, Hamza Ouarnoughi, Kaoutar El Maghraoui, and Smail Niar. Accelerating neural architecture search with rank-preserving surrogate models. In Manar Abu Talib, Laila Benhlima, and Kaoutar El Maghraoui, editors, ArabWIC 2021: The 7th Annual International Conference on Arab Women in Computing in Conjunction with the 2nd Forum of Women in Research, Sharjah, ACM 2021. Location in thesis: Chapter 3

Best Paper Award at ArabWIC 2021

### - Multi-Objective Hardware-Aware Neural Architecture Search with Pareto Rank- Preserving Surrogate Models

[4] Hadjer Benmeziane, Hamza Ouarnoughi, Kaoutar El Maghraoui, and Smail Niar. Multi-objective hardware-aware neural architecture search with Pareto rank-preserving surrogate models. 20(2), 2023. ACM Transactions on Architecture and Code Optimization.

Location in thesis: Chapter 3

### - Pareto rank surrogate model for hardware-aware neural architecture search

[5] Hadjer Benmeziane, Smail Niar, Hamza Ouarnoughi, and Kaoutar El Maghraoui. Pareto rank surrogate model for hardware-aware neural architecture search. In IEEE International Symposium on Performance Analysis of Systems and Software (IS-PASS), 2022.

Location in thesis: Chapter 3

#### - Pareto Rank-Preserving Supernetwork for HW-NAS

[6] Hadjer Benmeziane, Smail Niar, Hamza Ouarnoughi, and Kaoutar El Maghraoui. Pareto rank-preserving supernetwork for hardware-aware neural architecture search. European Conference on Artificial Intelligence ECAI 2023.

Location in thesis: Chapter 3

Best Poster Award at IBM/AICS 2022

### - Grassroots Operator Search for Model Edge Adaptation

[7] Hadjer Benmeziane, Smail Niar, Hamza Ouarnoughi, and Kaoutar El Maghraoui. Grassroots operator search for model edge adaptation. Submitted to Elsevier Future Generation Computer Systems.

Location in thesis: Chapter 4

### - CaW-NAS: Compression-aware Neural Architecture Search

[8] Hadjer Benmeziane, Hamza Ouranoughi, Sma¨ıl Niar, and Kaoutar El Maghraoui. Caw-nas: Compression aware neural architecture search. In 25th Euromicro Conference on Digital System Design, DSD, pages 391–397. IEEE, 2022. Location in thesis: Chapter 4

#### - AnalogNAS: A Neural Network Design Framework for Accurate Inference with Analog In-Memory Computing

[9] Hadjer Benmeziane, Corey Lammie, Irem Boybat, Malte J. Rasch, Manuel Le Gallo, Hsinyu Tsai, Ramachandran Muralidhar, Sma¨ıl Niar, Hamza Ouarnoughi, Vijay Narayanan, Abu Sebastian, and Kaoutar El Maghraoui. Analognas: A neural network design framework for accurate inference with analog in-memory computing. 2023. IEEE International Conference on Edge Computing & Communications. Location in thesis: Chapter 5

Best Paper Award at IEEE Edge 2023

#### - MED-NAS-Bench: A Generalized Neural Architecture Search for Medical Imaging Analysis

[10] Hadjer Benmeziane, Lotfi Abdelkrim Mecharbat, Smail Niar, Hamza Ouarnoughi, and Kaoutar El Maghraoui. Med-nas-bench: A generalized neural architecture search benchmark for medical imaging analysis. To be Submitted to Nature Methods, 2023. Location in thesis: Chapter 6

## List of publications not included in this thesis

#### - Real-time style transfer with efficient vision transformers

[11] Hadjer Benmeziane, Hamza Ouarnoughi, Kaoutar El Maghraoui, and Sma¨il Niar. Real-time style transfer with efficient vision transformers. In Aaron Yi Ding and Volker Hilt, editors, EdgeSys@EuroSys 2022: Proceedings of the 5th International Workshop on Edge Systems, Analytics and Networking, Rennes, France, April 5 - 8, 2022, pages 31–36. ACM, 2022

#### - HyT-NAS: Hybrid Transformers Neural Architecture Search for Edge Devices

[12] Lotfi Abdelkrim Mecharbat, Hadjer Benmeziane, Hamza Ouranoughi, and Sma¨ıl Niar. Hyt-nas: Hybrid transformers neural architecture search for edge devices. CoRR, abs/2303.04440, 2023

## - Treasure What You Have: Exploiting Similarity in Deep Neural Networks for Efficient Video Processing

[13] Hadjer Benmeziane, Halima Bouzidi, Hamza Ouarnoughi, Ozcan Ozturk, and Smail Niar. Treasure what you have: Exploiting similarity in deep neural networks for efficient video processing. CoRR, abs/2305.06492, 2023.

## - Skip Connections in Spiking Neural Networks: An Analysis of Their Effect on Network Training

[14] Hadjer Benmeziane, Amine Ziad Ounnoughene, Imane Hamzaoui, and Younes Bouhadjar. Skip connections in spiking neural networks: An analysis of their effect on network training. CoRR, abs/2303.13563, 2023.

## **Filed Patents**

### - CO-Design of a Model and Chip for Deep Learning Background (Filed)

Irem Boybat Kara, Hadjer Benmeziane, Manuel Le Gallo-Bourdeau, Kaoutar El Maghraoui, Malte Johannes Rasch, and HsinYu Tsai

VIII

## Contents

| Ré                                            | $\operatorname{sum}\acute{\mathrm{e}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ac                                            | $ cnowledgments \dots \dots$                                                                                                                                                                                                                                                                                                                                                                               |

|                                               | t of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | t of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Ac                                            | conyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Int                                           | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.1                                           | Context & Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

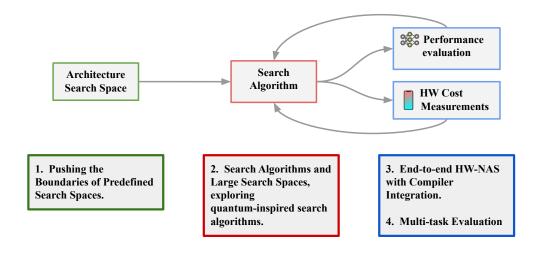

| 1.2                                           | Research Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3                                           | Summery of Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.4                                           | Open Source Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5                                           | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| - D                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| R                                             | elated Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ha                                            | rdware-aware Neural Architecture Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1                                           | Handcrafted models Vs. HW-NAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2                                           | Conventional Neural Architecture Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3                                           | Methodologies for Efficient Deep Learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $2.3 \\ 2.4$                                  | Methodologies for Efficient Deep Learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3                                           | Methodologies for Efficient Deep Learning       Taxonomy of HW-NAS         Taxonomy of HW-NAS       Search Spaces                                                                                                                                                                                                                                                                                                                                                                                                |

| $2.3 \\ 2.4$                                  | Methodologies for Efficient Deep Learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $2.3 \\ 2.4$                                  | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)                                                                                                                                                                                                                                                                                                                                                                           |

| $2.3 \\ 2.4 \\ 2.5$                           | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS Trends                                                                                                                                                                                                                                                                                                                                           |

| $2.3 \\ 2.4$                                  | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies                                                                                                                                                                                                                                                                                                                    |

| $2.3 \\ 2.4 \\ 2.5$                           | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation                                                                                                                                                                                                                                                                         |

| 2.3<br>2.4<br>2.5<br>2.6                      | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search Algorithms                                                                                                                                                                                                                                                   |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7               | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation Strategies                                                                                                                                                                                                                       |

| 2.3<br>2.4<br>2.5<br>2.6                      | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS                                                                                                                                                                            |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7               | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1Automatic Mixed-Precision Quantization                                                                                                                                 |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7               | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1 Architecture Search Space2.5.2 Hardware Search Space (HSS)2.5.3 Current Hardware-NAS TrendsOptimization strategies2.6.1 Hardware-aware NAS Problem Formulation2.6.2 Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1 Automatic Mixed-Precision Quantization2.8.2 Automatic Pruning                                                                                                    |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8        | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1Automatic Mixed-Precision Quantization2.8.2Automatic Pruning2.8.3Security and Reliability Considerations in NAS                                                        |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1Automatic Mixed-Precision Quantization2.8.3Security and Reliability Considerations in NASIn-memory Computing & HW-NAS                                                  |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1Automatic Mixed-Precision Quantization2.8.2Automatic Pruning2.8.3Security and Reliability Considerations in NASIn-memory Computing & HW-NAS0Challenges and Limitations |

| 2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | Methodologies for Efficient Deep LearningTaxonomy of HW-NASSearch Spaces2.5.1Architecture Search Space2.5.2Hardware Search Space (HSS)2.5.3Current Hardware-NAS TrendsOptimization strategies2.6.1Hardware-aware NAS Problem Formulation2.6.2Search AlgorithmsHW-NAS Estimation StrategiesOther Considerations for Hardware-aware NAS2.8.1Automatic Mixed-Precision Quantization2.8.3Security and Reliability Considerations in NASIn-memory Computing & HW-NAS                                                  |

| п | $\mathbf{E}$                                   | fficient HW-NAS methods                                               | 43           |

|---|------------------------------------------------|-----------------------------------------------------------------------|--------------|

| 3 | 3 Multi-objective Surrogate Model for HW-NAS 4 |                                                                       |              |

|   | 3.1                                            | Context                                                               | 46           |

|   | 3.2                                            | HW-PR-NAS                                                             | 46           |

|   |                                                | 3.2.1 Proposed Approach                                               | 48           |

|   |                                                | 3.2.2 Evaluation Methodology                                          | 53           |

|   |                                                | 3.2.3 End-to-End Results                                              | 55           |

|   |                                                | 3.2.4 Final Pareto Front Analysis                                     | 57           |

|   |                                                | 3.2.5 Generalization to More Objectives                               | 58           |

|   |                                                | 3.2.6 Generalisation to other use cases: Keywords Spotting            | 59           |

|   | 3.3                                            | PRP-NAS: Pareto Rank-preserving Supernetwork Training                 | 59           |

|   | 0.0                                            | 3.3.1 Proposed Approach                                               | 61           |

|   |                                                | 3.3.2 Evaluation Methodology                                          | 65           |

|   |                                                |                                                                       |              |

|   |                                                |                                                                       | 66<br>70     |

|   | 9.4                                            | 3.3.4 Battery Usage Preservation                                      | 70           |

|   | 3.4                                            | Conclusion                                                            | 71           |

| 4 |                                                | ancing HW-NAS Search Space                                            | 73           |

|   | 4.1                                            | Context                                                               | 74           |

|   | 4.2                                            | CaW-NAS                                                               | 74           |

|   |                                                | 4.2.1 Proposed Approach                                               | 75           |

|   |                                                | 4.2.2 Quantization Analysis                                           | 76           |

|   |                                                | 4.2.3 Search Strategy                                                 | 78           |

|   |                                                | 4.2.4 Evaluation Methodology                                          | 78           |

|   |                                                | 4.2.5 Search Results                                                  | 79           |

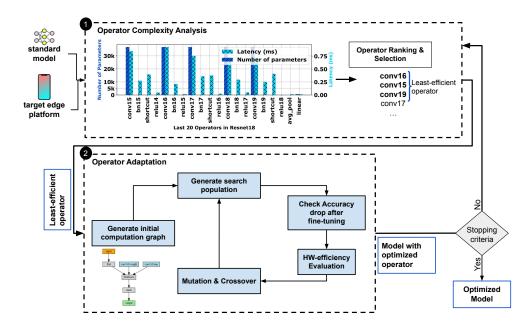

|   | 4.3                                            | Grassroots Operator Search for Model Edge Adaptation                  | 81           |

|   |                                                | 4.3.1 Proposed Approach                                               | 83           |

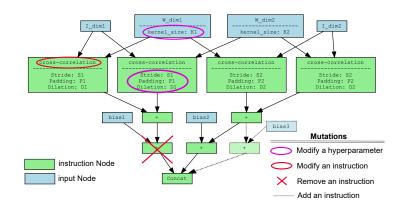

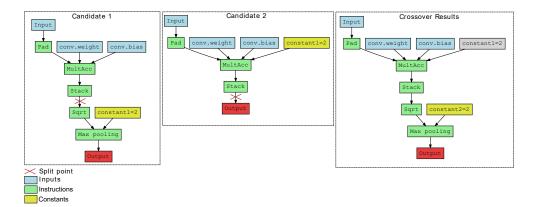

|   |                                                | 4.3.2 Search Algorithm                                                | 87           |

|   |                                                | 4.3.3 Evaluation Methodology                                          | 89           |

|   |                                                | 4.3.4 Optimizing an architecture for Edge Devices                     | 90           |

|   |                                                | 4.3.5 Use Case: Pulse Rate Estimation                                 | 92           |

|   | 4.4                                            | Conclusion                                                            | 96           |

|   |                                                |                                                                       |              |

| Π | I                                              | Applications of HW-NAS                                                | 97           |

| F | And                                            | alog-NAS                                                              | 99           |

| 9 | 5.1                                            |                                                                       |              |

|   | -                                              |                                                                       | 101          |

|   | 5.2                                            |                                                                       | 102          |

|   |                                                |                                                                       | 102          |

|   |                                                | 1                                                                     | 103          |

|   |                                                | 5.2.3 HWA-training and analog hardware accuracy evaluation simulation | 103          |

|   | 5.3                                            |                                                                       | 105          |

|   | 0.0                                            |                                                                       | 104          |

|   |                                                | 1                                                                     | $104 \\ 105$ |

|   |                                                | 0 0                                                                   | $105 \\ 107$ |

|   |                                                |                                                                       |              |

|   |                                                |                                                                       | 107          |

|   |                                                | 5.3.5 Search Algorithm                                                | 108          |

5.3.3

Search Strategy

107

5.3.4

Problem Formulation

107

5.3.5

Search Algorithm

108

5.4

Evaluation Methodology

110

5.5

Experiment Results

110

5.5.1

Comparison with Random Search

112

5.5.2

Search Time and AVM Threshold Trade-Off

113

5.6

Hardware Validation

113

|   |     | 5.6.2  | Simulated Hardware Energy and Latency                  | 113         |

|---|-----|--------|--------------------------------------------------------|-------------|

|   | 5.7 | Archit | ectural Recommendation for Analog AI                   | 114         |

|   |     | 5.7.1  | Are Wider or Deeper Networks More Robust to PCM Device |             |

|   |     |        | Drift?                                                 | 115         |

|   |     | 5.7.2  |                                                        |             |

|   | 5.8 | Conch  | usion                                                  |             |

|   |     |        |                                                        |             |

| 6 | HW  |        |                                                        | 117         |

|   | 6.1 |        | $\mathbf{xt}$                                          |             |

|   | 6.2 | MED-   | NAS-Bench                                              | 119         |

|   |     | 6.2.1  | Datasets                                               | 119         |

|   |     | 6.2.2  | Benchmark Design                                       | 121         |

|   |     | 6.2.3  | Evaluation methodology                                 | 124         |

|   |     | 6.2.4  | Performance Distribution                               | 125         |

|   |     | 6.2.5  | Architecture Distribution                              | 128         |

|   |     | 6.2.6  | Cross-datasets Correlations                            | 128         |

|   |     | 6.2.7  | State-of-the-art Search Methodologies                  | 129         |

|   | 6.3 | MT-M   | IIAS                                                   | 133         |

|   |     | 6.3.1  | Search Methodology                                     | 133         |

|   |     | 6.3.2  | Experiments Methodology                                |             |

|   |     | 6.3.3  | Search Results                                         |             |

|   | 6.4 | Conclu | usion                                                  | 141         |

| _ | C   |        |                                                        |             |

| 7 |     |        |                                                        | L <b>43</b> |

|   | 7.1 |        | usion                                                  |             |

|   | 7.2 | Future | e Work                                                 | 145         |

## List of Figures

| $1.1 \\ 1.2$ | Number of papers published on NAS and HW-NAS as of May 2023<br>Structure of the manuscript                                                                                                                                                                                                                                                                   | $\frac{3}{7}$ |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

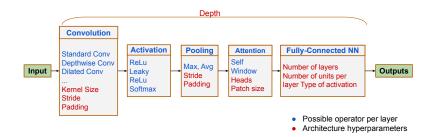

| 2.1          | Generic DL architecture. For each layer, an operator is chosen among a pre-defined list or operations (convolution, dilated convolution, depthwise convolution, max-pooling, batch_normalization, etc.). The sequence Convolution, Activation, Attention, etc. is repeated several                                                                           |               |

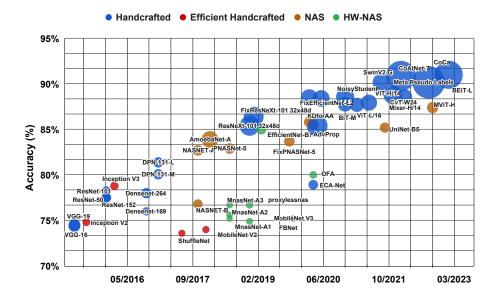

| 2.2          | times in DL architectures                                                                                                                                                                                                                                                                                                                                    | 13            |

| 0.9          | task with the number of parameters. Inspired by $[15]$                                                                                                                                                                                                                                                                                                       | 13            |

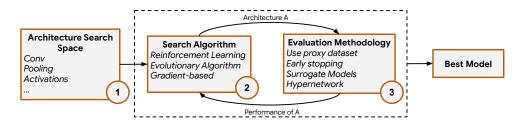

| 2.3          | Overview of conventional NAS components.                                                                                                                                                                                                                                                                                                                     | 14            |

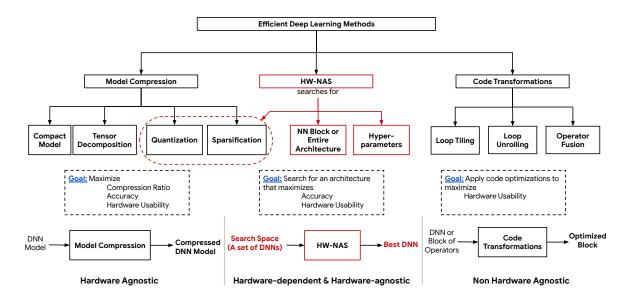

| 2.4          | Overview of efficient deep learning strategies.                                                                                                                                                                                                                                                                                                              | 16            |

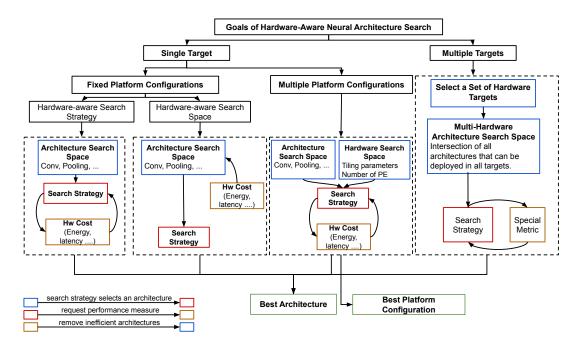

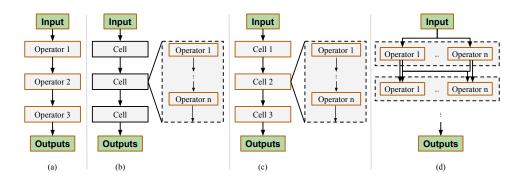

| $2.5 \\ 2.6$ | Overview of different hardware-aware NAS designs Architecture search spaces types. (a) Global search space, (b) Cell-<br>based search space, (c) Hierarchical search space, and (d) supernetwork                                                                                                                                                             | 17            |

|              | search space. In orange the operators considered during the search                                                                                                                                                                                                                                                                                           | 19            |

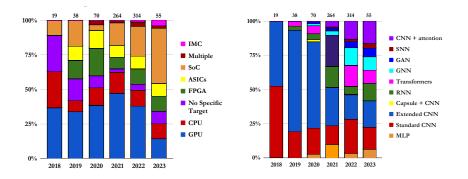

| 2.7          | Statistics on targeted platforms and type of networks described by the                                                                                                                                                                                                                                                                                       | -             |

|              | HW-NAS search spaces                                                                                                                                                                                                                                                                                                                                         | 23            |

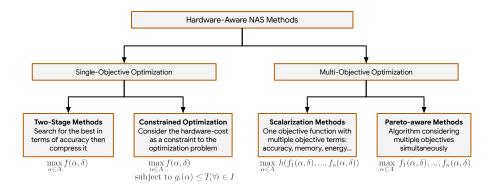

| 2.8          | HW-NAS problem formulations.                                                                                                                                                                                                                                                                                                                                 | 24            |

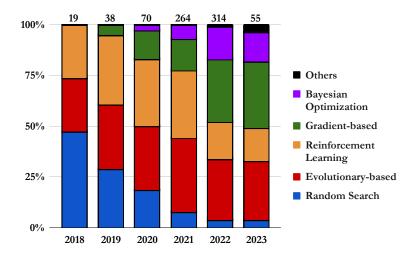

| 2.9          | Commonly used search algorithms                                                                                                                                                                                                                                                                                                                              | 27            |

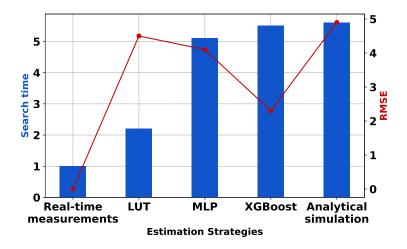

| 2.10         | Look Up Table. The speedups are calculated w.r.t Real-world mea-                                                                                                                                                                                                                                                                                             |               |

|              | surements                                                                                                                                                                                                                                                                                                                                                    | 33            |

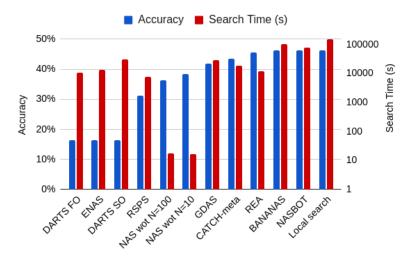

| 2.11         | Results of different search algorithms on NAS-Bench-201                                                                                                                                                                                                                                                                                                      | 38            |

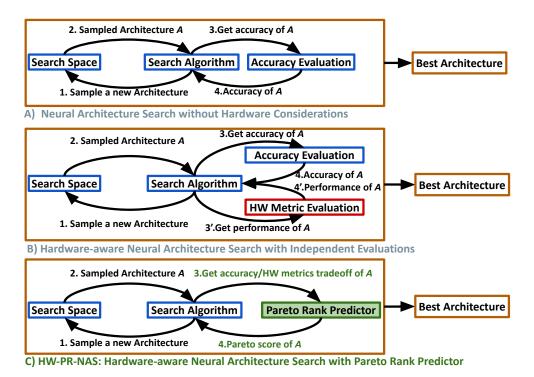

| 3.1          | Simplified illustration of the use of HW-PR-NAS in a NAS process.<br><i>HW Perf</i> means the Hardware performance of the architecture such as latency, power, etc.                                                                                                                                                                                          | 47            |

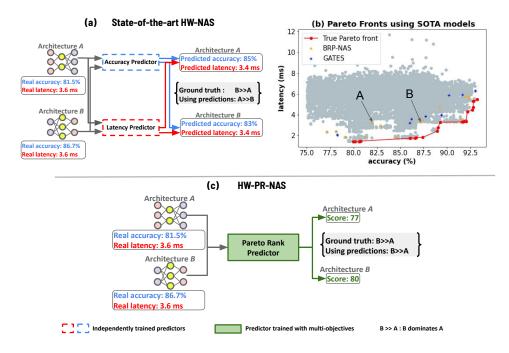

| 3.2          | This figure illustrates the limitation of state-of-the-art surrogate mod-<br>els alleviated by HW-PR-NAS. a) and b) illustrate how two indepen-<br>dently trained predictors exacerbate the dominance error and the re-<br>sults obtained using GATES [16] and BRP-NAS [17]. c) illustrates<br>how we solve this issue by building a single surrogate model. | 47            |

| 3.3          | General Overview of HW-PR-NAS                                                                                                                                                                                                                                                                                                                                | 49            |

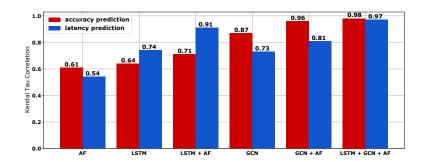

| 3.4          | Results of different encoding schemes for accuracy and latency pre-                                                                                                                                                                                                                                                                                          | 10            |

| 0.1          | dictions on NAS-Bench-201 and FBNet. AF refers to Architecture<br>Features. LSTM refers to Long Short-Term Memory neural network.                                                                                                                                                                                                                            |               |

|              | GCN refers to Graph Convolutional Networks.                                                                                                                                                                                                                                                                                                                  | 51            |

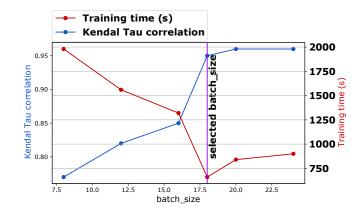

| 3.5          | Performance of the Pareto rank predictor using different batch_size values during training.                                                                                                                                                                                                                                                                  | 54            |

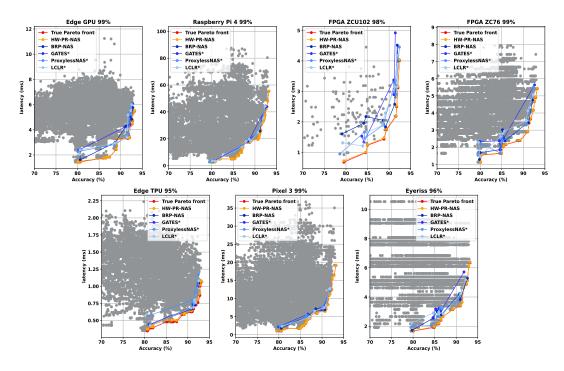

| 3.6          | Pareto front approximations on CIFAR-10 on edge hardware platforms.                                                                                                                                                                                                                                                                                          | 04            |

| 0.0          | We show the true accuracies and latencies of the different architectures                                                                                                                                                                                                                                                                                     |               |

|              | and the normalized hypervolume on each target platform.                                                                                                                                                                                                                                                                                                      | 56            |

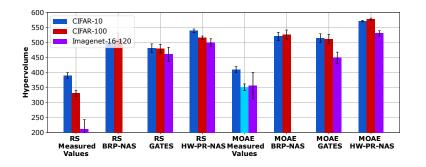

| 3.7   | Final Hypervolume obtained by each method on the three datasets.                                                                          | 56         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|

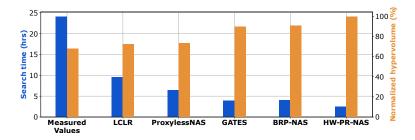

| 3.8   | We show the means $\pm$ standard errors based on 5 independent runs<br>Search time of MOAE using different surrogate models on 250 gener- | 90         |

| 3.0   | ations with a max time budget of 24 hours.                                                                                                | 57         |

| 3.9   | Pareto front Approximations using three objectives: accuracy, latency                                                                     | 51         |

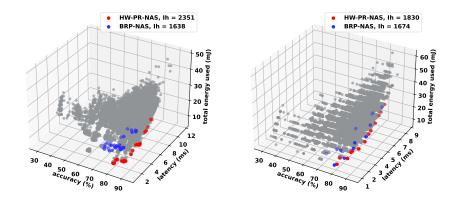

| 0.9   | and energy consumption on CIFAR-10 on Edge GPU (left), FPGA                                                                               |            |

|       | (right). In corresponds to the hypervolume.                                                                                               | 58         |

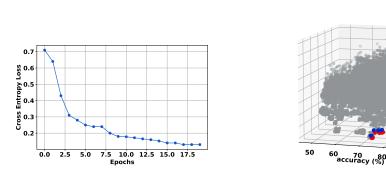

| 2 10  | Encoder fine-tuning: Cross-entropy loss over epochs.                                                                                      | 60         |

|       |                                                                                                                                           | 60<br>60   |

|       | Search result using HW-PR-NAS against True Pareto front                                                                                   | 00         |

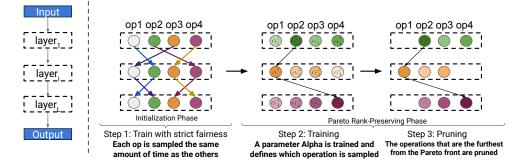

| 3.12  | Our Pareto Rank-Preserving Training methodology for Supernetwork.                                                                         |            |

|       | The strongest shades illustrate the most important operations for each                                                                    |            |

|       | layer at each iteration. $\alpha_o^l$ corresponds to the parameter alpha associ-                                                          | <u>co</u>  |

| 0 1 0 | ated with layer $l$ and operation $o$                                                                                                     | 60         |

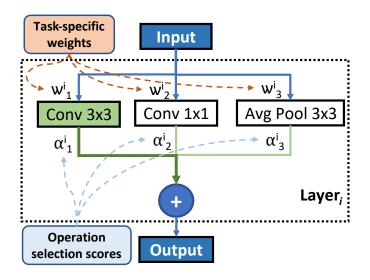

| 3.13  | Supernetwork definition when coupling task-specific weights $W$ and                                                                       |            |

|       | operation's score parameters $\alpha$ . Conv 3x3 is the operation with the                                                                | 01         |

| 0.14  | highest selection score.                                                                                                                  | 61         |

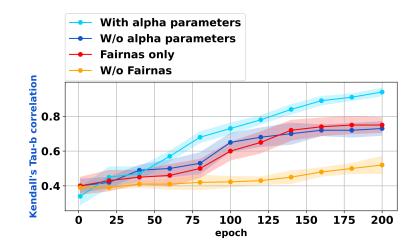

| 3.14  | Training performance computed with the Kendall's Tau Correlation                                                                          |            |

|       | between the independently trained Pareto ranks and the estimated                                                                          | <b>C</b> 4 |

| 9.15  | Pareto ranks obtained by training the supernetwork.                                                                                       | 64<br>67   |

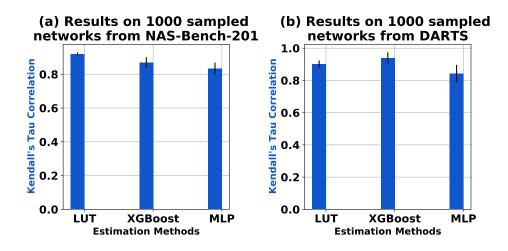

|       | Comparison of latency estimators on Jetson Nano.                                                                                          | 65<br>66   |

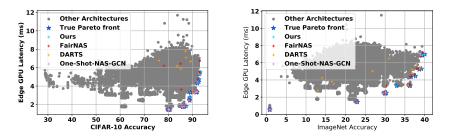

|       | Pareto front approximation comparison on CIFAR-10 and ImageNet                                                                            | 66<br>60   |

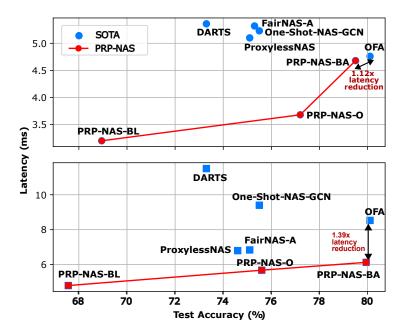

|       | Comparison with state-of-the-art ImageNet results.                                                                                        | 68         |

| 3.18  | Kendall's Tau-b correlation and hypervolume comparison using differ-                                                                      | 60         |

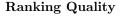

| 0.10  | ent estimators on DARTS.                                                                                                                  | 68         |

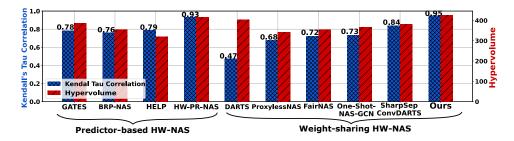

| 3.19  | Hypervolume analysis with an increasing number of sampled sub-                                                                            |            |

|       | networks for the final Pareto front throughout the search (higher is                                                                      | 60         |

| 0.00  | better) on NAS-Bench-201.                                                                                                                 | 69<br>70   |

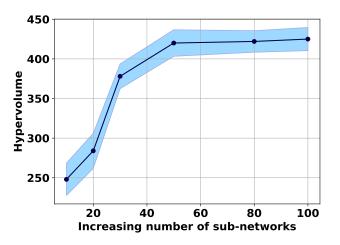

|       | Analysis of trained alpha values for layers 1 and 2                                                                                       | 70         |

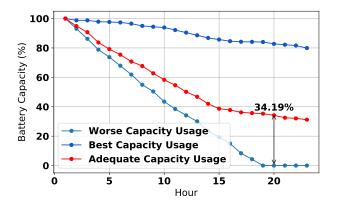

| 3.21  | Battery life management.                                                                                                                  | 71         |

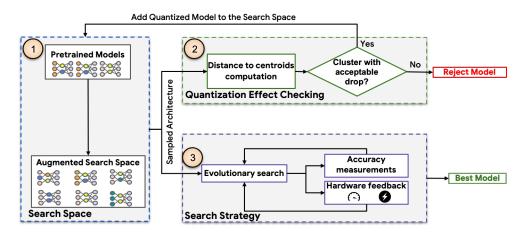

| 4.1   | Overview of CaW-NAS: Compression Aware Neural Architecture                                                                                | 75         |

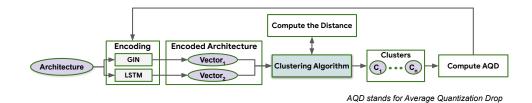

| 4.2   | Clustering strategy to analyze the quantization sensitivity                                                                               | 76         |

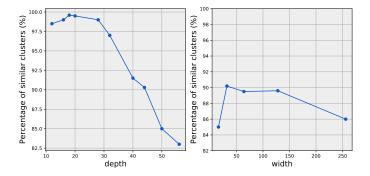

| 4.3   | Quantization effect on increasing depth and width in the architectures                                                                    | 77         |

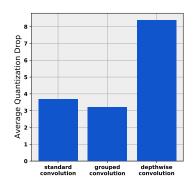

| 4.4   | Quantization effect on different convolution variants                                                                                     | 77         |

| 4.5   | Number of quantized architectures in the search space and population                                                                      | •••        |

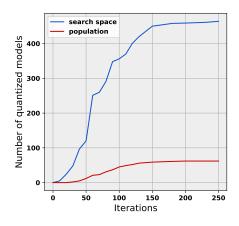

| 1.0   | over iterations.                                                                                                                          | 80         |

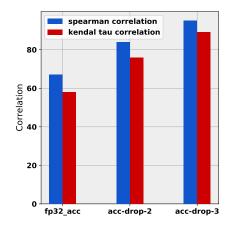

| 4.6   | Ranking correlation of accuracy proxies. <i>acc-drop-x</i> refers to the ac-                                                              | 00         |

| 1.0   | curacy proxy with x clusters                                                                                                              | 80         |

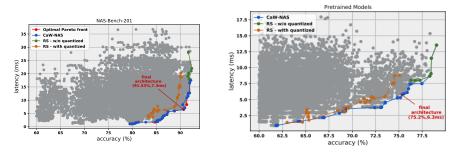

| 4.7   | Pareto front approximation results. Top figure: NAS-Bench-201 for                                                                         | 00         |

| 1.1   | CIFAR-10, Bottom figure: Pretrained Models for ImageNet                                                                                   | 81         |

| 4.8   | Overview of the operator replacement methodology.                                                                                         | 83         |

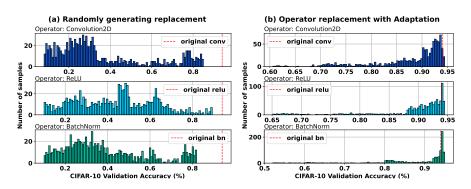

| 4.9   | CIFAR-10 accuracy histograms of 1k architectures randomly generated                                                                       | 00         |

| 1.0   | (a) and adapted from the original operator (b).                                                                                           | 85         |

| 4 10  | Detailed computation graph of the standard convolution 2D including                                                                       | 00         |

|       | the possible mutations applied to it.                                                                                                     | 87         |

| 4 11  | Illustration of the cross-over operation.                                                                                                 | 88         |

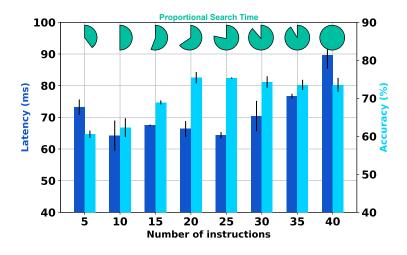

|       | Tuning of the maximum number of instructions per operator while                                                                           | 00         |

|       | searching for resnet18 GOS variant on Raspberry Pi.                                                                                       | 93         |

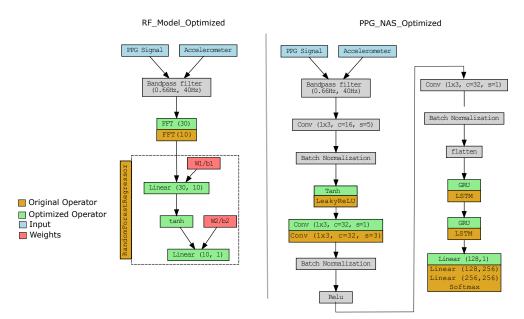

| 4.13  | Pulse Rate Estimation final Models. We do not display the weights                                                                         | 00         |

|       | node for PPG_NAS for the sake of clarity.                                                                                                 | 96         |

|       |                                                                                                                                           |            |

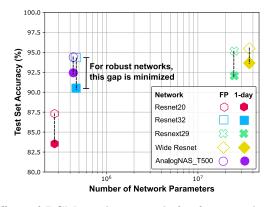

| 5.1   | The effect of PCM conductance drift after one day on standard CNN                                                                         |            |

|       | architectures and one architecture (AnalogNAS_T500) obtained using                                                                        |            |

|       | HW-NAS, evaluated using CIFAR-10.                                                                                                         | 101        |

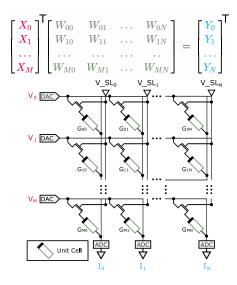

| 5.2   | Employed analog IMC tile and weight mapping scheme.                                                                                       |            |

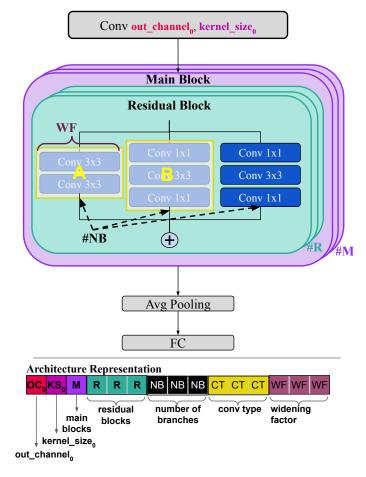

| 5.3   | Resnet-like macro architecture.                                                                                                           | 104        |

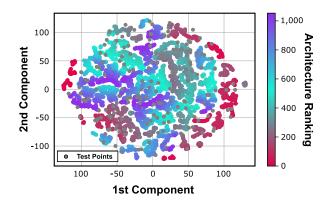

| 5.4  | t-Distributed Stochastic Neighbor Embedding (t-SNE) visualization of    |     |

|------|-------------------------------------------------------------------------|-----|

|      | the sampled architectures for CIFAR-10.                                 | 106 |

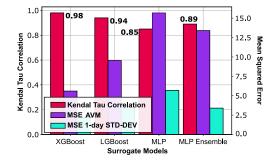

| 5.5  | Surrogate models comparison.                                            | 107 |

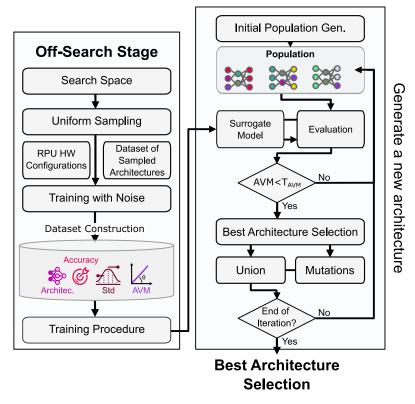

| 5.6  | Overview of the AnalogNAS framework.                                    | 108 |

| 5.7  | Simulated hardware comparison results on three benchmarks: (a,b)        |     |

|      | CIFAR-10, (c) VWW, and (d) KWS. The size of the marker represents       |     |

|      | the size (i.e., the number of parameters) of each model. The shaded     |     |

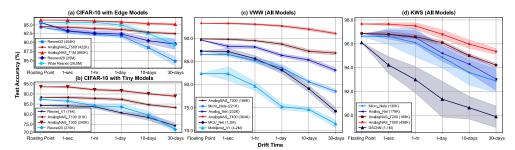

|      | area corresponds to the standard deviation at that time                 | 111 |

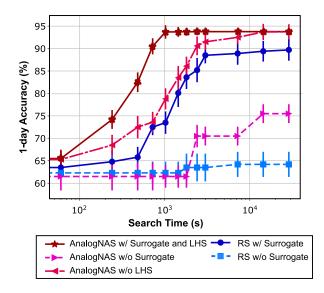

| 5.8  | Ablation study comparison against Random Search (RS). Mean and          |     |

|      | standard deviation values are reported across five experiment instances |     |

|      | (trials)                                                                | 112 |

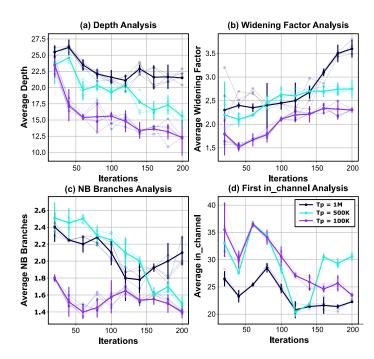

| 5.9  | Evolution of architecture characteristics in the population during the  |     |

|      | search for CIFAR-10. Random individual networks are shown.              | 114 |

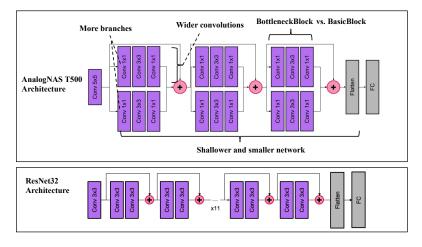

| 5.10 | Architectural differences between AnalogNAS_T500 and Resnet32. $\ .$ .  | 115 |

|      |                                                                         |     |

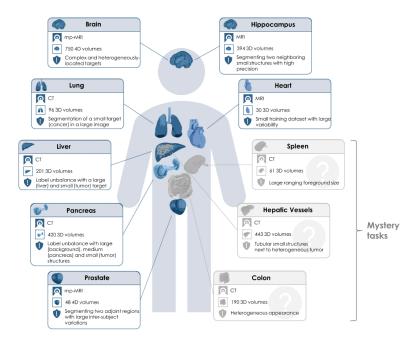

| 6.1  | Overview of the ten different tasks of the Medical Segmentation De-     |     |

|      | cathlon (MSD) [18]                                                      | 120 |

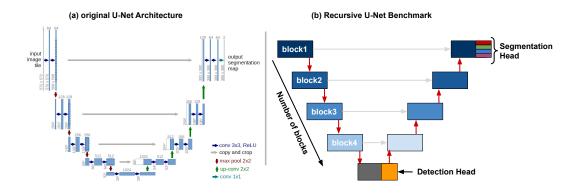

| 6.2  | Search Space of MED-NAS-Benchmark                                       | 121 |

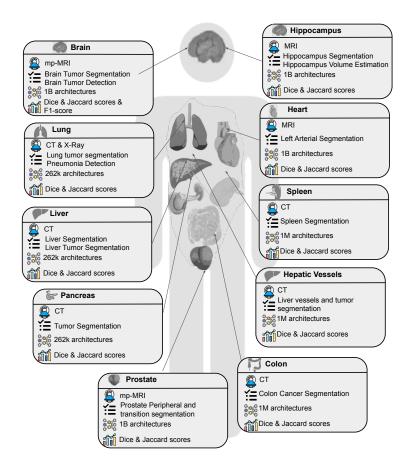

| 6.3  | Overview of MED-NAS-Bench. Inspired from MSD [18]                       | 123 |

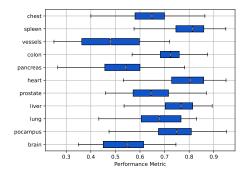

| 6.4  | MED-NAS-Bench performance across datasets                               | 126 |

| 6.5  | MED-NAS-Bench hardware efficiency across datasets on Raspberry          |     |

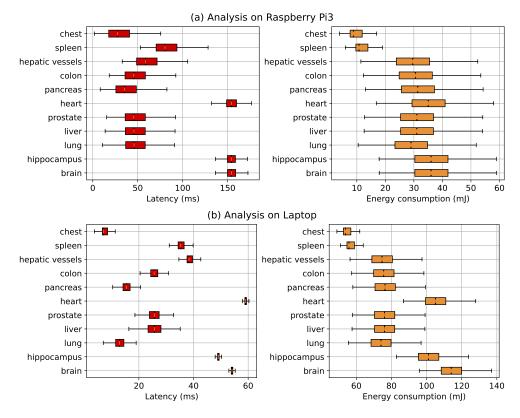

|      | Pi3 and Laptop.                                                         | 127 |

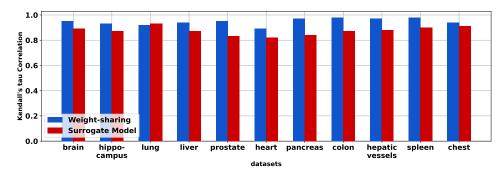

| 6.6  | Ranking correlation experiments across datasets.                        | 128 |

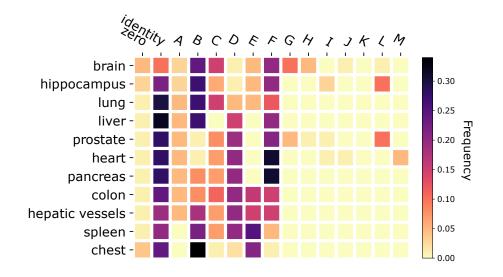

| 6.7  | Blocks operation frequency in top 1000 architectures for each dataset.  | 129 |

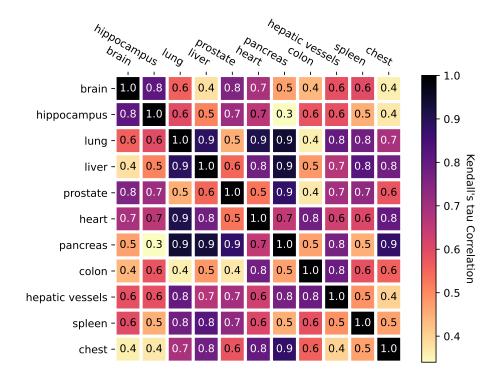

| 6.8  | Cross-datasets ranking correlation                                      | 130 |

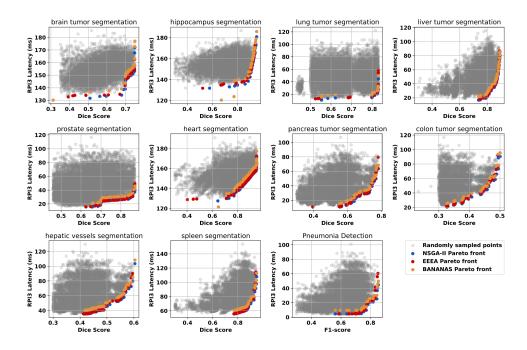

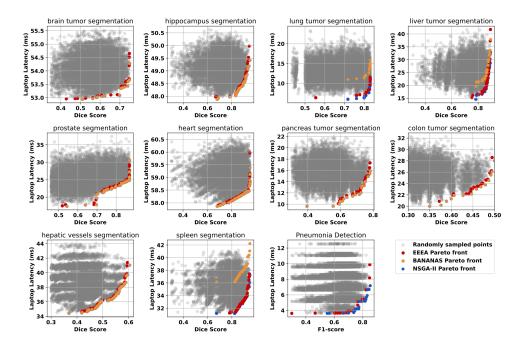

| 6.9  | Pareto front results of SOTA multi-objective optimizations on Rasp-     | 100 |

| 0.10 | berry Pi3.                                                              | 132 |

|      | Pareto front results of SOTA multi-objective optimizations on Laptop.   | 132 |

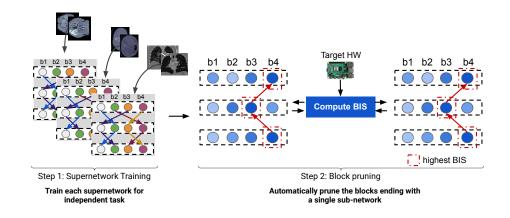

|      | Overview of MT-MIAS steps.                                              | 134 |

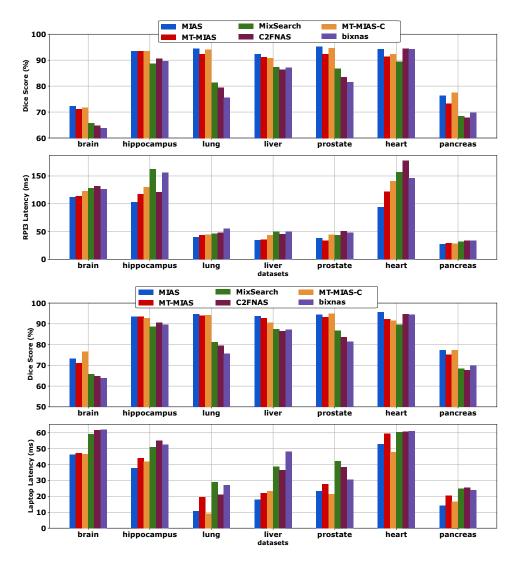

| 0.12 | Comparative results of MT-MIAS on MED-NAS-Bench, both on Rasp-          | 190 |

|      | berry PI3 (RPI3) and laptop.                                            | 139 |

| 7.1  | Future Works on top of HW-NAS framework.                                | 146 |

|      | ▲ ·                                                                     |     |

## List of Tables

| 2.1<br>2.2<br>2.3<br>2.4                 | Classification of HW-NAS based on their targeted Hardware Summary of Hardware Cost Estimation Methods Comparison of NAS Benchmarks                                                          | 22<br>31<br>37<br>41 |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.1                                      | Hyperparameters associated with GCN and LSTM encodings and the                                                                                                                              |                      |

| 3.2                                      | decoder used to train them                                                                                                                                                                  | 50                   |

| 3.3                                      | Kendal Tau Correlation                                                                                                                                                                      | 51                   |

| 3.4                                      | architecture features such as the number of convolutions and depth<br>Illustrative comparison of edge hardware platforms targeted in this                                                   | 54                   |

| 3.5                                      | work                                                                                                                                                                                        | 55                   |

|                                          | CIFAR-10                                                                                                                                                                                    | 57                   |

| 3.6                                      | Comparison of Optimal Architectures obtained in the Pareto Front for ImageNet                                                                                                               | 57                   |

| $\begin{array}{c} 3.7\\ 3.8 \end{array}$ | Accuracy and Latency Comparison for Keyword Spotting Training Hyperparameters                                                                                                               | $59 \\ 66$           |

| 3.9                                      | Comparison on NAS-Bench-201 CIFAR-10 on Edge GPU (Jetson Nano) and Mobile phone (Pixel 3).                                                                                                  | 67                   |

| 3.10                                     | Comparison to baselines on CIFAR-10 on FPGA ZCU-102 and Rasp-<br>berry Pi3                                                                                                                  | 67                   |

| 3.11                                     | Ablation results of Pruning of Pareto ranking for CIFAR-10.                                                                                                                                 | 69                   |

| $4.1 \\ 4.2$                             | CaW-NAS hyperparameters                                                                                                                                                                     | 79                   |

|                                          | the number of training for NAS on a new platform                                                                                                                                            | 80                   |

| $\begin{array}{c} 4.3\\ 4.4\end{array}$  | List of mathematical instructions defining the search space<br>Performance comparison of original models and adapted models on                                                              | 86                   |

| 4.5                                      | Raspberry Pi 3 and Redmi Note 7S                                                                                                                                                            | 91<br>92             |

| $4.6 \\ 4.7$                             | Notation Summary                                                                                                                                                                            | 92                   |

| · <b>T</b> •1                            | TROIKA Dataset [20]                                                                                                                                                                         | 95                   |

| $5.1 \\ 5.2$                             | Searchable hyper-parameters and their respective ranges Final Architectures for CIFAR-10, VWW, and KWS. Other networks for VWW and KWS are not listed, as they cannot easily be represented | 106                  |

|                                          | using our macro-architecture.                                                                                                                                                               | 111                  |

| 5.3  | AVM threshold variation results on CIFAR-10.                        | 113 |

|------|---------------------------------------------------------------------|-----|

| 5.4  | Experimental hardware accuracy validation and simulated power per-  |     |

|      | formance on the IMC system in [21]                                  | 114 |

| 6.1  | Details of the blocks and operations searched in the benchmark      | 122 |

| 6.2  | Datasets details and training hyperparameters                       | 124 |

| 6.3  | MED-NAS-Bench Hardware specifications.                              | 125 |

| 6.4  | Number of Non Deployable architectures in edge platforms            | 127 |

| 6.5  | Results of state-of-the-art search methodologies on MED-NAS-Bench.  |     |

|      | Dice and Jc stand for the dice and Jaccard scores respectively. EA  |     |

|      | and RS stand for evolutionary algorithm and random search, both are |     |

|      | classical search algorithms. C2FNAS_O is the original architecture  |     |