## Energy-Efficient Memristor-Based Artificial Intelligence Accelerators using In/Near Memory Computing

Kamel-Eddine Harabi

### ► To cite this version:

Kamel-Eddine Harabi. Energy-Efficient Memristor-Based Artificial Intelligence Accelerators using In/Near Memory Computing. Micro and nanotechnologies/Microelectronics. Université Paris-Saclay, 2023. English. NNT: 2023UPAST086. tel-04229739

## HAL Id: tel-04229739 https://theses.hal.science/tel-04229739v1

Submitted on 5 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Energy-Efficient Memristor-Based Artificial Intelligence Accelerators using In/Near Memory Computing

Accélérateurs d'Intelligence Artificielle à Base de Memristors à Faible Consommation d'Énergie utilisant le Calcul Dans/Proche de la Mémoire

#### Thèse de doctorat de l'université Paris-Saclay

École doctorale n°575: Electrical, Optical, Bio-Physics and Engineering Spécialité de doctorat: Electronique, Photonique et Micro-Nanotechnologies Graduate School : Sciences de l'ingénierie et des systèmes. Référent : Faculté des sciences d'Orsay

> Thèse préparée dans le **Centre de Nanosciences et de Nanotechnologies** (Université Paris-Saclay, CNRS), sous la direction de **Jacques-Olivier Klein**, Professeur, la co-direction de **Damien Querlioz**, Chargé de recherche, le co-encadrement de **Jean-Michel Portal**, Professeur.

> Thèse soutenue à Paris-Saclay, le 03 juillet 2023, par

### **Kamel-Eddine HARABI**

#### **Composition du jury**

| <b>Dr. Julie Grollier</b><br>Directrice de recherche, Unité Mixte de Physique<br>CNRS/Thales | Présidente                 |

|----------------------------------------------------------------------------------------------|----------------------------|

| Dr. Quentin Rafhay                                                                           | Rapporteur & Examinateur   |

| Maître de conférences, IMEP-LAHC, Université<br>Grenoble-Alpes                               |                            |

| Pr. Melika Payvand                                                                           | Rapportrice & Examinatrice |

| Professeur Assistante, Institute of Neuroinformat-<br>ics, University of Zurich / ETH Zurich |                            |

| Dr. Gilles Sassatelli                                                                        | Examinateur                |

| Directreur de recherche, LIRMM, CNRS/Université<br>Montpellier                               |                            |

THEÉSE DE DOCTORAT

**NNT : 2023UPAST086**

#### ÉCOLE DOCTORALE

Physique et ingénierie: Electrons, Photons, Sciences du vivant (EOBE)

**Titre**: Accélérateurs d'Intelligence Artificielle à Base de Memristors à Faible Consommation d'Énergie utilisant le Calcul Dans/Proche de la Mémoire.

**Mots clés:** Intelligence Artificielle, Faible consommation d'énergie, technologies de mémoire, Calcul Dans/Proche de la Mémoire, Memristors, Inférence Bayésienne

Résumé: L'Intelligence Artificielle (IA) émerge comme une force omniprésente dans notre vie quotidienne, possédant le potentiel de provoquer une révolution transformatrice dans une multitude de secteurs de la société. Cependant, sous cette promesse de transformation, l'IA est confrontée à deux défis majeurs qui nécessitent une attention urgente : l'efficacité énergétique et la fiabilité. Les besoins énergétiques croissants de l'industrie de l'IA contribuent aux émissions mondiales de carbone en raison des hautes exigences computationnelles des modèles d'IA, menaçant la durabilité environnementale. Parallèlement, la nature 'boîte noire' de nombreux systèmes d'IA, produisant des décisions difficiles à interpréter, soulève des questions de confiance. Ces incertitudes introduisent des risques dans des secteurs critiques, formant des barrières à l'acceptation plus large de l'IA. En réponse à ces défis, cette thèse propose une approche multidisciplinaire qui unifie l'intelligence artificielle, l'architecture informatique et les technologies émergentes. Notre stratégie implique le développement de circuits intégrés spécialisés utilisant la technologie de pointe des memristors, une technologie nanoelectronique conçue pour supporter des paradigmes de calcul à faible énergie pour les modèles d'IA, spécifiquement dans des contextes à ressources limitées. Le concept central de cette approche est d'exploiter la non-volatilité et les capacités de calcul Dans/Proche de la mémoire des memristors, tout en tenant compte de leurs caractéristiques non-idéales, pour atteindre une haute efficacité énergétique, particulièrement dans le domaine du edge computing. De plus, nous incorporons l'inférence Bayésienne, une technique d'IA totalement explicative, dans le circuit pour répondre aux problèmes de confiance associés à l'IA, favorisant ainsi le développement d'applications d'IA transparentes et fiables. Le

premier chapitre de cette thèse introduit une architecture de calcul Proche-mémoire conçue pour les applications d'IA de périphérie (AI at the Edge), inspirée par l'efficacité énergétique exceptionnelle du cerveau humain. Nous proposons une architecture de machine Bayésienne basée sur des memristors, qui ouvre la voie vers des modèles d'IA à haute efficacité énergétique. Dans le deuxième chapitre, nous explorons une machine Bayésienne qui emploie une approche de calcul stochastique au sein d'un système d'array de memristors distribué. Cette machine, que nous avons conçue, fabriquée et testée, présente une efficacité énergétique supérieure par rapport aux unités de microcontrôleurs traditionnelles pour des tâches telles que la reconnaissance gestuelle. Elle démontre une résilience aux erreurs logicielles et aux radiations, la rendant bien adaptée pour le déploiement dans des environnements rudes. Le troisième chapitre aborde les limitations du calcul stochastique dans notre machine Bayésienne et présente une solution alternative : une machine Bayésienne basée sur le calcul logarithmiques. Ce nouveau circuit, conçu, fabriqué et testé, améliore la précision et accélère les opérations d'inférence, tout en maintenant l'architecture et le design de la machine originale. Le chapitre fournit également une analyse comparative de nos machines Bayésiennes stochastiques et logarithmiques, élucidant leurs forces et faiblesses respectives. Dans le dernier chapitre, nous abordons les défis associés à l'utilisation des memristors. Nous introduisons une plateforme de prototypage basée sur des memristors multimodes qui facilite la mise en œuvre de projets analogiques et numériques. Actuellement, cette plateforme est utilisée dans deux laboratoires de recherche pour valider une gamme de concepts neuromorphiques analogiques et de logique numérique en mémoire.

**Title:** Energy-Efficient Memristor-Based Artificial Intelligence Accelerators using In/Near Memory Computing

**Keywords:** Artificial Intelligence, Low Energy consumption, Novel Memory Technologies, In/Near Memory Computing, Memristors, Bayesian inference

#### Abstract:

Artificial Intelligence (AI) is emerging as an omnipresent force in our everyday lives, possessing the potential to bring about a transformative revolution across a multitude of societal sectors. Yet, beneath this promise of transformation, AI is grappling with two significant challenges that need urgent attention: energy efficiency and trustworthiness. The AI industry's escalating energy demands are contributing to global carbon emissions due to the high computational needs of AI models, threatening environmental sustainability and restricting the deployment of AI in resource-constrained settings such as edge devices. Simultaneously, the 'black box' nature of many AI systems, producing difficult-to-interpret decisions, raises concerns about trust. These uncertainties introduce risks in critical sectors forming barriers to the wider acceptance of AI. In response to these challenges, this thesis proposes a multidisciplinary approach that unifies artificial intelligence, computer architecture, and emerging technologies. Our strategy involves the development of specialized integrated circuits utilizing cutting-edge memristor technology, a nanoelectronic technology designed to support low-energy computational paradigms for AI models, specifically in resource-constrained contexts. The central concept of this approach is to harness the non-volatility and in/near-memory capabilities of memristors, while accounting for their non-ideal characteristics, to achieve high energy efficiency, particularly in the realm of edge computing. Additionally, we incorporate Bayesian inference, a fully explainable AI technique, into the circuitry to address the trust issues associated with AI, fostering the development of transparent and

dependable AI applications. The first chapter of this thesis introduces a near-memory computing architecture designed for edge AI applications, inspired by the human brain's exceptional energy efficiency. We propose a memristor-based Bayesian machine architecture employing memristors, that paves the path towards energy-efficient AI models. In the second chapter, we delve into a Bayesian machine that employs a stochastic computing approach within a distributed memristor array system. This machine, which we have designed, fabricated, and tested, exhibits superior energy efficiency compared to traditional microcontroller units for tasks such as gesture recognition. lt demonstrates resilience to soft errors and radiation, making it well-suited for deployment in harsh environments. Chapter three addresses the limitations of stochastic computing in our memristorbased Bayesian machine and presents an alternative solution: a logarithmic memristor-based Bayesian machine. This newly designed, fabricated, and tested circuit enhances precision and accelerates inference operations, while maintaining the original machine's architecture and design. The chapter also provides a comparative analysis of the stochastic and logarithmic memristorbased Bayesian machines, elucidating their relative strengths and weaknesses. In the final chapter, we tackle challenges associated with memristor utilization. We introduce a multimode memristorbased prototyping platform that facilitates both analog and digital project implementation. Currently, this platform is being used in two research labs to validate a range of digital logic-in-memory and analog neuromorphic concepts.

Thèse effectuée au sein du **Centre de Nanosciences et de Nanotechnologies** de l'Université Paris-Saclay, CNRS 10 Boulevard Thomas Gobert 91120 Palaiseau FRANCE To those who believe in the power of knowledge and science to shape the destiny of society for the better.

## Acknowledgements

The completion of this Ph.D. thesis not only marks the culmination of my academic journey but also embodies a voyage enriched by the unwavering support, guidance, and inspiration of countless remarkable individuals.

Foremost, I extend my deepest gratitude to my supervisor, Dr. Damien Querlioz. I still recall our first meeting at the digital electronics course, where your enthusiasm and profound knowledge about the future of computing captivated me. It was then that I was introduced to the fascinating field of neuromorphic computing, which became the cornerstone of my research pursuits. Joining your research team, I immediately felt a sense of belonging amidst the vibrant and dynamic collaborations you had cultivated, making every day an extraordinary learning experience. Your extensive knowledge and ability to delve swiftly into new research areas brought a unique energy to our projects. I am immensely thankful for your unconditional support, close yet respectful supervision, which fostered an ideal environment for skill development and growth.

Additionally, I extend my sincere thanks to my co-supervisor, Pr. Jean-Michel Portal. your generous sharing of technical expertise in designing integrated circuits during my visits to your team in Marseilles was instrumental in sharpening my skills. Every interaction was a step forward, and for that, I am grateful. I must also express my appreciation for Pr. Jacques-Olivier Klein, another pivotal supervisor. Despite our limited meetings due to your administrative duties, I have greatly benefited from your advice, suggestions, and positive influence.

My sincere gratitude goes out to the members of my Ph.D. defense committee: Pr. Melika Payvand, Dr. Quentin Rafhay, Dr. Julie Grollier, and Dr. Gilles Sassatelli. I appreciate your willingness to be part of my committee, the time devoted to studying my manuscript, and your insightful comments and rigorous feedback that have significantly elevated the quality of my work. A special mention to Dr. Belgacem Habba for accepting my invitation and contributing to the discussion with your industry-oriented questions despite the early hour resulting from the time difference. I am also thankful to all the reviewers whose insights have further refined the research articles constituting this thesis manuscript.

My journey would have been far less enriched without the steadfast support of my research collaborators, who have been integral pillars throughout this venture. Dr. Tifenn Hirtzlin and Clement Turck deserve heartfelt appreciation for being unwavering co-first authors and partners in several projects. Collaborating with Tifenn on our first project, "The Memristor-based Bayesian Machine," was an enlightening experience; your blend of motivation and diverse skills greatly enriched our collaborative moments. Not to mention your sports insights and our activities of hiking in Grenoble and playing football in Saclay. I still remember that we haven't yet settled the debate on who is faster in a running race. Clement's involvement in our

#### ACKNOWLEDGEMENTS

group significantly elevated the value of every research project included in this thesis. Your rapid learning and adept multitasking were truly commendable; whether conducting Bayesian inference simulations, working on PCB design, or analyzing measurements, his contributions were invaluable. Collaborating on our successful projects has been an immense pleasure, and I extend my best wishes for his upcoming Ph.D. defense. I extend my appreciation to our interns—Thibaut Loiseau and Adrien Renaudineau—for your brilliant contributions to various projects. Your grasp of concepts and tasks, often with minimal discussion, was admirable.

I extend my acknowledgment to collaborators beyond our lab's confines. My gratitude flows towards Dr. Thomas Dalgaty from CEA-Leti for involving me in the project of the in-situ Memristor-based MCMC learning; such genius ideas come from a brilliant mind like yours. Dr. Mathieu Faye from IM2NP, your support in designing the MCMC sampling machine has notably enhanced my skills in crafting complex circuits. Drs. Fadi Jebali and Eloi Muhr from IM2NP, engaging with you on various projects and sharing discussions during my visits to Marseilles were opportunities I greatly appreciated. Special thanks to Dr. Marc Bocquet from Aix Marseille University; our exchanges have always been intellectually stimulating, and I am continually impressed by your precise and critical insights during our project discussions. Gratitude is also due to Dr. Elisa Vianello and Dr. Etienne Nowak from CEA Leti for their support in design and fabrication process, ensuring the success of our tape-out projects. Additionally, I value the successful collaborations with the team from HawAI.Tech startup, including Drs. Pierre Bessière, Jacques Drouez, and Raphael Laurent, particularly on the Bayesian machines projects. Acknowledgments are also extended to Dr. Louis Hutin from Spintech lab for the MTJ-based RNG project collaboration. Every individual, with their unique expertise and spirit of collaboration, has played a significant role in expanding the breadth and depth of my research, thereby making my Ph.D. journey all the more enriching and fulfilling.

The IntegNano team, filled with brilliant minds and warm hearts, significantly enriched my professional and personal experience at our lab. My journey began alongside Drs. Atreya Majumdar, Rohit Pachat, and Xing Chen, who quickly transitioned from being colleagues to my best friends. Our myriad of activities—traveling, playing board games, practicing football, and hiking—forged countless memories, far too many to enumerate here. Your unwavering support, particularly during the challenges of the COVID-19 lockdown, was invaluable. Although I miss them already, I hold the hope that our friendship will endure. Marie Drouhin, the discussions and your talks on equilibrium propagation projects were always enlightening. Your swift understanding and effective work with the AwesomeArray chip, leading to interesting results, were truly commendable. Best wishes for your upcoming Ph.D. defense!

Joining the team, I found myself amidst talented and productive young researchers who smoothed my path and simplified myriad challenges. I extend my gratitude to the preceding generation of researchers, beginning with office-mates. Dr. Maxence Ernoult, I fondly recall your invaluable assistance with implementing AI algorithms in Python, I also fondly remember the foosball games we played alongside Axel and Tifenn. Your sense of humor and camaraderie have been truly memorable. Dr. Axel Laborieux, the wise and humble presence in our group, offered precise explanations and positive feedback that greatly benefited us all. Dr. Mamour Sarr, your serene presence and friendly football rivalry were highlights of my days. A nod of thanks also goes to Dr. Bogdan Penkovsky; our shared wu-shu classes, despite it resulted to occasional late arrival at meetings, added a unique flavor to our interactions. Acknowledgment is also due to the newer doctoral students, including Mohammed Akib, with whom I had the chance to collaborate on the "p-bit for Ising machine" project. Our work was stimulating, and I foresee you designing remarkable p-bit circuits and obtaining fascinating results from our developed chips. Working with Théo Ballet on the placement and routing of a RISC-V processor was a valuable opportunity to delve into the physical design of a complex digital system. Théo, I am confident that your contributions will elevate our research projects to new system-level heights.

A heartfelt thanks to all colleagues and friends at C2N with whom I've had the pleasure to interact. Dr. Liza Herrera Diez, your generosity and vibrancy were refreshing, and I thoroughly enjoyed the delightful treats "Chocolates and bread" to our team and beautiful paintings you shared with us. Dr. Tanvi Bhatnagarschoeffmann, your positive vibes brought light to our team, despite the relentless food talks with Atreya! Dr. Gyan Vdjagt, organizing group activities made our time more enjoyable, Dr. Maryam Massouras , our engaging discussions and your valuable advice for my Ph.D. defense were much appreciated. Dr. Guanda Wang, our hiking adventures and your generous donations during the pandemic's initial wave showcased your kind heart. Asma Mouhoub and Amina Djemmah, your support during pivotal moments, including my Ph.D. defense, was invaluable. A nod to Djohan Bonnet, Bastien Imbert, Naimul Hassan, Thomas Bersani–Veroni, and Adrien Pontlevy; although your time in the lab was brief, our intellectual exchanges enriched my experience.

I extend my gratitude to all those working at C2N who contribute to the smooth functioning of the lab. Kudos to Christophe Chassat and Alain Péan from IT, Lydia Andalon, Lea Lemaitre, Carole Bonot, Laurence Sidibé, and Bernadette Laborde from the administration, and Sophie Bouchoule and Emilia Davodeau from the doctoral school. A special mention to ChatGPT for refining the English texts for my thesis, significantly enhancing the clarity and coherence of my writing.

Journeying through the intricate paths of academia, I've come to realize it's far from a solo venture. My Best friends Dr. Bassem Boukhebouze, Khaled Saadi, and my brother Abdelkarim Harabi have been unwavering pillars of support, anchoring me with their belief and strength from the very start. A heartfelt tribute to all family and friends, especially my parents; my father, a symbol of hard work and passion, and my mother, who cultivated my fascination for science and shared her aspirations with me. Their sacrifices, love, and steadfast faith have been the foundation of my journey. My thanks go to Dr. Pietro Ferreira from University of Paris-Saclay, for teaching me essential skills in circuit design and layout, and to all the devoted teachers who have been beacons of light at every stage of my academic path.

# Contents

| In | Introduction |        | 1                                                                  |    |

|----|--------------|--------|--------------------------------------------------------------------|----|

| 1  | The          | Case f | or Building Bayesian Machines with Memristors                      | 11 |

|    | 1.1          | In/Ne  | ear Memory Computing with Memristors                               | 13 |

|    |              | 1.1.1  | The Evolution of making Efficient Chips                            | 13 |

|    |              | 1.1.2  | Toward Non-Von Neumann Machines                                    | 24 |

|    |              | 1.1.3  | Memristors for Energy-Efficient Computing                          | 28 |

|    | 1.2          | The C  | Concept of Near-Memory Compute Architecture for a Bayesian Machine | 41 |

|    | 1.3          | Steps  | of the Bayesian Machine projects                                   | 45 |

|    |              | 1.3.1  | Design Flow for Memristor-based Chips                              | 46 |

|    |              | 1.3.2  | Measurement Setup for Memristor-based Chips                        | 49 |

|    |              | 1.3.3  | Task Implementation and Energy analysis                            | 51 |

|    | 1.4          | Comp   | parison of our Bayesian Machines with Other                        |    |

|    |              | Nano   | technology-Based Machine Learning Accelerators                     | 53 |

|    |              | 1.4.1  | Our Bayesian Machines vs. Nanodevice-Based Neural Networks         | 53 |

|    |              | 1.4.2  | Other Bayesian Concepts Involving Nanodevices                      | 55 |

|    | 1.5          | Conc   | lusion                                                             | 57 |

| 2  | A St         | ochast | ic Bayesian Machine                                                | 59 |

|    | 2.1          | Bayes  | ian Inference with Stochastic Computing                            | 61 |

|    | 2.2          | Desig  | n of the Stochastic Bayesian machine                               | 64 |

|    |              | 2.2.1  | The Big Pïcture                                                    | 64 |

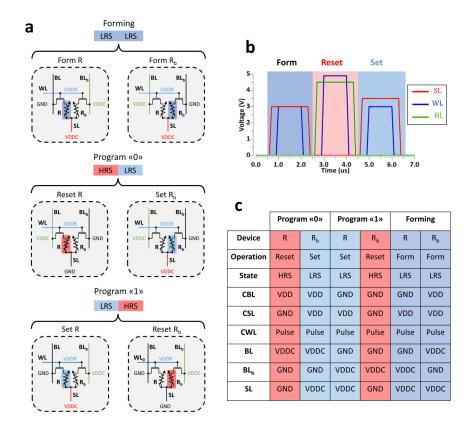

|    |              | 2.2.2  | Programming methodology of the Bayesian machine                    | 66 |

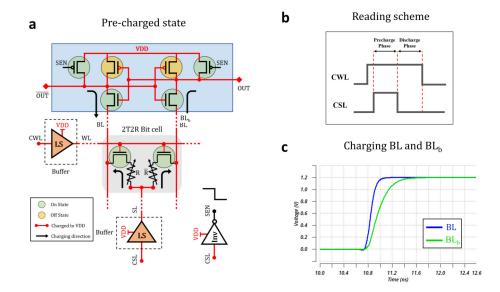

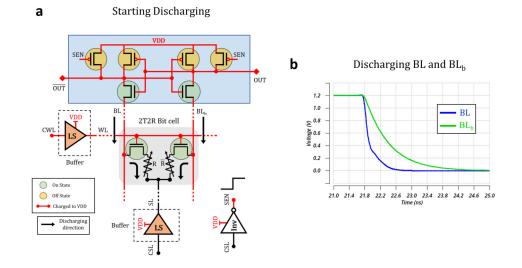

|    |              | 2.2.3  | Reading strategy and Read disturb on the Bayesian machine          | 71 |

|    |              | 2.2.4  | Inference Using a Bayesian machine                                 | 73 |

|    | 2.3          | Chara  | acterization of the Stochastic Bayesian Chip                       | 75 |

|    |              | 2.3.1  | Forming, Programming, and Read-Disturb Experiments                 | 75 |

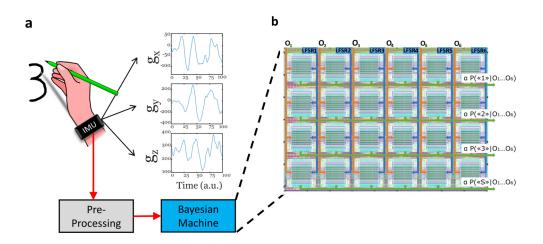

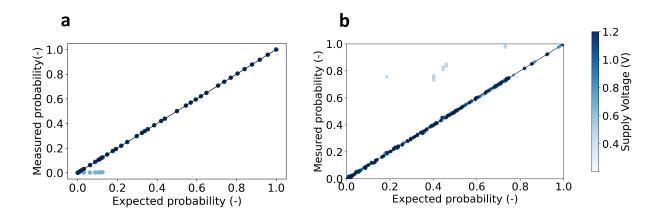

|    |              | 2.3.2  | Bayesian Inference Experiments                                     | 77 |

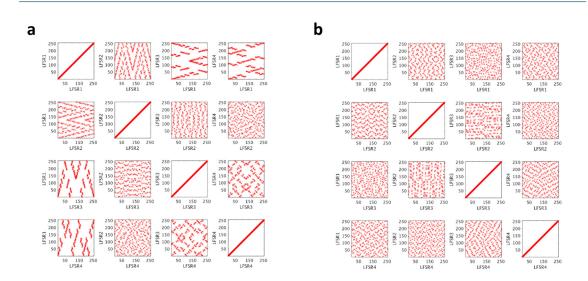

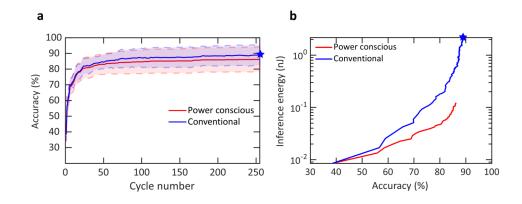

|    |              | 2.3.3  | The search for Optimal LFSR seeds                                  | 78 |

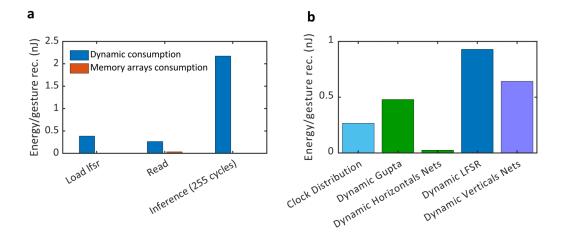

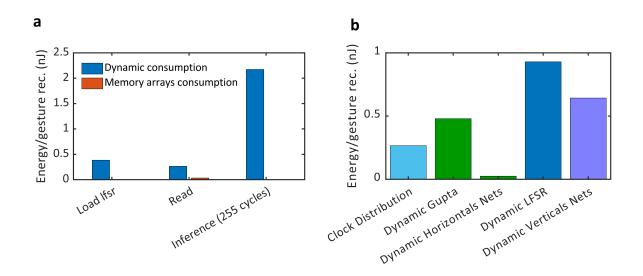

|    | 2.4          | Energ  | y efficiency of the Stochastic Bayesian machine                    | 80 |

|    | 2.5          | Nano   | device-Based True Random Number Generation                         | 84 |

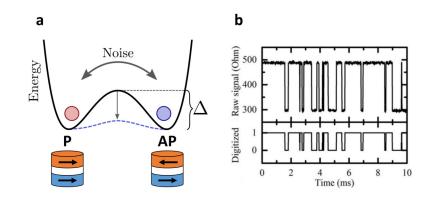

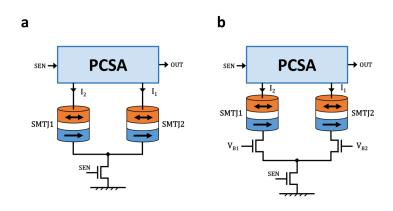

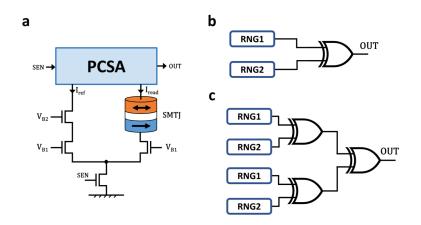

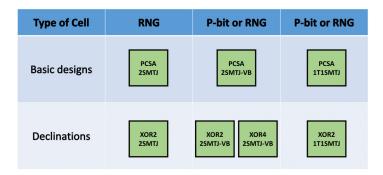

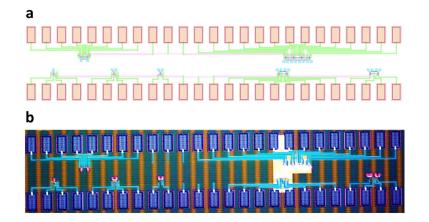

|    |              | 2.5.1 Random Number Generation with MTJs                        | 84  |

|----|--------------|-----------------------------------------------------------------|-----|

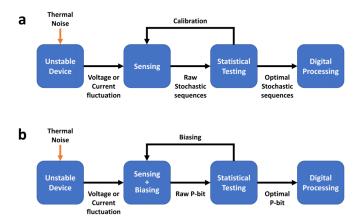

|    |              | 2.5.2 Randomness Sensing With Precharge Sense Amplifier         | 86  |

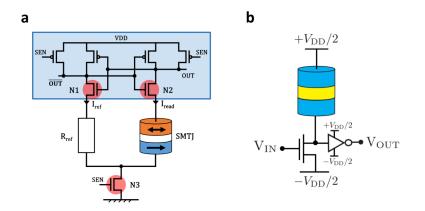

|    |              | 2.5.3 Design of SMTJ-Based RNG                                  | 88  |

|    | 2.6          | Conclusion                                                      | 92  |

|    |              | 2.6.1 Energy Estimation of a scaled stochastic Bayesian machine | 96  |

| 3  | A Lo         | garithmic Bayesian Machine                                      | 99  |

|    | 3.1          | Bayesian Inference with Logarithmic computing                   | 101 |

|    | 3.2          | Design of a Logarithmic Bayesian Machine                        | 105 |

|    | 3.3          | Measurements on the Logarithmic Bayesian machine                | 109 |

|    | 3.4          | Energy Efficiency of the Bayesian Machines                      | 113 |

|    | 3.5          | Large Scale Multi-computing Mode Bayesian machine               | 115 |

|    | 3.6          | Conclusion                                                      | 117 |

| 4  | Mul          | imode Memristor-based Prototyping Platform                      | 119 |

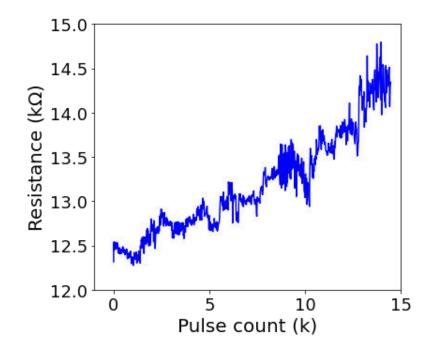

|    | 4.1          | Imperfect Memristors for Building New Computing Paradigms       | 121 |

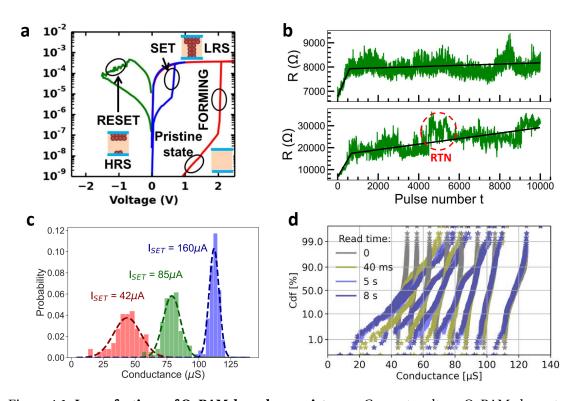

|    |              | 4.1.1 Non-Ideal Behavior of OxRAM-Based Memristor               | 121 |

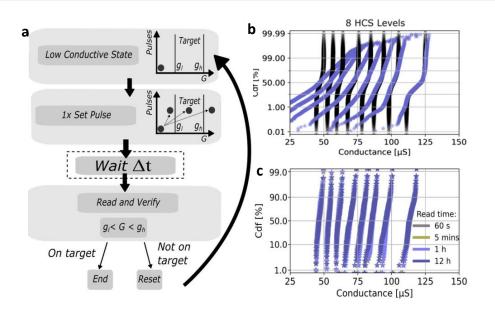

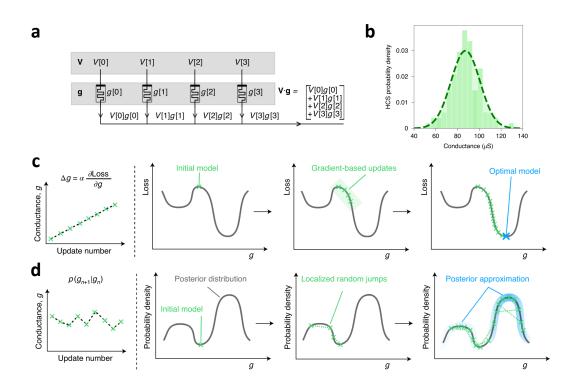

|    |              | 4.1.2 Mitigating Imperfections for Non-Conventional Computing   | 123 |

|    |              | 4.1.3 Embracing Imperfection for Non-Conventional Computing     | 125 |

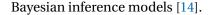

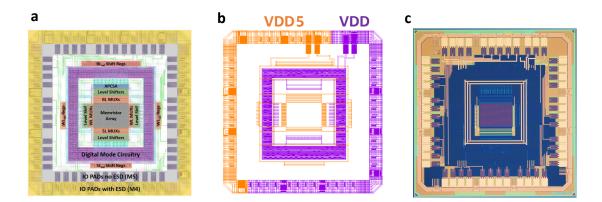

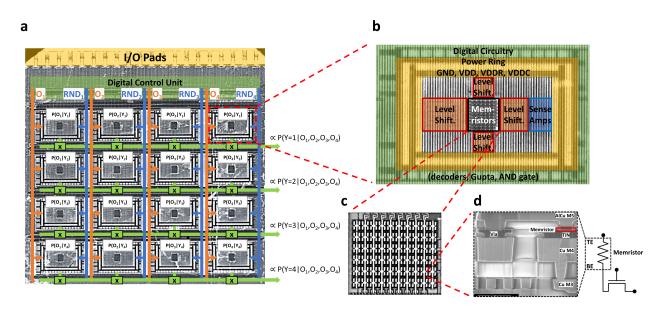

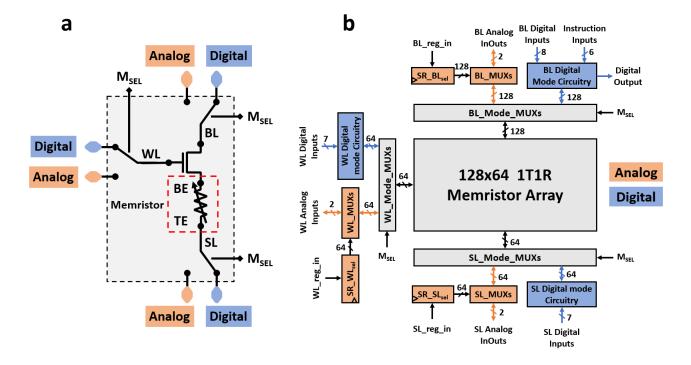

|    | 4.2          | Description of the Hybrid CMOS/Memristor Die                    | 128 |

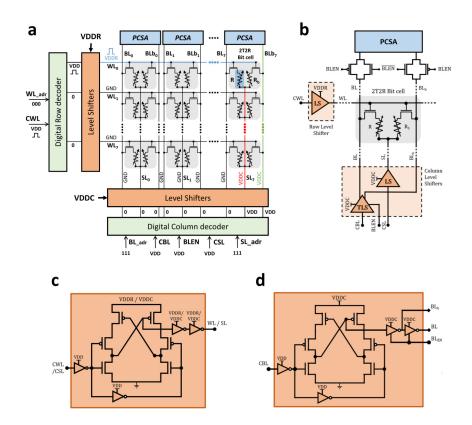

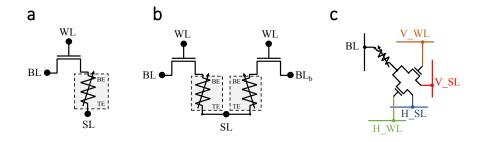

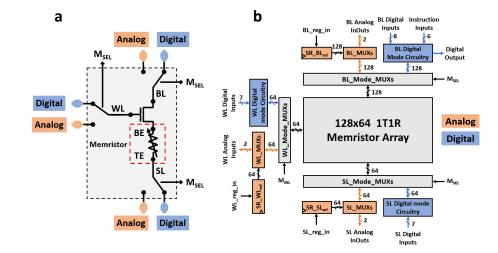

|    |              | 4.2.1 Digital Mode Circuitry                                    | 130 |

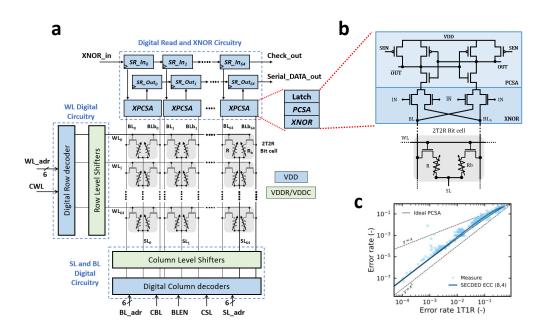

|    |              | 4.2.2 Analog Mode Circuitry                                     | 131 |

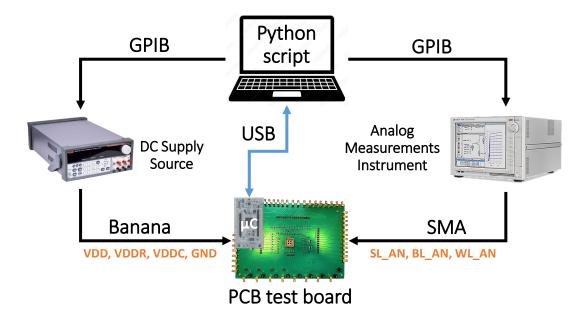

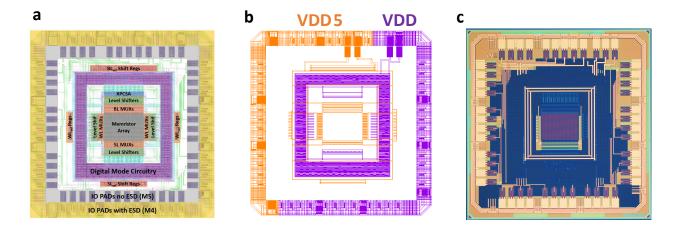

|    |              | 4.2.3 Design Signoff and Measurement Setup                      | 132 |

|    | 4.3          | Uses of the Platform                                            | 134 |

|    |              | 4.3.1 Digital Prototyping Projects                              | 134 |

|    |              | 4.3.2 Analog Prototyping Projects                               | 135 |

|    | 4.4          | Conclusion                                                      | 137 |

| Co | onclu        | sions and future work                                           | 139 |

| Li | stof         | ublications                                                     | 147 |

| Bi | Bibliography |                                                                 | 169 |

## **List of Figures**

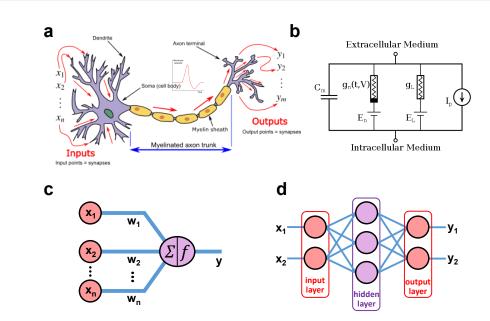

- From Biological Neuron to Artificial Neural Network. a Biological neuron (adapted from wikimedia). b An electrical circuit model for a neuron proposed by Hodgkin and Huxley, using basic electric circuit elements to implement bio-neuron behavior. c Artificial Neuron model (or perceptron), proposed by McCulloch-Pitts, the sum of the multiplication of the elements of an input vector X and a synaptic weight vector w is output by the neuron (followed by a non-linear function). d Artificial neural network with hidden layer, two inputs and two outputs.

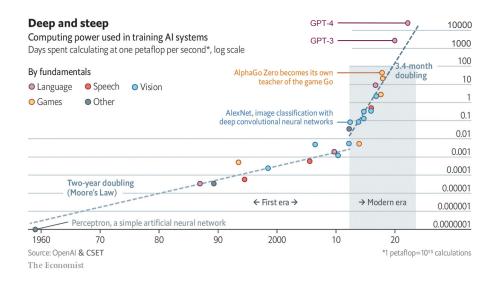

- 2 **Growth in AI compute power demands over the past six decades.** Plot of the computational power required by benchmark AI models, measured in PetaFlop-days (One petaFLOPS-day is the number of computations that could be performed in one day by a computer capable of calculating a 10<sup>15</sup> floating point operations per second). Models for several applications: vision, language, speech, and game models. Two different eras of progress can be distinguished based on the usage of growth slopes. In the first era, compute doubled every two years; in the second era, every 3.4 months [1, 2] (adapted from [3]).

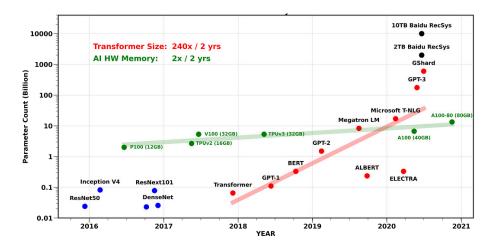

- **3 Growth in AI models parameters size, and the AI dedicated hardware memory size, from 2016 to 2021.** Growth of total number of parameters that a model needs over time. The plot shows the count for state-of-the-art models in computer vision (blue points), natural language processing (red points), recommender systems (black points), as well as the maximum memory capacity of AI hardware (green points). (Adapted from [4])

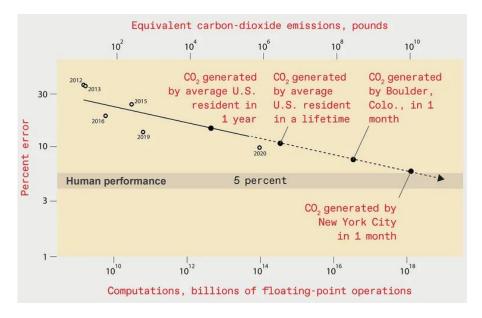

- 4 **Equivalent carbon-dioxide footprint for training AI on image recognition task.** The computing resources and energy required to train the best objects recognizing deep-learning systems designed for error levels at human performance (less than 5 percent in this graph) would be enormous, leading to the emission of as much carbon dioxide as New York City generates in one month [5] (adapted from [6]).

6

3

4

5

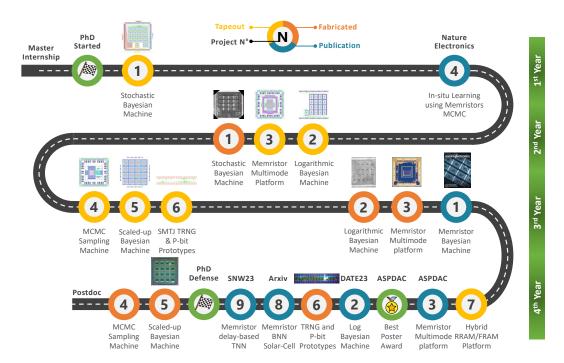

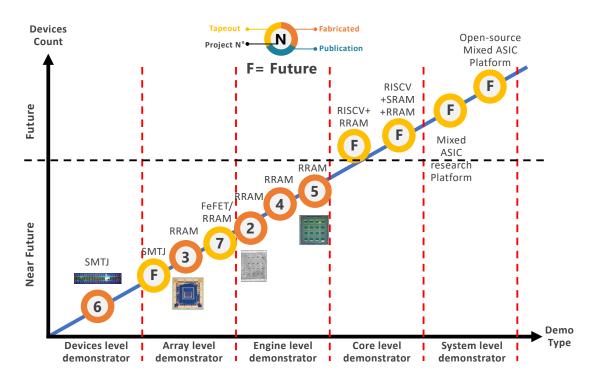

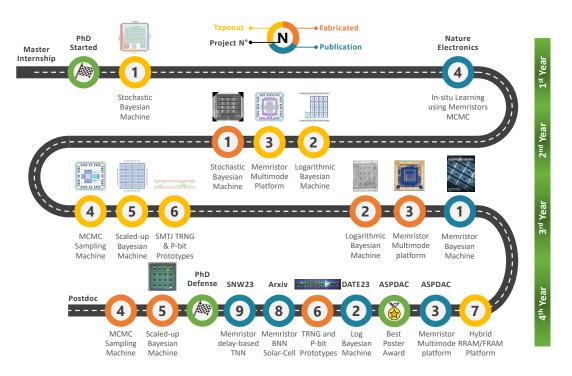

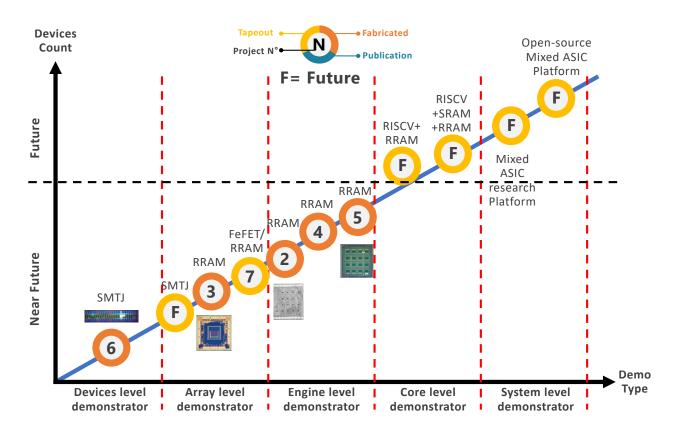

|   | 5   | <b>Ph.D. Thesis Infographic.</b> During my thesis, I have been incorporated mainly or     |    |

|---|-----|-------------------------------------------------------------------------------------------|----|

|   |     | partially in nine research projects, resulting in six publications (see list of publica-  |    |

|   |     | tions) and the design of seven emerging nanoelectronic-based integrated circuits          |    |

|   |     | (1, 2, 3, 4, and 5 are RRAM-based, 6 is MRAM-based, and 7 is FRAM based). The             |    |

|   |     | numbers stand for the projects, the color code is yellow for taped-out design (sent       |    |

|   |     | for fabrication), orange for fabricated circuits and started testing, and blue for        |    |

|   |     | paper publication. Most of the designs are fabricated in a hybrid 130nm CMOS-             |    |

|   |     | Nanodevice process; only design 7 is based on a hybrid 22nm FDSOI-Nanodevice              |    |

|   |     | process.                                                                                  | 10 |

| 1 | The | Case for Building Bayesian Machines with Memristors                                       | 11 |

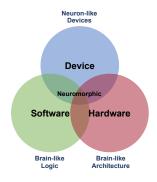

|   | 1.1 | <b>Brain-like Computing.</b> The confluence of advancements in AI algorithms, hard-       |    |

|   |     | ware technologies, and nanodevices contributes to the emergence of neuromor-              |    |

|   |     | phic computing, offering potential solutions to prevailing challenges in AI, such         |    |

|   |     | as energy efficiency.                                                                     | 12 |

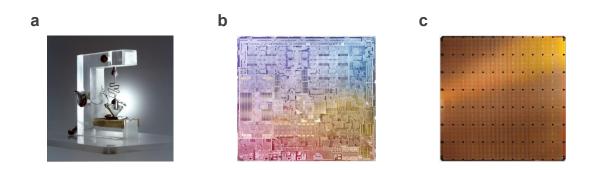

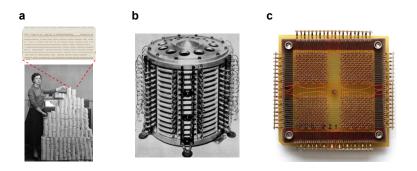

|   | 1.2 | <b>Transistors population: from one device to trillion device on a chip. a</b> The first  |    |

|   |     | transistor, developed by Walter Brattain and John Bardeen in 1947. (source: Nokia         |    |

|   |     | USA Inc. and AT&T Archives) <b>b</b> Apple M2 Chip (released on 2022), an ARM-based       |    |

|   |     | system on a chip (SoC) designed by Apple Inc. The M2 is made with TSMC's Fin-             |    |

|   |     | Fet Enhanced 5-nm technology, and it contains 20 billion transistors. The M2              |    |

|   |     | Max version contains 67 billion transistors (Source: Apple website). <b>c</b> Wafer Scale |    |

|   |     | Engine Two (WSE-2) chip, designed by Cerebras Systems, The Wafer Scale Engine             |    |

|   |     | (WSE) is a single, wafer-scale integrated circuit processor, it is designed for AI        |    |

|   |     | training and inference workloads in data-centers. The WSE-2 has 850,000 cores             |    |

|   |     | with a total of 2.6 trillion transistors, made with TSMC's FinFet 7-nm technology         |    |

|   |     | (Source: Cerebras website).                                                               | 14 |

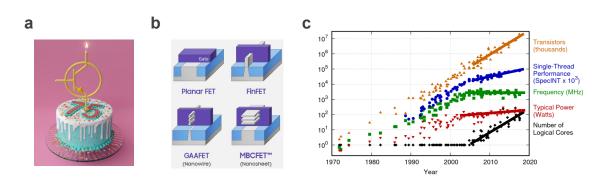

|   | 1.3 | The Evolution of the modern world's most important invention: the transistor.             |    |

|   |     | <b>a</b> 75th Transistor anniversary (cover image of the IEEE Spectrum magazine, by       |    |

|   |     | Lisa Sheehan). <b>b</b> The evolution of MOSFET Based transistors (Source: Samsung        |    |

|   |     | Tech Blog). <b>c</b> The Dennard scaling stoped around 2005, Moore's law trend might      |    |

|   |     | follow the same destiny (Reprofuced from [7]).                                            | 15 |

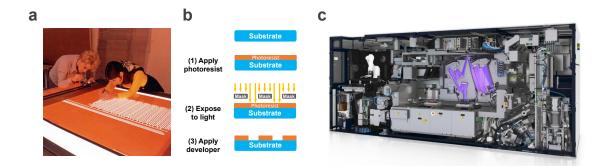

|   | 1.4 | Photolithography from Rubylith to EUV. a Hand drawing patterning on Rubylith              |    |

|   |     | photomasks (Source: Intel and Computer history museum). <b>b</b> The basic steps of       |    |

|   |     | the lithography process include substrate preparation, photoresist application,           |    |

|   |     | mask alignment and exposure, development, etching or deposition, and photore-             |    |

|   |     | sist removal. <b>c</b> ASML EUV machine (Source: ASML website)                            | 16 |

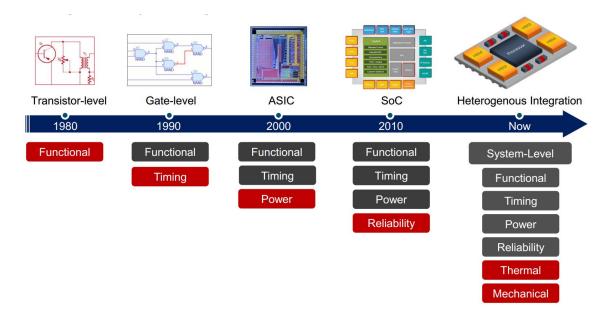

|   | 1.5 | Evolution of chip design complexity. From only functional design and verifi-              |    |

|   |     | cation of transistor level circuits, to multi-process multidisciplinary design and        |    |

|   |     | verification of Heterogeneous chips (Reproduced from [8]).                                | 18 |

#### **LIST OF FIGURES**

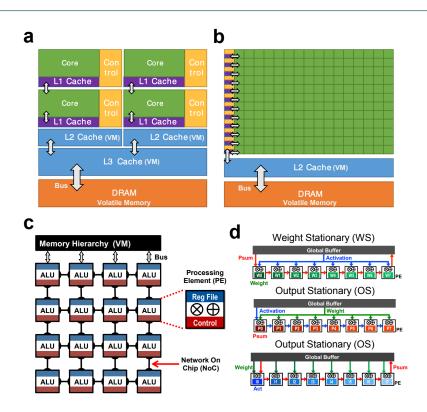

| 1.6  | <b>Current used Computer architecture. a</b> A Simplified CPU architectures, and <b>b</b>                                                                                  |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | a GPU architectures (adapted from the NVIDIA documentation). <b>c</b> Spatial Archi-                                                                                       |          |

|      | tecture for Highly-Parallel Computing, suited for NPUs, it has a tiling architecture,                                                                                      |          |

|      | consisting Parallel processing elements, interconnected by network on chip (Re-                                                                                            |          |

|      | produced from [9]). <b>d</b> Data reuse schemes, used in most of Spatial Architecture                                                                                      |          |

|      | based NPUs, for decreasing data movement by Minimizing weights movement                                                                                                    |          |

|      | with weight stationary scheme, Minimizing outputs movement with output sta-                                                                                                |          |

|      | tionary scheme, or Minimizing activation's movement with activation stationary                                                                                             |          |

|      | scheme (Reproduced from [9]).                                                                                                                                              | 20       |

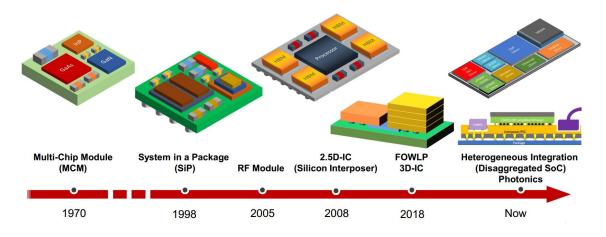

| 1.7  | Evolution of Multi-Chip/Chiplet Packaging (Reproduced from [8]).                                                                                                           | 22       |

| 1.8  | Data movement and the von Neumann bottleneck. a (Bottom) In the conven-                                                                                                    |          |

|      | tional von Neumann architecture, the memory unit and the processing unit are                                                                                               |          |

|      | physically separated; the data needs to be constantly shuttled through them via a                                                                                          |          |

|      | bus. This imposes a limitation in terms of speed and energy of computation: it is                                                                                          |          |

|      | called the von Neumann bottleneck. (Top) A worker, company and house anal-                                                                                                 |          |

|      | ogy. <b>b</b> The energy costs of single arithmetic operations for different precisions,                                                                                   |          |

|      | and energy of memory access to SRAM and DRAM in a modern computer (repro-                                                                                                  |          |

|      | duced from [10]). The energy for accessing DRAM is four orders of magnitude                                                                                                |          |

|      | time higher than performing 8-bit addition operation.                                                                                                                      | 24       |

|      |                                                                                                                                                                            |          |

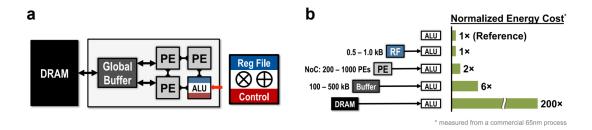

| 1.9  | Specialized memory hierarchy for a spatial architecture. a An example of Mem-                                                                                              |          |

| 1.9  | <b>Specialized memory hierarchy for a spatial architecture. a</b> An example of Memory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost |          |

| 1.9  |                                                                                                                                                                            | 25       |

|      | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost                                                                                    | 25       |

|      | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost of data movement in a memory hierarchy (Reproduced from [9])                       | 25       |

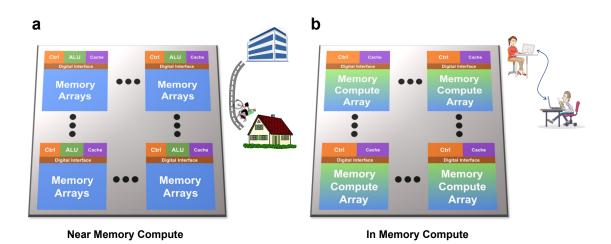

|      | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost of data movement in a memory hierarchy (Reproduced from [9])                       | 25<br>26 |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost of data movement in a memory hierarchy (Reproduced from [9])                       |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost of data movement in a memory hierarchy (Reproduced from [9])                       |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost of data movement in a memory hierarchy (Reproduced from [9])                       |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    |          |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    | 26       |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    | 26       |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    | 26       |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    | 26       |

| 1.10 | ory Hierarchy of a spatial architecture (Reproduced from [9]). <b>b</b> The Energy cost<br>of data movement in a memory hierarchy (Reproduced from [9])                    | 26       |

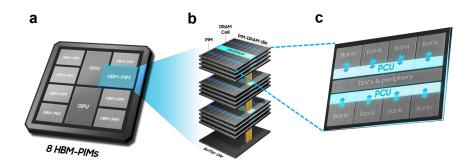

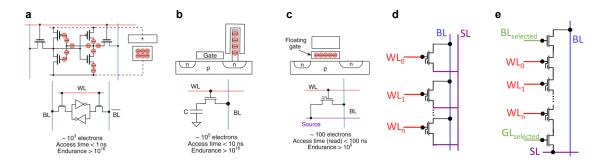

| 1.13 Semiconductor-Based Memory Technologies. a A 6T SRAM cell consists of two<br>CMOS inverters connected back to back. b A DRAM cell comprises a capacitor of<br>that serves as the storage node, which is connected in series to a FET. c Floating<br>gate transistor. The storage node of a flash memory cell is a floating gate of a<br>FET, and can be been used for d flash NOR structure or e flash NAND structure<br>(Reproduced from [11])                                                                                                                                                                                                                                                                                                                                               | g<br>a                                      |

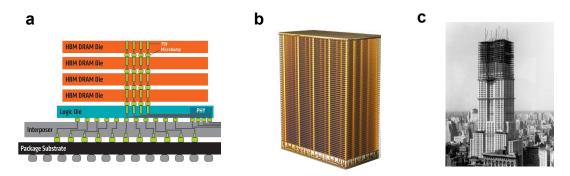

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| <ul> <li>1.14 <b>3D integration of Memory Technologies. a</b> 3D stacking of DRAM based HBM memories (Source: AMD website). <b>b</b> 3D NAND Memory from Micron (Source: Micron website) <b>c</b> Empire State Building (3D urban architecture) under construction. (Source: reddit)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                           |

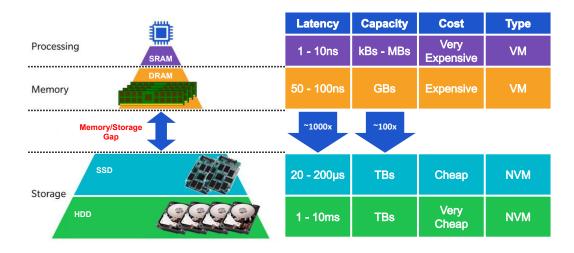

| 1.15 Memory Hierarchy and Addressing the Gap with Emerging Technologies. $~$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 33                                        |

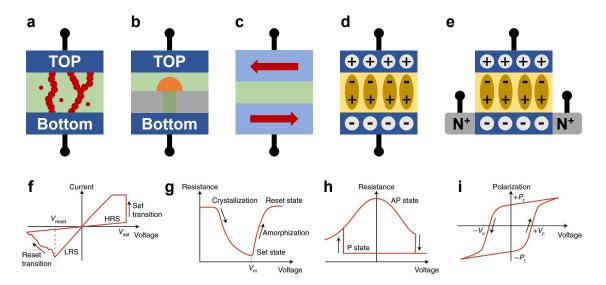

| 1.16 Emerging Memory Technologies. a Resistive RAM structure and its f current voltage (I-V) characteristics for a bipolar switching device. b Phase-change memory structure and its g resistance change characteristics. c Magnetic RAM structure and its h resistance-voltage characteristics. d Ferroelectric RAM structure and e Ferroelectric FET structure and their i polarization–voltage hysteretic characteristic. (Reproduced from [11])                                                                                                                                                                                                                                                                                                                                                | -<br>-<br>e                                 |

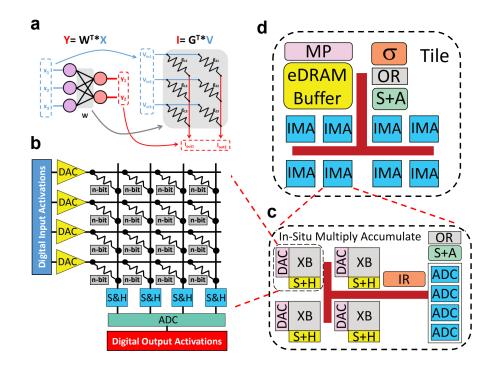

| 1.17 <b>In-Memory computing with Memristor crossbars for artificial neural network</b><br><b>a</b> Neural network with three inputs and two outputs mapped on a memristo<br>crossbar of three rows and two columns. The multiply-and-accumulation op<br>eration can be performed in the analog regime, taking advantage of Ohm's Law<br>and Kirchhoff's Law. <b>b</b> A memristor crossbar used as a vector-matrix multiplier<br>including ADCs, DACs, and digital input and output cicuitry. This crossbar is a<br>main element in the ISAAC architecture hierarchy, used to build <b>c</b> the In-Situ<br>Multiply-and-Accumulate block that is part of <b>d</b> the ISSAC Tile block. (Repro<br>duced from [12])                                                                                | r<br>-<br>v<br>;,<br>a<br>1                 |

| 1.18 <b>In-Memory computing with resistance summation for artificial neural network</b><br><b>a</b> Resistance summation crossbar array architecture. <b>b</b> Time-domain readour<br>method. A lumped capacitor and distributed parasitic capacitors in the array are<br>charged, and the time taken for the voltage at the end of the column to reach a<br>reference voltage is measured, correlating to the column resistance. The resist<br>tance value represent the dot product of the input vector and the weight vector. On<br>Bit-cell structure, which combines two parallel paths, each comprising a resistive<br>device and a MOSFET in series. <b>d</b> Implementation of an analog XNOR operation<br>the multiply operation for the binary neural network, by the bit-cell structure | t<br>e<br>a<br>-<br><b>c</b><br>e<br>e<br>, |

| (Reproduced from [13])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 39                                        |

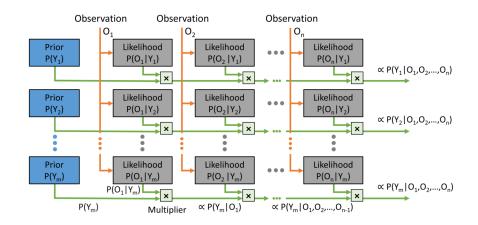

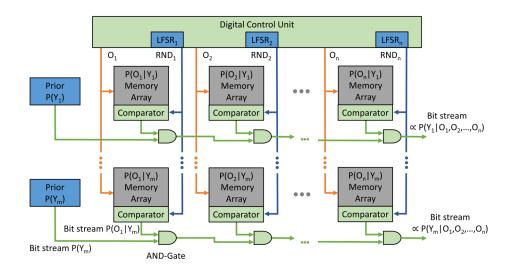

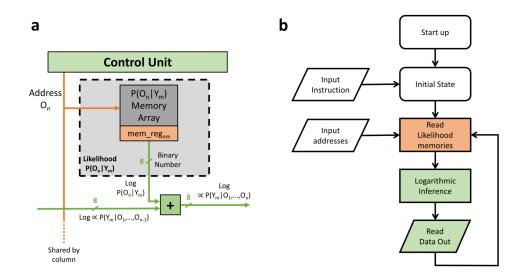

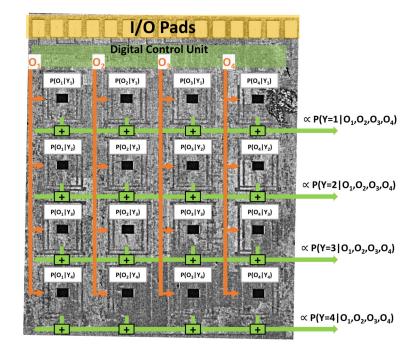

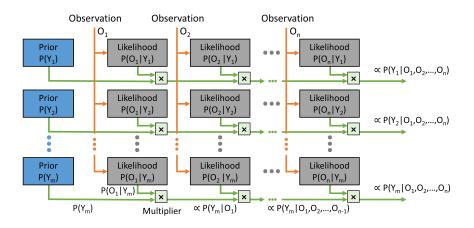

| 1.19 General architecture of the Bayesian machine. The likelihoods are stored in like-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| lihood memory arrays implemented by memristor arrays. Observations from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| real world choose the appropriate probability values from likelihood memory ar-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| rays, based on which the probability values are red from likelihood arrays, which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| are multiplied by multipliers. At the output, the generated results encode the pos-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| terior distribution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43       |

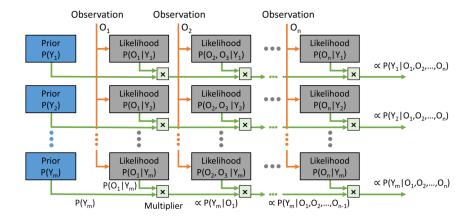

| $1.20 \ {\rm Architecture\ of\ the\ Bayesian\ machine\ with\ non-conditionally\ independent\ ob-$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| servations. This architecture performs non-naive Bayesian inference following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| eq. 1.5, by pooling observations $O_2$ and $O_3$ into the same column                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44       |

| 1.21 Affiliation of collaborating research entities in the Bayesian machine project.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| Including C2N, IM2NP, CEA-Leti, ISIR, and HawAI.tec. Along with image of our                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| paper on the cover of Nature Electronics Journal [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45       |

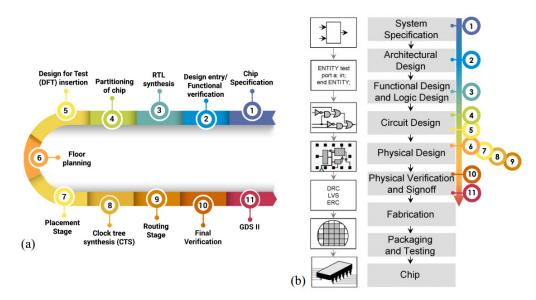

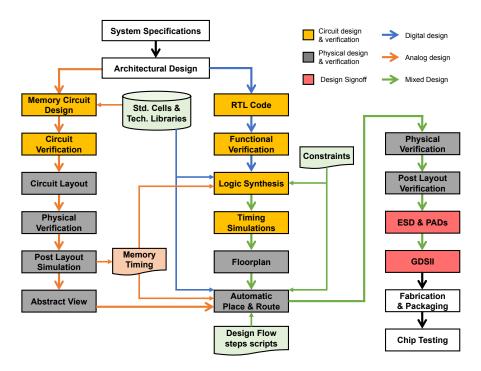

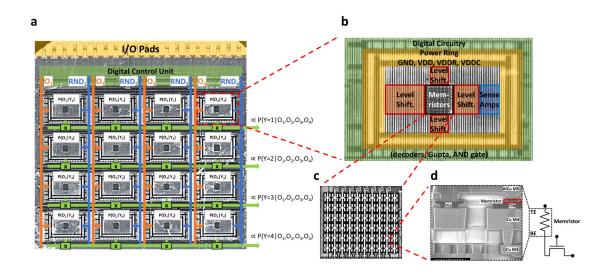

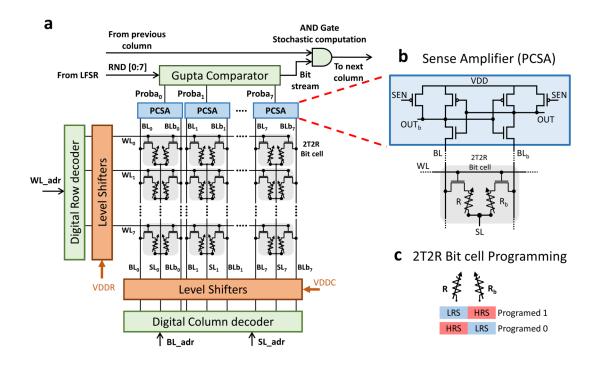

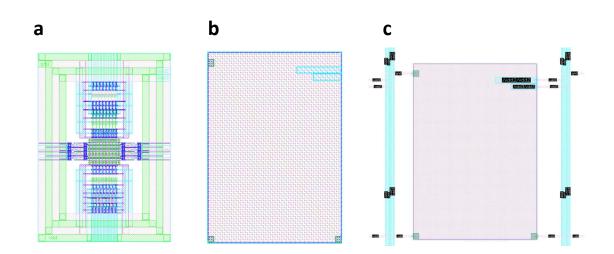

| 1.22 Overview of an Integrated Circuit Design Flow. a Computer-aided steps per-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| formed with EDA Tools. At the end, GDS mask layouts are obtained, ready for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| the fabrication process (Reproduced from [15]). <b>b</b> Diagram of the main steps for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| making a chip from system specification to ready-to-use chip (Reproduced from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| wikimedia)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 1.23 Diagram illustrating our custom-developed automated design flow for inte-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 1.23 Diagram illustrating our custom-developed automated design flow for inte-<br>grating mixed digital and memory circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48       |

| grating mixed digital and memory circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48       |

| grating mixed digital and memory circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48       |

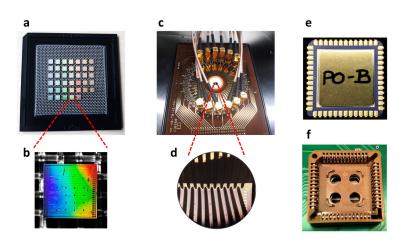

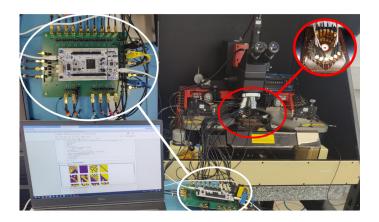

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48       |

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48       |

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 48       |

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used to form connections between packaged chips and PCB. Chips can be easily ex-</li> </ul>                                                                                                                                                                                                                                                                                                                                 |          |

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             | 48<br>50 |

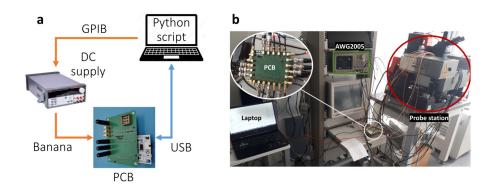

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used to form connections between packaged chips and PCB. Chips can be easily exchanged or removed.</li> <li>1.25 Measurement setups for Bayesian machine systems. a Setup for the packaged</li> </ul>                                                                                                                                                                                                                       |          |

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used to form connections between packaged chips and PCB. Chips can be easily exchanged or removed.</li> </ul>                                                                                                                                                                                                                                                                                                               |          |

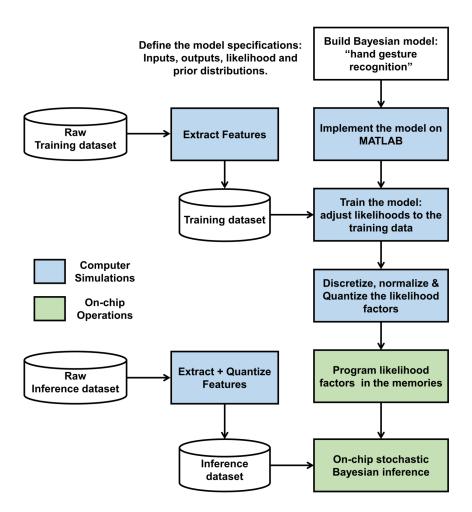

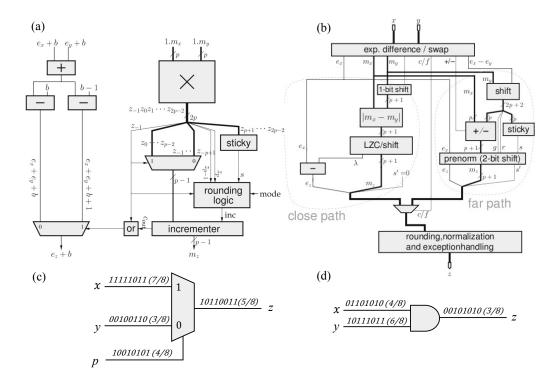

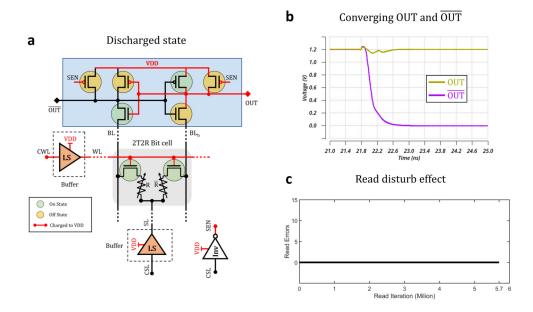

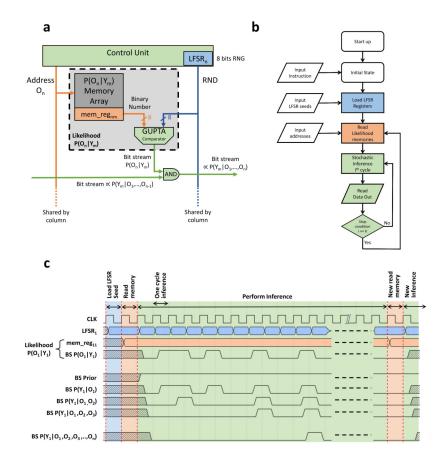

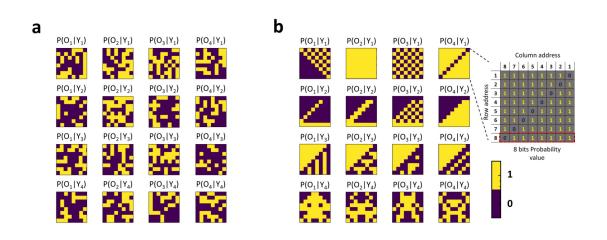

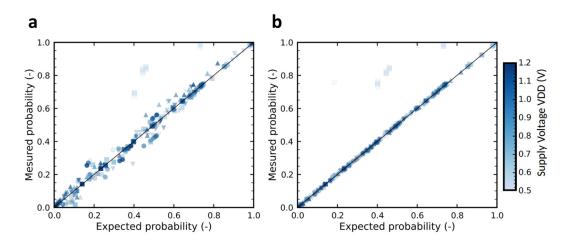

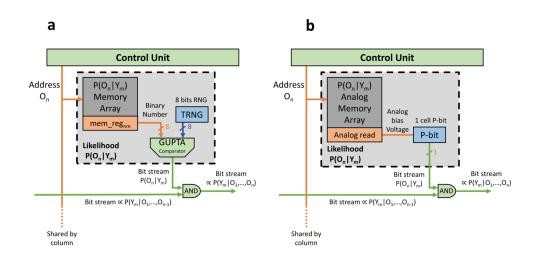

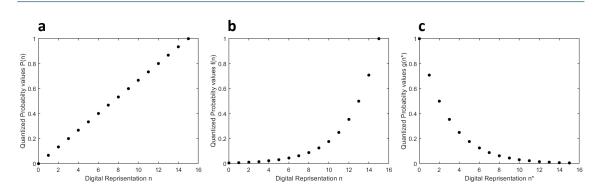

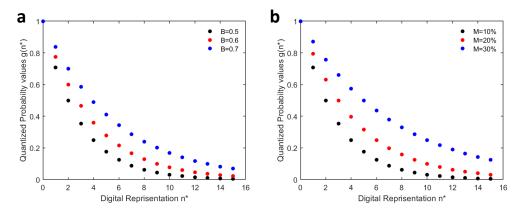

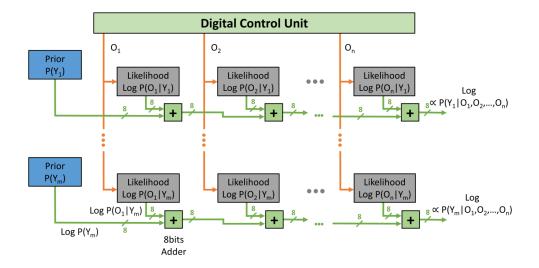

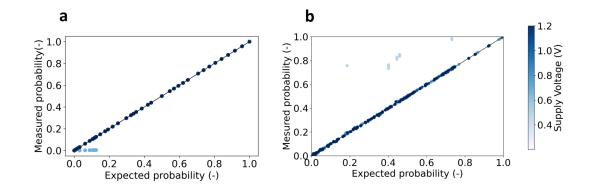

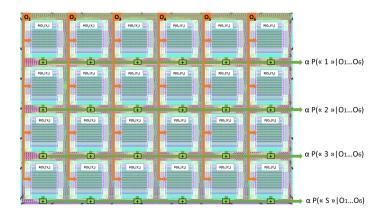

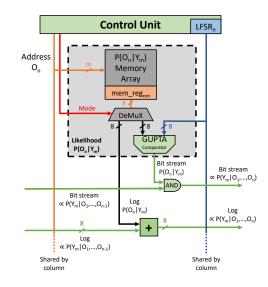

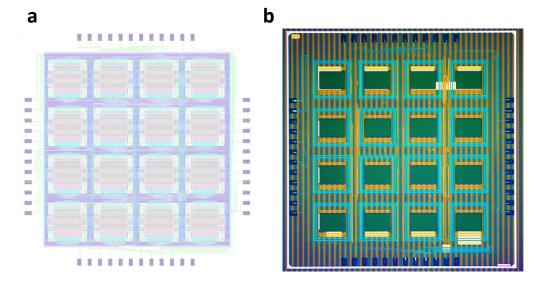

| <ul> <li>grating mixed digital and memory circuits.</li> <li>1.24 Packaging or probe testing of Bayesian machine dies. a Non-Packaged batch (Logarithmic chip) and b a zoom-in on one die. c The custom-made 25-pads probe card, used within the probe station to connect the pads of the non-packaged dies to SMA connectors. d The operation of connecting the 25 micro-probes to the 25 chip pads. e Packaged die with a J-Lead Ceramic Chip Carrier of 52 pins (JLCC52) and f a plastic leaded chip carriers (PLCC) sockets, a chip carrier used to form connections between packaged chips and PCB. Chips can be easily exchanged or removed.</li> <li>1.25 Measurement setups for Bayesian machine systems. a Setup for the packaged dies. b Setup for the non-packaged dies.</li> <li>1.26 The different steps of a project with the Bayesian machine, from training to on-</li> </ul>                                                                               | 50       |