### Développement prouvé de composants formels pour un générateur de code embarqué critique pré-qualifié

Nassima Izerrouken

#### ▶ To cite this version:

Nassima Izerrouken. Développement prouvé de composants formels pour un générateur de code embarqué critique pré-qualifié. Autre [cs.OH]. Institut National Polytechnique de Toulouse - INPT, 2011. Français. NNT: 2011INPT0137. tel-04240298

#### HAL Id: tel-04240298 https://theses.hal.science/tel-04240298

Submitted on 13 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

## En vue de l'obtention du DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

#### Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

#### Discipline ou spécialité:

Sûreté Logiciel et Calcul Haute Performance

#### Présentée et soutenue par :

Nassima IZERROUKEN

le: mercredi 6 juillet 2011

#### Titre:

Développement prouvé de composants formels pour un générateur de code embarqué critique pré-qualifié

#### **Ecole doctorale:**

Mathématiques Informatique Télécommunications (MITT)

#### Unité de recherche:

**IRIT**

#### Directeur(s) de Thèse:

M. Patrick SALLE, Prof., INPT-ENSEEIHT, Directeur de thèse M. Marc PANTEL, M.C., INPT-ENSEEIHT, Codirecteur de thèse

#### Rapporteurs:

Mme Sandrine BLAZY Prof., Université de Rennes M. Jean-Pierre TALPIN, D.R., INRIA-Rennes

#### Membre(s) du jury:

M. Yamine AIT-AMEUR, Prof., Université de Poitiers, Examinateur Mme Virginie WIELS, Ingénieur de recherche, ONERA-Toulouse, Examinateur M. Xavier THIRIOUX, M.C., INPT-ENSEEIHT, Examinateur M. Patrick SALLE, Prof., INPT-ENSEEIHT, Directeur de thèse M. Marc PANTEL, M.C., INPT-ENSEEIHT, Codirecteur de thèse

### REMERCIEMENTS

Le travail présenté dans ce document a été réalisé à l'Institut de Recherche en Informatique de Toulouse, au sein de l'équipe Assistance à la certification d'Applications DIstribuées et Embarquées (ACADIE) et également à Continental Automotive dans le cadre du projet européen GENEAUTO.

Je tiens à remercier en premier lieu mes chèrs encadrants Marc Pantel et Xavier Thirioux de m'avoir soutenue et guidée. Merci à Marc pour son humanité, sa sagesse, sa culture du domaine et la liberté qu'il m'a laissé pour guider ma recherche. Je le remercie d'avoir été disponible pour répondre aux nombreuses interrogations que je me posais de jour comme de nuit.

Merci à Xavier pour sa sympathie, son investissement pour m'initier au système CoQ, sa gentillesse, sa disponibilité et son imaginaire débordant tant dans la recherche que dans la vie quotidienne.

Je remercie également Olivier Ssi Yan Kai, mon tuteur industriel à Continental, qui m'a soutenu dans les différentes réunions de Geneauto. Merci à tous les membres du projet Geneauto pour les échanges fructueux qu'on avaient eu.

Merci à Patrick Sallé qui a accepté d'être mon directeur de thèse.

Je remercie les membres du jury qui ont accepté d'évaluer mon travail :

- Virginie Wiels qui a présidé le jury ;

- Sandrine Blazy et Jean-Pierre Talpin, tous les deux rapporteurs de ma thèse, qui ont lu et évalué mon travail;

- Jean-Louis Colaço et Yamine Ait-Ameur qui ont bien accepté d'examiner ma thèse;

Ma thèse n'aurait jamais vu le jour sans le soutien et l'encouragement de plusieurs personnes.

Mes pensées affectueuses à mes amis et collègues : Hejer Rejeb qui m'est plus une soeur qu'une amie, Fatiha Bouabache qui est toujours là, ma cobureau Mounira Kezadri qui a supporté mes crises de stress, Philippe Queinnec (mon psy), fort sympathique, qui est toujours là pour m'écouter et me conseiller mais également pour partager avec moi un peu de chocolat, je n'oublierai pas les fous rires avec Sandrine Mouysset et ViTToria Moya qui ont égayé mes journées au labo! Je remercie également Tanguy Le Berre et Nadège Pontisso pour les moments sympathiques que nous avons passés ensembles aux anciens bureaux. Merci à Andres Toom pour toutes les réponses qu'il m'a apporté lorsque SIMULINK se comporte "bizarrement"!

4 Remerciements

Un grand merci à Marcel Gandriau avec qui je me fait un plaisir d'enseigner le module «traduction des langages». Merci également à tous les membres ACADIE, notamment Philippe Mauran, Xavier Crégut, Christiane Massoutié et Aurélie Hurault pour leur sympathie.

Merci à l'équipe administrative et technique de l'IRIT-ENSEEIHT pour leur sympathie, je pense particulièrement à Sylvie Eichen et Sylvie Armengaud. Vous êtes les meilleures secrétaires!

Je remercie également André-Luc Beylot le directeur de l'IRIT-ENSEEIHT, Emmanuel Chaput et Riadh Dhaou pour leur sympathie.

Un remerciement particulier à mon amie Pascaline Parisot qui m'a soutenue du début de la thèse jusqu'à la fin, de m'avoir lu et corrigé le manuscrit et d'avoir été présente dans toutes les circonstances ...

Je souhaiterai remercier plusieurs personnes du coté de ma famille.

Je commence par tonton Moahand Tayeb Belarif qui sans lui je n'aurais rien fait de tout cela. You're the best ; )

Je ne remercierai jamais assez mes chers parents qui m'ont toujours fait confiance et ont cru en moi. Merci papa et merci maman pour tout ce que vous m'avez donné. Vous avez tout fais pour moi, je vous dois ce que je suis et je vous dois mon devenir.

Je remercie également mes frères Amine et Salah pour leur encouragement incessant et pour les blagues qui me distraient lorsque tout n'est pas rose.

Une grande pensée à la famille Izerrouken, Belarif et Kacimi.

Une immense dédicace à la plus belle ville du monde : Oran, la ville qui m'a bercé et qui m'a tant donné!

Enfin et non finalement, je remercie mon cher et tendre époux de m'avoir encouragé, soutenu et d'avoir supporté mon stress et surtout mon caractère! Encore une fois merci.

Je dédie cette thèse à mon ange Louna qui a éclairé mon obscurité ...

### Table des matières

| TA | BLE | DES N  | <b>ATIÈRE</b> | s                                                  | 5  |

|----|-----|--------|---------------|----------------------------------------------------|----|

| Lı | STE | DES FI | IGURES        |                                                    | 11 |

| Ι  | Int | roduc  | ction         |                                                    | 1  |

| 1  | Int | 'RODU  | CTION         |                                                    | 3  |

|    | 1.1 | Intro  | DUCTION       | 1                                                  | 3  |

|    | 1.2 | TRAVA  | AUX CONN      | JEXES                                              | 8  |

| 2  | ÉтА | T DE   | L'ART         |                                                    | 13 |

|    | 2.1 | Intro  | DUCTION       | 1                                                  | 13 |

|    | 2.2 | APER   | ÇU DES N      | ORMES DE CERTIFICATION                             | 14 |

|    | 2.3 | Taxo   | NOMIE DI      | ES TECHNIQUES DE VÉRIFICATION ET DE VALIDATION     | 15 |

|    |     | 2.3.1  | Techniq       | ues de vérification et de validation semi-formelle | 15 |

|    |     |        | 2.3.1.1       | Vérification par tests                             | 15 |

|    |     |        | 2.3.1.2       | Vérification par relecture                         | 16 |

|    |     | 2.3.2  | Techniq       | ues de vérification formelle                       | 16 |

|    |     |        | 2.3.2.1       | Génération automatique de tests et oracles         | 17 |

|    |     |        | 2.3.2.2       | Vérification à l'exécution                         | 17 |

|    |     |        | 2.3.2.3       | Vérification de modèles                            | 17 |

|    |     |        | 2.3.2.4       | Preuve de programmes                               | 17 |

|    |     |        | 2.3.2.5       | Analyse statique                                   | 18 |

|    |     |        | 2.3.2.6       | Validation de la traduction                        | 19 |

|    |     |        | 2.3.2.7       | Code auto-certifié                                 | 19 |

|    |     |        | 2.3.2.8       | Développement prouvé de compilateurs               | 19 |

|    | 2.4 |        |               | OISIE DANS GENEAUTO                                | 20 |

|    | 2.5 | Synti  | HÈSE          |                                                    | 21 |

| II | C   | ontext | te & Fo       | rmalisation                                        | 23 |

|    |     |        |               |                                                    |    |

| 3  | Élí | EMENT  | S DE MI       | SE EN ŒUVRE                                        | 25 |

| -  | 3.1 |        |               | · · · · · · · · · · · · · · · · · · ·              | 25 |

|    | 3.2 |        |               | IULINK ET STATEFLOW                                | 26 |

|    |     | 3.2.1  | SIMULIN       | ик par l'exemple                                   | 26 |

|    |     | 3.2.2  |               | ow par l'exemple                                   | 32 |

|    |     | 3.2.3  |               | nancement en Simulink                              | 36 |

|    |     |        | 3.2.3.1       | Circuits aux flots de données sans mémoire         | 36 |

|   |     |       | 3.2.3.2    | Circuits aux flots de données avec mémoire              | 37 |

|---|-----|-------|------------|---------------------------------------------------------|----|

|   |     |       | 3.2.3.3    | Circuits aux flots de contrôle                          | 38 |

|   |     | 3.2.4 | Typage e   | en Simulink                                             | 40 |

|   | 3.3 | GENE  | Auto : Gi  | ÉNÉRATEUR DE CODE AUTOMATIQUE                           | 43 |

|   |     | 3.3.1 | Architec   | ture de GeneAuto                                        | 44 |

|   | 3.4 | Lang  | AGES ET G  | ÉNÉRATEURS DE CODE                                      | 45 |

|   |     | 3.4.1 |            | e Workshop-Embedded Coder                               | 46 |

|   |     | 3.4.2 |            | nk                                                      | 46 |

|   |     | 3.4.3 |            | ,                                                       | 46 |

|   |     | 3.4.4 |            | s et outils synchrones                                  | 47 |

|   |     |       | 3.4.4.1    | Lustre                                                  | 47 |

|   |     |       | 3.4.4.2    | SIGNAL                                                  | 48 |

|   |     |       | 3.4.4.3    | Esterel                                                 | 48 |

|   |     |       | 3.4.4.4    | Syndex                                                  | 48 |

|   |     |       | 3.4.4.5    | Flots de Données Synchrones (SDF)                       | 49 |

|   |     | 3.4.5 | Langage    | s de description d'architecture                         | 49 |

|   |     |       | 3.4.5.1    | Aadl                                                    | 49 |

|   |     |       | 3.4.5.2    | UML                                                     | 50 |

|   | 3.5 | FORM  |            | N DES CIRCUITS ANALYSÉS                                 | 50 |

|   |     | 3.5.1 |            | ntation des circuits                                    | 52 |

|   | 3.6 | Assis |            | PREUVE COQ                                              | 53 |

|   |     | 3.6.1 |            | tion à Coq                                              | 53 |

|   |     |       | 3.6.1.1    | Types inductifs                                         | 54 |

|   |     |       | 3.6.1.2    | Types dépendants                                        | 56 |

|   |     |       | 3.6.1.3    | Définitions et fonctions                                | 56 |

|   |     |       | 3.6.1.4    | Modules                                                 | 57 |

|   |     |       | 3.6.1.5    | Preuves de théorème                                     | 58 |

|   |     |       | 3.6.1.6    | Programmation par la preuve                             | 58 |

|   |     | 3.6.2 |            | on de programmes                                        | 60 |

|   | 3.7 |       |            |                                                         | 61 |

|   |     |       |            |                                                         |    |

| 4 | Pro | CESSU | JS DE DÉ   | VELOPPEMENT D'OUTILS ÉLÉMENTAIRES                       | 63 |

|   | 4.1 |       |            |                                                         | 63 |

|   | 4.2 | Proci | ESSUS DE I | DÉVELOPPEMENT DANS GENEAUTO                             | 64 |

|   | 4.3 | Proci | ESSUS DE 1 | DÉVELOPPEMENT DES OUTILS ÉLÉMENTAIRES                   | 65 |

|   |     | 4.3.1 | Plan de    | développement classique                                 | 66 |

|   |     |       | 4.3.1.1    | Spécification des exigences                             | 66 |

|   |     |       | 4.3.1.2    | Phase de conception                                     | 66 |

|   |     |       | 4.3.1.3    | Phase d'implantation                                    | 67 |

|   |     |       | 4.3.1.4    | Livraison                                               | 67 |

|   |     | 4.3.2 | Plan de d  | développement exploitant les technologies formelles     | 67 |

|   |     |       | 4.3.2.1    | Phase de spécification de l'outil élémentaire           | 67 |

|   |     |       | 4.3.2.2    | Développement d'adaptateurs Java et OCAML               | 67 |

|   |     |       | 4.3.2.3    | Spécification formelle                                  | 68 |

|   |     |       | 4.3.2.4    | Description formelle de la conception                   | 69 |

|   |     |       | 4.3.2.5    | Génération de code exécutable                           | 70 |

|   | 4.4 | Proci | ESSUS DE V | VÉRIFICATION                                            | 70 |

|   |     | 4.4.1 | Processu   | s de vérification d'un outil élémentaire développé avec |    |

|   |     |       | des méth   | nodes classiques                                        | 70 |

|   |     |       | 4.4.1.1    | Vérification de la spécification                        | 70 |

|   |     |       | 4.4.1.2    | Vérification de la conception                           | 71 |

|   |     |       |            | 4.4.1.2.1 Vérification des données de conception        | 71 |

|    |               |       |                          | 4.4.1.2.2       | Vérification d standards |          |            |    | . 71         |

|----|---------------|-------|--------------------------|-----------------|--------------------------|----------|------------|----|--------------|

|    |               |       | 4.4.1.3                  | Várification    | n de l'implantatio       |          |            |    |              |

|    |               |       | 4.4.1.4                  |                 | n des outils éléme       |          |            |    |              |

|    |               | 4.4.2 |                          |                 | tion d'un outil éle      |          |            |    |              |

|    |               | 1.1.2 | 4.4.2.1                  |                 | n de la spécificati      |          |            |    |              |

|    |               |       | 4.4.2.2                  |                 | n de la conceptio        |          |            |    |              |

|    |               |       |                          |                 |                          |          | •          |    | . <b>7</b> 5 |

|    |               |       | 4.4.2.3                  |                 | n de la descriptio       |          |            |    |              |

|    |               |       | 4.4.2.4                  |                 | n de l'implantatio       |          |            |    |              |

|    |               |       | 4.4.2.5                  |                 | n du code exécuta        |          |            |    |              |

|    |               | 4.4.3 | Vérifica                 |                 | el GeneAuto cor          |          |            |    |              |

|    |               | 4.4.4 | Vérifica                 | tion de l'utili | sateur                   |          |            |    | . 77         |

|    | 4.5           | Qual  | IFICATIO                 | n de GeneA      | UTO                      |          |            |    | . 77         |

|    | 4.6           | Synti | HÈSE                     |                 |                          |          |            |    | . 78         |

| 5  | $C_{\Lambda}$ | DRE E | ORMEL I                  | DE DÉVELO       | PPEMENT                  |          |            |    | 79           |

| 0  | 5.1           |       |                          |                 |                          |          |            |    |              |

|    | 5.2           |       |                          |                 | T ORDONNÉS               |          |            |    |              |

|    | 5.3           |       |                          |                 | NTATION                  |          |            |    |              |

|    | 0.0           | 5.3.1 |                          |                 |                          |          |            |    |              |

|    |               | 5.3.2 |                          |                 | raite                    |          |            |    |              |

|    |               | 0.0.2 | 5.3.2.1                  |                 | ordre partiel            |          |            |    |              |

|    |               |       | 5.3.2.2                  |                 | ordre partiel inve       |          |            |    |              |

|    |               |       | 5.3.2.3                  |                 | ordre total              |          |            |    |              |

|    |               |       | 5.3.2.4                  |                 | rtésien d'ordres p       |          |            |    |              |

|    |               |       | 5.3.2.5                  |                 | icographique d'o         |          |            |    |              |

|    |               |       |                          | 5.3.2.5.1       | Ordre lexicog            |          |            |    |              |

|    |               |       |                          |                 | quences                  |          |            |    | . 88         |

|    |               | 5.3.3 | Treillis e               | et famille de t | reillis abstraits .      |          |            |    | . 88         |

|    |               |       | 5.3.3.1                  | Produit car     | tésien de famille        | s de tre | illis      |    | 90           |

|    |               |       | 5.3.3.2                  | Famille de      | treillis inverse .       |          |            |    | 90           |

|    |               | 5.3.4 | Environ                  | nement abstr    | ait                      |          |            |    | 91           |

|    |               |       | 5.3.4.1                  | Paramètre       | de l'environneme         | ent .    |            |    |              |

|    |               |       | 5.3.4.2                  | Ordre part      | iel de l'environne       | ement    |            |    |              |

|    |               |       | 5.3.4.3                  | Implantation    | on de l'environne        | ement    |            |    |              |

|    |               |       | 5.3.4.4                  |                 |                          |          |            |    |              |

|    |               | 5.3.5 | Fonction                 | n de propaga    | tion                     |          |            |    | 96           |

|    |               | 5.3.6 | Calcul d                 | le point fixe . |                          |          |            |    |              |

|    | 5.4           | Outi  | L <mark>S ÉLÉME</mark> I |                 |                          |          |            |    |              |

|    |               | 5.4.1 | Concept                  | tion d'un out   | il élémentaire           |          |            |    |              |

|    |               | 5.4.2 | Définition               | on d'un outil   | élémentaire              |          |            |    |              |

|    | 5.5           | Conc  | CLUSION E                | T DISCUSSIO     | N                        |          |            |    | 102          |

|    |               |       |                          |                 |                          |          |            |    |              |

| II | I É           | tude  | de cas                   |                 |                          |          |            |    | 103          |

|    |               |       |                          |                 |                          |          |            |    |              |

| 6  | Or            | DONN  | ANCEMI                   | ENT DES CI      | RCUITS SIMU              | LINK     |            |    | 105          |

|    | 6.1           | Моті  | VATION .                 |                 |                          |          |            |    | 105          |

|    | 6.2           | RAPP  | EL DES EX                | IGENCES SUI     | r l'ordonnanc            | EMENT    | DES CIRCUI | TS | 106          |

|    | 6.3           | Ordo  | NNANCE                   | MENT DES CI     | RCUITS AUX FLO           | TS DE 1  | DONNÉES .  |    | 108          |

|     | 6.3.1 | Ordonna  | ancement guidé par les rangs                                                                         | . 109 |

|-----|-------|----------|------------------------------------------------------------------------------------------------------|-------|

|     |       | 6.3.1.1  | Calcul des rangs                                                                                     |       |

|     |       | 6.3.1.2  | Calcul des rangs                                                                                     |       |

|     |       |          | 6.3.1.2.1 Domaine de calcul                                                                          | . 109 |

|     |       |          | 6.3.1.2.2 Famille de treillis des rangs                                                              | . 110 |

|     |       |          | 6.3.1.2.3 Environnement de calcul des rangs.                                                         |       |

|     |       |          | 6.3.1.2.4 Fonction de calcul des rangs                                                               |       |

|     |       | 6.3.1.3  | Calcul d'un ordre total                                                                              |       |

|     |       | 6.3.1.4  | Exemple                                                                                              | . 114 |

|     |       | 6.3.1.5  | Correction de l'algorithme d'ordonnancement                                                          | . 114 |

|     |       |          | 6.3.1.5.1 Croissance de la fonction de propaga                                                       |       |

|     |       |          | tion                                                                                                 |       |

|     |       |          | 6.3.1.5.2 Correction du calcul des rangs pa                                                          | ır    |

|     |       |          | rapport à la structure du circuit                                                                    |       |

|     |       |          | 6.3.1.5.3 Boucles algébriques                                                                        |       |

|     |       | 6.3.1.6  | Discussion                                                                                           | 440   |

|     | 6.3.2 | Ordonna  | ancement guidé par les dépendances                                                                   | . 118 |

|     |       | 6.3.2.1  | Calcul des dépendances                                                                               |       |

|     |       |          | 6.3.2.1.1 Domaine du calcul des dépendances                                                          |       |

|     |       |          | 6.3.2.1.2 Famille de treillis des dépendances .                                                      |       |

|     |       |          | 6.3.2.1.3 Environnement de calcul des déper                                                          |       |

|     |       |          | dances                                                                                               |       |

|     |       |          | 6.3.2.1.4 Fonction de propagation des déper                                                          |       |

|     |       |          | dances                                                                                               |       |

|     |       | 6.3.2.2  | Exemple                                                                                              |       |

|     |       | 6.3.2.3  | Construction d'un ordre total                                                                        |       |

|     |       | 0.0.2.0  | 6.3.2.3.1 Correction de l'ordre obtenu par rap                                                       |       |

|     |       |          | port aux dépendances calculées                                                                       |       |

|     |       | 6.3.2.4  | Discussion                                                                                           | . 127 |

| 6.4 | Ordo  |          | MENT DES CIRCUITS AUX FLOTS MIXTES                                                                   | . 127 |

| 0.1 | 6.4.1 |          | ns de dépendances événementielles                                                                    | . 127 |

|     | 0.1.1 | 6.4.1.1  | Contraintes de calcul des dépendances                                                                |       |

|     |       | 0.4.1.1  | 6.4.1.1.1 Contraintes structurelles                                                                  | . 128 |

|     |       |          | 6.4.1.1.2 Contraintes du code séquentiel                                                             |       |

|     |       | 6.4.1.2  | Équations de dépendances                                                                             |       |

|     | 6.4.2 |          | les dépendances événementielles                                                                      | . 135 |

|     | 0.4.2 | 6.4.2.1  | Domaine des dépendances événementielles                                                              |       |

|     |       | 6.4.2.2  |                                                                                                      |       |

|     |       | 6.4.2.3  | Famille de treillis des dépendances événementielles<br>Environnement de calcul des dépendances événe |       |

|     |       | 0.4.2.3  | mentielles                                                                                           |       |

|     |       | 6.4.2.4  | Fonction de propagation des dépendances événemer                                                     |       |

|     |       | 0.4.2.4  | tielles                                                                                              |       |

|     | 6.4.3 | Ondro to |                                                                                                      |       |

|     | 6.4.4 |          | otal                                                                                                 |       |

|     |       |          | e                                                                                                    |       |

|     | 6.4.5 |          |                                                                                                      |       |

|     |       | 6.4.5.1  | Croissance des fonctions de propagation                                                              |       |

|     |       |          | 6.4.5.1.1 Croissance de la fonction $\rho_{in}$                                                      |       |

|     |       | 6450     | 6.4.5.1.2 Croissance de la fonction $\rho_{out}$                                                     |       |

|     |       | 6.4.5.2  | Correction des équations de dépendances                                                              |       |

|     |       |          | 6.4.5.2.1 Correction des équations par rappor                                                        |       |

|     |       |          | aux flots de données                                                                                 | . 144 |

|   |     |       |           | 6.4.5.2.2 Correction des équations aux flots de contrôle |                | 145  |

|---|-----|-------|-----------|----------------------------------------------------------|----------------|------|

|   |     |       | 6.4.5.3   | Détection des boucles algébriques                        |                | 146  |

|   | 6.6 | CAS D |           | · · · · · · · · · · · · · · · · · · ·                    |                | 148  |

|   | 0.0 | 6.6.1 |           | ıde : Contrôleur automobile                              |                | 148  |

|   |     | 6.6.2 |           | as d'études                                              |                | 150  |

|   | 6.7 |       |           |                                                          |                | 150  |

| 7 | Тур | ACE D | ES CIDC   | JITS SIMULINK                                            |                | 151  |

| ′ | 7.1 |       |           |                                                          |                | 151  |

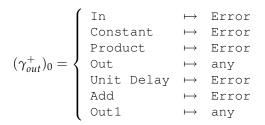

|   | 7.1 |       |           | DES ALGORITHMES DE TYPAGE                                |                | 151  |

|   | 7.2 |       |           |                                                          |                | 154  |

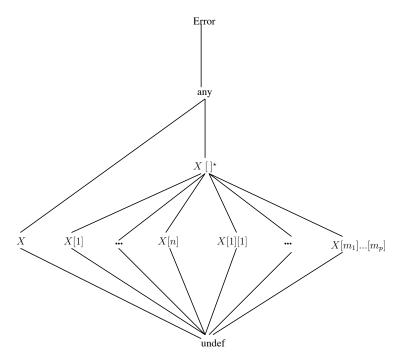

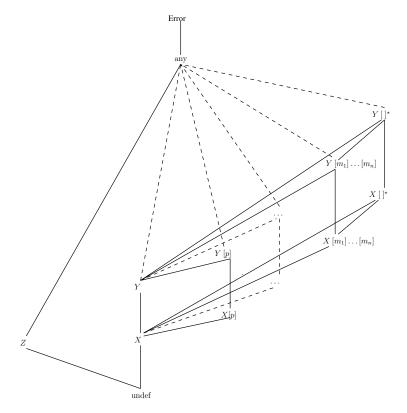

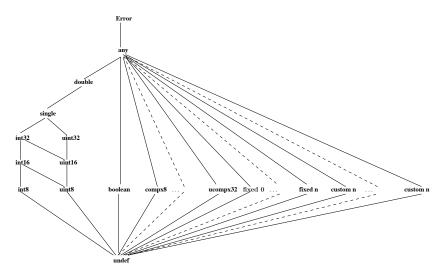

|   | 7.3 |       |           | PES                                                      |                | 154  |

|   |     | 7.3.1 |           | e de calcul                                              |                | 154  |

|   |     | 7.3.2 |           | le treillis des types                                    |                |      |

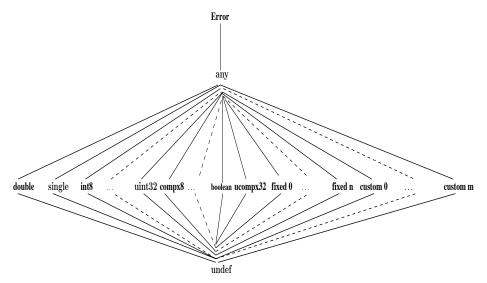

|   |     |       | 7.3.2.1   | Famille de treillis des types en SIMULIN                 |                | 156  |

|   |     |       | 7.3.2.2   | Famille de treillis des types en GENEAU                  |                | 159  |

|   |     |       |           | 7.3.2.2.1 Contraintes de typage er                       |                | 159  |

|   |     |       |           | 7.3.2.2.2 Famille de treillis des t                      | J 1            | 1.00 |

|   |     |       |           | NEAUTO                                                   |                | 160  |

|   |     | 7.3.3 |           | nement de l'inférence des types                          |                | 164  |

|   |     |       | 7.3.3.1   | Environnement des ports                                  |                | 165  |

|   |     |       | 7.3.3.2   | Environnement des blocs                                  |                | 166  |

|   |     |       | 7.3.3.3   | Initialisation de l'environnement                        |                | 166  |

|   | 7.4 | Fonc  | TIONS DE  |                                                          |                | 168  |

|   |     | 7.4.1 | Propriét  | d'adjonction                                             |                | 168  |

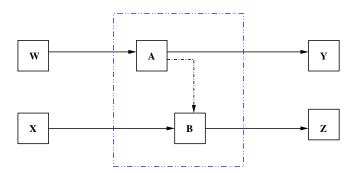

|   |     |       | 7.4.1.1   | Composition de blocs                                     |                | 170  |

|   |     |       | 7.4.1.2   | Superposition de blocs                                   |                | 170  |

|   |     | 7.4.2 | Blocs ide | ntité                                                    |                | 171  |

|   |     | 7.4.3 | Blocs so  | irce                                                     |                | 173  |

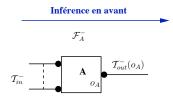

|   |     |       | 7.4.3.1   | Fonction de typage en avant                              |                | 173  |

|   |     |       | 7.4.3.2   | Fonction de typage en arrière                            |                | 174  |

|   |     |       | 7.4.3.3   | Correction des fonctions de typage des                   | blocs source . | 174  |

|   |     | 7.4.4 | Blocs cib | le                                                       |                | 174  |

|   |     |       | 7.4.4.1   | Fonction de typage en avant                              |                | 175  |

|   |     |       | 7.4.4.2   | Fonction de typage en arrière                            |                | 175  |

|   |     |       | 7.4.4.3   | Correction des fonctions de typage des                   | blocs cible    | 176  |

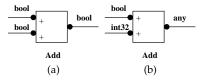

|   |     | 7.4.5 | Blocs con | nbinatoires                                              |                | 176  |

|   |     |       | 7.4.5.1   | Fonction de typage en avant                              |                | 177  |

|   |     |       | 7.4.5.2   | Fonction de typage en arrière                            |                | 178  |

|   |     |       | 7.4.5.3   | Correction des fonctions de typage de                    | s blocs combi- | 4.70 |

|   |     |       |           | natoires                                                 |                | 179  |

|   |     |       | 7.4.5.4   | Limite des fonctions de typage des blo                   |                |      |

|   |     | 7.4.6 |           | uentiels                                                 |                | 181  |

|   | 7.5 |       |           | ГҮРАGE                                                   |                | 182  |

|   |     | 7.5.1 | -         | s de typage des ports pour l'inférence et                |                | 183  |

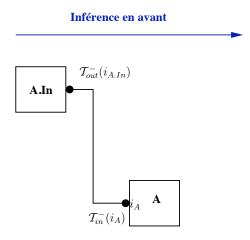

|   |     |       | 7.5.1.1   | Typage en avant des ports d'entrée d'u                   |                | 183  |

|   |     |       | 7.5.1.2   | ,, ,                                                     |                | 184  |

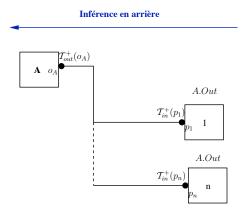

|   |     | 7.5.2 | _         | s de typage des ports pour l'inférence et                |                | 184  |

|   |     |       | 7.5.2.1   | Typage en arrière des ports d'entrée d'                  |                | 184  |

|   |     |       | 7.5.2.2   | Typage en arrière des ports de sortie                    |                | 185  |

|   |     |       |           | 7.5.2.2.1 Fonctions de propagation                       | n des types .  | 185  |

|   | 76  | Védie | CATION I  | DE L'OUTH ÉLÉMENTAIDE DE TYPACE                          |                | 187  |

|    | 7.7<br>7.8 | 7.6.1<br>7.6.2<br>Exemi<br>Synth | Croissance des fonctions de propagation                        | 188<br>188 |

|----|------------|----------------------------------|----------------------------------------------------------------|------------|

| IV | 7 <b>S</b> | ynthè                            | se                                                             | 195        |

| 8  | Coi        | NCLUS                            | ION & PERSPECTIVES                                             | 197        |

|    | 8.1        | Bilan                            | SUR LES TRAVAUX PRÉSENTÉS                                      | 197        |

|    |            | 8.1.1                            | Cadre Formel                                                   | 198        |

|    |            | 8.1.2                            | Spécifications précises                                        | 198        |

|    |            | 8.1.3                            | Processus de développement spécifique                          | 199        |

|    |            | 8.1.4                            | Un pas vers la certification selon les normes de certification | 199        |

|    |            | 8.1.5                            | Ordonnancement                                                 | 200        |

|    |            | 8.1.6                            | Limitations liées à l'usage des entiers de Peano               | 200        |

|    |            | 8.1.7                            | Manipulation efficace de l'application de fonctions            | 201        |

|    |            | 8.1.8                            | Typage des circuits Simulink                                   | 201        |

|    | 8.2        | PERSP                            | ECTIVES                                                        |            |

|    |            | 8.2.1                            | Vers une sémantique concrète?                                  | 202        |

|    |            | 8.2.2                            | Prendre en compte des exigences d'optimisation                 | 202        |

|    |            | 8.2.3                            | Explorer le typage au sens large                               |            |

|    |            | 8.2.4                            | Application du cadre à une sémantique synchrone                | 204        |

| A  | Lis        | TE DES                           | BLOCS                                                          | 205        |

| В  | Fic        | HIERS                            | Coq                                                            | 209        |

| Ві | BLIC       | GRAPI                            | не                                                             | 213        |

### LISTE DES FIGURES

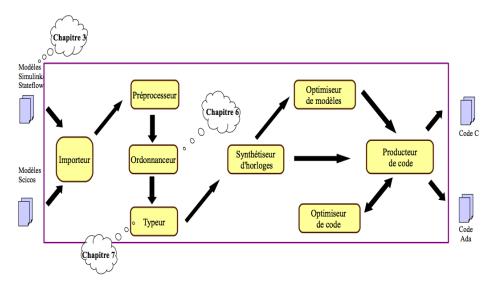

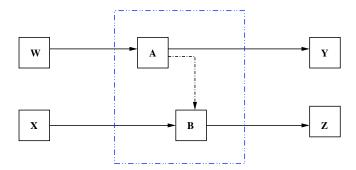

| 1.1  | Architecture du générateur de code GeneAuto               | 6  |

|------|-----------------------------------------------------------|----|

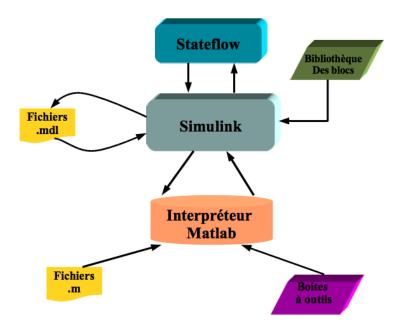

| 3.1  | La boîte à outils Matlab                                  | 26 |

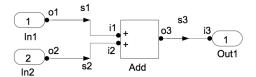

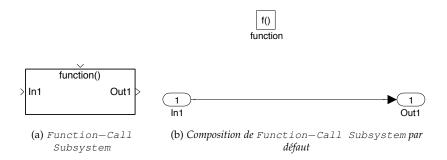

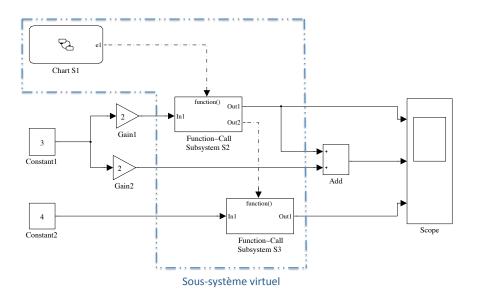

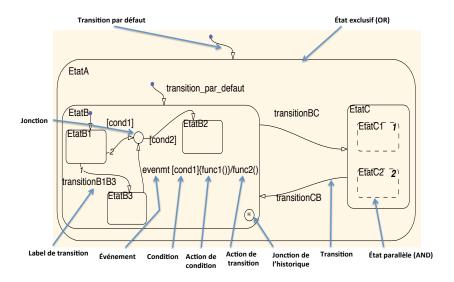

| 3.2  | Structure d'un circuit SIMULINK                           | 27 |

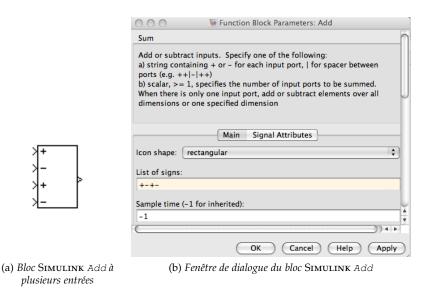

| 3.3  | Configuration du bloc Simulink Add                        | 27 |

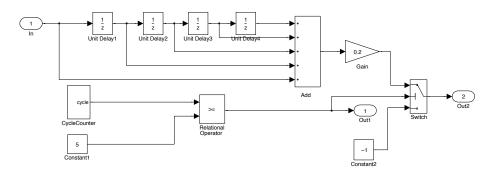

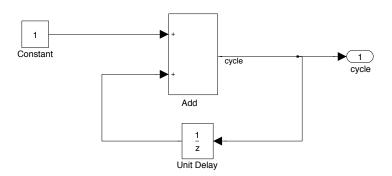

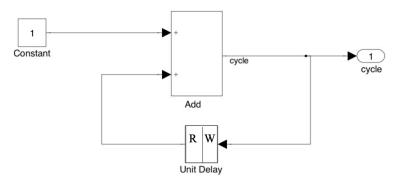

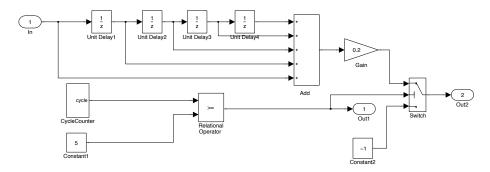

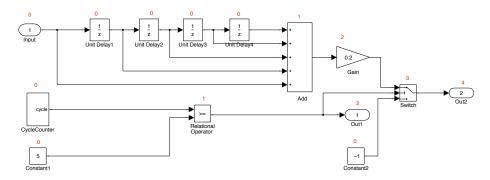

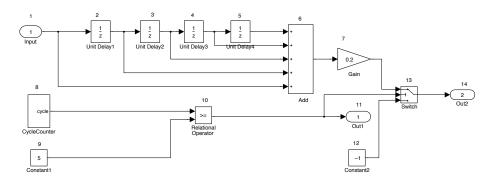

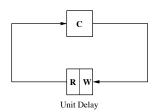

| 3.4  | Circuit moyenne 5 utilisant le bloc séquentiel Unit Delay | 28 |

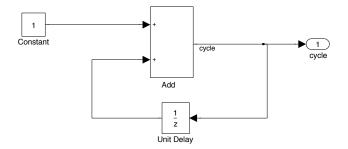

| 3.5  | Composition du bloc Cycle Counter                         | 29 |

| 3.6  | Bloc Enable                                               | 29 |

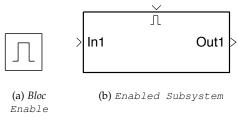

| 3.7  | Triggered Subsystem                                       | 30 |

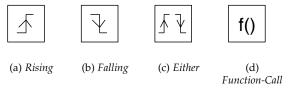

| 3.8  | Bloc Simulink Trigger                                     | 30 |

| 3.9  | Circuit Simulink à flots de contrôle                      | 31 |

| 3.10 | Structure générale d'un diagramme d'états en Stateflow    | 33 |

| 3.11 | Les actions associées à un état                           | 35 |

| 3.12 | Trigger un diagramme Stateflow                            | 35 |

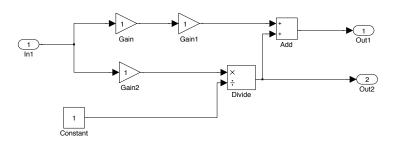

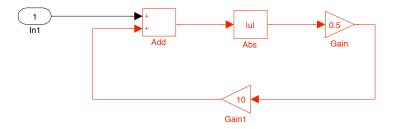

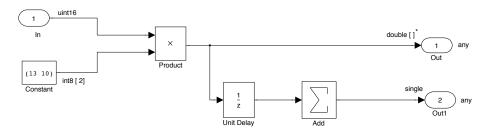

|      | Circuit Simulink à flot de données sans mémoire           | 36 |

| 3.14 | Circuit à boucle algébrique                               | 37 |

| 3.15 | Circuit Simulink à flots de données avec mémoire          | 37 |

| 3.16 | Découpage du bloc séquentiel en deux sous-blocs           | 38 |

| 3.17 | Circuit Simulink mixant flots de données et de contrôle   | 39 |

| 3.18 | Pseudo-code impératif généré pour l'exemple               | 39 |

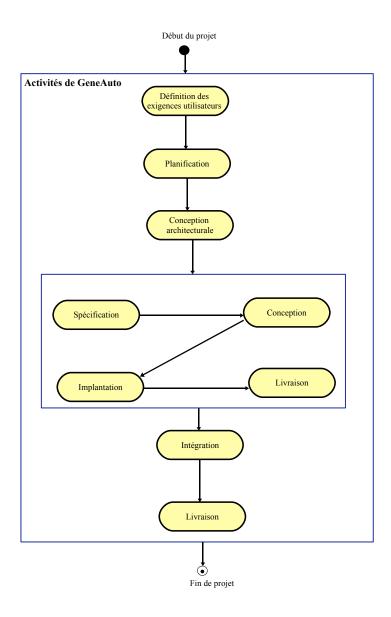

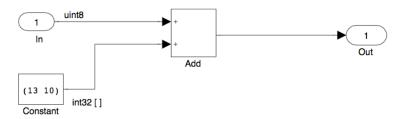

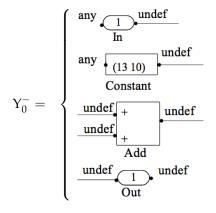

| 3.19 | Fenêtre de dialogue du bloc Simulink Add                  | 42 |

| 3.20 | La somme d'un entier et d'un booléen                      | 42 |

|      | Conversion implicite d'un entier en booléen               | 42 |

| 3.22 | Architecture du générateur de code GeneAuto               | 44 |

| 3.23 | Exemple de circuit complet en Simulink                    | 51 |

| 4.1  | Cycle de vie de développement de GeneAuto                 | 65 |

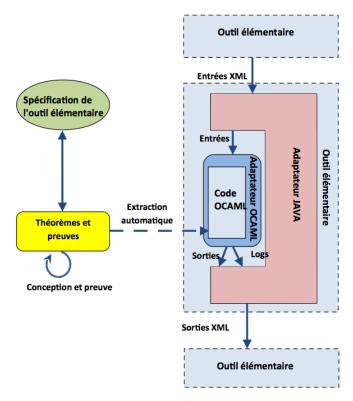

| 4.2  | Architecture d'un outil élémentaire formel                | 68 |

| 4.3  | Processus de vérification de codage                       | 73 |

| 4.4  | Processus de test des outils élémentaires                 | 74 |

| 4.5  | Processus de vérification des spécifications formelles    | 74 |

| 4.6  | Processus de vérification de la conception formelle       | 76 |

| 4.7  | Processus de vérification de l'implantation               | 76 |

| F 1  |                                                           | 00 |

| 5.1  | Signature d'un préordre partiel en Coq                    | 83 |

| 5.2  | Signature du module DataType                              | 84 |

| 5.3  | Définition de l'ordre inverse d'un ordre partiel          | 85 |

| 5.4  | Signature d'un préordre total en Coq                      | 85 |

| 5.5  | Produit cartésien d'ordres partiels                       | 86 |

| 5.6  | Produit lexicographique d'ordres partiels en Coq          | 87 |

| 5.7  | Définition d'un ordre lexicographique sur des séquences   | 88 |

| 5.8  | Signature d'une famille de treillis en Coq                        | 89  |

|------|-------------------------------------------------------------------|-----|

| 5.9  | Définition du produit cartésien de familles de treillis en Coq    | 91  |

| 5.10 | Implantation du foncteur LatticeInv                               | 92  |

| 5.11 | Signature Coo du module DataMap                                   | 93  |

|      | Définition d'un ordre partiel pour les types dépendants           |     |

|      | DependentMapPreOrder                                              | 94  |

| 5.13 | Définition d'un environnement                                     | 95  |

|      | Signature de la conception d'un outil élémentaire                 | 99  |

|      | Définition d'un outil élémentaire en Coq                          | 102 |

| 6.1  | Circuit Simulink représentant la moyenne 5                        | 106 |

| 6.2  | Code C généré pour le circuit moyenne 5                           | 106 |

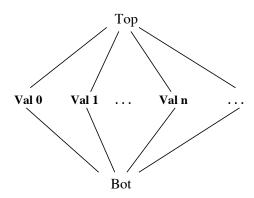

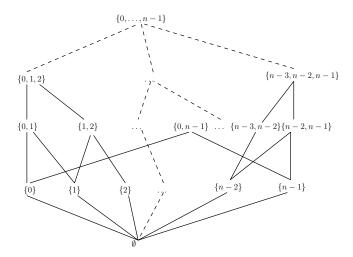

| 6.3  | Diagramme de Hasse de la famillle de treillis des rangs           | 111 |

| 6.4  | Rang d'un bloc à entrées multiples                                | 112 |

| 6.5  | Rangs des blocs du circuit «moyenne 5»                            | 114 |

| 6.6  | Ordre d'exécution des blocs du circuit moyenne 5                  | 114 |

| 6.7  | Circuit à boucle algébrique                                       | 117 |

| 6.8  | Diagramme de Hasse de la famille de treillis des ensembles de     |     |

|      | dépendances                                                       | 120 |

| 6.9  | Les dépendances des blocs de «moyenne 5»                          | 123 |

|      | Circuit Simulink à conflit d'exécution                            | 125 |

|      | Circuit moyenne 5 ordonnancé suivant les dépendances              | 126 |

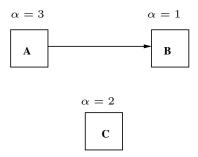

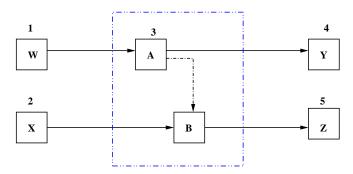

|      | Circuit combinant les flots de données et de contrôle             | 128 |

|      | Exécution de blocs reliés par flot de données                     | 129 |

|      | Circuit à bloc séquentiel                                         | 129 |

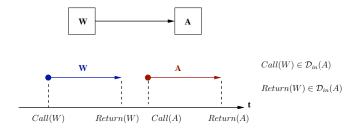

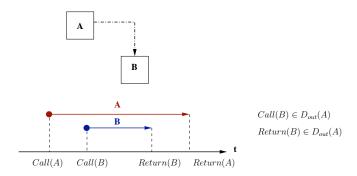

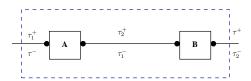

|      | Exécution du flot de contrôle entre <i>A</i> et <i>B</i>          | 130 |

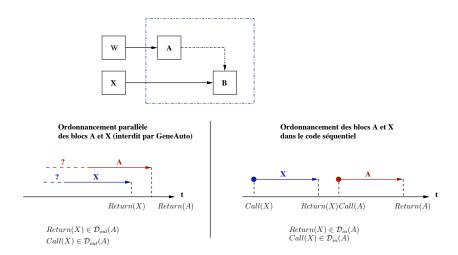

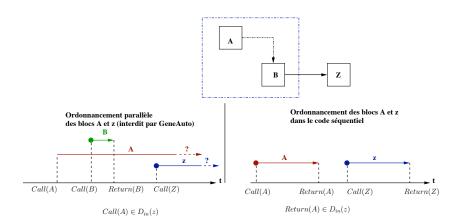

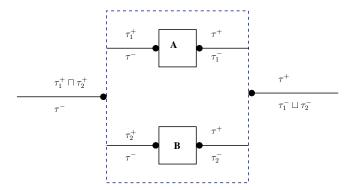

|      | Contraintes d'ordonnancement pour code séquentiel                 | 131 |

|      | Contraintes d'ordonnancement pour code séquentiel                 | 132 |

|      | Implantation du domaine des événements                            | 136 |

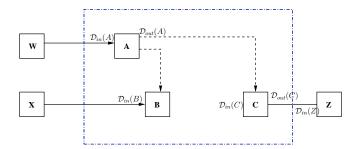

|      | Circuit combinant des flots de données et de contrôle             | 141 |

|      | Ensembles de dépendances d'entrée                                 | 141 |

|      | Ensembles de dépendances de sortie                                | 141 |

|      | Séquences de dépendances triées                                   | 142 |

|      | Circuit combinant des flots de données et de contrôle             | 142 |

|      | Transitivité de flot de données                                   | 144 |

|      | Circuit mixant les flots de données et de contrôle                | 145 |

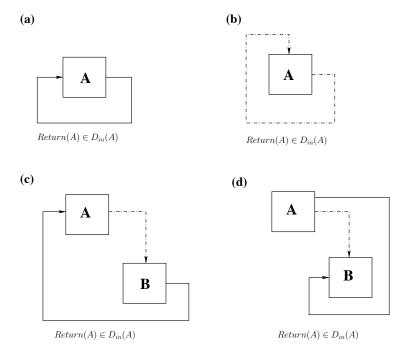

|      | Boucles de base en SIMULINK                                       | 145 |

|      |                                                                   |     |

|      | Dégâts du moteur causés par le cliquetis                          |     |

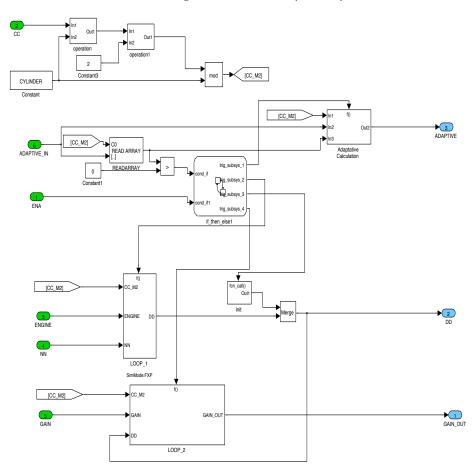

|      | Contrôleur d'un moteur automobile                                 | 149 |

| 6.29 | Récapitulatif des tailles d'autres études de cas industriels      | 150 |

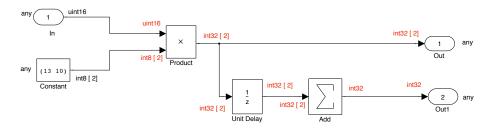

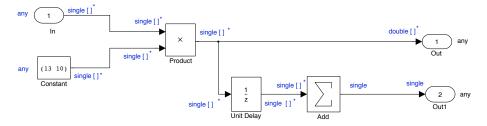

| 7.1  | Exemple d'inférence de type depuis les entrées vers les sorties . | 151 |

| 7.2  | Exemple d'inférence de type depuis les sorties vers les entrées . | 152 |

| 7.3  | Diagramme de Hasse du treillis des types scalaires d'une simple   |     |

|      | configuration en SIMULINK                                         | 158 |

| 7.4  | Diagramme de Hasse du treillis des vecteurs selon la configura-   |     |

|      | tion Simulink choisie                                             | 159 |

| 7.5  | Diagramme de Hasse de la famille de treillis des types en Ge-     | 207 |

| 0    | NEAUTO                                                            | 161 |

| 7.6  | Diagramme de Hasse de la famille de treillis des types scalaires  | 101 |

| 0    | en GeneAuto                                                       | 162 |

| 7.7  | Exemple de circuit à typer                                        | 167 |

|      |                                                                   | -0, |

| 7.8  | Composition de deux blocs                                             | 70 |

|------|-----------------------------------------------------------------------|----|

| 7.9  | Superposition de deux blocs                                           |    |

| 7.10 | Liste des blocs Simulink étudiés pour le typage                       | 72 |

| 7.11 | Anomalies de typage des blocs arithmétiques                           | 80 |

| 7.12 | Typage équivalent à celui d'un bloc Unit Delay 18                     | 82 |

| 7.13 | Typage du port d'entrée du bloc A par inférence en avant 18           | 83 |

| 7.14 | Typage du port de sortie du bloc <i>A</i> par inférence en avant 18   | 84 |

| 7.15 | Typage du port d'entrée du bloc <i>A</i> par inférence en arrière 18  | 84 |

| 7.16 | Typage du port de sortie du bloc <i>A</i> par inférence en arrière 18 | 85 |

| 7.17 | Exemple de circuit à typer                                            | 89 |

| 7.18 | Inférence en avant du circuit donné                                   | 89 |

| 7.19 | Inférence en arrière du circuit donné                                 | 90 |

| 7.20 | Circuit annoté par un type                                            | 93 |

| 7.21 | Transformation en circuit équivalent en typage                        | 93 |

| 7.22 | Transformation en sous-système ayant un typage équivalent 19          | 94 |

|      |                                                                       | _  |

| 8.1  | Tailles du code Coq développé dans le cadre cette thèse 19            |    |

| 8.2  | Réduire les variables locales                                         | 03 |

| 8.3  | Propagation de constante                                              | 03 |

### LISTE DES ALGORITHMES

| 1 | Algorithme de calcul des rangs pour les circuits flots de données . | 109 |

|---|---------------------------------------------------------------------|-----|

| 2 | Algorithme de calcul des dépendances pour les circuits aux flots    |     |

|   | de données                                                          | 119 |

| 3 | Algorithme de calcul des dépendances d'entrée et de sortie des      |     |

|   | circuits aux flots mixtes                                           | 134 |

| 4 | Algorithme de typage pour inférence en avant                        | 153 |

| 5 | Algorithme de typage pour inférence en arrière                      |     |

| _ | ingoinmine de typinge pour intereste est differe                    | -   |

### Première partie

### Introduction

Introduction

#### 1.1 Introduction

De nos jours, les logiciels prennent une place de plus en plus importante dans la plupart des composants des systèmes complexes tels un avion, une voiture, un appareil de radiologie, etc. Ils sont désignés comme *embarqués* pour caractériser le lien essentiel entre le matériel et le logiciel. Dans ces systèmes, le logiciel n'est pas l'objectif principal du système mais il joue un rôle fondamental dans la réalisation de cet objectif. Les systèmes embarqués sont de plus en plus à l'origine de l'innovation dans le domaine des systèmes critiques et notamment dans l'aéronautique, le spatial et l'automobile. L'adjectif *critique* signifie qu'un dysfonctionnement peut entraîner des conséquences dramatiques pour des vies humaines, des dégâts matériels importants, des pertes économiques substantielles ou encore des conséquences graves pour l'environnement. L'évolution de la complexité intrinsèque des systèmes critiques est exponentielle depuis de nombreuses années. La loi de Moore [Moo98] en est la caractéristique la plus célèbre. Ces systèmes ont donc des coûts de développement et de maintenance de plus en plus élevés.

L'ingénierie dirigée par les modèles (*Model Driven Engineering*) permet de réduire leur coût de développement. Il s'agit de vérifier et de valider les exigences du système et les intermédiaires dans le développement en s'appuyant sur des modèles (abstractions) du système. Cela permet de détecter les anomalies le plus tôt possible, puis d'exploiter la génération automatique de code à partir de ces modèles afin de réduire le nombre d'anomalies introduites par le codage manuel et d'accélérer la production du système final. Les modèles deviennent ainsi l'élément central du développement.

#### Compilateur et générateur de code

Usuellement, le terme *générateur de code* est utilisé pour désigner un outil informatique qui traduit un modèle en programme d'un langage de haut niveau. Tandis que le terme *compilateur* est utilisé pour désigner un outil informatique qui traduit un programme, d'un langage de programmation de plus ou moins haut niveau, en un code exécutable en langage machine.

Étant donné la complexité et la criticité des systèmes embarqués, une assurance élevée est requise pour le code produit par les générateurs de code. Les méthodes de vérification les plus répandues dans le monde industriel consistent à relire et à tester rigoureusement les modèles d'entrée et/ou le code généré. Cela permet d'atteindre des objectifs de couverture du comportement du système par des tests basés sur les exigences du système et sur la structure du code source.

Dans le cadre de la génération automatique de code pour un modèle validé et vérifié par simulation, c'est-à-dire des tests au niveau des modèles, il est indispensable que la vérification du code généré assure qu'aucune altération de la qualité du produit final ou, pire encore, un dysfonctionnement ne se produise. Or, les activités de vérification à base de tests sont coûteuses et non exhaustives.

Les modèles couramment manipulés pour la conception des systèmes embarqués critiques, dans le monde industriel, sont conçus avec des langages de modélisation et de simulation sophistiqués tels que Simulink/Stateflow [Sim], Scade [Dor08], Scicos [CCN09], etc.

Afin de réduire les coûts de tests du système final et les anomalies qui peuvent être introduites par la génération de code, il est indispensable d'exploiter des techniques plus rigoureuses, basées sur des formalismes mathématiques, pour développer les générateurs de code.

La vérification, telle qu'elle est définie par l'IEEE [IEE05], comprend toutes les techniques appropriées pour montrer qu'un système satisfait sa spécification. La spécification est l'ensemble des exigences concernant les besoins des utilisateurs et leurs attentes par rapport au système concerné.

L'activité de test assure, pour une situation particulière (un scénario de test), qu'un système a un comportement conforme à sa spécification. Un scénario de test est donc une forme de spécification du comportement attendu. Or, toute nouvelle entrée entraîne un changement du comportement du système informatique en question et requiert donc un nouveau scénario. Il est donc difficile d'assurer que la spécification du système sous la forme de scénarios et la couverture de ces scénarios par rapport au système final sont complètes.

De ce point de vue, les méthodes formelles sont plus avantageuses que ce soit pour la spécification ou la vérification. En effet, il est possible d'assurer formellement que tous les détails sur le fonctionnement d'un système sont couverts par les activités de spécification et de vérification, et donc que le système devrait fonctionner correctement pour toute entrée. Tandis qu'un oubli ou une ambiguïté de spécification et de vérification sont très courants lorsqu'il s'agit d'une argumentation sur papier.

Prouver la correction d'un programme ne correspond pas à la recherche et à la correction des erreurs qui est une action propre à la mise au point (debugging). Il s'agit plutôt de faire appel à des méthodes rigoureuses fondées sur les mathématiques, appelées *méthodes formelles*. Elles permettent de spécifier le programme qui doit être réalisé et de prouver que l'implantation fournie respecte toutes les propriétés décrites par sa spécification. Un tel programme est dit correct par construction : il n'est pas possible de construire un système incorrect.

Les méthodes formelles apportent une assurance très élevée aux systèmes informatiques. Toutefois, elles demandent un coût de mise en œuvre et de maintenance élevé. En conséquence, celles-ci ne sont pour l'instant préconisées que pour le développement des systèmes les plus critiques pour lesquels elles apportent une assurance très élevée et permettent de réduire le coût également très important des tests unitaires permettant d'obtenir les degrés de couverture exigé par certains standards. Des résultats relativement récents sur leur application pour des systèmes critiques ont montré à la fois la qualité des résultats et leur applicabilité pour des systèmes de grande taille. Nous citons ici les travaux de [BCC+03, CCF+05] qui appliquent la technique d'analyse statique par interprétation abstraite [CC77, CC92] sur des programmes C issues des applications de l'avionique. Ces travaux montrent bien l'intégration des méthodes formelles dans le processus de développement des systèmes embarqués critiques.

Les techniques de vérification sont dites statiques si elles n'ont pas besoin

1.1. Introduction 5

d'exécuter le programme à analyser. Parmi ces techniques, les plus connues sont la vérification des modèles (*model-checking*) [CGP99], l'analyse statique par interprétation abstraite et la preuve de programmes. Le point commun à la vérification des modèles et à l'analyse statique par interprétation abstraite est qu'elles se basent sur une abstraction du programme à analyser. Soit l'utilisateur construit l'abstraction dans le cadre de la vérification de modèles, soit l'outil la construit automatiquement dans le cadre de l'analyse statique et plus précisément de l'interprétation abstraite. Comme le générateur de code est un programme complexe, il est difficile d'appliquer ces deux techniques directement au générateur de code, notamment si ce dernier ne dispose pas de spécification, formelle ou pas, de la sémantique d'exécution des langages source et cible.

Dans le cadre de preuves de programmes, le développement correct par construction en utilisant un assistant de preuve a remporté un succès significatif à travers le projet Compcert [BDL06, Ler06, Ler09]. Celui-ci consiste à développer un compilateur C, correct par construction, en utilisant l'assistant de preuve Coq [BC04].

Un assistant de preuve en informatique, selon la définition de Wikipedia, est un logiciel permettant l'écriture et la vérification de preuves mathématiques, soit pour des théorèmes au sens usuel des mathématiques, soit pour des assertions relatives à l'exécution de programmes informatiques. Les assistants de preuves trouvent leurs origines dans les projets LCF [Mil79] et Auto-Math [dB70]. Ils s'appuient sur l'isomorphisme de Curry-Howard qui associe types et formules logiques, programmes et preuves. Ceux-ci permettent de formaliser des théories qui sont ensuite exploitées pour prouver des programmes, par exemple en s'appuyant sur la logique de Floyd-Hoare [Hoa69, Flo67] pour les programmes impératifs. Il existe plusieurs assistants de preuves qui ont été utilisés pour spécifier et vérifier des systèmes réels tels Coq [BC04], Isa-BELLE [Pau89], Pvs [OSR95] ...

Dans le monde des systèmes critiques industriels, la confiance en ces systèmes s'exprime par des normes de certification ou de qualification qui contraignent leur développement et leur utilisation. Ces dernières dépendent du domaine d'application, par exemple, la norme DO-178B [RTC99] pour le développement logiciel dans le domaine de l'aéronautique, la norme ISO 26262 pour le développement logiciel dans le domaine de l'automobile qui est, ellemême, issue de la norme générique IEC 61508 [Gro01]. Les dernières versions des normes de certification prennent en compte l'utilisation des méthodes formelles, du développement à base de modèles et la nécessité de qualifier des outils, pour le développement de systèmes critiques. Par exemple, un supplément a été réservé pour chacune de ces technologies dans la future version C de la norme DO-178.

#### LE PROJET GENEAUTO

Les travaux réalisés au cours de cette thèse ont été appliqués dans le cadre du projet GeneAuto <sup>1</sup>. Ce dernier consiste à développer un générateur de code qualifiable, selon la norme de certification DO-178B/ED-12B, qui transforme des circuits Simulink/Stateflow et Scicos en programmes C. Le générateur de code est constitué de plusieurs modules, appelés outils élémentaires, reliés

<sup>&</sup>lt;sup>1</sup>http://gforge.enseeiht.fr/projects/geneauto

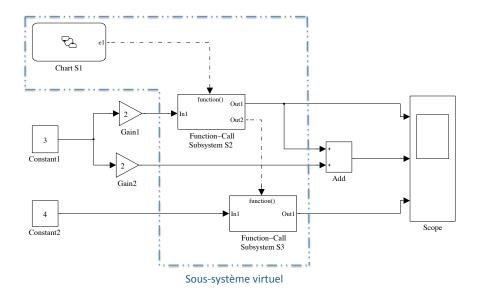

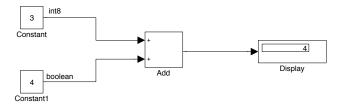

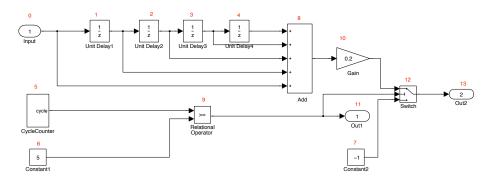

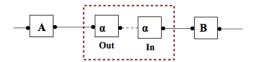

en cascade comme le montre la figure 1.1. Cette figure montre également les parties qui seront étudiées dans le présent manuscrit.

Fig. 1.1 – Architecture du générateur de code GeneAuto

Nous nous plaçons dans le cadre du développement correct par construction d'outils élémentaires (ordonnanceur et typeur) du générateur de code. Notre objectif, dans le projet Geneauto, était d'expérimenter le développement correct par construction en prenant en compte les contraintes de qualification. Une étude des différentes approches possibles a conduit au choix de l'assistant de preuve Coq [BC04], dans le cadre de systèmes critiques de grande taille, en s'inspirant des travaux de [BDL06, Ler06, Ler09].

Plusieurs raisons motivent l'intérêt de notre travail. D'une part, la vérification utilisée par l'ensemble des générateurs de code existants dans le monde industriel repose sur le respect d'un processus de développement très précis mais qui n'est formalisé qu'en langage naturel, sur des activités de vérification par relecture indépendante et par tests, avec des contraintes particulières sur la couverture de tests par rapport aux exigences et aux sources des programmes. Or, aussi poussée que soit leur couverture, les tests ne garantissent pas l'absence d'erreurs [Mye79]. Par exemple, le processus de développement du générateur de code de MathWorks, Real Time Workshop Embedded Coder<sup>2</sup>, propose une qualification compatible avec la norme ISO 26262, en s'appuyant sur une vérification à travers la génération de tests à partir du modèle qui assure que le code généré a le même comportement que le modèle simulé. Un autre exemple, le générateur de code qualifié SCADE KCG [Dor08] accepte en entrée des modèles en SCADE (langage de conception dérivé du formalisme Airbus SAO semblable à SIMULINK), avec une sémantique synchrone issue de Lustre [HCRP91] et génère du code C. La qualification de KCG exploite une vérification principalement basée sur le respect d'un processus compatible avec le standard DO-178B et sur une couverture des tests de type MC/DC (Modified Condition/Decision Coverage) adaptée au langage OCAML [PAC+08].

D'autre part, l'assistant de preuve Coq permet de spécifier formellement les exigences pour le générateur de code, puis d'écrire des programmes fonc-

<sup>&</sup>lt;sup>2</sup>http://www.mathworks.com/products/embedded-coder/

1.1. Introduction 7

tionnels dans le langage de spécification (*Gallina*), et enfin de prouver directement dans ce langage que les fonctions satisfont les exigences. Le mécanisme d'extraction de Coq produit automatiquement du code OCAML, HASKELL ou SCHEME à partir des spécifications. La spécification et la vérification réalisées avec le même langage permettent de produire des programmes corrects par construction, qui couvrent toutes les exigences spécifiées sans risque d'oubli ou d'ambiguïté.

Pour autoriser l'élimination des tests unitaires sur le code produit, le standard DO-178B exige que tout outil utilisé dans le processus de développement d'un système, qui peut introduire des erreurs dans le produit final, soit qualifié avec la même rigueur que le système produit. Afin de supprimer le risque que l'extracteur Coq puisse introduire des erreurs dans le programme vérifié en Coq, des travaux sur la vérification de l'extracteur de Coq sont nécessaires, il devrait être possible de s'appuyer sur les travaux suivants [Glo09].

#### **CONTRIBUTIONS**

De manière succincte, les contributions apportées par les travaux réalisés au cours de cette thèse sont résumées par les points suivants.

- Un processus de développement de générateurs de code qualifiés, combinant l'approche classique et l'approche formelle en utilisant l'assistant de preuve CoQ, a été défini. Ce processus a été mis en pratique sur deux outils élémentaires de l'atelier Gene Auto en charge de l'ordonnancement et du typage des blocs dans les diagrammes fonctionnels. La spécification du générateur de code est écrite de manière semi-formelle en langage naturel par les utilisateurs partenaires du projet. Les exigences en langage naturel, pour les outils élémentaires développés dans le cadre de cette thèse, sont traduites en spécifications formelles exprimées dans le langage de spécification Gallina;

- Un cadre formel générique a été défini pour le développement des outils élémentaires du générateur de code. Ce cadre représente la conception des outils élémentaires. Inspiré des principes de l'analyse statique par interprétation abstraite, il repose sur des ensembles partiellement ordonnés, des treillis de profondeur finie et sur le calcul du point fixe. Ce cadre générique a été appliqué aux deux cas d'étude pour le calcul des dépendances des blocs exploités pour l'ordonnancement du circuit et l'inférence de type des ports des blocs en avant et en arrière pour la vérification du typage du circuit. Chaque outil élémentaire est une instanciation du cadre formel et repose sur un algorithme dédié à l'analyse effectuée par chaque outil élémentaire;

- Plusieurs formes d'algorithmes ont été proposés pour ordonnancer les blocs des circuits considérés. Une première version est dédiée aux circuits ne contenant que des flots de données. Elle repose sur un calcul de rangs qui impose un ordre préalable plus contraignant que les exigences initiales. Une seconde version, qui repose sur le calcul des dépendances des blocs, a été proposée pour respecter exactement les exigences dans le cas des circuits ne comportant que des flots de données. Elle a ensuite été étendue aux dépendances événementielles pour ordonnancer tout type de circuit combinant les flots de données et de contrôle;

- Un algorithme de vérification des types des circuits considérés a été développé. Il s'appuie sur deux inférences de type : une inférence de type

- depuis les entrées vers les sorties du circuit et une inférence dans le sens inverse. Ceci permet de calculer une borne supérieure et inférieure pour les types autorisés pour chaque port des blocs du circuit;

- Le code source OCAML a été extrait pour les outils élémentaires développés, préservant les propriétés prouvées dans la spécification CoQ. Le code extrait a ensuite été intégré dans la chaîne de développement du générateur de code à l'aide d'interfaces simplifiées qui réduisent les échanges au minimum nécessaire pour simplifier la vérification des entrées/sorties;

- Contrairement aux générateurs de code industriels existants, GENEAUTO comporte des modules (outils élémentaires) entièrement spécifiés et vérifiés formellement pour lesquels les tests unitaires ne sont plus nécessaires. Par contre, les tests fonctionnels, qui permettent de valider les exigences, et les tests d'intégration, qui permettent de valider l'architecture choisie, restent partiellement nécessaires car les spécifications formelles n'expriment pas toutes les propriétés considérées;

- L'approche proposée a été présentée aux autorités de certification pour valider les choix technologiques effectués. Celles-ci ont donné un avis positif à l'égard du processus de développement et de l'intégration des méthodes formelles proposées dans Geneauto. Celui-ci permet de poursuivre ces expérimentations dans le but de développer d'autres modules pour obtenir un outil entièrement spécifié et vérifié en exploitant des méthodes formelles.

Les enjeux de ces travaux ne se limitent pas au développement d'outils élémentaires dans Geneauto. Nous avons montré à travers cette contribution la faisabilité de l'utilisation des méthodes formelles pour le développement d'outils qualifiés selon le standard DO-178B et leur intégration dans le processus de développement de systèmes embarqués critiques de grande taille.

De plus, la traduction des spécifications informelles dans le langage de spécification de CoQ a mis en évidence de nombreuses ambiguïtés et plusieurs lacunes au niveau de la spécification écrite en langage naturel. Cette spécification est écrite par les partenaires industriels experts des outils de génération de code pour les systèmes critiques et est validée par une relecture indépendante effectuée par les autres partenaires industriels du projet. Ce constat s'appuie sur la formalisation des exigences et sur les tentatives de preuves établies pour vérifier la cohérences de ces exigences, d'où tout l'intérêt de l'utilisation d'un langage formel comme Gallina.

En particulier, le développement formel à l'aide de CoQ a conduit à une clarification des mécanismes d'ordonnancement des blocs Simulink qui font partie de la sémantique d'exécution du langage, par rapport aux documents rédigés dans GeneAuto et aux ouvrages de référence sur le langage Simulink.

#### 1.2 Travaux connexes

Maulik A. Dave répertorie dans une synthèse bibliographique [Dav03] les travaux sur la vérification formelle de compilateurs et d'étapes de compilation. Nous nous intéressons plus particulièrement à la vérification et à la qualification des générateurs de code.

Il existe de nombreux travaux sur la génération de code à partir de modèles et sur la vérification de générateurs de code pour des systèmes critiques. Une grande partie de ces travaux sont dédiés aux langages synchrones tels Scade/KCG/Lustre [BCHP08, CHP07, CHP06, CP04]. La sémantique des mo-

dèles supportés par GeneAuto est significativement différente, car elle combine de manière fine les flots de données et de contrôle. En SIMULINK, la sémantique découle de l'ordonnancement des blocs contrairement aux langages synchrones où l'ordonnancement des blocs découle de la sémantique des flots de données des circuits. Des travaux existent pour transformer les circuits SI-MULINK en Lustre et exploiter ainsi le générateur de code Scade/KCG/Lustre qualifié [CCM+03, PAA+03]. Cependant, les travaux cités ne nous permettent pas de respecter facilement les contraintes de traçabilité imposées sur le circuit et/ou sur le code par les partenaires industriels de GENEAUTO pour assurer la couverture structurelle MC/DC des tests unitaires du code source généré imposée par le DO-178B. La sémantique et les aspects de la génération de code sont traités dans [CCM+03, PAA+03, bGJ91, HRR91]. Outre la difficulté d'établir la traçabilité, il n'y a pas de vérification formelle du générateur de code lui-même. Une grande importance est portée à la vérification formelle du code généré dans [BBF+00]. Ces travaux ont été appliqués avec succès aux systèmes critiques au sein de Dassault Aviation. Néanmoins, la vérification formelle a été appliquée aux programmes sources générés et pas au générateur lui-même. [Ler06, BDL06] proposent une approche prometteuse dans le développement correct par construction de compilateurs. Nos travaux sont inspirés de ceux-ci mais notre approche est relativement différente. Techniquement, les méthodes formelles utilisées pour prouver la correction de compilateurs sont habituellement basées sur la spécification formelle des sémantiques des langages source et cible, de la traduction et de la preuve d'équivalence entre les sémantiques observées des codes source et cible. Dans le cadre de GeneAuto, nous avons choisi de ne pas nous éloigner du processus de qualification usuel afin de faciliter son acceptation par les autorités de certification, donc, nous ne nous sommes pas basés directement sur le niveau sémantique mais sur les exigences en langage naturel telles qu'elles sont écrites habituellement par les partenaires industriels du projet.

#### Visite guidée du manuscrit

Nous présentons ici un bref résumé de chaque chapitre de ce document. Nous nous focalisons dans ce manuscrit sur le processus de développement combinant méthodes formelles et classiques pour la construction de générateurs de code qualifiables, sur la démarche suivie pour la définition d'un cadre général pour la construction de modules d'analyse semblables, ainsi que sur les outils élémentaires développés pour l'ordonnancement et le typage des circuits SIMULINK. Nous ne présentons pas exhaustivement toutes les preuves réalisées dans le cadre de l'utilisation de Coq pour la spécification et la vérification formelle de ces outils. Nous avons choisi de présenter les différentes spécifications et de décrire les preuves mathématiquement afin d'expliquer le principe. Cependant, nous avons décrit la majeure partie des spécifications et certaines preuves en Coq lorsque cela nous a semblé pertinent. L'ensemble du développement est disponible à l'adresse http://izerrouken.perso.enseeiht.fr/Code.

#### Chapitre 2 : État de l'art

Ce chapitre présente un aperçu des méthodes de vérification existantes ainsi que quelques éléments issus des standards de certification des systèmes critiques. La méthode de vérification la plus répandue dans le milieu industriel

est le test. Les normes de certification, entre autres la norme DO-178B pour le logiciel en aéronautique, incluent explicitement les tests comme une exigence pour les processus de vérification. Néanmoins, une future norme est en cours d'étude, la norme DO-178C, qui permet l'exploitation des méthodes formelles dans le processus. Comme cité précédemment, la vérification par tests ne peut garantir l'absence d'erreurs dans le système vérifié. D'autres approches plus rigoureuses, fondées sur les mathématiques, sont indispensables pour les systèmes embarqués critiques. Nous présentons les principes de ces approches et les comparons par rapport à nos besoins afin d'expliquer les choix effectués.

#### Chapitre 3 : Éléments de mise en œuvre

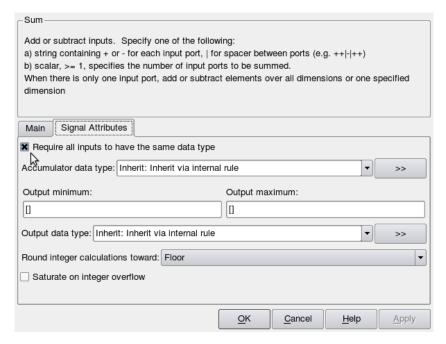

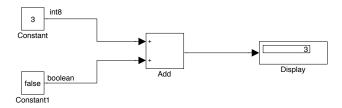

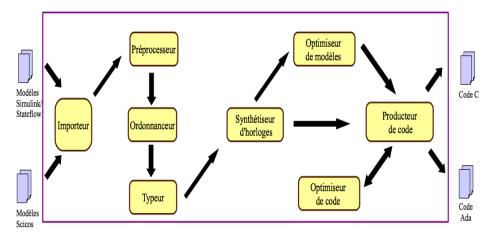

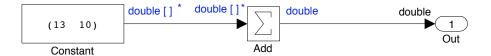

Le générateur de code Geneauto prend en entrée des circuits Simulink/Stateflow. Nous introduirons donc, dans ce chapitre, le langage de modélisation et de simulation Simulink ainsi que Stateflow. Il y sera également présenté le principe de l'ordonnancement et du typage des circuits en Simulink à travers des exemples. Nous présenterons les différentes contraintes pour l'ordonnancement des circuits Simulink. En effet, l'ordonnancement dépend de la nature des blocs et des signaux qui les relient. En ce qui concerne le typage, Simulink peut avoir plusieurs formes de typage en fonction de la configuration choisie. Cela implique des choix de typage, selon la forme retenue, pour les circuits Simulink lors de la spécification de l'outil élémentaire de typage.

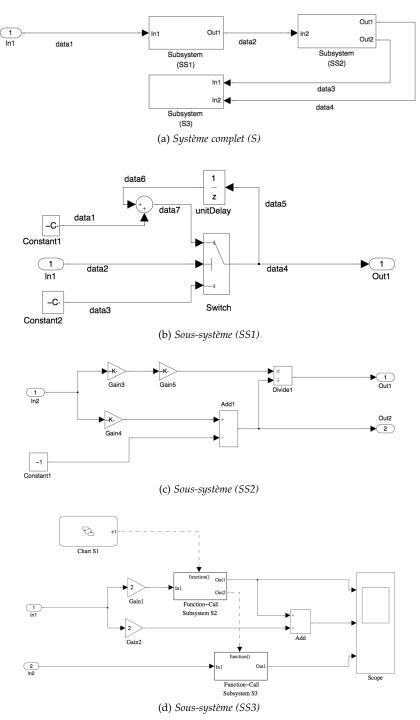

#### Chapitre 4 : Processus de développement d'outils élémentaires

Ce chapitre décrit le processus de développement tel qu'il est préconisé par la norme de certification DO-178B [RTC99]. Le processus de développement comprend des plans détaillés de développement, de vérification et de qualification. Les outils élémentaires développés en CoQ dans le cadre de cette thèse sont intégrés dans la chaîne de développement classique. Dès lors, il est important de montrer les deux facettes du processus de construction d'un générateur de code qualifié (développement, vérification et qualification) : avec des outils classiques comme JAVA et avec des technologies formelles comme CoQ.

#### Chapitre 5 : Cadre formel de développement

Ce chapitre présente la conception des outils élémentaires en Coq. Le but est d'exploiter les mêmes exigences pour les deux types de développement : en Java et en Coq. La sémantique concrète n'apparaît donc pas explicitement dans les exigences des outils élémentaires de Geneauto. Nous nous sommes donc limités à la sémantique abstraite déduite des exigences pour construire les composants d'analyse statique.

Nous nous sommes inspirés du principe de l'analyse statique par interprétation abstraite [CC77, CC79, CC92] pour définir un cadre formel commun aux outils d'ordonnancement et de typage. Il s'agit de s'appuyer sur les ensembles ordonnés, les treillis de profondeur finie et le calcul de point fixe en appliquant le théorème de Kleene [Col52] pour calculer une abstraction de toutes les exécutions possibles d'un circuit. Dans les travaux présentés dans cette thèse, nous définissons directement les domaines abstraits. Il serait certes plus satisfaisant de disposer de la sémantique concrète et des sémantiques abstraites des outils élémentaires afin de vérifier leur équivalence (correspondance de Galois).

Toutefois, nous ne disposons pas de la sémantique concrète. L'objectif était d'exploiter des exigences communes aux deux formes de développement.

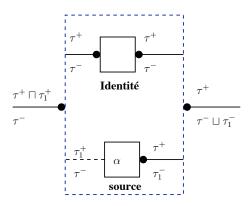

Le cadre est composé d'un domaine de calcul, d'une relation d'ordre partiel, d'une famille de treillis, d'un environnement de calcul, d'une fonction de propagation et d'une implantation de l'algorithme de Kleene, paramétré par ce domaine et cette fonction, qui calcule le résultat attendu pour chaque instanciation du cadre dans un outil élémentaire. Nous spécifions donc chacun de ces éléments en illustrant leur implantation en Coq. À la fin de ce chapitre, nous présenterons la signature de la conception d'un outil élémentaire qui sera ensuite utilisée pour définir les outils élémentaires étudiés.

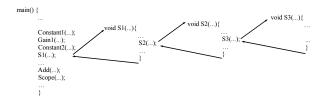

#### Chapitre 6: Ordonnancement des circuits Simulink

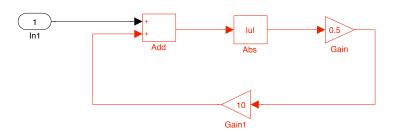

Ce chapitre présente plusieurs versions de l'algorithme d'ordonnancement des blocs en Simulink ainsi que les preuves de leurs propriétés respectives. Le premier algorithme, une version préliminaire présentée dans [ITPS08], calcule un entier naturel, le rang, pour chaque bloc d'un circuit Simulink comprenant uniquement des flots de données. Plusieurs blocs peuvent posséder le même rang. Le concepteur du circuit peut définir des priorités pour les blocs. Un ordre total est alors calculé en triant les blocs possédant le même rang par ordre lexicographique de leurs priorités. Toutefois, cet algorithme calcule un rang entier qui forme un préordre total, et donc impose un ordre pour des blocs indépendants. En conséquence, l'ordonnancement construit est plus contraignant que les exigences ne le demandent. Celles-ci peuvent être satisfaites en construisant un ordre partiel issu de l'ensemble des dépendances de chaque bloc, c'est-à-dire, de l'ensemble des blocs qui doivent avoir été exécutés pour qu'il puisse l'être. Nous avons proposé, dans un premier temps, un algorithme qui calcule les dépendances de chaque bloc. Cette version reste adaptée uniquement aux circuits ne contenant que des flots de données. En effet, les flots de contrôle nécessitent un traitement particulier car les dépendances d'un bloc changent selon qu'il contrôle un autre bloc ou qu'il soit lui-même contrôlé, mais aussi selon son étape dans l'exécution (début ou fin). Un troisième algorithme est alors proposé pour prendre en compte les circuits combinant des flots de données et de contrôle. Cet algorithme calcule les dépendances en exploitant des événements de début et de fin d'exécution des blocs. Cela a permis de prendre en compte tout type de circuit Simulink. Ces algorithmes ont été validés sur plusieurs cas d'étude dont la détection du cliquetis dans le domaine automobile qui sera présenté en fin de ce chapitre.

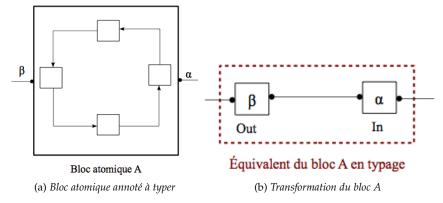

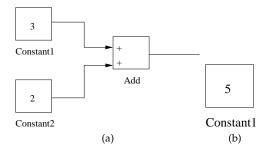

#### Chapitre 7 : Typage des circuits Simulink