### Scheduling Under Memory Constraint in Task-based Runtime Systems

Maxime Gonthier

#### ▶ To cite this version:

Maxime Gonthier. Scheduling Under Memory Constraint in Task-based Runtime Systems. Distributed, Parallel, and Cluster Computing [cs.DC]. Ecole normale supérieure de lyon - ENS LYON, 2023. English. NNT: 2023ENSL0061. tel-04260094

### HAL Id: tel-04260094 https://theses.hal.science/tel-04260094

Submitted on 26 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE en vue de l'obtention du grade de Docteur, délivré par l'ECOLE NORMALE SUPERIEURE DE LYON

Spécialité : Informatique

Soutenue publiquement le 25/09/2023, par :

#### **Maxime GONTHIER**

### Scheduling Under Memory Constraint in Task-based Runtime Systems

Ordonnancement Sous Contrainte Mémoire dans un Modèle de Programmation à Base de Tâches

#### Devant le jury composé de :

| Camille  | COTI     | Professeure, Ecole de Technologie Supérieure Montréal | Rapporteuse        |

|----------|----------|-------------------------------------------------------|--------------------|

| Julien   | LANGOU   | Professeur, University of Colorado Denver             | Rapporteur         |

| Thomas   | HERAULT  | Professeur, The University of Tennesse Knoxville      | Examinateur        |

| Isabelle | TERRASSE | Personnalité scientifique, Airbus                     | Examinatrice       |

| Loris    | MARCHAL  | Chargé de Recherche HDR, CNRS, LIP                    | Directeur de thèse |

| Samuel   | THIBAULT | Professeur des universités, Université de Bordeaux    | Directeur de thèse |

#### Scheduling Under Memory Constraint in Task-based Runtime Systems

**Abstract:** Hardware accelerators, such as GPUs, now provide a large part of the computational power used for scientific simulations. GPUs come with their own limited memory and are connected to the main memory of the machine via a bus with limited bandwidth. Scientific simulations often operate on very large data, to the point of not fitting in the limited GPU memory. In this case, one has to turn to out-of-core computing: data are kept in the CPU memory, and moved back and forth to the GPU memory when needed for the computation. This out-of-core situation also happens when processing on multi-core CPUs with limited memory huge datasets stored on disk.

In both cases, data movement quickly becomes a performance bottleneck. Task-based runtime schedulers have emerged as a convenient and efficient way to manage large applications on such heterogeneous platforms. They are in charge of choosing which tasks to assign on which processing unit and in which order they should be processed.

During this thesis, we worked on the problem of scheduling for a task-based runtime to improve data locality in an out-of-core setting, in order to reduce data movements. We designed strategies for both task scheduling and data eviction from limited memories. We implemented them in the STARPU runtime and compared them to existing scheduling techniques in runtime systems. Our strategies achieves significantly better performance when scheduling tasks on multiple GPUs with limited memory, as well as on multiple CPU cores with limited main memory.

We also worked on batch scheduling of IO intensive workloads. Similarly, we used data locality techniques to reduce the average latency of a job.

**Keywords:** Memory-aware scheduling, Eviction policy, Tasks sharing data, Runtime systems, Data locality, GPUs, CPUs, Job input sharing, Job scheduling

### Remerciements

Le début de cette thèse a été pour moi comme une navigation à l'aveugle dans un océan d'incertitudes. Je ne connaissais ni mes encadrants, ni les villes de Lyon et de Bordeaux, ni personne dans ces régions, j'avais un peu peur. Finalement, ce fut un voyage extrêmement enrichissant en expériences, rencontres et apprentissages, tous plus positifs les uns que les autres. Tout cela a été possible grâce à une multitude de personnes que je tiens à remercier.

En premier lieu, je souhaite exprimer ma gratitude envers le jury. Je tiens à remercier Julien et Camille pour avoir pris le temps de relire attentivement ce long manuscrit. J'espère que cette lecture vous a été agréable et je vous remercie pour vos retours. Un grand merci également à Thomas et Isabelle pour leur rôle d'examinateurs. J'ai été ravi de répondre à vos questions, toutes particulièrement intéressantes.

En second lieu, je voudrais remercier toutes les personnes qui ont pris le temps de relire et de contribuer, de près ou de loin, à l'élaboration de ce manuscrit. Je tiens donc à remercier Loris, Samuel, Mihail, Olivier, Radja, Laércio, Gwenolé, Amina, Emmanuelle, Lionel, Nathalie, Nicolas, Laureline et ma mère.

La première étape de mon périple fut de descendre le Rhône et d'accoster à Lyon. C'est là que j'ai fait la rencontre de Loris. J'ai grandement apprécié nos échanges. Grâce à tes encouragements, tes retours positifs et ta capacité inépuisable à générer de nouvelles idées, j'ai toujours travaillé en toute confiance. J'avais alors l'assurance que j'atteindrai bon port à l'issue de ces trois années. Je te suis reconnaissant pour le temps que tu as investi tout au long de cette thèse, que ce soit lors de nos nombreuses réunions ou par le biais de tes multiples contributions. J'avais ainsi le sentiment de ne pas travailler pour un directeur de thèse, mais bel et bien aux côtés d'un chercheur. Un grand merci également à toute l'équipe ROMA pour son accueil chaleureux. Grégoire, Anne, Yves, Frédéric, Bora, Anthony et Lucas, merci beaucoup.

Un an plus tard, j'ai achevé ma descente du Rhône, traversé le détroit de Gibraltar pour rejoindre le port de la Lune. C'est là que j'ai été chaleureusement accueilli par Samuel. Merci infiniment, Sam, de m'avoir fait ressentir le sentiment de chez-moi si rapidement. Je te suis reconnaissant pour le temps que tu as consacré à travailler avec moi sur tous mes problèmes liés à StarPU, parfois pendant des heures. J'ai véritablement apprécié nos échanges. Tu es une source inépuisable de conversations, toujours intéressantes. Merci à toute l'équipe STORM pour ces innombrables heures de discussions passées dans la salle café. Merci Emmanuelle pour tous tes précieux conseils sur la vie en postdoc. Mihail, merci pour tes séances de psychothéra-courses (en tout bien tout honneur). Amina je te remercie pour ta bienveillance et tes encouragements. Merci aussi à Olivier, Nathalie, Raymond, Marie-Christine, PAW, Laércio, Van Man et Denis.

vi Remerciements

J'ai aussi rencontré les membres de l'open space, qui ont rendu cette thèse mille fois plus amusante et j'aimerais les remercier. Vincent, merci à toi. Ton pardessus te donne un air de méchant tout droit sorti d'un film de James Bond, j'aime beaucoup. Merci Romain, finalement, j'aime bien ta tasse. Baptiste, je te remercie pour tes multiples propositions de pauses café quotidiennes. Gwenolé, merci pour ton sens de l'humour, ton professionnalisme et ta créativité en matière de déguisements. Merci Diane pour nos séances d'escalades véloces. Alice, tes fanfictions sont toujours un régal, merci. Merci Lana pour les super chaussons requins. Merci Kun de me forcer à faire des cookies. Merci Célia pour ta bonne humeur contagieuse. Radja, merci de courir plus vite que le bus. Merci Thomas de reprendre le flambeau des thèses StarPU avec autant de brio. Merci Albert pour nos sorties aux BT.

J'ai également eu l'occasion de discuter avec de nombreuses personnes d'autres équipes. Je remercie Alycia pour les montagnes de poils de Fifi que tu m'as généreusement laissées. Merci aussi à Lionel, Abdou, Mathieu, Olivier B, Philippe S, Philippe V, ainsi qu'à l'ensemble des équipes TADAAM, TOPAL et CONCACE.

I then sailed my boat toward the Baltic Sea for a 3-month stay at Uppsala University. It was a wonderful time that taught me how to work with new people and how to adapt to a new environment. I discovered the natural beauty of Sweden, but more importantly, the kindness of its people.

Thank you, Marina, for facilitating my arrival at Uppsala and for organizing so many events for me to join. Watching the big fire in Gamla is still vivid in my memory. Thanks to all my friends on the 6th floor of Sernanders väg 4. Thanks to Camille for introducing me to outdoor climbing. Thanks to Ivo, Lukas, Sonja, Gesina, Andreas, and everyone at the Division of Scientific Computing.

And, of course, thank you, Carl, for all your insightful advice on the direction our project should take. A special thanks to Elisabeth for being exceptionally welcoming and for inviting me to her birthday celebration in the beautiful Kallmyr. I hold my time in Uppsala dear, and much of that is thanks to you.

Une embarcation ne navigue pas sans une charpente solide. Celle-ci a été construite au fil du temps par ma famille. Merci à mes parents de m'avoir toujours inculqué l'amour de la science et de la culture. J'apprécie toujours autant de visiter des musées et de m'intéresser à la géographie, et c'est cette curiosité qui m'a aussi grandement aidé à mener à bien cette thèse. Je vous remercie également de m'avoir assisté lors de deux (bientôt trois) déménagements. À mon frère, un grand merci pour m'avoir montré la voie de la science et de la recherche. Grâce à toi, il m'a été beaucoup plus facile de me lancer dans cette aventure. Je te remercie aussi de m'avoir écouté parler de mes problèmes pendant trois ans, et d'être toujours aussi attentioné. À ma sœur, je tiens à te remercier pour ta bonne humeur constante, nos soirées sous les étoiles filantes et d'être toujours là pour moi. Tu es une grande sœur en or.

Un voyage en mer c'est encore mieux lorsqu'on peut rester en contact avec des amis sur le continent. Merci à Guillaume, pour être un ami extraordinaire, et ce depuis presque 10 ans (et merci pour les 70 euros). À Amandine et Bylitis, merci d'être toujours des amies fidèles, et ce depuis 13 ans ! C'est toujours un plaisir de vous voir et de savoir que je peux compter sur vous. Merci à Ben, je passe toujours d'excellents moments avec toi, même après de longues périodes de séparation. Merci à tous les membres de DOàT pour nos soirées du Nouvel An, la béchamel, le limoncello et les anniversaires. Un merci tout particulier également à Doruntine, Joseph, Fares, Hamza, Stéphane et tant d'autres que j'oublie sûrement.

Enfin je voudrais remercier Laureline, sans qui mon navire aurait sombré à coup sûr. Tu as rendu ces trois années absolument merveilleuses. À la maison, je me sentais bien, j'étais écouté, soutenu et con-

seillé. Merci d'avoir accepté de déménager à deux reprises avec moi. Merci de ne m'avoir jamais jugé et de me comprendre comme personne d'autre. Notre voyage ensemble comporte encore de nombreux écueils, mais je suis sûr que nous atteindrons de plus beaux rivages dans un futur proche.

Merci à Fifi d'être aussi mignon et d'avoir servi de petit canard pour mes problèmes dans StarPU tout au long de cette thèse, ce qui fait de toi, sans aucun doute, un ingénieur StarPU hors-pair.

Mon voyage m'amène maintenant à traverser l'Atlantique, et grâce à vous tous, je n'ai plus peur.

## Résumé en français

ES SCIENTIFIQUES mènent des efforts constants afin d'améliorer les performances de leurs applications, que ce soit pour accroître leur précision ou pour s'attaquer à des problèmes plus grands. Une puissance de calcul importante est nécessaire pour obtenir des résultats précis dans les domaines tels que la prévision météorologique, la prédiction de tremblements de terre ou la simulation de flux d'air. Les applications susmentionnées dépendent également de l'utilisation de grandes quantités de données d'entrée. Pour les applications modernes, la puissance de calcul et les besoins mémoire sont si importants que des machines dédiées, appelées supercalculateurs, sont devenues une nécessité. Les supercalculateurs ont donné naissance au domaine du calcul haute performance (HPC), qui se concentre sur l'optimisation de leurs utilisation afin de maximiser leurs capacités. Une réalité bien connue dans le domaine du calcul haute performance est qu'il existe un lien intrinsèque entre la puissance de calcul des supercalculateurs et leur mémoire.

Depuis ENIAC [70], le premier ordinateur électronique et programmable, construit en 1945, la gestion de la mémoire a toujours été une contrainte. La mémoire était alors constituée de 18 000 tubes à vide, et il en fallait 36 pour stocker un seul nombre en base 10. Les tubes à vide nécessitaient tellement d'énergie que plusieurs d'entre eux grillaient presque chaque jour, ce qui rendait l'ordinateur inutilisable la moitié du temps. La partie la plus critique du fonctionnement de l'ordinateur était donc le stockage de données.

Au fil des progrès technologiques, la nécessité d'une gestion efficace de la mémoire est restée d'actualité. On peut citer par exemple l'ordinateur Cray X-MP [41], construit en 1983 pour être l'ordinateur le plus rapide du monde. Il était composé de quatre CPUs avec 64 mégaoctets de mémoire partagée et pouvait atteindre une performance de pointe de près de 1 gigaflop/s, c.-à-d.,  $10^9$  opérations à virgule flottante par seconde. Lorsque la taille de l'ensemble des données d'entrée dépassait la mémoire du CPU, il était alors nécessaire de transférer les données depuis le disque dur à l'aide d'un câble dont la bande passante ne dépassait pas quelques mégaoctets par seconde. Afin d'éviter de ralentir les calculs, il était donc important de gérer le moment et la manière d'accéder aux données.

Afin d'atteindre des vitesses de calcul sans précédent, la tendance de la dernière décennie consiste à utiliser des GPUs en plus des CPUs. Depuis 2022, grâce à l'utilisation de plus de 37 000 GPUs, le supercalculateur Frontier [53] est la machine la plus puissante du monde, avec une performance de 1 exaflop/s, c.-à-d., 10<sup>18</sup> opérations à virgule flottante par seconde. Les GPUs sont rapides et massivement parallèles, mais n'intègrent qu'une mémoire relativement limitée. Lorsque les utilisateurs essayent de résoudre des applications très volumineuses, il est courant que toutes les données d'entrée du problème ne peuvent pas tenir dans la mémoire des unités de calcul. Pour des GPUs, cela signifie qu'il faut transférer les données depuis la mémoire d'un CPU en utilisant un bus dont la bande passante est limitée. Bien que les GPUs aient une puissance de calcul de l'ordre de milliers de gigaflop/s, les bus ont com-

munément une bande passante de l'ordre d'une douzaine de milliers de mégaoctets/s. Cette différence de rapport de 100 est un parfait exemple de l'écart grandissant entre la vitesse de calcul et les bandes passantes de communication. Cette évolution s'accompagne également d'une diminution de la mémoire par gigaflop/s. Ce qui signifie que le problème ne peut pas être résolu en chargeant toutes les données d'entrée en mémoire. Cet écart constitue un goulot d'étranglement pour les performances. Cela motive les chercheurs en calcul haute performance à travailler sur l'optimisation des techniques de gestion de la mémoire afin d'utiliser tout le potentiel des supercalculateurs.

Dans cette thèse, nous visons à combler cette lacune en répondant au problème suivant : Comment minimiser le temps d'exécution d'une application dont l'ensemble des données est plus grand que la mémoire des unités de calcul utilisées ? Une réponse possible consiste à améliorer le matériel utilisé. Cependant, l'ajout de mémoire est coûteux et ne constitue pas une solution permanente : si l'ensemble des données devient de plus en plus important, on ne peut pas ajouter de la mémoire indéfiniment. L'ajout de bus supplémentaires peut être une option pour améliorer les performances. Cependant, cela est difficile car les bus sont coûteux, consomment beaucoup d'énergie et prennent de la place dans un nœud de calcul déjà physiquement limité.

La réponse que nous proposons est plus générique et repose sur l'amélioration du logiciel d'un support d'exécution. Les optimisations logicielles génériques peuvent être appliquées à n'importe quel matériel et constituent donc un objectif complémentaire aux améliorations matérielles. Pour exploiter la puissance des plateformes hétérogènes complexes, il est devenu très courant d'utiliser la programmation à base de tâches, c.-à-d., d'exprimer le calcul de l'application sous la forme d'un graphe acyclique dirigé (DAG), et de laisser un support d'exécution dynamique gérer l'exécution du graphe de tâches sur de telles plateformes. La charge de l'allocation des données en mémoire, du choix de l'ordre de traitement des tâches et de leur répartition sur les unités de calcul est ainsi retirée au programmeur de l'application. Cette charge est alors gérée par le support d'exécution sous la forme d'un problème d'ordonnancement de tâches. Étant donné que le support d'exécution gère à la fois les données et les tâches, il est alors possible de créer des ordonnanceurs qui minimisent les mouvements de données. Cela améliore les performances lorsque la mémoire est une contrainte. La création de politiques d'ordonnancement est une approche plus générale car elle peut être appliquée à n'importe quelle architecture matérielle ou application à base de tâches. Notre objectif est donc de construire un ordonnanceur générique qui partitionne et ordonne des tâches sur une ou plusieurs unités de calcul à mémoire limitée, et qui apporte de meilleures performances que les stratégies d'ordonnancement actuelles. Pour atteindre cet objectif, dans le Chapitre 1 nous étudions d'abord le contexte dans lequel cette thèse a eu lieu, nous passons en revue les travaux connexes, et nous détaillons comment nous avons l'intention de résoudre le problème énoncé précédemment. Le Chapitre 2 présente la manière dont nous simplifions et modélisons le problème. Le Chapitre 3 présente une solution algorithmique pour l'ordonnancement statique de tâches indépendantes sur une seule unité de calcul. Nous étendons ensuite cette solution à plusieurs unités de calcul dans le chapitre 4 et proposons un nouvel ordonnanceur dynamique. Le Chapitre 5 décrit les améliorations apportées à notre ordonnanceur dynamique et les expériences menées avec des ensembles de tâches avec dépendances. Dans le Chapitre 6, nous transférons les leçons tirées de l'ordonnancement avec localité à l'ordonnancement batch<sup>1</sup> en introduisant de nouveaux algorithmes pour les systèmes batch. Les chapitres sont résumé ci-dessous.

<sup>&</sup>lt;sup>1</sup>Le concept *batch* désigne les techniques appliquées à l'échelle d'un supercalculateur pour gérer des *travaux*. Les travaux sont des applications ou codes soumis par des utilisateurs à un supercalculateur. Ainsi batch peut désigner de l'ordonnancement de travaux sur un supercalculateur appelé ordonnancement batch, des systèmes de gestions de travaux appelé systèmes batch ou alors un simulateur de travaux appelé simulateur batch.

#### Chapter 1: Contexte et Revue de la Littérature

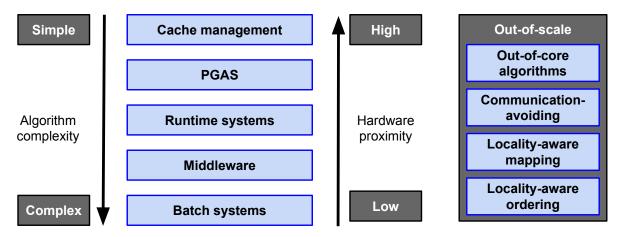

Dans ce premier chapitre, nous présentons le contexte dans lequel cette thèse a été conduite : le besoin d'exécuter des applications d'algèbre linéaire dont les données d'entrée ne tiennent pas dans la mémoire d'une unité de calcul. Nous expliquons également la motivation qui justifie l'approche que nous avons choisie pour résoudre ce problème. Le Chapitre 1 développe ensuite les travaux existants sur ce problème et comment ils interviennent à différent niveaux de l'architecture matérielle (du cache aux systèmes batch). Nous justifions ensuite notre choix de positionnement par rapport à la proximité de l'architecture matérielle. Enfin, nous expliquons comment nous avons réduit l'écart entre l'ordonnancement théorique et l'ordonnancement pratique.

#### Chapter 2: Énoncé de la Problématique et Intégration dans un Support d'Exécution

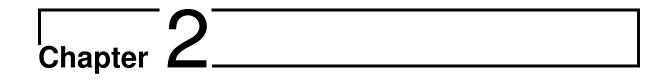

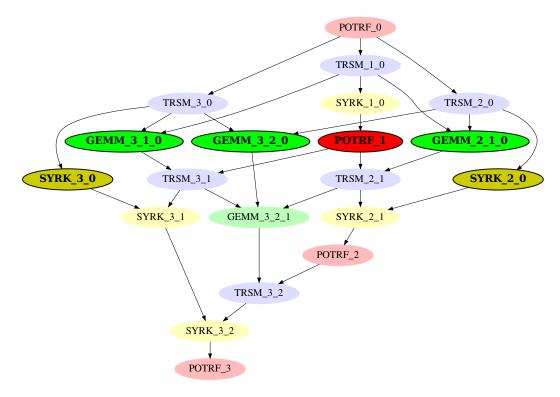

Le Chapitre 2 exprime notre problème à l'aide de différents modèles théoriques. Le modèle le plus simple est basé sur l'ordonnancement de tâches indépendantes sur une seule unité de calcul à mémoire limitée. En utilisant cette simplification, nous prouvons l'optimalité d'une politique d'éviction et démontrons la complexité de notre problème. Nous complexifions ensuite notre modèle en ajoutant plusieurs unités de calcul, des poids hétérogènes et des ensembles de tâches avec dépendances. Nous présentons également STARPU, le support d'exécution que nous avons utilisé pour implémenter nos algorithmes et mener nos expériences. Pour répondre à nos besoins, nous introduisons dans STARPU la capacité d'ajouter des politiques d'éviction personnalisées ainsi qu'un nouvel outil de collecte de données et de visualisation.

#### Chapter 3: Ordonnancement Statique pour une Seule Unité de Calcul [R1, IP1, W1, J1]

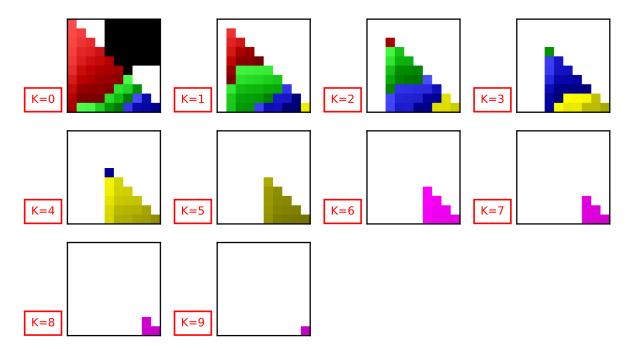

Une première solution algorithmique est proposée en considérant un problème d'empaquetage, que nous prouvons être NP-complet. À partir de ce problème d'empaquetage, nous avons développé un ordonnanceur appelé Hierarchical Fair Packing (HFP), qui regroupe des tâches partageant des données. Pour l'évaluer, nous adaptons deux méthodes de la littérature que nous estimons pertinentes par rapport à notre problème. Les trois stratégies mentionnées sont implémentées dans le support d'exécution STARPU. Nous évaluons expérimentalement les trois méthodes ainsi qu'un ordonnanceur de référence et un ordonnanceur de pointe et utilisons des variantes de la multiplication matricielle. Le Chapitre 3 contient ensuite une description des évaluations expérimentales et une explication des résultats grâce à notre outil de visualisation présenté dans le chapitre précédent.

#### Chapter 4: Exploiter la Puissance de Plusieurs GPUs [IP2, C1]

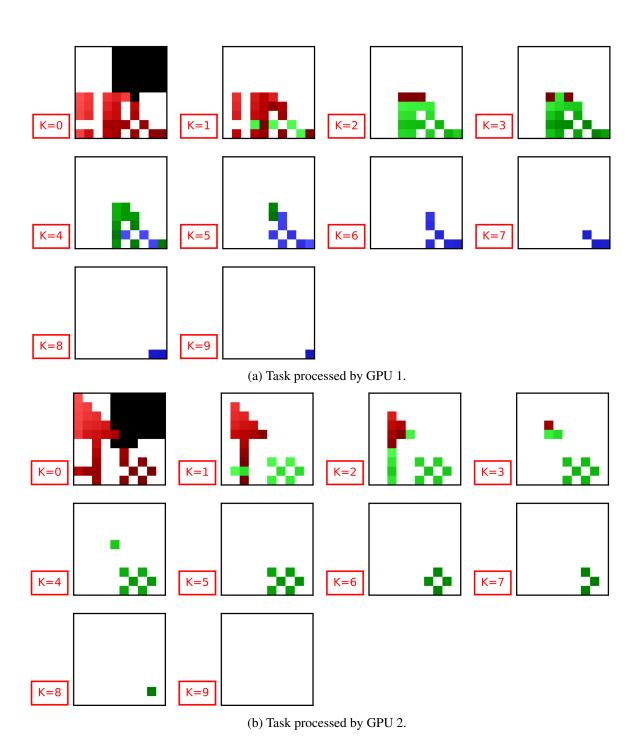

Alors que le chapitre précédent utilisait une seule unité de calcul, le Chapitre 4 se concentre sur les défis de l'ordonnancement de tâches sur plusieurs unités de calcul, chacune avec sa propre mémoire limitée. Le chapitre commence par une description du nœud de calcul utilisé. Cette description souligne l'importance de la localité spatiale lorsque sont utilisé plusieurs mémoires locales, en montrant comment l'ordonnanceur de pointe utilise une telle architecture. Nous présentons ensuite une technique de partitionnement de graphe, que nous avons adapté à notre problème en l'étendant avec du vol de tâches. Nous expliquons ensuite comment HFP est adapté pour devenir une stratégie de partitionnement et d'ordonnancement pour plusieurs unités de calcul : en y ajoutant des techniques d'équilibrage de charges et de vol de tâches. Nous présentons également une nouvelle stratégie dynamique appelée DARTS (Dynamic Data-Aware Reactive Task Scheduling), également implémenté dans STARPU. L'intuition de DARTS est de prendre en compte la localité des données avant l'allocation des tâches. DARTS utilise

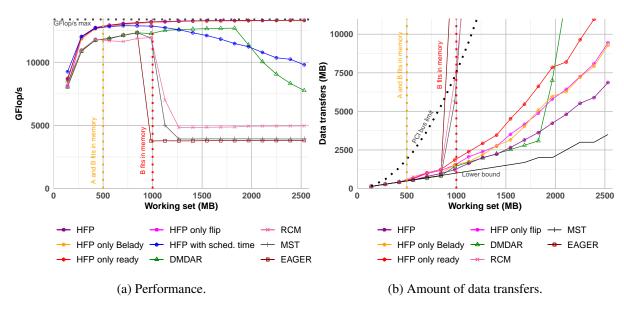

l'état de la mémoire des unités de calcul afin de choisir les données à charger et maximiser la réutilisation des données. Pour illustrer les performances de nos ordonnanceurs, le chapitre présente des résultats expérimentaux sur différentes variantes de la multiplication matricielle et des sous-ensembles de la factorisation de Cholesky.

#### Chapter 5: Ordonnancement Dynamique pour les Graphes de Tâches [N1, P1, R3]

Ce chapitre se concentre sur le problème d'ordonnancement d'ensembles de tâches avec dépendances sur plusieurs unités de calcul à mémoire limitée. Nous décrivons des algorithmes existants et largement utilisés dans les support d'exécution : une politique de vol de travail avec localité et un ordonnanceur du support d'exécution PaRSEC. Nous retravaillons la version de DARTS présentée dans le dernier chapitre afin de favoriser le transfert rapide de données, gérer les dépendances et inclure les priorités dans la prise de décision. Nous avons également travaillé à réduire la complexité de DARTS. Pour démontrer l'efficacité de ces techniques d'ordonnancement, le chapitre présente des études expérimentales utilisant GEMM, les factorisations Cholesky et LU, et en utilisant un ou plusieurs GPUs ou des cœurs CPU.

#### Chapter 6: Tirer Parti de la Localité pour les Ordonnanceurs Batch [R2]

Les travaux présentés dans ce chapitre ont été menés dans le cadre d'une collaboration avec Elisabeth LARSSON et Carl NETTELBLAD. Cette collaboration s'est accompagné d'un séjour de trois mois à l'université d'Uppsala en Suède. Nous avons adapté notre sujet d'étude afin de répondre à leurs besoins de recherche tout en gardant l'accent sur l'ordonnancement sous contrainte mémoire. L'université d'Uppsala exploite une plateforme de calcul à haute performance utilisée par des chercheurs pour soumettre des travaux utilisant de grandes quantités de données. Ces travaux nécessitent le chargement de fichiers d'entrée de plusieurs gigaoctets avant de pouvoir commencer leurs exécutions. Les ordonnanceurs batch traditionnels ne sont généralement pas conçus pour gérer des ensembles de travaux intense en Entrée/Sortie. Avec ces ensembles de travaux, les temps de chargement peuvent devenir significatifs, augmentant ainsi le temps d'attente pour tous les travaux. C'est pourquoi, dans le Chapitre 6, nous proposons de modéliser les avantages de la réutilisation de données entre des travaux successifs. Nous avons développé un simulateur batch et introduit de nouveaux ordonnanceurs batch qui ajoutent une telle réutilisation de données. En suivant quelles données sont chargées sur quel nœud, ils sont capables de réduire de la quantité de transfert de données, améliorant ainsi à la fois l'utilisation des ressources et la satisfaction des utilisateurs. Nous évaluons ces algorithmes en utilisant des traces de soumissions de travaux réellement observées sur la plateforme de calcul de l'université d'Uppsala et étudions les performances obtenues après avoir ordonné près de 2 millions de travaux.

## **Contents**

| Re | emerc | iements |                                                                       | V  |

|----|-------|---------|-----------------------------------------------------------------------|----|

| Ré | sumé  | en frai | nçais                                                                 | ix |

| In | trodu | ction   |                                                                       | 1  |

| 1  | Bacl  | kground | d and Literature Review                                               | 5  |

|    | 1.1   | Contex  | <u>xt</u>                                                             | 6  |

|    |       | 1.1.1   | Three real-world examples                                             | 6  |

|    |       | 1.1.2   | Hardware will not save us                                             | 7  |

|    |       | 1.1.3   | but maybe software can                                                | 9  |

|    |       | 1.1.4   | What happens when the memory is full?                                 | 9  |

|    |       | 1.1.5   | Problem statement                                                     | 10 |

|    | 1.2   | Relate  | d works                                                               | 11 |

|    |       | 1.2.1   | Cache management                                                      | 11 |

|    |       | 1.2.2   | Partitioned global address space                                      | 12 |

|    |       | 1.2.3   | Solutions in runtime systems                                          | 12 |

|    |       | 1.2.4   | An out-of-core middleware                                             | 13 |

|    |       | 1.2.5   | Scheduling for distributed platforms                                  | 14 |

|    |       | 1.2.6   | Out-of-core and communication-avoiding algorithms                     | 14 |

|    |       | 1.2.7   | Locality-aware mapping                                                | 15 |

|    |       | 1.2.8   | Locality-aware mapping and ordering                                   | 15 |

|    | 1.3   | Positio | oning in the hardware hierarchy                                       | 15 |

|    | 1.4   | Bridgi  | ng the gap between theoretical scheduling and runtime schedulers      | 17 |

| 2  | Prol  | olem St | atement and Integration into a Runtime System                         | 21 |

|    | 2.1   | Simpli  | ifying our optimization problems                                      | 22 |

|    |       | 2.1.1   | Expressing applications as task graphs                                | 22 |

|    |       | 2.1.2   | Avoiding the conflicting goals of using multiple processing units     | 23 |

|    |       | 2.1.3   | Considering homogeneous processing time and data size                 | 23 |

|    |       | 2.1.4   | Making the model complex again                                        | 24 |

|    | 2.2   | Simpli  | ified model with an independent task set and a single processing unit | 24 |

|    |       | 2.2.1   | Expressing applications as a bipartite graphs                         | 24 |

|    |       | 2.2.2   | Simplified optimization problem                                       | 25 |

XiV CONTENTS

|   |      | 2.2.3 Optimal eviction policy proof                                             | . 26 |

|---|------|---------------------------------------------------------------------------------|------|

|   |      | 2.2.4 Complexity of finding an optimal task order                               |      |

|   | 2.3  | Making the model parallel                                                       | . 28 |

|   |      | 2.3.1 Adding the partitioning problem to the bipartite graph                    | . 28 |

|   |      | 2.3.2 Optimization problem in parallel                                          | . 29 |

|   | 2.4  | Extension to heterogeneous task and data weights                                | . 29 |

|   | 2.5  | Adding dependencies to the model                                                | . 30 |

|   | 2.6  | The STARPU Runtime System                                                       | . 31 |

|   |      | 2.6.1 Task and data                                                             | . 32 |

|   |      | 2.6.2 Tasks submission                                                          | . 32 |

|   |      | 2.6.3 Task flow                                                                 | . 34 |

|   |      | 2.6.4 New functionality to add custom eviction policies                         | . 34 |

|   |      | 2.6.5 New logging and visualization tool                                        | . 37 |

|   | 2.7  | Summary                                                                         | . 41 |

| 3 | Stat | Scheduling for a Single Processing Unit                                         | 43   |

|   | 3.1  | Schedulers from the STARPU runtime system                                       | . 44 |

|   |      | 3.1.1 A greedy baseline: EAGER                                                  |      |

|   |      | 3.1.2 Deque Model Data Aware Ready (DMDAR)                                      |      |

|   | 3.2  | Adapted strategies from the literature                                          |      |

|   |      | 3.2.1 Reverse-Cuthill-McKee (RCM)                                               |      |

|   |      | 3.2.2 Maximum Spanning Tree (MST)                                               |      |

|   | 3.3  | Hierarchical Fair Packing (HFP)                                                 |      |

|   |      | 3.3.1 Intuition                                                                 |      |

|   |      | 3.3.2 An NP-complete problem                                                    | . 48 |

|   |      | 3.3.3 Strategy                                                                  |      |

|   |      | 3.3.4 Complexity of HFP                                                         | . 51 |

|   |      | 3.3.5 Improving HFP with package flipping                                       | . 52 |

|   |      | 3.3.6 Optimal eviction policy                                                   | . 53 |

|   |      | 3.3.7 Adaptation to heterogeneous data sizes                                    |      |

|   |      | 3.3.8 Improving the beginning of the schedule with the <i>Ready</i> re-ordering | . 54 |

|   | 3.4  | Experimental settings                                                           | . 54 |

|   | 3.5  | Experimental results and analysis                                               | . 57 |

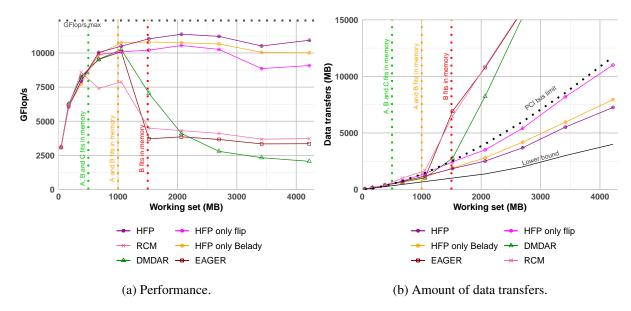

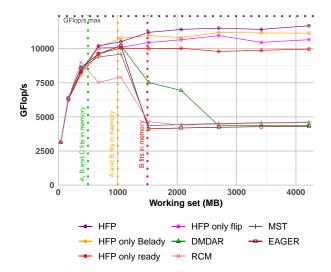

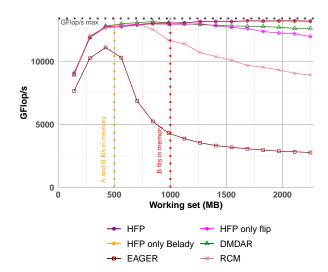

|   |      | 3.5.1 Results on the 2D matrix multiplication                                   | . 57 |

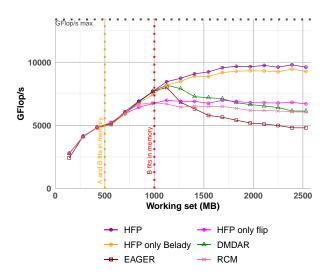

|   |      | 3.5.2 Results on the 3D matrix multiplication                                   | . 62 |

|   |      | 3.5.3 Results on the task set of the Cholesky factorization                     | . 65 |

|   |      | 3.5.4 Results on the 2D matrix multiplication with randomized task order        | . 66 |

|   |      | 3.5.5 Results on the randomized pairs with 2D inputs                            | . 68 |

|   |      | 3.5.6 Results on the sparse 2D matrix multiplication                            | . 69 |

|   | 3.6  | Conclusion on static scheduling for a single processing unit                    | . 70 |

| 4 | Har  | essing the Power of Multiple GPUs                                               | 73   |

|   | 4.1  | State-of-the-art schedulers                                                     |      |

|   |      | 4.1.1 Leveraging expected communication time with DMDAR                         |      |

|   |      | 4.1.2 Using (hyper-)graph partitioning                                          |      |

|   | 4.2  | Hierarchical Fair Packing adaptation to multiple processing units (mHFP)        |      |

|   |      | 4.2.1 Strategy                                                                  |      |

CONTENTS

|   |     | 4.2.2 Additional unused solutions explored for mHFP                        | 78 |

|---|-----|----------------------------------------------------------------------------|----|

|   | 4.3 | A dynamic data-aware scheduler: DARTS                                      | 81 |

|   |     | 4.3.1 Intuition                                                            | 81 |

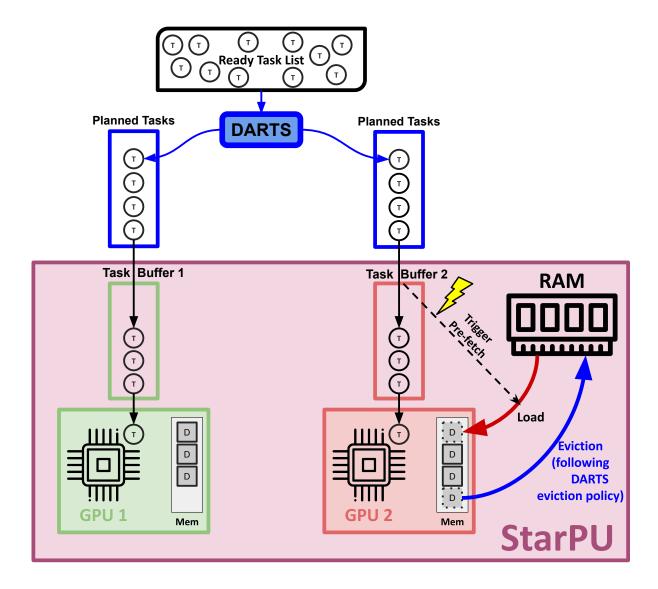

|   |     | 4.3.2 STARPU's task flow with DARTS                                        | 81 |

|   |     | 4.3.3 Strategy                                                             | 81 |

|   |     | 4.3.4 Eviction policy                                                      |    |

|   |     | 4.3.5 Dealing with more input data per task                                |    |

|   |     | 4.3.6 Reducing the scheduling overhead                                     |    |

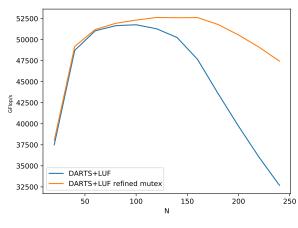

|   |     | 4.3.7 Faster code with fewer mutex                                         |    |

|   | 4.4 | Experimental evaluation with multiple processing units                     |    |

|   |     | 4.4.1 Settings                                                             |    |

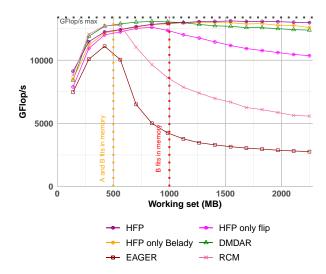

|   |     | 4.4.2 Results on the 2D matrix multiplication with a single GPU            |    |

|   |     |                                                                            | 87 |

|   |     | * *                                                                        | 93 |

|   |     | •                                                                          | 96 |

|   |     | 4.4.6 Result on the task set of the Cholesky factorization with 4 GPUs     |    |

|   |     | 4.4.7 Results on the sparse 2D matrix multiplication with 4 GPUs           |    |

|   | 4.5 | *                                                                          | 97 |

|   |     |                                                                            |    |

| 5 | •   | 8                                                                          | 99 |

|   | 5.1 | Existing runtime schedulers                                                |    |

|   |     | 5.1.1 A work stealing policy: LWS                                          |    |

|   |     | 5.1.2 A priority-based scheduler from the PaRSEC runtime: AP               |    |

|   | 5.2 | Improving the DARTS scheduler                                              |    |

|   |     | 5.2.1 Intuition                                                            |    |

|   |     | 5.2.2 Strategy                                                             |    |

|   |     | 5.2.3 Eviction policy                                                      |    |

|   | 5.3 | Experimental settings                                                      |    |

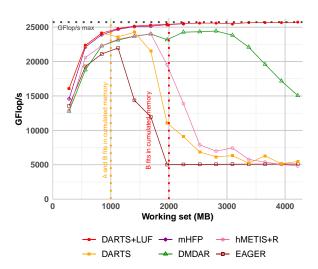

|   | 5.4 | Cholesky factorization with GPUs                                           |    |

|   |     | 5.4.1 Overview                                                             |    |

|   |     | 5.4.2 Optimal data access pattern                                          |    |

|   |     | 5.4.3 Single GPU case                                                      |    |

|   |     | 5.4.4 With multiple GPUs                                                   |    |

|   |     | 5.4.5 With multiple GPUs and no memory limitation                          |    |

|   | 5.5 | LU factorization with GPUs                                                 |    |

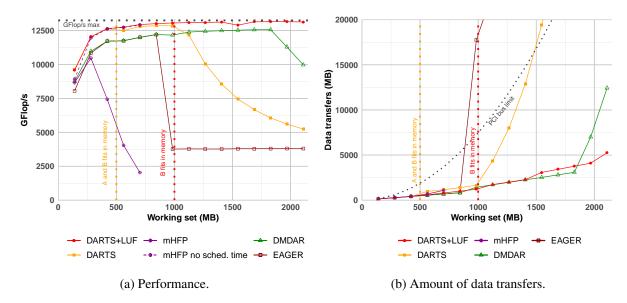

|   |     | 5.5.1 Results on 4 GPUs                                                    |    |

|   |     | 5.5.2 Results on a single GPU and no memory limitation                     |    |

|   | 5.6 | 3D matrix multiplication with GPUs                                         |    |

|   | 5.7 | LU factorization on a multi-core CPU                                       |    |

|   | 5.8 | Conclusion on dynamic scheduling of task sets with dependencies            | 16 |

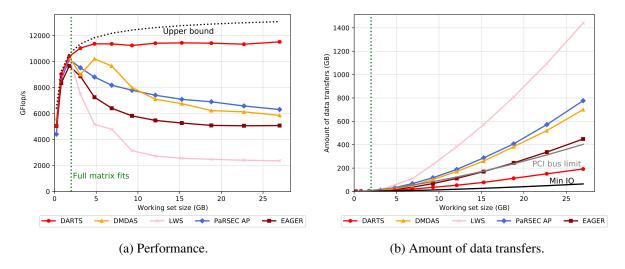

| 6 | Low | raging Locality for Batch Schedulers                                       | 17 |

| U | 6.1 | Motivation                                                                 |    |

|   | 6.2 | Related work                                                               |    |

|   | 0.2 | 6.2.1 Scheduling jobs on large clusters                                    |    |

|   |     | 6.2.2 Using distributed file systems to deal with data-intensive workloads |    |

|   |     | 6.2.3 Using schedulers to deal with data-intensive workloads               |    |

|   |     |                                                                            |    |

*CONTENTS*

|         | 6.2.4    | Reducing I/O contention                                | . 120 |

|---------|----------|--------------------------------------------------------|-------|

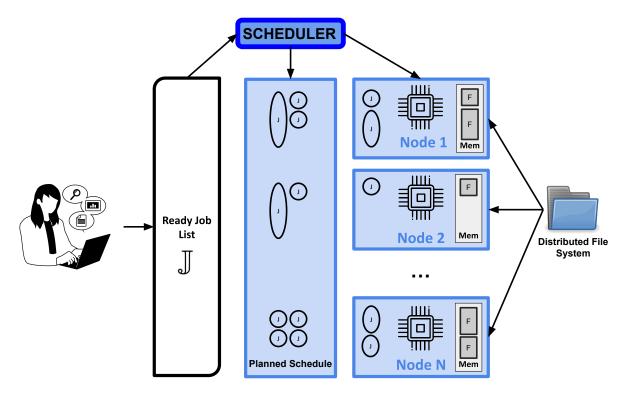

| 6.3     | Frame    | work                                                   | . 120 |

| 6.4     | Schedi   | ulers                                                  | . 122 |

|         | 6.4.1    | Two schedulers from the state of the art: FCFS and EFT | . 123 |

|         | 6.4.2    | Data-locality-based schedulers                         | . 123 |

|         | 6.4.3    | Adding backfilling to all strategies                   | . 125 |

| 6.5     | Experi   | mental settings                                        | . 126 |

|         | 6.5.1    | Platform description                                   | . 126 |

|         | 6.5.2    | Workloads description                                  | . 126 |

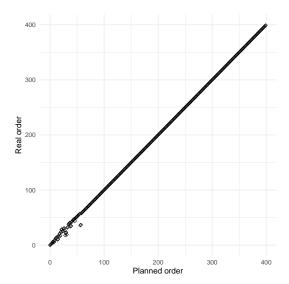

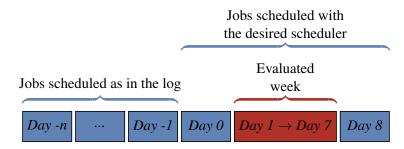

|         | 6.5.3    | Usage of real cluster logs                             | . 127 |

|         | 6.5.4    | Simulator description                                  | . 128 |

| 6.6     | Experi   | mental evaluation and analysis                         | . 129 |

|         | 6.6.1    | Results on an underutilized cluster                    |       |

|         | 6.6.2    | Results on a saturated cluster                         | . 131 |

|         | 6.6.3    | Complete results                                       | . 132 |

| 6.7     | Conclu   | usion on locality-aware batch scheduling               |       |

| Conclus | sion and | l Perspectives                                         | 137   |

| Bibliog | raphy    |                                                        | 143   |

| Publica | tions    |                                                        | 153   |

| Acknow  | vledgem  | ient                                                   | 155   |

# **List of Figures**

| 1.1  | Examples of datasets used for applications with dense linear algebra as the main com-                                                                                                                                                                                                                                                                                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | putation phase                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7  |

| 1.2  | Sources of computing performance over the last 50 years                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

| 1.3  | Platform topology of a multi-core CPU with shared memory                                                                                                                                                                                                                                                                                                                                                                                          | 9  |

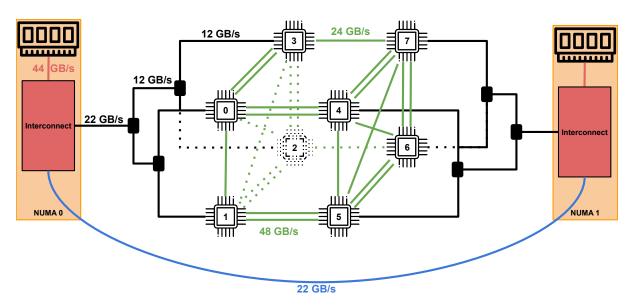

| 1.4  | Platform topology of multiple GPUs with distributed memory                                                                                                                                                                                                                                                                                                                                                                                        | 10 |

| 1.5  | The hierarchy of solutions for the MIN-EXEC-TIME-LIMITED-MEM problem                                                                                                                                                                                                                                                                                                                                                                              | 11 |

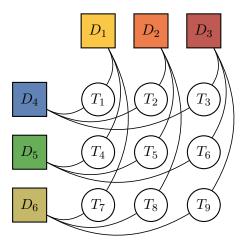

| 2.1  | Task set from the Cholesky factorization                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 2.2  | Example of bipartite graph and processing order with one processing unit                                                                                                                                                                                                                                                                                                                                                                          | 24 |

| 2.3  | Example of bipartite graph and processing order with two processing units                                                                                                                                                                                                                                                                                                                                                                         | 28 |

| 2.4  | Task insertion of the Cholesky factorization within the STARPU runtime system                                                                                                                                                                                                                                                                                                                                                                     | 33 |

| 2.5  | Task flow within the STARPU runtime                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |

| 2.6  | Function definitions needed for custom eviction policy within the STARPU runtime                                                                                                                                                                                                                                                                                                                                                                  | 36 |

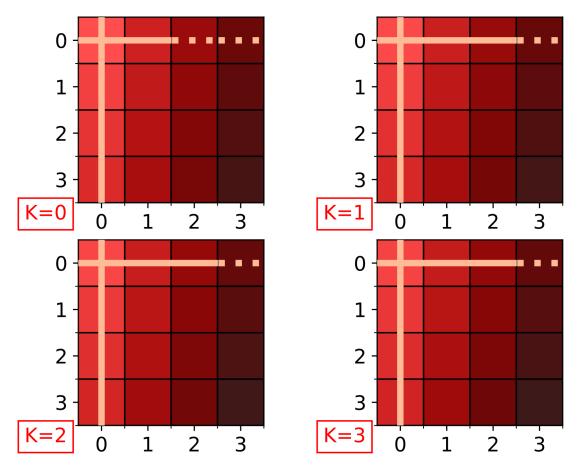

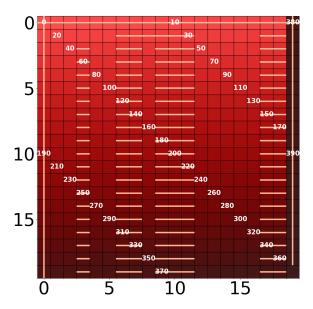

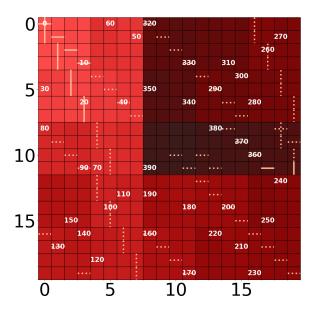

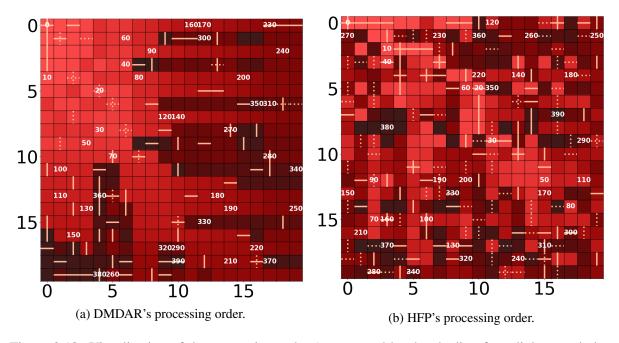

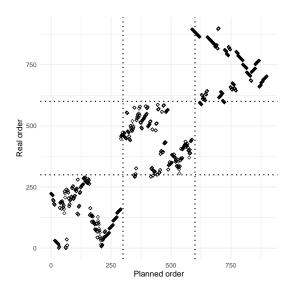

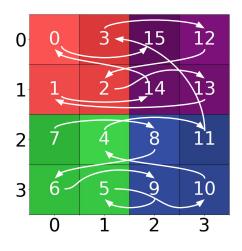

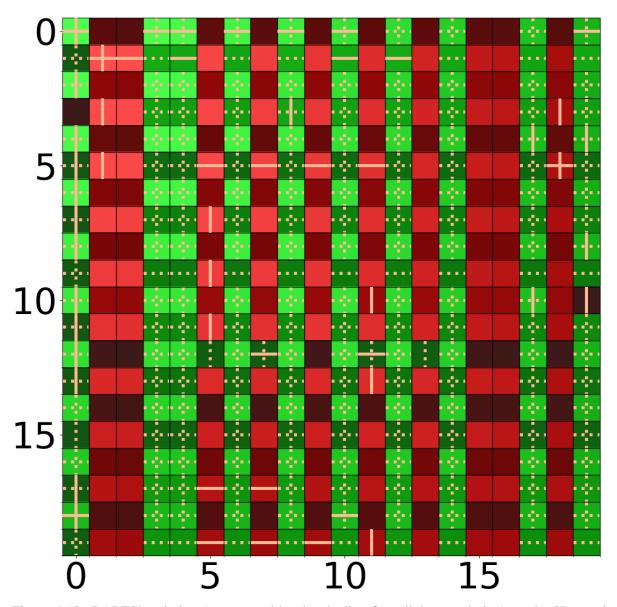

| 2.7  | Visualization of the processing order on a 2D matrix multiplication. Side of the input matrices $N=4$ . The shading, from lighter to darker, represents the ordering. A beige vertical (resp. horizontal) line in a square corresponds to a row (resp. column) load that was necessary to compute this tile. Solid lines are fetches while dotted lines are                                                                                       |    |

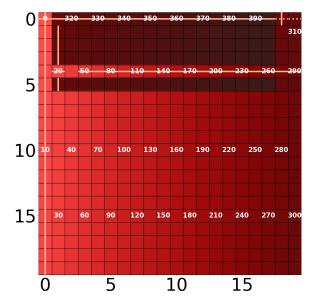

| 2.8  | prefetches. With multiple GPUs, each color is a set of tasks assigned to a GPU Visualization of the processing order on a 3D matrix multiplication with 1 GPU. Side of the input matrices $N=4$ . The shading, from lighter to darker, represents the ordering. A beige vertical (resp. horizontal) line in a square corresponds to a row (resp. column) load that was necessary to compute this tile. Solid lines are fetches while dotted lines | 37 |

| 2.9  | are prefetches                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

| 2.10 | can be loaded in memory                                                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

|      | can be readed in memory.                                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

xviii LIST OF FIGURES

| 3.1  | Reverse-Cuthill-McKee ordering on a symmetric sparse matrix                              | 46         |

|------|------------------------------------------------------------------------------------------|------------|

| 3.2  | Data sharing among tasks that reach worst-case complexity for HFP                        | 52         |

| 3.3  | Flipping packages to improve HFP                                                         | 52         |

| 3.4  | HFP's processing order on a 2D matrix multiplication with $M=4$                          | 53         |

| 3.5  | Difference between HFP and HFP with <i>Ready</i> ordering on a 2D matrix multiplication  |            |

|      | with a single GPU                                                                        | 54         |

| 3.6  | Data dependencies on a 2D matrix multiplication                                          | 56         |

| 3.7  | Conventions used in experimental evaluation figures                                      |            |

| 3.8  | Results on the 2D matrix multiplication in real execution with 1 Tesla V100 GPU. Mem-    |            |

|      | ory limited to 500 MB                                                                    | 57         |

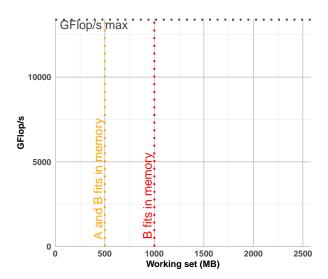

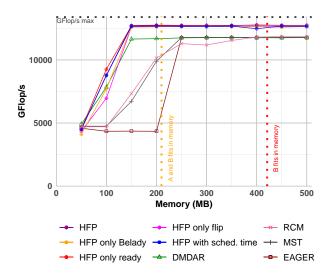

| 3.9  | Performance on the 2D matrix multiplication in real execution with 1 Tesla V100 GPU      |            |

|      | while varying the memory size                                                            | 58         |

| 3.10 | Visualization of RCM's processing order on the 2D matrix multiplication                  | 60         |

|      | Visualization of DMDAR's processing order on the 2D matrix multiplication                | 60         |

|      | Visualization of HFP's processing order on the 2D matrix multiplication                  | 61         |

|      | Results on the 3D matrix multiplication in real execution with 1 Tesla V100 GPU. Mem-    | -          |

|      | ory limited to 500 MB.                                                                   | 62         |

| 3.14 | Performance on the 3D matrix multiplication in simulation with the performance model     | ~ <b>_</b> |

|      | of 1 Tesla V100 GPU. Memory limited to 500 MB.                                           | 63         |

| 3.15 | Visualization of HFP's processing order on the 3D matrix multiplication                  | 64         |

|      | Performance on the task set of the Cholesky factorization in real execution with 1 Tesla |            |

|      | V100 GPU. Memory limited to 500 MB                                                       | 66         |

| 3.17 | Performance on the random task order from from 2D matrix multiplication in real exe-     |            |

|      | cution with 1 Tesla V100 GPU. Memory limited to 500 MB                                   | 67         |

| 3.18 | Visualization of the processing order on the random task order from from 2D matrix       |            |

|      | multiplication                                                                           | 67         |

| 3.19 | Performance on the randomized pairs with 2D inputs in real execution with 1 Tesla V100   |            |

|      | GPU. Memory limited to 500 MB                                                            | 69         |

| 3.20 | Performance on the sparse 2D matrix multiplication in real execution with 1 Tesla V100   |            |

|      | GPU. Memory limited to 500 MB                                                            | 70         |

|      | ·                                                                                        |            |

| 4.1  | Topology of the Gemini node                                                              |            |

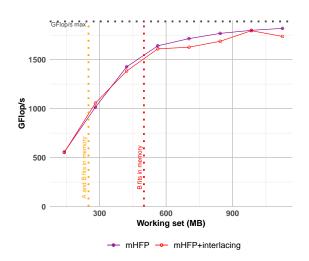

| 4.2  | Difference between mHFP and mHFP $^2$ on the 2D matrix multiplication with 3 GPUs        |            |

| 4.3  | Using interlacing with HFP                                                               | 80         |

| 4.4  | Simplified task flow within the STARPU runtime when using DARTS                          | 82         |

| 4.5  | Results of DARTS mutex policies on the 2D matrix multiplication with 4 Tesla V100        |            |

|      | GPUs                                                                                     | 86         |

| 4.6  | Results on the 2D matrix multiplication in real with 1 Tesla V100 GPU. Memory limited    |            |

|      | to 500 MB                                                                                | 87         |

| 4.7  | Performance on the 2D matrix multiplication in simulation with the performance models    |            |

|      | of 2 Tesla V100 GPUs                                                                     | 88         |

| 4.8  | Results on the 2D matrix multiplication in real with 2 Tesla V100 GPUs. Memory           |            |

|      | limited to 500 MB per GPU                                                                | 89         |

| 4.9  | HFP's ordering on the 2D matrix multiplication with 2 Tesla V100 GPUs                    | 90         |

|      | HFP's ordering on the 2D matrix multiplication with 8 Tesla V100 GPUs                    | 91         |

|      | DMDAR's ordering on the 2D matrix multiplication with 2 Tesla V100 GPUs                  | 92         |

| 4.12 | DARTS' ordering on the 2D matrix multiplication with 2 Tesla V100 GPUs                   | 94         |

LIST OF FIGURES xix

| 4.13       | Performance on the 2D matrix multiplication in real with 4 Tesla V100 GPUs. Memory limited to 500 MB per GPU.                       | 95  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.14       | Performance on the 2D matrix multiplication with randomized task order in real with 2                                               | )3  |

|            | Tesla V100 GPUs. Memory limited to 500 MB per GPU                                                                                   | 95  |

| 4.15       | Performance on the 3D matrix multiplication in simulation with the performance models                                               |     |

|            | of 4 Tesla V100 GPUs. Memory limited to 500 MB per GPU                                                                              | 96  |

| 4.16       | Performance on the task set of the Cholesky factorization in real with 4 Tesla V100                                                 |     |

| 117        | GPUs. Memory limited to 500 MB per GPU                                                                                              |     |

| 4.17       | refromance on the sparse 2D matrix multiplication in fear with 4 festa v 100 GFOs                                                   | 90  |

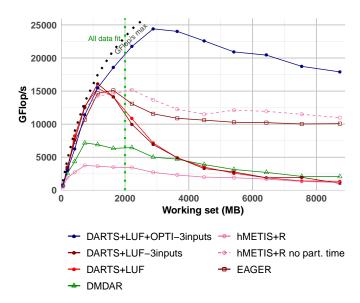

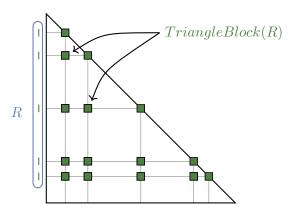

| 5.1        | Tiles computed by a triangle block in an iteration of the Cholesky factorization                                                    | 105 |

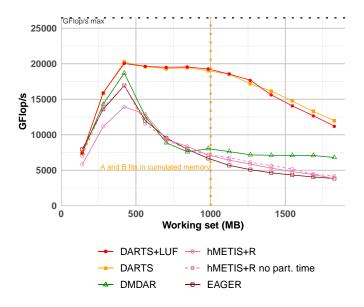

| 5.2        | Results on the Cholesky factorization with 1 Tesla V100 GPU. Memory limited to 2000                                                 | 100 |

| 5.2        | MB                                                                                                                                  | 106 |

| 5.3        | GPU                                                                                                                                 | 106 |

| 5.4        | DARTS' ordering on iterations 1 to 4 of the Cholesky factorization with 1 Tesla V100                                                | 100 |

|            | GPU                                                                                                                                 | 107 |

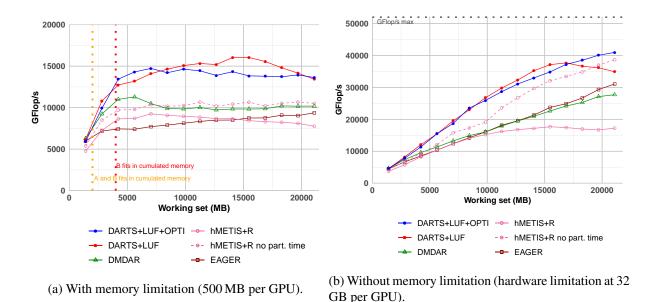

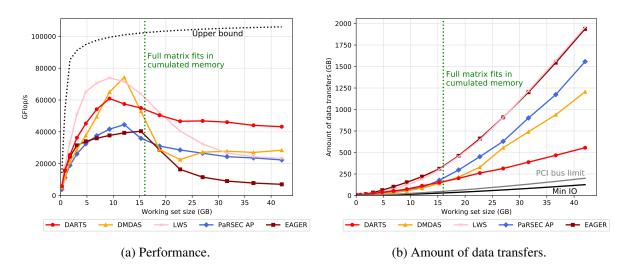

| 5.5        | Results on the Cholesky factorization with 8 Tesla V100 GPUs. Memory limited to                                                     |     |

|            | 2000 MB per GPU                                                                                                                     | 108 |

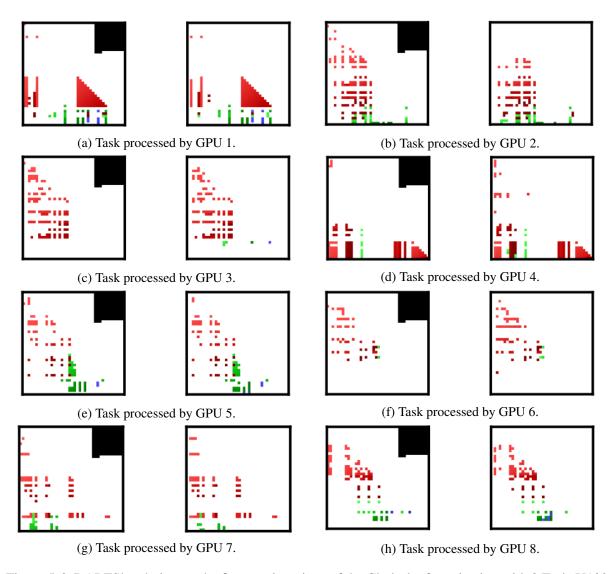

| 5.6        | DARTS' ordering on the first two iterations of the Cholesky factorization with 8 Tesla                                              |     |

| <i>-</i> 7 | V100 GPUs                                                                                                                           | 109 |

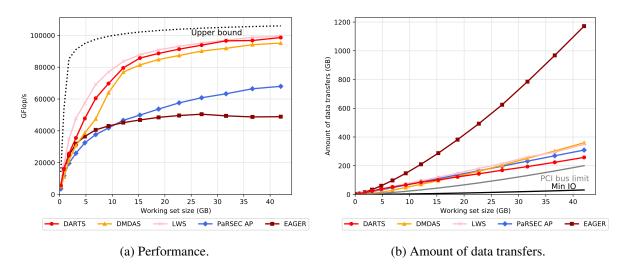

| 5.7        | Results on the Cholesky factorization with 8 Tesla V100 GPUs. Hardware limitation of each GPU memory at 32 GB                       | 110 |

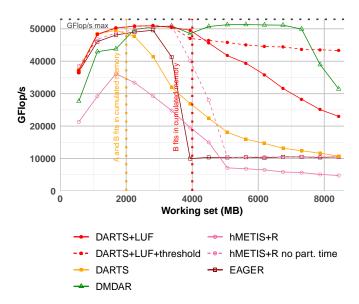

| 5.8        | Results on the LU factorization with 4 Tesla V100 GPUs. Memory limited to 2000 MB                                                   | 110 |

| 2.0        | per GPU                                                                                                                             | 111 |

| 5.9        | Results on the LU factorization with 1 Tesla V100 GPU. Hardware memory limitation                                                   |     |

|            | at 32 GB                                                                                                                            | 112 |

| 5.10       | Performance on the 3D matrix multiplication with Tesla V100 GPUs. Memory limited                                                    |     |

| C 11       | to 2000 MB.                                                                                                                         | 113 |

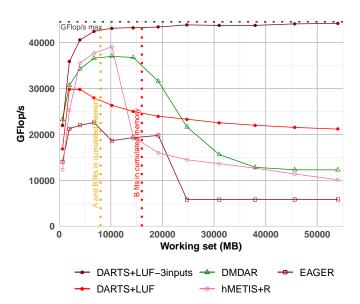

| 5.11       | Performance on the 3D matrix multiplication in simulation with the performance models of Tesla V100 GPUs. Memory limited to 2000 MB | 114 |

| 5 12       | Results on the LU factorization with an AMD EPYC 7642 CPU. Memory limited to                                                        | 114 |

| 3.12       | 2000 MB                                                                                                                             | 115 |

|            |                                                                                                                                     |     |

| 6.1        | Platform representation.                                                                                                            | 122 |

| 6.2        | Methodology followed to schedule and evaluate jobs from a specific week while avoiding edge effects                                 | 128 |

| 6.3        | Results on the workload of week 40.                                                                                                 |     |

| 6.4        | Stretch times of each user session from week 40 compared to FCFS                                                                    |     |

| 6.5        | Results on the workload of week 43                                                                                                  |     |

| 6.6        | Stretch times of each user session from week 43 using LEA compared to FCFS                                                          | 133 |

| 6.7        | Results without backfilling on all evaluated weeks                                                                                  |     |

| 6.8        | Results with backfilling on all evaluated weeks                                                                                     | 134 |

### Introduction

CIENTISTS are constantly striving for improved performance in their research applications, whether for enhancing accuracy or for tackling larger problems. For instance in domains such as weather forecasting, earthquake prediction or airflow simulation, significant computing power is required to achieve accurate results. All of the above applications are also highly dependent on large amounts of input data. The significance of computing power and memory requirements in modern applications is such that dedicated machines called supercomputers have become a necessity. With supercomputers came the field of High Performance Computing (HPC), which focuses on optimizing their utilization to maximize their capabilities. A well-known reality in HPC is that there has always been an intrinsic connection between the computing power of supercomputers and their memory.

Since ENIAC [70], the first programmable electronic computer built in 1945, dealing with memory has always been a constraint. The memory then consisted of 18 000 vacuum tubes, and it took 36 of them to store a single decimal number. Vacuum tubes required so much energy that several of them burned out almost every day, resulting in a non-functioning computer half the time. The most critical part when running the computer was data storage.

Throughout technological progress, the need for effective memory management remained relevant. For example, we can mention the Cray X-MP computer [41], released in 1983 to be the world's fastest computer. It consisted of four CPUs with a shared memory of 64 megabytes and could achieve a peak performance of almost 1 gigaflop/s, i.e.,  $10^9$  floating-point operations per seconds. A dataset larger than the CPUs memory required to transfer data from a hard drive through a cable with a limited bandwidth of a few megabytes per second. Therefore, it was important to manage how and when the data was accessed in order to avoid computational slowdowns.

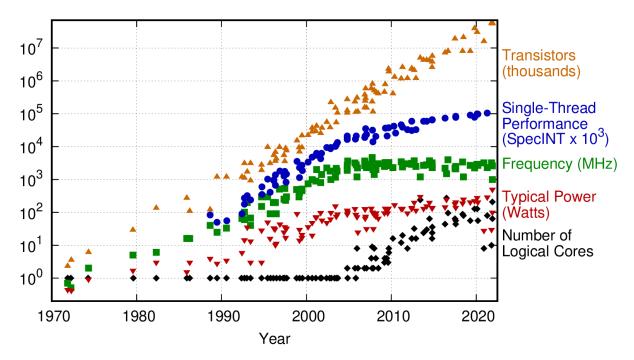

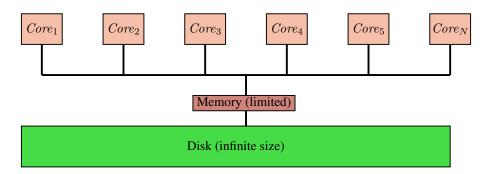

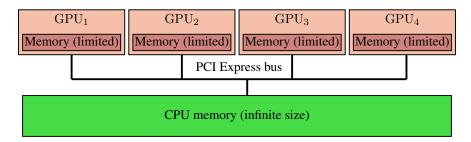

The last trend from the past decade is to leverage GPUs in addition to CPUs, to achieve unprecedented computing speed. Since 2022, the Frontier supercomputer [53], thanks to the use of more than 37 000 GPUs, is the most powerful machine in the world, with an achieved performance of 1 exaflop/s, i.e.,  $10^{18}$  floating-point operations per seconds. GPUs are fast and massively parallel but embed only relatively limited memory. With users trying to solve larger systems, it becomes common to encounter situations where all the input data of the problem cannot fit into the memory of the computing units. For GPUs, this means transferring data from a CPU memory using a bus with limited bandwidth. While they have a computing power on the order of thousands of gigaflop/s, the bus can typically exhibit a bandwidth on the order of a dozen thousands of megabyte/s. This ratio of 100 is a perfect example of the widening gap between computing speed and communication bandwidth. This is also accompanied by a decrease in memory per gigaflop/s, which means that problems cannot be solved by fitting all the input data into memory. This gap is a performance bottleneck and motivates HPC researchers to work on optimizing memory management techniques to unleash the full potential of supercomputers.

2 INTRODUCTION

In this thesis, we aim to fill this gap by answering the following problem: *How to minimize the execution time of an application whose dataset is larger than the memory of the processing units being used?* One possible answer is to improve the hardware. However, the addition of more memory is expensive and not a permanent solution: if the dataset gets larger and larger, one cannot add memory indefinitely. Adding more buses to enhance the hardware can be an option for improving performance. However, this is difficult because buses are expensive, consume a lot of energy, and take up space in an already physically limited compute node.

Our proposed answer is more generic and relies on improving the software of a runtime system. Generic software optimizations can be applied to any hardware and are thus a complementary goal to hardware improvements. To harness the power of complex heterogeneous computing platforms, it has become very common to use task-based programming, i.e. to express the application computation as a Directed Acyclic Graph (DAG), and let a dynamic runtime system manage the execution of the task graph over such distributed and heterogeneous platforms. The burden of allocating data in memory, choosing task processing order and mapping them is thus offloaded from the application programmer to the runtime system, in the form of a task scheduling problem. Since the runtime system handles both data and tasks, this provides an opportunity to build schedulers that minimize data movement, resulting in improved performance when memory is a constraint. Creating scheduling policies is a more general approach as it can be applied to any hardware or task-based application. Thus, our goal is to build a generic scheduler that partitions and orders tasks across one or more processing units with limited memory, and brings higher performance than current scheduling strategies. To achieve this goal, in Chapter 1 we first study the context in which this thesis took place, review related work, and detail how we intend to address the previously stated problem. Chapter 2 presents how we simplify and model the problem. Chapter 3 presents an algorithmic solution for static scheduling of independent tasks on a single processing unit. We then extend this solution to multiple processing units in Chapter 4 and propose a new dynamic scheduler. Chapter 5 describes improvements to our dynamic scheduler and experiments with dependent task sets. We take the opportunity to transfer the lessons learned from locality-aware scheduling to batch scheduling by introducing new algorithms for batch systems in Chapter 6. Each chapter is summarized below.

#### Chapter 1: Background and Literature Review

In this first chapter, we introduce the context in which this thesis was conducted: the need to execute linear algebra applications that does not fit in the memory of a processing unit. We also explain the motivation behind the approach chosen to solve this problem. Chapter 1 then elaborates on existing work on how this problem is addressed at different hardware levels (from cache to batch systems), before justifying our choice of positioning with regard to hardware proximity. Finally, we aim at bridging the gap between theoretical and practical scheduling.

#### Chapter 2: Problem Statement and Integration into a Runtime System

Chapter 2 expresses our stated problem with different theoretical models. The simplest model is based on the scheduling of independent tasks on a single processing unit with limited memory. Using this simplification, we prove the optimality of an eviction policy and demonstrate the complexity of our problem. We then complexify our model by adding multiple processing units, heterogeneous weights and task sets with dependencies. We also present STARPU, which is the runtime we used to implement our algorithms and conduct our experiments. To meet our needs, we introduce in STARPU the ability to use custom eviction policies as well as a new logging and visualization tool.

#### Chapter 3: Static Scheduling for a Single Processing Unit [R1, IP1, W1, J1]

A first algorithmic solution is provided by considering a packing problem, which we prove to be NP-complete. From the packing problem, we developed a scheduler called Hierarchical Fair Packing (HFP), which groups together tasks sharing data. To evaluate it, we adapt two methods from the literature that we believe may be relevant to our problem. The three mentioned strategies are implemented into the STARPU runtime. We experimentally evaluate the three methods along with a baseline and a state-of-the-art-runtime scheduler using variants of matrix multiplication and subsets of the Cholesky factorization. Chapter 3 discusses the results of experimental evaluations, with the help of the visualization tool presented in the previous chapter.

#### Chapter 4: Harnessing the Power of Multiple GPUs [IP2, C1]

While the previous chapter used a single processing unit, Chapter 4 focuses on the challenges of task-based scheduling on multiple processing units, each with its own limited memory. The chapter begins with a description of the used computing node. This description emphasizes the importance of spatial locality in a setting with multiple local memories by showing how the state-of-the-art runtime scheduler exploits such an architecture. We then introduce a graph partitioner, which we adapted to our problem by extending it with task-stealing methods. We then discuss how the HFP scheduler is adapted into a partitioning and ordering strategy by adding load-balancing and task-stealing to the strategy. We also introduce a new dynamic strategy called DARTS (Dynamic Data-Aware Reactive Task Scheduling), also implemented in STARPU. DARTS' intuition is to consider data locality before task allocation: it uses the state of the processing unit's memory to choose which data should be loaded to increase data reuse. To illustrate the performance of our schedulers, the chapter presents experimental results on different variants of matrix multiplication and subsets of the Cholesky factorization.

#### Chapter 5: Dynamic Scheduling for Task Graphs [N1, P1, R3]

This chapter focuses on the problem of scheduling task sets with dependencies on multiple processing units with limited memory. We describe existing algorithms that are widely used in runtime systems: a locality work stealing policy and a scheduler from the PaRSEC runtime. Based on the version of DARTS presented in the last chapter, we rebuilt it to favor fast data transfer, deal with dependencies, and include priorities in its decision making. We also worked on reducing the computational complexity of DARTS. To demonstrate the effectiveness of these scheduling techniques, the chapter presents studies on GEMM, the Cholesky and LU factorizations, using one or more GPUs as well as CPU cores.

#### Chapter 6: Leveraging Locality for Batch Schedulers [R2]

The work presented in this chapter was conducted as part of a research collaboration with Elisabeth LARSSON and Carl NETTELBLAD, during a three-month stay at Uppsala University in Sweden. We adapted our study to meet their specific research needs while keeping the focus on locality-aware scheduling under memory constraints. Uppsala University operates a high-performance computing platform that is used by researchers to submit highly data-dependent workloads. These workloads are jobs that require input files of multiple gigabytes to be loaded prior to computation. Traditional batch schedulers are generally not designed to handle data-intensive workloads. With those workloads, the load times can become significant, increasing the wait time for all jobs. Therefore, in Chapter 6 we propose to model the benefits of reusing data loads between successive jobs. We developed a batch simulator and introduce new batch schedulers that add such data reuse to the scheduling balance. By tracking which

4 INTRODUCTION

data is loaded on which node for the scheduled jobs, they are able to significantly reduce data loads, thereby improving both resource utilization and user satisfaction. We evaluate these algorithms by using traces of actual job submissions observed on the Uppsala University cluster and study the performance obtained after scheduling nearly 2 million jobs.

| -       |  |

|---------|--|

| Chapter |  |

# **Background and Literature Review**

| Contents |         |                                                                   |    |

|----------|---------|-------------------------------------------------------------------|----|

| 1.1      | Conte   | xt                                                                | 6  |

|          | 1.1.1   | Three real-world examples                                         | 6  |

|          | 1.1.2   | Hardware will not save us                                         | 7  |

|          | 1.1.3   | but maybe software can                                            | 9  |

|          | 1.1.4   | What happens when the memory is full?                             | 9  |

|          | 1.1.5   | Problem statement                                                 | 10 |

| 1.2      | Relate  | ed works                                                          | 11 |

|          | 1.2.1   | Cache management                                                  | 11 |

|          | 1.2.2   | Partitioned global address space                                  | 12 |

|          | 1.2.3   | Solutions in runtime systems                                      | 12 |

|          | 1.2.4   | An out-of-core middleware                                         | 13 |

|          | 1.2.5   | Scheduling for distributed platforms                              | 14 |

|          | 1.2.6   | Out-of-core and communication-avoiding algorithms                 | 14 |

|          | 1.2.7   | Locality-aware mapping                                            | 15 |

|          | 1.2.8   | Locality-aware mapping and ordering                               | 15 |

| 1.3      | Positio | oning in the hardware hierarchy                                   | 15 |

| 1.4      | Bridgi  | ing the gap between theoretical scheduling and runtime schedulers | 17 |

CIENTIFIC RESEARCH involves complex applications that require substantial computational resources. As scientific datasets continue to grow exponentially in size, researchers face a critical challenge: how to efficiently execute applications whose data exceeds the memory capacity of modern supercomputers? This is the foundation of this thesis. The context provided in Section 1.1 details the main challenge that modern scientific applications face: data. It also outlines different paths that can be taken to deal with such a challenge. After extracting a problem statement from it, we describe in Section 1.2 existing solutions from related work. Then, we explain in Section 1.3 how we choose to address the stated problem at two different levels of the hardware/software stack: runtimes and batch systems. Finally, in Section 1.4, we delve into the underlying challenges of using theoretical studies to build applied schedulers that work in runtime systems.

#### 1.1 Context

Challenging and impactful problems are the driving factors of modern scientists. Examples of engaging and significant areas of study include weather forecasting, acoustic and airflow simulations and earth-quake prediction. These examples have three characteristics in common.

**Computational intensity:** These domains heavily rely on sophisticated computational models to simulate and understand complex physical processes. For instance, weather forecasting models simulate atmospheric conditions, acoustic simulations replicate sound propagation, and seismic models analyze earth movements. These models involve intricate mathematical models and require significant computational resources to produce accurate results.

**Solvable with linear algebra:** Linear algebra provides a fundamental mathematical framework that enables the representation and resolution of such mathematical models.

**Data intensive:** All of these examples require the processing of large amounts of data. These datasets consist of measurements, observations, or simulated models with data volumes that can sometimes reach thousands of gigabytes.

We can point to three real-world examples that are impactful, computational intensive, rely on the resolution of large linear algebra applications, and require a large amount of input data.

#### 1.1.1 Three real-world examples

First, seismic tomography. It is a technique used in geophysics to create images of the Earth's subsurface structures by analyzing seismic waves. Seismic tomography plays a critical role in the assessment and prediction of natural hazards. It is also used to monitor volcanic activity. The recorded seismic data used as input is processed, typically reduced to solving a linear system such as the QR factorization, as shown in [27]. In this same paper, the authors state that the resolution matrix with  $267\,520\times267\,520$  elements requires over  $200\,\mathrm{GB}$  of memory. The more collected data, the better the resolution and accuracy of the resulting subsurface model. Therefore, seismic tomography requires large inputs, is useful to the masses, and is resolved by linear algebra.

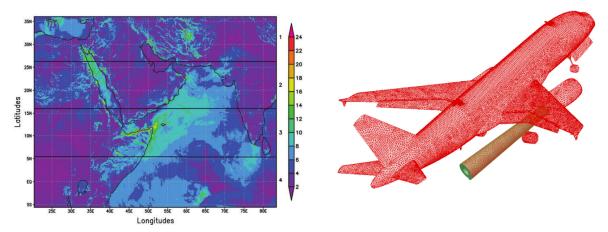

Second, geostatistics. It is a field of science where scientists try to accurately model and predict environmental phenomena. For example, some scientists use past wind speed measurements as inputs and aim to output accurate wind speed predictions for the coming days. An example of wind speed data used is shown in Figure 1.1a. This is important because wind speed has an impact on various sectors of activity, such as the energy production of a wind farm or the planning of construction activities.

1.1. CONTEXT

- (a) Example of wind speed data used for geostatistics. Figure from [2].

- (b) Example of discretization used for acoustic simulations. Figure from [10].

Figure 1.1: Examples of datasets used for applications with dense linear algebra as the main computation phase.

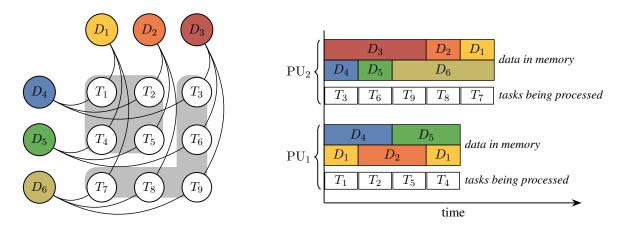

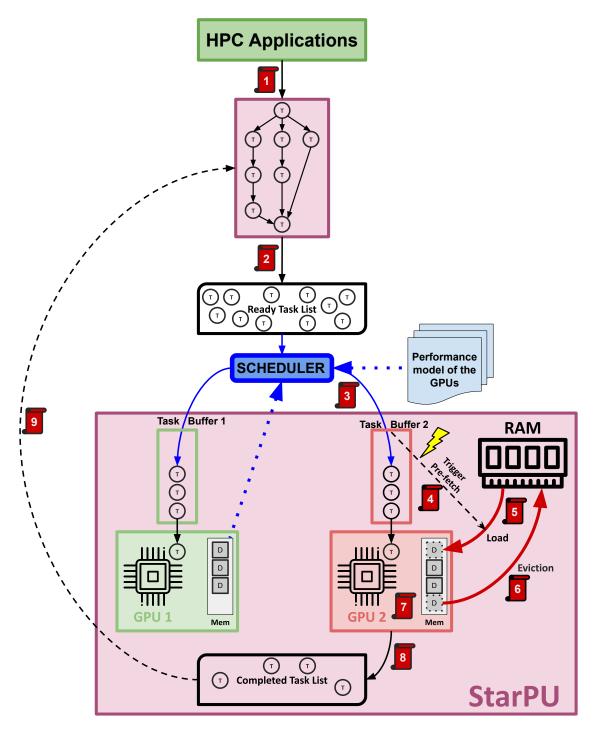

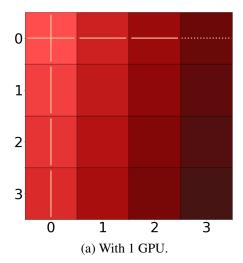

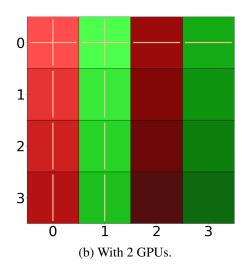

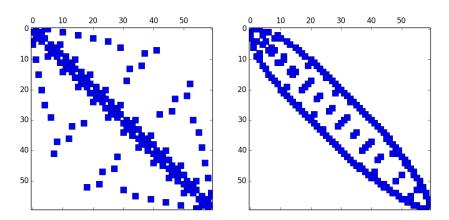

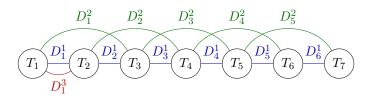

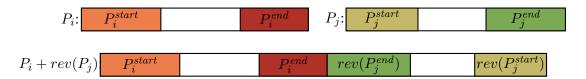

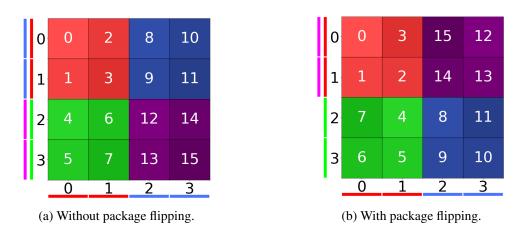

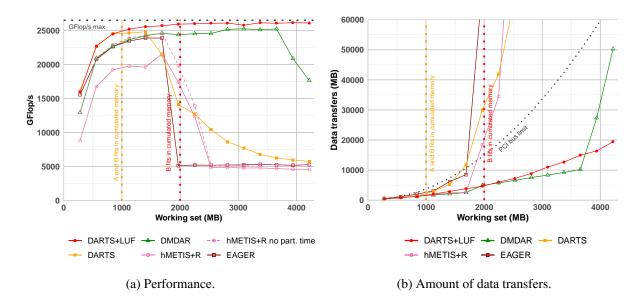

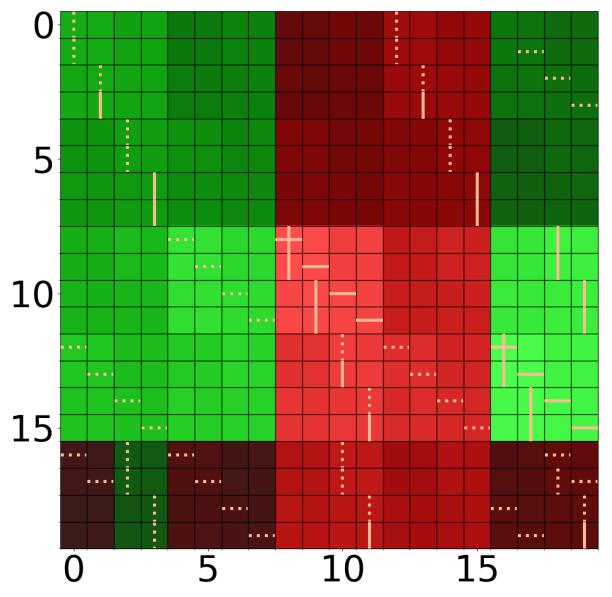

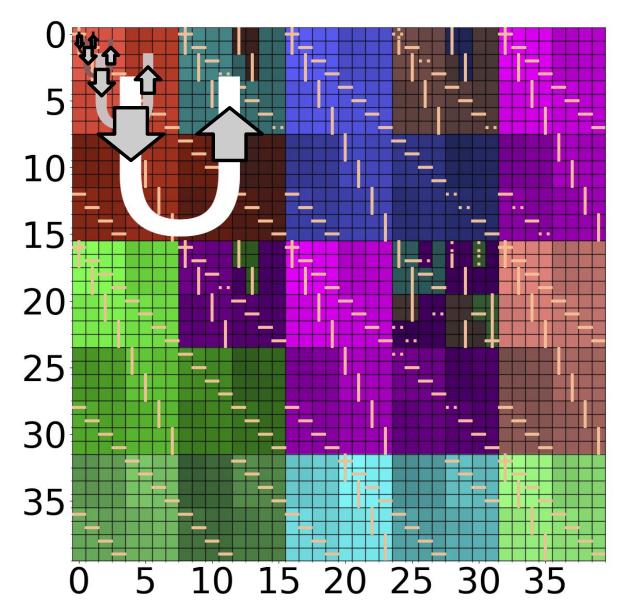

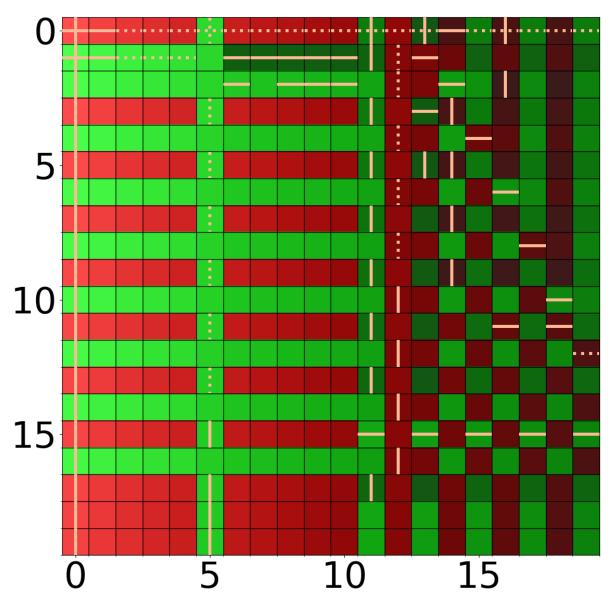

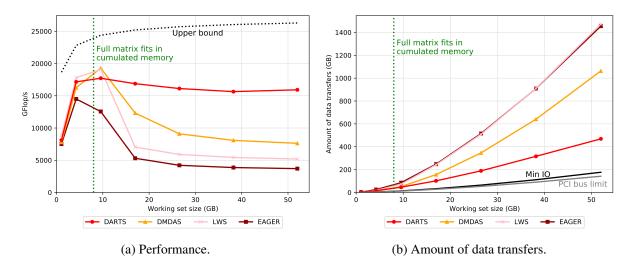

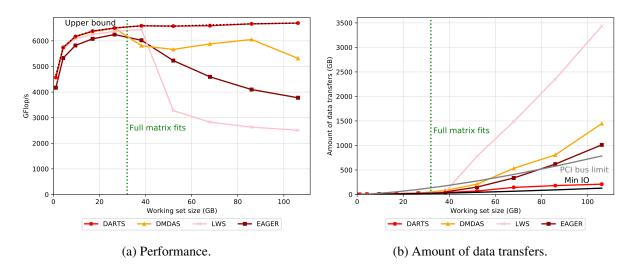

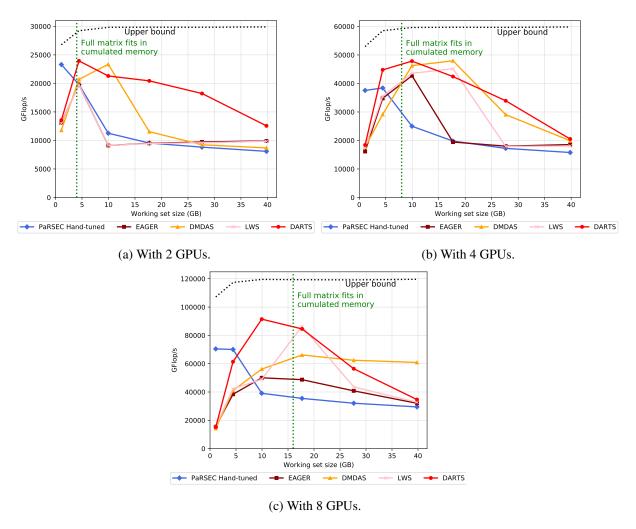

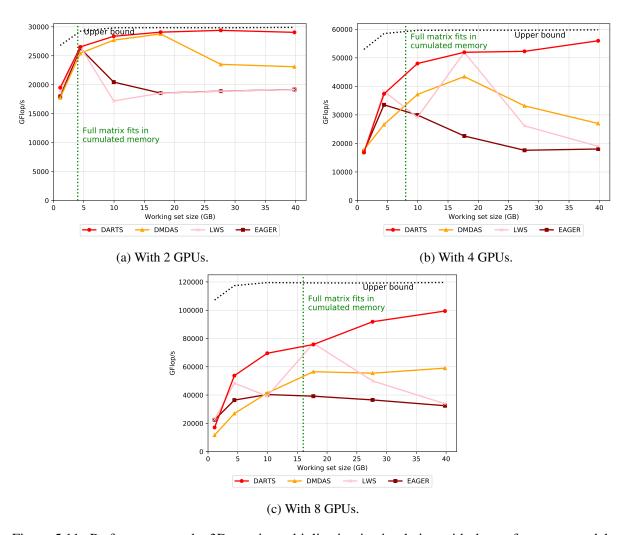

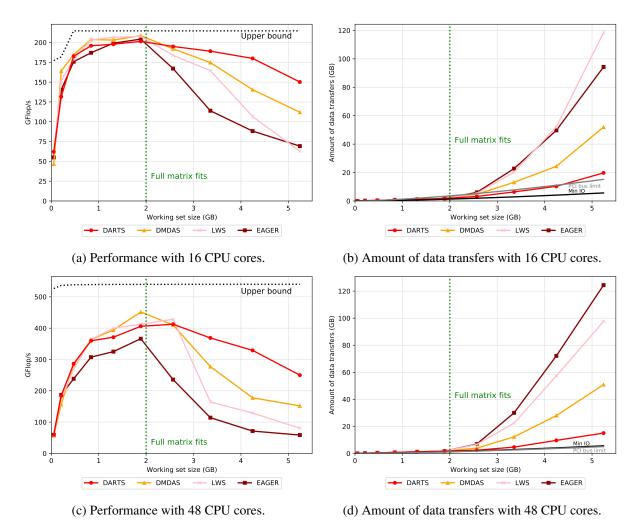

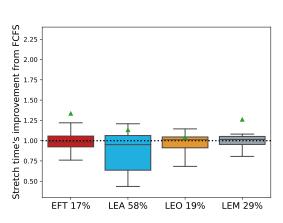

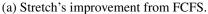

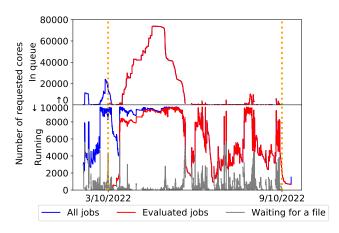

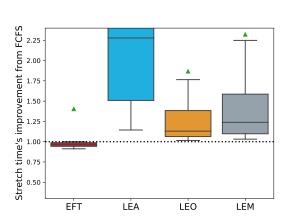

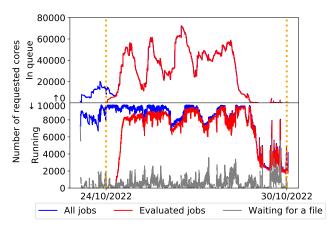

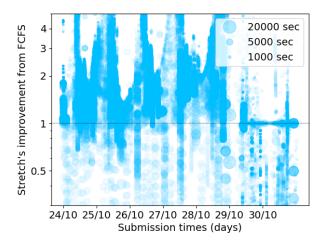

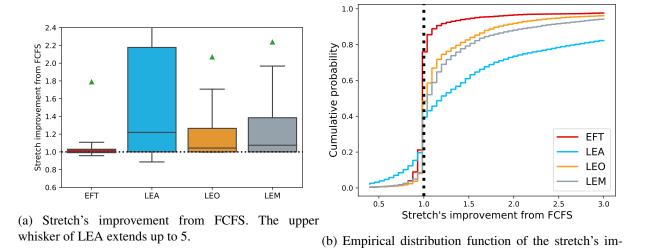

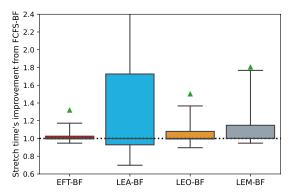

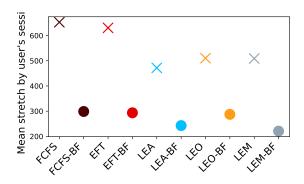

The EXAGEOSTAT software [1] is able to process such forecasts. In the case of wind prediction, EXAGEOSTAT uses large dense symmetric matrices that are solved using the Cholesky factorization [2]. They observed that they needed to move 3032 GB of data to produce the expected prediction.