# Methods and Tools for the Integration of Formal Verification in Domain-Specific Languages

Faiez Zalila

#### ► To cite this version:

Faiez Zalila. Methods and Tools for the Integration of Formal Verification in Domain-Specific Languages. Modeling and Simulation. Institut National Polytechnique De Toulouse, 2014. English. NNT: . tel-04261614v1

# HAL Id: tel-04261614 https://theses.hal.science/tel-04261614v1

Submitted on 3 Oct 2016 (v1), last revised 27 Oct 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Institut National Polytechnique de Toulouse (INP Toulouse)

Présentée et soutenue le Mardi 09/12/2014 par : FAIEZ ZALILA

Methods and Tools for the Integration of Formal Verification in Domain-Specific Languages

#### JURY

| M. Benoît COMBEMALE     | Maître de conférences, IRISA         | Examinateur            |

|-------------------------|--------------------------------------|------------------------|

| M. Xavier CRÉGUT        | Maître de conférences, INPT          | Encadrant scientifique |

| M. PIERRE-ETIENNE MORE. | AU Professeur, École des Mines Nancy | Rapporteur             |

| M. HASSAN MOUNTASSIR    | Professeur, UFC                      | Rapporteur             |

| M. MARC PANTEL          | Maître de conférences, INPT          | Encadrant scientifique |

| M. François VERNADAT    | Professeur, INSA de Toulouse         | Président du Jury      |

#### École doctorale et spécialité :

*MITT : Domaine STIC : Sureté de logiciel et calcul de haute performance* **Unité de Recherche :**

Institut de Recherche en Informatique de Toulouse (IRIT - UMR 5505) Directeur(s) de Thèse : Prof. Yamine AIT-AMEUR

#### **Rapporteurs** :

Prof. Pierre-Etienne MOREAU et Prof. Hassan MOUNTASSIR

# Remerciements

La réalisation d'une thèse est un travail qui nécessite beaucoup d'ambition, d'enthousiasme et de patience. En effet ce travail n'aurait jamais pu être réalisé sans le soutien d'un grand nombre de personnes.

Je tiens à remercier en premier lieu mes chers encadrants Marc Pantel et Xavier Crégut pour la confiance qu'ils m'ont accordée en acceptant d'encadrer mon stage de Master Recherche et ce travail doctoral.

J'étais vraiment chanceux d'être entouré par l'humanité, la gentillesse et la grande culture générale et scientifique de Marc Pantel. Je le remercie infiniment pour sa compréhension, son investissement et sa disponibilité de jour comme de nuit.

Un éternel merci à Xavier Crégut. Merci pour ta disponibilité, ton écoute, ta sympathie, tes conseils et la justesse de tes critiques qui ont guidé mes réflexions et qui ont fait de cette période une formation à la recherche très intéressante et l'objet d'un travail intense. Pour tout cela je vous suis infiniment redevable.

Merci à Yamine Ait-Ameur qui a accepté d'être mon directeur de thèse.

Je remercie Pierre-Etienne Moreau et Hassan Mountassir pour m'avoir fait l'honneur d'être rapporteurs de cette thèse. Je suis honoré pour l'intérêt qu'ils ont porté à ce travail.

Mes vifs remerciements à François Vernadat et Benoît Combemale qui ont bien accepté d'être examinateurs de cette thèse. Je leur exprime ma profonde reconnaissance d'être des membres du jury.

Je tiens à remercier tous les membres du laboratoire IRIT et l'ensemble du personnel de l'IRIT pour leur assistance administrative et logistique ainsi que pour leur sympathie et je pense particulièrement à nos chères secrétaires à Sylvie Eichen, Sylvie Armengaud-Metche et Audrey Cathala.

J'ai une pensée également pour tous les membres de l'équipe ACADIE et toutes les personnes avec qui j'ai partagé mon bureau: Florent, Arnaud, et Ning.

Mes vifs remerciements vont également à tous les amis ceux qui sont en Tunisie et qui m'encouragent toujours, ou que j'ai connu ici en France.

Je dédie cette thèse à mes parents pour leur soutien et leur encouragement à ma sœur et son mari pour leurs conseils et aides et à ma fiancée pour avoir supporté mon stress.

#### Faiez Zalila

# MÉTHODES ET OUTILS POUR L'INTÉGRATION DE LA VÉRIFICATION FORMELLE POUR LES LANGAGES DÉDIÉS

#### Résumé \_\_\_\_\_

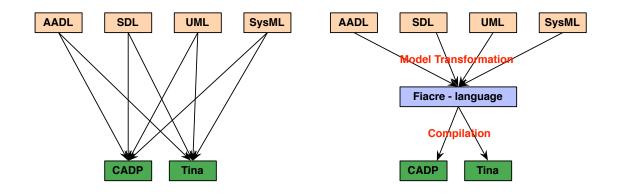

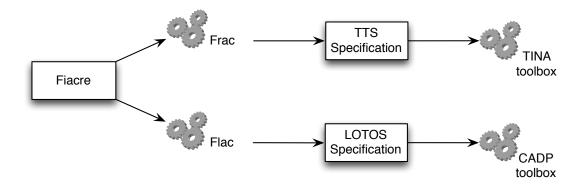

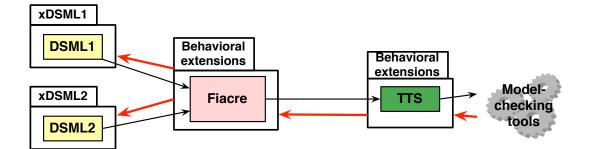

Les langages dédiés de modélisation (DSMLs) sont de plus en plus utilisés dans les phases amonts du développement des systèmes complexes, en particulier pour les systèmes critiques embarqués. L'objectif est de pouvoir raisonner très tôt dans le développement sur ces modèles et, notamment, de conduire des activités de vérification et validation (V&V). Une technique très utilisée est la vérification des modèles comportementaux par exploration exhaustive (*model-checking*) en utilisant une sémantique de traduction pour construire un modèle formel à partir des modèles métiers pour réutiliser les outils performants disponibles pour les modèles formels. Définir cette sémantique de traduction, exprimer les propriétés formelles à vérifier et analyser les résultats nécessite une expertise dans les méthodes formelles qui freine leur adoption et peut rebuter les concepteurs. Il est donc nécessaire de construire pour chaque DSML, une chaîne d'outils qui masque les aspects formels aux utilisateurs.

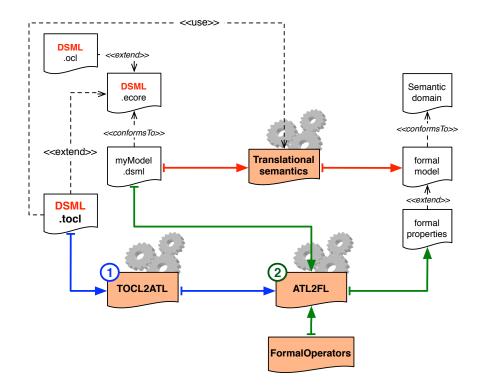

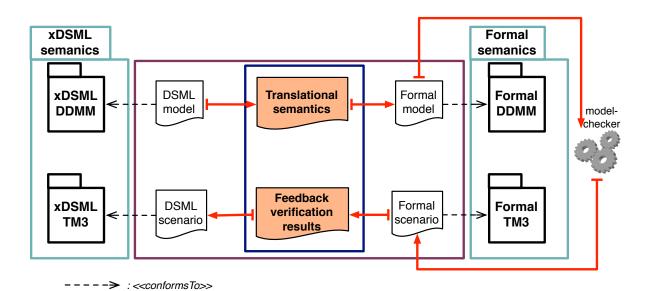

L'objectif de cette thèse est de faciliter le développement de telles chaînes de vérification. Notre contribution inclut 1) l'expression des propriétés comportementales au niveau métier en s'appuyant sur TOCL (Temporal Object Constraint Language), une extension temporelle du langage OCL; 2) la transformation automatique de ces propriétés en propriétés formelles en réutilisant les éléments clés de la sémantique de traduction; 3) la remontée des résultats de vérification grâce à une transformation d'ordre supérieur et un langage de description de correspondance entre le domaine métier et le domaine formel et 4) le processus associé de mise en œuvre.

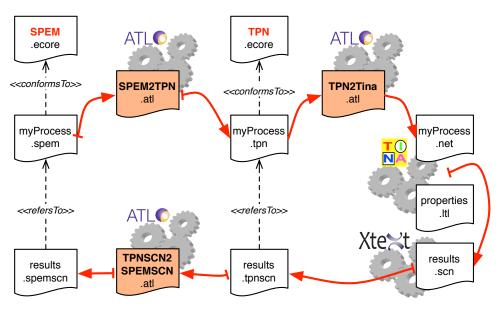

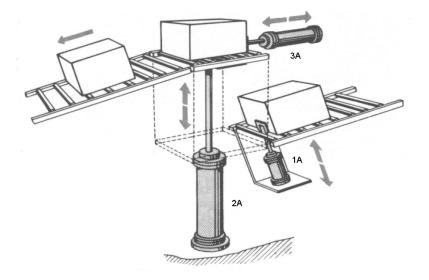

Notre approche a été validée par l'expérimentation sur un sous-ensemble du langage de modélisation de processus de développement SPEM, et sur le langage de commande d'automates programmables Ladder Diagram, ainsi que par l'intégration d'un langage formel intermédiaire (FIACRE) dans la chaîne outillée de vérification. Ce dernier point permet de réduire l'écart sémantique entre les DSMLs et les domaines formels.

**mots clés:** Ingénierie dirigée par les modèles (IDM), Langage dédié de modélisation (DSML), vérification et validation (V&V), Object Constraint Language (OCL), vérification formelle, vérification de modèle par exploration exhaustive, sémantique translationnelle, traçabilité, remontée de vérification

#### Institut de Recherche en Informatique de Toulouse - UMR 5505

#### Faiez Zalila

## METHODS AND TOOLS FOR THE INTEGRATION OF FORMAL VERIFICATION IN DOMAIN-SPECIFIC LANGUAGES

#### \_ Abstract \_\_\_\_\_

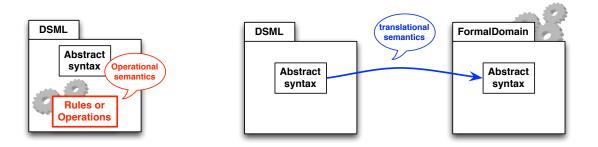

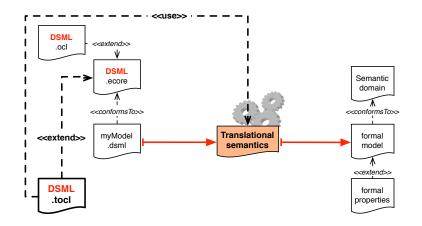

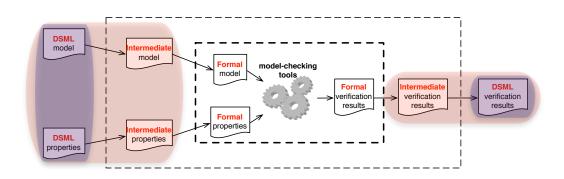

Domain specific Modeling Languages (DSMLs) are increasingly used at the early phases in the development of complex systems, in particular, for safety critical systems. The goal is to be able to reason early in the development on these models and, in particular, to fulfill verification and validation activities (V&V). A widely used technique is the exhaustive behavioral model verification using *model-checking* by providing a translational semantics to build a formal model from DSML conforming models in order to reuse powerful tools available for this formal domain.

Defining a translational semantics, expressing formal properties to be assessed and analysing such verification results require such an expertise in formal methods that it restricts their adoption and may discourage the designers. It is thus necessary to build for each DSML, a toolchain which hides formal aspects for DSML end-users.

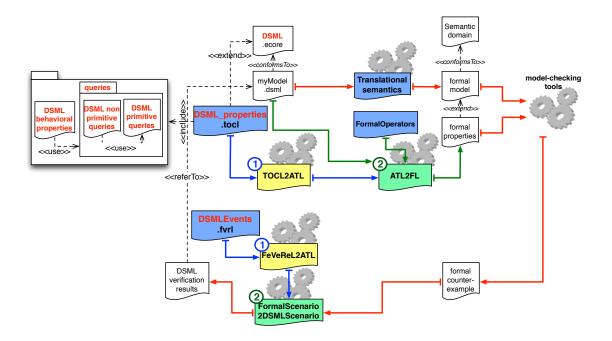

The goal of this thesis consists in easing the development of such verification toolchains. Our contribution includes 1) expressing behavioral properties in the DSML level by relying on TOCL (Temporal Object Constraint Language), a temporal extension of OCL; 2) An automated transformation of these properties on formal properties while reusing the key elements of the translational semantics; 3) the feedback of verification results thanks to a higher-order transformation and a language which defines mappings between DSML and formal levels; 4) the associated process implementation.

Our approach was validated by the experimentation on a subset of the development process modeling language SPEM, and on Ladder Diagram language used to specify programmable logic controllers (PLCs), and by the integration of a formal intermediate language (FIACRE) in the verification toolchain. This last point allows to reduce the semantic gap between DSMLs and formal domains.

**keywords:** Model Driven Engineering (MDE), Domain specific Modeling Language (DSML), verification and validation (V&V), Object Constraint Language (OCL), Formal verification, Model checking, Translational semantics, Traceability, Verification feedback.

#### Institut de Recherche en Informatique de Toulouse - UMR 5505

# Contents

| Re               | Remerciements<br>Introduction |                          |                                    |    |  |

|------------------|-------------------------------|--------------------------|------------------------------------|----|--|

| In               |                               |                          |                                    |    |  |

|                  | 0.1                           | Conte                    | xt and challenges                  | 5  |  |

|                  | 0.2                           | Descri                   | iption of the thesis contributions | 6  |  |

|                  | 0.3                           |                          | ne of this thesis                  | 7  |  |

| I                | Stat                          | te of th                 | e Art                              | 10 |  |

| 1                | Moo                           | Model-driven Engineering |                                    |    |  |

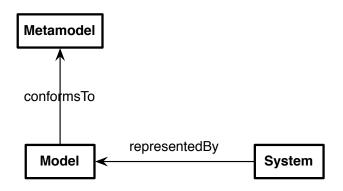

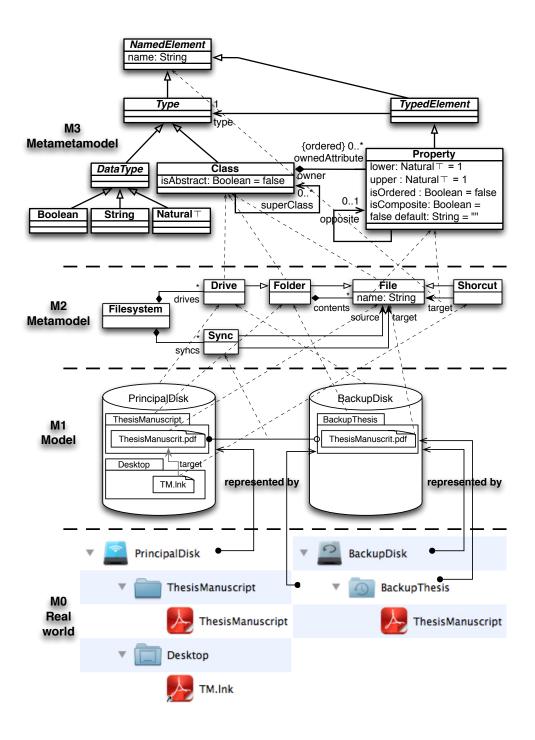

|                  | 1.1                           | Mode                     | l and Metamodel                    | 14 |  |

|                  | 1.2                           | Mode                     | l-driven Architecture              | 15 |  |

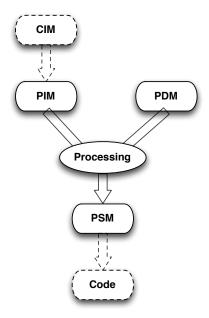

|                  |                               | 1.2.1                    | The MDA approach                   | 15 |  |

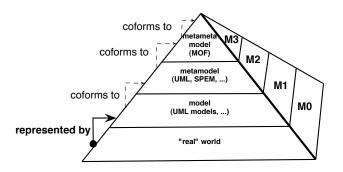

|                  |                               | 1.2.2                    | The MDA architecture               | 17 |  |

|                  | 1.3                           | Mode                     | l Transformation                   | 18 |  |

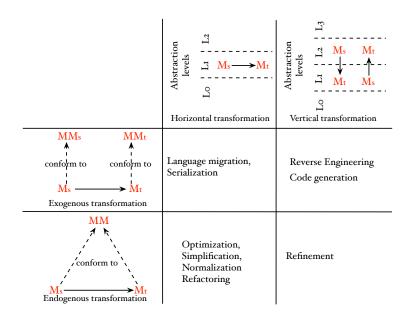

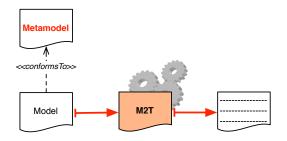

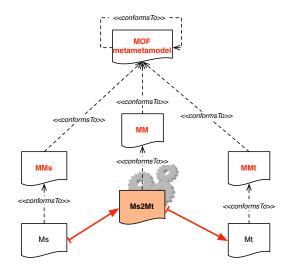

|                  |                               | 1.3.1                    | Model transformation types         | 19 |  |

|                  |                               | 1.3.2                    | Model transformation languages     | 21 |  |

| 2                | Dor                           | nain-sp                  | ecific Modeling Languages          | 24 |  |

|                  | 2.1                           | Differ                   | ent elements defining a DSML       | 26 |  |

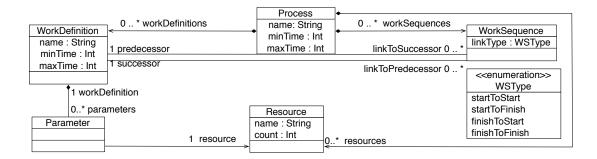

|                  |                               | 2.1.1                    | Abstract syntax of a DSML          | 27 |  |

|                  |                               | 2.1.2                    | Concrete syntax of a DSML          | 28 |  |

|                  |                               | 2.1.3                    | Behavioral semantics for a DSML    | 29 |  |

|                  | 2.2                           | Mode                     | l verification for DSMLs           | 31 |  |

| 3 SPEM as a DSML |                               | M as a                   | DSML                               | 34 |  |

|                  | 3.1                           | Verific                  | cation of SPEM models              | 35 |  |

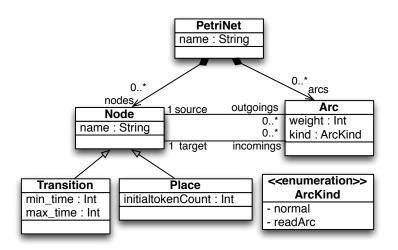

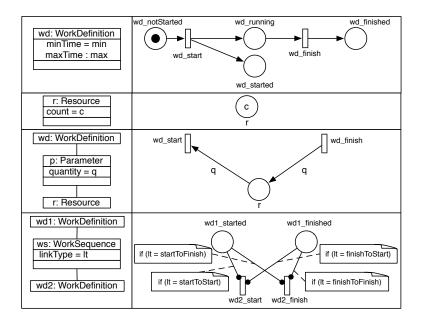

|         |                   | 3.1.1                                                  | Time Petri nets, SE-LTL and Tina toolbox                                                                                                                                                                                                                                                                                           | 36                                                                           |

|---------|-------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

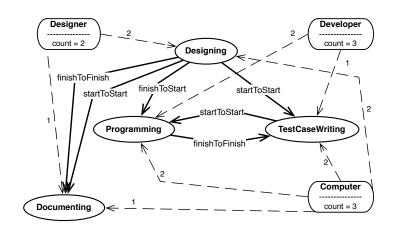

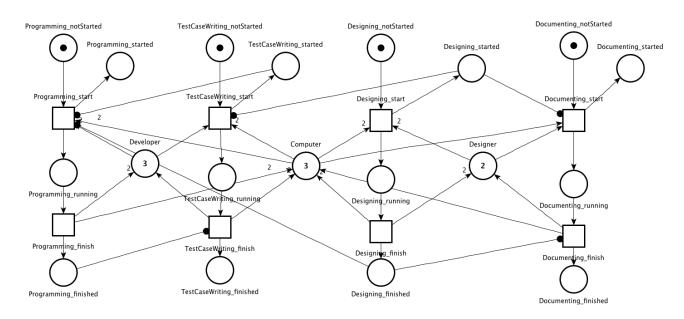

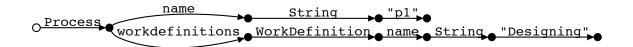

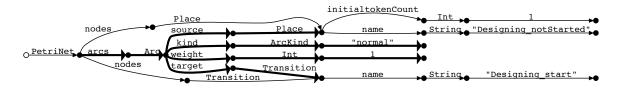

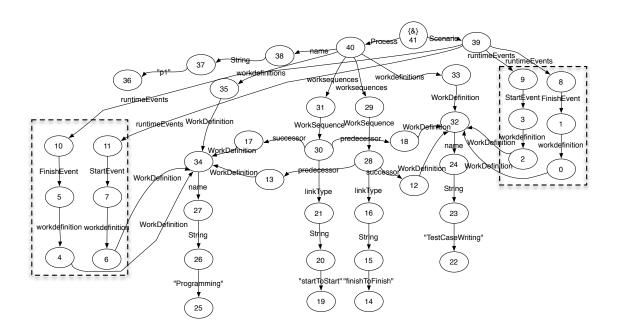

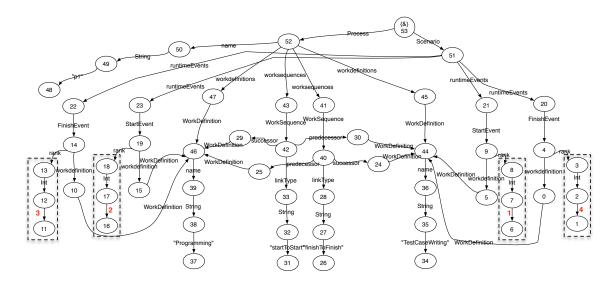

|         |                   | 3.1.2                                                  | Translational semantics of SPEM into Petri nets                                                                                                                                                                                                                                                                                    | 38                                                                           |

|         |                   | 3.1.3                                                  | Expressing and generating formal properties                                                                                                                                                                                                                                                                                        | 39                                                                           |

|         |                   | 3.1.4                                                  | Performing the formal verification                                                                                                                                                                                                                                                                                                 | 40                                                                           |

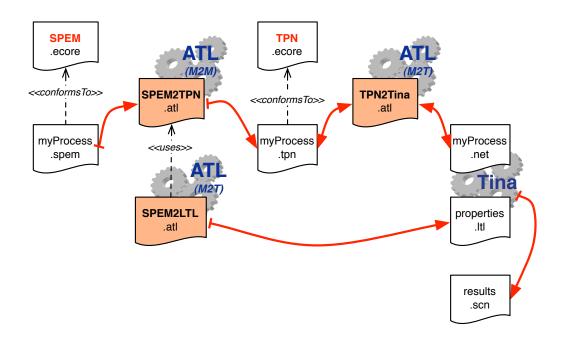

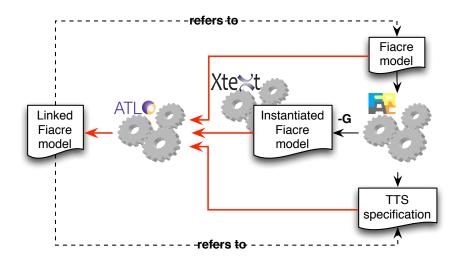

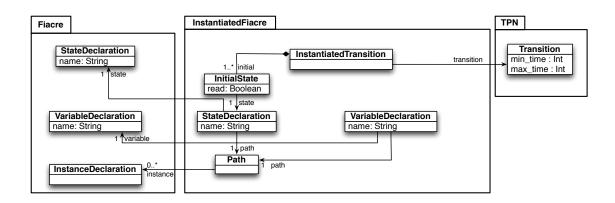

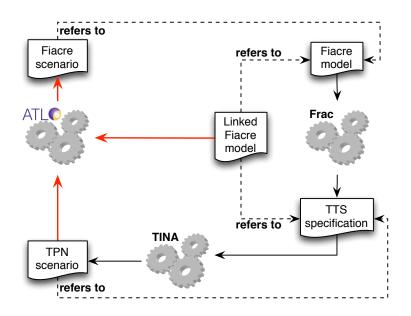

|         |                   | 3.1.5                                                  | Implementation of the approach                                                                                                                                                                                                                                                                                                     | 42                                                                           |

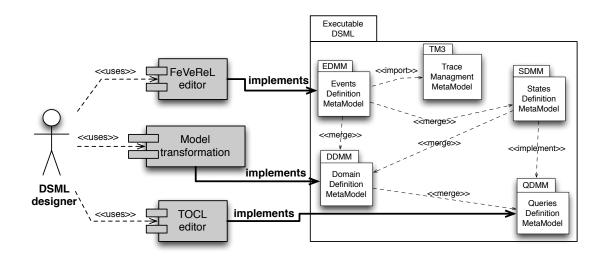

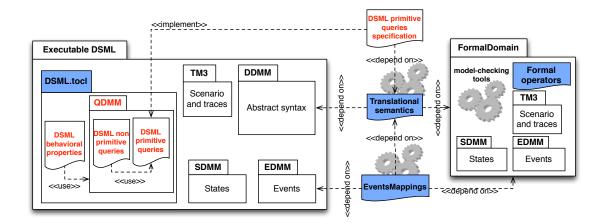

|         | 3.2               | Towar                                                  | ds the definition of an eXecutable DSML ( $xDSML$ )                                                                                                                                                                                                                                                                                | 43                                                                           |

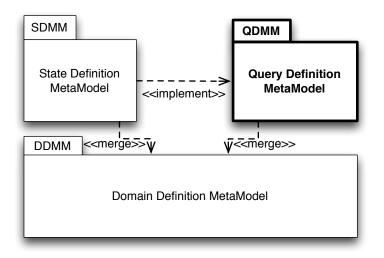

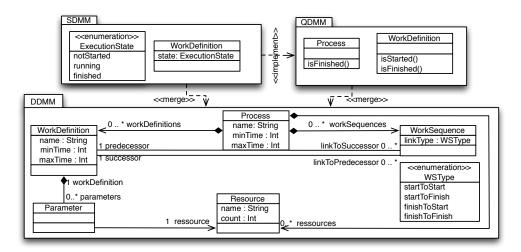

|         |                   | 3.2.1                                                  | The <i>Executable DSML pattern</i>                                                                                                                                                                                                                                                                                                 | 43                                                                           |

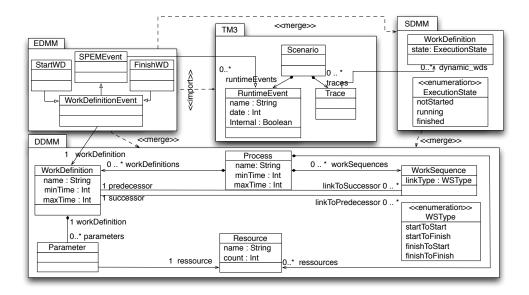

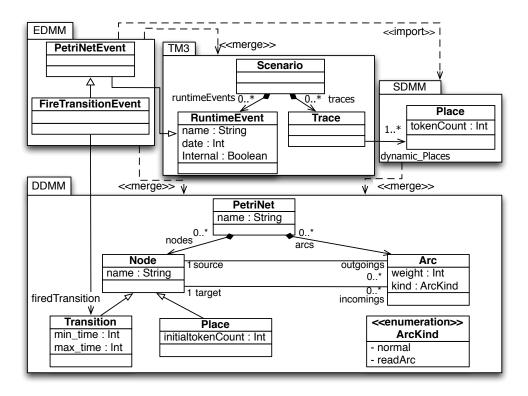

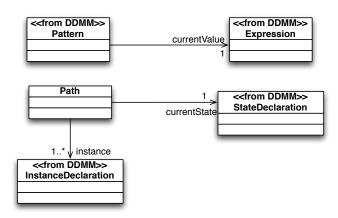

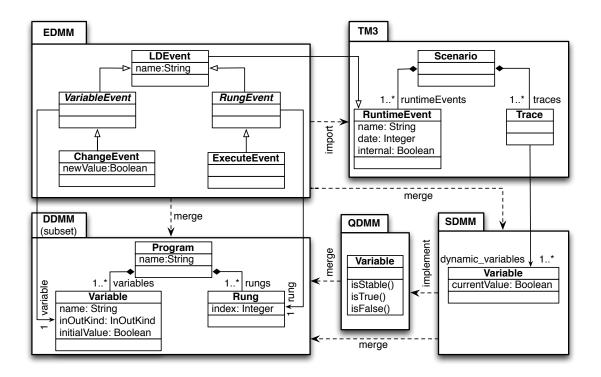

|         |                   |                                                        | 3.2.1.1 Domain Definition MetaModel (DDMM)                                                                                                                                                                                                                                                                                         | 44                                                                           |

|         |                   |                                                        | 3.2.1.2 State Definition MetaModel (SDMM)                                                                                                                                                                                                                                                                                          | 44                                                                           |

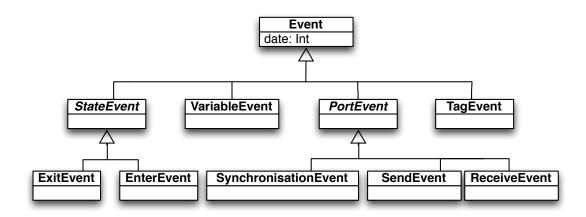

|         |                   |                                                        | 3.2.1.3 Event Definition MetaModel (EDMM)                                                                                                                                                                                                                                                                                          | 45                                                                           |

|         |                   |                                                        | 3.2.1.4 Trace Management MetaModel (TM3)                                                                                                                                                                                                                                                                                           | 45                                                                           |

|         |                   | 3.2.2                                                  | Application of the Executable DSML pattern to TPN                                                                                                                                                                                                                                                                                  | 46                                                                           |

|         | 3.3               | The ev                                                 | valuation of the approach                                                                                                                                                                                                                                                                                                          | 46                                                                           |

|         |                   | 3.3.1                                                  | Resolved MDE disadvantages                                                                                                                                                                                                                                                                                                         | 47                                                                           |

|         |                   | 3.3.2                                                  | Unresolved formal methods disadvantages                                                                                                                                                                                                                                                                                            | 48                                                                           |

|         | 3.4               | Goals                                                  |                                                                                                                                                                                                                                                                                                                                    | 49                                                                           |

|         |                   | 3.4.1                                                  | DSML end-user expectations                                                                                                                                                                                                                                                                                                         | 49                                                                           |

|         |                   | 0 4 0                                                  |                                                                                                                                                                                                                                                                                                                                    | 10                                                                           |

|         |                   | 3.4.2                                                  | DSML expert and designer expectations                                                                                                                                                                                                                                                                                              | 49                                                                           |

|         |                   | 3.4.2                                                  | DSML expert and designer expectations                                                                                                                                                                                                                                                                                              | 49                                                                           |

| II      | Co                | 3.4.2<br>ntribu                                        |                                                                                                                                                                                                                                                                                                                                    | 49<br>52                                                                     |

| II<br>4 |                   | ntribu                                                 |                                                                                                                                                                                                                                                                                                                                    |                                                                              |

|         |                   | ntribu<br>ressing                                      | tion                                                                                                                                                                                                                                                                                                                               | 52                                                                           |

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion<br>and verifying behavioral properties                                                                                                                                                                                                                                                                                        | 52<br>54                                                                     |

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion and verifying behavioral properties apression of behavioral properties                                                                                                                                                                                                                                                        | <b>52</b><br><b>54</b><br>56                                                 |

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion and verifying behavioral properties cpression of behavioral properties                                                                                                                                                                                                                                                        | <b>52</b><br><b>54</b><br>56<br>56                                           |

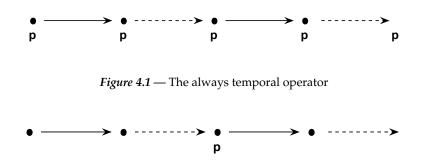

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion         and verifying behavioral properties         xpression of behavioral properties         The temporal extension of OCL         4.1.1.1         always operator                                                                                                                                                          | <b>52</b><br><b>54</b><br>56<br>56<br>57                                     |

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion and verifying behavioral properties apression of behavioral properties                                                                                                                                                                                                                                                        | <b>52</b><br><b>54</b><br>56<br>56<br>57<br>57                               |

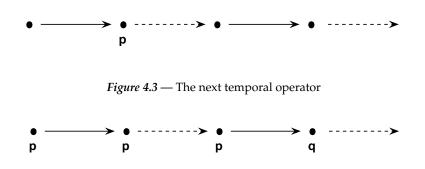

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion and verifying behavioral properties apression of behavioral properties                                                                                                                                                                                                                                                        | <b>52</b><br><b>54</b><br>56<br>56<br>57<br>57<br>57                         |

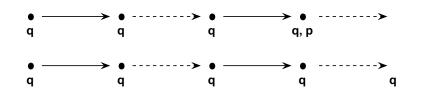

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | and verifying behavioral properties         and verifying behavioral properties         appression of behavioral properties         The temporal extension of OCL         4.1.1.1         always operator         4.1.1.2         eventually operator         4.1.1.3         next operator         4.1.1.4         until operator | <b>52</b><br><b>54</b><br>56<br>57<br>57<br>57<br>58                         |

|         | Expi              | <b>ntribu</b><br>ressing<br>The e×                     | tion<br>and verifying behavioral properties<br>corression of behavioral properties                                                                                                                                                                                                                                                 | <b>52</b><br><b>54</b><br>56<br>57<br>57<br>57<br>57<br>58<br>58             |

|         | Expi              | ntribu<br>ressing<br>The ex<br>4.1.1                   | tion<br>and verifying behavioral properties<br>spression of behavioral properties                                                                                                                                                                                                                                                  | <b>52</b><br><b>54</b><br>56<br>57<br>57<br>57<br>57<br>58<br>58<br>58       |

|         | Expi              | ntribu<br>ressing<br>The ex<br>4.1.1<br>4.1.2<br>4.1.2 | tion and verifying behavioral properties apression of behavioral properties The temporal extension of OCL 4.1.1.1 always operator 4.1.1.2 eventually operator 4.1.1.3 next operator 4.1.1.4 until operator 4.1.1.5 release operator 4.1.1.6 precedence operators The Query Definition MetaModel (QDMM) extension                   | <b>52</b><br><b>54</b><br>56<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58 |

|         | <b>Exp</b><br>4.1 | ntribu<br>ressing<br>The ex<br>4.1.1<br>4.1.2<br>4.1.2 | tion<br>and verifying behavioral properties<br>cpression of behavioral properties                                                                                                                                                                                                                                                  | 52<br>54<br>56<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>62         |

|    | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Relate                                                                                                               | d works                                                                                                      | 70                                                                                |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| 5  | Feed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dback v                                                                                                              | verification results                                                                                         | 72                                                                                |  |

|    | 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Defini                                                                                                               | ng a backward transformation                                                                                 | 74                                                                                |  |

|    | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The us                                                                                                               | se of bidirectional transformation                                                                           | 76                                                                                |  |

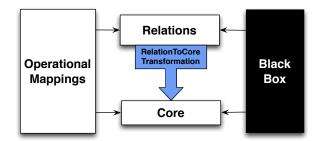

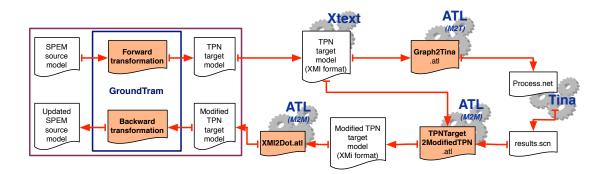

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.2.1                                                                                                                | Bidirectional Model Transformation with GROUNDTRAM                                                           | 76                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      | 5.2.1.1 Data Model                                                                                           | 77                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      | 5.2.1.2 Bidirectional Transformations                                                                        | 77                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.2.2                                                                                                                | Combining the <i>Executable DSML pattern</i> with the GROUNDTRAM framework                                   | 78                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.2.3                                                                                                                | Implementation                                                                                               | 80                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.2.4                                                                                                                | Synthesis and discussion                                                                                     | 81                                                                                |  |

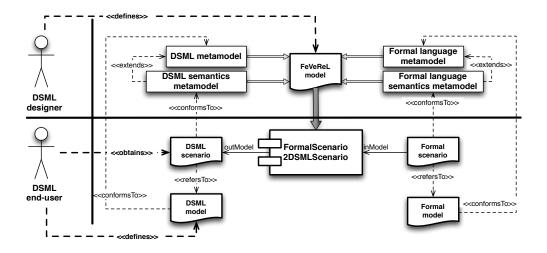

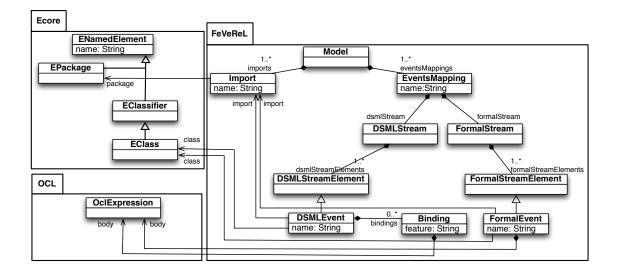

|    | 5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FEVE                                                                                                                 | REL: Feedback Verification Results Language                                                                  | 81                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.1                                                                                                                | Motivations                                                                                                  | 82                                                                                |  |

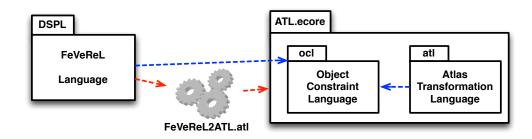

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.2                                                                                                                | Architecture of FEVEREL                                                                                      | 83                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.3                                                                                                                | Implementation of FEVEREL language                                                                           | 84                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5.3.4                                                                                                                | Syntaxes and semantics of FEVEREL                                                                            | 85                                                                                |  |

|    | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Relate                                                                                                               | d works                                                                                                      | 88                                                                                |  |

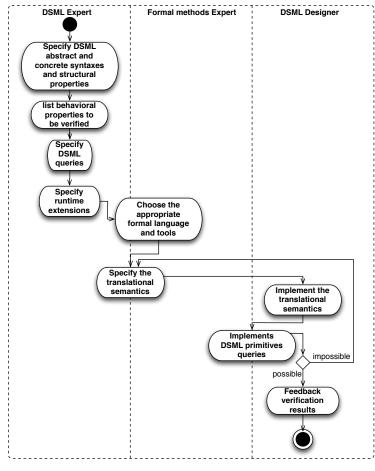

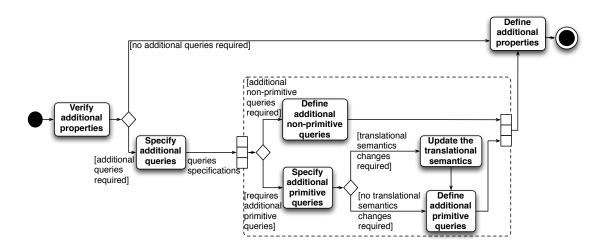

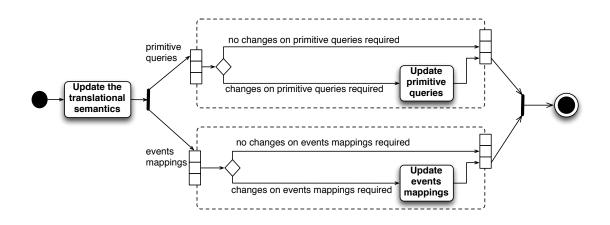

| 6  | Building a verification framework for an executable DSML 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                      |                                                                                                              |                                                                                   |  |

| 6  | Bui                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | lding a                                                                                                              | verification framework for an executable DSML                                                                | 90                                                                                |  |

| 6  | <b>Bui</b><br>6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U                                                                                                                    | <b>verification framework for an executable DSML</b><br>tecture of the verification framework for a new DSML | <b>90</b><br>92                                                                   |  |