## Property driven verification framework: application to real time property for UML MARTE software design $_{\rm Ning~Ge}$

#### ▶ To cite this version:

Ning Ge. Property driven verification framework: application to real time property for UML MARTE software design. Modeling and Simulation. Institut national polytechnique de Toulouse (INPT); Institut de Recherche en Informatique de Toulouse (IRIT), Université Paul Sabatier, 118 route de Narbonne, 31062 Toulouse cedex 9, 2014. English. NNT: . tel-04262123v1

#### HAL Id: tel-04262123 https://theses.hal.science/tel-04262123v1

Submitted on 11 Nov 2016 (v1), last revised 27 Oct 2023 (v3)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

#### En vue de l'obtention du

#### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

#### Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

#### Discipline ou spécialité :

Sureté de Logiciel et Calcul à Haute Performance

#### Présentée et soutenue par :

Mme NING GE le mardi 13 mai 2014

#### Titre:

PROPERTY DRIVEN VERIFICATION FRAMEWORK: APPLICATION TO REAL TIME PROPERTY FOR UML MARTE SOFTWARE DESIGN.

#### **Ecole doctorale:**

Mathématiques, Informatique, Télécommunications de Toulouse (MITT)

#### Unité de recherche :

Institut de Recherche en Informatique de Toulouse (I.R.I.T.)

#### Directeur(s) de Thèse :

M. MARC PANTEL

M. YAMINE AIT AMEUR

#### Rapporteurs:

M. FRÉDÉRIC MALLET, UNIVERSITE DE NICE SOPHIA ANTIPOLIS M. KAMEL BARKAOUI, CNAM PARIS

#### Membre(s) du jury :

M. FERHAT KHENDEK, UNIVERSITE CONCORDIA MONTREAL, Président M. FREDERIC BONIOL, INP TOULOUSE, Membre M. MARC PANTEL, INP TOULOUSE, Membre M. PHILIPPE DHAUSSY, ENSTA BRETAGNE, Membre M. SILVANO DAL ZILIO, LAAS TOULOUSE, Membre M. YAMINE AIT AMEUR, INP TOULOUSE, Membre

#### Acknowledgments

The work presented in this thesis has been completed in the ACADIE team in IRIT, with the financial support from the French Ministry of Industry through the ITEA OPEES project and the FUI P project. The experience as a Ph.D student is full of excitement and adventure. At the end moment, I wish to express my gratitude to my supervisors, colleagues and families.

First and foremost I offer my sincerest gratitude to my principal supervisor Marc Pantel for the continuous support of my Ph.D study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better supervisor and mentor for my Ph.D study. I offer the same gratitude to Yamine Aït Ameur for accepting to be the director of my thesis, and to Xavier Crégut for accepting to be cosupervisor of my thesis. Their good advice and support have been invaluable, for which I am extremely grateful.

I express the deepest appreciation to Kamel Barkaoui, professor at Cedric Cnam Paris, and Frédéric Mallet, associate professor (HDR) at Université de Nice Sophia Antipolis for accepting to examine my Ph.D work. I express the same appreciation to Ferhat Khendek, professor at Concordia University, Philippe Dhaussy, associate professor (HDR) at ENSTA Bretagne, Frédéric Boniol, professor at Université INPT and ONERA Toulouse, and Silvano Dal Zilio, full time researcher at LAAS-CNRS for accepting to be the jury members. I extend my gratitude for their constructive comments and open discussions during my Ph.D work and on the defense of the thesis.

In this Ph.D study, I had the opportunity to discuss my work with Bernard Berthomieu, Silvano Dal Zilio and François Vernadat at LAAS. I have greatly benefited from their advice and unsurpassed knowledge of model checking and formal verification. I am deeply grateful to all of them.

I would like to offer my thank to Michaël Lauer and Frédéric Boniol for their permission to use the case

study they developed.

I would like to offer my special thank to Shin Nakajima, professor at National Institute of Informatics in Japan, with whom I have worked 3 months during the research internship, for his insightful comments and suggestions on my research directions. I would like to thank Aurélie Hurault for her support and encouragement in this internship.

I thank all the colleagues at IRIT, with special attention to Sylvie EICHEN and Sylvie Armengaud-Metche. They are always available to help me manage the administrative problems. Thanks so much to both for their kindness and efficiency. I also thank a lot to all members of ACADIE team. I would like to express my gratitude to Philippe Quélinnec, Mamoun Filali, Jean-Paul Bodeveix, Philippe Mauran, Xavier Thirioux, Meriem Quederni and Mounira Kezadri for their advice during my Ph.D study and their kindness. I want to thank the colleges sharing the same office with me: Arnaud, Florent and Faiez. It was a pleasure to work with them.

I cannot finish without thanking with all my heart my parents, for their support, encouragement and love throughout my whole life.

At last, I reserve my final thanks to you, Hongyu, my best friend, soul-mate and dear husband. Thank you for your continued and unfailing love, support and understanding my persistence in the research career.

#### **Abstract**

Automatic formal verification such as model checking faces the combinatorial explosion issue, and thus limits its application in industrial projects. This issue is caused by the explosion of the number of states during system's execution, as it may easily exceed the amount of available computing or storage resources.

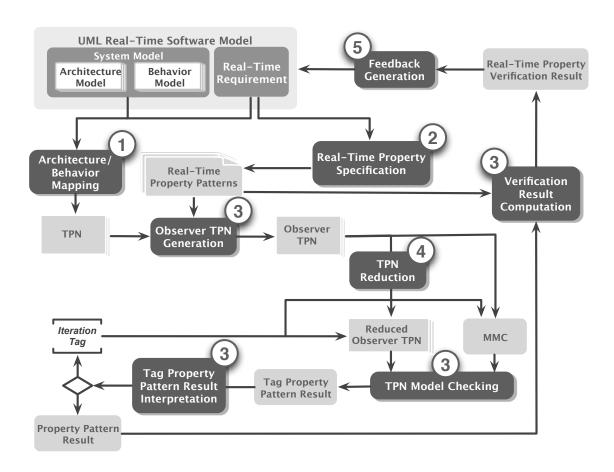

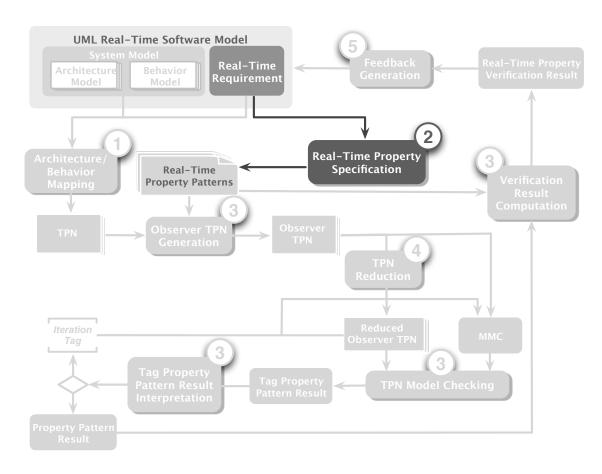

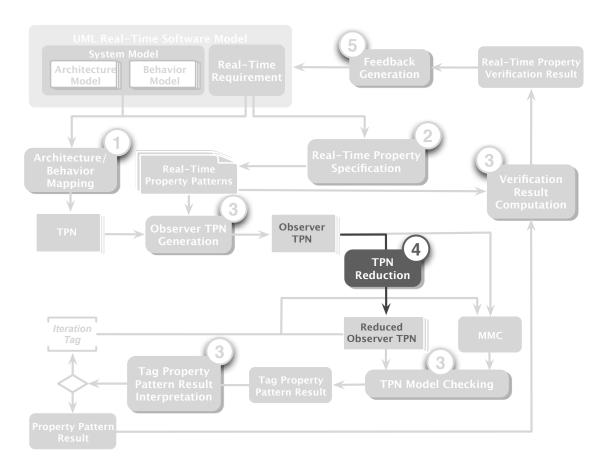

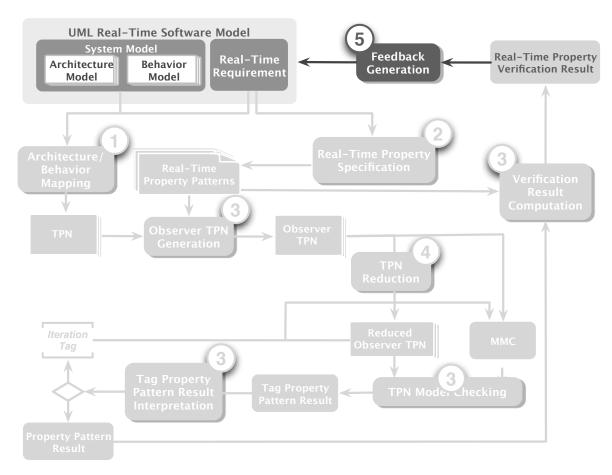

This thesis designs and experiments a set of methods for the development of scalable verification tools based on the property-driven approach. We propose efficient approaches based on model checking to verify real-time requirements expressed in large scale UML-MARTE real-time system designs. We rely on the UML and its profile MARTE as the end-user modeling language, and on the Time Petri Net (TPN) as the verification language. The main contribution of this thesis is the design and implementation of a property-driven verification methodology dedicated to real-time properties verification for UML-MARTE real-time software designs. We validate this method using an avionic use case and its user requirements. This method was implemented as a prototype toolset that includes five contributions: definition of real-time property specific execution semantics for UML-MARTE architecture and behavior models; specification of real-time requirements relying on a set of verification dedicated atomic real-time property patterns; real-time property specific observer-based model checking approach in TPN; real-time property specific state space reduction approach for TPN; and fault localization approach in model checking.

#### Résumé

Les techniques formelles de la famille « vérification de modèles » (« model checking ») se heurtent au problème de l'explosion combinatoire. Ceci limite les perspectives d'exploitation dans des projets industriels. Ce problème est provoqué par la combinatoire dans la construction de l'espace des états possibles durant l'exécution des systèmes modélisés. Le nombre d'états pour des modèles de systèmes industriels réalistes dépasse régulièrement les capacités des ressources disponibles en calcul et stockage.

Cette thèse défend l'idée qu'il est possible de réduire cette combinatoire en spécialisant les outils pour des familles de propriétés. Elle propose puis valide expérimentalement un ensemble de méthodes pour le développement de ce type d'outils en suivant une approche guidée par les propriétés appliquée au contexte temps réel. Il s'agit donc de construire des outils d'analyse performants pour des propriétés temps réel qui soient exploitables pour des modèles industriels de taille réaliste. Les langages considérés sont, d'une part UML étendu par le profil MARTE pour la modélisation par les utilisateurs, et d'autre part les réseaux de pétri temporisés comme support pour la vérification. Les propositions sont validées sur un cas d'étude industriel réaliste issu du monde avionique : l'étude de la latence et la fraicheur des données dans un système de gestion des alarmes exploitant les technologies d'Avionique Modulaire Intégrée. Ces propositions ont été mise en oeuvre comme une boite à outils qui intègre les cinq contributions suivantes: la définition de la sémantique d'exécution spécifiques aux propriétés temps réel pour les modèles d'architecture et de comportement spécifiés en UML/MARTE; la spécification des exigences temps réel en s'appuyant sur un ensemble de patrons de vérification atomiques dédiés aux propriété temps réel; une méthode itérative d'analyse à base d'observateurs pour des réseaux de Petri temporisés; des techniques de réduction de l'espace d'états spécifiques aux propriétés temps réel pour des Réseaux de Petri temporisés; une approche pour l'analyse des erreurs détectées par « vérification des modèles » en s'appuyant sur des idées inspirées de la « fouille de données » (« data mining »).

#### Contents

| Ac | know    | ledgments                                    | 1  |

|----|---------|----------------------------------------------|----|

| Ał | ostrac  | t                                            | 2  |

| Ré | ésumé   |                                              | 3  |

| Ta | ble of  | Contents                                     | 8  |

| Li | st of F | igures                                       | 13 |

| I  | Int     | roduction                                    | 14 |

| 1  | Intro   | oduction                                     | 15 |

|    | 1.1     | Safety Critical Real-Time System Development | 17 |

|    | 1.2     | Model Driven Engineering                     | 17 |

|    | 1.3     | Formal Methods                               | 19 |

|    | 1.4     | Methodology: Property Driven Approach        | 19 |

|    | 1.5     | Real-Time Requirements                       | 20 |

|    | 1.6     | Challenges                                   | 22 |

|    | 1.7     | Contributions                                | 24 |

|    | 1.8     | The Structure of the Thesis                  | 26 |

| 2  | State   | e of the Art                                 | 28 |

|    | 2.1     | Model-Driven Engineering                     | 31 |

|    | 2.2     | Modeling of Real-Time Systems                | 32 |

|    | 2.3     | Formal Specification of Real-Time Systems    | 34 |

|    |         | 2.3.1 Timed Automata                         | 35 |

|    |         | 2.3.2 Time Petri Net                         | 36 |

|    | 2.4     | Model Transformation                         | 28 |

#### CONTENTS

|    | 2.5 | Verification of Real-Time Systems                     | 39 |

|----|-----|-------------------------------------------------------|----|

|    |     | 2.5.1 Static Analysis                                 | 40 |

|    |     | 2.5.2 Theorem Proving                                 | 41 |

|    |     | 2.5.3 Model Checking                                  | 42 |

|    | 2.6 | State Space Reduction of Model Checking               | 46 |

|    |     |                                                       | 46 |

|    |     |                                                       | 47 |

|    |     | 2.6.3 Compositional Reasoning                         | 48 |

|    |     | 2.6.4 Abstraction                                     | 48 |

|    |     | 2.6.5 Symmetry                                        | 49 |

|    | 2.7 |                                                       | 49 |

|    | 2.8 |                                                       | 52 |

|    |     |                                                       |    |

| II | Co  | ontribution to Property-Driven Approaches             | 3  |

| 3  | Sem | antic Mapping from UML-MARTE to Property-Specific TPN | 54 |

|    | 3.1 | Introduction                                          | 58 |

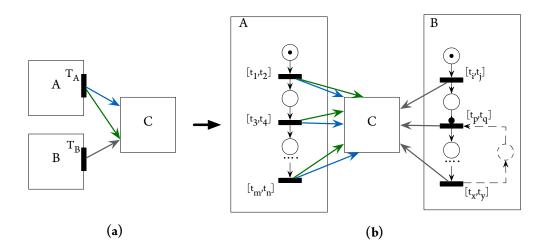

|    | 3.2 | Property-Driven Approach                              | 61 |

|    |     | 3.2.1 Core Idea                                       | 61 |

|    |     | 3.2.2 Principles of Semantic Mapping                  | 63 |

|    | 3.3 | Composite Structure Diagram Mapping Semantics         | 64 |

|    |     | 3.3.1 Part & Role                                     | 65 |

|    |     | 3.3.2 Port & Interface                                | 66 |

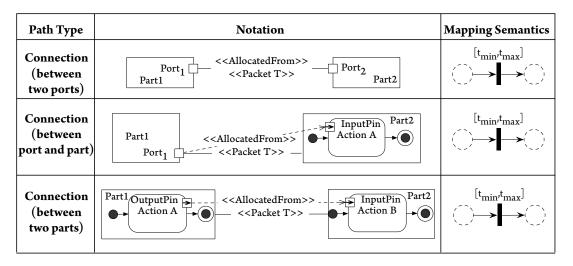

|    |     | 3.3.3 Connector                                       | 67 |

|    | 3.4 | Activity Diagram Mapping Semantics                    | 68 |

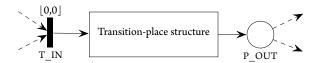

|    |     | 3.4.1 Semantic Mapping Pattern                        | 69 |

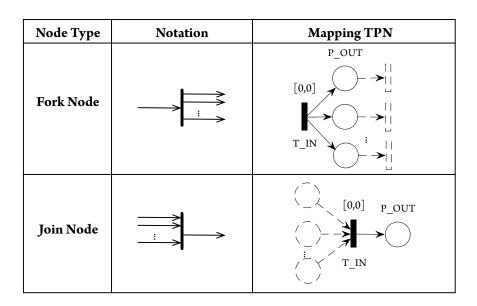

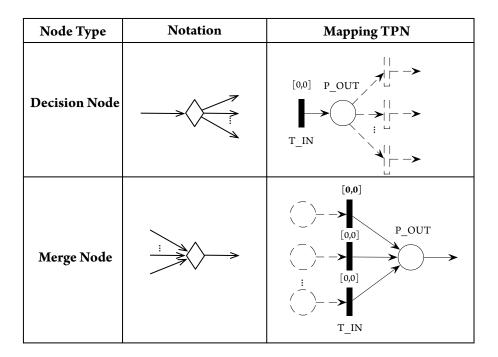

|    |     | 3.4.2 Control Nodes                                   | 69 |

|    |     | 3.4.3 Action                                          | 73 |

|    |     |                                                       | 78 |

|    |     |                                                       | 83 |

|    | 3.5 |                                                       | 84 |

|    |     |                                                       | 86 |

|    |     |                                                       | 90 |

|    |     |                                                       | 91 |

|    |     | 3.5.4 Mapping Semantics                               |    |

|    | 3.6 | Resource Mapping Semantics                            |    |

|    | ٥   | 3.6.1 Generic Resource Scheduling                     |    |

|   |      | 3.6.2 Non-preemptive Resource Scheduling                 |

|---|------|----------------------------------------------------------|

|   |      | 3.6.3 Preemptive Resource Scheduling                     |

|   | 3.7  | Time Semantics in Multi-Clock Modeling                   |

|   | 3.8  | Discussion                                               |

|   |      | 3.8.1 Verification of Model Transformation               |

|   |      | 3.8.2 Boundedness and Decidability Issue                 |

|   | 3.9  | Conclusion                                               |

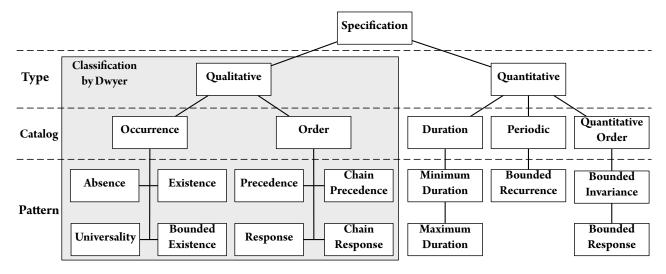

| 1 | Spec | cification of Real-Time Property 128                     |

|   | 4.1  | Introduction                                             |

|   | 4.2  | Preliminaries                                            |

|   |      | 4.2.1 Qualitative & Quantitative Property                |

|   |      | 4.2.2 Occurrence & Predicate & Scope                     |

|   |      | 4.2.3 Event & State                                      |

|   | 4.3  | Property Pattern Approach                                |

|   |      | 4.3.1 Qualitative Property Patterns                      |

|   |      | 4.3.2 Real-Time Suffix                                   |

|   | 4.4  | Catalog of Real-Time Property Patterns                   |

|   |      | 4.4.1 Occurrence Modifier                                |

|   |      | 4.4.2 Basic Event Modifier                               |

|   |      | 4.4.3 Basic Predicate                                    |

|   |      | 4.4.4 Basic Scope Modifiers                              |

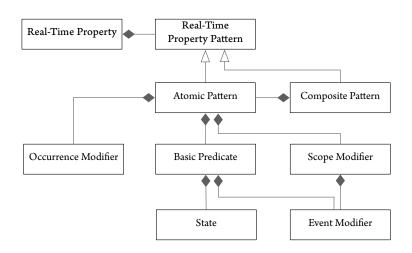

|   | 4.5  | Metamodel and Mapping Library                            |

|   | 4.6  | Pattern Composition: Application to CCSL Constraints     |

|   |      | 4.6.1 What is CCSL                                       |

|   |      | 4.6.2 Time Tolerance in Verification                     |

|   |      | 4.6.3 Specification of CCSL Constraints                  |

|   |      | 4.6.4 Specification of CCSL-based Task Level Constraints |

|   | 4.7  | Conclusion                                               |

| 5 | Prop | perty Verification based on TPN/tts Observers            |

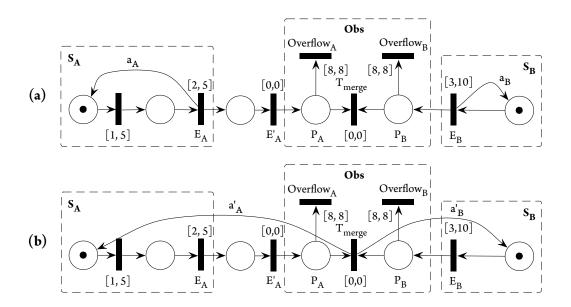

|   | 5.1  | Introduction                                             |

|   | 5.2  | Design Principles of TPN/tts Observers                   |

|   |      | 5.2.1 Structure of Observer                              |

|   |      | 5.2.2 Soundness of Observer                              |

|   |      | 5.2.3 Efficiency of Observer                             |

|   | 5.3  | Catalog of TPN/tts Observers                             |

|   |      | 5.3.1 Event Modifier Observers                           |

#### **CONTENTS**

|    |      | 5.3.2 Basic Predicate Observers                                  |

|----|------|------------------------------------------------------------------|

|    |      | 5.3.3 Scope Modifier Observers                                   |

|    |      | 5.3.4 Occurrence Modifiers                                       |

|    | 5.4  | Observer-based Verification Example                              |

|    |      | 5.4.1 Example Verification                                       |

|    |      | 5.4.2 Verification Result                                        |

|    | 5.5  | Computing Bound Value of Quantitative Property                   |

|    |      | 5.5.1 WCET Property Verification                                 |

|    |      | 5.5.2 Computation of WCET Bound Value                            |

|    |      | 5.5.3 Discussion: K-ary Searching Algorithm                      |

|    |      | 5.5.4 Discussion: Cavity in Computation of Bound Value 179       |

|    | 5.6  | Verification Scalability                                         |

|    |      | 5.6.1 On-the-Fly Model Checking                                  |

|    |      | 5.6.2 State Abstraction                                          |

|    | 5.7  | Conclusion                                                       |

| _  | D I  | Time Describe Consider De Janting for TDN                        |

| 6  |      | -Time Property- Specific Reduction for TPN 183                   |

|    | 6.1  | Introduction                                                     |

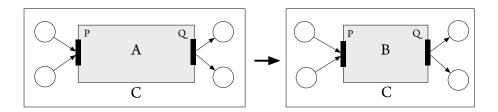

|    | 6.2  | Reduction for Property-Irrelevant Structures                     |

|    |      | 6.2.1 Relevancy Analysis for TPN Extended with Data Handling 190 |

|    |      | 6.2.2 Algorithm for Reducing Property-Irrelevant Structure       |

|    | 6.3  | Reduction for Property-Relevant Structures                       |

|    | 6.4  | Reduction using Topology-Implicit Semantic Equivalence           |

|    |      | 6.4.1 Redundant Zero-Time Patterns                               |

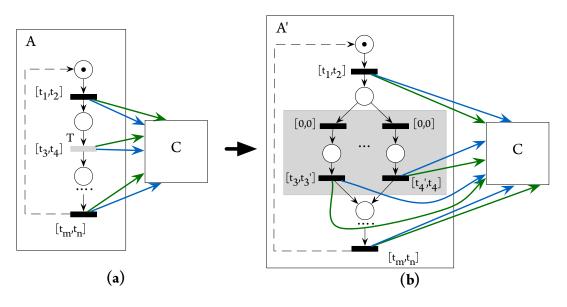

|    |      | 6.4.2 Sequential Encapsulation Pattern                           |

|    | 6.5  | Reduction using Behavioral Equivalence                           |

|    |      | 6.5.1 Example of Behavioral Equivalence                          |

|    |      | 6.5.2 Approach Overview                                          |

|    |      | 6.5.3 One-Way-Out Behavioral Equivalence Pattern                 |

|    |      | 6.5.4 Generic Behavioral Equivalence Pattern                     |

|    |      | 6.5.5 Discussion                                                 |

|    | 6.6  | Conclusion                                                       |

|    |      |                                                                  |

| II | ı C  | ontribution to Fault Localization 219                            |

| 7  | Auto | omated Fault Localization in Model Checking 220                  |

|    | 7.1  | Introduction                                                     |

|    | 7.2  | Problem Statement                                                |

|    |      | 7.2.1 Abstraction Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                        |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    |      | 7.2.2 Fault Localization Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .7                                                       |

|    |      | 7.2.3 Existing Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .7                                                       |

|    |      | 7.2.4 Proposed Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .8                                                       |

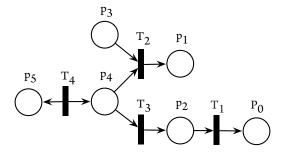

|    | 7.3  | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,9                                                       |

|    |      | 7.3.1 Reachability Graph & Violation States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ,9                                                       |

|    |      | 7.3.2 Error Traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ,9                                                       |

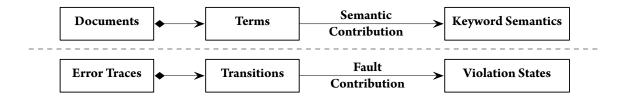

|    |      | 7.3.3 Kullback-Leibler Divergence Applied to Textual Documents 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | О                                                        |

|    |      | 7.3.4 Term Frequency - Inverse Document Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | , 1                                                      |

|    | 7.4  | Ranking Suspicious Faulty Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                        |

|    |      | 7.4.1 Core Idea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                                        |

|    |      | 7.4.2 Fault Localization Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                                                        |

|    |      | 7.4.3 TC-ITC Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                        |

|    | 7.5  | Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                        |

|    |      | 7.5.1 Automated Test Bed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                                        |

|    |      | 7.5.2 Evaluation of Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .0                                                       |

|    |      | 7.5.3 Evaluation of Effectiveness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 1                                                      |

|    | 7.6  | Back-Tracing Fault Transitions in UML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 1                                                      |

|    | 7.7  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

|    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |

| IV | / In | dustrial Application & Conclusion 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                        |

| 8  | Ann  | lication to Flight Management System 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                        |

| O  | 8.1  | treation to 1 light Management System 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

|    | 0.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                        |

|    | 8 2  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                        |

|    | 8.2  | Case Study: Flight Management System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -7<br>-8                                                 |

|    | 8.2  | Case Study: Flight Management System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -7<br>-8<br>-8                                           |

|    | 8.2  | Case Study: Flight Management System248.2.1 Integrated Modular Avionics248.2.2 Avionics Full-Duplex Switched Ethernet25                                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                        |

|    | 8.2  | Case Study: Flight Management System248.2.1 Integrated Modular Avionics248.2.2 Avionics Full-Duplex Switched Ethernet258.2.3 Functions25                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>8<br>8<br>0                                         |

|    |      | Case Study: Flight Management System248.2.1 Integrated Modular Avionics248.2.2 Avionics Full-Duplex Switched Ethernet258.2.3 Functions258.2.4 Real-Time Requirements25                                                                                                                                                                                                                                                                                                                                                              | 17<br>18<br>18<br>10<br>11                               |

|    | 8.2  | Case Study: Flight Management System248.2.1 Integrated Modular Avionics248.2.2 Avionics Full-Duplex Switched Ethernet258.2.3 Functions258.2.4 Real-Time Requirements25Modeling and Semantics25                                                                                                                                                                                                                                                                                                                                      | 7<br>8<br>8<br>0<br>1<br>3                               |

|    |      | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25                                                                                                                                                                                            | 18<br>18<br>10<br>13<br>14                               |

|    |      | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25         8.3.2 Architecture Model       25                                                                                                                                                  | 17<br>18<br>18<br>10<br>13<br>14<br>14                   |

|    |      | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25         8.3.2 Architecture Model       25         8.3.3 Behavior Model       25                                                                                                            | 7<br>8<br>8<br>10<br>13<br>14<br>7<br>8                  |

|    | 8.3  | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25         8.3.2 Architecture Model       25         8.3.3 Behavior Model       25         8.3.4 Real-Time Requirement Specification       26                                                 | 7<br>8<br>8<br>0<br>1<br>3<br>4<br>7<br>8                |

|    |      | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25         8.3.2 Architecture Model       25         8.3.3 Behavior Model       25         8.3.4 Real-Time Requirement Specification       26         Mapping UML-MARTE to TPN Model       26 | 7<br>8<br>8<br>0<br>1<br>3<br>4<br>7<br>8<br>1<br>1      |

|    | 8.3  | Case Study: Flight Management System       24         8.2.1 Integrated Modular Avionics       24         8.2.2 Avionics Full-Duplex Switched Ethernet       25         8.2.3 Functions       25         8.2.4 Real-Time Requirements       25         Modeling and Semantics       25         8.3.1 Abstraction of AFDX Network       25         8.3.2 Architecture Model       25         8.3.3 Behavior Model       25         8.3.4 Real-Time Requirement Specification       26                                                 | 7<br>8<br>8<br>0<br>1<br>3<br>4<br>7<br>8<br>1<br>1<br>1 |

#### **CONTENTS**

|      | 8.5   | Verification of Real-Time Property                                       | 264 |

|------|-------|--------------------------------------------------------------------------|-----|

|      | 8.6   | Scalability Tests                                                        | 265 |

|      |       | 8.6.1 Experiments on the Latency Functional Chain                        | 265 |

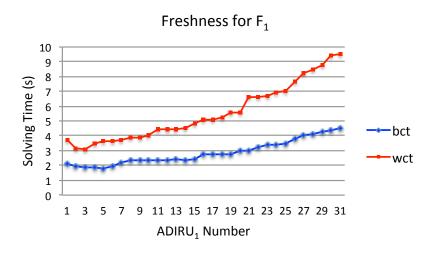

|      |       | 8.6.2 Experiments on the Freshness Functional Chain                      | 268 |

|      | 8.7   | Comparison to the Results in the Work of Lauer                           | 268 |

|      | 8.8   | Conclusion                                                               | 270 |

| 9    | Conc  | clusion                                                                  | 271 |

|      | 9.1   | Fulfillment of Objectives                                                | 274 |

|      | 9.2   | Application of Research Results                                          | 276 |

|      | 9.3   | Future Research Directions                                               | 277 |

|      |       | 9.3.1 Short Term Activities                                              | 277 |

|      |       | 9.3.2 Resource scheduling semantics mapping                              | 277 |

|      |       | 9.3.3 Future Research Direction for Property Specific Reduction Approach | 278 |

|      |       | 9.3.4 Verification of Model Transformation                               | 279 |

|      |       | 9.3.5 Application of the Approaches to Other Modeling Language           | 280 |

| A    | Appe  | endix A:                                                                 |     |

|      | Cove  | erage Library: Mapping UML-MARTE to TPN                                  | 281 |

|      | A.1   | Coverage Library of Composite Structure Diagram                          | 282 |

|      | A.2   | Coverage Library of Activity Diagram                                     | 283 |

|      | A.3   | Coverage Library of State Machine Diagram                                | 284 |

| В    | Appe  | endix B:                                                                 |     |

|      | Map   | ping Library: Real-Time Property Pattern                                 | 285 |

|      | B.1   | Pattern Mapping Library                                                  | 286 |

|      | B.2   | Scope Mapping Library                                                    | 288 |

| Δ +- | peno  | liv                                                                      | 281 |

| лļ   | pent  | JIA                                                                      | 201 |

| Bi   | bliog | graphy                                                                   | 289 |

### Listing of figures

| 1.2.1 V-Model in Model-Driven Engineering                      | 3 |

|----------------------------------------------------------------|---|

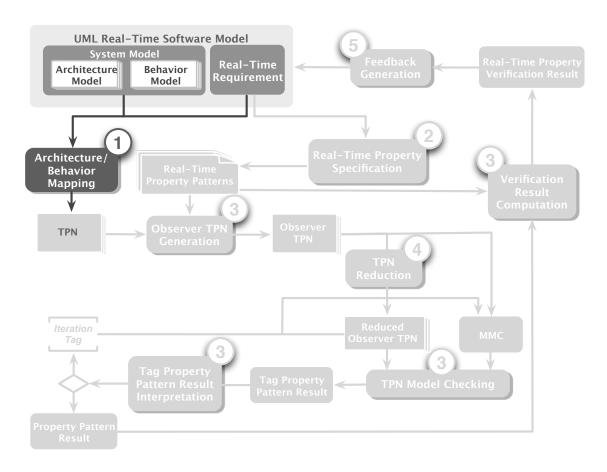

| 1.7.1 UML-MARTE Real-Time Properties Verification Architecture | 5 |

| 2.2.1 Architecture of MARTE Profile                            | 4 |

| 2.3.1 Timed Automata Example                                   |   |

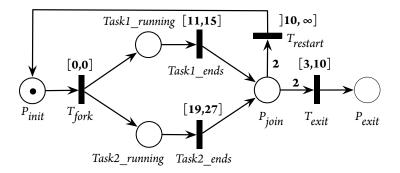

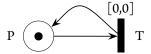

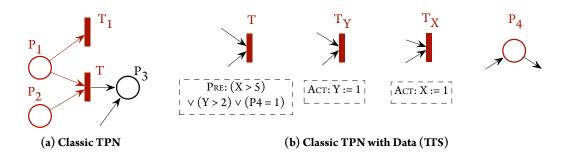

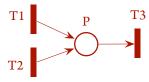

| 2.3.2 Time Petri Net Example                                   |   |

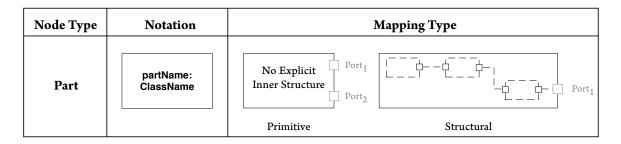

| 3.3.1 Mapping Semantics for Part                               | 5 |

| 3.3.2 Mapping Semantics for Port                               | 5 |

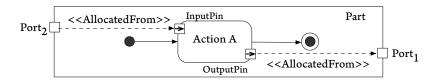

| 3.3.3 Example of Port Allocation Semantics                     | 7 |

| 3.3.4 Mapping Semantics for CSD Connector                      | 7 |

| 3.3.5 Mapping Semantics for CSD Connection                     | 3 |

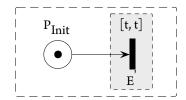

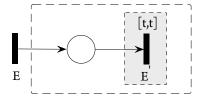

| 3.4.1 Generic Semantic Pattern of Activity Elements            | 9 |

| 3.4.2 Initial Node & Flow Final Mapping Semantics              | o |

| 3.4.3 Activity Final Node Mapping Semantics                    | Э |

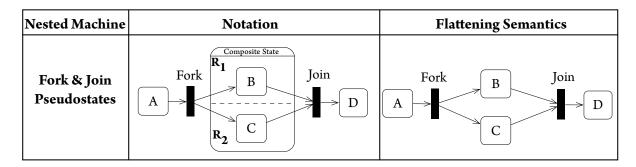

| 3.4.4 Fork Node & Join Node Mapping Semantics                  | 1 |

| 3.4.5 Decision Node & Merge Node Mapping Semantics             | 2 |

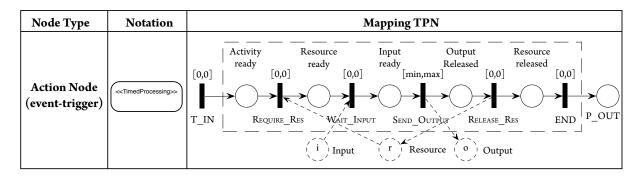

| 3.4.6 Event-trigger Action Mapping Semantics                   | 5 |

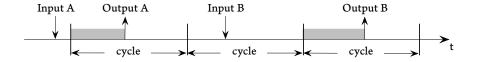

| 3.4.7 Time-trigger Action Pattern                              | 5 |

| 3.4.8 Time-trigger Action Mapping Semantics                    | 6 |

| 3.4.9 Upper Bound Mapping Semantics                            | 9 |

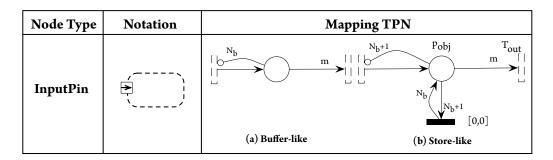

| 3.4.10Input Pin Mapping Semantics                              | 1 |

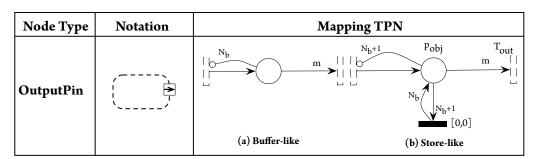

| 3.4.11Output Pin Mapping Semantics                             | 1 |

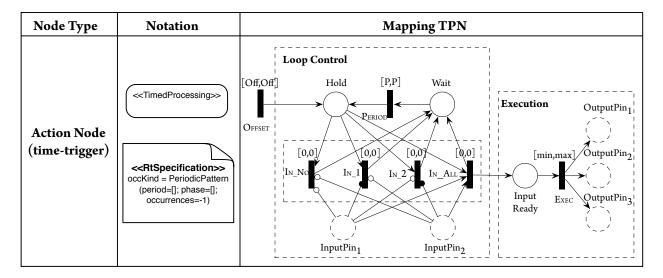

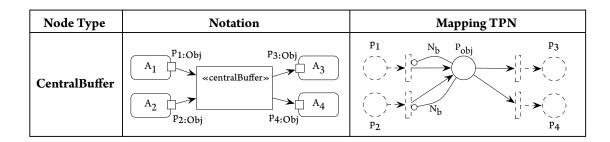

| 3.4.12Central Buffer Mapping Semantics                         | 2 |

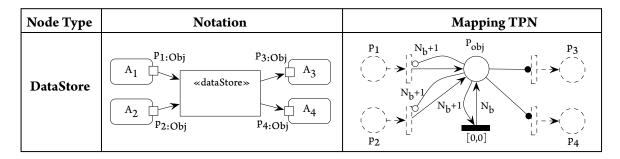

| 3.4.13DataStore Mapping Semantics                              | 3 |

| 3.4.14Control Flow Mapping Semantics                           | 3 |

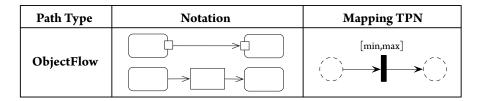

| 3.4.15Object Flow Mapping Semantics                            | 4 |

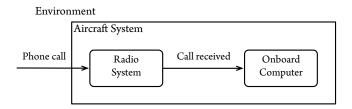

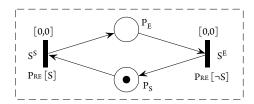

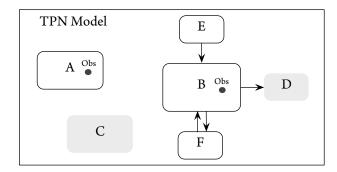

| 3.5.1 Event Categories Example: System & Environment           | 7 |

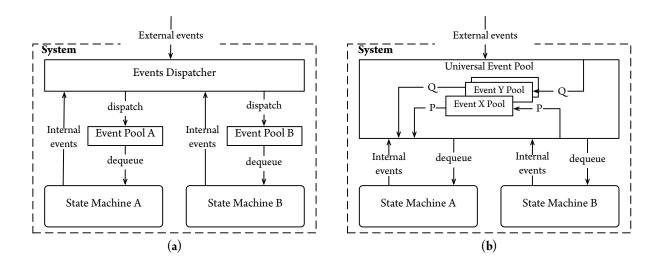

| 2 S 2 Event Pool Model                                         | a |

#### LISTING OF FIGURES

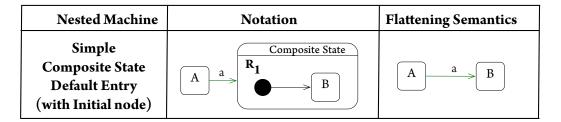

| 3.5.3 Default Entry Flattening Semantics for Simple Composite State            |

|--------------------------------------------------------------------------------|

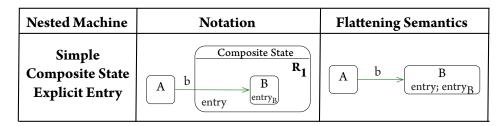

| 3.5.4 Explicit Entry Flattening Semantics for Simple Composite State           |

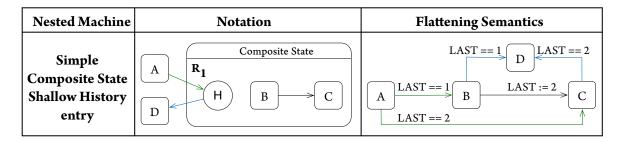

| 3.5.5 Shallow History Entry Flattening Semantics for Simple Composite State 92 |

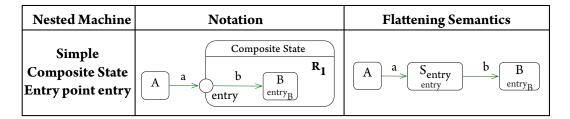

| 3.5.6 Entry Point Entry Flattening Semantics for Simple Composite State        |

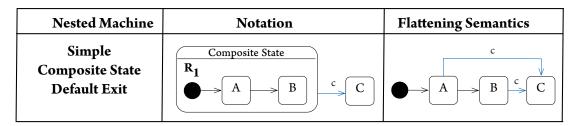

| 3.5.7 Default Exit Flattening Semantics for Simple Composite State             |

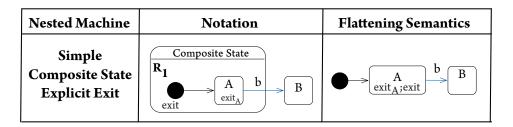

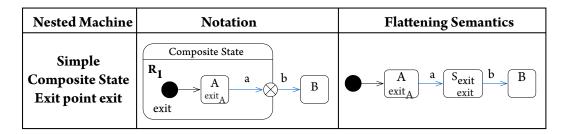

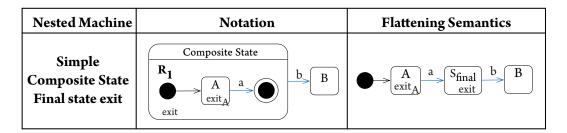

| 3.5.8 Explicit Exit Flattening Semantics for Simple Composite State            |

| 3.5.9 Exit Point Exit Flattening Semantics for Simple Composite State          |

| 3.5.10Final State Exit Flattening Semantics for Simple Composite State         |

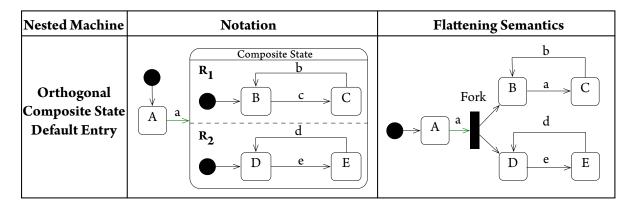

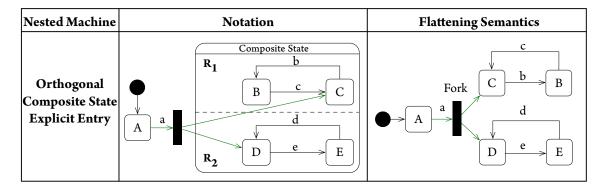

| 3.5.11Default Entry Flattening Semantics for Orthogonal Composite State        |

| 3.5.12Explicit Entry Flattening Semantics for Orthogonal Composite State       |

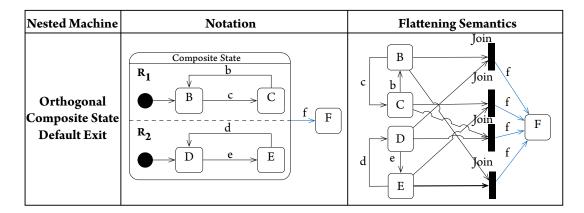

| 3.5.13Default Exit Flattening Semantics for Orthogonal Composite State         |

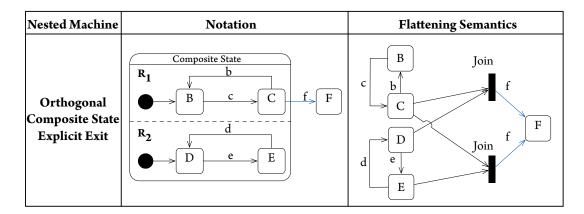

| 3.5.14Explicit Exit Flattening Semantics for Orthogonal Composite State        |

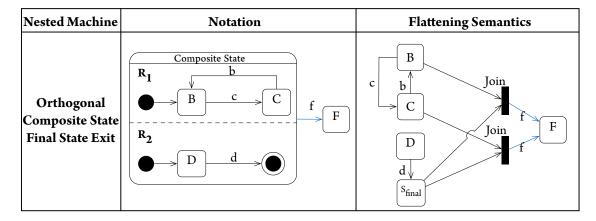

| 3.5.15Final State Exit Flattening Semantics for Orthogonal Composite State     |

| 3.5.16Fork & Join Pseudostate Flattening Semantics                             |

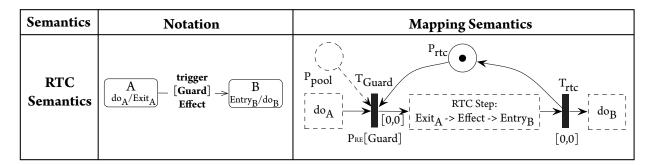

| 3.5.17Run-to-Completion Semantics                                              |

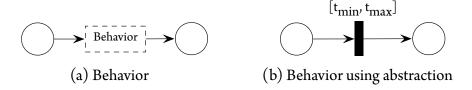

| 3.5.18Do/Exit/Entry/Effect Behavior                                            |

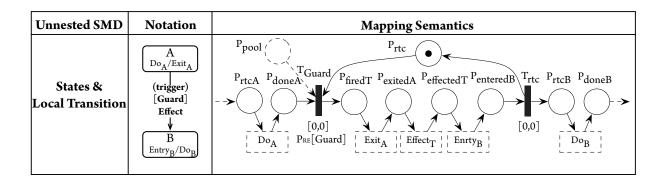

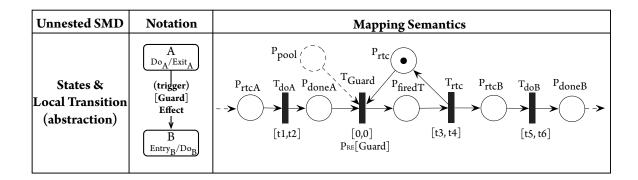

| 3.5.19Local Transition Mapping Semantics                                       |

| 3.5.20Abstract Local Transition Mapping Semantics                              |

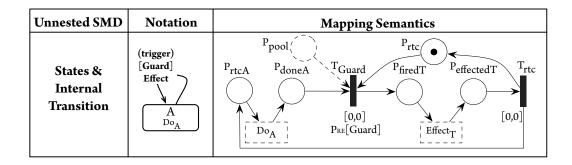

| 3.5.21Internal Transition Mapping Semantics                                    |

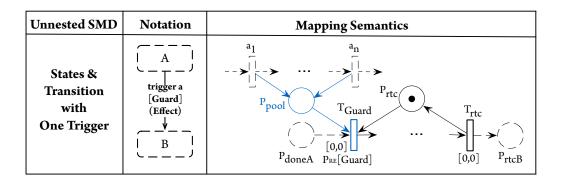

| 3.5.22Single Trigger Transition Mapping Semantics                              |

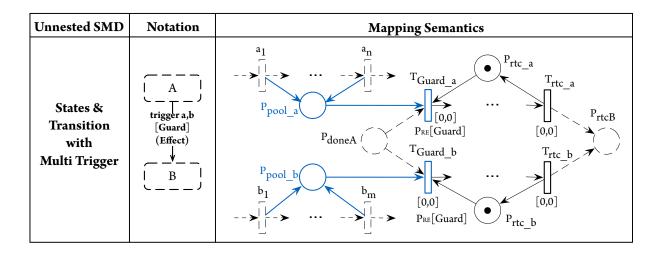

| 3.5.23 Multiple Trigger Mapping Semantics                                      |

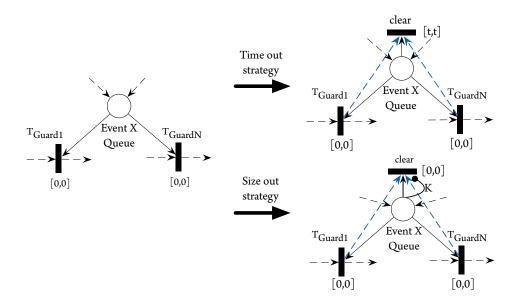

| 3.5.24Mapping Semantics: Event Pool Clearance Mechanism                        |

| 3.5.25Final State Mapping Semantics                                            |

| 3.5.26Initial Pseudostate and Outgoing Transition Mapping Semantics            |

| 3.5.27 Terminate Pseudostate Mapping Semantics                                 |

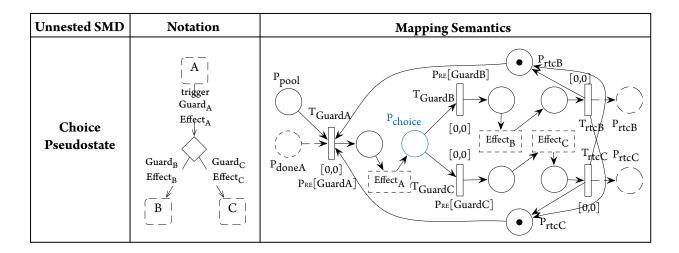

| 3.5.28Choice Pseudostate Mapping Semantics                                     |

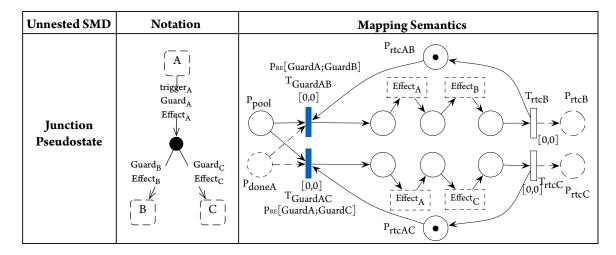

| 3.5.29Junction Pseudostate Mapping Semantics                                   |

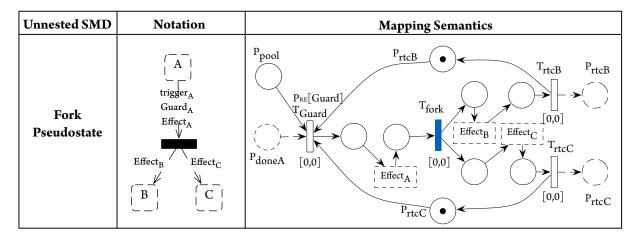

| 3.5.30Fork Pseudostate Mapping Semantics                                       |

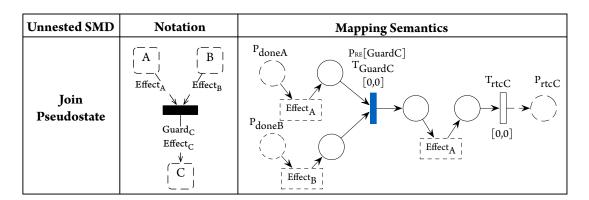

| 3.5.31 Join Pseudostate Mapping Semantics                                      |

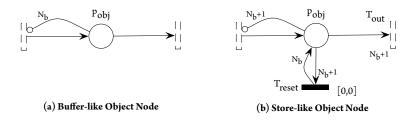

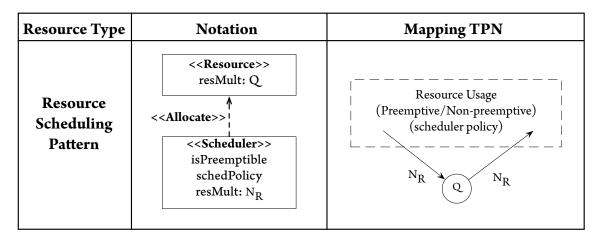

| 3.6.1 Generic Resource Scheduling Mapping Semantics                            |

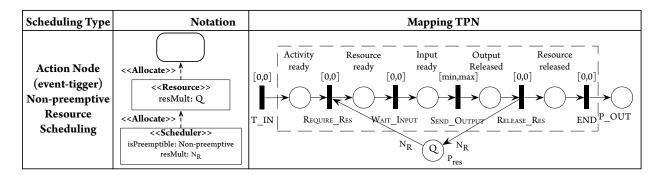

| 3.6.2 Non-Preemptive Resource Scheduling Semantics                             |

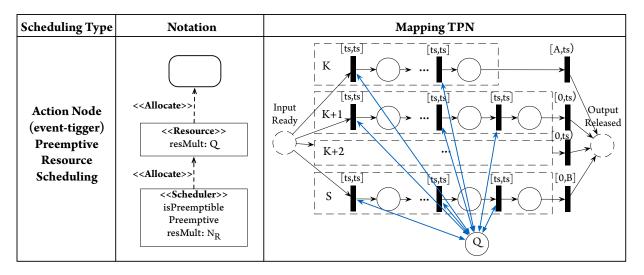

| 3.6.3 Preemptive Resource Scheduling Semantics                                 |

| 3.8.1 Verification of Model Transformation                                     |

| 4.2.1 Pattorn Higgarchy                                                        |

| 4.3.1 Pattern Hierarchy                                                        |

| 4.4.1 Temporal Property Verification Pattern System                            |

| 4.4.2 to Occurrence Of E                                                       |

|                                                                                |

| 4.4.4 Sub-Occurrence of $E$                                             |

|-------------------------------------------------------------------------|

| 4.4.5 T after System Initialization                                     |

| 4.4.6 T after E                                                         |

| 4.4.7 Entering and Exiting event of State                               |

| 4.6.1 Example of Sub-clock                                              |

| 4.6.2 Example of Tight Sub-clock                                        |

| 4.6.3 Example of Equality                                               |

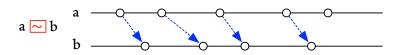

| 4.6.4 Example of Strict Precedence                                      |

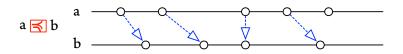

| 4.6.5 Example of Precedence                                             |

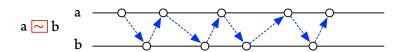

| 4.6.6 Example of Alternation                                            |

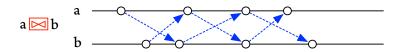

| 4.6.7 Example of Synchronization                                        |

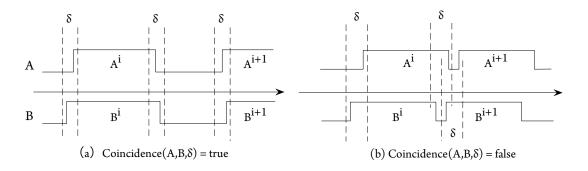

| 4.6.8 Coincidence Constraint                                            |

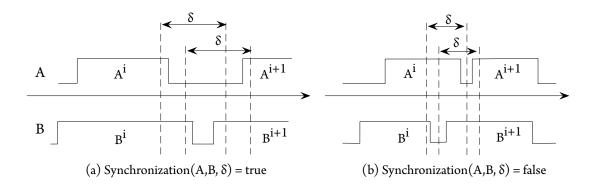

| 4.6.9 Synchronization Constraint                                        |

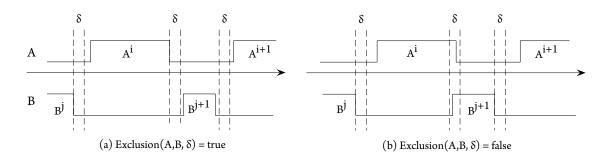

| 4.6.10Exclusion Temporal Constraint                                     |

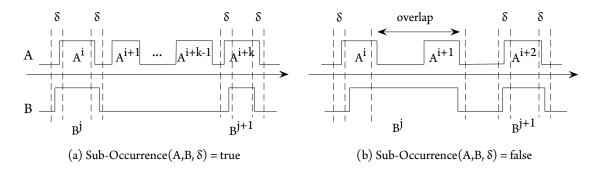

| 4.6.11Sub-occurrence Constraint                                         |

| 4.6.12Precedence Constraint                                             |

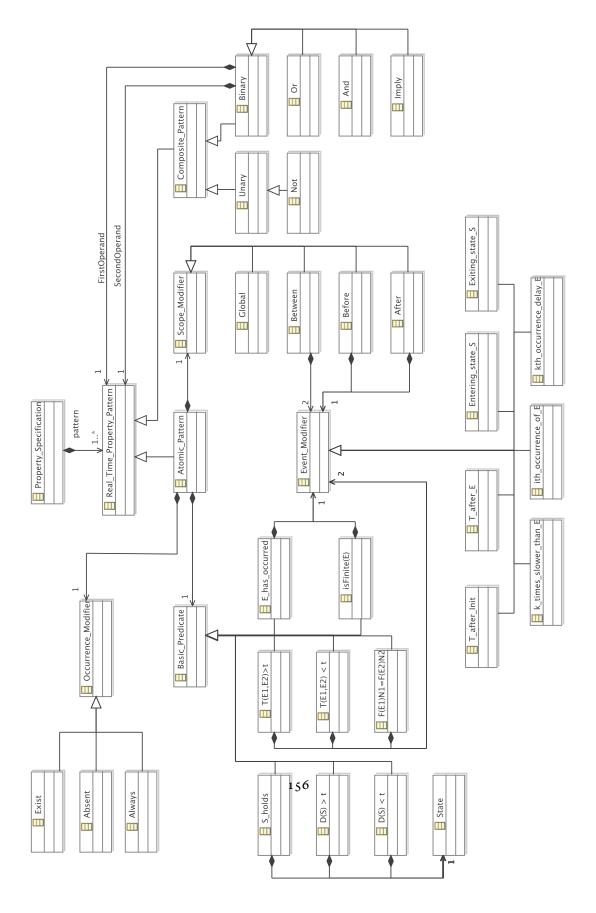

| 4.7.1 Metamodel of Temporal Property Pattern                            |

|                                                                         |

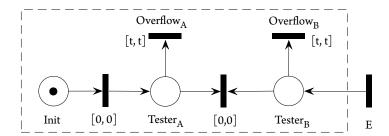

| 5.2.1 Observer Structure                                                |

| 5.3.1 Generic Observer Pattern                                          |

| 5.3.2 Event Observer: $i^{th}$ Occurrence of $E$                        |

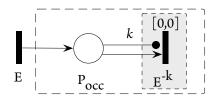

| 5.3.3 Event Observer: $k$ Times Occurrence Delay of $E$                 |

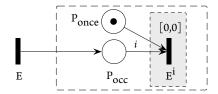

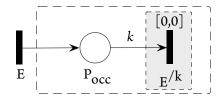

| 5.3.4 Event Observer: Sub-occurrence $k$ Times Slower than $E$          |

| 5.3.5 Event Observer: Time Passed since System Initialization           |

| 5.3.6 Event Observer: Time Passed since $E$                             |

| 5.3.7 Event Observer: Starting and Ending Event of S                    |

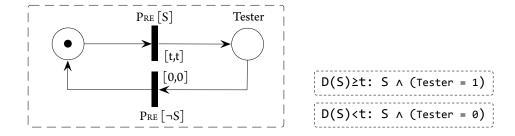

| 5.3.8 Predicate Observer Pattern                                        |

| 5.3.9 Predicate Observer: Occurrence of $E^i$                           |

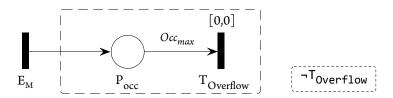

| 5.3.10Predicate Observer: Occurrence of $E$ is bounded                  |

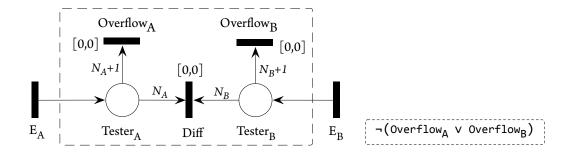

| 5.3.11Predicate Observer: Same Frequency between $E_A$ and $E_B$        |

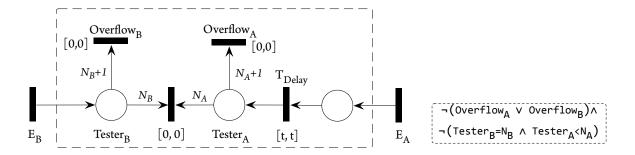

| 5.3.12Predicate Observer: Minimum Time Interval between $E_A$ and $E_B$ |

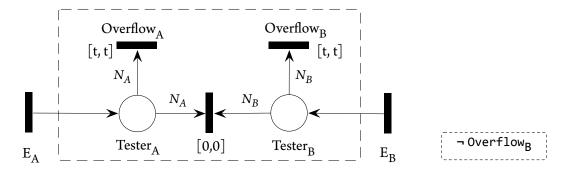

| 5.3.13Predicate Observer: Maximum Time Interval between $E_A$ and $E_B$ |

| 5.3.14Predicate Observer: Time Duration of State                        |

| 5.3.15Scope Observer: Before E & After E                                |

| 5.3.16Scope Observer: Between two Events                                |

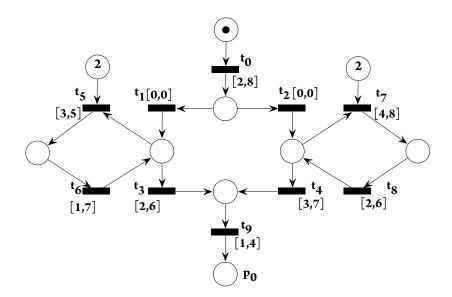

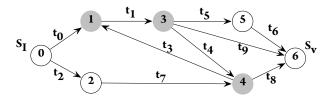

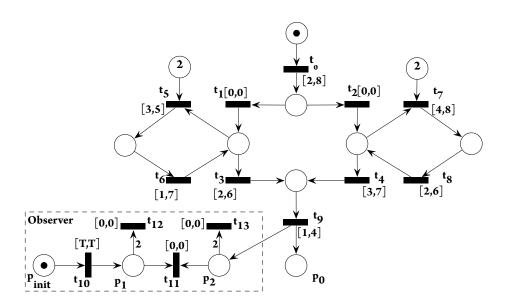

| 5.4.1 Observer-based Verification Example                               |

| 5.4.2 Verification of Example                                           |

| 5.4.3 Reachability Graph of Verification Example                        |

#### LISTING OF FIGURES

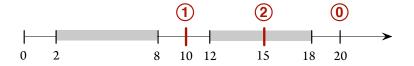

| 5.5.1 | Property Computation Example: WCET                              | 178 |

|-------|-----------------------------------------------------------------|-----|

| 5.5.2 | Cavity Discussion Example                                       | 179 |

| 6.2.1 | Relevancy between System Components                             | 189 |

| 6.2.2 | Time Divergence Issue                                           | 190 |

|       | Relevant Structure for TPN Transition                           |     |

|       | Relevant Structure for TPN Place                                |     |

|       | Example of Propagation of Property-Relevant TPN Structure       |     |

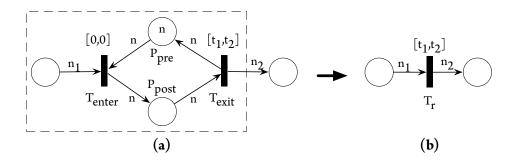

| 6.4.1 | Redundant Zero-Time Pattern: Sequential                         | 198 |

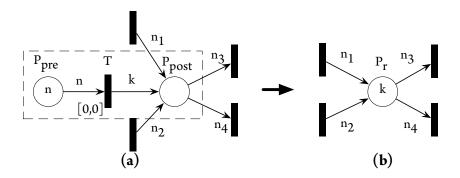

|       | Redundant Zero-Time Pattern: Indirect Initialization            |     |

|       | Redundant Zero-Time Pattern: Shorten Cycle                      |     |

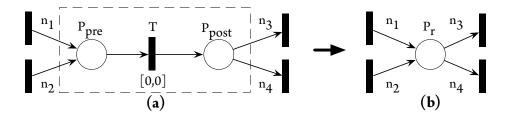

| 6.4.4 | Sequential Encapsulation Pattern                                | 201 |

| 6.5.1 | Example of Behavioral Equivalence                               | 204 |

|       | Example Result of Behavioral Equivalence                        |     |

|       | Overview of Behavior Equivalence Approach                       |     |

|       | Reduction pattern of Behavioral Equivalence                     |     |

|       | Example of Refinement                                           |     |

|       | Generic Behavioral Equivalence Pattern                          |     |

|       | Example of Impact and Impacted Sets                             |     |

|       | Behavioral Equivalence Pattern: Hole on Time Interval           |     |

|       | Behavioral Equivalence Pattern: Deal with Hole on Time Interval |     |

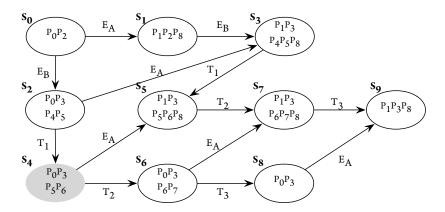

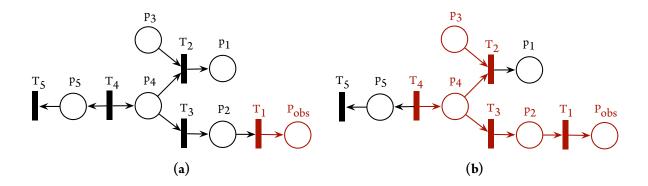

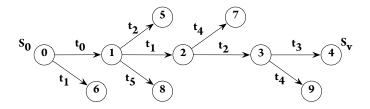

| 721   | Error Trace Example                                             | 220 |

|       |                                                                 |     |

|       | Comparison to TF-IDF                                            |     |

|       | Example of Fault Localization Algorithm                         |     |

|       | Cycle on Error Traces                                           |     |

|       | Verification of Fault Localization Example                      |     |

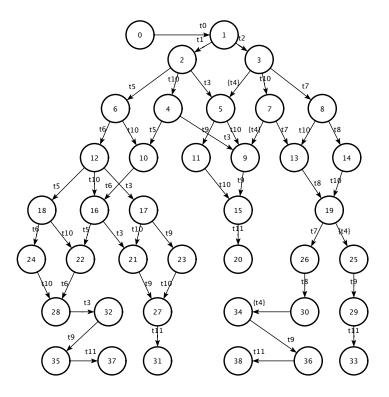

| 7.4.5 | Reachability Graph of Fault Localization Example                | 236 |

| 7.4.6 | Feedback of Fault Localization Example                          | 237 |

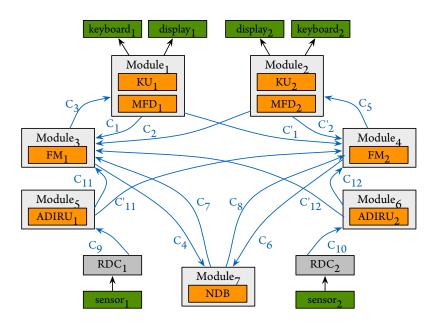

| 8.2.1 | Architecture of the Case Study                                  | 249 |

| 8.2.2 | Functional Chain: Sporadic Response to Request                  | 252 |

| 8.2.3 | Functional Chain: Production of Periodic Data                   | 252 |

| 8.2.4 | Latency Real-Time Requirement                                   | 253 |

|       | Freshness Real-Time Requirement                                 |     |

|       | Abstract Network of Case Study                                  |     |

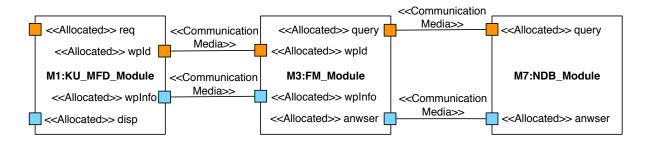

|       | UML-MARTE Architecture for Latency Real-Time Property           |     |

|       | UML-MARTE Architecture for Freshness Real-Time Property         |     |

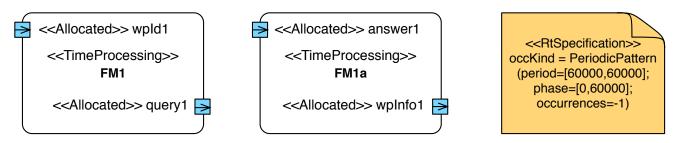

|       |                                                                 | 250 |

#### LISTING OF FIGURES

| 8.3.5 | UML-MARTE Behavior for Freshness Real-Time Property    | 59 |

|-------|--------------------------------------------------------|----|

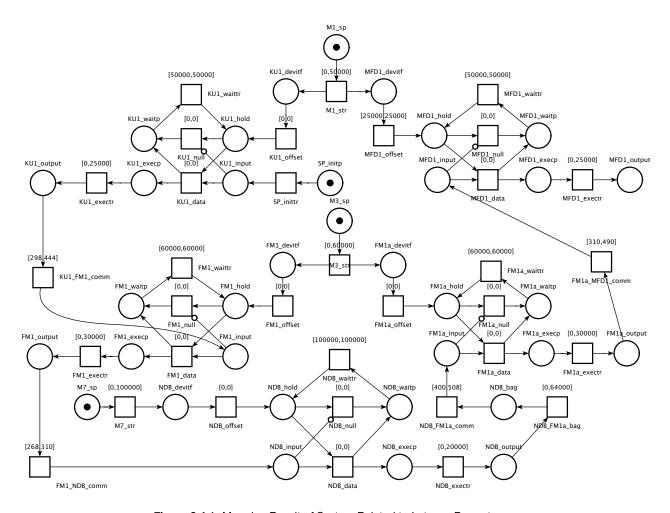

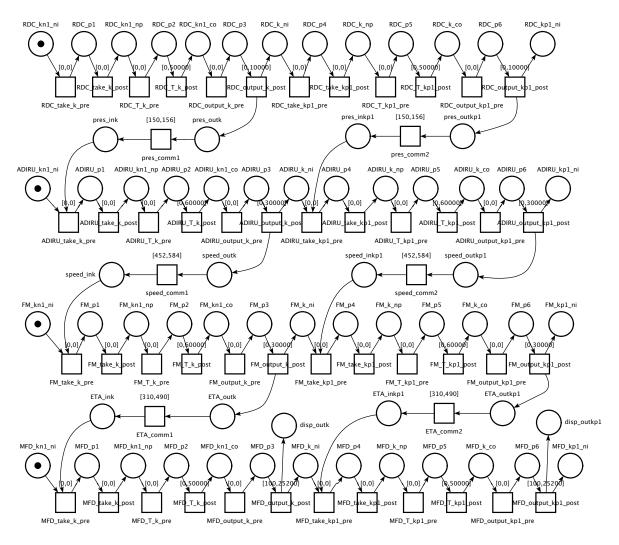

| 8.4.1 | Mapping Result of System Related to Latency Property   | 62 |

| 8.4.2 | Mapping Result of System Related to Freshness Property | 63 |

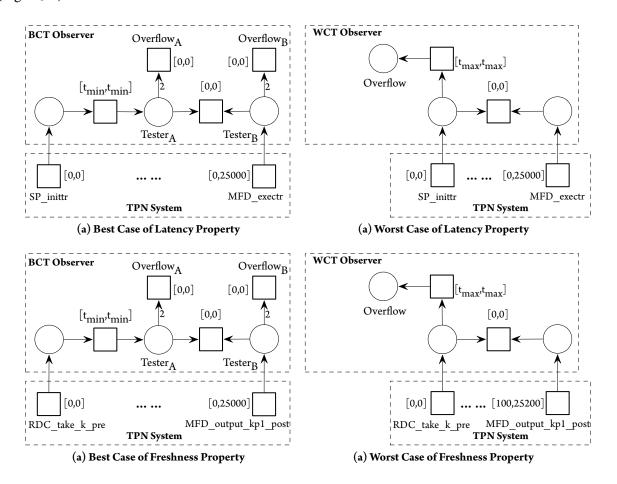

| 8.5.1 | TPN Observer for Latency and Freshness Property        | 64 |

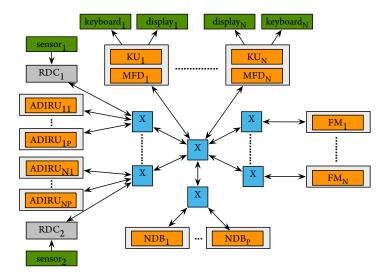

| 8.6.1 | Architecture with Scalability Parameters               | 66 |

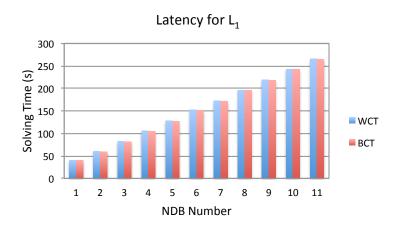

| 8.6.2 | Solving Time of Scalable Latency Property              | 67 |

| 8.6.3 | Solving Time of Freshness Property                     | 68 |

## Part I Introduction

# Introduction

#### Résumé

Le premier chapitre introduit la contexte de recherche, les défis et les contributions de cette thèse. Les systèmes embarquées temps réels jouent un rôle clé dans de nombreuses facettes de la vie quotidienne. Certains sont des applications spécialisées de grande échelle dans les domaines critiques tels que l'avionique, l'aérospatial, la défense, le nucléaire, l'automobile, la santé et le matériel médical. Ils doivent donc satisfaire de fortes exigences concernant la sécurité et la fiabilité. Tout manquement à ces exigences peut entraîner des conséquences graves en terme de pertes matérielles et de sécurité des personnes. La sécurité et la fiabilité des systèmes temps réels dépendent fortement de la satisfaction des exigences temps réel, à la fois pour les aspects qualitatifs et quantitatifs. L'état de l'art actuel des connaissances propose que ces exigences soient vérifiées et validées en utilisant des méthodes formelles en combinaison avec l'ingénierie dirigée par les modèles. Les méthodes formelles sont des techniques issues des mathématiques pour la spécification, le conception, la programmation et la vérification des systèmes matériels et logiciels. L'utilisation

d'approches mathématiques permet d'obtenir une plus grande assurance en ce qui concerne la fiabilité et la robustesse d'un système.

Les techniques formelles de la famille « vérification de modèles » (« model checking ») sont bien adaptées à une exploitation industrielle car elles permettent une automatisation complète des activités de vérification et la synthèse de contre exemples en cas de non satisfaction des exigences. Mais elles se heurtent au problème de l'explosion combinatoire qui impose la construction de modèles dédiés à la vérification de chaque exigence et limite les perspectives d'exploitation dans des projets de grande taille. Ce problème est lié à la combinatoire dans la construction de l'espace des états possibles durant l'exécution des systèmes modélisés. Le nombre d'états pour des modèles de systèmes industriels réalistes dépasse régulièrement les ressources disponibles en calcul et stockage.

En s'appuyant sur la pratique actuelle de la « vérification de modèles » consistant à construire des modèles dédiés à chaque vérification, cette thèse défend l'idée qu'il est possible de réduire cette combinatoire en spécialisant les outils selon des familles de propriétés. Elle propose puis valide expérimentalement un ensemble de méthodes pour le développement de ce type d'outils en suivant une approche guidée par les propriétés appliquée pour le contexte temps réel. Il s'agit donc de construire des outils d'analyse performants pour des propriétés temps réel qui soient exploitables pour des modèles industriels de taille réaliste. Les langages considérés sont, d'une part UML étendu par le profil MARTE pour la modélisation par les utilisateurs, et d'autre part les réseaux de pétri temporisés comme support pour la vérification. Les propositions effectuées sont validées en exploitant un cas d'étude industriel réaliste issu du monde avionique : l'étude de la latence et la fraicheur des données dans un système de gestion des alarmes exploitant les technologies d'Avionique Modulaire Intégrée. Ces propositions ont été mise en oeuvre sous la forme d'une boite à outils qui intègre les cinq contributions suivantes: la définition de la sémantique d'exécution spécifique aux propriétés temps réel pour les modèles d'architecture et de comportement spécifiés en UML/MARTE; la spécification des exigences temps réel en s'appuyant sur une traduction vers un ensemble de patrons de vérification atomiques dédiés aux propriété temps réel; une méthode itérative d'analyse à base d'observateurs pour des réseaux de Petri temporisés; des techniques de réduction de l'espace d'états spécifiques aux propriétés temps réel pour des Réseaux de Petri temporisés; une approche pour l'analyse des erreurs détectées par « vérification des modèles » en s'appuyant sur des idées inspirées de la « fouille de données » (« data mining »).

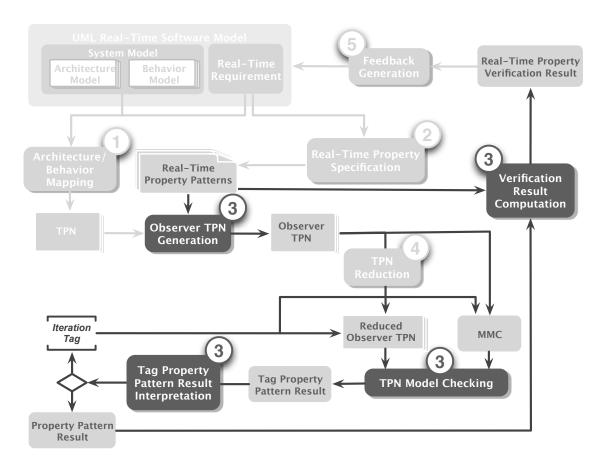

This thesis designs and experiments a set of methods for the development of scalable verification tools based on a property-driven approach. It develops efficient approaches based on model checking to verify real-time requirements expressed in large scale UML-MARTE real-time system designs.

#### 1.1 SAFETY CRITICAL REAL-TIME SYSTEM DEVELOPMENT

Real-time embedded systems play a key role in many facets of daily life. Some are specialized and large scale applications in the critical domains such as avionics, aerospace, defense, nuclear power, motor vehicles, health and medical equipment and thus have strong requirements concerning system's safety and reliability. Any failure could cause serious consequences that may result in massive material losses or endanger human safety. [Neu95] listed a large amount of accidents and disasters caused by errors in real-time systems. If it is possible to avoid these failures, large efforts and costs would be saved. In June 1996, the first flight of Ariane 5 launcher ended in failure caused by an overflow error. About 37 seconds after ignition, the rocket broke and self destruction was initiated. This accident led to a 370 million dollars cost [Liog6]. In December 1999, the last telemetry from Mars Polar Lander was sent. Just prior to cruise stage separation and the subsequent atmospheric entry, no further signals were received from the spacecraft. The most likely cause of this mishap was different interpretations of floating point data, which was implicitly specified as meters by NASA and implemented as feet by Rockwell Collins. This accident led to a 165 million dollars loss BCAA00. For systems where failure is unacceptable, reliable software is mandatory. Thus safe and efficient techniques are required to detect errors and thus avoid the accidents in such systems. The research context and main motivation of this work is how to design and implement safe and reliable real-time systems.

#### 1.2 Model Driven Engineering

Model-Driven Engineering (MDE) targets the improvement of the reliability and efficiency of the traditional software engineering by introducing models and early verification and validation  $(V \not e V)$  including the use of formal methods. It has evolved over the last 20 years and achieved success in many domains. Models are reduced/abstract representations of real systems that selectively remove some semantics to highlight the remaining expected properties from a given point of view. In the context of safety critical systems, models can be used during the requirement engineering process to derive the requirements for a system, during the

design process to describe the intended system to the implementation engineers, to verify and validate the properties, to automatically generate software, and also to document the system's structure and behavior after implementation.

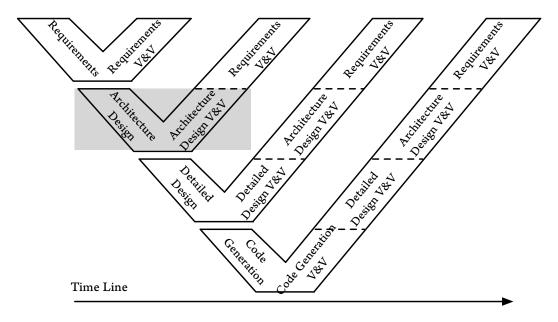

The V-model [FM95] is a software development process broadly adopted in the industry to illustrate the various activities involved in the development of software and their ideal sequencing. In this thesis, we rely on the multi V-model (see Fig. 1.2.1) proposed in the MeMVaTEx methodology [ABD+07, ABB+08] to illustrate the use of MDE for developing real-time systems. In order to generate reliable software, the V of V activities are performed at each phase of the system development lifecycle. The architecture design is the phase to define the hardware and software architectures which is referred to as high-level design. It should involve a brief and abstract functionality of each module, their interface relationships, dependability, architecture diagrams, etc. The detailed design model can also be called module or function design model, where the low-level design including detailed functional logic of the module can be specified.

Figure 1.2.1: V-Model in Model-Driven Engineering

From the current practice, the architecture is usually modeled using Domain Specific Languages (DSL) such as AADL and EAST-ADL or specific diagrams in a General Purpose Language (GPL) such as UML Composite Structure Diagram, while the detailed design is usually modeled using DSL such as Simulink/ Stateflow

and SCADE or specific GPL diagrams such as UML Activity, State Machine diagrams, or ALF (Action Language for Foundational UML). The main purpose of our work is to propose efficient and effective formal verification tools to ease the use of MDE when developing large scale real-time systems. More precisely, this work targets the use of UML-MARTE in the early phases of MDE, that corresponds to the *Architecture Design* phase in the multi V-model (the grey box part in Fig. 1.2.1).

#### 1.3 FORMAL METHODS

Formal Methods (FM) are mathematically based techniques for the specification, development and verification of software and hardware systems. The use of mathematical analysis can contribute to the reliability and robustness of a design [Hol97a]. Verification methodologies such as model checking, abstract interpretation, automated proof, etc. provide rules for inferring useful information from the specification. The conjunction of MDE and FM is a promising answer to the development of real-time systems, which makes it feasible to assess system's requirements since the early phases of system lifecycle and to iteratively improve the models according to the verification results.

However, automatic formal verification such as model checking faces the combinatorial explosion issue. This limits its application in industrial projects [CE82, HP94]. This issue is caused by the exponential number of generated states during system's execution that may easily exceed the amount of available computing or storage resources.

#### 1.4 Methodology: Property Driven Approach

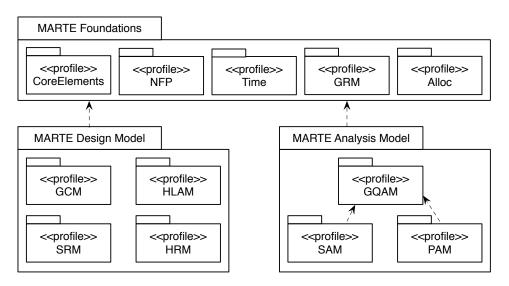

UML (Unified Modeling Language) [OMG11c] was developed to provide a common language for specification, modeling and documentation in the software development process in the 1990s. Today, UML is the industry standard for software modeling and specification. MARTE (Modeling and Analysis of Real-Time and Embedded Systems) [OMG09] provides support for specification, design, and  $V \not c V$  for real-time and embedded system. We use the term UML-MARTE in the whole thesis to indicate the specification language.

As UML is a semi-formal language which exhibits ambiguous and imprecise (in terms of mathematical precision) semantics, most of the requirements expressed in UML models cannot be directly assessed using formal methods. Therefore, providing a formal executable semantics is now a common approach used to

assess the user requirements in UML models. There exists a number of formal languages dealing with real-time analysis issues, such as Timed Automata [AD94] and several extended Petri Nets such as Timed Petri Nets [RH80, Zub91], Stochastic Timed Petri Net [FFN91], Time Petri Net (TPN) [MF76], etc. Our work relies on TPN as the execution model, and uses the TINA toolset as the analysis toolbox.

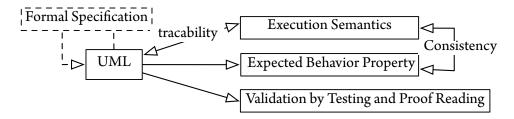

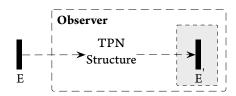

From the viewpoint of methodology, our work is based on the pioneering work [CCG<sup>+</sup>o<sub>7</sub>] by Combemale et al. Aimed to define all the steps from the property specification to effective verification, they introduced in [CCG<sup>+</sup>o<sub>7</sub>] a generic approach to define the operational semantics (a semantics of observable events) built upon the properties expressed at the metamodel level. They illustrated this contribution through a simple process description language: SIMPLEPDL on which a set of temporal properties were expressed. Property-driven means that the formal activities in the development process are based on the purpose of property-verification-ease. From a language point of view, a precise definition of model elements behavior allows the execution of behavioral models with respect to the intended requirements that must be assessed.

We follow the same methodology proposed by Combemale et al., and propose a property-driven framework dedicated to real-time property verification for UML-MARTE real-time designs. A key objective in our work is to assess this property driven approach on a large scale system relying on industrial modeling languages, requirements and use cases.

#### 1.5 REAL-TIME REQUIREMENTS

A real-time system is a system whose correct operation depends on both the results produced by the system and the time at which these results are produced [Som10]. The safety and reliability of real-time systems strongly depend on the satisfaction of its real-time requirements, in both qualitative and quantitative aspects. According to the survey collected from the industrial partners in several collaborative projects such as projects P <sup>1</sup>, TOPCASED <sup>2</sup>, OPEES <sup>3</sup>, QUARTEFT <sup>4</sup>, SPICES <sup>5</sup>, SPACIFY <sup>6</sup>, HiMOCO <sup>7</sup> and CESAR <sup>8</sup>, we list some examples of in-

<sup>&</sup>lt;sup>1</sup>http://www.open-do.org/projects/p/

<sup>&</sup>lt;sup>2</sup>http://www.topcased.org/

<sup>&</sup>lt;sup>3</sup>http://www.opees.org/

<sup>&</sup>lt;sup>4</sup>http://projects.laas.fr/fiacre/

<sup>&</sup>lt;sup>5</sup>http://www.spices-itea.org/public/news.php

<sup>&</sup>lt;sup>6</sup>http://spacify.gforge.enseeiht.fr/

<sup>&</sup>lt;sup>7</sup>http://www.systematic-paris-region.org/fr/projets/himoco

<sup>8</sup>http://www.cesarproject.eu/

dustrial real-time requirements in Table 1.5.1. To simplify the expression, we use  $E_1$ ,  $E_2$  and  $E_3$  to denote events, and [a,b] to denote a time interval.

Table 1.5.1: Examples of Real-Time Requirements

| No. | Real-Time Requirements                                                                                                  |

|-----|-------------------------------------------------------------------------------------------------------------------------|

| 1   | $E_{\scriptscriptstyle 1}$ must be sent after the reception of $E_{\scriptscriptstyle 2}$ .                             |

| 2   | A task cannot be executed after the emission of $E_1$ .                                                                 |

| 3   | The third occurrence of $E_1$ must be sent between the reception of $E_2$ and the emission of $E_3$ .                   |

| 4   | A system state holds for at least $n$ time unit ( $t.u.$ )                                                              |

| 5   | A system state holds for at most $n$ $t.u.$ after the emission of $E_1$ .                                               |

| 6   | If $E_1$ is sent, $E_2$ must be received after the emission of $E_1$ within [a,b].                                      |

| 7   | $E_1$ is received more than $n$ times after the reception of $E_2$ within [a,b].                                        |

| 8   | $E_{\scriptscriptstyle 1}$ and $E_{\scriptscriptstyle 2}$ must be sent simultaneously, within time tolerance $\delta$ . |

| 9   | The execution of a task must start after the reception of $E_1$ within [a,b] in each period.                            |

| 10  | If $E_{\rm 1}$ has been received, $E_{\rm 2}$ must be sent before the reception within [a,b] in each period.            |

| 11  | The worst case execution time of a task is <i>n t.u.</i> in each periodic execution.                                    |

In Table 1.5.1, the requirements 1 - 3 are related to the logical time, while 4 - 11 are related to the physical time. The requirements 9 - 11 are applicable to systems with periodic execution. Regarding the logical time requirements, there exist many works to specify and assess real-time properties using logic formulae. In the context of this thesis, we focus on the physical time (quantitative) properties in finite state concurrent reactive systems. These real-time requirements are critical, and thus their correctness must be guaranteed at any cost. Appropriate development processes, methods and tools are expected to enable the efficient verification, and to help the users to improve their designs when the errors have been detected. However, in today's highly competitive industrial market, the scale and complexity of safety critical real-time system are rapidly increasing due to the growth of functional and non-functional requirements. For instance, since Airbus A300, the number of software control systems has been increased to add new functionality such as flight envelop protection, ground proximity warning and traffic collision avoidance for improved safety [ITI07]. Consequently, verification of the real-time requirements for real-time system development is becoming more and more difficult and expensive. Therefore, although many progresses in the last 20 years, how to design and implement highly safety critical real-time system and in the meanwhile control

the development cost is still an open problem in both industry and academia.

#### 1.6 CHALLENGES

The key obstacle that prevents a wide application of model checking in the industry is the scalability issue. The classic verification methodology usually encounters scalability issue very quickly along with the growth of system size. A complex system usually has thousands and even millions of states and transitions. Although a huge part of the impossible transition firing sequences is eliminated during the building of system's behavior, the probable permutation of all others is still a very large number that easily causes combinatorial state space explosion.

Although many formal verification languages such as Petri Net [Pet62] and Automata [Sal85] and their analysis tools are theoretically mature enough, the efficient application for real size systems is still an open question. As the scalability issues introduced by the combinatorial explosion problem is still one of the bottlenecks, the industrial partners would rather verify and validate the requirements using traditional final system tests. Another key issue is effective fault analysis for the verification failures. Once an error has occurred, effective debug information is expected to be derived from the verification results to help the designers improve their designs. The challenges in this work can be summarized as the following five aspects:

- Challenge 1: Specification, implementation and validation of a real-time property specific execution semantics for UML-MARTE models that allows scalable verification. As revealed by a number of surveys, even the most recent versions of the UML specification suffer from multiple ambiguities, inconsistency and incompleteness regarding the semantics of the language for the formal verification purpose. This is a major problem for MDE because the semantics contained in the user models will be directly propagated to the verification models. A formal execution semantics should thus be defined. The manner the execution semantics is defined is one of the important factors that impact the verification efficiency, especially for the large scale system development. The optimal execution semantics only preserves minimal property-relevant semantics. This may reduce the risk of combinatorial state explosion problem during model checking.

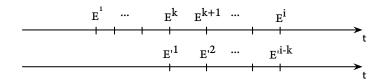

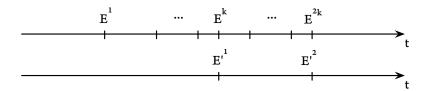

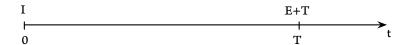

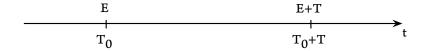

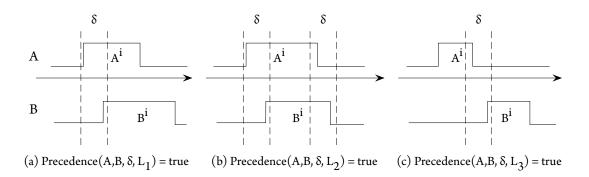

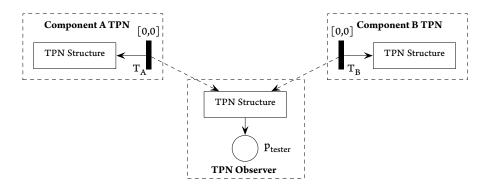

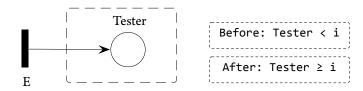

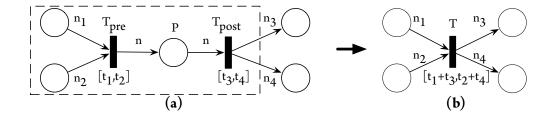

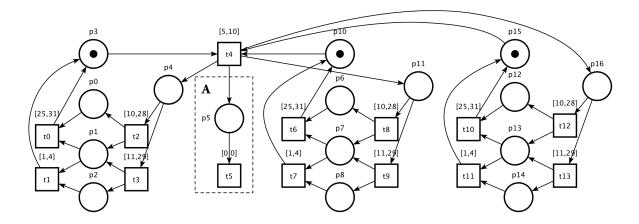

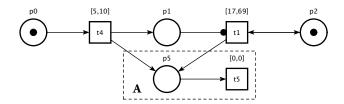

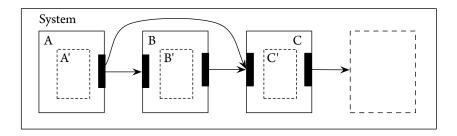

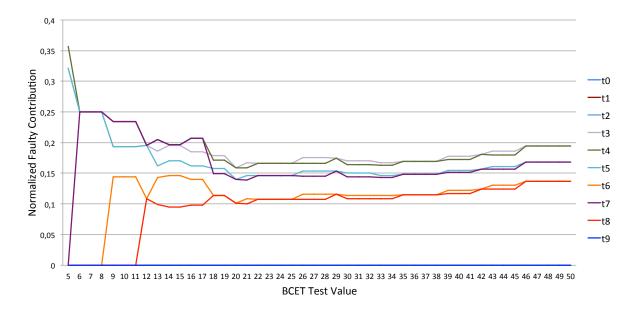

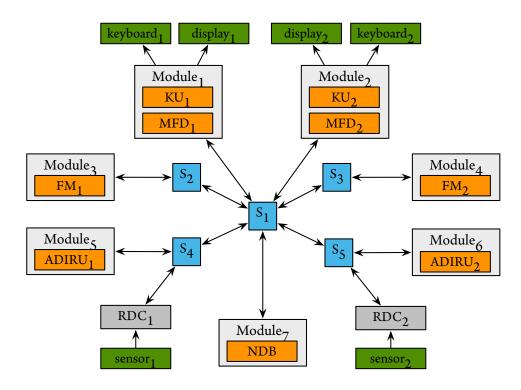

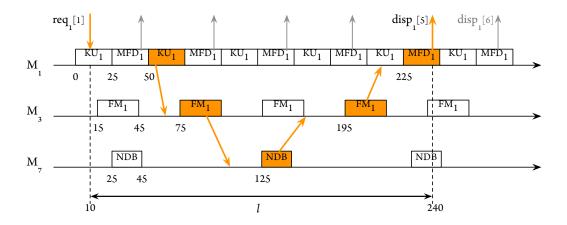

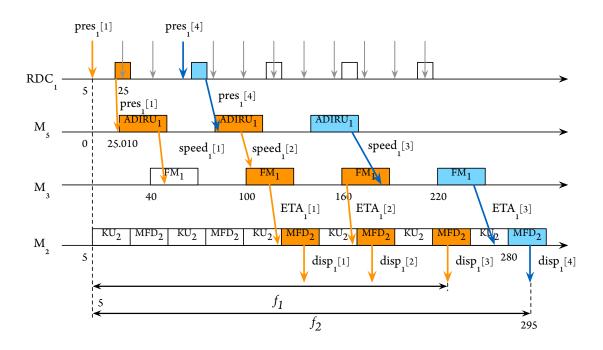

- Challenge 2: Need for practical real-time requirement specification method for verification purpose. Many studies have shown that most of the real-time requirements are composite proper-