### Modeling and design of neural network architectures for neural artificial-biological hybridization based on synchronous approach

Marino Rasamuel

#### ▶ To cite this version:

Marino Rasamuel. Modeling and design of neural network architectures for neural artificial-biological hybridization based on synchronous approach. Neural and Evolutionary Computing [cs.NE]. Université Côte d'Azur, 2023. English. NNT: 2023COAZ4055. tel-04278659

### HAL Id: tel-04278659 https://theses.hal.science/tel-04278659v1

Submitted on 10 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

SCIENCES ET

TECHNOLOGIES DE

L'INFORMATION ET DE

LA COMMUNICATION

Modélisation et conception par approche synchrone d'architectures neuronales hybrides biologique-artificiel

### **Marino RASAMUEL**

Laboratoire d'Électronique, Antennes et Télécommunications (LEAT)

Présentée en vue de l'obtention du grade de docteur en Électronique d'Université Côte d'Azur

**Dirigée par :** Benoît MIRAMOND, PR, LEAT, Université Côte d'Azur

Co-encadrée par : Daniel GAFFÉ, MCF,

LEAT, Université Côte d'Azur **Soutenue le :** 18-07-2023

#### Devant le jury, composé de :

Timothée Levi, PR, Université de Bordeaux Pierre Boulet, PR, Université de Lille Bertrand Granado, PR, Sorbonne Université

Dumitru Potop-Butucaru, CR, INRIA Gilles Bernot, PR, Université Côte d'Azur

## Modélisation et conception par approche synchrone d'architectures neuronales hybrides biologique-artificiel

Modeling and design of neural network architectures for neural artificial-biological hybridization based on synchronous approach

#### Marino RASAMUEL

$\triangleright \triangleleft$

#### Jury:

#### Président du jury

Timothée Levi, PR, Université de Bordeaux

#### **Rapporteurs**

Pierre Boulet, PR, Université de Lille Bertrand Granado, PR, Sorbonne Université

#### **Examinateur**

Dumitru Potop-Butucaru, CR, INRIA

#### Directeur de thèse

Benoît MIRAMOND, PR, LEAT, Université Côte d'Azur

#### Co-encadrant de thèse

Daniel Gaffé, MCF, LEAT, Université Côte d'Azur

#### Membre invité

Gilles Bernot, PR, Université Côte d'Azur

| <br>Université Côte d'Azur |

|----------------------------|

#### Marino RASAMUEL

Modélisation et conception par approche synchrone d'architectures neuronales hybrides biologique-artificiel

xiii+199 p.

## Modélisation et conception par approche synchrone d'architectures neuronales hybrides biologique-artificiel

#### Résumé

Alors que les Réseaux de Neurones Artificiels (RNA) continuent de progresser dans des domaines tels que l'apprentissage automatique, la robotique, les véhicules autonomes et le diagnostic de santé, un nouveau cadre d'application gagne du terrain à la fois dans les secteurs académique et industriel : la Neurobiohybridation. Ce domaine cherche à établir des connexions entre des neurones artificiels et biologiques dans le but de comprendre et potentiellement de réparer ou remplacer des fonctions cérébrales perdues suite à des maladies ou des accidents. Dans cette perspective, le développement de réseaux de neurones artificiels inspirés biologiquement, souvent appelés Réseaux de Neurones à Spikes (SNNs), est essentiel pour améliorer la compatibilité entre les systèmes neuronaux artificiels et biologiques. Cette thèse s'inscrit dans ce contexte en utilisant l'approche synchrone pour modéliser, mettre en œuvre et simuler des SNNs bio-inspirés et biomimétiques. En utilisant des vérificateurs de modèles, qui permettent de prouver ou d'extraire des propriétés des systèmes de manière formelle, notre objectif est d'acquérir une compréhension plus complète des comportements biologiques dans le future. Pour la première fois dans ce contexte, nous utilisons le langage Light Esterel pour atteindre nos objectifs. Nous démontrons son potentiel dans la mise en oeuvre de modèles neuronaux, initiant une bibliothèque de modèles pour explorer différents types de SNNs. Tout au long de cette thèse, nous avons développé un cadre complet basé sur Light Esterel pour modéliser, simuler et mettre en oeuvre divers modèles de SNNs. Pour aborder les expériences de neurobiohybridation, nous avons développé notre propre architecture matérielle, SynchNN, capable d'exécuter en temps réel des SNNs récurrents en utilisant notre bibliothèque de modèles. L'environnement de modélisation que nous avons développé est complété par un framework de simulation, en cours de développement, visant à réaliser des expériences de neurobiohybridation à l'avenir.

**Mots-clés :** Réseaux de neurones impulsionnels, Approche Synchrone, Langage Light Esterel, FPGA, neurobiohybridation

## Modeling and design of neural network architectures for neural artificial-biological hybridization based on synchronous approach

#### **Abstract**

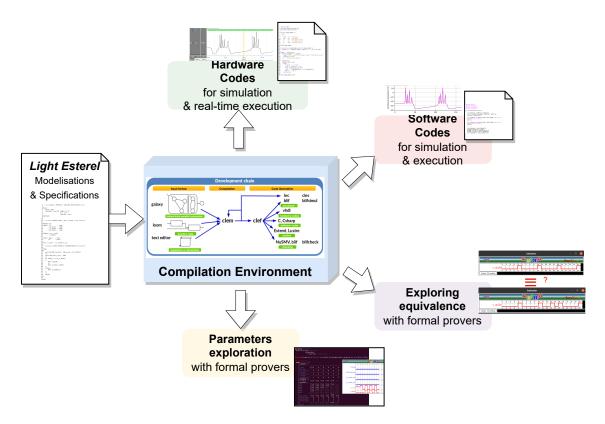

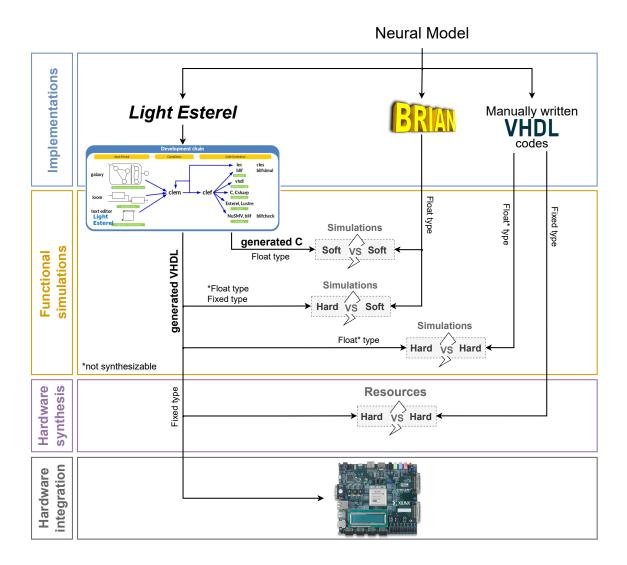

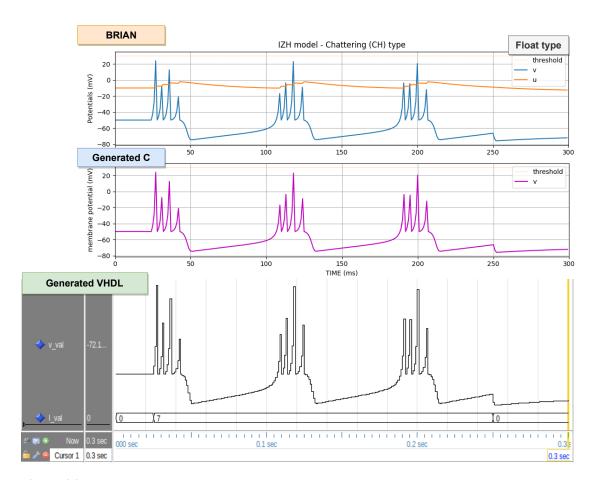

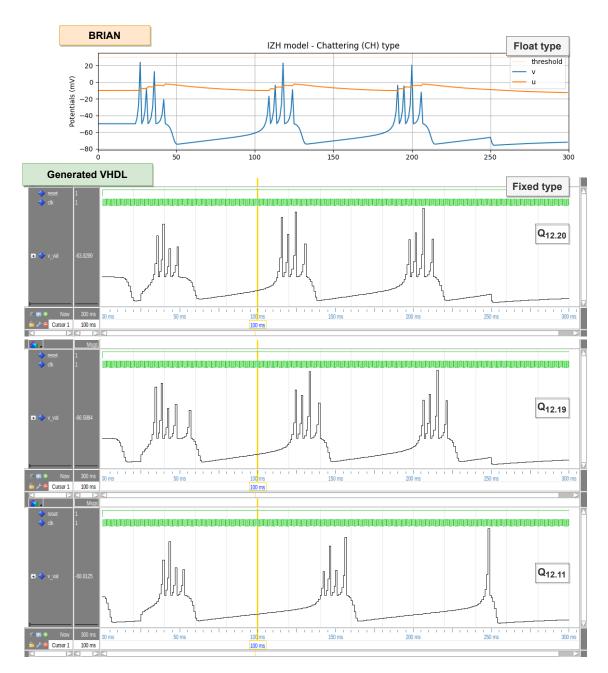

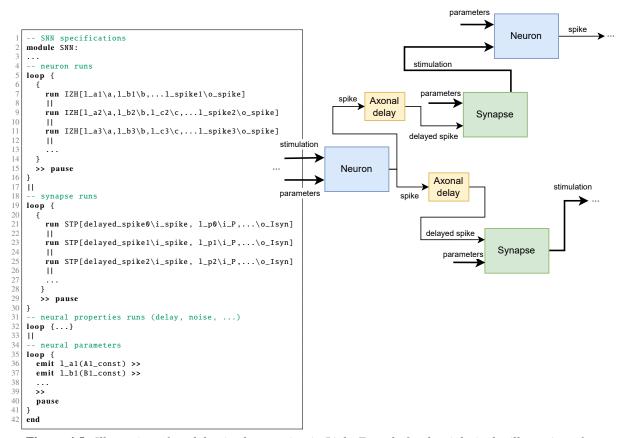

As Artificial Neural Networks (ANNs) continue to advance in fields like machine learning, robotics, autonomous vehicles, and healthcare diagnostics, an application domain is gaining attraction in both academic and industrial sectors: Neurobiohybridization. This domain seeks to establish connections between artificial and biological neurons with the goal of understanding and potentially repairing or replacing lost brain functions due to disease or accidents. In pursuit of this, the development of biologically inspired artificial neural networks, often referred to as Spiking Neural Networks (SNNs), is essential to enhance compatibility between artificial and biological neural systems. This thesis fits into this context by using the synchronous approach to model, implement, and simulate bio-inspired and biomimetic SNNs. Leveraging model checkers, that allow to prove or extract properties in systems in formal manner, our aim is to gain a more comprehensive understanding of biological behaviors in the future. For the first time in this context, we utilize the Light Esterel language to achieve our objectives. We demonstrate its potential in implementing neural models, initiating a library of models for exploring different types of SNNs. Throughout this thesis, we developed an entire framework based on Light Esterel in order to model, simulate and implement various SNN models. To address neurobiohybridization experiments, we developped our own hardware architecture, SynchNN, capable of executing recurrent SNNs in real-time using our library of models. This framework we developed is completed with an on-going simulation framework aiming to conduct neurobiohybrid experiments in the future.

**Keywords:** Spiking Neural Networks, Synchronous Approach, Light Esterel language, FPGA, neurobiohybridization

### Remerciements

Je tiens à exprimer tout d'abord ma sincère gratitude envers mon directeur de thèse, Benoît Miramond, pour l'opportunité exceptionnelle qu'il m'a offerte de m'engager dans la recherche. Son expertise, sa passion pour son domaine et ses conseils scientifiques ont été une source constante d'inspiration tout au long de ce voyage académique. Cependant, ce qui distingue véritablement Benoît va au-delà du rôle traditionnel d'un directeur de thèse. Il a été là dans les moments les plus difficiles, continuant à me soutenir malgré tout, avec une compréhension profonde et une amitié sincère. Il est un modèle pour sa force et sa générosité. Pour tout cela, je lui en suis infiniment reconnaissant.

Je souhaite également adresser mes remerciements les plus chaleureux à mon encadrant de thèse, Daniel Gaffé. En master, il a cru en mes capacités et m'a poussé à donner le meilleur de moi-même. Son rôle dans mon évolution académique a été fondamental. Les discussions parfois animées que nous avons eues ont enrichi cette expérience académique de manière significative, et je suis reconnaissant d'avoir pu les partager avec lui. Merci, Daniel, pour le temps que tu m'as consacré, ton soutien inébranlable et pour m'avoir poussé jusqu'à la fin de ce voyage.

Ensuite, je tiens à exprimer ma sincère gratitude envers tous les membres du Jury pour avoir consacré leur précieux temps à l'évaluation de mes travaux. Je voudrais adresser mes remerciements les plus sincères à Pierre Boulet et Bertrand Granado d'avoir accepté le rôle de rapporteurs pour ma thèse. Je tiens également à exprimer un remerciement tout particulier à Timothée Levi pour sa bienveillance et son accueil chaleureux au Japon. Je suis honoré de l'avoir eu en tant que président de mon Jury, ce qui a couronné magnifiquement la conclusion de mon travail.

Évidemment, ces années passées au LEAT m'ont permis de rencontrer et de tisser des liens forts avec plusieurs personnes exceptionnelles que je tiens à remercier du fond du cœur. Leur amitié et leur soutien ont rendu ces années académiques particulièrement agréables. Je tiens à exprimer ma reconnaissance spéciale à Roland Kromes, un ami extraordinaire, un précieux collègue de bureau, et une personne formidable avec qui chaque instant passé au bureau était empreint d'une dose supplémentaire d'amusement. Je m'excuse sincèrement de ne pas pouvoir citer tout le monde ici, mais je vous remercie d'avoir partagé cette aventure avec moi et d'avoir contribué à en faire une expérience mémorable.

Enfin, je tiens à exprimer ma profonde gratitude envers ma famille, qu'elle soit près ou loin, pour leur soutien inébranlable qui a été une force constante dans ma vie. Ma sœur, Mahefa, a apporté un soutien précieux, parfois différent de ce qui est standard, mais toujours inestimable. Mon frère, Matio, pour sa précieuse présence. Mes nièces, Mélina et Laurina, ont été des rayons de soleil, apportant des rires et de la joie même lors des moments les plus difficiles. Spécialement à ma mère, Jeanne, mes mots ne peuvent que gratter la surface de son sacrifice extraordinaire. Aujourd'hui, alors qu'elle lutte courageusement contre la maladie d'Alzheimer, son amour inconditionnel continue de briller comme une lumière dans nos vies. Je lui suis infiniment reconnaissant, et c'est désormais à notre tour de prendre soin d'elle, avec la même tendresse et le même dévouement qu'elle a toujours eu à notre égard.

## **Contents**

| 1 | Intr | oductio        | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   |

|---|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 1.1  | Project        | t context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3   |

|   | 1.2  | Thesis         | context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3   |

|   | 1.3  | Proble         | matics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6   |

|   | 1.4  | Object         | ives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7   |

|   | 1.5  | Contril        | butions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7   |

|   | 1.6  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8   |

| 2 | Neu  | ral Netv       | vorks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9   |

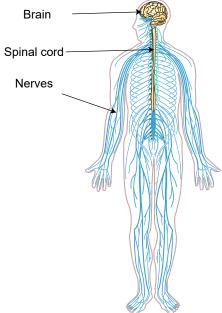

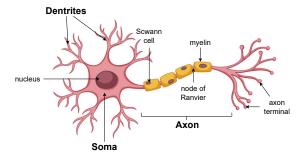

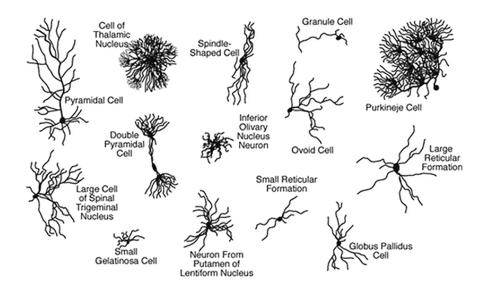

|   | 2.1  | Neuron         | <mark>1</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1   |

|   |      | 2.1.1          | Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   |

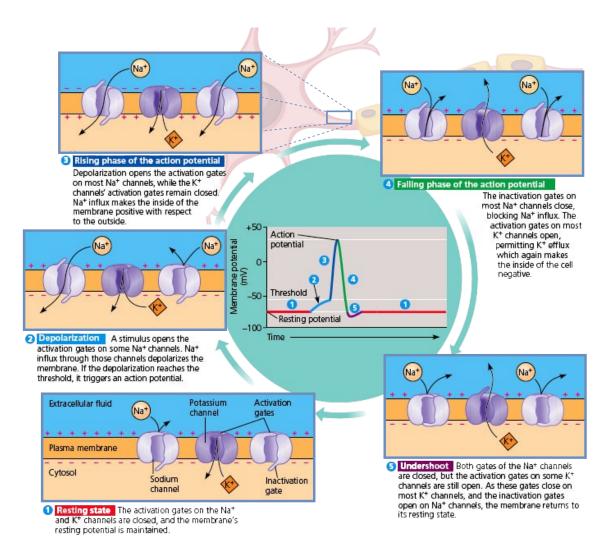

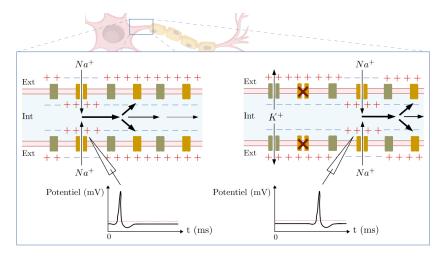

|   |      | 2.1.2          | Action potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3   |

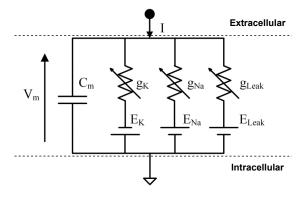

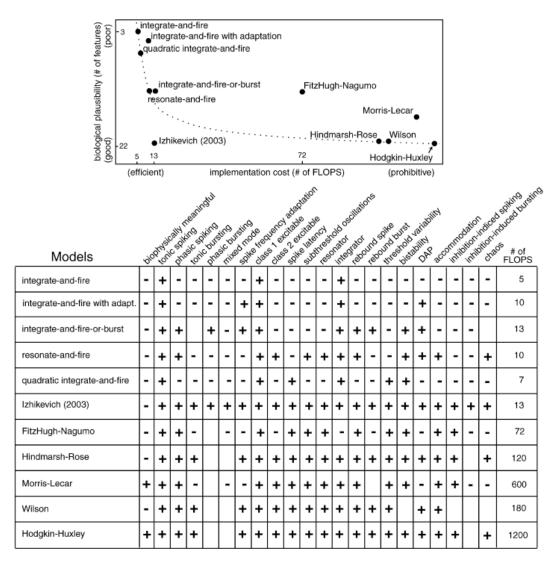

|   |      | 2.1.3          | Spiking neuron models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   |

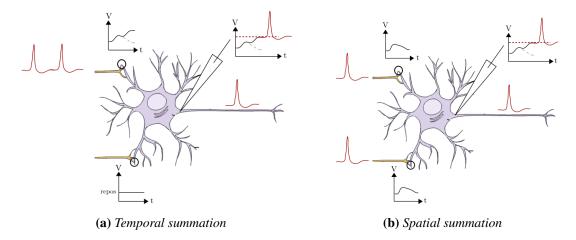

|   | 2.2  | Models         | s of neural properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4   |

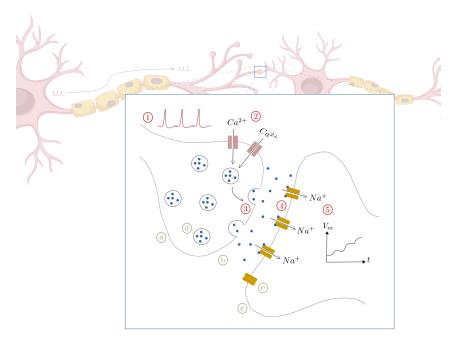

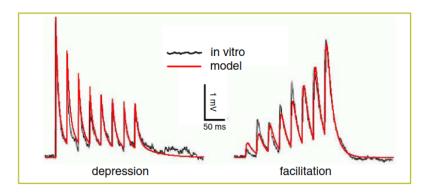

|   |      | 2.2.1          | AMPA and GABA dynamics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4   |

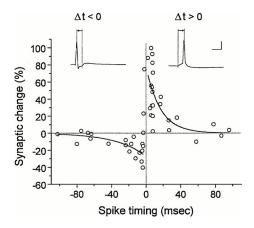

|   |      | 2.2.2          | Plasticity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4   |

|   |      | 2.2.3          | Axonal delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|   |      | 2.2.4          | Biological noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8   |

|   | 2.3  | Spikin         | g Neural Network (SNN) behavorial simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9   |

|   |      | 2.3.1          | Software approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|   |      | 2.3.2          | Hardware approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|   | 2.4  |                | cing artificial with biological neurons: Neurobiohybridization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   |      | 2.4.1          | Applications and objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

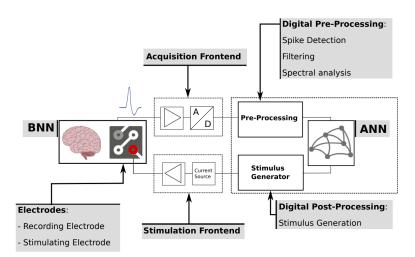

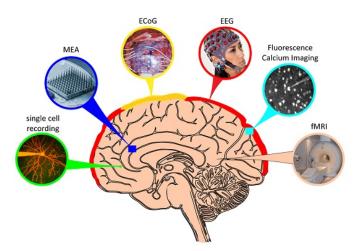

|   |      | 2.4.2          | Technologies and methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|   |      | 2.4.3          | Some limitations and challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   | 2.5  |                | ision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 3 | Sync | chronou        | is approach 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q   |

| J | 3.1  | Paradi         | THE THE STATE OF T |     |

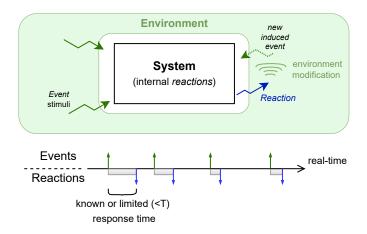

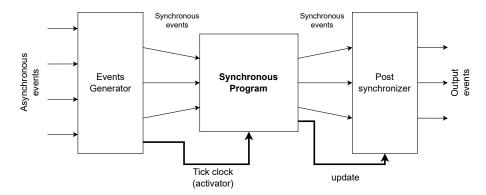

|   | 3.1  | 3.1.1          | Real-time reactive system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _   |

|   |      | 3.1.1          | Some programming approaches and their limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

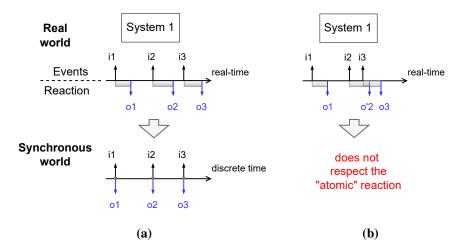

|   |      | 3.1.2          | Synchronous approach paradigm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|   |      | 3.1.3          | Synchronous languages or models overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

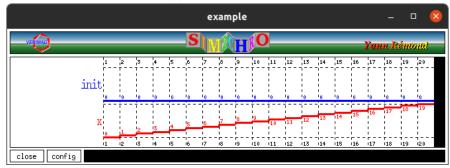

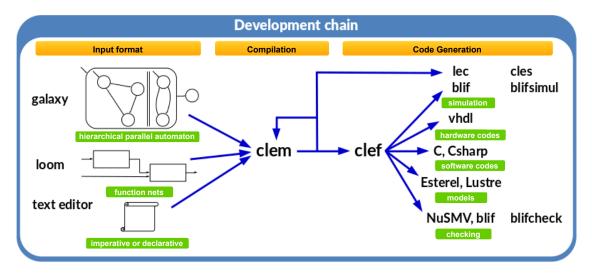

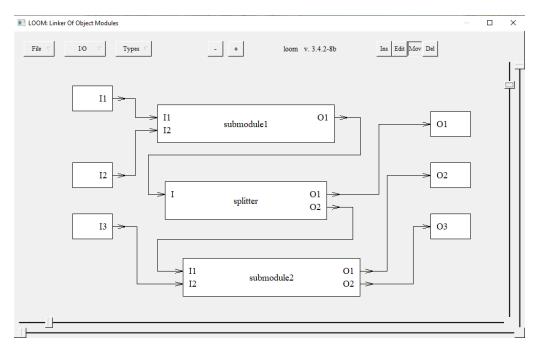

|   | 3.2  |                | oosen language: Light Esterel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

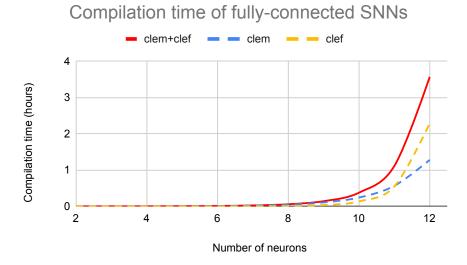

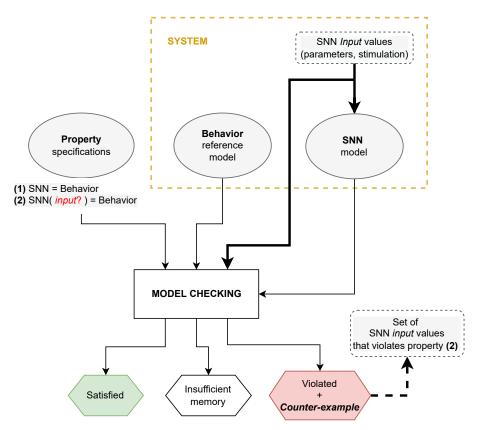

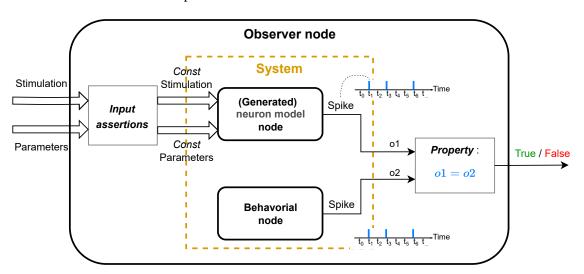

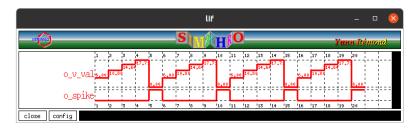

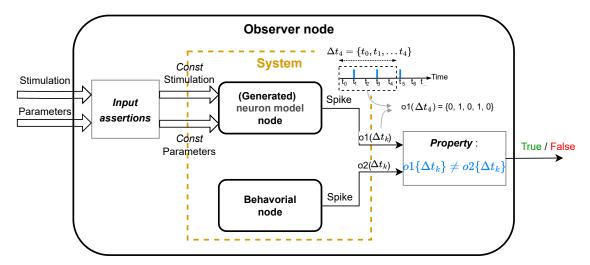

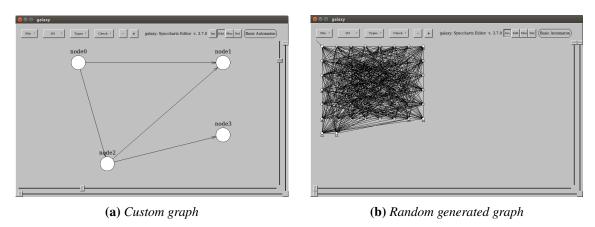

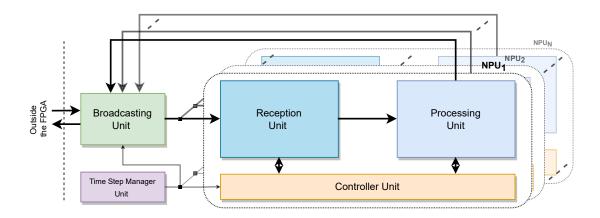

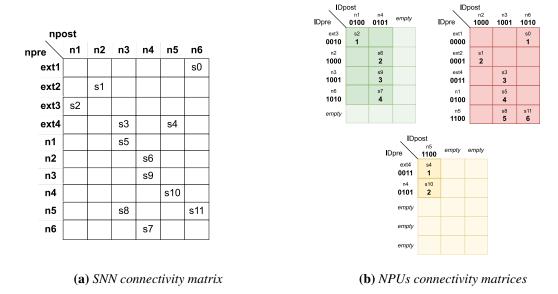

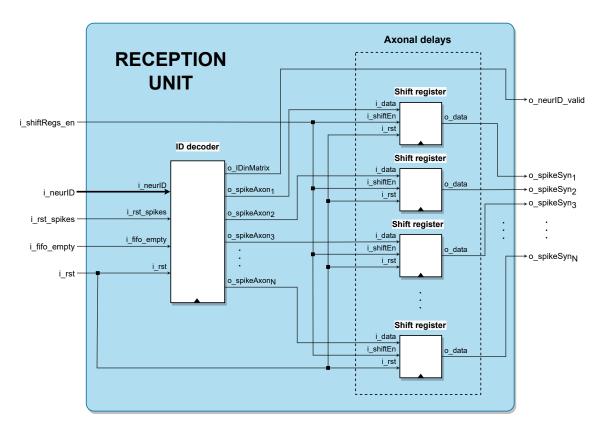

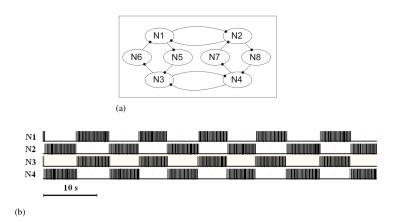

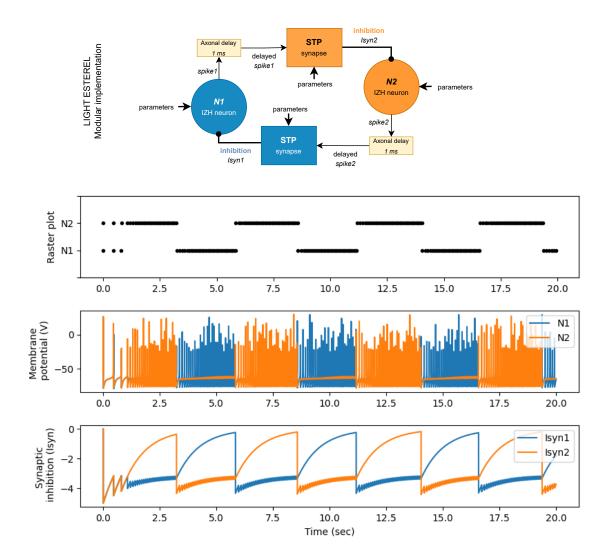

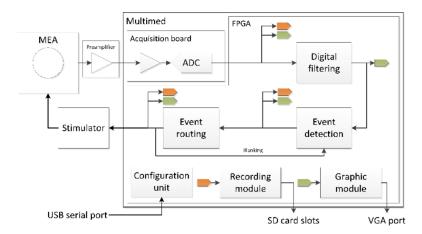

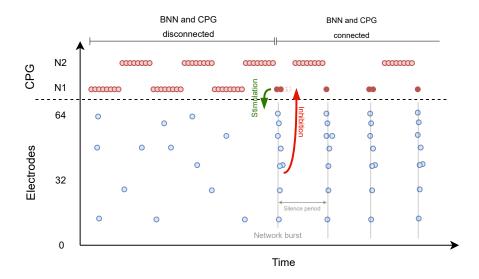

|   | 5.2  | 3.2.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |