# Modélisation du comportement temporel du pipeline pour le calcul de WCET

Zhenyu Bai

### ▶ To cite this version:

Zhenyu Bai. Modélisation du comportement temporel du pipeline pour le calcul de WCET. Réseaux et télécommunications [cs.NI]. Université Paul Sabatier - Toulouse III, 2023. Français. NNT: 2023TOU30053. tel-04288859

## HAL Id: tel-04288859 https://theses.hal.science/tel-04288859v1

Submitted on 16 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

# En vue de l'obtention du DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par l'Université Toulouse 3 - Paul Sabatier

# Présentée et soutenue par Zhenyu BAI

Le 12 mai 2023

# Modélisation du Comportement Temporel du Pipeline pour le Calcul de WCET

Ecole doctorale : **EDMITT - Ecole Doctorale Mathématiques, Informatique et Télécommunications de Toulouse**

Spécialité : Informatique et Télécommunications

Unité de recherche :

IRIT : Institut de Recherche en Informatique de Toulouse

Thèse dirigée par

**Christine ROCHANGE et Hugues CASSE**

Jury

Mme Isabelle PUAUT, Rapporteure

M. Mathieu JAN, Rapporteur

M. Jean-Paul BODEVEIX, Examinateur

M. Pascal RAYMOND, Examinateur

Mme Christine ROCHANGE, Directrice de thèse

M. Hugues CASSé, Co-directeur de thèse

# Modélisation du comportement temporel du pipeline pour le calcul de WCET

Zhenyu Bai

16 mai 2023

### Résumé

Le calcul du pire temps d'exécution (WCET, Worst Case Execution Time) est une phase indispensable pour la vérification et la certification des systèmes embarqués strictement temps-réel. Le temps d'exécution des programmes, dont l'évaluation nécessitant une précision au niveau du cycle machine, est le produit du fonctionnement de la micro-architecture du processeur qui exécute le programme. Cependant, les processeurs modernes tendent à être de plus en plus complexes : ils sont équipés de pipelines et de mécanismes d'accélération comme les mémoires caches, la prédiction de branchement, etc.

Ces mécanismes introduisent des *variations temporelles* qu'il est nécessaire de prendre en compte lors du calcul du temps d'exécution. Par exemple, la latence d'accès à une mémoire cache est différente qu'elle contient la donnée (*Hit*) ou non (*Miss*).

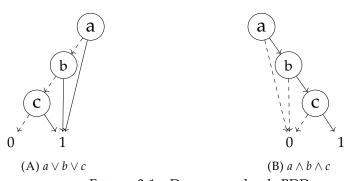

En combinant le pipeline et les mécanismes d'accélération, le temps d'exécution devient une fonction complexe des instructions, de la structure du pipeline et des variations temporelles. Dans cette thèse, nous proposons une nouvelle structure de données nommée XDD (*eXecution Decision Diagram*) qui permet de représenter efficacement et précisément la relation entre le temps d'exécution et les variations temporelles. Comme son nom l'indique, cette représentation est inspirée des BDD (*Binary Decision Diagrams*).

À l'aide des XDD, nous proposons un modèle de calcul du temps dans le pipeline qui représente de manière compacte cette fonction temporelle complexe sous forme d'un ensemble de matrices associées aux blocs d'instructions machine composant le programme. Il est alors possible de calculer l'ensemble des états temporels tout au long des chemins d'exécution du programme de manière efficace et d'en déduire le WCET.

Nous avons expérimenté ce modèle sur des benchmarks classiques (TACLe) pour des processeurs avec exécution dans l'ordre du programme, ainsi que pour des processeurs contenant des ressources allouées dans le désordre (bus mémoire). Les résultats expérimentaux montrent une amélioration significative de la précision du WCET calculé par rapport à la méthode originale utilisée dans l'outil OTAWA, ainsi qu'une amélioration importante des performances de calcul.

### **Abstract**

The computation of the Worst-Case Execution Time (WCET) of tasks is an essential step for the verification and certification of critical real-time embedded systems. The execution time at the precision of the processor cycle is determined by the microarchitecture of processor executing the programs. However, modern processors tend to be more and more complex: they are pipelined and equipped with several *acceleration mechanisms* such as caches, branch predictors, etc.

These mechanisms introduce *timing variations* that must be taken into account when computing the execution time. For example, the latency of a cache access may result in a *Hit* if the data is present in the cache, or in a *Miss* otherwise.

By combining the pipeline and the acceleration mechanisms, the execution time becomes a complex function of instructions, pipeline structure, and timing variations. In this thesis, we present a new data structure named XDD (*eXecution Decision Diagram*) which allows to efficiently and accurately represent the relationship between execution time and timing variations. As its name suggests, it is inspired by BDDs (*Binary Decision Diagrams*).

Using XDDs, we present a model for computing the execution time in the processor pipeline, which represents efficiently this complex function of execution time by a set of matrices associated with the blocks of machine instructions composing the program. It is then possible to compute efficiently the set of timing states along the execution paths of the program and to deduce the WCET therefrom.

We experimented this model on classical benchmarks (TACLe), for in-order processors, as well as for processors containing out-of-order resources (memory bus). The experimental results show a significant improvement in the accuracy of the computed WCET compared to the original method used in the OTAWA tool as well as a significant improvement in terms of analysis time.

### Remerciements

Je tiens à remercier d'abord les trois personnes qui m'ont énormément aidé et m'ont accompagné avec gentillesse tout au long de ma thèse : Docteur Hugues Cassé, Professeur Christine Rochange et Docteur Thomas Carle. Ils ont toujours été là pour m'aider dans la recherche, dans la rédaction des articles, dans l'enseignement. Ils m'ont transmis, en se servant d'exemples, leurs valeurs, leur goût, dans l'enseignement et dans la recherche. Je me sens très heureux de commencer ma carrière académique, avec de la passion, grâce à eux. D'autre part, ils sont non seulement des encadrants et des collègues qui m'ont appris les compétences professionnelles, mais ils sont toujours disponibles pour discuter, pour m'écouter comme des amis, comme de la famille.

Tout d'abord, Hugues Cassé m'a encadré tout au long de ma thèse. Étant mon cocodirecteur, il a toujours été là pour m'apprendre, pour m'aider, pour m'encourager, pour me transmettre sans réserve ses expériences et ses savoir-faire. Il s'est toujours montré gentil et patient pour m'aider dans la rédaction des articles, spécialement cette thèse. Cela a été plaisant de discuter de la technique, passionnant de faire de la recherche avec lui et amusant d'encadrer des projets d'enseignement avec lui.

Christine Rochange, ma directrice de thèse, a toujours été disponible pour m'aider dans les affaires administratives, pour me donner des conseils d'enseignement, de recherche et pour ma carrière professionnelle.

Je dois absolument remercier également mon collègue, Thomas Carle, qui est toujours présent pour m'aider dans la rédaction des articles, pour m'écouter et pour m'encourager avec ses magnifiques blagues et plaisanteries.

Je voudrais aussi remercier les autres membres de l'équipe TRACES pour leur gentillesse. Ce n'était que du plaisir de travailler avec eux.

Je profite de cette opportunité pour également remercier les rapporteurs, Monsieur Mathieu Jan et Madame Isabelle Puaut, ainsi que tous les examinateurs du jury : Monsieur Jean-Paul Bodeveix et Monsieur Pascal Raymond, de prendre votre temps précieux pour lire ma thèse et pour d'assister à ma soutenance.

# Table des matières

| Re | emerc | riements                                                             | 7  |

|----|-------|----------------------------------------------------------------------|----|

| 1  | Intr  | oduction                                                             | 1  |

|    | 1.1   | Pourquoi le calcul du WCET est-il difficile?                         | 2  |

|    |       | 1.1.1 Les évènements                                                 | 3  |

|    |       | 1.1.2 La source des évènements                                       | 4  |

|    |       | 1.1.3 Les évènements dans le pipeline                                | 5  |

|    |       | 1.1.4 Les ressources allouées dans le désordre et les anomalies tem- |    |

|    |       | porelles                                                             | 6  |

|    | 1.2   | Objectif de la thèse                                                 | 7  |

|    | 1.3   | Plan                                                                 | 7  |

| 2  | État  | de l'art                                                             | 9  |

|    | 2.1   | Concepts pour l'analyse statique                                     | 9  |

|    |       | 2.1.1 Le Graphe de Flot de Contrôle                                  | 9  |

|    |       | 2.1.2 Abstraction                                                    | 9  |

|    | 2.2   | Interprétation Abstraite                                             | 10 |

|    |       | 2.2.1 La sémantique                                                  | 11 |

|    |       | 2.2.2 La sémantique collectrice                                      | 11 |

|    |       | 2.2.3 La conception des abstractions                                 | 12 |

|    | 2.3   | La structure de l'analyse de WCET                                    | 14 |

|    |       | 2.3.1 Construction du CFG                                            | 14 |

|    |       | 2.3.2 Les analyses globales                                          | 16 |

|    |       | 2.3.3 La méthode IPET                                                | 16 |

|    |       | 2.3.4 Analyse de pipeline                                            | 18 |

|    |       | 2.3.5 Discussion                                                     | 18 |

|    | 2.4   | Vérification de modèles                                              | 19 |

|    | 2.5   | AbsInt                                                               | 20 |

|    |       | 2.5.1 Le Modèle de pipeline dans <i>aiT</i>                          | 20 |

|    |       | 2.5.2 Performances d'aiT                                             | 21 |

|    |       | Compactage de la représentation d'état et de transition              | 21 |

|    |       | Suppression des états                                                | 22 |

|    |       | Pipeline d'exécution strictement dans l'ordre                        |    |

|    |       | Discussion                                                           |    |

|    | 2.6   | Graphe d'exécution                                                   | 23 |

|    |       | *                                                                    |    |

|    | 2.7   | Conclusion                                                           | 27 |

|    |       |                                                                      |    |

| 3  | `     | gramme de Décision d'Exécution – XDD                                 | 29 |

|    | 3.1   | Diagramme de Décision Binaire                                        | 30 |

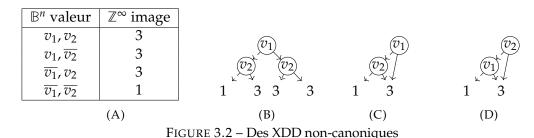

|    | 3.2   | Représenter le temps avec des XDD                                    | 31 |

|    | 0.0   | 3.2.1 Canonicité                                                     | 32 |

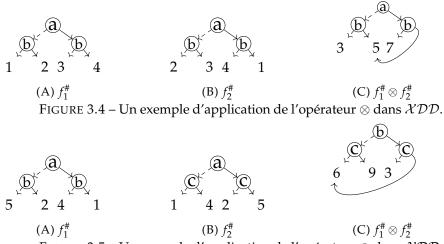

|    | 3.3   | Opérateurs sur le domaine $\mathcal{XDD}$                            | 35 |

10 Table des matières

|   |     | Canonicité du XDD produit                                                  | 37           |

|---|-----|----------------------------------------------------------------------------|--------------|

|   |     | Validité des opérateurs                                                    | 38           |

|   | 3.4 | Optimisations des XDD                                                      | 41           |

|   |     | 3.4.1 Mémoïsation                                                          | 41           |

|   |     | 3.4.2 Ordre des variables                                                  | 41           |

|   |     | 3.4.3 Optimisation des opérateurs sur $\mathcal{XDD}$                      | 42           |

|   | 3.5 | Algèbre linéaire sur le demi-anneau $\mathcal{XDD}$                        | 45           |

|   | 3.6 | Conclusion                                                                 | 47           |

| 4 | Ana | lyse de pipeline avec les XDD                                              | 49           |

|   | 4.1 |                                                                            | 50           |

|   | 4.2 | Le calcul de temps avec le graphe d'exécution                              | 55           |

|   | 4.3 | Les évènements dans les graphes d'exécution                                | 56           |

|   | 4.4 | Évaluation                                                                 | 59           |

|   |     | 4.4.1 Mise en place de l'expérience                                        | 59           |

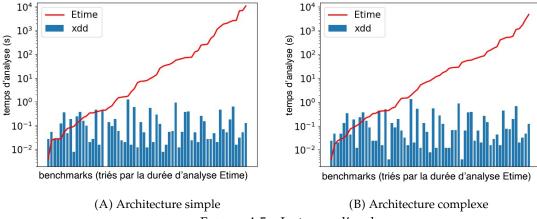

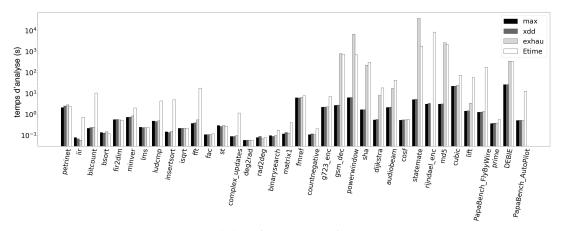

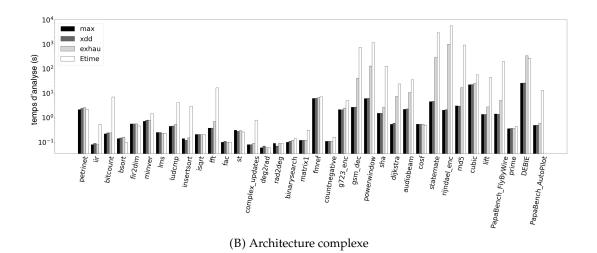

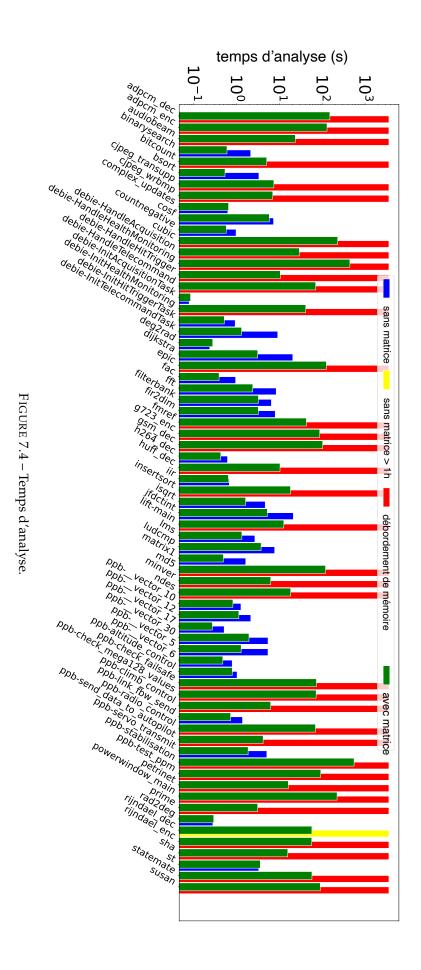

|   |     | 4.4.2 Le temps d'analyse                                                   | 61           |

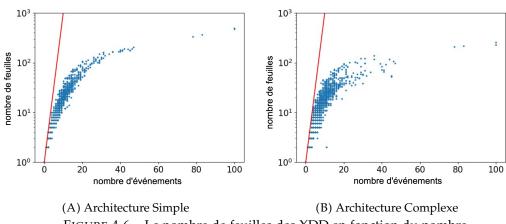

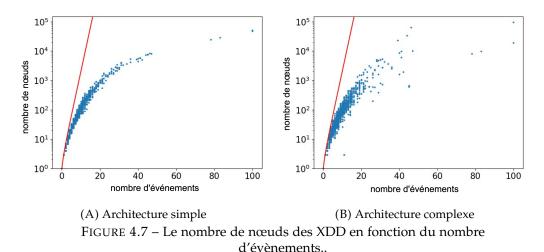

|   |     | 4.4.3 La compacité des XDD                                                 | 62           |

|   | 4.5 | Conclusion                                                                 | 63           |

| _ |     |                                                                            | <b></b>      |

| 5 | 5.1 | élioration de la méthode IPET  La méthode IPET avec plusieurs temps par BB | <b>65</b> 65 |

|   | 5.2 | Partitionnement des configurations                                         | 66           |

|   | 5.3 | Effet de maximisation                                                      | 67           |

|   | 5.4 | Borner les compteurs de parties                                            | 70           |

|   | 0.1 | 5.4.1 Contraintes sur les parties entièrement bornées                      | 71           |

|   |     | 5.4.2 Contraintes sur les parties partiellement bornées                    | 71           |

|   | 5.5 | Génération du système ILP avec des XDD                                     | 73           |

|   | 5.6 | Évaluation                                                                 | 76           |

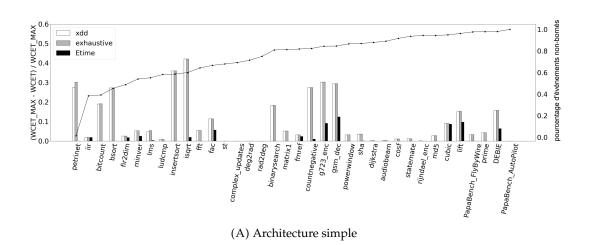

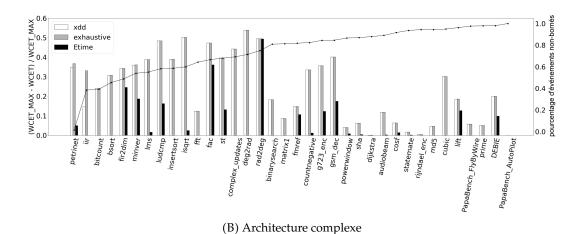

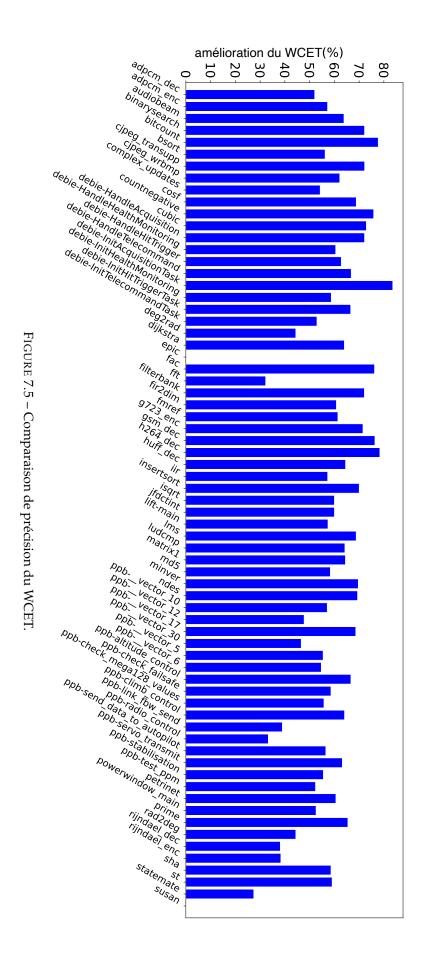

|   | 0.0 | 5.6.1 Précision                                                            | 77           |

|   |     | 5.6.2 Temps d'analyse                                                      | 78           |

|   |     | 5.6.3 Conclusion                                                           | 79           |

|   |     |                                                                            | 04           |

| 6 |     | lyse de pipeline basée sur les ressources                                  | <b>81</b> 81 |

|   | 6.2 | État temporel du pipeline                                                  | 84           |

|   | 6.3 | Calcul avec des matrices                                                   | 86           |

|   | 6.4 | Analyse de pipeline au niveau du CFG                                       | 88           |

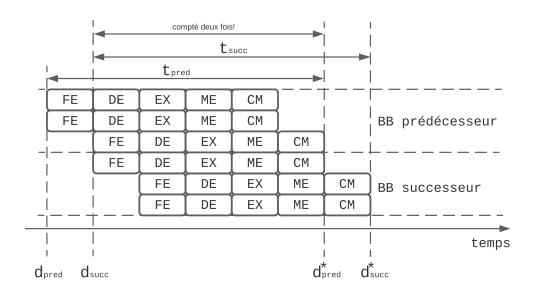

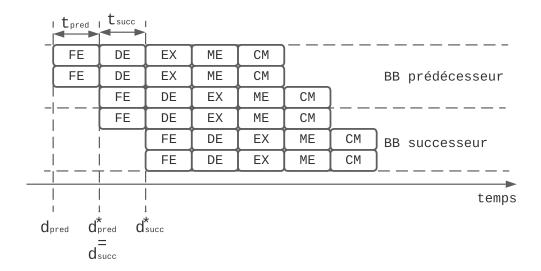

|   | 0.4 | 6.4.1 Début et fin de BB                                                   | 89           |

|   |     | Le contexte                                                                | 90           |

|   |     | Analyse de pipeline sur le CFG                                             | 92           |

|   |     | Effet du rebasage sur le contexte                                          | 92           |

|   | 6.5 | Génération des évènements dans les boucles                                 | 93           |

|   | 6.6 | Analyse du pipeline sur le CFG                                             | 94           |

|   | 6.7 | Conclusion                                                                 | 95           |

|   |     |                                                                            |              |

| 7 |     | délisation des ressources allouées dans le désordre                        | 97           |

|   | 7.1 | Ordre d'allocation du bus partagé FCFS                                     | 98           |

|   | 7.2 | Ordonnancement du bus avec les XDD                                         |              |

|   | 7.3 | Algorithme de contention                                                   |              |

|   | 7.4 | Évaluation                                                                 |              |

|   |     | 7.4.1 Mise en place                                                        | 105          |

Table des matières 11

|   |     | 7.4.2 Nombre d'états temporels |

|---|-----|--------------------------------|

|   | 7.5 | Temps d'analyse                |

|   | 7.6 | Précision                      |

| 8 |     | lusion 113                     |

|   | 8.1 | Résumé des travaux réalisés    |

|   | 8.2 | Perspectives de recherche      |

# Liste des Abréviations

WCET Worst Case Execution Time

ISA Instruction Set Architecture

FCFS First-Come-First-Served

CFG Control Flow Graph

BB Basic Block

IPET Implicit Path Enumeration Techniques

ILP Integer Linear ProgrammingBDD Binary Decision Diagram

FIFO First-In-First-Out

DAG Directed Acyclic GraphXDD eXecution Decision DiagramROBDD Reduced and Ordered BDD

BFS Breadth-First Search

# Liste des Symboles

$1_{\boxtimes}$

$e \in \mathcal{E}$ Évènement et l'ensemble des évènements  $a \in V_{CFG}$ Bloc de base et l'ensemble des blocs de base d'un CFG.  $a \rightarrow b \in E_{CFG}$ Arc entre deux blocs de bases de l'ensemble des arcs d'un CFG. Ensemble des instructions machine.  $\mathcal{I}^*$ Séquence d'instructions  $\mathcal{D}$ Domaine (en interprétation abstraite).  $X^{\#}$ Marque du symbole X dans la sémantique abstraite.  $\wp(S)$ Ensemble des parties de l'ensemble S. Date de démarrage. ρ  $\rho^*$ Date de fin. Fonction d'abstraction (en interprétation abstraite) Fonction de concrétisation (en interprétation abstraite)  $\gamma$  $\preceq$ Ordre partiel (pour un treillis ou un ordre partiel complet) Fonction de jonction (pour un treillis ou un ordre partiel complet) Borne supérieure d'un treillis ou un ordre partiel  $\perp$ Borne inférieure d'un treillis ou un ordre partiel  $\mathsf{s} \in \mathsf{S}$ Ensemble d'étage d'un pipeline Ensemble de nombres naturels  $\wp(\mathcal{D})$ Ensemble des parties de l'ensemble  ${\mathcal D}$ Date de démarrage (d'un nœud du graphe d'exécution)  $\rho^*$ Date de fin (d'un nœud du graphe d'exécution)  $\emptyset$ Ensemble vide  $\mathbb{Z}^{\infty}$ Ensemble des entiers étendu des infinies  $f^{\#} \in \mathcal{XDD}$  $\mathcal{XDD}$  dans le domaine des XDD. Nœud XDD  $NODE(v, \overline{f^{\#}}, f^{\#})$ Feuille XDD LEAF(k)Ensemble des variables booléennes.  $\mathbb{B}^n$ Ensemble des vecteurs de *n* variables booléennes.  $\mathcal{X}\mathcal{D}\mathcal{D}$ Domaine des XDD  $f^{\#}[\gamma]$ Évaluation d'un XDD avec une configuration  $\gamma$  $\mathbb{Z} \cup \{-\infty, +\infty\}$ Opérateur binaire dans le domaine  $Z^{\infty}$  $\Box$ • transféré dans le domaine D  $\bullet$  ou  $\square$  transféré dans le domaine  $\mathcal{XDD}$ (•) Maximum transféré dans le domaine  $\mathcal{XDD}$ .  $\oplus$  $\ominus$ Minimum transféré dans le domaine  $\mathcal{XDD}$ . Addition transférée dans le domaine  $\mathcal{XDD}$ .  $\otimes$ Soustraction transférée dans le domaine  $\mathcal{XDD}$ . 0  $\mathbb{O}_{\mathbb{H}}$ Élément absorbant de  $\oplus$  (pour le demi-anneau sur  $\mathbb{D}$ ).

Élément neutre de  $\otimes$  (pour le demi-anneau  $\mathbb{D}$ ).

| $\mathbb{O}_{\oplus}$                                                                                                                                                                      | Élément absorbant de $\oplus$ (pour le demi-anneau sur $\mathcal{XDD}$ ).                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbb{1}_{\otimes}$                                                                                                                                                                     | Élément neutre de $\otimes$ (pour le demi-anneau sur $\mathcal{XDD}$ ).                                                                                                                                                                                                                                                                              |

| $\mathbb{D}: \mathbb{B}^n \to \mathbb{Z}^{\infty}$                                                                                                                                         | Représentation explicite de la relation entre les variables binaires et des entiers                                                                                                                                                                                                                                                                  |

| $\mathcal{XDD} \overset{lpha}{\overset{eta}{eta}} \mathbb{D}$                                                                                                                              | Isomorphisme entre le domaine des XDD et la représentation explicite                                                                                                                                                                                                                                                                                 |

| $\mathcal{M}$                                                                                                                                                                              | Matrice de XDD                                                                                                                                                                                                                                                                                                                                       |

| $[I, s] \in V_{XG}$ $[I_0, s_0] \rightarrow [I_1, s_1] \in E_{XG}$ $\mathcal{I}^{ N_I }$ $\lambda_v$ $\delta(v \rightarrow w)$ $ s_k $ $\mathcal{R}eg$ $q \in \mathcal{Q}$ $s_q^p$ $s_q^c$ | Nœud du graphe d'exécution Arc du graphe d'exécution Séquence de $N_I$ instructions Latence d'un nœud du graphe d'exécution Type d'arc du graphe d'exécution (solide ou pointillé) Capacité de l'étage $s_k$ Ensemble des registres du processeur Ensemble des files du processeur Étage producteur de la file $q$ Étage consommateur de la file $q$ |

| $egin{array}{l} \gamma \in \Gamma \ X_e \geq x_e \ \Gamma^* \ \gamma^* \ \mathcal{E}^{Entire}_{\Gamma} \ \mathcal{E}^{Partial}_{\Gamma} \end{array}$                                       | Configuration et l'ensemble de configurations (d'évènements) Nombre d'occurrences maximal (i.e. la borne) d'un évènement Partie nullifiée Configuration nullifiée Ensemble d'évènements bornant entièrement une partie Ensemble d'évènements bornant partiellement une partie                                                                        |

| $\overrightarrow{S} \in \mathcal{S}$ $\mathcal{R}$ $r \in \mathcal{R}, i_r$ $\mathcal{D}$ $	au_{reset/wait/move/consume}$ $\varrho$                                                        | État temporel (vecteur de XDD) de l'ensemble d'états temporels<br>Ensemble des ressources temporelles<br>Index de la ressource $r$ dans l'état temporel<br>Ensemble des dépendances temporelles<br>Quatre transitions basiques de l'état temporel<br>Pointeur de temps                                                                               |

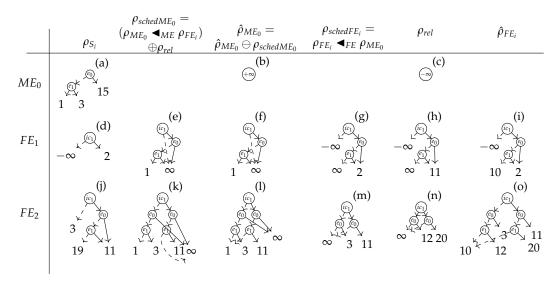

| ρ̂<br>ρ <sub>sched</sub><br>ρ <sub>rel</sub><br>◀ME, ◀FE                                                                                                                                   | Ordonnancement définitif des <i>points de contention</i> .  Ordonnancement dans une itération.  Dates de libération du bus  Opérateurs de comparaison (pour déterminer la disponibilité des <i>points de contention</i> )                                                                                                                            |

## Chapitre 1

# Introduction

Les systèmes embarqués, dits *Temps Réel*, interagissent avec l'environnement et doivent fournir une réponse aux stimuli extérieurs en un temps inférieur à un certain seuil. Une réaction trop longue est considérée comme un échec pouvant causer la perte du système ou comme un facteur dégradant son fonctionnement. Ce type de système est donc soumis à des contraintes sur le temps de réponse en plus de contraintes de correction du résultat. Dans certains cas, l'échec temporel du système peut engendrer des catastrophes (risques pour la sécurité des personnes, impact économique important, etc). De tels systèmes, dont le comportement temporel doit être vérifié rigoureusement, sont appelés des systèmes temps-réel critiques et constituent l'objet principal de cette thèse. Les exemples ci-dessous sont typiques de ce genre de système :

- 1. Le système qui contrôle les airbags d'une voiture doit déclencher les airbags dans un temps limité après avoir détecté une collision à l'aide de capteurs.

- 2. Le système de commandes de vol électrique (*fly-by-wire system*) des avions doit correctement contrôler les organes de pilotage dans un temps limité après avoir reçu des commandes des pilotes ou des capteurs pour garantir la stabilité de l'avion.

Dans les applications industrielles, ce genre de système est soumis à des processus de certification qui reposent sur une vérification du comportement fonctionnel – est-ce que les programmes calculent bien ce qu'ils doivent calculer? Et du comportement temporel – est-ce que les programmes calculent le résultat dans un délai acceptable?

En ce qui concerne le comportement temporel, si nous considérons que le système est composé de plusieurs tâches, la vérification porte sur le pire temps de réponse du système qui résulte de l'ordonnancement des tâches BRIL et al., 2009; GRAILLAT et al., 2019. Cet ordonnancement est généralement calculé à partir de leur pire temps d'exécution (WCET, Worst-Case Execution Time WILHELM et al., 2008).

Le calcul du WCET peut être fait selon deux approches majeures : les analyses statiques et les analyses dynamiques. Le principe des analyses dynamiques est d'exécuter le programme dans des situations variées (i.e. avec des entrées différentes) et de mesurer le temps d'exécution. Comme il est généralement impossible d'exécuter le programme avec toutes les entrées possibles, cette approche est souvent combinée avec la théorie des probabilités et fournit un WCET probabiliste (BERNAT et al., 2002; DAVID et al., 2004). Les analyses probabilistes peuvent être combinées avec des analyses statiques (BETTS et al., 2010) et éventuellement d'autres techniques comme de l'apprentissage automatique (AMALOU et al., 2021) : on parle alors d'analyses hybrides. Mais les approches fondées sur des techniques d'analyse dynamiques ne peuvent garantir une sûreté absolue du WCET que si la couverture des tests est suffisante (ABELLA et al., 2014).

L'analyse statique des programmes propose plusieurs approches. L'analyse de programme par exécution symbolique (BIERE et al., 2013; BENHAMAMOUCH et al., 2008; KEBBAL et al., 2006; BENHAMAMOUCH et al., 2009) a pour principe d'exécuter le programme "symboliquement" en suivants les différents chemins d'exécution qui composent le programme. La différence entre l'approche par l'exécution symbolique et les approches dynamiques est que le premier n'exécute (simule) pas le programme concrètement, mais avec un état symbolique et synthétique du programme. Les approches par exécution symbolique doivent faire face au problème d'explosion combinatoire du nombre de chemins : en pratique, il est généralement impossible de considérer tous les chemins d'un programme. C'est la raison pour laquelle cette technique est spécialement utilisée dans le domaine du test des programmes où le but est de trouver des cas (des entrées) pour lesquels certaines contraintes ne sont pas satisfaites par le programme plutôt que de prouver que le programme est valide pour toute entrée possible. Dans le cas du problème du WCET, quand la sûreté est exigée et quand ce dernier doit être valide pour toute entrée possible, les approches par exécution symbolique souffrent donc particulièrement du problème de perfor-

Contrairement aux approches présentées ci-dessus, nous nous intéressons aux approches purement statiques. Elles ont pour principe d'examiner le programme sans vraiment l'exécuter, mais calculent une surestimation des propriétés que nous voulons vérifier. Pour le problème du WCET, la propriété visée est le temps d'exécution. Dans des situations extrêmement critiques, il faut pouvoir garantir un WCET avec une sûreté absolue. Donc le calcul du WCET par analyse statique vise à déterminer une borne garantie supérieure au pire temps réel d'exécution du programme, quelle que soit l'entrée du programme. On accepte que les approches purement statiques introduisent de la surestimation, ce qui donne la possibilité d'atténuer le problème de complexité combinatoire rencontré lors de l'analyse des programmes.

### 1.1 Pourquoi le calcul du WCET est-il difficile?

Le temps d'exécution d'un programme en nombre de cycles du processeur dépend fortement de sa micro-architecture. Cependant, pour la plupart des processeurs d'aujourd'hui, cette information temporelle n'est accessible ni dans l'ISA (*Instruction Set Architecture*), ni dans les langages de programmation de plus haut niveau. En effet, le temps d'exécution précis n'est pas utile pour la plupart des applications.

Ainsi beaucoup d'analyses statiques se basent sur le code source écrit dans un langage haut niveau (comme C ou Java) ou sur un langage intermédiaire du compilateur, tel que l'IR (*Intermediate Representation*) du compilateur LLVM (LATTNER et al., 2004) qui est une abstraction de l'ISA. Ces langages ne sont pas donc suffisants pour spécifier le comportement temporel du programme et du processeur et l'analyse temporelle est par conséquent incapable de calculer un WCET précis sur ces représentations. Ainsi, les outils existants pour le calcul du WCET par analyse statique utilisent plutôt une représentation intermédiaire ad-hoc permettant de fournir l'information temporelle liée au processeur. Dans la plupart des cas, ils travaillent directement sur des programmes binaires, et dérivent les informations temporelles à partir d'une description additionnelle de la micro-architecture, comme le font par exemple *chronos* (LI et al., 2007), *Bound-T* (HOLSTI et al., 2000) ou *aiT* (FERDINAND et al., 2004). Cela est également vrai pour l'outil que nous utilisons, OTAWA (BALLABRIGA

et al., 2010). Il existe aussi des outils qui se basent sur des représentations intermédiaires du compilateur, comme *llvmta* (HAHN et al., 2022), mais en se basant sur une représentation bas niveau (plus bas que l'IR) dans le compilateur LLVM, et en rajoutant des spécifications complémentaires afin de considérer plus précisément le comportement temporel.

Pour calculer un WCET précis, la micro-architecture du processeur doit être modélisée. Or, la micro-architecture des processeurs modernes est complexe : ils sont souvent pipelinés, équipés de mémoires caches; ils mettent en œuvre la prédiction de branchement, l'exécution dans le désordre et d'autres mécanismes d'accélération. Ces mécanismes introduisent des variations temporelles, c'est-à-dire que le comportement temporel de ces mécanismes est variable, tout en dépendant de l'état de la micro-architecture du processeur durant l'exécution. Par conséquent, l'analyse temporelle doit considérer l'état du processeur plus précisément pour déterminer des temps d'exécution précis - ce qui augmente la complexité. Cette caractéristique permet de classifier les processeurs par leur prédictibilité – le niveau de difficulté qu'une micro-architecture impose sur ses analyses. Typiquement, les processeurs utilisés dans les ordinateurs personnels (cœurs Intel, AMD) ont des microarchitectures beaucoup trop complexes et donc moins prédictibles que celles des microprocesseurs ou des micro-contrôleurs utilisés dans les systèmes embarqués. Cependant, avec les technologies de conception et de fabrication de processeur actuelles, et avec la mode de l'edge computing (VARGHESE et al., 2016), les processeurs embarqués ont des structures de plus en plus complexes pour supporter une forte demande de calcul provenant du transfert de responsabilité des serveurs centraux vers les dispositifs embarqués. Les techniques de modélisation doivent aussi évoluer pour supporter ces situations.

La prédictibilité des architectures a une importance majeure pour le calcul de WCET mais ne constitue pas le sujet principal de cette thèse. SCHOEBERL et al., 2015; SAINRAT et al., 2014; PELLIZZONI et al., 2011; BAK et al., 2012; SCHUH et al., 2020 abordent ce domaine en examinant différents aspects : pipeline, multi-cœur, ordonnancement, etc. Dans ce document, nous nous intéressons plutôt au pipeline des processeurs mono-cœur et aux mécanismes d'accélération dont le comportement temporel peut être représenté par des évènements.

#### 1.1.1 Les évènements

Des variations dans le temps d'exécution sont introduites par les mécanismes qui ont un comportement dynamique lors de l'exécution. Un exemple typique d'un tel mécanisme est la mémoire cache. Pour un processeur équipé d'une mémoire cache d'instruction par exemple, le temps de chargement d'une instruction est variable : si l'instruction est déjà présente dans le cache, la latence du chargement est courte; sinon, l'instruction est chargée depuis la mémoire principale ou depuis un cache de niveau plus haut ce qui prend plus de temps.

Un constat similaire peut-être fait au sujet de la prédiction de branchement : si le branchement est bien prédit, l'exécution continue normalement; si le branchement est mal prédit, le pipeline est vidé pour charger les instructions du chemin correct – ce qui prend plus de temps et conduit à un état de pipeline totalement différent.

Pour le cache et la prédiction de branchement, les variations sont binaires : il existe deux situations possibles (Miss / Hit, bien prédit/mal prédit). Nous appelons ces variations binaires des *évènements* (on note  $e \in \mathcal{E}$  un évènement e dans l'ensemble

$\mathcal{E}$  des évènements du programme). Le cas où une latence supplémentaire est introduite (*Miss* ou mal prédit) est qualifié d'*activation* de l'évènement, et le cas contraire est qualifié d'*inactivation* de l'évènement.

Dans cette thèse, nous nous intéressons principalement aux *variations temporelles* binaires – les *évènements*. Néanmoins, les processeurs réels peuvent avoir des composants avec des latences plus complexes. Par exemple, la division implémentée matériellement présente souvent plusieurs latences possibles en fonction des valeurs des opérandes. Dans cas, il est facile de composer des variables binaires pour sélectionner différents comportements temporels, même si nos expérimentations n'ont pas porté sur ce genre de situation.

### 1.1.2 La source des évènements

Un processeur qui n'a pas de mécanisme aléatoire est déterministe, c'est-à-dire qu'étant donné une entrée du programme et l'état initial du cache, il est tout à fait possible de calculer le comportement **exact** du cache tout au long de l'exécution. Néanmoins, l'entrée du programme est souvent inconnue en réalité. À cause du nombre très important des chemins d'exécution, l'analyse statique est généralement incapable de réaliser le calcul, en un temps raisonnable, du comportement du cache pour toute exécution possible.

Des abstractions sont alors nécessaires pour diminuer la complexité. Nous nous étendrons plus en détail sur la notion d'abstraction dans la section 2.1.2 mais ici, on peut qualifier simplement l'approche comme étant "des techniques d'analyse statique qui font de l'approximation lors du calcul contre un gain en performance". Pour les analyses de cache, l'abstraction est généralement faite d'abord sur le chemin d'exécution : le comportement est déterminé typiquement par les analyses may et must qui classifient les accès mémoire en toujours Miss (always miss) ou toujours Hit (always hit) (THEILING et al., 2000); les accès qui sont ni always miss, ni always hit sont qualifiés (not classified— Not Classified). Ici, un accès mémoire signifie "une instruction qui accède à la mémoire via le cache en prenant en compte tous les chemins d'exécution passant par cette instruction". En effet, always hit, respectivement always miss, signifie "cet accès mémoire fait toujours un Hit, respectivement un Miss, quel que soit le chemin d'exécution.

Pour les accès classifiés en *always miss* ou *always hit*, même si le chemin d'exécution n'est pas explicite, le comportement est valide pour tout chemin, donc il n'y a pas de surestimation introduite. Cependant, les accès *not classified* peuvent faire soit un *Miss* (sur certains chemins), soit un *Hit* (sur les autres chemins), mais la relation entre le comportement et le chemin est perdue – une abstraction (ou une surestimation) est faite. De plus, il existe un écart entre les catégories existantes et la capacité des analyses de cache qui classifient précisément les accès avec ces catégories : en fonction de la précision de l'analyse *may* (qui détermine les *always miss*) et de l'analyse *must* (qui détermine les *always hit*), il est possible que certains accès soient effectivement *always miss* ou *always hit*, mais sont classifiés *not classified*. Même si dans certains cas, les accès *not classified* sont le résultat de l'approximation de l'algorithme d'analyse, il existe des cas où les *not classified* sont définitifs quelque soit l'algorithme d'analyse (TOUZEAU et al., 2017).

La conséquence des abstractions faites par les analyses statiques des mécanismes d'accélération est que le comportement de ces mécanismes devient variable du point de vue de l'analyse temporelle – donc représenté par des *évènements*.

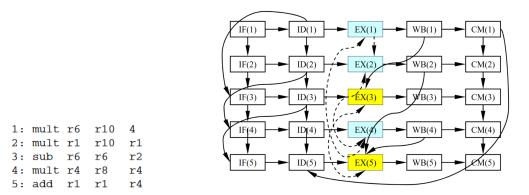

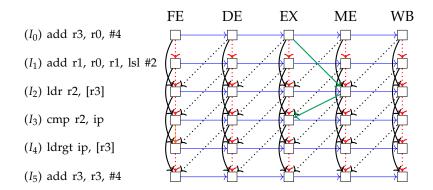

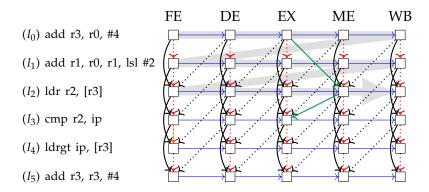

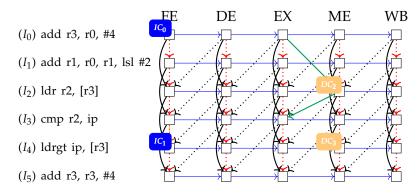

### 1.1.3 Les évènements dans le pipeline

Pour avoir une meilleure performance en nombre d'instructions exécutées par cycle, les processeurs modernes utilisent des pipelines. Cela signifie que les instructions ne sont pas exécutées indépendamment les unes après les autres, mais parallèlement en partageant certaines ressources du pipeline. Or, le nombre d'instructions exécutées en parallèle est dynamique (autrement dit, la bande passante du pipeline est variable) en fonction de l'opération réalisée par chaque instruction, des dépendances entre les instructions et de la capacité des ressources du pipeline. La conséquence de ce fonctionnement est que le temps d'exécution d'une séquence d'instructions n'est pas la somme linéaire du temps d'exécution de chaque instruction, mais une fonction complexe qui dépend des instructions exécutées et de l'état de la micro-architecture. L'analyse de pipeline est la phase de l'analyse du WCET qui crée un modèle de pipeline pour calculer le temps d'exécution des instructions tout en considérant les effets du pipeline et de l'état de la micro-architecture.

En présence des évènements, le temps d'exécution dépend en plus de leur activation. Intuitivement, l'analyse de pipeline a deux choix possibles lors de la rencontre d'un évènement : (a) comme seul le WCET du programme est intéressant, nous pouvons considérer uniquement le pire cas pour cet évènement, ou (b) nous considérons les deux possibilités.

L'option (a) présente deux inconvénients majeurs. Tout d'abord, elle engendre un problème de précision : parmi tous les chemins d'exécution passant par une séquence d'instructions, le pire cas ne se produit généralement pas à chaque coup. Donc le WCET calculé en considérant toujours le pire cas est surestimé. Un exemple d'une telle situation est le comportement typique du cache dans les boucles, appelé la persistance de cache. Au sein d'une boucle, un accès à la mémoire produit souvent un Miss à la première itération, pour charger les instructions/données dans le cache, et puis uniquement des *Hit* dans les itérations restantes car les instructions/données ont été déjà chargées à la première itération. Dans ce scénario, l'évènement de cache existe effectivement (Hit et Miss sont tous les deux possibles), mais si nous considérons un Miss à chaque itération, la surestimation devient énorme car le pire cas qui n'arrive qu'une seule fois est compté pour chaque itération. L'autre inconvénient de l'option (a) concerne les anomalies temporelles – pour certaines micro-architectures, le pire cas local n'est pas forcément le pire cas global. Autrement dit, considérer l'activation de chaque évènement ne produit pas forcément un WCET valide. Nous allons donner des explications plus détaillées concernant les anomalies temporelles dans la section suivante.

L'option (b) pose simplement un problème de performance. Considérer les deux possibilités lors d'un évènement cause une divergence d'état du pipeline. Par conséquent, l'analyse de pipeline qui considère toutes les combinaisons d'activation ou d'inactivation des évènements a une complexité combinatoire en fonction de leur nombre. Malgré ce problème, cette option fournit une meilleure précision et ne souffre pas du problème de validité induit par les *anomalies temporelles*, deux points qui sont précisément les défauts de l'option (a). Par conséquent, dans les approches proposées dans la suite de ce document, nous visons l'option (b) mais nous allons créer de nouvelles techniques pour atténuer le problème de performance de l'analyse de pipeline et, ainsi, rendre l'approche utilisable dans des situations réalistes.

# 1.1.4 Les ressources allouées dans le désordre et les anomalies temporelles

La notion d'anomalie temporelle a d'abord été introduite dans le domaine du calcul parallèle (GRAHAM, 1969). Dans ce contexte, des tâches sont exécutées en parallèle sur plusieurs processeurs avec des dépendances potentielles entre elles. Les processeurs exécutent les tâches en suivant une politique du FCFS (First-Come-First-Served) en respectant les dépendances entre les tâches. Dans cette configuration, des cas "anormaux" (contre-intuitifs) se présentent où (a) l'augmentation du nombre de processeurs augmente le temps d'exécution total, ou (b) la diminution du temps d'exécution de certaines tâches augmente le temps d'exécution total.

Ce phénomène est causé par le nombre limité de ressources partagées (dans ce cas, les processeurs), et par les dépendances qui empêchent la libre exécution des tâches. Les deux contraintes combinées font que le vrai chemin critique (la chaîne de dépendances la plus longue) ne peut pas être ordonnancé idéalement sur les ressources disponibles.

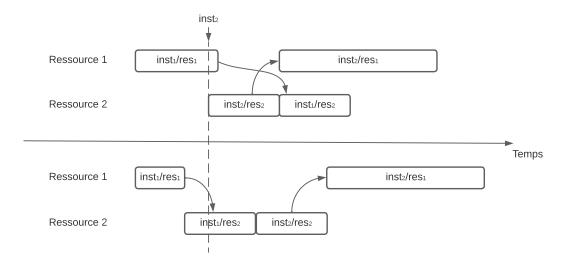

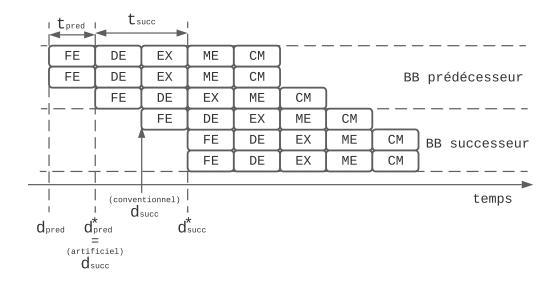

Ce modèle d'exécution de tâches concurrentes sur des ressources partagées est très similaire à l'exécution des instructions dans le pipeline, où les instructions peuvent être considérées comme des tâches et les ressources sont celles du pipeline partagées par les instructions exécutées en parallèle. Par conséquent, l'ordonnancement des instructions dans le pipeline peut également souffrir d'anomalies temporelles. La figure 1.1 montre un exemple de l'occurrence d'une anomalie temporelle. Dans cet exemple, deux instructions (1 et 2) sont exécutées sur les ressources 1 et 2. La ressource 2 du pipeline est allouée avec la politique FCFS. L'instruction 2 entre dans le pipeline plus tard que l'instruction 1, à l'instant indiqué par la ligne pointillée. L'instruction 1 utilise d'abord la ressource 1 puis la ressource 2, inversement pour l'instruction 2. Les dépendances entre l'exécution des instructions sont représentées par les flèches solides. Dans le premier scénario (celui du haut), la ressource 2 est d'abord allouée à l'instruction 2 car elle est la première instruction prête (l'instruction 1 doit d'abord finir d'utiliser la ressource 1). Dans le deuxième scénario, l'instruction 1 prend moins de temps dans la ressource 1 et donc la ressource 2 est d'abord allouée à l'instruction 1. Finalement, on peut constater que la réduction du temps d'exécution de l'instruction 1 sur la ressource 1 cause contre-intuitivement l'augmentation du temps d'exécution total. Une explication simple est que, dans le deuxième scénario, l'allocation de la ressource 2 à l'instruction 1 empêche le démarrage de l'instruction 2 et donc limite le parallélisme entre les deux instructions.

Plusieurs définitions de anomalies temporelles existent en fonction du modèle de pipeline (EISINGER et al., 2006; CASSEZ et al., 2012; REINEKE et al., 2006; BINDER et al., 2022; KIRNER et al., 2009; BINDER et al., 2021) mais le problème causé par les anomalies temporelles reste le même : lors d'évènements, le temps d'exécution d'une instruction (dans une ressource, typiquement un étage) est variable. Mais si on considère l'activation des évènements comme le pire cas, le WCET final calculé risque d'être invalide, comme dans l'exemple de la figure 1.1 : une durée plus courte de l'exécution de certaines instructions peut produire un temps d'exécution total plus long. L'analyse de WCET peut toujours essayer de couvrir la pire latence induite par un évènement (qui est plus longue que la latence d'activation en considérant les anomalies temporelles), mais une telle latence peut introduire une surestimation considérable du WCET final. De plus, l'article GEBHARD, 2010 a montré que l'effet des anomalies temporelles ne peut pas être couvert par une simple constante  $k \in \mathbb{N}$  qui serait ajoutée au WCET calculé sans compter les anomalies temporelles, mais par une fonction plus complexe dépendant du programme.

FIGURE 1.1 – Un exemple de l'anomalie temporelle.

Pour éviter le problème de validité causé par les *anomalies temporelles*, il est possible d'utiliser des processeurs garantissant leur absence (HAHN et al., 2020) : l'article WENZEL et al., 2005 montre que la présence des ressources allouées dans le désordre dans le pipeline est une condition nécessaire pour la présence d'anomalies temporelles. Donc, on peut montrer qu'un pipeline sans ce type de ressources est insensible aux *anomalies temporelles*. Au contraire, dans le cas où des *anomalies temporelles* peuvent se présenter, considérer explicitement la divergence d'état de pipeline (à cause des évènements) nous assure un WCET valide et peut améliorer la précision du WCET calculé.

### 1.2 Objectif de la thèse

Cette thèse se focalise sur l'analyse de pipeline, la phase où le temps d'exécution des instructions est déterminé en considérant les détails du pipeline et de la microarchitecture.

Comme discuté précédemment, pour supporter les *anomalies temporelles* et préserver la précision de l'analyse de WCET, nous choisissons de traiter explicitement la divergence d'état provoquée par des évènements. Le problème principal de ce choix est la performance puisque le nombre d'états du pipeline est combinatoire en fonction du nombre d'évènements. Par conséquent, nous avons exploré des modèles de pipeline efficaces et des techniques spécifiques pour atténuer l'explosion combinatoire de cette analyse. Ces modèles doivent supporter des processeurs à exécution dans l'ordre mais également des ressources allouées dans le désordre (ce qui rend le processeur sensible aux *anomalies temporelles*).

### **1.3** Plan

Après ce chapitre d'introduction, nous présentons, dans le chapitre 2, les notions et les théories de base qui seront utilisées dans cette thèse. Ensuite, nous discutons de l'état de l'art sur le calcul de WCET par analyse statique et spécialement des techniques utilisées dans l'analyse de pipeline.

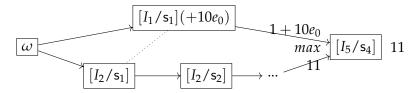

Dans le chapitre 3 est introduite une nouvelle structure de données, appelée XDD, qui permet de représenter efficacement la relation entre les temps d'exécution et les évènements. L'utilisation des XDD dans l'analyse de pipeline permet de réaliser une analyse **exacte** du comportement temporel du pipeline tout en gardant une performance acceptable.

Dans le chapitre 4, nous présentons notre nouvelle analyse de pipeline qui intègre l'utilisation des XDD. Cette analyse est capable de calculer **tous** les temps d'exécution possibles et exacts d'une séquence d'instructions quelconque en fonction des évènements. Cette analyse est seulement compatible avec les processeurs à exécution dans l'ordre.

La nouvelle analyse de pipeline calcule **tous** les temps d'exécution possibles. Cependant, dans des approches plus anciennes, seul le pire temps d'exécution des séquences d'instructions était pris en compte. Pour profiter du gain de précision de notre nouvelle analyse, une amélioration est proposée pour augmenter la précision du WCET produit. Notre analyse calcule séparément les temps d'exécution des séquences d'instructions du programme mais, lorsqu'on considère le programme en entier, le temps d'exécution de chaque morceau de code dépend aussi de son *contexte d'exécution*, c'est-à-dire de l'historique d'exécution du programme avant ce morceau code. Pour mieux profiter du *contexte d'exécution*, notre analyse est étendue dans le chapitre 6 pour s'appliquer globalement au programme entier et non à chaque séquence d'instructions séparément.

La structure de données XDD apporte des propriétés algébriques intéressantes : nous montrons, dans le chapitre 3, que les XDD forment un demi-anneau tropical (aussi appelé *algèbre max-plus*) (COHEN et al., 1999; HEIDERGOTT et al., 2006). Dans la version étendue de notre analyse de pipeline présentée dans le chapitre 6, les états du pipeline sont alors représentés sous forme de *vecteurs* de XDD et les transitions se révèlent être finalement des fonctions affines sur le demi-anneau des XDD. Ces fonctions affines sont analogues aux applications linéaires sur des espaces vectoriels *de nombres réels*, c'est-à-dire que les transitions d'état de pipeline peuvent être représentées par une multiplication de matrices de XDD. Comme le demi-anneau des XDD garantit l'associativité de la multiplication matricielle, il devient possible de résumer les transitions induites par d'une séquence d'instructions par *une matrice unique résultat de la multiplication des matrices de chaque étape d'exécution* ce qui, finalement, permet d'accélérer l'analyse.

Dans le chapitre 7, nous étendons notre modèle pour supporter des ressources allouées dans le désordre. Nous nous concentrons sur un exemple typique pour des petits microprocesseurs utilisés dans l'embarqué : le bus de mémoire FCFS partagé par le cache d'instructions et le cache de données. Nous présentons une nouvelle méthode pour calculer la latence supplémentaire causée par les contentions lors d'accès à ce bus. Nous montrons que, à l'aide des XDD, l'analyse est capable de calculer les temps d'exécution **exacts** avec un temps d'analyse raisonnable. Finalement, nous concluons cette thèse et proposons des perspectives de recherche dans le chapitre 8.

9

## **Chapitre 2**

# État de l'art

Le calcul de WCET reste un domaine très actif dans la communauté scientifique de la vérification, des systèmes embarqués et de l'analyse statique. Pour les processeurs modernes, les évènements <sup>1</sup>, la divergence d'état qu'ils induisent et la complexité combinatoire qui en résulte est une problématique importante de l'analyse du WCET, spécialement dans l'analyse de pipeline. La compréhension de ces analyses nécessite d'abord d'exposer, dans ce chapitre, plusieurs concepts et théories plus largement utilisés dans le domaine de l'analyse statique. Dans une seconde partie, nous discutons des approches statiques existantes traitant du problème de calcul de WCET, spécialement en examinant le modèle de pipeline et comment les évènements y sont traités.

### 2.1 Concepts pour l'analyse statique

### 2.1.1 Le Graphe de Flot de Contrôle

Dans le calcul de WCET par analyse statique, la représentation quasi-standard d'un programme est le *Graphe de Flot de Contrôle* (CFG, *Control-Flow Graph*). Un CFG est un graphe  $CFG: V_{CFG} \times E_{CFG}$ , dont l'ensemble des sommets ( $V_{CFG}$ ) représente des blocs de base (BB, *Basic Block*). Un BB dans un CFG  $a \in V_{CFG}$  est une séquence d'instructions machine ( $a \in \mathcal{I}^*$ ) exécutées séquentiellement de manière unitaire : seule la dernière instruction peut être un branchement et seule la première instruction peut être la cible d'un branchement. L'ensemble des arcs  $E_{CFG}: V_{CFG} \times V_{CFG}$  du CFG représentent l'ordre d'exécution entre les BB. Un arc entre deux BB  $a \to b \in E_{CFG}$  indique que b peut s'exécuter après a.

#### 2.1.2 Abstraction

Le terme abstraction, dans le domaine de l'analyse statique, désigne une représentation partielle ou approximative d'une certaine sémantique du programme. Elle est nécessaire car il est généralement impossible de simuler toutes les exécutions concrètes : il existe trop de chemins d'exécution possibles. L'analyse d'une abstraction permet d'extraire une propriété partielle du programme vis-à-vis du comportement qui nous intéresse. Elle omet certaines informations afin de diminuer la complexité de l'analyse. Une bonne abstraction est une abstraction qui cache le plus d'informations possible tout en supportant une analyse fournissant des résultats suffisamment précis pour décrire et exploiter le comportement qui nous intéresse.

<sup>1.</sup> Même si cette terminologie n'est pas communément adoptée, on retrouve des concepts similaires.

**Exemple.** On veut vérifier que la valeur des variables d'un programme n'est jamais négative. Une méthode sans abstraction consiste à simuler le programme pour toute entrée possible et à vérifier si les variables ont été négatives le long de chaque exécution. Intuitivement, cette analyse a une complexité élevée, d'une part si le nombre d'entrées possibles peut être très grand et d'autre part si le programme est lui-même complexe : le temps d'analyse peut alors devenir rédhibitoire. Une abstraction de la propriété prise en exemple consiste à se concentrer uniquement sur le signe des variables en représentant leur valeur par l'abstraction  $\{+,-,0,?\}$ , positive, négative, nulle ou inconnue. De plus, on ne s'intéresse pas au signe des variables pour chaque chemin d'exécution individuel, mais au(x) signe(s) possible(s) pour tous les chemins d'exécution. Intuitivement, une simulation qui ne représente les valeurs numériques que par  $\{+,-,0,?\}$  doit être beaucoup plus simple à produire qu'une simulation complète car elle ne calcule qu'une sous-propriété (signe) par rapport à la sémantique concrète (valeur exacte).

Cependant, cette abstraction a un prix : le résultat "?" – parfois, on ne sait pas déterminer le signe d'une variable (de manière analogue à la catégorie *not classified* pour l'analyse du cache). Ce "?" est engendré par deux abstractions : (a) <u>l'abstraction</u> du chemin d'exécution – lorsque la variable est positive sur un chemin, mais négative sur un autre, et (b) <u>l'abstraction</u> de la valeur concrète : les variables sont représentées par leur signe, et la somme de deux variables de signes différents ou la soustraction de variables de même signe a un signe imprévisible. Par exemple, pour la séquence x = 4; y = 3; x = x - y;, x reste positif. Mais si on ne connaît que les signes, le calcul devient : x = +; y = +, et le signe de x - y est inconnu.

L'abstraction (b) peut être réparée si l'**ensemble** des valeurs **exactes** des variables est connu – le signe peut être correctement calculé. Cependant, quand on utilise le terme **d'ensemble des valeurs**, une abstraction sur les chemins d'exécution est sousentendue. Les vraies valeurs concrètes des variables sont en fait la valeur exacte par chemin d'exécution depuis le début du programme. Cependant, calculer la valeur exacte pour tout chemin est très proche d'une simulation complète du programme pour toute entrée possible et de complexité combinatoire. L'abstraction de la valeur exacte par le signe introduit de la perte de précision mais est indispensable pour réduire la complexité de l'analyse.

### 2.2 Interprétation Abstraite

L'abstraction est un concept central de l'analyse statique par interprétation abstraite. Généralement, on veut que l'abstraction soit valide. La définition de la validité (soundness en anglais) d'une analyse est dérivée de sa définition en logique <sup>2</sup> où "un système logique est valide si et seulement si toutes les formules qui peuvent être prouvées sont valides par rapport à la sémantique du système". Autrement dit, tout ce qui peut être prouvé par les formules (la syntaxe) est forcément vrai selon la sémantique, mais ce qui ne peut pas être prouvé par les formules n'est pas forcément faux selon la sémantique. Dans le contexte de l'analyse de programme, la validité est souvent exprimée par "tout ce que l'analyse affirme est forcément vrai, mais l'analyse a le droit de dire qu'elle ne sait pas."

<sup>2.</sup> En anglais, le terme *soundness* est utilisé à la fois dans le domaine de logique et dans le domaine de l'analyse de programme. Mais en français, le terme correspondant est *cohérence* ou *validité* dans le domaine d'analyse de programme et *correction* dans le domaine de la logique. Pour ne pas confondre ces notions, dans cette thèse, le terme *validité* désigne la *soundness* et le terme *correction* correspond à la notion de *correctness* en anglais.

L'interprétation abstraite (COUSOT et al., 1977; COUSOT et al., 1992; COUSOT, 1996) est une base théorique qui fournit un cadre pour la conception d'abstractions. En suivant ce cadre, les analyses conçues sont garanties valides.

L'exemple donné dans la section 2.1.2 est un cas typique d'interprétation abstraite qui s'intéresse uniquement au signe des variables – une abstraction des valeurs exactes. De la même manière, nous pouvons concevoir une analyse du comportement d'une mémoire cache, du comportement d'un prédicteur de branchements et nombreuses autres analyses qui fournissent des informations utiles à l'analyse de WCET.

L'interprétation abstraite permet de prouver la validité d'une abstraction mais elle nécessite d'abord de trouver artificiellement une telle abstraction. La performance de l'abstraction (typiquement le temps d'analyse) n'est pas garantie par le cadre de l'interprétation abstraite mais dépend du choix artificiel de l'abstraction. Ceci étant dit, trouver une bonne abstraction par rapport à une sémantique intéressante est loin d'être une tâche aisée.

Le but de cette thèse n'est pas d'aborder en détails l'interprétation abstraite. Nous allons seulement présenter son principe et les notions importantes, ce qui va permettre de simplifier la lecture des chapitres suivants.

### 2.2.1 La sémantique

Informellement, la sémantique d'un programme est une propriété du programme. Dans l'interprétation abstraite, on s'intéresse à l'abstraction des sémantiques. Si une sémantique est une représentation abstraite (ou approximative) d'une autre sémantique, cette dernière est appelée "sémantique concrète" et la première est appelée "sémantique abstraite".

Une sémantique opérationnelle, concrète ou abstraite, est définie par un domaine d'états et une fonction de transition, notée *Update*. Le domaine définit la représentation des états et la fonction de transition définit comment ces états évoluent tout au long de l'exécution.

Dans l'exemple de la sémantique du signe des variables proposée précédemment, le domaine est  $\{+,-,0,?\}$  et la fonction de transition est définie par rapport à la sémantique du langage de programmation, typiquement, dans un langage impératif :

- L'affectation remplace la valeur de la variable à gauche par la valeur de l'expression à droite, donc le signe de la variable après l'affectation est égal au signe de l'expression.

- Le signe d'une expression est calculé à partir des opérations réalisées dans l'expression. Par exemple, la somme de deux opérandes de même signe ou nuls garde le signe, sinon le signe est inconnu. On procède de manière similaire pour la soustraction, la multiplication, etc., en fonction de la nature de l'opération.

### 2.2.2 La sémantique collectrice

Dans un programme à analyser, nous pouvons imaginer des *points de programme*, par exemple, à la fin de chaque instruction. En considérant la sémantique concrète (par exemple, la valeur des variables lors d'une exécution réelle), en un même point du programme, correspondent en général un ensemble d'états concrets possibles (par exemple, la valeur des variables à la fin de chaque instruction peut être totalement différente en fonction du chemin d'exécution du programme).

La sémantique collectrice est définie comme l'ensemble de tous les états concrets en chaque point du programme. Par conséquent, le domaine de la sémantique collectrice est défini par l'ensemble des parties de l'ensemble des états concrets. Nous pouvons utiliser la sémantique collectrice comme un outil théorique pour tester la validité de certaines propriétés du programme mais elle est rarement calculable. Par exemple, si le **sur-ensemble** des valeurs d'une variable booléenne dans la condition d'un *IF* (en certain point du programme) est {*TRUE*}, on peut être sûr que la condition n'est jamais *FALSE* et donc que le *IF* est **toujours pris** quelle que soit l'exécution du programme.

La fonction *Update* de la *sémantique collectrice* est simplement obtenue en appliquant *Update* de la sémantique concrète à chaque élément de l'ensemble d'états concrets produits par la *sémantique collectrice*.

De plus, les programmes sont rarement linéaires et contiennent des instructions de contrôle de flot. Pour **collecter** tous les états concrets en chaque point du programme, une fonction *Join* doit être définie pour décrire la fusion des états abstraits aux points de jonction du flot de contrôle. Le *Join* de la *sémantique collectrice* est simplement l'union des ensembles des états concrets. La *sémantique collectrice* est une sémantique basique qui fait uniquement l'abstraction sur le chemin d'exécution (car les états concrets sont groupés dans des ensembles en chaque point du programme sans prendre en compte la relation avec les chemins d'exécution). En général, pour concevoir une analyse, on commence par définir une sémantique concrète. Ensuite, la *sémantique collectrice* peut être directement déduite de la sémantique concrète. Les abstractions plus avancées sont conçues plus tard en se basant sur la *sémantique collectrice*, c'est-à-dire en considérant la sémantique collectrice comme la sémantique concrète.

Lorsque l'on conçoit une abstraction, il faut que l'abstraction finale (la plus abstraite) soit *valide* par rapport à la sémantique concrète initiale. Cela signifie que l'état abstrait calculé en chaque point du programme "inclut", au moins, tous les états concrets en ce point. Cette inclusion peut être implicite ou explicite. Dans le cas de la *sémantique collectrice*, "l'inclusion" désigne une inclusion explicite – tout état concret possible en chaque point du programme est dans l'ensemble d'états concrets calculé par la *sémantique collectrice*. Un exemple "d'inclusion" implicite est la représentation  $\{+,-,0,?\}$  du signe des variables – le "?" représente tous les signes possibles : on a donc '?' qui inclut toutes les autres valeurs '+', '-' et '0'.

### 2.2.3 La conception des abstractions

L'interprétation abstraite fournit un cadre pour concevoir les abstractions et prouver leur validité. En général, on exige que tout domaine  $\mathcal{D}$ , abstrait ou concret, soit au moins un *Ordre Partiel Complet*,  $\langle \mathcal{D}, \preceq, \top \rangle$ : un ensemble  $\mathcal{D}$ , un ordre partiel  $\preceq$  défini sur les éléments de  $\mathcal{D}$ , et un élément  $\top$  qui est supérieur à tous les éléments de  $\mathcal{D}$ . Pour des raisons pratiques, souvent un plus petit élément  $\bot$  est ajouté et permet de former un *treillis complet* (ce qui est aussi le cas de la *sémantique collectrice*, pour qui  $\bot$  est l'ensemble vide).

Pour former une abstraction valide, nous devons assurer que tout état abstrait "inclut" au moins tous les états concrets correspondants. C'est-à-dire que le domaine concret  $\langle \mathcal{D}, \preceq, \top \rangle$  et le domaine abstrait  $\langle \mathcal{D}^\#, \preceq^\#, \top^\# \rangle$  forment une connexion de Galois :

$$\langle \mathcal{D}, \preceq, \top \rangle \stackrel{\gamma}{\underset{\alpha}{\rightleftharpoons}} \langle \mathcal{D}^{\sharp}, \preceq^{\sharp}, \top^{\sharp} \rangle$$

(2.1)

avec l'opérateur d'abstraction  $\alpha: \mathcal{D} \to \mathcal{D}^{\#}$  et l'opérateur de concrétisation  $\gamma: \mathcal{D}^{\#} \to \mathcal{D}$  tels que :

$$\forall d \in \mathcal{D}, d^{\#} \in \mathcal{D}^{\#}, \alpha(d) \leq^{\#} d^{\#} \Leftrightarrow d \leq \gamma(d^{\#})$$

(2.2)

Donc l'état abstrait obtenu par l'abstraction d'un état concret *inclut* forcément l'état concret dans le sens où la concrétisation ( $\gamma$ ) de l'état abstrait est forcément supérieure ( $\preceq$ ) à l'état concret initial.

Soit une fonction de transition dans le domaine concret,  $inter: \mathcal{D} \to \mathcal{D}$  qui interprète le programme (ou une partie du programme) dans la sémantique concrète, et la fonction correspondante  $inter^{\#}: \mathcal{D}^{\#} \to \mathcal{D}^{\#}$  qui interprète le programme dans la sémantique abstraite. Grâce à la connexion de Galois, nous savons que la relation ci-dessous tient si  $\alpha$ ,  $\gamma$ , inter et  $inter^{\#}$  sont monotones sur leurs domaines respectifs et donc que notre abstraction est valide :

$$inter(d) \leq \gamma \circ inter^{\#} \circ \alpha(d)$$

(2.3)

Dans la pratique, la fonction *inter* est souvent exprimée par deux fonctions : *Update* pour interpréter l'exécution d'une séquence de programme et *Join* pour exprimer la fusion d'états lors de la jonction du flot de contrôle. Nous pouvons ainsi dériver les propriétés ci-dessous qui sont exigées pour former une abstraction valide :

$$Update(d) \leq \gamma \circ Update^{\#} \circ \alpha(d)$$

$$Join(a,b) \prec \gamma \circ Join^{\#}(\alpha(a),\alpha(b))$$

(2.4)

Enfin, la relation entre états est représentée sur la figure 2.1 : il y a deux états d'entrée, l'état concret d, et l'état abstrait  $d^{\#} = \alpha(d)$ . Ces deux états subissent les mêmes transformations : les Update, Join du domaine concret et les transformations correspondantes dans le domaine abstrait  $Update^{\#}$   $Join^{\#}$ .

$$d^{\#} \in \mathcal{D}^{\#} \xrightarrow{Update^{\#}, Join^{\#}} d'^{\#} \in \mathcal{D}^{\#}$$

$$\uparrow \alpha \qquad \qquad \downarrow d' \leq \gamma(d'^{\#})$$

$$d \in \mathcal{D} \xrightarrow{Update, Join} d' \in \mathcal{D}$$

FIGURE 2.1 – Connexion de Galois entre les sémantiques concrètes et abstraites.

Comme toutes les fonctions Update et Join sont consistantes par rapport à la connexion de Galois (équation 2.4), on est donc sûr qu'après des transitions ( $Update^{\#}$ ,  $Join^{\#}$ ) dans le domaine abstrait, l'état  $d'^{\#}$  obtenu est valide par rapport au résultat des transitions correspondantes dans le domaine concret avec l'état final d', car la concrétisation de  $d'^{\#}$  donne un état supérieur à d' – un état qui inclut le résultat concret.

Finalement, pour calculer les propriétés du programme, l'analyse commence par le début du programme et applique des Update et des Join en suivant le flot de contrôle dans le CFG pour mettre à jour l'état en chaque point du programme. Comme un programme peut contenir des boucles, un point du programme peut être visité plusieurs fois. Le caractère croissant de ces opérateurs, ainsi que l'existence de l'élément maximal  $\top$  assure l'existence d'un point fixe des états. Il faut remarquer

que l'existence du point fixe assure seulement une terminaison **théorique** de l'analyse. Dans des cas réalistes, beaucoup de sémantiques ne sont pas calculables en un temps raisonnable.

De la même manière, nous pouvons appliquer *Update*<sup>#</sup> et *Join*<sup>#</sup> pour travailler dans le domaine abstrait. En général, on travaille dans le domaine abstrait pour avoir une meilleure performance parce que le domaine est plus petit et les fonctions de transitions sont croissantes : l'analyse converge donc plus vite. L'abstraction étant valide, le résultat obtenu est lui-même automatiquement valide par rapport à la sémantique concrète.

### 2.3 La structure de l'analyse de WCET

L'analyse de WCET est influencée par deux composantes principales : le programme lui-même et la micro-architecture du processeur sur lequel le programme est exécuté. La micro-architecture des processeurs modernes est complexe en raison de la présence de mécanismes d'accélération avancés comme les mémoires caches, le pipeline, la prédiction de branchement, etc. Les combiner augmente la combinatoire de l'analyse : si les domaines d'états de l'analyse des deux mécanismes sont respectivement A et B, le domaine d'états qui considère les deux composants simultanément est  $A \times B$  – le produit cartésien des domaines. Le nombre d'états de l'analyse sur  $A \times B$  est ainsi beaucoup plus grand que celui sur A **plus** celui sur B. C'est pour cette raison que l'analyse de WCET est généralement divisée en plusieurs sous-analyses, présentées ci-après. Il est important de noter que cette structure n'est pas la même pour tous les outils de WCET. Par exemple, les approches par vérification de modèle (que nous allons présenter plus tard dans ce chapitre) ont des structures assez différentes puisqu'elles font peu ou pas d'abstraction. Cependant les autres outils par analyse statique (aiT (FERDINAND et al., 2004), Chronos (LI et al., 2007), OTAWA (BALLABRIGA et al., 2010), etc.) ont des structures assez proches.

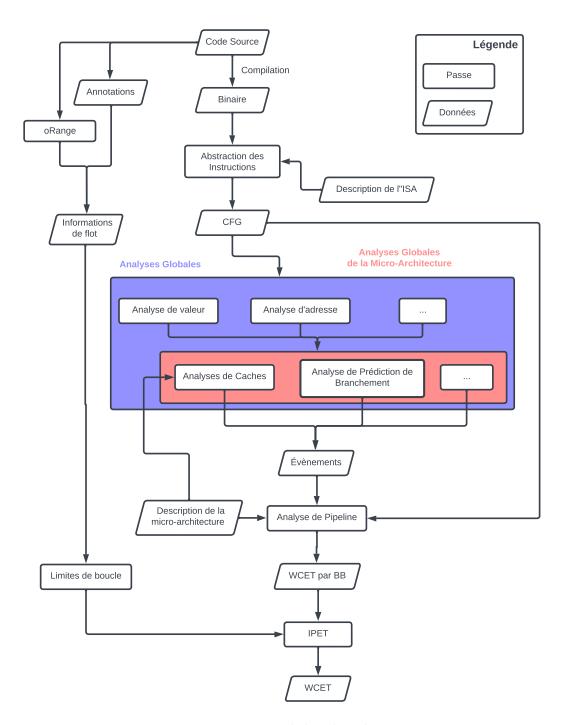

Dans cette section, nous présentons uniquement la structure de l'outil OTAWA illustrée par la figure 2.2. Les détails sont exposés en quatre parties : la construction des chemins d'exécution, les analyses globales, le calcul de WCET selon la méthode IPET et l'analyse du pipeline pour obtenir le temps des blocs.

#### 2.3.1 Construction du CFG

Du point de vue du développement des systèmes temps-réel embarqués, les logiciels sont souvent développés avec des langages de programmation haut niveau (comme du C, C++, Ada, etc). Cependant, le code source est compilé sous forme de fichiers binaires exécutables sur lesquels se base le calcul de WCET. L'outil OTAWA commence par lire et décoder ce fichier binaire grâce à une description du jeu d'instructions (ISA, *Instruction Set Architecture*) exprimée à l'aide du langage de description *Sim-NML* (RAJESH et al., 1999; HERBEGUE et al., 2014; RATSIAMBAHOTRA et al., 2009). De nombreuses ISAs sont actuellement supportées par OTAWA: ARM, RISC-V, PowerPC, TriCore, etc. Nous pouvons faire une analogie entre cette phase dans le calcul du WCET et le front-end d'un compilateur: ils ont tous les deux comme but de générer une représentation intermédiaire des instructions. Concrètement, cela consiste à annoter les instructions avec des informations spécifiées par l'ISA, typiquement:

— le type d'instruction / l'opération réalisée (branchement / arithmétique / multiplication /...),

FIGURE 2.2 – Structure de l'analyse de WCET

- les registres lus et écrits par l'instruction,

- l'adresse de l'instruction,

- l'adresse cible pour une instruction de branchement,

- la sémantique de l'instruction par rapport au pipeline, c'est-à-dire la liste et l'ordre des ressources du pipeline utilisées par l'instruction,

- etc.

Cette interface permet aux analyses suivantes de travailler dans un environnement indépendant de l'ISA.

Ensuite, le graphe de flot de contrôle (CFG, Control Flow Graph) du programme peut être construit.

### 2.3.2 Les analyses globales

Commence ensuite la phase des analyses globales. Dans un premier temps, des analyses de valeur et d'adresse sont appliquées pour déterminer les valeurs possibles des registres et des adresses accédées en mémoire. Puis, les analyses des mécanismes d'accélération de la micro-architecture sont réalisées pour déterminer leur comportement temporel lors de l'exécution. Il s'agit typiquement de l'analyse du cache d'instructions et du cache de données ainsi que des analyses du prédicteur de branchement, du buffer d'écriture, etc. Ces analyses prennent en compte les informations fournies par les analyses de valeur et d'adresse ainsi que la description de la micro-architecture (qui contient par exemple les caractéristiques des caches). En sortie de ces analyses globales, les évènements (que nous avons présentés dans la section 1.1.1) sont générés pour décrire les variations temporelles engendrées par ces mécanismes. Par exemple, les évènements de cache concernent les accès mémoire pouvant donner lieu parfois à des *Hit*, ou parfois à des *Miss*.

#### 2.3.3 La méthode IPET

Généralement, le nombre de chemins d'exécution possibles d'un programme est trop élevé pour les représenter explicitement. Il est impossible de calculer le temps d'exécution de chaque chemin et d'en prendre le maximum pour déterminer le WCET. Une solution classique à ce problème est la méthode IPET (Implicit Path Enumeration Technique ou technique d'énumération implicite des chemins) (LI et al., 1995).

Cette méthode représente le temps d'exécution du programme par la somme des WCETs de chaque bloc de base ( $t_a$ ) pondérés par leurs nombres d'exécution ( $x_a$ ):

$$WCET = \sum_{a \in V_{CFG}} (t_a \times x_a)$$

(2.5)

Les compteurs  $x_a$  représentent le nombre d'exécutions d'un bloc sur le pire chemin "implicite" d'exécution. Ils sont soumis aux contraintes de flots. Par exemple, pour chaque BB du CFG, le flot entrant est égal au flot sortant :

$$\forall a \in V_{\text{CFG}}, \sum_{b \to a \in IN(a)} x_{b \to a} = \sum_{a \to b \in OUT(a)} x_{a \to b} = x_a$$

(2.6)

où les fonctions *IN* et *OUT* renvoient l'ensemble des arcs entrants et sortants d'un bloc de base.

De plus, les programmes peuvent contenir des boucles, ce qui créent également des boucles dans le CFG correspondant. Les contraintes de flot décrites précédemment ne sont alors pas suffisantes car il faut aussi donner une borne supérieure aux compteurs des arcs retour de ces boucles : sans cela, une boucle est considérée comme s'exécutant un nombre infini de fois. Par conséquent, des contraintes supplémentaires sont obligatoires pour limiter les compteurs concernés. Ces contraintes sont appelées des *contraintes de limite de boucle* :

$$\forall loop \in LOOPS(CFG), \sum_{a \to b \in BACK(loop)} x_{a \to b} \le LOOP\_BOUND(loop)$$

(2.7)

La fonction *LOOPS* renvoie l'ensemble des boucles du CFG, *BACK* renvoie l'ensemble des arcs retour d'une boucle donnée et la fonction *LOOP\_BOUND* donne la limite d'une boucle : une borne supérieure de son nombre d'itérations.

La fonction objectif, qui maximise l'expression du WCET (équation 2.5) et les contraintes sur les flots forment un programme linéaire en nombres entiers (ILP, *Integer Linear Programming*). Par conséquent, la méthode IPET est utilisée dans la dernière étape de notre schéma de l'analyse de WCET (figure 2.2). Elle reçoit en entrée le WCET de chaque BB (calculé par l'analyse de pipeline que nous allons présenter dans la section suivante) et les bornes de boucles.

Pour que le système ILP converge, une borne doit être déterminée pour chaque boucle (les *limites de boucle* dans la figure 2.2). Cette information est obtenue avec *oRange* (MICHIEL et al., 2010), un outil qui calcule les bornes de boucle à partir du code source. Dans le cas où l'outil est incapable de calculer les bornes de certaines boucles, ces informations peuvent être fournies par des annotations (dans un fichier indépendant), au format de *FFX* (BONENFANT et al., 2012). Dans l'équation 2.7, nous exploitons les bornes de boucle pour créer des contraintes sur les arcs retour des boucles, mais ces contraintes sont automatiquement transférées aux arcs entrants par l'égalité des flots (l'équation 2.6).

Nous pouvons voir le système ILP comme une abstraction des chemins d'exécution par rapport à la sémantique temporelle du programme parce que nous ne nous intéressons pas explicitement aux chemins d'exécution mais au nombre d'exécutions de chaque bloc (d'où le nom *énumération implicite des chemins*).