# Analysis and optimizations for partitioned global address space based HPC applications

Célia Tassadit Ait Kaci

# ▶ To cite this version:

Célia Tassadit Ait Kaci. Analysis and optimizations for partitioned global address space based HPC applications. Other [cs.OH]. Université de Bordeaux, 2022. English. NNT: 2022BORD0464. tel-04291830

# HAL Id: tel-04291830 https://theses.hal.science/tel-04291830

Submitted on 17 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR

# OBTENIR LE GRADE DE

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

Ecole Doctorale de Mathématiques et Informatique Bordeaux

Spécialité : Informatique

# Par Célia Tassadit AIT KACI

Sous la direction de : Denis Barthou

# Analyse et optimisations pour les applications HPC à mémoire distribuée et adressable globalement

Soutenance le 28 Novembre 2022 devant la commisission d'examen composée de :

| M. William Jalby         | Professeur, Université de Paris Saclay - Versailles    | Rapporteur                |

|--------------------------|--------------------------------------------------------|---------------------------|

| M. Laurent Colombet      | Directeur de Recherche, CEA                            | Rapporteur                |

| M. Denis Barthou         | Professeur, Bordeaux INP                               | Directeur de thèse        |

| M. Brice Goglin          | Directeur de Recherche, Inria                          | Examinateur               |

| Mme. Corinne Ancourt     | Directrice de Recherche, Ecole des Mines de Paris      | Examinatrice              |

| Mme. Emmanuelle Saillard | Chargée de Recherche, Inria                            | Examinatrice (Encadrante) |

| M. Marc Sergent          | Ingénieur de Recherche, Atos                           | Examinateur (Encadrant)   |

| M. Scott Baden           | Professeur Émérite, Université de San Diego Californie | Invité                    |

1

## Résumé

Le monde du Calcul Haute Performance ne cesse d'évoluer, en proposant des modèles de programmation parallèles vastes et variés. Pour s'adapter aux exigences de l'exascale en terme de puissance de calcul et de traitement rapide. Le modèle de programma- tion parallèle le plus utilisé est le Message Passing Interface (MPI). Le standard MPI a été utilisé dans le HPC pendant des décennies. Le protocole de communication point à point send/receive, appelé two-sided MPI, est largement utilisé et privilégié dans les applications. Une alternative à ce modèle de communication point à point est les com- munications one-sided, principalement implémenté dans les langages et bibliothèques PGAS (Partitioned Global Address Space). Le standard MPI-3, qui a été présenté en Septembre 2012, a inclus une mise à jour importante des communications one-sided dans MPI, aussi appelées les RMA (Remote Memory Access) et adoptées par le standard de- puis MPI-2, pour fournir plus de performance et introduire de nouveaux modes d'accès aux données. Cependant, les performances des communications one-sided restent loin d'être celles attendues.

Développer un programme parallèle est souvent plus difficile mais plus performant dans de la mémoire partagée plutôt que d'utiliser des transferts send/receiv pour échan- ger des données, les processus peuvent implicitement communiquer dans la mémoire partagée avec une utilisation de certains mécanismes de synchronisation (verrous, séma- phores..) pour garantir un accés sans concurrence à la partie mémoire souhaitée.

Dans ces travaux de recherche nous allons principalement nous intéresser au modèles de programmation à mémoire distribuée et globalement adressable MPI-RMA dont le principe est de designer un espace mémoire virtuel global et partagé dans les systèmes à mémoire distribuée, ce qui permet aux processus de communiquer à travers cette mémoire. Bien que le modèle PGAS existe depuis très longtemps, et promet plus d'asyn- chronisme. Ce modèle reste peu utilisé par la communauté du HPC à cause de plusieurs raisons notamment les modes de synchronisation requis pour sécuriser le programme. Comme le modèle PGAS propose un concept de programmation en mémoire partagée dans de la mémoire distribuée. Les problèmes de concurrence d'accès s y appliquent. Pour cette raison la programmation PGAS peut se révéler très difficile, car l'utilisateur a la responsabilité de gérer explicitement tous les accès mémoire pour garantir la co- hérence du programme. Il est donc intéressant pour les programmeurs d'applications, d'avoir des outils qui leur permettent de faciliter la programmation. De développer des codes correctes et efficaces.

Dans le cadre de ces travaux de recherche l'objectif principal est de développer une analyse dynamique à l'exécution, et une analyse statique à la compilation, pour vérifier les codes des applications PGAS. Cette analyse mixte permet d'exploiter les avantages des deux approches. une approche dynamique qui repose sur des exécutions concrètes qui dépendent d'un seul jeu d'entrée, et donc se limiter à détecter que les erreurs présentes dans l'exécution analysée. Une approche statique qui ne dépend pas du jeu d'entrée et offre une vue globale du code, et considère tous les chemins d'exécution possibles.

Durant cette thèse nous avons developpé un outil qui regroupe les deux analyses statique et dynamique appelé RMA-Analyzer. Il a été propsé dans but d'aider à la programmation de codes MPI-RMA, notamment en proposant une aide avancée à l'utilisateur dans la détection d'erreurs de concurrence connus comme accès illégaux liés aux applications MPI-RMA. Dans le but de faciliter la programmation aux utilisateurs, avec une aide dynamique sur la réalité et l'origine des éventuels blocages en MPI-RMA.

Mots clès : Programmation parallèle, MPI-RMA, Analyse statique et dynmaique.

### Contexte de la recherche

La simulation numérique demande des codes qui ont un fort besoin en puissance de calcul et de traitement rapide, pour résoudre des problèmes à très grande taille. Cela a conduit à la conception de machines très puissantes et massivement parallèles et qui visent le milliard de milliards d'opérations par seconde (exaflops). Pour utiliser ces ma- chines efficacement, nous avons besoin de modèles de programmation parallèles simples et de supports d'exécution efficaces. Dans ce contexte, nous allons nous intéresser au modèle de programmation parallèle basé sur des communications unilatérales appelé MPI-RMA.

Développer un programme parallèle en utilisant MPI-RMA est souvent plus difficile, mais plus performant grace aux accès directs à la mémoire partagée entre les processus, plutôt que d'utiliser des transferts send/receive pour échanger des données, les processus peuvent implicitement communiquer directement en utilisant les communications unila- térales. Dans le cadre de l'utilisation de ces communications, et comme la mémoire et globalement accessible par tous les processus d'un communicateur, des erreurs d'accès à la mémoire partagée peuvent avoir lieu. La détection de ces erreurs peut se révéler difficile et cela peut avoir des impacts négatifs et réduit l'utilisation de ce modèle de programmation.

Très peu d'outils ont été developpés dans le cadre de la détection d'accès concurrents dans des programmes MPI-RMA. Les outils qui existent privilégient des solutions à base de fichiers de traces qui proposent des retours à l'utilisateur à la fin du programme. Les developpeurs sont donc contraints d'attendre la fin de leurs programmes pour retrouver l'erreur avec très peu d'aide. En plus, la taille des fichiers de traces peut vite devenir très grande. Ces solutions ne sont pas adaptées à des applications à très grande échelles.

Durant cette thèse, nous nous sommes intéressés à la détection des erreurs d'accès concurrents à la mémoire partagée entre processus dans les applications MPI-RMA. Nous avons développé un outil de vérification appelé le RMA-Analyzer qui effectue une analyse

statique et une analyse dynamique afin de détecter les erreurs d'accès concurrents dans des applications MPI-RMA. Le RMA-Analayzer vérifie à la compilation la présence de potentielles erreurs locales de concurrence pour alerter l'utilisateur avant le lancement du programme. Ensuite, le RMA-Analyzer vérifie tous les accès concurrents à l'exécution pour arrêter le programme à la première erreur trouvée.

#### Démarche adoptée

Dans le cadre de cette thèse, notre but principal est d'apporter une aide efficace au programmeur pour lui faciliter la programmation en MPI-RMA. Programmer en MPI-RMA requiert une connaissance particulière de comment programmer en mémoire distribué et globalement adressable pour avoir une partie de la mémoire qui sera par- tagée entre processus. Un programmeur doit d'abord ouvrir une fenêtre mémoire pour que les processus s'échangent les accès, et à la fin du programme, cette fenêtre mémoire est libérée. Durant la vie de cette fenêtre mémoire des communications entre processus peuvent avoir lieu dans des époques de synchronisation bien précises pour préciser avec quel processus et quel type d'opération vont avoir lieu sur une zone mémoire ciblée. Avec ce principe de programmation, des zones mémoires sont partagées entre processus et des opérations de lecture écriture sur une même zone mémoire peuvent vite devenir problématiques. Des accès concurrents peuvent avoir lieu sur la même zone mémoire.

Notre outil repère les erreurs de concurrence d'accès à la mémoire et se charge de les montrer à l'utilisateur. Pour cela, pendant l'exécution du programme, note outil instru- mente le code pour vérifier les erreurs. Nous traçons tous les accès mémoire et nous les enregistrons dans une structure de données appelée arbre binaire de recherche et nous analysons tous les accès mémoire entre les processus d'un même communicateur loca-lement et globalement. Les processus se partagent chacun les accès enregistrés à leurs mémoires respectives aussi en s'envoyant les informations grâce à un protocole de Send/- Recv classique. Si deux accès concurrents sont détectés et au moins un des accès est une opération d'écriture, on arrête immédiatement le programme. Une analyse statique a été ajoutée comme un support à cette analyse dynamique dans le but d'alerter le program- meur pendant la compilation des potentielles erreurs liées aux accès concurrents. Toutes les erreurs locales à un processus sont ainsi détectable au préalable de l'exécution. Ce- pendant, comme le jeu d'entrée n'est pas connu au moment de la compilation, nous ne pouvons pas affirmer la présence des erreurs.

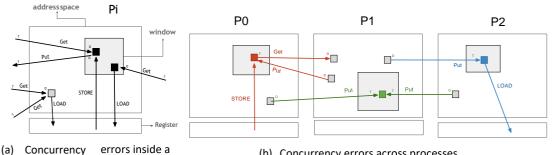

Notre première contribution consiste à identifier les d'afférents types d'erreurs qui peuvent avoir lieu dans un programme MPI-RMA. Le premier type d'erreur peut avoir lieu au sein d'un même processus et donc, des accès natifs load et store peuvent se chevaucher avec des accès distants (RMA) ou que des accès RMA entre eux (nous ne détectons pas les erreurs de concurrence d'accès purement natives). Le deuxième type d'erreur c'est les erreurs d'accès concurrents qui peuvent impliquer plusieurs processus d'un même communicateur. Ces accès peuvent avoir lieu au sein d'une mémoire d'un

processus donné avec des accès provenant de différents processus. Il peut aussi y avoir un chevauchement entre les accès load/store et les opérations RMA de plusieurs proces- sus visant la même adresse mémoire. En identifiant les types d'erreurs, nous avons créé une matrice avec croisement des accès locaux et distants dans le but de l'utiliser durant le process de la vérification d'erreur.

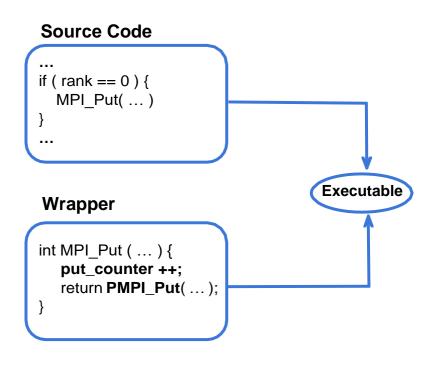

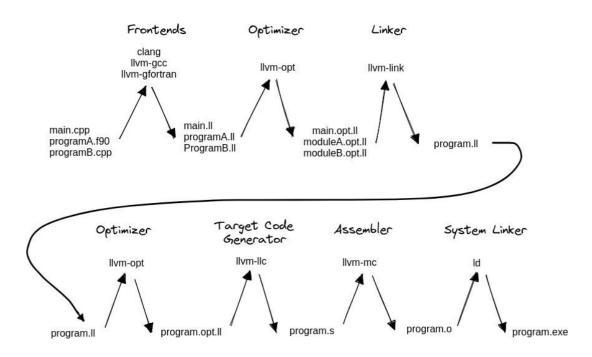

Une fois les types d'erreurs sont connus et identifiés, Cette matrice sera utile à notre algorithme de détection dynamique pourlever une erreur de concurrence si elle existe. À l'aide de la platforme de profiling MPI (PMPI). Nous enregistrons tous les accès d'un jeu de données durant le temps d'exécution du programme. Nous construisons des intervalles qui représentent la zone mémoire sur laquelle un des processus lit ou écrit selon l'opéra- tion de communication. La borne inférieure de l'intervalle représente le début de la zone mémoire choisie et la borne inférieure représente la fin de la zone mémoire. Ces inter-valles sont tous enregistrés avec leurs types d'accès (lecture, écriture) durant le temps d'exécution. Selon le type d'accès et la zone mémoire, s'il y a un chevauchement entre les intervalles (intersection d'intervalle), ca veut dire qu'une zone mémoire est simultané- ment accédée avec au moins un accès en écriture. Nous précisons ici que Le programme s'arrête dès la première erreur trouvée, car d'autres erreurs de concurrences dans le pro-gramme peuvent être des séquelles de la première, d'où notre intérêt de traiter le plus tôt possible ce type d'erreurs. Cette démarche implique aussi une instrumentation des accès load /store grâce à une pass LLVM pour enregistrer tous les accès locaux aussi et les comparer avec les accès RMA. Ceci peut engendrer un temps d'exécution beaucoup plus élevé au moment on nous exceutons un programme avec notre outil. C'est pourquoi nous avons réfléchi à notre deuxième contribution qui est de faire une analyse statique qui sera un support à la première analyse.

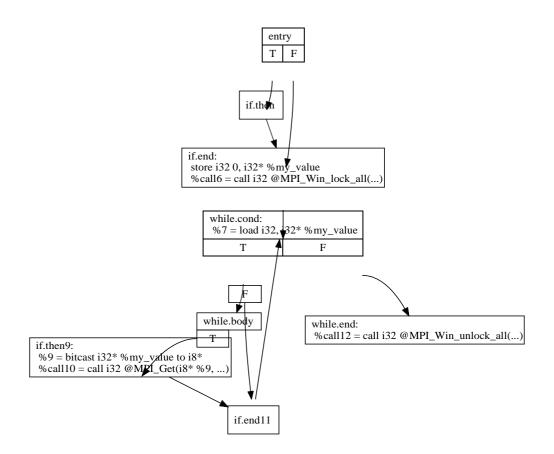

Une analyse statique a pour but de trouver où se placer dans la chaîne de compilation pour analyser le flot de contrôle du programme et de regarder tous les chemins possibles du code. Nous allons ensuite appliquer une recherche en largeur et en profondeur du Graphe de Flot de Contrôle (CFG) pour rechercher des accès concurrents à la mémoire dans les différentes branches du CFG et être sûr de tout vérifier. Comme le CFG dépend fortement du rang de chaque processus, il est important de souligner que certaines er- reurs de concurrence entre plusieurs processus ne peuvent pas être visibles et donc, pas détectables avec une simple analyse statique. Cela dit, toutes les erreurs potentielles et locales à un seul processus peuvent être examinées et détectées avec cetteanalyse.

## **Résultats obtenus**

Nous avons implémenté le RMA-Analyzer comme étant un outil indépendant qui peut être utilisé pour la vérification des programmes MPI-RMA écrits en C et Fortran. Car, un support pour les codes Fortran a été ajouté.

Nous avons utilisé pour nos tests la machine *Pise* qui appartient à l'équipe MPI et IA distribuée de la R&D de l'entreprise Atos située à Échirolles.

À fin de nous rendre compte du bon fonctionnement du RMA-Analyzer, nous avons développé une suite de tests qui contient toutes les erreurs possibles qui peuvent avoir lieu à cause de différents accès à la même zone mémoire et qui couvre tous les croisements possibles de la matrice d'erreur précédemment décrite. Cette matrice a été réduite pour le cas d'erreurs locales détectables statiquement. Notre outil détecte toutes ces erreurs dynamiquement et statiquement aussi, mais uniquement pour les tests qui contiennent des erreurs locales. L'outil renvoie un retour à l'utilisateur en soulignant le fichier, la ligne et le type d'erreur. De plus, nous avons fait tourner notre outil sur deux grandes applications appelées CFD-Proxy et Nemo.

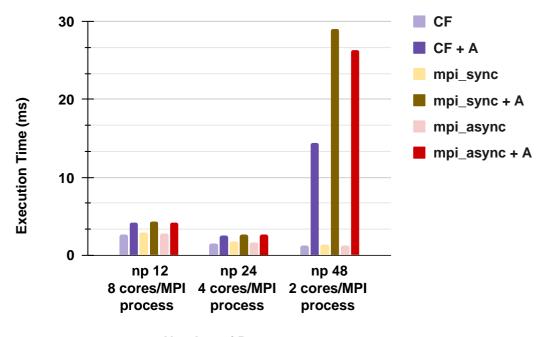

Nous avons utilisé CFD-Proxy pour l'instrumentation partielle avec les accès MPI- RMA seulement sans les accès locaux load/store, pour mesurer le cout engendré par l'utilisation de l'outil en faisant une comparaison entre les temps d'exécution avec et sans le RMA-Analyzer. Le coût engendré par le RMA-Analyzer sur CFD-Proxy est re- lativement haut, mais raisonnable avec un taux à 40% au mieux sur l'une des variantes de cette application.

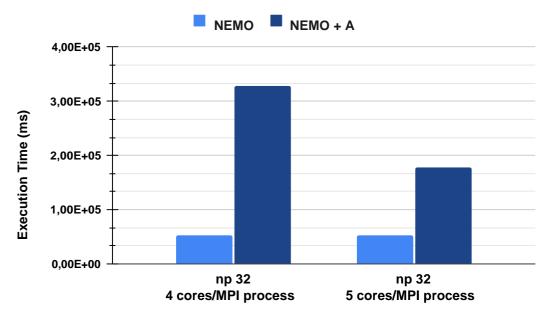

Nous avons ensuite testé le RMA-Anlayzer sur Nemo pour une instrumentation glo- bale en prenant en compte cette fois-ci les accès locaux, load/store. Nous avons effectué une comparaison des temps d'exécution sur deux variantes de l'application avec et sans le RMA-Analyzer. Le coût engendré sur l'application Nemo avec une instrumentation générale augmente considérablement à cause des enregistrements des accès load/store.

Nous avons utilisé notre analyse statique sur un code expérimental d'environ 3500 lignes de codes, écrits en C++. Le code est basé sur le benchmark Global Update Ran- domAccess (AKA GUPS). Le code que nous avons utilisé est une version MPI-RMA d'un code existant écrit en UPC++. Notre analyse arrive à détecter les erreurs locales trouvées dans ce code.

#### Conclusion

Les programmeurs des applications MPI ont besoin d'outils efficaces et fiables à fin de pouvoir détecter des erreurs de programmation. Dans le cadre de cette thèse, nous proposons un outil appelé le RMA-Analyzer qui a pour but d'aider au mieux les programmeurs des applications MPI-RMA à détecter les erreurs liées aux accès concurrents à la mémoire. Le RMA-Analyzer propose une analyse dynamique accompagnée d'une analyse statique pour vérifier les erreurs de concurrence dans des programmes MPI- RMA. La particularité de cet outil est qu'il propose une analyse complète qui détecte toutes les erreurs durant le temps d'exécution du programme et arrête immédiatement le programme dès la première erreur trouvée. Cet outil est le premier à pouvoir rajouter une analyse statique pour détecter statiquement les potentielles erreurs de concurrence locales. L'outil alerte l'utilisateur de la présence des erreurs avec un retour précis de l'endroit et du type de l'erreur. Comme travaux futurs, nous prévoyons d'améliorer l'outil sur plusieurs axes :

- —Améliorer le coût engendré par l'outil en améliorant l'analyse statique pour pou- voir détecter des erreurs entre processus, et ensuite combiner les deux analyses.

- —Notre outil ne prend pas en compte les synchronisations unilatérales, mais uniquement les synchronisations globales entre les époques. De ce fait, l'outil peut être amélioré pour prendre les synchronisations inter époques.

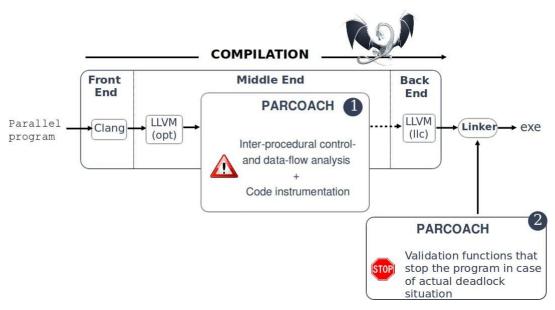

- —Nous prévoyons d'intégrer les travaux de cette thèse dans PARCOACH : PARallel COntrol flow Anomaly CHecker. Cet outil est utilisé dans la détection d'erreur liées aux blocages de fonctions collectives dans des programmes MPI,OpenMP, MPI+OpenMP.

- —Nous prévoyaons aussi d'étendre la vérification d'erreurs à d'autres applications PGAS. Comme le modèle de communication unilatéral et le modèle de mémoire basé sur PGAS de MPI-RMA est compatible avec d'autres runtimes et implé- mentations PGAS. Étendre l'outil dans cette direction va aider d'autres pro- grammeurs.

#### Abstract

Almost all high performance computing applications are written in MPI, which will continue to be the case for at least the next several years. MPI offers one-sided communications which is a well known distributed programming paradigm for high performance computers, as its properties allows for a greater asynchronism and computation/communication overlap than classical message passing mechanisms. In this work, we focus on the Remote Memory Access interface of MPI (MPI-RMA), in which each process explicitly exposes an area of its local memory as accessible to other processes to pro- vide asynchronous one-sided reads, writes and updates. While MPI-RMA is expected to greatly enhance the performance and permit efficient implementations on multiple platforms, it also comes with several challenges with respect to memory consistency. This programming model imposes restrictions with respect to performing asynchronous accesses to shared data. Developers must handle complex memory consistency models and complex programming semantics.

This thesis focuses on detecting memory consistency errors in MPI-RMA programs. We developed an hybrid approach verification tool for MPI-RMA programs that can provide solutions in detecting errors over the space of memory consistency (also known as data races) in MPI-RMA programs.

Our method combines two analyses. First, we perform an on-the-fly analysis to stop the program in case of a consistency violation during runtime. Second, a static analysis support is added to detect local concurrency errors and warn the user of the presence of potential memory consistency errors at compile time.

The experimental results demonstrate that our method is validated on a collection of codes containing errors and on two real applications. Our experiments show that our approach is scalable when running on MPI one-sided applications with an overhead of 40% at best on one of our experiments. We also show on several tests and an MPI-RMA variant of the GUPS benchmark that the static analysis allows to detect such errors on user codes. The error codes have been validated for an integration in the MPIBugs Initiative open-source test suite (MBI).

Key words : High Performance Computing, Hybrid analysis, MPI-RMA

## Acknowledgement

Avant de tourner la page de cette magnifique aventure qui est ma thèse et partir pour une nouvelle aventure, je tiens à remercier mes encadrants Emmanuelle et Marc de m'avoir permise de réaliser cette thèse. Je n'oublierai jamais nos moments ensemble.. Biarritz, Bordeaux, Grenoble, Denver, Zurich ou encore l'Ile d'Oléron.. J'ai pris beau- coup de plaisir à travailler avec vous. Merci pour votre suivi, vos conseils avisés, votre précieuse aide et votre soutien. Un Merci tout particulier à mon directeur de thèse Denis d'avoir su me comprendre et d'avoir été là pour orienter et assurer le bon déroulement de ma thèse. Merci de m'avoir formé à la recherche durant cette thèse, avec beaucoup de patience il faut le dire ! Merci d'avoir su constituer une équipe dans laquelle il fait plus que bon vivre! J'ai appris tant humainement que professionnellement à tes côtés. Je ne pouvais demander mieux comme directeur de thèse j'ai été très chanceuse.

J'adresse également mes remerciements à mes rapporteurs William Jalby et Laurent Colombet pour la lecture de mon manuscrit et leurs retours constructifs. Merci à Brice Coglin et Corrine Ancourt d'avoir accepté de se joindre à mon jury en tant que président de jury et examinatrice.

Merci à mon comité de suivi de thèse Laurent Simon et Serge Chaumette d'avoir challengé mes résultats lors de nos réunions et aider ainsi à développer mon esprit scien- tifique et répondre mieux aux questions posées lors de mes présentations.

Scott Baden thank you for always teaching me new things and telling me lot of stories from your sabbatical year. Thank you as well for being part of my thesis Jury as guest of honor I'm the one honored by having you. I can't forget all the amazing moments we have had together your pictures are the best ever ..

Merci à toute mon équipe STORM Amina, Nathalie, Marie Christine, Olivier, Sa- muel, Raymond et Pierre André pour votre accueil, les pauses chocolats, nos moments d'échange au restaurant les vendredis ou à la cafette et les nombreuses présentations très enrichissantes. J'adorais parler avec chacun d'entre vous. Raymond tu m'as beaucoup fait rire avec les anecdotes CEA lors de nos nombreuses pauses dans l'openspace.

Merci à tous les doctorants stagiaires et ingénieurs STORM, quelle joie de venir vous raconter mes galères de parking le matin à mon arrivée et de partager despauses chocolat ou encore des pauses sans intérêt scientifique juste pour faire de la politique avec des débats interminables. Merci à toi Baptiste d'avoir su me distraire tous les ven- dredis pour rédiger zéro phrase car impossible de résister aux pauses avec toi et devoir rédiger le week-end pour rattraper. Merci Chiheb de ton aide pour l'installation logiciel sur plafrim et pour nos nombreuses discussions sur tes entretiens et ton ressenti sur le HPC de tes nombreux conseils pour une carrière réussie après la thèse. Merci Vincent de nous avoir toujours fait rire avec ton projet de ventilation dans l'open space et denous

avoir fait de belles présentations de ce projet brillantissime qui va surement devenir une belle idée de startup merci de t'être incrusté à pratiquement toutes les pauses STORM ou ailleurs pour nous donner le max d'infos. Merci Gwenolé d'avoir toujours été sage d'avoir toujours défendu avec moi les doctorants contre les nouveaux stagiaires qui nous envahissaient. Merci aussi de m'avoir aidé à ajuster mes figures durant ma rédaction, c'était un plaisir de te voir tous les jours et de t'entendre rigoler très souvent avec nous et surtour avec Maxime. Merci à Maxime d'avoir souvent proposé des plans sorties ou j'ai souvent été absente car j'avais souvent une sortie de prévue, et d'avoir été Mon- sieur chemise du lundi. On s'impatientait d'entendre tes histoires avec tes étudiants et les galères techniques de tes cours. Romain notre voyage à Rome après notre école d'été restera toujours et à jamais dans ma tête. Merci d'avoir été le quide par excellence pour la visite de cette magnifique ville. Radja merci de nous avoir fait rire pendant ton stage avec tes beaux ongles et tes blagues parisiennes merci de m'avoir écouté sur les avantages de la thèse et pas que ... et te voilà doctorant. Je te souhaite bon courage pour la suite. Bastien, merci pour nos échanges passionnants sur comment gagner plus d'argent après la thèse d'avoir toujours été présent pour une pause café à n'importe quelle heure de la journée. Merci Van Man de m'avoir écouté me plaindre sur les inscriptions chères de la thèse durant toutes ses dernières années et merci pour ton résumé de thèse pour mon related work :p Pierre Antoine merci de m'avoir écouté quand je me plaignais des RMA et de m'avoir souvent posé des questions pertinentes sur mon sujet de thèse. Beaucoup de belles choses à toi pour la suite. Merci Thomas pour les discussions intéressantes sur ta formation et tes stages. Gwenolé, Maxime, Bastien, Chiheb, Radja, Romain, Bap-tiste, Thomas, VanMan et Pierre Antoine vous étiez plus que des collèques pour moi vous êtes de vrais bons amis. Je n'oublierai jamais votre soutien pendant ma rédaction de thèse (à part Maxime qui n'était pas dutout rassurant :D) . Je ne pouvais pas oublier de remercier les anciens STORM aussi Adrien et Pierre merci de m'avoir aidé à bien commencer cette aventure en 2019 vous m'aviez dit Célia t'inquiète pas tu vas y arriver à notre toute première pause déjeuner au haut carrée.

Un merci tout particulier à Alice, Diane, et Pélagie pour nos nombreuses discussions rigolades et pauses thée girly. Alice merci d'avoir toujours eu les mots justes pour me dire à quel point je paraissais apaisée et relaxée pendant ma rédaction et que ça te donnait limite envie de rédiger en première année;) tu as toujours su trouver la phrase parfaite au bon moment pour moi. Je vous souhaite à toutes les deux (Alice et Diane) de vivre vos meilleures thèses. Je sais que vous allez faire du bon boulot. Bon courage Pélagie avec ton nouveau travail chez Atos.

Merci à Kun et Mariem mes meilleures amies et collègues d'avoir toujours été là pour moi. Merci de m'avoir encouragé et donné la force pour continuer cette aventure. Merci Mariem pour tes délicieux plats tunisiens et gâteaux, merci de m'avoir fait goûter à tes merveilles. Kun t'avoir à côté de moi dans l'open space quand je m'arrachais les cheveux durant la rédaction me réconfortait tellement. Nos très nombreuses pauses, fous rires sur la terrasse de l'Inria et nos apéros chez moi demeureront sans doutes dans ma tête à jamais merci pour ta gentillesse sans limite. Mariem et Kun je vous aime énor- mément.

#### À mes très chers parents :

Source de vie, d'amour, de joie et d'affection. Dont le mérite, les sacrifices, les qualités humaines m'ont permis de vivre ce jour. Ce travail et ces longues années d'études c'est aussi grâce à vous deux. MERCI de m'avoir tout donné et de m'avoir tout appris et de m'avoir transmis les bonnes valeurs que je transmettrai à mon tour à mes enfants plus tard. Merci maman pour tes nombreuses nuits blanches pour rester avec moi durant mes révisions de bac scientifique, merci de m'avoir préparé mes plats préférés et de m'avoir toujours encouragé à finir mes études et d'aller le plus loin possible. Merci à toi papa de m'avoir toujours attendu devant notre portail après mes cours au lycée pour faire quelques pas ensemble avant de rentrer à la maison parler d'une nouvelle politique, de ce que j'ai appris de ma journée ou juste rigoler pensemble avant de retrouver les bons plats de maman au déjeuner. Tu m'as tout donné et tu as tout fait pour que je puisse poursuivre mes études en France. Merci de nous avoir aidé à accomplir nos meilleures carrières mes frères, soeurs et moi. Ce travail aujourd'hui je vous le dédie entièrement à vous. C'est moi qui suis fière de vous avoir et pasl'inverse.

#### À mon tendre et cher mari :

Merci d'avoir été à mes côtés dès le début de cette aventure, de m'avoir si fortement soutenu et de m'avoir donné tant d'amour et de courage pour affronter mes doutes. Tu me donnais tous les jours la joie et la confiance dont j'avais besoin. A notre plus beau jour le jour de notre mariage le 12 juin 2021, à notre inoubliable voyage de noces en République Dominicaine à nos nombreux voyages à deux et celui des Maldives cet été ou j'avais complètement oublié que j'avais une thèse à rédiger tellement on s'amusait comme des petits sur la plage, à nos restaurants et dégustation de plats inconnus, à nos sorties et escapades en amoureux, à chacun des instants vécus à tes côtés à nos innombrables discussions et débats politiques à nos passions la découverte le sport et les voyages ce travail t'est dédié. La vie avec toi m'a tout simplement rendue heureuse et m'a permise d'avancer même quand je pensais que c'était impossible. Merci pour tout. Il me tarde de vivre l'après thèse avec nos futurs projets ensemble (Très nombreux)<3.

À mes deux chères soeurs adorées merci d'avoir été ma source d'inspiration et merci d'avoir été toujours présentes aux plus beaux moments de ma vie et de m'avoir soutenu au moments durs merci de m'avoir donné deux merveilleux neveux et une très belle nièce. La vies est tellement belle avec des soeurs.

#### À ma famille et belle famille :

Merci de m'avoir fait confiance et de m'avoir toujours encouragé et pour toutes les belles occasions célébrées avec vous.

À mes supers amies Belinda, Alicia, Louiza, Kenza et plus particulièrement à toi Lynda je n'oublierai jamais notre voyage en côte d'Azur et les merveilleux moments passés avec toi .. les fous rires, les jeux de cartes, nos balades dans Paris les week-ends d'anniversaires .. un pur bonheur merci pour absolument tout.

"Living your dreams takes courage, persistence, and lots of trial and error"

–By me!

# CONTENTS

| 1 | Intro | oductior | n27                                                         |    |

|---|-------|----------|-------------------------------------------------------------|----|

|   | 1.1   | Plan of  | f Study                                                     | 29 |

|   | 1.2   | Terms    | Used                                                        | 30 |

|   | 1.3   | Thesis   | Contributions                                               | 31 |

| 2 | Bacl  | kground  | and Motivation32                                            |    |

|   | 2.1   |          | uction                                                      |    |

|   | 2.2   | Partitio | oned Global Address Space (PGAS)                            |    |

|   |       | 2.2.1    | PGAS Languages                                              |    |

|   |       | 2.2.2    | PGAS Libraries                                              | 35 |

|   |       | 2.2.3    | PGAS Data Distribution Model                                | 35 |

|   |       | 2.2.4    | PGAS Data Access Model                                      | 35 |

|   | 2.3   | The M    | essage Passing Interface (MPI)                              | 36 |

|   |       | 2.3.1    | Point to Point Communication                                | 37 |

|   |       | 2.3.2    | Collective Communication                                    |    |

|   |       | 2.3.3    | MPI One-sided Communication with Remote Memory Access (RMA) | 41 |

|   | 2.4   | MPI-RI   | MA programming Overview                                     | 43 |

|   |       | 2.4.1    | Key Benefits of MPI-RMA Programming                         | 45 |

|   |       | 2.4.2    | Comparing MPI-RMA and MPI Two-sided Programming Models.45   |    |

|   |       | 2.4.3    | Implementation of MPI-RMA Operations                        | 46 |

|   |       | 2.4.4    | MPI-RMA Window Creation                                     | 47 |

|   |       | 2.4.5    | MPI-RMA Data Movement Operations                            | 47 |

|   |       | 2.4.6    | Accumulates Purpose                                         |    |

|   |       | 2.4.7    | Synchronization in MPI-RMA                                  | 50 |

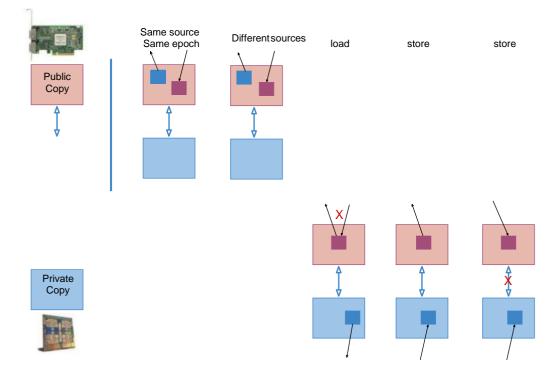

|   |       | 2.4.8    | MPI-RMA Memory Model                                        | 52 |

|   |       | 2.4.9    | MPI-RMA Operation Ordering                                  | 55 |

|   |       | 2.4.10   | MPI-RMA Request Based operations                            | 56 |

|   | 2.5   | MPI-RI   | MA Proprieties and Programming Challenges                   | 57 |

|   | 2.6  | Conclusion                                                            | 59   |

|---|------|-----------------------------------------------------------------------|------|

| 3 | Dyn  | amic Data Race Errors Detection in MPI-RMA Programs60                 |      |

|   | 3.1  | Introduction                                                          | . 60 |

|   | 3.2  | Memory Consistency in MPI-RMA                                         | 61   |

|   |      | 3.2.1 Happens-before Rules                                            | 51   |

|   |      | 3.2.2 Consistency Order Rules                                         | .62  |

|   |      | 3.2.3 Memory Consistency Errors in MPI-RMA Programs (Data Race.62     |      |

|   |      | 3.2.3.1 Non-determinism in MPI-RMA                                    | . 64 |

|   |      | 3.2.4 Motivating Examples of MPI-RMA Programs                         | 65   |

|   |      | 3.2.5 Extending MPI-RMA Operations Compatibility                      | 59   |

|   | 3.3  | Dynamic Data Race Detection Algorithm                                 | 71   |

|   | 3.4  | Design and Implementations of the RMA-Analyzer                        | 74   |

|   |      | 3.4.1 The MPI profiling Interface                                     |      |

|   |      | 3.4.2 LLVM Pass                                                       | 75   |

|   |      | 3.4.3 Parallel Control Flow Anomaly Checker (PARCOACH)                | 77   |

|   |      | 3.4.4 The RMA-Analyzer Framework Overview                             | 80   |

|   | 3.5  | Implementation concerns                                               | . 81 |

|   | 3.6  | Experimental Results                                                  | . 82 |

|   |      | 3.6.1 Experimental Setup                                              | 32   |

|   |      | 3.6.2 Targeted Applications                                           | 82   |

|   |      | 3.6.3 Microbenchmarks                                                 | . 83 |

|   |      | 3.6.4 Runtime Overhead Impacts of Dynamic verification on CFD-Proxy84 |      |

|   |      | 3.6.5 Runtime Overhead Impacts of Dynamic verification on NEMO        | 87   |

|   |      | 3.6.6 Memory Consumption Impacts                                      | 88   |

|   | 3.7  | Conclusion                                                            | 39   |

| 4 | Stat | ic Data Race Detection in MPI-RMA Programs90                          |      |

|   | 4.1  | Introduction                                                          | . 90 |

|   | 4.2  | Motivating Examples                                                   | .91  |

|   | 4.3  | Static Detection of Local Concurrency Errors                          | 95   |

|   | 4.4  | Local Concurrency Errors Detection Algorithm                          | 95   |

|   |      | 4.4.1 Example of a Control Flow Graph                                 | 97   |

|   |      | 4.4.2 Proof of the Algorithm                                          | . 98 |

|   | 4.5  | Experimental Results                                                  | . 99 |

|   | 4.6  | Conclusion 1                                                          | .01  |

| 5 | Rela | ated Work103                                                          |      |

|   | 5.1  | Introduction                                                          |      |

|   | 5.2  | Debugging and Correctness Checking Tools for MPI Programs             | .03  |

|   |      | 5.2.1 Debugging tools 1                                               | 104  |

|   |      | 5.2.2 Correctness Checking Tools for MPI Programs                     | 104  |

|   |      | 5.2.3 Discussion                                                      | .109 |

| Data ra<br>109 | ace errors detection Tools for MPI-RMA and Shared Memory | Pro- grams                                                                                                                                                                                          |

|----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3.1          | Data Race Detection Tools for MPI-RMA Programs           | 109                                                                                                                                                                                                 |

| 5.3.2          | Data Race Detection tools for SharedMemory Programs      | 111                                                                                                                                                                                                 |

| 5.3.3          | Discussion                                               |                                                                                                                                                                                                     |

| Summ           | ary                                                      | 113                                                                                                                                                                                                 |

|                | 109<br>5.3.1<br>5.3.2<br>5.3.3                           | Data race errors detection Tools for MPI-RMA and Shared Memory1095.3.1Data Race Detection Tools for MPI-RMA Programs5.3.2Data Race Detection tools for Shared Memory Programs5.3.3DiscussionSummary |

# 6 Conclusion115

# LIST OF FIGURES

| 1.1        | MPI One-sided communication bug28                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1        | Overview of the Partitioned Global Address Space (PGAS) model                                                                                                     |

| 2.2<br>2.3 | Comparing the syntax used in CAF, X10, and UPC to access remotedata.36<br>Example of asynchronous point-to-point communication using the rendez- vous<br>protocol |

| 2.4        | Comparing the syntax of MPI_Putwith MPI_Send                                                                                                                      |

| 2.5        | One-sided communication example. Process 1 is not actively involved in the communication                                                                          |

| 2.6        | Comparing MPI one-sided and MPI two sided programming Models                                                                                                      |

| 2.7        | MPI-RMA window initialisation operations                                                                                                                          |

| 2.8        | MPI-3 memory window creation variants                                                                                                                             |

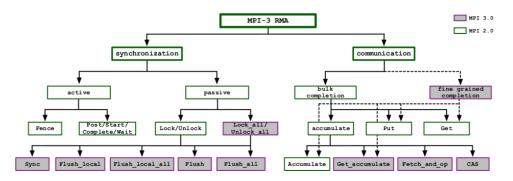

| 2.9        | Overview of communication options in the MPI-3 specification from [49] 49                                                                                         |

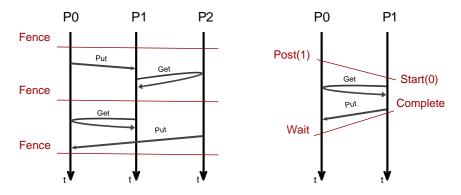

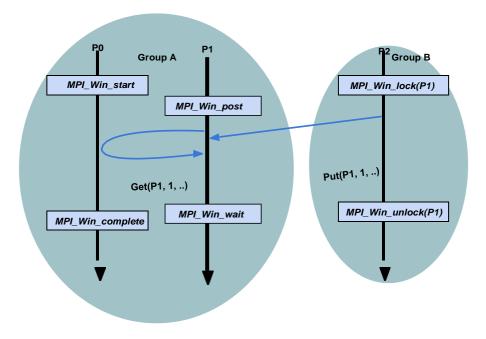

| 2.10       | Examples of Active Target modes where synchronizations are made through Fence functions (on the left) or with Post-Start-Complete-Wait (on the right)             |

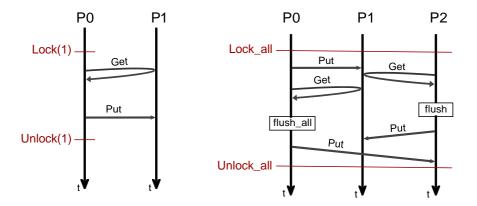

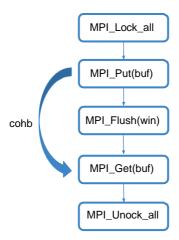

| 2.11       | Lock/Unlock functions targeting a specific process (on the left) or Lock_all                                                                                      |

| 2 1 2      | Unlock_all (on the right)                                                                                                                                         |

|            | MPI RMA memory model (separate windows)                                                                                                                           |

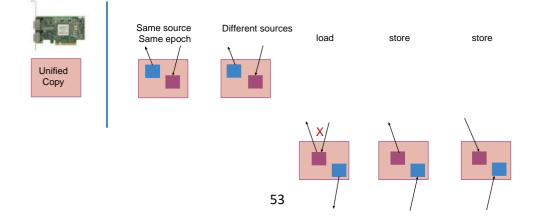

|            | MPI RMA memory model (unified windows)                                                                                                                            |

|            | Ordered accumulate operations                                                                                                                                     |

|            | Ordering by synchronizations                                                                                                                                      |

| 2.16       | An example illustrating an unknown completion of MPI-RMA operations inside an epoch                                                                               |

| 2.17       | An example illustrating the lack of ordering when using MPI-RMA oper- ations.                                                                                     |

|            | 58                                                                                                                                                                |

| 3.1        | Conflicting two operations in the same program63                                                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2        | Synchronized operations in an MPI-RMA program63                                                                                                                                                                                             |

| 3.3        | Example of a non-deterministic behavior in RMA programs64                                                                                                                                                                                   |

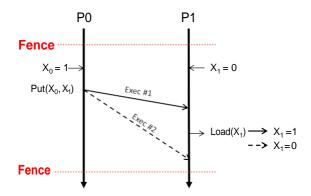

| 3.4        | Memory consistency error within an epoch at a single process                                                                                                                                                                                |

| 3.5        | Memory consistency error occurring in several synchronization epochs                                                                                                                                                                        |

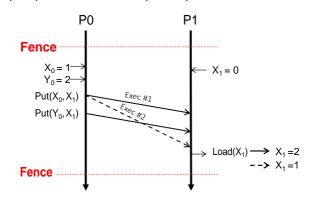

| 3.6        | Consistency error between two processes                                                                                                                                                                                                     |

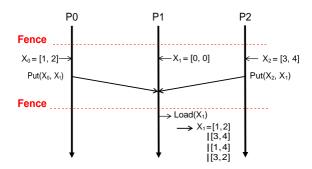

| 3.7        | Consistency error between three processes                                                                                                                                                                                                   |

| 3.8<br>3.9 | Consistency error between native Store and MPI_Put across two pro- cesses 69<br>Example of memory consistency errors. Dashed edges represent WRITE<br>operations while plain edges represent READ operations on the colored boxes. <i>O</i> |

|            | and <i>T</i> respectively indicate the origin and target processes                                                                                                                                                                          |

| 3.10       | A simple example of PMPI wrapper counting the number of MPI_Put.75                                                                                                                                                                          |

|            | Static compilation using the llvm toolchain                                                                                                                                                                                                 |

|            | Overview of the PARCOACH Framework                                                                                                                                                                                                          |

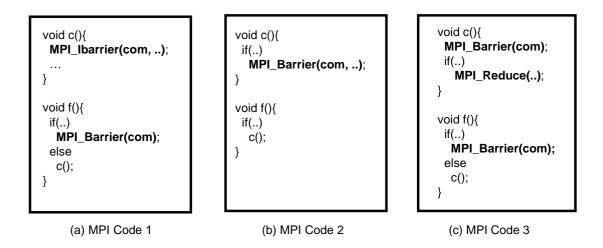

| 3.13       | Examples of MPI codes containing collectives                                                                                                                                                                                                |

|            | MPI Code 2 functions CFG (left) and the corresponding PPCFG (right).79                                                                                                                                                                      |

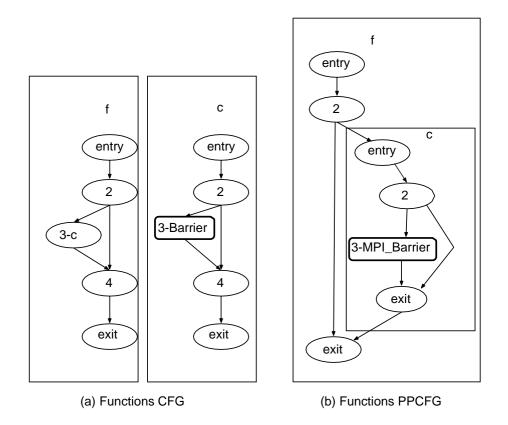

|            | Error output returned by PARCAOCH used for the code infigure3.13(a).79                                                                                                                                                                      |

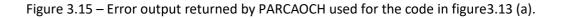

| 3.16       | Overview of the RMA-Analyzer Framework                                                                                                                                                                                                      |

|            | Error output returned by the RMA-Analyzer tool used for the code of Figure3.7<br>84                                                                                                                                                         |

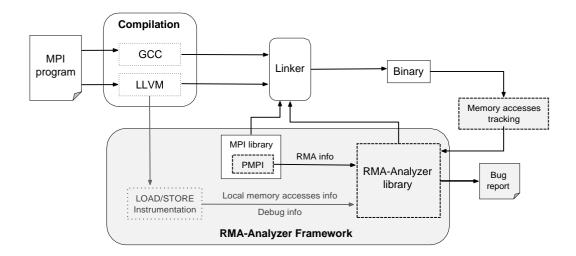

| 3.18       | Runtime overhead of the RMA-Analyzer on CFD-Proxy passive target with tree approaches. CF = Comm Free, PT = Passive Target, NPT                                                                                                             |

|            | = Notified Passive Target. "+ A" means execution time with the RMA- Analyzer.                                                                                                                                                               |

| 2 10       |                                                                                                                                                                                                                                             |

| 3.19       | Runtime overhead of the RMA-Analyzer on CFD-Proxy active target with tree approaches. CF = Comm Free, mpi sync = Bulk fence synchroniza- tion version,                                                                                      |

|            | mpi_async = MPI fence with early receives in asynchronous manner. "+ A"                                                                                                                                                                     |

| 2 20       | means execution time with the RMA-Analyzer                                                                                                                                                                                                  |

| 3.20       | Runtime overhead of the RMA-Analyzer on NEMO tra_adv kernel. "+ A" means execution time with the RMA-Analyzer                                                                                                                               |

| 4.1        | An example of local memory concurrency errors at origin process PO in passive                                                                                                                                                               |

|            | target "Lock/Unlock_all" mode. Bold statements are conflicting memory                                                                                                                                                                       |

| 4.2        | accesses(Get, Get) at origin side. X = Window memory location of <i>PO</i> 91<br>An example of local memory concurrency errors at origin process <i>P1</i> in passive                                                                       |

| 4.2        | target "Lock/Unlock all" mode. Bold statements are conflicting memory                                                                                                                                                                       |

|            | accesses (Put,Get) at origin side. Y = Window memory location of <i>P1</i>                                                                                                                                                                  |

| 4.3  | An example of local memory concurrency errors at origin process <i>P2</i> in passive target "Lock/Unlock_all" mode. Bold statements are conflicting memory accesses (Get with Store on <b>buf</b> ) at origin side. Z = Window memory location of <i>P2</i> |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4  | An example of local memory concurrency errors at origin <i>PO</i> in active target<br>"Fence" mode. Bold statements are conflicting memory accesses (Get with Put)<br>at origin side. X = Window memory location of <i>PO</i>                               |

| 4.5  | An example of local memory concurrency errors at origin <i>P1</i> in active target<br>"Fence" mode. Bold statements are conflicting memory accesses (Get with Load<br>on <b>buf</b> ) at origin side. Y = Window memory location of <i>P1</i>               |

| 4.6  | An example of local memory concurrency errors at origin <i>P2</i> in active target<br>"Fence" mode. Bold statements are conflicting memory accesses (Put with Store<br>on <b>buf</b> ) at origin side. Z = Window memory location Of <i>P2</i>              |

| 4.7  | Correction of code4.1                                                                                                                                                                                                                                       |

| 4.8  | Correction of code4.6                                                                                                                                                                                                                                       |

| 4.9  | CFG from a benchmark computing a binary tree broadcast algorithm.98                                                                                                                                                                                         |

| 4.10 | Output returned by the analysis on thecode figure 4.1                                                                                                                                                                                                       |

| 4.11 | Code snippet from an MPI-RMA version of GUPS101                                                                                                                                                                                                             |

# LIST OF TABLES

| 2.1 | MPI-RMA operation compatibility table when two or more processes ac- cess a window at the same target concurrently in the unified memory model.<br>OVL: Overlapping operations permitted. NOVL:<br>Non-overlapping operations permitted.<br>From [31]                                    | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | MPI-RMA operation compatibility table when two or more processes ac- cess a window at the same target concurrently in the separate memory model.<br>OVL: Overlapping operations permitted. NOVL:<br>Non-overlapping operations permitted. X: The combination of operations is erroneous. |    |

|     | From [31]                                                                                                                                                                                                                                                                                | 1  |

| 3.1 | Compatibility of RMA operations and local load/store accesses on the same address space. O=ORIGIN, T=TARGET, $\sqrt{=}$ overlapping is per- mitted, x=undefine behavior, overlapping isnot permitted                                                                                     |    |

| 3.2 | Transition table for access types. Given an address with an access type (first row) and a new operation to this address (first column), the table defines the new access type after the operation. We assume there is no data race within a (multithreaded) process.                     |    |

| 3.3 | RMA-Analyzer statistics on BST for each application. Memory sizes are in KB 8                                                                                                                                                                                                            | 8  |

| 4.1 | Compatibility of RMA operations and local load/store accesses on the same address space. $\sqrt{=}$ overlapping is permitted, x= undefined behavior, overlapping is not permitted. R = READ, W = WRITE                                                                                   | 5  |

| 4.2 | Results on our microbenchmark suite 10                                                                                                                                                                                                                                                   | )0 |

| 5.1 | List of MPI correctness checking tools 10                                                                                                                                                                                                                                                | )9 |

| 5.2 | List of MPI-RMA memory | y consistency checking tools |  |

|-----|------------------------|------------------------------|--|

|-----|------------------------|------------------------------|--|

# LISTINGS

| 2.1  | A Simple MPI program with send receive pattern        | .37  |

|------|-------------------------------------------------------|------|

| 2.2  | An MPI Program Calculating $\pi$ by Using Collectives | 41   |

| 2.3  | Example of One-sided Communication                    | 43   |

| 2.4  | Pseudo Code Using Request-based Operations            | . 57 |

| imag | es/scottscode.c 1                                     | 01   |

# LIST OF ALGORITHMS

| 1 | Data Race Errors Detection         |    |

|---|------------------------------------|----|

| 2 | Local Concurrency Errors Detection |    |

| 3 | Breadth-first Search               | 96 |

| 4 | Analysis of a basic block          |    |

CHAPTER 1

# INTRODUCTION

High-Performance Computing (HPC) has become an important area of progress across a wide range of scientific and engineering disciplines like Computational Fluid Dynamics (CFD) engineering, climate simulation, weather prediction, computational chemistry, bio-informatics and nuclear reactors. High performance computing is the ability to process data and perform complex calculations at high speeds which predicted the increase in frequency of a computer's Central Processing Unit (CPU). Today su- percomputers are becoming faster, cheaper, and more popular, the future growth in computing power will have to come from both the hardware side and the software side. Programmers who are used to think and code sequential software now have to turn to parallel software to achieve the desired performance. Parallel programs can be written by using different programming paradigms. Among them, the Message Passing Inter- face (MPI) [42], and the Partitioned Global Address Space (PGAS) [104] model that are largely used in HPC systems. While MPI and PGAS are often referred as two different programming paradigms MPI is the industry standard communication library for HPC. MPI is the most widely used programming API for writing parallel programs that run on large clusters. The design goals of MPI are flexibility, performance and portability.

MPI accomplishes those goals by providing a very rich semantics that incorporate the features of synchronous and asynchronous systems with several communication modes. Synchronous communications are easy to use and understand in contrast to asynchronous communications which are more complex. MPI introduces a model for asynchronous and remote memory access called MPI-RMA first presented in the MPI-2 specification and then improved and updated in MPI-3. this programming model is quite similar to PGAS, as it is also based on one-sided communications of data, and global access of partitioned memory. Unlike MPI two-sided, where the sender and the receiver explicitly call the send and receive functions, one-sided communications decouple data movement from synchronization and offer asynchronous reads, writes, and updates without involving the target process. MPI-RMA allows efficient data movement between processes with

less synchronizations but the performance and flexibility of MPI-RMA come with several debugging challenges. MPI programs, especially under the presence of non-determinism, are notoriously hard to debug. It thus poses programming challenges to use as few synchronizations as possible, while preventing data race and unsafe accesses without tampering with the performance.

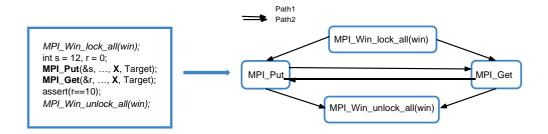

MPI\_Win\_lock\_all(win)

MPI\_Get(&buf, 1, MPI\_INT, 0, 0, 1, MPI\_INT, win)

if(buf%2 == 0) /\*bug:load/store access of buf \*/

buf ++;

MPI\_Win\_unlock\_all(win)

Figure 1.1 – MPI One-sided communication bug.

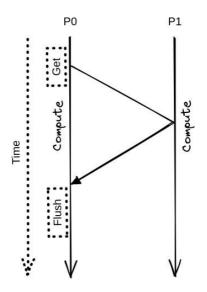

To highlight how difficult debugging can get with MPI, we consider a simple MPI- RMA program shown in figure 1.1 which contains a subtle bug where the one-sided MPI Get operation is asynchronous, it retrieves the data from the target process and as a result the data may not be ready before the MPI\_Win\_unlock. Because of this situation the load access of **buf** can retrieve an old value and the store access on **buf** can be overwritten by a value retrieved from MPI Get. This example illustrates the need for more powerful verification techniques tools than ordinary random testing on a cluster. These tools can help maintaining data consistency in the presence of asynchronous data accesses from multiple processes. Even though there are many techniques and tools that help developers discover MPI nondeterminism errors, they basically fall into one of these three categories: static methods, dynamic methods, and model checking. Static methods have the advantages of being inputindependent since they verify the program at the source code level. However, they tend to provide too many false alarms, especially for a large code base, due to the lack of runtime knowledge. Model checking methods are very powerful for small programs in terms of verification coverage but they quickly become impractical for large software due to the infeasibility of building models for such software. Dynamic methods such as testing or dynamic verification are the most applicable methods for large MPI programs since they produce no false alarms and also require little work from the tool users.

Unfortunately, the state of the art in MPI-RMA debugging remains a fundamental chal- lenge and to the best of our knowledge, very few works exist to detect concurrency bugs in MPI-RMA and most of them rely on post-mortem analyses.

This thesis was set up as part of a collaboration between Inria Bordeuax Sud-Ouest and Atos Echirolles. The main objective was to develop a tool that can help the pro- grammer to easily code MPI-RMA applications. This tool should provide solutions to detect memory consistency errors in MPI-RMA applications. We will introduce the RMA-Analyzer, a framework that identifies memory consistency errors in MPI-RMA programs written in C and Fortran. Our framework uses a static and a dynamic on-the- fly analyses and focuses on MPI-3 features. The advantages of our approach are twofold. First, contrary to state-of-the-art solutions, this analysis can detect potential local con- currency errors at compile time. Second, it detects all consistency errors that can happen during the execution of an MPI-RMA program for a given set of input data. When an error occurs, the analysis can directly stop the program, warn the user about the error, and provide detailed information on the conflicting accesses. Indeed, since a silent race condition can provoke errors later in the program, it is mandatory to detect the first race condition and immediately warn the user that an error has happened, instead of waiting until the end of the program to do so. We argue that these two properties are of tantamount importance for helping users porting large-scale code bases on MPI-RMA.

The RMA-Analyzer will be fully integrated into the *PARallel Control flow Anomaly CHecker* (PARCOACH) [85]. PARCOACH was developed to provide a combination of static and dynamic analyses to enable an early verification of hybrid HPC applications. This thesis proposes to extend the PARCOACH framework to help and guide the pro- grammer in the development of PGAS programs, in particular by detecting data race errors with a dynamic help on the reality of these issues with precise feedback to the user. It can also provide an optimization of an MPI program into a PGAS or MPI one-sided program.

### 1.1 Plan of Study

This thesis focuses on data race detection for MPI-RMA programs. We talk about two main pieces. The first part, focuses on dynamic analysis of MPI-RMA programs to detect all the errors that can occur during the execution time of the program. The second part, focuses on a static analysis of MPI-RMA programs that comes as support to the dynamic analysis with the aim of detecting more relevant local concurrency errors before executing the program.

The rest of this thesis is organized as follows: Chapter 2 presents the related background and motivation of this work. Chapter 3 and chapter 4 describe both the corresponding contributions. Chapter 5 discuss the related work to survey some debugging and correctness tools of MPI programs. Chapter 6 concludes the work and discuss the future research directions.

## 1.2 Terms Used

A **cluster** consists of hundreds or thousands of compute servers that are networked together. Each server is called a **node**which in each cluster work in parallel with each other, boosting processing speed to deliver high performance computing.

A **process** is an entity that encapsulates a private local memory space, i.e., memory that by default is only accessible from within that process. A process may expose parts of its local memory space to other processes, either through shared memory to allow access to other processes on the same node, or by contributing it to a global memory space, in which memory is available to processes executing on different nodes. Inside a process, several threads of execution (or threads) may execute concurrently with shared access to the memory in the local memory space and shared node-local and global memory that the process has access to.

A **thread** typically executes in a local execution context, i.e., local variables and a pri- vate stack to call functions, but has access to global variables shared by all threads in the process. The concurrent execution may be real parallel execution on distinct CPU cores or seemingly parallel through time-slicing performed by the operating system or a user-level runtime library. Thus, threads (in the meaning of the term used in this work) are preemptable, i.e., the operating system scheduler may force the thread to yield the core and schedule another thread or process to execute on it. A **task** typically consists of an action to be executed, i.e., a function call, as well as a set of inputs and outputs. The task's action is executed either directly on the stack of the executing thread or in the context of a user-level thread (ULT), which then contains the execution state throughout the course of execution of the action. The difference between a thread and task is that tasks are typically non-preemptable and a cooperative scheduler relies on the task to eventually complete its execution. A task is a self-contained work-package that transforms a set of input data into a set of output data.

The term **parallel** will be used to describe actions that actually happen at the same time, e.g., two processes executing on two different nodes run in parallel.

A **communicator** : a group of processes. An MPI applications starts always by in- cluding all processes in a default communicator called MPI\_COMM\_WORLD. New communicators can be created from the MPI\_COMM\_WORLD. MPI ensures that each communicator is unique thus a communicator can be seen as a system defined tag. Col- lective communications rely on communicators.

A **window** is composed of a group of processes, specified at window creation time by a communicator and a contiguous region of memory at each process and this memory region may differ in size and address.

An **epoch** is the execution span occurring between calls to MPI synchronization func- tions.

The term **concurrent** will be used to describe actions that may happen at the same time, e.g., two independent operations may be executed at the same time. The term **concurrency** on the other hand, describes the maximally possible degree of parallelism, i.e., the set of actions that could be executed at the same time in the absence of resource

restrictions.

The term **runtime** system (or runtime) refers to an entity that is part of the soft- ware stack and typically resides between the application and the operating system or hardware, coordinating operations and resources requested by the application. Task schedulers and MPI implementations are two examples of runtime systems.

# **1.3** Thesis Contributions

This thesis makes the following contributions :

We present the extended compatibility table to show all the errors that can possibly occur in MPI-RMA programs. Errors are grouped into two categories : local concur- rency errors and remote concurrency errors depending on the process that performs the communication operation (origin or target). We bring forward our data race detec- tion algorithms to discuss our technique that comes with a new hybrid approach. Our method presents two main steps to detect memory consistency errors in MPI-RMA pro- grams. Firstly, at execution time we perform an on-the-fly analysis to collect relevant MPI-RMA operations and load/store accesses. If a data race error is found we stop the program and report a consistency violation. Secondly, we present a static analysis that has been added in order to automate the dynamic analysis. It detects all common local concurrency errors before dynamic analysis takes place.

CHAPTER 2

# BACKGROUND AND MOTIVATION

Since the work described in this thesis is largely relying on MPI communication paradigms, with an emphasis on the semantics of MPI one-sided communication, in this chapter we provide related background on MPI communication paradigms so that the reader can better understand the semantics provided by the MPIstandard.

## 2.1 Introduction

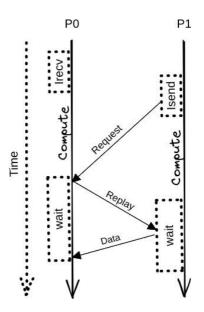

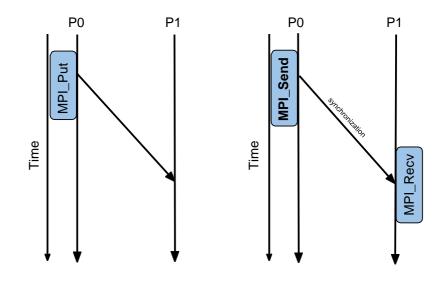

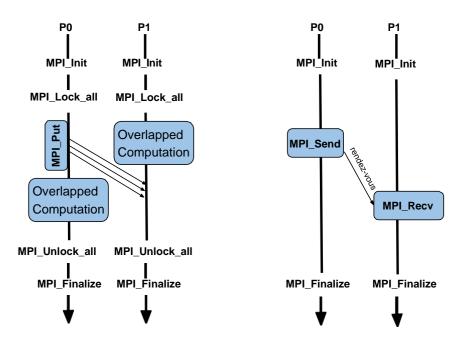

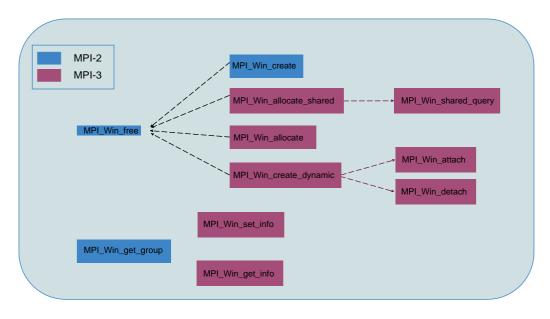

Parallel programs can be written by using different programming paradigms. Among them, the Message Passing Interface (MPI), and the Parallel Global Address Space (PGAS). These paradigms are largely used in HPC systems. While MPI and PGAS are often referred as two different programming paradigms, MPI allows a model for remote memory access called MPI-RMA also called MPI one-sided communication. First in- troduced in the MPI-2 specification, and has updated and seen a major review in the MPI-3 by including several routines in order to handle additional window allocations and add new synchronization modes. The main goal of these modifications is to fully take advantage of the network's low-level remote direct memory access (RDMA) ca- pabilities[31]. This programming model is quite similar to PGAS, as it is also based on one-sided communications of data, and global access of partitioned memory. Unlike MPI two-sided, where the sender and the receiver explicitly call the send and receive functions, one-sided communication decouples data movement from synchronization and offer asynchronous reads, writes, and updates without involving the target process and allow a better overlap of computation with communication. While MPI-RMA allows efficient data movement between processes with less synchronizations, its programming is error-prone as it is the user responsibility to ensure memory consistency. It thus poses programming challenges to use as few synchronizations as possible, while preventing data race and unsafe accesses without tampering with the performance. In this chapter we give the background according to PGAS and both MPI two-sided and one-sided communications. We first, introduce the partitioned global address space and its languages and system-level libraries. Second, we discuss both MPI point-to-point communication and collectives. Finally, we introduce MPI one-sided by giving its overview, and its programming challenges.

# 2.2 Partitioned Global Address Space (PGAS)

PGAS is a parallel programming paradigm that aims to improve programmer productivity while at the same time targeting for high performance. The main premise of PGAS is that a globally shared address space improves productivity, and that distinction between local and remote data accesses allow performance optimizations and support scalability on largescale parallel architectures. To this end, PGAS preserves the global address space while embracing awareness of non-uniform communicationcosts.

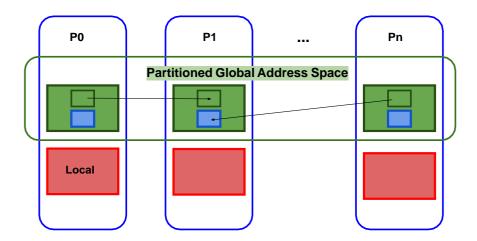

In PGAS programs, each process exposes a part of its local memory to other processes as shown in figure 2.1. This way, the memory of other processes can be directly ad- dressed from a sender, thus allowing to perform one-sided communications (e.g. Put, Get). This communication model is known to significantly improve the asynchronism and the overlap of communications with computations, which is why it is expected to gain focus in the next years for the Exascale era and beyond [7]. Compute Express Link CXL [99] which is a cache-coherent interconnect for processors, memory expansion, and accelerators implements advanced PGAS inter-process communication mechanism. It maintains a unified coherent memory space between the CPU and any memory on the attached CXL device. It is designed to address the growing needs of high-performance computational workloads by supporting heterogeneous processing and memory systems.

Figure 2.1 – Overview of the Partitioned Global Address Space (PGAS) model.

#### 2.2.1 PGAS Languages

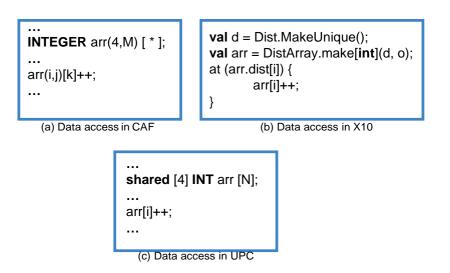

Today, about a dozen languages exist that adhere to the PGAS model here we men- tion: **Co-ArrayFortran** (CAF) [73] is a very old PGAS language, however, it remains one of the most known. It is a parallel extension of Fortran 95 which adds the Co-Array as a feature to the language. CAF aims to manage and explicit the cost of accessing remote data asynchronously. CAF fosters the programmer to use the local proprieties of the code. Remote accesses are different from the classic Fortran code.

**Titanium**[105] is a Java language designed for high-performance parallel scientific com- puting. It was conceived at UC Berkeley and provides implementations for symmetric multiprocessing (SMP) as well as for distributed systems. The language is designed to enable explicit asynchronous parallel programming, while facilitating compiler optimiza- tions for optimal performance. It provides the notion of local and remote references and uses explicit asynchronous communication primitives to exchange data.

**Unified Parallel C** (UPC) [39] is a PGAS extension of the C language. It integrates features from three proposals: PCP [13], Split C [26], and AC. The specification of the UPC language is provided by the UPC consortium, which consists of academic and government institutions as well as companies. Well-known implementations of the UPC language include Berkeley UPC, GNU GCC UPC, and HP UPC. UPC programs can make use of shared data objects, which is the main PGAS facility of the language. Data values that reside in shared memory are hosted by one of multiple threads but can be accessed asynchronously in a syntactically transparent way from different threads, even though a 'remote access' normally comes at a communication cost.

**Chapel**[17] is a parallel programming language developed by Cray as part of the Cray Cascade project [16]. It identifies the global view of computation and give the support for both task and data-driven parallelism, besides, the separation of the algorithm and data structure details is the main programmability concepts of the language. Chapel provides concepts for multi-threaded and locality-aware parallel programming. The language also supports many concepts from object-oriented languages and generic programming.

**X10** [20] is a programming language developed by IBM Research. The name X10 refers to times 10, the aim of the language to achieve 10 times more productivity in HPC soft- ware development. X10 is described as a modern object-oriented programming language providing an asynchronous PGAS programming model with the goal of enabling scalable parallel programming for high-end computers. X10 extends the PGAS model with asyn- chronicity by supporting lightweight asynchronous activities and enforcing asynchronous access to non-local state. Its explicit fork/join programming abstractions and a sophis- ticated type system are meant to guide the programmer to write highly parallel and scalable code, while making the cost of communication explicit. The task parallelism is implemented on top of a work-stealing scheduler.

**Fortress** [94] is a programming language designed for high-performance computing, originally developed by Sun Micro-systems. The expressive type system facilitates static analysis, while efficient scheduling of implicitly parallel computations is guaranteed by the work-stealing algorithm. Another characteristic of Fortress is its mathematical syn-

tax. The use of uni-code for instance for the sum operator and the idea of "typeset- ting" code give the language a mathematical look-and-feel. This language is no longer under development.

#### 2.2.2 PGAS Libraries

PGAS terminology is also used to design a system level in the context of a num- ber of communication libraries such as MPI-2 [42], GASNet [9], ARMCI [72], GPI [45] and OpenSHMEM [19]. These libraries are used for SPMD programs to store memory segments for remote memory access through one-sided operations such as put, get and accumulate. MPI-3 [38] proposes to fix the MPI-2 RMA API as it does not respond to the needs of application programmers. GASNet is used by Berkely UPC and other PGAS languages, while ARMCI is used by Global Arrays. Theses libraries are not meant to be used by application developers.

UPC++ [6] is also a C++ library that supports PGAS programming, and is designed to interoperate with MPI, OpenMP [18], CUDA [25], ROCm HIP [59] and other HPC frameworks. It leverages GASNet-EX [8] to deliver low-overhead, fine-grained commu- nication, including Remote Memory Access and Remote Procedure Call (RPC) [69].

In the context of this thesis, we will only focus on MPI library with a particular interest in MPI-3 specification.

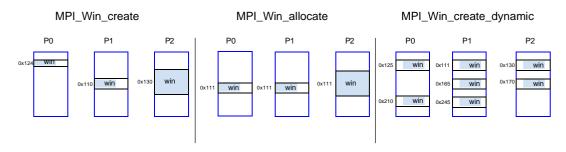

#### 2.2.3 PGAS Data Distribution Model