# **RF switches based on 2D materials** Simon Skrzypczak

#### ▶ To cite this version:

Simon Skrzypczak. RF switches based on 2D materials. Micro and nanotechnologies/Microelectronics. Université de Lille, 2023. English. NNT: 2023ULILN006 . tel-04320864

# HAL Id: tel-04320864 https://theses.hal.science/tel-04320864

Submitted on 4 Dec 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE

Présentée à l'Université de Lille

Ecole Doctorale Sciences de l'Ingénierie et des Systèmes

Pour obtenir le grade de :

# Docteur de l'Université

# Spécialité : Micro et Nano Technologies, Acoustique et Télécommunications

Par

SKRZYPCZAK Simon

Unité de recherche: IEMN

RF switches based on 2D materials

Commutateurs RF fabriqués à partir de matériaux 2D

Soutenue le 29 Mars 2023 devant la Commission d'examen

Membres du jury :

| Mr. Henri HAPPY (Professeur)                     | Directeur de thèse (IEMN – Lille) |

|--------------------------------------------------|-----------------------------------|

| Mme. Christelle AUPETIT-BERTHELEMOT (Professeur) | Présidente du Jury (Université de |

| Limoges – Limoges)                               |                                   |

| Mme. Florence PODEVIN (Professeur)               | Rapporteur (INP – Grenoble)       |

| Mr. Renato NEGRA (Professeur)                    | Rapporteur (RWTH – Aachen)        |

| Mr. Emiliano PALLECCHI (Maître de conférences)   | Examinateur (IEMN – Lille)        |

| Mr. Deji AKINWANDE (Professeur)                  | Examinateur (University of Texas  |

| – Austin)                                        |                                   |

| Mr. Mario LANZA (Professeur associé)             | Examinateur (KAUST – Thuwal)      |

| Mr. Guillaume DUCOURNAU (Professeur)             | Invité (IEMN – Lille)             |

# Table of Content

| Gene | eral In | ntroduction:                                                        | 5  |

|------|---------|---------------------------------------------------------------------|----|

| CHAI | PTER I  | I State of the art of RF Switches                                   | 10 |

| 1.   | Int     | troduction                                                          | 12 |

| 2.   | RF      | switch characteristics                                              | 12 |

|      | 2.1.    | Main topology of RF switch                                          | 16 |

| 3.   | Тес     | chnologies used nowadays                                            | 16 |

|      | 3.1.    | PIN diode - short description                                       | 16 |

|      | 3.2.    | FET - Short description                                             | 18 |

|      | 3.3.    | MEMS switching devices                                              | 21 |

| 4.   | Em      | nerging switching technologies                                      | 24 |

|      | 4.1.    | Description of metal insulator transition (MIT) switch              | 25 |

|      | 4.2.    | Phase change material (PCM) switches                                | 26 |

|      | 4.3.    | Conductive bridge switches                                          | 27 |

|      | 4.4.    | Resistive switching observed with 2D material                       | 28 |

|      | 4.5.    | Application for emerging technology RF switches                     | 30 |

| 5.   | Со      | mparison between different RF switches                              | 30 |

| 6.   | Со      | nclusion                                                            | 32 |

| 7.   | Ref     | ferences                                                            | 33 |

| CHAI | PTER I  | II Optimization of the 2D RF switch layout and RF measurement setup | 37 |

| 1.   | Int     | troduction                                                          | 39 |

| 2.   | RF      | study                                                               | 39 |

|      | 2.1     | Coplanar waveguide (CPW)                                            | 39 |

|      | 2.2     | CPW study                                                           | 40 |

|    | 2.3  | 3        | Structure of 2D switch                                                                | 42  |

|----|------|----------|---------------------------------------------------------------------------------------|-----|

| 3  |      | De       | scription of DC and RF measurement procedure                                          | 48  |

|    | 3.1  | L        | RF measurement procedure                                                              | 48  |

|    | 3.2  | 2        | De-embedding procedure                                                                | 49  |

| 4  | •    | Соі      | nclusion                                                                              | 52  |

| 5  |      | Ref      | ferences                                                                              | 53  |

| СН | APTE | ER I     | III Fabrication and RF characterization of 2D based switches                          | 55  |

| 1  |      | Int      | roduction                                                                             | 58  |

| 2  | •    | Fab      | prication process                                                                     | 59  |

|    | 2.1  | L        | Overview of microfabrication                                                          | 59  |

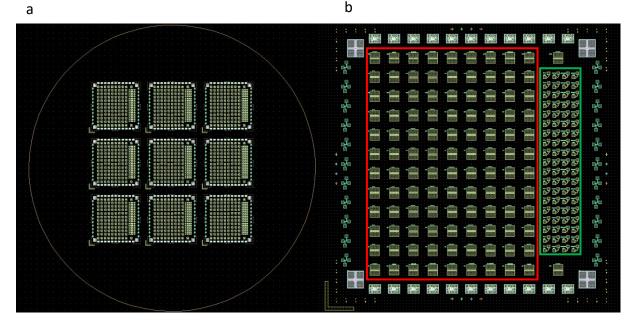

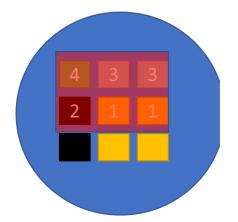

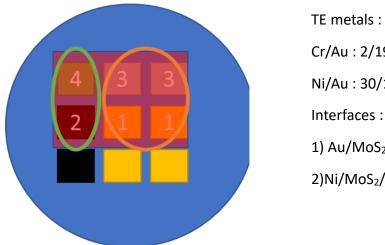

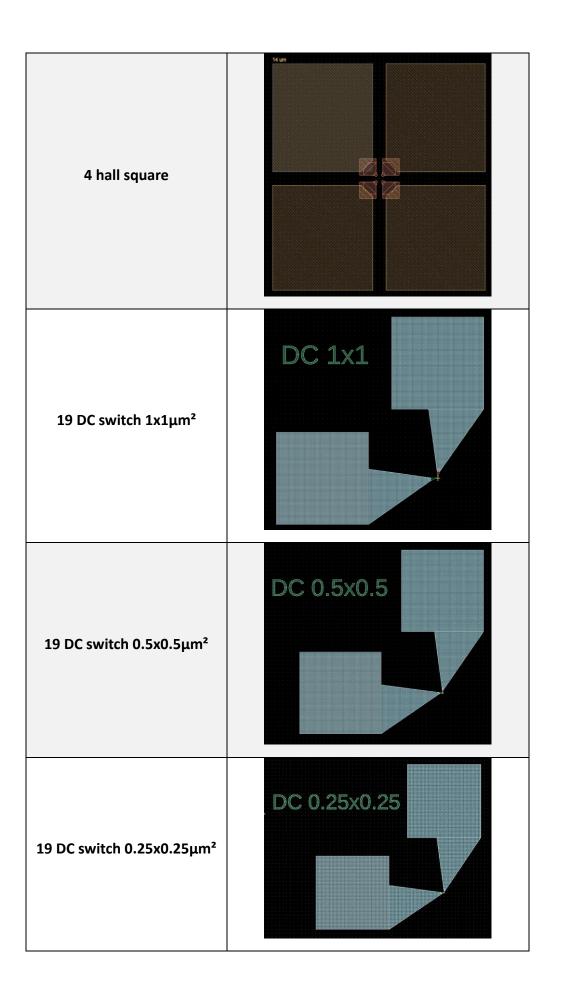

|    | 2.2  | 2        | Description of the layout                                                             | 60  |

|    | 2.3  | 3        | Fabrication of alignment marks                                                        | 52  |

|    | 2.4  | 1        | Fabrication of the bottom electrode (BE)                                              | 53  |

|    | 2.5  | 5        | 2D material transfer and patterning                                                   | 65  |

|    | 2.6  | 5        | Fabrication of the top electrode (TE)                                                 | 58  |

|    | 2.7  | 7        | CPW pads deposition                                                                   | 70  |

| 3  |      | I-V      | characterization and S-parameters study                                               | 71  |

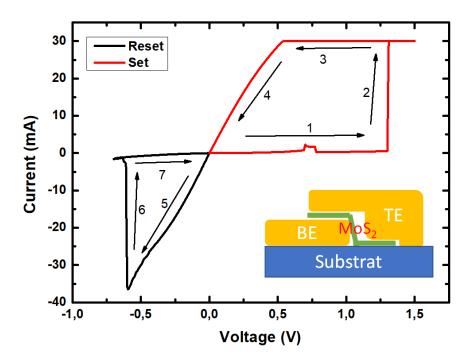

|    | 3.1  | L        | Switching phenomenon description                                                      | 71  |

|    | 3.2  | 2        | Measurement protocol                                                                  | 73  |

|    | 3.3  | 3        | I-V characteristics measurement and S-parameters of switches with 6 monolaye          | ers |

|    | of   | Mo       | S <sub>2</sub> (SS03)                                                                 | 76  |

|    | 3.4  | 1        | I-V characteristics and S-parameters measurement of Ni/MoS <sub>2</sub> /Pt interface | 30  |

|    | 3.5  | 5        | SS07 I-V characteristic and S-parameters measurement                                  | 34  |

| 4  |      | De<br>88 | embedding of devices and FOM parameters extraction of 3MLs and 6 MLs of Mo            | S2  |

| 5  | •    | Соі      | nclusion                                                                              | 91  |

| 6   |      | Ref   | erences                                                                      |

|-----|------|-------|------------------------------------------------------------------------------|

| CHA | ٩PT  | ER I  | V Linearity and data communication94                                         |

| 1   |      | Intr  | roduction96                                                                  |

| 2   |      | Line  | earity97                                                                     |

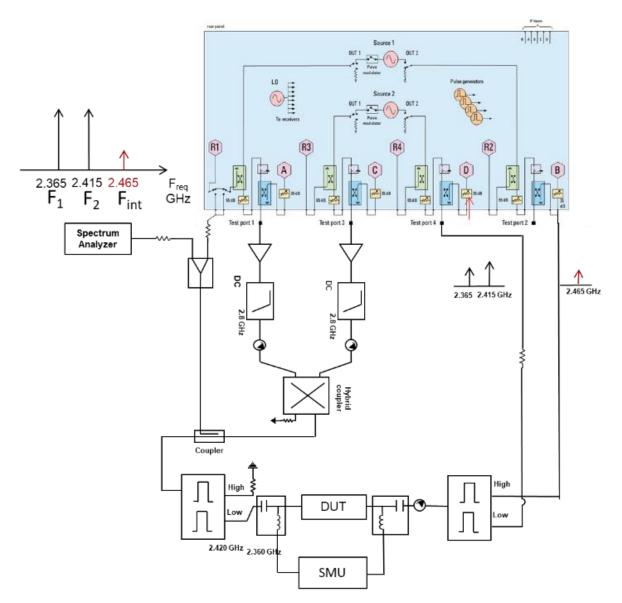

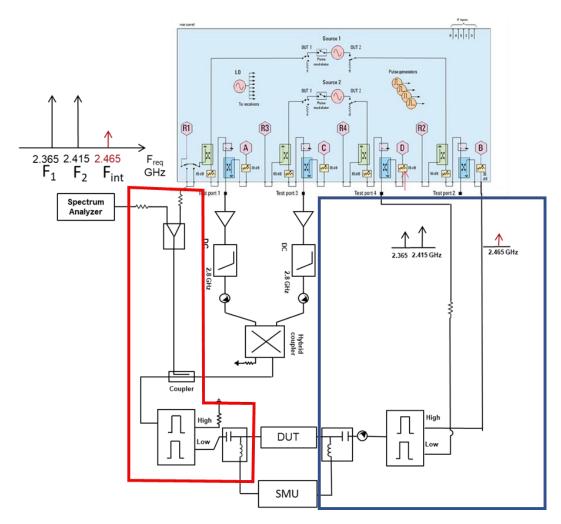

|     | 2.:  | 1.    | IP3 measurement principle98                                                  |

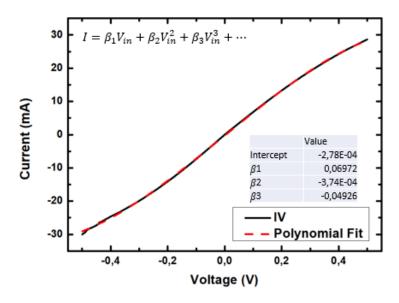

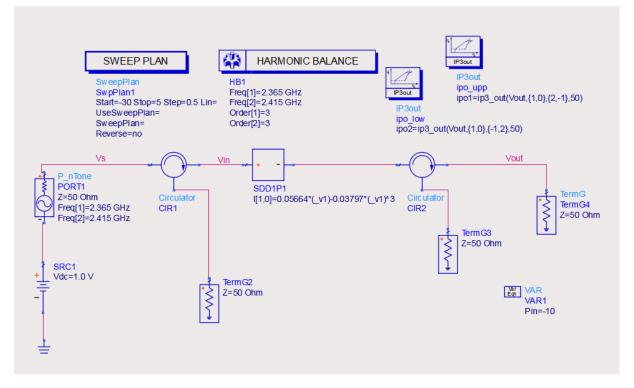

|     | 2.2  | 2.    | Polynomial fit and extraction for ADS simulation100                          |

|     | 2.3  | 3.    | Result of the IP3 measurement102                                             |

|     | 2.4  | 4.    | IP3 conclusion                                                               |

| 3   |      | Rea   | al life scenario: data communication104                                      |

|     | 3.:  | 1.    | Structures of switches used for data communications104                       |

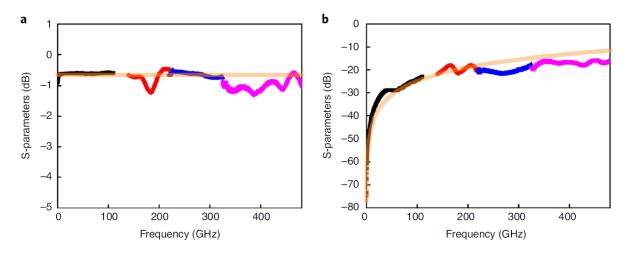

|     | 3.2  | 2.    | RF characteristics of switches used for data communications                  |

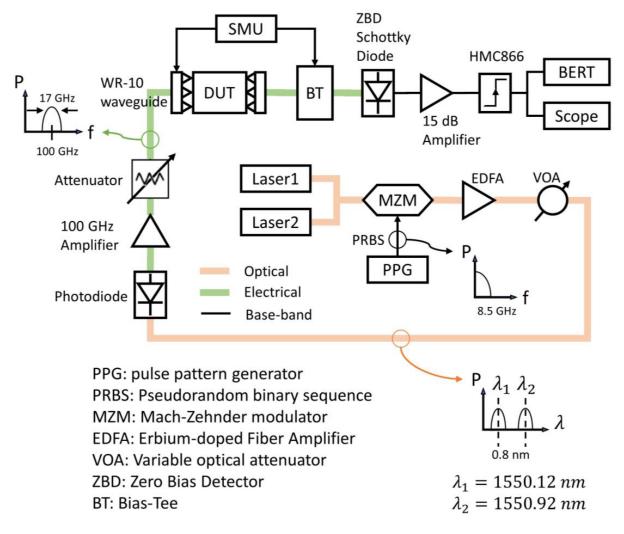

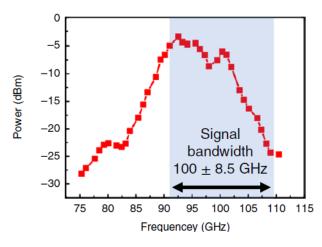

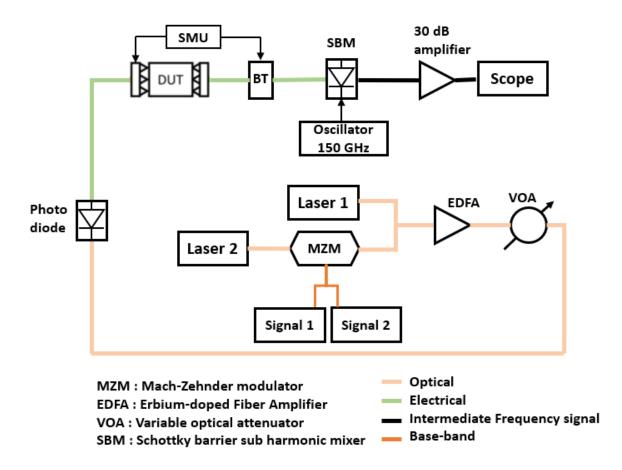

|     | 3.3  | 3.    | Setup for data communication at 100 GHz107                                   |

|     | 3.4  | 4.    | RF result on data communication at 100 GHz 109                               |

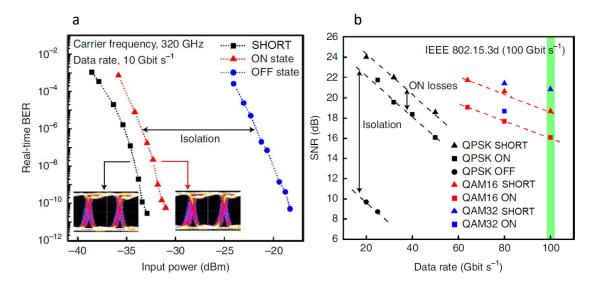

|     | 3.   | 5.    | Data communication at 320 GHz 111                                            |

|     | 3.   | 6.    | Setup for data communication at 320GHz and advanced vectorial modulation 112 |

|     | 3.   | 7.    | RF result on data communication at 320 GHz113                                |

| 4   |      | Cor   | nclusion                                                                     |

| 5   |      | Ref   | erences                                                                      |

| Cor | iclu | sion  | and perspectives                                                             |

| Ρ   | ers  | pect  | ives:                                                                        |

| ANI | NEX  | (     |                                                                              |

| A   | nne  | ex o  | f chapter 2                                                                  |

| A   | nne  | ex o  | f chapter 3                                                                  |

| A   | nne  | ex o  | f chapter 4142                                                               |

| Sun | nma  | ary . |                                                                              |

# Acknowledgement

First, I would like to express my appreciation to my supervisor Dr E. Pallecchi and my director Professor Henri Happy for their patience, their expertise and their continuous support during my thesis. Their kindness and guidance were what make me able to finish this doctoral study. Without their help, this work would not have been possible.

I would like to thank the reviewers of this work: Professor F. Podevin and Professor R. Negra for their comments on this dissertation and Professor C. Aupetit-berthelemot; Professor D Akinwande and Associated Professor M. Lanza for participating in the defense committee.

I give my appreciation to Dr D. Vignaud, thanks to him I learned a lot on 2D materials this last three years. I also thank Professor G. Ducournau for its precious help for the RF part of this work and its precious advices.

I thank our partner from CEA Leti and IMEP that work with me in this project. They are Dr R. Gassilloud, Dr A. Cresti and Dr J. David-Vifflantzeff. I also thank the partner from University of Texas in Austin for their exchange who are Professor D. Akinwande, Dr K. Myungsoo and S. Jin Yang.

I would like to express my gratitude to all the cleanroom engineers who helped me in many ways for the fabrication, the optical characterization. They are Dr F. Vaurette; Mr Y. Deblock; Mr P. Tilmant; Mr M. Dewitte; Dr I. Roch-jeune; Mr C. Boyaval; Mrs S. Ouendi Dr D. Yarekha and Mr T. Bertrand. I would like to express my gratitude to the engineers of the characterization center who are Ms V. Avramovic; Mr E. Okada; Dr S. Eliet and Ms S. Lepilliet. I also thank Dr D. Guerin for its help.

I also thank all my friends from IEMN that support me during this thesis. They are Thomas, Yevheniia, Houda, Nemanja, Louis, Quentin, Jeyan, Martin, Yasmine, Fawzi, Rupali and Leslie. Thanks for all the memories of these 3 years. I thank aswell all the people which I work to this past 3 year that I did not named before.

Finally, I would like to thank my family: my parents and sister, and finally Lucile my fiancee. I also thank my cat Yuumi which help me relieve some stress. Thank for giving me your support and love which give me courage to move forward.

5

# **General Introduction:**

With the growth of the market of telecommunication with 4G and 5G and the place that the internet of things is taking in our everyday life, more and more wireless telecommunication systems are needed and have to work at very high frequency. The future 6G is currently a discussion topic and its working frequency band will be above 100GHz.

Radio frequency (RF) switches play an important role in these wireless systems, where they are used for multiple applications such as: routing high frequency signals through systems, routing the signal in the front-end module of telecommunication systems for transceivers, ...

The main technologies used for RF switches nowadays are complementary metal oxide semiconductor (CMOS) technology, field effect transistors (FET), positive intrinsic negative (PIN) diodes and micromechanical system (MEMS). However, the first and the second show their limits in terms of frequency range, and the latter one has constraint in terms of switching time. De facto, a novel approach is necessary to reach the requirement of the future systems. With the highlight of 2D material thanks to various funding programs such as the GRAPHENE flagship, and the scientific breakthroughs in the fabrication and characterization of these materials, various applications start to emerge. In 2018, one application using transition metal dichalcogenides (TMD) 2D material shows promising results for high performance RF switches. It is in this context that my thesis on "RF switches based on 2D materials" takes place. The objectives of my thesis are the development, the fabrication and the characterization of 2D RF switches. This thesis was made in the framework of ANR project SWIT n° ANR-19-CE24-0004-01 under the coordination of Dr. Emiliano PALLECCHI, with the following partners: CEA LETI, IMEP-LaHC.

Given the large scope of the 2D material existing, this thesis will focus on the development of MoS<sub>2</sub> based switches, which have a great interest for the consortium of SWIT project. The first chapter focuses on providing the state of the art about the existing technology for RF switches. After a description of the characteristics of an RF switch, a brief presentation of switches based on semiconductor materials as well as MEMS-based structurers are presented. We then discuss emerging technologies based on switches made of transition or phase change

materials, as well as resistive switches. These technologies are derived from memory technologies and have undeniable advantages in terms of system integration. Our attention is then focused on RF switches based on 2D materials, which have the advantage of combining an easy integration in RF systems (no complex switch activation circuit), and of allowing an operation at frequencies close to THz. The active part of the switch is directly inserted in the structure of the transmission line (coplanar transmission lines are used) and the switch is controlled by a DC voltage applied to the transmission line. These devices will be the main work of this thesis.

One of the major objectives of this thesis is to demonstrate that switches based on 2D materials can achieve very high performance in terms of working frequency. Chapter 2 presents the work done to analyze and optimize the proposed structures. This is done through: (i) the optimization of the propagation structures (coplanar waveguide transmission lines) to reach frequencies of the order of 500 GHz, (ii) the calibration and de-embedding techniques to extract the characteristics of the passive switch, (iii) as well as the characterization methodology implemented. The characterization set-ups of the Lab allow to make measurement with RF probes up to the THz regime.

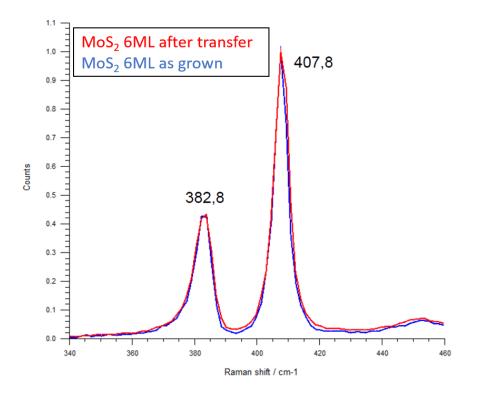

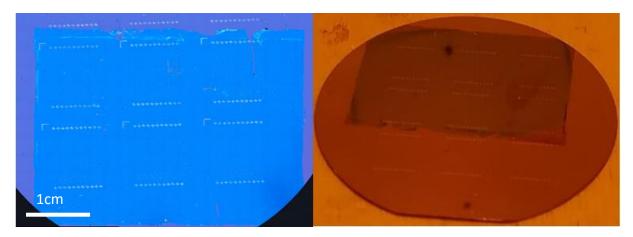

The third chapter focuses on the fabrication and characterization of resistive switches based on molybdenum disulfide (MoS<sub>2</sub>). This subject being new in the laboratory, all the steps of the manufacturing process were designed and optimized in the framework of the thesis. Moreover, it was necessary to ensure the compatibility of the manufacturing processes with the 2D material transfer technique, a technological step carried out by the LETI in Grenoble.

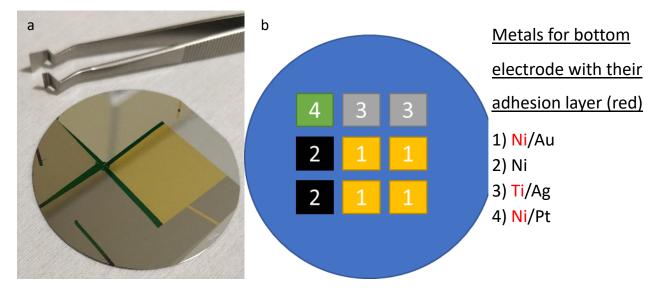

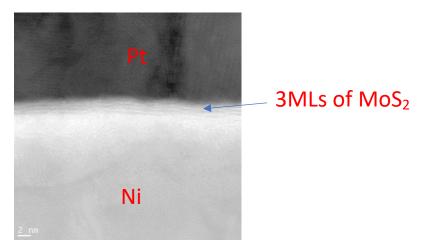

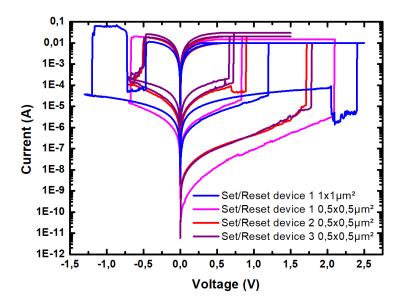

The first part of the chapter describes the technological steps used to manufacture the switches. To improve the understanding of the switching mechanisms, several combinations of metals are used as contacts (Bottom and top electrodes) for the 2D material. The size of the active part of the switch is also explored. Three manufacturing batches are fabricated with success: 2 substrates with six monolayers of MoS<sub>2</sub> named SS03 and SS04 and one substrate with three monolayers of MoS<sub>2</sub> named SS07.

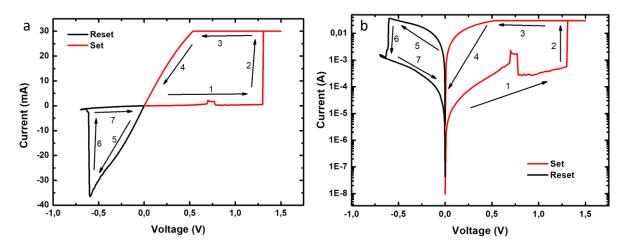

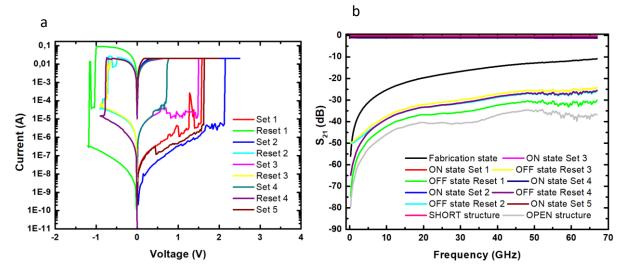

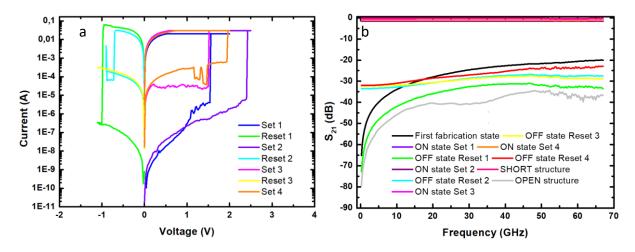

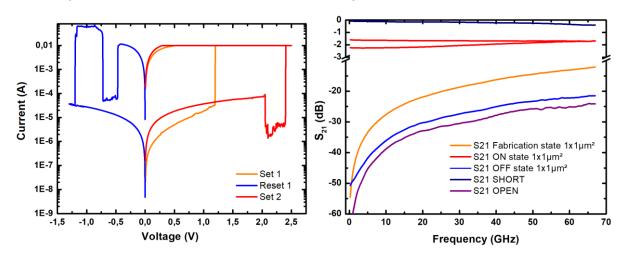

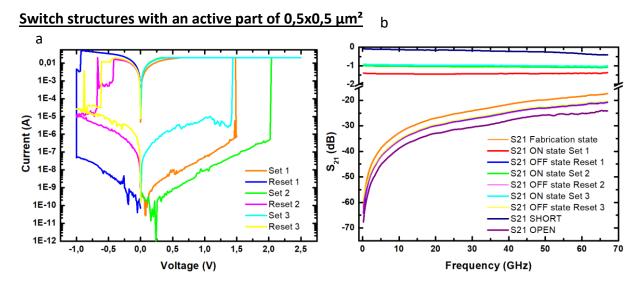

In the second part dc and RF analysis of switches from the 3 substrates were explored. For this analysis, it is necessary to switch the device ON (SET) and OFF (RESET) according to the

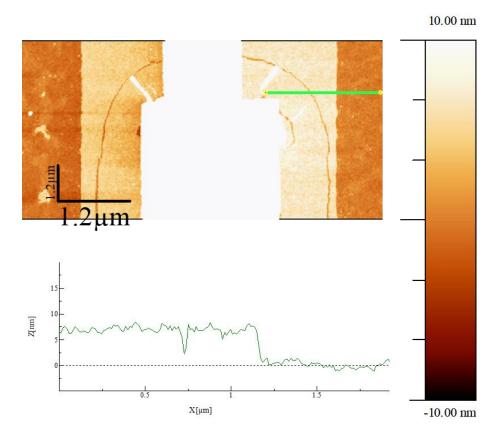

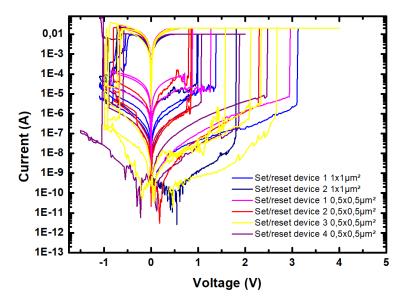

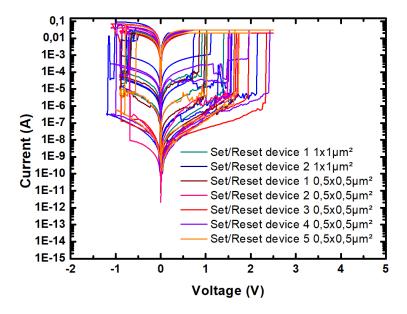

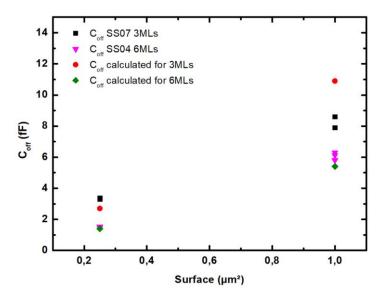

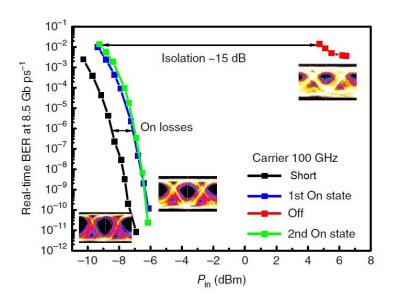

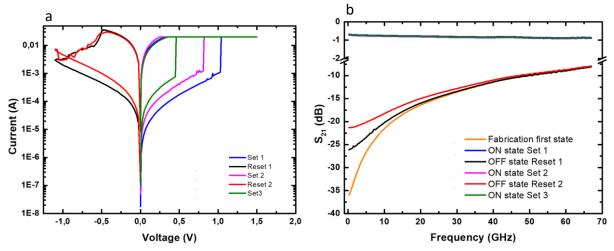

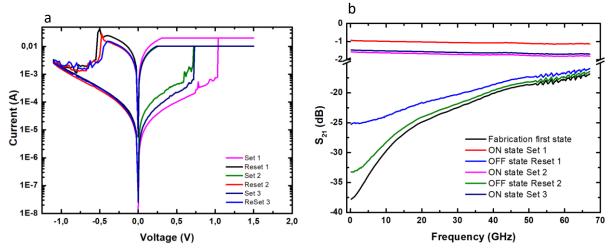

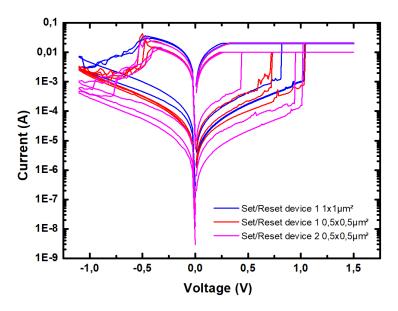

measurement made. For the ON state (positive bias), a current limitation is necessary to avoid device destruction. This is not necessary when the switch is turned to the OFF state (negative bias). The DC analysis shows the reliability of the fabrication process. The impact of ON state current on the resistance of the switch is also pointed out. The highest ON state current is correlated with lower insertion loss. Another important result is the impact of the size of the switch: The best reproducibility is achieved with the 0,5x0,5  $\mu$ m<sup>2</sup> switches. Considering RF performances, measurement on these fabricated multilayer MoS2 devices were limited to 67 GHz in this chapter. The measurements made show that the initial objective of 15 dB difference between ON state and OFF state is achieved both on transmission without any optimization (substrate 1) and with optimization (substrate 2 and 3). Considering the variation of the devices after already a few switching cycles it was not obvious to extract and to compare efficiently the figure of merit of different batches. But the results are good enough to explore the properties of these devices in a real system. This exploration is made in the next chapter.

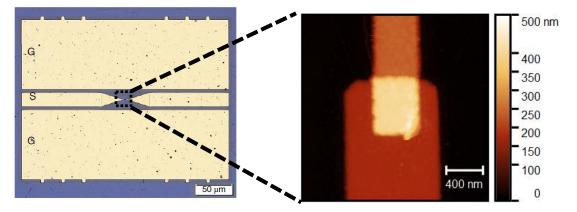

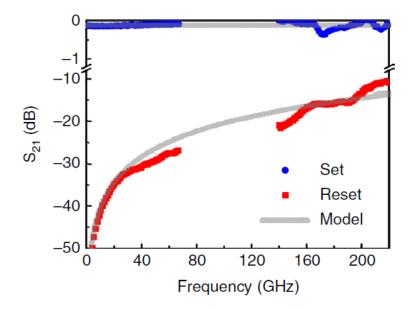

Chapter 4 focuses on the practical application of these switches in a real data communication system. This part was developed in collaboration with the university of Texas Austin (research group of Deji Akinwande) and the Photonic-THz group (G. Ducournau) at IEMN. The university of Texas provided us a first batch of device with a monolayer of hexagonal boron nitride (hBN) material as 2D material in a coplanar waveguide (CPW) without any optimization, and a second batch with a monolayer of MoS2 embedded in optimized CPW design in chapter 2. These devices are fabricated on diamond substrate, and could be considered as the thinnest switches that exist. The electrodes (Top and Bottom electrodes) are made of gold.

In the first part of this chapter, an analysis of the nonlinear behaviour of the 2D multilayer resistive switches is carried out. The main reason is that in the ON state, RF input power can cause self-heating of the device and cause the characteristics of the switch to vary due to thermal effects. The measurements made on switches with multiple layers of MoS<sub>2</sub> show good stability (IP3 above 26 dBm) and are compatible with the polynomial model extracted from simulation in the ADS software.

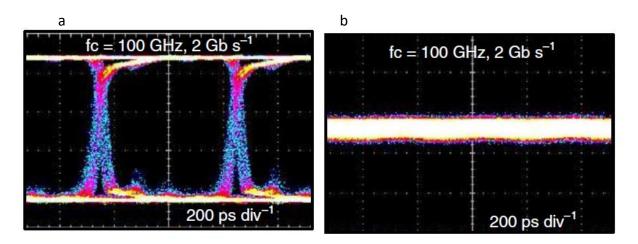

The first batch of device received from the University of Austin was characterized at IEMN up to 220 GHz, and an on off keying (OOK) modulation was applied with a carrier signal at 100 GHz. The measurement system composed of terahertz photonic devices is described and

permits to investigate the viability of hBN switches for high-speed data communication. This study concludes by showing the quality of the devices using eye diagramme and bit error rate measurements for an 8.5 Gbit.s<sup>-1</sup> data stream.

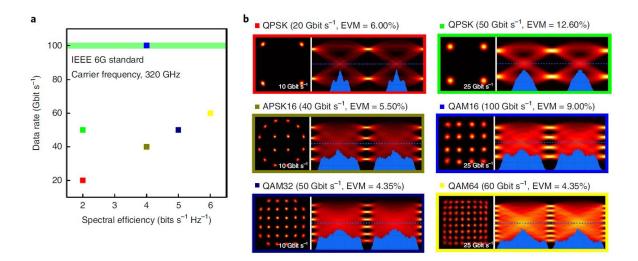

Finally, the second batch with a monolayer of MoS2 was measured up to 480 GHz. The insertion loss was around 0.8 dB in the ON state and the isolation was around -20 dB at 480 GHz. The objectives of these device were to match the new IEEE standard for future 6G which involves advanced modulation uses for spectral efficiency, high data rates of at least 100 Gbit.s<sup>-1</sup> to support the future application modulation at high carrier frequencies (around 300 GHz). Those requirements were achieved with success using a carrier frequency at 320 GHz. Optimized devices could attain a 100 Gbit.s<sup>-1</sup> data rate using 16 quadrature amplitude modulation. This result represents the state-of-the-art, and shows that these devices are suited for 6G communication systems.

A final conclusion on this work will then be given, and the perspective will be described.

# CHAPTER I State of the art of RF Switches

# Table of Contents

| CH/ | APTER | I State of the art of RF Switches                      | 10 |

|-----|-------|--------------------------------------------------------|----|

| 1   | . Int | troduction                                             | 12 |

| 2   | . RF  | switch characteristics                                 | 12 |

|     | 2.1.  | Main topology of RF switch                             | 16 |

| 3   | . Те  | chnologies used nowadays                               | 16 |

|     | 3.1.  | PIN diode - short description                          | 16 |

|     | 3.2.  | FET - Short description                                | 18 |

|     | 3.3.  | MEMS switching devices                                 | 21 |

| 4   | . En  | nerging switching technologies                         | 24 |

|     | 4.1.  | Description of metal insulator transition (MIT) switch | 25 |

|     | 4.2.  | Phase change material (PCM) switches                   | 26 |

|     | 4.3.  | Conductive bridge switches                             | 27 |

|     | 4.4.  | Resistive switching observed with 2D material          | 28 |

|     | 4.5.  | Application for emerging technology RF switches        | 30 |

| 5   | . Co  | omparison between different RF switches                | 30 |

| 6   | . Co  | onclusion                                              | 32 |

| 7   | . Re  | eferences                                              | 33 |

#### 1. Introduction

Radio Frequency (RF) switches are critical components used in telecommunication systems. They are used to route high frequency signals through systems. They can be found in the frontend module just before the antenna to switch the system from transmitting to receiving data, in cellular phones or in systems where redundance and reconfigurability are needed. One of the most widely used technologies for RF switch is complementary metal oxide semiconductor (CMOS) technology. Infineon report sales of over 1 billion unit for 2018 and over 5 billion units over the next 5 years. RF switches are therefore a key part of wireless technology.

In this chapter, I will introduce RF switches and describe successively:

- The characteristics of RF switches. Based on a simplified small-signal equivalent circuit of an RF switch, I will present the main figure-of-merits (FOMs). I will discuss some examples of RF applications with their specific requirements.

- Some technological families of RF switches based on active components (diodes and transistors) or passive components (Micro Electro Mechanical Systems - MEMS) are described with illustrative examples from the literature. The main characteristics of each family of components are given.

- The emerging field of switches based on materials whose properties change according to stimuli such as temperature, electric field, etc. This field is very active and many materials are investigated nowadays. I will describe here some of these components based on metal insulator transition (MIT), phase change material (PCM), and conductive bridge (CB). I will then discuss RF switches based on 2D materials, which will be the subject of our study. The potential of these devices up to the THz regime will be explained.

Finally, a synthesis table of the state of the art of this field is displayed.

#### 2. RF switch characteristics

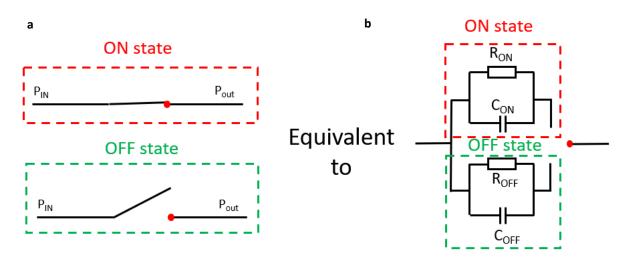

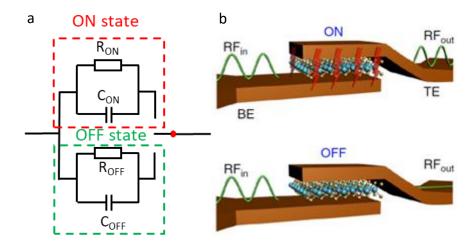

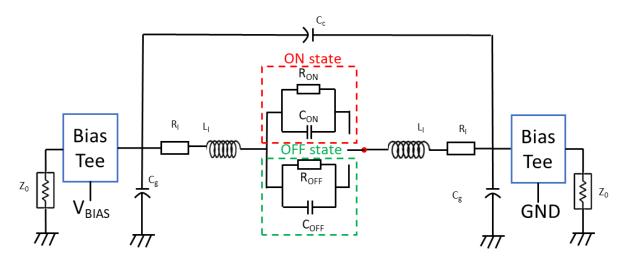

An RF switch is a device that possesses two distinct states, as shown in Fig. 1a. When the switch is in its low resistance state (LRS) – also called the ON state – a high-frequency signal

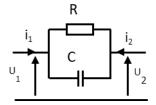

can be transmitted through the device. A simple electrical equivalent circuit model of an RF switch in the ON state consists of a low resistance,  $R_{ON}$ , in parallel to a capacitance,  $C_{ON}$ , as shown in the red square of Fig. 1b. When the switch is in its high resistance state (HRS) – also called the OFF state – an RF signal is blocked by the device. Its equivalent circuit is then a small capacitance,  $C_{OFF}$ , in parallel to a large resistance,  $R_{OFF}$ , (green square Fig. 1.b). An ideal switch in the ON state can be viewed as a short circuit and an OFF switch as an open circuit. The value of  $R_{ON}$  has an impact on the losses of the system whereas  $C_{OFF}$  affects its operation at high frequencies.

Figure 1: (a) Classical representation of an RF switch. In the ON state (red rectangle) a signal can flow through the device while in the OFF state (green rectangle) the signal is blocked by the device. (b) Equivalent electrical diagram of an RF switch in the ON state (red square) composed of a resistance,  $R_{ON}$ , in parallel with a capacitance,  $C_{ON}$ , and in the OFF state (green square) with a resistance,  $R_{OFF}$ , in parallel with a capacitance  $C_{OFF}$

We now discuss the figure-of-merits (FOMs) for RF switches, starting with one of the most important for telecommunications applications, the so-called  $R_{ON}*C_{OFF}$  product. The  $R_{ON}*C_{OFF}$  product is used to evaluate the high-frequency performances of the device and to calculate the **cut-off frequency**, **f**<sub>c</sub>, which is defined in the literature [1] as:

$$f_c = \frac{1}{2\pi * R_{ON} * C_{OFF}}$$

RF switches have several other figure-of-merits:

- Insertion loss represents the attenuation of the signal that flow through the switch in the ON state. The lower the insertion loss the better is the performance of the RF switch in the ON state.

- **Isolation** represents the attenuation of the signal in the OFF state of the device. The higher the isolation the better the RF switch block the RF signal in its OFF state.

- Power handling represents the maximal power capability measured in dBm [1] that the switch can handle without permanent electrical performance deterioration or selfswitching.

- Endurance is the durability of a RF switch represented by the number of switching cycles before failure.

- Non-volatility is the capacity for a device to keep its state without external stimuli.

- Linearity is the capacity of the device to exhibit a linear I-V characteristics. It is evaluated by the Third order intercept point (IP3)

The above figure-of-merits describe the basic electrical properties of an RF switch and are essential means of comparison of different switch technologies.

RF switches have various applications depending of their performances and are used either as fundamental element or as a Front-end subsystem. In table 1 in the next page, we list some of the main applications and their requirements.

Table 1 Some applications of RF switches from [2]

| Fundamental elements            |                                                                                      |  |  |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| Elements                        | Requirement                                                                          |  |  |  |  |  |

| Tunable inductor                |                                                                                      |  |  |  |  |  |

| Tunable capacitor               | • Low R <sub>ON</sub> , low C <sub>OFF</sub>                                         |  |  |  |  |  |

| Multiplexers                    | • Endurance >10 <sup>6</sup>                                                         |  |  |  |  |  |

| Tunable antenna                 |                                                                                      |  |  |  |  |  |

| RF Front-End                    | l Subsystems                                                                         |  |  |  |  |  |

| Subsystem                       | Requirement                                                                          |  |  |  |  |  |

| Switching networks              |                                                                                      |  |  |  |  |  |

| Tunable attenuators             |                                                                                      |  |  |  |  |  |

| Tunable filters                 | <ul> <li>Low R<sub>ON</sub>, low C<sub>OFF</sub></li> <li>Small footprint</li> </ul> |  |  |  |  |  |

| Switched antenna                | • Endurance $10^6 - 10^9$                                                            |  |  |  |  |  |

| Phase shifters                  | <ul> <li>Low biasing circuit overhead</li> </ul>                                     |  |  |  |  |  |

| Switched matching networks      |                                                                                      |  |  |  |  |  |

| Switched oscillators amplifiers |                                                                                      |  |  |  |  |  |

| RF Front-e                      | nd Systems                                                                           |  |  |  |  |  |

| System                          | Requirement                                                                          |  |  |  |  |  |

|                                 | High performance RF switch                                                           |  |  |  |  |  |

| Reconfigurable radio            | Small foot print                                                                     |  |  |  |  |  |

|                                 | Multiple switching networks                                                          |  |  |  |  |  |

| Phased array                    | Low-loss phase shifters                                                              |  |  |  |  |  |

|                                 | Small footprint switches                                                             |  |  |  |  |  |

| Constrained power/energy radio  | Low power switching                                                                  |  |  |  |  |  |

|                                 | Low static energy                                                                    |  |  |  |  |  |

#### 2.1. Main topology of RF switch

RF switches are categorized by the number of inputs and outputs, *i.e.*, number of poles and throws respectively. The number of poles and throws vary accordingly to the use of the RF switch.

A Single Pole Single Throw (SPST) switch consist of one input and one output. This type of switch is the only one fabricated in this thesis. The SPST switch serves as on-off switch in a circuit allowing the signal to pass through in the ON state and stopping it in the OFF state. An example of the most used SPST switch technology is reported by M. Uzunkol et G. M. Rebeiz [1]. (Fig. 1a)

#### 3. Technologies used nowadays

This part focuses on the presentation of mature and commercially available technologies of RF switches. First, we will talk about solid-state technology. Solid-state switches are made by using a semiconductor. Semiconductors are materials with electrical conductivity laying in a range between conductors (usually metals) and insulators. A highly tunable conductivity in semiconductors is usually achieved by means of doping, *i.e.*, the introduction of impurities to a material in a controllable way. N-type doping can be realized with chemical elements, which behave as donors and give free electrons to a semiconductor, while P-type doping with chemical elements which accept electrons. Semiconductor materials mainly utilized for RF devices are from the III-V group such as gallium arsenide (GaAs)[4] or indium phosphide (InP) [5]. A semiconductor RF switch can also be based on PIN diodes and Field Effect Transistors (FETs), such as high electron mobility transistors (HEMTs) and CMOS devices. MEMS switches are another type of commercially available of RF switches.

#### 3.1. PIN diode - short description

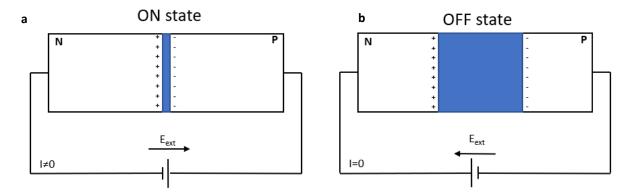

A PIN diode is a semiconductor device. It is composed of an intrinsic zone with high resistivity sandwiched between two other zones with p-and n-type doping. This diode possesses two states. The direct polarization or ON state happen when a positive voltage is applied to the diode directly, thus RF signal is allowed to pass through and the insertion loss is low. The

reverse polarization or OFF state happens when the diode is under reversed bias. In this case, the PIN diode does not let the signal go through and possess a high isolation. PIN diodes are used as power limiter [6], [7], phase shifters [8], [9] or as a SPDT RF switches [10], [11]. Fig. 2 shows the structure of a PIN diode used in a shunt configuration of a SPST RF switch, under direct bias and (Fig. 2a) and reverse bias (Fig. 2b) [10].

Figure 2 Representation of a PIN diode in (a) direct polarization (ON state) and (b) in reverse polarization (OFF state)

The advantage of PIN diode lies in its high-speed switching with value on the order of 100 ns. However, a bias current is required to maintain the ON state. As a consequence, there is a continuous power consumption for this state.

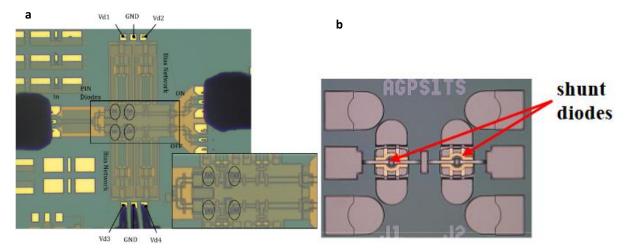

Figure 3 SPDT RF switches with PIN diode from [11] SPST RF switch with 2 shunt diodes from [10]

Regarding the FOM of a typical commercially available PIN diodes: the frequency range of a PIN diode a switch spans from 0.3 to 18 GHz, it possesses an insertion loss of -3.7 dB and an isolation of -55 dB with a switching time of 100ns. The power consumption is around 200 mW

for the commercially available model presented. <sup>1</sup> For higher frequency devices, a single pole double throw (SPDT) device can achieve an insertion loss of 2.8 dB at 85 GHz and an isolation of 30 dB at 85 GHz from [11]. (Fig. 3)

#### 3.2. FET - Short description

This part focuses on a brief description of an FET transistor, the HEMT, as some RF switches available commercially are made with this technology. It follows the CMOS technology that is most used as RF switches nowadays.

An FET is an electronic semiconductor device, which uses the electric field effect to control the current flow. An FET has three terminals: source, drain and gate. As mentioned above, the FET controls the current flow through the voltage applied to its gate. Thus, altering the conductivity of the channel between the drain and the source electrodes.

#### 3.2.1. HEMT devices as RF switches

High-electron mobility transistors (HEMT) are field-effect transistors that works by incorporating a junction between two materials with different bandgaps as the channel. Conventional HEMTs are generally made out of a combination of GaAs with AlGaAs (Fig. 4) and it is used here for illustration. It is worth to mention that today, many other efficient HEMT device families exist.

<sup>&</sup>lt;sup>1</sup> https://www.pulsarmicrowave.com/product/switch/SW1AD-33

| Cap Layer                 | Small gap doped   |

|---------------------------|-------------------|

| Schottky                  | Big gap undoped   |

| Donor layer               | Big gap doped     |

| Spacer                    | Big gap undoped   |

| Channel                   | Small gap undoped |

| Buffer                    | Big gap undoped   |

| Substrate semi insulating |                   |

Figure 4 Schematic cross section of a conventional HEMT

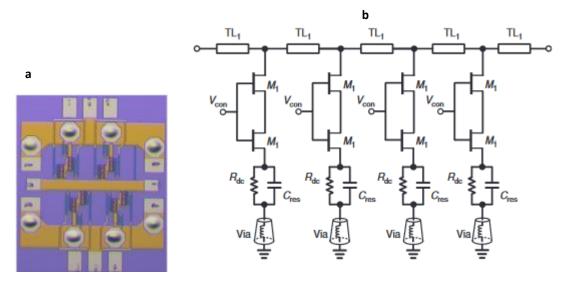

The HEMT works by applying a tension to the gate that controls the density of the charge carriers in the channel (2D electron gas). The density of the charge carriers in the 2D electron gas then controls the drain current. Depending on the value on the gate bias, the device switches from its ON state to its OFF state or from its OFF state to its ON state. Fig. 5 displays a HEMT RF switch working in the 59-77GHz frequency range and its implementation [12].

Figure 5 Photography of the chip of a HEMT-based RF switch and its implementation from [12]

This type of device is used for high speed, high frequencies and microwave circuits and it can be used as an RF switch.[13] It possesses a low insertion loss <1,1 dB and an high isolation > 25dB over a frequency range of 59-77 GHz. It has a switching speed in the order of nanosecond.

#### 3.2.2. CMOS - the most available RF switches

Complementary Metal Oxide Semiconductor (CMOS) is the main technology used for RF switches nowadays because of its low insertion loss and high isolation.

#### 3.2.2.1. CMOS operational principles

CMOS is a type of MOSFET composed of complementary pairs of nMOS and pMOS. When the nMOS is ON, the pMOS is OFF and vice versa. The power in this case is only consumed during the switching transitions between these two states.

Figure 6 Top view of a CMOS with parasitic devices from [14]

Fig. 6 shows an SPST RF CMOS switch from [14] using a coupled-line topology with MOSFET employed as variable impedance components. Most of the high frequency CMOS RF switch are based on coupled lines. In literature CMOS RF switches are reported to work with coupled lines at high frequencies, *i.e.*, in a frequency range of 250-320 GHz. They possess a high insertion loss of 4 dB at 303 GHz and an isolation of 40.3 dB at 303 GHz [14].

#### 3.2.2.2. CMOS Benefits for RF switch

CMOS possess some benefit that makes it the best RF switch for the actual use thanks to a method of fabrication that was matured for decade and a close to zero static power dissipation. The main benefits are:

- Low fabrication cost

- Large-scale integration

- Compact device size with a gate size down to tens of nanometres

- Low static power consumption on the order of 0.1 mW

- Low switching time in the order of nanoseconds

- Low insertion loss around 0.4 dB at 1 GHz and high isolation around 40 dB at 1 GHz for commercial switch in the frequency range from 0 to 3.5 GHz.<sup>2</sup>

Regardless of the listed advantages, CMOS technology suffers from limitations like their low power handling (maximum 15 dBm) caused by their low voltage operation and their narrow band operation for coupled-line-based designs at high frequency (over 100 GHz). [15] Thus, other RF switching technologies need to be improved or need to be developed to overcome existing challenges.

#### 3.3. MEMS switching devices

MEMS switches are surface micromachined devices, they consist of anchor points and a moving part that moves according to external stimuli provided by an actuator. They are classified depending on the source of the physical phenomenon that produce the stimuli to generate the mechanical movement which can be electrostatic, thermal, piezoelectric and magnetostatic.

Considering RF MEMS, two types of MEMSs - with ohmic contacts and with capacitive contacts - will be presented.

#### 3.3.1. RF MEMS with ohmic contact -serial contact

MEMSs with ohmic contacts possess a contact zone, where the cantilever and the electrode are put in contact with each other when the device switch into its ON state. In the OFF state, the cantilever is suspended on top of the contact zone. The air gap between the cantilever and the contact has a capacitance, C<sub>OFF</sub>. Switching from OFF to ON occurs when the actuation

<sup>&</sup>lt;sup>2</sup> https://www.mouser.fr/new/infineon/Infineon-bgsx44ma12-rf-cmos-switch/

electrode is biased. Thus, an electrostatic force is formed and attracts the cantilever forming the contact with the electrode. The metal-metal contact is characterized by the resistance,  $R_{ON}$ .

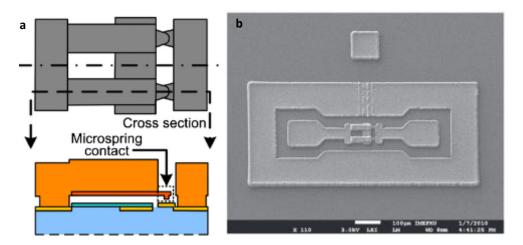

Fig.7 shows an example of a MEMS with ohmic contact, where the contact between the cantilever and the contact electrode is realized by means of a microspring. [16]

Figure 7 (a) Schematic of a microspring contact in a metal-to-metal contact MEMS switch configuration (b) SEM image of the fabricated switch from [16]. The microspring is put in contact with the metallic part to switch the device to its ON state. In the OFF, the microspring lays on top of the metallic contact without touching it.

This switch provides: from 0 to 20 GHz, an insertion loss of 0.2 dB and an isolation of 22 dB at 20 GHz. The actuation voltage for this device is around 50 V.

#### 3.3.2. RF MEMS with capacitive contact- parallel circuit

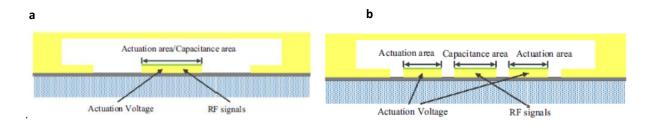

MEMSs with capacitive contacts are similar to the one with ohmic contacts. The difference is the presence of a dielectric deposited on top of the signal electrode, as shown on Fig. 8a changing its capacitance. The circuit model of this type of switch is different compared to the one presented at the beginning of this chapter. This type of switch is characterized by a  $C_{r-}$  ratio where  $C_r = C_{OFF}/C_{ON}$ . A high  $C_r$  ratio is required for capacitive MEMSs to be used as RF switches.

Figure 8 (a) Classic capacitive MEMS device (b) Capacitive MEMS switch with specific deign from [17]

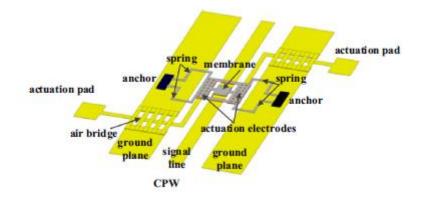

In the OFF state, the cantilever and the capacitance area are separated by air and the dielectric, the  $C_{OFF}$  capacitance is high. By applying a voltage to the actuation pad, the cantilever is attracted by the electrostatic force and makes a contact with the dielectric on top of the actuation pad. The device attains its  $C_{ON}$  capacitance and switches from its OFF state to the ON state. An improved capacitive MEMS device is shown on Fig. 8b and 9. This device is embedded in a coplanar waveguide for RF application, where the actuation zone surrounds the capacitive area [17].

Figure 9 Structure of the MEMS switch from [17]. The coplanar waveguide (yellow) embeds the switching area

#### 3.3.3. MEMS for high frequency

Recently made state-of-the-art MEMS RF switches are designed to work at high frequency. For example, the switch, displayed in Fig. 10, operates with a signal at 240-325 GHz and possess some advantage: MEMS RF switches can achieve an extremely low IL (<0.5 dB at 235 GHz) and high isolation (25 dB at 235 GHz). Overall this kind of devices shows high linearity [16]–[22]. MEMS RF switches have low power consumption due to voltage actuation.

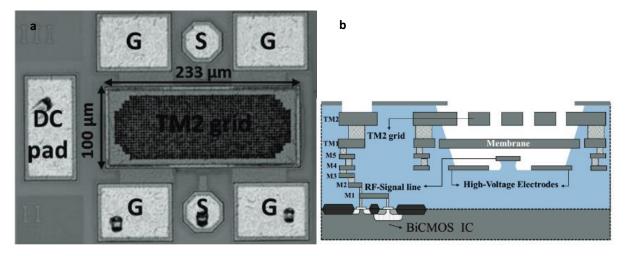

Figure 10 (a) Optical image of a 240GHz RF MEMS switch and (b) schematic and cross section of the RF MEMS from[18]

However, MEMS RF switches have the following drawback: regardless recent achievements in commercially available MEMS switches operating at voltage of 3 V (ADGM1003)<sup>3</sup>, most of MEMS devices require a high actuation voltage (> 30 V). Low switching speed (around 120  $\mu$ s) and relatively to solid-state switches low power handling (around 30 dBm) are also considered as limitation. Finally, they are really sensitive to exterior contamination and need to be protected by encapsulation. Nevertheless, this switch technology is widely and successfully used in reconfigurable antennas [23], [24].

# 4. Emerging switching technologies

The development of emerging technologies based on different resistive states to store information has shown promising results [2]. This part reviews four different emerging switching technologies starting with metal insulator transition (MIT) switches that is a volatile technology. It is then followed by three other nonvolatile emerging technologies that can be used for RF switches such as phase change material (PCM) switches, conductive bridge (CB) switch technology and finally 2D-based switches. The nonvolatility of a device implies that it does not consume energy to maintain its current state. This term is borrowed from memory

<sup>&</sup>lt;sup>3</sup> Web address: https://www.analog.com/en/products/adgm1003

device where this technology comes from. The description of 2D-based RF switches that has been recently developed is finalizing the section.

#### 4.1. Description of metal insulator transition (MIT) switch

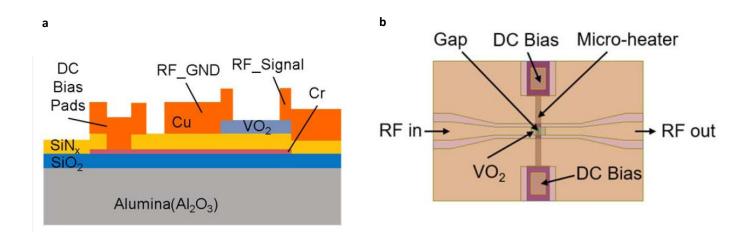

Vanadium dioxide (VO<sub>2</sub>) is a favourable material for RF switches devices due to its metal to insulator and insulator to metal transition. This phenomenon occurs when the VO<sub>2</sub> reaches a critical temperature of 68°C and becomes conductive. This temperature needs to be maintained to keep the device in the ON state. An RF switch is fabricated by separation of two metal electrodes by a VO<sub>2</sub> zone (Fig. 11). MIT RF switches possess low insertion loss, a high isolation and a high switching speed. However, the power consumption of the device is high due to the need to maintain the temperature at 68°C in the ON state.

Figure 11 MIT RF switch (a) cross view and (b) top view after fabrication embedded in a coplanar waveguide from [25]

For the VO<sub>2</sub> switch from [25], the insertion loss and isolation are 0.5 dB and 25 dB respectively at 20 GHz and simulations suggest that it could operate up to 75 GHz. The state-of-the-art for VO<sub>2</sub> switch exhibit a frequency range from 210 GHz to 290 GHz with a insertion loss and an isolation of 1.5 dB and 12 dB respectively at 290 GHz.[26]

# 4.2. Phase change material (PCM) switches

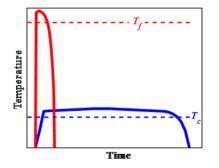

A PCM switch uses phase change materials such as GeTe. A phase change material is a material that has two – or more – distinct state. For the GeTe, the two states are its amorphous phase that is a High Resistive State (HRS), and its crystalline phase that is a Low Resistive State (LRS). The phase transition is controllable by changing the temperature of the active material (Fig. 12). In short, when the GeTe is in its crystalline phase, the switch is in its ON state. To switch it, the device is heated for a short time above the melting temperature,  $T_{f,r}$ , and suddenly freezed, then GeTe becomes amorphous and the switch is in its OFF state. The device is nonvolatile meaning that its state will not change if it is not submitted to an exterior stimulus, here a temperature change. To turn the device back ON, it is heat up to the temperature of crystallization,  $T_c$ , so that the GeTe crystallize back and the device goes in its LRS. A high resistance in the amorphous state of the material and a low resistance in the crystalline phase makes PCM a viable candidate for RF switches.

Figure 12 Cycle of PCM switch from [27]. In dashed red is represented the melting temperature,  $T_{f}$ , of GeTe. Above this temperature the GeTe changes phase from its crystalline state to its amorphous state. In blue is represented the crystallization temperature of GeTe. By heating the device, a slightly above this temperature, the phase of the GeTe changes from amorphous to crystalline.

PCMs are nonvolatile device and possess a retaining time of a few years. A different  $R_{ON}/R_{OFF}$  ratio and endurance can be achieved by stoichiometric evolution. Fig. 13 shows an example of one of the PCM material switches made with GeTe, it is basically a coplanar waveguide that guide the RF signal with a DC part for the heating of the GeTe.

Figure 13 (a) Top view and (b) cross view of PCM switch from [27]

The figure-of-merit of PCM switches presented in [27] are: from 0 to 20 GHz with an insertion loss of 2 dB at 20 GHz, an isolation of 18 dB at 20 GHz, that is a typical performance.

# 4.3. Conductive bridge switches

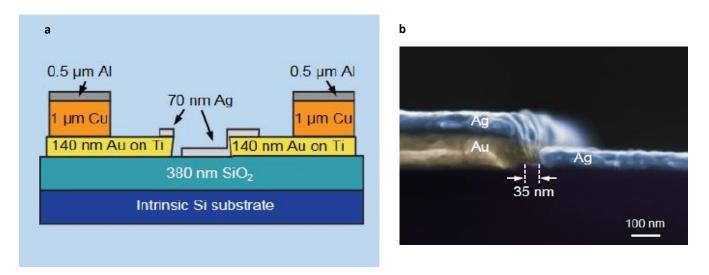

Conductive-Bridge devices (CB) are also known as electrochemical metallization memory. They are composed of two asymmetric metal electrodes, one active and one inert, and separated from each other by a small gap [28] (Fig. 14) or by an insulating layer [29]. Fig. 14 shows a gap type CB [28].

Figure 14 (a) cross view of a gap CBRAM switch. (b) Colored view of a SEM image of a CB switch from [28]

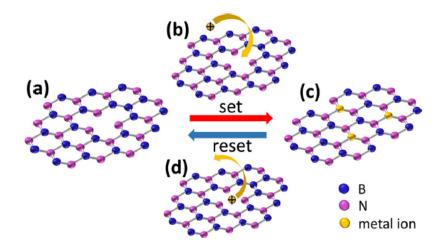

The switching mechanism is based on a redox process. A metallic filament is formed by ion migration from the active electrode to the inert electrode when an external electric field is applied to them. This process is named SET. Under reversed electric field, the metallic filament is ruptured and dissolves itself as the ions migrate back to the active electrode. This process is named as RESET. This switch is also embedded into a CPW for RF operation (Fig. 15).

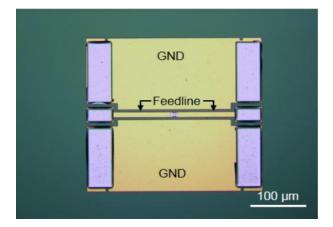

Figure 15 Optical image of an RF CB switch in a CPW configuration

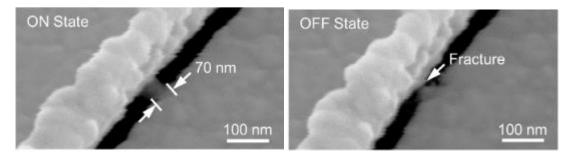

A SEM image of the filament between both electrodes is shown in Fig. 16. [28]

The state-of-the-art possesses the following figures of merit: a frequency range measured till 110 GHz, an insertion loss of 0.33 dB and an isolation of 29.8 dB measured at 40 GHz. For the intrinsic parameters, an  $R_{ON}$  of 3.6  $\Omega$  and a  $C_{OFF}$  of 1.37 fF were determined.

Figure 16 SEM image of the gap switch in its (a)ON state and (b) OFF state from [28]. In (a), a filament is observed that link both electrodes.

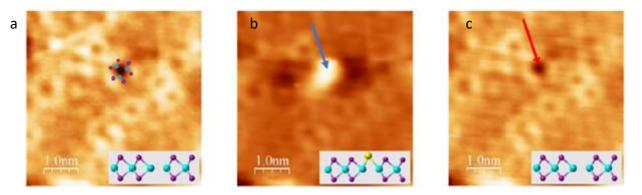

# 4.4. Resistive switching observed with 2D material

This is the last type of RF switches that is presented and the main focus of this thesis.

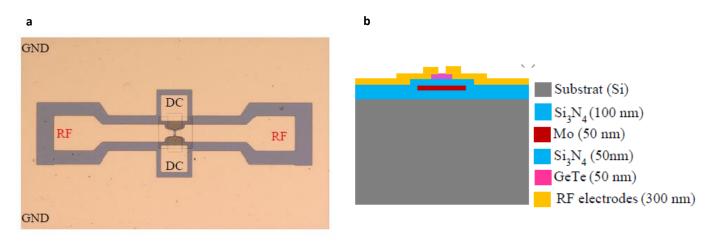

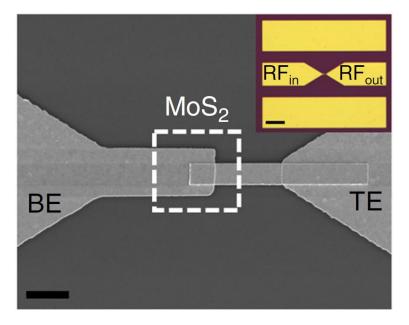

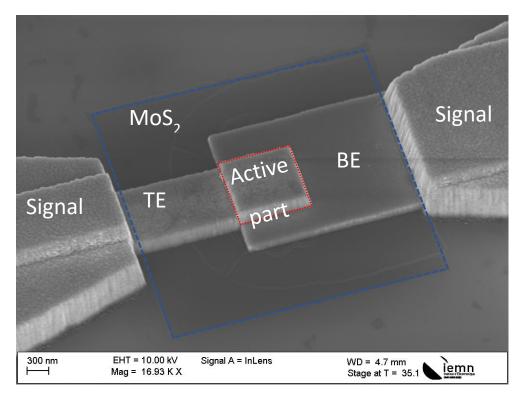

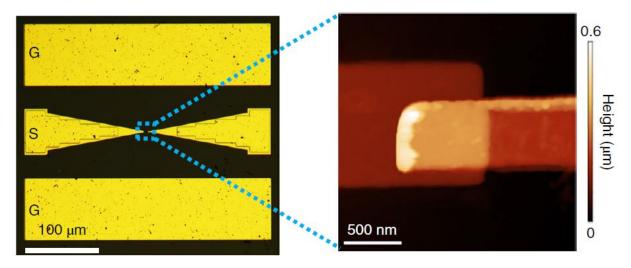

Resistive switching in 2D materials as monolayer hexagonal boron nitride (hBN) or Tungsten disulphide (WS<sub>2</sub>) or molybdenum disulphide (MoS<sub>2</sub>) has been demonstrated recently [30]. Following this seminal work, RF switches based on the 2D material are currently researched for high frequency and memory application. Such 2D switches consist of 2D material sandwiched by two metal electrodes (Fig. 17). For RF application, they are embedded into coplanar wave guides. Devices are usually fabricated utilizing CVD grown 2D materials, which are then transferred on the top of the electrodes from the growth substrate. Switches based on 2D materials exhibit remarkable high frequencies performances due to the ultimate thickness of the 2D materials, thus they become promising for RF application as well as for memory application.

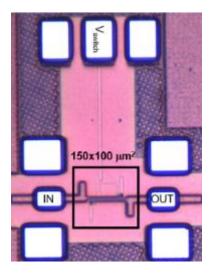

Figure 17 SEM image of 2D switch and inset: microscopy image of 2D switch CPW from [31]. A 2D material (dashed square), is sandwiched between a bottom electrode (BE) and a top electrode (TE).

The switch is nonvolatile meaning that the switch retains its ON state or OFF state without consuming any power. The RF switch in [29] possesses a correct insertion loss (1.2 dB) and isolation (12 dB) at 50 GHz. The endurance of these devices requires an improvement as it is still low [32]. The mechanism behind the 2D RF switches were not investigated at the beginning of my thesis and will be explained in chapter 3.

# 4.5. Application for emerging technology RF switches

New emerging RF switches using the technology presented above are under wide investigation nowadays because of their:

- High state-of-the-art FOM

- Low switching energy

- Nonvolatility

- Small footprint

- Low energy necessary for activation

Possible applications for the resistive RF switch are summarized in Table 1 in the beginning of the chapter [2]. Applications are various, from fundamental elements such as tunable inductors or capacitors as part of subsystems like switching networks or phase shifters in RF front-end modules because of their low  $R_{ON}$  and low  $C_{OFF}$ .

# 5. Comparison between different RF switches

Table 2 resumes different figure-of-merits of the devices from the state-of-the-art literature for the technologies discussed above.

| Dof  | Tashaalasa                  | IL    | IS    | Bandwidth | R <sub>ON</sub> (Ω) | C <sub>OFF</sub> (fF) | Fc (THz) | Control     |

|------|-----------------------------|-------|-------|-----------|---------------------|-----------------------|----------|-------------|

| Ref  | Technology                  | (dB)  | (dB)  | (GHz)     |                     |                       |          | voltage (V) |

| [12] | 70nm GaAs                   | -1.1  | -25   | 59-77     | 5.4                 | 36                    | 0.81     | /           |

| [12] | m-HEMT SPST                 | 1.1   |       |           |                     |                       |          | /           |

| [14] | 65nm CMOS SPST              | -4    | -40   | 250-320   | /                   | /                     | /        | /           |

| [33] | CMOS SOI SPST               | <-3   | -50   | 0-43      | /                   | /                     | /        | < 3         |

| [16] | MEMS                        | -0.2  | -22   | 0-20      | /                   | /                     | /        | 50          |

| [10] | Ohmic contact               | -0.2  | -22   |           |                     |                       |          | 50          |

| [17] | MEMS                        | -0.3  | -20.5 | 0-40      | /                   | /                     | /        | 18.3        |

| [17] | capacitive contact          | 0.5   |       |           |                     |                       |          |             |

| [18] | MEMS BICMOS                 | -0.44 | -24.6 | 220-325   | /                   | /                     | /        | 70          |

| [10] | SPST PIN diode              | -0.3  | -50   | 0-50      | /                   | /                     | /        | /           |

| [11] | SPDT PIN diode              | -2.8  | -30   | 55-105    | 10                  | 23                    | 0.69     | 1.8         |

| [25] | SPST VO <sub>2</sub> switch | -0.4  | -28   | 0-20      | /                   | /                     | /        | 15          |

| [26] | SPST VO <sub>2</sub> switch | -1    | -12   | 210-290   | /                   | /                     | /        | 1           |

| [27] | SPST GeTe switch            | -2    | -15.5 | 0-20      | 25                  | 10                    | 0.63     | /           |

| [34] | GeTe switch                 | -0.6  | >20   | 0-67      | /                   | /                     | /        | /           |

| [37] | GeTe switch                 | -0.15 | >25   | 0-40      | 1.1                 | 6.8                   | 11       | 7.5         |

| [35] | CB switch                   | -1.1  | -25   | 0-3       | 2                   | 1681                  | 0.04     | 16          |

| [28] | CB switch                   | -0.3  | -30   | 0-40      | 2.6                 | 1.45                  | 42.2     | 3           |

| [32] | MoS <sub>2</sub> Atomristor | -0.25 | -29   | 0-50      | 11                  | 7.7                   | 1.87     | 1           |

At high frequency (around 300 GHz), some devices possess issues with for example high insertion loss for CMOS or high voltage needed for MEMS technology. On the other hand, we can observe that emerging technologies like CB switch, PCMs and finally 2D switch feature high FOMs around 40-60 GHz frequency. Further study is then needed to improve them and see their functionality in the 300 GHz frequency range.

#### 6. Conclusion

In this chapter, the figure-of-merits and the topology of RF switches are introduced. Furthermore, for 6G and very high frequency applications, commercially available switches have limitations such as the high voltage needed for MEMS devices or the narrow operation band and low power handling of CMOS devices.

Therefore, emerging technologies are an active research field, starting with MIT VO<sub>2</sub> switches that are promising thanks to their excellent insertion loss, isolation and their capability to work at high frequency. Nevertheless, VO<sub>2</sub> requires to be heated up to 68°C to maintain its ON state, causing a high energy consumption and limiting the scalability. PCM devices are nonvolatile and feature a good insertion loss and isolation over a relative broad frequency range but a reduction of the parasitic capacitance is necessary to reach higher frequency. That is also the case for CB that shows great expectation from its insertion loss and isolation as well. However, both these technologies need to reach higher frequency to be able to match the requirement for future 6G applications [36] . Finally, the latest and most recent switch presented in this thesis, the 2D material based switch possess an enormous potential because of the absolute thickness of the 2D material and great scaling with frequency and its simple switching control, despite a first operation report limited at 50GHz [32].

The goal of this thesis is to develop and optimize nonvolatile 2D-based RF switches to assess their potential for high frequency application (above 100 GHz) for 5G and beyond. To match the requirement for 6G, the study of metallic electrode, thickness of the 2D material, scaling need to be carried out. The objective is to improve our understanding of the device to match requirement for real application and to comply with constraints imposed by future integration in a semiconductor production line.

#### 7. References

- [1] D. M. Pozar, *Microwave Engineering*, 4th Edition. Wiley, 2011.

- [2] N. Wainstein, G. Adam, E. Yalon, et S. Kvatinsky, « Radiofrequency Switches Based on Emerging Resistive Memory Technologies - A Survey », *Proc. IEEE*, vol. 109, nº 1, p. 77-95, jan. 2021, doi: 10.1109/JPROC.2020.3011953.

- [3] M. Uzunkol et G. M. Rebeiz, «140–220 GHz SPST and SPDT Switches in 45 nm CMOS SOI », *IEEE Microw. Wirel. Compon. Lett.*, vol. 22, nº 8, p. 412-414, agu. 2012, doi: 10.1109/LMWC.2012.2206017.

- [4] A. Gopinath et J. B. Rankin, « GaAs FET RF switches », *IEEE Trans. Electron Devices*, vol. 32, nº 7, p. 1272-1278, 1985, doi: 10.1109/T-ED.1985.22111.

- [5] J. S.-C. Chien et J. F. Buckwalter, « Compact, High-Isolation 110-140-GHz SPST and SPDT Switches Using a 250-nm InP HBT Process », in 2022 IEEE/MTT-S International Microwave Symposium - IMS 2022, 2022, p. 152-155. doi: 10.1109/IMS37962.2022.9865636.

- [6] E. Gatard, R. Sommet, P. Bouysse, R. Quere, M. Stanislawiak, et J.-M. Bureau, « High power S band limiter simulation with a physics-based accurate nonlinear PIN diode model », in 2007 European Microwave Integrated Circuit Conference, 2007, p. 72-75. doi: 10.1109/EMICC.2007.4412650.

- [7] A. V. Bezruk, A. Y. Yushchenko, G. I. Ayzenshtat, V. G. Bozhkov, et V. I. Perfiliev, « The microwave power limiter based on pin-diodes for the frequency range of 100–110 GHz in form of waveguide MIC », in 2013 23rd International Crimean Conference « Microwave & Telecommunication Technology », sept. 2013, p. 74-75.

- [8] J. Zhang, S. W. Cheung, et T. I. Yuk, « A compact 6-bit phase shifter with high-power capacity based on composite right/left-handed transmission line », in *The 40th European Microwave Conference*, sept. 2010, p. 437-440. doi: 10.23919/EUMC.2010.5616000.

- [9] M. U. Nazir, M. Kashif, N. Ahsan, et Z. Y. Malik, « PIN diode modelling for simulation and development of high power limiter, digitally controlled phase shifter and high isolation SPDT switch », in *Proceedings of 2013 10th International Bhurban Conference on Applied Sciences Technology (IBCAST)*, 2013, p. 439-445. doi: 10.1109/IBCAST.2013.6512197.

- [10] T. Boles, J. Brogle, D. Hoag, et D. Curcio, « AlGaAs PIN diode multi-octave, mmW switches », in 2011 IEEE International Conference on Microwaves, Communications,

Antennas and Electronic Systems (COMCAS 2011), nov. 2011, p. 1-5. doi: 10.1109/COMCAS.2011.6105783.

- [11] V. Vassilev, A. Vilenskiy, H. -T. Chou, M. Ivashina, et H. Zirath, « A 55-105 GHz PIN Diode SPDT Switch », in 2021 International Symposium on Antennas and Propagation (ISAP), oct. 2021, p. 1-2. doi: 10.23919/ISAP47258.2021.9614359.

- [12] Y. Kim et S. Jeon, « Mm-wave single-pole single-throw m-HEMT switch with low loss and high linearity », *Electron. Lett.*, vol. 56, n° 14, p. 719-721, 2020, doi: https://doi.org/10.1049/el.2020.0969.

- [13] G. Shen, H. Zhu, Q. Xue, et W. Che, « An 11–40-GHz High-Power Switch With Miniaturized High-Order Topology Using 100-nm GaN-on-Si HEMTs », *IEEE Trans. Electron Devices*, p. 1-8, 2022, doi: 10.1109/TED.2022.3204511.

- [14] J. Kim, S. Kim, K. Song, et J.-S. Rieh, « A 300-GHz SPST Switch With a New Coupled-Line Topology in 65-nm CMOS Technology », *IEEE Trans. Terahertz Sci. Technol.*, vol. 9, nº 2, p. 215-218, 2019, doi: 10.1109/TTHZ.2019.2898815.

- [15] J. Sobolewski et Y. Yashchyshyn, « State of the Art Sub-Terahertz Switching Solutions », *IEEE Access*, vol. 10, p. 12983-12999, 2022, doi: 10.1109/ACCESS.2022.3147019.

- [16] B. Liu, Z. Lv, X. He, M. Liu, Y. Hao, et Z. Li, « Improving performance of the metalto-metal contact RF MEMS switch with a Pt–Au microspring contact design », J. *Micromechanics Microengineering Struct. Devices Syst.*, vol. 21, nº 6, p. 9, june 2011, [En ligne]. Disponible sur: http://inis.iaea.org/search/search.aspx?orig\_q=RN:47010002

- [17] M. Li, J. Zhao, Z. You, et G. Zhao, « Design and fabrication of a low insertion loss capacitive RF MEMS switch with novel micro-structures for actuation », *Solid-State Electron.*, vol. 127, p. 32-37, jan. 2017, doi: 10.1016/j.sse.2016.10.004.

- [18] S. T. Wipf et al., «240 GHz RF-MEMS switch in a 0.13 μm SiGe BiCMOS Technology », in 2017 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), 2017, p. 54-57. doi: 10.1109/BCTM.2017.8112910.

- [19] C.-Y. Lin, C.-C. Hsu, et C.-L. Dai, « Fabrication of a Micromachined Capacitive Switch Using the CMOS-MEMS Technology », *Micromachines*, vol. 6, nº 11, 2015, doi: 10.3390/mi6111447.

- [20] A. Persano, A. Tazzoli, P. Farinelli, G. Meneghesso, P. Siciliano, et F. Quaranta, « K-band capacitive MEMS switches on GaAs substrate: Design, fabrication, and reliability », *Spec. ISSUE 23rd Eur. Symp. Reliab. ELECTRON DEVICES Fail. Phys. Anal.*, vol. 52, n° 9, p. 2245-2249, sept. 2012, doi: 10.1016/j.microrel.2012.06.008.

- [21] Y. Zhu, L. Han, M. Qin, et Q. Huang, « Novel DC-40GHz MEMS series-shunt switch for high isolation and high power applications », *Sens. Actuators Phys.*, vol. 214, p. 101-110, agu 2014, doi: 10.1016/j.sna.2014.04.024.

- [22] M. Fernandez-Bolanos Badia, E. Buitrago, et A. M. Ionescu, « RF MEMS Shunt Capacitive Switches Using AlN Compared to \$\hbox{Si}\_{3}\hbox{N}\_{4}\$ Dielectric », J. Microelectromechanical Syst., vol. 21, nº 5, p. 1229-1240, oct. 2012, doi: 10.1109/JMEMS.2012.2203101.

- [23] B. A. Cetiner, G. Roqueta Crusats, L. Jofre, et N. Biyikli, « RF MEMS Integrated Frequency Reconfigurable Annular Slot Antenna », *IEEE Trans. Antennas Propag.*, vol. 58, nº 3, p. 626-632, march 2010, doi: 10.1109/TAP.2009.2039300.

- [24] D. E. Anagnostou *et al.*, « Design, fabrication, and measurements of an RF-MEMS-based self-similar reconfigurable antenna », *IEEE Trans. Antennas Propag.*, vol. 54, nº 2, p. 422-432, feb. 2006, doi: 10.1109/TAP.2005.863399.

- [25] J. Jiang, G. Chugunov, et R. R. Mansour, « Fabrication and characterization of VO2based series and parallel RF switches », in 2017 IEEE MTT-S International Microwave Symposium (IMS), june 2017, p. 278-280. doi: 10.1109/MWSYM.2017.8059096.

- [26] C. Hillman, P. Stupar, et Z. Griffith, « Scaleable vanadium dioxide switches with submillimeterwave bandwidth: VO2 switches with impoved RF bandwidth and power handling », in 2017 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), 2017, p. 1-4. doi: 10.1109/CSICS.2017.8240450.

- [27] A. Hariri, A. Crunteanu, C. Guines, C. Hallepee, D. Passerieux, et P. Blondy, « Double-Port Double-Throw (DPDT) Switch Matrix Based on Phase Change Material (PCM) », in 2018 48th European Microwave Conference (EuMC), sept. 2018, p. 479-482. doi: 10.23919/EuMC.2018.8541405.

- [28] S. Pi, M. Ghadiri-Sadrabadi, J. C. Bardin, et Q. Xia, « Memristors as radiofrequency switches », in 2016 IEEE International Symposium on Circuits and Systems (ISCAS), may 2016, p. 377-380. doi: 10.1109/ISCAS.2016.7527249.

- [29] U. Celano *et al.*, « Conductive-AFM tomography for 3D filament observation in resistive switching devices », in 2013 IEEE International Electron Devices Meeting, dec. 2013, p. 21.6.1-21.6.4. doi: 10.1109/IEDM.2013.6724679.

- [30] R. Ge *et al.*, « A Library of Atomically Thin 2D Materials Featuring the Conductive-Point Resistive Switching Phenomenon », *Adv. Mater.*, vol. 33, nº 7, p. 2007792, feb. 2021, doi: 10.1002/adma.202007792.

- [31] M. Kim *et al.*, «Zero-static power radio-frequency switches based on MoS2 atomristors », *Nat. Commun.*, vol. 9, nº 1, p. 2524, june 2018, doi: 10.1038/s41467-018-04934-x.

- [32] R. Ge *et al.*, « Atomristor: Nonvolatile Resistance Switching in Atomic Sheets of Transition Metal Dichalcogenides », *Nano Lett.*, vol. 18, nº 1, p. 434-441, jan. 2018, doi: 10.1021/acs.nanolett.7b04342.

- [33] A. Eltaliawy et J. R. Long, « A Broadband, mm-Wave SPST Switch With Minimum 50-dB Isolation in 45-nm SOI-CMOS », *IEEE Trans. Microw. Theory Tech.*, vol. 69, nº 6, p. 2899-2906, 2021, doi: 10.1109/TMTT.2021.3066977.

- [34] T. Singh et R. R. Mansour, « Monolithic PCM Based Miniaturized T-type RF Switch for Millimeter Wave Redundancy Switch Matrix Applications », in 2019 IEEE MTT-S International Microwave Symposium (IMS), 2019, p. 658-660. doi: 10.1109/MWSYM.2019.8700946.

- [35] S. López-Soriano, J. Methapettyparambu Purushothama, A. Vena, et E. Perret, « CBRAM technology: transition from a memory cell to a programmable and non-volatile impedance for new radiofrequency applications », *Sci. Rep.*, vol. 12, n<sup>o</sup> 1, p. 4105, march 2022, doi: 10.1038/s41598-022-08127-x.

- [36] V. Petrov, T. Kurner, et I. Hosako, « IEEE 802.15.3d: First Standardization Efforts for Sub-Terahertz Band Communications toward 6G », *IEEE Commun. Mag.*, vol. 58, nº 11, p. 28-33, 2020, doi: 10.1109/MCOM.001.2000273.

[37] A. Léon *et al.*, "RF Power-Handling Performance for Direct Actuation of Germanium Telluride Switches," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 1, pp. 60-73, Jan. 2020, doi: 10.1109/TMTT.2019.2946145.

# CHAPTER II Optimization of the 2D RF switch layout and RF measurement setup

# Table of Contents

| CHAPTER II Optimization of the 2D RF switch layout and RF measurement setup   |

|-------------------------------------------------------------------------------|

| 1. Introduction                                                               |

| 2. RF study                                                                   |

| 2.1 Coplanar waveguide (CPW)                                                  |

| 2.2 CPW study                                                                 |

| 2.2.1 CPW Dimension calculation and simulation41                              |

| 2.3 Structure of 2D switch                                                    |

| 2.3.1 OPEN/SHORT structures simulation43                                      |

| 2.3.2 Comparison between measurement and simulation for SHORT/OPEN structures |

| 45                                                                            |

| 2.3.3 Optimisation up to 480 GHz 46                                           |

| 3. Description of DC and RF measurement procedure48                           |

| 3.1 RF measurement procedure                                                  |

| 3.2 De-embedding procedure                                                    |

| 3.2.1 Removing of the parasitic elements51                                    |

| 3.2.2 Determination of the intrinsic parameters:                              |

| 4. Conclusion                                                                 |

| 5. References                                                                 |

### 1. Introduction

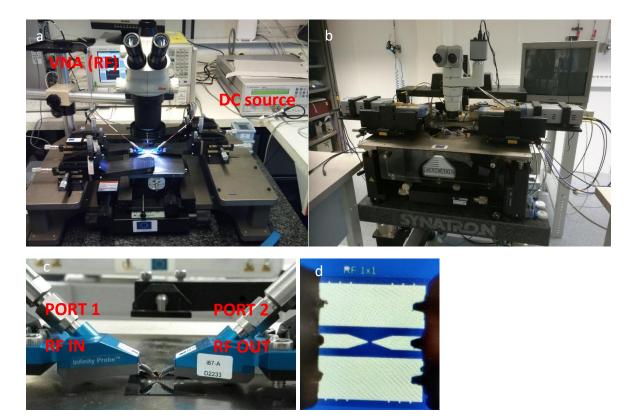

This chapter focuses on the structure of the 2D-based RF switch. Our 2D RF switch is a device embedded in a coplanar waveguide (CPW). First, we design a CPW operating from 0-67 GHz. Then, based on the CPW design, two more structures are developed. The first one is an OPEN representing the OFF state of an ideal 2D switch and the second one is a SHORT representing the ON state of an ideal 2D switch. Both of these structures are simulated up to 67 GHz, fabricated, and simulation results are compared with measurements. These structures are used for de-embedding purpose to extract the intrinsic figure of merits (FOMs) of our devices. Finally, an optimization of the design of the CPW is realized to reach a working frequency of 480 GHz. This new design is then simulated from 0 to 480 GHz. To conclude this chapter, RF and DC measurement setup and procedures are presented, followed by an explanation of the de-embedding technique used to extract the FOMs of our devices.

### 2. RF study

# 2.1 Coplanar waveguide (CPW)

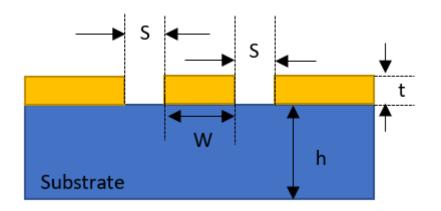

A coplanar waveguide is a transmission line mainly used in the design of microwave circuit. A CPW consists of a conductor strip called signal, which is located in the middle of two grounds. It is used for our device because they work at high frequencies without entailing any parasitic discontinuities [1]. Fig. 1 shows the cross section of a CPW where the yellow rectangles correspond to the metallic conductors and the blue one represents the dielectric substrate.

Figure 1 Cross section of a CPW, the metallic contacts are represented by the yellow rectangles and the substrate is represented by the blue rectangle. In this figure, W is the width of the signal, S the distance between the signal and the ground, h the thickness of the substrate and t the thickness of the contacts

The characteristic impedance of a CPW depends on the width of the conductor line (W), the space (S) between the conductor line and the ground, and on the dielectric permittivity of the substrate ( $\varepsilon_r$ ). The metal thickness (t) affects the ohmic losses. Main advantages of CPW are their low dispersion up to very high frequencies. [2] and the simple realization.

# 2.2 CPW study

The goal here is to determine the dimensions, W and S, required for an impedance of the line close to  $50 \Omega$ . These values are then used for the CPW embedding our 2D RF switch. The design is constrained by three factors: (i) (S) has to be small to avoid parasitic modes at high frequency, (ii) the width of the signal line cannot be smaller than 20 µm because of the size of the measurement probes, and (iii) (2S+W) need to be smaller than twice the pitch of the probes, the pitch is 100 µm in our station at this frequency range.

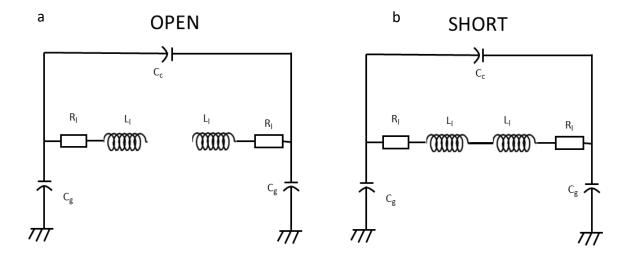

To design the CPW, we have used the software Pathwave Advanced Design System (ADS) from Keysight which allow to design and simulate high frequency devices and circuits. First, a tool from ADS called Controlled Impedance Line Designer is used to calculate the dimension of our CPW with our constraints. Afterwards, a simulation of the S-parameters of the CPW is carried out up to 67 GHz. Then, as mentioned above, two structures based on the dimension of the CPW are studied. The first one is the OPEN structure (corresponding to an open circuit) which represents the lower limit of the isolation obtainable for the RF switch OFF state. The second is the SHORT structure (corresponding to a short circuit) which represents the lower limit of the insertion loss obtainable for the RF switch in the ON state. Both of these structures are then simulated up to 67 GHz and then compared to the fabricated one.

### 2.2.1 CPW Dimension calculation and simulation

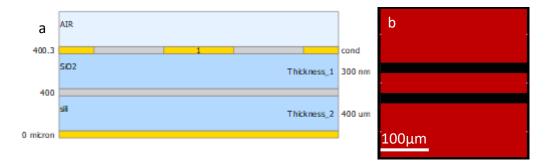

To determine the width of the signal line (W) and the gap between ground and source (S), we first create a file that corresponds to our substrate and specify the conductive metal and the dielectric. This substrate file is used in the Controlled Impedance Line Designer tool to calculate the coplanar waveguides dimension. The substrate chosen is  $Si/SiO_2$  that is a standard substrate for microelectronics, its dielectric constant is 11,68 (Fig. 2a). A width of the signal line W of 40 µm and a gap S of 22 µm are determined for a frequency up to 67GHz, giving an impedance of 49.7  $\Omega$ .

Figure 2 (a) Si/SiO<sub>2</sub> substrate parameters and (b) structure of the CPW simulated with W= 40 $\mu$ m, S=22  $\mu$ m and the length of the coplanar L = 300  $\mu$ m

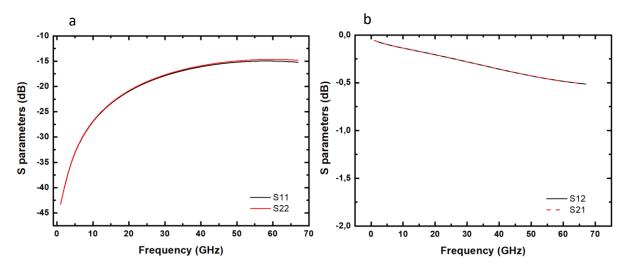

An S-parameters simulation of the CPW shown in Fig. 3b is realized using a finite element method (FEM) simulation. Fig. 3a shows the reflection parameters  $S_{11}$  and  $S_{22}$  and Fig. 3b shows the transmission parameters  $S_{12}$  and  $S_{21}$ .

Figure 3 (a) Reflexion parameters  $S_{11}$  and  $S_{22}$  (b) transmission parameters  $S_{12}$  and  $S_{21}$  of the CPW. The  $S_{21}$  is -0.5 dB at 67 GHz (89.1% of the power transmitted). For the reflexion it reaches -15 dB at 67 GHz (3.16% of the power is reflected)

The reflexion coefficient at 67 GHz of this CPW is -15 dB meaning that only 3.16% of the power is reflected under matched conditions, which is sufficient for our application.

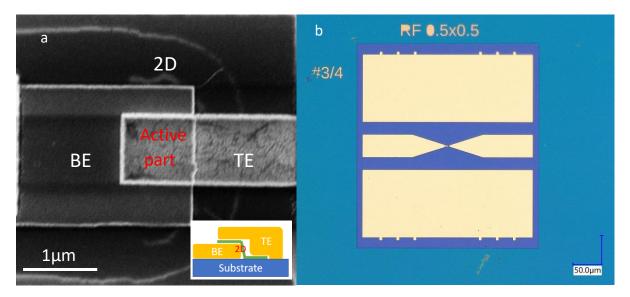

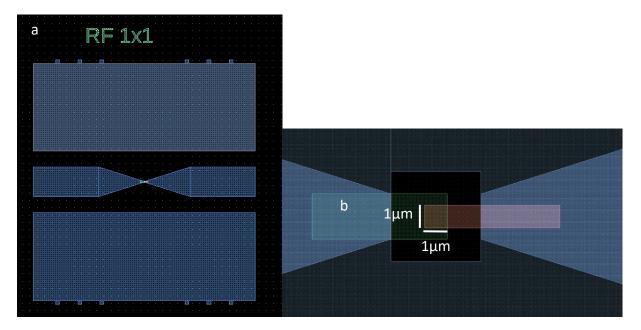

# 2.3 Structure of 2D switch

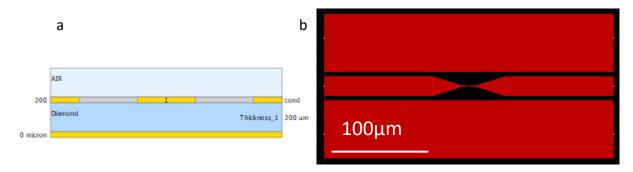

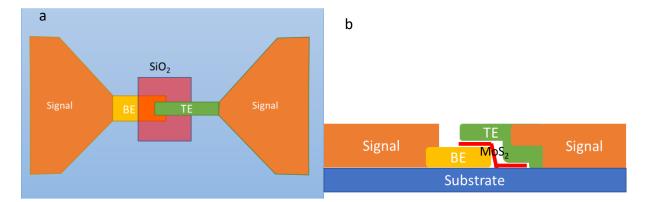

Our devices consist of a vertical metal isolator metal (MIM) structure made with a metallic electrode for the bottom electrode (BE) and the top electrode (TE) and with a 2D film sandwiched in between (Fig. 4a). To measure the switch at RF frequencies, the device needs

to be embedded in a CPW. Consequently, the signal line needs to be gradually reduced from  $40 \,\mu\text{m}$  to the dimension of the 2D switch (Fig. 4b).

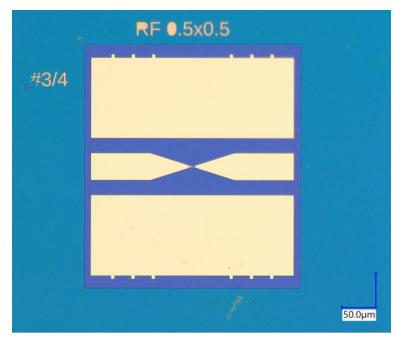

Figure 4 (a) SEM photography of the switch based (top view). The inset show the cross-section composition of the switch (b) Optical photography of the switch embedded in the CPW test structure.

### 2.3.1 OPEN/SHORT structures simulation

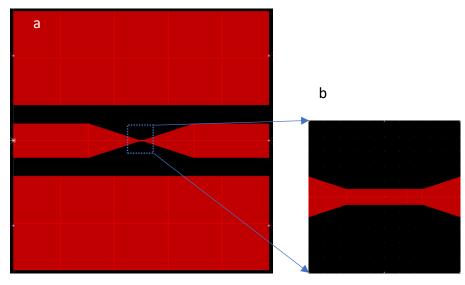

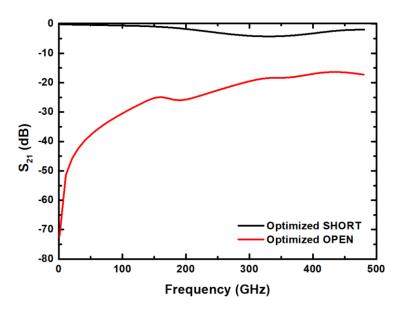

The layout of the SHORT and OPEN are displayed in Fig. 5a and 6a. They represent an ideal 2D RF switch in ON state and OFF state, respectively. The SHORT layout is based on the CPW structure studied but with a signal line of reduced width (1  $\mu$ m) at the place of the future 2D switch (Fig. 5b). The OPEN structure is realized by creating a gap of 3  $\mu$ m in the middle of the signal line (Fig. 6b). As one represents the limit of the ON state performances of the switch and the other represent the limit for the OFF state, it is mandatory that the difference of the S<sub>21</sub> parameters between the ideal ON and the ideal OFF state is as large as possible.

Figure 5 (a) SHORT structure (b) Zoom in of the junction

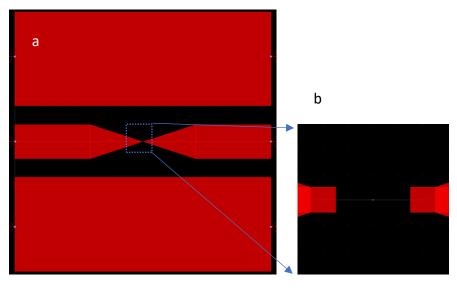

Figure 6 (a) OPEN structure (b) Zoom in of the junction with a 3  $\mu m$  gap

To validate our design, both structures are simulated up to 67 GHz. The layout of the global device is first created in the layout system of ADS. Once the design is created, we define the ports that simulate the measurements probes and assign them to left (input) and right (output) side of the CPW. Then, the substrate previously defined with its thickness, its dielectric constant and the thickness of the metal electrode is selected. Finally, the finite element method (FEM) and the frequency range for the simulation are chosen in the software. The simulation of S-parameters for both OPEN and SHORT is then obtained.

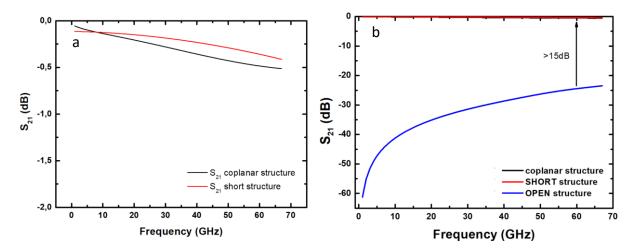

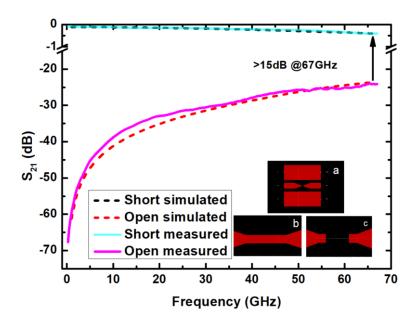

Figure 7 (a) Comparison of S<sub>21</sub> parameters between the classical CPW and the modified SHORT structure. The classical CPW reaches a value of -0.5 dB at 67 GHz and the SHORT structure is around - 0.4 dB at 67 GHz. (b) S<sub>21</sub> parameters for SHORT/OPEN and the classical CPW, a difference >15dB is observed between the S<sub>21</sub> parameter of the OPEN and the SHORT best structure. The insertion loss of the SHORT is - 0.4dB at 67 GHz and the isolation of the OPEN is -22 dB at 67 GHz

Fig. 7 shows a comparison of the  $S_{21}$  parameters between the first coplanar waves guide and the SHORT structure. We can observe that the reduction of the signal line in the SHORT does not affect significantly the transmission, compared to the CPW. For a CPW with a gap of 3 um as OPEN structure, the transmission is less than -20 dB at 67 GHz. Therefore, a difference of more than 15 dB between the SHORT and the OPEN is achieved up to 67 GHz.

# 2.3.2 Comparison between measurement and simulation for SHORT/OPEN structures

The OPEN and SHORT test structures are then fabricated on a silicon/silicon oxide (Si/SiO<sub>2</sub>) substrate. The measurements of the fabricated OPEN/SHORT structures are compared to the results obtained in simulations. Fig. 8 shows  $S_{21}$  as a function of frequency up to 67 GHz for the Si/SiO<sub>2</sub> substrate. We observe that for both the OPEN and the SHORT structure the simulation results and measurements data are close to each other. The difference between  $S_{21}$  of the SHORT and the OPEN is around 23 dB at 67 GHz.

Figure 8  $S_{21}$  parameters comparison between simulated inset (a) general structure of (b) SHORT and (c) OPEN. The SHORT structure reaches a value of -0.4 dB for both the measurement and the simulation at 67 GHz. The OPEN structure reaches a value of -25 dB for both the measurement and simulation

The difference between  $S_{21}$  in the ON state and in the OFF state should be as high as possible. For practical data communication, a difference of at least 10 dB between the ON and the OFF state allows to differentiate each state. For the demonstration of the practical use of our device, we aim to have a difference in  $S_{21}$  of at least 15 dB between ON and OFF state to allow a better distinction between both states.

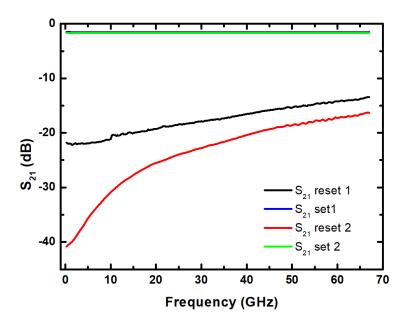

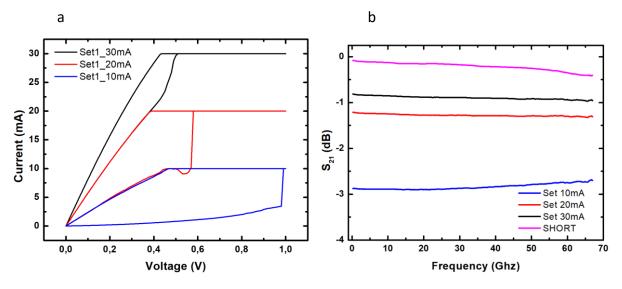

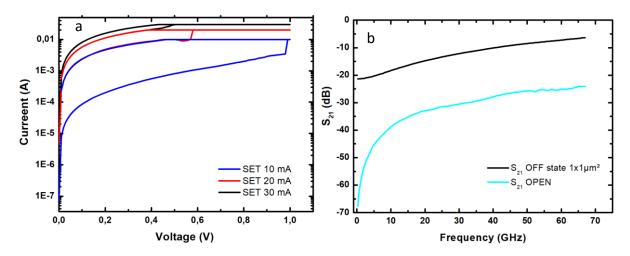

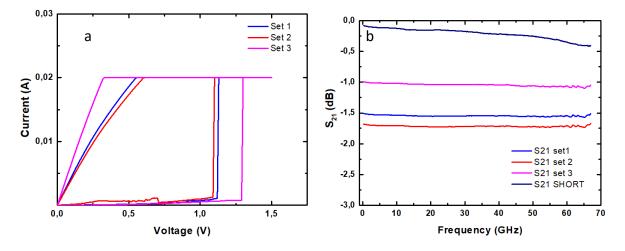

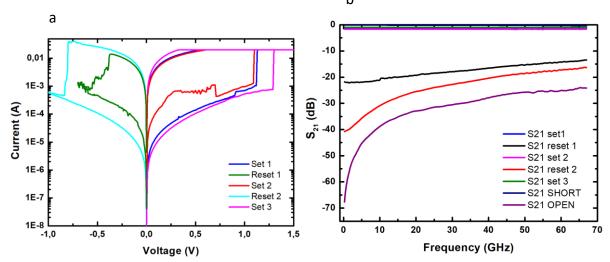

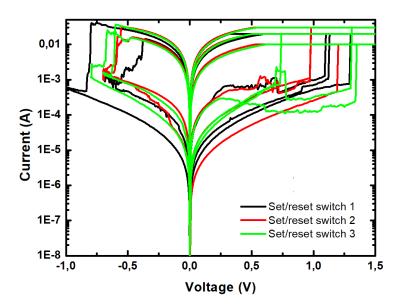

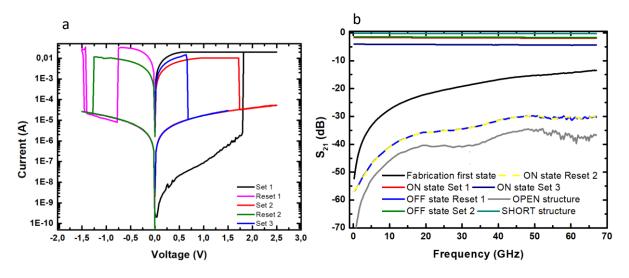

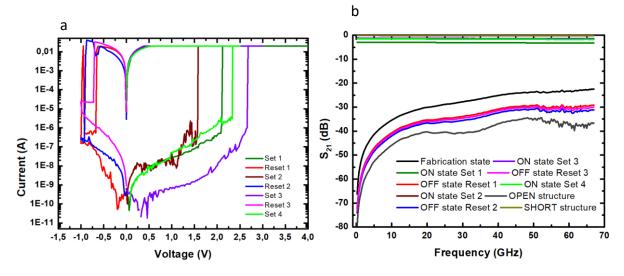

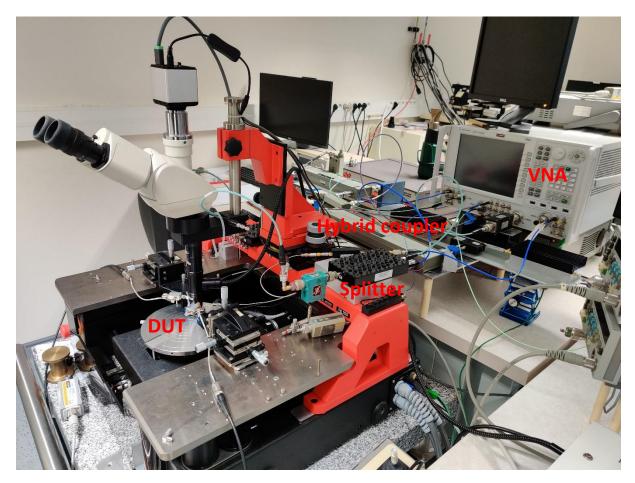

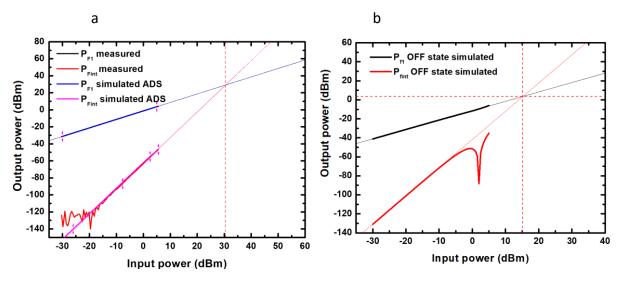

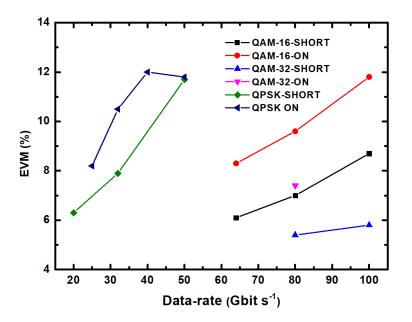

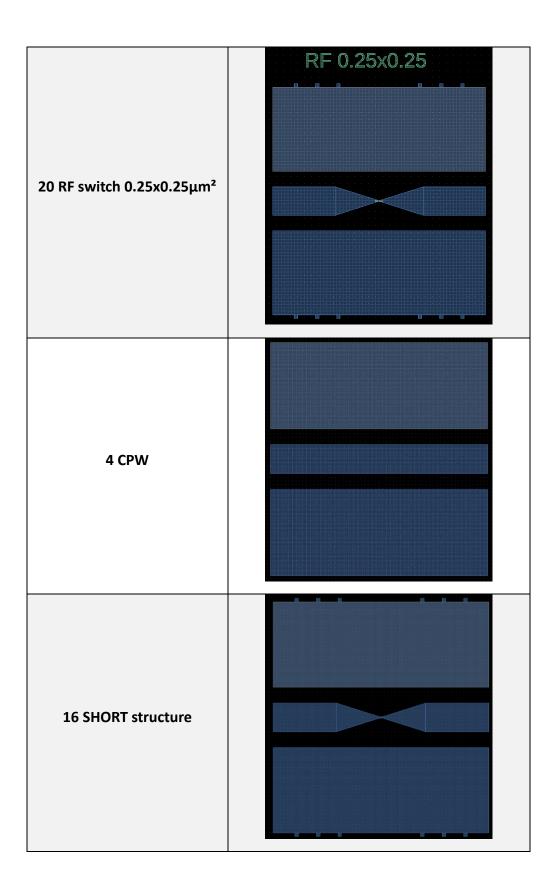

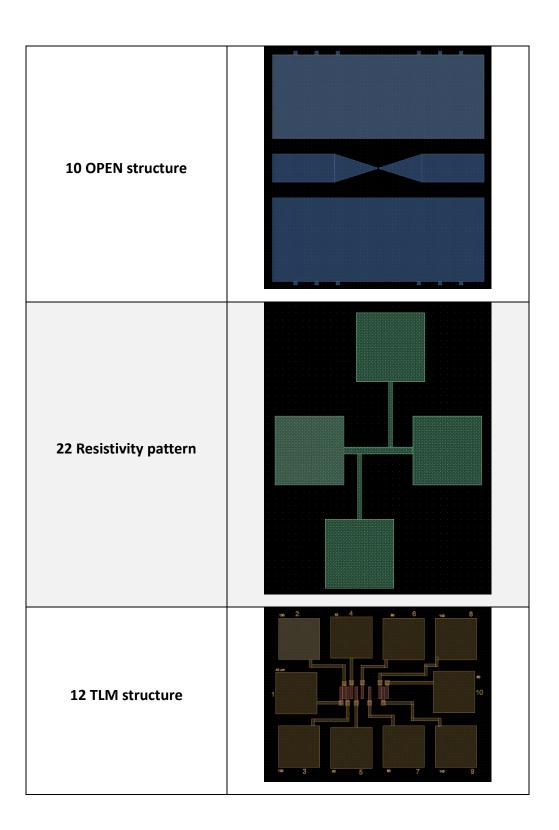

### 2.3.3 Optimization up to 480 GHz