### Models and algorithms for implementing energy-efficient spiking neural networks on neuromorphic hardware at the edge

Manon Dampfhoffer

### ▶ To cite this version:

Manon Dampfhoffer. Models and algorithms for implementing energy-efficient spiking neural networks on neuromorphic hardware at the edge. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT045. tel-04331152

### HAL Id: tel-04331152 https://theses.hal.science/tel-04331152

Submitted on 8 Dec 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

### **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

École doctorale : EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Spécialité : Nano électronique et Nano technologies

Unité de recherche : Spintronique et Technologie des Composants

Modèles et algorithmes pour l'implémentation de réseaux de neurones impulsionnels à faible consommation énergétique sur du matériel neuromorphique

Models and algorithms for implementing energy-efficient spiking neural networks on neuromorphic hardware at the edge

Présentée par :

#### **Manon DAMPFHOFFER**

#### Direction de thèse :

Lorena ANGHEL Directrice de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Alexandre VALENTIAN Co-encadrant de thèse

Ingénieur de recherche, Université Grenoble Alpes

Thomas MESQUIDA Co-encadrant de thèse

**CEA Grenoble**

#### Rapporteurs:

**Timothée MASQUELIER**

DIRECTEUR DE RECHERCHE, CNRS DELEGATION OCCITANIE OUEST

Benoît MIRAMOND

PROFESSEUR DES UNIVERSITES, UNIVERSITE COTE D'AZUR

#### Thèse soutenue publiquement le 4 septembre 2023, devant le jury composé de :

Lorena ANGHEL Directrice de thèse

PROFESSEURE DES UNIVERSITES, UNIVERSITE GRENOBLE

**ALPES**

Timothée MASQUELIER Rapporteur

DIRECTEUR DE RECHERCHE, CNRS DELEGATION OCCITANIE

**OUEST**

Benoît MIRAMOND Rapporteur

PROFESSEUR DES UNIVERSITES, UNIVERSITE COTE D'AZUR

Melika PAYVAND Examinatrice

ASSISTANT PROFESSOR, Universität Zürich

Pascal PERRIER Président

PROFESSEUR DES UNIVERSITES, GRENOBLE INP

Damien QUERLIOZ Examinateur

CHARGEE DE RECHERCHE HDR, CNRS DELEGATION ILE-DE-FRANCE SUD

#### Invités:

**Thomas Mesquida**

INGENIEUR DOCTEUR, Université Grenoble Alpes, CEA, List

Alexandre Valentian

INGENIEUR DOCTEUR, Université Grenoble Alpes, CEA, List

### **Abstract**

Deep learning in Artificial Neural Networks (ANNs), a branch of Artificial Intelligence (AI), is considered a revolution in computing and is impacting every sectors of the economy. However, ANNs are very compute- and memory-intensive, which limits their integration into edge devices for embedded applications. Bio-inspired Spiking Neural Networks (SNNs) are promising energy-efficient alternatives to ANNs, and hence are good candidates for edge AI implementations using neuromorphic hardware. Indeed, SNNs encode the information using sparse temporal events (called spikes) instead of dense and high precision activations. However, the gap between the algorithmic development of SNNs on the one hand, and their hardware implementation on the other hand, makes it difficult to achieve truly efficient solutions. In this context, this thesis follows a hardware-aware approach to drive algorithmic developments of SNNs. In particular, models and algorithms are proposed for improving the accuracy and energy efficiency of SNNs, considering both digital and analog hardware implementations.

In the interests of comparing SNNs and ANNs implementations on dedicated neural network accelerators, a high-fidelity model of their energy efficiency is provided. In particular, it is found that spike sparsity plays a key role in the efficiency of SNNs. Consequently, a novel SNN model, SpikGRU, combining the accuracy of gated recurrent ANNs with a high spike sparsity, is proposed. In addition, the implementation of synaptic weights with analog non-volatile memories is considered to further increase the energy efficiency. With an adapted training methodology, SNNs are demonstrated to be very robust to these highly-quantized and noisy weights. A case study using resistive memories further validates the approach.

By promoting algorithm-hardware co-development, this work aims at paving the way for efficient neural network implementations at the edge.

**Keywords:** deep learning, artificial neural networks, spiking neural networks, neuromorphic hardware, neural network accelerators, non-volatile memories

### Résumé

L'apprentissage profond dans les réseaux de neurones artificiels (ANNs), une branche de l'intelligence artificielle (IA), est considéré comme une révolution dans l'informatique et a un impact sur tous les secteurs de l'économie. Cependant, les ANNs sont très gourmands en ressources de calcul et en mémoire, ce qui limite leur intégration à la périphérie du réseau pour des applications embarquées. Les réseaux de neurones impulsionnels (SNNs) sont des alternatives prometteuses aux ANNs en termes d'efficacité énergétique et sont donc de bons candidats pour les implémentations IA embarquées utilisant du matériel neuromorphique. En effet, les SNNs encodent les informations en utilisant des événements temporels épars (appelés "spikes") au lieu d'activations denses et précises. Cependant, l'écart entre le développement algorithmique des SNNs d'une part, et leur implémentation matérielle d'autre part, rend difficile l'obtention de solutions réellement efficaces. Dans ce contexte, cette thèse suit une approche tenant compte du matériel pour conduire les développements algorithmiques des SNNs. En particulier, des modèles et des algorithmes sont proposés pour améliorer la précision et l'efficacité énergétique des SNNs, en considérant des implémentations matérielles numériques et analogiques.

Afin de comparer les implémentations des SNNs et des ANNs sur des accélérateurs de réseaux de neurones dédiés, un modèle de leur efficacité énergétique est fourni. En particulier, on constate que la parcimonie des activations joue un rôle clé dans l'efficacité des SNNs. Par conséquent, un nouveau modèle de SNN, SpikGRU, combinant la précision des ANNs récurrents à porte avec une parcimonie des activations, est proposé. En outre, l'implémentation des poids synaptiques utilisant des mémoires analogiques non volatiles est envisagée pour augmenter encore l'efficacité énergétique. Avec une méthodologie d'apprentissage adaptée, les SNNs se révèlent très robustes à ces poids hautement quantifiés et avec un haut niveau de bruit. Une étude de cas utilisant des mémoires résistives valide l'approche.

En encourageant le co-développement algorithme-matériel, ce travail vise à ouvrir la voie à des implémentations efficaces de réseaux de neurones embarqués.

**Mots-clés:** apprentissage profond, réseaux de neurones artificiels, réseaux de neurones impulsionnels, matériel neuromorphique, accélérateurs de réseaux de neurones, mémoires non-volatiles

## List of publications

### Journals:

- J. Minguet Lopez, T. Hirtzlin, M. Dampfhoffer, L. Grenouillet, L. Reganaz, G. Navarro, C. Carabasse, E. Vianello, T. Magis, D. Deleruyelle, M. Bocquet, J. M. Portal, F. Andrieu and G. Molas, OxRAM+OTS optimization for binarized neural network hardware implementation, *Semicond. Science Tech.* **2022**, 37, 014001, doi: 10.1088/1361-6641/ac31e2.

- J. Minguet Lopez, Q. Rafhay, M. Dampfhoffer, L. Reganaz, N. Castellani, V. Meli, S. Martin, L. Grenouillet, G. Navarro, T. Magis, C. Carabasse, T. Hirtzlin, E. Vianello, D. Deleruyelle, J. M. Portal, G. Molas and F. Andrieu, 1S1R optimization for high-frequency inference on Binary Spiking Neural Networks, *Advanced Electronic Materials* 2022, 2200323, doi: 10.1002/aelm.202200323.

- M. Dampfhoffer, T. Mesquida, A. Valentian and L. Anghel, Backpropagation-Based Learning Techniques for Deep Spiking Neural Networks: A Survey, in IEEE Transactions on Neural Networks and Learning Systems, 2023, doi: 10.1109/TNNLS.2023.3263008.

- M. Dampfhoffer, T. Mesquida, A. Valentian and L. Anghel, Are SNNs Really More Energy-Efficient Than ANNs? an In-Depth Hardware-Aware Study, in *IEEE Transactions on Emerging Topics in Computational Intelligence*, vol. 7, no. 3, pp. 731-741, June **2023**, doi: 10.1109/TETCI.2022.3214509.

#### Conferences:

- M. Dampfhoffer, T. Mesquida, A. Valentian and L. Anghel, Investigating Current-Based and Gating Approaches for Accurate and Energy-Efficient Spiking Recurrent Neural Networks. In: Pimenidis, E., Angelov, P., Jayne, C., Papaleonidas, A., Aydin, M. (eds) Artificial Neural Networks and Machine Learning ICANN 2022. ICANN 2022. Lecture Notes in Computer Science, vol 13531. Springer, Cham. doi: 10.1007/978-3-031-15934-3 30.

- M. Dampfhoffer, T. Mesquida, E. Hardy, A. Valentian and L. Anghel, Leveraging Sparsity with Spiking Recurrent Neural Networks for Energy-Efficient Keyword Spotting, ICASSP 2023 2023 IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), Rhodes Island, Greece, 2023, pp. 1-5, doi: 10.1109/ICASSP49357.2023.10097174.

- M. Dampfhoffer, J. Minguet Lopez, T. Mesquida, A. Valentian and L. Anghel, Improving the Robustness of Neural Networks to Noisy Multi-Level Non-Volatile Memory-based Synapses, *International Joint Conference on Neural Networks (IJCNN)*, Gold Coast, Australia, **2023**, pp. 1-8, doi: 10.1109/IJCNN54540.2023.10191804.

- J. Minguet Lopez, M. Dampfhoffer, T. Hirtzlin, L. Reganaz, L. Grenouillet, G. Navarro, M. Bernard, T. Magis, C. Carabasse, N. Castellani, V.Meli, E. Vianello, D. Deleruyelle, M. Bocquet, J. M. Portal, G. Molas and F. Andrieu, "1S1R Sub-Threshold Operation in Crossbar Arrays for Neural Networks Hardware Implementation," 2023 30th International Conference on Mixed Design of Integrated Circuits and System (MIXDES), Kraków, Poland, 2023, pp. 1-6, doi: 10.23919/MIXDES58562.2023.10203226.

- T. Mesquida, M. Dampfhoffer, T. Dalgaty, P. Vivet, A. Sironi and C. Posch, "G2N2: Lightweight Event Stream Classification with GRU Graph Neural Networks", 34th British Machine Vision Conference 2023, BMVC 2023, Aberdeen, UK, November 20-24, 2023.

## Acknowledgments

This thesis would not have been as it is without the support of the people around me. In particular, I want to express my gratitude to my thesis directors, Lorena Anghel and Alexandre Valentian for giving me the opportunity to do this thesis and for their encouragement. I want to specially thank my co-supervisor Thomas Mesquida for the endless discussions on digital design and algorithms and for having shared his knowledge and ideas with me.

I want to thank the University Grenoble Alpes and MIAI institute, who funded this thesis. I also want to thank the people at DSCIN for their support, and in particular people in the LSTA laboratory for accompanying me during this thesis. I want to express my gratitude to people from the neuro team, in particular Ivan Miro Panades, François Rummens, for their helpful advice. I would also like to thank Antoine Héraud, Stéphane Burel, Michele Martemucci, Yannick Malot for having shared a part of the PhD journey. I would like to specially thank Adrian Evans for his support and advice, for helping the students, and whose scientific rigor inspired me. I want to thank Pascal Vivet for following my thesis work and his advice.

I want to express my gratitude to people from the LIIM laboratory who followed my thesis project, such as Marielle Malfante, Marina Reyboz and Thomas Dalgaty. I also want to thank Diego Puschini, Olivier Antoni, Anca Molnos and Romain Lemaire, for having shared with me their projects. I also want to thank Johannes Thiele from LIAE laboratory for passing on his vision on spiking neural networks.

I want to thank all the people in Spintec laboratory for sharing their interest in physics and AI, in particular Lucian Prejbeanu, Philippe Talatchian, Ursula Ebels, Kamal Danouchi, Guillaume Prenat and Gregory Di Pendina.

I want to express my gratitude to people from CEA-Leti for sharing their passion for analog devices and design: Gabriel Molas, Elisa Vianello, Tifenn Hirtzlin and, in particular, Joel Minguet Lopez for introducing me to non-volatile memories, and Emmanuel Hardy for sharing his experience on low-power design for keyword spotting.

I also want to thank the members of the jury, Timothée Masquelier, Benoît Miramond, Damien Querlioz, Melika Payvand and Pascal Perrier, for having accepted to examine my work.

Finally, I want to express my gratitude to my loved ones, for their support throughout this thesis.

## **Contents**

| Al | ostrac  | et                                                                                                                                                                                                                                                                  | iii                  |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Ré | sume    | é                                                                                                                                                                                                                                                                   | iv                   |

| Li | st of 1 | publications                                                                                                                                                                                                                                                        | v                    |

| 1  | Intro   | oduction                                                                                                                                                                                                                                                            | 1                    |

| 2  | Back    | kground and State of the Art                                                                                                                                                                                                                                        | 5                    |

|    | 2.1     | <ul> <li>2.1.1 Models and Coding Strategies</li></ul>                                                                                                                                                                                                               | 5<br>9<br>13         |

|    | 2.2     | Training Spiking Neural Networks                                                                                                                                                                                                                                    | 14<br>14             |

|    | 2.3     | <ul><li>2.2.2 Backpropagation-Based Training</li></ul>                                                                                                                                                                                                              | 17<br>25<br>25<br>31 |

|    | 2.4     | 2.3.3 Estimating Energy Efficiency                                                                                                                                                                                                                                  | 33<br>35             |

| 3  | Ene     | rgy Efficiency of Spiking vs. Artificial Neural Networks                                                                                                                                                                                                            | 37                   |

|    | 3.1     |                                                                                                                                                                                                                                                                     | 37                   |

|    | 3.2     | 3.2.1 Architecture of Neural Network Accelerators                                                                                                                                                                                                                   | 38<br>38<br>40       |

|    | 3.3     | Dynamic Energy Consumption of ANNs and SNNs                                                                                                                                                                                                                         | 40<br>41<br>41<br>43 |

|    | 3.4     | <ul> <li>3.3.4 Application to SNN Algorithms</li> <li>ANN Models Considering Data Reuse and Exploitation of Sparsity</li> <li>3.4.1 Best Case ANN: Ideal Exploitation of Data Reuse and Sparsity</li> <li>3.4.2 Real Case Study: the Eyeriss Accelerator</li> </ul> | 46<br>47<br>48<br>49 |

|    | 3.5     | ·                                                                                                                                                                                                                                                                   | 52<br>55             |

|    |         | , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                               | 56                   |

| 4  | Imp   | roving A | Accuracy and Efficiency of Spiking Neural Networks              | 59  |

|----|-------|----------|-----------------------------------------------------------------|-----|

|    | 4.1   |          | action                                                          |     |

|    | 4.2   |          | el Recurrent SNN Model: SpikGRU                                 |     |

|    |       | 4.2.1    | Models of Recurrent SNNs                                        |     |

|    |       | 4.2.2    | SpikGRU: a Spiking Gated Recurrent Unit                         |     |

|    |       |          | Experiments on Audio Spiking Datasets                           |     |

|    |       | 4.2.4    | Number of operations in Spiking vs. Artificial RNNs             |     |

|    |       |          | Discussion                                                      |     |

|    | 4.3   | _        | ging Sparsity in Recurrent SNNs                                 |     |

|    |       |          | Experiments on a Keyword Spotting Task                          |     |

|    |       | 4.3.2    | Increasing Sparsity with Gradient Descent                       | 72  |

|    |       | 4.3.3    | Increasing Sparsity with Spiking Input Data                     | 75  |

|    |       |          | Discussion                                                      |     |

|    | 4.4   | 0,       | Efficiency of Spiking vs. Artificial RNNs                       |     |

|    |       |          | Extension of the Model of Energy Efficiency to RNN topologies . |     |

|    |       |          | Comparison of Gated Recurrent ANNs and SNNs                     |     |

|    |       |          | Discussion                                                      |     |

|    | 4.5   | Conclus  | sion                                                            | 84  |

| 5  | Imp   | roving A | Accuracy and Efficiency with Analog Synapses                    | 87  |

|    | 5.1   | _        | iction                                                          | 87  |

|    | 5.2   | Improv   | ing Robustness to Noisy Quantized Weights                       | 88  |

|    |       | 5.2.1    | Fault Model and Training Strategy for NVM-based Synapses        | 89  |

|    |       | 5.2.2    | Robustness of Neural Networks to Noisy Weights                  | 93  |

|    |       | 5.2.3    | Analysis of Error-Aware Training                                | 97  |

|    |       | 5.2.4    | Discussion                                                      | 100 |

|    | 5.3   |          | udy: Resistive Memories                                         |     |

|    |       | 5.3.1    | Simulations of BSNNs with Resistive Memory Devices              | 102 |

|    |       | 5.3.2    | Improving the Robustness to Errors of BSNNs                     | 104 |

|    |       | 5.3.3    | Improving the Efficiency of BSNNs                               | 105 |

|    |       | 5.3.4    | Discussion                                                      | 107 |

|    | 5.4   | Conclus  | sion                                                            | 107 |

| 6  | Sun   | nmary an | nd Perspectives                                                 | 109 |

| Bi | bliog | raphy    |                                                                 | 113 |

|    | _     |          |                                                                 |     |

# **List of Figures**

| 2.1 | Models and coding strategies for Spiking Neural Networks. (a) Feed-                   |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | forward fully-connected neural network. (b) ANN and SNN neuron and                    |    |

|     | synapse models. (c) Input encoding: example of pixel-to-spike conver-                 |    |

|     | sion with a rate coding or temporal (latency) coding                                  | 6  |

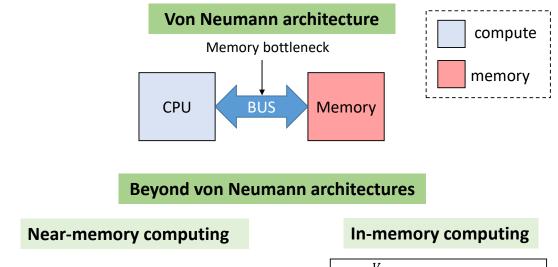

| 2.2 | Hardware implementations of Spiking Neural Networks. Traditional                      |    |

|     | computer architectures, such as Central or Graphics Processing Units                  |    |

|     | (CPUs, GPUs), are based on the von Neumann paradigm, where com-                       |    |

|     | pute and memory are physically separated, causing a memory bottle-                    |    |

|     | neck. In beyond von Neumann architectures, compute and memory are                     |    |

|     | co-localized inside a core. A chip is composed of several cores commu-                |    |

|     | nicating using a network-on-chip (NOC). Among the architectures that                  |    |

|     | are used in efficient neural networks accelerators, near- and in-memory               |    |

|     | computing (NMC, IMC) can be distinguished. In NMC, although com-                      |    |

|     | pute and memory units are close, they are still separated. In IMC, part               |    |

|     | of the computation (multiply and accumulate operations) is performed                  |    |

|     | inside the memory, using the physical properties of the devices                       | 10 |

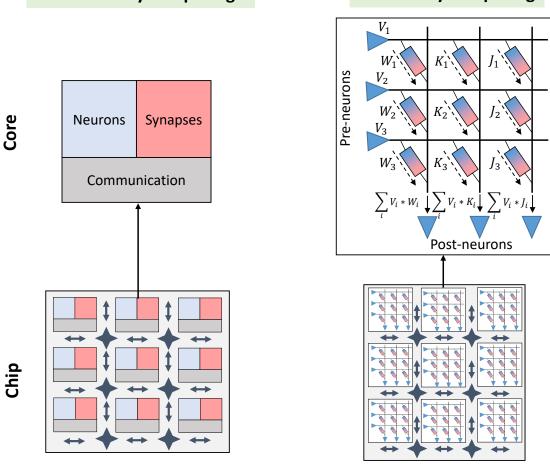

| 2.3 | Non-Volatile Memories can be used to encode synaptic weights. A. Re-                  |    |

|     | sistive Random Access Memory (RRAM) device. The resistance of the                     |    |

|     | dielectric layer depends on the formation of the conductive filament.                 |    |

|     | Low (resp. high) resistive state encodes the "0" (resp. "1"). <b>B.</b> Magnetic      |    |

|     | Random Access Memory (MRAM) device. The resistance of the mag-                        |    |

|     | netic tunnel junction depends on the orientation of the magnetization of              |    |

|     | the free layer: parallel (resp. anti-parallel) corresponds to a low (resp.            |    |

|     | high) resistive state and encodes the "0" (resp. "1")                                 | 12 |

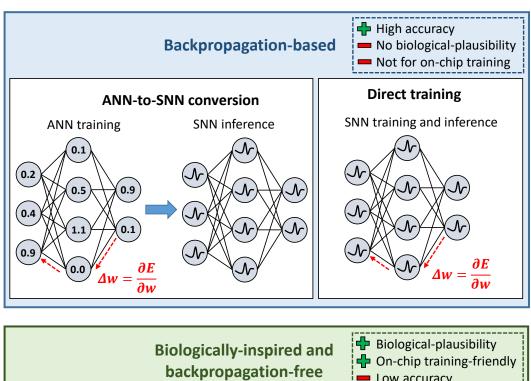

| 2.4 | Training strategies for Spiking Neural Networks. Backpropagation-                     |    |

|     | based strategies (top) are based on gradient descent, in which a cost                 |    |

|     | function <b>E</b> is minimized and weight updates $\delta w$ are performed by com-    |    |

|     | puting the derivative of <b>E</b> with respect to the weight <b>w</b> . Training with |    |

|     | gradient descent is performed either on a equivalent ANN and then its                 |    |

|     | weights are transferred to the SNN (ANN-to-SNN conversion), or di-                    |    |

|     | rectly on the SNN. Biologically-inspired and backpropagation-free strate-             |    |

|     | gies (bottom) are based either on the biologically-plausible unsuper-                 |    |

|     | vised Spike-Timing-Dependent Plasiticity rule, or on approximations of                |    |

|     | the backpropagation algorithm                                                         | 15 |

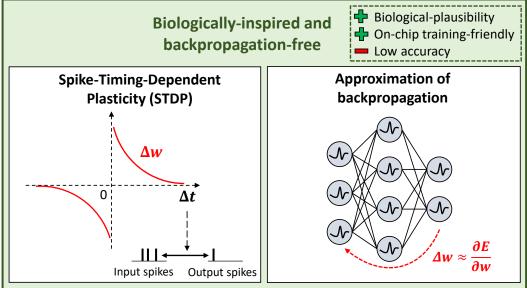

| 2.5 | Supervised learning with backpropagation in SNNs. In the forward                                                                                                                                                                                              |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | pass, the inputs are propagated through the layers resulting in output <b>Y</b> . During the backward pass, <b>Y</b> is compared to a target <b>T</b> using a loss function <b>L</b> , defining the cost <b>E</b> to be minimized with gradient descent. Then |    |

|     | each weight <b>w</b> is updated according to the derivative of the cost <b>E</b> with respect to <b>w</b> . This derivative is computed using the chain rule, which                                                                                           |    |

|     | requires to compute the derivative of all previous operations. This al-                                                                                                                                                                                       |    |

|     | lows to backpropagate the errors through all the layers of the network.                                                                                                                                                                                       |    |

|     | However, in SNNs, the activation function $\mathbf{f}$ of neurons has the derivative equals to zero everywhere except in $\theta$ where it is infinite. Therefore,                                                                                            |    |

|     | the derivative of a surrogate function is used to compute the gradients                                                                                                                                                                                       |    |

|     | during the backward pass                                                                                                                                                                                                                                      | 21 |

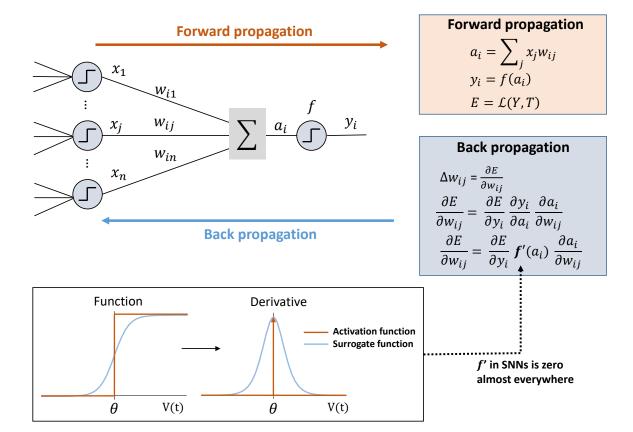

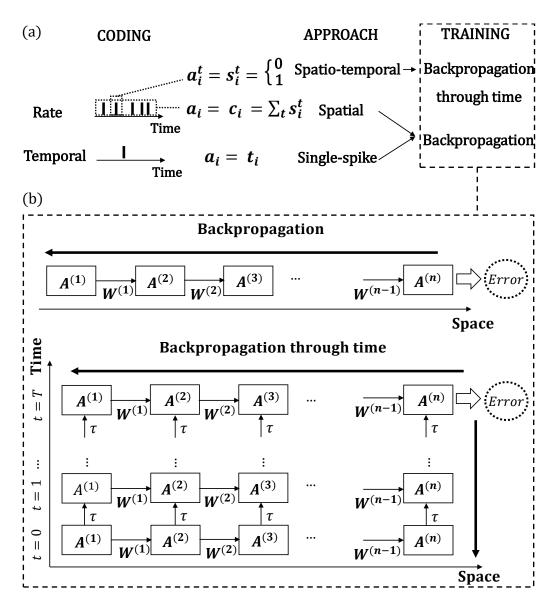

| 2.6 | (a) Backpropagation-based learning algorithms. Spatial and spatio-tempora approaches use a rate coding while the single-spike approach use a tem-                                                                                                             | al |

|     | poral (latency) coding. On the one hand, the spatio-temporal approach                                                                                                                                                                                         |    |

|     | considers the activation of each neuron at each timestep $a_i^t$ , corresponding to the emission or not of a spike $s_i^t$ . BPTT is used to backpropagate                                                                                                    |    |

|     | the error in both space and time dimensions. On the other hand, the spa-                                                                                                                                                                                      |    |

|     | tial and single-spike approaches consider for each neuron a single acti-                                                                                                                                                                                      |    |

|     | vation $a_i$ for the forward pass, which can correspond to the spike count $c_i$                                                                                                                                                                              |    |

|     | for the former or the timing of the unique spike emitted by the neuron $t_i$ for the latter. Therefore, the backpropagation is used to backpropagate                                                                                                          |    |

|     | the error only in the space dimension. (b) Backpropagation and BPTT                                                                                                                                                                                           |    |

|     | training. Notations: $n$ number of layers, $T$ number of timesteps used                                                                                                                                                                                       |    |

|     | in the SNN inference, $A^{(l)}$ activation of neurons in layer $l$ , $W^{(l)}$ weight                                                                                                                                                                         |    |

|     | vector from layer $l$ to $l+1$ , $\tau$ membrane potential and postsynaptic po-                                                                                                                                                                               | 20 |

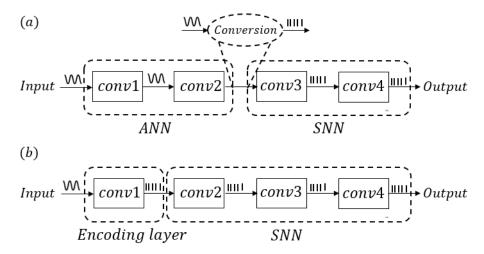

| 2.7 | tential update (for LIF neurons and continuous synapses)                                                                                                                                                                                                      | 22 |

| 2.7 | are done in ANN mode (using high precision activations and MACs operations) and the last convolutions are performed in SNN mode (ACs operations with spikes). A conversion from analog values to spikes is                                                    |    |

|     | performed between ANN and SNN layers. (b) Encoding layer. The first                                                                                                                                                                                           |    |

|     | layer is hybrid ANN-SNN, as synapses perform MAC operations be-                                                                                                                                                                                               |    |

|     | tween weights and real-valued inputs, but neurons are spiking. This                                                                                                                                                                                           |    |

| 2.0 | layer allows the conversion from analog values to spikes.                                                                                                                                                                                                     | 29 |

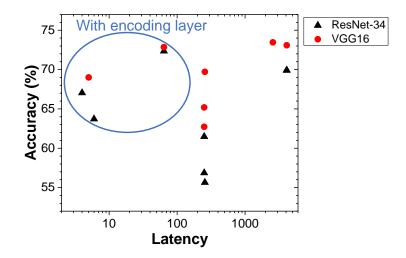

| 2.8 | Impact of encoding layer and network topology on the accuracy-latency trade-off, using SNN algorithms from Table 2.3 on the ImageNet dataset.                                                                                                                 | 33 |

|     |                                                                                                                                                                                                                                                               | 00 |

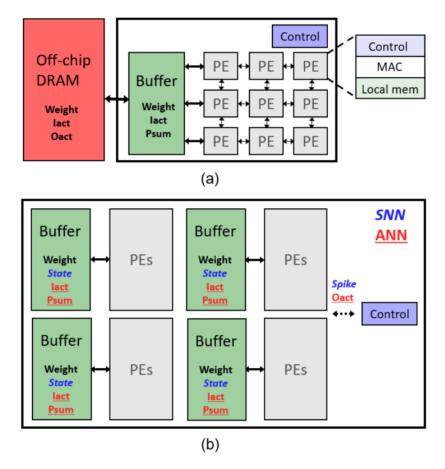

| 3.1 | (a) Spatially folded architecture (such as the Eyeriss v1 chip from Chen et al., 2017). (b) Spatially expanded architecture. Data types specific                                                                                                              |    |

|     | to ANN and SNN are highlighted and in italic, respectively. Memory buffers on-chip are used to store weights and states (such as membrane potentials or input currents) for SNNs. For ANNs, input activations                                                 |    |

|     | (iact) and partial sums (psum) (used to store partial results of MAC op-                                                                                                                                                                                      |    |

|     | erations) must be stored in addition to weights                                                                                                                                                                                                               | 39 |

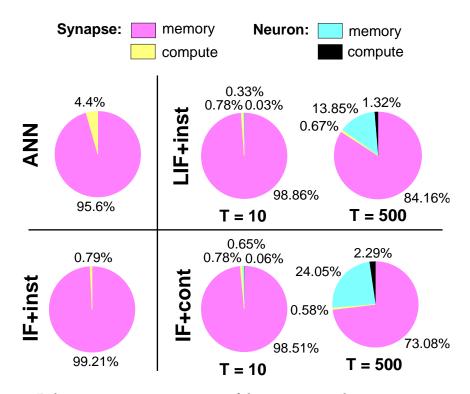

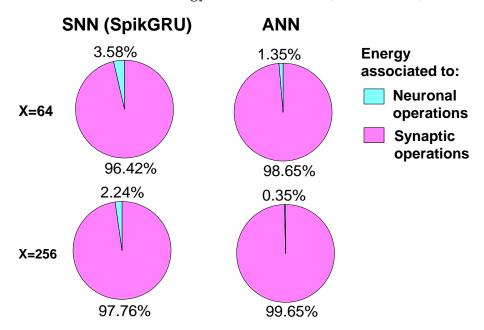

| 3.2 | Relative energy consumption of the memory and compute associated with synapse operations (at each spike) and neuron operations (at each timestep) of the ANN and the different SNN models described in Sec-                                                                                                                                                                                                                                                                                                                       |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | tion 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44 |

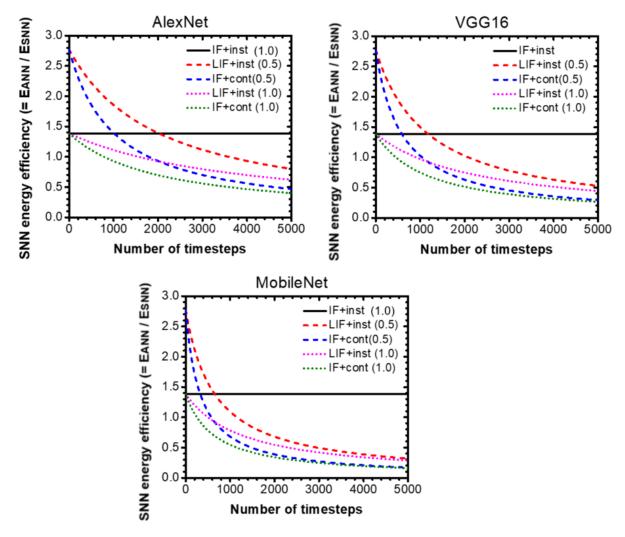

| 3.3 | SNN energy efficiency relative to ANN ( $=E_{ANN}/E_{SNN}$ ) as a function of the number of timesteps (T), depending on the SNN model and $N_{spikes/syn}$ (in parenthesis). The AlexNet, VGG16 and MobileNet topologies have                                                                                                                                                                                                                                                                                                     |    |

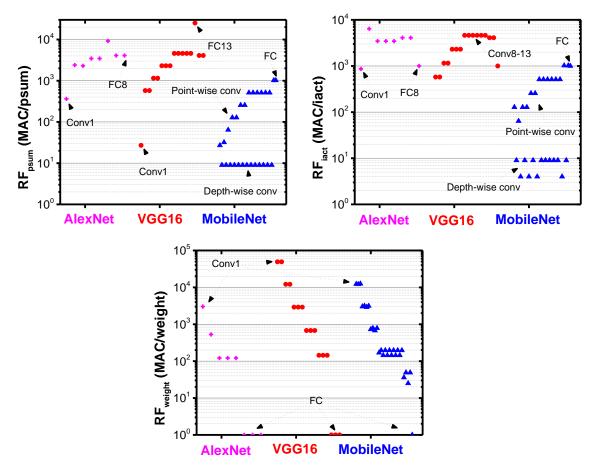

| 3.4 | $N_{syn}/N_{neur} = 2.9 \times 10^3$ , $1.7 \times 10^3$ , $9.4 \times 10^2$ , respectively Ideal data reuse (Reuse Factor) of the three data types (left: <i>psum</i> , right: <i>iact</i> , bottom: weight) for AlexNet, VGG16 and MobileNet topologies (inspired by Chen et al., 2019). Each point represents a layer of the neural                                                                                                                                                                                            | 45 |

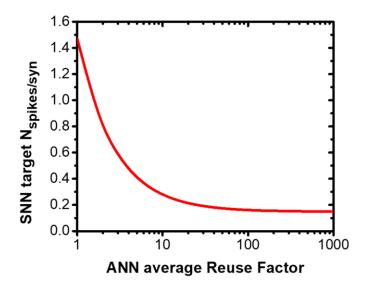

| 3.5 | network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48 |

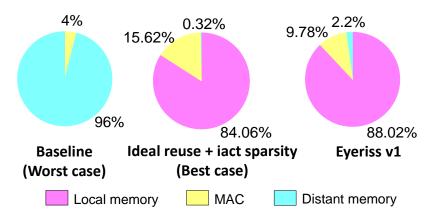

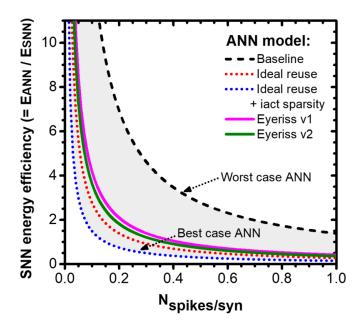

| 3.6 | function of the average data Reuse Factor in the ANN                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50 |

| 2.7 | and (3.13), from left to right). AlexNet topology is used in Eyeriss v1 case.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52 |

| 3.7 | SNN $IF$ + $inst$ energy efficiency relative to ANN (= $E_{ANN}/E_{SNN}$ ) as a function of $N_{spikes/syn}$ for the different ANN models considered, using AlexNet                                                                                                                                                                                                                                                                                                                                                               |    |

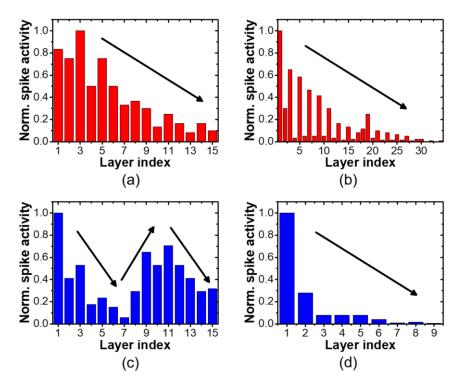

| 3.8 | topology in Eyeriss v1 and v2 models. Normalized layer-wise spike activity of different SNNs with different training methods and datasets. (a) VGG16 from conversion pre-training with spiking backpropagation fine-tuning on ImageNet (Rathi et al., 2021b). (b) ResNet-34 from conversion on ImageNet (Sengupta et al., 2019). (c) VGG16 from conversion pre-training with spiking backpropagation fine-tuning on CIFAR10 (Rathi et al., 2021b). (d) VGG9 with spiking backpropagation training on CIFAR10 (Lee et al., 2020a). | 53 |

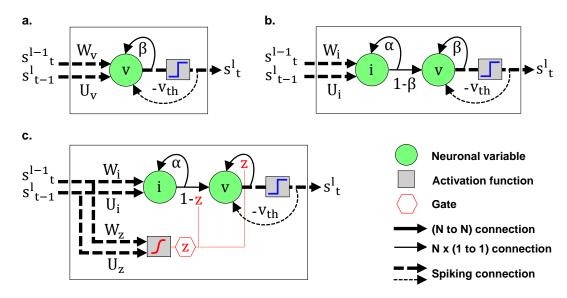

| 4.1 | Recurrent SNN models considered (a. LIF, b. Cuba-LIF, c. SpikGRU), assuming a layer with input and output size <b>N</b> and omitting biases for                                                                                                                                                                                                                                                                                                                                                                                   |    |

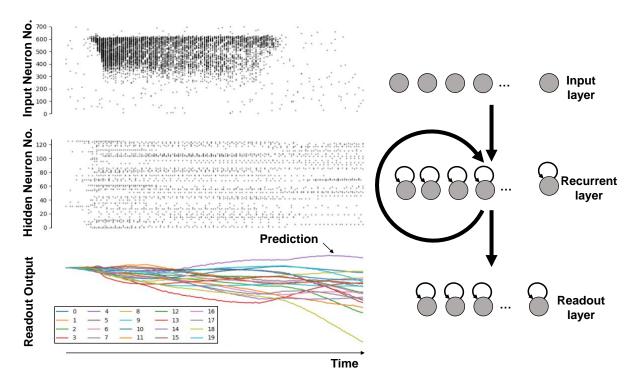

| 4.2 | clarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63 |

|     | rent layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64 |

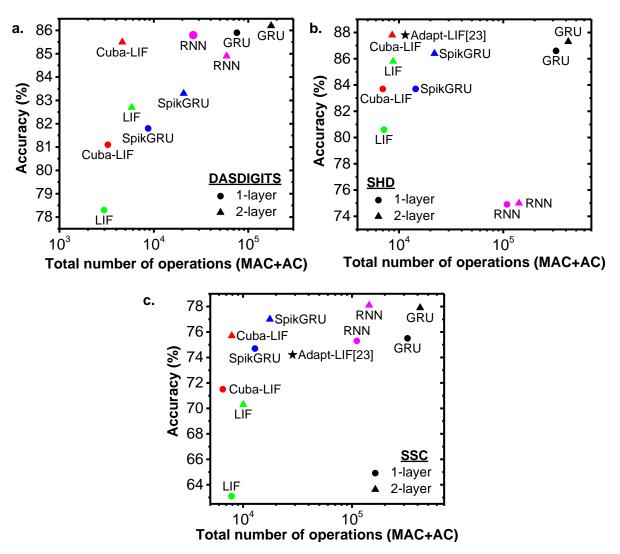

| 4.3 | Accuracy vs. total number of operations (MAC + AC) per timestep for processing one sample from the (a) DASDIGITS, (b) SHD and (c) SSC datasets.                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

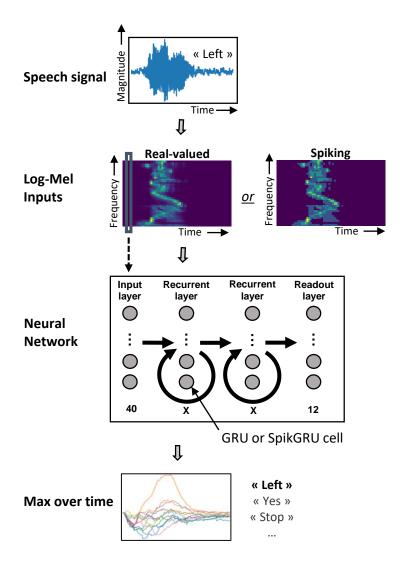

| 4.4 | Keyword spotting task. Log-Mel features are extracted from the raw audio signal and either the real values (experiment 1, Section 4.3.2) or the converted spiking inputs with spike count (experiment 2, Section 4.3.3) are fed to the neural network at each timestep. The neural network has two recurrent layers of <i>X</i> GRU or SpikGRU cells. The maximum value                                                                                                                                                           | 09 |

|     | over time of the readout neurons is used for the prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

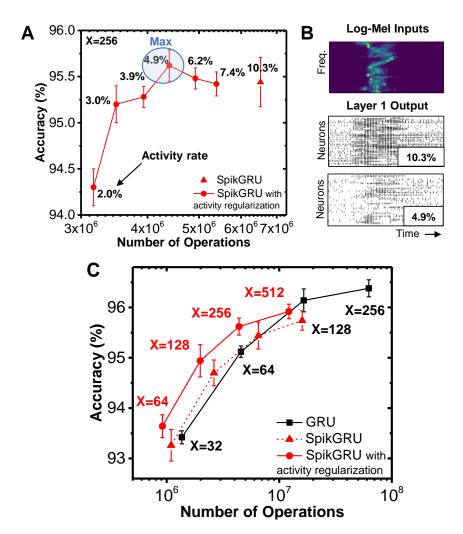

| 4.5 | <b>A.</b> Accuracy vs. number of operations per sample for SpikGRU (with                 |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | size $X=256$ ) with the different levels of activity regularization ( $\lambda \in$      |    |

|     | {0.5, 1, 2, 4, 10, 50}). <b>B.</b> Output spikes from the first layer in SpikGRU         |    |

|     | with different activity rates. C. Accuracy vs. total number of operations                |    |

|     | (MAC + AC) per sample for GRU and SpikGRU with different layer                           |    |

|     | sizes $(X)$ , with and without activity regularization for SpikGRU                       | 74 |

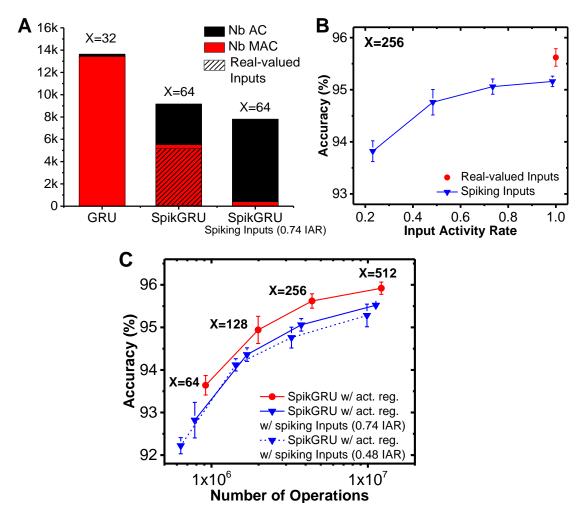

| 4.6 | <b>A.</b> Number of MAC and AC operations per timestep for GRU and Spik-                 |    |

|     | GRU (real-valued inputs) and SpikGRU with spiking inputs, with Input                     |    |

|     | Activity Rate (IAR) of 0.74. MACs due to real-valued inputs in SpikGRU                   |    |

|     | are highlighted. <b>B.</b> Accuracy vs. input activity rate with spiking inputs.         |    |

|     | C. Accuracy vs. number of operations per sample for SpikGRU with ac-                     |    |

|     | tivity regularization (act. reg.) with real-valued or spiking inputs (IAR                |    |

|     | 0.74 and 0.48) with different hidden layer sizes ( $X$ )                                 | 76 |

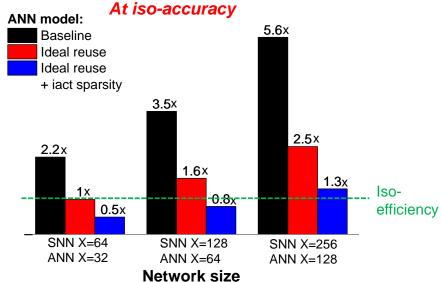

| 4.7 | Ratio of energy associated with neuronal operations and synaptic oper-                   |    |

|     | ations in the SNN and ANN with ideal data reuse and exploitation of                      |    |

|     | <i>iact</i> sparsity (equations 4.15 and 4.21), for two topology sizes (X)               | 81 |

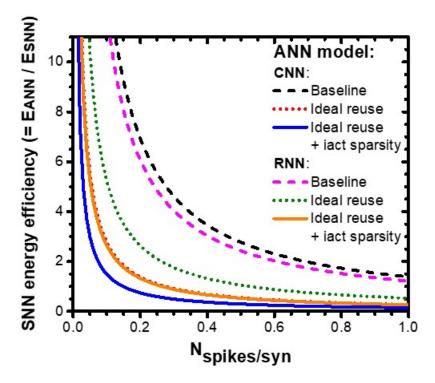

| 4.8 | SNN energy efficiency compared to the ANN (with same topology, with                      |    |

|     | X=256 hidden neurons in recurrent layers) as a function of the SNN spik-                 |    |

|     | ing activity ( $N_{spikes/syn}$ being the average number of spikes per synapses),        |    |

|     | depending on the ANN implementation. Baseline corresponds to the                         |    |

|     | naive implementation, while Ideal reuse and Ideal reuse + iact sparsity                  |    |

|     | consider ideal ANN implementations, considering only data reuse, or                      |    |

|     | data reuse and the exploitation of <i>iact</i> sparsity, respectively. The case of       |    |

|     | CNN and RNN topologies is compared. The data for CNN are extracted                       |    |

|     | from Chapter 3 while the equations for RNNs are described in this Section.               | 82 |

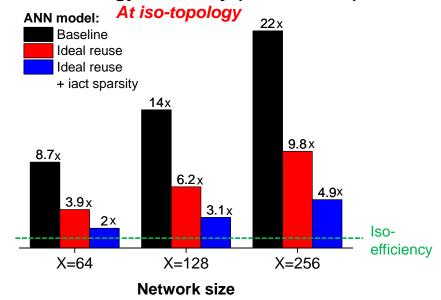

| 4.9 | SNN energy efficiency compared to ANN depending on the ANN im-                           |    |

|     | plementation for recurrent topologies, in the case of A. same topology                   |    |

|     | for ANN and SNN or <b>B.</b> similar accuracy for ANN and SNN. For the                   |    |

|     | hardware implementation, SpikGRU is used as SNN model and a light                        |    |

|     | version of the GRU equivalent to SpikGRU (i.e. with a single gate) is                    |    |

|     | used for ANN. Data come from the KWS experiments described in Sec-                       |    |

|     | tion 4.3. Note that the accuracy results for the ANN were obtained with                  |    |

|     | the standard GRU implementation (two gates).                                             | 83 |

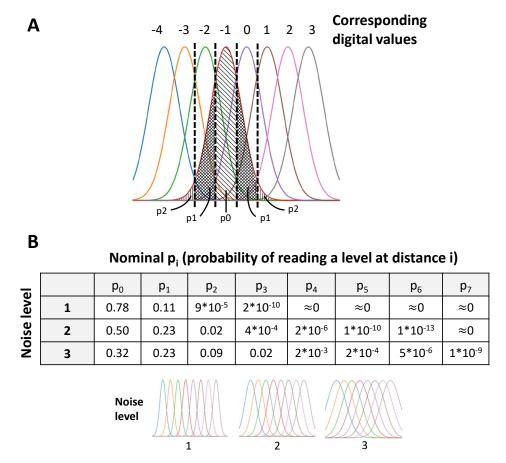

| 5.1 | Fault model for multi-level NVMs. A. Noise model in 8-level NVMs                         |    |

| 0.1 | (digital values associated to each level in these experiments are indi-                  |    |

|     | cated). $p_i$ is the probability to read the level at distance $i$ (in particular        |    |

|     | $p_0$ is the probability to correctly read the level). <b>B.</b> Probabilities of errors |    |

|     | $(p_i)$ depending on the distance between two levels, for three noise levels             |    |

|     | (varying sigma in the gaussian distribution)                                             | 90 |

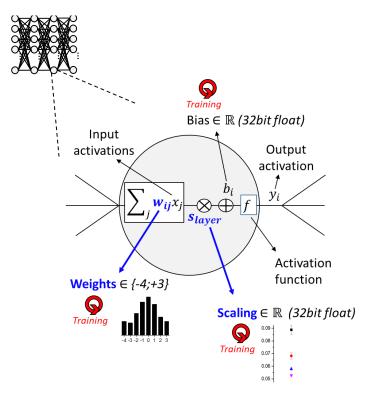

| 5.2 | Neural Network with highly-quantized weights. Illustration of the op-                    | 70 |

| 0.2 | erations for computing the output activation of a neuron. Input activa-                  |    |

|     | tions are multiplied with the quantized weights (8 levels) and by a scal-                |    |

|     | ing (full precision, 1 per layer) to adjust the range of the pre-activation.             |    |

|     | A bias (in full precision, 1 per neuron for RNNs and 1 per channel for                   |    |

|     | CNNs) is added before the activation function. Weights, scaling and bias                 |    |

|     | are trained                                                                              | 92 |

|     | NEW MINIEUM I I I I I I I I I I I I I I I I I I I                                        |    |

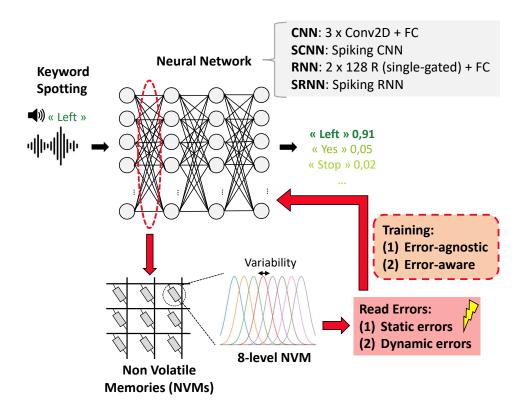

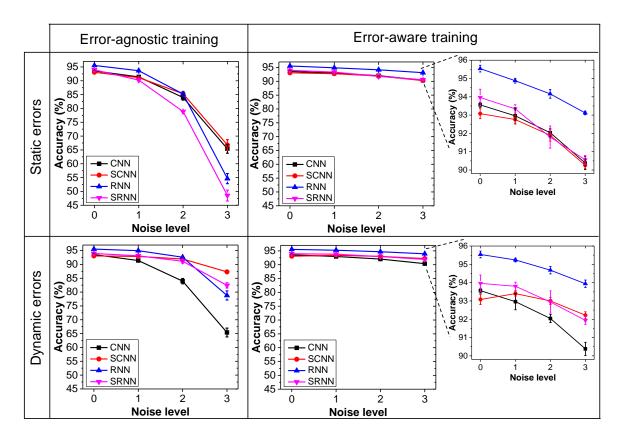

| 5.3             | <b>Experiments on the keyword spotting task</b> . Four types of neural net-                                                                                   |     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                 | works using 8-level NVMs for weight implementation are simulated on                                                                                           |     |

|                 | a keyword spotting task. The effects of two training strategies (error-                                                                                       |     |

|                 | agnostic and error-aware) and two types of errors (static and dynamic) are considered.                                                                        | 93  |

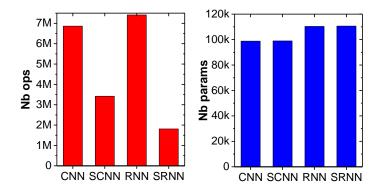

| 5.4             | Number of operations per inference (left) and number of parameters                                                                                            | 93  |

| J. <del>4</del> | (right) of the models                                                                                                                                         | 95  |

| 5.5             | Test accuracy of the different neural networks (shown with a 95% confi-                                                                                       | )   |

| 0.0             | dence interval) on the keyword spotting task. Static (top) and dynamic                                                                                        |     |

|                 | (bottom) errors are considered with different noise levels (cf Fig. 5.1),                                                                                     |     |

|                 | noise level 0 corresponding to the error-free case. Error-agnostic train-                                                                                     |     |

|                 | ing (left) and error-aware training (right) are compared. In error-aware                                                                                      |     |

|                 | training, models are trained at the same noise levels as those used for                                                                                       |     |

|                 | testing                                                                                                                                                       | 96  |

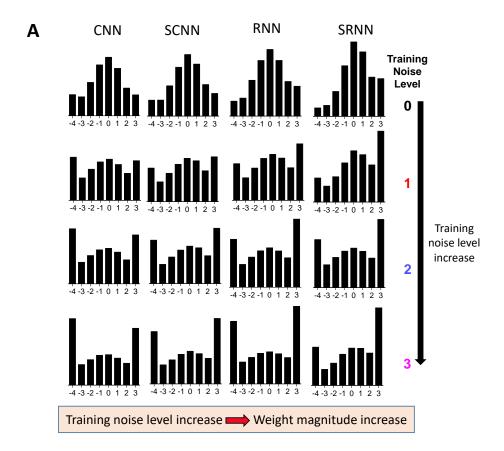

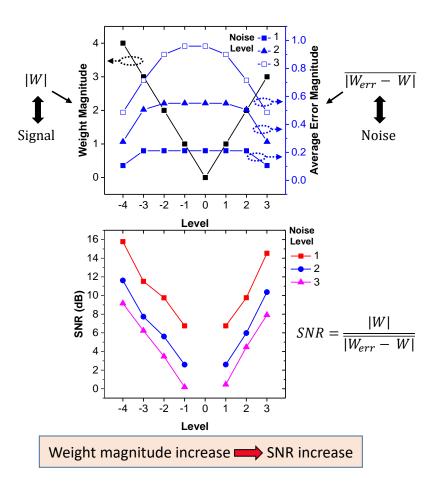

| 5.6             | Analysis of error training. Weight distribution (A) and scaling of each                                                                                       |     |

|                 | layer (B) for the different models after training, when the models are                                                                                        |     |

|                 | trained with different noise levels (cf Fig. 5.1), noise level 0 correspond-                                                                                  |     |

|                 | ing to the error-free case                                                                                                                                    | 98  |

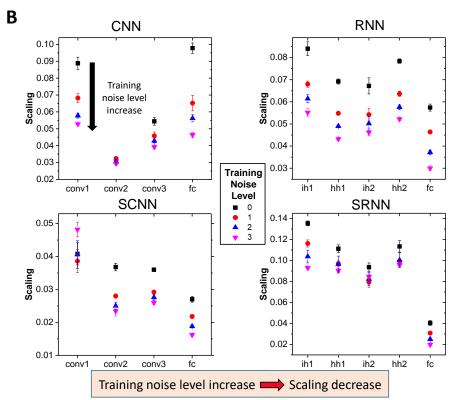

| 5.7             | Analysis of error training. Weight Magnitude and Average Error Mag-                                                                                           |     |

|                 | nitude (Top) and Signal-to-Noise Ratio (Bottom) of the 8 NVM levels, for                                                                                      |     |

|                 | different noise levels (cf Fig. 5.1). As the level associated with the digital value "0" has a signal amplitude of "0", its SNR in dB is $-\infty$ and is not |     |

|                 | represented                                                                                                                                                   | 99  |

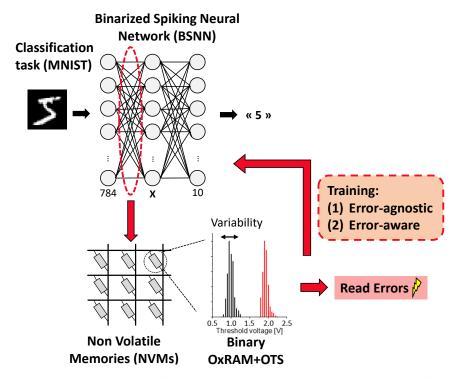

| 5.8             | Implementation of the BSNN using OxRAM+OTS (1S1R) for synaptic                                                                                                |     |

| 0.0             | weights storage. The BSNN is implemented with varying hidden layer                                                                                            |     |

|                 | size (X). For these experiments, only one timestep is used to simulate                                                                                        |     |

|                 | the SNN dynamics, therefore no distinction is made between static and                                                                                         |     |

|                 | dynamic errors in the fault model                                                                                                                             | 103 |

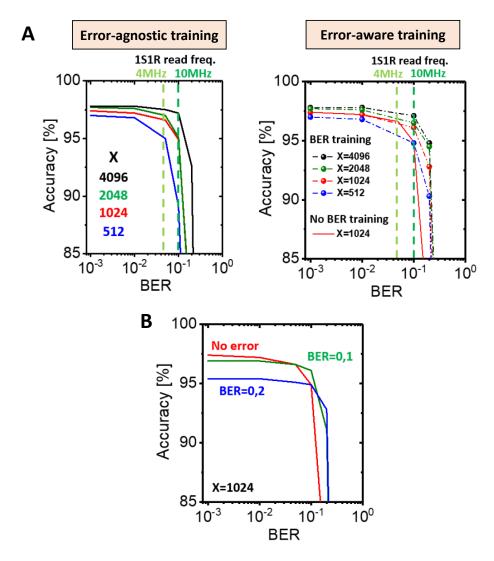

| 5.9             | <b>Robustness to errors of the BSNN. A.</b> Accuracy of the BSNN with dif-                                                                                    |     |

|                 | ferent hidden layer size (X) with the Bit Error Rate (BER) of the binary                                                                                      |     |

|                 | weights implemented using OxRAM+OTS in error-agnostic (left) and                                                                                              |     |

|                 | error-aware (right) training conditions. In the error-aware condition,                                                                                        |     |

|                 | the BER used for training is the same as the BER used for testing. The BER corresponding to the two considered reading frequencies are high-                  |     |

|                 | lighted. <b>B.</b> Accuracy of the BSNN with the BER (during test) depending                                                                                  |     |

|                 | on the BER used for training in error-aware training condition ( <i>No error</i>                                                                              |     |

|                 | corresponds to error-agnostic training), for topology X=1024                                                                                                  | 104 |

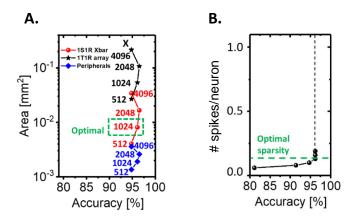

| 5.10            | Optimization of the efficiency of the BSNN. A. Trade-off between the                                                                                          |     |

|                 | area of the memory array and accuracy of BSNNs with different hidden                                                                                          |     |

|                 | layer size. The area of the 1S1R array, the equivalent 1T1R array, and                                                                                        |     |

|                 | the peripherals of the 1S1R array are shown (details of the computation                                                                                       |     |

|                 | can be found in Minguet Lopez et al., 2022). <b>B.</b> BSNN activity (average                                                                                 |     |

|                 | number of spikes per neuron per inference) depending on the BSNN                                                                                              | 107 |

|                 | accuracy (topology X=1024)                                                                                                                                    | 106 |

## **List of Tables**

| 2.1        | Comparison of backpropagation-based direct training strategies on static vision datasets                                                                                                                                                                                                                                                                                  | 25       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | Comparison of backpropagation-based algorithms on neuromorphic vi-                                                                                                                                                                                                                                                                                                        | 26       |

| 2.3        | Impact of input encoding, training and network architecture width on the accuracy-latency trade-off                                                                                                                                                                                                                                                                       | 32       |

| 3.1<br>3.2 | Energy efficiency of state-of-the-art SNNs relative to ANN (= $E_{ANN}/E_{SNN}$ ) using models from Section 3.3 and energy ratio in Table 3.1. ANN IS CONSIDERED WITH A NAIVE (NON-OPTIMIZED) IMPLEMENTA-                                                                                                                                                                 | 44       |

| 3.3        | Target spike activity for the SNN <i>IF</i> + <i>inst</i> model to be at least as efficient                                                                                                                                                                                                                                                                               |          |

|            | as the ANN depending on the ANN accelerator model                                                                                                                                                                                                                                                                                                                         | 53       |

| 4.1        | Testing accuracy (%) of the spiking (LIF, Cuba-LIF, SpikGRU) and non-spiking (RNN, GRU) models on the DASDIGITS, SHD and SSC datasets, shown with the 95% confidence interval. The best accuracy for each topology for spiking and non-spiking models is highlighted. Results from related works are also indicated. The number of parameters (#Params) is given for SHD. | 66       |

| 4.2        | Number of MAC and AC operations per timestep for one layer of the ANN and SNN models. $m$ and $n$ are respectively input and output size of the layer. For SNN models, $a_{in}$ and $a_{out}$ are respectively input and                                                                                                                                                  |          |

| 4.3        | output activity rate (spikes per neuron per timestep) of the layer Accuracy and number of operations per sample on GSCD v2 for Spik-GRU (with activity regularization) and GRU, and previous state-of-the-art SNNs                                                                                                                                                        | 68<br>74 |

| 5.1        | Strengths and weaknesses of different models (ANN vs SNN) and topologies (RNN vs CNN)                                                                                                                                                                                                                                                                                     | 100      |

### List of Abbreviations

1S1R 1 Selector 1 Resistor1T1R 1 Transistor 1 Resistor

**AC** ACcumulate

Adapt-LIF Adaptive Leaky Integrate-and-Fire

AER Address Event Representation

ANN Artificial Neural Network

**ASIC** Application Specific Integrated Circuit

**BER** Bit Error Rate

**BN** Batch Normalization

BPTT BackPropagation Through TimeBSNN Binary Spiking Neural NetworkCNN Convolutional Neural Network

**CPU** Central Processing Unit

**Cuba-LIF** Current-based Leaky Integrate-and-Fire

**DAS** Dynamic Audio Sensor

**DRAM** Dynamic Random Access Memory

**DVS** Dynamic Vision Sensor

**FC** Fully Connected

**FPGA** Field Programmable Gate Array

**GLB** GLobal Buffer

GPU Graphics Processing Unit GRU Gated Recurrent Unit iact Input activation

IF Integrate-and-Fire

IMC In-Memory Computing

KWS KeyWord Spotting

LIF Leaky Integrate-and-Fire

LSTM Long Short-Term Memory

MAC Multiply-and-ACcumulate

NMC Near-Memory Computing

NVM Non-Volatile Memory

oact Output activation

PE Processing Element

**psum** Partial sum

**ReLU** Rectified Linear Unit

**RF** Reuse Factor

**RNN** Recurrent Neural Network

RRAM Resistive Random Access MemorySCNN Spiking Convolutional Neural Network

SNNSpiking Neural NetworkSpikGRUSpiking Gated Recurrent UnitSRAMStatic Random Access MemorySRNNSpiking Recurrent Neural NetworkSTDPSpike-Timing-Dependent Plasticity

tanh Hyperbolic tangent

### Chapter 1

### Introduction

Deep learning in Artificial Neural Networks (ANNs), a branch of artificial intelligence (AI), is considered a revolution in computing and is impacting every sectors of the economy. Indeed, ANNs can now solve difficult tasks at the human level and beyond, and are a game changer in many fields, such as transportation, health, or industry. For instance, ANNs are used in many applications such as image recognition (Krizhevsky et al., 2009), object detection (Girshick et al., 2014), speech recognition (Hinton et al., 2012), medical diagnosis (Esteva et al., 2017), game playing (Silver et al., 2016), etc. Nevertheless, ANNs are very compute- and memory-intensive and are responsible, in part, for the growth of the CO2 emissions of the Cloud (Li et al., 2016). Therefore, directly integrating AI algorithms into edge devices can allow to decrease data transfer between the devices and the Cloud, hence reducing energy consumption, but also latency, dependency on connectivity, as well as improving security and privacy. To this end, research is increasingly moving towards efficient hardware implementations of ANNs on dedicated accelerators, which could be deployed at the edge. While an increased speed and energy efficiency have been achieved, further gains could result from the combination of specialized hardware and more efficient algorithms.

By more closely mimicking the brain, Spiking Neural Networks (SNNs) appear to be energy-efficient alternatives to ANNs. In the brain, neurons use electrical pulses to transmit information through the synapses in a sparse and asynchronous manner. Similarly, SNNs encode the information using sparse temporal events (called spikes) instead of dense and high precision activations. These input spikes are integrated through time in the membrane potential of neurons, the latter firing when reaching its threshold, following the Integrate-and-Fire (IF) dynamics (Lapicque, 1907). In addition, their ability to exploit spatio-temporal information makes them attractive for various applications, and in particular for processing event data produced by low-power dynamic sensors (Lichtsteiner et al., 2008).

SNNs present many advantages for efficient implementation on so-called neuromorphic hardware (Mead, 1990). Indeed, while ANNs process the high precision information in a one-shot fashion using matrix multiplications, information in SNN is coded in a binary signal distributed over time. The use of spikes allows replacing costly multiply-accumulate (MAC) operations in ANNs by simpler accumulate (AC) operations, which consume less energy and occupy less area (Horowitz, 2014). Moreover, the high spike sparsity can be leveraged efficiently in event-based implementations (Merolla et al., 2014; Davies et al., 2018; Moradi et al., 2018). Therefore, SNNs are considered good candidates for edge AI implementations.

However, the gap between the algorithmic development of SNNs on the one hand, and their hardware implementation on the other hand, makes it difficult to achieve

truly efficient solutions. Indeed, there is currently no general model allowing to estimate the energy consumption of SNNs on neuromorphic hardware, making it difficult to ensure that they are actually more efficient than ANNs. Moreover, analog hardware implementations of SNNs, in particular using emerging non-volatile memories (NVMs) to encode synaptic weights, can achieve significant gains compared to fully-digital implementations (Hung et al., 2022). However, analog systems are prone to variability, inducing the occurrence of errors, which can significantly degrade the accuracy of the system (Higuchi et al., 2022; Yan et al., 2023). Therefore, a hardware-algorithm co-development strategy is needed in order to obtain accurate and energy-efficient solutions for edge AI applications.

In this thesis, we first propose a high-fidelity model of the dynamic energy consumption of SNNs and ANNs, in the interests of comparing their implementation on dedicated neural network accelerators. We provide lower and upper bounds on the relative efficiency of ANNs and SNNs, as well as a case study using state-of-the-art neural network accelerators. In particular, we find that spike sparsity plays a key role in the efficiency of SNNs. Unfortunately, we show that SNN algorithms based on convolutional topologies for processing static data do not reach a sufficient spike sparsity to compete with efficient ANN implementations.

Consequently, we propose a novel SNN model, SpikGRU, combining the accuracy of gated recurrent ANNs with a high spike sparsity, for processing spatio-temporal data. SpikGRU is compared with various recurrent SNN and ANN models on several spiking and non-spiking data, using speech recognition tasks. Furthermore, with the example of SpikGRU, we show that sparsity in SNNs can be further leveraged by optimizing the activity of neurons through gradient descent, or by using sparse spiking input data. In addition, we demonstrate that SpikGRU can allow higher energy efficiency than ANN equivalents on a dedicated neuromorphic hardware implementation, while being as accurate.

Furthermore, we consider the implementation of synaptic weights with analog NVMs as a solution to improve the efficiency of both ANN and SNN implementations. We present a fault model applicable to all kind of single- and multi-level NVMs and an adapted training methodology. ANNs and SNNs with convolutional and recurrent topologies are demonstrated to be robust to errors in these highly-quantized and noisy weights. A case study using resistive memories further validates the approach.

This thesis is organized as follows:

- In Chapter 2, the background on SNN algorithms and hardware implementations is presented, focusing on strategies to improve their accuracy and energy efficiency.

- In Chapter 3, a model of the dynamic energy consumption of SNNs and ANNs on dedicated neural network accelerators is proposed, providing guidelines for improving SNN algorithms and hardware.

- In Chapter 4, a novel gated recurrent SNN model (SpikGRU) is introduced and its high accuracy and energy efficiency are demonstrated on several spoken word recognition tasks.

- In Chapter 5, SNNs and ANNs robustness to errors in highly-quantized and noisy weights is studied, in the objective of implementing the synaptic weights with NVMs. A case study with resistive memories is considered.

- In Chapter 6, a summary of the contributions of the thesis and the perspectives are presented.

### **Chapter 2**

## Background and State of the Art

Spiking Neural Networks (SNNs) are studied from the perspective of neurosciences, machine learning and neuromorphic hardware, with different objectives, and hence are characterized by an important heterogeneity. Various approaches, with varying degrees of biological plausibility, have been proposed to model and train SNNs. Moreover, different types of neuromorphic hardware, from digital to analog, have been considered to efficiently implement SNNs. This chapter provides a general overview of the state-of-the-art on SNNs, with a focus on the background that was used for this work.

This chapter is organized as follows:

- In Section 2.1, models and implementations of SNNs are presented, including models of neurons and synapses, information encoding with spikes, software and hardware implementations of SNNs, and applications for SNNs.

- In Section 2.2, training strategies for SNNs are reviewed, from biologically-inspired learning rules to high performance backpropagation-based training.

- In Section 2.3, strategies to enhance accuracy and efficiency (such as latency and spike sparsity) of SNNs are presented. Special attention is given to the trade-off between accuracy and latency, as well as the estimation of the energy efficiency.

Part of the state of the art presented in this chapter has been published in Dampfhoffer et al., 2023c.

# 2.1 Models and Implementations of Spiking Neural Networks

### 2.1.1 Models and Coding Strategies

#### **SNN Models**

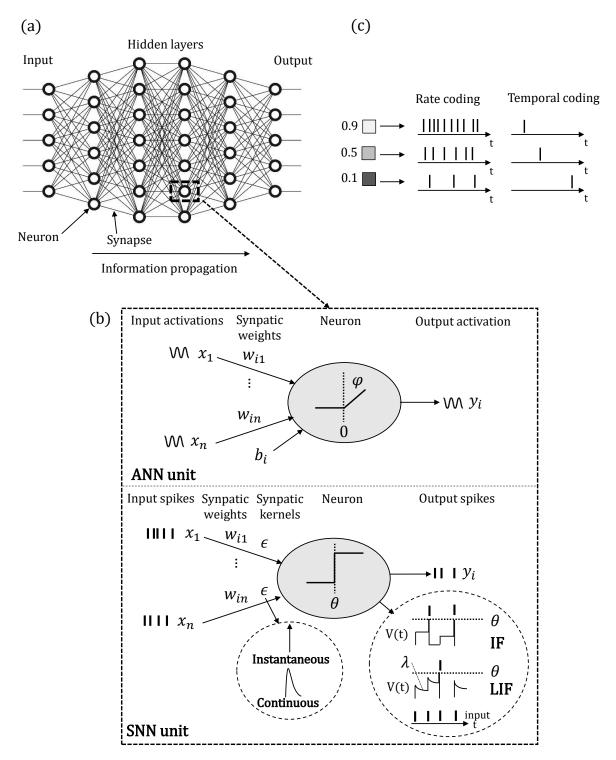

The basic ANNs and SNNs units in a neural networks are shown in Fig.2.1. In ANNs, the output of a neuron is a function defined as:

$$y_i = \varphi(\sum_j x_j w_{ij} + b_i) \tag{2.1}$$

where  $y_i$  is the output activation of neuron i,  $b_i$  is the bias of neuron i,  $x_j$  is the input activation from presynaptic neuron j, and  $w_{ij}$  is the synaptic weight between neurons

FIGURE 2.1: **Models and coding strategies for Spiking Neural Networks.** (a) Feedforward fully-connected neural network. (b) ANN and SNN neuron and synapse models. (c) Input encoding: example of pixel-to-spike conversion with a rate coding or temporal (latency) coding.

i and j.  $\varphi$  is an activation function, such as the Rectified linear unit (ReLU). While in ANNs the information propagates synchronously on a layer-by-layer basis, the information processing in SNNs is asynchronous and in a depth-first manner. Indeed, neurons in a layer fire spikes without waiting for other neurons in the same layer to fire. Moreover, due to the temporal dynamics of the neurons, SNNs necessarily operate in the spatio-temporal domain, while standard ANNs operate only in the spatial domain.

The most popular neuron model for SNNs is the Leaky Integrate-and-Fire model (LIF) Lapicque, 1907; Gerstner et al., 2014. More biogically-plausible neuron models exist, such as Hodgkin et al., 1952; Izhikevich, 2003, but have not yet demonstrated superior performance than the simple LIF model for deep learning applications and are computationally much more expensive.

In the LIF model, similar to biological neurons, the neuron integrates the weighted input spikes into its membrane potential. When the latter reaches its threshold, the neuron fires an output spike and the membrane potential is reset. The membrane potential  $V_i(t)$  of the neuron i in the LIF model is described as:

$$\lambda \frac{\mathrm{d}V_i}{\mathrm{d}t} = -V_i + \sum_j w_{ij} \sum_k \epsilon(t - t_{jk}) \tag{2.2}$$

$$V_i(t) = V_{reset}$$

, if  $V_i(t) \ge v_{th}$  (2.3)

where  $\lambda$  is the membrane time constant,  $w_{ij}$  is the synaptic weight from neuron j to i,  $\varepsilon(.)$  is the synaptic kernel,  $t_{jk}$  is the  $k^{th}$  spike of the input neuron j,  $V_{reset}$  is the reset membrane potential and  $v_{th}$  is the membrane potential threshold. This model describes many types of LIF variants. For instance, in the non-leaky version of the LIF neuron (IF), the membrane potential does not decay over time, and hence remains constant in between spikes. This is obtained by removing the  $-V_i$  and setting  $\lambda$  to 1 in equation 2.2. Moreover, the synapse model is defined by the kernel function  $\varepsilon(.)$ , corresponding to the response of the membrane potential to the presynaptic spike. The synapse can be instantaneous (Dirac kernel function) or continuous (e.g. linear, exponential, or alpha kernel functions), allowing to model various synaptic behaviors. In particular, the combination of LIF neurons with exponential continuous synapses is also called Current-based LIF (Cuba-LIF). Note that other variants exist that are not described by this model, such as the Adaptive LIF (Adapt-LIF) (e.g. in Bellec et al., 2018b; Yin et al., 2021), that uses an adaptive threshold described with temporal dynamics (the threshold is increased after each spike fired and decays exponentially with time).

The inference phase of SNNs is usually discretized in timesteps in order to simulate their spatio-temporal dynamics. Each timestep corresponding to a forward pass in the network, the number of timestep can allow to estimate the future latency of the SNN inference in hardware. In this context, an iterative version of the LIF model (as in Wu et al., 2018) is used, similar to the description of Recurrent Neural Networks (RNNs). A common iterative description of the LIF with an instantaneous synapse in a deep SNN is:

$$V_i^l(t) = \beta V_i^l(t-1) + \sum_j w_{ij} s_j^{l-1}(t) + b_i - v_{th} s_i^l(t-1)$$

(2.4)

$$s_i^l(t) = H[V_i^l(t) - v_{th}] (2.5)$$

$s_i^l(t)$  denotes the output spikes of neuron i from layer l at time t. Spike firing happens when the membrane potential is superior to the threshold  $v_{th}$ , which corresponds to the Heaviside step function H. In this description, the threshold  $v_{th}$  is substracted from the membrane potential after each spike. This corresponds to a "soft" version of the reset (Han et al., 2020b) instead the "hard" version of the reset described in equation 2.2. The parameters of the models are W and b, respectively weights and biases, and the time constant  $\beta$ .

### **Information Encoding With Spikes**

While ANNs use static high precision activations per neuron per inference, SNNs use one or several binary spikes to code the activation. There are several coding strategies based on the spike rate, timing, rank, phase, etc. (for a review see Auge et al., 2021), but the majority of works in deep SNNs use either the spike rate or the spike timing. The rate coding strategy uses several spikes to represent one unit of information while in temporal coding, the information is carried by individual spike times. Note that, in order to be efficient in neuromorphic hardware, the coding strategy should use a minimum number of spikes, as the energy consumption is strongly correlated to the spiking activity. Moreover, the choice of the coding strategy is associated with the learning strategy (see Section 2.2).

The coding strategy must consider both the encoding of the input to the network and the decoding of the output. Indeed, to process real-valued data, such as pixels for images, these values can be converted into spikes in order to be processed by the SNN. Data can also be already in the form of spikes that can be fed directly to the SNN without pre-processing. This is the case for neuromorphic sensors, such as event cameras (Lichtsteiner et al., 2008) or artificial cochleas (Chan et al., 2007). Fig.2.1 represents a typical pixel-to-spike conversion in rate and time. The rate-based strategy matches each pixel intensity with a firing rate, using a probabilistic sampling (generally Poisson) to generate the spike trains: the higher the pixel value, the higher the firing rate of the corresponding input. A simple time-based strategy, also called latency coding, consists in associating the pixel intensity with the latency of a single spike. In that case, the latency is inversely proportional to the pixel intensity: earlier spikes encode higher values and later spikes encode lower values. More recently, Stanojevic et al., 2022 have used a linear latency coding (where the spike time is defined as the difference between a maximum predefined time and the ANN equivalent activation), also preserving this relationship (earlier spikes correspond to higher activations).

Decoding the output in a classification task consists in determining the most activated neuron in the output layer, each neuron being associated with a class. With rate coding, this can be done by using the highest spike rate, or the highest membrane potential value in non-spiking output neurons. With temporal coding, a solution called Time-To-First-Spike (TTFS) consist in using the first spike fired by one of the output neurons.

Temporal codes are supposed to be sparse and can have a lower latency (e.g. when the TTFS decoding is used). However, temporal coding may require high temporal resolution because each spike carries important information, which may be difficult to implement efficiently in neuromorphic hardware.

### 2.1.2 Software and Hardware Implementations

### Off-Chip vs. On-Chip Training

Training of ANNs and SNNs is said "on-chip" or "off-chip", whether the training is performed on the chip that will also be used for the inference, or if the training is performed on a different computer architecture. The advantage of the latter is the possibility to train the networks with high-performance algorithms and computing architecture. However, in this case, the training cannot be performed once the network has been deployed on the chip. On the opposite, on-chip training could not only allow more efficient training of neural networks, but also could allow the system to continue to learn through its life-time using incremental learning techniques (such as Solinas. et al., 2021). Nevertheless, current high performance training algorithms, such as backpropagation, are very costly to implement on chip (Bengio et al., 2016). Therefore, if the system is not meant to be trained on-chip, using off-chip training techniques has allowed to reach the best performance so far. Hence, in the interest of maximizing accuracy and efficiency of SNNs only during the inference phase, off-chip training techniques have been used in this work.

#### **Software Simulations of SNNs**