# Confiance matérielle : solutions de conception de verrouillage numérique

Quang-Linh Nguyen

### ▶ To cite this version:

Quang-Linh Nguyen. Confiance matérielle : solutions de conception de verrouillage numérique. Cryptographie et sécurité [cs.CR]. Université de Montpellier, 2022. Français. NNT : 2022UMONS105 . tel-04336960

## HAL Id: tel-04336960 https://theses.hal.science/tel-04336960

Submitted on 12 Dec 2023  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITE DE MONTPELLIER

En Systèmes Automatiques et Microélectroniques

École doctorale : Information, Structures, Systèmes

Unité de recherche Laboratoire d'Informatique, de Robotique et de Micro-électronique de Montpellier

## CONFIANCE MATÉRIELLE : SOLUTIONS DE CONCEPTION DE VERROUILLAGE NUMÉRIQUE HARDWARE TRUST: DESIGN SOLUTIONS FOR LOGIC LOCKING

## Présentée par Quang-Linh NGUYEN Le 18/05/2022

### Sous la direction de Bruno ROUZEYRE, Marie-Lise FLOTTES et Sophie DUPUIS

### Devant le jury composé de

| Roselyne Chotin, Maîtresse de Conférences, Sorbonne Université, CNRS, LIP6                           | Rapporteur         |

|------------------------------------------------------------------------------------------------------|--------------------|

| Alberto Bosio, Professeur d'université, École Centrale de Lyon, CNRS, INL                            | Rapporteur         |

| Vincent Beroulle, Professeur d'université, LCIS, Univ. Grenoble Alpes, Grenoble INP                  | Président          |

| Sophie Dupuis, Maîtresse de Conf <mark>érences, LIRMM, Université de M</mark> ontpellier, CNRS       | Co-Encadrante      |

| Marie-Lise FLottes, Chargée de r <mark>echerche CNRS, LIRMM, Univers</mark> ité de Montpellier, CNRS | Co-Encadrante      |

| Bruno Rouzeyre, Professeur d'université, LIRMM, Université de Montpellier, CNRS                      | Directeur de thèse |

## Abstract

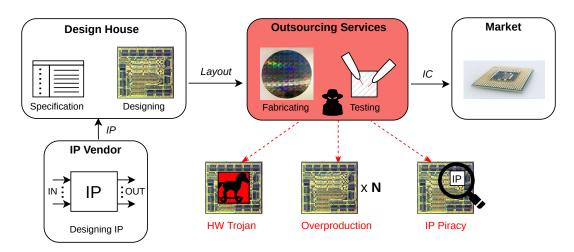

In the globalized semiconductor supply chain, increasing outsourcing to external contractors, e.g., offshore foundry, results in possible exposure of hardware designs to adversaries. Consequently, security threats such as integrated circuit (IC) overproduction, intellectual property (IP) piracy and hardware Trojans have emerged, which poses a serious impact on the technology industry as well as the national security. Logic locking is a holistic Designfor-Trust method that can address those issues. By inserting key-controlled logic, logic locking allows locking the circuit functionality with a key only known by the IP/IC owner. The requirements for logic locking are to secure the logic locking key as well as effectively disrupting the circuit functionality. The security of logic locking is greatly challenged by oracle-guided attacks, notably the SAT attack. The attack is based on SAT solver and takes advantages of open scan chain access. Ensuring functionality disruption necessitates sufficient corruption at outputs, which is influenced by the insertion strategy of key-controlled logic. In this thesis, we develop secure and effective logic locking schemes, by focusing on three aspects, insertion strategy, SAT-secure logic lock and scan chain protection. For optimizing output corruption, we propose a key-gate insertion strategy called KIP. Based on signal probability analysis, the strategy selects nodes where corruption at such location is highly observable at multiple outputs. Furthermore, we propose a secure logic locking technique called SKG-Lock. It consist of inserting socalled switchable key-gates that are controlled by a switch controller. The technique provides provable SAT resilience and significant output corruption, especially when using KIP for insertion. Finally, we propose a scan controller for protecting logic locking against oracle-guided attacks. The scan controller introduces a key-based authentication mechanism, thus, prevents unauthorized access to the scan chains once the IC is deployed in the field.

iii

Des menaces de sécurité telles que la surproduction de circuits intégrés (IC), le piratage de la propriété intellectuelle (IP) ou l'insertion de chevaux de Troie matériels sont apparues dues à l'externalisation de certaines phases de conception / production auprès de sous-traitants externes, par exemple une fonderie offshore. Le verrouillage logique ou Logic Locking est une méthode de conception permettant de contrecarrer de telles menaces. Il consiste à insérer une logique contrôlée par une clé connue uniquement du propriétaire du circuit et activée en retour de fabrication par celui-ci. L'utilisation de tout autre clef conduit à un dysfonctionnement du circuit. Toutefois, la sécurité apportée par le verrouillage logique a été fortement remise en cause par l'apparition d'attaques dites guidées par oracle, notamment l'attaque SAT. Celle-ci est basée sur l'utilisation d'un solveur SAT et tire parti de l'accès aux chaines de scan nécessaires à un test efficace du circuit. Garantir un dysfonctionnement suffisant pour que le circuit soit inemployable avec une mauvaise clef nécessite une corruption suffisante au niveau des sorties, qui est elle-même influencée par la stratégie d'insertion de la logique contrôlée par la clé. Dans cette thèse, nous développons des schémas de verrouillage logique sécurisés et efficaces, en nous concentrant sur trois aspects, la stratégie d'insertion, le verrouillage logique sécurisé SAT et la protection de la chaîne de scan. Pour optimiser la corruption de sortie, nous proposons une stratégie d'insertion de porte-clés appelée KIP. Sur la base d'une analyse de probabilité de signal, la stratégie sélectionne les nœuds où la corruption influence un grand nombre de sorties. De plus, nous proposons une technique de verrouillage logique sécurisée appelée SKG-Lock. Elle consiste à insérer des porte-clés dits commutables qui sont contrôlés par un contrôleur de commutations. Cette technique offre une résistance aux attaques SAT et une corruption de sortie importante, en particulier lorsque la stratégie KIP est utilisée. Enfin, nous proposons un contrôleur de chaines de scan pour protéger le verrouillage logique contre les attaques guidées par oracle. Le contrôleur de balayage implante un mécanisme d'authentification basé sur une clé, empêchant ainsi tout accès non autorisé aux chaînes de scan.

## Résumé

### Introduction

Le modèle économique de l'industrie des semi-conducteurs est actuellement majoritairement un modèle d'externalisation. Les coûts de fabrication étant devenus prohibitifs, l'externalisation du processus de fabrication vers des fonderies étrangères est devenue une tendance majeure. Ceci conduit à une exposition accrue de la propriété intellectuelle de la conception du matériel à des acteurs externes, potentiellement non fiables. En outre, les techniques de rétro-ingénierie matérielle sont devenues plus avancées, ce qui facilite la tâche des adversaires. En raison de la perte de contrôle sur l'utilisation de la propriété intellectuelle et de la multiplication des adversaires potentiels dans cette chaîne d'approvisionnement mondialisée, la surproduction de circuits intégrés, le piratage de la propriété intellectuelle et l'insertion de chevaux de Troie *matériels* sont devenus des sources majeures de préoccupation en matière de cyber sécurité [1]–[3]. Ces menaces ont un impact sérieux sur l'industrie des semi-conducteurs ainsi que sur la sécurité nationale, car des secteurs critiques tels que l'armée et l'aérospatiale reposent fortement sur l'électronique [4]–[6]. Par conséquent, des méthodes préventives, appelées Design-for-Trust (conception pour la confiance), sont d'une importance capitale pour regagner la confiance dans la conception des circuits intégrés.

De nombreuses approches récentes de *Design-for-Trust* introduisent des mécanismes préventifs au moment de la conception [7] : les techniques de prévention des chevaux de Troie matériels améliorent la détectabilité des chevaux de Troie, empêchent l'insertion de chevaux de Troie ou contournent les cœurs infectés par des chevaux de Troie [8] ; le *watermarking* et le *fingerprinting* démontrent la conformité de la propriété intellectuelle [9] ; le *metering* permet d'identifier les circuits intégrés fabriqués [10] ; le *camouflaging* empêche la rétro-ingénierie [11], [12] ; enfin, le verrouillage numérique, ou *Logic Locking*, permet de «verrouiller» la fonctionnalité d'un circuit avec une clé secrète, connue uniquement du propriétaire de la propriété intellectuelle [13]–[15].

### Verrouillage Numérique

Le verrouillage numérique insère de la logique combinatoire dans un circuit, contrôlée par des entrées de clé supplémentaires. Il a plusieurs vertus par rapport aux autres solutions de conception pour la confiance. Il permet de

lutter contre le piratage de la propriété intellectuelle puisque le circuit extrait des outils de rétro-ingénierie n'est pas un circuit fonctionnel. Il fournit au concepteur un contrôle post-fabrication sur les circuits intégrés afin d'éviter la surproduction, puisque seul le bureau d'études ou un partenaire autorisé peut déverrouiller la fonctionnalité des circuits intégrés verrouillés. Parmi les solutions de Design-for-Trust, le verrouillage numérique offre la protection la plus polyvalente. Il suppose que seul le concepteur, c'est-à-dire le bureau d'études ou le propriétaire de la propriété intellectuelle, est digne de confiance. Par contre, tous les acteurs de toutes les étapes ultérieures dans le flot de production de circuits intégrés sont de potentiels adversaires. En résumé, le verrouillage numérique peut être déployé sur un cœur de propriété intellectuelle, pour prévenir de son utilisation non légale, ou sur un circuit en conception, pour empêcher la surproduction par une fonderie ; tout en empêchant la rétro-ingénierie, et l'insertion de chevaux de Troie.

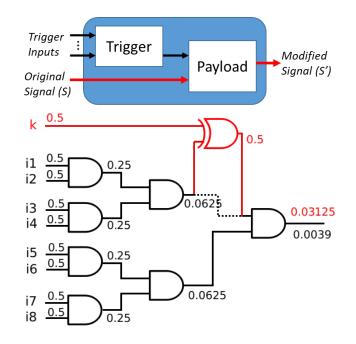

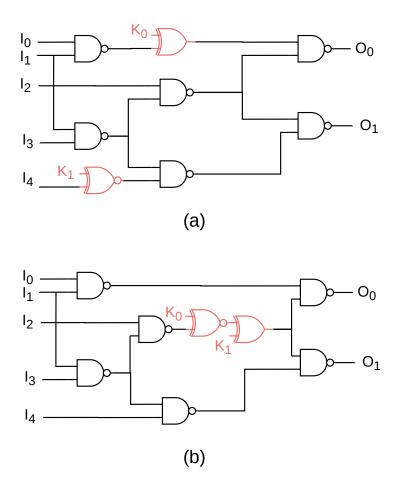

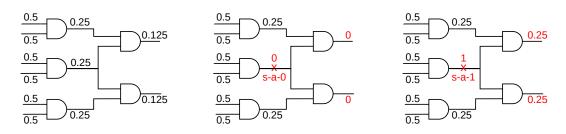

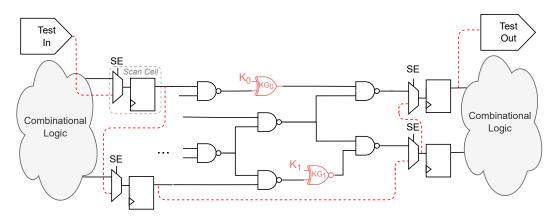

Un moyen simple mais efficace de verrouiller la fonctionnalité d'un circuit consiste à insérer des «portes-clé», i.e., des portes logiques, par exemple XOR/XNOR, contrôlées par une entrée de clé. Le signal sur lequel une porte est insérée sera corrompu si une clé incorrecte est appliquée à son entrée. Ensuite, l'erreur se propagera et provoquera potentiellement de la corruption aux sorties du circuit. Avec une clé incorrecte, une corruption de sortie significative est souhaitable de sorte que le circuit verrouillé soit inutilisable. La stratégie d'insertion de la porte a donc son importance, puisqu'elle a un impact direct sur la corruption de la sortie.

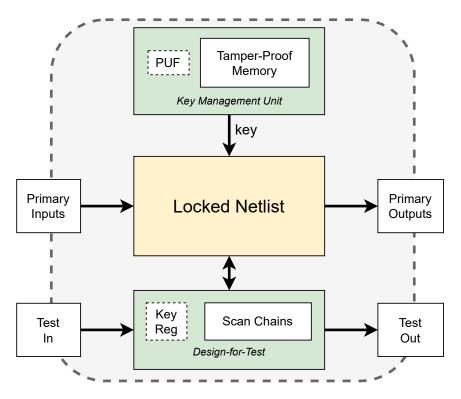

Une conception à verrouillage numérique contient également une unité de gestion des clés et une structure de conception pour le test (*Design for Test -* DfT). L'unité de gestion des clés, qui comprend généralement une mémoire inviolable, est chargée de stocker et de délivrer la clé aux entrées de clé du circuit verrouillé. La structure DfT, qui comprend généralement comprend des chaînes de scan (registres à décalage), vise à faciliter les tests post-silicium.

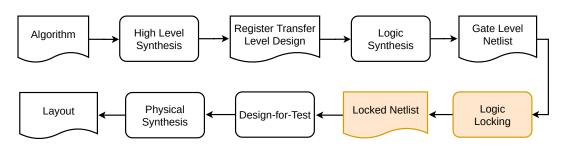

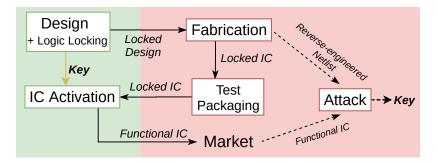

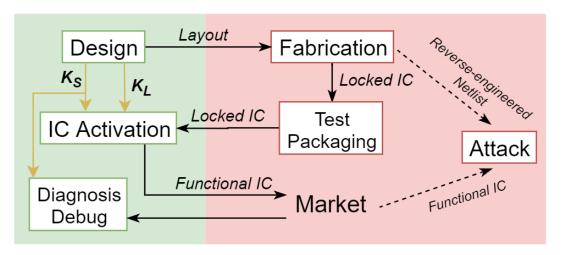

Dans le flux de conception d'un circuit intégré, le verrouillage logique peut être appliqué au niveau netlist, i.e. sur la description du circuit en interconnexions de portes logiques, qui est obtenue après l'étape de synthèse logique. La netlist résultante, appelée *netlist verrouillée*, peut ensuite être transformée en description physique – layout - par synthèse physique. Pour la fabrication du circuit intégré, la description physique verrouillée peut être envoyée à des installations offshore, pour la fabrication, le test et la mise en puce – packaging. La fonderie fabrique les puces de silicium à partir de la vue physique verrouillée. Par conséquent, les tests sont effectués avant l'activation des circuits intégrés, c'est-à-dire sur les circuits intégrés verrouillés. Cela est possible car le test de fabrication, qui est essentiellement un test structurel, peut être effectué indépendamment de la fonctionnalité du circuit. Après la fabrication, le test et le packaging, les circuits intégrés sont déverrouillés avant d'être disponibles à l'achat. L'activation des circuits intégrés consiste à programmer la clé de verrouillage logique dans la mémoire inviolable du circuit intégré. Cette opération peut être effectuée en interne lorsque les puces sont renvoyées au bureau d'études, ou à distance chez un tiers de confiance.

### Les vulnérabilités du verrouillage numérique

Le modèle de menace pour le verrouillage logique suppose que les attaquants de la chaîne d'approvisionnement peuvent obtenir la netlist du circuit verrouillé et/ou un oracle. Une fonderie non fiable peut en effet effectuer une rétro-ingénierie du de la vue physique verrouillée pour obtenir la netlist verrouillée. Un attaquant peut également obtenir la netlist verrouillée en négociant avec la fonderie ou en procédant à la rétro-ingénierie d'un circuit intégré. Les circuits intégrés prêts à l'emploi, c'est-à-dire les circuits intégrés non verrouillés, notamment pour l'électronique grand public, peuvent être achetés sur le marché et accessibles à tous. Un circuit intégré non verrouillé fournit les paires d'entrée-sortie correctes et peut donc être utilisé comme oracle lors d'une attaque. Le scénario d'attaque dans lequel l'attaquant possède la netlist verrouillée et un circuit intégré déverrouillé est appelé attaque guidée par un oracle. D'autre part, les produits électroniques fabriqués sur mesure pour certains secteurs critiques tels que l'armée ou l'aérospatiale peuvent ne pas être disponibles à la vente pour les consommateurs. Le scénario d'attaque dans lequel l'attaquant possède uniquement la netlist verrouillée est appelé attaque sans oracle.

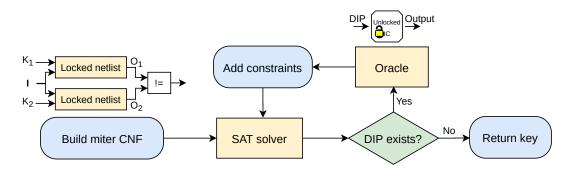

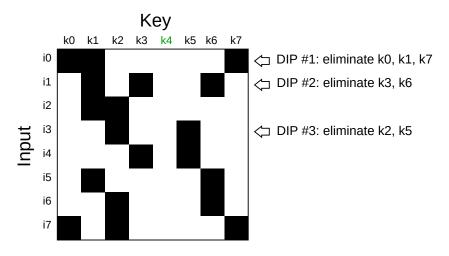

Le tournant de la recherche sur le verrouillage numérique a été l'introduction de l'attaque dite *SAT* [16], qui présente la technique d'attaque guidée par un oracle la plus puissante, capable de casser toutes les défenses précédentes. À chaque itération, cette attaque trouve un vecteur d'entrée distinctif (*Differential Input Pattern* - DIP) qui donne des sorties différentes pour deux valeurs de clés différentes. La principale force de l'attaque SAT repose sur deux facteurs importants :

- (i) la capacité d'éliminer une grande quantité de clés erronées pour chaque DIP,

- (ii) la possibilité de cibler n'importe quelle partie combinatoire du circuit grâce à l'accès aux chaînes de scan.

La première génération de techniques de verrouillage numérique résistantes à l'attaque SAT [17], [18] vise à réduire le nombre de fausses clés pouvant être éliminées par chaque DIP. Cependant, ce résultat est obtenu grâce à un compromis sur la corruption des sorties.

### Contributions

La sécurité du verrouillage numérique est mise en péril par les attaques guidées par un oracle, notamment les attaques basées sur des solveurs SAT. De plus, un verrouillage numérique efficace doit fournir une corruption des sorties suffisante. Dans cette thèse, nous avons pour objectif de proposer des méthodes de verrouillage numérique à la fois *sûres* et *efficaces*. Les contributions de cette thèse sont au nombre de trois :

- (i) KIP: une stratégie d'insertion de portes-clé optimisée pour la corruption des sorties, basée sur l'analyse de l'impact des portes-clé sur la probabilité des sorties du circuit ;

- (ii) SKG-Lock: une technique de verrouillage numérique efficace et sécurisée contre les attaques SAT qui permet de contrôler la commutation des portes-clé;

- (iii) Scan controller: une solution de chaîne de scan sécurisée pour la prévention des attaques guidées par un oracle, qui empêche l'accès non autorisé aux chaînes de scan.

## État de l'art

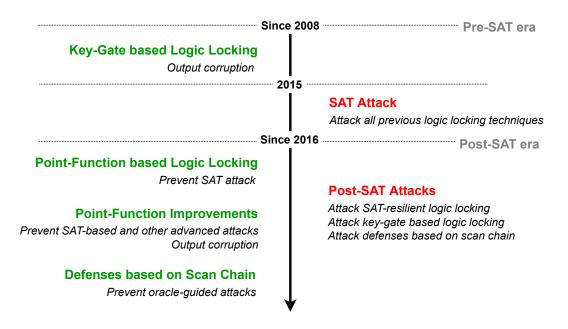

Depuis 2008, la recherche sur le verrouillage numérique s'est développée de manière prolifique, suivant un jeu du chat et de la souris entre les défenses et les attaques. Comme l'introduction de « l'attaque SAT » a eu un impact durable sur la recherche sur le verrouillage numérique, la chronologie peut être considérée possédant deux ères : l'ère pré-SAT et l'ère post-SAT.

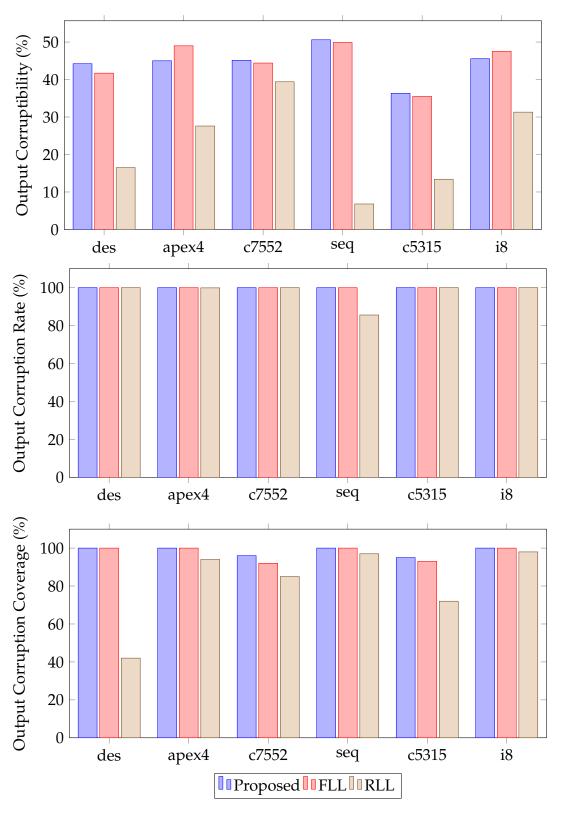

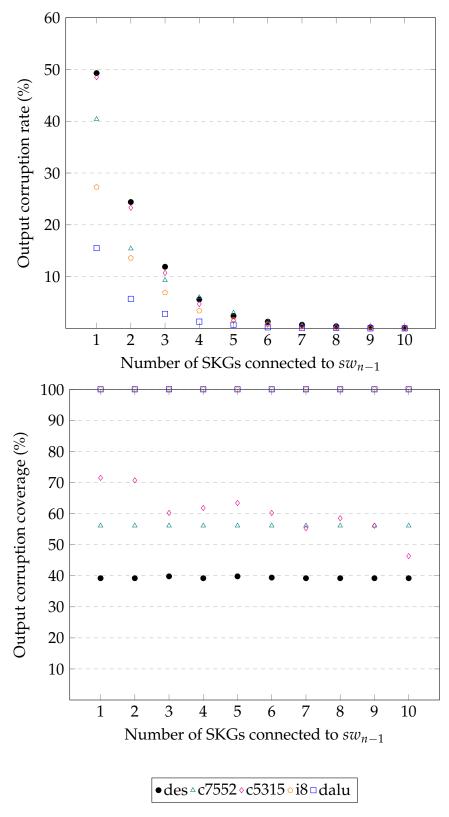

Dans l'ère pré-SAT, les techniques de verrouillage numériques étaient basées sur l'insertion de portes-clé. La corruption de la sortie était l'objectif le plus important de ces techniques. La corruption des sorties peut être caractérisée par les métriques suivantes : le *taux de corruption des sorties* présente la probabilité d'observer un ou plusieurs bits erronés au niveau du vecteur de sorties d'un circuit verrouillé ; la *couverture de la corruption des sorties* présente l'ampleur de la corruption propagée aux sorties du circuit i.e. le nombre de bits de sorties erronés cumulés; la *corruptibilité des sorties* présente la probabilité d'observer un ou plusieurs bits erronés au niveau du vecteur de sortie d'un circuit verrouillé. Le verrouillage numérique dit «basé sur les fautes» (*Fault based Logic Locking -* FLL) [19], [20] fournit la stratégie d'insertion de porte-clés la plus efficace en termes de corruption de sorties. Pour insérer chaque porte-clé, cette méthode trouve le signal ayant le plus fort impact sur les fautes, une métrique basée sur la simulation de fautes.

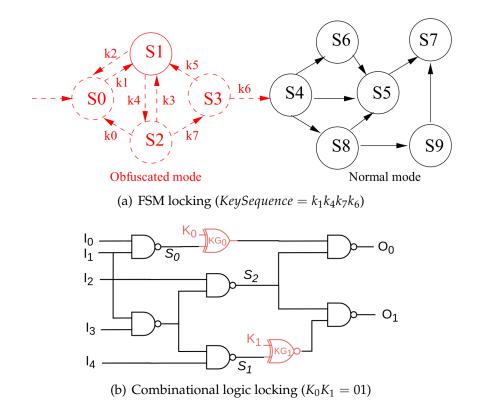

L'attaque SAT a été capable de briser toutes les techniques basées sur les portes-clé lorsqu'elle a été introduite pour la première fois. L'attaque est basée sur un solveur SAT (satisfaisabilité booléenne). À chaque itération, il trouve un DIP, qui est ensuite appliqué à l'oracle. La réponse correcte obtenue est ajoutée à la formule du solveur en tant que nouvelle contrainte, ce qui permet d'éliminer une partie de l'espace de recherche des clés pour l'itération suivante. Progressivement, jusqu'à ce que plus aucun DIP ne puisse

être trouvé, l'attaque élimine des valeurs de clé jusqu'à déduire la clé correcte. Les circuits séquentiels ne sont sensibles à cette attaque que lorsque *les chaînes de scan sont accessibles* à l'attaquant.

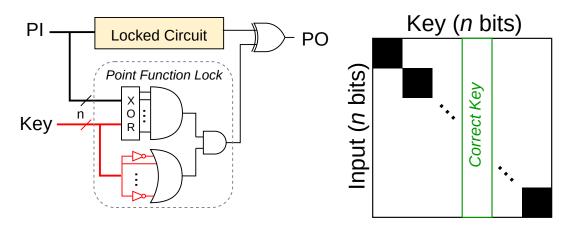

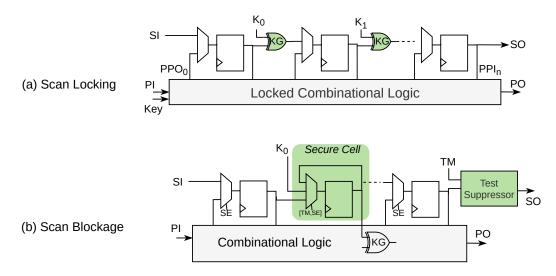

Dans l'ère post-SAT, la résilience aux attaques SAT devient une nécessité pour le verrouillage logique. Deux directions vers la résilience aux attaques et la corruption de sortie pour le schéma de verrouillage logique ont été développées. La première direction est d'augmenter drastiquement le temps de calcul de l'attaque. Le verrouillage crypté [21], [22] empêche l'attaque SAT en augmentant de manière exponentielle le temps d'exécution de chaque itération mais est très coûteux et attaquable par d'autres types d'attaques. Le verrouillage numérique basé sur une fonction «1-point» [17], [18] a été la première contre-mesure contre l'attaque SAT dont la sécurité est prouvée. Il consiste à insérer un verrou avec une fonction «1-point» dans le circuit. Pour chaque valeur d'entrée, ce verrou n'altère les sorties du circuit que pour une valeur de clé. Par conséquent, toutes les valeurs d'entrée sont des DIP ne pouvant éliminer qu'une valeur de clé unique, que l'attaque SAT doit donc parcourir exhaustivement pour exclure toutes les valeurs de clé incorrectes. Cependant, pour ce type de technique, la corruption de la sortie est fortement compromise. Les techniques les plus récentes de verrouillage logique, dans la même mouvance que les travaux développés dans cette thèse, commencent permettre de créer des protections qui résistent aux attaques SAT, tout en augmentant la corruptibilité [23]–[26]. Une autre direction est celle des défenses basées sur la protection des chaînes de scan, qui peuvent empêcher non seulement l'attaque SAT mais aussi d'autres attaques guidées par oracle. Les techniques existantes comprennent le verrouillage des chaînes de scan [27], [28], le blocage des chaînes de scan [29]–[31] et le contrôle des chaînes de scan [32], [33].

Du côté offensif, des attaques ont également été proposées pour évaluer la sécurité des défenses récentes. Grâce à son efficacité, l'attaque SAT a été la base de diverses attaques suivantes. Les attaques SAT guidées par oracle [34]–[37] peuvent inclure des étapes ou des contraintes supplémentaires, ou utiliser un solveur plus polyvalent. Les attaques sans oracle visent à supprimer la logique de protection insérée pour récupérer la netlist originale [38], [39] ou à analyser la structure du circuit pour deviner la valeur de la clé [40], [41].

## Stratégie d'insertion de portes-clé pour un verrouillage numérique efficace

Cette contribution est une stratégie évolutive d'insertion de porte-clés basée sur l'analyse de probabilité (KIP) qui est optimisée pour les métriques de corruption des sorties. Le principe de la stratégie proposée est de classer chaque signal d'un circuit en fonction d'une métrique appelée *score de corruption de sortie*. Pour chaque signal, cette métrique reflète l'impact sur les sorties si le signal est corrompu à cause d'une porte-clé insérée. Comme pour FLL, cette stratégie émule la corruption en insérant des fautes de collage à ce signal. L'impact d'une faute donnée sur les sorties est mesuré en enregistrant la différence de probabilité des sorties de valoir 1/0 avec et sans la faute. Par conséquent, le score de corruption des sorties est obtenu comme le produit de la différence de probabilité totale et du nombre de sorties impactées. L'insertion de portesclé sur les signaux ayant un score élevé aura un impact sur la plupart des sorties pour la plupart des valeurs d'entrée, ce qui entraîne une couverture de corruption de sortie et un taux de corruption élevés.

L'algorithme de KIP comprend deux étapes, le classement des signaux et la sélection des signaux sur lesquels insérer une porte-clé. Le score de corruption de sortie de chaque signal est calculé et les signaux sont classés en fonction de leur score dans un ordre décroissant. Ensuite, la sélection des signaux commence par le signal ayant le score le plus élevé. Ici, un critère supplémentaire est appliqué : un seul signal est choisi parmi les signaux ayant le même score, afin d'éviter les séries de portes-clé. Le temps d'exécution de la stratégie KIP est essentiellement l'étape de classement des signaux. Par rapport à FLL, KIP ne classe les nœuds qu'une seule fois, alors que FLL refait le classement à chaque fois qu'une porte-clé est insérée.

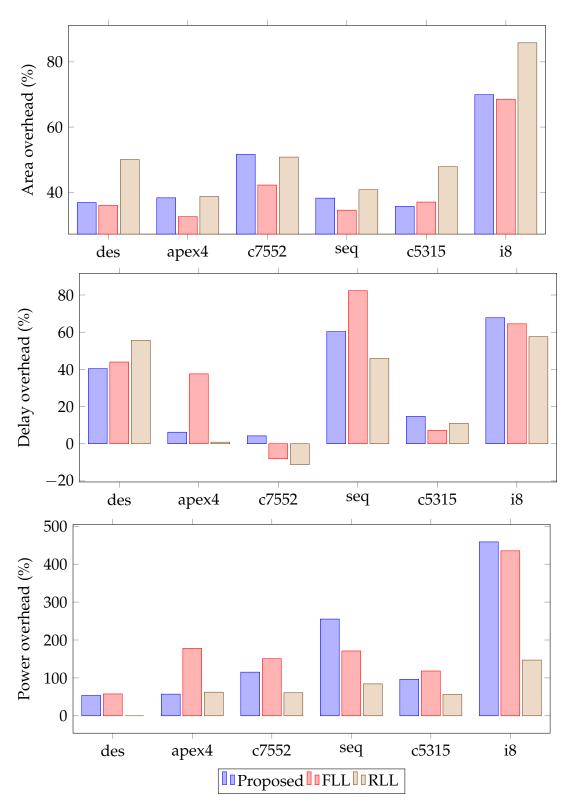

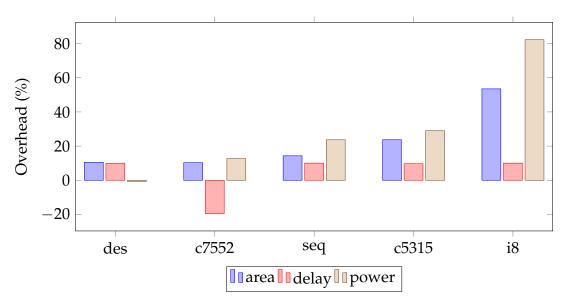

Effectué avec l'insertion d'une porte-clé XOR, KIP obtient des résultats optimaux dans toutes les métriques de corruption de sortie ; un taux de corruption de sortie de 100%, une couverture de corruption de sortie de 100% et une corruptibilité de sortie de 50% sont obtenus dans plusieurs circuits. KIP est plus évolutif que FLL en termes de temps d'exécution ; par exemple, avec le circuit c7552, la stratégie KIP s'est terminée en 10 minutes, alors que l'algorithme FLL prend 2 heures pour le même circuit.

## Un verrouillage numérique sécurisé et efficace grâce à des portes-clé commutables

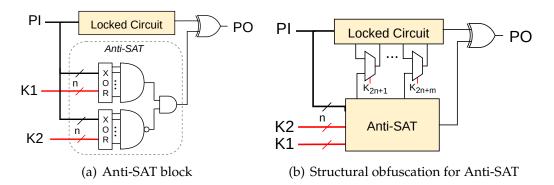

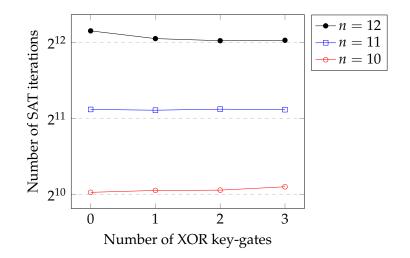

Cette seconde contribution est une nouvelle technique de verrouillage numérique sécurisé, appelée *SKG-Lock*, qui vise à contrecarrer les attaques basées sur un solveur SAT, tout en maintenant une corruption de sortie significative.

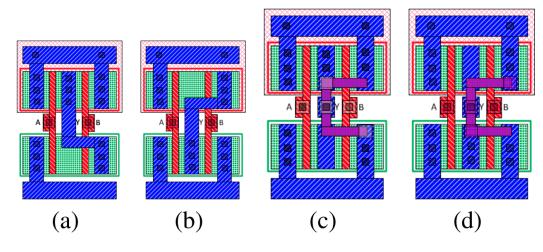

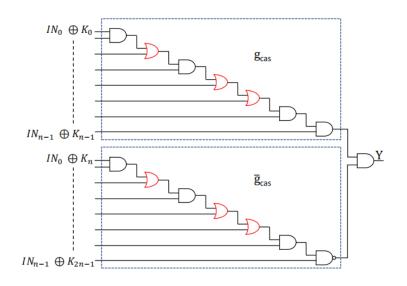

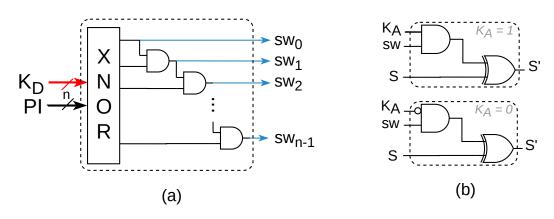

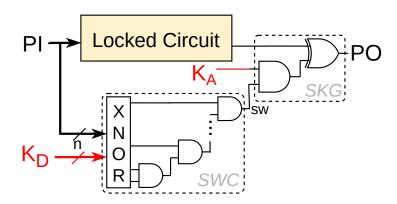

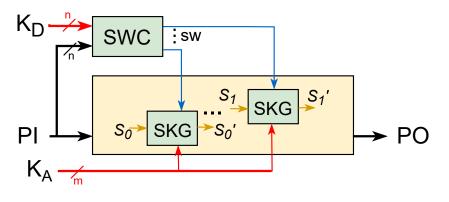

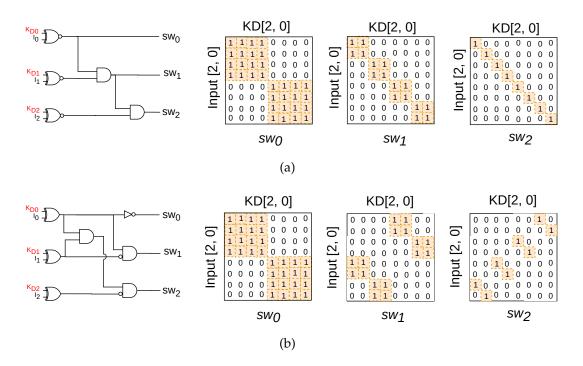

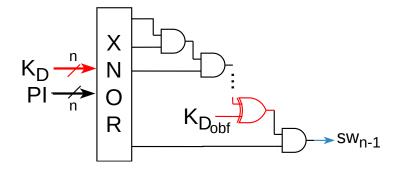

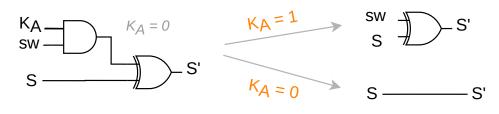

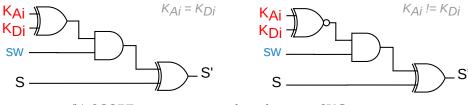

Les deux composants fondamentaux de SKG-Lock sont des portes-clé commutables (*Switchable key-gates* - SKGs) et un contrôleur de commutation (*Switch controller* - SWC). Les portes-clé commutables possèdent trois entrées, deux signaux de commande — une entrée de la clé  $K_A$  et un signal de commutation sw — et un signal S provenant du circuit verrouillé. Le contrôleur de commutation contrôle les signaux de commutation des portes-clé commutables. Une conception générale pour un contrôleur de commutation est un comparateur entre l'entrée clé  $K_D$  et les entrées du circuit, construit avec une rangée de portes XNOR et une cascade de portes AND. Cette structure du contrôleur de commutation produit des signaux de commutation, chacun provenant de chaque nœud de la cascade AND, c'est-à-dire que chacun a une corruptibilité différente.

Deux ensembles d'entrées de clé, la clé d'activation (*Activation key* -  $K_A$ ) et la clé de leurre (*Decoy key* -  $K_D$ ) sont introduits :  $K_A$  est connectée aux portes-clé commutables ;  $K_D$  est connectée au contrôleur de commutation. Elles proviennent toutes deux d'une mémoire inviolable. Bien que le circuit soit déverrouillé en insérant la bonne valeur de clé  $K_A$  pour chaque SKG, la valeur de clé  $K_D$  est importante pour obtenir la résilience contre les attaques SAT.

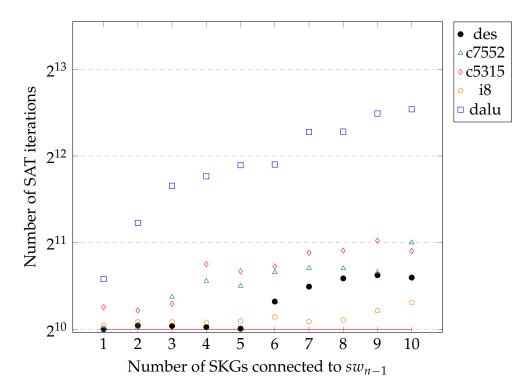

La structure proposée de SKG-Lock consiste à insérer plusieurs portes-clé commutables contrôlées par différents signaux de commutation, chacun ayant une corruptibilité différente. Le signal de commutation ayant la corruptibilité la plus faible est la sortie d'une fonction 1-point entre  $K_D$  et les entrées primaires, qui génère une complexité maximale pour l'attaque SAT. L'utilisation d'autres signaux de commutation avec des corruptibilités plus élevées permet d'augmenter la corruption des sorties de l'ensemble du système. La stratégie KIP est utilisée pour l'insertion des portes-clé commutables afin d'optimiser davantage la corruption des sorties. L'utilisation de plusieurs signaux de commutation et de plusieurs portes-clé commutables crée des connexions multiples, c'est-à-dire une intrication structurelle, entre le contrôleur de commutation et le circuit verrouillé.

Nous proposons l'analyse la sécurité de SKG-Lock contre diverses attaques. La résilience maximale contre l'attaque SAT est obtenue tant qu'il y a au moins une porte-clé commutable contrôlée par le signal de commutation de moindre corruptibilité, indépendamment des autres portes-clé commutables insérées avec une corruptibilité plus élevée. L'utilisation de plusieurs portes-clé commutables avec des corruptibilités différentes empêche d'autres attaques basées sur des solveurs SAT, comme l'attaque approximée App-SAT [34] et l'attaque Bypass [35]. Des contre-mesures contre des attaques potentielles sans oracle [38], [41] contre SKG-Lock peuvent être incorporées avec des modifications structurelles : des portes-clé supplémentaires pour « cacher » le contrôleur de commutation, ce qui permet de ne pas avoir des signaux « reconnaissables » avec une très faible probabilité de commutation ; des portes-clé commutables modifiées, déverrouillables avec un bit de  $K_A$  et un bit de  $K_D$ . Notez que ces modifications structurelles n'ont pas d'impact sur la résilience de SKG-Lock contre les attaques SAT.

Un verrou à fonction 1-point peut être recréé avec un contrôleur de commutation et une seule porte-clé commutable contrôlée par le signal de commutation de moindre corruptibilité. Cette option «légère» de SKG-Lock atteint le même niveau de résilience SAT tout en nécessitant un surcout en aire deux fois moindre par rapport aux verrouillages numériques à fonctions 1-point connus [17], [18].

Comparé aux techniques résilientes contre les attaques SAT [17], [18], [24], [26], SKG-Lock fournit une corruption de sortie significativement plus élevée et une meilleure résilience contre les attaques. L'évaluation du surcout en aire montre que SKG-Lock a un surcout acceptable sur de petits circuits. Notez que ce surcout est proportionnel à la taille des clés, et indépendant de celle du circuit à verrouiller. Donc le surcout est moindre pour de plus gros circuits.

## Contrôleur de chaîne de scan pour protéger le verrouillage numérique contre les attaques guidées par un oracle

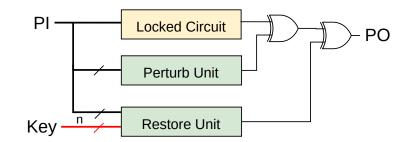

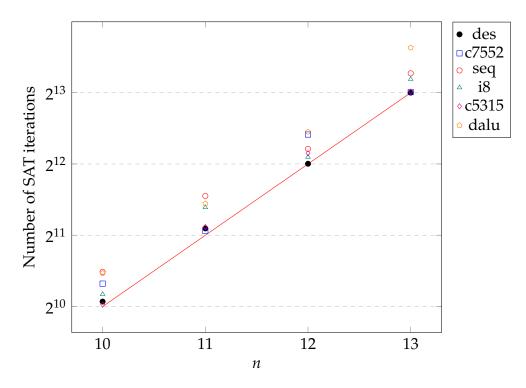

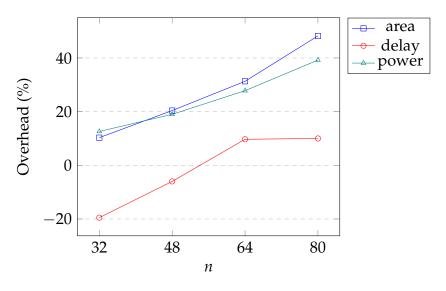

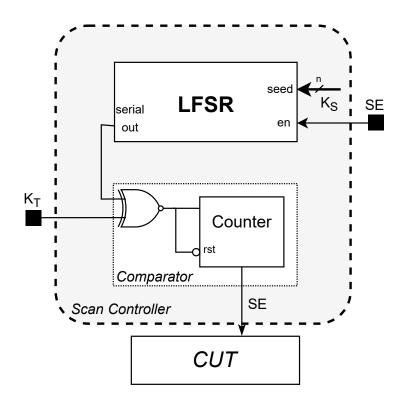

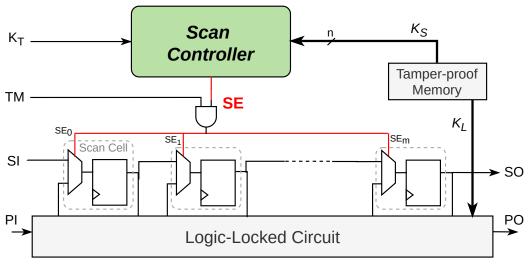

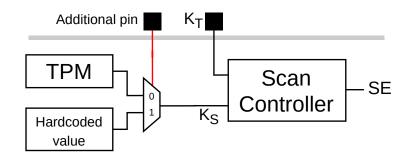

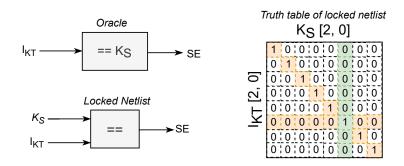

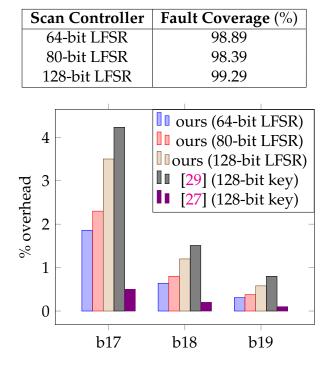

Cette contribution est un contrôleur de chaîne de scan qui limite l'accès aux chaînes de scan aux seuls utilisateurs autorisés. L'idée principale de la solution proposée est d'utiliser une authentification basée sur une clé (*Scan Access Key* –  $K_S$ ) pour contrôler les opérations de décalage servant au contrôle/«remplissage» (*shift-in*) et à l'observation (*shift-out*) des chaînes de scan. Le contrôleur de chaîne de scan contient un registre à décalage à rétroaction linéaire (*linear feedback shift register* - LFSR) de n bits et un comparateur. La valeur de KS, stockée dans une mémoire inviolable, est la «graine» du LFSR. Le contrôleur de chaîne de scan "verrouille" le signal d'activation de la chaîne de scan (*scan enable* - SE) en le mettant à "0". SE n'est mis à "1" que lors de l'insertion continue d'une séquence correcte via la broche supplémentaire  $K_T$  de la clé de test. Le flux de bits  $K_T$  correct doit correspondre à la sortie du LFSR, qui dépend de  $K_S$ .

Dans le flot de conception, le contrôleur de chaîne de scan est inséré pendant l'insertion du DfT. Pendant le test de fabrication, pour permettre l'accès aux chaînes de scan sans partager la valeur secrète  $K_S$ , une valeur codée en dur est utilisée comme valeur temporaire de  $K_S$  pendant le test et cette valeur peut être partagée avec le testeur. Une broche supplémentaire utilisée pour permettre cette option est ensuite supprimée après le processus de packaging. Ensuite,  $K_S$ , ainsi que la clé de verrouillage numérique, sont programmées dans la mémoire inviolable pendant la phase d'activation du circuit intégré. Pour le débogage et l'analyse des défaillances, un testeur autorisé qui obtient  $K_S$  et la structure du LFSR peut construire un modèle équivalent du LFSR pour générer le flux de bits  $K_T$  requis qui active les chaînes de scan.

Le schéma de verrouillage numérique proposé, composé d'une protection à deux couches basée sur le contrôleur de chaînes de scan et la technique d'insertion de portes-clé utilisant la stratégie KIP, est très efficace et sécurisé contre de nombreuses attaques.

xii

Le contrôleur de chaînes de scan proposé bloque les opérations de décalage dans les chaînes de scan effectuées par les attaquants, ce qui empêche la mise en œuvre de puissantes attaques guidées par oracle qui nécessitent un accès aux chaînes de scan [16], [34], [36]. Par exemple, l'attaque SAT nécessite de contrôler et d'observer respectivement les entrées et les sorties de la partie combinatoire attaquée. Dans ce cas, l'attaquant ne peut appliquer aucun DIP généré aux entrées de la partie combinatoire, et il ne peut pas non plus lire la réponse correcte pour l'élimination de la mauvaise clé. Par conséquent, l'attaque ne peut pas être mise en œuvre.

En adaptant le modèle de menace du verrouillage numérique, nous avons identifié des schémas d'attaque potentiels sur le contrôleur de chaînes de scan. Grâce au mécanisme basé sur un comparateur, les attaques qui visent à deviner la clé d'accès aux chaînes de scan ne peuvent pas être plus efficaces que la force brute. La suppression et le contournement potentiels du contrôleur de chaînes de scan peuvent être détectés. La solution est testable, facile à intégrer et supporte des tests complets. En outre, elle présente un faible surcoût par rapport aux défenses basées sur les chaînes de scan.

## Conclusion

Les exigences du verrouillage numérique sont de sécuriser la clé de verrouillage et de perturber efficacement la fonctionnalité du circuit verrouillé. Pour assurer la perturbation de la fonctionnalité, il faut une corruption suffisante des sorties, qui est influencée par la stratégie d'insertion de la logique contrôlée par la clé. Pour évaluer la sécurité du verrouillage numérique, de nombreuses attaques ont été développées. L'attaque SAT a introduit la méthode d'attaque la plus efficace, basée sur la satisfiabilité booléenne et guidée par un oracle. L'utilisation d'un solveur SAT permet de distinguer rapidement la bonne clé de celles qui ne le sont pas, de sorte que chaque itération du processus d'attaque peut éliminer un grand nombre de clés erronées. En outre, l'attaque tire parti des chaînes de scan dans l'oracle pour cibler directement chaque partie combinatoire verrouillée, ce qui rend l'attaque faisable en un temps restreint. Par conséquent, une forte résistance contre l'attaque SAT a été une priorité pour les techniques de verrouillage numériques sécurisées. Les techniques existantes basées sur les fonctions 1-point sont manifestement protégées contre l'attaque SAT, mais au prix d'une corruption minimale des sorties. De plus, non seulement l'attaque SAT, mais d'autres attaques guidées par un oracle, exploitent également les chaînes de scan de l'oracle. Dans cette thèse, nous identifions trois aspects pour développer un verrouillage numérique sûr et efficace, à savoir la stratégie d'insertion des portes-clé, le verrouillage numérique sécurisé contre les attaques SAT et la protection des chaînes de scan. Finalement, les contributions de cette thèse construisent deux schémas de verrouillage numérique :

- (i) SKG-Lock + KIP : ce schéma consiste en l'utilisation de la protection SKG-Lock basée sur la stratégie KIP pour l'insertion des portes-clé commutables. Il s'agit d'une technique de verrouillage numérique générique qui peut être utilisée dans tous les cas par n'importe quel défenseur. Elle fournit une sécurité prouvable contre les attaques SAT ainsi qu'une grande résilience contre d'autres attaques efficaces guidées par un oracle ou sans oracle. Cependant, l'utilisation d'une structure de fonction 1-point peut laisser une vulnérabilité structurelle. Ce schéma montre des résultats significatifs à la fois dans le taux de corruption des sorties et la couverture de corruption. Le surcoût en surface est raisonnable.

- (ii) KIP + Scan Controller : ce schéma consiste en une protection à deux couches, l'insertion de portes-clé XOR avec la stratégie KIP pour le verrouillage du circuit et un contrôleur de chaînes de scan pour la protection des chaînes de scan. Il convient dans les cas où les manipulations dans l'insertion DfT et la génération de test sont autorisées. Une protection complète contre les attaques guidées par oracle est réalisée. Cependant, le schéma peut encore être vulnérable aux attaques potentielles sans oracle. La technique des portes-clés utilisant la stratégie KIP fournit une corruption de sortie très élevée. Le surcoût des portes-clé insérées dans le circuit protégé est faible. Le contrôleur de chaînes de scan ajoute un surcoût matériel acceptable à l'infrastructure DfT du circuit. Il entraîne également une surcharge dans le temps de test.

Chaque schéma présente une direction différente vers un verrouillage logique sûr et efficace, avec des avantages différents. Nous avons également identifié les points clés à améliorer dans les solutions proposées.

# Acknowledgements

I would like to express my sincere gratitude to my supervisors, Sophie Dupuis, Marie-Lise Flottes and Bruno Rouzeyre. I am grateful for their guidance, support and patience. Thank you for this opportunity to work on an exciting and challenging project.

I would like to extend my thanks to Roselyne Chotin and Alberto Bosio for agreeing to review my work and being member of my thesis committee, and to Vincent Beroulle for agreeing to join the thesis committee.

I deeply treasure the time I had working at LIRMM. It was a privilege to work side by side with such brilliant minds. My thanks also go to the staffs of LIRMM for all the administrative support.

I would like to thank the collaborators from MOOSIC project and SAFEST project. It was a pleasure to have such in-depth discussions with you.

I extend my thanks to all my friends in France and in Vietnam, who were with me and encouraged me so much throughout this journey.

I would like to express my heartfelt gratitude to my family back home, my parents and my younger brother, for their unwavering support and encouragement.

# Contents

| Ab  | strac                     | t                                  |                                                                                                                                                                                                                | iii                                           |

|-----|---------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Rés | sumé                      | 5                                  |                                                                                                                                                                                                                | v                                             |

| Acl | knov                      | vledge                             | ments                                                                                                                                                                                                          | xv                                            |

| Co  | nten                      | ts                                 |                                                                                                                                                                                                                | xvii                                          |

| Lis | t of l                    | Figures                            |                                                                                                                                                                                                                | xxi                                           |

| Lis | t of 🛛                    | <b>Fables</b>                      |                                                                                                                                                                                                                | xxiii                                         |

| Lis | t of A                    | Abbrev                             | iations                                                                                                                                                                                                        | xxv                                           |

|     | Intro<br>1.1              | oductic<br>The D<br>1.1.1<br>1.1.2 | emand for Design-for-TrustHardware Security Threats Emerged from Semiconduc-<br>tor Supply ChainDesign-for-Trust solutionsHardware Trojan PreventionWatermarking & FingerprintingHardware MeteringCamouflaging | 1<br>2<br>4<br>4<br>4<br>5<br>5               |

|     | 1.2                       | 1.2.1<br>1.2.2                     | How to Lock a Circuit                                                                                                                                                                                          | 6<br>7<br>8<br>8<br>9<br>10<br>10<br>11<br>11 |

|     | <b>Bacl</b><br>2.1<br>2.2 | Brief I<br>Key-C                   | d & State-of-the-Art<br>History of Logic Locking                                                                                                                                                               | <b>15</b><br>16<br>16<br>17                   |

xviii

|   |                   |          | Metrics for Output Corruption                           | 17              |

|---|-------------------|----------|---------------------------------------------------------|-----------------|

|   |                   | 2.2.2    | Insertion Strategies for Output Corruption              | 18              |

|   |                   | 2.2.3    | Attacks & Countermeasures                               | 20              |

|   | 2.3               | SAT A    | Attack & Point-Function based Logic Locking             | 21              |

|   |                   | 2.3.1    | SAT Attack                                              | 21              |

|   |                   | 2.3.2    | Point-Function based Logic Locking                      | 23              |

|   |                   |          | Metric for SAT Resilience of Point-Function based Tech- |                 |

|   |                   |          | niques                                                  | 25              |

|   | 2.4               | Post-S   | SAT Logic Locking Techniques                            | 25              |

|   |                   | 2.4.1    | Point-Function Lock Improvements                        | 25              |

|   |                   | 2.4.2    | Corrupt-and-Correct Locking                             | 26              |

|   |                   | 2.4.3    | Crypto-based Locking                                    | 28              |

|   | 2.5               | Post-S   | SAT Logic Locking Attacks                               | 28              |

|   |                   | 2.5.1    | Oracle-Guided Attacks                                   | 28              |

|   |                   |          | Approximate & Bypass Attacks                            | 29              |

|   |                   |          | Attacks with Advanced Solvers                           | 29              |

|   |                   |          | Sequential SAT Attacks                                  | 30              |

|   |                   | 2.5.2    | Oracle-Less Attacks                                     | 31              |

|   |                   |          | Removal Attacks                                         | 31              |

|   |                   |          | Synthesis-based Attacks                                 | 31              |

|   | 2.6               |          | ses based on Scan Chains                                | 32              |

|   |                   | 2.6.1    | Scan Locking                                            | 32              |

|   |                   | 2.6.2    | Scan Blockage                                           | 33              |

|   |                   | 2.6.3    | Scan Controlling                                        | 34              |

| 3 | Kev               | -Gate I  | Insertion Strategy for Effective Logic Locking          | 35              |

| 0 | 3.1               |          | luction                                                 | 36              |

|   | 3.2               |          | osed Key-Gate Insertion Strategy                        | 38              |

|   |                   | 3.2.1    | Node Ranking                                            | 38              |

|   |                   |          | Score Calculation                                       | 39              |

|   |                   | 3.2.2    | Algorithm                                               | 39              |

|   |                   |          | Scalability                                             | 39              |

|   | 3.3               | Exper    | imental Results                                         | 40              |

|   |                   | 3.3.1    | Runtime Evaluation                                      | 40              |

|   |                   | 3.3.2    | Output Corruption Evaluation                            | 41              |

|   |                   | 3.3.3    | Overhead Evaluation                                     | 44              |

|   | 3.4               | Concl    | usion                                                   | 44              |

| 4 | וי ת              | 1. 0     |                                                         |                 |

| 4 | Gat               | <b>U</b> | ecure and Effective Logic Locking with Switchable Key   |                 |

|   | <b>Gau</b><br>4.1 |          | luction                                                 | <b>45</b><br>47 |

|   | 4.1<br>4.2        |          | ponents of SKG-Lock                                     | 47              |

|   | 4.2<br>4.3        | -        | Weight SKG-Lock                                         | 40<br>49        |

|   | т.Ј               | 4.3.1    | Architecture                                            | 49              |

|   |                   | 4.3.2    | Security against SAT Attack                             | 49              |

|   |                   | 4.3.3    | Analysis                                                |                 |

|   |                   | 1.0.0    | · · · · · · · · · · · · · · · · · · ·                   | 50              |

|   | 4.4                             | SKG-l                                                                                  | Lock Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51                                                                                                              |

|---|---------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|   |                                 | 4.4.1                                                                                  | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                                              |

|   |                                 |                                                                                        | SWC Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                              |

|   |                                 | 4.4.2                                                                                  | Locking Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53                                                                                                              |

|   |                                 |                                                                                        | SKG Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                              |

|   |                                 |                                                                                        | Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                                                              |

|   |                                 | 4.4.3                                                                                  | Security against Oracle-Guided Attacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                              |

|   |                                 |                                                                                        | Key Sensitization Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                                                              |

|   |                                 |                                                                                        | SAT Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                              |

|   |                                 |                                                                                        | AppSAT Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                                                              |

|   |                                 |                                                                                        | Bypass Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                                                              |

|   |                                 | 4.4.4                                                                                  | Countermeasures against Oracle-Less Attacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                                                                                                              |

|   |                                 |                                                                                        | Removal Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56                                                                                                              |

|   |                                 |                                                                                        | SCOPE Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                                              |

|   | 4.5                             | Exper                                                                                  | imental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59                                                                                                              |

|   |                                 | 4.5.1                                                                                  | Security Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59                                                                                                              |

|   |                                 |                                                                                        | SAT Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                                                                                                              |

|   |                                 |                                                                                        | AppSAT Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                                                              |

|   |                                 |                                                                                        | Removal Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                                                                                                              |

|   |                                 |                                                                                        | SCOPE Attack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                                                              |

|   |                                 | 4.5.2                                                                                  | Output Corruption Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                              |

|   |                                 | 4.5.3                                                                                  | Overhead Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                                                              |