# Constrained deep learning for MEMS sensors-based applications

Minh Tri Lê

### ▶ To cite this version:

Minh Tri Lê. Constrained deep learning for MEMS sensors-based applications. Machine Learning [cs.LG]. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALM035. tel-04363136v2

# HAL Id: tel-04363136 https://theses.hal.science/tel-04363136v2

Submitted on 8 Jan 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

## **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

École doctorale : MSTII - Mathématiques, Sciences et technologies de l'information, Informatique

Spécialité : Mathématiques et Informatique

Unité de recherche : Institut National de Recherche en Informatique et en Automatique

Deep Learning contraint pour la résolution de problèmes algorithmiques appliqués aux capteurs MEMS (Microsystème Electromécanique)

Constrained deep learning for MEMS sensors-based applications

Présentée par :

## Minh Tri LÊ

#### Direction de thèse :

**Julyan ARBEL** Directeur de thèse

CHARGE DE RECHERCHE HDR, INRIA CENTRE GRENOBLE-RHONE-

**ALPES**

Etienne DE FORAS Co-encadrant de thèse

Movea SAS

### Rapporteurs:

**MATHIEU SALZMANN**

SENIOR SCIENTIST, ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE

**EIMAN KANJO**

PROFESSEUR, NOTTINGHAM TRENT UNIVERSITY

Thèse soutenue publiquement le 6 juillet 2023, devant le jury composé de :

MATHIEU SALZMANN Rapporteur

SENIOR SCIENTIST, ECOLE POLYTECHNIQUE FEDERALE DE

LAUSANNE

EIMAN KANJO Rapporteure

PROFESSEUR, NOTTINGHAM TRENT UNIVERSITY

VALERIE PERRIER Présidente

PROFESSEUR DES UNIVERSITES, GRENOBLE INP

INNA KUCHER Examinatrice

INGENIEUR DOCTEUR, CEA CENTRE DE PARIS-SACLAY

ETIENNE DE FORAS INGENIEUR DE RECHERCHE, MOVEA SAS JULYAN ARBEL

CHARGE DE RECHERCHE HDR, INRIA CENTRE GRENOBLE-RHONEALPES

# Abstract

Deep learning has become a powerful technique for solving complex problems across numerous domains, owing to its ability to learn and model intricate non-linear relationships from data. However, the substantial computational power, memory, and energy requirements of deep learning models make them unsuitable for deployment on devices with limited resources. Simultaneously, the emergence of microelectromechanical sensors (MEMS), microcontroller units (MCUs), and the Internet of Things (IoT) has resulted in a growing number of applications that depend on embedded systems for local data processing and environmental interaction. MEMS provide an interface to continuously sense data from the real world to the digital world. MCUs are low-cost devices with high consumer market volumes, where targeting the lowest-power hardware can result in billions in saving per year. Thus, delivering always-on, real-time sensing pose ultra-low power constraints, with direct and high technical and economic implications and challenges.

The intersection of deep learning and embedded systems has given rise to the field of tinyML, which offers significant opportunities and challenges. Deep learning promises the automation of the algorithm design process, which enables practitioners to customize a product behavior at will. The primary challenge lies in adapting deep learning techniques to operate efficiently on ultra-low-power MEMS-based devices with constrained resources and operations, while maintaining acceptable performance levels.

This thesis aims to provide strategies for optimizing power footprint and deploying deep learning models in ultra-low power settings for MEMS-based applications. We first investigate model compression methods, such as pruning, knowledge distillation, and quantization. Then, we enable end-to-end deployment of deep learning models for efficient inference on the most resource-constrained MCUs in the industry and state-of-the-art, effectively redefining the concept of ultra-low power as extreme-low power. Finally, we present a novel approach to generalize the quantization process, accommodating any number of bits, and extending to extreme quantization levels, such as 1-bit.

The outcomes of this research contribute to the advancement of tinyML and enable the broader adoption of intelligent sensing devices across various real-world applications.

# Résumé

L'apprentissage profond est devenu une technique puissante pour résoudre des problèmes complexes dans de nombreux domaines, grâce à sa capacité à apprendre et à modéliser des relations non linéaires complexes à partir de données. Cependant, la puissance de calcul, la mémoire et les besoins énergétiques substantiels des modèles d'apprentissage profond peuvent les rendre inadaptés au déploiement sur des systèmes à ressources limitées. Parallèlement, l'émergence des capteurs microélectromécaniques (MEMS), des microcontrôleurs (MCUs) et de l'Internet des objets (IoT) a entraîné un nombre croissant d'applications qui dépendent de systèmes embarqués pour le traitement local des données et pouvant interagir avec l'environnement. Les MEMS fournissent une interface permettant de détecter en continu des données du monde réel vers le monde numérique. Les MCUs sont des plateformes à faible coût ayant des volumes de marché très élevés pour les consommateurs, où cibler le matériel à la plus faible consommation peut entraîner des économies de plusieurs milliards par an. Ainsi, offrir une inférence en temps réel et en continu impose des contraintes ultra-faibles en matière de consommation d'énergie, avec des implications et des défis techniques et économiques directs et significatifs.

L'intersection de l'apprentissage profond et des systèmes embarqués a donné naissance au domaine du tinyML, qui offre à la fois des opportunités et des défis significatifs. Le principal défi consiste à adapter les techniques d'apprentissage profond pour fonctionner efficacement sur des systèmes MEMS ultra-faible consommation avec des ressources et des opérations limitées, tout en maintenant des niveaux de performance acceptables.

Cette thèse vise à fournir des stratégies pour optimiser l'empreinte énergétique et le déploiement des modèles d'apprentissage profond dans des contextes ultra-faible consommation pour des applications basées sur des MEMS. Nous étudions d'abord les méthodes de compression de modèles, telles que l'élagage, la distillation de connaissance et la quantification. Ensuite, nous permettons le déploiement de bout en bout de modèles d'apprentissage profond pour une inférence efficace sur les MCUs les plus limités en ressources de l'industrie, redéfinissant ainsi le concept de l'inférence ultra-faible consommation en tant qu'extrème-faible consommation. Enfin, nous présentons une nouvelle approche pour généraliser le processus de quantification, compatible avec

n'importe quel nombre de bits et s'étendant à des niveaux de quantification extrêmes, tels que 1-bit.

Les résultats de ces recherches contribuent à l'avancement du domaine tinyML et permettent une adoption plus large des systèmes de détection intelligents embarqués dans diverses applications du monde réel.

# Acknowledgements

This thesis would not have been possible without all the people I have met and shaped me along this Ph.D. journey.

I express my gratitude towards my supervisors, Etienne and Julyan for their support in training me to become a good researcher, patience, and most of all for keeping trust in my work throughout the years.

I want to thank my jury: Mathieu Salzmann and Eiman Kanjo for reviewing this manuscript and providing constructive feedback, Valérie Perrier for presiding the jury, and Inna Kucher for evaluating my work.

I want to thank TDK InvenSense, and in particular Bruno, Peter, and Philippe for letting me contribute to deep learning R&D at TDK and for funding this project. I also thank the algo team, Bruno, Daniela, Étienne, Jiali, Rémi, and Soufiane for their collaboration and our brainstorming and interesting discussion. Likewise, I also want to thank IFR, ISJ offices for their support. I can't wait to see the future of deep learning innovations and patents at TDK.

I want to thank the Statifiers (not the Satisfiers) with whom I shared the Ph.D. life struggles: Argheesh for always starting adventures, Alexandre for your remarkable +1 day wisdom, Benoit for the PhD work wisdom, Dasha for your kindness, Florence for being a cool chef and the Statify days, Geoffroy for your sugar and dishwashing addiction, Jacopo for teaching us "la vie d'artiste", Jean-Baptiste for your interest, Jhouben for the best post-wake up joke, Jonathan for the cool discussions, Julien for being there or maybe not, Hanâ for the PhD journey discussions, Kostas for finding the best AC in Grenoble, Louise for never buying walking poles (yet?), Lucrezia for your practical originality for adventures, Masha for being the first BDE president, mousquetaire and your unique craziness, Meryem for being part of the BDE and mousquetaire, and having the warmest soul, Pascal for your support, Pedro for the constructive comments, Pierre for the always insightful discussions, Sophie for the essential feedback, Stéphane for the witted jokes, Théo for the best clandestine pizza ever tasted, Tin for the encouragements, and Yuchen for your determination. I also want to thank ex-Statify members, a.k.a

Mistis: Brice for your humor and our reassuring discussions, and Karina for the hikes and photoshoot.

Then, I want to thank older and new friends around the globe: Alice and Samuel for the once again Genova adventures sìsì, Augustin for always giving the best tips since the UTC, who motivated me to go for a Ph.D., and the random Bulgarian parties, Henri for appearing out of nowhere to the pot, Nico and Val for the Indo trip, Juan for the largest post-curfew party in Genova, and being the best, Jonas for the Leipzig discoveries and Rob for the best indo insights.

Lastly, I would not be there without my family: my sister, brother, and especially my parents. Con rất biết ơn ba mẹ đã hy sinh cuộc đời này cho chúng con cơ hội có được một cuộc sống tốt đẹp hơn, và hy vọng chúng con không cần phải làm việc vất vả nhiều như ba mẹ ngày xưa, và rất biết ơn ba mẹ đã dạy cho con những giá trị của công việc, sự kiên trì và tôn trọng. Ba mẹ luôn ở đây ủng hộ con, mặc dù không phải lúc nào chúng ta cũng thấu hiểu nhau nhưng con mong ba tự hào về con như là con đang tự hào được là con của ba mẹ. Cảm ơn ba mẹ.

It's not easy to do, but try — try and do what you love with people you love.

And if you can manage that, it's the definition of heaven on earth."

— Conan O'Brien

# Table of contents

| Li | st of | figure  | ${f s}$                                                  | xiii |

|----|-------|---------|----------------------------------------------------------|------|

| Li | st of | tables  |                                                          | xvii |

| 1  | Intr  | oducti  | ion                                                      | 1    |

|    | 1.1   | Neura   | l networks                                               | 4    |

|    |       | 1.1.1   | Feedforward neural networks                              | 4    |

|    |       | 1.1.2   | Properties                                               | 5    |

|    |       | 1.1.3   | Modern deep learning                                     | 6    |

|    |       | 1.1.4   | From large deep learning models to tinyML                | 10   |

|    | 1.2   | MEMS    | S-based applications on ultra-low power microcontrollers | 13   |

|    |       | 1.2.1   | Overview                                                 | 13   |

|    |       | 1.2.2   | Scope of applications                                    | 14   |

|    |       | 1.2.3   | Challenges of ultra-low power hardware                   | 15   |

|    | 1.3   | Efficie | ent neural networks for tinyML                           | 17   |

|    |       | 1.3.1   | Efficient RNNs                                           | 17   |

|    |       | 1.3.2   | Overview of model compression techniques                 | 18   |

|    |       | 1.3.3   | Summary                                                  | 27   |

|    | 1.4   | Deploy  | yment of deep learning models on ultra-low power MCUs    | 27   |

|    |       | 1.4.1   | TinyML tools                                             | 29   |

|    | 1.5   | Summ    | nary and contributions                                   | 31   |

| 2  | Me    | thods f | for design of efficient neural networks                  | 33   |

|    | 2.1   | Efficie | ent RNNs                                                 | 34   |

|    | 2.2   | Knowl   | ledge distillation                                       | 35   |

|    |       | 2.2.1   | MNIST dataset                                            | 35   |

|    |       | 2.2.2   | HAR dataset                                              | 35   |

|    | 23    | Model   | nruning                                                  | 37   |

Table of contents

|   |      | 2.3.1    | MNIST dataset                                                    | 38         |

|---|------|----------|------------------------------------------------------------------|------------|

|   |      | 2.3.2    | HAR dataset                                                      | 38         |

|   | 2.4  | Concl    | usion                                                            | 40         |

|   |      | 2.4.1    | Discussion and limitations                                       | 40         |

|   |      | 2.4.2    | Future work                                                      | 42         |

| 3 | Ting | yML f    | or 8-bit neural networks on ultra-low power MCUs                 | 45         |

|   | 3.1  | Introd   | luction                                                          | 46         |

|   | 3.2  | TinyN    | ILOps for ultra-low power MCUs applied to frame-based events     | 47         |

|   |      | 3.2.1    | Introduction                                                     | 47         |

|   |      | 3.2.2    | TinyMLOps for real-time sensors applied to frame-based event     |            |

|   |      |          | classification                                                   | 50         |

|   |      | 3.2.3    | Conclusion                                                       | 54         |

|   | 3.3  |          | ICU: Towards automated large-scale deployment of tiny neural     |            |

|   |      |          | rks                                                              | 54         |

|   |      | 3.3.1    | Dataset design                                                   | 55         |

|   |      | 3.3.2    | Model design and training                                        | 57         |

|   |      | 3.3.3    | Deployment                                                       | 58         |

|   |      | 3.3.4    | Evaluation                                                       | 64         |

|   | 3.4  |          | 58                                                               | 64         |

|   | 3.5  |          | ssion                                                            | 65         |

|   |      | 3.5.1    | Conclusion                                                       | 65         |

|   |      | 3.5.2    | Limitations                                                      | 67         |

|   |      | 3.5.3    | Future work                                                      | 67         |

|   | App  | pendix   |                                                                  | 69         |

|   | 3.A  | Gener    | alized confusion matrix for multiclass event classifications     | 69         |

|   | 3.B  | Audio    | Sample API class documentation                                   | 69         |

| 4 | Reg  | ulariza  | ation for hybrid $N$ -Bit weight quantization of neural networks | 8          |

|   | on t | ultra-lo | ow power microcontrollers                                        | <b>75</b>  |

|   | 4.1  | Introd   | luction                                                          | 77         |

|   | 4.2  | Propo    | sed method                                                       | <b>7</b> 9 |

|   |      | 4.2.1    | 1-bit regularization                                             | 80         |

|   |      | 4.2.2    | N-bit generalization                                             | 82         |

|   |      | 4.2.3    | Scheduled regularized quantization                               | 83         |

|   |      | 4.2.4    | Post-training quantization                                       | 84         |

Table of contents xi

| 4.3     | Experi  | ments                                                       | . 84       |

|---------|---------|-------------------------------------------------------------|------------|

|         | 4.3.1   | Datasets                                                    | . 85       |

|         | 4.3.2   | Model                                                       | . 85       |

|         | 4.3.3   | Experimental design                                         | . 86       |

|         | 4.3.4   | Deployment and evaluation                                   | . 87       |

| 4.4     | Result  | S                                                           | . 88       |

|         | 4.4.1   | Regularization configuration                                | . 88       |

|         | 4.4.2   | Model configuration                                         | . 90       |

|         | 4.4.3   | Key results                                                 | . 91       |

| 4.5     | Conclu  | sion                                                        |            |

| A       | andin   |                                                             | 95         |

|         | endix   |                                                             |            |

| 4.A     | Hybric  | $\{1,8\}$ -bit model byte size reference on the BTS dataset | . 95       |

|         | 4.A.1   | CNN1D only                                                  | . 96       |

|         | 4.A.2   | GRU only                                                    | . 98       |

|         | 4.A.3   | CNN1D+GRU only                                              | . 99       |

|         | 4.A.4   | All layers                                                  | . 101      |

| 5 Disc  | cussion |                                                             | 103        |

| 5.1     | Conclu  | ısion                                                       | 103        |

| 5.2     |         | e directions                                                |            |

|         |         |                                                             |            |

| Referen | nces    |                                                             | <b>107</b> |

# List of figures

| 1.1 | TinyML as the intersection between artificial intelligence and embedded                                    |    |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | systems                                                                                                    | 3  |

| 1.2 | Feedforward neural network                                                                                 | 5  |

| 1.3 | Illustration of memory hierarchies for a mobile processor (left) and an                                    |    |

|     | Arm Cortex-M7 microcontroller (right). The microcontrollers process all                                    |    |

|     | computation and data transfer on-chip                                                                      | 15 |

| 1.4 | Floating-point and fixed-point 32-bit representations. Floating-point                                      |    |

|     | allows a dynamic range (minimal to maximal possible value) of roughly                                      |    |

|     | $[-10^{38}, 10^{38}]$ , compared to fixed-point $[-2^{m-1}, 2^{m-1} - 2^{-n}] \approx [-2^{15}, 2^{16}]$ , |    |

|     | which is approximately a $10^{33}$ smaller range (Novac et al., 2021). The                                 |    |

|     | smallest resolution (step between each consecutive representable value) of                                 |    |

|     | floating-point is $\approx 10^{-38}$ while it is $[2^{-n}] \approx 10^{-5}$ for $n = 16$ for fixed-point.  | 16 |

| 1.5 | Unstructured pruning (left panel) versus structured pruning (middle and                                    |    |

|     | right panels)                                                                                              | 20 |

| 1.6 | Pruning rate over epochs with a polynomial schedule function (Zhu and                                      |    |

|     | Gupta, 2017) with $s_f = 0.8$ , $s_0 = 0$ , $t_0 = 0$ , $n = 13260$ , $\Delta t = 100$                     |    |

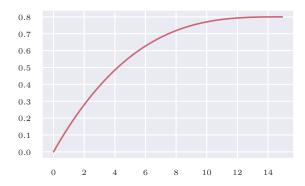

|     | (Equation $(1.6)$ )                                                                                        | 21 |

| 1.7 | TinyMLOps pipeline                                                                                         | 28 |

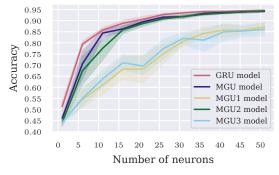

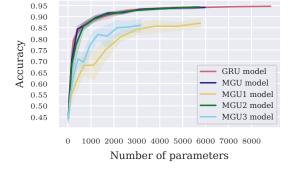

| 2.1 | Comparison of test results of GRU baseline (Chung et al., 2014) versus                                     |    |

|     | MGU (Zhou et al., 2016) versus MGU1, MGU2, MGU3 (Heck and Salem,                                           |    |

|     | 2017) over the number of neurons (left) and parameters (right). Each                                       |    |

|     | training is repeated 10 independent times on an HAR dataset                                                | 34 |

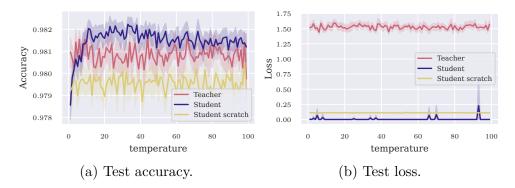

| 2.2 | Knowledge distillation on MNIST dataset with CNN models. Comparing                                         |    |

|     | student models trained with the teacher, teacher, and student models                                       |    |

|     | trained from scratch. The teacher is 10 times larger than the student model.                               | 36 |

**xiv** List of figures

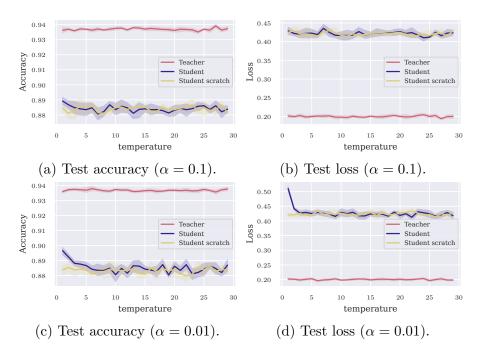

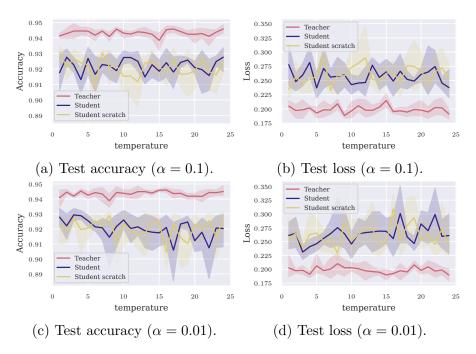

| 2.3 | Knowledge distillation on HAR dataset with MLP models. Comparing student models trained with the teacher, teacher, and student models trained from scratch. The teacher is 5 times larger than the student model.                                                                                                                                                                                                                | 36       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

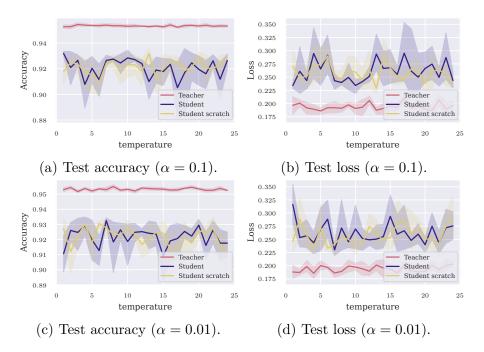

| 2.4 | Knowledge distillation on HAR dataset with GRU(80) to GRU(30) models. Comparing student models trained with the teacher, teacher, and student models trained from scratch. The teacher is about 6 times larger than the                                                                                                                                                                                                          |          |

| 2.5 | student model                                                                                                                                                                                                                                                                                                                                                                                                                    | 37       |

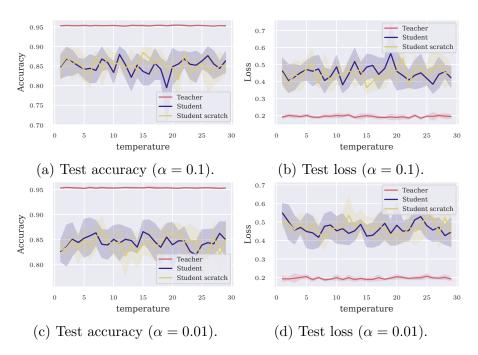

| 2.6 | the student model                                                                                                                                                                                                                                                                                                                                                                                                                | 38       |

| 2.7 | larger than the student model                                                                                                                                                                                                                                                                                                                                                                                                    | 39       |

|     | fine-tuning                                                                                                                                                                                                                                                                                                                                                                                                                      | 40       |

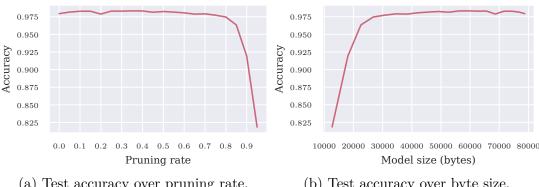

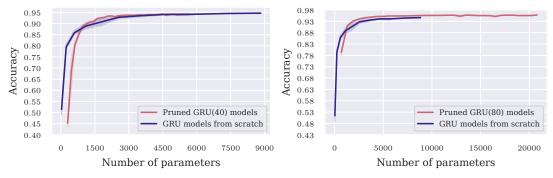

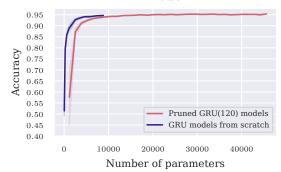

| 2.8 | Magnitude-based (unstructured) pruning with polynomial decay (Zhu and Gupta, 2017) on GRU models applied to the HAR dataset. The blue curve is obtained from five independent training of GRU models at different sizes, acting as a baseline. This baseline is the same for all three plots. The red curve is obtained from re-pruning five GRU models (large, medium, and small) for each sparsity rate (5% pruning step rate) | 41       |

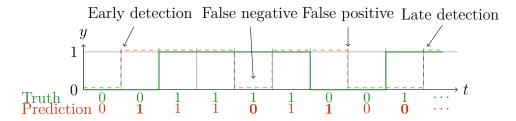

| 3.1 | Example of a frame-by-frame event-based classification encoded by binary                                                                                                                                                                                                                                                                                                                                                         | 40       |

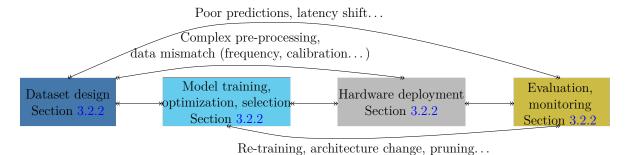

| 3.2 | vectors. We observe four possible misclassifications                                                                                                                                                                                                                                                                                                                                                                             | 49<br>50 |

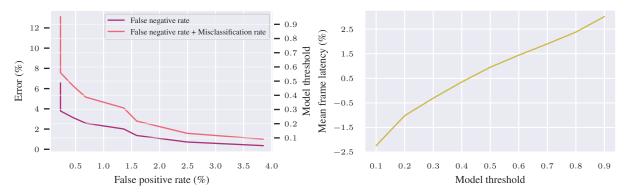

| 3.3 | Custom metrics evaluated by varying the decision threshold and measuring event errors or latency of a GRU model on a four-class head gesture test set. The model is deployed on an Arm Cortex-M0+ MCU                                                                                                                                                                                                                            | 53       |

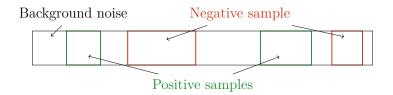

| 3.4 | Illustration of an audio sample, with random samples, position, and a                                                                                                                                                                                                                                                                                                                                                            | 00       |

| 0.1 | number of positive and negative keywords                                                                                                                                                                                                                                                                                                                                                                                         | 58       |

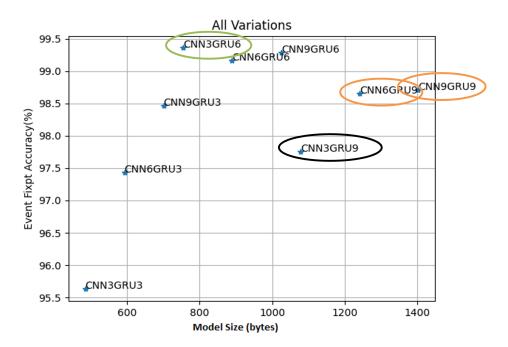

| 3.5 | Tradeoff between size and on-device accuracy for a CGRU model applied on the bring-to-see dataset, using ML2MCU's meta-optimizer. Optimal tradeoffs are highlighted in green, suboptimal tradeoffs in red, and manually                                                                                                                                                                                                          |          |

|     | designed models in black                                                                                                                                                                                                                                                                                                                                                                                                         | 59       |

List of figures  $\mathbf{x}\mathbf{v}$

| 3.6   | Elu versus hard Elu function. A $L^1$ distance between the original Elu and                                                                                                                                                                                                                               | co                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|       | our approximation $\approx 0.32$ for $x \in \mathbb{R}$                                                                                                                                                                                                                                                   | 63                    |

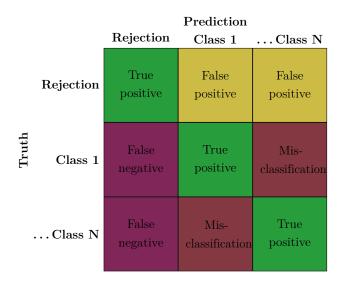

| 3.A.  | 1Error types of a generalized confusion matrix for multiclass event classifications with a rejection class (i.e., non-event). There is an additional error type compared to binary event classification: misclassification between positive classes                                                       | 69                    |

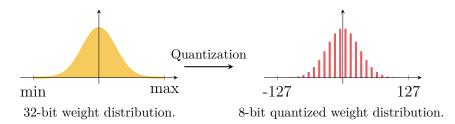

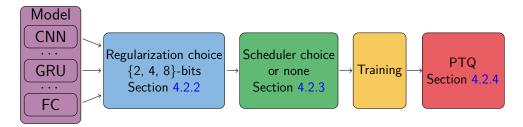

| 4.2.1 | Regularized quantization pipeline using hybrid $\{1, 2, 4, 8\}$ -bits quantization with schedule option using a convolutional (CNN) GRU model with a                                                                                                                                                      |                       |

|       | fully-connected (FC) layer as example                                                                                                                                                                                                                                                                     | 80                    |

| 4.2.2 | 21-bit regularization functions of Equations $(4.1)$ , $(4.3)$ , $(4.4)$ , and $(4.5)$ .                                                                                                                                                                                                                  | 81                    |

| 4.2.3 | 3 N-bit regularization functions of Equation (4.5) and Equation (4.6), $N \in$                                                                                                                                                                                                                            |                       |

|       | $\{1,2,4,8\}$                                                                                                                                                                                                                                                                                             | 82                    |

| 4.2.4 | 4 Schedule functions for quantized regularization for $t_{\rm final}=350.\ldots$                                                                                                                                                                                                                          | 83                    |

| 4.2.5 | Scheduled regularization of GRU weights at epoch 1, 25, and 500 (left                                                                                                                                                                                                                                     |                       |

|       | to right) to 4-bits with Reg <sub>4</sub> regularization and linear schedule in the                                                                                                                                                                                                                       |                       |

|       | background, on the BTS dataset.                                                                                                                                                                                                                                                                           | 85                    |

| 4.4.1 | Hybrid {1, 8}-bits quantization test accuracy results on the BTS (left) and GSCv2-12 dataset (right), without schedule (blue) or with schedule (green) (Section 4.2.3). The baseline is trained normally without regularization and quantized to 8-bits. For BTS, we exclude training with schedulers for |                       |

| 4.4.2 | CNN1D+GRU. For GSCv2-12, we exclude training with CNN1D+GRU. 2 Hybrid {2, 4, 8}-bit quantization test accuracy results on the BTS (left) and GSCv2-12 dataset (right), without schedule (blue) or with schedule (green). The baseline is trained without regularization and quantized to                  | 88                    |

|       | 8-bits                                                                                                                                                                                                                                                                                                    | 89                    |

| 4.4.3 | Scheduler comparison of our 1-bit quantization results using our 1-bit                                                                                                                                                                                                                                    |                       |

|       | (top) and {2, 4, 8}-bits (bottom) regularization, on the BTS (left) and GSCv2-12 (right) dataset, across all scenarios. Schedulers are ordered from fastest to slowest at mid-training time (as shown in Figure 4.2.4). The baseline is trained without regularization and quantized to 8-bits. For       |                       |

|       | {2, 4, 8}-bits, inverse polynomial and step-based bounded are omitted from experiments                                                                                                                                                                                                                    | 90                    |

|       | 11 O 111 O A D O 1 111 O 110 O 1 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                    | $- \upsilon \upsilon$ |

xvi List of figures

|    | 4.4.4 Hybrid {1, 8}-bits weight quantization accuracy versus the number of |

|----|----------------------------------------------------------------------------|

|    | CNN channels and GRU cells for various combinations of quantized layers,   |

|    | with ReLU or PReLU as CNN activation on the BTS dataset. 1st row:          |

|    | All layers, 2nd: CNN1D layer only, 3rd: CNN1D and GRU layers, and 4th:     |

|    | GRU layer. For reference, we also added the baseline model architecture    |

|    | at 6 channels and 5 cells with hybrid quantized layers. Darker colors are  |

|    | better. Each model here is trained using our 1-bit regularization (Section |

| 92 | 4.2.1) without a schedule                                                  |

|    |                                                                            |

# List of tables

| 1.1   | Summary of standard architectures used in modern deep learning                                                                             | 9  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2   | Reference table of standard activation functions                                                                                           | 9  |

| 1.3   | Comparison of representative deep learning model sizes across cloud,                                                                       |    |

|       | mobile, and MCU platforms                                                                                                                  | 12 |

| 1.4   | Comparison of hardware for cloud, mobile, and TinyML, including the MCU targeted in this work, provided by TDK InvenSense (Banbury et al., |    |

|       | 2021a, Saha et al., 2022)                                                                                                                  | 14 |

| 1.5   | Example of sensor applications and their target MCU devices. We indicate                                                                   |    |

| 1.0   | our focus applications in italics                                                                                                          | 15 |

| 3.1   | Comparison of a model quantized to int8 deployed on an Arm Cortex-                                                                         |    |

|       | M4 MCU using tf.lite (David et al., 2021), NNoM (Ma, 2020) and our                                                                         |    |

|       | tinyMLOps solution on an activity recognition dataset                                                                                      | 52 |

| 3.2   | Dataset reference for TDK InvenSense's MEMS-based applications                                                                             | 56 |

| 3.3   | Benchmark results of 8-bit neural networks deployed on ultra-low power                                                                     |    |

|       | MCUs for motion detection datasets                                                                                                         | 65 |

| 3.4   | Benchmark results of 8-bit neural networks deployed on ultra-low power                                                                     |    |

|       | MCUs for audio applications                                                                                                                | 66 |

| 4.2.1 | Schedule functions for regularization. Here, $d$ is set to 0.01 and 0.001 for                                                              |    |

|       | schedule inverse linear and inverse polynomial respectively, and rate is set                                                               |    |

|       | to 0.8 by default. For step-based functions, step is set to 10 by default.                                                                 |    |

|       | For step-based inverse, a higher rate leads to a faster schedule, contrary                                                                 |    |

|       | to step-based bounded                                                                                                                      | 84 |

| 4.3.1 | Baseline model configuration size and parameters where $(c, k)$ refers to                                                                  |    |

|       | the number of channels and the kernel size of the CNN1D. Weights are                                                                       |    |

|       | stored in 8-bits and activations in 32-bits integers                                                                                       | 86 |

xviii List of tables

| 4.A.1Bytes size of the BTS baseline ReLU model with CNN1D weights quantized  |     |

|------------------------------------------------------------------------------|-----|

| to 1-bit                                                                     | 96  |

| 4.A.2Bytes size of the BTS baseline PReLU model with CNN1D weights           |     |

| quantized to 1-bit.                                                          | 97  |

| 4.A.3Bytes size of the BTS baseline ReLU model with GRU weights quantized    |     |

| to 1-bit                                                                     | 98  |

| 4.A.4Bytes size of the BTS baseline PReLU model with GRU weights quantized   |     |

| to 1-bit                                                                     | 98  |

| 4.A.5Bytes size of the BTS baseline ReLU model with CNN1D+GRU weights        |     |

| quantized to 1-bit.                                                          | 99  |

| 4.A.6Bytes size of the BTS baseline PReLU model with CNN1D+GRU weights       |     |

| quantized to 1-bit                                                           | 100 |

| 4.A.7Bytes size of the BTS baseline ReLU model with all weights quantized to |     |

| 1-bit                                                                        | 101 |

| 4.A.8Bytes size of the BTS baseline PReLU model with all weights quantized   |     |

| to 1-bit                                                                     | 101 |

# List of Algorithms

| 1 | High-level data augmentation for robust audio samples for keyword spotting.    | 57 |

|---|--------------------------------------------------------------------------------|----|

| 2 | Symmetric quantization of a floating-point matrix to $N$ -bits : NBitQuantize. | 61 |

| 3 | Floating-point fully-connected: FloatFC                                        | 62 |

| 4 | Integer-only fixed-point fully-connected inference: QuantizedFC                | 62 |

| 5 | Floating-point hard Elu: FloatHardElu                                          | 63 |

| 6 | Fixed-point hard Elu: QuantizedHardElu                                         | 63 |

# Chapter 1

# Introduction

"Everything is both simpler than we can imagine, and more complicated that we can conceive."

— Johann Wolfgang von Goethe

**Artificial intelligence.** Over the last decade, *artificial intelligence* (AI) has revolutionized our daily experiences and technological advancements, empowering machines to perform tasks that traditionally require human-like intelligence, such as recognizing objects or speech or playing advanced games like Go.

Machine learning (ML) is the most prominent AI approach, which trains computers to learn patterns and representations from data without explicit programming.

Deep learning (DL) is an advanced subset of machine learning inspired by the organization of the brain, using artificial neural networks (NNs) to model and solve complex problems in a wide variety of fields, including language processing, protein generation, or automation.

Sensors and microcontrollers. Simultaneously, there has been an increase in the adoption and development of the *Internet of Things* (IoT), bringing new devices and applications into our daily lives. *Microelectromechanical sensors* (MEMS) and *microcontroller units* (MCUs) are essential hardware components of IoT, which allows hardware devices to collect and process information (movement, voice, temperature, pressure, ...) directly at the source, in their local environment, excluding the need for additional resources or external communication. Local and autonomous data processing optimizes the flow of information but inherently poses power constraints. Some applications also require

continuous data processing, which put additional power constraints. MEMS and MCUs serve as the interface to sense information between the analog and the digital world. These devices are found in a wide range of applications, including mobiles, cars, wearables, environmental monitoring, and healthcare systems. Their consumer market scales to several billion in annual sales, so a slight deviation in power constraints can result in significant costs.

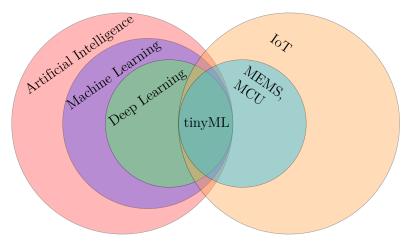

**TinyML.** The convergence of machine learning and IoT has sparked significant interest in research and industry because it enables embedded hardware to process local data and interact with their environment in an automated and intelligent way, thus leading to the emerging field of tinyML (Figure 1.1). TinyML focuses on developing efficient neural network models and deployment techniques tailored for low-power, resource-constrained devices. Some examples of tinyML applications are detecting or counting events, gesture recognition, predictive maintenance, or keyword spotting, commonly found in home appliances, remote control devices, smartphones, smart watches, or augmented reality glasses.

However, the exponential growth of deep learning is closely linked to the development of powerful hardware, such as graphical processing units (GPUs), capable of supporting its large computation requirements. Therefore, deep learning has yet to reach the same growth and support on low-power devices, such as microcontrollers, to enable deep learning to run at the edge. Indeed, the power footprint of deep learning, as well as the vast landscape of embedded devices, pose new challenges but exciting opportunities that must be addressed by researchers and industrials.

Industrial context. TDK InvenSense is a world-leading manufacturer and supplier of motion, sound, or pressure sensors. Their sensors are integrated into a wide range of applications and products, including smartphones, wearables, cars, home appliances, remote controls, ... In many of these applications, the sensors must operate always-on and in real-time, which requires extreme attention to memory, latency, and power constraints. Meeting these power constraints can help reduce costs and differentiate their products in a highly competitive industry that sells billions of units annually.

Moreover, the promise of deep learning to automatically learn, extract and classify information from labeled data with state-of-the-art performance under a fast time-to-market and uniform design process is highly attractive. Practically, this would allow non-practitioners to create and design new sensor-based algorithms at will. However, while deep learning has proven high performance, it is an expensive method in terms of

data collection, training, and inference, which makes it challenging to deploy on the most constrained devices. Moreover, even a slight increase in power footprint may require the use of an upgraded hardware model, resulting in significant additional costs for consumers and a less competitive market advantage.

Therefore, researching new ways to incorporate the promises of neural networks into the extreme ultra-low power class of embedded targets poses significant challenges and opportunities.

Introduction outline. In the following section, we introduce deep learning, its applications, and limitations (Section 1.1), for low-power devices (Section 1.2) for research and industry. This has led us to explore the challenges and methods (Section 1.3), along with the tools and practices (Section 1.4) used to combine both areas, contributing to the emerging field of tinyML.

Fig. 1.1 TinyML as the intersection between artificial intelligence and embedded systems.

# 1.1 Neural networks

We introduce neural networks (Section 1.1.1), then we motivate how their theoretical properties (Section 1.1.2) and modern architectures (Section 1.1.3) are of interests in tinyML, and finally explain its implications for our work (Section 1.1.4).

### 1.1.1 Feedforward neural networks

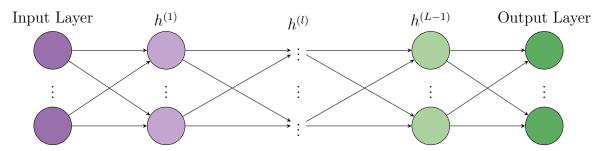

The concept of artificial neural networks was introduced by McCulloch and Pitts (1943) as a mathematical model to simulate the human biological neural system but was limited in its ability to learn. This laid the foundation for the perceptron model, which was the first neural model capable of learning and classifying linearly separable data (Rosenblatt, 1958, Sakib et al., 2018). In turn, the backpropagation (Rumelhart et al., 1986) and gradient descent algorithms (Baldi, 1995, Lecun et al., 1998) were developed to allow efficient training of multi-layer perceptron (MLP) that is capable of classifying non-linear inputs. The MLP is a type of feedforward neural network that consists of alternatively stacking multiple layers L of neurons and non-linear functions  $\phi$  (Rumelhart et al., 1986, Huang, 2009) as represented in Figure 1.2. These layers include an input layer, one or more hidden layers, and an output layer. Stochastic gradient descent (SGD) and backpropagation algorithms, and progress in hardware computation have enabled the revolution in the field of neural networks, leading to the modern era of deep learning algorithms (LeCun et al., 2015), for example capable of achieving state-of-the-art performance on ImageNet (Krizhevsky et al., 2012).

Formally, a neural network can be defined as a function f and a directed, weighted graph composed of nodes (neurons) and edges (connections between neurons) with associated weight parameters W, bias B, where inputs x are propagated forward in the graph to produce an output y. The objective of the neural network f defined as

$$y = f(x) = h^{(L)}$$

$$h^{(l)} = \phi^{(l)} \left( W^{(l)} h^{(l-1)} + B^{(l)} \right) \quad \text{for } l = 1, \dots, L$$

$$h^{(0)} = x$$

(1.1)

is to approximate some function  $f^*$  mapping an input vector x to an output vector y by learning weights matrix W (Goodfellow et al., 2016).

Neural networks have interesting theoretical and practical properties, as we will see in the next sections.

1.1 Neural networks 5

Fig. 1.2 Feedforward neural network.

## 1.1.2 Properties

Neural networks possess powerful theoretical properties that stand out from standard machine learning approaches, making them of great interest for a wide range of applications.

### Expressiveness

Neural networks are universal approximators. Cybenko (1989), Hornik et al. (1989) have theorized that a sufficiently wide hidden layer is able to approximate any continuous function on a compact set to an arbitrary level of precision. More recent work by Lin and Jegelka (2018) has extended the universal approximation theorem to residual neural networks (ResNets) (He et al., 2016), proving that a sufficiently deep neural network with one-neuron hidden layers with residual connections has enough expressive power to approximate any continuous function.

The direct implication is that feature extraction can be done automatically without domain knowledge, unlike standard machine learning. Thus, this allows for a uniform algorithm design process across a wide range of applications, facilitating the creation of algorithms from a set of labeled data, and their use in the industry and research fields.

Although these theorems prove that neural networks are able to learn "by heart" any function, given enough input samples, they do not tell anything about *how* to reach generalization ability to new samples.

#### Generalization

Neural network models have shown that it is possible to generalize to new data with fewer examples than parameters with very large models (Li and Liang, 2018, Kawaguchi and Huang, 2019), and are even capable of labeling random data (Zhang et al., 2021a). This overparametrization results in a highly-dimensional non-convex space and redundancy, but results in higher quality and quantity of local minima (Choromańska et al., 2014). This implies that the optimization function has a higher chance of not getting stuck

in a bad local minimum compared to small-size networks. These results differentiate neural networks from standard ML models where the overparametrization is usually detrimental to generalization, especially if there are more parameters than needed. Thus, the learnable capacity of neural networks makes them of great interest for performing various tasks in tinyML, using a uniform approach.

We saw an overview of the theoretical properties of deep learning, we will now explore which modern deep learning architectures are commonly used in practice and why.

# 1.1.3 Modern deep learning

Although in the modern deep learning era, the hardware progress can allow supporting the given high volume of computation and data, the design of the architecture is critical to the final performance and depends on the applications.

Developing and finding new neural network architectures is of great interest in research to surpass the state-of-the-art. Most of these state-of-the-art architectures are variations and combinations of the one we present below. Table 1.1 provides a summary of standard architectures used in modern deep learning, and their strengths and weaknesses.

#### Fully-connected layers

Fully-connected (FC) layers, also known as dense layers were the first type of layers used in neural networks, specifically in MLP as presented in Section 1.1.3 and depicted in Figure 1.2. They connect each neuron of a layer to all the neurons in the next layer and process each input independently. by applying a non-linear transformation. They are often used toward the end of the model to aggregate the higher-level features from the previous layer and make the final predictions. The simplest form of a fully-connected layer is a weighted sum, which makes them very general and not specialized to any particular application. Thus, they are building blocks of modern deep learning architectures. However, they are prone to overfitting, and may poorly perform on spatial or temporal data.

#### Convolutional neural networks

Convolutional neural networks (CNNs) are commonly used as feature extractors, showing their strength in processing spatial structures, such as images (Krizhevsky et al., 2012), videos (Simonyan and Zisserman, 2014), or signal processing (Alnaim and Abbod, 2019, Gong and Poellabauer, 2018). As they suggest, they consist of applying convolutional operations using filters, also called kernels on the input in 1D, 2D or 3D, and are shared across the spatial dimensions. They are often stacked all together with max-pooling, to

1.1 Neural networks 7

summarize a group of values by their maximum, (Krizhevsky et al., 2012), batchnorm to normalize activations and facilitate training (Ioffe and Szegedy, 2015), and ReLU activation for non-linearity. Compared to FC layers, this design allows CNNs to efficiently learn spatial hierarchical structures and detect local to global patterns, such as edges, shapes, and textures. In addition, the weight sharing aspect reduces the number of parameters and makes them more robust to spatial translations and distortions. Some classic CNN architectures are AlexNet (Krizhevsky et al., 2012), VGGNet (Simonyan and Zisserman, 2015), or GoogleLeNet (Szegedy et al., 2015), each using increasing network depths, thereby large model size.

Thus, in modern deep learning architectures, CNNs are often found in the early stages of the network serving as powerful feature extractors, but they have shown limitations in learning with sequential data structure or modeling long-range dependencies (Shorten and Khoshgoftaar, 2019, Liu et al., 2020a).

#### Recurrent neural network

Recurrent neural networks (RNNs) are specialized layers for modeling sequential data (Rumelhart et al., 1986, Elman, 1990), such as signals (Graves and Jaitly, 2014, Alnaim and Abbod, 2019), speech (Zhang et al., 2018) or text (Bahdanau et al., 2015). Compared to CNNs, they are able to model longer temporal contexts by keeping a description of previous contexts because each output directly depends on previous inputs. This is of particular interest for sensor-based applications that inherently deal with sequential data.

The building block of an RNN can be defined as a simple RNN (Elman, 1990):

$$h_{t} = \phi_{h}(W_{h}[h_{t-1}, x_{t}] + b_{h}),$$

$$y_{t} = \phi_{y}(W_{y}h_{t} + b_{y}),$$

(1.2)

where  $x_t$  is the input,  $h_t$  is a shared internal state, serving as a *memory* at time t,  $b_h$  and  $b_y$  are bias terms. However, they are difficult to train because of the effects of the vanishing or exploding gradient when the sequence is long (Bengio et al., 1994). Then long-short term memory (LSTM) (Hochreiter and Schmidhuber, 1997, Gers et al., 1999, 2003) and gated-recurrent units (GRU) (Chung et al., 2014) layers were designed to alleviate the limitations of the simple RNN.

They are based on two forms of memory updates:

- "Leak": Progressive update of the current memory:  $h_{t+1} = h_t + \phi(h_t, x_t)$

- "Gate": Context-dependent updates of the memory:  $h_{t+1} = \alpha h_t + (1 \alpha)\phi(h_t, x_t)$ ,

where  $\alpha$  can be a scalar or the output of a gated function  $g(h_t, x_t) \in [0, 1]$  as in GRU or LSTM. Note that the "gated" mechanism is a specific form of the attention mechanism (Vaswani et al., 2017), allowing it to focus its attention on specific inputs depending on the context.

In particular, LSTM has three gates (input, forget, and output) and has two hidden temporal streams  $c_t$  and  $h_t$  where  $c_t$  corresponds to  $h_t$  in the previous definition of the RNN (Equation (1.2)) and  $h_t$  is an auxiliary stream used to compute  $\alpha$  thus controlling the quantity of updates.

GRU is a simplified version of LSTM (update and forget) as well as one hidden temporal stream  $h_t$ , which has shown performance close to LSTM with a lower power footprint (Cahuantzi et al., 2021).

However, RNNs are limited in handling spatially structured data and processing sequences in parallel. This is because RNNs process input one time step at a time (Equation 1.2).

#### Residual neural networks

Residual neural networks (ResNets) were introduced in He et al. (2016). They provide each layer with direct feedback from distant previous layers to minimize the loss of gradient information during the backpropagation in deep networks. Although ResNets has shown state-of-the-art performance in computer vision (Khan et al., 2020), they are typically on the scale of millions of parameters (Menghani, 2023) and are more commonly applied on deep networks, which is not suitable for tinyML hardware.

#### **Transformers**

Transformers are attention-based models introduced in Vaswani et al. (2017) that surpass state-of-the-art performance on large-scale natural language processing tasks or computer vision tasks (Lin et al., 2022). They allow the model to focus their attention on each token of the input sequence (local) with respect to other tokens (global). This design addresses the limitations of CNNs and RNNs as stated previously because Transformers can process long-term dependencies and sequences in parallel. Although they have encountered great success and interest, they require a large amount of data, and a power footprint for both training and inference, even more than ResNets, which makes them bad candidates for tinyML.

1.1 Neural networks 9

Table 1.1 Summary of standard architectures used in modern deep learning.

| Layer        | Definition                                      | Strength                            | Weakness                                |

|--------------|-------------------------------------------------|-------------------------------------|-----------------------------------------|

| FC           | Connects all neurons in-between layers          | High-level aggregations             | Overfitting, not specialized            |

| CNN          | Convolutional operations with shared parameters | Local and global spatial patterns   | Struggles with sequences                |

| RNN          | Processes sequences with a hidden state         | Temporal dependencies               | Struggles with spatial patterns         |

| ResNets      | Deep nets with residual connections             | Eases training deep networks        | Large model size, expensive             |

| Transformers | Self-attention for input relationships          | Long-term local and global patterns | Large training data and power footprint |

#### **Activation functions**

Activation functions in deep learning introduce non-linearity to the model, enabling deep learning models to achieve higher levels of expressiveness and create more complex decision boundaries. This non-linearity is essential for processing real-world data, characterized by diverse and often non-linear features, effectively capturing intricate relationships within the data. Table 1.2 references standard activations used in modern deep learning.

Table 1.2 Reference table of standard activation functions.

| Name       | Definition                                                                                  | Notes                                  |

|------------|---------------------------------------------------------------------------------------------|----------------------------------------|

| ReLU       | $f(x) = \begin{cases} x, & \text{if } x \ge 0\\ 0, & \text{otherwise} \end{cases}$          | Returns identity if positive, else 0   |

| Leaky ReLU | $f(x) = \begin{cases} x, & \text{if } x \ge 0\\ \alpha x, & \text{otherwise} \end{cases}$   | Allows small negative values           |

| PReLU      | $f(x) = \begin{cases} x, & \text{if } x \ge 0\\ \alpha_i x, & \text{otherwise} \end{cases}$ | Per-neuron learnable $\alpha_i$ values |

| Tanh       | $f(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}}$                                                  | Returns value in range $[-1,1]$        |

| Sigmoid    | $f(x) = \frac{1}{1 + e^{-x}}$                                                               | Returns value in range $[0,1]$         |

| Softmax    | $f(x_i) = \frac{e^{x_i}}{\sum_{j=1}^K e^{x_j}}$                                             | Returns class probabilities            |

#### Regularization

In Section 1.1.2, we have seen that neural networks possess interesting generalization properties. We will now explore popular regularization choices that help with generalization in practice.

As in standard machine learning, regularization can help neural networks to generalize better to unseen data, and make them less complex. Regularization techniques can either be of two forms, based on whether or not they directly alter the objective function:

• Explicit:

$-L_1$  penalizes the absolute values of the weights, encouraging sparsity, and thus simpler models,

-  $L_2$  penalizes the squared values of the weights, constraining their magnitude, and thus encourages smoother and simpler models.

### • Implicit:

- Dropout (Srivastava et al., 2014) as an average of probabilistic architectures where each dropout-realization results in a different sub-network (Gal and Ghahramani, 2016),

- Batch normalization limits the range of values and adds noise to the activation, preventing the model from memorizing the training data too well (Ioffe and Szegedy, 2015, Bjorck et al., 2018),

- Early-stopping prevents the model from becoming too specialized during training (Sjöberg and Ljung, 1992, Bishop, 1995),

- Data augmentation increases the size and diversity of the training set, which helps the model learn more robust features (Shorten and Khoshgoftaar, 2019),

- Random noise injected into the input (also a form of data augmentation)

(Goodfellow et al., 2016),

- Noise introduced by SGD optimization (Poggio et al., 2020a,b).

Most of these regularization methods add negligible computation costs and help with generalization performance.

In this section, we provided a brief overview of the layers used in modern deep learning and which have the most potential for low-power hardware applications.

# 1.1.4 From large deep learning models to tinyML

In this section, we give an overview of the recent trends of deep learning model sizes, then we explicit the challenges of tinyML based on the neural network theory (Section 1.1.2) and practices (Section 1.1.3), and motivate our interest to apply them for tinyML.

Trend in deep learning models. Since the first AlexNet model was trained on a graphic processor unit (GPU) (Krizhevsky et al., 2012), we entered the modern era of deep learning where the limits of the state-of-the-art are regularly pushed on numerous complex tasks. Meanwhile, deep learning models are geared towards exponential increases in model size. As of 2023, the GPT4 model (OpenAI, 2023) is said to be even larger than

1.1 Neural networks 11

the GPT3 model with 175 billion parameters ( $\approx 800 \text{GB}$ ) (Brown et al., 2020), marking a growth of 179900% parameters size in just over 5 years. In general cases, model sizes are at least in the order of  $10^7$  parameters.

Although model performance can benefit from overparameterization, large neural networks have been shown to have high redundancy (Han et al., 2016, Frankle and Carbin, 2019). Denil et al. (2013) estimated that in some cases only  $\approx 5\%$  of the total parameters are critical to the final output decision. Thus, we can see that these models fail in terms of algorithm efficiency, where the objective is to achieve a task with minimal effort.

This raises questions on how to train more efficient models and also suggests the existence of smaller but viable models.

Trend in efficient deep learning models. A new wave of efficient deep learning models emerged, such as SqueezeNet (Iandola et al., 2016), MobileNet V1, V2, and V3 (Howard et al., 2017, Sandler et al., 2018, Howard et al., 2019), or EfficientNet (Tan and Le, 2019), ranging in one to five million parameters, entering the scale of the feasibility on mobile devices. These new models can achieve up to a 510 time model size reduction compared to AlexNet (Tan and Le, 2019) with equal performance. In general cases, model sizes are in the order of at least 10<sup>6</sup>.

Trend in ultra-low power deep learning models. Although mobile-sized models show a great shift toward efficient deep learning architectures, they are still too large for deployment on microcontrollers (Liberis and Lane, 2020, Lin et al., 2020, Banbury et al., 2021a). Deep learning on microcontrollers (Unlu, 2020) is an alternative paradigm that is still at an earlier stage compared to mobile-size research, where the term tinyML has been first appearing in 2019 (Han and Siebert, 2022). However, there has been a success in the deployment of neural networks on MCUs on audio classification tasks (Zhang et al., 2018, Lin et al., 2020, Fedorov et al., 2020) by using efficient CNNs, RNNs, or NAS (Banbury et al., 2021a). In Lin et al. (2020), they succeeded in deploying a person detection model with less than 1MB memory. In general cases, model sizes must be in the order of less than 10<sup>6</sup> and less than 1MB. These models reach a memory size of under 512 kB or even 256 kB, entering the scale of microcontroller hardware. The high resource limitations of MCUs present unique requirements and need the design of dedicated workflow and tools to enable end-to-end deep learning pipelines. Table 1.3 provides a summary of example model sizes for each platform we reviewed.

**Motivations.** Neural networks are powerful algorithms that can operate with a uniform approach in terms of algorithm design: labeled data, automated feature extraction and

Table 1.3 Comparison of representative deep learning model sizes across cloud, mobile, and MCU platforms.

| Platform | Model        | Parameters | Model size              |

|----------|--------------|------------|-------------------------|

| Cloud    | Inception-v3 |            | $\geq 10^2 \mathrm{MB}$ |

| Mobile   | MobileNet-v3 |            | $\geq 10^0 \mathrm{MB}$ |

| MCU      | MCUNet       |            | $< 10^0 \mathrm{MB}$    |

modeling, and deployment, for a wide range of applications. This makes them a great class of algorithm candidates for MEMS-based applications relying on signal processing.

Unfortunately, the expressiveness and generalization ability of neural networks is dependent on their size, which makes them inherently complex and "black box" functions that are analytically difficult to interpret and design. However, they are mostly composed of very primitive operations (Equation (1.1)): multiplications and additions, which are accessible to any microcontrollers. Concerning the non-linear activations, some are very straightforward, such as ReLU (Fukushima, 1975, Nair and Hinton, 2010) or LeakyReLU (Maas et al., 2013), while other activations like tanh or sigmoid pose more challenges due to their computational complexity.

Moreover, prior literature has shown that it is *possible*, albeit *challenging*, to design and deploy small enough neural networks on resource-constrained microcontrollers. Therefore, following the trend of efficient deep learning models to reduce their inherent power footprint, we are interested in pushing the state-of-the-art of low-power footprint models to make them viable to microcontrollers, without degrading performance. Additionally, deep learning models in practice are commonly overparametrized (Denil et al., 2013), so the field of deep learning will benefit from more contributions to designing and deploying more efficient and accessible neural networks.

To summarize, we provided background on neural network theory and practices, their limitations and challenges, and why they are of great research interest for MEMS-based applications running in ultra-low power settings.

Next, we explore the literature on specialized methods to design efficient deep learning models for tinyML in Section 1.3, but we must first provide the necessary background on embedded hardware, which we will reference throughout our work in Section 1.2.

# 1.2 MEMS-based applications on ultra-low power microcontrollers

We provide a brief overview of MEMS and MCU hardware technology (1.2.1) to understand which specific applications we will focus on in this work (1.2.2) and their intrinsic challenges for deep learning (1.2.3).

### 1.2.1 Overview

MEMS and MCUs. MEMS are miniaturized (microscale dimensions) sensors and actuators omnipresent in a wide range of electronic devices, as they convert physical and analog information into digital inputs about their local environment (Lammel, 2015, Zhu et al., 2020), that can be processed by MCUs in real-time. Some examples of MEMS are accelerometers, microphones, or pressure sensors. Table 1.5 provides examples of different sensor types and their applications. Thus, they provide an interface to sense real-world information from hardware to software.

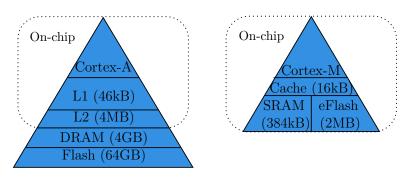

MCUs are miniaturized computers that are non-invasive (~1 mm<sup>2</sup> silicon area), cheap (~1\$), low-power ( $\leq 0.5$  W), and are dedicated to performing one task for months or even years within a device (Banbury et al., 2021a, Garbay et al., 2022). MCUs are composed of connectors, input/output interface, on-chip storage (ROM), volatile memory (SRAM) for intermediate data, and a CPU with a frequency usually below the 10<sup>3</sup> MHz range (Banbury et al., 2021a). With over 250 billion MCUs already in use, forecasts predict a volume of 38.2 billion in 2023 alone (Lin et al., 2020). In this context, we emphasize that even a small difference in the power footprint between low-power hardware targets can translate to several billions of dollars in savings for the consumer market. This is exemplified by the 2\$ difference observed between the low-end of MCUs in Table 1.4. Even between MCUs, there are several orders of magnitude in terms of low-power (Table 1.4). For example, the Cortex-M4 only consumes 0.1W, yet it still represents a target that is 1500 times more power-hungry and 20 times more memory (SRAM) capacity compared to the Cortex-M0+. Additionally, it is three times more costly for consumers. Consequently, it is important to highlight the strong industrial incentive to target the low-cost and low-power consumer market as much as possible with tiny hardware targets. By focusing on the power scale between these targets, we can realize billions in cost savings and other benefits that low-power MCUs offer for the consumer market.

**Applicability.** Sensing data at the edge allows for offline operations, as opposed to using online cloud computing, always-on and real-time processing, no network latency,

Table 1.4 Comparison of hardware for cloud, mobile, and TinyML, including the MCU targeted in this work, provided by TDK InvenSense (Banbury et al., 2021a, Saha et al., 2022).

| Platform                                                | Architecture                                          | Memory                               | Storage                                       | Frequency                              | Power                        | FLOPS                        | Price             |

|---------------------------------------------------------|-------------------------------------------------------|--------------------------------------|-----------------------------------------------|----------------------------------------|------------------------------|------------------------------|-------------------|

| <b>Cloud</b><br>Nvidia V100S                            | GPU<br>NVIDIA Volta                                   | HBM<br>32GB                          | SSD/Disk<br>TB~PB                             | 1.2GHz-1.3GHz                          | 250W                         | ~16.4G                       | 14500\$           |

| Mobile<br>Galaxy Note 20                                | CPU<br>Kryo 585                                       | DRAM<br>8GB                          | Flash<br>128GB                                | 1.8GHz-3.1GHz                          | ~8W                          | 1.2T                         | 550\$             |

| TinyML<br>SAME70Q21B<br>SAMG55J19<br>Newport<br>Newport | MCU<br>Cortex-M7<br>Cortex-M4<br>Cortex-M0+<br>eDMPv1 | SRAM<br>384kB<br>160kB<br>8kB<br>4kB | eFlash/ROM<br>2048kB<br>512kB<br>16kB<br>16kB | 300MHz<br>120MHz<br>6.14MHz<br>6.14MHz | 0.3W<br>0.1W<br>70μW<br>66μW | ~432M<br>~180M<br>N/A<br>N/A | 5\$<br>3\$<br>1\$ |

limited energy overhead, and inherent privacy. MCUs are ubiquitous in modern electronic devices, including cars, mobiles, TVs, and cameras. Their high volume in the consumer market and wide applicability reinforce the significance of research and industry efforts in tinyML applications.

In this work, we target the most extreme low-end range of MCUs, with less than 8kB of RAM and 10MHz processing speed for extreme low-power deep learning inference. Therefore, we aim to push the hardware limit that is currently not considered in the state-of-the-art for embedded deep learning. In particular, we focus on the common ARM Cortex-M series microcontrollers (Yiu, 2019), and particularly the Cortex-M0+ and M4 (Table 1.4), or the eDMPv1 depending on the application. Hardware is provided by TDK InvenSense.

# 1.2.2 Scope of applications

As previously stated, the ability to embed neural networks at the edge can already benefit a wide variety of applications and can potentially lead to completely new types of products (Kanjo, 2022).

In this work, we will focus on motion detection, gesture recognition, such as human activity recognition (HAR), and keyword spotting. Note that these are all wireless applications, that must operate in real-time and are always-on. In this context, the device returns a decision at all times, so it is expected to provide a seamless user experience (e.g., not missing any user intention (false negatives) or over-triggering (false positives)). Their sensor types and target devices are specified in Table 1.5. Data is provided by TDK InvenSense.

| Sensor types   | Applications                            | Target devices         |

|----------------|-----------------------------------------|------------------------|

| Accelerometer, | Human activity recognition,             |                        |

| Gyroscope,     | gesture recognition, motion detection,  | Arm Cortex-M0+, eDMPv1 |

| Magnetometer   | voice detection, predictive maintenance |                        |

| Pressure       | Fingerprint detection                   | Arm Cortex-M0+, M4     |

| Microphone     | Sound classification, keyword spotting  | Arm Cortex-M4, M7      |

Table 1.5 Example of sensor applications and their target MCU devices. We indicate our focus applications in italics.

# 1.2.3 Challenges of ultra-low power hardware

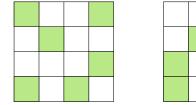

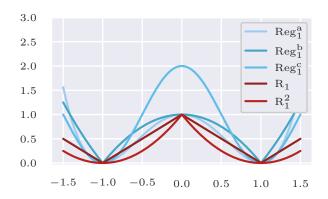

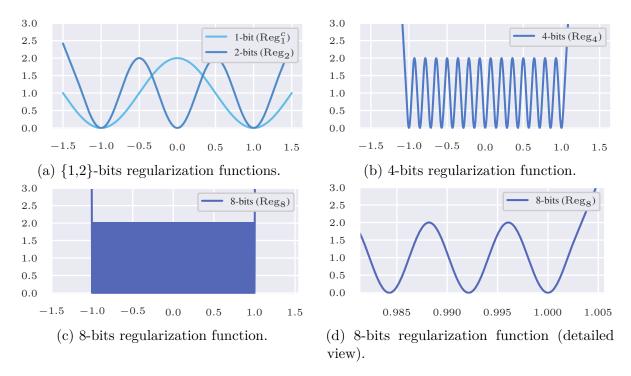

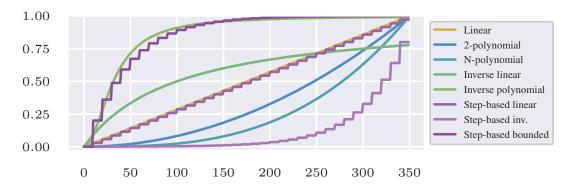

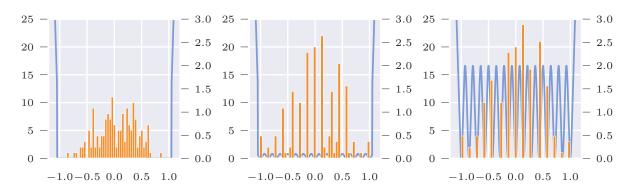

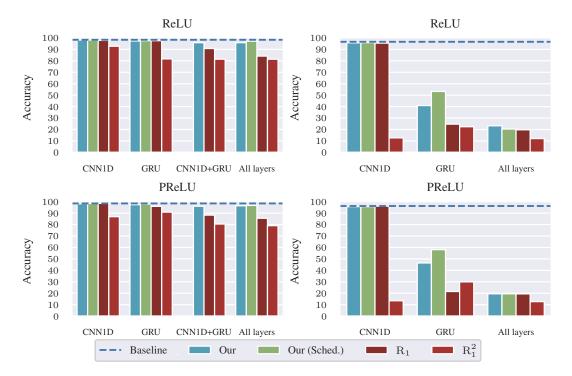

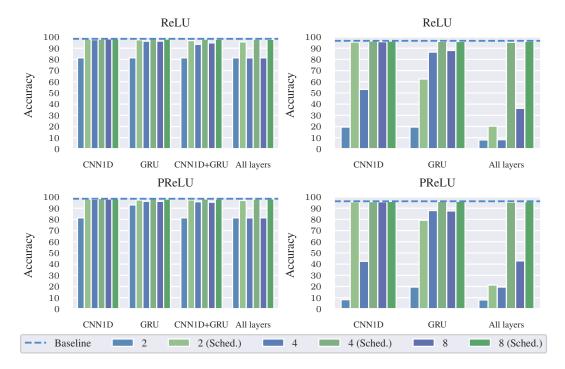

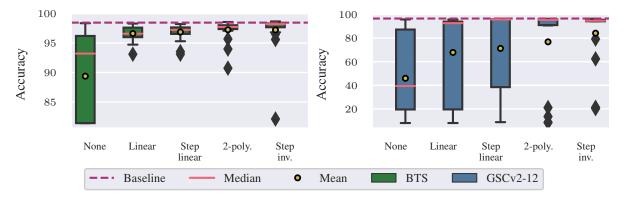

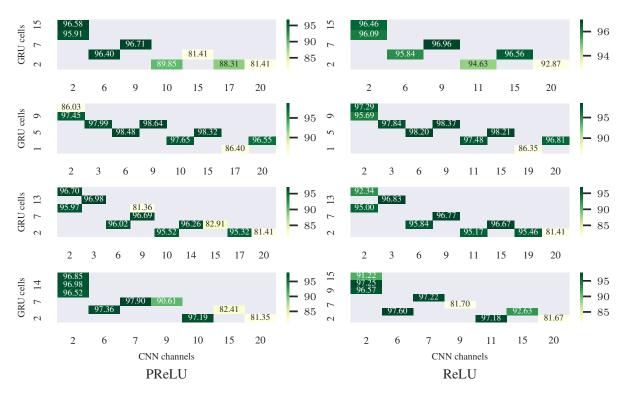

Fig. 1.3 Illustration of memory hierarchies for a mobile processor (left) and an Arm Cortex-M7 microcontroller (right). The microcontrollers process all computation and data transfer on-chip.