# Conception de systèmes efficaces en énergie dédiés à l'inférence bayésienne exploitant des nouvelles technologies mémoires

Clément Turck

### ▶ To cite this version:

Clément Turck. Conception de systèmes efficaces en énergie dédiés à l'inférence bayésienne exploitant des nouvelles technologies mémoires. Intelligence artificielle [cs.AI]. Université Paris-Saclay, 2023. Français. NNT: 2023UPAST166. tel-04381851

## HAL Id: tel-04381851 https://theses.hal.science/tel-04381851

Submitted on 9 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Conception de systèmes efficaces en énergie dédiés à l'inférence bayésienne exploitant des nouvelles technologies mémoires

Energy efficient bayesian reasoning using novel memory technologies

### Thèse de doctorat de l'université Paris-Saclay

École doctorale n° 575, electrical, optical, bio : physics and engineering (EOBE) Spécialité de doctorat : Electronique, Photonique et Micro-Nanotechnologies Graduate School : Sciences de l'ingénierie et des systèmes Référent : Faculté des sciences d'Orsay

Thèse préparée dans l'unité de recherche Centre de Nanosciences et de Nanotechnologies (Université Paris-Saclay, CNRS), sous la direction de **Damien QUERLIOZ**, Directeur de Recherche, le co-encadrement de **Jean-Michel PORTAL**,

Professeur des Universités

Thèse soutenue à Paris-Saclay, le 27 novembre 2023, par

### **Clément TURCK**

### **Composition du Jury**

Membres du jury avec voix délibérative

| Jérôme SAINT MARTIN                                |                          |

|----------------------------------------------------|--------------------------|

| Professeur des universités, Ecole Normale          | Président                |

| Supérieure Paris-Saclay                            |                          |

| Alberto BOSIO                                      | Dannartour & Evaminatour |

| Professeur des universités, Ecole Centrale de Lyon | Rapporteur & Examinateur |

| Louis HUTIN                                        |                          |

| Cadre scientifique des EPIC (HDR), CEA, Université | Rapporteur & Examinateur |

| Grenoble Alpes                                     |                          |

| Marina REYBOZ                                      |                          |

| Cadre scientifique des EPIC, CEA, Université       | Examinatrice             |

| Grenoble Alpes                                     |                          |

**Titre :** Conception de systèmes efficaces en énergie dédiés à l'inférence bayésienne exploitant des nouvelles technologies mémoires

Mots clés: Inférence bayésienne, Mémoire, Efficacité énergétique

Résumé: L'intelligence artificielle (IA) est centrale aux avancées actuelles, dont l'analyse de données et la médecine. Des modèles comme ChatGPT et Dall-E exploitent le cloud, centralisant d'immenses volumes données. Cependant, leur consommation énergétique est problématique, spécialement pour des appareils à ressources limitées, vus comme une alternative à la centralisation. Par exemple, l'entraînement du modèle Llama-2 de Meta consomme autant qu'annuellement 33 foyers français. Une solution serait d'entraîner le modèle hors de l'appareil, puis d'exécuter l'inférence sur celui-ci, malgré les contraintes de performance. Audelà des défis énergétiques, l'IA est souvent pointée du doigt pour son manque de transparence. En médecine ou dans la conduite autonome, il est impératif de comprendre le raisonnement derrière chaque décision prise par l'IA.

Dans cette thèse, nous nous concentrons sur l'inférence bayésienne, une solution possible pour des modèles IA plus économes en énergie, explicites et transparents.

Dans le premier chapitre, nous explorons l'architecture Von-Neumann des circuits actuels puis nous abordons l'avancée des nouvelles architectures inspirées du fonctionnement du cerveau, mettant l'accent sur les memristors et leur potentiel pour le calcul en mémoire. Dans le deuxième et troisième chapitre, nous présentons une « machine bayésienne », de sa théorie à sa conception. L'explication de son fonctionnement est abordée, jusqu'à une application réelle de reconnaissance de geste, en passant par l'architecture de cette machine bayésienne. Dans cette partie, nous nous penchons sur une méthode de calcul qui permet de diminuer la consommation énergétique : le calcul stochastique. Elle est présentée comme une solution réduisant également l'encombrement des multiplicateurs nécessaires à l'inférence bayésienne.

Les applications pratiques de cette approche sont ensuite examinées dans la conception des circuits et les possibilités offertes pour une application pratique, la reconnaissance des gestes, sont explorées. Ensuite, la performance de l'inférence bayésienne pour cette application est évaluée dans des contextes à faible volume de données, et le caractère explicable de la machine est étudié. Les étapes du processus de fabrication sont ensuite détaillées, en mettant en lumière les innovations récentes dans la structuration et la programmation de cette machine. Nous explorons également les défis et les opportunités associés à la mesure et à la caractérisation de ces systèmes, avant de conclure avec une discussion sur les perspectives d'amélioration de l'efficacité énergétique. Le chapitre est consacré à comparaison entre deux architectures de calcul pour une machine, le calcul stochastique étudié précédemment et le calcul logarithmique nouvellement développé. Nous faisons comparaison tant en termes d'application, sur la reconnaissance de geste et également sur une application plus médicale qu'est la reconnaissance des cycles du sommeil, qu'en termes énergétiques. Par la suite, une intégration de cette puce dans un système est présentée, composé d'un cœur RISC-V et d'une nouvelle puce multimode de calcul avec une plus grande capacité mémoire. En conclusion, la recherche, tant du côté software, avec les différentes applications possibles de l'inférence bayésienne, que du côté hardware, avec l'intégration des nouvelles technologies mémoires comme les memristors et l'intégration des systèmes de collecte d'énergie, est présentée comme une étape importante dans l'innovation de l'intelligence artificielle à faible consommation d'énergie et plus particulièrement de l'intelligence artificielle embarquée.

Title: Energy efficient bayesian reasoning using novel memory technologies

**Keywords:** Energy efficient, Bayesian Inference, Memory

Abstract: Artificial Intelligence (AI) plays a key role in modern advancements, especially in data analysis and healthcare. Large models, such as ChatGPT and Dall-E, rely on cloud platforms, consolidating vast amounts of data. However, their high energy consumption poses challenges, particularly for devices with limited resources, which are seen as a decentralizing alternative. For context, training the Llama-2 model from Meta uses as much energy as 33 French households consume in a year. One solution might be to train the model externally and then run the inference on the device itself, even with performance challenges. Beyond energy concerns, Al's lack of transparency is a critique. In medical applications or autonomous driving, understanding Al decision-making is crucial.

In this thesis, we will investigate Bayesian inference, a potential answer for energy efficient, clearer, and more transparent Al models.

In the first chapter, we delve into the von Neumann architecture of current circuits, followed by a look at the advancements in new architectures inspired by the brain's function. The role of memristors and their potential for in-memory computing are emphasized. In the second and third chapters, we discuss a "Bayesian machine", from its theoretical foundation to its design. This includes an explanation of its operation and its real-world application in gesture recognition, taking into account the architecture of this Bayesian machine. The machine relies on stochastic computing, a computing method that reduces energy consumption.

This approach also helps minimize the size of multipliers used in Bayesian inference. Its practical applications in circuit design are then assessed, particularly for gesture recognition. Additionally, the efficiency of Bayesian inference in scenarios with limited data is evaluated and the machine's explainability is explored. The next chapter details the manufacturing process of the machine, spotlighting recent innovations in the structuring and programming of the machine. Challenges and opportunities associated with measuring and characterizing these systems are also delved into, concluding with thoughts on energy efficiency improvements. The fourth chapter contrasts two computational architectures for machines: the previously discussed stochastic computing and the newly introduced logarithmic computing. They are compared both in terms of applications - from gesture recognition to a medical application of sleep cycle detection - and in energy efficiency. The integration of the chip into a system with a RISC-V core and a new multimode computing chip with enhanced memory capacity is then presented. In conclusion, research, both from the software perspective with the varied applications of Bayesian inference, and the hardware side with the adoption of innovative memory technologies like memristors and energy harvesting systems, signifies a crucial step in the advancement of low-energy Al, specifically embedded AI.

À ma grand-mère qui, je sais, d'où elle est, est fière de moi. À ma famille. vi REMERCIEMENTS

# Remerciements

Je tiens avant tout à exprimer ma profonde gratitude à mon directeur de thèse, Damien pour m'avoir déjà supporté puis soutenu et encouragé pendant ces trois et quelques années. Ton expertise et tes conseils précieux m'ont permis de réaliser pleinement ce travail de recherche. J'ai vraiment passé trois belles années à tes côtés. Je remercie également Jean-Michel qui m'a co-encadré. Nos échanges et tes conseils m'ont énormément apportés. Je tiens à remercier l'ensemble des membres du jury, Louis Hutin, Alberto Bosio, Marina Reyboz, Jérome Saint-Martin et David Novo pour d'une part avoir bien voulu faire partie de mon jury et d'avoir étudié mon manuscrit et d'autre part pour les critiques constructives et leurs discussions enrichissantes.

J'ai fait partie d'une équipe formidable durant cette thèse, IntegNano. Tout d'abord, merci à mon binôme, Kamel, sans qui aucune des puces n'auraient pu être envoyées en production, nous avons été vraiment complémentaires sur l'intégralité de nos travaux respectifs. Nous avons tellement travaillés ensemble que nous sommes co-auteurs de tous nos articles. Je te souhaite de trouver ton équipe de Foot miniature. Merci à Marie, jumelle de thèse comme elle aimait m'appeler, nous avons commencé le même jour et fini avec juste une semaine d'écart. Notre soutient mutuel lors de la rédaction m'a permis d'avancer rapidement. Je te souhaite une belle réussite dans ta carrière pour que tu puisse réaliser ton rêve d'achat. Merci à Maryam, ma co-bureau pendant un an et demi, j'ai vraiment aimé nos discussions tant sur le travail que sur la vie en général. Je te souhaite une belle réussite dans ta carrière. Merci à Atreya, ton enthousiasme et ta passion pour la nourriture m'a toujours fasciné. Merci à Tifenn pour avoir lancé le projet avec Kamel. Merci à Théo pour tes discussions sur l'architecture des ordinateurs et le RISC-V, j'ai beaucoup appris. Merci à Adrien R., l'éternel stagiaire, en stage dans l'équipe depuis la licence, tu as su réaliser le travail d'un doctorant pour la mise en place des setups de test. J'ai vraiment adoré travailler avec toi. Merci à Adrien P. je te souhaite de trouver ton expression dans le théâtre. Merci à Thomas pour ta bonne humeur dans le labo. Merci à Tanvi pour tes conseils sur les enfants, je te souhaite beaucoup de bonheur avec ta famille. Merci à Gyan pour ton entrain, ta bonne humeur et ta joie de vivre. Merci à Akib pour tes anecdotes intéressantes sur ton pays. Merci à Liza, j'adore vraiment tes tableaux. Merci au reste de l'équipe, Djohan qui va bientôt finir, Bastien, Guillaume. Enfin, merci à toutes les personnes avec qui j'ai travaillé, discuté et partagé des bons moments, Thibaut, Rohit, Fadi, Elmer, Maïkane, Matthieu, Yanis, Song et Louis.

Je remercie également toute ma famille et belle famille, c'est grâce à eux que j'ai pu terminer toutes ces longues années d'études. Je me souviens des séances de révisions avec ma maman le soir pour apprendre mes leçons, mes poésies, mes tables de multiplications. Je me souviens des séances de bricolage avec mon papa, enfin, j'étais plus le commis qui tenait la lampe mais c'est des moments précieux pour moi. Je me souviens des séances de jeux avec mon frère, de nos chamailleries aussi. Je me souviens des moments passés avec mes grand-parents, des sorties

REMERCIEMENTS vii

au parc avec mamie Roselyne et tonton Nono, des nuits passées chez mamie Françoise et mon parrain, à jouer aux petites voitures. Je me souviens des vacances passées chez ma marraine à regarder Fort-Boyard sur le petit écran de la télé, des sorties avec mes cousines et leurs enfants. Je me souviens des anniversaires chez Nathalie, avec Benjamin et Laurine que je considère comme mes cousins. Je me souviens et, là, c'est plus récent (enfin 10 ans quand même) de l'accueil chaleureux, de l'amour immédiat de Frédéric et Isabelle que j'ai eu en arrivant dans la famille de ma femme. Tous ces moments, tous ces souvenirs m'ont vraiment aidé dans la réalisation de cette thèse et je veux vraiment dire un grand **merci** à tout le monde pour leur soutien.

Guillaume, je ne vais pas écrire un paragraphe sur toi uniquement mais tu as ta petite marque dans cette thèse. Je sais que j'ai fait un sacrilège en inversant les titres mais après toutes ces années, tu me le pardonneras. Merci, d'être mon meilleur ami depuis l'école primaire, merci d'avoir été toujours présent à mes côtés. Un grand merci aussi à mes amis de longue date pour les bons moments passés ensemble, Thibaut, Fouad, Son-Dorian, Quentin, Julien, Rémy et Antoine.

Enfin, la dernière personne mais la plus importante à mes yeux, celle qui m'a soutenu quand j'avais des coups de mou, celle qui m'a encouragé, celle qui m'a poussé à aller jusqu'au bout, celle qui m'a donné un fils, mon petit Léandre qui a assisté dans le ventre de sa maman à ma soutenance, ma chipoustouquette chérie comme je l'appelle souvent, bref, Alicia, ma femme, je t'aime et merci.

Voilà, j'ai fini je pense. Je m'excuse si j'ai oublié quelqu'un, je remercie toutes celles avec qui j'ai discuté et qui m'ont écouté.

Normalement, les remerciements dans les films sont à la fin, mais pour cette thèse, je vais faire une exception. Je vous laisse maintenant profiter de la lecture et bon visionnage.

Clément

Le petit post-scriptum de la fin : des parties de ce manuscrit ont été révisées avec l'aide d'un grand modèle de langage (OpenAI ChatGPT).

viii REMERCIEMENTS

# **Contents**

| In | ntroduction |         |                                                                 | 1  |

|----|-------------|---------|-----------------------------------------------------------------|----|

| 1  | Éne         | rgie et | Mémoires résistives : Un voyage inattendu                       | 7  |

|    | 1.1         | Vers u  | ne optimisation de l'efficacité énergétique des circuits        | 8  |

|    |             | 1.1.1   | Évolution des circuits et de l'architecture de Von-Neumann      | 8  |

|    |             | 1.1.2   | Architecture inspirée par le Cerveau                            | 13 |

|    | 1.2         | A u     | ne nouvelle technologie de mémoire : les memristors             | 17 |

|    |             | 1.2.1   | Mémoires actuelles : SRAM, DRAM, Flash                          | 17 |

|    |             | 1.2.2   | Différents types de memristors                                  | 19 |

|    |             | 1.2.3   | Leur intégration pour le calcul en mémoire                      | 21 |

| 2  | Lac         | ommu    | mauté de la Machine Bayésienne                                  | 29 |

|    | 2.1         | Princi  | ipes Fondamentaux de l'Approche Bayésienne                      | 30 |

|    |             | 2.1.1   | Indépendance Conditionnelle : Au-delà de l'Approximation Naïve  | 31 |

|    |             | 2.1.2   | Techniques de Multiplication dans l'Analyse Bayésienne          | 32 |

|    | 2.2         | Intégi  | ration de la Machine Bayésienne dans la Conception des Circuits | 34 |

|    |             | 2.2.1   | Exploration de l'Architecture                                   | 34 |

|    |             | 2.2.2   | L'Importance du Choix des Seeds                                 | 38 |

|    | 2.3         | Appli   | cation Pratique : Reconnaissance des Gestes                     | 41 |

|    |             | 2.3.1   | Fonctionnement de l'Application                                 | 41 |

|    |             | 2.3.2   | Analyse des Résultats                                           | 43 |

|    |             | 2.3.3   | Vers une Explicabilité Accrue                                   | 49 |

|    |             | 2.3.4   | Performances sur des Ensembles de Données Réduits               | 53 |

| 3  | Mad         | chine E | Bayésienne II, le retour du roi                                 | 57 |

|    | 3.1         | Desig   | n et Fabrication de la Puce Bayésienne                          | 58 |

|    |             | 3.1.1   | Processus de Fabrication                                        | 58 |

|    |             | 3.1.2   | Structure 2T2R                                                  | 59 |

|    |             | 3.1.3   | Étape de Programmation                                          | 59 |

|    |             | 3.1.4   | Étapes de Lecture et d'Inférence                                | 61 |

|    |             | 3.1.5   | Synthèse : Étapes pour l'Utilisation de la Machine Bayésienne   | 63 |

CONTENTS

|    | 3.2   | Analy   | se Approfondie : Mesures et Caractérisation                                       | 70        |

|----|-------|---------|-----------------------------------------------------------------------------------|-----------|

|    |       | 3.2.1   | Exploration des Applications à Faible Tension : La Puce sans Package $$ . $$ .    | 70        |

|    |       | 3.2.2   | La Puce Packagée : Comprendre les Perturbations de Lecture                        | 72        |

|    | 3.3   | Estim   | ations des Performances Énergétiques                                              | 76        |

|    |       | 3.3.1   | Simulations : Un Outil pour l'Analyse Énergétique                                 | 76        |

|    |       | 3.3.2   | Conclusion et Perspectives d'Améliorations                                        | 79        |

| 4  | Mad   | chine B | Bayésienne III, les deux modes!                                                   | 83        |

|    | 4.1   | Une N   | Machine Bayésienne Logarithmique                                                  | 84        |

|    |       | 4.1.1   | Le Calcul Logarithmique                                                           | 84        |

|    |       | 4.1.2   | Une Nouvelle Application : les Cycles du Sommeil                                  | 85        |

|    |       | 4.1.3   | Comparaison des Deux Méthodes de Calcul                                           | 89        |

|    | 4.2   | Mesu    | res de la Nouvelle Puce                                                           | 94        |

|    |       | 4.2.1   | Reconnaissance des cycles du sommeil                                              | 94        |

|    |       | 4.2.2   | Intégration de la Machine Bayésienne dans un Coeur RISC-V                         | 95        |

|    | 4.3   | Vers u  | ne Version Agrandie et Multi-Modes de la Machine Bayésienne                       | 97        |

| Co | nclu  | sions ( | et Perspectives                                                                   | 101       |

| Li | st of | publica | ations                                                                            | 107       |

| A  |       |         | A Multimode Hybrid Memristor-CMOS Prototyping Platform Supporting Analog Projects | ıg<br>109 |

| В  | Ann   | exe 2 : | Powering AI at the Edge: A Robust, Memristor-based Binarized Neural Ne            | t-        |

|    | wor   | k with  | Near-Memory Computing and Miniaturized Solar Cell                                 | 113       |

| C  | Ann   | exe 3   | : In situ learning using intrinsic memristor variability via Markov chai          | in        |

|    | Moı   | nte Car | lo sampling                                                                       | 129       |

| Bi | bliog | graphy  |                                                                                   | 150       |

# **List of Figures**

| 1   | Image de moi présentant ma thèse, générée par Stable Diffusion. Entraînenement du modèle en utilisant des photos de moi et l'environnement kohya_ss (https://github.com/bmaltais/kohya_ss) puis générée en utilsant l'environnement AUTOMATIC1111 (https://github.com/AUTOMATIC1111/stable-diffusion-webui) avec le modèle SD-XL [1] en 60 itérations. | 3               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

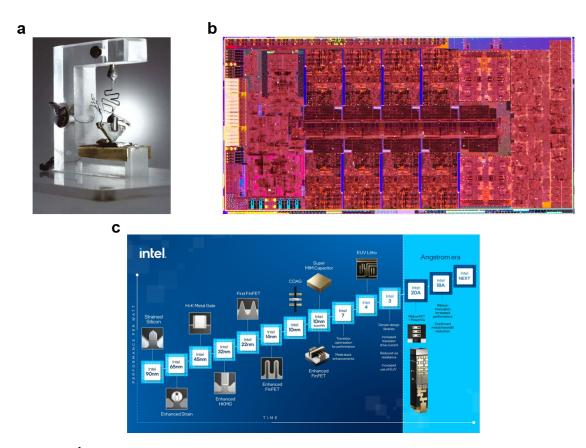

| 1.1 | Évolution du transistor : du premier aux 1000 milliards sur puce. a Le premier                                                                                                                                                                                                                                                                         |                 |

|     | transistor, développé par Walter Brattain et John Bardeen en 1947, source:Alcatel-                                                                                                                                                                                                                                                                     |                 |

|     | Lucent USA, Inc ${\bf b}$ Photo du die du i<br>9-12900K de Intel, source:<br>Intel et ${\bf c}$ Évolution                                                                                                                                                                                                                                              |                 |

|     | de la technologie de fabrication d'Intel, du passé au futur, source:https://www.intel.                                                                                                                                                                                                                                                                 | com/content/www |

|     | law.html                                                                                                                                                                                                                                                                                                                                               | 9               |

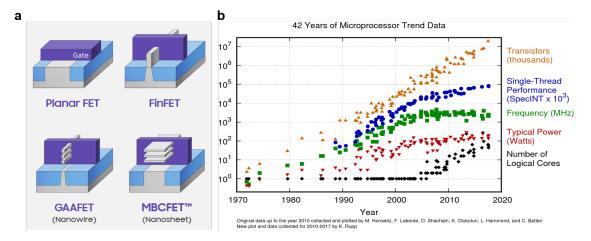

| 1.2 | Évolution du MOSFET. a Évolution de l'architecture du MOSFET, source : Sam-                                                                                                                                                                                                                                                                            |                 |

|     | sung, https://www.samsungfoundry.com/foundry/homepage.do <b>b</b> Graphe illus-                                                                                                                                                                                                                                                                        |                 |

|     | trant la fin de l'augmentation exponentielle des performances; la loi de Moore va                                                                                                                                                                                                                                                                      |                 |

|     | sûrement se terminer aussi, tiré de [2]                                                                                                                                                                                                                                                                                                                | 10              |

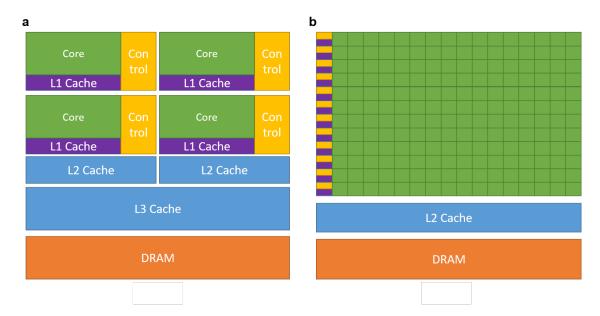

| 1.3 | Architecture des ordinateurs actuels. a Schéma d'une architecture d'un CPU                                                                                                                                                                                                                                                                             |                 |

|     | simplifiée et ${\bf b}$ d'un GPU, adapté de la documentation CUDA de NVIDIA                                                                                                                                                                                                                                                                            | 11              |

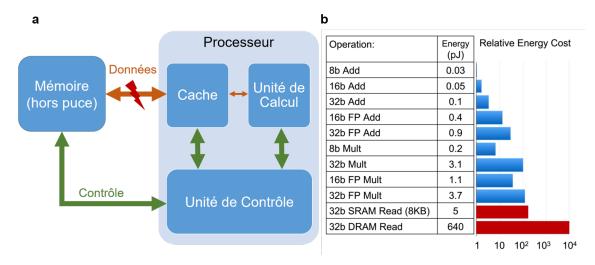

| 1.4 | Limites de l'architecture de Von Neumann. a Schéma d'une architecture d'un                                                                                                                                                                                                                                                                             |                 |

|     | CPU simplifiée avec le goulot d'étranglement de Von Neumann à cause de la sé-                                                                                                                                                                                                                                                                          |                 |

|     | paration physique de la mémoire et du calcul et <b>b</b> Coûts énergétiques pour dif-                                                                                                                                                                                                                                                                  |                 |

|     | férentes opérations arithmétique comparés aux coûts pour l'accès mémoire, tiré                                                                                                                                                                                                                                                                         |                 |

|     | de [3]. L'accès à la DRAM est 4 ordres de grandeur plus énergivore que l'addition                                                                                                                                                                                                                                                                      |                 |

|     | sur 8 bits                                                                                                                                                                                                                                                                                                                                             | 13              |

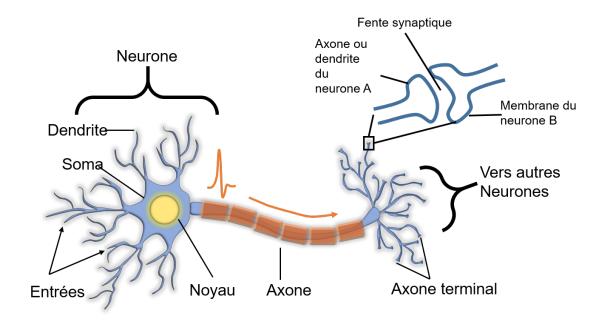

| 1.5 | Schéma d'un neurone. Les signaux neuronaux entrent par les dendrites, des                                                                                                                                                                                                                                                                              |                 |

|     | $branches  vastes  et  \acute{e}paisses  qui  \acute{e}mergent  du  soma,  et  sont  recouvertes  de  synapses.$                                                                                                                                                                                                                                       |                 |

|     | Ces signaux, appelés potentiels d'action, transitent ensuite vers d'autres neu-                                                                                                                                                                                                                                                                        |                 |

|     | rones via des axones. Ces derniers, capables de s'étendre sur de grandes dis-                                                                                                                                                                                                                                                                          |                 |

|     | tances, peuvent atteindre plus d'un mètre de long et se ramifient de nombreuses                                                                                                                                                                                                                                                                        |                 |

|     | fois pour permettre une communication efficace. Un seul neurone peut ainsi in-                                                                                                                                                                                                                                                                         |                 |

|     | tágrar plus de 10 000 sypanses (Scháma adaptá de Shuai Li)                                                                                                                                                                                                                                                                                             | 1.4             |

xii LIST OF FIGURES

| 1.6  | Applications de l'inspiration du cerveau. a Réseau de neurones pour identifier                     |       |

|------|----------------------------------------------------------------------------------------------------|-------|

|      | un chat et <b>b</b> Architecture pour le calcul proche mémoire où les neurones (unités             |       |

|      | de calcul) sont co-localisés avec les synapses (mémoire)                                           | 17    |

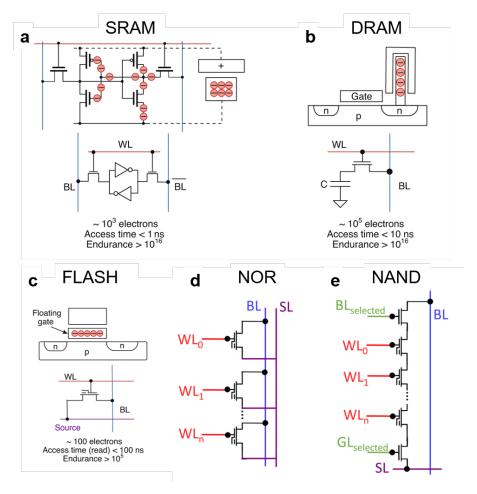

| 1.7  | Différentes technologies de mémoire. a Mémoire SRAM composée de 6 transis-                         |       |

|      | tors formant deux inverseurs tête-bêche ${\bf b}$ Mémoire DRAM comprenant un con-                  |       |

|      | densateur C réalisant le stockage, connecté en série avec un transistor FET ${\bf c}$ Mé-          |       |

|      | moire FLASH, le stockage est ici effectué par une porte flottante d'un transistor                  |       |

|      | FET et peut être utilisé pour <b>d</b> la structure NOR ou <b>e</b> la structure NAND, tiré de [4] | 19    |

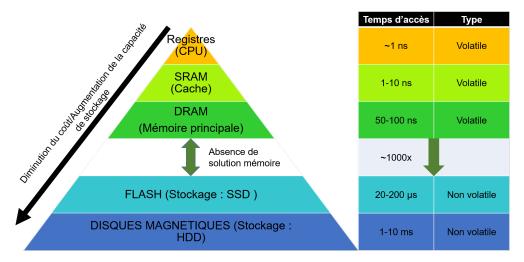

| 1.8  | Hiérarchie de la mémoire et comblement du trou avec les nouvelles technolo-                        |       |

|      | gies de mémoires                                                                                   | 20    |

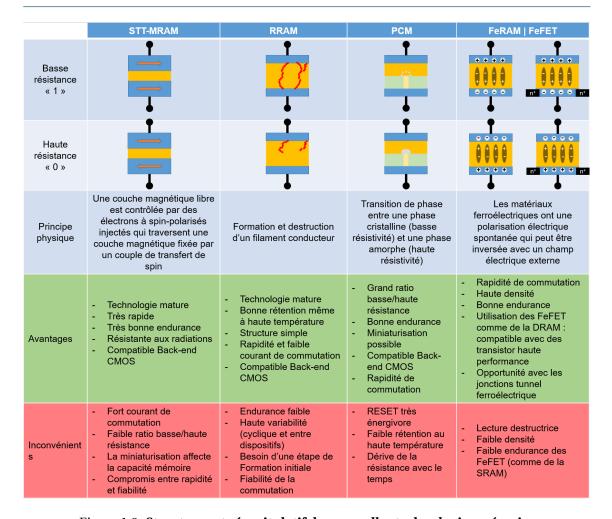

| 1.9  | Structures et récapitulatif des nouvelles technologies mémoire                                     | 22    |

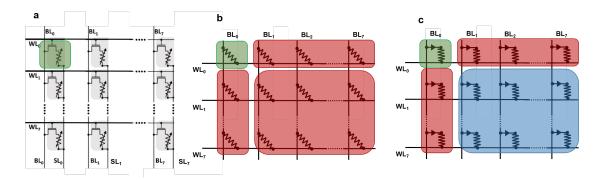

| 1.10 | Structures d'utilisation des nouvelles technologies mémoire. a 1T1R, cellule                       |       |

|      | composée d'un transistor et d'un memristor, ${\bf b}$ cellule composée uniquement                  |       |

|      | d'un memristor, l'application d'une différence de tension entre BL et WL sur la                    |       |

|      | cellule verte (celle programmée) se répercute sur l'ensemble des autres memris-                    |       |

|      | tors, en rouge, et <b>c</b> cellule composée d'un sélectionneur et d'un memristor (1S1R),          |       |

|      | seuls les cellules en rouge reçoivent la différence de tension, celles en bleu sont                |       |

|      | intactes                                                                                           | 23    |

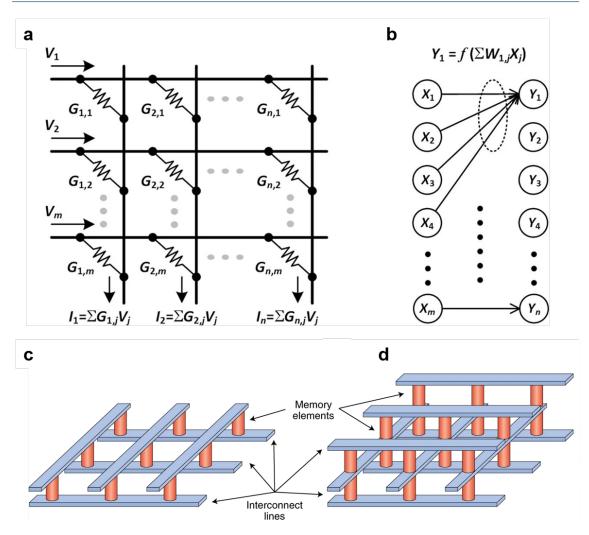

| 1.11 | Architecture crossbar pour le calcul en mémoire analogique a Schéma de l'archite                   | cture |

|      | crossbar pour réaliser les opérations MAC d'un ${\bf b}$ réseau de neurones, ${\bf c}$ structure   |       |

|      | croisée avec composée de RRAM sur une seule couche et ${\bf d}$ sur plusieurs couches              |       |

|      | (tiré de [5] et [6])                                                                               | 25    |

| 1.12 | 2 Architecture crossbar pour le calcul en mémoire avec sommation des résis-                        |       |

|      | tances a b c d (tiré de [6])                                                                       | 26    |

|      |                                                                                                    |       |

|      |                                                                                                    |       |

| La c | ommunauté de la Machine Bayésienne                                                                 | 29    |

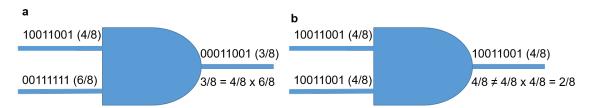

| 2.1  | Calcul stochastique pour deux flux de bits. a opération de multiplication si les                   |       |

|      | flux ne sont pas corrélés, le résultat est bien le produit des deux flux en entrée et              |       |

|      | ${f b}$ si les flux sont corrélés, le résultat ne correspond pas au produit des deux flux          |       |

|      | en entrée                                                                                          | 33    |

2

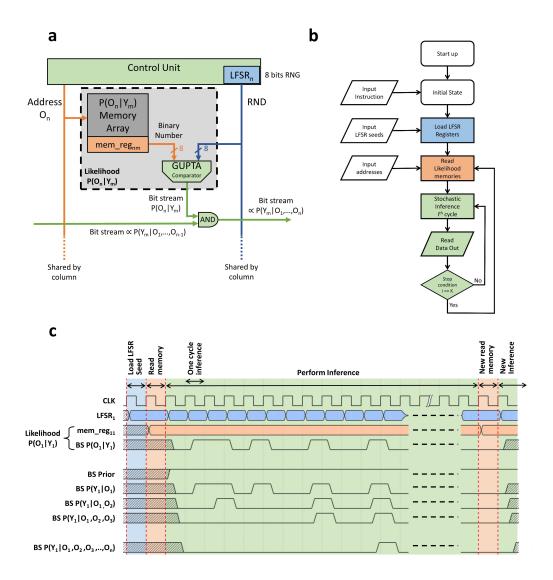

LIST OF FIGURES xiii

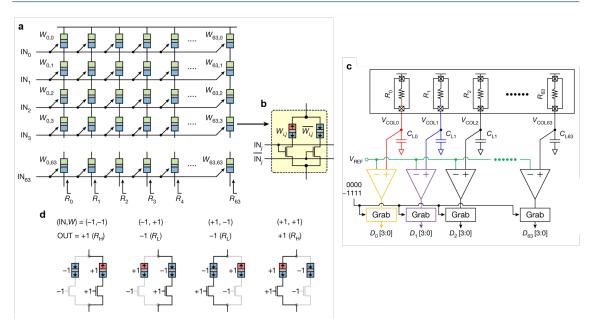

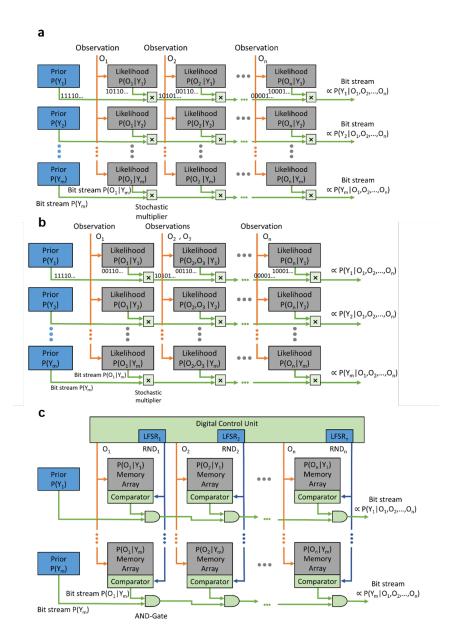

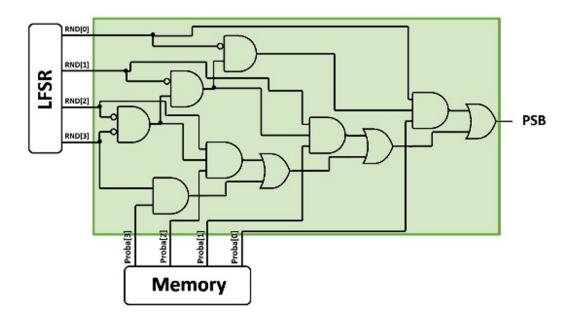

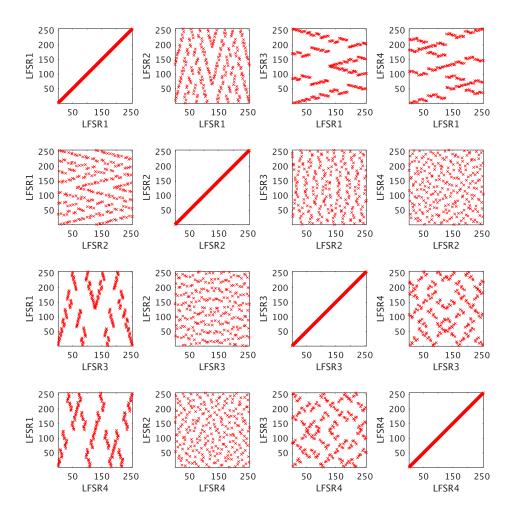

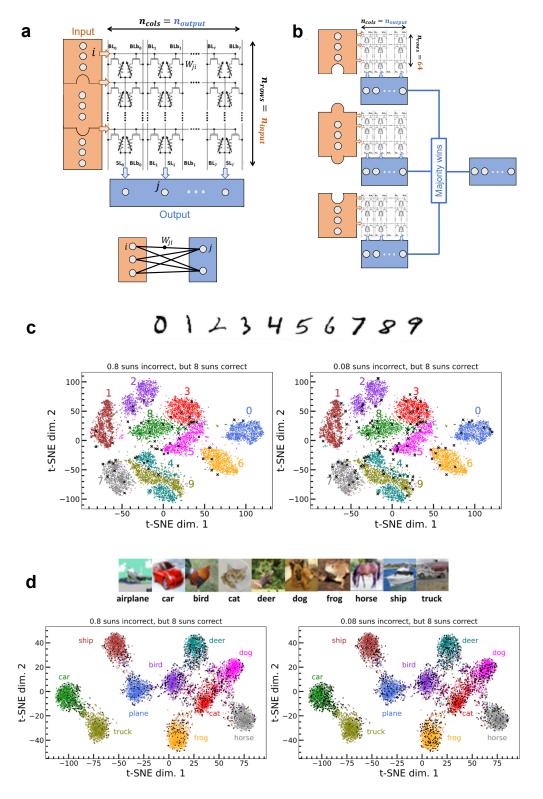

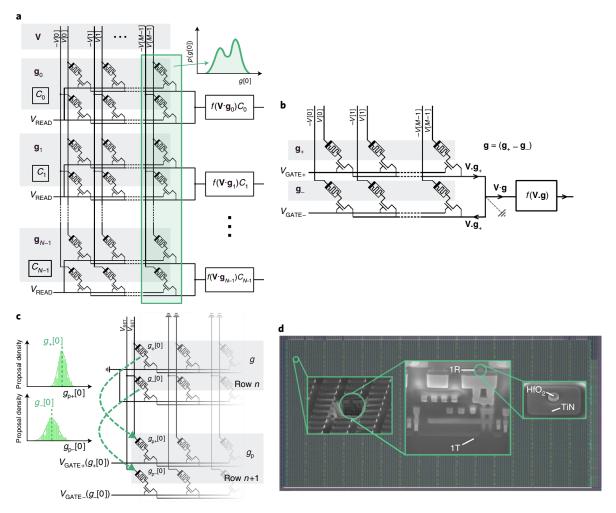

2.2 Architecture générale de la machine bayésienne. a Architecture générale. Les vraisemblances sont stockées dans des matrices de mémoire de vraisemblance implémentées par des matrices de memristors. Les observations du monde réel choisissent la valeur de probabilité appropriée à partir des matrices de mémoire de vraisemblance, sur la base desquelles des flux de bits stochastiques proportionnels sont générés et multipliés par un multiplicateur stochastique. En sortie, les flux de bits encodent naturellement la distribution a posteriori. **b** Architecture de la machine bayésienne avec des observations non conditionnellement indépendantes. Cette architecture réalise une inférence bayésienne non naïve suivant l'équation 2.5, en regroupant les observations  $O_2$  et  $O_3$  dans la même colonne. c Optimisation de la machine bayésienne pour le matériel. Des nombres aléatoires (RND) sont générés à l'aide de registres à décalage à rétroaction linéaire (LFSRs), partagés par colonne, puis convertis en utilisant des circuits numériques "Gupta" en une série de bits aléatoires proportionnels à la probabilité appropriée. De plus, les vraisemblances sont normalisées par la valeur de vraisemblance maximale de la colonne afin de maximiser la vitesse de convergence de la machine. La multiplication stochastique est mise en œuvre à l'aide d'une porte logique ET 36 2.3 Schéma du circuit comparateur de Gupta [7], utilisé pour générer le flux de bits aléatoires de vraisemblance en comparant la probabilité lue en mémoire avec le nombre aléatoire généré par le LFSR. Pour des raisons de compacité, le circuit est présenté ici dans une version à quatre bits. Une version à huit bits est mise en 37 2.4 Corrélations des nombres aléatoires générés par quatre LFSR, avec des graines initialement choisies au hasard Chaque graphique présente la sortie de l'un des quatre LFSR de la machine bayésienne, en fonction de la sortie d'un autre LFSR. Chaque graphique contient 255 points correspondant aux 255 cycles de fonctionnement de la machine bayésienne. Les graphiques sur la diagonale (LFSR1/LFSR1, LFSR2/LFSR2, LFSR3/LFSR3, LFSR4/LFSR4) apparaissent comme des lignes x=y, par définition. La présence de motifs très discernables dans certains des graphiques (LFSR1/LFSR3, LFSR1/LFSR4) indique l'existence d'une forte corrélation entre la sortie de certains LFSR. D'un autre côté, les sorties de certains LFSR semblent largement non corrélées (LFSR1/LFSR2, LFSR2/LFSR3, LFSR2/LFSR4). Les graines pour les quatre LFSR sont, respectivement, en représentation hexadécimale : 50,

39

xiv LIST OF FIGURES

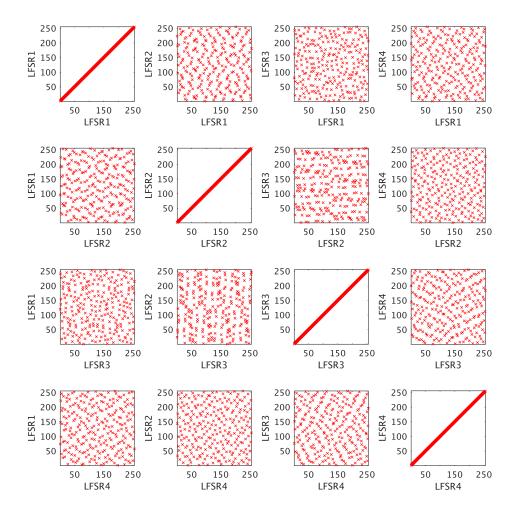

| 2.5 | <b>Corrélations des nombres aléatoires générés par quatre LFSR, avec les graines optimales.</b> Cette Figure, tracée avec les mêmes conventions que la Fig.2.4, montre l'absence de corrélation évidente entre les sorties des différents LFSR. Les graines pour les quatre LFSR sont, respectivement, en représentation hexadécimale : EB, FB, 7F, et 5C                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

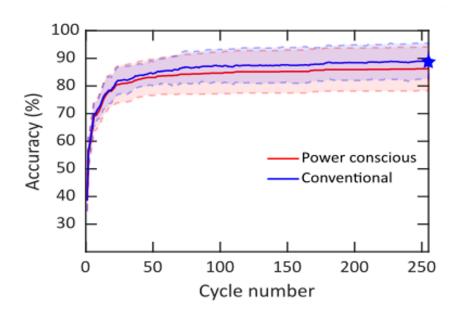

| 2.6 | Résultats de la machine bayésienne à une tâche pratique de reconnaissance de gestes. <i>Précision moyenne</i> en fonction du nombre de cycles pour deux types de calcul: en utilisant une méthode économe en énergie en ne prenant en compte que le premier '1' pour la décision (en rouge) et en utilisant le calcul stochastique conventionnel en utilisant le nombre maximum de '1' pour la décision (en bleu). Les ombres autour du graphique montrent un écart-type de la précision moyenne sur les dix sujets.                                                                                                                                                                                                                                                                           | 44 |

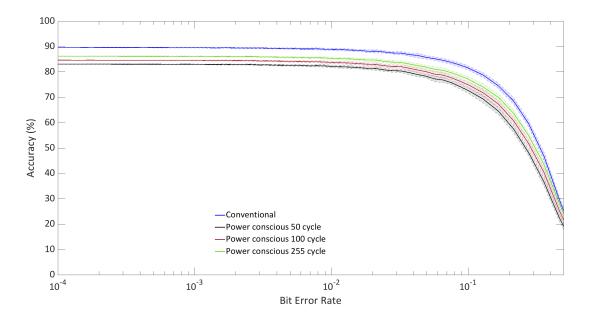

| 2.7 | Impact des erreurs sur les bits de mémoire sur la précision de la tâche de reconnaissance des gestes. Précision moyenne simulée sur la tâche de reconnaissance des gestes, lorsque des erreurs de bits ont été artificiellement introduites dans les bits de mémoire, en fonction du taux d'erreur de bit de mémoire. La simulation a été répétée 40 fois, les ombres autour du graphique montrent l'écart type de la précision moyenne le long de ces répétitions. Les résultats sont présentés pour le mode power-conscious avec un seuil à 50, 100, et 255 cycles, et pour le mode de calcul stochastique conventionnel utilisant tous les 255 cycles.                                                                                                                                      | 45 |

| 2.8 | Impact des erreurs uniques sur la précision de la tâche de reconnaissance des gestes. Précision moyenne simulée sur la tâche de reconnaissance des gestes, lorsque des erreurs uniques ont été artificiellement introduites dans le calcul, en fonction du taux d'erreur de bit de mémoire. Les erreurs uniques sont introduites à la sortie des circuits Gupta (c'est-à-dire sur les flux de bits stochastiques créés par chaque bloc de vraisemblance). La simulation a été répétée 100 fois, les ombres autour du graphique montrent un écart type de la précision moyenne le long de ces répétitions. Les résultats sont présentés pour le mode power-conscious avec un seuil à 50, 100, et 255 cycles, et pour le mode de calcul stochastique conventionnel utilisant tous les 255 cycles | 47 |

LIST OF FIGURES xv

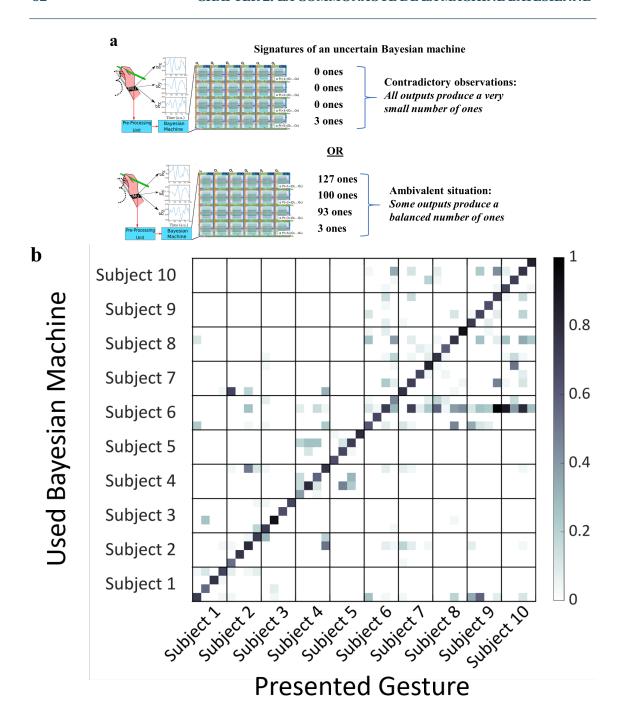

| 2.9  | Capacité de la machine bayésienne à identifier les situations incertaines. a       |

|------|------------------------------------------------------------------------------------|

|      | Illustration schématique des deux signatures d'une machine bayésienne incer-       |

|      | taine. <b>b</b> Réponse moyenne simulée de la machine bayésienne, pour la tâche    |

|      | de reconnaissance de gestes, dans des situations où un geste présenté à la ma-     |

|      | chine bayésienne peut provenir d'un sujet différent de celui sur lequel la ma-     |

|      | chine a été entraînée. Abscisse : geste présenté. Pour chaque sujet, les quatre    |

|      | points représentent les gestes un, deux, trois, et la signature. Ordonnée : ma-    |

|      | chine bayésienne utilisée. Les différents points représentent les différentes sor- |

|      | ties de la machine dans le même ordre que l'abscisse. Couleur : proportion de      |

|      | cas conduisant à la sortie dans l'ordonnée pour les gestes présentés correspon-    |

|      | dant à l'abscisse, avec la machine bayésienne fournissant une sortie certaine. Les |

|      | résultats sont présentés pour un seuil de certitude T de 10%                       |

|      |                                                                                    |

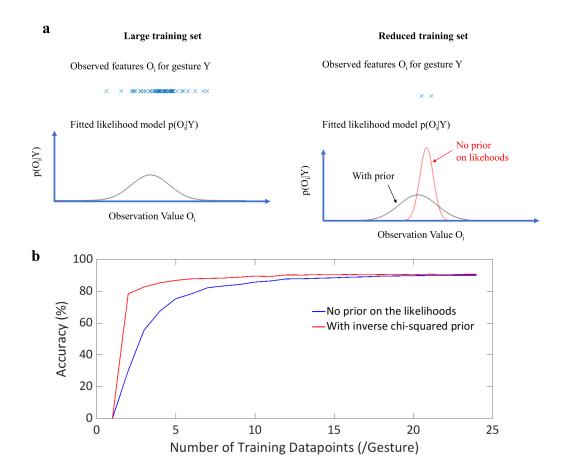

| 2.10 | Impact de la taille de l'ensemble de données d'entraînement sur la précision       |

|      | de la machine bayésienne. a Illustration du défi des petites données. Lors de      |

|      | l'utilisation d'un grand ensemble de données d'entraînement représentatif, les     |

|      | modèles de vraisemblance peuvent être ajustés directement aux données d'entraîneme |

|      | En revanche, les ensembles de données réduits peuvent ne pas être représen-        |

|      | tatifs, et l'ajustement direct d'un modèle de vraisemblance aux données peut       |

|      |                                                                                    |

xvi LIST OF FIGURES

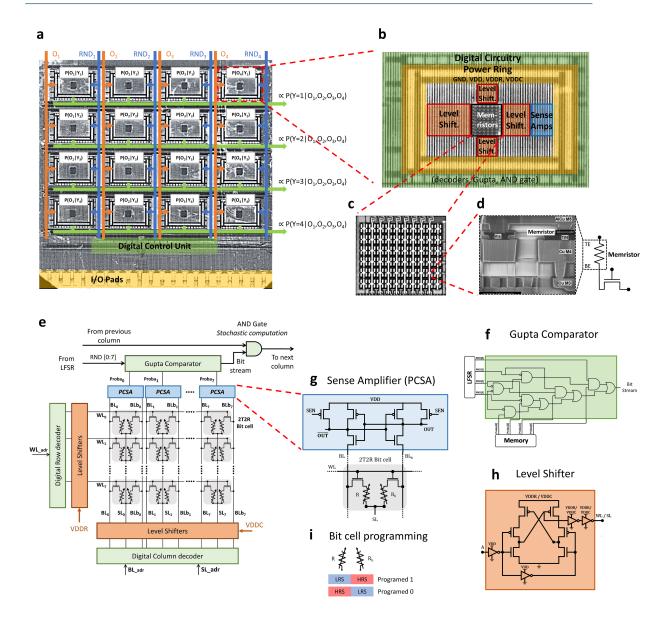

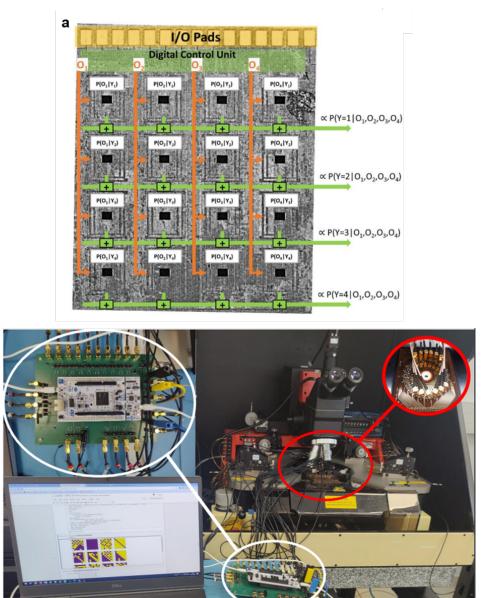

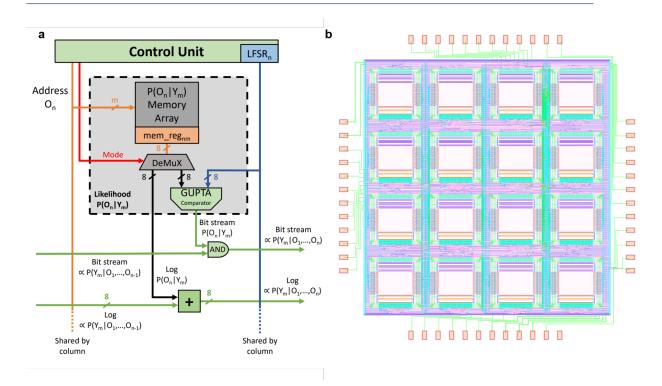

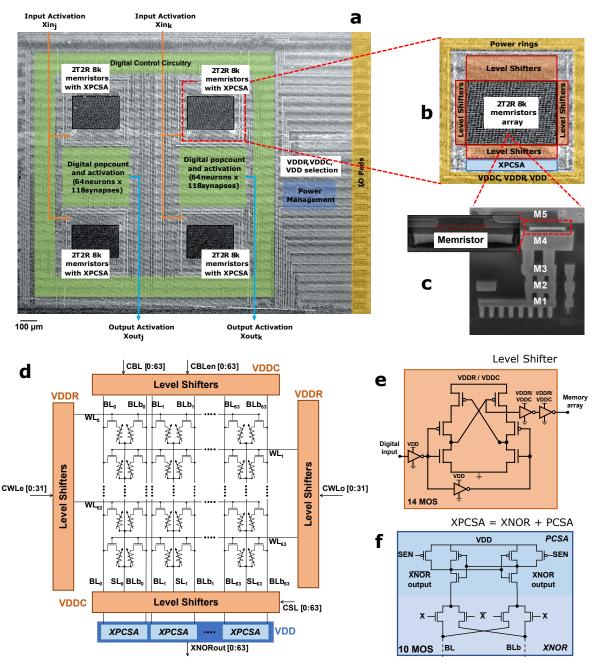

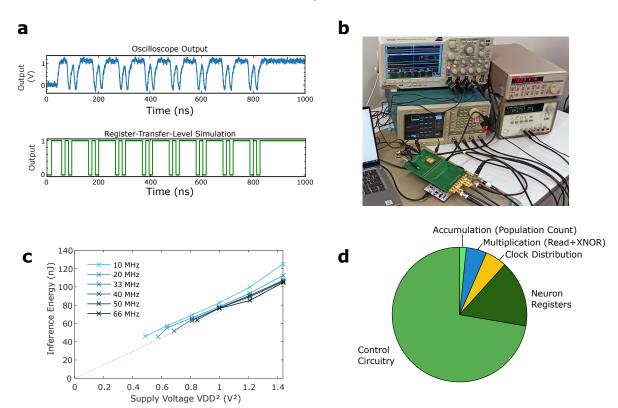

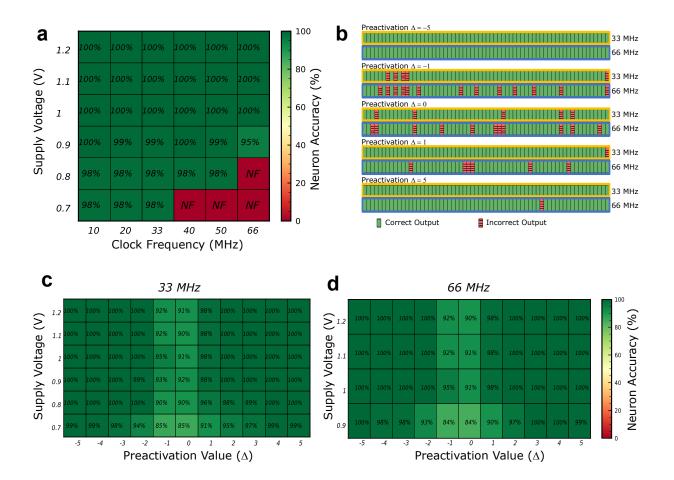

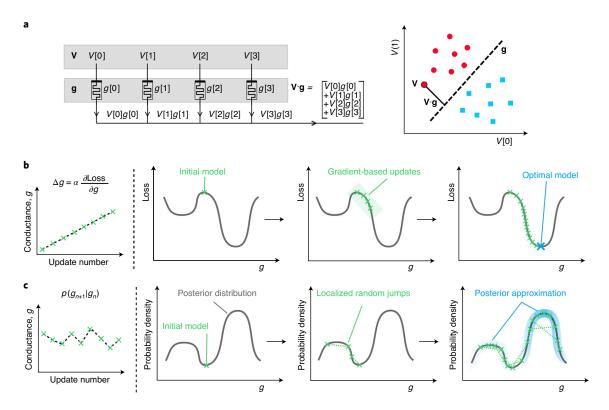

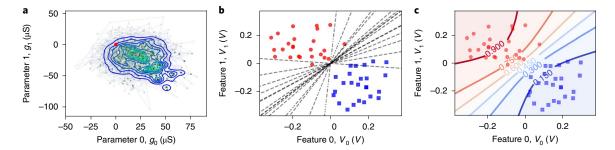

3.1 Machine bayésienne à base de memristors fabriquée. a Photographie au microscope optique de la puce du système bayésien. **b** Détail du bloc de vraisemblance, qui comprend un circuit numérique et un bloc de mémoire avec son circuit périphérique. c Photographie du réseau de memristors 2T2R. d Image de microscopie électronique à balayage d'un memristor dans le back-end de notre processus hybride memristor/CMOS. e Schéma du bloc de vraisemblance présenté dans b. f Schéma du circuit comparateur Gupta[7], utilisé pour générer le flux de bits aléatoires de vraisemblance en comparant la probabilité lue en mémoire avec le nombre aléatoire généré par le LFSR. Pour des raisons de compacité, le circuit est présenté ici dans une version à quatre bits. Une version à huit bits est mise en œuvre sur la puce. g Schéma de l'amplificateur de détection différentiel utilisé pour lire les états binaires des memristors. h Schéma du convertisseur de tension, utilisé pour adapter la tension d'entrée nominale aux tensions de formation et de programmation des memristors. i Principe de la programmation complémentaire des memristors de la cellule de bit 2T2R. Toutes les sous-figures

64

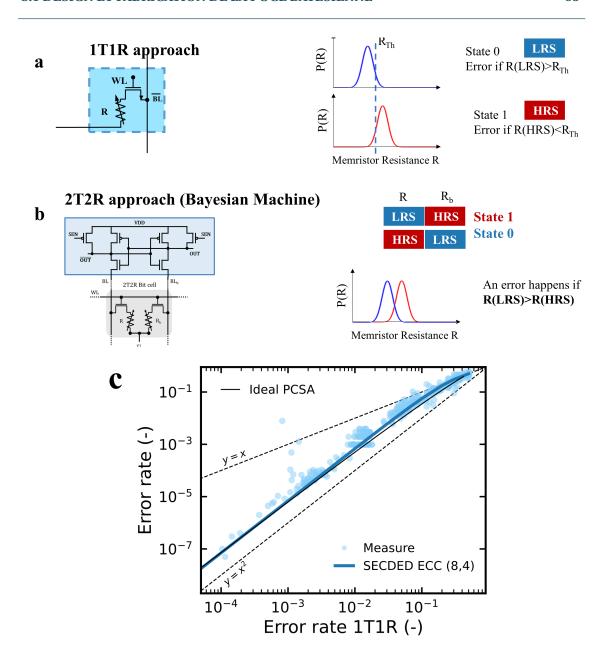

# 3.2 **Réduction des effets de la variabilité des dispositifs avec l'approche 2T2R. a**Dans l'approche conventionnelle, une erreur se produit si un dispositif programmé

en LRS a une résistance supérieure au seuil entre LRS et HRS, ou si un dispositif programmé en HRS a une résistance inférieure à ce seuil. **b** Dans l'approche 2T2R de la machine bayésienne, une erreur se produit si un dispositif programmé en LRS a une résistance supérieure à celle de son dispositif complémentaire programmé en HRS : les deux dispositifs doivent se trouver en fin de distribution pour qu'une erreur se produise. **c** Taux d'erreur de l'approche 2T2R en fonction du taux d'erreur de l'approche 1T1R, dans des simulations supposant un amplificateur de détection parfait (ligne noire) ou mesuré expérimentalement sur le circuit intégré de [8] (points bleu clair). Ligne bleue : taux d'erreur d'un code ECC SECDED utilisant le même nombre de dispositifs que notre approche 2T2R. . . . .

LIST OF FIGURES xvii

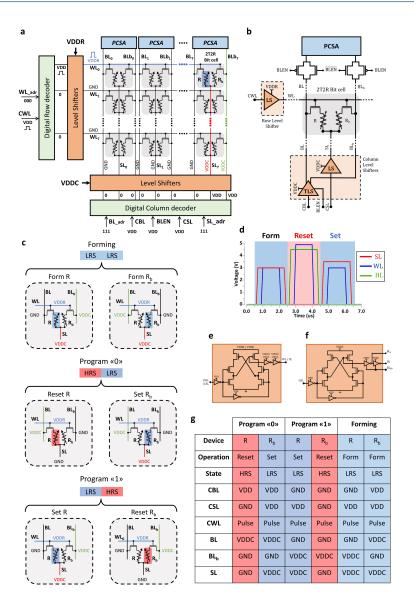

| 3.3             | Circuit de programmation pour les matrices de mémoire de vraisemblance.                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                 | a Schémas détaillés de la matrice de mémoire de vraisemblance, avec son cir-                                                                  |

|                 | cuit de périphérie de programmation et de lecture, affichant les tensions néces-                                                              |

|                 | saires pour effectuer une opération SET sur le premier memristor R de la première                                                             |

|                 | rangée, dernière colonne. <b>b</b> Schémas des connexions de la cellule de bit 2T2R au                                                        |

|                 | circuit de lecture et de programmation. Deux convertisseurs de tension (conver-                                                               |

|                 | tisseur de tension conventionnel LS et convertisseur de tension à trois états TLS)                                                            |

|                 | et un amplificateur de détection (PCSA) sont implémentés dans chaque colonne.                                                                 |

|                 | Un convertisseur de tension est implémenté dans chaque rangée. Le signal numérique                                                            |

|                 | BLEN permet de choisir entre le mode de lecture ou de programmation. <b>c</b> Ten-                                                            |

|                 | sions qui doivent être appliquées sur la ligne de bit BL, la ligne de bit inverse BLb                                                         |

|                 | et la ligne source SL pour le forming, la programmation d'un 'zéro' et la program-                                                            |

|                 | mation d'un 'un' dans une cellule de bit 2T2R. <b>d</b> Niveaux de tension et chrono-                                                         |

|                 | grammes utilisés pour les opérations de forming, de RESET et de SET. e Sché-                                                                  |

|                 | mas au niveau du transistor du convertisseur de tension (LS) et <b>f</b> des circuits du                                                      |

|                 | convertisseur de tension à trois états (TLS). <b>g</b> Tableau résumant la configuration                                                      |

|                 | des signaux de programmation (convertisseurs de tension) pour les différentes                                                                 |

|                 | opérations de programmation prises en charge par la matrice de mémoire (form-                                                                 |

|                 | ing, programmation d'un 'zéro' et programmation d'un 'un')                                                                                    |

|                 |                                                                                                                                               |

|                 |                                                                                                                                               |

|                 |                                                                                                                                               |

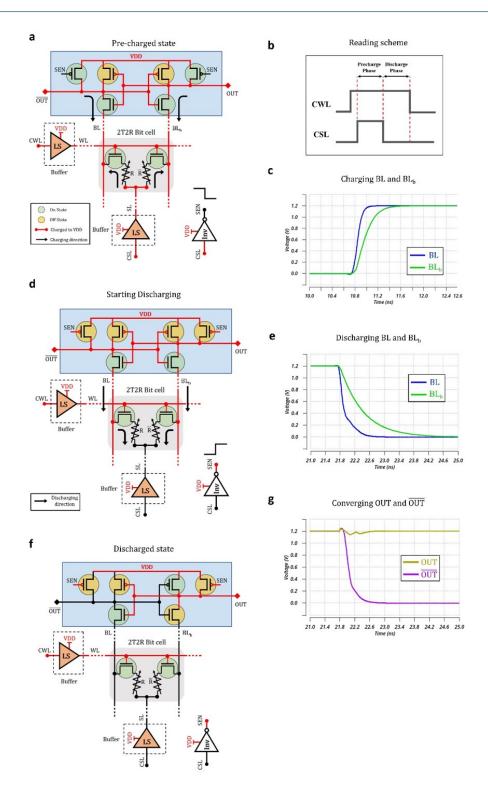

| 3.4             | Circuit de lecture pour les matrices de mémoire de vraisemblance. Cette figure                                                                |

| J. <del>T</del> | présente les schémas de circuit ( <b>a</b> , <b>d</b> et <b>f</b> ) et les simulations ( <b>c</b> , <b>e</b> , <b>g</b> et <b>h</b> ) qui ex- |

|                 | pliquent l'opération de lecture de la matrice mémoire. <b>b</b> Le schéma de lecture im-                                                      |

présente les schémas de circuit (**a**, **d** et **f**) et les simulations (**c**, **e**, **g** et **h**) qui expliquent l'opération de lecture de la matrice mémoire. **b** Le schéma de lecture implique une phase de précharge et une phase de décharge. **a** Schéma et **c** simulation du circuit de la phase de précharge. BL et BLb sont chargées à VDD. **d** Schéma et **e** simulation du circuit de la phase de décharge, BL et BLb sont déchargées à la masse avec une vitesse différente. **f** Schémas et **g** simulation des sorties de l'amplificateur de détection convergeant vers un état stable, pendant que BL et BLb sont complètement déchargées à la masse.

67

68

xviii LIST OF FIGURES

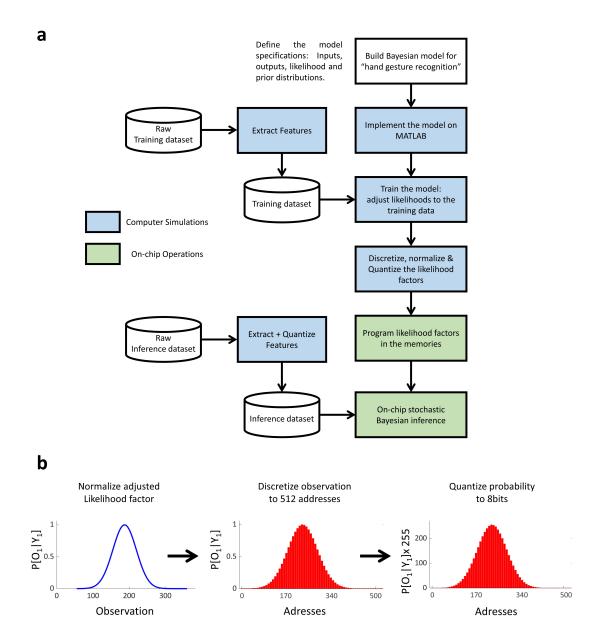

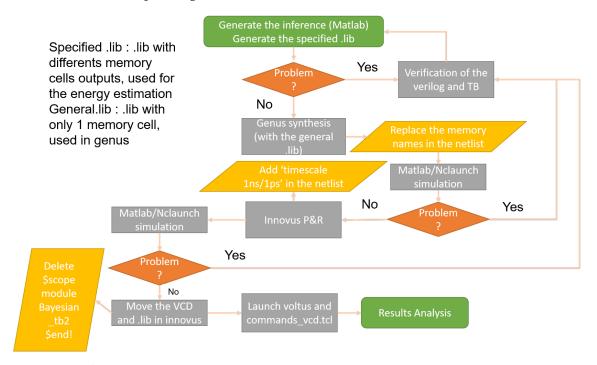

| 3.6  | Les différentes étapes d'un projet avec la machine bayésienne, de l'entraînement                  |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | à l'inférence sur puce. a Diagramme résumant les principales étapes d'un pro-                     |    |

|      | jet impliquant la machine bayésienne, de la construction du modèle bayésien à                     |    |

|      | l'utilisation de la machine bayésienne pour effectuer une inférence sur puce. <b>b</b>            |    |

|      | Illustration des différentes étapes de normalisation, de discrétisation et de quan-               |    |

|      | tification des facteurs de vraisemblance, nécessaires avant la programmation des                  |    |

|      | tableaux de mémoire de vraisemblance sur puce                                                     | 69 |

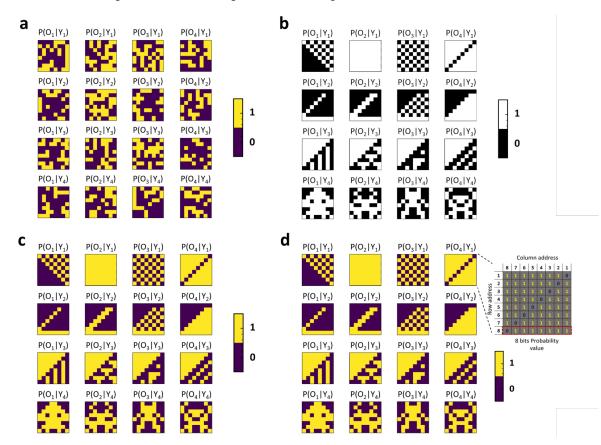

| 3.7  | Mesures des vraisemblances stockées dans le démonstrateur. a Motifs mesurés                       |    |

|      | avant l'étape de formation (forming). Les résultats des mesures semblent aléa-                    |    |

|      | toires. ${\bf b}$ Motifs destinés à être stockés. ${\bf c}$ Motifs mesurés immédiatement après la |    |

|      | programmation. <b>d</b> Motifs mesurés après cinq mois, pendant lesquels le démon-                |    |

|      | strateur a été conservé à température ambiante. Les images a, c, d sont présen-                   |    |

|      | tées en couleurs pour exprimer qu'elles représentent des mesures effectuées sur                   |    |

|      | puce, tandis que l'image <b>b</b> est présentée en noir et blanc pour exprimer qu'elle            |    |

|      | représente un motif prévu.                                                                        | 71 |

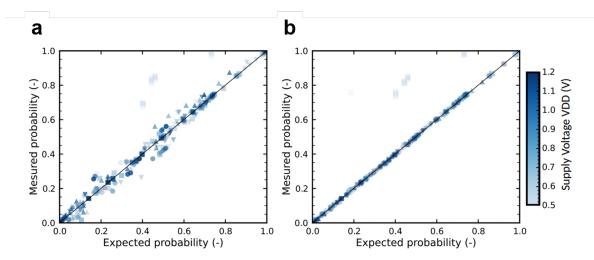

| 3.8  | Mesures de la machine bayésienne à base de memristors fabriquée. a Sortie de                      |    |

|      | la machine bayésienne : probabilité postérieure mesurée en fonction de la valeur                  |    |

|      | attendue de la loi de Bayes. Les différents points correspondent à des entrées                    |    |

|      | d'observations aléatoires. Les différentes lignes sont regroupées dans le même                    |    |

|      | graphique. Les points sont obtenus avec différentes tensions d'alimentation VDD                   |    |

|      | comprises entre 0,5 et 1,2 volts. Ce graphique est obtenu avec des <i>seeds</i> LFSR non          |    |

|      | optimaux. Les probabilités mesurées sont obtenues en moyennant les mesures                        |    |

|      | expérimentales sur toute la période LFSR (255 cycles). <b>b</b> Identique à <b>a</b> , en util-   |    |

|      | isant des seeds LFSR optimaux. Les symboles indiquent quelle ligne de la ma-                      |    |

|      | chine bayésienne a été utilisée (cercle, triangle vers le haut, triangle vers le bas,             |    |

|      | carré : première, deuxième, troisième et quatrième ligne)                                         | 73 |

| 3.9  | Systèmes de tests des deux puces bayésiennes. a Installation sous la station                      |    |

|      | sous pointes au laboratoire IM2NP à Marseille et <b>b</b> Installation dans un package            |    |

|      | JLCC52 et PCB, réalisée au C2N                                                                    | 74 |

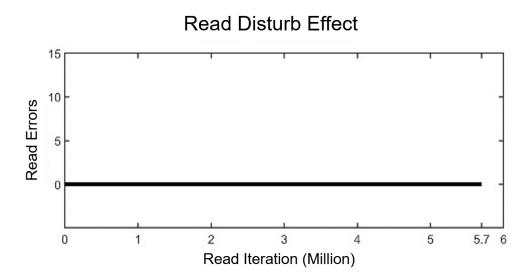

| 3.10 | Mesure expérimentale de la perturbation due à la lecture sur une matrice de                       |    |

|      | mémoire de vraisemblance, avec une valeur VDD de 1,2 volts. Même après 5,7                        |    |

|      | millions d'opérations de lecture de l'ensemble de la matrice, aucune erreur n'est                 |    |

|      | observée                                                                                          | 75 |

| 3.11 | Étapes de la simulation de consommation énergétique des puces constituées                         |    |

|      | de memristors.                                                                                    | 77 |

LIST OF FIGURES xix

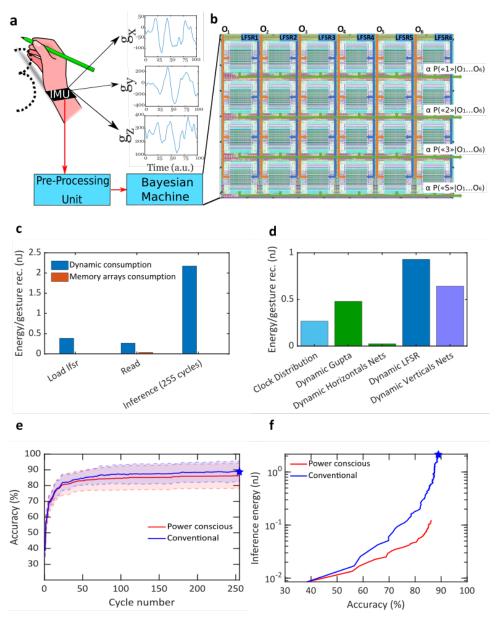

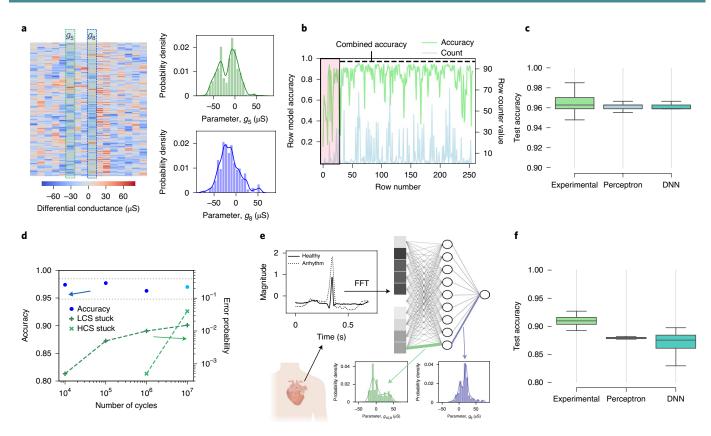

| 3.12 | Application de la machine bayésienne à une tâche pratique de reconnaissance                     |

|------|-------------------------------------------------------------------------------------------------|

|      | de gestes. a Configuration avec une unité de mesure inertielle utilisée pour en-                |

|      | registrer l'ensemble de données de reconnaissance de gestes. <b>b</b> Masques de la             |

|      | conception de la machine bayésienne placée et routée utilisée pour effectuer                    |

|      | l'analyse de la reconnaissance de gestes au niveau de la conception. ${\bf c}$ Consom-          |

|      | mation d'énergie du système (consommation dynamique et matrices de mémoire)                     |

|      | au cours des trois phases de calcul : chargement des <i>seeds</i> dans le LFSR, lecture         |

|      | des mémoires et inférence réelle de 255 cycles. <b>d</b> Consommation d'énergie des             |

|      | points importants du système pendant la phase d'inférence pour 255 cycles. <b>e</b>             |

|      | Précision moyenne en fonction du nombre de cycles pour deux types de calcul :                   |

|      | en utilisant une méthode économe en énergie en ne prenant en compte que le                      |

|      | premier '1' pour la décision (en rouge) et en utilisant le calcul stochastique con-             |

|      | ventionnel en utilisant le nombre maximum de '1' pour la décision (en bleu). Les                |

|      | ombres autour du graphique montrent un écart-type de la précision moyenne sur                   |

|      | les dix sujets. f Consommation d'énergie pendant la phase d'inférence en fonc-                  |

|      | tion de la précision pour la reconnaissance de gestes pour les deux méthodes.                   |

|      | Les étoiles correspondent au même point dans les graphiques ${\bf e}$ et ${\bf f}$ . Toutes les |

|      | valeurs d'énergie sont données pour une tension d'alimentation de 1,2 volts                     |

82

83

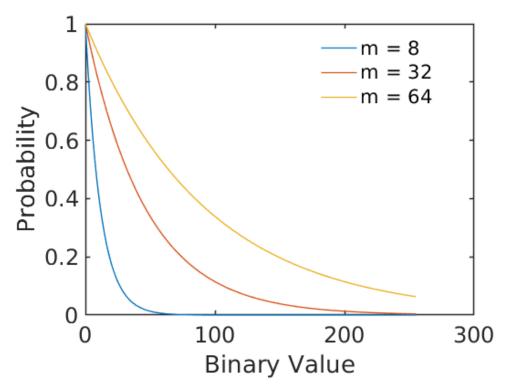

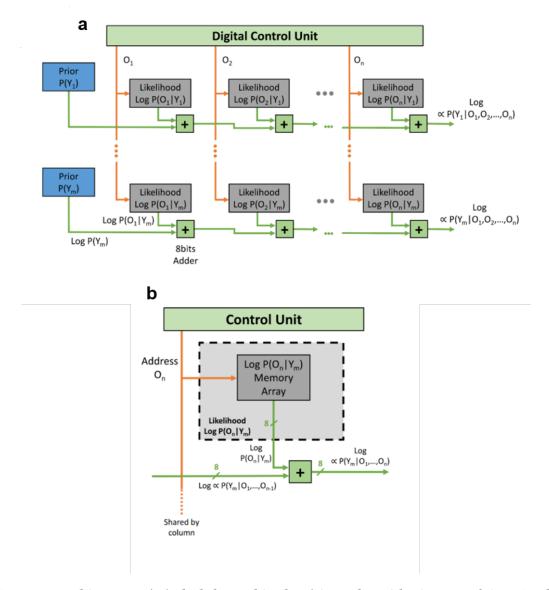

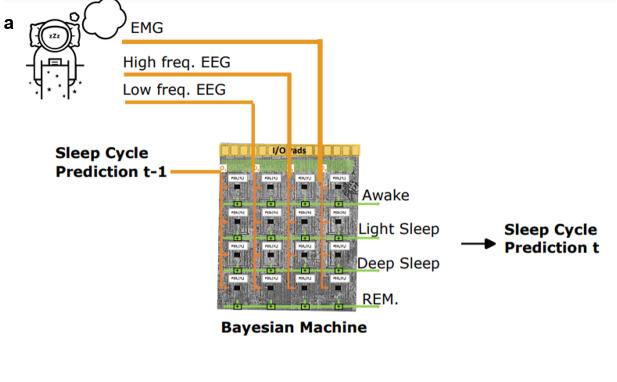

| <ul> <li>4.2 Architecture générale de la machine bayésienne logarithmique. a Schéma simplifié de la machine bayésienne logarithmique mise en œuvre. b Schéma simplifié de la likelihood comprenant les additionneurs.</li> <li>4.3 Mise en œuvre expérimentale de la classification des phases du sommeil tout au long de la nuit. a Entrées et sorties de la machine bayésienne logarithmique</li> </ul> | 4.1 | Fonction logarithmique transformant la probabilité en entier 8 bits, pour trois valeurs de $m: 8, 32, 64$                                                                                                                                                        | 86 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| au long de la nuit. a Entrées et sorties de la machine bayésienne logarithmique                                                                                                                                                                                                                                                                                                                           | 4.2 | plifié de la machine bayésienne logarithmique mise en œuvre. <b>b</b> Schéma simpli-                                                                                                                                                                             | 87 |

| implémenté sur la machine bayésienne logarithmique utilisée pour la classifica-                                                                                                                                                                                                                                                                                                                           | 4.3 | <b>au long de la nuit. a</b> Entrées et sorties de la machine bayésienne logarithmique utilisée pour la classification des phases du sommeil. <b>b</b> Modèle de réseau bayésien implémenté sur la machine bayésienne logarithmique utilisée pour la classifica- | 89 |

4 Machine Bayésienne III, les deux modes!

XX LIST OF FIGURES

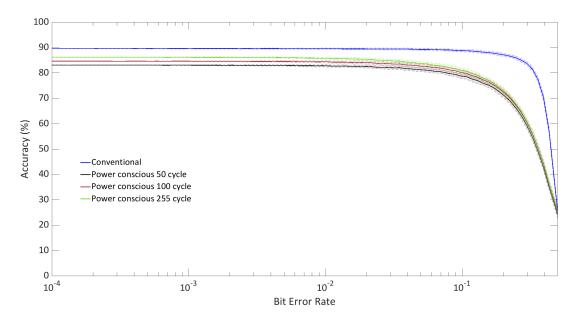

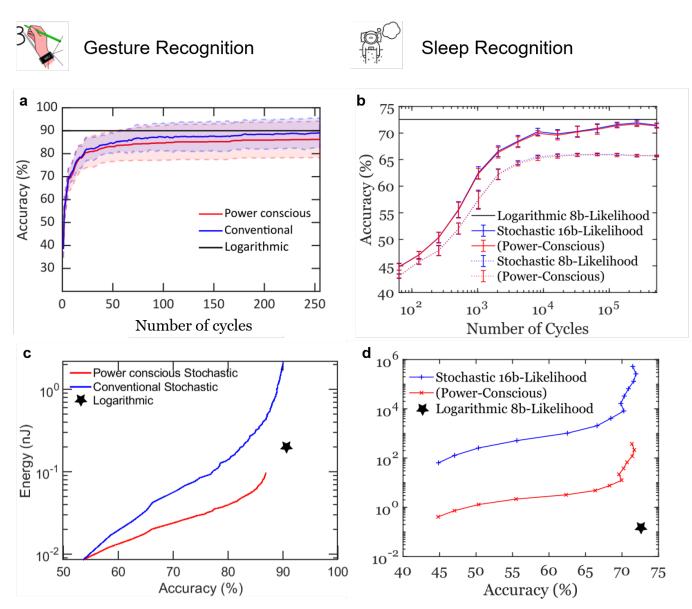

| 4.4 | Évaluation de la précision et de la consommation d'énergie des machines bayési-                     |    |

|-----|-----------------------------------------------------------------------------------------------------|----|

|     | ennes stochastiques et logarithmiques. a,b Précision de la machine stochas-                         |    |

|     | tique pour ${\bf a}$ la reconnaissance des gestes et ${\bf b}$ la classification des phases du som- |    |

|     | meil, en fonction du nombre de cycles d'horloge, en utilisant le calcul stochas-                    |    |

|     | tique conventionnel ou l'approche "power-conscious". La précision de la ma-                         |    |

|     | chine logarithmique (un cycle d'horloge) est tracée comme référence. <b>c,d</b> Con-                |    |

|     | sommation d'énergie en fonction de la précision pour ${\bf c}$ la reconnaissance des                |    |

|     | gestes et ${\bf d}$ la classification des phases du sommeil, en utilisant toutes les ap-            |    |

|     | proches considérées dans a et b. Cette figure est obtenue en associant plusieurs                    |    |

|     | méthodologies de simulation. Les barres d'erreur/ombres représentent un écart                       |    |

|     | type                                                                                                | 90 |

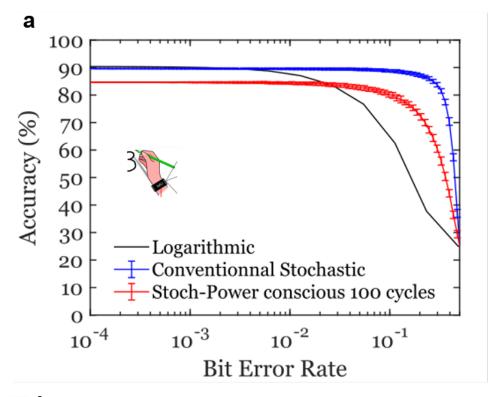

| 4.5 | Évaluation de la Résilience au taux d'erreur de bit de memristor de la machine                      |    |

|     | bayésienne stochastique et logarithmique. Précision des machines bayésiennes                        |    |

|     | stochastiques (utilisant le calcul conventionnel et "power-conscious") et loga-                     |    |

|     | rithmiques en fonction des taux d'erreur de bit de memristor, pour <b>a</b> la reconnais-           |    |

|     | sance des gestes et ${\bf b}$ les tâches de classification des phases du sommeil. Cette fig-        |    |

|     | ure est obtenue en utilisant la simulation de Monte Carlo. Les barres d'erreur/ombr                 | es |

|     | représentent un écart type.                                                                         | 93 |

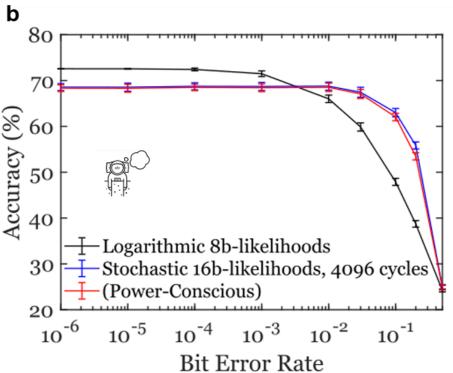

| 4.6 | Puce bayésienne logarithmique et son système de test. a Image de microscopie                        |    |

|     | optique de la puce de la machine fabriquée. <b>b</b> Photographie de la configuration               |    |

|     | du test de la machine bayésienne logarithmique.                                                     | 94 |

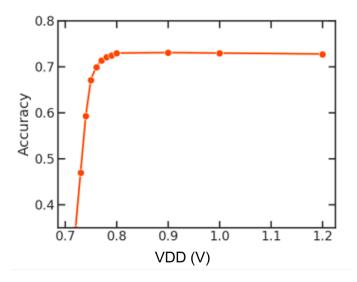

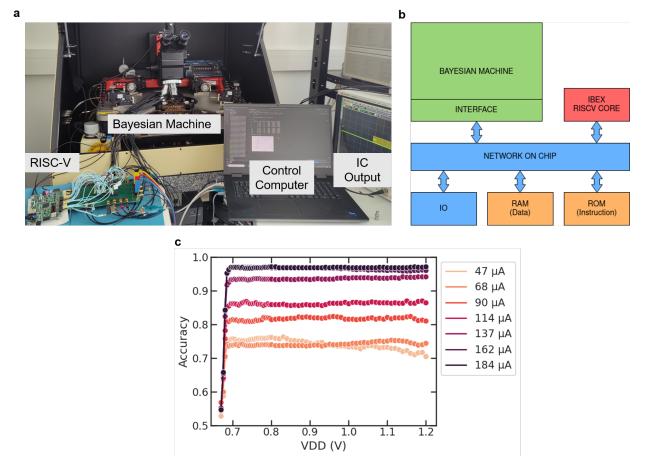

| 4.7 | Résulat de mesures de la puce bayésienne Précision mesurée expérimentale-                           |    |

|     | ment de la machine bayésienne logarithmique, moyennée sur 1000 segments de                          |    |

|     | cinq secondes. La mesure a été répétée pour différentes tensions d'alimentation                     |    |

|     | VDD                                                                                                 | 95 |

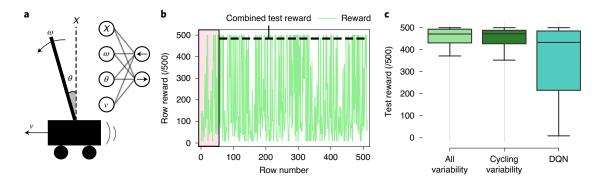

| 4.8 | Intégration des machines bayésiennes avec un cœur RISC-V. a Configuration du                        |    |

|     | test expérimental avec machine bayésienne et cœur RISC-V. <b>b</b> Schéma de l'intégrati            | on |

|     | de la machine bayésienne dans un coeur RISC-V. <b>c</b> Précision mesurée de la sortie              |    |

|     | de la machine bayésienne logarithmique (moyenne sur 4 096 entrées), en fonc-                        |    |

|     | tion de la tension d'alimentation, pour différents courants de compliance SET                       |    |

|     | (contrôlés par la tension de grille du transistor de sélection)                                     | 97 |

## Introduction

On m'attribue le mérite d'être l'un des plus grands travailleurs et peut-être le suis-je, si la pensée est considérée comme un équivalent du travail, car j'y ai consacré presque toutes mes heures d'éveil. Mais si l'on interprète le travail comme une activité définie dans un temps déterminé et selon une norme rigide, alors je suis peut-être le pire des paresseux. Tout effort imposé demande un sacrifice de l'énergie vitale. Je n'ai jamais payé un tel prix. Au contraire, je me suis épanoui dans mes pensées.

Nikola Tesla

Enfoncez-vous bien dans votre fauteuil, prenez un paquet de pop-corn et laissezvous maintenant embarquer dans ce voyage merveilleux."

Dans le panorama technologique actuel, l'intelligence artificielle (IA) s'est affirmée comme une force centrale dans une multitude de domaines, catalysant des avancées significatives dans des secteurs aussi variés que l'analyse de données, la médecine, et la robotique. Les systèmes IA contemporains, y compris les modèles génératifs avancés tels que ChatGPT, Llama, Claude dans la génération de texte ou encore Midjourney, Dall-E dans la génération d'images, opèrent principalement dans des environnements cloud, centralisant ainsi une quantité colossale de données. Cette centralisation dans le cloud, bien qu'elle facilite l'accès et la manipulation des données, engendre des préoccupations croissantes en matière de sécurité des données. Comme le souligne Castets-Renard [9], cette centralisation peut créer des vulnérabilités significatives, exposant les utilisateurs à des risques de violations de données et d'attaques cybernétiques.

Dans ce contexte, l'adoption de l'IA dans les systèmes embarqués tels les smartphones, smartwatch et autres appareils mobiles se présente comme une alternative prometteuse. Cela permettrait une décentralisation des données et une réduction des risques associés à la centralisation. Cependant, cette transition est loin d'être sans obstacles. Un des défis majeurs réside dans la consommation massive d'énergie associée aux opérations de l'IA, un problème qui est exacerbé dans les environnements mobiles où les ressources sont limitées. En effet, les IA ont besoin d'être entraînées et cet entraînement consomme énormément de ressources et d'énergie. Un exemple dans le cadre de l'entraînement, récemment Meta a publié les données pour son modèle de langage Llama-2. Pour l'entraînement de leur plus petit modèle avec sept milliards de paramètres (Llama-2 7B), il a fallu 184320 heures sur des cartes graphiques A100-80GB qui ont une puissance maximale de 400 W. Ce qui donne une consommation énergétique de 73.7 MWh soit l'équivalent de la consommation annuelle moyenne de 33 foyers français[10]. Au vu de ces chiffres, l'entraînement n'est pas réalisable sur un appareil mobile avec une capacité limitée. Cependant il est possible de réaliser l'entraînement en dehors de l'appareil et de transférer le modèle obtenu puis de réaliser uniquement l'inférence sur l'appareil. Un autre exemple que j'aimerais vous proposer et l'utilisation de l'inférence pour générer des images. La figure 1 a été générée en utilisant le modèle SDXL 1.0 [1] sur mon ordinateur avec une carte graphique RTX Titan qui consomme au maximum 280 W. Elle a été générée en 25.2 s ce qui donne une consommation de 1.96 Wh ce qui reste énorme pour faire juste une inférence. De plus, pour générer cette image, il faut une puissance de calcul appropriée. Cela signifie que le matériel utilisé doit être suffisamment performant et adapté pour traiter les données et exécuter les algorithmes requis par l'inférence, faute de quoi, le processus peut être gravement compromis ou même impossible à réaliser. Ce niveau de performance n'est généralement pas disponible dans des appareils aux capacités limitées, tels que les appareils mobiles.

En plus du problème énergétique, l'IA actuelle est souvent critiquée pour son manque de transparence et d'explicabilité, ce qui peut entraver son adoption dans des domaines où la compréhension des processus décisionnels est cruciale comme le domaine médical ou encore la conduite autonome. Dans cette optique, une méthode plus explicable comme l'inférence

Figure 1: **Image de moi présentant ma thèse, générée par Stable Diffusion.** Entraînenement du modèle en utilisant des photos de moi et l'environnement kohya\_ss (https://github.com/bmaltais/kohya\_ss) puis générée en utilsant l'environnement AUTOMATIC1111 (https://github.com/AUTOMATIC1111/stable-diffusion-webui) avec le modèle SD-XL [1] en 60 itérations.

bayésienne permettrait de devenir une solution prometteuse. En adoptant des principes probabilistes dans l'IA, il est possible de développer des modèles qui non seulement sont capables de rationaliser leurs décisions, mais aussi d'offrir une plus grande transparence dans leurs opérations.

C'est dans cette optique de consommation énergétique que je vais commencer cette thèse avec dans le premier chapitre une exploration de l'architecture des circuits actuels puis de l'avancée des nouvelles architectures inspirées sur le fonctionnement du cerveau qui m'amènera à discuter des mémoires émergentes, en mettant un accent particulier sur les memristors et leur potentiel pour révolutionner le calcul en mémoire.

Dans le deuxième chapitre, je présenterai la machine bayésienne. Depuis l'explication du fonctionnement jusqu'à une application réelle de reconnaissance de gestes en passant par l'architecture de cette machine bayésienne. Je décomposerai les principes fondamentaux qui sous-tendent cette approche, en examinant de près les techniques d'approximation et de multiplication qui sont centrales à son fonctionnement. Cette partie se penchera également sur les applications pratiques de cette approche dans la conception des circuits, explorant les possibilités offertes pour la reconnaissance des gestes et évaluant la performance de ces systèmes dans des contextes à faible volume de données et surtout du caractère explicable de la machine.

Le troisième chapitre est consacré sur l'aspect conception et réalisation de la machine bayésienne où je détaillerai les étapes clés du processus de fabrication, en mettant en lumière les innovations récentes dans la structuration et la programmation de cette machine. J'explorerai

également les défis et les opportunités associés à la mesure et à la caractérisation de ces systèmes, avant de conclure avec une discussion sur les perspectives d'amélioration de l'efficacité énergétique.

Enfin, le quatrième chapitre est consacré à une comparaison entre deux architectures de calcul pour une machine bayésienne, je ferai la comparaison tant en terme d'application, sur la reconnaissance de gestes et également sur une application plus médicale qui est la reconnaissance des cycles du sommeil, qu'en terme énergétique. Puis, je présenterai une intégration de cette puce dans un système composé d'un coeur RISC-V. Pour terminer, je discuterai brièvement d'une nouvelle puce regroupant les deux méthodes de calcul.

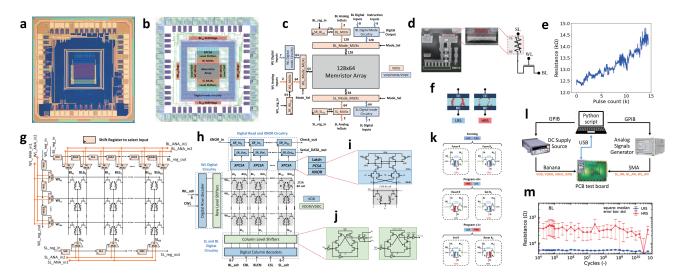

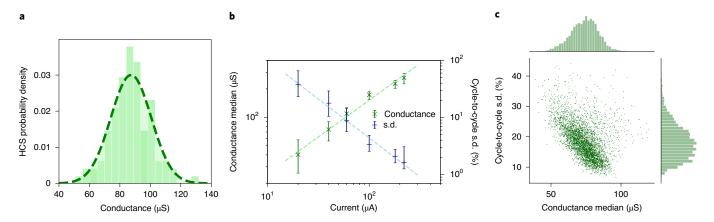

J'ai également eu l'opportunité de participer à d'autres projets décrits dans les annexes de cette thèse. Le premier (annexe A) consiste à la conception d'une puce bimodale (analogique et numérique) constituée d'un tableau de 64x128 memristors inclus dans une structure 2T2R [11]. Cette puce permet d'effectuer des opérations de lecture et d'écriture de manière numérique mais également une opération de lecture analogique permettant de mesurer l'état de résistance des memristors. Cette plateforme permet d'optimiser les conditions de lecture et d'écriture des memristors, ainsi que de développer et de tester des concepts neuromorphiques innovants basés sur les memristors. Dans ce projet, j'ai conçu la puce la partie numérique de la puce et effectué les tests de vérifications de fonctionnement avant la fabrication.

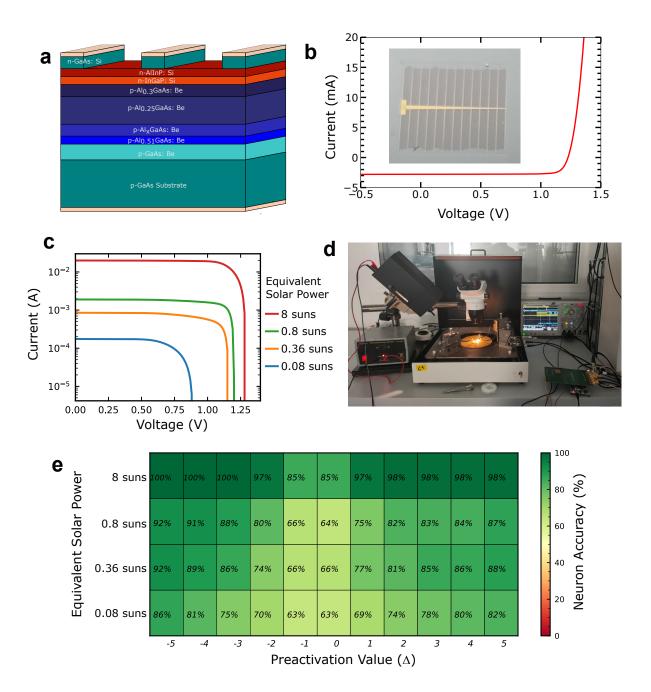

Dans le deuxième projet (annexe B), nous avons développé un réseau neuronal binarisé robuste, composé de 32 768 memristors et alimenté par une cellule solaire optimisée, destiné à des applications sur des systèmes embarqués [12]. La conception unique du circuit permet un calcul numérique efficace et résilient proche de la mémoire, éliminant le besoin de compensation ou de calibration et assurant une performance optimale sous diverses conditions. Il a démontré une performance d'inférence comparable à une alimentation de laboratoire sous une forte illumination et a maintenu sa fonctionnalité avec une précision légèrement réduite dans des conditions de faible éclairage. Ma participation dans ce projet consiste à l'évaluation de la consommation énergétique de la puce en simulation.

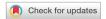

Enfin, le troisième projet (annexe C) présente une méthode d'apprentissage automatique qui exploite la variabilité des memristors pour mettre en œuvre l'échantillonnage de Markov chain Monte Carlo dans un réseau fabriqué de 16 384 dispositifs, configuré comme un modèle d'apprentissage machine bayésien [13]. Nous expérimentons cette approche pour effectuer la reconnaissance de tissus malins et la détection d'arythmie cardiaque, et, à l'aide d'un simulateur calibré, nous abordons la tâche d'apprentissage par renforcement de cartpole. Notre méthode démontre une robustesse face à la dégradation des dispositifs à dix millions de cycles d'endurance et, selon des simulations au niveau du circuit et du système, l'énergie totale requise pour entraîner les modèles est estimée à l'ordre des microjoules, ce qui est notablement inférieur aux approches basées sur les technologies CMOS. J'ai effectué les estimations énergétiques de la puce en simulation sur l'application du cartpole.

J'ai effectué cette thèse en collaboration avec différentes équipes, notamment l'équipe d'Elisa

Vianello du CEA-LETI à Grenoble pour la fabrication des memristors et l'équipe de Jean-Michel Portal et Marc Bocquet de l'IM2NP pour la conception des puces. Au cours de ma thèse, j'ai également collaboré avec les étudiants suivants du C2N : Kamel-Eddine Harabi, Tifenn Hirtzlin, Marie Drouhin, Atreya Majumdar, Adrien Renaudineau, Théo Ballet, Adrien Pontlevy et Fadi Jebali tant dans la conception des puces que dans leurs tests et leurs applications.

La puce Bayésienne stochastique (Chapitres 2 et 3) a été conçue avant ma thèse par Kamel-Eddine Harabi et Tifenn Hirtzlin. J'ai contribué à son test électrique, développé la version passée à l'échelle du système et effectué toutes les analyses sur cette version passée à l'échelle du système, notamment toutes les études concernant la reconnaissance de gestes (Chapitres 2 et 3). J'ai également développé la méthodologie pour l'évaluation énergétique de la puce. J'ai développé le concept de la machine Bayésienne logarithmique. J'ai conçu sa démonstration ASIC (en collaboration avec Kamel-Eddine Harabi), le PCB pour son test et réalisé sa caractérisation électrique (Chapitre 4). Le travail sur les cycles du sommeil a été réalisé par Adrien Pontlevy, sous ma supervision conjointe avec celle de mon directeur de thèse (Chapitre 4). L'intégration dans le RISC-V a été effectuée par le stagiaire Théo Ballet (Chapitre 4). J'ai conçu la grande machine Bayésienne multimode (en collaboration avec Kamel-Eddine Harabi) et développé son PCB de test (Chapitre 4). J'ai conçu la plateforme de tests multimodes analogique/numérique en collaboration avec Kamel-Eddine Harabi et développé son PCB de tests (Annexe A). J'ai réalisé l'analyse énergétique d'une puce de l'IM2NP implémentant un réseau de neurones (Annexe B) et d'un système d'échantillonnage MCMC utilisant la physique des memristors (Annexe C).

# **Chapter 1**

# Énergie et Mémoires résistives : Un voyage inattendu

L'association des mémoires résistives et du calcul procheen mémoire pour diminuer la consommation des circuits

> "L'Homme ne trouvera jamais une invention plus belle, plus simple ou plus directe que la nature, car dans ses inventions rien ne manque et rien n'est excessif."

> > Léonard de Vinci

# 1.1 Vers une optimisation de l'efficacité énergétique des circuits...

L'efficacité énergétique des circuits intégrés est une préoccupation majeure dans le domaine de l'électronique, de l'informatique et maintenant de l'intelligence artificielle. La miniaturisation des transistors et l'augmentation de leur densité sur les puces ont permis d'augmenter considérablement les performances des circuits, mais ont également posé de nouveaux défis en termes de gestion de l'énergie et de la chaleur.

L'architecture de Von Neumann, qui est à la base de la plupart des ordinateurs modernes, a joué un rôle clé dans cette évolution. Cette architecture, qui sépare le stockage des données et leur traitement, a permis de concevoir des machines universelles capables d'exécuter n'importe quel programme stocké sous forme de données. Cependant, le transport des données entre le processeur et la mémoire consomme une grande partie de l'énergie utilisée par les ordinateurs modernes, ce qui limite leur efficacité énergétique [14].

Face à ces défis, de nouvelles architectures sont explorées, inspirées par le fonctionnement du cerveau humain. Ces architectures, dites neuromorphiques, cherchent à imiter la manière dont les neurones et les synapses du cerveau traitent et stockent l'information de manière distribuée et parallèle. Elles promettent une efficacité énergétique bien supérieure à celle des architectures traditionnelles, en particulier pour les tâches liées à l'intelligence artificielle et à l'apprentissage machine [15].

#### 1.1.1 Évolution des circuits et de l'architecture de Von-Neumann

#### 1.1.1.1 Évolution des circuits

J'aimerai faire l'analogie avec les débuts de l'aviation, seulement 65 ans séparent le premier vol en avion des frères Wright en 1903 jusqu'au premier pied posé par Neil Armstrong sur la Lune en 1969 [16], de la même manière, en seulement 75 ans, nous sommes passés de l'invention du transistor en 1947 [17, 18] qui a remplacé les vieux tubes à vide encombrants et énergivores. Puis, en passant par l'utilisation des nouveaux matériaux semiconducteurs comme le silicium [19] à des systèmes électroniques complexes capables de réaliser des milliards d'opérations par seconde[20]. Ces avancées ont permis l'émergence de technologies que nous utilisons quotidiennement, comme les ordinateurs, les smartphones et l'Internet. Tout comme l'aviation a transformé notre façon de voyager et de comprendre le monde, l'évolution des transistors a révolutionné notre façon de communiquer, de travailler et de vivre

La croissance exponentielle dans la miniaturisation des transistors a été prédite par Gordon Moore en 1965 [21], la loi de Moore formule une multiplication par deux des transistors dans une puce tous les un an et demi permettant ainsi l'augmentation des performances et l'efficacité de la consommation énergétique de celle-ci. Cette loi a été respectée pendant plus