# Design of a single photon sensor in a 28 nm FD-SOI CMOS technology

Mohammadreza Dolatpoor Lakeh

## ▶ To cite this version:

Mohammadreza Dolatpoor Lakeh. Design of a single photon sensor in a 28 nm FD-SOI CMOS technology. Optics [physics.optics]. Universit\'e de Strasbourg, 2023. English. NNT: 2023STRAD034. tel-04395908

# HAL Id: tel-04395908 https://theses.hal.science/tel-04395908v1

Submitted on 15 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE Mathématiques, Science de l'information et de l'ingénieur ICube UMR 7357

# THÈSE présentée par :

# Mohammadreza DOLATPOOR LAKEH

soutenue le : 10 Octobre 2023

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline: Electronique, Microélectronique, photonique

Spécialité : Micro et Nanoélectronique

# Design of a Single Photon Sensor in a 28 nm FD-SOI CMOS technology

THÈSE dirigée par :

M KAMMERER Jean-Baptiste Docteur HDR, université de Strasbourg, France

M UHRING Wilfried Professeur, université de Strasbourg, France

**RAPPORTEURS:**

M BRUSCHINI Claudio Docteur HDR, EPFL, Suisse

M MAGNAN Pierre Professeur, ISAE SUPAERO, Toulouse, France

#### **AUTRES MEMBRES DU JURY:**

Mme Cathelin Andreia Docteur HDR, STMicroelectronics, France

M Calmon Francis Professeur, INSA Lyon, France

M Dartigues Alexandre (invité) Docteur, STMicroelectronics, France

M Schell Jean-Baptiste (invité) Docteur, CNRS, France

# Acknowledgments

This research was conducted at the ICube laboratory of the University of Strasbourg and CNRS, UMR 7357, and was funded by a grant from Agence Nationale de la Recherche (ANR-18-CE24-0010).

I wish to express my profound gratitude to my dedicated mentors, Professor Wilfried Uhring and Dr. Jean-Baptiste Kammerer, whose support and guidance have been instrumental at every stage of my doctoral journey. Working under their supervision was not only a scientific privilege but also a valuable source of life lessons. They have profoundly shaped my scientific identity, exemplifying dedication, and passion for the pursuit of knowledge.

I would also like to extend my heartfelt appreciation to my colleagues at ICube, Dr. Fabrice Aguenounon, Pascal Leindecker, and Nicolas Collin, for their invaluable technical support, especially during the chip characterization phase. Special thanks are owed to Dr. Jean-Baptiste Schell for his consistent availability in answering my queries.

Gratitude is also extended to ST Microelectronics and CMP for granting access to their technology and providing essential IC fabrication services. I offer special thanks to Andreia Cathelin for her assistance.

I am deeply thankful to Professor Francis Calmon for leading the SPADFDSOI project and for supplying the SPADs vital to this research.

I owe a debt of gratitude to Professor Luc Hebrard and Dr. Morgan Madec for affording me the opportunity to start my doctoral journey in France.

To my family and friends, I extend my heartfelt thanks for your encouragement and belief in me. Your unwavering emotional support has been an eternal source of motivation.

Lastly, I reserve a special place of honor and gratitude for my wife, who stood by my side throughout my years of PhD pursuit, offering her eternal love and support.

# Table of contents

| Acknowl   | edgm  | ents                                               | 1    |

|-----------|-------|----------------------------------------------------|------|

| Table of  | conte | ents                                               | 1    |

| List of A | crony | ms                                                 | 0    |

| Introduc  | tion  |                                                    | 1    |

|           |       |                                                    |      |

| SPAD an   | d Que | enching Circuits                                   | 3    |

| 1.1.      | SPA   | D Operation Principals                             | 3    |

| 1.2.      | SPA   | D Performance Parameters                           | 5    |

| 1.2.      | .1.   | Photon Detection Probability (PDP)                 | 5    |

| 1.2.      | .2.   | Timing Jitter                                      | 6    |

| 1.2.      | .3.   | Dark Count Rate (DCR)                              | 7    |

| 1.2.      | .4.   | Afterpulsing                                       | 9    |

| 1.2.      | .5.   | Fill Factor & Photon Detection Efficiency (PDE)    | 10   |

| 1.2.      | .6.   | Crosstalk                                          | 12   |

| 1.3.      | Que   | nching Circuits State of the Arts                  | 13   |

| 1.3.      | .1.   | Passive Quenching                                  | 13   |

| 1.3.      | .2.   | Active Quenching                                   | 17   |

| 1.3.      | .3.   | State-of-the-Art Active Quenching Circuits         | 19   |

| 1.4.      | The   | sis Objective                                      | 31   |

| 1.4.      | .1.   | Monolithic 3D SPAD Pixel in FD-SOI CMOS Technology | 31   |

| Chapter   | 2     |                                                    | 34   |

| 2.1.      | Intr  | oduction                                           | 34   |

| 2.2.      | Low   | Threshold Inverter as an Avalanche Detector        | 35   |

| 2.2       | .1.   | Delay Reduction Through Inverter Sizing            | 36   |

| 2.2       | .2.   | Delay Reduction Through Body Biasing               | 38   |

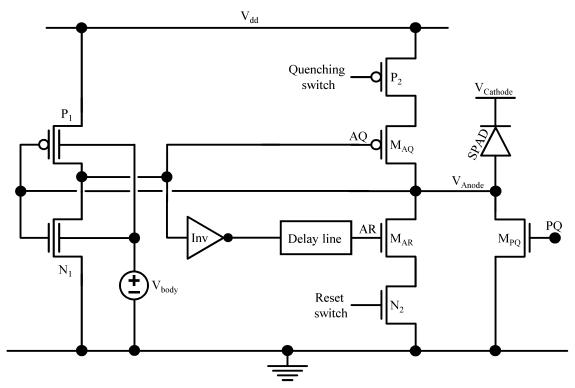

| 2.3.      | Bod   | y Biased Inverter Based AQAR Circuit               | 41   |

| 2.4.      | Resi  | ults and Discussions                               | . 44 |

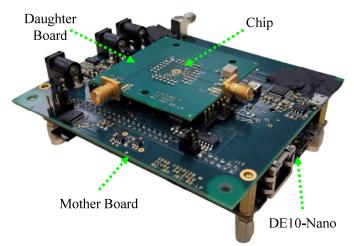

| 2.4       | .1.   | Chip and Test Bench                                | 45   |

| 2.4       | .2.   | Simulation Results                                 | 50   |

| 2.4       | .3.   | Experimental Results                               | . 52 |

| Chantar   | 2     |                                                    | ЕО   |

| 3.1. Int  | roduction58                                       |  |

|-----------|---------------------------------------------------|--|

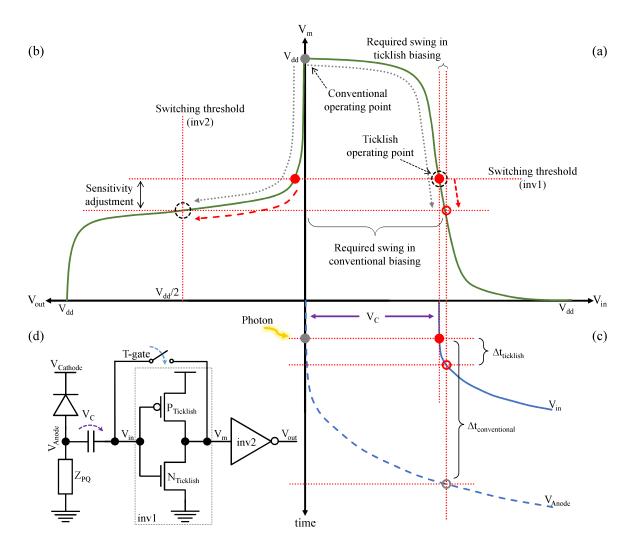

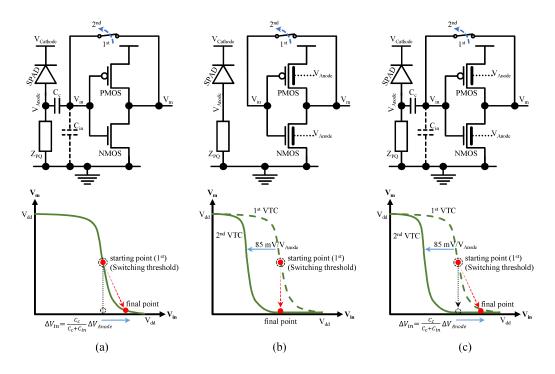

| 3.2. Tic  | klish Inverter for Avalanche Detection            |  |

| 3.2.1.    | Ticklish Avalanche Detector                       |  |

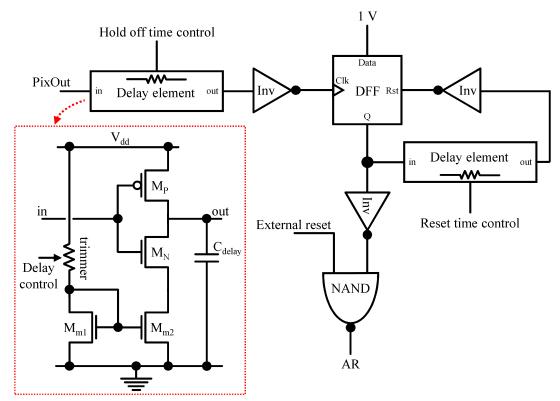

| 3.2.2.    | Ticklish Active Quenching Active Reset Circuit    |  |

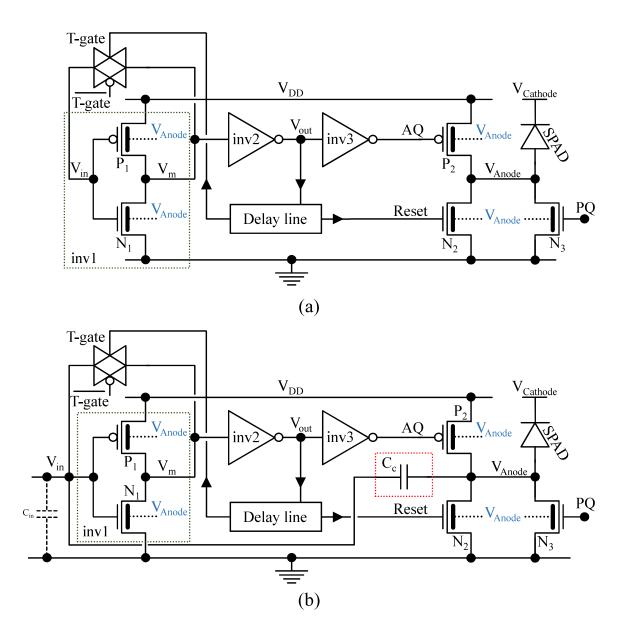

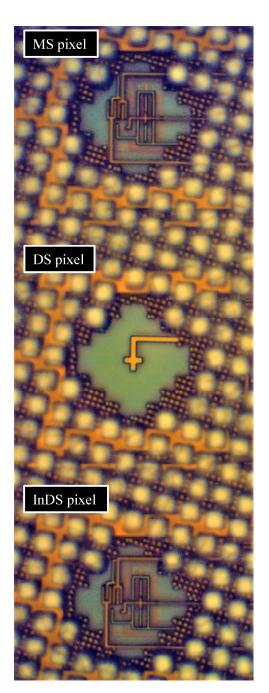

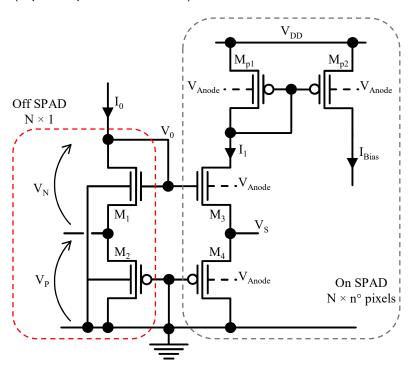

| 3.3. Na   | tive 3D SPAD Active Pixel65                       |  |

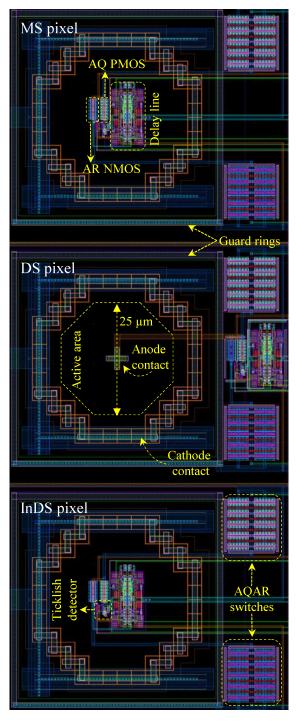

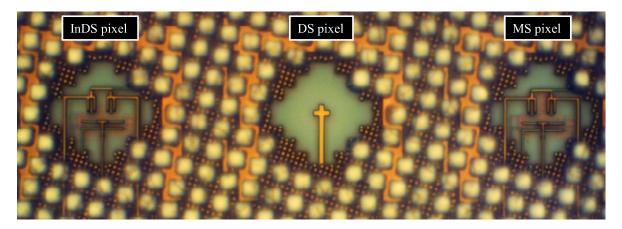

| 3.3.1.    | Native 3D Pixel Structure                         |  |

| 3.3.2.    | Placing the Circuit Over SPAD67                   |  |

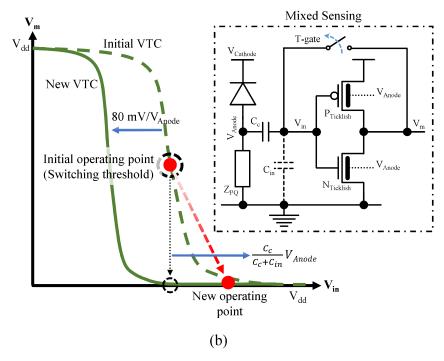

| 3.3.3.    | Mixed Sensing and Indirect Sensing Pixels         |  |

| 3.4. Res  | sults and Discussion                              |  |

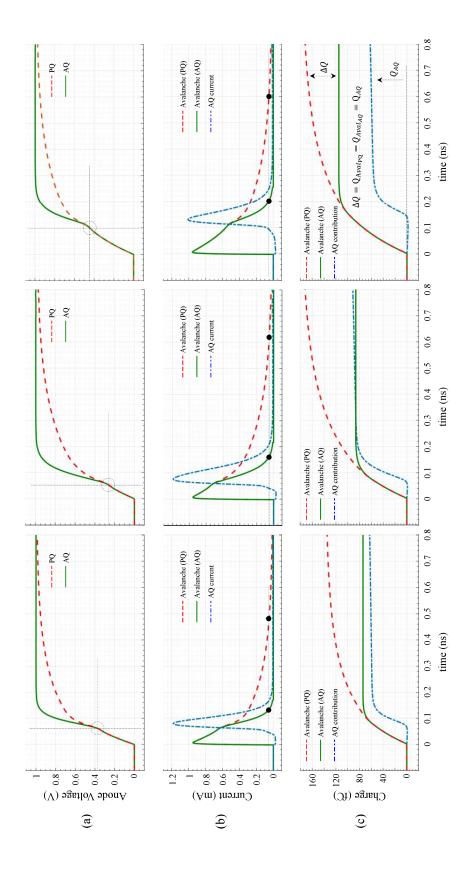

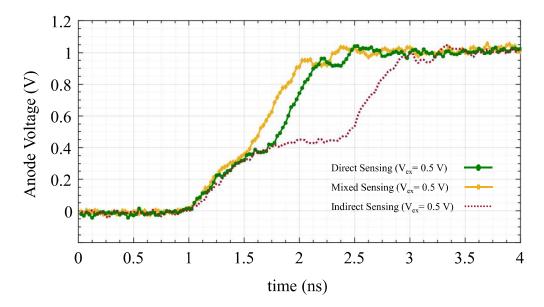

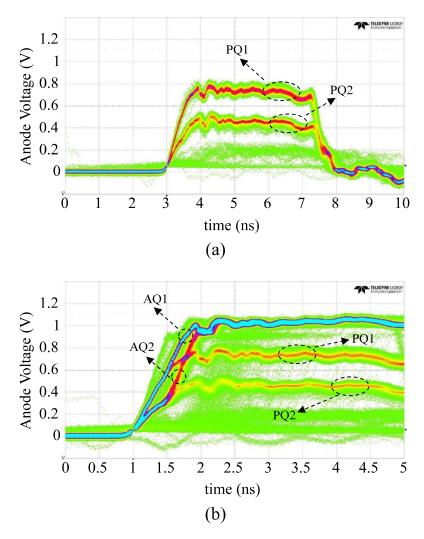

| 3.4.1.    | Post Layout Simulation Results                    |  |

| 3.4.2.    | Experimental Results                              |  |

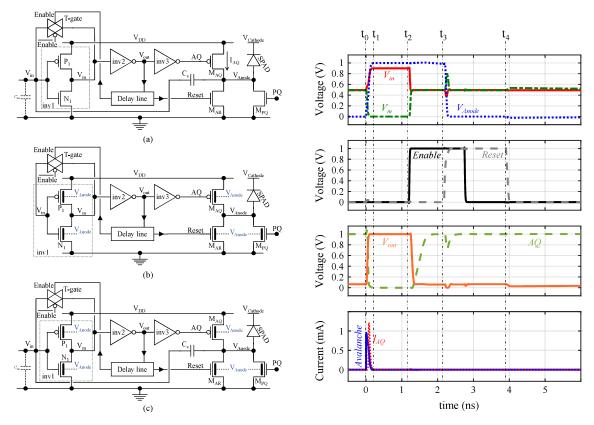

| Chapter 4 | 86                                                |  |

| 4.1. Int  | roduction86                                       |  |

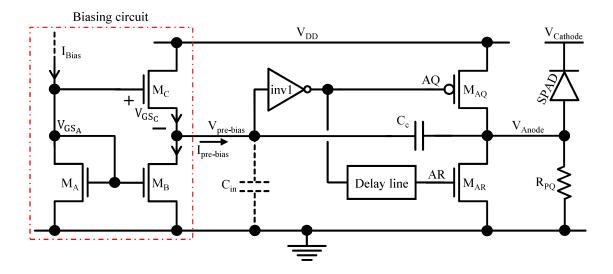

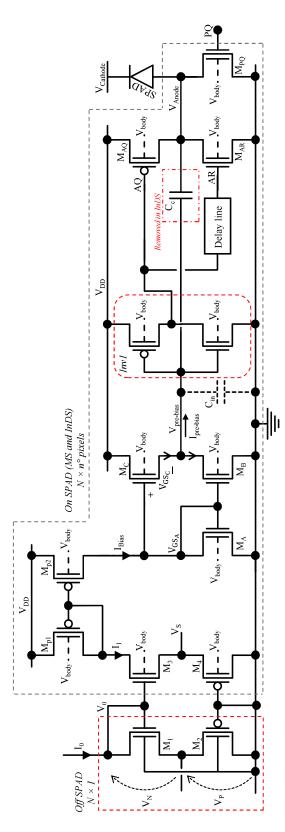

| 4.2. Pre  | e-biased Inverter for Avalanche Detection         |  |

| 4.2.1.    | Pre-biasing Idea86                                |  |

| 4.2.2.    | Biasing Circuit                                   |  |

| 4.3. Na   | tive 3D Pixel & Body Biasing Issue94              |  |

| 4.3.1.    | Body Effect in FD-SOI Technology                  |  |

| 4.3.2.    | Body Independent Biasing Circuit                  |  |

| 4.3.3.    | Body Independent Current Source                   |  |

| 4.4. Pre  | e-Biased Active Quenching Active Reset Circuits99 |  |

| 4.5. Res  | sults and Discussion                              |  |

| 4.5.1.    | Post Layout Simulation Results                    |  |

| 4.5.2.    | Experimental Results                              |  |

| Chapter 5 |                                                   |  |

| 5.1. Co   | nclusions                                         |  |

| 5.2. Per  | rspectives                                        |  |

# List of Acronyms

ACR Afterpulsing Count Rate

ANR Agence Nationale de la Recherche Française

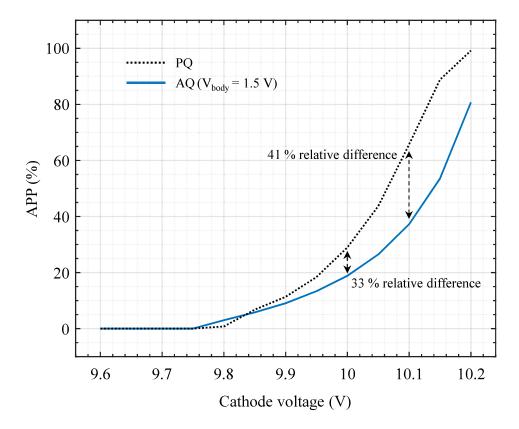

APP Afterpulsing Probability Percentage

AQ Active Quenching

AQAR Active Quenching-Active Reset

AR Active Reset

ATP Avalanche Triggering Probability

BBI Body Biased Inverter-Based

BOX Buried Oxide layer

BSI Back-Side Illumination

CTC Current Transfer Characteristic

DAC Digital to Analog Converters

DCR Dark Count Rate

DRC Design Rule Checking

DS Direct Sensing

FAQ Fast Active Quenching

FD--SOI Fully Depleted-Silicon on Insulator

FLIM Fluorescence-lifetime imaging microscopy

FPGA Field-Programmable Gate Array

FSI Front-Side Illumination

FW Flipped Well

FWHM Full Width at Half Maximum

InDS InDirect Sensing

INL Institut des Nanotechnologies de Lyon

LiDAR Light Detection and Ranging

MS Mixed Sensing

OPW Optical Wireless Communication

PDE Photon Detection Efficiency

PDP Photon Detection Probability

PQ Passive Quenching

PQPR Passive Quenching-Active Reset

PR Passive Reset

RW Regular Well

SCR Space Charge Region

SPAD Single Photon Avalanche Diode

STI Shallow Trench Isolators

TCSPC Time-correlated Single Photon Counting

VLC Visible Light Communication

VLQC Variable Load Quenching Circuit

VTC Voltage Transfer Characteristic

# Introduction

Thanks to their high sensitivity in the optical signal detection and picosecond range temporal resolution, Single Photon Avalanche Diodes (SPADs) play a significant role in a variety of applications that require photon counting or photon timing measurements. Light Detection and Ranging (LiDAR), quantum computing, quantum cryptography, Fluorescence Lifetime Imaging Microscopy (FLIM), and Time-Correlated Single Photon Counting (TCSPC) are some of these applications.

SPADs are PN junctions, reversely biased over the breakdown voltage. This biasing enables them to detect single photons with an incredibly low jitter. SPADs flag a photon by generating a surging current, called the avalanche current. Quenching circuits control the flow of the avalanche current inside the SPAD, and finally extinguish it completely to avoid devices overheating or destruction.

In some emerging applications of the SPAD such as Optical Wireless Communication (OPW), high density arrays and high photon count rates are required. High count rate by a single device is only achievable by shortening the dead time of the SPAD, the time during which SPAD is unresponsive to single photons. Unfortunately shortening the dead time severely increases the afterpulsing effect. Afterpulsing effect is a correlated noise in SPAD that generates spurious avalanches in a short random time after the main photo-generated avalanche. This effect degrades the overall system performance by reducing the dynamic, the signal-to-noise ratio and it also modifies the temporal profile of the signal. Afterpulsing effect can be reduced by utilizing Active Quenching-Active Reset (AQAR) circuits. However, the increased pixel area due to the implementation of these circuits, reduces the sensitivity of the SPAD pixel, which is expressed as Photon Detection Efficiency (PDE). This trade-off between maximum photon count rate, afterpulsing effect, and PDE has raised new research interest on AQAR circuits and innovative pixels structure such as stacked 3D pixels.

The aim pf this Ph.D. thesis is to propose ultra-fast AQAR circuits in a 28 nm Fully Depleted-Silicon on Insulator (FD-SOI) CMOS technology, alongside with a novel avalanche sensing method and a new SPAD pixel structure, that are able to mitigate the mentioned trade-off without the extra expenses of 3D stacking process at wafer level. This work is a collaboration between ICube laboratory of University of Strasbourg and Institut des Nanotechnologies de Lyon (INL), which provide SPAD devices structures and layouts. The project is funded by the Agence Nationale de la Recherche Française through the grant of the project "SPAD-FDSOI" (ANR-18-CE24-0010).

The manuscript organization is as follows: in chapter 1 a brief introduction on SPAD physics and its operation principles is presented. It follows by introducing some of the SPAD important parameters such as Photon Detection Probability (PDP), jitter, Dark Count Rate (DCR), afterpulsing effect. The rest of this chapter is dedicated to the state of the arts of AQAR circuits. At the end of this chapter, the SPAD devices used in this thesis are briefly introduced.

In chapter 2, an ultra-fast AQAR circuit, featuring a simple and compact avalanche detection circuit is presented. Through post layout simulations and experimental results, the functionality and efficiency of the proposed AQAR circuit in the afterpulsing reduction are investigated.

In chapter 3, a novel avalanche detection circuit with three different variants is presented, which results in three AQAR circuits. The concept of monolithic 3D SPAD pixel is introduced and based on that the first active monolithic 3D SPAD pixel is introduced. A new avalanche sensing method is also proposed that can increase the efficiency of AQAR circuits. Thanks to the post-layout simulation and experimental results, all the proposed circuits are validated. Also, effects and challenges of placing electronics over the SPAD in the active monolithic 3D SPAD pixel is discussed.

In chapter 4, body biasing in the FD-SOI CMOS technology and its effect on the active monolithic 3D SPAD is investigated. The first body voltage independent current source is presented to bias the circuits in the monolithic 3D pixel. Another avalanche detection circuit in three different variants is proposed. Each variant leads to a low power ultra-fast AQAR circuit. Like the last two chapters, post-layout simulations and experimental results are presented.

Finally, chapter 5 concludes the manuscript by comparing the different proposed AQAR circuits. Furthermore, this chapter outlines potential avenues for future development and research, highlighting the prospects of the thesis.

# Chapter 1 SPAD and Quenching Circuits

# 1.1. SPAD Operation Principals

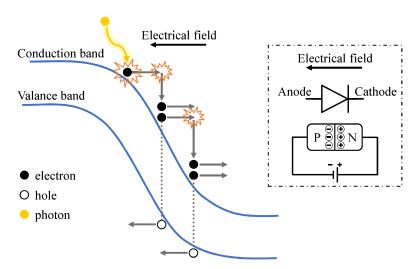

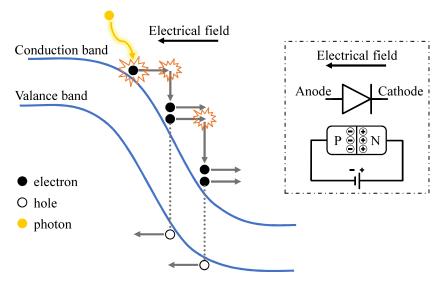

Reversely biasing a diode over its breakdown voltage generates a strong electric field across the diode junction. Under this biasing condition, the impact ionization can occur in the multiplication region [1]–[3]. The multiplication region is part of the depleted area of the junction where has the highest electric field. In this region, a free carrier, either an electron or a hole, has enough energy to break a bond in the semiconductor lattice and thus generates an electron-hole pair. The newly generated carriers also undergo the same scenario, and a positive feedback loop of impact ionization arises in the Space Charge Region (SCR). At breakdown voltage the multiplication factor of the PN junction is infinity [4], [5]. Thus, a fast-rising avalanche of charge carriers flows through the SCR. The initial free carrier can be generated by an incident photon thanks to the internal photoelectric effect [6], [7]. Single Photon Avalanche Diodes (SPADs), based on these principles, are able to convert a single photon to a measurable current, called the avalanche current, within a few tens to hundreds of picoseconds[1], [8]–[11]. The avalanche process in a reversed biased PN junction is illustrated in Fig. 1.1.

Fig. 1.1 Avalanche process in a reverse biased PN junction due to the photo electric phenomenon. Inset: a diode in the reverse bias with its electrical symbol.

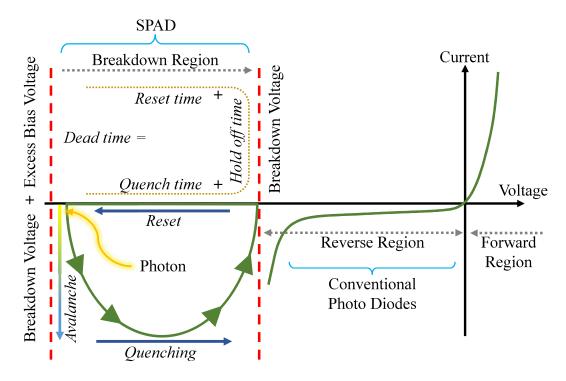

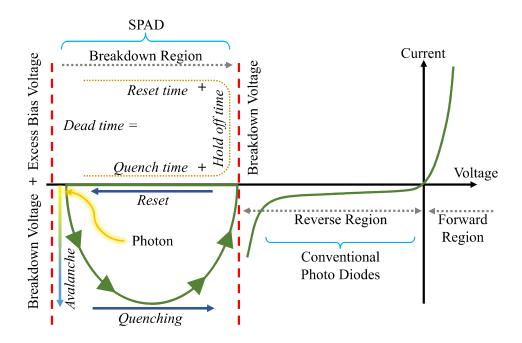

Fig. 1.2 Symbolic I-V characteristic of a SPAD with quench-reset dynamic.

Fig. 1.2 shows the I-V characteristic of a typical diode. To operate as a SPAD, the diode is biased in the breakdown region, over the breakdown voltage. The difference between the SPAD biasing voltage in the breakdown region and the breakdown voltage is called excess bias voltage. In this region, an incident photon can generate a self-sustaining avalanche current [12]. The current can be high enough to destroy the diode if it is not stopped. The process of stopping avalanche current to flow is called quenching [13]. To quench the SPAD, the voltage across its junction must drop below the breakdown voltage. The quenching can be done by means of an active circuit, which is called Active Quenching (AQ), or simply by putting a large resistor in series with the SPAD, in the Passive Quenching (PQ) case [14], [15]. Once the avalanche is quenched and the SPAD is biased out of its breakdown region, the electric field across the junction is reduced and consequently the SPAD cannot generate a self-sustaining avalanche current. To prepare the SPAD for the next photon detection, it must be biased again in the breakdown region. Similar to the quenching process, resetting (recharging) the SPAD can be done by an active circuit, Active Reset (AR), or by a passive resistive path, Passive Reset (PR) [16], [17]. The avalanche dynamic behavior is illustrated in Fig. 1.2. The time interval between the onset of the avalanche and end of the reset phase is known as deadtime, during which the SPAD is unable to detect a new photon. It is composed of quenching time, reset time, and hold-off time, during which the SPAD is below the breakdown voltage. A short deadtime increases the photon count rate, at the cost of increasing SPAD noise [9]. This trade-off is discussed in the following sections.

The ability to detect a single photon with a high temporal resolution makes SPAD suitable for photon counting and photon timing applications. SPADs play a critical role in a wide range of applications, from bio photonic to quantum computing, including Fluorescence Lifetime Imaging (FLIM), optical tomography, quantum random number generator, Light Detection and Ranging (LiDAR), Visible Light Communication (VLC), and many others [18]–[51].

## 1.2. SPAD Performance Parameters

There are several parameters that determine the SPAD performance, from the pixel level up to the system level, in the mentioned applications. In this section some of the most important parameters of SPAD are briefly introduced, and the proposed solutions in the literature to improve these parameters are presented.

## 1.2.1. Photon Detection Probability (PDP)

SPAD is a single photon detector, however, not all the impinging photons to its light sensitive area can be necessarily detected. The probability that an incident photon generates a self-sustaining measurable avalanche current is defined as Photon Detection Probability (PDP), which indicates the sensitivity of a SPAD. There are several possible scenarios for the incident photons to a SPAD: some of them are reflected by the different material stacks in the technology structure. Some of the incident photons are absorbed in the neutral regions of the junction. Among the resulting photogenerated carriers, the majority carriers (electrons in N and holes in P) are repelled by the electric field across the multiplication region, thus, it is impossible for them to start an impact ionization. The minority carriers have the chance to diffuse into the multiplication region, however, they can also be trapped or recombined before reaching the multiplication region [1], [52], [53]. Even a carrier that reaches the multiplication region or is absorbed in that region, because of the statistical nature of the impact ionization, has a certain possibility to trigger an avalanche, defined as the Avalanche Triggering Probability (ATP) [54], [55]. Therefore, PDP of a SPAD cannot reach 100 %. ATP is increased by the electric field across the junction. Therefore, to increase the PDP, one can increase the excess bias voltage and apply a uniform electric field through the doping

engineering [56]–[64]. Anti-reflection coating is another approach to increase the PDP by decreasing the number of reflected photons [65], [66].

PDP also depends on the wavelength of the incident light and the optical absorption of the SPAD material [1], [58], [67]. Thus, to have an optimum PDP at a specific wavelength range from near ultra-violet to near infra-red (250 nm – 1550 nm), different semiconductor materials (silicon and other compound semiconductors) are used to implement the SPAD [47], [48], [68]–[87].

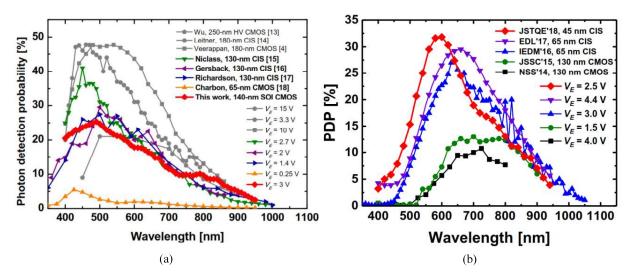

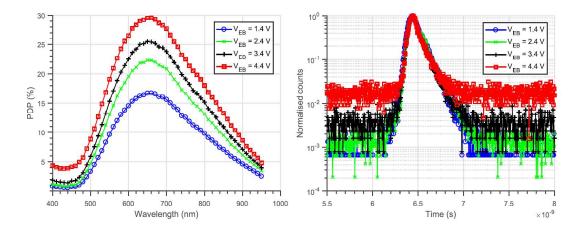

The PDP peak occurs at different wavelengths regarding the illumination configurations. Fig 1.3 shows that in a Front-Side Illumination (FSI), the peak PDP is around the near ultra-violet and blue range, while in the Back-Side Illumination (BSI), the peak PDP is shifted around the infrared range. Also, the technology scaling effect on the PDP is also observable in Fig. 1.3 (a). In the lower technology nodes, the PDP peak becomes lower and narrower [88], [89].

Fig. 1.3 Photon Detection Probability (PDP) versus impinging light wavelength at different technology nodes: (a) Front-Side Illumination (FSI) [88] (b) Back-Side Illumination (BSI) [89].

#### 1.2.2. Timing Jitter

Thanks to the high electric field over the multiplication region, SPAD has an ultra-fast time response, i.e., the avalanche process starts almost immediately by an impinging photon [10], [11]. However, the coming photons, as explained previously, are not necessarily absorbed in the multiplication region. Those carriers generated by the photons who land in the neutral regions, pass different paths to reach the multiplication region, which takes different times. Also, each carrier in the multiplication region can experience a different avalanche build-up [90] process due to the

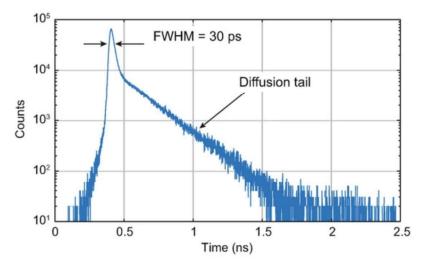

statistical nature of the impact ionization [91]–[95]. These effects introduce fluctuations in the time response of the SPAD, which is called timing jitter. It is expressed as the distribution of the photon arrival time at its Full Width at Half Maximum (FWHM). To measure the jitter, a picosecond laser pulse repeatedly illuminates the SPAD. Each time the interval between the trigger time of the laser pulse and the photon detection time is measured to obtain the photon arrival time histogram [96], [97]. Fig. 1.4 shows an arrival time histogram presented in [98]. The exponential part of the histogram is called the diffusion tail, representing the avalanches generated by the photons absorbed in the neutral regions [99]. The jitter of a SPAD can be as low as a few tens of picoseconds [87], [97], [100]–[103]. Same as in PDP case, a higher electric field improves the SPAD jitter [102].

Fig. 1.4 Photon arrival time histogram of a SPAD, composed of a Gaussian peak and a diffusion tail [98].

#### 1.2.3. Dark Count Rate (DCR)

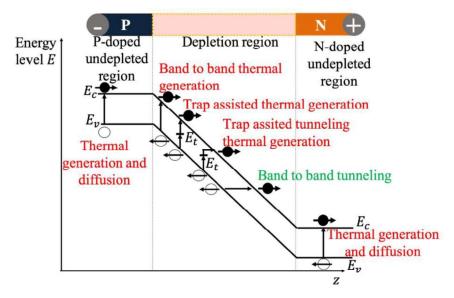

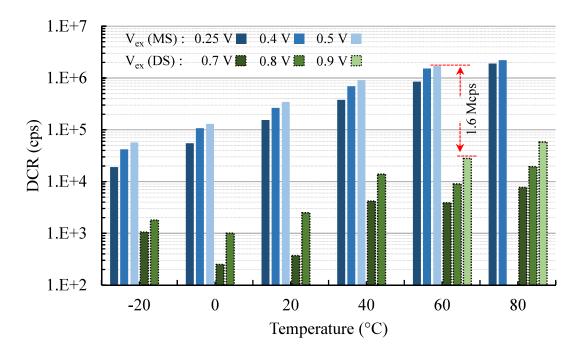

Photoelectric phenomenon is not the only way that starts an avalanche. A thermally generated carrier or a free carrier by tunneling effect can also trigger the impact ionization process [1], [104], [105]. Thus, in the absence of light, SPAD may generate non-photogenerated avalanches. These spurious avalanches are one of the main noise sources of SPADs, called dark counts. Thermal generation, trap-assisted generation, band to band tunneling, and trap-assisted tunneling are responsible for dark counts [106], [107], see Fig. 1.5. Dark Count Rate (DCR) is defined as the number of avalanches per second when the SPAD is placed in complete darkness. DCR delimits the minimum photon count rate of a SPAD, thus, for the applications with low intensity input light is crucially important. DCR is dependent on the semiconductor materials, doping profile,

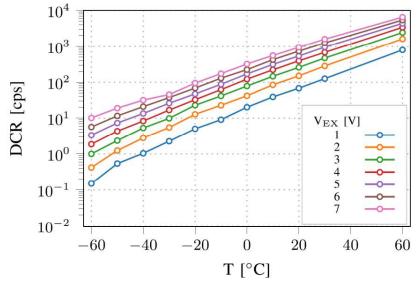

temperature, and the junction electric field [9], [108]. Despite PDP and jitter, a high excess bias voltage increases DCR, therefore, there is a trade-off between these parameters. A common way to decrease the DCR is to cool down the SPAD, since there is a proportional relationship between the DCR and the temperature [9], [56], [87], [97]. Fig. 1.6 shows the dependency of DCR on the excess bias voltage and the temperature.

Fig. 1.5 DCR contributions illustration for a reverse biased p-n junction [106].

Fig. 1.6 Temperature and excess bias voltage dependence of DCR for a SPAD presented in [56].

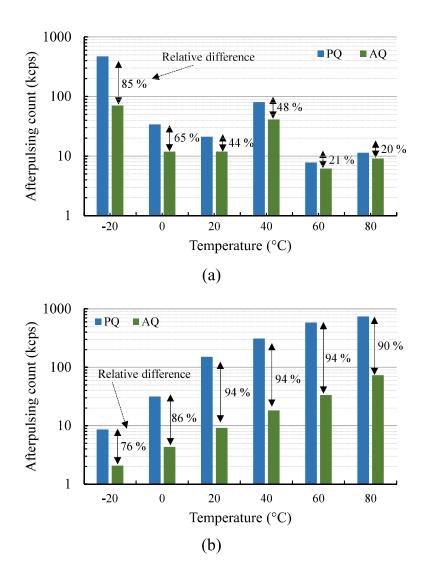

## 1.2.4. Afterpulsing

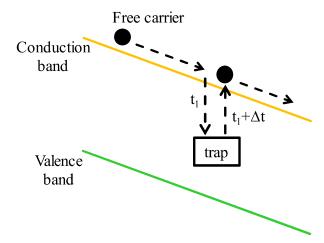

When the avalanche current is passing through the SCR, some of the carriers are captured by the traps inside the semiconductor lattice. These traps, which are the result of defects and impurities in the semiconductor material, hold the carrier for a random time, depending on the temperature and the energy of the trap [109], see Fig. 1.7. The captivity time can reach up to the microsecond range. Two possibilities exist for the released carrier: after the main photo-generated avalanche, if the SPAD is reset sooner than the longest trap lifetime, the released carrier can trigger a new impact ionization, resulting in a non-photo-generated avalanche. This spurious avalanche, which has a correlation with the main photo-generated avalanche, is called afterpulse, and the process of the afterpulse generation is called afterpulsing effect or simply afterpulsing. Afterpulsing effect, alongside with the DCR, is a main noise source in SPADs that delimit their maximum photon count rate [9].

Fig. 1.7 Trapping and release of a free carrier in an avalanche photo diode: the origin of afterpulsing effect.

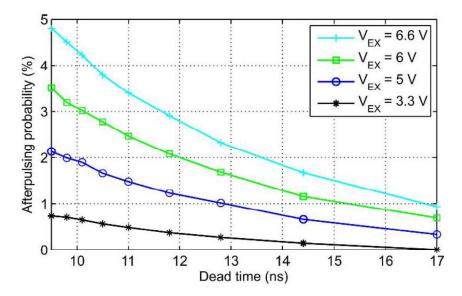

However, in the second scenario, if the carrier is released while the SPAD is out of the breakdown region, i.e., during the hold-off time, the electric field is not high enough to allow the released carrier to start an avalanche. Therefore, it is a common solution in the afterpulsing reduction to prolong the dead time of the SPAD [110]–[113]. Fig. 1.8 shows the dependency of afterpulsing on the dead time [113]. On the other hand, prolonging the dead time, severely decrease the maximum photon count rate, which is not desired in the photon counting applications such as VLC and LiDAR [114]. Also, cooling down the SPAD to reduce the DCR, increases the afterpulsing effect, because at lower temperatures the traps tend to hold the carriers for a longer

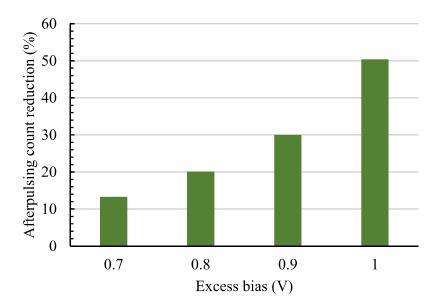

time [109]. A higher electric field, as in the DCR case, increases the afterpulsing effect as shown in Fig. 1.8.

Fig. 1.8 Afterpulsing probability versus dead time at different excess bias voltages (VEX) [113].

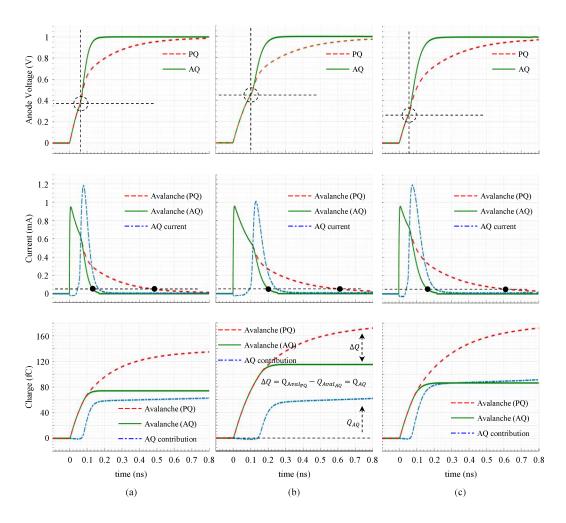

Afterpulsing effect depends on the number of traps in the semiconductor lattice and the number of charge carriers during an avalanche. Thus, a way to reduce the afterpulsing effect is decreasing the avalanche charge [115]. This is done by AQ circuits, which provide part of the charge that is needed to bias the SPAD out of the breakdown region and stop the impact ionization process. It allows the SPAD not to generate all the required charge for the quenching, and therefore reduces the charge carriers in the SCR. In this solution, afterpulsing effect is reduced without affecting the maximum photon count rate [116]. The AQ circuits are discussed in detail in this chapter. However, the AQ circuits have some drawbacks that are highlighted in the next section.

#### 1.2.5. Fill Factor & Photon Detection Efficiency (PDE)

The ratio between the SPAD active (light sensitive) area and the whole pixel area, including the guard ring, quench/reset circuits, and readout circuit, is defined as fill factor. The fill factor value is presented as a percentage and is always less than 100 %. It measures how efficient the total area of a pixel is used to detect the incident photons. A larger fill factor means more photons can be absorbed in the active area of the SPAD pixel. Thus, there is a proportional relationship between the fill factor and the sensitivity of a pixel [47], [114]. This relationship is defined by another important SPAD parameter, named Photon Detection Efficiency (PDE). PDE is the product of PDP

and fill factor [117]. It is the probability of detecting a photon colliding on the SPAD pixel and measures the sensitivity and efficiency of a pixel in detecting a photon.

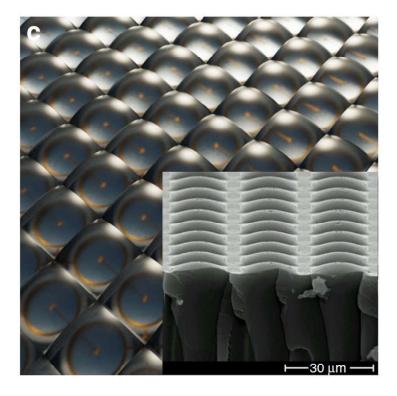

To have the maximum sensitivity, the fill factor must be maximized. The electronic interface of the pixel, e.g., Active Quenching-Active Reset (AQAR) circuits, which are necessary for afterpulsing reduction and other functionality of the pixel such as dead time control, severely reduces the fill factor, and therefore the PDE. One can see a trade-off between afterpulsing effect, maximum photon count rate and fill factor or PDE [47], [114]. A few solutions are proposed in the literature to alleviate this trade-off. Using microlenses is one of these solutions [70], [75], [118]–[125]. A microlense is literally a small lens that focuses the coming photons onto the active area of the pixel. Collecting more photons on the SPAD active area and consequently detecting more, results in a higher fill factor and PDE. Fig. 1.9 shows a microlens array integrated with an SPAD array [18]. The main drawback of microlenses is the extra fabrication costs and technological constraints.

Fig. 1.9 Microlens array integration with a SPAD array [18]. Inset: scanning electron microscope image of the microlens array from ref. [125].

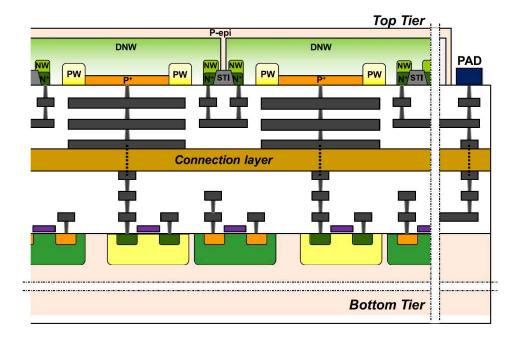

Another solution is the stacked 3D IC technology. In this method, the SPAD array and the peripheric circuitry are fabricated on separate dies and then bonded together through specific

bonding processes [30], [76], [126]–[129], see Fig. 1.10. In the absence of the interface electronics, the pixel area is mostly occupied by the SPAD active area, resulting in a very high fill factor and PDE. Beside this main advantage, stacked 3D IC technology allows utilizing specific technologies for each separate die. Implementing SPADs in customized SPAD technology gives the opportunity to fine tune the SPAD performance parameter such as PDP and DCR. Also, it is possible to use scaled technology nodes for the electronics to benefit from their high area density and low power consumption [64], [130]–[132]. The drawback of this method is the high manufacturing costs due to the two separate dies, in comparison with the conventional 2D IC technology. Also, the fabrication process is complicated by the interconnections of the dies [18], [133].

Fig. 1.10 Cross section of a 3D stacked backside illuminated SPAD array [126].

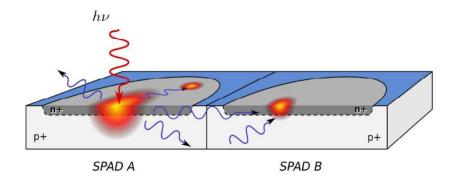

#### 1.2.6. Crosstalk

In a SPAD array, avalanche flows through the SCR of a SPAD can trigger other avalanches in the neighboring SPADs. The spurious avalanche that is correlated with the first avalanche is another noise source of the SPAD, called crosstalk. When an avalanche of carriers is flowing into the junction, some of the carriers can diffuse to junction of the neighboring SPADs. There, as a free carrier, it can start a new avalanche. This type of crosstalk is categorized as electrical crosstalk. The avalanche carriers can also undergo an electron-hole recombination process as explained in

Fig. 1.11 Symbolic representation of optical cross talk between two SPADs [135].

the PDP section. The electron-hole recombination generates a photon that can be absorbed by the neighboring SPADs [52]. This secondary photo-generated avalanche is optical cross talk, see Fig. 1.11. To reduce the crosstalk noise, it is proposed to place insulators between adjacent SPAD or increase the distance between the SPADs in the array [9], [134]–[136]. Also, one can see the source of crosstalk are avalanche charge carriers [137]. Thus, as an ultimate solution, reducing the avalanche charge can reduce crosstalk. Same as in the afterpulsing case, this avalanche charge reduction can be done through the AQ circuits. However, implementing each of these solutions degrades fill factor, pitch, and PDE of the SPAD, which is an obstacle in realizing dense SPAD arrays.

# 1.3. Quenching Circuits State of the Arts

In the breakdown region, even one single photon can generate an avalanche of current carriers, which can keep flowing till damaging the device. Thus, as it is already explained, once an avalanche has occurred it is mandatory to stop its flow through the SPAD to avoid devices overheating or destruction. This action is done by biasing the SPAD out of its breakdown region through a quenching circuit. When the voltage across the SPAD is below or equal to the breakdown voltage, the SPAD is unable to generate a self-sustaining avalanche current. A quenching circuit is also necessary for determining and limiting the dead time and the count rate of the device, and to make the device reusable for the next coming photons.

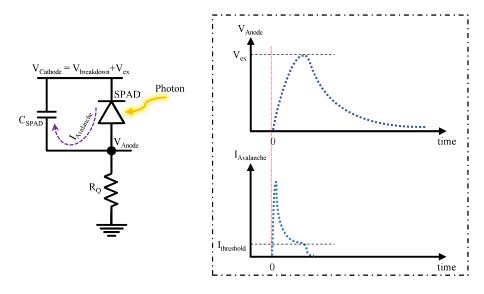

## 1.3.1. Passive Quenching

There are two general categories of quenching circuits based on their components: Active Quenching (AQ) and Passive Quenching (PQ) circuits. In PQ circuit, SPAD is connected to a high

impedance path which can be a high value resistor or a transistor that operates as a resistor. Fig. 1.12. shows schematic of a PQ circuit. In this circuit, once an avalanche breakdown occurs, the avalanche current starts to charge the SPAD junction capacitance  $C_{SPAD}$ . Thus, the voltage across the quenching resistor  $R_Q$  increases till it reaches the excess bias voltage. Now the SPAD is quenched, and the avalanche current has stopped.

Fig. 1.12 Schematic of the PQ circuit with the anode voltage and the avalanche current transitions during an avalanche.

It should be noted that in PQ circuit, the diode voltage cannot reach below the breakdown voltage, thus, the current can still flow through the SCR. In the literature, however, a threshold is defined for the avalanche current, which below this threshold, the avalanche cannot be a self-sustaining current and the carriers will leave the SCR before triggering a self-sustaining avalanche [13]. It establishes a minimum value for the passive quenching resistor [15]. The maximum current passing through RQ is equal to:

$$I_{max,Q} = \frac{V_{ex}}{R_Q} \tag{1}$$

Where  $V_{ex}$  is the excess bias voltage. This current is provided by the SPAD. Thus, to effectively quench the SPAD, this current must be sufficiently lower than the avalanche threshold current that implies a minimum RQ value. A lower  $R_Q$ , makes the SPAD to function almost as a Zener diode with a potentially very high current that can destroy the diode.

The quenching time in PQ circuit is mostly determined by  $C_{SPAD}$  and other physical phenomena that are involved in the avalanche build up process. In fact, almost all the avalanche current is passing through the SPAD junction capacitance, while only a negligible amount of current is passing through the quenching resistance. Therefore,  $R_Q$  has almost no effect on the quenching time. Since the avalanche build up is a statistical process, the quenching time in a PQ circuit is also statistical. Even though, a higher quenching resistor can slightly decrease the quenching time [13].

In the reset phase however,  $R_Q$  plays a major role and defines the reset time constant with  $C_{SPAD}$ . Since  $R_Q$  typically is high, the reset phase in PQ circuit is long. During the reset phase, the SPAD voltage is above the breakdown, thus, the possibility of new avalanche triggering exists before complete reset of the SPAD. A new avalanche in this condition prolongs further the reset time and limits the maximum photon count rate. Moreover, it makes the reset also a statistical process which depends on the number and duration of the weak avalanches during the reset phase.

PQ circuits are easy to implement and occupy a very small area which makes them desirable for realizing SPAD arrays [138], [139]. However, as mentioned already, they suffer from indefinite quenching and reset times. Even though integrating an AR circuit with a PQ circuit can result in a well-defined reset time [17], [64], [97], [140], [141], yet the quenching time is a problem. Besides, by adding electronics for implementing the AR circuit, the resulting circuit cannot be as compact as it is claimed. Another drawback of the PQ circuit is that it cannot reduce the afterpulsing effect, since in this quenching method, all the required quenching current (the current that needs to charge  $C_{SPAD}$ ) is provided by SPAD itself.

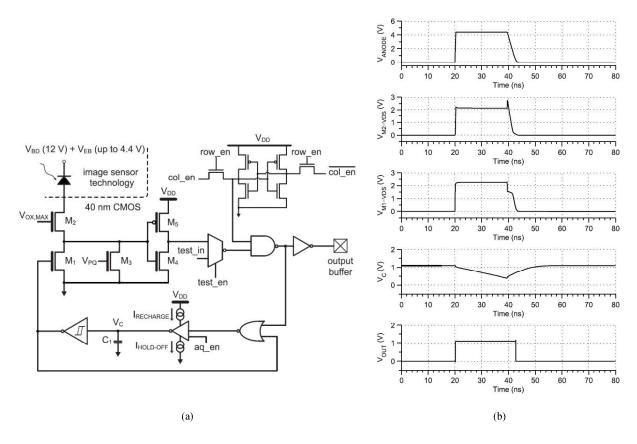

Fig. 1.13 (a) shows a Passive Quenching-Active Reset (PQAR) circuit which is presented in [64] and with slight modifications in [97]. The authors used the cascode technique to enable the SPAD to operate with a higher excess bias voltage than the oxide breakdown of the transistors. By cascoding  $M_2$  with  $M_3$  which is implementing the passive quenching resistor, the anode voltage (and consequently the excess bias voltage) can safely reach a voltage two times higher than the maximum tolerable voltage of the oxide of  $M_3$ . Since the MOSFETs  $M_1$  to  $M_5$  are thick oxide MOSFETs, their maximum tolerable voltage is 2.75 V in the used technology. By applying 4.4 V of  $V_{ex}$ , thanks to this technique, around 30 % improvement in the peak PDP value of the device and 13 ps reduction of the jitter is achieved in comparison with  $V_{ex} = 2.4$  V. Fig. 1.14 shows the

Fig. 1.13 (a) Schematic of the PQAR circuit presented in [64]. (b) Timing diagram of the circuit in (a).

PDP and jitter improvements in this circuit. It should be noted that for a safe operation at 4.4 V of  $V_{ex}$ , the gate voltage of  $M_2$   $V_{OX,MAX}$ , must be the highest possible value (2.75 V).

The timing diagram of the circuit is presented in Fig. 1.13 (b). Avalanche current flow raises the anode voltage. The anode voltage distributes between the drain-source voltages of M<sub>1</sub> and M<sub>3</sub> as well, till completely quenches the SPAD. During this time M<sub>1</sub> is set to be off. The drain-source voltage rise of M<sub>3</sub> is sensed by the inverter composed of M<sub>4</sub> and M<sub>5</sub>. This inverter finally drives a current starved inverter which controls the hold off time and reset time of SPAD through I<sub>RECHARGE</sub>, I<sub>HOLD-OFF</sub>, and C<sub>1</sub>. During the quenching phase C<sub>1</sub> is discharged by I<sub>HOLD-OFF</sub> till it reaches the lower threshold of the Schmitt trigger. Now M<sub>1</sub> turns on and the SPAD is reset through M<sub>1</sub> and M<sub>2</sub>. After a determined time, C<sub>1</sub> is charged by I<sub>RECHARGE</sub> till V<sub>C</sub> passes the upper threshold of the Schmitt trigger that turns M<sub>1</sub> off once again to end the reset phase and make the pixel ready for a new event. The total circuit area is 25.2 μm<sup>2</sup>.

Fig. 1.14 (Left) PDP versus wavelength at different excess bias voltages and (Right) Jitter at different excess bias voltages for the pixel presented in [64].

## 1.3.2. Active Quenching

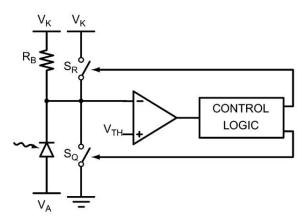

Nondeterministic quench and reset timing, plus inability in afterpulsing reduction, as two main drawbacks in PQ circuits, has led to another type of quenching circuit, named Active Quenching (AQ) circuit. An AQ circuit is typically composed of two main parts: an avalanche detection circuit and a fast switch or a variable load. The avalanche detection circuit, which can be a comparator, senses the avalanche and reacts to it by generating a driver signal for the switch or the variable load. The switch then turns on and biases the SPAD out of its breakdown region by lowering the voltage across the SPAD. In the variable load case, the driver signal generated by the detection circuit increases the load at the dynamic node of the SPAD to quench the SPAD sooner. Fig. 1.15 shows a symbolic schematic of an AQ circuit.

Fig. 1.15 Schematic of an AQAR circuit. SQ and SR are AQ and AR switches, respectively.

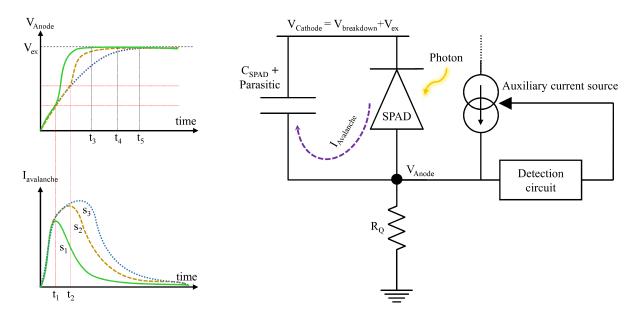

Fig. 1.16 Avalanche current reduction through AQ circuit. Different detection times results in different avalanche currents  $(S_1, S_2, S_3)$  and different quenching times  $(t_3, t_4, t_5)$ .

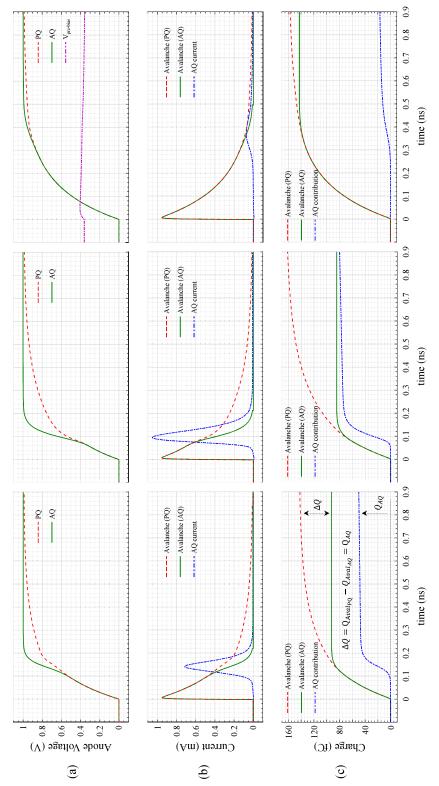

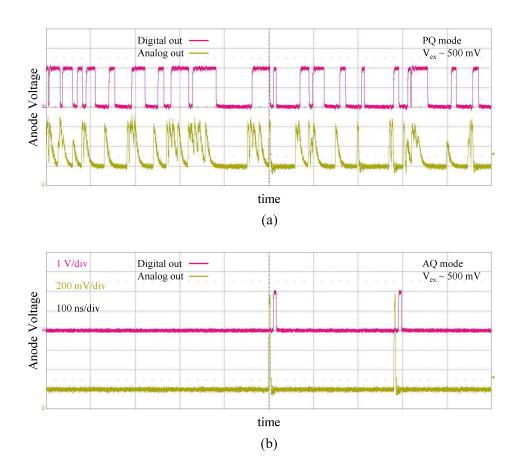

In an AQ circuit, if the SPAD is quenched sooner than in the pure PQ mode, the avalanche current would be lowered. Lower current in the SCR means less trapping probability, which results in less afterpulsing effect without increasing the dead time. This interesting feature of AQ circuits prompts several research on implementing such a circuit to reduce the noise of the SPAD and mitigate the tradeoff between the afterpulsing effect and the maximum photon count rate of the SPAD. The efficiency of an AQ circuit is determined by its contribution in providing the required charge for charging the SPAD junction capacitance to bias the SPAD out of the breakdown region. In this case one can consider the switch as an auxiliary current source which provides this charge, see Fig. 1.16. Thus, the amount of current that it provides, and the moment that it starts its contribution are two determining factors in the afterpulsing reduction. The more the auxiliary current is, the less the avalanche current and consequently the less the afterpulsing effect. A higher auxiliary current is highly dependent on the time for the switch to be turned on. If the switch starts to conduct at the end of the quenching phase, it cannot speed up the quenching process and help the SPAD in providing the required charge for quenching. Thus, to have an efficient quenching for the afterpulsing reduction, it is of the highest importance to detect the avalanche at its very early stages and react to that as soon as possible. It can be concluded that the efficiency of an AQ circuit in the afterpulsing reduction strongly depends on the speed of its avalanche detection circuit.

Fig. 1.16 shows how a sooner avalanche detection results in a faster quenching and less avalanche charge.

## 1.3.3. State-of-the-Art Active Quenching Circuits

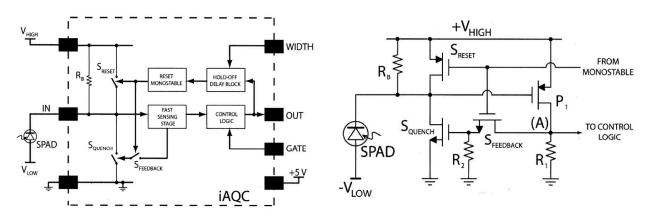

The first integrated AQ circuit, aiming afterpulsing reduction through the avalanche current decrease, has been presented in [14]. Fig. 1.17 shows the schematic of the proposed AQAR circuit in this work. In the standby mode the SPAD is biased in the breakdown region, and a signal from the monostable turns the reset switch (S<sub>RESET</sub>) and feedback switch (S<sub>FEEDBACK</sub>) off and on, respectively. When an avalanche occurs, the PQ phase starts through R<sub>B</sub> which implements the PQ resistor, and thus the cathode voltage (IN) increases. This voltage increase is sensed through the sensing stage realized by MOSFET P<sub>1</sub>. Thus, the voltage at node (A) is increased in a positive feedback loop and turns the quenching switch (S<sub>QUENCH</sub>) on. Now the AQ phase is started till it completely quenches the SPAD, see Fig. 1.18. A delay block controls the hold off time from 50-500 ns. After a certain hold off time, the monostable turns S<sub>FEEDBACK</sub> off and S<sub>RESET</sub> on to start the AR phase. After the reset phase, once again the monostable turns the S<sub>RESET</sub> off and S<sub>FEEDBACK</sub> on to prepare the SPAD for a new event.

The proposed circuit is fabricated in a high voltage  $0.8~\mu m$  CMOS technology and occupies an area of  $2mm^2$  (pads included). The AQAR circuit detects the avalanche in less than 12~ns and quenches it in 25~ns for a 20~V of  $V_{ex}$ . The reset phase takes about 20~ns. The maximum count rate of the pixel is 20~MC/s, and the circuit dissipates 20~mW of power in the quiescent mode.

Fig. 1.17 (Left) Symbolic view of the proposed AQAR circuit in [14], (Right) Schematic diagram of the input sensing stage.

Fig. 1.18 Cathode voltage (IN) transitions during an avalanche. Voltage scale: 5 V/div, time scale: 20 ns/div [14].

One of the solutions to reduce the AQAR circuit area is to realize all the circuit by NMOS transistors to avoid implementing isolated N-wells for PMOS transistors.

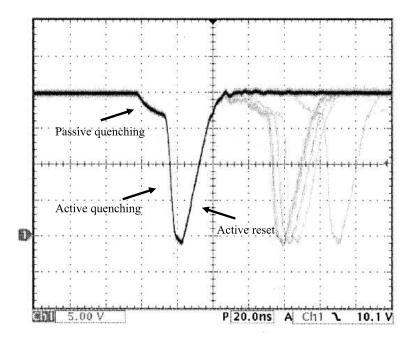

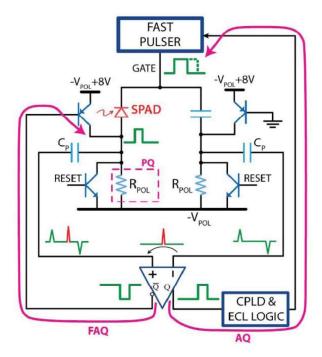

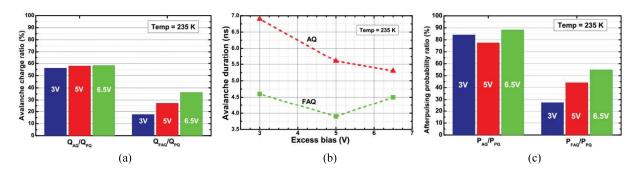

Fig. 1.19 shows an AQAR circuit presented in [142]. In this circuit three different paths for quenching exist: R<sub>POL</sub> which realizes the passive quenching resistor, a FAST PULSER unit which gates on and off the SPAD, and a wideband pnp transistor connected to anode which actively quenches the SPAD. The authors call the gating in this paper "AQ," and the AQ realized by the pnp transistor Fast AQ "FAQ." Occurrence of an avalanche increases the anode voltage thanks to the PQ resistor R<sub>POL</sub>. This voltage increase is sensed by a comparator which drives the Gating circuit ("AQ") and FAQ pnp. Now the AQ phase is started till the end of the quenching phase. After a certain hold-off time the RESET npn transistor reset the SPAD for another avalanche detection. The right side of the circuit is almost identical to the left side, which is the main branch of the circuit. On the right side a capacitor imitates the SPAD junction capacitor, and the rest of the circuit components exist to reproduce the parasitic at the SPAD anode to generate a precise reference voltage for the sensing comparator. Bipolar technology is used to speed up the quenching process. The avalanche charge reduction for different quenching methods in comparison with the PQ mode is presented in Fig. 1.20 (a). In the best case (FAQ with 3 V V<sub>ex</sub>), the avalanche charge

Fig. 1.19 Quenching and reset front end presented in [142] composed of passive quenching (R<sub>POL</sub>), active quenching (FAQ), Gating (AQ), and reset circuits.

Fig. 1.20 (a) Estimated avalanche charge with active quenching  $(Q_{AQ})$  and fast active quenching  $(Q_{FQ})$  normalized to the passive quenching case  $(Q_{PQ})$ . (b) Dependence of quenching time on the excess bias voltage in different quenching circuits. (c) Estimated afterpulsing probability with active quenching (AQ) and fast active quenching (FAQ) circuits, normalized to the passive quenching case [142].

is about 20 % of the avalanche charge in PQ mode, which means 80 % charge reduction. This is due to the shortened quenching time in the AQ modes in comparison with the PQ mode. Fig. 1.20 (b) shows the quenching time for the AQ modes. The FAQ mode presents the fastest quenching time of about 4 ns. Fig. 1.20 (c) concludes that a shortened quenching time results in a reduced avalanche charge which ends in a less afterpulsing probability. In the best case (FAQ with  $3 \text{ V V}_{ex}$ ) the afterpulsing probability is reduced by 75 % in comparison with the pure PQ mode.

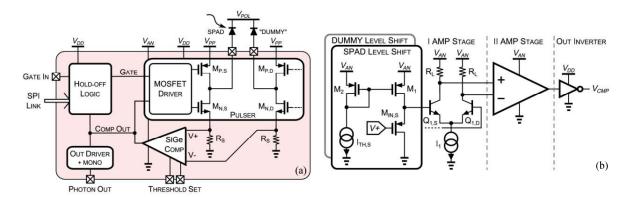

Fig. 1.21 (a) Block diagram of the quenching and gating circuit presented in [143]. (b) Schematic of the comparator in (a).

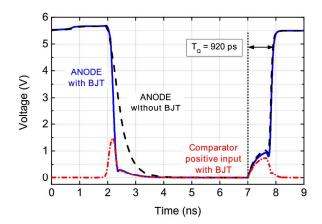

Fig. 1.22 Simulated waveforms at SPAD anode and at comparator positive input at 230 K. Anode voltage is reported with and without  $Q_S$  and  $Q_D$  BJT transistors that speed up the reset transition [143].

Almost the same circuit is presented by the same team in [143] and [144]. The proposed circuit is fabricated in a 0.35 µm SiGe BiCMOS technology with bipolar transistors with unity gain frequency up to 40 GHz. Fig. 1.21 (a) shows the block diagram of the circuit. Here the quenching is done by the MOSFET M<sub>P,S</sub> and the avalanche is sensed through a SiGe comparator with 1 GHz bandwidth. The comparator drives the quenching MOSFET and a delay block (HOLD-OFF LOGIC) to control the hold-off and reset time. Fig. 1.21 (b) shows the schematic of the comparator composed by four stages: the first stage is a CMOS level shifter to set the level of the input signals in the common mode range of the following stage. The second stage is a bipolar differential amplifier like the third stage. The last stage is an inverter which generates digital signal to drive the logic parts of the circuit and the quenching MOSFET. According to the simulation results, the avalanche is detected in about 800 ps and quenched in less than 1 ns, see Fig. 1.22. However, in

Fig. 1.23 (a) Schematic of the Variable Load Quenching Circuit (VLQC) presented in [145]. (b) timing diagram of the VLQC. (c) Cathode current of the circuit in (a) during an avalanche.

the measurements, the quenching time is reported to be less than 2 ns. The circuit area is  $100~\mu m \times 370~\mu m$ , and the power consumption is around 30 mW at 1 Mc/s.

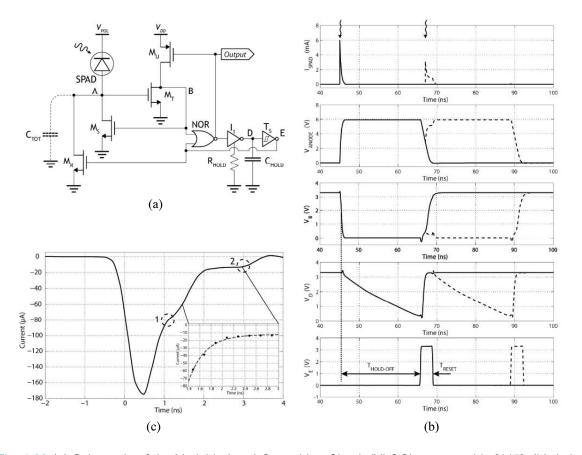

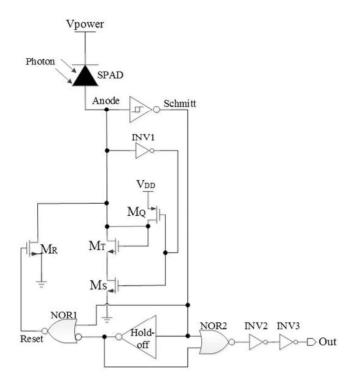

In [145] a novel quenching circuit is introduced named Variable Load Quenching Circuit (VLQC). Fig. 1.23 (a) shows the schematic of the proposed VLQC. In this circuit the anode is connected to a transistor (MS) which functions as a PQ resistor, as well as an AQ element. Ms has the minimum size to reduce the parasitic capacitance at anode, and more importantly, to realize a high impedance path for PQ. In the standby mode this MOSFET is on and in the triode region. Thus, at the onset of an avalanche, the anode voltage rises due to the PQ implemented by Ms. This voltage increase is sensed through MT and falls down the voltage at B which is the gate of MS. Therefore, the resistivity of MS is increased until it completely turns off and finally quenches the SPAD. After a hold-off time set by RHOLD and CHOLD, the Schmitt trigger TS turns on the reset MOSFET MR and starts the reset phase. Anode voltage falls (node "A") and MT turns off. NOR

Fig. 1.24 Improved version of VLQC with an AQ switch (MP) presented in [147].

gate forces MU to increase the voltage at node "B" up to VDD. Now the Schmitt trigger turns MR off to end the reset phase and make the SPAD ready for a new event. The timing diagram of the circuit is presented in Fig. 1.23 (b).

The proposed circuit is fabricated in a 0.35  $\mu$ m CMOS technology and occupies an area of 28  $\mu$ m  $\times$  24  $\mu$ m. The maximum count rate can reach 50 Mc/s and the current consumption is 83  $\mu$ A from V<sub>DD</sub>. The total quenching time is about 3 ns, of which the first 1 ns is the AQ duration, see Fig. 1.23 (c). Unfortunately, no comparison between the proposed VLQC and a PQ circuit has been presented to evaluate the efficiency of VLQC in avalanche current and afterpulsing reduction.

Even though, a higher quenching resistor results in a faster quenching, and the avalanche is quenched through a positive feedback loop between  $M_T$  and  $M_S$ , however, calling VLQC an AQ circuit cannot be completely true, since, same as in PQ circuit, this is finally the high impedance path that quenches the SPAD.

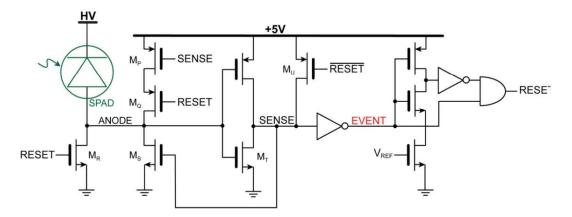

Two developed versions of the same circuit as [145] are presented in [146] and [147]. Fig. 1.24 presents the AQAR circuit presented in [147] by the same team as in [145]. The base of the circuit is the VLQC which is already presented. Here, the MOSFET M<sub>P</sub> is added to assist the quenching process and realize the AQ switch. Also, M<sub>T</sub> is used in the inverter composition. The hold-off time is set by V<sub>REF</sub> which controls the current of a current starved inverter. When an avalanche starts, the anode voltage rises thanks to the M<sub>S</sub> which is in the ohmic region and implements the PQ resistor. The voltage rise is sensed by the inverter which includes M<sub>T</sub>. Therefore, the voltage at node "SENSE" increases and turns M<sub>P</sub> on. Now the real AQ process starts till completely quenches

the SPAD. Meanwhile, the EVENT signal rises and after a delay set by V<sub>REF</sub>, turns on the reset transistor M<sub>R</sub> and M<sub>U</sub>, and turns off M<sub>Q</sub>. The reset phase starts, however, there is no control over the reset time. As soon as the anode voltage passes the threshold of the first inverter realized by M<sub>T</sub>, before reaching the ground, the RESET signal falls and turns the reset MOSFET M<sub>R</sub> off. Thus, the reset phase ends while the SPAD is not fully reset. The maximum reset time is equal to the propagation delays of the inverters and the AND gate. An uncomplete reset makes the SPAD operate in a lower excess bias voltage and thus increases jitter and lowers PDP. Unfortunately, no timing diagram or a simulated waveform is presented by the authors to evaluate the reset functionality of the circuit. The authors have claimed that the quenching time is about 100 ps for 5 V of Vex. However, no evidence, neither a simulation result nor a measured waveform is presented. The circuit is fabricated in a 160 nm BiCMOS DMOS (BCD) technology, and its area is  $37 \times 35 \,\mu\text{m}^2$ . The used transistors are thick oxide MOSFETs. The dead time is around 930 ps which can result in a maximum count rate of more than 1 Gc/s. An extremely low APP of 0.14 % is reported. However, no comparison is made between the AQ circuit and pure PQ mode of operation to see how much of this low APP is due to the AQ circuit contribution in the quenching process, and how much is related to the low intrinsic noise of the SPAD.

Fig. 1.25 shows the AQAR circuit presented in [146]. The circuit is very similar to the previous circuit: MOSFETs  $M_S$  and  $M_R$  have the same functionality as in the previous circuit.  $M_T$  is a diode connected MOSFETs which increases the impedance of  $M_S$  for a faster PQ and  $M_Q$  realizes the AQ switch. The quenching is done through positive feedback between INV1,  $M_S$ , and  $M_Q$ . The reset has a separate path which is controlled by a Schmitt trigger, thus better control over the reset time is achieved. The circuit is fabricated in 0.18  $\mu$ m CMOS technology with an area of 306  $\mu$ m<sup>2</sup>. The quenching time is 700 ps (simulation results) and the maximum count rate is 200 Mc/s. At 4 ns hold-off time 0.75 % APP is reported. Here also no comparison between the AQ circuit performance and the PQ mode is made which remains the effectiveness of the proposed AQAR in afterpulsing reduction ambiguous.

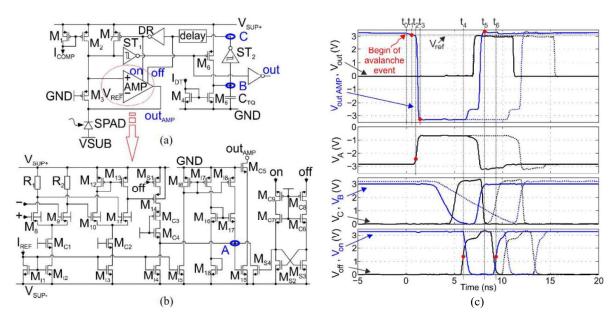

In [113] and [148]–[150] an almost same team has presented the same quenching strategy with slight changes at circuit level. Fig. 1.26 (a) shows the circuit presented in [113]. The main part of the circuit is a fast comparator ("AMP") which quenches the SPAD in a positive feedback loop.

Fig. 1.25 Schematic of the proposed quenching circuit in [146].

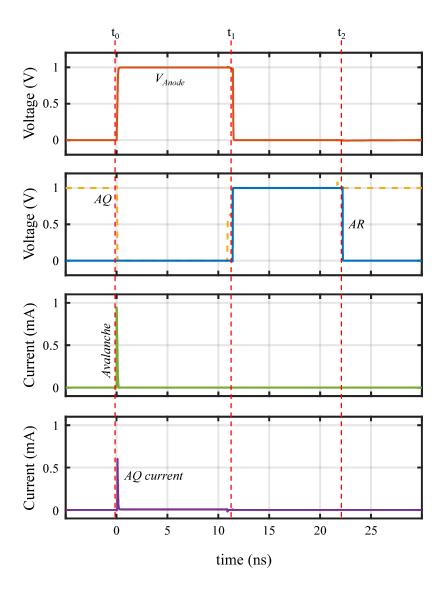

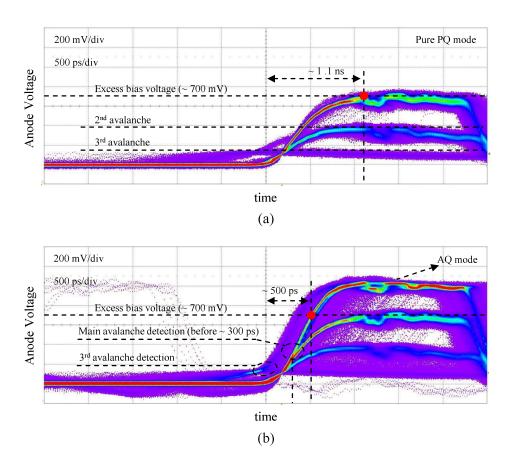

Fig. 1.26 (c) shows the timing diagram of the circuit. In the quiescent mode, the cathode voltage is almost equal to  $V_{SUP^+}$  (3.3 V), neglecting the voltage drop over  $M_2$  and  $M_3$ . The output of the Schmitt trigger  $ST_1$  is high, thus  $M_6$  has charged  $C_{TQ}$  (node "B"). The output of the second Schmitt trigger  $ST_2$  falls (node "C"), which turns on "AMP" to detect an avalanche. When an avalanche occurs ( $t_0$ ), PQ through  $M_3$  and  $M_2$  starts and decreases the cathode voltage and so the non-inverting input of the comparator. The voltage at this input reaches the reference voltage of the comparator  $V_{REF}$  at  $t_1$ . From  $t_1$  to  $t_2$  it takes the comparator to start the AQ phase and finally at  $t_3$  the quenching phase is finished by lowering the cathode voltage down to  $V_{SUP}$ . Now the output of  $ST_1$  rises and turns off  $M_6$ . Thus,  $C_{TQ}$  is discharged through  $M_5$ . Node "B" falls, and node "C" rises. After a certain delay, the comparator turns off and  $M_7$  turns on ( $t_4$ ). Now the reset phase starts until the fully recharge of the SPAD at  $t_5$ . By reaching to the threshold of  $ST_1$ , at  $t_6$  once again the comparator is ready to detect an avalanche.

The comparator is a 4-stage amplifier, see Fig. 1.26 (b). Two differential pairs ( $M_8$ - $M_{13}$ ) followed by a PMOS common source stage ( $M_{14}$ ). The Last stage is a cascode stage realized by  $M_{15}$  and  $M_{C5}$ .  $M_{I1}$ - $M_{I8}$  are biasing and pre-biasing current sources.  $M_{C1}$ - $M_{C9}$  are cascode transistors.

Fig. 1.26 (a) Proposed AQAR circuit in [113]. (b) Schematic of the AMP comparator used in (a). (c) timing diagram of the AQAR circuit.

The last stage ( $M_{15}$ ) is pre-biased  $M_{16}$  and  $M_{17}$  to have a faster response.  $M_{S2}$  and  $M_{S3}$  form a latch that controls  $M_{S4}$ , which along with  $M_{S1}$ , partially turn off the amplifier. However, the two first stages and the pre-biasing current mirrors still consume current. It results in 4.8 mW of power consumption in the idle mode and 10.03 mW at 100 Mc/s.

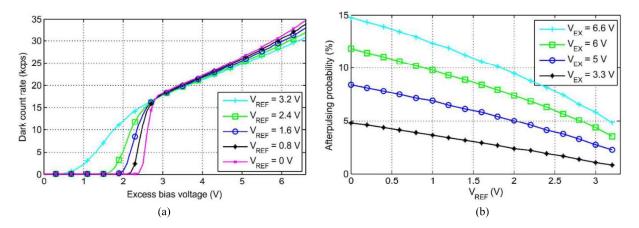

The circuit is fabricated in a 0.35  $\mu m$  CMOS technology and occupies an area of  $130 \times 134 \ \mu m^2$ . With  $V_{ex} = 6.6 \ V$ , in the fastest and most sensitive case ( $V_{REF} = 3.2 \ V$  and so a threshold of 100 mV for the comparator), the total quenching time is 1.04 ns (simulation results). Fig 1.27 (a) presents the DCR versus excess bias voltage of the used SPAD in this work, measured by the proposed AQAR circuit at different  $V_{REF}$ . A higher  $V_{REF}$  means a higher detection sensitivity and a lower threshold for the comparator. It shows that a less sensitive circuit (low  $V_{REF}$ ) cannot detect avalanches with lower  $V_{ex}$ , while the same SPAD shows a higher DCR value with a more sensitive circuit (higher  $V_{REF}$ ). This result is an important proof of the underestimation of the SPAD noise in the measurement with a low sensitivity avalanche detection circuit. In other words, the measured noise of a SPAD can strongly depend on the sensitivity of the avalanche detection circuit. Fig. 1.27 (b) shows the APP at different excess bias voltages for different sensitivity levels. At 6.6 V of  $V_{ex}$ , in the highest sensitivity ( $V_{REF} = 3.2 \ V$ ) the APP is 4.8 %, and in the lowest sensitivity ( $V_{REF} = 0 \ V$ ) this value is 14.7 %. It means around 67 % relative improvement in the APP.

Fig. 1.27 (a) DCR versus excess bias voltage at different sensitivity level. (b) APP versus sensitivity level at different excess bias voltage. Dead time is 9.5 ns [113].

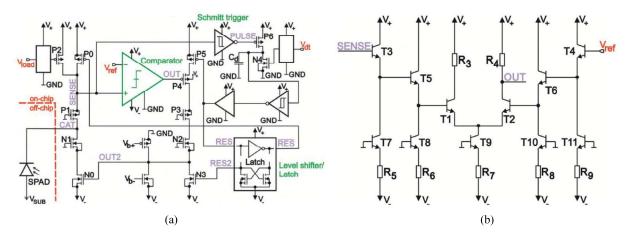

In [150] the same circuit is redesigned by employing bipolar transistors. Fig. 1.28 (a) shows the AQAR circuit diagram. It is similar to the circuit in Fig. 1.26 (a). The first two stages of the "AMP" in the previous circuit are shown by "Comparator" in the schematic. The third stage is single ended common source amplifier realized by  $P_4$ , and the last stage which acts as a quenching switch is implemented by  $N_0$ . The "comparator" is realized by bipolar transistors to speed up the quenching process. Fig. 1.28 (b) shows the bipolar comparator schematic: two bipolar level shifters placed in series at each input of a bipolar differential pair. In comparison with the CMOS version of the circuit in [113], the power consumption is increased by a factor of 4. At 40 Mc/s the bipolar AQAR circuit consumes 58 mW (simulation results). The circuit is fabricated in 3.3 V/ 0.35  $\mu$ m BiCMOS technology and its area is twice the area of the CMOS version. At a  $V_{REF} = 3$  V the active

Fig. 1.28 (a) Schematic of the AQAR circuit presented in [150]. (b) Schematic of the bipolar comparator with level shifters.

Fig. 1.29 Cathode voltage variations during an avalanche at different excess bias voltages for CMOS and bipolar comparators [150].

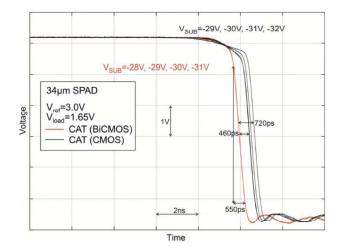

quenching phase starts sooner than the CMOS version, from 460 ps to 720 ps depends on the excess bias voltage. A higher  $V_{ex}$  results in a shorter reaction time of the comparator. However, the AQ phase slope is the same for both bipolar and CMOS versions (550 ps fall time at the cathode voltage). The total quenching time is slightly higher than 2ns. Fig. 1.29 shows the cathode voltage variations for bipolar and CMOS AQAR circuits at different  $V_{ex}$  and  $V_{REF} = 3$  V.

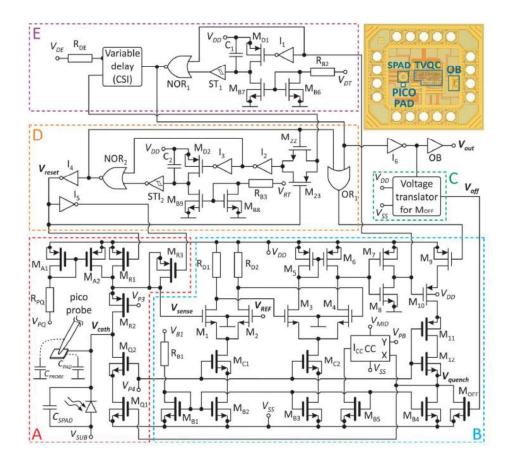

In [148] the same circuit as in [113] is presented with the modifications in the timing control circuits. Fig. 1.30 shows the schematic of the proposed AQAR circuit, named triple voltage quenching circuit. The reason for this naming is 9.9 V of  $V_{ex}$  that the pixel can tolerate which is 3 times of the technology voltage headroom. To achieve this ability, many high voltage (5 V) MOSFETs (drawn in bold) are used in a cascode structure that increases the circuit area. The proposed circuit is marked by five parts from A to E. Part A is the quenching and reset switches ( $M_{Q1}$  and  $M_{R1}$ ) with their cascode MOSFETs. Part B is almost the same comparator as in [113]. The third stage of the comparator is realized by an inverter instead of a common source stage. In [113] the active quenching switch is included in the four stages of the used comparator as the fourth stage, however, in this circuit a separate quenching switch is driven by the 4-stage comparator. A current conveyor, controlled by  $V_{PB}$  ("CC"), pre-biases the quenching switch  $M_{Q1}$  for a faster quenching. Since the quenching switch must be a very wide transistor, the pre-biasing can increase its leakage current. Part C turns off the quenching switch by pulling its gate voltage to the ground. Part D generates the reset signal and controls the reset time through  $V_{RT}$  and by driving the reset

Fig. 1.30 Schematic of the proposed triple voltage AQAR circuit in [148] with micrograph of the chip.

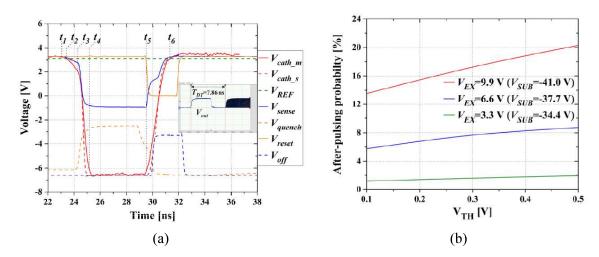

Fig. 1.31 (a) Operation principal of the presented circuit in [148] at its highest sensitivity ( $V_{th}$  = 100 mV).  $V_{cath\_m}$  and  $V_{cath\_s}$  are measured and simulated cathode voltages. (b) APP versus sensitivity level at different excess bias voltage. Dead time is 8 ns.

switch M<sub>R1</sub>. Part E controls the hold-off time through V<sub>DT</sub> by triggering the reset process through

a tunable delay ("CSI") controlled by  $V_{DE}$ . It also turns off the last stage of the comparator ( $M_{10}$ ) by switching off  $M_9$  for the reset phase. The circuit is fabricated in a 0.35  $\mu$ m CMOS technology and occupies an area of  $236 \times 108 \ \mu\text{m}^2$ . The power consumption of the circuit with 8 ns dead time is 14.4 mW. The measured quenching time is claimed to be 1.7 ns, however due to the measured waveform presented in Fig. 1.31 (a), this time is almost 2 ns ( $t_1 - t_4$ ). Fig. 1.31 (b) shows the APP versus the sensitivity ( $V_{TH} = 3.3 \ V - V_{REF}$ ) of the comparator controlled by  $V_{REF}$ . In the best case, at  $V_{ex} = 9.9 \ V$  and 8 ns dead time, the highest sensitivity ( $V_{TH} = 100 \ mV$ ) results in 13.4 % APP, while at the lower sensitivity of  $V_{TH} = 500 \ mV$ , the APP is 20.3 %. It means about 34 % relative improvement in APP.

# 1.4. Thesis Objective

At the beginning of this chapter, we discussed the noise sources of the SPAD and the solutions to reduce these noises. It is already explained how avalanche charge reduction can reduce the afterpulsing effect as a main noise source. However, as it is addressed previously, there are severe trade-offs between fill factor, PDE, maximum photons count rates, and the afterpulsing effect. A very few solutions to mitigate these trade-offs are costly, such as the 3D stacked IC technology. Besides, according to the state-of-the-art, the AQ circuits still suffer from several drawbacks in afterpulsing reduction, such as low sensitivity in the avalanche detection, long quenching time, high static power consumption, and large circuit area.

In this thesis, we aim to introduce the innovative AQAR circuits, which are sensitive enough to strongly reduce the afterpulsing effect, while consuming low power and small areas to mitigate the aforementioned trade-offs. Also, we investigate the monolithic 3D integration of SPAD with AQ circuits for the first time, which can remove the dependence of the fill factor and thus PDE on the area of the SPAD front end circuitry in a Back-Side Illumination (BSI) configuration. This can be an ultimate solution for the trade-offs between PDE, noise, and the count rate. To better understand this concept, we explain this technology in the following.

#### 1.4.1. Monolithic 3D SPAD Pixel in FD-SOI CMOS Technology

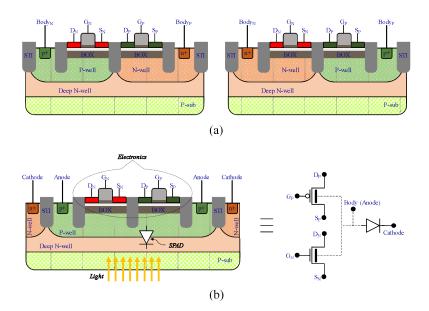

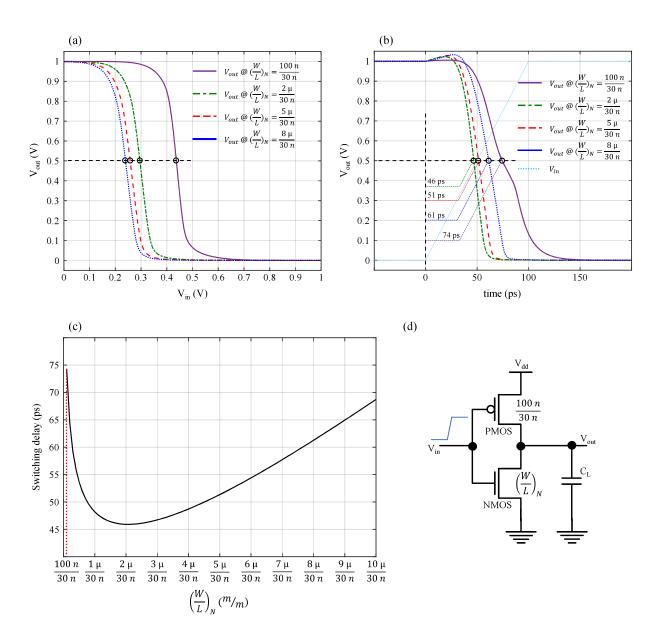

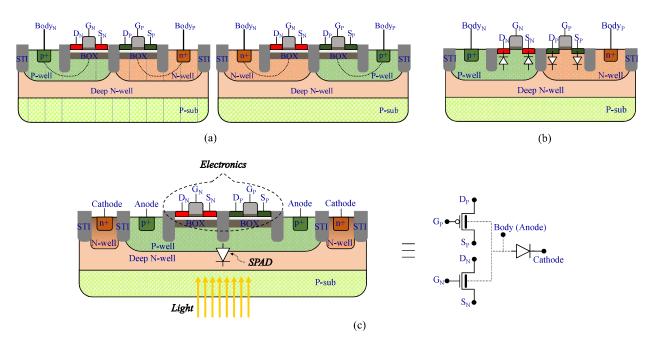

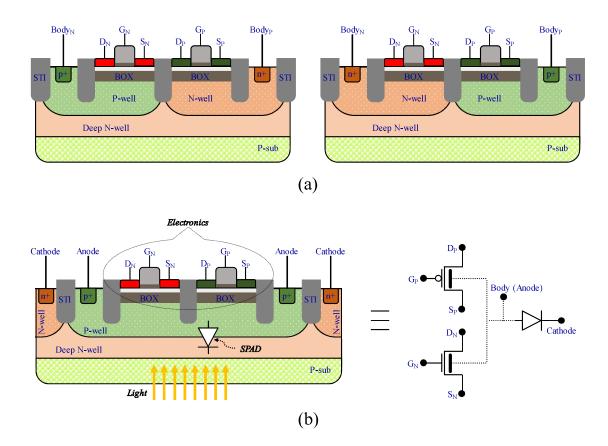

The technology that is used in this thesis is a 28 nm Fully Depleted Silicon On Insulator (FD-SOI) CMOS technology. In Fig. 1.32 (a) a cross section of this FD-SOI technology is presented. The transistors are fabricated over a 25 nm thick Buried Oxide layer (BOX). This structure yields

Fig. 1.32 Symbolic cross section of: (a) FD-SOI CMOS technology, regular well (left) and flip well (right), (b) mix of the flip well and the regular well in the FD-SOI CMOS technology and forming of the SPAD at the junction of P-well and the deep N-well which results in the intrinsic 3D pixel (left) and its schematic counterpart (right). The pixel is expected to be backside illuminated.

electrical isolation for the active devices over the BOX from their corresponding wells. In this technology, two different MOSFET families exist; Flipped well (FW) and Regular Well (RW). In FW MOSFETs, NMOS are fabricated in an N-well and PMOS in a P-well, while in the RW family it is the opposite [151]–[153]. It is possible to mix these two MOSFET categories and have both NMOS and PMOS in the same well as it is shown in Fig. 1.32 (b). One can note that the junction between P-well and deep N-well can be used to form a SPAD.

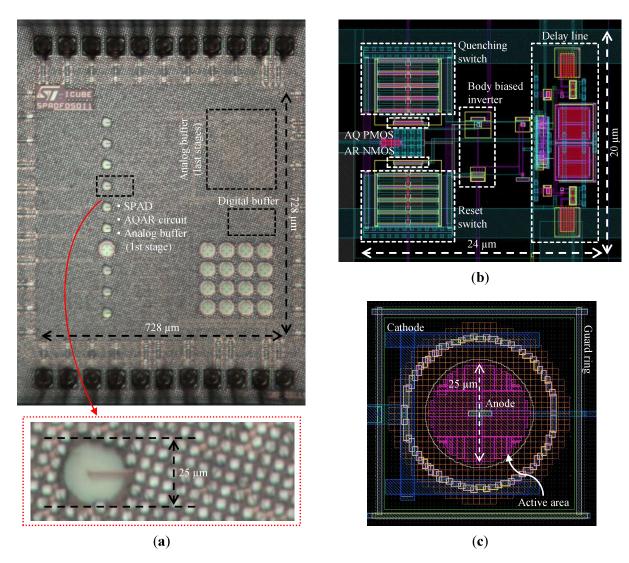

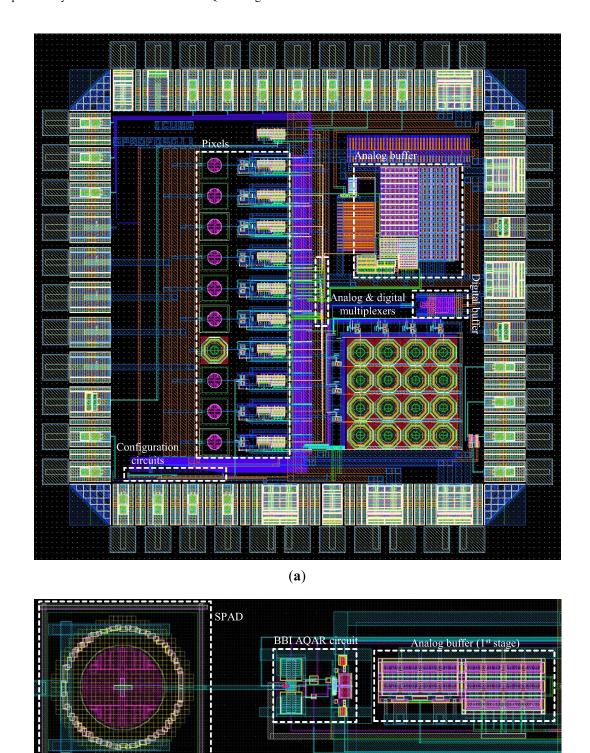

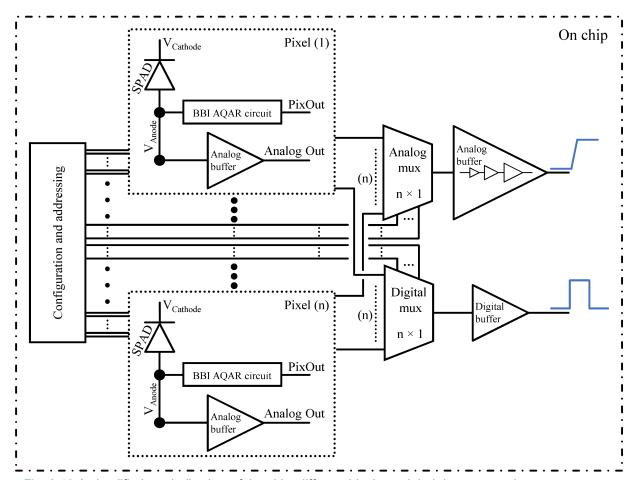

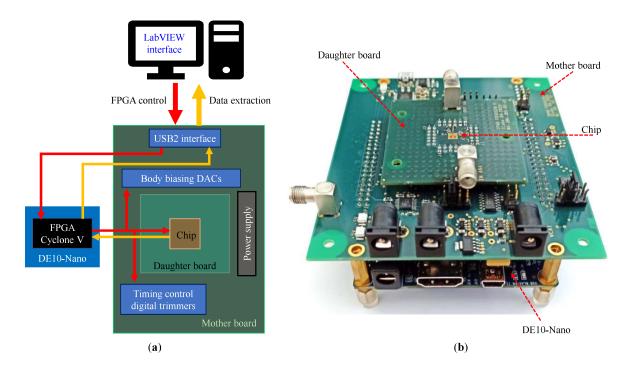

Based on this, the first SPAD in a 28 nm FD-SOI CMOS technology is presented in [154]. The SPAD is implemented in a commercial FD-SOI CMOS technology without any process modifications i.e., with the default standard junction doping profile. The SPAD is laid out without any Design Rule Checking (DRC) violations. It has a quasi-octagonal shape to respect DRC, and its diameter is 25 µm. These all have resulted in a promising albeit non-optimized SPAD. However, for the purposes of this paper, a non-optimized SPAD can demonstrate more clearly the effectiveness of the proposed AQAR circuits in the afterpulsing reduction. In this regard, this SPAD is chosen to evaluate the proposed AQAR circuit. Nonetheless, the optimizations to improve the FD-SOI SPAD parameters are presented in [155]–[159].

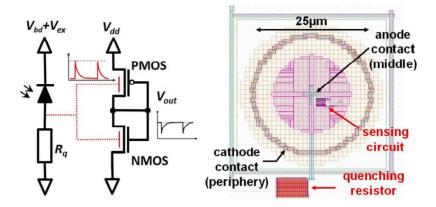

Fig. 1.33 (right) Schematic of a voltage divider as a sensing circuit for SPAD-FDSOI (the dashed red line represents the body-biasing, i.e., the indirect coupling between the SPAD anode and transistors). (left) layout view of the SPAD-FDSOI with the divider on top of the SPAD and also the quenching resistor.

Thanks to the insulating BOX layer, electronic devices can be placed over the SPAD while being electrically isolated from it. This forms a monolithic 3D SPAD pixel, see Fig. 1.32 (b). Despite the conventional 3D pixels, this pixel occupies one die and reduces the fabrication costs. The first attempts to realize this pixel are presented in [160], [161], in which two MOSFETs, realizing a divider as an avalanche detection circuit, are placed over the SPAD, see Fig. 1.33. Yet, the structure has more potential: integrating an ultra-fast AQAR circuit in the pixel, alongside a Back-Side Illumination (BSI), can drastically reduce or remove the dependence of the FF and PDE on the electronics.

Although a die thinning is mandatory to allow the BSI in the monolithic 3D SPAD pixel, the manufacturing process cost of the used FD-SOI CMOS technology is 10% less than the classical bulk CMOS technology [151].

In this thesis the focus is on the design and characterization of the first ultra-fast AQAR circuits which are compatible with the monolithic 3D SPAD pixel as well as conventional SPAD pixels.

# Chapter 2 Body Biased Inverter Based Active Quenching Active Reset Circuit

# 2.1. Introduction

It has already been discussed that to decrease the afterpulsing effect without degrading the maximum count rate, an AQ circuit is mandatory. Such a circuit is composed of two main parts: avalanche detection or sensing circuit, and quenching circuit. The quenching circuit can be as simple as a switch or a current source that discharges the SPAD junction capacitance. The effectiveness of an AQ circuit in the afterpulsing reduction is determined by these two parts. A sensitive detection circuit can signal early stages of an avalanche to the quenching part, and the quenching part should start its contribution in the quenching process as soon as possible, before the SPAD itself completely quenches the avalanche. The quenching part should provide a portion of the required charge carriers that discharge the SPAD capacitance. The greater the contribution of the AQ circuit, the less the flow of avalanche current in the SCR, and thus less afterpulsing effect. Also, the sooner the AQ part starts to intervene, the more it can contribute. The time that the AQ part starts its auxiliary role is determined by the detection circuit. Therefore, it is crucially important to design a very fast and sensitive avalanche detection circuit to have an effective AQ circuit.

Another important consideration in designing an AQAR circuit is its area. The circuit added area increases the pixel area while the light sensitive area (active area) remains constant. This reduces the pixel fill factor and thus its PDE. Therefore, an AQAR circuit should be compact and area efficient.

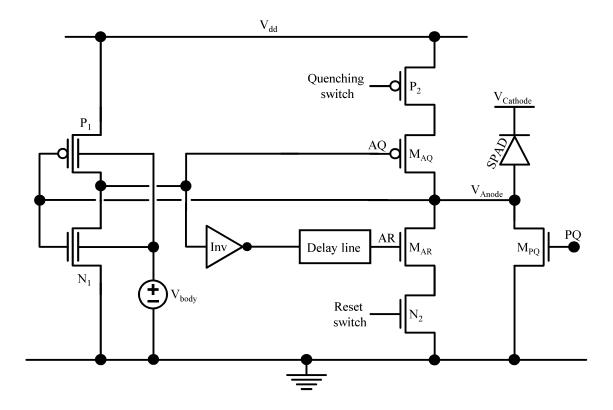

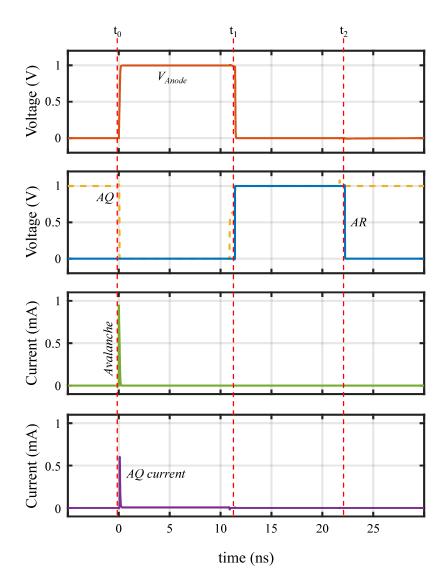

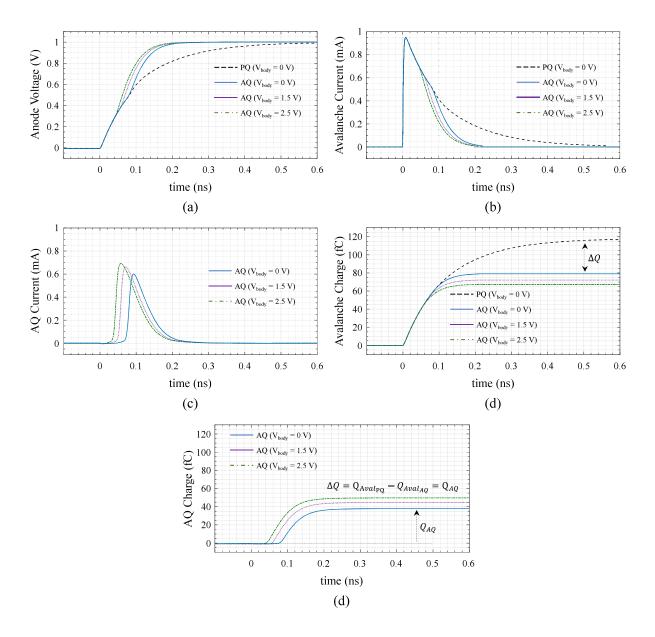

In this chapter we introduce a new AQAR circuit in a 28 nm FD-SOI CMOS technology. Utilizing specific characteristics of FD-SOI CMOS technology, a very fast detection circuit is proposed, which detects the avalanche quickly and reduces the afterpulsing effect effectively. The circuit can be very compact and does not add considerably parasitic to SPAD.

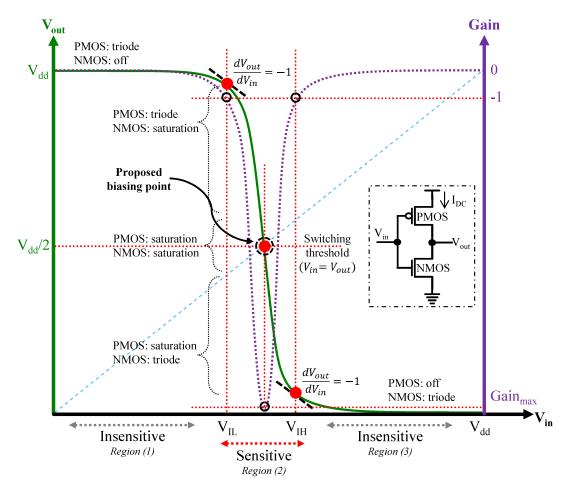

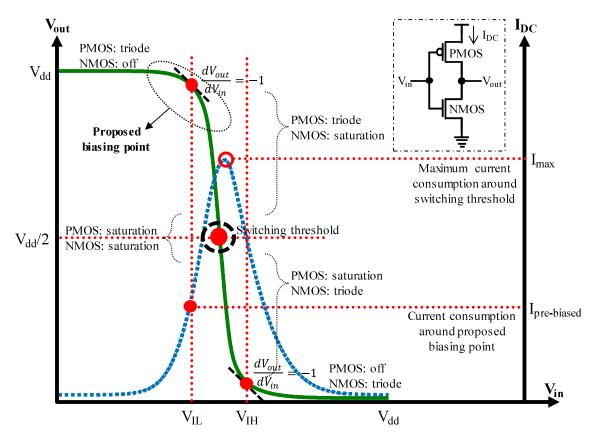

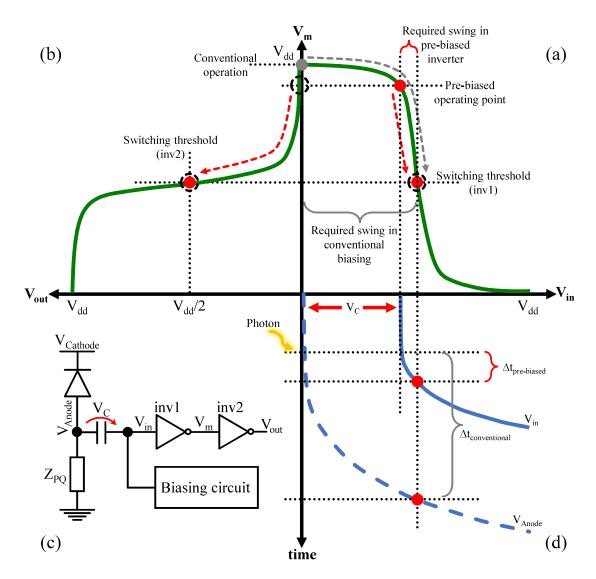

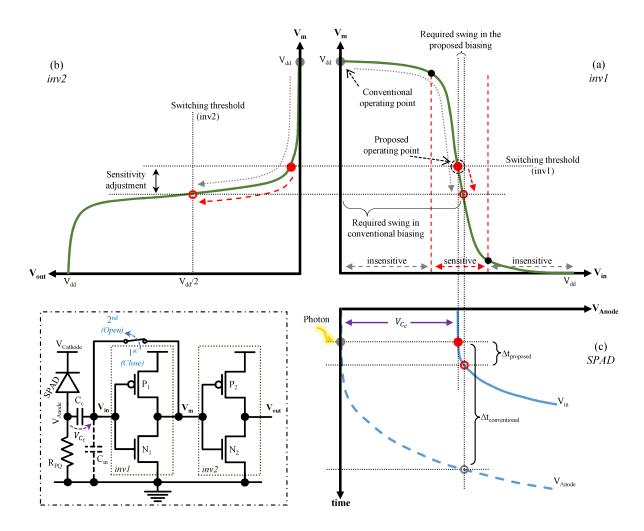

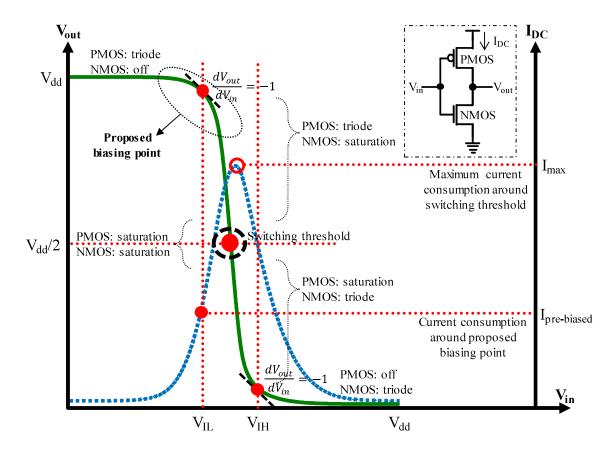

## 2.2. Low Threshold Inverter as an Avalanche Detector

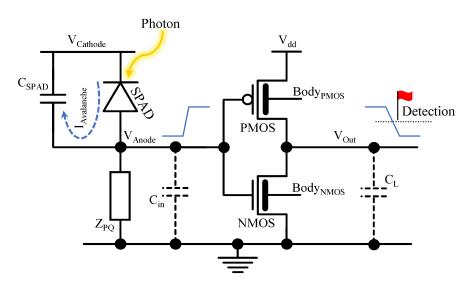

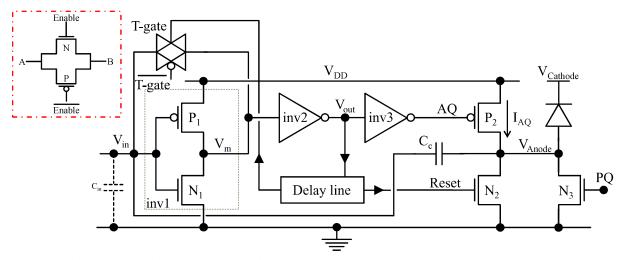

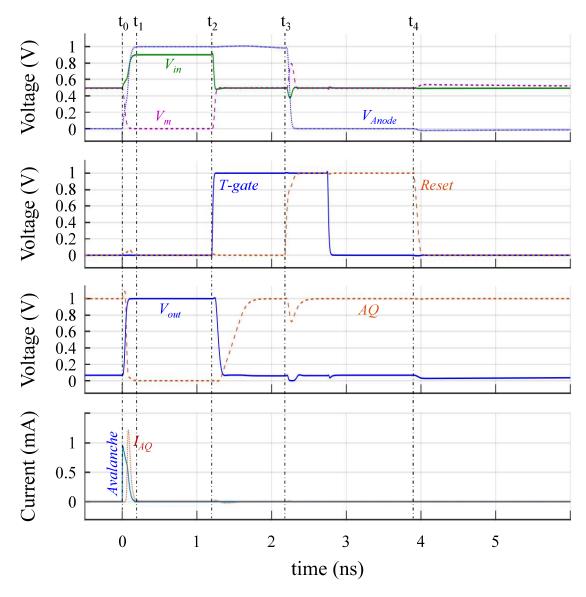

Despite their fame in digital electronics, inverters are also used in analog circuits, especially in more scaled technology nodes. They are used as comparators, output buffer stages, and even analog amplifiers [162]. Thanks to their compact area and low power consumption, inverters are also used for the avalanche detection as it is reported in the literature [163], [164]. Fig 2.1 shows the schematic of a SPAD pixel utilizing an inverter as a detection circuit. When an avalanche occurs, the anode voltage rises, till it reaches switching threshold of the inverter. At this point inverter output changes and flags the photon arrival. The time that it takes to detect an avalanche through an inverter can be characterized by the high to low propagation delay  $(t_{pHL})$  or switching delay.

Fig. 2.1 Schematic of a SPAD pixel featuring an inverter as the avalanche sensing circuit.

The propagation delay is the interval between the time that input signal of an inverter is at its 50 % and the time that its output signal reaches to its 50% [165]. Even though, in the avalanche detection case, 50 % of input signal swing translates to a slow detection, yet the propagation delay can give an insight to the efficiency of an inverter in detecting an avalanche. Based on this definition, for the very fast transient signals where the rise and fall time of the input signal are within the range of those of the output signal, finding a precise equation for the propagation delay is not trivial. However, it is possible to form a proportional relationship between the switching delay and circuit parameters:

$$t_{pHL} \propto \frac{C_L \cdot V_{dd}}{(\frac{W}{L})_n \cdot (V_{dd} - V_{th_n})}$$

(2.1)

where  $C_L$  is all the parasitic capacitances at the output node of the inverter,  $V_{dd}$  is the power supply,  $(\frac{W}{L})_n$  is the width over length ratio of NMOS, and  $V_{th_n}$  is the threshold voltage of NMOS. The shorter this time, the sooner the avalanche is detected, and thus the more efficient is the AQ circuit. According to this relationship, to have a short delay, it is required to properly size the inverter while keeping  $C_L$  minimum.

## 2.2.1. Delay Reduction Through Inverter Sizing

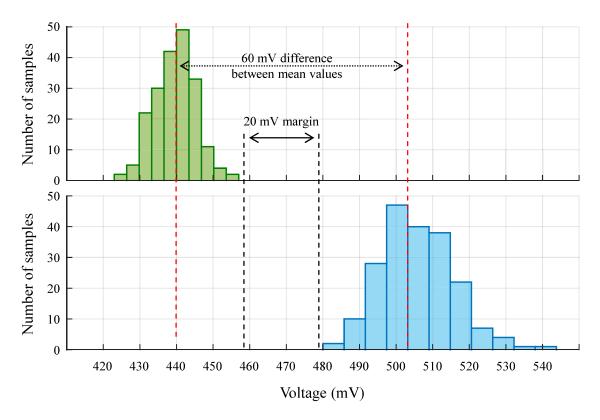

Relationship 2.1 shows that a wider NMOS can result in a shorter delay. Increasing NMOS width, while keeping the one of PMOS constants, decreases the switching threshold of the inverter by the following equation:

$$V_{M} = \frac{V_{dd} - |V_{th_{P}}| + V_{th_{N}} \cdot \sqrt{\frac{\mu_{N} \cdot (\frac{W}{L})_{N}}{\mu_{P} \cdot (\frac{W}{L})_{P}}}}{1 + \sqrt{\frac{\mu_{N} \cdot (\frac{W}{L})_{N}}{\mu_{P} \cdot (\frac{W}{L})_{P}}}}$$

(2.2)

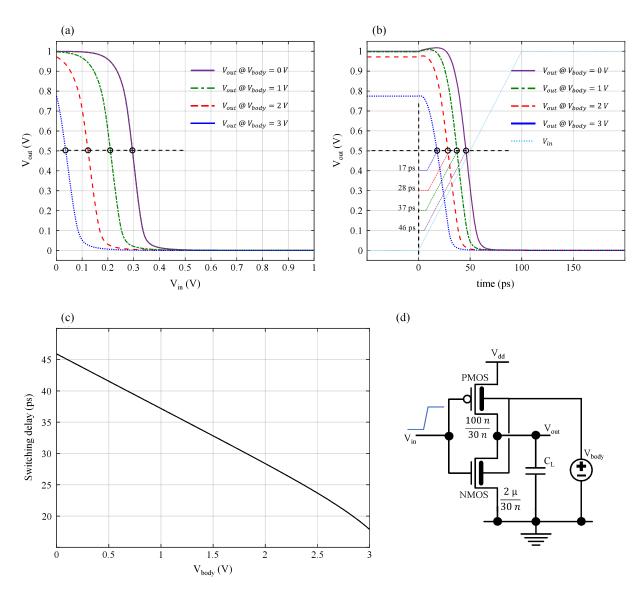

where  $V_{th_N}$  and  $V_{th_P}$  are the threshold voltages of NMOS and PMOS.  $\mu_N$  and  $\mu_P$  are the mobilities of electrons and holes, respectively, and  $(\frac{W}{L})_N$  and  $(\frac{W}{L})_P$  are the width to length ratios of NMOS and PMOS. This is shown in Fig. 2.2 (a), where Voltage Transfer Characteristic (VTC) of an inverter is pushed back by increasing NMOS width. Therefore, at a lower input voltage (V<sub>in</sub>) the output state changes, which in the time domain means faster detection.

However, increasing the size of its transistor also increases the load capacitance (C<sub>L</sub>) of the inverter. Regarding relationship 2.1, this increases the delay. Thus, there is an optimum width that results in the minimum delay and increasing the width further than that, increases the delay. This is observable in Fig. 2.2 (b), where a 100 ps ramp is applied to an inverter for different NMOS widths. Here we define another delay indicator that is more intuitive in the avalanche detection

Fig. 2.2 Reducing switching delay of an inverter through sizing of its transistors. (a) VTC of the inverter at different NMOS sizes. (b) Transient response of the inverter for a 100 ps input ramp at different NMOS sizes. (c) Switching delay of the inverter versus NMOS size. (d) schematic of the tested inverter.

case. The switching delay is defined as the time interval between the beginning of the rise of the input signal and the time that the output signal reaches the switching threshold of a (following) standard inverter gate. Fig. 2.2 (c) shows the switching delay variations versus  $(\frac{W}{L})_N$ . A maximum 40 % (~ 30 ps) delay reduction is obtained by 20 times increasing the size of NMOS.

Besides the parasitic capacitances, the area consumption is another limiting factor in this method. The added area for the purpose of delay reduction, increases the inactive pixel area and therefore degrades the fill factor and PDE, and increases the pitch.

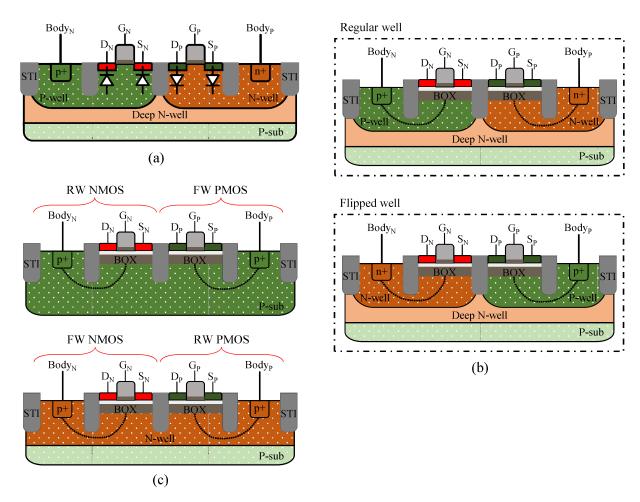

## 2.2.2. Delay Reduction Through Body Biasing

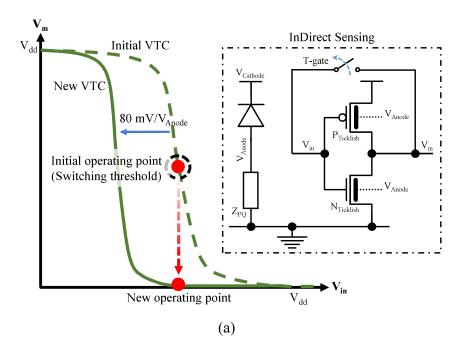

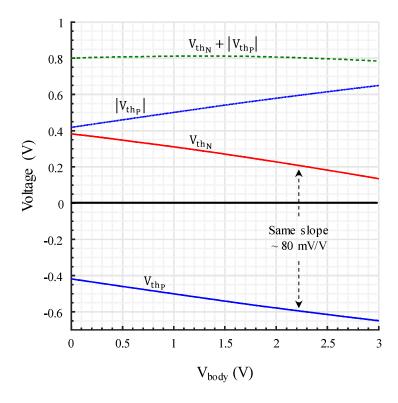

Another solution to reduce the delay, regarding the relationship 2.1, is decreasing the NMOS threshold voltage  $V_{th_N}$ . Equation 2.2 also propose to decrease  $V_{th_N}$  and increase the PMOS threshold voltage  $V_{th_P}$  to lower the switching threshold of the inverter. However, in standard CMOS technology, this is not a very practical solution. As it is shown in Fig. 2.3 (a), in the bulk CMOS technology, there are parasitic diodes between P-well and N-well, and between each well and Drain and Source of inside wells. These diodes limit the maximum applicable body voltage to their forward bias voltage, which is typically about 0.7 V.

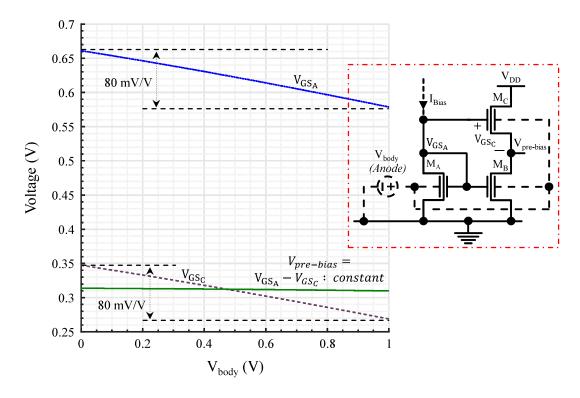

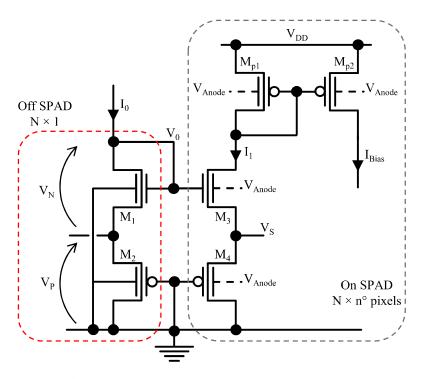

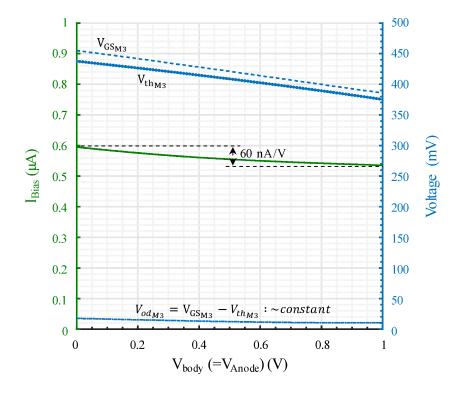

In the FD-SOI CMOS technology an insulator (BOX layer) separates the MOSFETS and other devices from their corresponding wells and creates a capacitive link between the body and the channel of MOSFETs, see Fig. 2.3 (b). This structure yields two advantageous features: 1) the parasitic diodes cannot be formed anymore between Drain/Source and wells 2) the BOX layer is in fact a second gate or a back gate. These features allow to apply body biasing to the MOSFETs up to the maximum tolerable voltage of the buried oxide (BOX). In the used FD-SOI CMOS technology, the thickness of the back oxide is three times of the front gate oxide. Therefore, the back gate can tolerate three times of the technology voltage headroom (3×1 V). Despite the square root relationship in the bulk CMOS technology, the threshold voltage depends almost linearly on the body voltage in the FD-SOI CMOS technology [166]. This will be further discussed in chapter 4. The rate of this dependence, called body biasing factor (α), is about 80 mV/V, i.e., 1 V body voltage variation results in 80 mV threshold voltage variation. Therefore, a maximum threshold voltage modulation of about 240 mV is achievable in this technology.

To reduce the switching threshold of the inverter a positive voltage should be applied to the bodies of NMOS and PMOS. This requires a well separation through a deep N-well layer. Consequently, the circuit area is increased which is not desirable for a quenching circuit. However, in the FD-SOI CMOS technology there is a solution for this problem. As it is depicted in

Fig. 2.3 (a) Symbolic cross section of a standard CMOS technology featuring a deep N-well layer. (b) Symbolic cross sections of the used FD-SOI CMOS technology. Top: regular well family, bottom: flipped well family. (c) Combining the two families of FD-SOI technology in a same well. Top: regular well NMOS and flipped well PMOS in a shared P-well, bottom: flipped well NMOS and regular well PMOS in a shared N-well.

Fig. 2.3 (b), there are two families of MOSFET in this technology: Regular Well (RW) and Flipped Well (FW). In the flipped well family, NMOS is implemented in an N-well and PMOS in a P-well, while in the regular well this is the reverse. By respecting the electrostatic considerations, and since the two transistors require the same body voltage, it is possible to mix the two families and have both NMOS and PMOS in the same well. As a result, two structures are possible that are shown in Fig. 2.3 (c): RW NMOS and FW PMOS in a P-well or RW PMOS and FW NMOS in an N-well. Both implementations are valid and yield a small circuit area. Even though in our design a conventional well separation is used for measurement purposes.

Fig. 2.4 Reducing switching delay of an inverter through body biasing of its transistors. (a) VTC of the inverter at different body voltages. (b) Transient response of the inverter for a 100 ps input ramp at different body voltages. (c) Switching delay of the inverter versus body voltage of NMOS and PMOS. (d) schematic of the tested inverter.

Fig. 2.4 shows the simulation setup and results for body biasing of an inverter. By applying the same voltage to NMOS and PMOS and sweep it from 0 V to 3 V, the switching threshold of the inverter is reduced by about 240 mV, as can be seen in Fig. 2.4 (a). In this simulation the optimum sizing which has been obtained in the previous section is used. Applying a 100 ps ramp to the inverter (driving the same  $C_L$  as in the sizing simulations), while sweeping the body voltage is presented in Fig. 2.4 (b). Despite the sizing method, here at each sweep step the switching delay is reduced. The full range of variation for switching delay versus body voltage is presented in

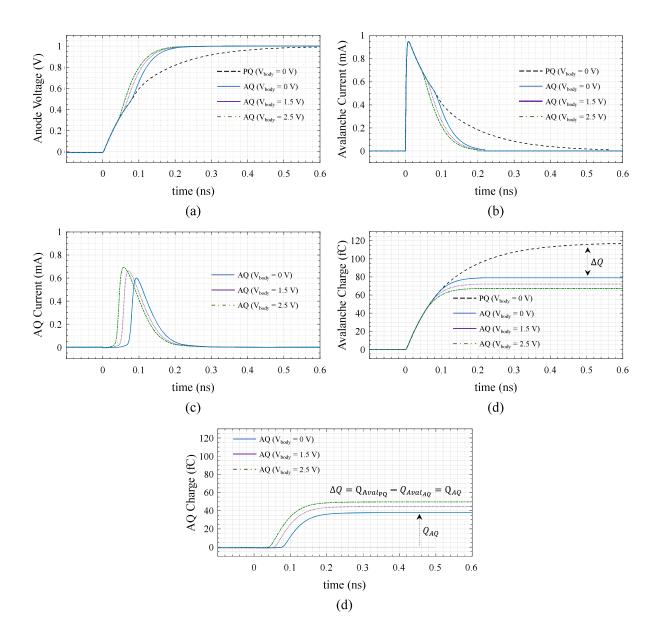

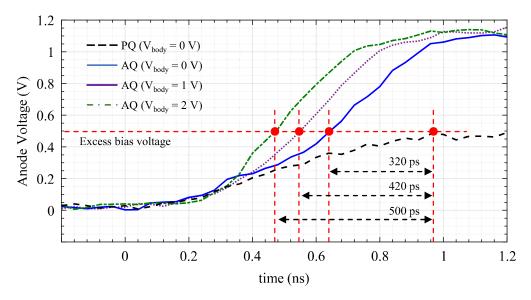

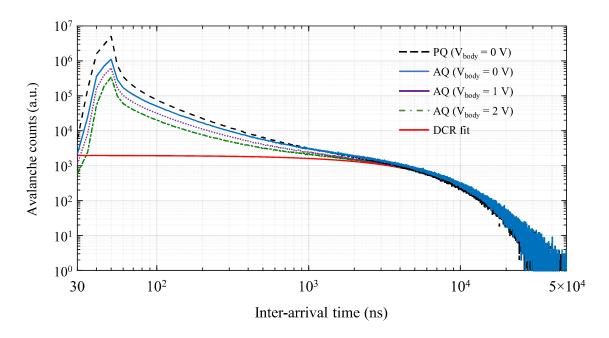

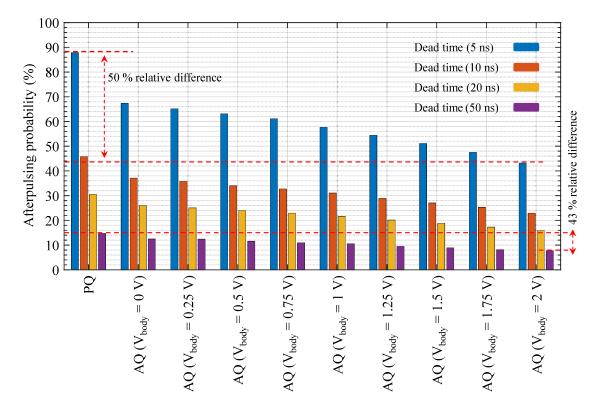

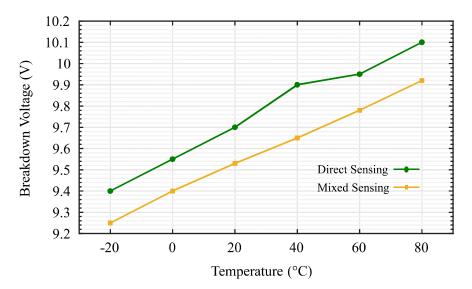

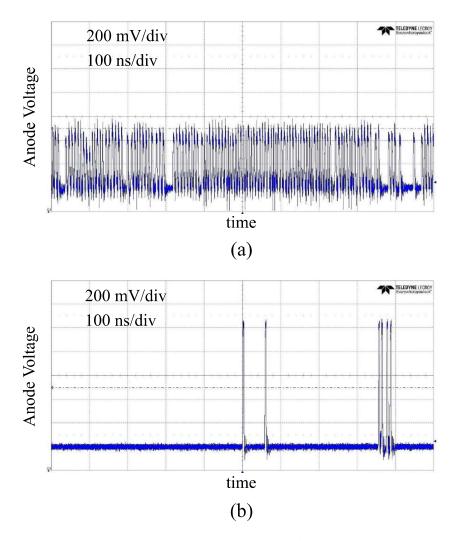

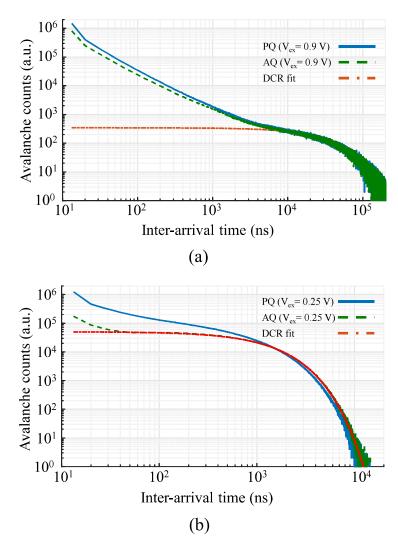

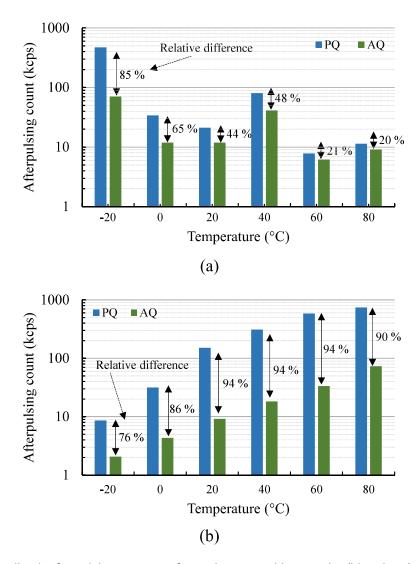

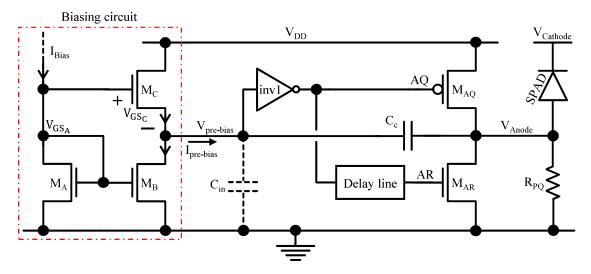

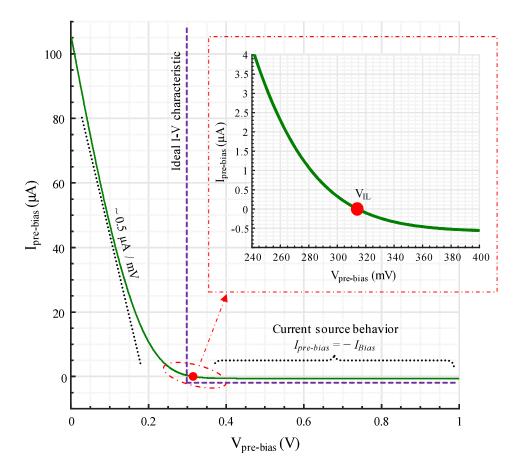

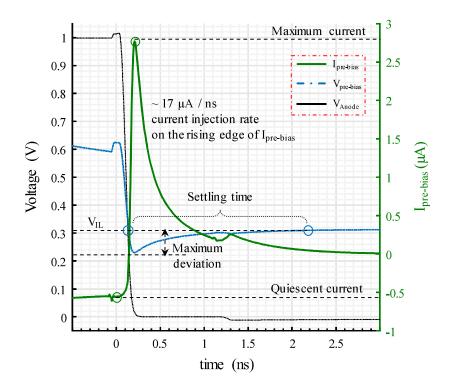

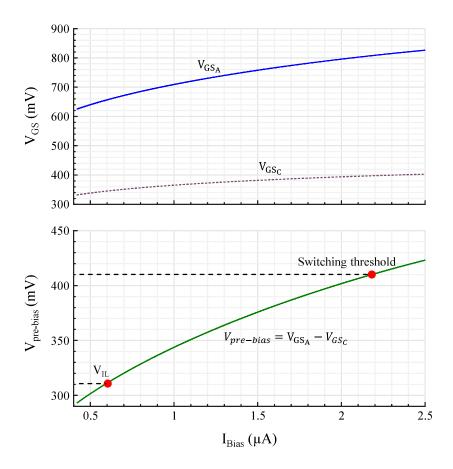

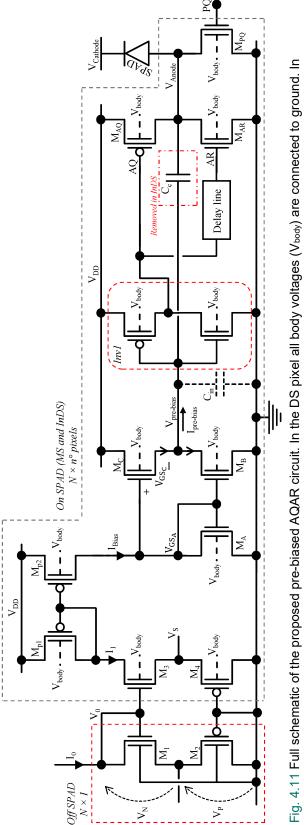

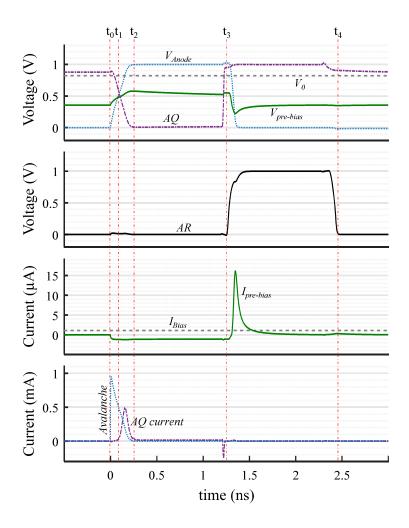

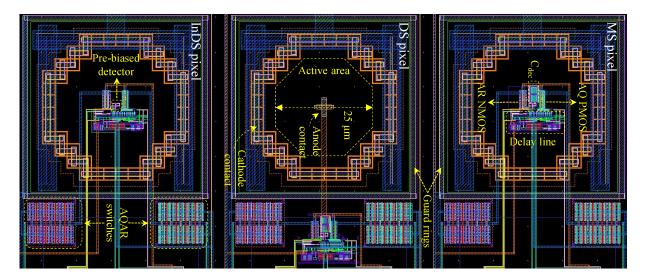

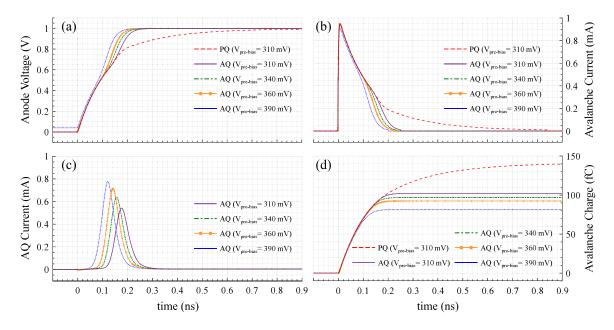

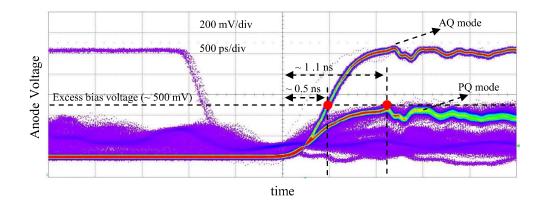

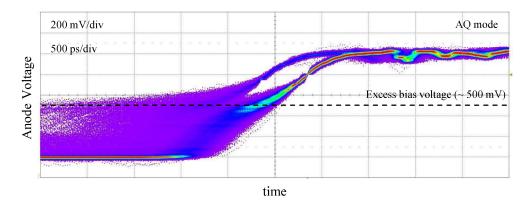

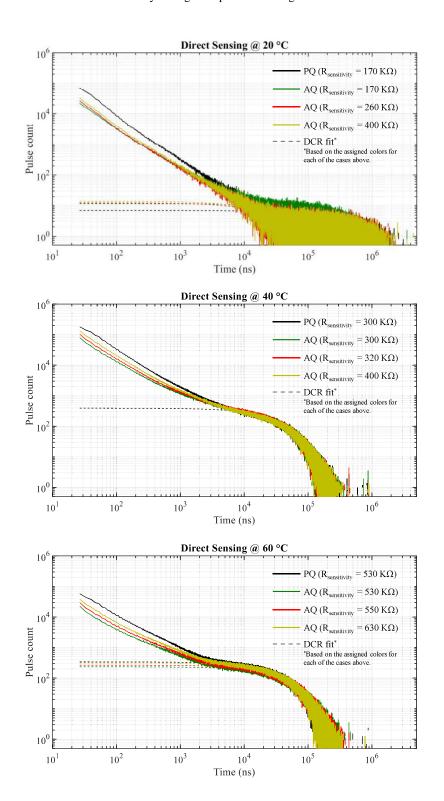

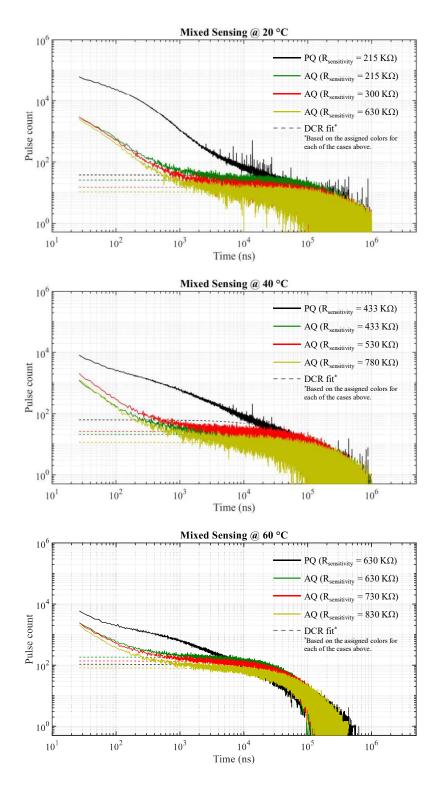

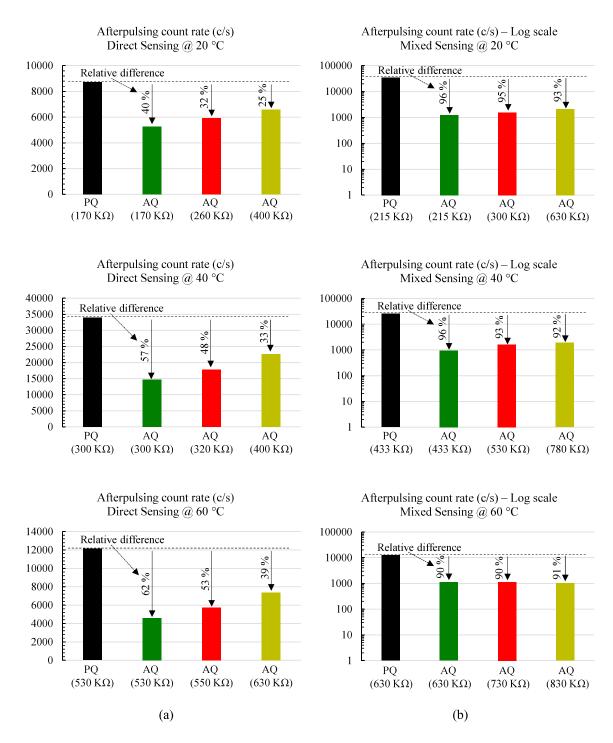

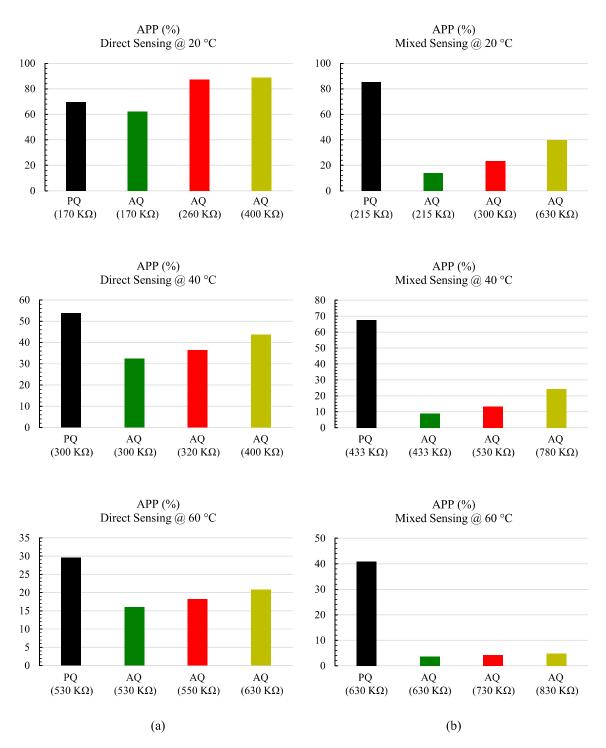

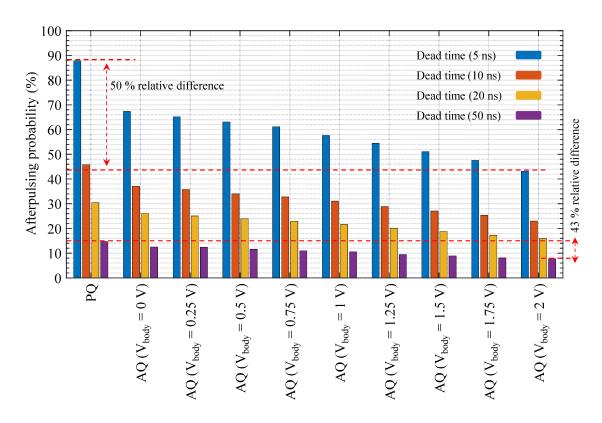

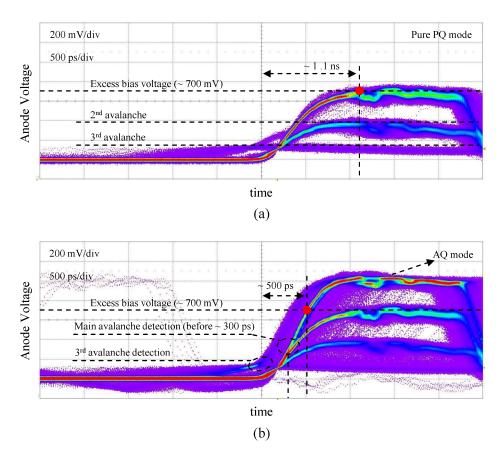

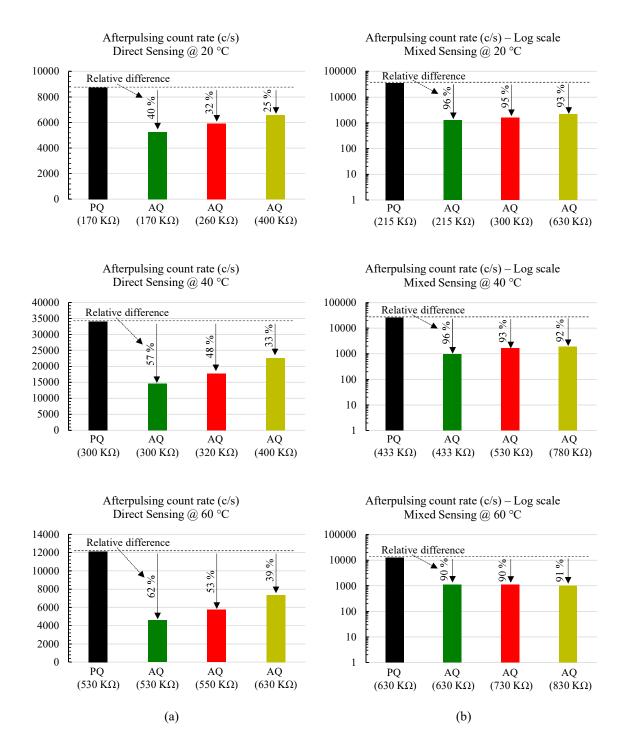

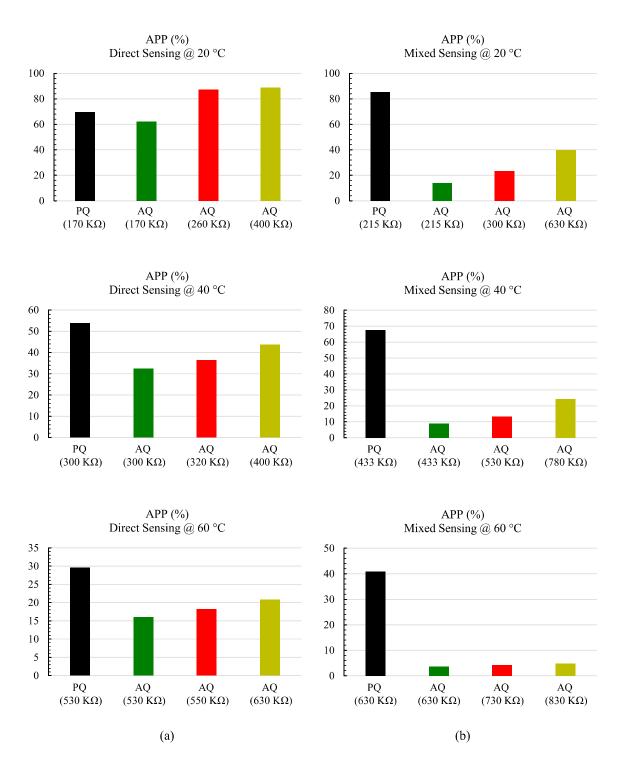

Fig. 2.4 (c). There is an almost linear relationship between the switching delay and body voltage. This is due to the linear relationship between the body voltage and the threshold voltage in the FD-SOI CMOS technology. A maximum 66% ( $\sim 30$  ps) switching delay reduction is obtained by 3 V increase in the body voltage.