## Contribution to wake-up radio design for sensor network applications

Ruochen Ding

#### ▶ To cite this version:

Ruochen Ding. Contribution to wake-up radio design for sensor network applications. Electromagnetism. Université Côte d'Azur, 2023. English. NNT: 2023COAZ4081. tel-04402733

#### HAL Id: tel-04402733 https://theses.hal.science/tel-04402733

Submitted on 18 Jan2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ÉCOLE DOCTORALE

CIENCES ET ECHNOLOGIES DE INFORMATION ET DE A COMMUNICATION

# THÈSE DE DOCTORAT

Contribution à la conception et à la modélisation de wake-up radio pour réseaux de capteurs

## **Ruochen DING**

Laboratoire d'Electronique, Antennes et Télécommunications (LEAT)

Présentée en vue de l'obtention du grade de docteur en Electronique d'Université Côte d'Azur Dirigée par : William TATINIAN Soutenue le : 1 décembre 2023

#### Devant le jury, composé de :

Olivier BERDER, Professeur, Université de Rennes Alexandru TAKACS, MCF-HDR, Université Toulouse Tân-Phu VUONG, Professeur, Université Grenoble Alpes Alain PEGATOQUET, Professeur, Université Côte d'Azur Robert STARAJ, Professeur, Université Côte d'Azur William TATINIAN, MCF-HDR, Université Côte d'Azur

# Contribution à la conception et à la modélisation de wake-up radio pour réseaux de capteurs

#### Jury :

#### Président du jury :

• Olivier BERDER, Professeur des universités, Université de Rennes

#### **Rapporteurs :**

- Alexandru TAKACS, Maitre de conférences HDR, Université Toulouse

- Tân-Phu VUONG, Professeur des universités, Université Grenoble Alpes

#### Examinateurs :

- Alain PEGATOQUET, Professeur des universités, Université Côte d'Azur

- Robert STARAJ, Professeur des universités, Université Côte d'Azur

- William TATINIAN, Maitre de conférences HDR, Université Côte d'Azur

## Résumé

L'utilisation de la wake-up radio (WUR) dans les applications de réseaux de capteurs est en croissance constante car elle permet de réduire considérablement la consommation d'énergie globale et d'augmenter la durée de vie de la batterie des capteurs. Le rôle de la WUR est de permettre à la radio principale de rester en mode veille le plus longtemps possible si aucune action n'est requise.

Cependant, la plupart des publications discutent de la théorie, de la simulation SPICE, ou des mesures de WUR, pour une seule topologie de WUR à la fois. Dans cette thèse, nous comparons plusieurs topologies. Ce travail décrit en détail le processus de simulation des circuits, la modélisation théorique, la conception de PCB, les mesures et l'optimisation du prototype. De plus, cette étude a réalisé des simulations de différents scénarios dans OMNeT++ pour examiner le comportement des nœuds dotés d'un WUR semi-actif sous différents modèles et frameworks. Nous avons proposé une méthode de modélisation de la couche physique pour considérer les performances de la WUR et son impact sur la transmission de données, complémentaire à la modélisation de la couche MAC.

Le Chapitre II a présenté une analyse et classification complète de l'état de l'art de la technologie de la wake-up radio. Nous avons résumé les principales caractéristiques du WUR sur la base de notre revue de la littérature, incluant type, technologie, sensibilité, consommation d'énergie, fréquence, modulation, latence, débit de données et adressage. L'analyse et les premiers résultats de simulation ont été fournis comme étude préliminaire pour un design adaptable à des cas particuliers, préparant l'implémentation et la modélisation de l'appareil.

Dans le Chapitre III, nous nous sommes concentrés sur la conception et la modélisation de la wake-up radio semi-active. Il peut y avoir des réveil manqués ou indésirés lors de la transmission, augmentant ainsi le temps de transmission et l'énergie moyenne par bit transmis. Pour tenir compte avec précision de ces effets, une modélisation exacte de la WUR est nécessaire. Nous avons détaillé le processus de simulation SPICE, le développement d'un modèle théorique ainsi que la conception et les mesures des prototypes pour la wake-up radio semi-active. Nous avons fourni une description complète de la wake-up radio, y compris ses parties analogiques et numériques.

Au Chapitre IV, nous nous sommes concentrés sur l'optimisation du système de wake-up radio semi-active Ce chapitre est divisé en trois parties, chacune abordant le processus d'optimisation sous différents angles. La première partie a comparé les performances de la wake-up radio semi-actif en utilisant deux approches d'intégration différentes: une fabrication hétérogène, combinant PCB et CMOS intégré ; et une intégration PCB plus classique. La seconde partie a détaillé le processus de conception pour notre PCB à 4 couches et un résumé des règles de conception que nous avons suivies. La dernière partie de ce chapitre présente le développement d'un prototype à partir d'un module Arduino équipée d'une WUR à 4 couches optimisée. Nous avons détaillé tout le processus, de la conception à la réalisation.

Au Chapitre V, nous nous sommes concentrés sur l'utilisation du simulateur de réseau comme un outil efficace pour les réseaux de capteurs, en particulier dans le contexte des réseaux de capteurs sans fil (WSN) caractérisés par un grand nombre de nœuds et des ressources limitées. Cette démarche nous permet de surmonter les contraintes matérielles et de refléter les mesures du monde réel, réduisant ainsi les coûts expérimentaux et améliorant l'efficacité du développement. Ce chapitre a montré la valeur de l'utilisation du simulateur de réseau dans l'évaluation de la WUR et offre une comparaison des différents modèles et cadres.

En résumé, notre travail a fourni une analyse au niveau système de l'utilisation des WURs dans les WSNs, apportant un soutien pour les recherches futures dans ce domaine.

#### Mots clés

Wake-up radio; Réseaux de capteurs sans fil; Modélisation de circuits analogiques et RF; Conception de CI; Simulation de réseaux de capteurs

#### Résumé vulgarisé

L'utilisation de la wake-up radio (WUR) dans les applications de réseaux de capteurs est en croissance constante car elle permet de réduire considérablement la consommation d'énergie globale et d'augmenter la durée de vie de la batterie des capteurs. Le rôle de la WUR est de permettre à la radio principale de rester en mode veille le plus longtemps possible si aucune action n'est requise. Cependant, la plupart des publications discutent de la théorie, de la simulation SPICE, ou des mesures de WUR, pour une seule topologie de WUR à la fois. Dans cette thèse, nous comparons plusieurs topologies. Ce travail décrit en détail le processus de simulation des circuits, la modélisation théorique, la conception de PCB, les mesures et l'optimisation du prototype. De plus, cette étude propose des simulations de différents scénarios dans OMNeT++ pour examiner le comportement des nœuds dotés d'un WUR semi-actif sous différents modèles et frameworks. Nous proposerons une méthode de modélisation de la couche physique pour considérer les performances de la WUR et son impact sur la transmission de données, complémentaire à la modélisation de la couche MAC. En conclusion, cette thèse apporte une contribution au développement de la conception de la radio de réveil pour les applications de réseau de capteurs, fournissant une analyse au niveau du système qui soutient la poursuite des recherches dans ce domaine.

### Abstract

The use of wake-up radio (WUR) in sensor network applications has been continuously growing, as it allows to significantly reduce the overall power consumption and increase the lifetime of sensors' battery. The role of the wake-up radio is to allow the main radio to remain in sleep mode as long as possible if no action is required.

However, most of the related work discusses the theory, SPICE simulation, or measurement of only one wake-up radio topology at a time. In this thesis, we comprehensively compare all methods. This work described in detail the whole process of WUR circuit simulation, theoretical modeling, PCB implementation, prototype testing and optimization. Furthermore, this study conducted simulations of different scenarios in OMNeT++ to investigate the behavior of nodes equipped with semi-active WUR under different models and frameworks. We proposed a physical layer modeling approach to consider the performance of the wake-up radio and its impact on data transmission, which is complementary to the MAC layer modeling.

Chapter II presented a comprehensive analysis and classification of the state-of-the-art for wake-up radio technology. We summarize the main characteristics of WUR based on our review of the literature, including type, technology, sensitivity, power consumption, frequency, modulation, latency, data rate, and addressability. And the analysis and initial simulation results were provided as a preliminary study for the design which can be easily adapted to the particular cases and prepared for the implementation and modeling of the device.

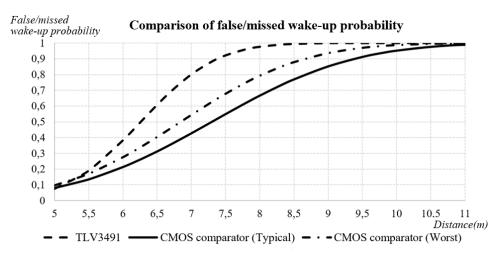

In Chapter III, we focused on the design and modeling of semi-active wake-up radio. There may be false wake-ups or missed wake-ups during the transmission, thus increasing the transmission time and the average energy per transmitted bit. To accurately account for these effects, an accurate modeling of the WUR is necessary. We gave the detailed process of SPICE simulation, development of a theoretical model, as well as the prototype design and measurement for a semi-active wake-up radio. we provided a comprehensive description of the wake-up radio, including its analog and digital parts.

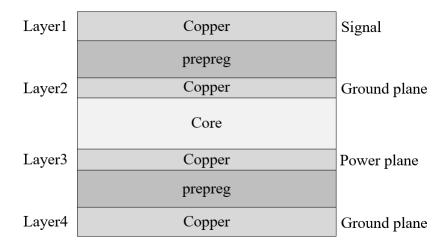

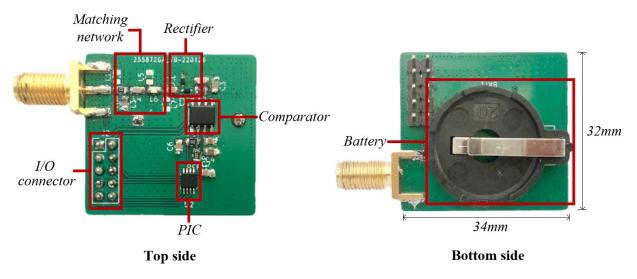

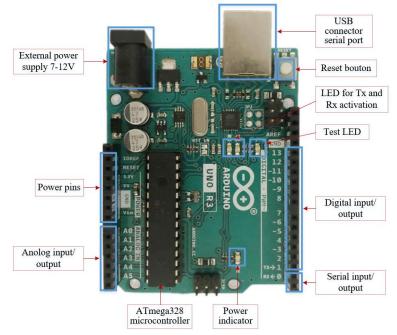

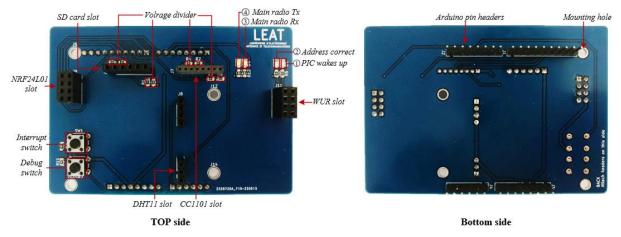

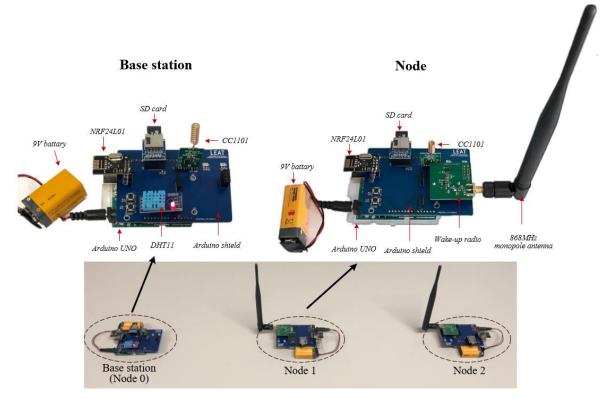

In chapter IV, we concentrated on the optimization of the semi-active wake-up radio system. This chapter is partitioned into three sections that each approach the optimization process from different perspectives. The first part compared the performances of the semi-active wake-up radio using two different integration approaches: a heterogeneous fabrication, combining PCB and integrated CMOS; and a more classical PCB integration. The second part provided the design process for our 4-layer PCB. and a summary of the design rules that we followed during this process. The final part of this chapter presents the development of a prototype of an Arduino

shield equipped with an optimized 4-layer WUR. And we detailed the entire process from shield design to realization.

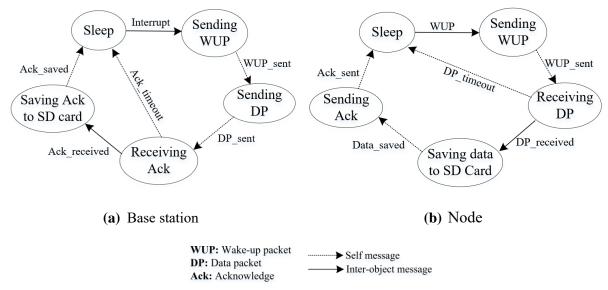

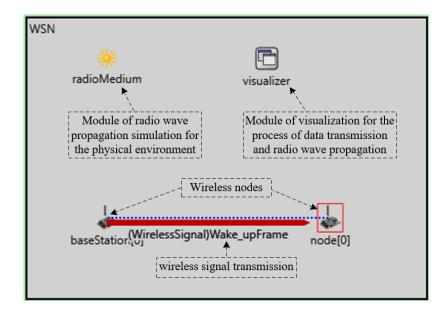

In chapter V, we focused on using network simulator as an effective tool in the sensor networks, particularly within the context of wireless sensor networks (WSNs) characterized by a great number of nodes and limited resources. This approach allows us to overcome material constraints and reflect real-world measurements, thus reducing experimental costs and improving development efficiency. This chapter highlights the value of using network simulator in WUR assessment and provides a comparison of different models and framework, providing a basis for future research on WUR in WSN.

In summary, our work provided a system-level analysis of the use of wake-up radios in wireless sensor networks, providing support for further research in this field.

#### Key words

Wake-up radio; Wireless sensor networks; Analog and RF circuit modeling; IC design; Sensor network simulation.

#### **Vulgarized abstract**

The use of wake-up radio (WUR) in sensor network applications has been continuously growing, as it allows to significantly reduce the overall power consumption and increase the lifetime of sensors' battery. The role of the wake-up radio is to allow the main radio to remain in sleep mode as long as possible if no action is required. However, most of related works discuss theory, SPICE simulation, or measurements, for only one WUR topology at a time. In this thesis, we compare several topologies. This work describes in detail the whole process of WUR circuit simulation, theoretical modeling, PCB implementation, prototype testing and optimization. Furthermore, this study conduct simulations of different scenarios in OMNeT++ to investigate the behavior of nodes equipped with semi-active WUR under different models and frameworks. We propose a physical layer modeling approach to consider the performance of the wake-up radio and its impact on data transmission, which is complementary to the MAC layer modeling. In summary, this thesis gives a contribution to the development of wake-up radio design for sensor network applications, providing a system-level analysis that supports further research in this field.

## **Table of contents**

| Résumé                                                                                  | 1     |

|-----------------------------------------------------------------------------------------|-------|

| Abstract                                                                                | 3     |

| Abbreviations                                                                           | 9     |

| Publications                                                                            | 10    |

| Chapter I: General introduction                                                         | 11    |

| I.1 Background                                                                          | 11    |

| I.2 Motivation and objective                                                            | 12    |

| I.3 Thesis work                                                                         | 12    |

| I.4 Reference                                                                           | 13    |

| Chapter II: State-of-the-art of wake-up radio and preliminary study of semi-active v    | vake- |

| up radio                                                                                |       |

| II.1 Introduction                                                                       | 15    |

| II.2 State-of-the-art of wake-up radio                                                  | 15    |

| II.2.2 Fully-passive wake-up radio                                                      |       |

| II.2.3 Fully-active wake-up radio                                                       |       |

| II.2.4 Semi-active wake-up radio                                                        | 25    |

| II.2.5 Choice of modulation and frequency                                               |       |

| II.3 Study of rectifier in semi-active wake-up radio                                    | 34    |

| II.3.1 Efficiency of rectifier                                                          | 34    |

| II.3.2 Key element of rectifier: Schottky diode                                         | 35    |

| II.3.3 Choice of Schottky diode                                                         | 35    |

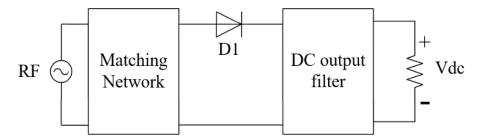

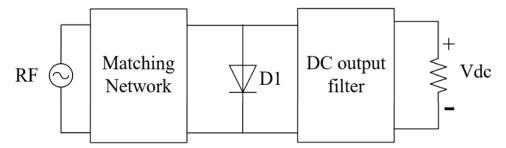

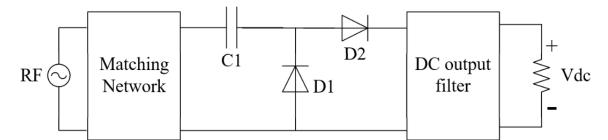

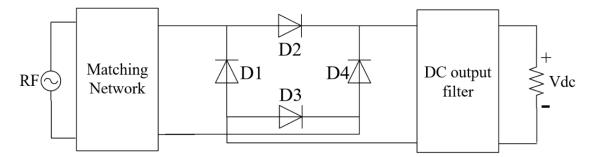

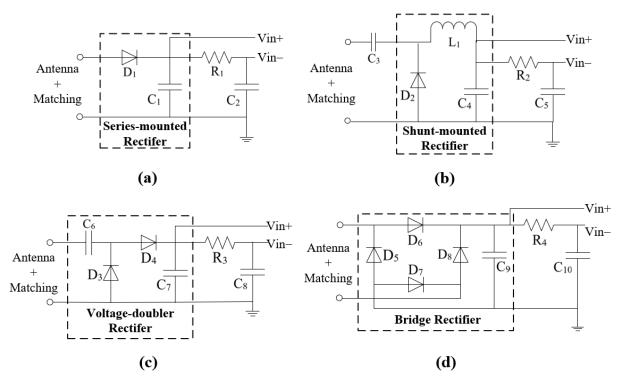

| II.3.4 Different topologies of rectifier                                                | 36    |

| II.3.5 Choice of topology of rectifier                                                  | 38    |

| II.4 Semi-active wake-up radio's analog part analysis                                   | 39    |

| II.4.2 Elements of the analog circuit                                                   | 39    |

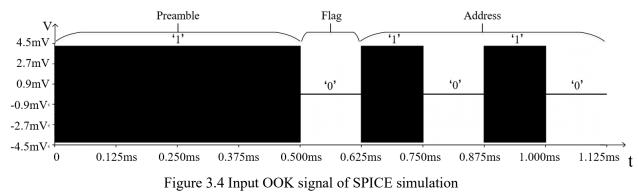

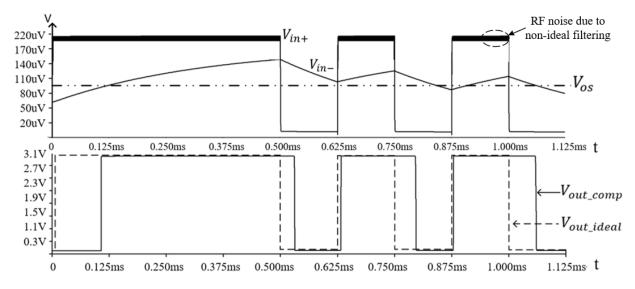

| II.4.3 Example of SPICE simulation result                                               | 41    |

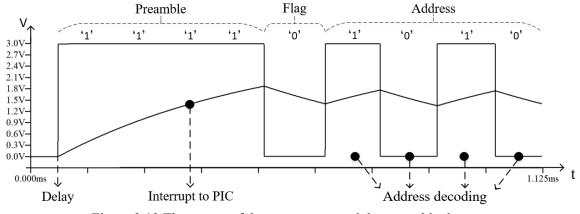

| II.5 Semi-active wake-up radio's digital part analysis                                  | 42    |

| II.5.1 Addressing mechanism                                                             | 42    |

| II.5.2 Programming of ultra-low-power microcontroller (ULP MCU)                         | 43    |

| II.7 Conclusion                                                                         | 44    |

| II.8 Reference                                                                          | 45    |

| Chapter III: Design and modeling of semi-active wake-up radio                           | 49    |

| III.1 Introduction                                                                      | 49    |

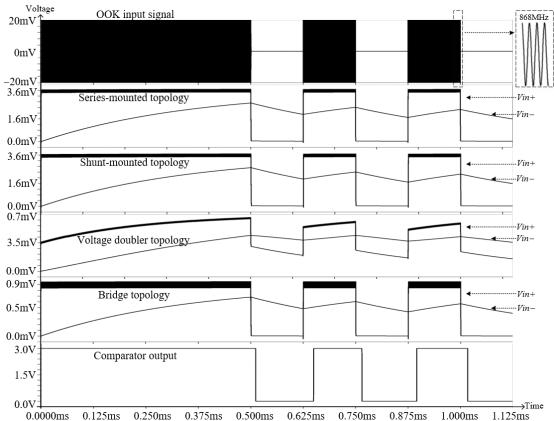

| III.2 SPICE simulations, experimental measurements, and performance comparison of semi- |       |

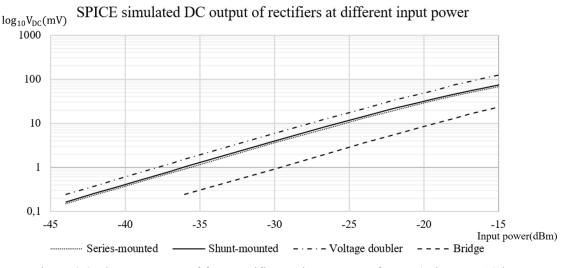

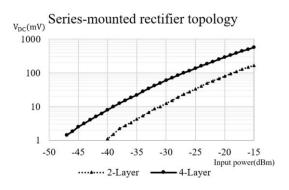

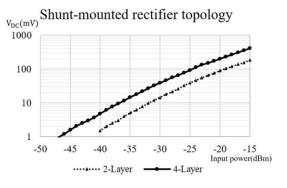

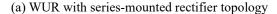

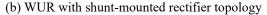

| wake-up radio with different rectifier topologies                                       | 51    |

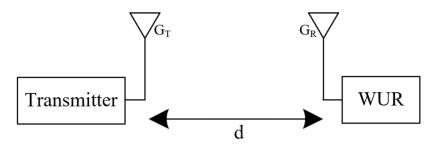

| III.3 Modeling of free space propagation                                                | 57    |

| III.4 Modeling of different topologies of rectifier                                     | 58    |

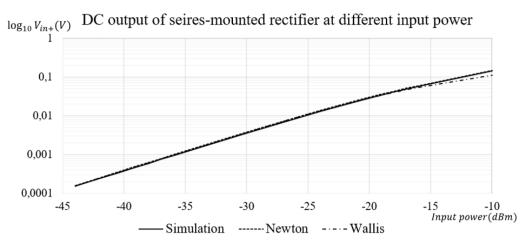

| III.4.1 Modeling of series-mounted topology                                             | 59    |

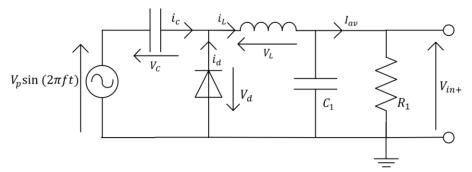

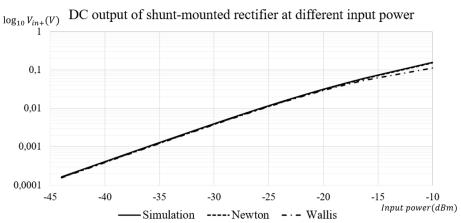

| III.4.2 Modeling of shunt-mounted topology                                              |       |

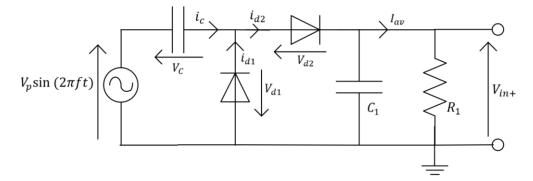

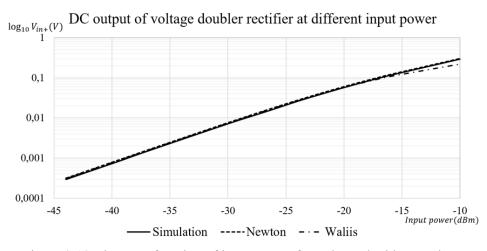

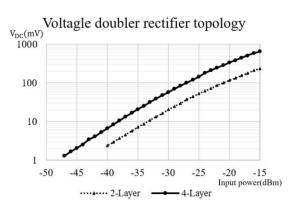

| III.4.3 Modeling of voltage-doubler topology                                            | 65    |

| III.5 Modeling of semi-active wake-up radio's analog part                               |       |

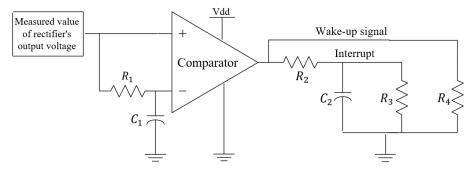

| III.5.1 Comparator                                                                      | 66    |

| III.5.2 Wake-up interrupt / preamble detector<br>III.6 Modeling of semi-active's digital part |           |

|-----------------------------------------------------------------------------------------------|-----------|

|                                                                                               |           |

| III.6.2 Transmit error probability (BER / PER)                                                | 69        |

| III.7 Implementation of different topologies of rectifier in semi-active wake-up radio        | 70        |

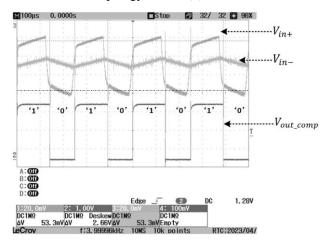

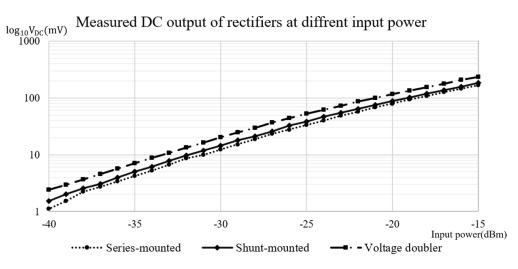

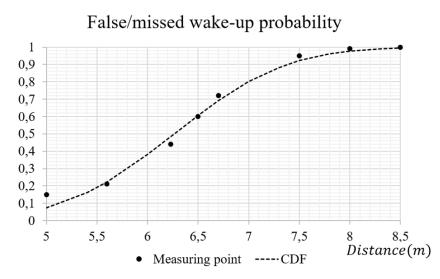

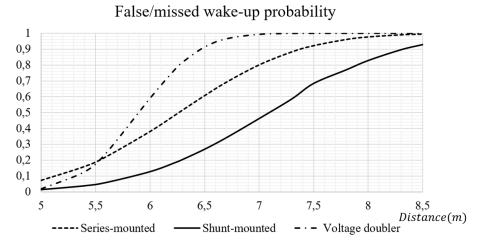

| III.7.1 Experimental measurement                                                              | 70        |

| III.7.2 Results comparison with SPICE simulation                                              | 78        |

| III.8 Conclusion                                                                              | 78        |

| III.9 Reference                                                                               | 79        |

| Chapter IV: Optimization and hardware integration of nodes with wake-up                       | radio for |

| wireless sensor network applications                                                          |           |

| IV.1 Introduction                                                                             | 81        |

| IV.2 Design of heterogeneous semi-active wake-up radio                                        |           |

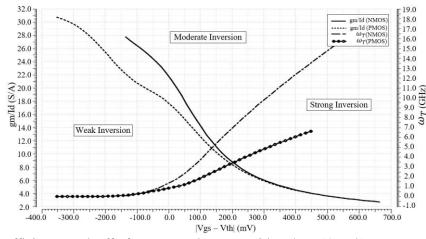

| IV.2.1 $g_m/I_d$ design methodology                                                           |           |

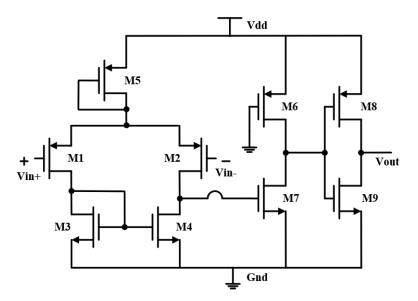

| IV.2.2 Purpose-designed CMOS comparator                                                       |           |

| IV.2.3 Layout of the comparator                                                               |           |

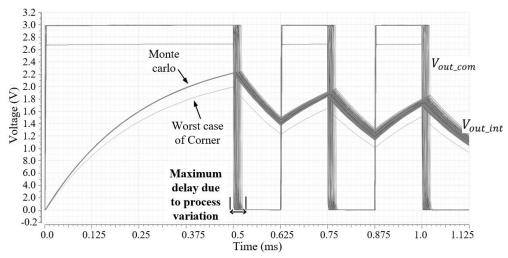

| IV.2.4 Simulation Results                                                                     |           |

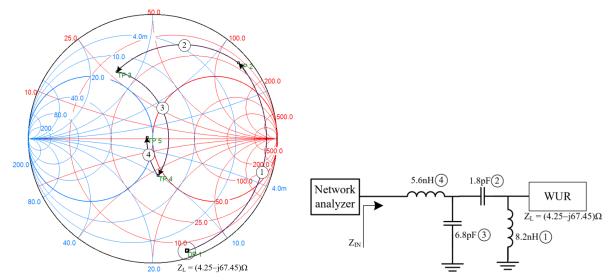

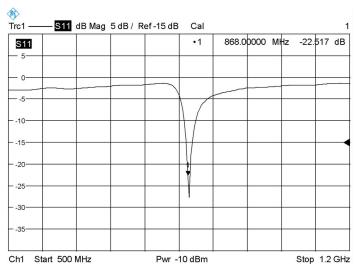

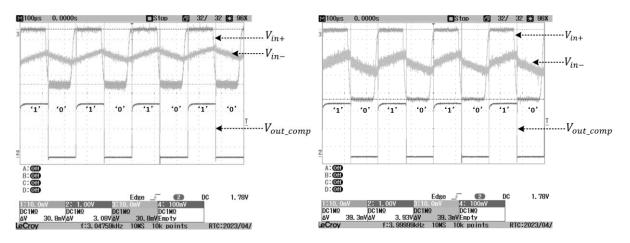

| IV.3 Optimization of semi-active wake-up radio prototypes                                     | 91        |

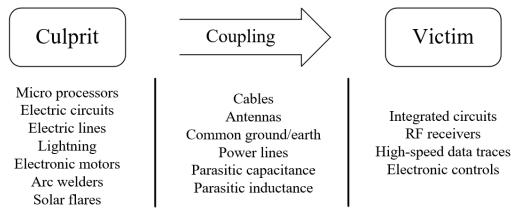

| IV.3.1 Electromagnetic compatibility (EMC)                                                    | 91        |

| IV.3.2 4-layer prototype design                                                               | 92        |

| IV.3.3 Summary of layout design rules<br>IV.3.4 Experimental Measurement                      | 93        |

|                                                                                               | 95        |

| IV.3.4 Performances' comparison                                                               | 99        |

| IV.4 Development of Arduino shield prototype                                                  |           |

| IV.4.1 List of modules in the node                                                            |           |

| IV.4.2 Implementation with micro-controller Arduino UNO                                       |           |

| IV.4.3 Shield prototype design                                                                |           |

| IV.4.4 Experimental measurement of scenario with 3 nodes                                      |           |

| IV.5 Conclusion                                                                               |           |

| IV.6 Reference                                                                                |           |

| Chapter V: Simulation of sensor networks with semi-active wake-up radio in O                  | MNeT++    |

| •••••••••••••••••••••••••••••••••••••••                                                       | 117       |

| V.1 Introduction                                                                              | 117       |

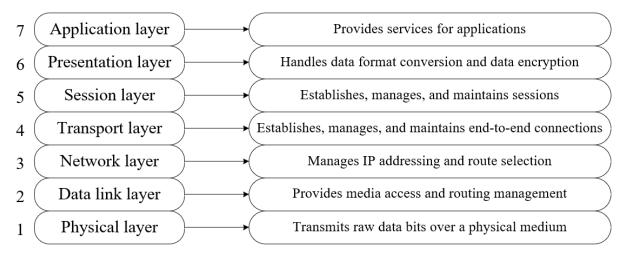

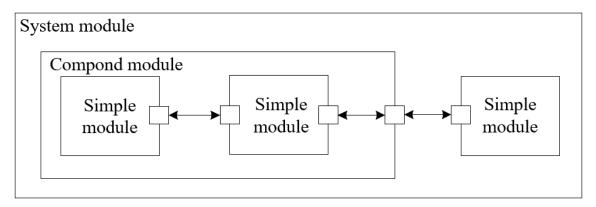

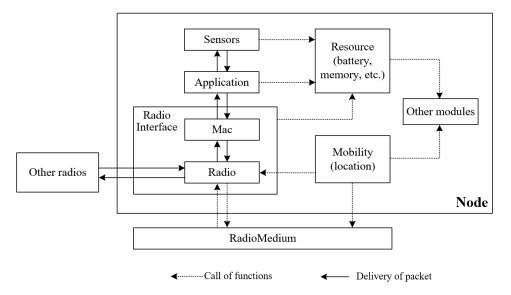

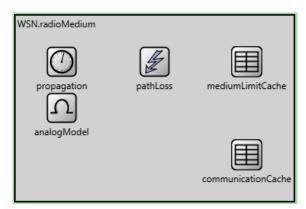

| V.2 Implementations of physical layer in OMNeT++                                              | 118       |

| V.3 Evaluation of semi-active wake-up radio's electronical models without framework           |           |

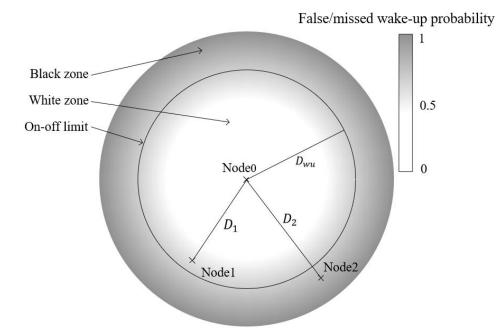

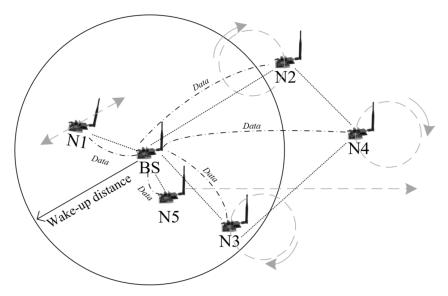

| V.3.1 Modeling description                                                                    | 121       |

| V.3.2 Simulation scenario                                                                     |           |

| V.3.3 Implemented models                                                                      |           |

| V.3.4 Simulation results                                                                      |           |

| V.4 Evaluation of node's performances with framework                                          |           |

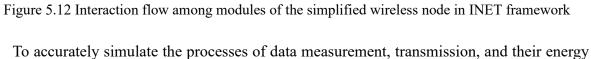

| V.4.1 INET framework                                                                          |           |

| V.4.2 Modeling description                                                                    |           |

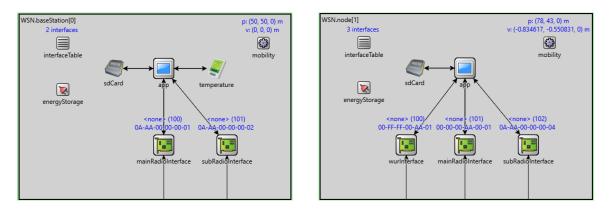

| V.4.3 Simulation scenario                                                                     |           |

| V.4.4 Simulation results                                                                      |           |

| V.5 Conclusion                                 |  |

|------------------------------------------------|--|

| V.6 Reference                                  |  |

| Chapter VI: General conclusion and perspective |  |

| VI.1 Conclusion                                |  |

| VI.2 Perspective                               |  |

| VI.3 Reference                                 |  |

|                                                |  |

## Abbreviations

| Ack             | Acknowledge                             |

|-----------------|-----------------------------------------|

| ASK             | Amplitude Shift Keying                  |

| AWGN            | Additive White Gaussian Noise           |

| CDF             | Cumulative Distribution Function        |

| CMOS            | Complementary Metal-Oxide-Semiconductor |

| $D_d$           | Data Transmit Range                     |

| $D_{wu}$        | Wake-Up Range                           |

| ED              | Envelope Detector                       |

| EMC             | Electromagnetic Compatibility           |

| EMI             | Electromagnetic Interference            |

| EPB             | Energy Per Bit                          |

| FSK             | Frequency Shift Keying                  |

| MCU             | Microcontroller Unit                    |

| OOK             | On-Off Keying                           |

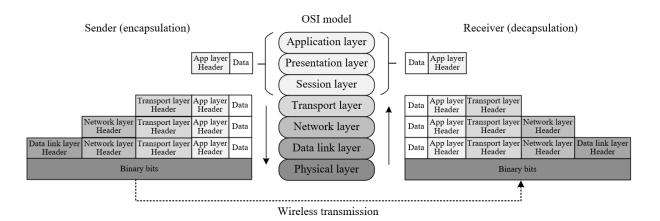

| OSI             | Open Systems Interconnection            |

| PCE             | Power Conversion Efficiency             |

| RFID            | Radio Frequency Identification          |

| SNR             | Signal to Noise Ratio                   |

| SR              | Slew Rate                               |

| ULP MCU         | Ultra-Low Power Microcontroller         |

| Vos             | Offset Voltage                          |

| V <sub>ov</sub> | Overdrive Voltage                       |

| $V_{th}$        | Threshold Voltage                       |

| WUP             | Wake-Up Packet                          |

| WUR             | Wake-Up Radio                           |

| WSN             | Wireless Sensors Network                |

## **Publications**

#### **International Conferences**

- R. Ding and W. Tatinian, "Design and modeling of heterogeneous semi-active wake-up radio for sensor network applications," 2023 21st IEEE Interregional NEWCAS Conference (NEWCAS), Edinburgh, United Kingdom, 2023.

- R. Ding and W. Tatinian, "Hierarchical Modeling of 868MHz Wake-up Radio in OMNeT++," 2022 37th Conference on Design of Circuits and Integrated Systems (DCIS), Pamplona, Spain, 2022.

- R. Ding and W. Tatinian, "Contribution to wake-up radio design for wireless sensor network." 2021 36th Conference on Design of Circuits and Integrated Systems (DCIS). Vila do Conde, Portugal, 2021.

#### **National Conferences**

- R. Ding and W. Tatinian, "Electrical modeling of wake-up radio for false wake-up prediction in sensor networks." 16ème Colloque du GDR SoC2. 2022.

- R. Ding and W. Tatinian, "Contribution to wake-up radio design for wireless sensor network." 1er Workshop CSC-Polytech, Paris, 2022.

- R. Ding and W. Tatinian, "Study of rectenna topologies of semi-active wake-up radio applications." 15ème Colloque National du GDR SoC2, 2021.

## **Chapter I: General introduction**

#### **I.1 Background**

Over the past decades, wireless sensor networks (WSNs) have been widely used in various fields, such as military, industrial, environmental monitoring and marine exploration applications [1]. Wireless sensor networks consist of a dense deployment of sensor nodes, equipped with the capability of wireless communication and monitoring and analyzing various environmental or physical conditions [2].

With the growing number of communicating objects and the energy constraints of wireless sensor nodes, their limited battery still restricts the development of large-scale network application. Since the radio receiver is one of the components with the highest power consumption, aside from the transmitter, it may cause the problem of power wastage in the receiver's idle listening. One solution is to turn off the main radio and introduce a wake-up radio (WUR). This is a small chip that requests a very low power to stay on for a continuous idle listening of the channel and turn on the main radio only when needed.

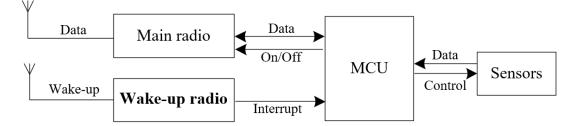

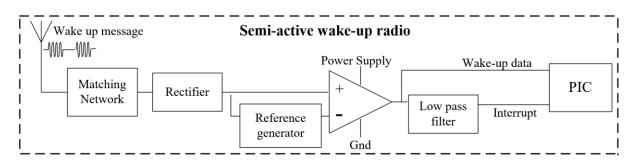

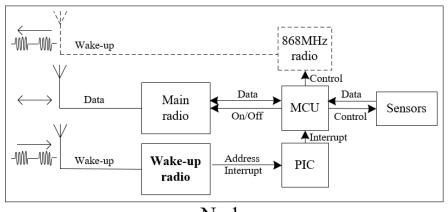

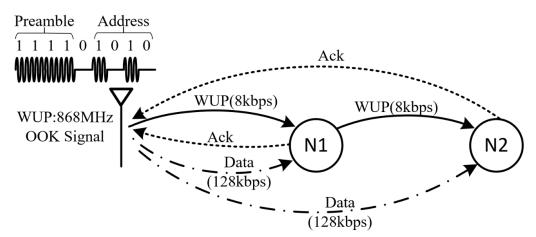

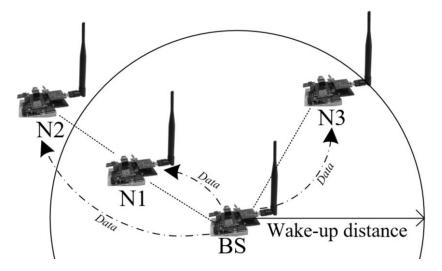

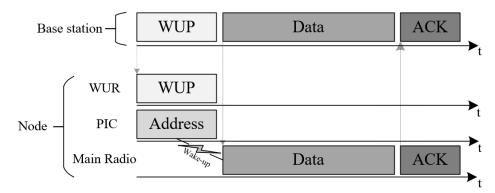

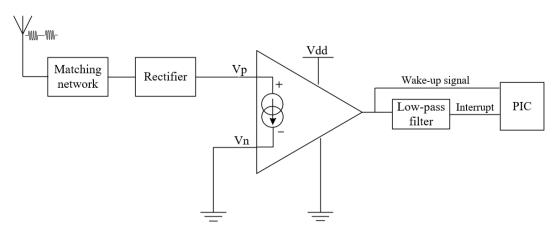

In the structure of wake-up radio's strategy, the main radio remains in deep standby or off mode until the request is received. Instead, the wake-up radio is always on to receive the messages. When the transmission part has a data packet to send, it will send a wake-up packet first. Then, the wake-up radio detects the wake-up message and generates an interrupt to the microcontroller unit (MCU) to switch it from standby mode to active mode. Next, the main radio will be turned on to exchange data packets in a conventional manner. The structure of this receiving part is shown in Figure 1.1:

Figure 1.1 Principal block diagram of wake-up radio-based receiver

#### I.2 Motivation and objective

Although a lot of works have published on this topic, most of them tend to study individual aspects like theory, SPICE simulation, or measurements. In this work, we provide a complete discussion, addressing all these areas comprehensively.

Our primary attention is on discrete semi-active wake-up radio. While most research usually discusses one WUR topology at a time, we compare multiple topologies in detail, covering from theory and SPICE simulations to measuring prototypes.

Moreover, to estimate the quality of the communication, it is particularly important to account for the probability of false wake-up or missed wake-up. Because it will not only affect the function of a single node, but also increase the transmission time and the average energy of each transmitted bit, thus affecting the entire data transmission. To accurately account for these effects, accurate modeling of WUR is required.

Finally, we implement some wake-up radio models in a sensor network simulator and run some scenarios with these new models to see how the wake-up radio behaves in practice, by comparing between theory, SPICE simulations and measurements.

In all these works, we will highlight our contributions to the field of wake-up radio technology by linking our findings to the existing state-of-the-art.

#### I.3 Thesis work

The adopted methodology begins with electrical simulations on the WUR to preliminarily assess its potential performance. Subsequently, we proceed on theoretical modeling. The most challenging task in the theoretical study is to establish a model for nonlinear components, especially the diodes of the rectifier, as the model must maintain accuracy across a dynamic range of several tens of dB. We then assemble and test the circuits, comparing the results with the simulation. Afterwards, we optimize the WUR, including the layout and routing of the prototype to enhance its robustness. Furthermore, we also develop a node that combines WUR with other key modules, allowing us to evaluate the performance of WUR-based nodes in real-world situations. And then, the models are updated based on actual measurements and compared

to theoretical predictions. In the end, we can perform the simulations of these models in a network simulator OMNeT++.

This thesis describes in detail the whole process of WUR circuit simulation, theoretical modeling, PCB implementation, prototype testing and optimization. Additionally, this study conducts simulations of different scenarios in OMNeT++ to investigate the behavior of nodes equipped with semi-active WUR under different models and frameworks. We propose a physical layer modeling approach to consider the performance of the wake-up radio and its impact on data transmission, which is complementary to the MAC layer modeling.

The rest of manuscript is organized as follows: Chapter II presents a comprehensive analysis and classification of the state-of-the-art for wake-up radio technology. In Chapter III, we focus on the design and modeling of semi-active wake-up radio. In chapter IV, we concentrate on the optimization of the semi-active wake-up radio system. Chapter V highlights the value of using network simulator, providing a comparison of different models of WUR and framework. Finally, Chapter VI gives a general conclusion and some perspectives to end this manuscript.

#### I.4 Reference

[1] J. Ma, J. Wang, and T. Zhang, "A survey of recent achievements for wireless sensor networks testbeds," in 2017 International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery (CyberC), IEEE, 2017, pp. 378–381.

[2] U. M. Colesanti, C. Crociani, and A. Vitaletti, "On the accuracy of omnet++ in the wireless sensornetworks domain: simulation vs. testbed," in *Proceedings of the 4th ACM workshop on Performance evaluation of wireless ad hoc, sensor, and ubiquitous networks*, 2007, pp. 25–31.

## Chapter II: State-of-the-art of wake-up radio and preliminary study of semi-active wake-up radio

#### **II.1 Introduction**

This chapter presents a comprehensive analysis and classification of the state-of-the-art wake-up radio (WUR) technology. The characteristics of each type of WUR are discussed in detail. We then choose to focus on the semi-active wake-up radio and analyze the key components of the circuit. Furthermore, we divide the semi-active WUR circuit into the analog part and the digital part, and study them separately. Performances of semi-active WUR are simulated and presented.

The remainder of this chapter is organized as follows: Section II.2 discusses the state-ofthe-art of wake-up radio. In Section II.3, we study the rectifiers in semi-active wake-up radios, including how to choose nonlinear components and rectifier topologies. And then, preliminary simulations and analyzes based on discrete components of semi-active wake-up radio are given in Sections II.4 and 5. Finally, Section II.7 concludes the chapter.

#### **II.2 State-of-the-art of wake-up radio**

Numerous studies are conducted on the use of wake-up radios in wireless sensor networks (WSNs) to reduce power consumption. This section presents a state-of-the-art review of WUR literature. By the power supply method, it can be classified into three groups of wake-up radio circuits: fully-passive, fully-active, and semi-active. To ensure clarity in the discussions, we will divide each type of WUR into three categories based on technology: prototypes constructed using off-the-shelf discrete components, implementations with complementary metal-oxide-semiconductor (CMOS) technology for integrated circuits, and those based on radio-frequency identification (RFID) technology.

The use of off-the-shelf discrete components simplifies the rapid prototyping of WUR.

CMOS implementations integrate all components directly onto silicon, resulting in more compact circuits and better performance for the same function. And RFID technology is another option. These WUR can draw power from the electromagnetic field generated by the reader device, which are mainly used in passive WUR. And then, we also analyze the selection of RF modulation and carrier frequency in WUR. The state-of-the-art of wake-up radio is investigated by studying the following main characteristics:

*Sensitivity:* it's the minimum signal strength that the wake-up radio can successfully detect and process while maintaining the functionality. This determines the transmit distance of the wake-up radio at the same transmission power and frequency.

*Power consumption:* it's the amount of electrical energy consumed by the wake-up radio. In battery-powered systems, it directly affects the battery life.

Frequency: generally, it refers to the carrier frequency of the wake-up signal.

*Modulation:* it's the process of manipulating the wake-up signal and combining it with a carrier to make it suitable for channel transmission. Typically, the information of the signal source contains a DC component and a lower frequency component, which is referred to as a baseband signal.

*Latency:* it generally refers to the time it takes between when the transmitter sends a wakeup signal and when the main radio wakes up.

*Data rate:* it represents the quantity of bits transmitted through a communication channel per unit time, generally expressed in bits per second (bps), It's influenced by factors such as the modulation, baseband frequency, and signal-to-noise ratio, etc. [1]. High data rate can reduce wake-up latency, but they may lead to decreased sensitivity. On the other hand, at lower data rate, the transmitter needs to spend more time on sending, resulting in higher power consumption on the transmitting side [2].

*Addressability:* it's the ability to selectively activate nodes in the network to achieve more efficient communication [1]. By assigning a unique address to the main radio in each node, unnecessary activation of other nodes can be prevented, to save energy. This requires the wake-up radio to decode the received wake-up signal to determine if the signal is intended for the main radio in its node.

Our review of the state-of-the-art is based on the main characteristics mentioned above. If

certain characteristics are not discussed, it may be due to their lesser significance in the respective research articles, or the authors didn't mention them.

#### **II.2.2** Fully-passive wake-up radio

Fully-passive wake-up radio circuits do not necessitate a power supply. Although the WUR circuit requires power to operate, it does not require external battery power. This can be achieved by harvesting energy from the incoming RF signal.

Energy harvesting circuits can capture energy from wind, heat, light or electromagnetic radiation in the environment and convert it into electrical energy. This energy can either be used to power comparators and ultra-low-power micro-controllers, or be stored in capacitors. Better energy harvesting efficiency will lead to better performance of fully-passive wake-up radios [1]. However, we need to attach more hardware to the WUR to provide this functionality. This increases the size and complexity of the circuit. In addition, the process of energy recovery leads to a delay in main radio's wake-up due to the need for sufficient time to accumulate energy. Therefore, the transmitter may transmit the wake-up signal longer, which consumes more energy [4].

Passive wake-up radio is mainly made using discrete Schottky diodes, RFID or integrated CMOS technologies. CMOS technology is more popular due to its low power consumption and low threshold voltage in ICs. RFID is also widely used because it already has energy harvesting capabilities, which reduces development time.

#### Discrete

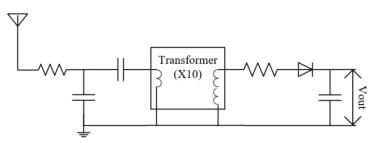

The first proof of concept for WUR was presented by Gu et al. (2005) [5]. They proposed the structure of a Basic Radio-Triggered Circuit shown in Figure 2.1, which was an entirely passive circuit that was simulated using SPICE. The circuit operated at a frequency of 433MHz and achieved a transmission distance of 3m at a transmit power of +10dBm with a latency of 5ms. To evaluate the application lifetime of the sensor network, the authors used the NS-2 network simulator. Their findings showed that WUR can save up to 98% of energy for systems without power management. The authors also proposed structures with longer transmission distances, such as energy harvesting circuits, which could store energy from the radio signal

and use it later. However, this required adding some delay. Furthermore, a multi-frequency technology called radio-triggered identification (RTID) was presented, which provided better selectivity in energy management services.

Figure 2.1 Radio trigger circuit with step-up transformer

#### CMOS

Chung et al. (2011) [6] proposed a passive integrated WUR fabricated using the 0.18 $\mu$ m CMOS process. The device consisted of a RF front-end and a 512-bit digital baseband with non-volatile memory. The RF front end comprised of a voltage multiplier (VM), voltage limiter, demodulator, modulator, ring oscillator, power-on reset (POR), and bias circuit. The voltage multiplier operated by harvesting RF energy. In read mode, the device achieved a sensitivity of -17dBm with a power consumption of 2.64 $\mu$ W. The oscillator frequency was measured to be approximately 2.07MHz, and the power-up time was 100 $\mu$ s.

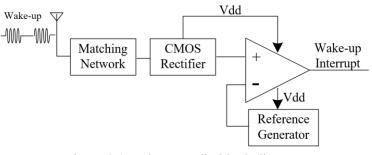

Kamalinejad et al. (2014) [7] designed and simulated a WUR circuit using a  $0.13\mu$ m CMOS technology. The circuit consisted of a rectifier, a bandgap reference generator, and a low power comparator. In the rectifier, the authors developed a bias scheme to increase the gate voltage of the switching transistor. They employed a quasi-floating gate architecture with the gate of the switching transistor connected to a boosted voltage level to achieve high power conversion efficiency (PCE) at small input levels. The rectifier rectified the differential RF and detected the envelope of the OOK wake-up signal. Then the rectified DC voltage was utilized to power the comparator and the bandgap reference generator. The block diagram is shown in Figure 2.2. Simulation results indicated a sensitivity of -33dBm at a wake-up signal of 100kbps. However, the authors only did the simulation, and thus further experimental validation was required.

Zgaren et al. (2015) [8] implemented a WUR in the 0.13µm CMOS process. This WUR included an antenna shared with the main transceiver, an RF-DC rectifier, and a comparator

with a voltage reference. The RF-DC rectifier was used to generate the envelope of the OOK signal, which was converted into a DC voltage to power the comparator. The WUR achieved a sensitivity of -53dBm with a data rate of 100kbps and a power dissipation of  $0.2\mu$ W. There are other studies that also investigated CMOS technology, as reported in [9-11].

Figure 2.2 Wake-up radio block diagram

#### RFID

RFID technology is one of the possible approaches to achieve passive WUR, since it has a well-defined communication protocol and uses energy harvesting to enable this communication [12].

Wireless Identification and Sensing Platform (WISP) was the first fully programmable platform without external power supply that used power transmitted from a long range ultrahigh frequency (UHF) RFID reader. It included a 16-bit micro-controller with an analog-to-digital converter, as shown in Figure 2.3. The center frequency was 915MHz. Experimental tests presented that the distance could be up to 4.5m with a transmit power equal to +30dBm. However, this also meant that the sensitivity was only –6.7dBm [13].

Figure 2.3 WISP Platform Block Diagram

Ba et al. (2013) [14] introduced a new passive WUR called WISP-Mote, which used passive programmable RFID tags as wake-up radios for traditional sensor nodes. To extend the wake-up range, they disabled WISP-reader communication and eliminated all other

computational loads in the WISP MCU. Then, they characterized the WISP-Mote with field tests in different operating environments. The results showed that the WISP-Mote had a relatively stable wake-up range of up to 4.5m<sup>\*</sup> in an open environment. In a noisy environment, the probability of waking up reaches 80% when the communication distance is 3m<sup>\*</sup>. They also tested with duty cycling approaches, where a timer was set and the firing of the timer wakes up the node. They found that wake-up radio sensor networks have great potential over duty cycling for energy efficiency, while providing similar latency and packet delivery performance [15].

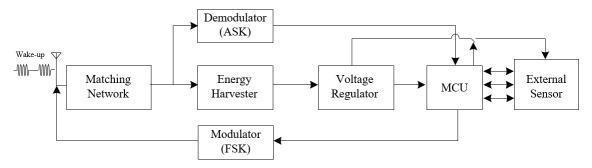

In [12], Chen et al. (2015) also proposed the energy harvester WISP-Mote (EH-WISP-Mote), which paralleled the WISP-mote circuit with the energy harvesting circuit to provide additional energy harvesting capability to extend the wake-up range, as shown in Figure 2.4. During testing, they found that the wake-up range reaches 5.2m<sup>\*</sup> and the total wake-up area was increased by 30%.

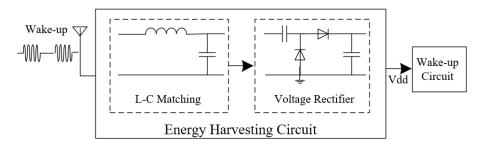

Figure 2.4 Energy harvesting circuit in EH-WISP-Mote

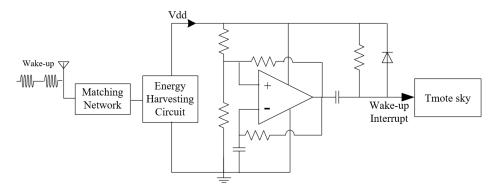

The Range EnhAnCing energy Harvester-Mote (REACH-Mote) was composed of an energy harvesting circuit and an ultra-low power wake-up circuit (pulse generator) presented in Figure 2.5, and had a communication range of up to 11.3m<sup>\*</sup> on broadcast-based wake-ups. The energy harvesting module was improved by increasing the number of energy harvesters and connecting them in series to increase the output voltage. A voltage regulator and a front control switch using the Tmote Sky WSN platform were added to change the supply voltage. By sleeping on low voltage power, the Tmote Sky had a lower trigger wake-up requirement. When the Tmote Sky woke up, the power returned to 3V. The improved prototype, named REACH2-Mote, achieved a wake-up range of 13.4m [3], [12].

De Donno et al. (2014) [16] introduced two types of fully-passive 868MHz WURs, called WWU (Write Wake Up) and MWU (Multicast Wake Up), using UHF RFID tags. The WWU

<sup>\*</sup>The authors didn't mention the value of transmit power.

was ID-based, had a transmission range of up to 11m with a transmission power of +30dBm, and a delay of 258ms. The MWU was diffusion-based, composed of a single-stage full-wave rectifier and a DC-DC charge pump. It had a transmission range of 10m, but a smaller delay of 30ms [17].

Figure 2.5 Main components of the REACH-Mote system

#### **II.2.3 Fully-active wake-up radio**

Unlike fully-passive WUR, which doesn't rely on a power supply, a fully-active WUR is powered by an external power source to operate and usually listens for signals in an always-on manner. It typically consumes more power. However, it can offer faster response times and better performance in certain situations, especially when it comes to longer communication ranges and complex signal processing. Based on the results of survey, it can be concluded that CMOS technology is the most commonly utilized technology for fully-active wake-up radio, due to its low power consumption and high level of integration.

#### Discrete

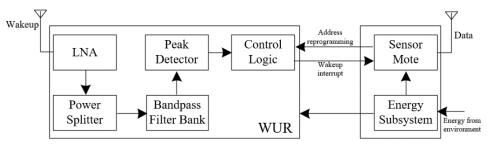

Petroli et al. (2014) [18] presented a novel topology that operated in the 2.4GHz ISM band and complied to the IEEE 802.15.4 standard. The receiver's front end was composed of an antenna, low noise amplifier, power divider, and filters, as illustrated in Figure 2.6. The LNA and filter were designed using integrated technology. A prototype was fabricated using off-theshelf methods to validate the feasibility of the proposed design. The prototype hardware considered four different channels, allowing node addressing. However, the test results of the prototype have not been published yet. The authors also introduced two protocols, FLOOD-WUP and GREEN-WUP, which employed selective wake-up and dynamic address allocation to enhance system performance. FLOOD-WUP was a flooding wake-up protocol that achieves better latency vs. energy consumption performance, while GREEN-WUP was a hop-countbased converge casting wake-up protocol. Compared to traditional WSN protocols, the new approach demonstrated superior performance in terms of addressing delay and power consumption.

Figure 2.6 Block diagram of WUR with 4 channels for addressing

#### CMOS

CMOS fully-active wake-up radio can be broadly categorized into two groups based on the presence of mixers or oscillators. In cases where these high-power consumption components are present, the sensitivity of WUR is enhanced at the cost of increased power consumption. Conversely, with the envelope detector (ED), power consumption in the nanowatt range can be achieved.

#### Frequency-mixing topology

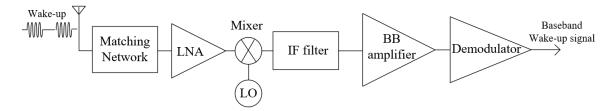

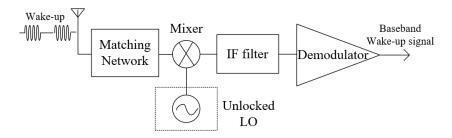

Many frequency-mixing topology proposed in active circuits use heterodyne methods, as showed in Figure 2.7. The principle is to mix the received RF signal with the local oscillator circuit to generate an intermediate frequency (IF) signal. The IF signal is then amplified and detected to restore the original signal. Milosiu et al. (2013) achieved a  $7\mu$ W 2.4GHz wake-up radio with -80dBm sensitivity in [19]. And in [20], Liu et al. (2020) proposed a WUR which incorporated an inductor-capacitor voltage-controlled oscillator (LC-VCO) and a frequency locked loop (FLL) achieved a sensitivity of -92.6dBm, but also consumed a very high power of 495 $\mu$ W.

Additionally, super-regenerative amplifiers are commonly used in WUR systems due to their lower power consumption and better sensitivity. When the wake-up receiver is in standby mode, the super-regenerative amplifier continuously generates and attenuates an oscillating signal, thereby facilitating the sensitive detection of radio frequency signals. Upon receiving the wake-up signal, the super-regenerative amplifier amplifies the signal and outputs it to the subsequent circuit to initiate the main chip of the system. The WUR in [21] proposed by Cho et al. (2015) achieved a power consumption of  $42.5\mu$ W at data rate of 100kbps and the sensitivity reaches -72dBm. Based on this super-regenerative architecture, Petäjäjärvi et al. (2016) in [22] proposed a WUR using Hybrid Broadcast Channel (HBC). Their approach used self-quenching and relaxed synchronization at 1.25kbps, achieving -97dBm sensitivity while consuming  $40\mu$ W.

Figure 2.7 Block diagram of heterodyne WUR

Furthermore, for frequency-mixing topology, power consumption is usually limited by the high power of the LO. low power high sensitivity uncertain IF Architecture is another implementation for forming a wake-up receiver: it uses a low power ring oscillator to down convert the RF signal to the IF frequency, as shown in Figure 2.8. Since the signal is amplified at the IF frequency, its consumption is lower.

Figure 2.8 Block diagram of uncertain IF WUR

Pletcher et al. (2008) [23] introduced a comprehensive implementation of WUR using an uncertain-IF architecture. This design approach relaxed the requirements for phase noise and frequency accuracy, thereby enabling the utilization of a free-running ring oscillator for LO generation and eliminating the need for a PLL. The WUR comprised a bulk acoustic wave (BAW) resonator for network impedance matching, a front-end IF amplifier for radio frequency

(RF) signal conditioning and amplification, and an envelope detector. The implemented WUR achieves a sensitivity of -72dBm at a bit error rate of 100kbps while consuming  $52\mu$ W of power [24].

#### RFED-based technology

The radio frequency envelope detection (RFED) architecture has been the most widely adopted approach for developing a WUR [22]. It's a simple and low-cost solution that is highly sensitive to weak signals, making it suitable for low-power, low-data-rate wake-up radio applications.

In [25], a WUR utilizing ED technology was presented by Wang et al. (2018), boasting a sensitivity of -69dBm and a remarkably low power consumption of 4.5nW. To achieve reasonable immunity to interference, a combination of techniques was employed, including low carrier frequency operation and reduced WUR data rates, as well as the implementation of passive, high-Q transformers/filters to achieve a 25dB gain passively. These measures ensured effective operation in the presence of interfering signals. Moreover, a sub- $\mu$ W WUR was introduced by Mangal et al. (2019) in [26] with a sensitivity of -79dBm. This achievement was made possible by utilizing multi-stage passive energy detectors and a high-Q input matching network. However, it should be noted that the implementation of such techniques came at the cost of relaxing latency constraints. Other active WUR that were based on ED technology can be found in [27-30].

#### RFID

Jurdak et al. (2010) [31] provided comprehensive information regarding WUR designs utilizing commercially available active RFID tags. The analysis confirmed that RFIDImpulse, equipped with Adaptive Low Power Mode, consumed approximately 20 times less energy, compared to IEEE 802.15.4 in low traffic scenarios. In terms of operation, when a node transmitter intended to send a packet, it activated the RFID reader to trigger the corresponding RFID tag. The signal received by the neighbouring receiver generates a wake-up interrupt to the local MCU, which subsequently awakened the radio and prepared to receive incoming packets. However, it was worth noting that this receiver didn't use addressing to selectively awaken sensor nodes. The authors then provided simulations and comparisons of binary tree

scenarios for B-MAC, IEEE 802.15.4, and RFID Impulse's WUR designs. The results showed that RFIDImpulse had the lowest overall energy consumption, which was about 20 times lower than IEEE 802.15.4 and 13 times lower than B-MAC [32].

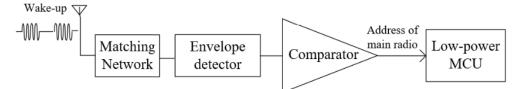

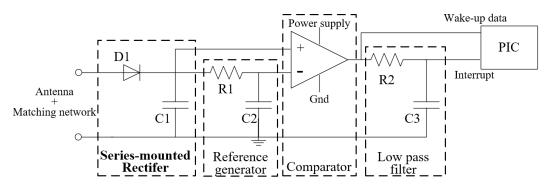

#### II.2.4 Semi-active wake-up radio

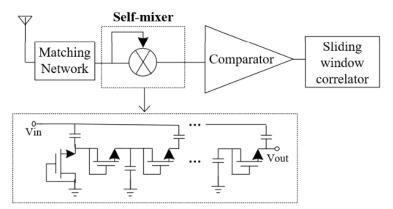

The majority of proposed WUR design approaches are semi-active, resulting in compromised consumption and sensitivity [33]. In such approaches, only a part of components necessitates a continuous power supply from external sources. The prevalent technique involves implementing an envelope detector utilizing passive components such as Schottky diodes or MOSFETs. Then, active components such as correlators and comparators are utilized to generate interrupts to the microcontroller unit for addressing, as presented in Figure 2.9. This approach is considered the most common among the various WUR design methods available.

Figure 2.9 Block diagram of most common used semi-active WUR

#### Discrete

The first operational WUR prototype was developed by Van der Doorn et al. (2009) [34]. In this study, the author proposed the integration of a low-power MCU to facilitate the exposure and decoding of wake-up signal and to notify the AT-mega128L processor through an interrupt. The power consumption of WUR was  $819\mu$ W in listen mode with a sensitivity of -28dBm. Despite the short communication distance and high-power consumption, the author has sorted out various requirements such as low cost, low interference, 10-meter range, and low delay that WUR should meet through prototype testing. This achievement inspired follow-up research in this field.

Magno et al. (2016) [33] proposed a low-sensitivity low-power wake-up radio, which employed OOK modulation and was composed of four main building blocks: matching network, passive envelope detector, comparator, and preamble detector. Upon reception of a valid wakeup address, the output of the preamble detector interrupts a low-power MCU responsible for address matching and triggering the main sensor node. This WUR outperformed previous techniques, providing a flexible solution with low power consumption  $(1.2\mu W)$ , high sensitivity (-55dBm) and addressability. Experimental results demonstrated that addressing could reduce false/missed wake-ups. Simulation of real-world scenarios comparisons with other WUR solutions and duty-cycling protocols were also done in this paper.

Recently, Kazdaridis et al. (2021) proposed a method for enhancing the sensitivity of the WUR based on the circuit in [33]. This method was capable of significantly improving the sensitivity of the WUR to a level lower than -70dBm, while keeping the power consumption at a similar level. The authors noted that in all previously published WUR, the signal from the envelope detector was directly fed to the comparator, which meant that the sensitivity of the WUR was dependent on the characteristics of the comparator used. To address this issue, the authors proposed inserting an operational amplifier between the envelope detector and the comparator. This arrangement amplified the low-level signal DC signal, which was then further amplified by the comparator. The consumption of the operational amplifier was 450nA. And then, the authors chose a high input offset voltage (Vos) but low-consumption (110nA) comparator, as the proposed circuit was no longer dependent on the Vos of the comparator. However, this WUR introduced an external fixed reference as the negative input of the comparator, which may not be optimal from a convenience standpoint [35].

In addition, instead of relying on a low-power MCU for decoding, Ammar et al. (2015) [36] proposed a WUR that used an address decoder based on flip-flops and a low-power clock generator. The proposed RF front-end WUR employed passive circuit elements, which resulted in no static current consumption. In active mode, their serial code detector, which served as an address decoder, dissipated 13.41µW. Although the WUR based on flip-flops consumed more power, it could significantly reduce latency to only 80µs. Based on this, Khodr et al. (2017) [37] proposed an enhanced address decoder design. Their approach involved using XNOR gates with open drain output and replacing all AND gates with a single pull-up resistor, which could reduce power consumption and circuit complexity.

#### AS393x

There are many proposals in the literature where authors employed a commercially available WUR chip for address decoding in their prototypes. One such chip is the AS393x

series from Austria Microsystems, which is a 3D low-power, low-frequency Amplitude Shift Keying (ASK) WUR capable of generating a wake-up interrupt upon detecting a signal at a carrier frequency between 15-150KHz. One of its unique features is its integrated correlator, which allows for the implementation of a 16-bit or 32-bit wake-up address decoding scheme, making it a pattern recognizer. The AS393x WUR boasts a maximum sensitivity of -69 dBm, with current consumption varying from  $1.7\mu$ A to  $12\mu$ A. Its capabilities make it an attractive option for designers looking for a WUR solution.

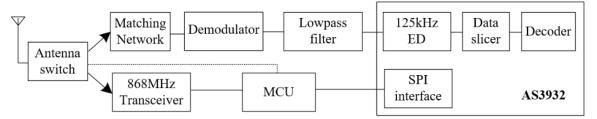

Gamm et al. (2010) [38] introduced the first in-band sub-carrier modulation WUR system based on AS3932, representing the first complete WUR transceiver. In this system, the main radio also functioned as a transmitter to generate the wake-up signal. The WUR had an active power consumption of  $7.8\mu$ W, while achieving a maximum sensitivity of -52dBm with a data rate of 250kbps. Figure 2.10 shows the block diagram of the proposed senor node. The AS3932 extracted the 125KHz signal from the 868MHz wake-up signal and decoded the original data for address comparison. Once the address was matched, the main node was triggered, and an antenna switch was used to bypass the WUR, allowing data exchange to occur via the main radio.

Figure 2.10 Block diagram of the proposed senor node in [38]

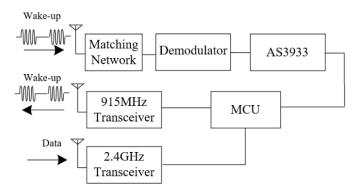

Cabarcas et al. (2020) [39] presented an application of WUR, which supported a dual-stack architecture designed to operate in the 915MHz and 2.4GHz ISM bands for the WUR and main radio, respectively. Their approach featured a passive demodulator, combining with AS3933 chip as the WUR. The overall architecture is presented in Figure 2.11.

Oller et al. (2013) [40] compared a SuA-WUR (not embedded with AS393x) and AS393xbased WUR. They concluded that SuA-WUR was a more energy-saving and cost-effective alternative based on AS3933. SuA-WUR had lower power consumption and was not so complicated in hardware components. Although it currently didn't support the addressing function, it could use alternative energy-saving addressing methods. They also looked at several criteria for systems from the perspective of WUR. The criteria studied include the type of antenna, the use of noise filters, and the number of rectifier stages and impedance matching inductors. Measurements were performed analysing the effect of receiver height and distance from the location of the transmitter, the material composition of the WUR, the output power of the transmitter, and the type of environment (inside or outside).

Figure 2.11 Block diagram of the node combining with AS3933 chip

#### CMOS

The first complete implementation of a WUR with a power consumption of around  $10\mu$ W was presented by Durante et al. (2009) The solution included on-chip MOS detector, programmable amplifiers, and integrators. For reasons of flexibility in implementation, an FPGA was dedicated to digital decoding. Its static power consumption was 12.5 $\mu$ W and the sensitivity/data rate was -57dBm/100kbps [41].

Ishige et al. (2016) [42] proposed a WUR which comprised a LC matching network, a 30stage CMOS voltage multiplier, and a Schmitt trigger comparator. The voltage multiplier was specifically designed for 65 nm SOTB (Silicon On Thin Buried Oxide) technology to enable low voltage operation. Simulation results demonstrated that the WUR achieved a sensitivity of -30 dBm, and the comparator had a power consumption of 6.7nW. However, it should be noted that an external reference voltage was used and only simulation results were available.

Moody et al. (2019) [43] compared the performance of passive and active CMOS detectors in WUR by modeling them. They analyzed the detectors' sensitivity and power consumption, taking into account the lack of RF gain and the noise produced by the detectors. Based on their findings, they determined that the choice between the two types of detectors depended on the IF bandwidth and DC power requirements of the application. Passive detectors were superior for low bias currents (<100nA) due to their better noise sensitivity and lower power consumption, whereas active detectors were more suitable for higher IF bandwidths and dc powers due to their lower thermal noise and decreased overall contribution of noise.

Mangal et al. (2019) [44] proposed a WUR which was fabricated in 0.13µm CMOS and operated from a 0.5V supply. The sensitivity was -56.4dBm with a power consumption of 222nW. A 10 stages voltage multiplying self-mixer using MOS transistors in weak inversion consumed 2.7nW and offers multi-stage conversion gain at baseband. The block diagram is shown in the Figure 2.12. The authors point out that the sensitivity of the envelope detector (ED) is affected by flicker noise and that it has a delay of more than 10ms due to its low bandwidth. Selectivity to modulated interferers is limited by the RF matching network. Compared with ED, the self-mixer technique offers better sensitivity and shorter delay, according to the authors.

Figure 2.12 block diagram of WUR based on self-mixer

Galante-Sempere et al. (2022) [45] compared the performance of an off-chip RFED WUR implemented with AS3933 and a fully integrated CMOS WUR. The off-chip WUR showed higher selectivity due to a high-Q input filter, while the fully integrated WUR achieved a sensitivity of -63.2dBm with low power consumption ( $6.77\mu$ W). The circuit included a single MOSFET-based envelope detector with an integrated transformer to enhance sensitivity while keeping power consumption low. However, this design resulted in a larger circuit area. The study highlights the choice of implementation depends on specific requirements such as selectivity, sensitivity, power consumption, and circuit area.

#### RFID

Malinowski et al. (2007) [46] used a 300MHz RFID WUR to activate CargoNet, which was an ultra-low-power WSN mote based on the MSP430. The RFID WUR circuit was composed of an LC tank that amplified the signal received by the antenna and a Schottky diode that functioned as an envelope detector. Additionally, an operational amplifier provided voltage gain. The sensitivity was -65dBm with a power consumption of 2.8µW.

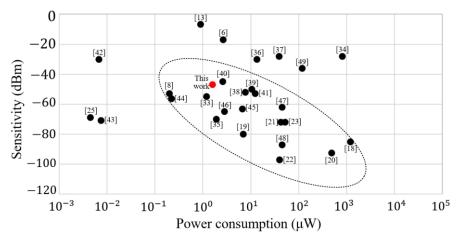

Figure 2.13 presents the sensitivity as a function of power consumption for the WUR related work published in recent years. Each dot represents a study, with the majority of them being concentrated within the encircled region. A linear trend indicates a correlation between sensitivity and power consumption. In general, higher power consumption results in better sensitivity. In this thesis, our WUR achieves a sensitivity of -47dBm at a power consumption of  $1.7\mu$ W, shown in red on the figure. Its sensitivity and power consumption relationship are within the typical range, compared with the existing literature. It's worth to note that some points lie outside the circle, with those in the upper often representing earlier publications. Additionally, the two reference papers to the left of the circle achieved high sensitivity with very low power consumption. However, in practice, sensitivity is influenced by various factors, such as the technology used, component selection, implementation complexity, and other characteristics like modulation, frequency, and data rate, etc. Case-specific analysis is necessary to fully understand each situation.

Figure 2.13 Sensitivity as a function of power consumption

#### **II.2.5** Choice of modulation and frequency

#### **Choice of modulation**

After conducting a comprehensive analysis, it's concluded that On-Off Keying (OOK) and Frequency Shift Keying (FSK) are the two most extensively utilized modulation techniques in wake-up radio applications. It is worth noting that a substantial proportion of the wake-up radios described earlier utilize OOK modulation. OOK stands for the simplest form of Amplitude Shift Keying (ASK) which represents digital data such as the presence or absence of a carrier wave. In this case, a '1' is encoded by transmitting the RF carrier, while a '0' is simply the absence of the carrier. OOK modulation is easier to implement and requires less complex hardware. Additionally, OOK modulation requires only one frequency band, which makes it simpler to implement in low-power and low-cost devices.

In contrast, FSK modulation is more complex and dissipates more power, as it necessitates the use of an accurate local oscillator and I/Q signal path to demodulate the received RF signals. FSK modulation is also a digital modulation technique in which the information signal is modulated onto the frequency of the carrier signal. Compared to OOK modulation, FSK is more resilient to noise and interference. This is because the receiver only needs to detect the frequency of the carrier signal, which is less susceptible to noise.

Bea et al. (2015) [47] proposed a WUR designed with the demodulation of FSK. This WUR incorporated a digitally controlled oscillator, which was coupled with an envelope detector. The power consumption of this WUR was  $45\mu$ W, which was relatively high when compared to its operating frequency of 80 MHz. Abe et al. (2014) [48] presented a method for reducing power consumption in the FSK wake-up radio, which comprised two main parts: an ultra-low power energy detection receiver (EDRX) and an address detection FSK receiver (ADRX). The ADRX was activated only when a wake-up packet was detected by the EDRX, thereby reducing power consumption. The ADRX used the FSK modulated address information from the second data packet (ADP) to activate the main receiver. The EDRX performed bit-length detection, while the ADRX performed address detection, resulting in improved noise immunity and lower average power consumption. The proposed receiver achieved a sensitivity of -87dBm while consuming an average power of  $45.5\mu$ W.

Furthermore, Taris et al. (2015) [49] proposed a novel low power demodulator compatible with both OOK and FSK modulations, which featured an LC oscillator coupled with an envelope detector and is implemented using a 65nm CMOS technology. The circuit consumed  $120\mu$ W, and properly demodulated OOK and FSK modulated signal at 2.4GHz with data rate up to 500kbps.

In general, both OOK and FSK modulation are popular choices in wake-up radio applications. The design of WUR systems leans towards using OOK, given its simplified implementation and lower power consumption. Similarly, in this thesis, we also opt for OOK modulation. Nonetheless, in scenarios where communication channels are noisy or congested, FSK modulation might prove to be a more suitable choice. The selection of the modulation technique is dependent on the specific requirements of the application, such as power consumption, reliability, and robustness.

#### **Choice of frequency**

Selecting an appropriate frequency for wake-up radio is also an important factor that affects several characteristics such as receiving antenna size, operating range, matching network, and selection of required components. Previous studies indicated a trend for wake-up radio from sub-GHz bands to 2.4 GHz. Based on Friis equation, with a sensitivity of -30dBm, transmit power of +10dBm, and a carrier frequency of 868 MHz, the theoretical maximal transmit distance is 4 meters. However, at higher frequencies, such as 2.4 GHz, the signal attenuation increases, causing it to decrease more quickly than a sub-GHz signal. This leads to needing more power to keep the same transmit distance. Nonetheless, the 2.4 GHz frequency provides a higher data rate and allows more compact antenna sizes compared to 868MHz. However, the 2.4GHz band is often congested and subject to interference, which can negatively affect signal reliability and robustness. In cases where higher data rates are crucial and interference levels are manageable, 2.4GHz can be a better choice.

Moreover, reducing the transmission frequency can increase the transmission distance, but it also increases the antenna's size. Based on the relationship between wavelength and the speed of light ( $\lambda$ =c/f), a quarter-wavelength antenna at 868MHz, the antenna size is 8cm, compared to 3.2cm for 2.4GHz.

Depending on the application scenario, both antenna size and signal attenuation caused by high frequency must be considered. In this thesis, we adopt 868MHz as the carrier frequency. The 868MHz bands are authorized by European regulations for data transmission, making them suitable for license-free radio frequency communications, providing simple and effective solutions.

Table 2.1 summarizes the main characteristics of WUR based on our review of the literature, including type, technology, sensitivity, power consumption, frequency, modulation, latency, data rate, and addressability.

| Reference | Year | Туре        | Technology | Sensitivity     | Consumption | Frequency | Modulation | Latency    | Data rate        | Addressability |

|-----------|------|-------------|------------|-----------------|-------------|-----------|------------|------------|------------------|----------------|

| [5]       | 2005 | Passive     | Discrete   | -25dBm          | -           | 433MHz    | OOK        | 5ms        | -                | Yes            |

| [6]       | 2011 | Passive     | 180nm CMOS | -17dBm          | 2.64µW      | 900MHz    | ASK        | 100µs      | -                | -              |

| [7]       | 2014 | Passive     | 130nm CMOS | -33dBm          | -           | 868MHz    | OOK        | 30µs       | 100kbps          | No             |

| [8]       | 2015 | Passive     | 130nm CMOS | -53dBm          | 0.2µW       | 915 MHz   | OOK        | -          | 100kbps          | -              |

| [13]      | 2007 | Passive     | RFID       | -6.7dBm         | 0.9µW       | 915MHz    | -          | 2ms        | 140kbps          | No             |

| [14]      | 2014 | Passive     | RFID       | -80dBm          | -           | 915MHz    | ASK        | -          | _                | Yes            |

| [12]      | 2015 | Passive     | RFID       | -               | -           | 915MHz    | -          | 10ms       | -                | -              |

| [17]      | 2014 | Passive     | RFID       | -16dBm          | -           | 868MHz    | -          | 258ms      | -                | Yes            |

| [18]      | 2014 | Active      | Discrete   | -85dBm          | 1.2mW       | 2.4GHz    | OOK        | _          | 250kbps          | Yes            |

| [19]      | 2013 | Active      | 130nm CMOS | -80dBm          | 7μW         | 2.4GHz    | OOK        | 30ms       | 10kbps           | Yes            |

| [20]      | 2020 | Active      | 28nm CMOS  | -92.6dBm        | 495µW       | 2.4GHz    | OOK        | 128µs/64µs | 62.5kbps/250kbps | -              |

| [21]      | 2015 | Active      | 65nm CMOS  | -72dBm          | 42.5µW      | 160MHz    | OOK        | -          | 100kbps          | -              |

| [22]      | 2016 | Active      | CMOS       | -97dBm          | 40µW        | 28MHz     | PWM        | -          | 1.25kbps         | Yes            |

| [23]      | 2008 | Active      | 90nm CMOS  | -72dBm          | 52µW        | 2GHz      | OOK        | -          | 100kbps          | No             |

| [25]      | 2018 | Active      | 180nm CMOS | -69dBm          | 4.5nW       | 113.5MHz  | OOK        | -          | 300bps           | -              |

| [26]      | 2019 | Active      | 65nm CMOS  | -79dBm          | 420pW       | 434MHz    | OOK        | 10ms       | 100bps           | -              |

| [31]      | 2010 | Active      | RFID       | -               | 80µW        | 2.4GHz    | ASK        | 32µs       | 250kbps          | -              |

| [34]      | 2009 | Semi-active | Discrete   | -28dBm          | 819µW       | 868MHz    | OOK        | 23.7ms     | 1.724kbps        | Yes            |

| [33]      | 2016 | Semi-active | Discrete   | -55dBm          | 1.2µW       | 868MHz    | OOK        | 60µs       | 1kbps            | Yes            |

| [35]      | 2021 | Semi-active | Discrete   | -70dBm          | 1.9µW       | 868MHz    | OOK        | -          | -                | Yes            |

| [36]      | 2015 | Semi-active | Discrete   | -30dBm          | 13.41µW     | 868MHz    | OOK        | 80µs       | 200kbps          | Yes            |

| [37]      | 2017 | Semi-active | Discrete   | -28dBm          | 39µW        | 2.4GHz    | OOK        | 16.06ms    | 1kbps            | Yes            |

| [38]      | 2010 | Semi-active | AS393x     | -52dBm          | 7.8µW       | 868MHz    | OOK        | 13ms       | 250kbps          | Yes            |

| [39]      | 2020 | Semi-active | AS393x     | -50dBm          | 10.5µW      | 915MHz    | OOK        | -          | 250kbps          | Yes            |

| [40]      | 2013 | Semi-active | Discrete   | -45dBm          | 2.6µW       | 868MHz    | OOK        | -          | 1kbps            | Yes            |

| [41]      | 2009 | Semi-active | 120nm CMOS | -53dBm          | 12.5µW      | 2.4GHz    | OOK        | -          | 100kbps          | -              |

| [42]      | 2016 | Semi-active | 65 nm SOTB | -30 dBm         | 6.7nW       | 920MHz    | -          | -          | -                | No             |

| [43]      | 2019 | Semi-active | 130nm CMOS | -71dBm          | 7.4nW       | 433MHz    | OOK        | -          | 200bps           | Yes            |

| [44]      | 2019 | Semi-active | 130nm CMOS | -56.4dBm        | 220nW       | 550MHz    | OOK        | 100µs      | 400kbps          | -              |

| [45]      | 2022 | Semi-active | CMOS       | -63.2dBm        | 6.77µW      | 868MHz    | OOK        | -          | 0.5kbps          | Yes            |

| [46]      | 2007 | Semi-active | RFID       | -65dBm          | 2.8µW       | 300MHz    | OOK        | -          | -                | Yes            |

| [47]      | 2015 | Active      | 180nm CMOS | -62dBm          | 45µW        | 80 MHz    | FSK        | 102µs      | 312kbps          | -              |

| [48]      | 2014 | Active      | 65nm CMOS  | -87dBm          | 45.5µW      | 924.4MHz  | FSK        | -          | 50kbps           | Yes            |

| [49]      | 2015 | Active      | 65 nm CMOS | -36 dBm/-27 dBm | 120µW       | 2.4 GHz   | OOK/FSK    | -          | 150kbps/300kbps  | No             |

Table 2.1 Comparison of wake-up radios' characteristics in the literature

## II.3 Study of rectifier in semi-active wake-up radio

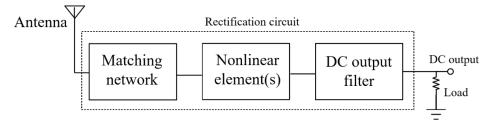

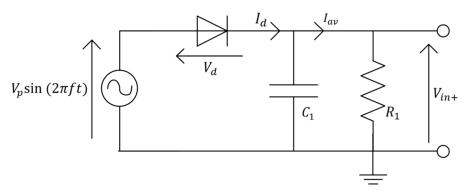

In the context of wake-up radio, the rectifier is an essential component because it allows the radio to convert the incoming electromagnetic waves into usable DC current. As we mentioned before, for the WUR operating at 868MHz and transmit power of +10dBm, the RF signal power received by the antenna is already -30dBm or less at a separation distance of 5m. A good rectifier is especially important for improving sensitivity of the wake-up radio. A general block diagram of a rectifier is shown in Figure 2.14:

Figure 2.14 A general block diagram of a rectifier

*Matching network:* The matching network should be optimized to match the impedance of the antenna to the rectifier, which helps to maximize the power transfer efficiency.

*Nonlinear elements:* They are used to rectify the AC signal to DC. The diode is the most commonly used and the key element in rectifier circuits. Since the peak voltage of the AC signal obtained from the antenna and matching network is very low, it is best to use a diode with the lowest possible bias voltage [50].

*DC output filter:* This is a low pass filter which most often consists of a parallel capacitance block. The role of this filter is to remove the fundamental and harmonic frequencies from the output.

### **II.3.1 Efficiency of rectifier**

The rectifier is the first stage of WUR and is responsible for rectifying the incoming RF signal to DC voltage. It must be capable of operating at low input voltage and providing an acceptable conversion efficiency at low power levels. RF-DC conversion efficiency can be optimal by using an efficient diode, choosing an appropriate topology, and allowing good impedance matching between the diode and the antenna. In this section, particular emphasis

will be put on the selection of the key element and the topology of rectifier.

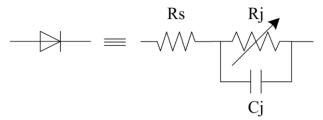

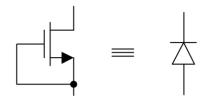

#### II.3.2 Key element of rectifier: Schottky diode

The diode can be one source of power losses, and its performance has a significant impact on the performance of rectifiers. Schottky diodes are commonly used in rectifiers for wake-up radio due to their low forward voltage drop, which leads to higher efficiency. Figure 2.15 shows the equivalent circuit:

Figure 2.15 Equivalent circuit of Schottky diode

$R_s$  is the series resistance, it limits the efficiency of diodes. Because the current flowing through the diode will dissipate the power in the semiconductor.

$R_j$  is the parasitic junction resistance of the diode, which reflects the ohmic loss of the diode and is a function of the total current flowing through the diode. It is expressed as a function of the bias current  $I_b$ :

$$R_j = \frac{8.33 \times 10^{-5} nT}{I_b + I_s} \tag{2.1}$$

Where I<sub>s</sub> is the saturation current, T is the temperature and n is the ideality factor.

The diode junction capacitance, denoted as  $C_j$ , is dependent on the bias voltage  $V_b$  and can be mathematically expressed using the following formula:

$$C_j = C_{j0} \times (1 - \frac{V_b}{V_j})^{-M}$$

(2.2)

where  $C_{j0}$  is the zero-bias junction capacitance of the diode.  $V_j$  is the amount of reverse bias potential applied on the device. M is the grading coefficient, which is a constant related to the geometry and material properties of the diode.

#### **II.3.3** Choice of Schottky diode

Three key parameters of the diode impact the RF-DC conversion efficiency [51]. The series

resistance ( $R_s$ ) limits the efficiency by means of dissipation losses, the zero-bias junction capacitance ( $C_{j0}$ ) affects the harmonic currents through the diode and the breakdown voltage ( $V_b$ ) limits the power handling capability of the rectifier. Generally, the reduction in  $C_{j0}$  will result in increasing of Rs and decreasing of  $V_b$ . We must make a good compromise between the parameters when designing a diode.

For low-power WUR applications, the received power is quite low, necessitating the selection of a diode with a low threshold voltage  $V_{th}$ . Table 2.2 presents three widely used commercial Schottky diodes. Among them, SMS7630 has the lowest  $V_{th}$ . Moreover, it has a low  $C_{j0}$  of only 0.14pF, which can have small harmonic currents through the diode to decrease the noise, making it suitable for high-frequency low-power applications. Thus, we choose the SMS7630 in our WUR application.

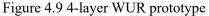

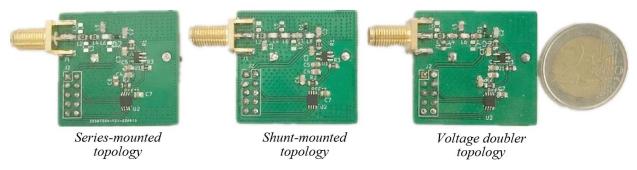

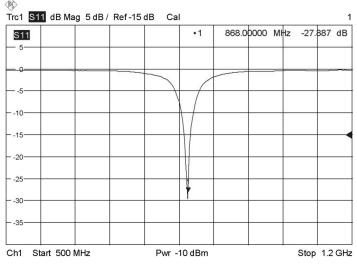

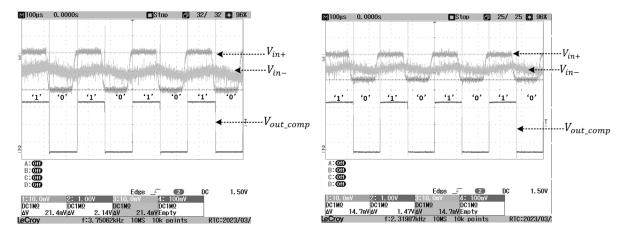

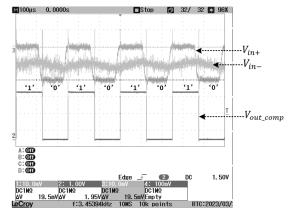

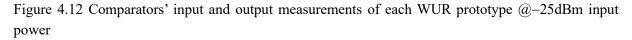

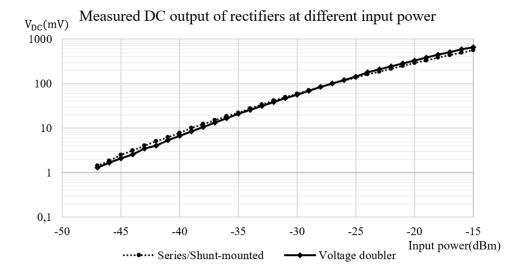

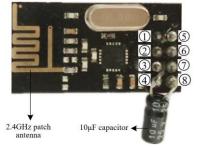

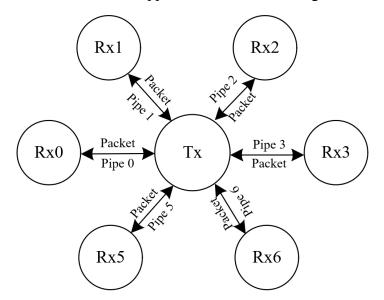

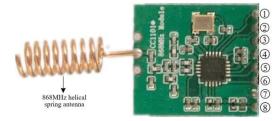

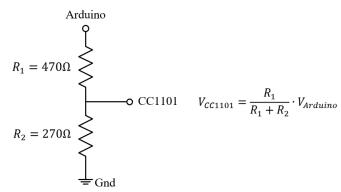

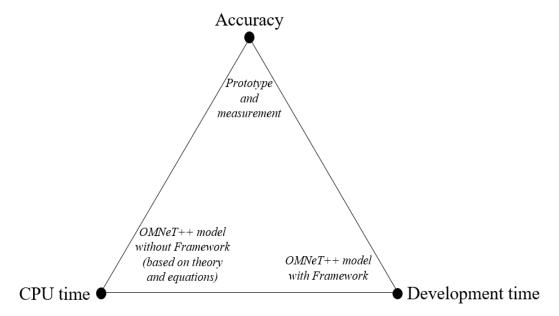

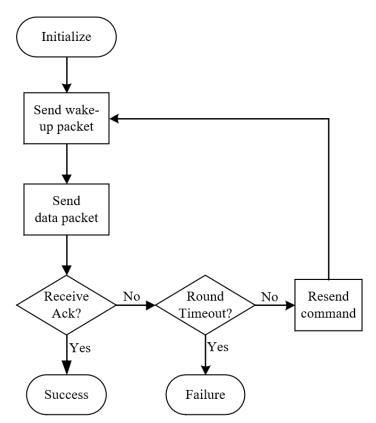

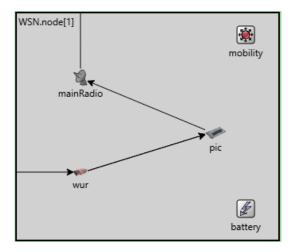

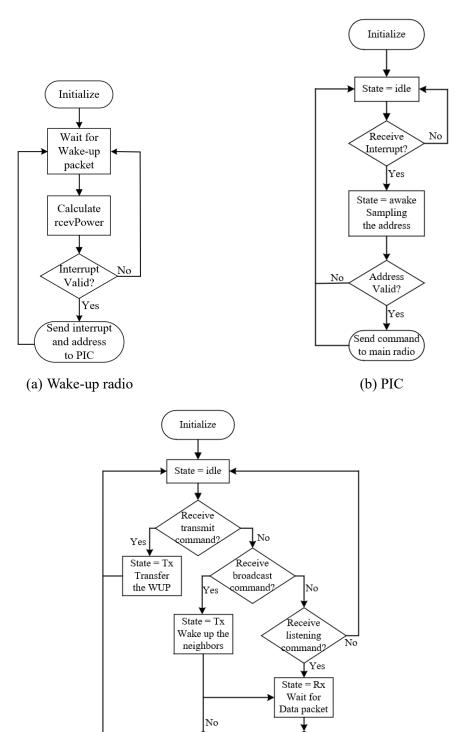

| Parameter         | Bat1503W | SMS7630 | HSMS2820 |