## Verified programming and secure integration of operating system libraries in Coq

Shenghao Yuan

## ▶ To cite this version:

Shenghao Yuan. Verified programming and secure integration of operating system libraries in Coq. Systems and Control [cs.SY]. Université de Rennes, 2023. English. NNT: 2023URENS060. tel-04405955

## HAL Id: tel-04405955 https://theses.hal.science/tel-04405955v1

Submitted on 19 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

## L'Université de Rennes

École Doctorale Nº 601 Mathématiques, Télécommunications, Informatique, Signal, Systèmes, Électronique

Spécialité : Informatique

Par

## **Shenghao Yuan**

Verified programming and secure integration of operating system libraries in Coq

Thèse présentée et soutenue à Rennes en salle Métivier, INRIA, le 8 décembre 2023 à 14h30

### Rapporteurs avant soutenance :

Yongwang ZHAO Professeur à l'Université de Zhejiang, Chine Gilles GRIMAUD Professeur des Universités à l'Université de Lille

**Composition du Jury:**

Présidente : Sandrine Blazy Professeur à l'Université de Rennes

Rapporteurs: Yongwang ZHAO Professeur à l'Université de Zhejiang, Chine

Gilles GRIMAUD Professeur des Universités à l'Université de Lille

Examinateurs : Emmanuel Bachelli Chargé de Recherce, INRIA Rennes

Frédéric Besson Chargé de Recherche, INRIA Rennes

Dir. de thèse : Jean-Pierre TALPIN Directeur de Recherche, INRIA Rennes

#### Abstract

The C programming language presents a dual nature, offering low-level control over memory and high efficiency, while also being prone to error, especially in terms of memory management. Legacy C code remains in operation in critical fields such as finance, transportation, digital networks, and the Internet of Things (IoT). Despite its advantages, the potential for vulnerabilities, such as buffer overflows and use-after-free errors, presents significant challenges.

Formal methods offer a rigorous approach by abstracting low-level code into high-level models and mathematically verifying expected properties. This manuscript explores the use of Interactive Theorem Proving (ITP) within the proof assistant Coq to ensure program correctness.

The first part of this manuscript proposes an end-to-end verification approach that minimizes the verification gap between Gallina implementation and extracted C code. This approach starts with a proof model written in Gallina and certifies the expected properties of the model in Coq. It then derives a verified executable C implementation from this proof model.

The manuscript then applies this end-to-end approach to a subsystem of the IoT operating system RIOT-OS: rBPF. rBPF is a virtual machine integrated into RIOT-OS for sandboxing untrusted extensions. The current rBPF system, consisting of a verifier and a defensive interpreter, faces challenges related to safety and performance.

The second part of the manuscript presents a fault-isolating virtual machine, CertrBPF. CertrBPF is a formally verified model and implementation of rBPF in Coq. CertrBPF formalizes the syntax and semantics of all rBPF instructions, implements a formal model of the rBPF interpreter, completes the proof of fault isolation, and extracts C code from this formalization.

The third part of the manuscript introduces a JIT compiler to dynamically generate ARM binary code from rBPF bytecode. This JIT compiler is designed to speed up computation tasks in rBPF programs while reusing the existing rBPF interpreter CertrBPF to execute security-sensitive branch and memory instructions, subject to complex run-time checking.

Finally, we integrate CertrBPF and the JIT compiler into RIOT-OS and evaluate their performance on a popular ARM microcontroller. The results show significant improvements in security, memory footprint, and execution time compared to the existing rBPF interpreter.

# RÉSUMÉ EN FRANÇAIS

Les fonctionnalités bas niveaux offertes par le langage de programmation C sont à la fois un atout et une source d'erreurs. D'une part, il a été conçu [KR02] pour offrir un contrôle très détaillé de la représentation des données au niveau octet en mémoire informatique. Cette fonctionnalité de bas niveau permet aux programmeurs de développer des artefacts hautement efficaces, économes en ressources, et faciles à lire par rapport au code d'assemblage au niveau machine. Par conséquent, des milliards de lignes de code C hérité sont toujours en service dans des domaines critiques (et non critiques), notamment la finance, les transports, les réseaux numériques et en particulier l'Internet des objets (IoT). D'autre part, le revers de la médaille est que l'utilisation du C facilite les erreurs de gestion de la mémoire de bas niveau, telles que le débordement de flottant, le dépassement de tableau, et l'utilisation après libération, etc. L'abstraction de bas niveau du code C accroît également les vulnérabilités dans des systèmes distribués complexes et parfois critiques, par exemple, en introduisant des erreurs logiques.

Il existe plusieurs façons de détecter les défauts logiciels. Une solution consiste à suivre un processus de développement logiciel strict et qualifiable pour mettre en œuvre des artefacts certifiés (e.g., SCADE KCG [Ber07]) qui satisfont aux exigences de certification (e.g., DO-178C [Rie17]) pour des domaines critiques spécifiques. Une autre approche consiste à concevoir un nouveau langage doté de fonctionnalités de sécurité spécifiques (e.g., Rust [MK14] pour garantir la sécurité de la mémoire). Bien que ces mesures soient capables de détecter certaines vulnérabilités, elles ne peuvent généralement pas garantir l'absence de vulnérabilités, en particulier pas de manière rigoureuse sur le plan mathématique.

Techniques formelles. Les méthodes formelles offrent des garanties plus solides d'absence de bogues en abstrayant les programmes de bas niveau en modèles de haut niveau, permettant ainsi de raisonner mathématiquement sur leurs propriétés attendues. Par exemple, la ligne de production de code Airbus combine plusieurs méthodes formelles : i) L'analyseur statique Astrée [Cou+05] prouve l'absence de certains types spécifiques de bogues dans les programmes C, par exemple, les dépassements de tableau. ii) L'outil d'analyse formelle Frama-C [Kir+15] garantit les propriétés fonctionnelles des programmes C. iii) Le com-

pilateur vérifié CompCert [Ler09] traduit les programmes C en code binaire.

Les méthodes formelles englobent diverses techniques, notamment l'interprétation abstraite, la vérification de modèles, et la démonstration de théorèmes (automatique ou interactive). Parmi toutes les méthodes de vérification formelle, la preuve interactive de théorèmes (ITP) est probablement la technique la plus complète et rigoureuse pour garantir de manière constructive la correction d'un programme par le raisonnement mathématique sur l'exécution du programme (sémantique du programme). En résumé, le processus ITP implique : i) Une description mathématique des comportements du programme définie par l'humain, c'est-à-dire une sémantique formelle. ii) Des preuves mathématiques fournies par l'humain (dans certains langages de tactiques) de propriétés cibles. iii) La vérification de la correction des preuves par la machine. Toutes ces étapes sont réalisées au sein d'un assistant de preuve. Les assistants de preuve courants incluent Coq [BC13], Isabelle/HOL [NWP02], et Lean [Mou+15], etc. Par exemple, le compilateur CompCert est formellement vérifié en utilisant l'assistant de preuve Coq : toutes les langues intermédiaires et transformations pertinentes sont spécifiées dans le langage fonctionnel Gallina [Hue92], intégré dans Coq, et toutes les preuves vérifiées par machine concernant le théorème de préservation du comportement sont exprimées à l'aide du langage de tactiques Ltac [Del00] au sein de Coq.

Approches de vérification de bout en bout. Nous nous concentrons sur la spécification et la vérification des logiciels IoT, qui sont généralement écrits en C. Il existe des méthodes qui vérifient directement du code C de bas niveau écrit à la main, telles que VCC [Coh+09], VeriFast [JP08], RefinedC [Sam+21], et VST [App+14]. En revanche, cette thèse considère une approche de vérification de bout en bout différente qui modélise abstraitement des spécifications de haut niveau dans le langage de programmation d'un assistant de preuve. Ce modèle abstrait élimine les détails spécifiques du code de bas niveau, permettant aux utilisateurs de tirer pleinement parti de la puissance de l'assistant de preuve pour vérifier les programmes.

Les approches de vérification de bout en bout nécessitent également un compilateur vérifié ou de confiance pour relier les modèles abstraits aux implémentations de bas niveau. Des compilateurs existants tels que CertiCoq (Coq) [Ana+17], Cogent (Isabelle/HOL) [Riz+16], KaRaMeL (F\*/Low\*) [Pro+17], et d'autres ont été développés, mais aucun d'entre eux ne peut simultanément remplir les exigences suivantes :

— compilation vérifiée pour garantir que les propriétés attendues des spécifications de

- haut niveau sont préservées dans les programmes de bas niveau;

- hautes performances du code C généré, par exemple, exempt de gestion automatique de la mémoire (collecte des déchets);

- une base de calcul de confiance minimale (Trusted Computing Base TCB).

L'objectif principal de cette thèse est de proposer une approche de vérification de bout en bout qui réponde à ces exigences. Nous appliquons cette approche pour vérifier un sous-système d'un système d'exploitation IoT du monde réel, RIOT-OS [Bac+18] : rBPF [ZB20].

rBPF. Dans de nombreux cas, les systèmes d'exploitation adoptent des techniques de confinement pour isoler les extensions non fiables dans le noyau. Pour ce faire, la communauté Linux a étendu les filtres Berkeley classiques [MJ93] (BPF) pour permettre l'exécution de code de machine virtuelle (VM) personnalisé en mode noyau. Cette VM est intégrée dans divers sous-systèmes, servant à des fins autres que le filtrage de paquets [Fle17]. L'extension de l'eBPF aux microcontrôleurs a conduit à la spécification du rBPF dans RIOT-OS.

Le rBPF actuel se compose d'un vérificateur compact et d'un interpréteur défensif sophistiqué, mais il est confronté à deux principaux défis :

- **Sécurité rBPF**: Tout comme le rôle de l'eBPF dans Linux, le rBPF fonctionne au sein du noyau sensible et critique de RIOT-OS. Étant donné qu'il fonctionne en mode noyau, le rBPF pourrait compromettre la sécurité et l'intégrité du système d'exploitation en exécutant du code non fiable de tiers. Le vérificateur rBPF pourrait ne pas parvenir à identifier des scripts malveillants ou erronés, et l'interpréteur pourrait ne pas être en mesure d'empêcher leur exécution. Cette menace est possible, compte tenu de plusieurs vulnérabilités de l'eBPF signalées à la communauté Linux à diverses occasions, telles que CVE-2023-0160 (défaut de blocage), CVE-2022-3646 (fuite de mémoire), CVE-2022-3623 (attaque par condition de concurrence), et plus encore.

- **Performances rBPF**: Le rBPF sacrifie les performances en adoptant un interpréteur défensif comme moteur d'exécution. Bien que ce choix garantisse que du code non fiable, erroné ou malveillant puisse s'exécuter dans un environnement ouvert ou potentiellement hostile, tout en isolant les erreurs pour protéger l'intégrité de l'hôte, il conduit naturellement à des performances plus faibles par rapport à une implémentation Just-In-Time (JIT) qui optimise la vitesse d'exécution du programme

en traduisant un bytecode générique à partir d'un script source en un ensemble d'instructions spécifiques à la machine. Cependant, l'intégration d'un compilateur JIT Linux traditionnel dans le rBPF est difficile en raison de la complexité des stratégies de défense du rBPF. L'incorporation d'un compilateur JIT pourrait également introduire de nouvelles erreurs potentiellement plus insidieuses au niveau binaire, rendant plus difficile la garantie de la propriété d'isolement.

Contenu de cette thèse. Développer une machine virtuelle isolante de pannes pour les microcontrôleurs (MCU) pose deux défis majeurs. Le premier est d'intégrer la VM au sein du micro-noyau du MCU et de réduire la taille de son code et de son environnement d'exécution. L'autre est de réduire l'écart de vérification entre son modèle de preuve et le code réel en cours d'exécution.

Dans cette thèse, nous relevons ces défis et présentons la première vérification de bout en bout et la synthèse d'une machine virtuelle complète du monde réel pour la famille d'ensembles d'instructions BPF : CertrBPF, un interprète adapté aux architectures de MCU fonctionnant sous RIOT-OS, avec des ressources limitées.

Cette thèse expose nos solutions pour le développement et la preuve de la correction de rBPF. Plus précisément, nous présentons les contributions suivantes :

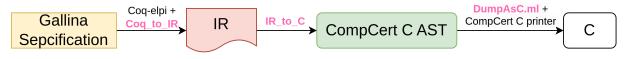

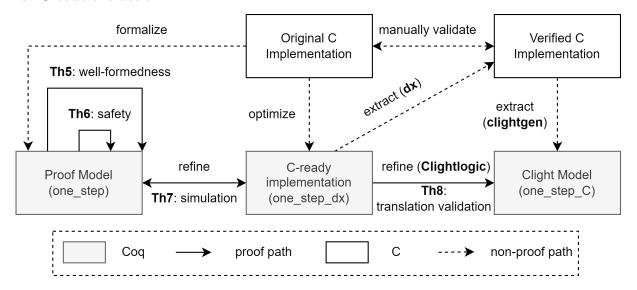

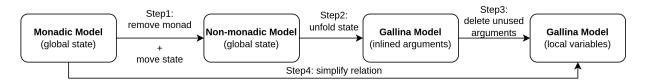

Approche de Vérification de Bout en Bout : Nous introduisons une approche de vérification de bout en bout pour réduire l'écart entre une implémentation Gallina vérifiée et son code C extrait non-vérifié. Notre point de départ est un modèle de preuve écrit en Gallina. Nous utilisons ce modèle de preuve pour certifier les propriétés attendues. À partir de ce modèle de preuve, nous dérivons ensuite un modèle de synthèse dont nous extrayons une version exécutable en Clight, que nous prouvons finalement pour effectuer les mêmes transitions d'état.

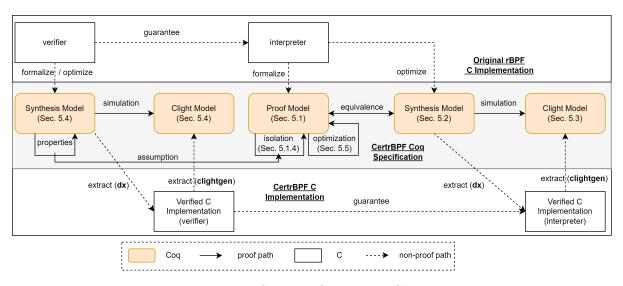

Interprète rBPF Certifié: CertrBPF est un modèle vérifié et une implémentation de rBPF en Coq. Nous formalisons la syntaxe et la sémantique de toutes les instructions rBPF, nous mettons en place un modèle formel de son interprète (femto-conteneur), nous achevons la preuve des propriétés critiques de notre modèle, et nous extrayons et vérifions le code CompCert C de cette formalisation. Notre approche de bout en bout obtient une machine virtuelle entièrement vérifiée. Non seulement la spécification Gallina de la VM est prouvée comme étant isolée du noyau et de la mémoire à l'aide de l'assistant de preuve Coq, mais l'interprétation directe de sa sémantique attendue sous forme de code CompCert C est elle-même vérifiée comme étant cor-

recte. Cela permet d'obtenir un programme binaire entièrement vérifié offrant une sécurité maximale et une empreinte mémoire minimale, et réduit la base de calcul de confiance (TCB) : CertrBPF, une machine virtuelle de niveau noyau efficace en mémoire qui isole les erreurs logicielles d'exécution à l'aide d'un code défensif et ne nécessite pas de vérification hors ligne.

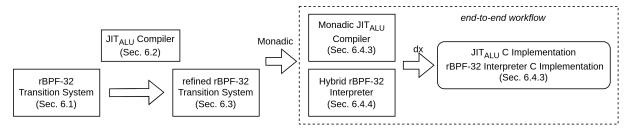

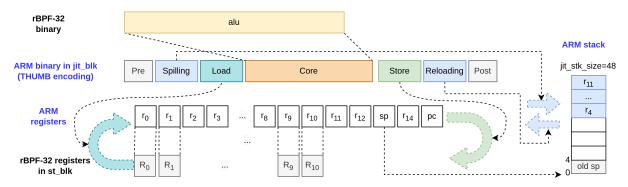

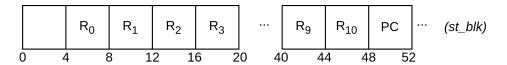

Compilateur JIT rBPF Certifié: Nous introduisons JIT<sub>ALU</sub>, une spécification basée sur Gallina d'un compilateur JIT qui génère dynamiquement du code binaire ARM à partir du bytecode rBPF. La compilation JIT accélère considérablement les tâches de calcul dans les programmes rBPF tout en réutilisant l'interprète rBPF CertrBPF existant pour exécuter les instructions de branches et de mémoire sensibles à la sécurité, soumises à une vérification complexe à l'exécution. L'implémentation exécutable en CompCert C de la spécification hybride VM+JIT, appelée HAVM, est directement obtenue à partir de sa spécification monadique en Gallina dans Coq. Nous fournissons également le code de liaison : une procédure jit\_call, qui construit un environnement ARM approprié à partir de la VM pour sauter directement à l'adresse du code jited. Son implémentation se compose de 5 lignes de code en langage d'assemblage écrites en C, et sa spécification est formellement définie dans Coq. En combinant jit\_call avec les implémentations C vérifiées de CertrBPF et JIT<sub>ALU</sub>, nous obtenons une implémentation prête à l'emploi de HAVM.

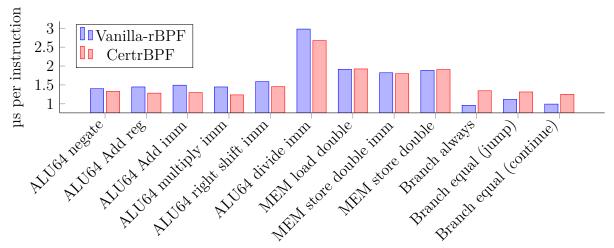

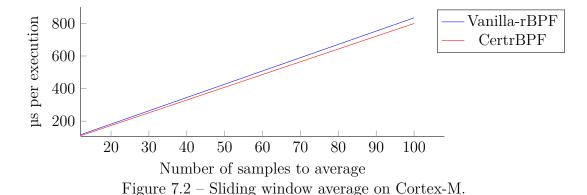

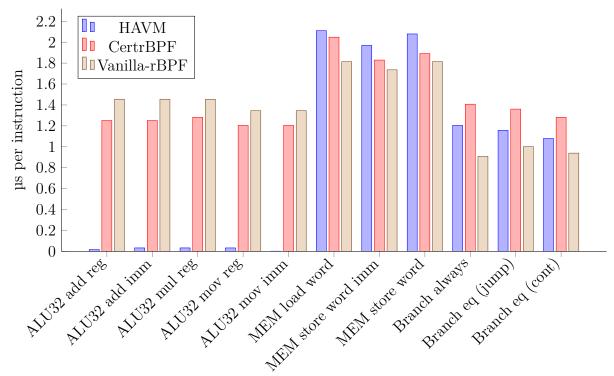

Intégration Sécurisée et Évaluations: Nous intégrons CertrBPF et HAVM en tant que remplacement direct de l'interprète rBPF non vérifié actuel dans RIOT-OS. Nous évaluons ensuite de manière comparative les performances de CertrBPF intégré dans RIOT-OS, fonctionnant sur diverses architectures de microcontrôleurs 32 bits. Nos évaluations montrent qu'en pratique, CertrBPF apporte non seulement une sécurité, mais réduit également l'empreinte mémoire ainsi que le temps d'exécution. Comme prévu, nous observons des accélérations significatives par rapport aux interprètes rBPF existants. Chapter 7 présente l'évaluation prometteuse des performances de notre HAVM par rapport à RIOT-OS CertrBPF et aux anciens micro-benchmarks Vanilla-VM sur une plateforme Cortex-M de développement.

## **ACKNOWLEDGEMENT**

I would like to extend my heartfelt gratitude to my advisors, Jean-Pierre Talpin and Frederic Besson, for affording me the remarkable opportunity to working on operating systems-related and compilers-related formal verification using Coq. I have learned and gained significant insights from our weekly meetings and occasional discussions.

I also wish to express my profound appreciation to my PhD jury. It is an honor to share my research topic with such esteemed experts. I am deeply thankful to my reviewers, Yongwang Zhao and Gilles Grimaud, for dedicating their valuable time to review this document and offering invaluable comments.

My sincere thanks go out to my collaborators: Emmanuel Bachelli and his RIOT operating system, Samuel Hym and his innovative dx tool, and Koen Zandberg for his work on the rBPF virtual machine. I am also indebted to my colleagues: Benjamin Lion, Lucas Franceschino, Jean-Joseph Marty, and Stéphane Kastenbaum, for their discussions and many help.

My time in Rennes has been enriched by the daily activities and sports I enjoyed with friends, including badminton, tennis, ping-pong, and running. Lastly, I offer profound gratitude to my family for their unwavering support throughout my PhD journey.

# **TABLE OF CONTENTS**

| Li | st of | Figure          | es                                                        | 15 |

|----|-------|-----------------|-----------------------------------------------------------|----|

| Li | st of | Tables          | 3                                                         | 17 |

| 1  | Intr  | oducti          | on                                                        | 19 |

|    | 1.1   | Motiva          | ation                                                     | 19 |

|    | 1.2   | Contri          | butions                                                   | 22 |

|    | 1.3   | Outlin          | e                                                         | 23 |

| 2  | Sta   | te of tl        | ne Art on End-to-End Verification Approaches and BPF Ver- | -  |

|    | ifica | ation           |                                                           | 25 |

|    | 2.1   | End-to          | o-End Verification Approaches                             | 26 |

|    | 2.2   | BPF v           | verification                                              | 30 |

|    |       | 2.2.1           | Conclusion                                                | 32 |

| 3  | Bac   | kgroui          | $\operatorname{ad}$                                       | 33 |

|    | 3.1   | Berkel          | ey Packet Filters (BPFs)                                  | 33 |

|    |       | 3.1.1           | cBPF vs eBPF                                              | 33 |

|    |       | 3.1.2           | RIOT-OS rBPF                                              | 36 |

|    | 3.2   | Comp            | Cert                                                      | 37 |

|    |       | 3.2.1           | CompCert Architecture                                     | 37 |

|    |       | 3.2.2           | CompCert Programs                                         |    |

|    |       | 3.2.3           | CompCert Memory Model                                     |    |

|    |       | 3.2.4           | CompCert Simulation Framework                             |    |

|    |       | 3.2.5           | CompCert Ecosystem                                        |    |

|    | 3.3   | $\partial x$ Co | $\begin{array}{cccccccccccccccccccccccccccccccccccc$      |    |

|    | 3.4   |                 | ision                                                     |    |

| 4  | An    | End-to          | o-End Verification Approach in Coq                        | 53 |

|    |       |                 | ssion: Which Way Do We Select                             | 53 |

## TABLE OF CONTENTS

|   | 4.2 | A Workflow for End-to-End Verification in Coq   |

|---|-----|-------------------------------------------------|

|   |     | 4.2.1 Proof-Oriented Specification              |

|   |     | 4.2.2 C-ready implementation                    |

|   |     | 4.2.3 Translation Validation of C code          |

|   |     | 4.2.4 Summary                                   |

|   | 4.3 | Applications                                    |

| 5 | Cer | trBPF: A fully Verified rBPF Virtual Machine 61 |

|   | 5.1 | A Proof-Oriented Virtual Machine Model          |

|   |     | 5.1.1 Syntax                                    |

|   |     | 5.1.2 Machine State                             |

|   |     | 5.1.3 rBPF Interpreter                          |

|   |     | 5.1.4 Proof of Isolation                        |

|   | 5.2 | A Synthesis-Oriented rBPF Interpreter           |

|   |     | 5.2.1 Synthesis Model                           |

|   |     | 5.2.2 C-ready Model                             |

|   | 5.3 | Simulation Proof of the C rBPF Virtual Machine  |

|   | 5.4 | CertrBPF Verifier                               |

|   | 5.5 | Optimization                                    |

|   |     | 5.5.1 check_mem Optimization                    |

|   |     | 5.5.2 Equivalence Proof                         |

|   | 5.6 | Conclusion                                      |

| 6 | Cer | etrBPF-JIT 97                                   |

|   | 6.1 | rBPF-32                                         |

|   | 6.2 | Just-In-Time Compilation                        |

|   |     | 6.2.1 Structure                                 |

|   |     | 6.2.2 Core Mapping                              |

|   |     | 6.2.3 Interaction                               |

|   | 6.3 | Refinement of rBPF-32: rBPF-32-JIT              |

|   |     | 6.3.1 Symbolic CompCert ARM                     |

|   |     | 6.3.2 Transition Semantics of rBPF-32-JIT       |

|   | 6.4 | Hybrid JIT Interpreter                          |

|   |     | 6.4.1 Overview                                  |

|   |     | 6.4.2 CompCert ARM Interpreter                  |

|   |     |                                                 |

|    |       | 6.4.3   | Monadic JIT Compiler                                 | . 116 |

|----|-------|---------|------------------------------------------------------|-------|

|    |       | 6.4.4   | Hybrid rBPF-32 Interpreter                           | . 117 |

|    |       | 6.4.5   | rBPF-32 C Implementation                             | . 118 |

|    | 6.5   | Discus  | ssion                                                | . 120 |

|    |       | 6.5.1   | Proof Overview                                       | . 120 |

|    |       | 6.5.2   | Defensive JIT <sub>ALU</sub>                         | . 122 |

| 7  | Eva   | luation | 1                                                    | 127   |

|    | 7.1   | Imple   | mentation                                            | . 127 |

|    |       | 7.1.1   | Coq Implementation                                   | . 127 |

|    |       | 7.1.2   | C Implementation                                     | . 128 |

|    | 7.2   | Exper   | ${ m iment}$                                         | . 129 |

|    |       | 7.2.1   | Experimental Evaluation Setup                        | . 129 |

|    |       | 7.2.2   | Benchmarks                                           | . 130 |

|    |       | 7.2.3   | Research Question: Memory Footprint                  | . 130 |

|    |       | 7.2.4   | Research Question: CertrBPF Interpreter Performance  | . 131 |

|    |       | 7.2.5   | Research Question: CertrBPF Interpreter Optimization | . 134 |

|    |       | 7.2.6   | Research Question: HAVM Optimization                 | . 134 |

| 8  | Con   | clusio  | $\mathbf{n}$                                         | 137   |

|    | 8.1   | Summ    | ary                                                  | . 137 |

|    | 8.2   | Perspe  | ectives                                              | . 138 |

|    |       | 8.2.1   | Short-term Perspectives                              | . 138 |

|    |       | 8.2.2   | Long-term Perspectives                               | . 139 |

| Bi | bliog | graphy  |                                                      | 141   |

# LIST OF FIGURES

| 2.1 | The $F^*/Low^*$ workflow                                                    | 26  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | The Cogent workflow                                                         | 27  |

| 2.3 | The CertiCoq workflow (solid arrow: verified, dashed arrow: proof underway) | 28  |

| 2.4 | The Œuf workflow                                                            | 29  |

| 2.5 | The JITK compilation                                                        | 31  |

| 2.6 | The Jitk compilation                                                        | 32  |

| 3.1 | Linux eBPF instruction encodings                                            | 34  |

| 3.2 | Linux eBPF Workflow                                                         | 36  |

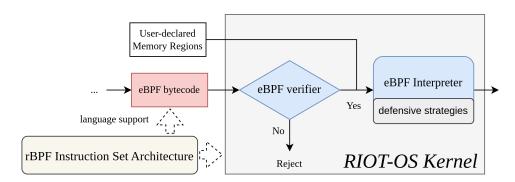

| 3.3 | RIOT-OS rBPF Structure                                                      | 37  |

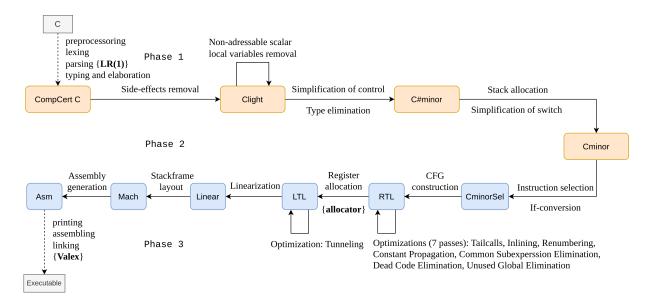

| 3.4 | CompCert Architecture                                                       | 38  |

| 3.5 | Syntax of CompCert Programs                                                 | 39  |

| 3.6 | CompCert Backward Simulation                                                | 43  |

| 3.7 | CompCert Forward Simulation                                                 | 44  |

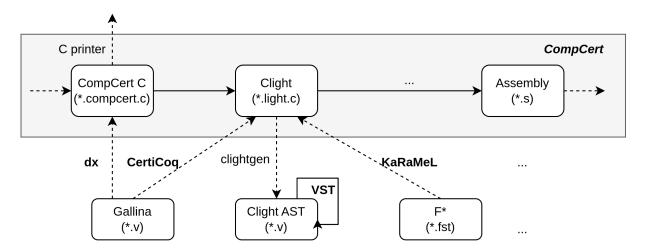

| 3.8 | CompCert tools and related projects                                         | 46  |

| 3.9 | $\partial x$ workflow                                                       | 47  |

| 4.1 | End-to-end verification and synthesis workflow                              | 54  |

| 5.1 | Chapter Structure: CertrBPF                                                 | 61  |

| 5.2 | Core syntax of rBPF instruction set                                         | 63  |

| 5.3 | Maps between (C) physical memory and (CompCert) memory model                | 65  |

| 5.4 | Simulation relation R between $st_{rbpf}$ , left, and rBPFClight, right     | 80  |

| 5.5 | Synthesis model: check_mem optimization                                     | 85  |

| 5.6 | Function tree of the optimized interpreter                                  | 89  |

| 5.7 | The simplification process                                                  | 90  |

| 6.1 | Chapter Structure: CertrBPF-JIT                                             | 97  |

| 6.2 | Syntax of rBPF-32 instruction set                                           | 99  |

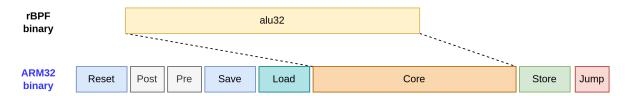

| 6.3 | JIT procedure: from rBPF-32 Alu32 binary to ARM binary                      | 102 |

## LIST OF FIGURES

| 6.4  | state block layout (The first 52 byte)                                  |

|------|-------------------------------------------------------------------------|

| 6.5  | HAVM Overview                                                           |

| 6.6  | Three cases of <i>entry point</i>                                       |

| 6.7  | JIT Proof Overview                                                      |

| 6.8  | JIT Simulation Diagrams                                                 |

| 6.9  | JIT defensive procedure                                                 |

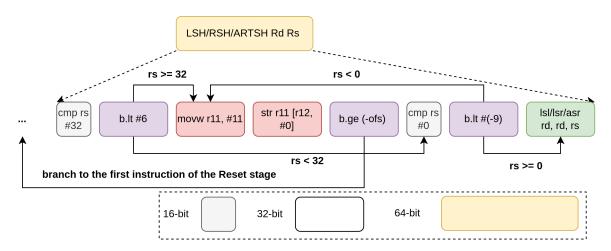

| 6.10 | JIT defensive procedure: shift instructions                             |

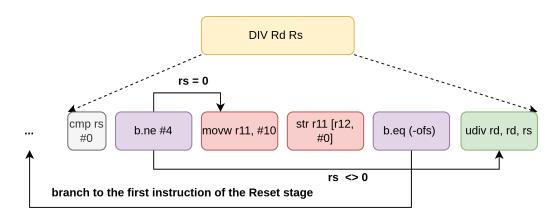

| 6.11 | JIT defensive procedure: $DIV$ instruction                              |

| 7.1  | Time per instructions on the Cortex-M4 platform                         |

| 7.2  | Sliding window average on Cortex-M                                      |

| 7.3  | Execution time per instruction, on an Arm Cortex-M4 microcontroller 135 |

# LIST OF TABLES

|     | eBPF instruction classes                                 |

|-----|----------------------------------------------------------|

| 5.1 | Mapping relation in the $\partial x$ -CompCert library   |

| 6.1 | Mapping relation from rBPF-32 Alu32 reg to ARM           |

| 6.2 | Mapping relation from rBPF-32 Alu32 imm to ARM           |

| 7.1 | Coq code statistics of CertrBPF                          |

| 7.2 | C code statistics of CertrBPF                            |

| 7.3 | Memory footprint of rBPF engines                         |

| 7.4 | Execution time of real-world benchmarks (64-bit)         |

| 7.5 | JIT compilation and execution time of alu32 instructions |

| 7.6 | Execution time of real-world benchmarks (32-bit)         |

## INTRODUCTION

## 1.1 Motivation

The C programming language both benefits from and is burdened by its low-level idioms and features. On the one hand, it was designed [KR02] to provide fine-grained control over byte-level data representation in computer memory. This low-level feature allows programmers to develop highly efficient, resource-frugal, and easily readable artifacts in comparison to machine-level assembly code. Consequently, there are billions of lines of legacy C code <sup>1</sup> still in operation across critical (and non-critical) fields, including finance, transportation, digital networks, and especially the Internet of Things (IoT). At the same time, the flip side of the coin is that using C is error-prone because it makes low-level memory management mistakes easy, for instance, float overflow, array out-of-bounds, and use-after-free, etc. The low-level abstraction of C code also increases the vulnerabilities in complex and sometimes critical distributed systems, e.g., logic errors.

There are several ways to detect defects in software. One solution is to follow a strict and qualifiable software development process (including testing) to implement certified artifacts (e.g., SCADE KCG<sup>2</sup> [Ber07]) that satisfy certification requirements (e.g., DO-178C [Rie17]) for specific critical fields. Another approach involves designing a new language with specific safety features (e.g., Rust [MK14] for ensuring memory safety). While these measures are capable of detecting certain vulnerabilities, they usually cannot guarantee the absence of vulnerabilities, especially not in a mathematically rigorous manner.

Formal Techniques. Formal methods provide stronger guarantees for the absence of bugs by abstracting low-level programs into high-level models, allowing their expected properties to be mathematically reasoned about. For instance, the Airbus code production

<sup>1.</sup> Slogan: Code becomes legacy as soon as it's written.

<sup>2.</sup> SCADE stands for Safety-Critical Development Environment, KCG stands for 'qualified code generator'

line combines several formal methods: i) The static analyzer Astrée [Cou+05] proves the absence of some specific types of bugs in C programs, e.g., array-out-of-bound. ii) The formal analysis tool Frama-C [Kir+15] guarantees the functional properties of C programs. iii) The verified CompCert [Ler09] compiler translates C programs into binary code.

Formal methods encompass various techniques, including abstract interpretation, model checking, and (automated or interactive) theorem proving. Among all formal verification methods, Interactive Theorem Proving (ITP) is arguably the most comprehensive and rigorous technique to constructively guarantee the correctness of a program through mathematical reasoning about program execution (program semantics). In essence, the ITP process involves: i) Human-defined mathematical description of program behaviors, i.e., formal semantics. ii) Human-provided mathematical proofs (in some tactic languages) of target properties. iii) Machine-checked correctness of proofs. All of these steps are performed within a proof assistant. Common proof assistants include Coq [BC13], Isabelle/HOL [NWP02], and Lean [Mou+15], etc. For instance, the CompCert compiler is formally verified using the Coq proof assistant: all relevant languages and transformations are specified in the functional language Gallina [Hue92], embedded in Coq, and all machine-checked proofs regarding the correctness theorem of behavior preservation are expressed using the tactic language Ltac [Del00] within Coq.

End-to-end Verification Approaches. We focus on the specification and verification of IoT software, which is typically written in C. There are methods that directly verify hand-written low-level C code, such as VCC [Coh+09], VeriFast [JP08], RefinedC [Sam+21], and VST [App+14]. In contrast, this thesis considers a different end-to-end verification approach that abstractly models high-level specifications in the programming language of a proof assistant. This abstract model eliminates specific details from low-level code, allowing users to harness the full power of the proof assistant to verify programs.

End-to-end verification approaches also necessitate a verified or trusted compiler to connect abstract models with low-level implementations. Existing compilers like CertiCoq (Coq) [Ana+17], Cogent (Isabelle/HOL) [Riz+16], KaRaMeL (F\*/Low\*) [Pro+17], and others have been developed, but none can simultaneously fulfill the following requirements:

- Verified compilation to ensure that the expected properties of high-level specifications are preserved in the low-level programs.

- High-performance generated C code, e.g., free of automatic memory management (garbage collection).

— A minimal trusted computing base (TCB).

The primary objective of this thesis is to propose an end-to-end verification approach that meets these requirements. We apply this approach to verify a subsystem of a real-world IoT operating system (OS), RIOT-OS [Bac+18]: rBPF [ZB20].

**rBPF.** In many cases, operating systems adopt sandboxing techniques to isolate untrusted extensions within the kernel. To achieve this, the Linux community extended the classical Berkeley Packet Filters [MJ93] (BPF) to enable the execution of custom in-kernel virtual machine (VM) code. This VM is integrated into various subsystems, serving purposes beyond packet filtering [Fle17]. The extension of eBPF to micro-controllers led to the specification of rBPF in RIOT-OS.

The current rBPF consists of a compact verifier and a sophisticated defensive interpreter, but it faces two main challenges:

- **rBPF Security**: Similar to eBPF's role in Linux, rBPF operates within the sensitive and critical RIOT-OS kernel. As it functions in-kernel, rBPF could potentially compromise the operating system's security by executing untrusted code from third parties. The rBPF verifier might fail to identify malicious or erroneous scripts, and the interpreter might be unable to prevent their execution. This threat is possible, considering multiple eBPF vulnerabilities reported to the Linux community on various occasions, such as CVE-2023-0160 (deadlock flaw), CVE-2022-3646 (memory leak), CVE-2022-3623 (race condition attack), and more.

- rBPF Performance: rBPF sacrifices performance by adopting a defensive interpreter as its execution engine. While this choice ensures that untrusted, erroneous, or adversarial code can run in an open or possibly hostile environment, while isolating faults to protect the host's integrity, it naturally leads to lower performance compared to a Just-In-Time (JIT) implementation that optimizes program execution speed by translating generic bytecode from a source script into the machine-specific instruction set. However, integrating a traditional Linux JIT compiler into rBPF is challenging due to the complexity of rBPF's defensive strategies. Incorporating a JIT compiler could also introduce new and potentially more insidious errors at the binary level, making it harder to ensure the isolation property.

## 1.2 Contributions

Developing a fault-isolating virtual machine for Microcontrollers (MCUs) poses two major challenges. One is to embed the VM within the MCU's micro-kernel and minimize its code size and execution environment. Another is to reduce the verification gap between its proof model and the actual running code.

In this thesis, we address these challenges by presenting the first end-to-end verification workflow, synthesizing a comprehensive real-world virtual machine for the BPF instruction set family: CertrBPF, and designing a JIT compiler to accelerate CertrBPF.

This thesis outlines our solutions for developing and proving the correctness of rBPF. Specifically, we present the following contributions:

End-to-end Verification Approach: We introduce an end-to-end verification approach to remove the gap between a verified Gallina implementation and its unverified extracted C code. Our starting point is a proof model written in Gallina. We use this proof model to certify expected properties. From this proof model, we then derive a synthesis model of which we extract an executable version in Clight, that we finally prove to perform the same state transitions.

Certified rBPF Interpreter: CertrBPF is a verified model and implementation of rBPF in Coq. We formalize the syntax and semantics of all rBPF instructions, implement a formal model of its interpreter (femto-container), complete the proof of critical properties of our model, and extract and verify CompCert C code from this formalization. Our end-to-end approach obtains a fully verified virtual machine. Not only is the Gallina specification of the VM proved kernel- and memory-isolated using the Coq proof assistant, but the direct interpretation of its intended semantics as CompCert C code is, itself, verified correct. This yields a fully verified binary program of maximum security and minimal memory footprint and reduced the TCB: CertrBPF, a memory-efficient kernel-level virtual machine that isolates runtime software faults using defensive code and does not necessitate offline verification.

Certified rBPF JIT Compiler: We introduce JIT<sub>ALU</sub>, a Gallina-based specification of a JIT compiler that dynamically generates ARM binary code from rBPF byte-code. This numerical accelerator significantly speeds up computation tasks in rBPF programs while reusing the existing rBPF interpreter CertrBPF to execute security-sensitive branch and memory instructions, subject to complex run-time checking. The executable CompCert C implementation of the hybrid VM+JIT specification,

named hybridly accelerated virtual machine (HAVM for short), is directly obtained from its monadic Gallina specification in Coq. We also provide the glue code: a jit\_call procedure, that builds a proper ARM environment from the VM to directly jump at the address of the jited code. Its implementation consists of 5 assembly code lines written in C and its specification is formally defined in Coq. By combining jit\_call with the verified C implementations of CertrBPF and JIT\_ALU, we obtain a readily executable implementation of HAVM.

Secure Integration and Benchmarks: We integrate CertrBPF and HAVM as a dropin replacement of the current, non-verified rBPF interpreter in RIOT-OS. We then

comparatively evaluate the performance of CertrBPF integrated in RIOT-OS, running on various 32-bit micro-controller architectures. Our benchmarks demonstrate

that, in practice, CertrBPF not just gains security, but reduces memory footprint as

well as execution time. As expected, we observe significant speedups compared to existing rBPF interpreters. Chapter 7 reports the promising performance evaluation of

our HAVM against RIOT-OS CertrBPF and earlier Vanilla-VM micro-benchmarks

on a development Cortex-M platform.

## 1.3 Outline

The main body of this thesis is structured as follows: Chapter 2 introduces the state of the art, including end-to-end verification and BPF verification. Chapter 3 presents the BPF family, CompCert, and the  $\partial x$  code extraction tool. Chapter 4 presents our end-to-end verification approach, which involves formally refining monadic Gallina programs into C programs. This methodology consists of a proof model with certified properties, a refined synthesis model with optimization, and a verified Clight model with behavior-equivalent proof. Chapter 5 defines CertrBPF, a verified model and implementation of the rBPF virtual machine in Coq. In particular, its proof model encompasses the semantics of our VM and isolation theorems, and the synthesis and implementation models are proven to satisfy the refinement relation, and a formally verified verifier establishes the invariants needed by the VM. In Chapter 6, we present JIT<sub>ALU</sub>, a JIT compiler dynamically translating rBPF ALU32 bytecode to ARM binary code. This numerical accelerator is designed to speed up computation tasks. We then detail our solution to integrate JIT<sub>ALU</sub> into CertrBPF to create a hybrid interpreter. In this design, ALU32 bytecode is compiled by JIT<sub>ALU</sub> and executed directly by the hardware, while the more complex bytecode

(defensive memory operations) is still interpreted by CertrBPF. Chapter 7 conducts a case study on the performance of our two generated VM implementations, CertrBPF and HAVM, in relation to off-the-shelf RIOT femto-containers. Chapter 8 concludes and presents avenues for future work.

The CertrBPF project is the main contribution of the work package 3 in the Inria challenge project RIOT-fp, which aims to provide formal proofs on RIOT-OS components. The source code associated with this thesis, and more broadly, with the entire CertrBPF project, is publicly available online in the project's GitLab repository [Cer23a; Cer23b]. We provide links to this online source code for several definitions and theorems in this thesis in the form of Coq logos .

# STATE OF THE ART ON END-TO-END VERIFICATION APPROACHES AND BPF VERIFICATION

Since Tony Hoare proposed the manifesto 'The Verified Software Initiative' that aims to construct error-free software systems, the successful verification of realistic software components has been established, especially for compilers and operating systems.

- In terms of compilers, the CompCert project [Ler09], led by Xavier Leroy, successfully verifies a C compiler that guarantees the compilation correctness from a large C99 subset (CompCert Clight) to various target assembly languages. Further details of CompCert are introduced in Section 3.2. Subsequently, many verified compilers are proposed: CakeML [MO12] implements a verified compilation from a subset of Standard ML to assembly, the Vellvm project [Zha+13] focuses on building a verified LLVM compiler, Vélus [Bou+17] is a verified compiler from the Lustre dataflow synchronous language [Cas+87] to CompCert Clight, and so on.

- In terms of verified OS kernels, the seL4 project [Kle+09] is the first to build a proof of functional correctness for a realistic microkernel, the proof is conducted over a high-level specification and then propagated down to a concrete implementation. Ironclad [Haw+14] establishes end-to-end security properties from the application layer down to kernel assembly. It uses the Dafny verifier [Lei10], built on the Z3 SMT solver [DB08], to help automate proofs. Other verified OS kernels are implemented for various purposes, e.g., CertiKOS with multicore support [Gu+16],  $\mu$ C/OS-II [Xu+16] for interrupt reasoning, Hyperkernel [Nel+17] with a high degree of proof automation, verified Zephyr RTOS [ZS19] with concurrent buddy memory allocation, and the Pip proto-kernel [Jom+18a; Jom+18b] for memory isolation on memory management unit (MMU).

In this chapter, we narrow our focus to two specific topics:

- End-to-end verification approach (X-to-C): This part belongs to the topic of compiler verification, it involves a proof-assistant-related language on one side and the C programming language on the other.

- BPF-related verification: This topic involves the verified OS components, and it covers the verification of the Linux eBPF verifier, interpreter, and JIT compiler.

## 2.1 End-to-End Verification Approaches

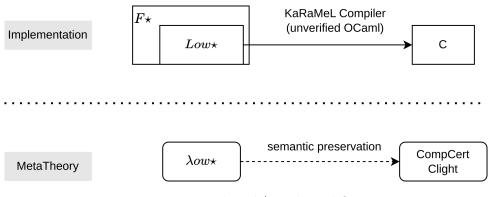

$F^*$  [Swa+13] is a proof-oriented functional language with effects and has been used to develop many high-assurance cryptographic algorithms, such as Chacha20, Poly1305, and SHA-3. For low-level code verification,  $F^*$  embeds a domain-specific language (DSL) called Low\* [Pro+17], which is a subset of  $F^*$ . Low\* includes a lower-level C-like memory model and libraries of C-style arrays and structs. As shown in Figure 2.1,  $F^*$  also offers a compiler from Low\* to C named KaRaMeL. While KaRaMeL has an on-paper semantics-preservation proof from the Low\* semantics model  $\lambda ow$  to CompCert Clight [BL09], its current implementation, written in the functional language OCaml, remains unverified.

Figure 2.1 – The F\*/Low\* workflow

#### Comparison.

— pros: The F\*/Low\* approach offers a higher level of automation compared to our methodology. KaRaMeL incorporates a built-in mapping relation from F\*/Low\* types to C types whereas our methodology additionally requires users to manually rename their synthesis model with  $\partial x$  type configurations.

— cons: The F\*/Low\* approach involves a larger TCB which includes the F\* type-checker, the Z3 SMT solver, and the KaRaMeL compiler. In contrast, our intended TCB is only limited solely to the Coq type-checker.

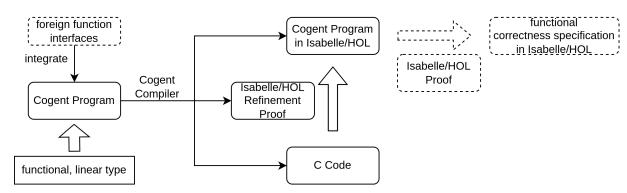

Another approach is Cogent [Riz+16], which aims to develop verified applications on top of the SeL4 [Kle+09] micro-kernel. Cogent, as depicted in Figure 2.2, consists of a functional language with linear types for specifying source programs and generates C code along with Isabelle/HOL proof information. Cogent lacks built-in recursion, and its iteration is expressed through integrated foreign function interfaces (FFI) that are verified by users. The Cogent compiler offers certifications to verify that the extracted C code refines a high-level Isabelle/HOL functional specification within the Isabelle/HOL proof assistant. Users can then prove that the Isabelle/HOL specification preserves the expected correctness properties.

Figure 2.2 – The Cogent workflow

## Comparison.

- pros: Cogent offers a higher degree of proof automation in contrast to our methodology. It provides a certifying compiler that ensures the simulation relation between the generated Isabelle/HOL model and extracted C code, In our approach, we use an unverified code generator, which needs an additional simulation proof from each input Gallina model to the output C implementation.

- cons: Our method is more direct than the co-specification approach (Cogent + Isabelle/HOL) in Cogent: We directly formalize specifications in Gallina that is embedded in Coq, then translate Gallina specifications into C code and performs the end-to-end verification in Coq.

When the scope is narrowed down to the topic of converting Gallina programs into executables, there are various techniques.

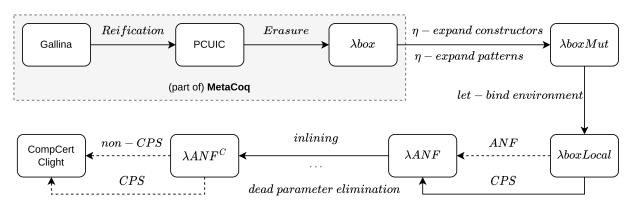

To begin with, Coq comes with a built-in extraction mechanism [Let02] that generates OCaml, Haskell, or Scheme. This path has a rather large TCB (Coq extraction and a compiler). CertiCoq [Ana+17] is an ongoing project aiming at generating CompCert C code from Gallina. This is achieved through several specific Intermediate Representations (IRs) and multiple transformation passes, as shown in Figure 2.3. The project's initial two passes, named reification, and erasure, are part of the MetaCoq project [Soz+20]. After the eta expansion of constructors and patterns, as well as the let-binding of environment, CertiCoq introduces two alternative transformations: the Administrative Normal Form (ANF) or the Continuation-Passing Style (CPS) to generate the  $\lambda_{ANF}$  intermediate representation. ANF and CPS are two common low-level functional intermediate representations. Importantly, the  $\lambda_{ANF}$  representation in CertiCoq is syntactically a superset of CPS, and this allows users to obtain a  $\lambda_{ANF}$  program by choosing either ANF or CPS conversion to  $\lambda_{ANF}$ . Then the  $\lambda_{ANF}$  is compiled to  $\lambda_{ANF}$  that is a subset of the ANF language without nested functions. The final step involves C code generation including two procedures: one for handling CPS code and another for the full  $\lambda_{ANFC}$  representation.

Figure 2.3 – The CertiCoq workflow (solid arrow: verified, dashed arrow: proof underway)

#### Comparison.

— pros: Similar to CakeML [MO12], CertiCoq performs a compilation from the full functional language Gallina to CompCert C, while our approach is limited to a subset of Gallina in monadic form. Once CertiCoq is completed, it will allow one to rely on a small TCB, akin to ours.

#### — cons:

Readability: CertiCoq often yields C code that is less readable compared to our approach, which produces C programs much more conducive to manual review. — Garbage Collection: As a generic functional language compiler, CertiCoq generates C code with an (verified) external garbage collector, which is usually unsuitable for real-time IoT operating systems, e.g., RIOT-OS. In contrast, our method is free of garbage collection.

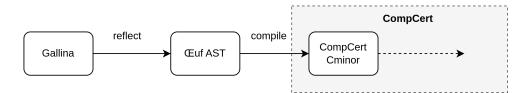

Œuf [Mul+18] is another tool for compiling Gallina to C. The first compilation step, as shown in Figure 2.4, involves reflecting Gallina terms into corresponding Abstract Syntax Trees (ASTs) within the Œuf source language. This Œuf language is a lambda-lifted simply typed lambda calculus over a particular set of base types. The reflection procedure does not require to be trusted, as it is verified using translation validation [PSS98]. Subsequently, The process translates Œuf ASTs into the CompCert Cminor IR, followed by the reuse the CompCert backend to obtain the target machine code.

#### Comparison.

- pros: Œuf enjoys a higher degree of proof automation compared to our methodology.

- cons: Similar to CertiCoq, the C code generated by Œuf also relies on an unverified garbage collector. This can often result in increased overhead or memory footprint, which are highly constrained resources in IoT devices.

Figure 2.4 – The Œuf workflow

Codegen [Tan21] converts Gallina to C with partial evaluation. It primarily focuses on eliminating polymorphism and dependent types from Gallina, transforming Gallina functions into a form that closely resembles C within the Gallina language, and subsequently extracting C code from it.

#### Comparison.

- pros: Codegen offers the ability to configure the representation of values. For example, it can safely replace natural numbers with finite-size integers.

- cons: The main limitation of Codegen is that its transformations are unverified.

Rupicola [Pit+22] presents an original and promising approach that regards a compiler as a partial decision procedure. It comprises a proof search procedure, which may either

fail or produce a target program in bedrock2 [Erb+21] (a C-like low-level language AST embedded in Coq) along with a proof of equivalence.

#### Comparison.

- pros: Rupicola offers a higher level of proof automation compared to our approach.

- cons: Currently, Rupicola has only been tested for small algorithms, while our methodology aims for end-to-end verification of complex real-world applications.

## 2.2 BPF verification

Several existing formal approaches have addressed the Linux eBPF verifier, including verification of the soundness of range analysis in the verifier [SH23; Vis+23], abstract interpretation (PREVAIL [Ger+19]), and symbolic evaluation (Serval [Nel+19]).

## Comparison.

- pros: All of the above approaches are designed for a sophisticated verifier, whereas our target, RIOT-OS rBPF, employs a tiny verifier.

- cons: None of these approaches can guarantee the termination of eBPF programs. In contrast, our scenario naturally guarantees termination, as rBPF introduces a default fuel mechanism for termination.

The JITK framework [Wan+14] uses Coq to implement and verify the correctness of a JIT compiler for the classic Berkeley Packet Filter language (not eBPF) in the Linux kernel. As depicted in Figure 2.5, JITK first introduces a high-level specification language called System Call Policy Language (SCPL) to specify the desired system call policies, It then implements a verified compiler for translating SCPL rules to BPF bytecode. Subsequently, JITK translates the BPF bytecode into the CompCert Cminor intermediate representation and leverages the CompCert backend to generate target code. The JITK compiler is extracted to OCaml implementation using the Coq extraction mechanism.

#### Comparison.

- pros: Jitk supports the specification of system call policies as BPF filters. In contrast, our CertrBPF only supports limited build-in RIOT-OS system calls as same as the vanilla rBPF.

- cons: JITK adopts the Coq extraction mechanism to translate their JIT into an executable OCaml implementation, which runs in the Linux user space and requires modifications to the kernel for upcalls. Additionally, the Coq extraction approach is

not suitable for RIOT-OS, a resource-limited IoT operating system, due to JITK's dependency on the OCaml runtime, an assembler, and a linker. Conversely, our method targets executable implementations written in CompCert C.

Figure 2.5 – The JITK compilation

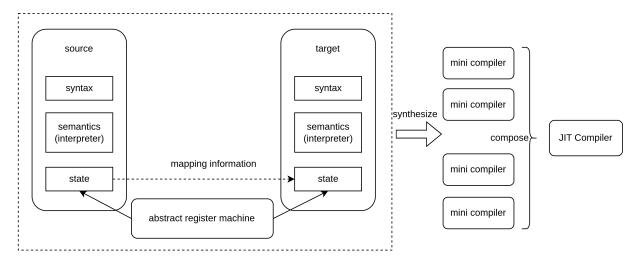

JITSYNTH [Gef+20] is a tool designed for synthesizing verified JITs for in-kernel DSLs. As shown in Figure 2.6, it takes input information, including the syntax, semantics, and abstract register machine state for both the source and target instruction set architectures (ISA). The semantics are expressed in the form of an interpreter, and the machine state contains a register map, a memory model, and a program counter. By establishing mapping relations from the source state to the target state, JITSYNTH synthesizes a *mini* compiler from every instruction in the source language to a sequence of instructions in the target language. These per-instruction compilers are then composed into a full compiler using a trusted outer loop and a switch statement. JITSYNTH has been applied to synthesize a JIT compiler from eBPF to RISC-V.

#### Comparison.

- pros: JITSYNTH offers a method for synthesizing verified JITs from interpreters, while our case study implements a verified rBPF interpreter and an unverified JIT compiler respectively.

- cons: Jitsynth exhibits a verification gap between their formal models and the low-level C implementation, as the final C artifact is manually written. We bridge this verification gap by leveraging our end-to-end verification approach in Coq to generate verified C implementations.

JITTERBUG [Nel+20] is a framework to write in-kernel JITs and prove them correct. This framework consists of three key components: i) formalizing the specification for JIT correctness, *i.e.*, the behavioral equivalence between the abstract machines of eBPF and target architectures, ii) proposing an automated proof strategy using symbolic evaluation to prove JIT correctness and iii) defining a C DSL for developing JITs, the DSL is a shallow embedding of a structured subset of C in Rosette [TB14], a solver-aided host

Figure 2.6 – The *Jitk* compilation

language. JITTERBUG has been used to implement and verify a new eBPF JIT for 32-bit RISC-V architectures.

#### Comparison.

- pros: JITTERBUG demonstrates a high degree of proof automation by using Rosette to formalize JITs specifications. While our approach requires more manual proof work.

- cons: Similar to Jitsynth, Jitterbug faces a verification gap, wherein the low-level C implementation is extracted through an unverified extraction mechanism. In contract, Our intended goals are verified C programs.

## 2.2.1 Conclusion

The verification of realistic compilers and operating systems have been the subjects of vast development and verification efforts due to the sheer code size of the artifacts at stake. These full-scale case studies gave rise to new strategies and methodologies to address the challenge of verifying large-scale software. This chapter introduces the related work about the end-to-end verification approach and BPF verification, and shows the comparison between each related research and our methodology.

## **BACKGROUND**

In this chapter, we introduce essential concepts necessary for our refinement methodology along with a verified rBPF implementation. We begin by focusing on BPF and its variants, with particular attention to Linux eBPF and RIOT-OS rBPF. Following that, we provide an overview of the formally verified CompCert C Compiler, including its intermediate languages, memory model, and the simulation framework. Finally, we discuss the key features of the  $\partial x$  code generation tool, which offers automatic but unverified extraction from monadic Gallina specifications to executable C code.

## 3.1 Berkeley Packet Filters (BPFs)

## 3.1.1 cBPF vs eBPF

Originally, Berkeley Packet Filters (BPF) [MJ93] was designed to provide Unix-BSD systems with network packets filtering capabilities and tools such as tcpdump. This classical BPF, also known as cBPF, takes the form of an assembly language that defines a virtual RISC-like ISA in which succinct and cautiously written scripts can be executed to parameterize privileged, mission-critical, network stacks. cBPF is highly restrictive and limited, featuring only two registers and bytecode interpretation. This restrictiveness becomes an obstacle for emerging scenarios that require rich functionality and low overhead.

For machines like PCs, servers, and routers, the Linux community extended the concept of cBPF to provide ways to run custom in-kernel virtualized (VM) code, hooked as "plugins" to various services and for varieties of purposes beyond packet filtering [Fle17]. This expanded version of BPF, known as eBPF or Linux eBPF, includes:

- *ISA*: Derived from the 64-bit RISC-V family, it offers 10 general-purpose registers as well as a read-only frame pointer register.

- *verifier*: This component statically analyzes eBPF binary instructions, rejecting all potentially unsafe programs. The C implementation spans over 10 thousands of lines

- of code (KLOC).

- interpreter: It executes eBPF binary instruction one by one.

- just-in-time (JIT) compiler: This module translates eBPF binary into various 64/32-bit architectures, such as x86, ARM, and RISC-V.

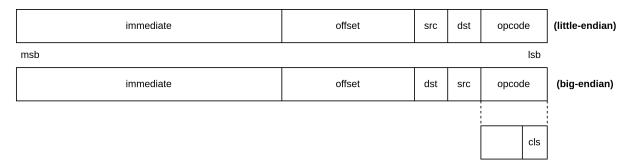

**eBPF ISA encoding.** The eBPF ISA has two instruction encodings: little-endian encoding and big-endian encoding, as shown in Figure 3.1.

Figure 3.1 – Linux eBPF instruction encodings

A 64-bit eBPF instruction, from least significant bit (lsb) to most significant bit (msb), consists of the following fields:

- 8-bit opcode

- 4-bit destination register and 4-bit source register (their locations are target-dependent)

- 16-bit signed integer offset

- 32-bit signed integer immediate value

Most instructions do not use all of these fields, so eBPF specifies that unused fields should be all-zero. Details of eBPF instruction encodings can be found in the eBPF Instruction Set Specification.

eBPF uses the three least significant bits of the opcode to define instruction classes ('cls'), as shown in Table 3.1. The instruction class includes memory load ('0x00' and '0x01'), memory store ('0x02' and '0x03'), 32-bit and 64-bit arithmetic instruction ('0x04' and '0x07'), and branch ('0x05' and '0x06').

Consider the 64-bit arithmetic instruction class (ie '0x07') shown in Table 3.2, both opcodes '0xX7' and '0xXf' (X representing an arbitrary hexadecimal number) are in this class. eBPF specifies such as '0x07' representing the 64-bit addition with immediate value instruction, '0x0f' denoting the 64-bit addition with source register instruction, and '0x17'

Table 3.1 – eBPF instruction classes

| Class                                                            | Value                                        | Description                                                                                                                                                                   |

|------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPF_LD<br>BPF_LDX<br>BPF_ST<br>BPF_STX<br>BPF_ALU32<br>BPF_JMP64 | 0x00<br>0x01<br>0x02<br>0x03<br>0x04<br>0x05 | non-standard load operations load into register operations store from immediate operations store from register operations 32-bit arithmetic operations 64-bit jump operations |

| BPF_JMP32<br>BPF_ALU64                                           | 0x06 $0x06$ $0x07$                           | 32-bit jump operations 64-bit arithmetic operations                                                                                                                           |

for the 64-bit subtract with immediate value instruction, etc. For example, assuming a little-end target, the 64-bit binary '0x000000000000050f' corresponds to 'BPF\_ADD64 R5 R2' which means adding the value of destination register R5 to the value of source register R2 and updating R5 with the result.

Table 3.2 – eBPF ALU64 instructions

| Instructions                        |                      |                      | Opcode | Description                                                                              |

|-------------------------------------|----------------------|----------------------|--------|------------------------------------------------------------------------------------------|

| BPF_ADD64<br>BPF_ADD64<br>BPF_SUB64 | $\operatorname{dst}$ | $\operatorname{src}$ | 0x0f   | addition with immediate value<br>addition with register<br>subtract with immediate value |

|                                     |                      |                      |        | • • •                                                                                    |

eBPF verifier. The eBPF validation process involves static analysis of eBPF bytecode before execution. It establishes two key properties for eBPF bytecode: memory safety and termination. For memory safety, the eBPF verifier ensures that the program only accesses memory locations within its allocated regions. To validate eBPF program termination, the verifier explores all reachable execution paths to ensure they safely terminate without errors. The eBPF verifier rejects programs beyond a finite complexity threshold of one million instructions.

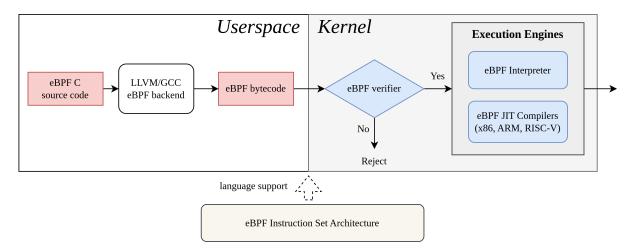

**eBPF** workflow. While the Linux kernel expects eBPF programs to be loaded in the form of bytecode, application developers often prefer to write these programs in a high-level abstraction, *e.g.*, pseudo-C code. Then, these programs are translated into bytecode

Figure 3.2 – Linux eBPF Workflow

using compiler suites like LLVM or GCC. As shown in Figure 3.2, if the eBPF verifier validates the provided bytecode scripts, the selected eBPF execution engine runs them.

Linux eBPF has broad extensions for specific purposes, For instance, a userspace eBPF (uBPF) enables the execution of eBPF programs on non-Linux systems, and Microsoft's ebpf-for-windows builds on uBPF and the PREVAIL formal verifier.

#### 3.1.2 RIOT-OS rBPF

eBPF was then ported to micro-controllers, resulting in the RIOT-OS rBPF specification. Just like eBPF, rBPF is designed as a 64-bit register-based VM, using fixed-size 64-bit instructions and a reduced instruction set architecture derived from eBPF. rBPF also employs a fixed-size stack (512 bytes) and excludes any heap interaction, thereby minimizing VM memory overhead in RAM.

rBPF comprises two key components: a compact verifier (less than 0.1 KLOC) for basic validation, e.g., excluding illegal opcodes, and a defensive interpreter for execution.

The primary distinction between rBPF and eBPF is that rBPF adopts dynamic runtime checking to implement its fault-isolated, defensive strategies, while eBPF employs static analysis techniques via an offline, sophisticated verifier. Users of rBPF must declare all memory regions accessed by their programs, specifying fine-grained permissions for each region. The memory region declaration is defined as a C linear structure, encompassing details like start address pointer, size, and permission type.

```

const uint8_t *start; // starting address of current region

size_t len; // offset

uint8_t flag; // permission type

};

```

The workflow of rBPF mirrors that of eBPF, as shown in Figure 3.3. The main difference is that rBPF only leverages an interpreter to execute the bytecode script.

Figure 3.3 – RIOT-OS rBPF Structure

# 3.2 CompCert

CompCert [Ler09] is a C compiler that has been both programmed and proved correct using the Coq proof assistant. It compiles C programs into assembly programs that support mainstream target architectures (32 or 64-bits), including x86, ARM, and RISC-V. CompCert follows a *software-proof* codesign approach where development is carried out directly in Coq alongside its proof. It uses Coq's extraction facility to generate executable OCaml code capable of compiling C programs.

This section mainly describes the architecture, programs, memory model, and simulation theorem of the CompCert compiler, which are essential for our work.

# 3.2.1 CompCert Architecture

As depicted in Figure 3.4, the CompCert C compiler is structured as a pipeline of 20 compilation passes that bridge the gap between source C code and target object files. It traverses 11 intermediate languages (IRs) in the process. The passes can be grouped into three successive phases:

Figure 3.4 – CompCert Architecture

First, CompCert converts a C program into a precise, unambiguous CompCert C AST. The phase comprises preprocessing, lexing, parsing, type-checking, etc. Only the LR(1) parser is formally verified [JPL12].

The second phase is the most significant part of CompCert: a fully verified compilation process that transforms CompCert C AST into assembly ASTs. The front-end <sup>1</sup> translates a CompCert C AST into a Cminor AST, which is the lowest-level language still processor independent in the CompCert compilation chain. The back-end performs code transformation into a standard compiler IR, *i.e.*, register transfer language (RTL), performs optimizing passes, allocates registers by an external allocator written in OCaml, and finally obtains assembly code with various target architectures.

The last part consists of assembling and linking, executed by an external assembler and linker. While CompCert doesn't provide formal guarantees for this phase, the Valex tool from AbsInt uses translation validation to recheck the ELF executable files generated by the linker against the CompCert back-end assembly ASTs.

## 3.2.2 CompCert Programs

The syntax of programs in the all CompCert languages shares a common structure, shown in Figure 3.5.

<sup>1.</sup> The original paper of CompCert front-end[BDL06] starts from Clight, the version presented here simplifies our presentation.

```

Programs:

P ::= \{ \text{ global\_defs} = id_0 = Gd_0; \dots; id_n = Gd_n; \text{ global definitions} \}

\mathtt{pub\_names} = id_0; id_1; \dots; id_n;

public names

main = id }

entry point

Global definitions:

Gd

::= Gv \mid Fd

Definitions of global variables:

Gv ::= \{ global\_info = v; \}

(language-dependent)

global\_init = data; \ldots \}

initialization data,...

Function definitions:

::= internal(F) | external(Fe)

Definitions of internal functions:

::= \{ sig = sig; body = \ldots; \ldots \}

(language-dependent)

Definitions of external functions:

Fe ::= \{ name = str; sig = sig \}

Function signatures:

sig ::= \{ \overrightarrow{args} = \overrightarrow{ty};

list of arguments type

res(ty \mid void);

return type

cc }

calling convention

Types:

integers and pointers

ty

::=

int

float

floating-point numbers

```

Figure 3.5 – Syntax of CompCert Programs

A program consists of

- global\_defs: a list of global definitions, either global variables Gv with their initialization data or functions Fd;

- pub\_names: a collection of public names that are visible outside of the program;

- main: the name of the main function that constitutes the program entry point.

CompCert supports two kinds of function definitions. Internal functions F are defined within the given language, and include at least i) a signature specifying the number and types of arguments and results, along with the additional information on which calling convention to use; ii) a body defining the computation task, e.g., statements in C and instructions in assembly.

External functions Fe are defined outside the program, such as systems calls or compiler built-in functions, and are declared with an external name with string type (str) and a signature. The observable behavior of the program is defined in terms of a trace of invocations of external functions.

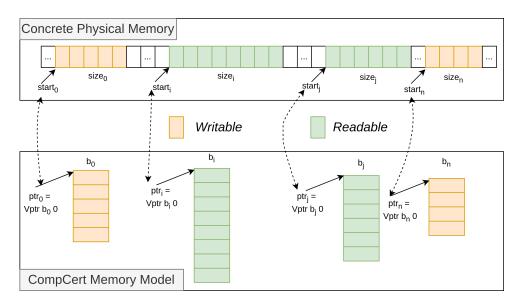

### 3.2.3 CompCert Memory Model

The memory model [LB08; Ler+12] and the representation of values are shared across all intermediate languages in CompCert. The set of values val is defined as follows:

$$val \ni v ::= Vint(i) \mid Vlong(i) \mid Vptr(b, o) \mid Vundef \mid \dots$$

A value  $v \in \text{val}$  can be a 32-bit integer Vint(i); a 64-bit integer Vlong(i), a pointer Vptr(b,o) composed of a block identifier b and an offset o, or the undefined value Vundef. The undefined value Vundef represents an unspecified value and is not, strictly speaking, an undefined behavior. Yet, as most of the C operators are strict in Vundef, and because branching over Vundef or de-referencing Vundef are undefined behaviors. CompCert values also include floating-point numbers; they play no role in our development.

CompCert's memory consists of a collection of separate arrays, each with a fixed size determined at allocation time and identified by an uninterpreted block  $b \in block$ . The memory provides an API for basic operations:

— alloc(M, lo, hi) = (b, M'): Allocate a fresh block with bounds [lo, hi), initially containing undefined cells. Return its identifies b and the updated memory M'.

- $load(k, M, b, ofs) = \lfloor v \rfloor$ : Read the value v of memory chunk k from memory M, at block b, starting at index ofs.

- $store(k, M, b, ofs, v) = \lfloor M' \rfloor$ : Store value v in memory chunk k of block b at offset ofs. Return the updated memory M'.

- $free(M, b, lo, hi) = \lfloor M' \rfloor$ : Free the block b within the given bounds. Returns the updated memory M' where the interval [lo, hi) of block b has been invalidated: not allowed to read or write anymore.

The memory chunk k involved in load and store specifies the number of bytes to be written or read and how to interpret bytes as a value  $v \in val$ . For instance, Mint32 specifies a 32-bit value. The alloc operation never fails because CompCert assumes an infinite memory. load and store may fail when given an invalid block b, an out-of-bounds offset ofs, or invalid permissions, free may also fail because it requires freeable permission on the given range. Therefore, those operations return option types, with  $\lfloor v \rfloor$  (i.e., Some v), denoting success with result v, and  $\emptyset$  (i.e., None) denoting failure.

#### 3.2.4 CompCert Simulation Framework

CompCert is organized into passes that utilize several intermediate languages, as illustrated in Figure 3.4. Each intermediate language is equipped with a formal semantics and each pass is rigorously proved to preserve the observational behavior of programs. For each pass, CompCert employs one of two verification approaches:

- Direct proof of correctness.

- Validation a posteriori (*i.e.*, translation validation) with proof of the validator's correctness.

In this section, we primarily focus on the first approach, which is adopted by most CompCert passes. The translation validation technique is specifically applied in the transformation from RTL to LTL due to the ease of proving the validator's correctness. For detailed information on the proof, we refer the interested reader to [RL10].

**Transition Semantics.** The operational semantics for all CompCert languages are defined as label transition systems. The transition relation, denoted as  $G \vdash S \xrightarrow{t} S'$ , represents a single execution step from state S to state S' within the global environment G. Each step is associated with a trace t of observable external I/O events (e.g., a system

call) or an internal event  $\epsilon$ . CompCert also defines transitive closures star  $\to^*$  (zero, one or many steps) and plus  $\to^+$  (one or many steps) from the one step  $\to$ . Additionally, each CompCert language defines two special predicates initial\_state and final\_state to represent when the execution of a program in the language starts and stops.

- initial\_state(P, S): Signifies that state S is an initial state for program P, typically corresponding to the invocation of the main function of P.

- final\_state(S, n): Indicates that S is a final state with an exit code n, implying that the program is returning from the initial invocation of its main function, producing value Vint(n).

Generic Simulation Diagrams. CompCert uses a *simulation* approach to prove that each pass preserves the semantics between source and target languages. Two types of simulations are used in CompCert: forward simulation and backward simulation. Intuitively, a forward simulation asserts that every step in the source language corresponds to a set of steps in the target language, while a backward simulation states that each step in the target language corresponds to a set of steps in the source language.

Consider two languages,  $L_1$  and  $L_2$ , defined by their transition semantics. Let  $P_1$  be a source program in  $L_1$ , and  $P_2$  be the translated target program in  $L_2$ . We construct a relation  $S \sim T$  between states of  $L_1$  and states of  $L_2$  and demonstrate that it constitutes either a forward or a backward simulation. To begin, we ensure that initial states and final states are related by  $\sim$  as follows:

- Initial states: if initial\_state( $P_1, S$ ) and initial\_state( $P_2, T$ ), then  $S \sim T$

- Final states:

- (forward): if  $S \sim T$  and final\_state(S, n), then final\_state(T, n)).

- (backward): if  $S \sim T$  and final\_state(T, n), then final\_state(S, n)).

Furthermore, assuming  $S \sim T$ , we relate transitions starting from S in  $L_1$  with transitions starting from T in  $L_2$ .

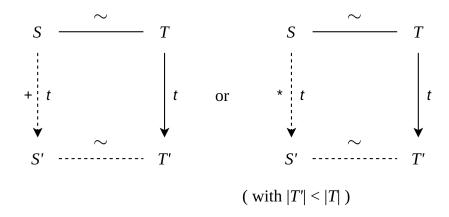

The standard technique is to prove that  $\sim$  is a backward simulation, as shown in Figure 3.6. A backward simulation assumes that S from the source program  $P_1$  and T from the target program  $P_2$  preserve the simulation relation  $\sim$ , if the target  $P_2$  performs one transition and results in the updated state T', then there exists a new state S' obtained by corresponding many transitions (star or plus) of the source  $P_1$  such that either the updated states S' and T' still preserve the same relation, or the measure |T'| is less than the measure

|T| in a well-founded ordering <sup>2</sup> and S' and T' preserve  $\sim$ . The backward simulation also requires the observable events align between the source transition and the corresponding target transitions.  $G_1$  and  $G_2$  represent the global environments corresponding to  $P_1$  and  $P_2$ , respectively. The measure strictly decreases to rule out the infinite stuttering case.

Theorem 1 (Backward Simulation).

$$\forall S \ T \ T', \ S \sim T \ \land \ G_2 \vdash T \xrightarrow{t} T' \Rightarrow$$

$$\exists S', \ (G_1 \vdash S \xrightarrow{t}^+ S' \ \land \ S' \sim T') \ \lor \ (|T'| < |T| \ \land \ G_1 \vdash S \xrightarrow{t}^* S' \ \land \ S' \sim T')$$

Figure 3.6 – CompCert Backward Simulation

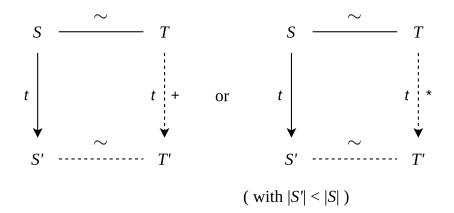

An alternative to backward simulation is forward simulation, where every step in the source language is matched with a number of steps in the target language.

**Theorem 2** (Forward Simulation).

$$\forall S \ T \ S', \ S \sim T \ \land \ G_1 \vdash S \xrightarrow{t} S' \Rightarrow$$

$$\exists \ T', \ (G_2 \vdash T \xrightarrow{t}^+ T' \ \land \ S' \sim T') \ \lor \ (|S'| < |S| \ \land \ G_2 \vdash T \xrightarrow{t}^* T' \ \land \ S' \sim T')$$

CompCert also proves a crucial theorem that a forward simulation implies a backward simulation when the source language  $L_1$  is receptive and the target language  $L_2$  is determinate.

<sup>2.</sup> there are no infinite decreasing chains

Figure 3.7 – CompCert Forward Simulation

**Theorem 3** (Forward to Backward).

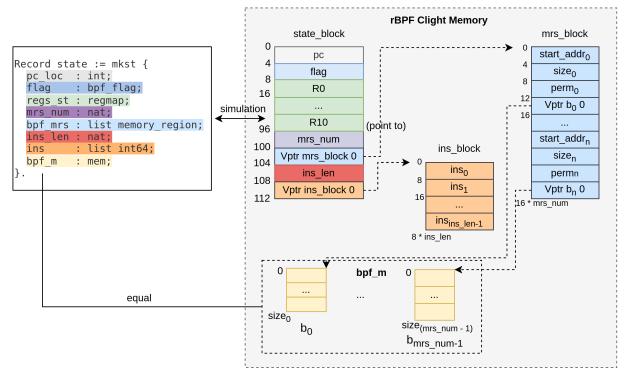

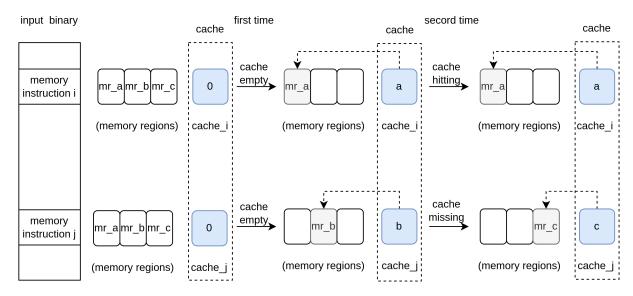

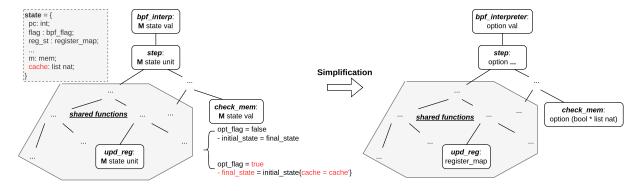

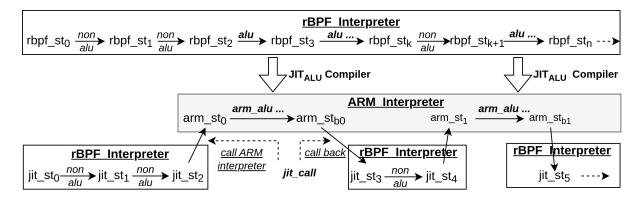

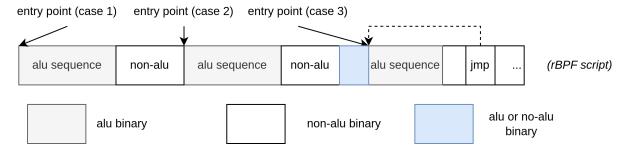

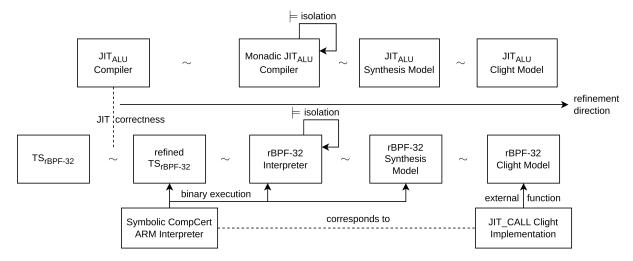

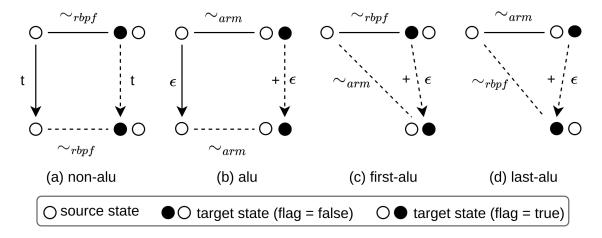

$$\forall L_1 L_2, forward\_simulation L_1 L_2 \rightarrow receptive L_1 \rightarrow determinate L_2 \rightarrow backward simulation L_1 L_2$$