# Versatile time-correlated single photon counting system and applications

Wassim Khaddour

#### ▶ To cite this version:

Wassim Khaddour. Versatile time-correlated single photon counting system and applications. Optics / Photonic. Université de Strasbourg, 2023. English. NNT: 2023STRAD041 . tel-04415192

### HAL Id: tel-04415192 https://theses.hal.science/tel-04415192

Submitted on 24 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE MATHEMATIQUES, SCIENCES DE L'INFORMATION ET DE L'INGENIEUR – ED269

UMR 7357 - Laboratoire des sciences de l'Ingénieur, de l'Informatique et de l'Imagerie (ICube)

THÈSE présentée par :

**Wassim KHADDOUR**

soutenue le : 21 septembre 2023

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline/ Spécialité : Micro et Nanoélectronique

# Versatile Time-Correlated Single Photon Counting System and Applications

THÈSE dirigée par :

M. MADEC MorganM. UHRING WilfriedMCF HDR, Université de StrasbourgProfesseur, Université de Strasbourg

**RAPPORTEURS:**

M. GINHAC DominiqueM. FERUGLIO SylvainProfesseur, Université de BourgogneMDC HDR, Sorbonne Université

**AUTRES MEMBRES DU JURY:**

Mme. DESGREYS Patricia Professeur, Telecom Paris

M. GRIFFITHS Andrew Professeur, ESPCI

M. DADOUCHE FoudilM. DUMAS NorbertMCF, Université de StrasbourgMCF, Université de Strasbourg

**INVITÉS:**

M. CLERMONT Lionel Ingénieur de recherche, Centre Spatial de Liège

# Versatile Time-Correlated Single Photon Counting System and Applications

|                           |                 | École do    | С | torale  |     |

|---------------------------|-----------------|-------------|---|---------|-----|

| Ма                        | thém            | nématiques, |   |         |     |

| sciences de l'information |                 | on          |   |         |     |

| et o                      | de l' <b>in</b> | génieur     | E | D 269   |     |

|                           | Univ            | ersité de   | S | trasbou | ırg |

#### Résumé

Dans cette thèse, nous présentons un système TCSPC polyvalent sur une plateforme SoC-FPGA à faible coût, capable de mesurer des signaux optiques avec haute sensibilité, résolution et précision. Nous proposons deux conceptions de TDC, un système efficace de transfert de données, et un programme C qui s'exécute sur un processeur embarqué. Nous introduisons également une nouvelle méthode de calibration et une méthode robuste pour la détection de microgouttelettes en microfluidique. Les performances du système ont été évaluées en résolution, précision, et stabilité. Le système a été utilisé dans quatre applications dans les domaines environnementale, biologique et astronomique : capteur de pollution de l'eau, capteur de turbidité, criblage et tri de microgouttelettes et caractérisation de la lumière parasite dans les optiques spatiales. Le système réalise des mesures TCSPC de haute performance et avec flexibilité pour diverses applications.

TDC, TCSPC, FPGA, FLT, tri de microgouttelettes.

### Résumé en anglais

In this thesis, we present a versatile TCSPC system on a low-cost SoC-FPGA platform that can measure periodic optical signals with high sensitivity, resolution and precision. We propose two TDC designs, an efficient data transfer design, and a data processing C program that runs on an embedded processor. We also introduce a novel calibration method for asynchronous TDCs and a robust method for the detection of microfluidic droplets. The system performance was evaluated in terms of resolution, precision, accuracy and stability. The system was employed in four different applications in environmental, biological, and astronomical fields; water pollution sensor, turbidity measurement, microdroplet screening and sorting, and stray light characterization in spatial optics. The results showed that the system can achieve high-performance TCSPC measurements at low cost and high flexibility for various applications.

TDC, TCSPC, FPGA, FLT, Microfluidic microdroplet sorting.

### Acknowledgement

This thesis is the result of a long and demanding journey, which I could not have accomplished without the help and support of many people.

I am extremely grateful to my thesis directors, Prof. Wilfried Uhring and Dr. Morgan Madec for their invaluable guidance, and encouragement throughout this project. My deepest and utmost gratitude goes to Prof. Wilfried Uhring who has given me the opportunity to pursue this research project. He was more than a mentor, a supporter, and a friend to me. His remarkable passion and enthusiasm for his research inspired me and his expertise and encouragement guided me through the challenges and difficulties of this work. Words fail to express my gratitude for his kindness, his confidence in me, and the friendship he extended to me since my first day in the laboratory. It was a true honor for me to be one of his students. My heartfelt gratitude also goes to to Dr. Foudil Dadouche, who opened the door for me to embark on this journey, as he was the one who first recommended me to join the laboratory in an internship; I thank him for his precious advice, invaluable guidance and continuous support. I am also profoundly grateful to Dr. Norbert Dumas for his guidance and vital help especially during the long days of manipulations and experiments.

I would also like to convey my sincere appreciation and gratitude to my defense committee, consisting of Prof. Patricia Desgreys, Prof. Dominique Ginhac, Dr. Sylvain Feruglio, Prof. Andrew Griffiths, and Dr. Lionel Clermont for their constructive and positive feedback and recommendations. I appreciate their time and expertise in evaluating my thesis.

I am also thankful to Dr. Anne Pallarès, Dr. Philippe Schmitt, and Gwenaël Pallarès from the MécaFlu research team, and Lionel Clermont and Pascal Blain from the "Centre Spatial de Liege", for their collaboration and contribution to my research.

I would like to thank my fellow PhD students and all the members of ICube laboratory, especially Nicolas Colin, Pascal Leindecker, and Jérémy Bartringer for their help and technical support.

Last but not least, I wish to express my heartfelt gratitude to my friends and family, who have always been there for me with their unconditional love and support. I am grateful to my sisters and brother for their care and encouragement, and I owe a special thanks to my sister Rana without whom this journey would not have been possible. The utmost and ultimate gratitude goes to my parents for all their hard work, dedication, and support over the years. I will be forever indebted to them, and to them I dedicate this thesis.

### **Abstract**

Time-correlated single photon counting (TCSPC) is a powerful technique for recording periodic optical signals with high sensitivity, resolution, and precision. It is applied in a wide range of applications in physics, biology, engineering, and quantum technologies. Traditional TCSPC systems have been widely utilized in scientific and industrial research. However, these systems have several drawbacks such as high cost, bulky size, and low performance. To overcome these limitations, integrated TCSPC systems have been developed in application-specific integrated circuits (ASIC). The different components of the TCSPC system as well as the data processing electronics are integrated on a single silicon chip, enabling the design of high-performance compact TCSPC systems. However, ASIC systems also have many disadvantages such as the long development cycle, high cost for small production runs, and lack of flexibility. On the other hand, recent advances in field programmable gate array (FPGA) technology have enabled the implementation of high-performance TCSPC systems with many features such as low cost, short development cycle, flexibility, and reconfigurability. Moreover, a system-on-chip FPGA (SoC-FPGA) integrates a powerful embedded processor with the FPGA fabric on the same chip, providing an efficient platform for the realization of high-performance hardware/software coprocessing applications.

This thesis presents the design and implementation of a versatile TCSPC system on a low-cost SoC-FPGA platform that can be used for different applications. The thesis proposes two time-to-digital converter (TDC) designs with a resolution of about 20 ps, one for synchronous light sources and the other for asynchronous ones. It also proposes an efficient design for high-speed data transfer between the FPGA and the embedded processor, as well as a bare-metal C program that runs on the processor and performs all the TCSPC data processing onboard. Furthermore, this thesis introduces a novel calibration method for asynchronous TDCs that enhances the linearity by a factor of 10.

The performance of the proposed system is evaluated in terms of speed, accuracy, resolution and linearity. The versatility of the system is demonstrated by employing it in four different applications: a water pollution sensor, time-resolved optical turbidity, high-throughput microfluidic droplet screening, and sorting and stray light characterization.

For the droplet sorting application, a robust method for the detection of microfluidic droplets in real time is proposed. With this method, the system is able to detect and screen droplets based on their fluorescence lifetime at a droplet rate of more than 3500 droplets/second.

The contributions of this thesis advance the state-of-the-art in FPGA-based TCSPC systems and high-throughput droplet screening and provide a low-cost, flexible, high-performance TCSPC system for various applications that require high-precision time measurement and droplet analysis.

## **Contents**

| Abstract iii                               |

|--------------------------------------------|

| Contentsv                                  |

| List of Figuresix                          |

| List of Tablesxvii                         |

| Abbreviationsxix                           |

| Chapter 1: Introduction                    |

| 1.1 Background                             |

| 1.2 Research Aim                           |

| 1.3 Contributions6                         |

| 1.4 Outline                                |

| Chapter 2: Literature Review9              |

| 2.1 TCSPC Technique9                       |

| 2.2 Pulsed Light Sources                   |

| 2.2.1 Adopted Pulsed Light Sources         |

| 2.3 Photon Detectors                       |

| 2.3.1 Photomultiplier Tube (PMT)           |

| 2.3.2 Single-Photon Avalanche Diode (SPAD) |

| 2.3.3 Adopted Photon Detector              |

| 2.4 Time-to-Digital Converters (TDCs)      |

| 2.4.1 TDC Operation Parameters             |

| 2.4.2 TDC Architectures                    |

| 2.5 TDC Implementation                     |

| 2.5.1 ASIC-Rased TDCs                      |

| 2.5.2 FPGA-Based TDCs                                  | 34 |

|--------------------------------------------------------|----|

| 2.6 Conclusion                                         | 35 |

| Chapter 3: Time-to-Digital Converter                   | 39 |

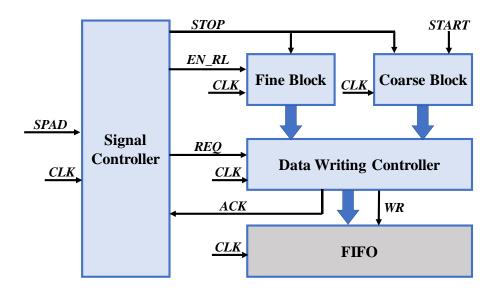

| 3.1 Synchronous TDC                                    | 40 |

| 3.1.1 Fine Block                                       | 41 |

| 3.1.2 Coarse Block                                     | 52 |

| 3.1.3 Signal Controller                                | 56 |

| 3.1.4 Data Writing Controller                          | 62 |

| 3.1.5 Supplementary Blocks                             | 63 |

| 3.2 Asynchronous TDC                                   | 66 |

| 3.2.1 Asynchronous Coarse Block                        | 67 |

| 3.2.2 Asynchronous Fine Block                          | 68 |

| 3.2.3 Asynchronous Signal Controller                   | 69 |

| 3.2.4 Asynchronous Data Writing Controller             | 71 |

| 3.2.5 Asynchronous Driving of Excitation Light Sources | 71 |

| 3.3 Conclusion                                         | 71 |

| Chapter 4: Data Processing                             | 73 |

| 4.1 Data Transfer                                      | 74 |

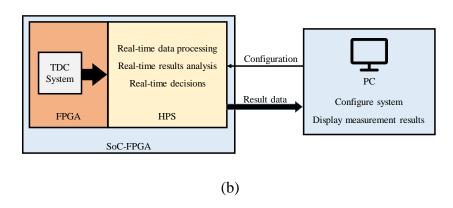

| 4.1.1 Cyclone V SoC-FPGA Architecture – HPS            | 75 |

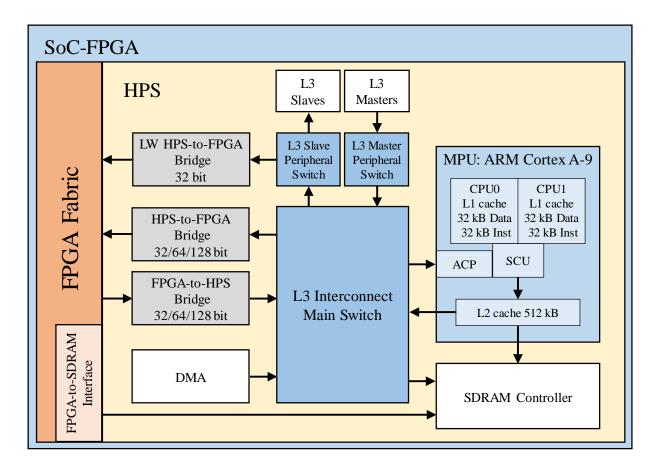

| 4.1.2 Implemented Data Transfer Mechanism              | 77 |

| 4.1.3 DMA-Based Data Transfer Problems                 | 81 |

| 4.2 Data Processing                                    | 90 |

| 4.2.1 Histogram Construction                           | 90 |

| 4.2.2 Photon Counting (Intensity Measurement)          | 92 |

| 4.2.3 TDC Calibration                                  | 93 |

| 4.2.4 Background Signal Elimination                    | 94 |

| 4.2.5 Afterpulsing Noise Suppression                   | 95 |

| 4.2.6 Calculation of Additional Parameters                   | 95  |

|--------------------------------------------------------------|-----|

| 4.3 Conclusion                                               | 97  |

| Chapter 5: TDC Calibration                                   | 99  |

| 5.1 Calibration of Synchronous TDCs                          | 99  |

| 5.1.1 Bin-by-Bin Calibration for Synchronous TDCs            | 100 |

| 5.1.2 Average-Bin-Width Calibration                          | 101 |

| 5.2 Calibration of Asynchronous TDCs                         | 103 |

| 5.2.1 Bin-by-Bin Calibration for Asynchronous TDCs           | 104 |

| 5.2.2 Matrix Calibration                                     | 104 |

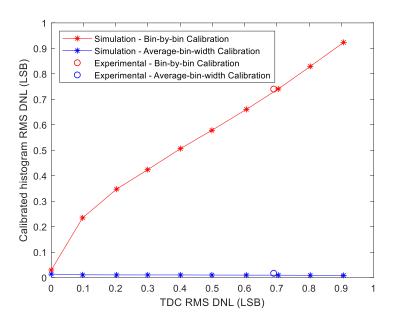

| 5.3 Simulation Results                                       | 107 |

| 5.4 Experimental Results                                     | 114 |

| 5.5 Conclusion                                               | 117 |

| Chapter 6: System Characterizations                          | 119 |

| 6.1 TDCs Characterization                                    | 120 |

| 6.1.1 RMS Precision                                          | 120 |

| 6.1.2 Accuracy                                               | 127 |

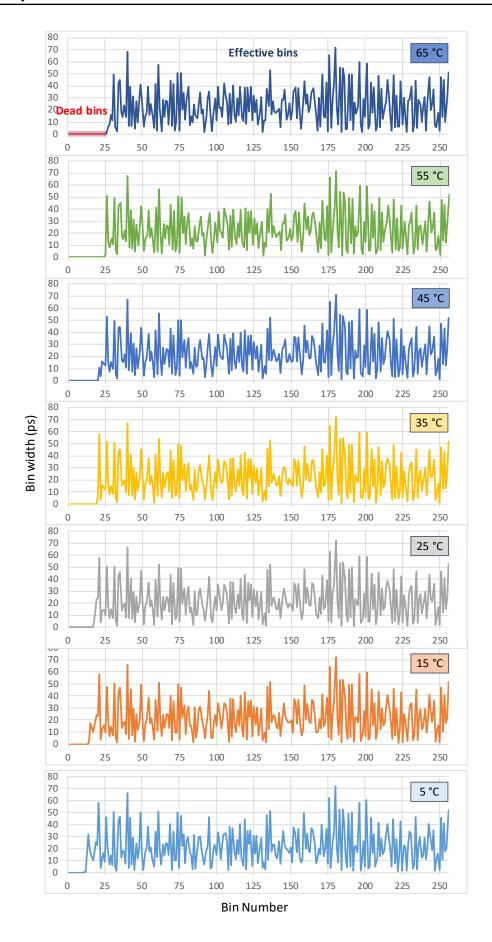

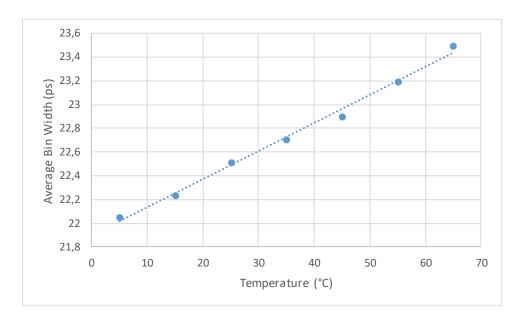

| 6.1.3 Temperature Influence on the TDL Propagation Time      | 135 |

| 6.2 TCSPC System Characterization                            | 137 |

| 6.2.1 IRF Measurement                                        | 137 |

| 6.2.2 Florescence Lifetime Measurement                       | 138 |

| 6.3 Conclusion                                               | 139 |

| Chapter 7: Applications                                      | 141 |

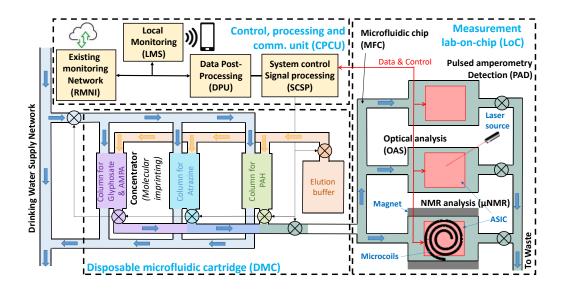

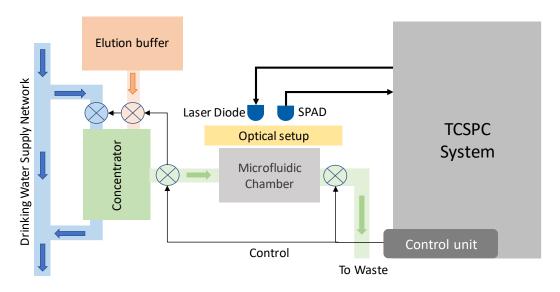

| 7.1 Water Pollution Sensor (WPS)                             | 141 |

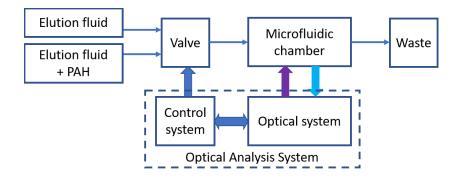

| 7.1.1 Optical Analysis System (OAS)                          | 143 |

| 7.1.2 Experimental Study                                     | 143 |

| 7.2 Microfluidic Droplet Screening and Sorting               | 149 |

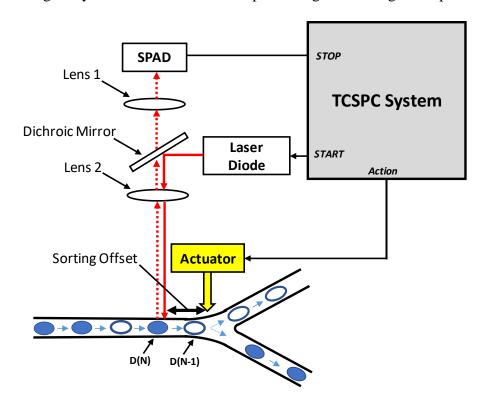

| 7.2.1 System Modifications for Droplet Detection and Sorting | 150 |

| 7.2.2 Experimental Study                           | 154 |

|----------------------------------------------------|-----|

| 7.2.3 Discrimination of Two Populations of Samples | 158 |

| 7.3 Time-Resolved Optical Turbidity                | 159 |

| 7.3.1 System Modifications for TROT                | 161 |

| 7.3.2 Experimental Results                         | 162 |

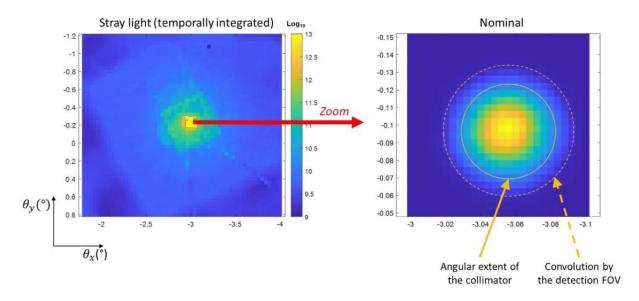

| 7.4 Stray Light Characterization                   | 167 |

| 7.4.1 Experimental Results                         | 170 |

| 7.5 Conclusion                                     | 174 |

| Chapter 8: Conclusion and Future Work              | 175 |

| 8.1 Conclusion                                     | 175 |

| 8.2 Future Work                                    | 177 |

| Bibliography                                       | 179 |

| List of Publications                               | 197 |

| RESUME DE LA THESE DE DOCTORAT                     | 199 |

# **List of Figures**

| Figure 1.1 General principle of time-correlated single photon counting [14]                | 2                   |

|--------------------------------------------------------------------------------------------|---------------------|

| Figure 1.2 Classic TCSPC setup [14].                                                       | 4                   |

| Figure 1.3 Schematic diagram of the proposed hardware/software co-design of the T          | CSPC                |

| system.                                                                                    | 6                   |

| Figure 2.1 Operating principle of linear focused PMT.                                      | 14                  |

| Figure 2.2 PMT timing jitter using a simple level trigger due to the amplitude fluctuation | ı15                 |

| Figure 2.3 (a) P-N junction operating modes in reverse bias, (b) SPAD biasing cycle        | 16                  |

| Figure 2.4 Quantization function of an ideal TDC and a real one.                           | 18                  |

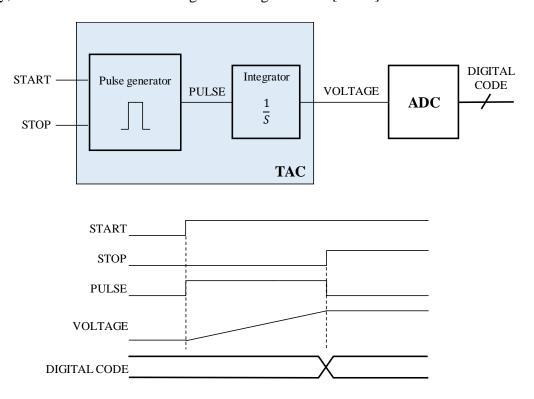

| Figure 2.5 Block and signal diagram of a basic analog-based time-to-digital converter      | 21                  |

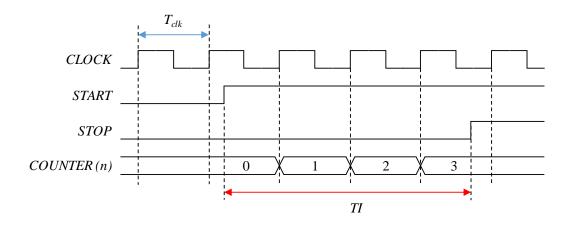

| Figure 2.6 Operating principle of the direct counting TDC.                                 | 23                  |

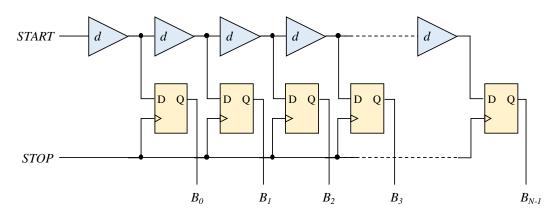

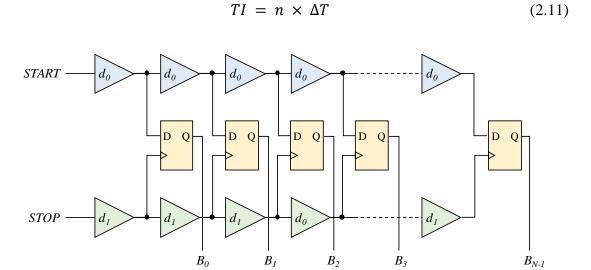

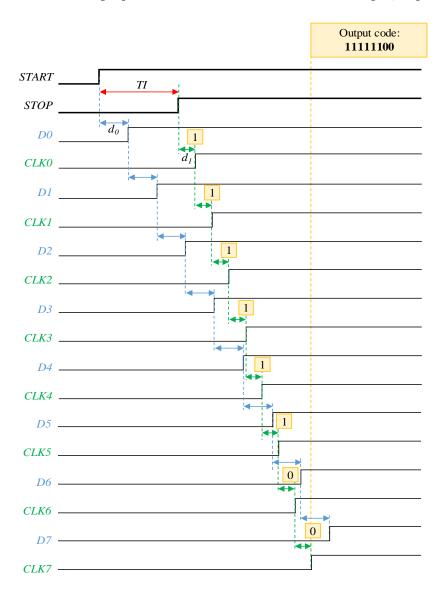

| Figure 2.7 Basic architecture of a tapped delay line-based TDC                             | 23                  |

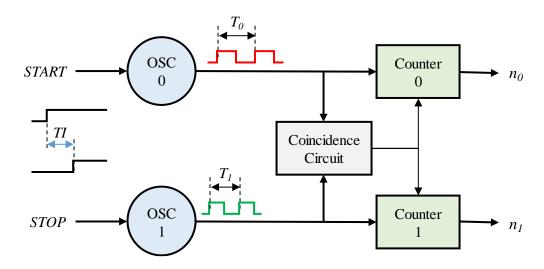

| Figure 2.8 Basic architecture of Vernier TDC.                                              | 25                  |

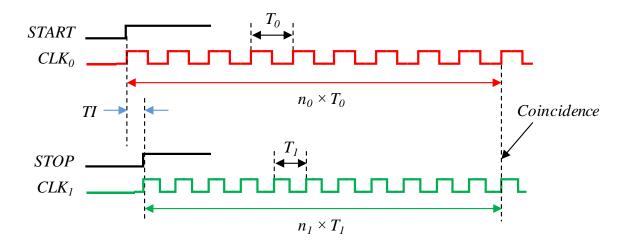

| Figure 2.9 Timing diagram of Vernier TDC                                                   | 25                  |

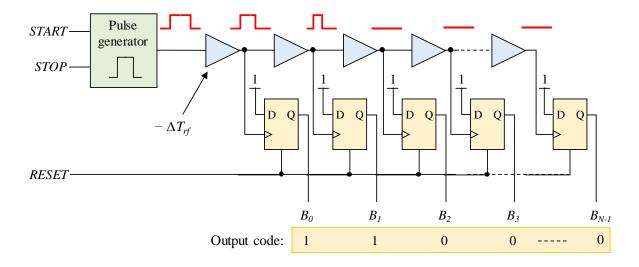

| Figure 2.10 Block diagram of VDL TDC.                                                      | 26                  |

| Figure 2.11 Timing diagram of VDL TDC                                                      | 27                  |

| Figure 2.12 Block diagram and operating principle of a pulse shrinking TDC                 | 28                  |

| Figure 2.13 (a) General block diagram of multiphase clock architecture, (b) Timing diagram | ram of              |

| a four-phase clock TDC                                                                     | 29                  |

| Figure 2.14 Block and timing diagram of multiphase clock TDC in two configuration n        | nodes:              |

| (a) Clock triggering, (b) Signal triggering.                                               | 30                  |

| Figure 2.15 Basic architecture of a ring oscillator TDC                                    | 31                  |

| Figure 2.16 General principle of Nutt method.                                              | 32                  |

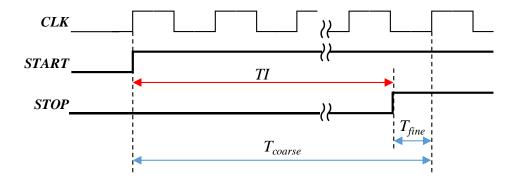

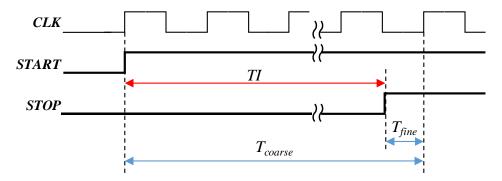

| Figure 3.1 Timing diagram of Synchronous TDC. TI is decomposed into two components         | T <sub>coarse</sub> |

| and T <sub>fine</sub> .                                                                    | 40                  |

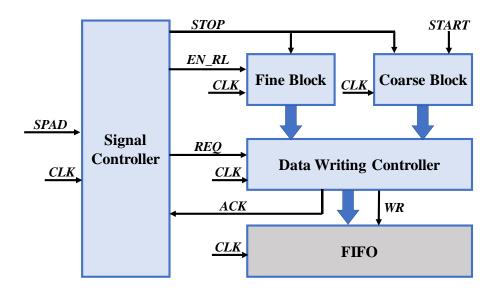

| Figure 3.2 Global architecture of the synchronous TDC                                      | 41                  |

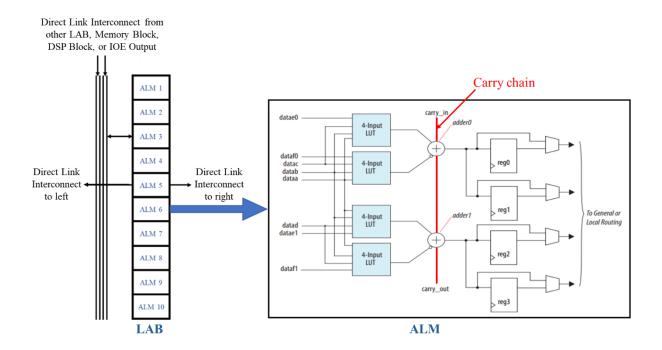

| Figure 3.3 Logical architecture of Cyclone V FPGA [131]                                    | 42                  |

| Figure 3.4 Carry-chain-based TDL architecture                                              | 13                  |

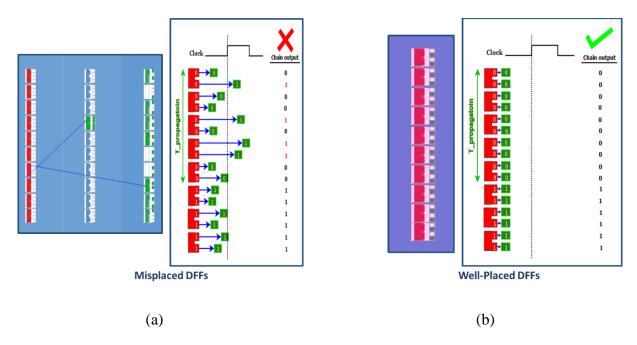

| Figure 3.5 Registers placement problem: (a) without logic lock region, the registers are                                        |

|---------------------------------------------------------------------------------------------------------------------------------|

| misplaced, (b) with logic lock region, the registers are placed in the same ALMs as their                                       |

| corresponding adders                                                                                                            |

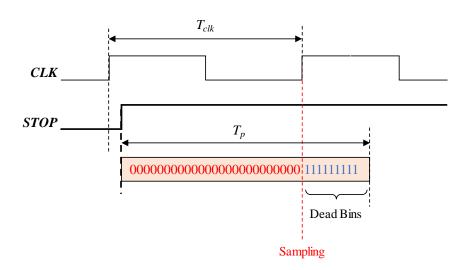

| Figure 3.6 Dead bins in the case of a clock period much shorter than the TDL delay45                                            |

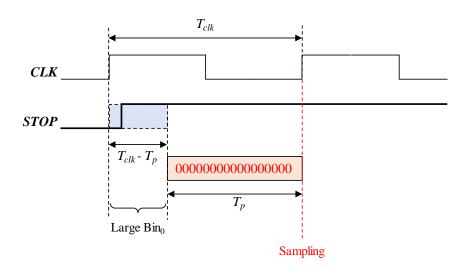

| Figure 3.7 Large width of $Bin_0$ in the case of a clock period longer than the TDL delay46                                     |

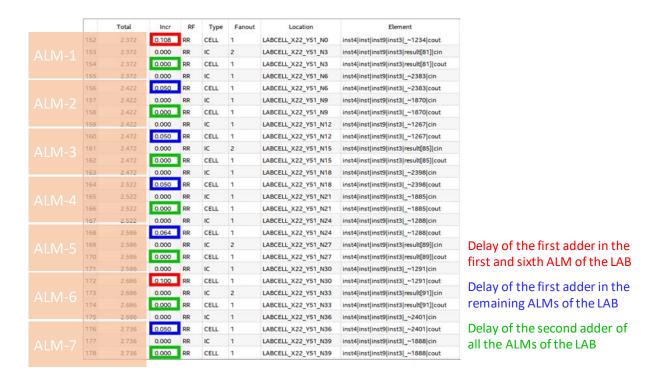

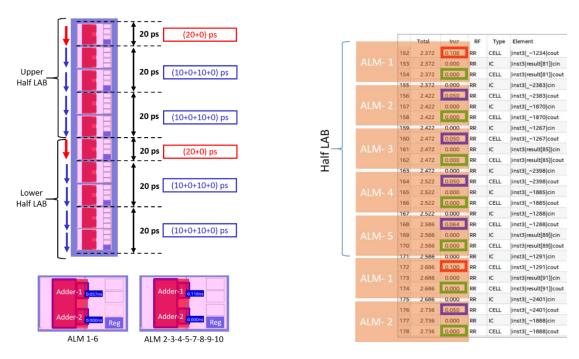

| Figure 3.8 Carry-chain path report in the timing analyzer tool                                                                  |

| Figure 3.9 Tuned downsampling: three delay elements are implemented in each half LAB with                                       |

| an identical delay of about 20 ps                                                                                               |

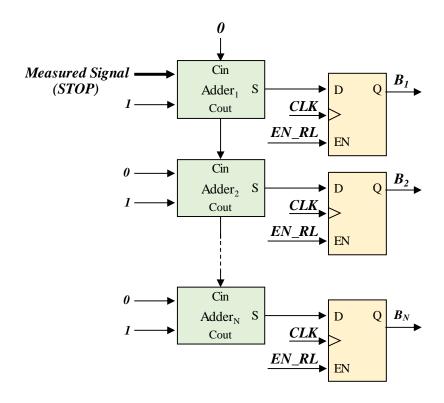

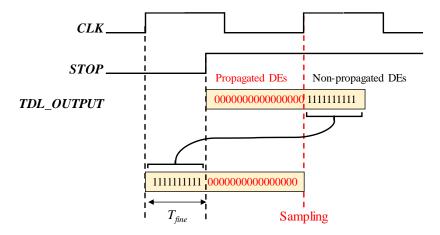

| Figure 3.10 Ones-counter encoding principle                                                                                     |

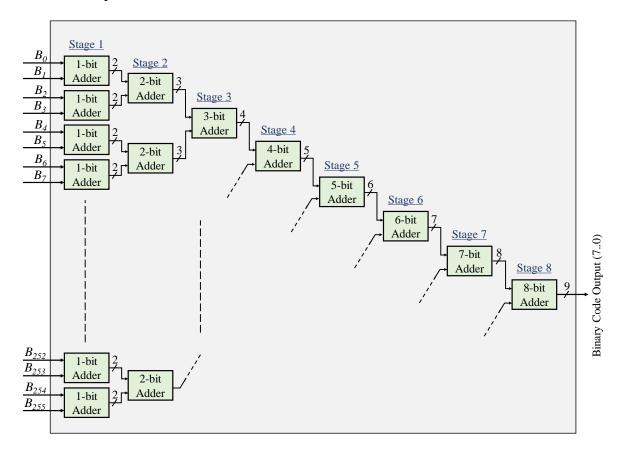

| Figure 3.11 Basic architecture of a 255-to-8-bit ones-counter encoder, it consists of 8 stages of                               |

| adders that count the number of ones in the thermometer code and convert it into a binary code.                                 |

| 51                                                                                                                              |

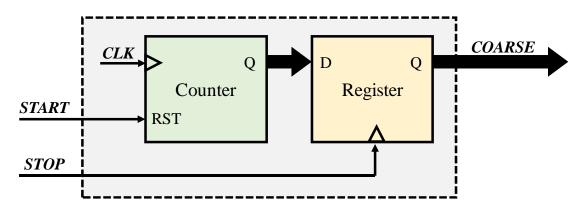

| Figure 3.12 Coarse block                                                                                                        |

| Figure 3.13 Timing diagram of the dual counter solution for the metastability issue arising from                                |

| the asynchronous sampling53                                                                                                     |

| Figure 3.14 Schematic diagram of the Coarse block                                                                               |

| Figure 3.15 Selection sub-block operation principle; the stable coarse value is selected based                                  |

| on the fine value, which indicates the STOP signal's arrival time within the clock period55                                     |

| Figure 3.16 Basic architecture of the selection sub-block                                                                       |

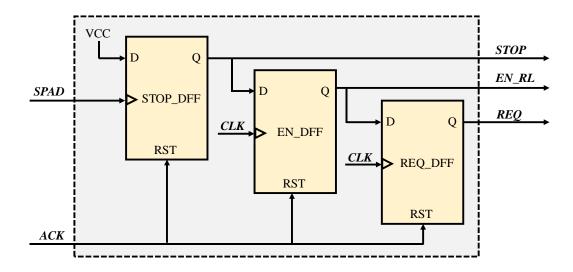

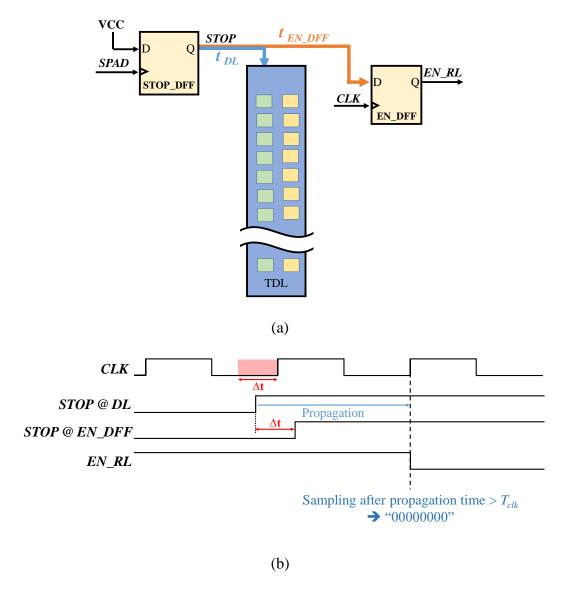

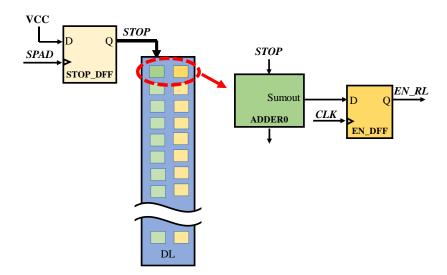

| Figure 3.17 Signal controller architecture                                                                                      |

| Figure 3.18 Examples of the delay ( $\Delta t$ ) between the arrival time of the STOP signal at the                             |

| EN_DFF and at the TDL for two different compilations: (a) $t_{TDL} > t_{EN\_RL}$ ( $\Delta t > 0$ ), (b) $t_{TDL} < t_{EN\_RL}$ |

| $t_{\text{EN\_RL}} (\Delta t < 0)$ 58                                                                                           |

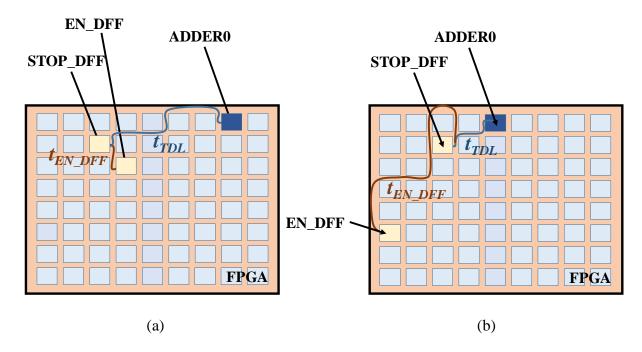

| Figure 3.19 Case 1, the STOP signal arrives at EN_DFF before the TDL: (a) the STOP routing                                      |

| path to TDL is longer than its path to EN_DFF, (b) when the STOP signal arrives at the TDL                                      |

| in the red range, the DL would be sampled at the previous clock rising edge, resulting in an                                    |

| incorrect code of 255                                                                                                           |

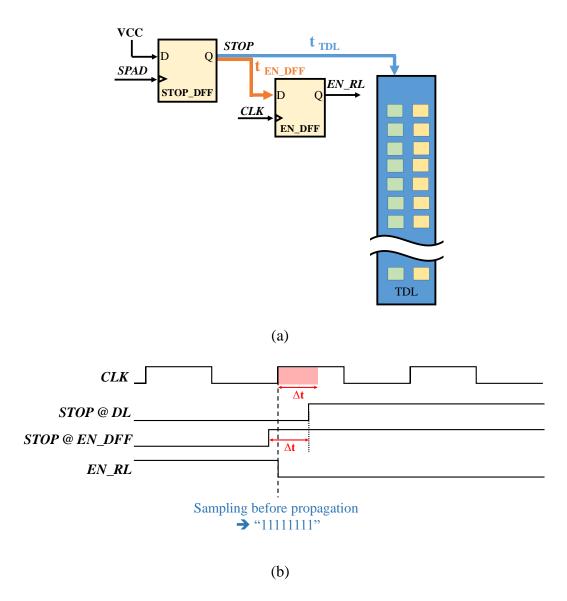

| Figure 3.20 Case 2, the STOP signal arrives at the TDL before EN_DFF: (a) the STOP routing                                      |

| path to TDL is shorter than its path to EN_DFF, (b) when the STOP signal arrives at the TDL                                     |

| in the red range, the DL would be sampled at the second following clock rising edge resulting                                   |

| in an incorrect code of 060                                                                                                     |

| Figure 3.21 EN_DFF placement at the beginning of the TDL. The DFF associated with the first                                     |

| adder is used as the EN DFF to minimize the delay                                                                               |

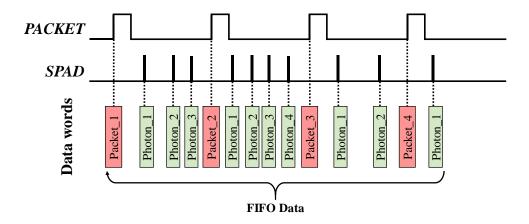

| Figure 3.22 Temporal packetizing principle: at each packet pulse the data writing controller               |

|------------------------------------------------------------------------------------------------------------|

| writes to the FIFO a packet word indicating the macro time of the photons detected during that             |

| packet period                                                                                              |

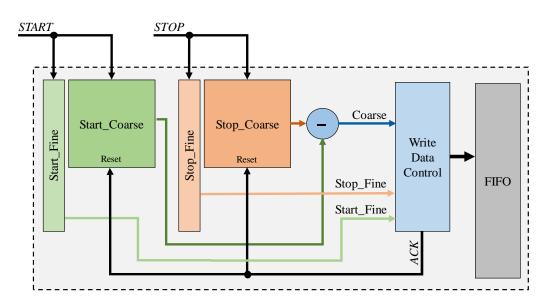

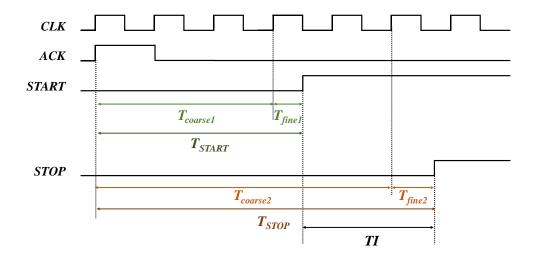

| Figure 3.23 Asynchronous TDC basic architecture                                                            |

| Figure 3.24 Operating principle of asynchronous TDC: two time measurement channels                         |

| measure the arrival times of the START and STOP signals ( $T_{START}$ , $T_{STOP}$ ), and TI is calculated |

| by the subtraction of these two times                                                                      |

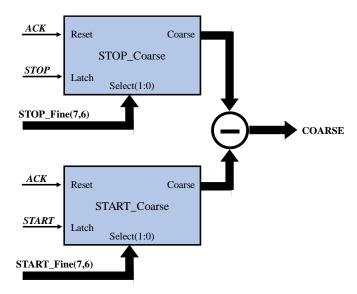

| Figure 3.25 The global architecture of the Coarse block: it consists of two coarse sub-blocks              |

| for the START and STOP signals, the final coarse value is calculated by subtracting the two                |

| coarse values                                                                                              |

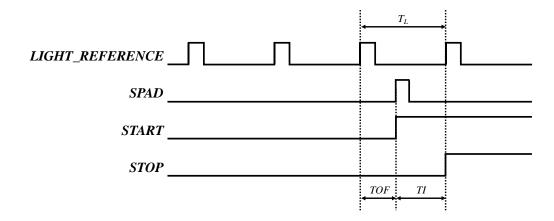

| Figure 3.26 Revers start-stop mode: the SPAD signal represents the START signal and the                    |

| excitation light reference represents the STOP signal, TOF is calculated by subtracting the                |

| measured time interval from the excitation light period                                                    |

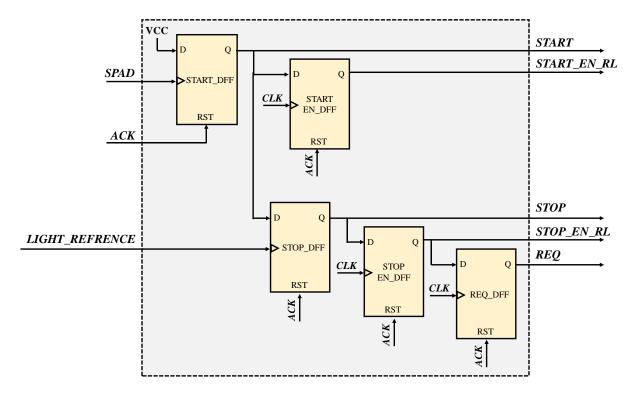

| Figure 3.27 Asynchronous signal controller architecture                                                    |

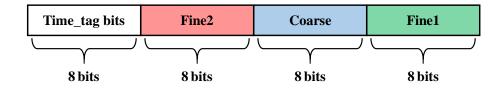

| Figure 3.28 Photon word: a 32-bit word that combines the coarse value, the two fine values,                |

| and additional time-tag bits71                                                                             |

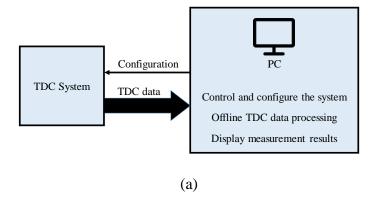

| Figure 4.1 Data processing modes: (a) data processing is performed by the control PC, (b) data             |

| processing is executed locally by the HPS integrated in the SoC-FPGA board and the results                 |

| are transmitted to the PC                                                                                  |

| Figure 4.2 Schematic representation of the main components and interfaces of the Cyclone V                 |

| SoC-FPGA architecture                                                                                      |

| Figure 4.3 Data transfer mechanism: a Qsys design integrates an mSGDMA IP for the data                     |

| transfer directly into the SDRAM through the FPGA-to-SDRAM interface                                       |

| Figure 4.4 Offline mode: considering the maximum detectable photon rate, the processor should              |

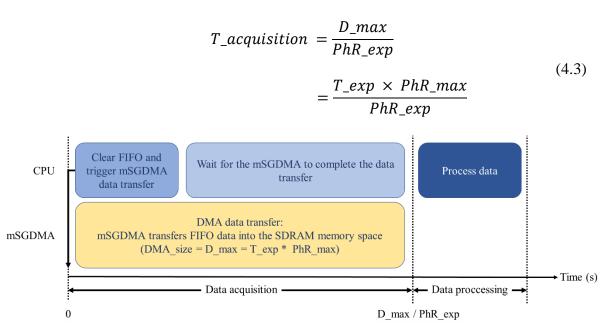

| wait for the mSGDMA to transfer D_max data word before processing data82                                   |

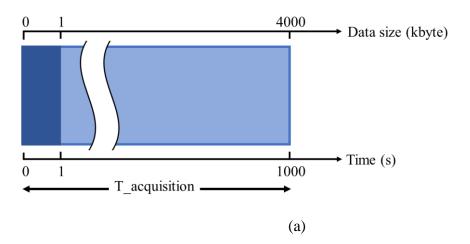

| Figure 4.5 DMA data size in offline mode: (a) the maximum detectable photon rate approach,                 |

| (b) the constant data writing rate approach.                                                               |

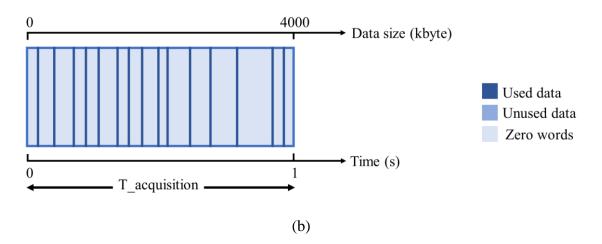

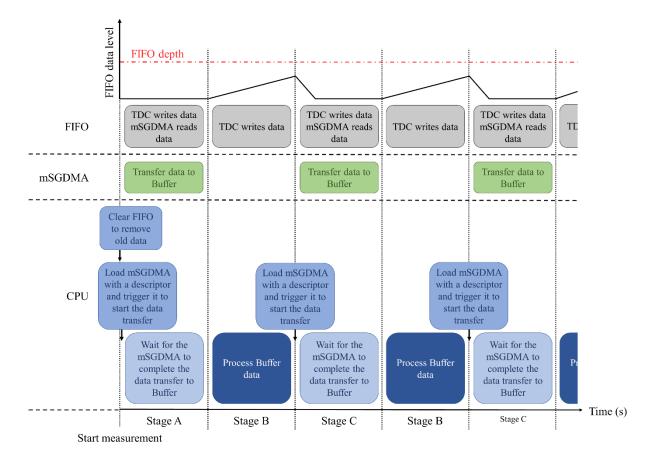

| Figure 4.6 Data buffering and processing flow in real-time mode: data are buffered in the                  |

| SDRAM before being processed. While buffered data are being processed, new data are being                  |

| written into the FIFO.                                                                                     |

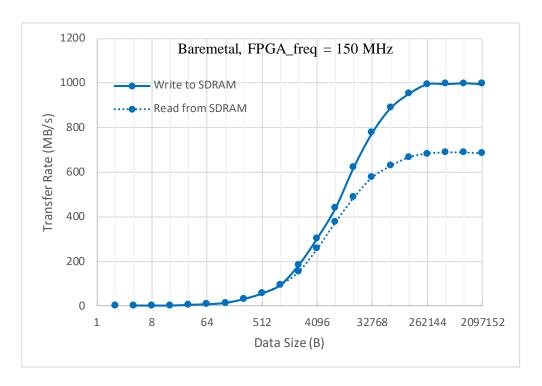

| Figure 4.7 DMA transfer rate as a function of the data size (DMA_size) through the FPGA-to-                |

| SDRAM interface with a bare-metal application at an FPGA frequency of 150 MHz [152], .88                   |

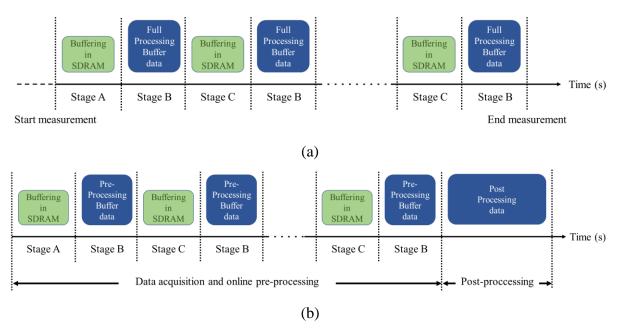

| Figure 4.8 Data buffering and processing flow: (a) in real-time mode, data are fully processed    |

|---------------------------------------------------------------------------------------------------|

| in Stages B, (b) in single-measurement mode, data are pre-processed in Stages B and post-         |

| processed at the end of the measurement                                                           |

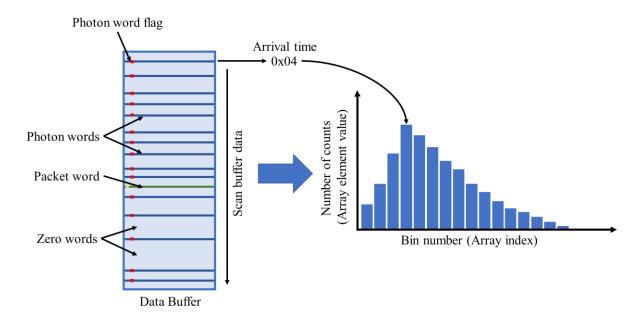

| Figure 4.9 Histogram creation in synchronous system: the photon words are read from the           |

| buffer and mapped to the corresponding bins in the histogram array based on their arrival time.   |

| 91                                                                                                |

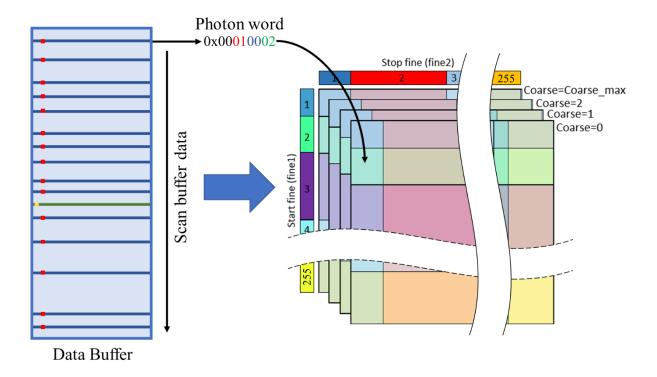

| Figure 4.10 Histogram creation in asynchronous systems: the photon words are read from the        |

| buffer and mapped to the corresponding cell in the 3D array based on their fine1, fine2 and       |

| Coarse values                                                                                     |

| Figure 4.11 Photon counting: (a) Real-time photon counting mode, (b) Intensity histogram          |

| mode, (c) Fluorescence intensity distribution analysis (FIDA)93                                   |

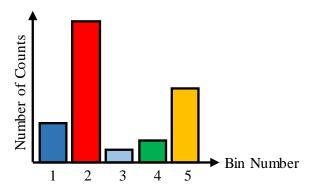

| Figure 5.1 Code density histogram of a simple synchronous TDC with five bins and a total          |

| delay of T                                                                                        |

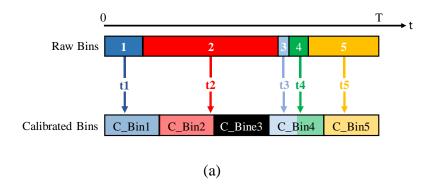

| Figure 5.2 Calculating the calibrated times and calibrated bins of the raw bins; (b) Bin-by-bin   |

| calibration lookup table                                                                          |

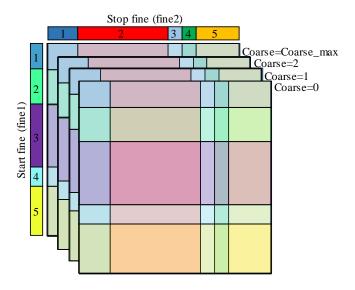

| Figure 5.3 Average-bin-width calibration: redistributing the total counts on identical calibrated |

| bins and creating the calibration table that defines the percentage share of the raw bins in each |

| calibrated bin                                                                                    |

| Figure 5.4 Calibration table: it describes the percentage share of the raw bins in the calibrated |

| bins                                                                                              |

| Figure 5.5 Three-dimension code density histogram of an asynchronous TDC: the Stop and            |

| Start fine bin numbers are respectively represented on x and y, whereas the Coarse value is       |

| represented on z                                                                                  |

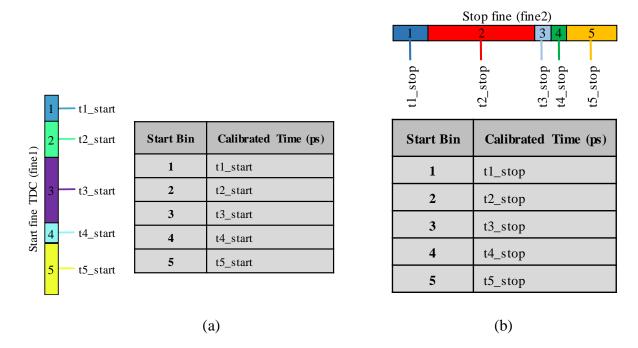

| Figure 5.6 Lookup tables of the two fine TDCs: (a) Start fine TDC LUT, (b) Stop fine TDL          |

| LUT                                                                                               |

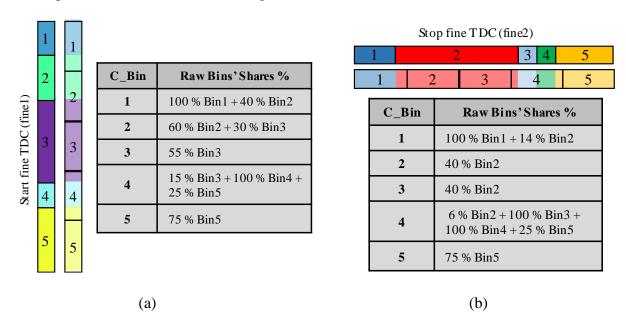

| Figure 5.7 Individual calibration tables: (a) Start fine TDC calibration table, (b) Stop fine TDC |

| calibration table                                                                                 |

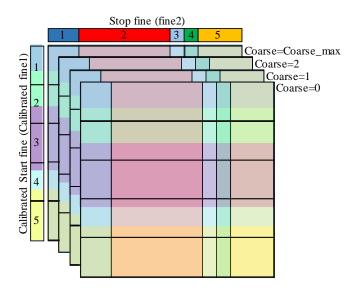

| Figure 5.8 Column calibration: the individual calibration of the columns using the average-bin-   |

| width method gives a semi-calibrated histogram where all the rows have the same height106         |

| Figure 5.9 Row calibration; the average-bin-width calibration is applied to the rows, resulting   |

| in a calibrated 3D histogram with identical cell size                                             |

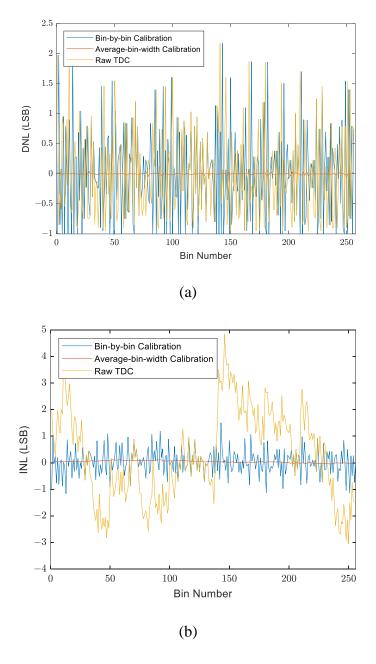

| Figure 5.10 Simulation and experimental results for synchronous TDCs: the DNL after applying      |

| the calibration methods compared to the DNL of the raw TDC                                        |

| Figure 5.11 DNL and INL values for a synchronous TDC model, before and after applying the         |

|---------------------------------------------------------------------------------------------------|

| bin-by-bin and the average-bin-width calibration methods: (a) DNL values, (b) INL values.         |

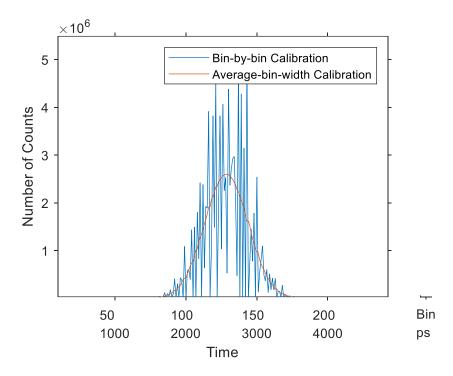

| Figure 5.12 Calibrated histogram of a Gaussian signal using bin-by-bin and average-bin-width      |

| methods for synchronous TDCs. 110                                                                 |

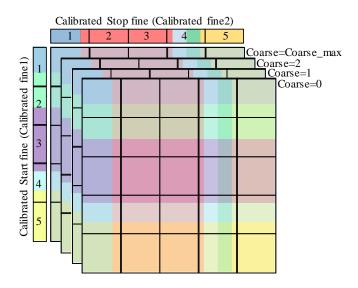

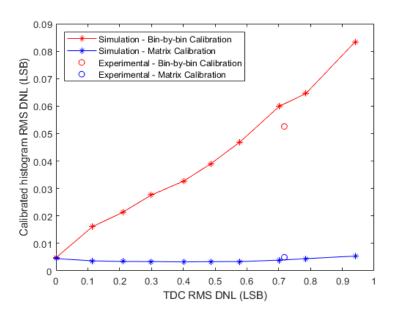

| Figure 5.13 Simulation and experimental results for asynchronous TDCs: the DNL after              |

| applying the calibration methods compared to the DNL of the raw TDC111                            |

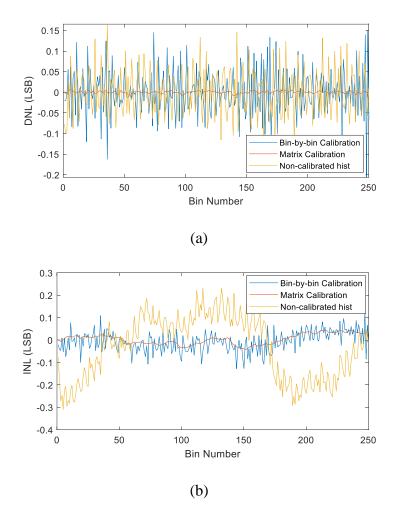

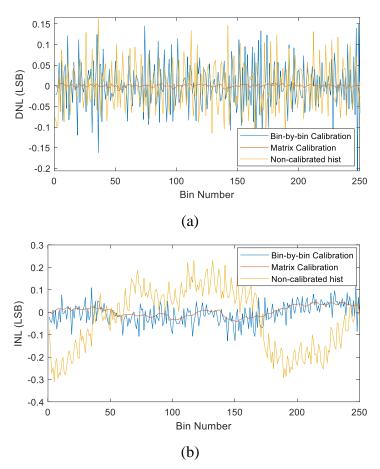

| Figure 5.14 DNL and INL values for the asynchronous TDC model, before and after applying          |

| the bin-by-bin and the Matrix calibration methods: (a) DNL values, (b) INL values112              |

| Figure 5.15 Calibrated histogram of a Gaussian signal using bin-by-bin and Matrix calibration     |

| methods for asynchronous TDCs                                                                     |

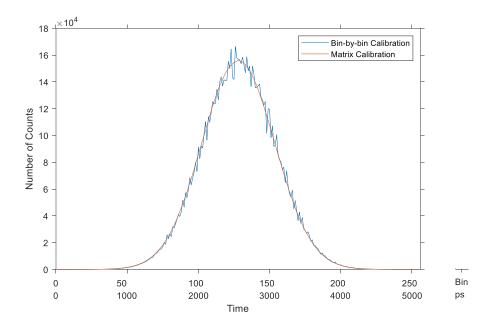

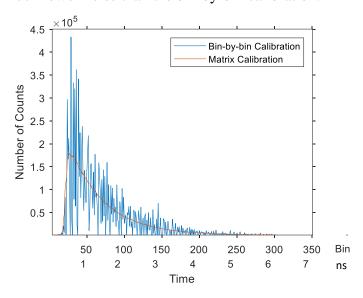

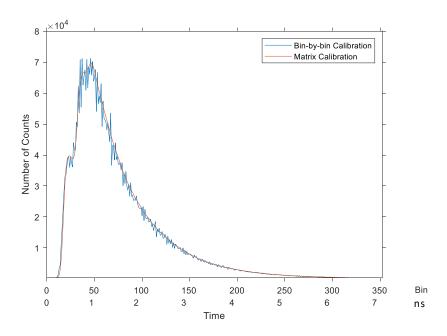

| Figure 5.16 Calibrated histograms of the fluorescence signal of a piece of paper obtained with    |

| the bin-by-bin and the average-bin-width calibration methods for synchronous TDC114               |

| Figure 5.17 Calibrated histograms of the fluorescence signal of a piece of paper obtained with    |

| the bin-by-bin and the Matrix calibration methods for asynchronous TDC115                         |

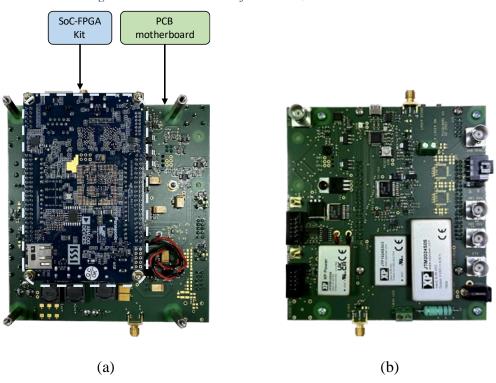

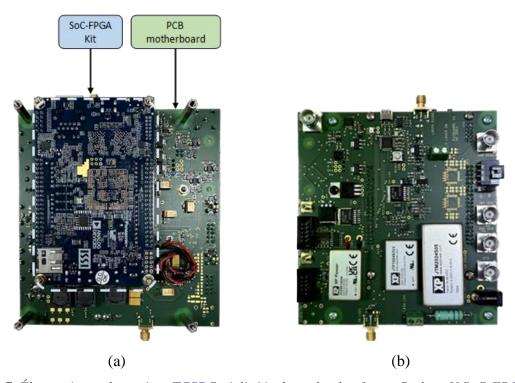

| Figure 6.1 Exterior view of the realized TCSPC device                                             |

| Figure 6.2 Electronics of the realized TCSPC system with the Cyclone V SoC-FPGA platform          |

| and custom PCB motherboard: (a) bottom view, (b) top view                                         |

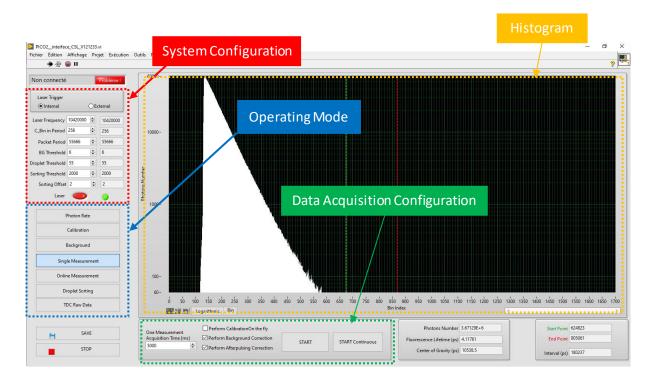

| Figure 6.3 Labview interface of the TCSPC system in the single-measurement mode 120               |

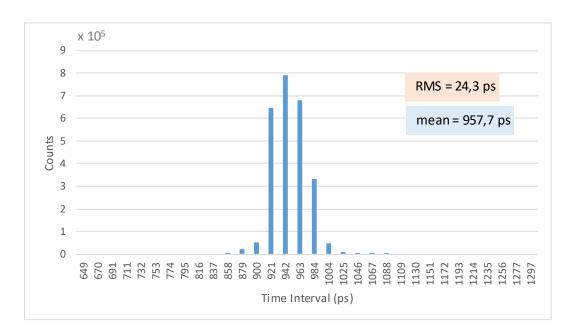

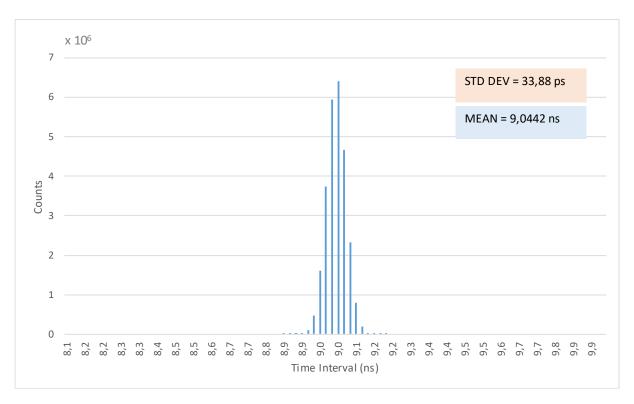

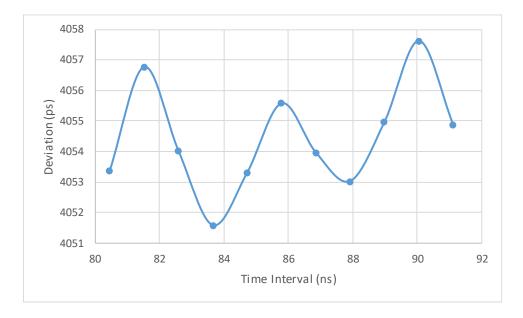

| Figure 6.4 RMS precision of the synchronous TDC.                                                  |

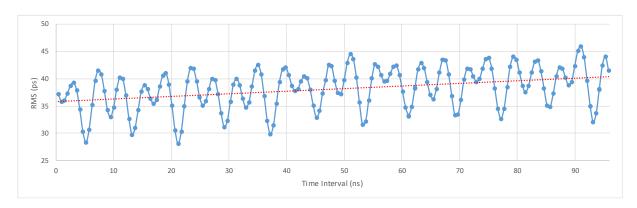

| Figure 6.5 RMS precision variation across the TDL measurement range                               |

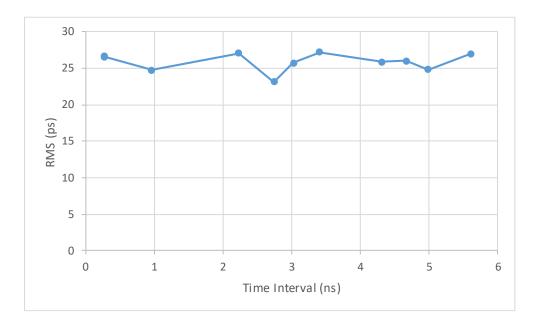

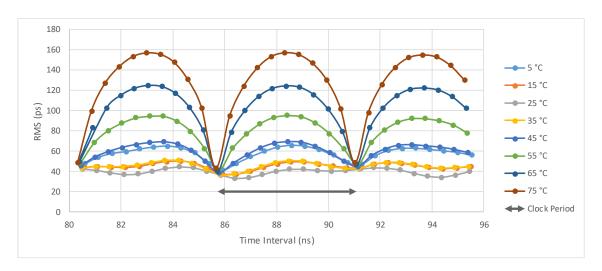

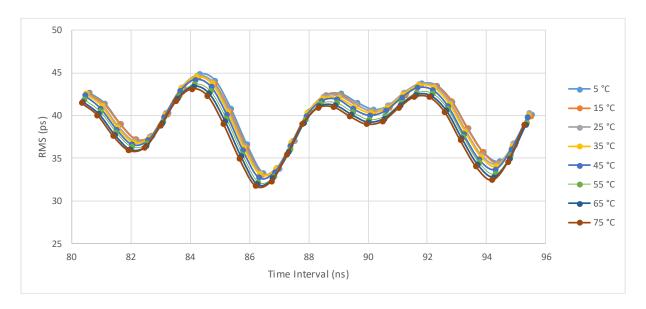

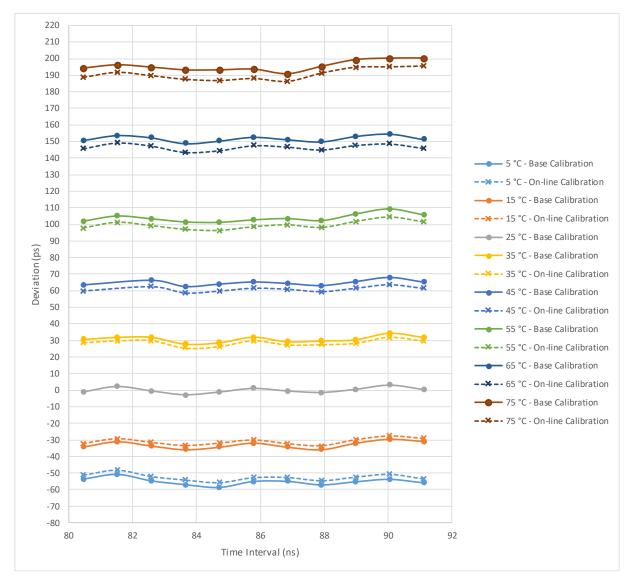

| Figure 6.6 Overall RMS precision of synchronous TDC at different ambient temperatures: (a)        |

| with base calibration table, (b) with online calibration                                          |

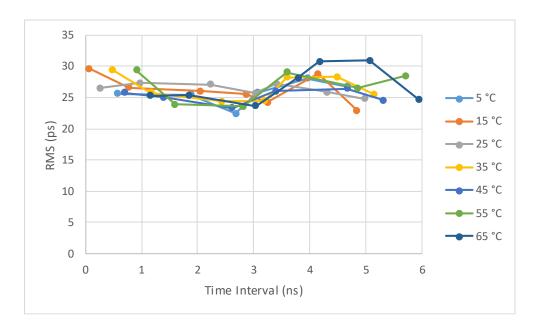

| Figure 6.7 RMS precision of asynchronous TDC.                                                     |

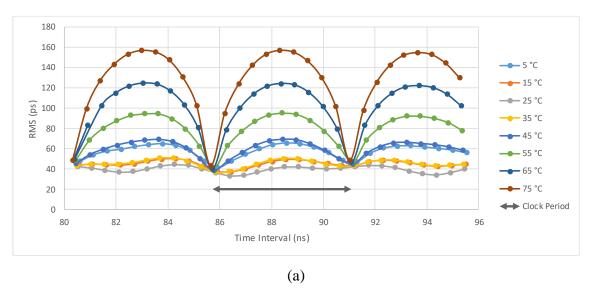

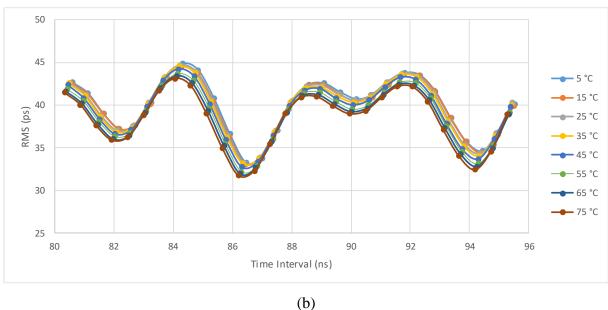

| Figure 6.8 RMS precision of asynchronous TDC as a function of the time interval125                |

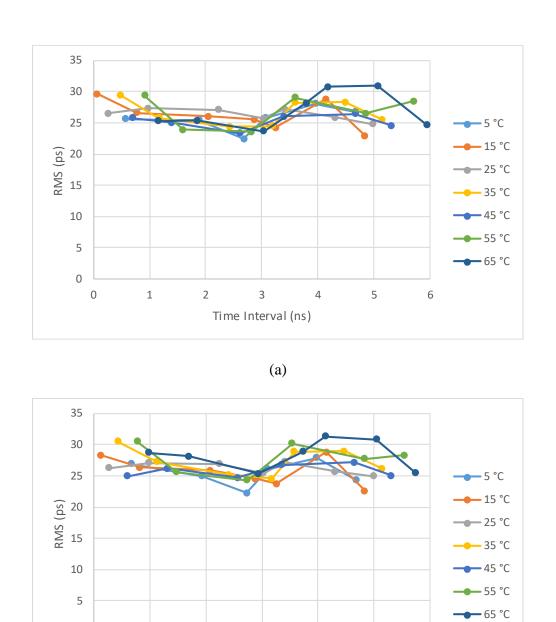

| Figure 6.9 Overall RMS precision of asynchronous TDC at different ambient temperatures with       |

| base calibration                                                                                  |

| Figure 6.10 Overall RMS precision of asynchronous TDC at different ambient temperatures           |

| with online calibration                                                                           |

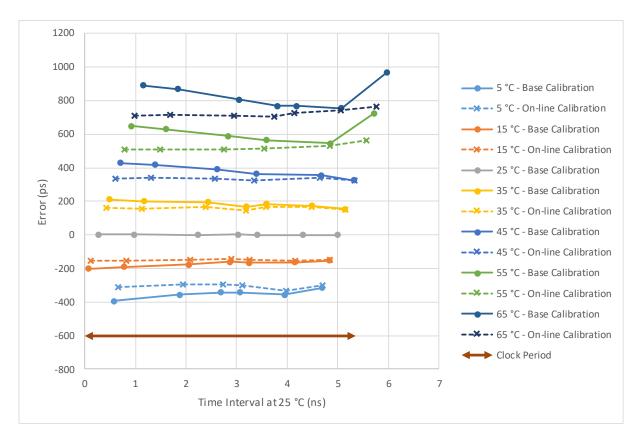

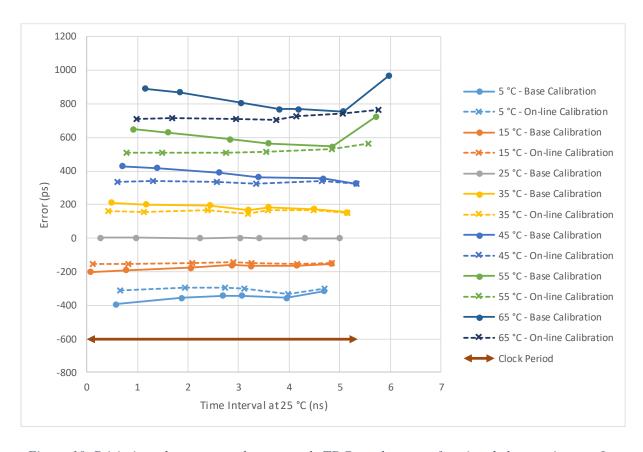

| Figure 6.11 Deviations in the mean time interval measured by the synchronous TDC for              |

| different cable lengths and at different temperatures. The solid curves show the results obtained |

| with base calibration, while the dotted curves show the results obtained with online calibration. |

| 128                                                                                               |

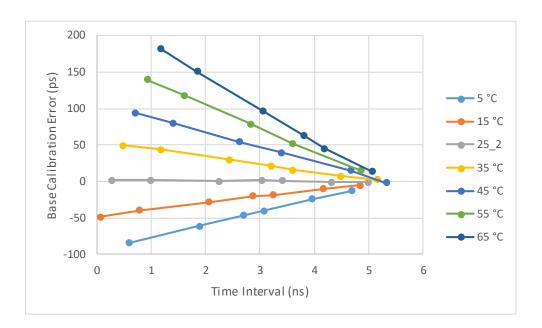

| Figure 6.12 Deviations in the synchronous TDC's measurements due to the gain error at             |

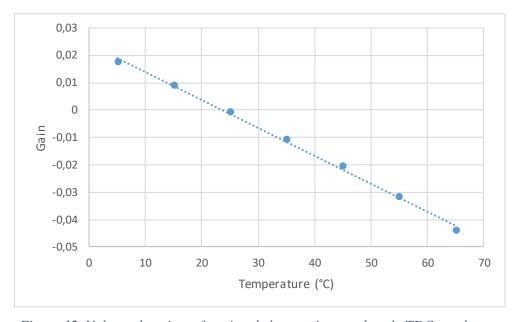

|---------------------------------------------------------------------------------------------------|

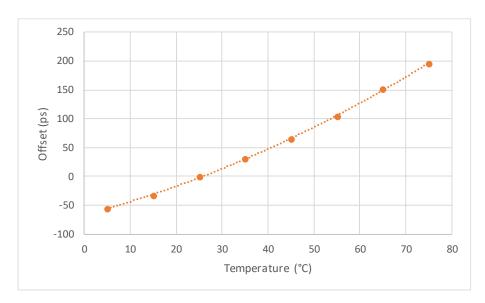

| different temperatures                                                                            |

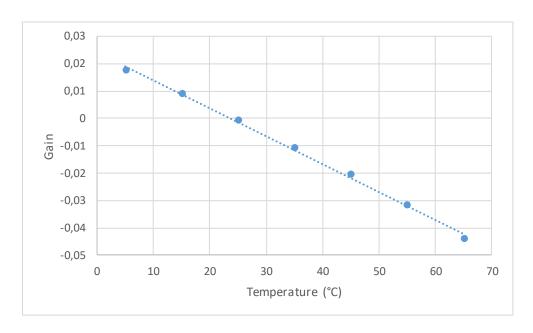

| Figure 6.13 Gain values as a function of temperature in synchronous TDC130                        |

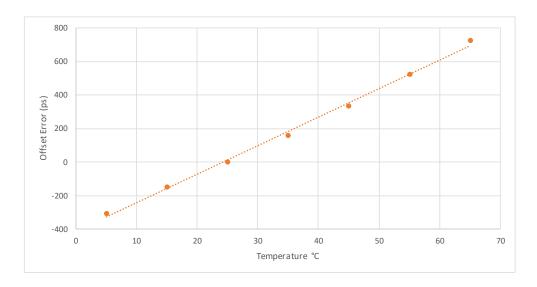

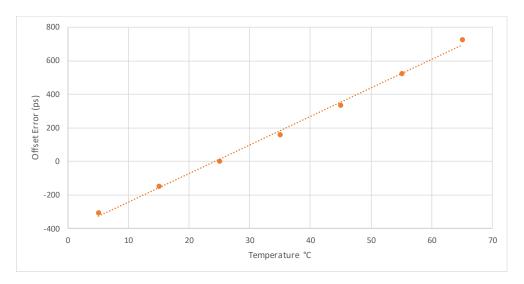

| Figure 6.14 Offset error as a function of temperature in synchronous TDC131                       |

| Figure 6.15 Deviation between the measured and expected time intervals using the                  |

| asynchronous TDC                                                                                  |

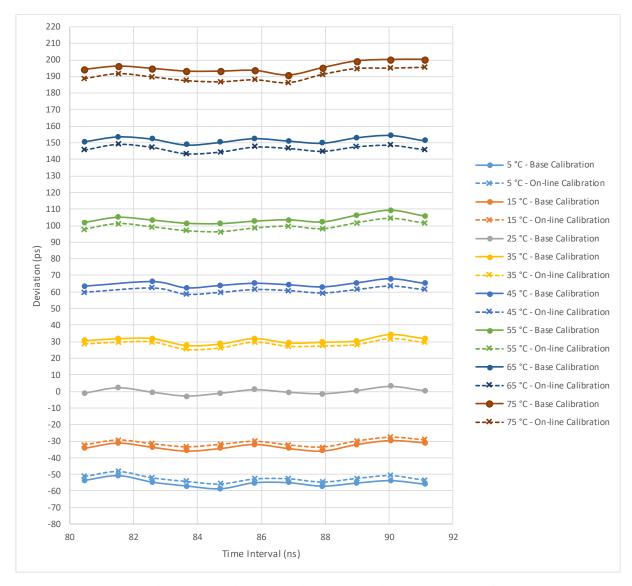

| Figure 6.16 Deviation between measured and expected time intervals at different temperatures      |

| for the asynchronous TDC with base and online calibration                                         |

| Figure 6.17 Offset error as a function of temperature in the asynchronous TDC134                  |

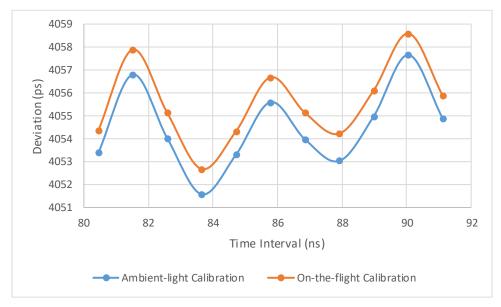

| Figure 6.18 Comparison of the mean measured time intervals obtained by SPAD-based and on-         |

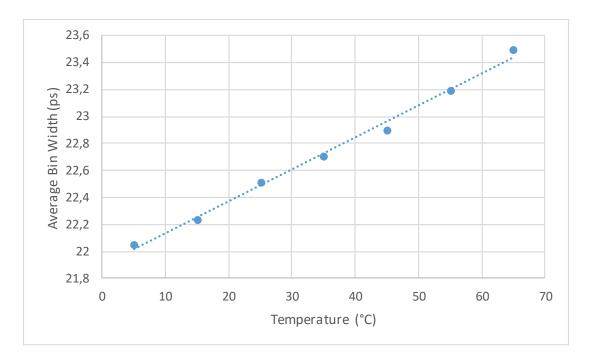

| the-flight calibration techniques                                                                 |

| Figure 6.19 TDL bins' widths at different temperatures                                            |

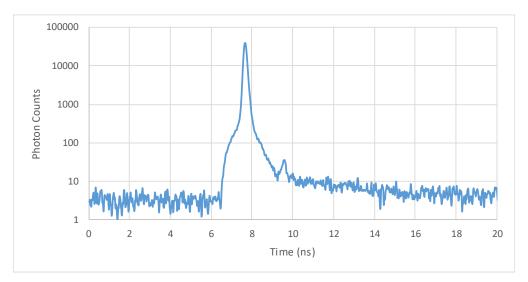

| Figure 6.20 Average bin width of the TDL as a function of temperature                             |

| Figure 6.21 Instrument response function of the synchronous TCSPC system using a 405-nm           |

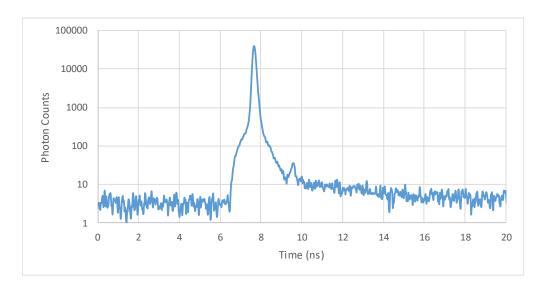

| pulsed laser diode. The FWHM is about 130 ps                                                      |

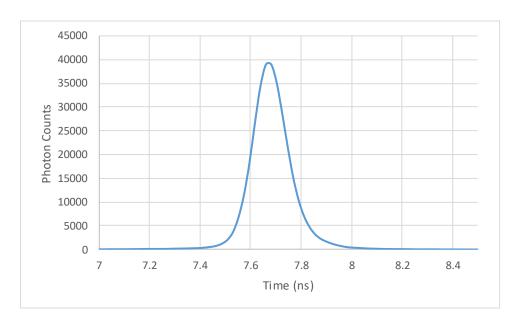

| Figure 6.22 Laser pulse signal after excluding the noise caused by ambient light138               |

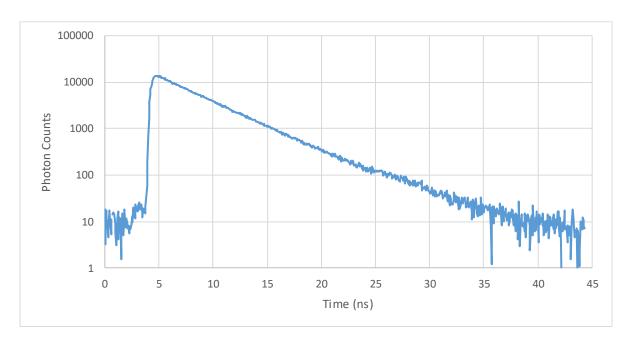

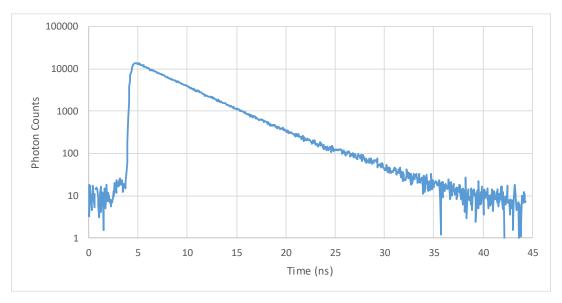

| Figure 6.23 Fluorescence signal of Sodium Fluorescein in PBS measured by the synchronous          |

| TCSPC system. The estimated FLT is 4.11 ns                                                        |

| Figure 7.1 Schematic diagram of the water pollution sensor (WPS) device                           |

| Figure 7.2 Global architecture of the optical analysis system                                     |

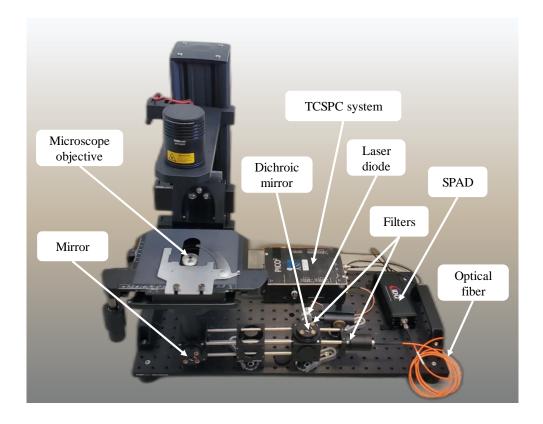

| Figure 7.3 Optical setup                                                                          |

| Figure 7.4 Schematic diagram of microfluidic circuit                                              |

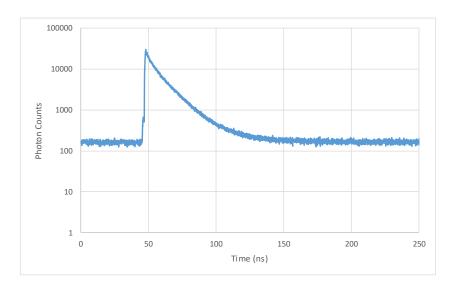

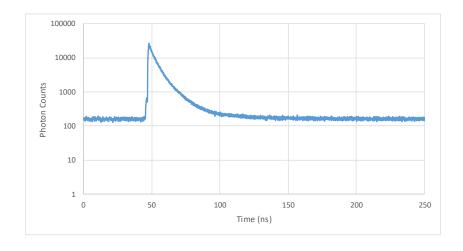

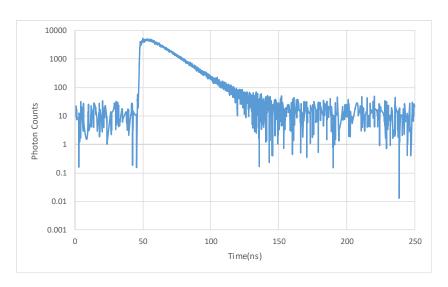

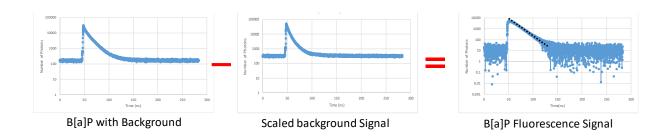

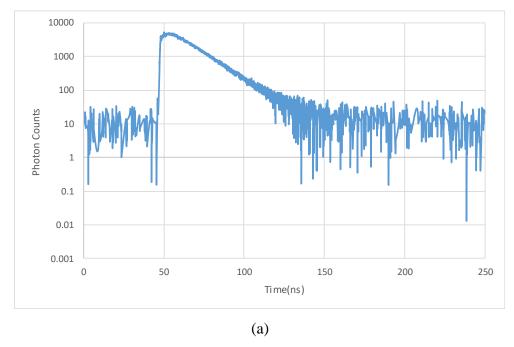

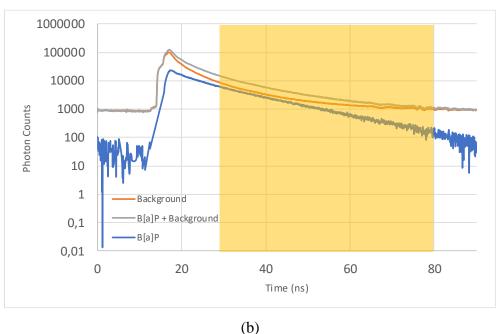

| Figure 7.5 Fluorescence signal of B[a]P in pure ethanol at a concentration of 750 $\mu M$ without |

| background suppression                                                                            |

| Figure 7.6 Scaled background signal                                                               |

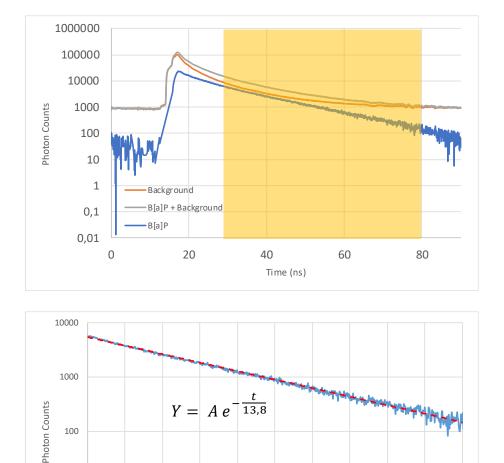

| Figure 7.7 Fluorescence signal of B[a]P in pure ethanol at a concentration of 750 $\mu M$ after   |

| background suppression                                                                            |

| Figure 7.8 Principle of background signal suppression                                             |

| Figure 7.9 Fluorescence signal of B[a]P in pure ethanol at a concentration of 40 $\mu M$ after    |

| background signal suppression                                                                     |

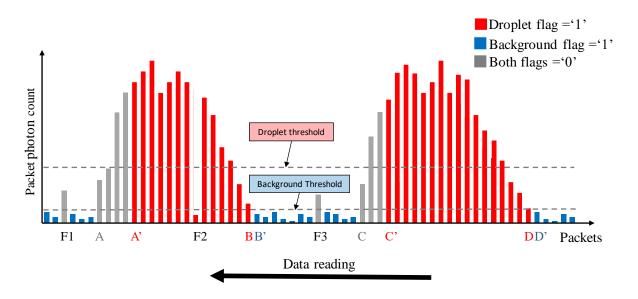

| Figure 7.10 Droplet detection: two thresholds are defined to determine the beginning and the      |

| end of the droplet and avoid noise spikes                                                         |

| Figure 7.11 Schematic diagram of the droplet sorting system with the optical and microfluidic     |

| narte 15/                                                                                         |

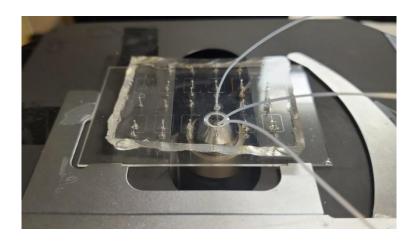

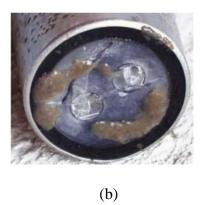

| Figure 7.12 Microfluidic chip                                                                      |

|----------------------------------------------------------------------------------------------------|

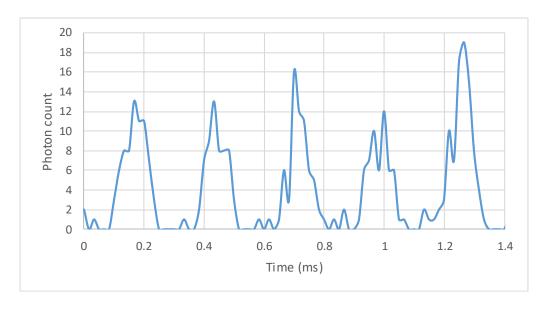

| Figure 7.13 Droplet detection based on the packets' photon counts at a droplet rate of             |

| 3573 droplets/second                                                                               |

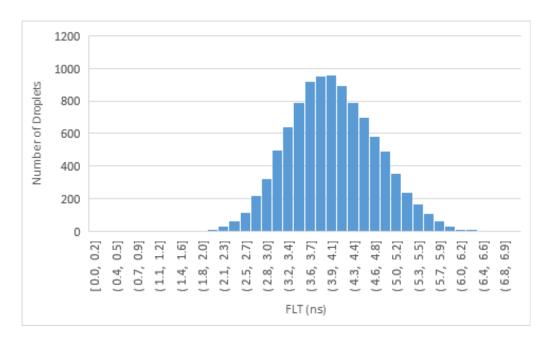

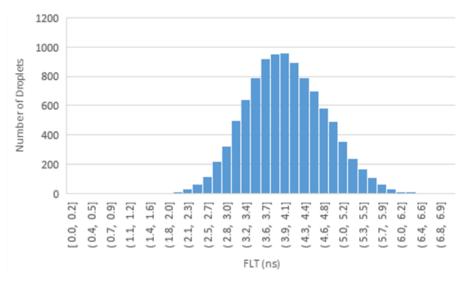

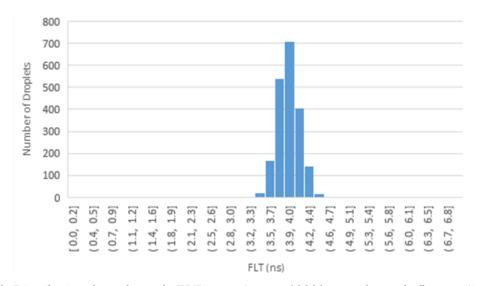

| Figure 7.14 FLT distribution of 10000 droplets of fluorescein in PBS at 3573 droplets/second.      |

|                                                                                                    |

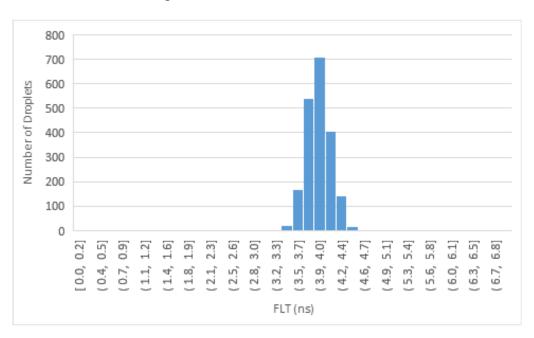

| Figure 7.15 FLT distribution of 2000 droplets of fluorescein in PBS at 1000 droplets/second.       |

|                                                                                                    |

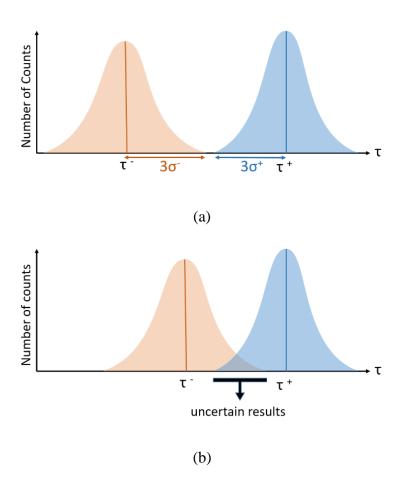

| Figure 7.16 Discrimination of two populations of samples: (a) the distributions of the FLT         |

| values for the two populations are clearly separated, (b) the distributions of the FLT values for  |

| the two populations overlap, resulting in uncertain results                                        |

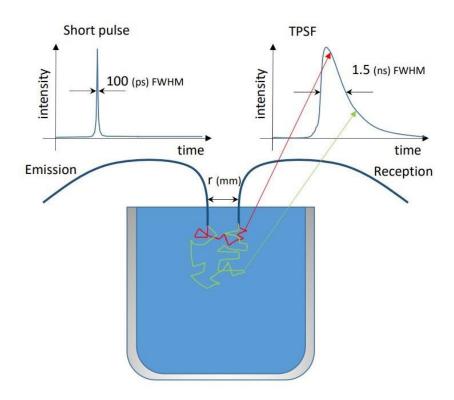

| Figure 7.17 Principle of Time-Resolved Optical Turbidity (TROT)161                                 |

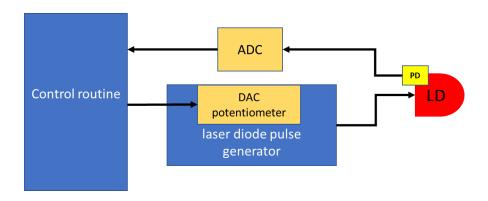

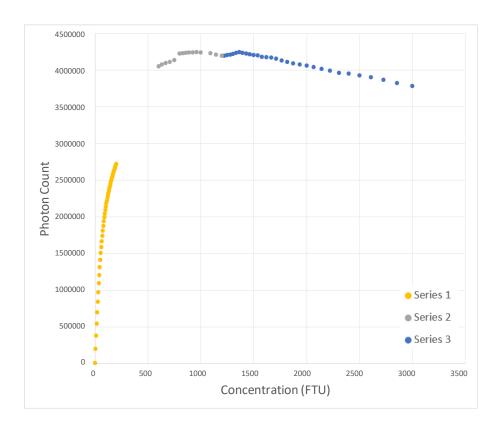

| Figure 7.18 Feedback control loop for stabilizing the laser power                                  |

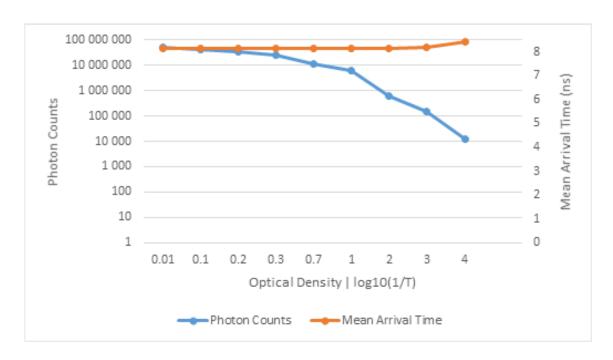

| Figure 7.19 Detected photon count as a function of concentration                                   |

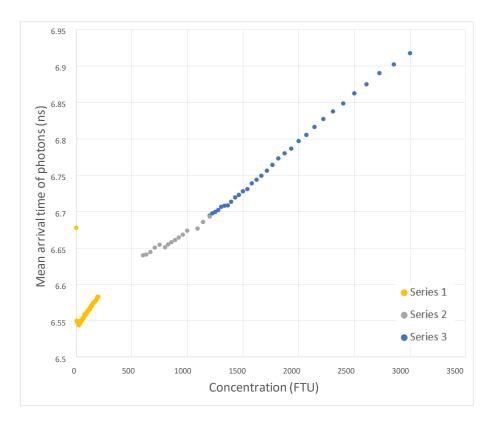

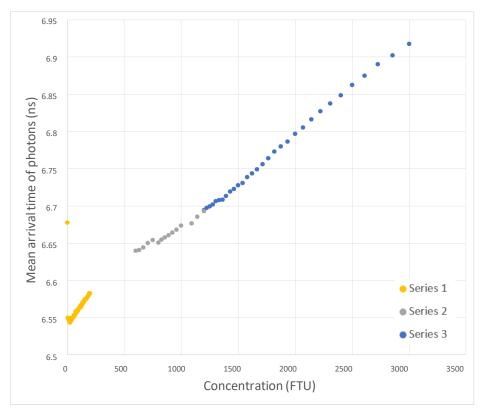

| Figure 7.20 Mean arrival time of detected photons as a function of concentration163                |

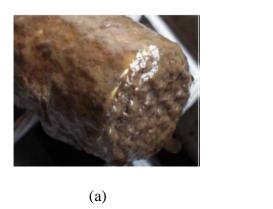

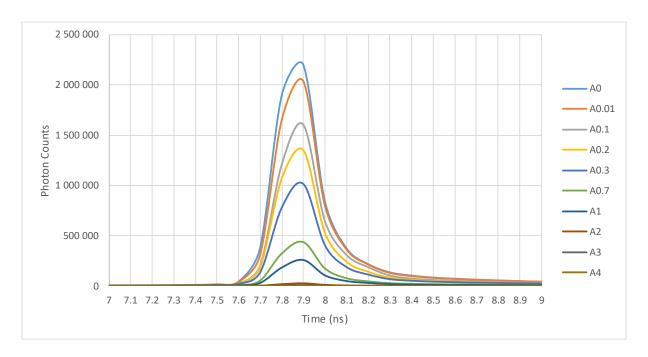

| Figure 7.21 Biofouling effect in optical turbidimeter: (a) after 30 days in a wastewater treatment |

| plant, (b) after ultrasonic cleaning                                                               |

| Figure 7.22 Simulating different levels of biofouling by inserting optical attenuators with        |

| different optical densities between the laser diode and the SPAD164                                |

| Figure 7.23 Laser pulse recorded at different levels of attenuation that simulate different levels |

| of biofouling                                                                                      |

| Figure 7.24 Photon count and mean arrival time of photons of the signals recorded at different     |

| levels of attenuation                                                                              |

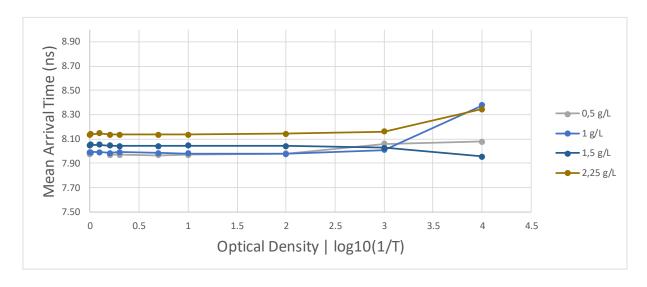

| Figure 7.25 Mean arrival times of detected photons at different turbidity and attenuation levels.  |

| 166                                                                                                |

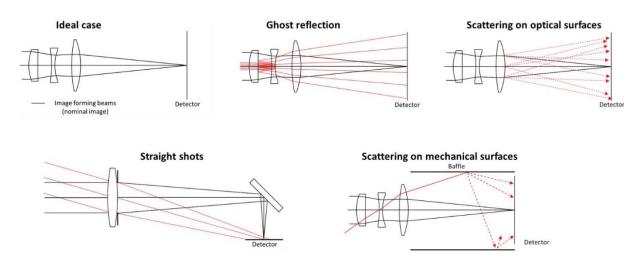

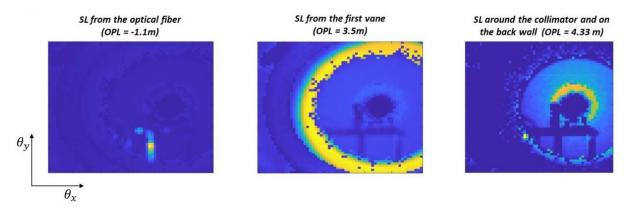

| Figure 7.26 Illustration of different types of stray light effects                                 |

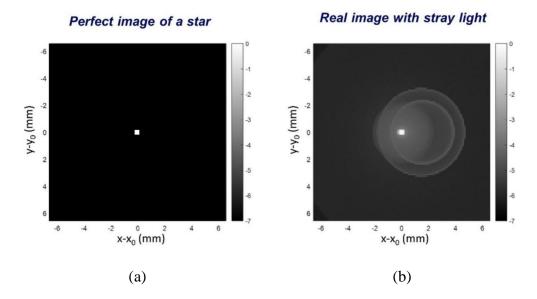

| Figure 7.27 An example of the stray light effect: (a) perfect image of a star, (b) realistic image |

| of that star with stray light effects                                                              |

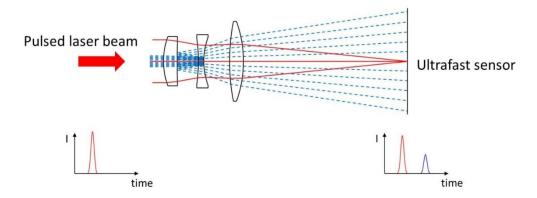

| Figure 7.28 Illustration of TOF-based stray light characterization: when a pulsed beam             |

| illuminates the optical system, the nominal beam and the different ghost paths reach the detector  |

| at different times due to their different optical path lengths                                     |

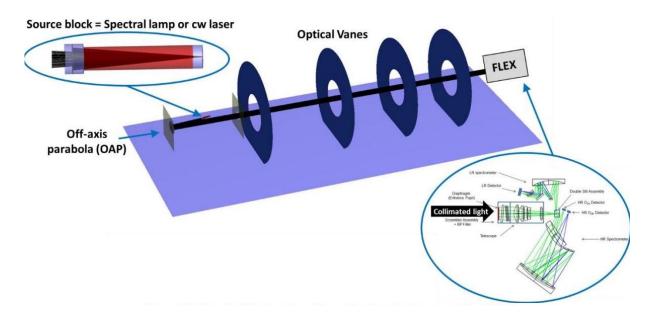

| Figure 7.29 (a) Optical calibration facility in a vacuum chamber, (b) Sketch of the FLEX           |

| mission spectro-imager                                                                             |

| Figure 7.30 Three-dimensional sketch of the optical calibration facility with the FLEX             |

| instrument 171                                                                                     |

#### List of Figures

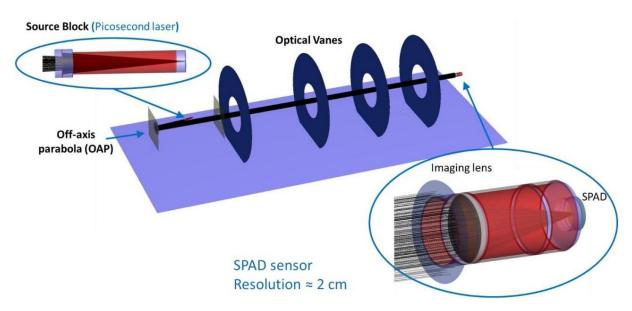

| Figure 7.31 Experimental setup: the FLEX instrument is replaced by the SPAD of the TC                | SPC   |

|------------------------------------------------------------------------------------------------------|-------|

| system to validate the characterization facility.                                                    | .171  |

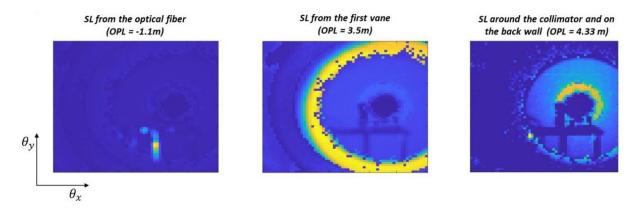

| Figure 7.32 Illustration of stray light pattern arriving at the SPAD detector at different momentum. | ents, |

| showing different stray light contributors.                                                          | .172  |

| Figure 7.33 Stray light from the facility arriving at the same moment as the nominal                 | .173  |

| Figure 7.34 Picture of the SPAD front side, showing the sensitive area and the surroun               | ding  |

| window.                                                                                              | .173  |

### **List of Tables**

| Table 2.1 Comparison of excitation light sources                                            |

|---------------------------------------------------------------------------------------------|

| Table 2.2 Comparison of different implementation methods of TDCs37                          |

| Table 3.1 Coarse value selection rules based on the fine value                              |

| Table 5.1 DNL and INL statistics for the synchronous TDC model, calculated for the raw      |

| histogram and the calibrated histograms of the bin-by-bin and average-bin-width calibration |

| methods                                                                                     |

| Table 5.2 DNL and INL statistics for the asynchronous TDC model, calculated for the non-    |

| calibrated histogram and the calibrated histograms using bin-by-bin and Matrix calibration  |

| methods                                                                                     |

| Table 5.3 Calibration processing speed comparison between the bin-by-bin and the Matrix     |

| calibration                                                                                 |

| Table 6.1 Gain error values in synchronous TDC at different temperatures130                 |

| Table 8.1 Performance parameters of the TCSPC system in synchronous mode176                 |

| Table 8.2 Performance parameters of the TCSPC system in asynchronous mode                   |

## **Abbreviations**

| ACP  | Accelerator Coherency Port                   |

|------|----------------------------------------------|

| ADC  | Analog-to-Digital Converter                  |

| ALM  | Adaptive Logic Module                        |

| APD  | Avalanche Photodiodes                        |

| API  | Application Programming Interface            |

| ASIC | Application-Specific Integrated Circuit      |

| CDPU | Control and Data Processing Unit             |

| CFD  | Constant Fraction Discriminator              |

| CMOS | Complementary Metal-Oxide-Semiconductor      |

| COG  | Center Of Gravity                            |

| CPU  | Central Processing Unit                      |

| CSL  | Center spatial de liege                      |

| DAC  | Digital-to-Analog Converter                  |

| DCR  | Dark Count Rate                              |

| DFF  | D Flip-Flop                                  |

| DMA  | Direct Memory Access                         |

| DNL  | Differential Nonlinearity                    |

| DOT  | Diffuse Optical Tomography                   |

| DSP  | Digital Signal Processing                    |

| EOM  | Electro-Optic Modulator                      |

| FACS | Fluorescence-Activated Cell Sorting          |

| FIDA | Fluorescence Intensity Distribution Analysis |

| FIFO | First In First Out                           |

| FLIM | Fluorescence Lifetime Imaging Microscopy     |

| FLT  | Fluorescence Lifetime                        |

| FOV  | Field Of View                                |

| FPGA | Field-Programmable Gate Array                |

| FRET | Förster Resonance Energy Transfer            |

| FWHM | Full Width at Half Maximum                   |

| HDL   | Hardware Descriptions Language     |

|-------|------------------------------------|

| HPS   | Hard Processor System              |

| HTS   | High-throughput screening          |

| HWLIB | Hardware Library                   |

| INL   | Integral Nonlinearity              |

| IP    | Intellectual Property              |

| IRF   | Instrument Response Function       |

| LAB   | Logic Array Block                  |

| LIDAR | Light Detection And Ranging        |

| LSB   | Least Significant Byte             |

| LUT   | Lookup Table                       |

| MLE   | Maximum Likelihood Estimator       |

| MMU   | Memory Management Unit             |

| MPU   | Microprocessor Unit                |

| OAS   | Optical Analysis System            |

| PAH   | Polycyclic Aromatic Hydrocarbon    |

| PBS   | Phosphate-Buffered Saline          |

| PDMS  | Polydimethylsiloxane               |

| PIO   | parallel I/O                       |

| PLL   | Phase-Locked Loop                  |

| PMT   | Photomultiplier Tube               |

| PVT   | Process, Voltage and Temperature   |

| QE    | Quantum Efficiency                 |

| QY    | Quantum Yield                      |

| RCU   | Replaceable Concentrator Unit      |

| RL    | Register Line                      |

| RMS   | Root Mean Square                   |

| SCU   | Snoop Control Unit                 |

| SER   | Single Electron Response           |

| SNR   | Signal-to-Noise Ratio              |

| SPAD  | Single-Photon Avalanche Diode      |

| SPI   | Serial Peripheral Interface        |

| SPST  | Spatial Point Source Transmittance |

| STD   | Standard Deviation                 |

| TAC   | Time-to-Amplitude Converter        |

|       |                                    |

| TCSPC | Time-Correlated Single Photon Counting        |

|-------|-----------------------------------------------|

| TDC   | Time-to-Digital Converter                     |

| TDL   | Tapped Delay Line                             |

| TOF   | Time Of Flight                                |

| TPSF  | Temporal Point Spread Function                |

| TROT  | Time-Resolved Optical Turbidity               |

| TSS   | Total Suspended Solids                        |

| TTS   | Transit Time Spread                           |

| UV    | Ultra-Violent                                 |

| VDL   | Vernier Delay Line                            |

| VHDL  | Very High-Speed Hardware Description Language |

| WFD   | Water Framework Directive                     |

| WPS   | Water Pollution Sensor                        |

### **Chapter 1: Introduction**

#### 1.1 Background

Time-correlated single photon counting (TCSPC) is a powerful technique for the recording of periodic optical signals with extremely high sensitivity, resolution, and precision. It is suitable for applications that deal with low-level signals, such as fluorescence decay measurements, light detection and ranging (LIDAR), and diffuse optical tomography (DOT).

TCSPC originated from the 'delayed coincidence' method, which was used to measure the lifetimes of excited nuclear states [1, 2]. In the 1960s, photon counting was applied in photon correlation spectroscopy for the measurement of diffusion coefficients [3]. In that time, flashlamps with short pulse widths of around 2 ns became available, which enabled the TCSPC technique [4]. The first application of TCSPC for the spectroscopy of excited molecules was reported in the early 1970s. Since then, this technique has been widely adopted for timeresolved spectroscopy, particularly for assessing fluorescence lifetimes in solutions [5-12]. Nonetheless, due to the low repetition rate of the light sources and the limited speed of the signal processing electronics in the 1970s and 1980s, the acquisition times were extremely long to integrate a sufficient number of photon counts [5, 6, 9, 11, 13, 14]. Furthermore, TCSPC was limited to be one-dimensional, and restricted to the recording of periodic light signals. Rapid advances in electronics and laser technology during the 1990s enabled significant increases in the repetition rate and power of pulsed light sources. This in turn led to important improvements in TCSPC systems in terms of measurement speed, accuracy, and sensitivity. Furthermore, the development of laser scanning confocal microscopes and the arrays of photon detectors allowed the implementation of multidimensional TCSPC systems for further applications, such as fluorescence lifetime imaging (FLIM) [15, 16].

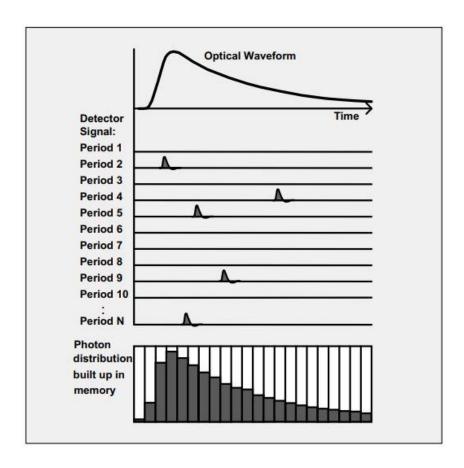

The general principle of TCSPC is illustrated in Figure 1.1. It is based on the detection of single photons of a periodic optical signal, the measurement of the relative arrival time of the detected photons within the signal period, and the creation of a histogram from the arrival times. By accumulating a large number of photon counts, the constructed histogram represents the waveform of the periodic signal [10, 17]. This technique requires a low intensity and a high

repetition rate of the signal so that the probability of detecting one photon in one signal period is much less than one. Typically, an average count rate of 0.01 to 0.1 photon/period is acceptable [12]. Much higher count rates would lead to distortions in the recorded signal due to the pile-up effect.

Figure 1.1 General principle of time-correlated single photon counting [14].

TCSPC has a broad range of applications in various scientific research and industrial fields such as physics, biology, and engineering. Some of the main applications are:

1- Time-resolved fluorescence lifetime measurement: fluorescence lifetime is the time required for a population of excited molecules to decrease exponentially by a factor of e as a result of fluorescence, i.e. emitting photons, and other nonradiative processes [18]. In biology, fluorescence measurement is a powerful tool to observe biological processes [19]. Fluorescence characteristics of dyes or other molecules are influenced by the reactions taking place. The fluorescence intensity depends on the reaction under study. However, it also depends on the probing volume and many other parameters such as the concentration and the excitation light intensity. In contrast, fluorescence lifetime (FLT)

is an intrinsic property that is independent of these parameters [20]. Hence, fluorescence lifetime measurement provides more reliability than intensity measurement, and it has various applications in many fields such as biochemistry, environmental sensing, and biomedical analysis [21].

TCSPC is a typical method for measuring fluorescence lifetime with high temporal resolution. It is used in a wide variety of applications, such as single-point spectroscopy [22], fluorescence lifetime imaging microscopy (FLIM) [23, 24], and Forster Resonance Energy Transfer (FRET) [25].

- 2- Light detection and ranging (LIDAR) applications: LIDAR is a popular technique for distance determination based on the time of flight (TOF) measurement [26, 27]. The LIDAR technique is widely applied in numerous areas, including autonomous vehicles, industrial robots, drones [28], augmented reality [29], and space science [30]. In LIDAR systems, a light source, usually a laser, emits short pulses. A portion of the emitted light is reflected back by the target object and detected by a photon detector. The time interval between the emission and detection is measured by a time-to-digital converter (TDC) and is then used to calculate the distance to the target [31]. TCSPC-based LIDAR provides high-precision depth measurement with high sensitivity to low-level signals.

- 3- Quantum measurements: The TCSPC technique is an essential tool for various emerging quantum technologies, such as quantum imaging and sensing, quantum-state preparations, quantum cryptography, and emission tomography [32].

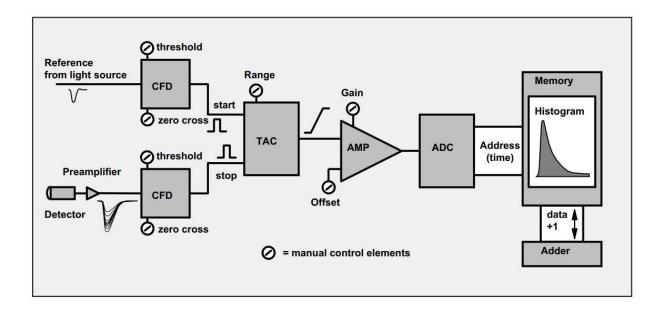

Figure 1.2 shows the architecture of a classic TCSPC setup. A photon detector, commonly a single photon avalanche diode (SPAD) or a photomultiplier tube (PMT), generates a pulse for each detected photon, which is called the *STOP* signal. However, if a PMT is used as the photon detector, a constant fraction discriminator (CFD) should be used to reduce the timing jitter resulting from the amplitude jitter of the PMT [33].

A photodiode is generally used to generate the reference signal, i.e. the *START* signal, synchronous with the excitation light pulses. A second CFD is used to reduce the timing jitter of the *START* signal.

A timing channel measures the arrival time of the detected photons as follows: a time-to-amplitude converter (TAC) receives the *START* and *STOP* signals and generates an analog signal with an amplitude proportional to the time interval between these signals. The output of the TAC is then amplified and fed to an analog-to-digital converter (ADC) to be converted into

a digital value representing the photon arrival time. The digital value serves as an address for a memory unit. Each memory location corresponds to a specific time bin and stores the number of photons detected within that bin. When a photon is detected, the number of counts in the addressed memory location corresponding to its arrival time is incremented by one. Thus, a histogram representing the temporal distribution of the detected photons throughout the measurement is built up in the memory. Finally, the measurement histogram is sent to a PC for further data processing, for instance, computing the fluorescence lifetime.

Figure 1.2 Classic TCSPC setup [14].

Traditional TCSPC systems have many limitations such as high cost, bulky size, and low pulse repetition rates and detection rates. To overcome these limitations, integrated TCSPC systems have been developed to replace the discrete electronics of classic TCSPC systems. The dead time was reduced and the count rate was improved by integrating arrays of SPADS, high-throughput fully digital TDC, and embedded signal processing on a single silicon chip as an application-specific integrated circuit (ASIC) [34]. Furthermore, recent advances in FPGA technology have enabled the implementation of high-performance TCSPC systems with high-resolution TDCs. In recent years, FPGA-based TCSPC systems have been the focus of many scientific research works [35-37].

#### 1.2 Research Aim

The aim of this thesis is to design and implement a versatile TCSPC system on a low-cost SoC-FPGA platform that can be employed in different applications. The TCSPC technique is used

in a wide variety of applications in various fields. However, each application requires specific customizations and different post-processing of the measurement histogram data. Moreover, in typical TCSPC systems, the measurement histogram is transferred to a PC for data processing. The limited transfer rate of the interface between the system electronics and the PC creates a bottleneck that limits the system performance and prevents real-time operation. Implementing the data processing, including calibration, background suppression and post-processing, on an ASIC is a complex, inflexible, and expensive approach. On the other hand, the recent advancement in technology enables the integration of powerful hard processor systems with FPGA fabrics in a single chip, creating System-on-Chip FPGAs (SoC-FPGAs) [36]. These devices are available at low cost and offer an excellent platform for the development of high-performance hardware/software co-processing applications. This research addresses the limitations of TCSPC systems in terms of cost and versatility, by taking advantage of the features of SoC-FPGA platforms, such as low cost, flexibility, short development time, and the embedded hard processor system. The objectives of this research are:

- To design and implement two time-to-digital converters (TDCs) with high-resolution and low-nonlinearity for TCSPC systems on a low-cost SoC-FPGA kit. These TDCs should be able to measure the arrival time of photons with high accuracy and at high rates and to operate with different light sources: one for synchronous sources and the other for asynchronous ones.

- To realize a high-speed data transfer system based on direct-memory-access (DMA) for the data transfer between the FPGA and the embedded processor. This design should ensure transferring the time measurement data at a high rate that enables real-time operation.

- To develop a bare-metal C program that runs on the embedded processor and performs all the data processing, including the TDC calibration, the different histogram corrections, and the data post-processing, onboard which enables supporting applications that require real-time operation.

- To evaluate the performance of the proposed TCSPC system in terms of speed, accuracy, resolution, and linearity.

- To demonstrate the versatility of the system by deploying it in four different applications which are: a water pollution sensor (WPS), time-resolved optical turbidity (TROT), high-throughput microfluidic droplet screening and sorting, and stray light characterization.

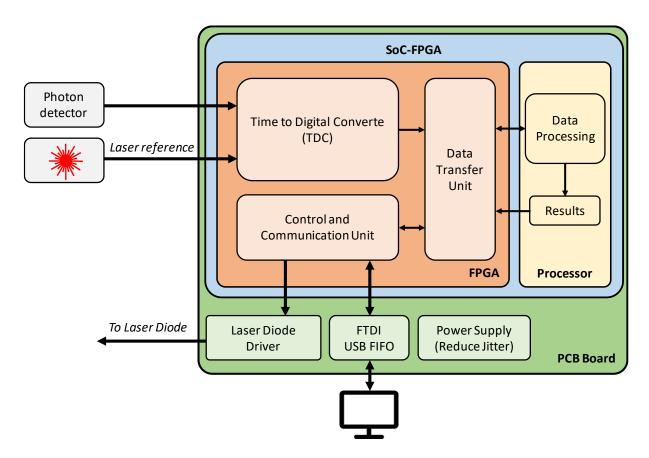

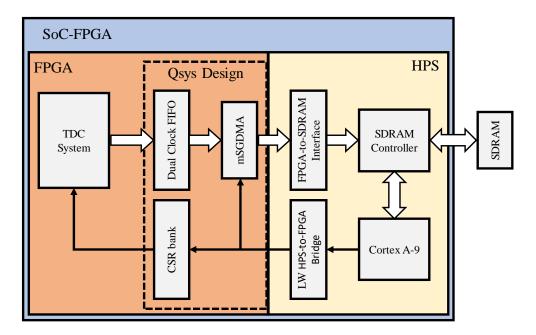

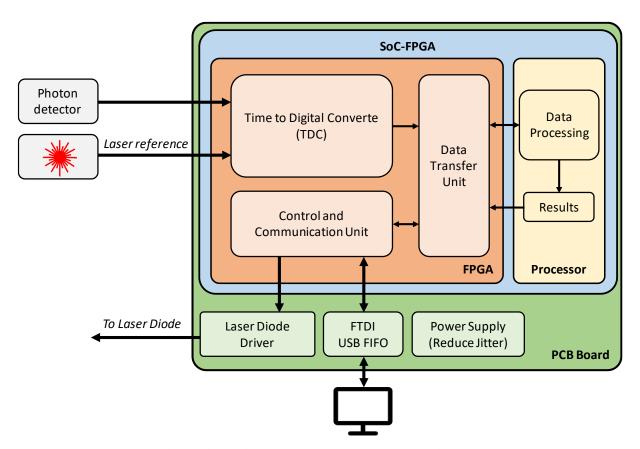

Figure 1.3 shows a schematic diagram of the proposed co-design of the TCSPC system. The TDC design will be implemented on the FPGA logic, while the Data processing will be executed on the hard processor system of the SoC-FPGA platform. The system will also integrate a custom-built PCB motherboard that supplies stable power to the SoC-FPGA, enables USB communications with the PC, and incorporates a laser diode pulse generator, among other components.

Figure 1.3 Schematic diagram of the proposed hardware/software co-design of the TCSPC system.

#### 1.3 Contributions

The main contributions of this thesis are as follows:

- It presents the design and the implementation of two TDCs, a synchronous one and an asynchronous one, on a low-cost Cyclone V FPGA with a temporal resolution of about 20 ps and a high linearity.

- It proposes and implements an innovative calibration method for asynchronous TDCs that improves the linearity by up to an order of magnitude compared to the conventional bin-by-bin method applied to histograms.

• It develops a robust method for the detection of microfluidic droplets at high rates and in real-time. This method enables the TCSPC system to be applied for high-throughput droplet screening at more than 3500 droplets/second based on the fluorescence lifetime, which surpasses the droplet rate achieved by a more complex and costly system reported in the literature.

These contributions advance the state-of-the-art in FPGA-based TCSPC systems and high-throughput droplet screening and provide a low-cost, flexible, high-performance solution for various applications that require high-precision time measurement and droplet analysis.

#### 1.4 Outline

This thesis presents the design and implementation of a versatile TCSPC system on a low-cost FPGA. The remainder of this thesis is organized as follows:

Chapter 2 provides a comprehensive review of the literature on the TCSPC technique and the TDCs, which are the key components of TCSPC systems. It explains the operating principle, characteristics, and the various architectures of TDCs.

Chapter 3 presents the design and implementation of a synchronous and an asynchronous FPGA-based TDC, and proposes solutions to address the challenges encountered due to the limitations of low-cost FPGAs. It also proposes methods to enhance the TDC linearity, which is one of the most critical characteristics.

Chapter 4 discusses a hardware/software co-design for the transmission of measurement data from the TDC FIFO buffer in the FPGA to the SDRAM of the embedded processor. It also discusses the different data processing algorithms implemented in the C program, including the creation of histograms, the elimination of the background signal and the other noise sources, as well as the different data post-processing algorithms.

Chapter 5 discusses in detail the calibration of the two types of TDC. In addition, it proposes, verifies, and evaluates a novel and innovative method for the calibration of asynchronous TDCs.

Chapter 6 reports the experimental results obtained for the characterization of the designed TDCs in terms of linearity, precision, accuracy, and stability. Moreover, the reliability and accuracy of the TCSPC system are assessed by performing a basic fluorescence lifetime measurement of a standard fluorophore.

Chapter 7 evaluates the versatility of the designed TCSPC system by deploying it in four applications from different fields. This chapter analyzes the specific requirements of each application and proposes optimizations and improvements that enable the system to meet these requirements.

Chapter 8 presents a conclusion and some perspectives for future research.

# **Chapter 2: Literature Review**

The principle of the TCSPC technique is based on the detection of single photons of a periodic optical signal, the measurement of the detection time of these photons within the signal period, and finally the reconstruction of the light waveform from the statistical distribution of the individual time measurements, after repeating the measurements for a sufficient number of times. As demonstrated in the introduction, a TCSPC system includes three essential components: a pulsed light source, a single photon detector, and a time-to-digital converter (TDC). This chapter first discusses the figures of merit of the TCSPC technique, then provides a literature review of the main components of TCSPC systems, with a particular focus on the TDC, as one of the major contributions of this thesis is the design of an FPGA-based TDC.

# 2.1 TCSPC Technique

The TCSPC technique relies on the fact that, for a low-level high-repetition-rate signal, the photon flux is so weak that the probability of detecting a single photon during one signal period is much less than one [38]. The detector output, in this case, is a sequence of pulses randomly distributed along the experiment time corresponding to the detection instances of the individual photons. With these considerations, there would be many signal periods with no photon pulse, while others would contain one photon pulse, and the periods with more than one pulse would be extremely rare.

To appreciate the merits of TCSPC, it is compared with the direct alternative technique for the recording of optical signals, which is the analog technique. Analog recording interprets the detector signal as an analog waveform. The detector signal is first sampled at short time intervals, then digitized, and accumulated throughout many signal periods. The signal-to-noise ratio (SNR) is determined by the square root of the number of photons N within the impulse response time of the detector. At low intensity, this ratio drops far below one and the baseline instability and the electronic noise limit the number of accumulations and hence the sensitivity of the analog recording system. Obviously, analog recording is more suitable for low-repetition-rate and high-intensity signals. For instance, in fluorescence decay measurement, this can be achieved by using low-frequency high-peak-power pulsed lasers for the excitation of the studied

samples. However, this might lead to saturation effects in the sample, nonlinearity errors, and long-term degradation of the detector performance [39]. On the other hand, in the TCSPC technique, the signal intensity is determined by the pulse density of the detector signal rather than its amplitude. Each detected photon generates a pulse at the detector output and thus a photon count that contributes to the final measurement histogram. This leads to an almost ideal counting efficiency and thereby to an optimum SNR value for a given number of detected photons.

In analog recording, the width of the instrument response function (IRF) cannot be shorter than the single electron response (SER) of the detector. Thus, the bandwidth of an analog recording system is limited by that of the used detector. In contrast, in the TCSPC technique, the arrival time of the photon pulse rising edge is measured with high precision to construct the histogram. Therefore, the resolution is not limited by the width of the detector SER but rather by the accuracy of the arrival time measurement, and the bandwidth is only limited by the transit time spread (TTS) of the pulses in the detector, which is usually an order of magnitude shorter than the SER width. Consequently, for a given detector, the TCSPC technique yields a higher bandwidth and a shorter IRF than the analog recording method.

Another advantage of the TCSPC technique over analog recording is its immunity to the gain noise of the photon detector. In practice, a TCSPC system counts all the detected photons with the same weight regardless of their pulse amplitude, so the SNR is not influenced by the gain noise of the detector. In contrast, the analog recording technique is highly sensitive to this noise, as the magnitude of the detector signal is directly affected by the gain fluctuations due to the variations in the supply voltage.

## 2.2 Pulsed Light Sources

In early TCSPC systems, nanosecond flashlamps were used as excitation light sources [40, 41]. However, these sources had several limitations, such as low repetition rate, low excitation power, and large pulse width, which made them unsuitable for the measurement of short lifetimes and increased the measurement acquisition time. Nonetheless, flashlamps had the advantage of providing almost any excitation wavelength when coupled with a monochromator.

Modern fluorescence measurement devices use pulsed lasers as the excitation light source, such as mode-locked argon and frequency-multiplied Nd:YAG lasers. However, these sources offer a limited number of discrete wavelengths. This drawback was partly overcome by synchronously pumped jet-stream dye lasers [42]. Pulsed lasers provide short pulses with a

pulse width of less than 100 ps and a high repetition rate of up to 120 MHz. Nevertheless, these laser systems are costly, complex, and require constant maintenance.

The next advancement in pulsed light sources was the development of titanium-sapphire (Ti:Sa) lasers. These lasers offer tunable wavelengths, high repetition rates, ultra-short pulse durations in the picosecond and femtosecond range, and virtually unlimited power peaks [43]. In addition, these lasers enable the generation of UV wavelengths by frequency doubling and tripling [44]. In fact, Ti:Sa lasers are almost ideal excitation light sources for fluorescence measurement. However, the high cost of these lasers is the only drawback.

Recently, picosecond laser diodes have become the most widely used excitation light sources in TCSPC systems [45-48]. They have many advantages over other sources, such as low cost and high reliability, and require no maintenance or alignment [49]. Laser diodes are available with a wide range of discrete wavelengths that can match the absorption spectra of various fluorophores. Moreover, tunable wavelengths can be generated by swapping lasers of different wavelengths, or by combing the beams of several lasers optically and selecting the desired laser electronically.

# 2.2.1 Adopted Pulsed Light Sources

We used different pulsed light sources in our TCSPC system depending on the application. For the stray light characterization, a picosecond pulsed laser with a wavelength of 532 nm and a repetition rate of 21.42 MHz was used. For the other applications, pulsed laser diodes with different wavelengths were coupled with a high-repetition-rate pulse generator [50]. A 405-nm laser diode served as the light source for the demonstration of the water pollution sensor and the microfluidic droplet sorting. However, this wavelength is not optimal for the excitation of the target pollutants and fluorophores. For the time-resolved optical turbidimeter, a wavelength of 530 nm was used.

#### 2.3 Photon Detectors

Photon detectors can be categorized into two main types based on the photoelectric effect mechanism:

Detectors that rely on based on the external photoelectric effect, where a photocathode emits photoelectrons upon the absorption of a photon, such as photomultiplier tubes (PMTs), microchannel plate photomultipliers (MCP-PMTs), and hybrid photomultiplier tubes (HPMTs). 2) Detectors that rely on the internal photoelectric effect, where photoelectrons are generated internally within the detector material when a photon is absorbed, such as single-photon avalanche diodes (SPADs) and superconducting nanowire single-photon detectors (SNSPDs) [51].

The choice of the photon detector depends on the specifications and requirements of the target application, such as the photon rate, the wavelength, range, and the temporal resolution. The photon detectors are usually characterized by the following key parameters:

## 1- Quantum efficiency (QE):

Quantum efficiency, also referred to as detection efficiency, describes the sensitivity of the detectors. It is the probability that an incident photon produces a measurable electrical pulse at the detector output. QE can also be defined as the ratio between the number of generated photoelectrons and the number of photons reaching the active area of the detector [52]. QE depends on the wavelength of the detected light [53], which is an important factor to consider for selecting an appropriate photon detector for a specific application.

#### 2- Dark count rate (DCR):

The dark count rate of a photon detector is the rate of false pulses generated at the detector output in the absence of incident photons. It is the count rate under complete darkness. Dark counts are random events that are independent of the detected photons. They have different origins according to the type of detector, such as thermionic emission, tunneling, or impurities in the detector material [54, 55]. DCR is affected by different factors, such as the bias level and the temperature. Dark counts are a major source of noise in the photon detector that affects its sensibility and overall performance. Therefore, it is important to choose a photon detector with a low DCR, especially when the detection of weak signals is required.

#### 3- Transit time spread (TTS) or Jitter:

The transit time is the time interval between absorbing a photon and the generation of an electrical pulse at the detector output. This interval is unstable and varies from one photon to another, resulting in the jitter of the detector. The jitter is a crucial parameter, especially for time-resolved applications, that affects the timing measurement precision and the temporal resolution of the TCSPC system [14].

#### 4- Afterpulsing probability:

Photon detectors may generate more than one electrical pulse for a single detected photon. Afterpulsing probability is the likelihood that the detector produces a second electrical pulse within a few microseconds following the photon pulse. Hence, afterpulsing counts are false counts that are temporally correlated with true counts. Afterpulsing is an important parameter that may cause serious problems at high repetition rates because afterpulsing counts generated during many signal periods cause a considerable signal-dependent background. Usually, afterpulsing probability is expressed as a percentage, indicating the probability that the detector generates an afterpulsing event following a real event after a given time interval.

Photomultiplier tubes (PMTs) and single-photon avalanche diodes (SPADs) are the most commonly used photon detectors in TCSPC systems. In the following, we present a brief review of these detectors.

## 2.3.1 Photomultiplier Tube (PMT)

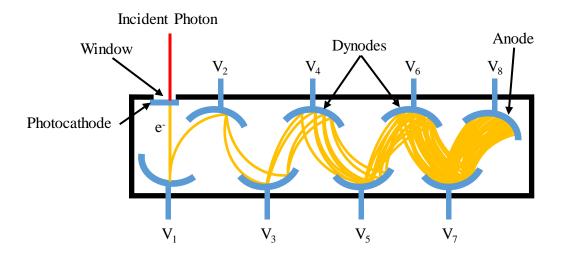

Photomultiplier tubes (PMTs) are conventional detectors for single-photon counting systems. PMTs were first demonstrated in the 1930s, after the development of photocathodes, secondary emissive surfaces, and electron multipliers [56]. A PMT typically consists of three main components enclosed in an evacuated glass tube: a photocathode, an electron multiplier (consisting of dynode stages), and an anode. When photons hit the photocathode, the latter emits photoelectrons into the vacuum by the external photoelectric effect. The photoelectrons are then amplified along the dynode stages by the secondary electron emission process. The photoelectron emitted by the photocathode is accelerated towards the first positively charged dynode, where it collides and releases more electrons. These electrons are then accelerated towards the next dynode, where they collide and cause the emission of more electrons, and so forth. Thus, this process significantly amplifies the signal, as the number of electrons increases with each dynode stage. The secondary electrons emitted from the last dynode stage are then collected by the anode which delivers the electron current to an external circuit. The anode current at the output of the PMT is proportional to the amount of light captured by the photocathode. At very low light intensities, the PMT output would be in the form of discrete, well-separated pulses that could be amplified and then processed by photon counting electronics.

There is a variety of dynode geometries with different gain, response time, and transit-time spread. The "linear focused dynodes" structure, depicted in Figure 2.1, is the most suitable structure for single-photon counting because it provides fast response and low jitter. The amplification process is very effective and typically yields gain values between 10<sup>6</sup> and 10<sup>7</sup> [57]. However, the dynode stages require high operating voltages of a few kV. Because of this, as well as the complex design of the multiple dynode stages, PMTs are relatively large and bulky detectors. Nevertheless, recent advancements have enabled the miniaturization of PMT designs and the integration of high-voltage power supplies into small compact units [58].

Figure 2.1 Operating principle of linear focused PMT.

In addition to their large size, PMTs typically have several drawbacks, such as the saturation at moderate light intensities, their substantial timing jitter, and their modest quantum efficiency.

- **Saturation:** PMTs are only suitable for very low-level optical signals. At high light intensities, the output pulses of individually amplified photoelectrons overlap and cannot be resolved as discrete pulses.

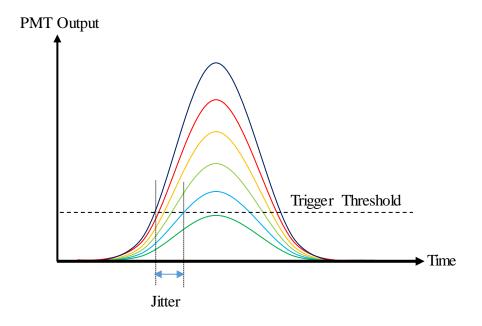

- **Substantial timing jitter:** the PMT output pulses have amplitude fluctuations due to variations in the amplification process of the dynodes. These fluctuations result in a timing jitter of the order of the pulse rise time, which necessitates the use of a constant fraction discriminator, as illustrated in Figure 2.2.

- Modest quantum efficiency: PMTs rely on the external photoelectric effect. The

disadvantage of this effect is that the photoelectrons are emitted in all directions,

including backward. Therefore, the quantum efficiency is always lower than 0.5. In

practice, the maximum achievable quantum efficiency is about 0.4 in the wavelength

range from 400 to 500 nm [59].

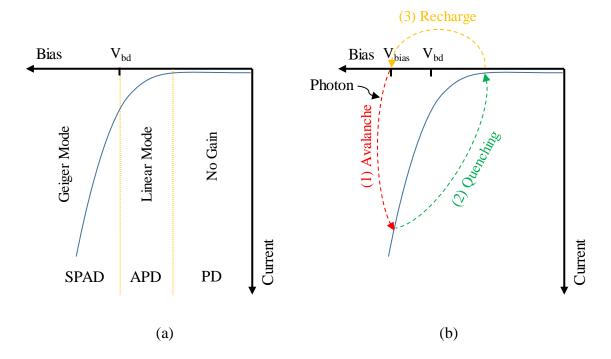

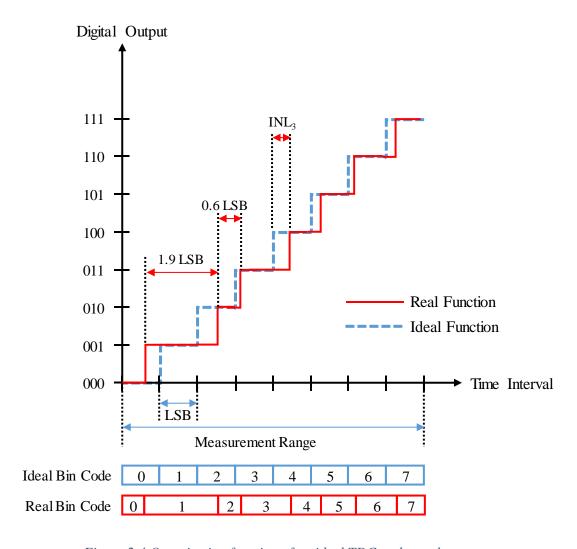

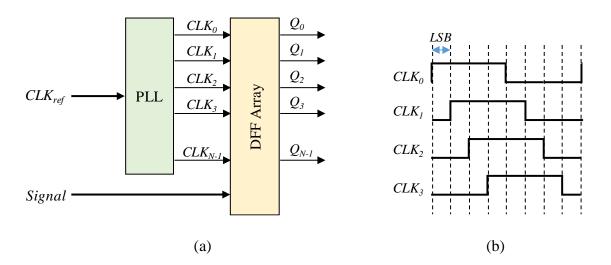

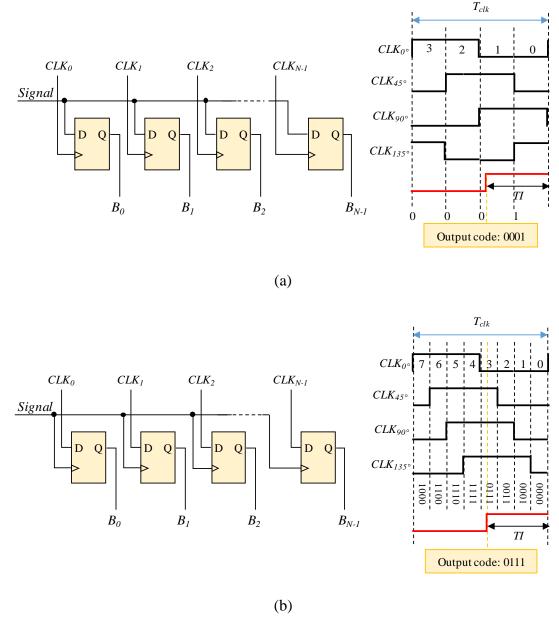

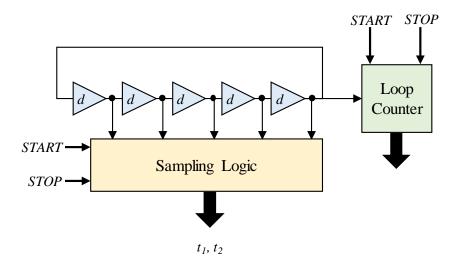

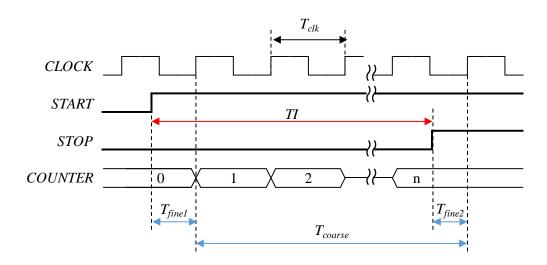

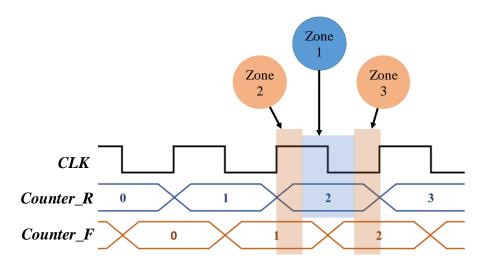

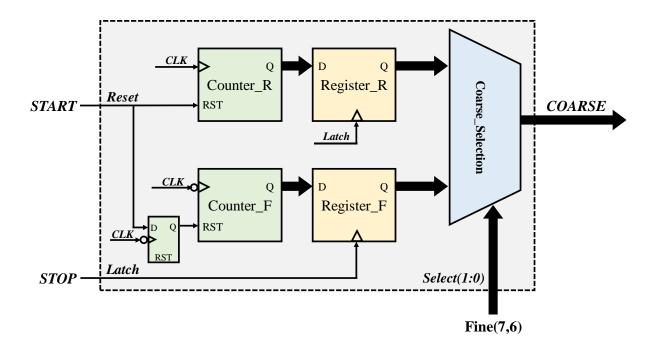

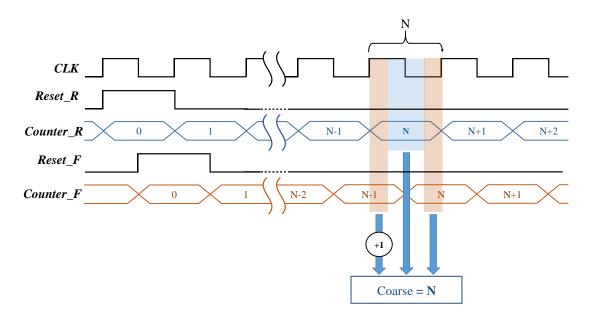

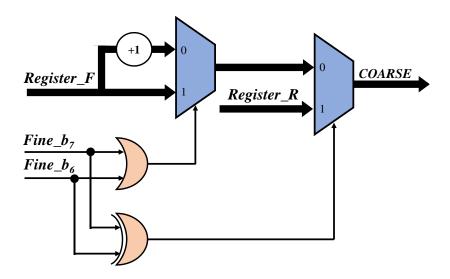

Figure 2.2 PMT timing jitter using a simple level trigger due to the amplitude fluctuation.