## Cross-Layer Fault Analysis for Microprocessor Architectures (CLAM)

Ihab Alshaer

#### ▶ To cite this version:

Ihab Alshaer. Cross-Layer Fault Analysis for Microprocessor Architectures (CLAM). Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes [2020-..], 2023. English. NNT: 2023GRALT062. tel-04417620

## HAL Id: tel-04417620 https://theses.hal.science/tel-04417620

Submitted on 25 Jan 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE

Pour obtenir le grade de

#### **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

École doctorale: EEATS - Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Spécialité : Nano électronique et Nano technologies

Unité de recherche : Laboratoire de conception et d'intégration des systèmes

# Analyse multi-niveaux des fautes dans les architectures de processeurs

**Cross-Layer Fault Analysis for Microprocessor Architectures (CLAM)**

Présentée par :

#### **Ihab ALSHAER**

#### Direction de thèse :

Vincent BEROULLE Directeur de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Paolo MAISTRI Co-encadrant de thèse

CHARGE DE RECHERCHE, Université Grenoble Alpes

Brice COLOMBIER Co-encadrant de thèse

MAITRE DE CONFERENCES, Université Jean-Monnet Saint-Étienne

#### Rapporteurs:

#### Jean-Max DUTERTRE

PROFESSEUR DES UNIVERSITES, Ecole Nationale Supérieure des Mines de Saint-Étienne **Pascal BENOIT**

MAITRE DE CONFERENCES HDR, LIRMM, CNRS, Université de Montpellier

#### Thèse soutenue publiquement le **16 octobre 2023**, devant le jury composé de :

Vincent BEROULLE Directeur de thèse

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Jean-Max DUTERTRE Rapporteur

PROFESSEUR DES UNIVERSITES, Ecole Nationale Supérieure des

Mines de Saint-Étienne

Pascal BENOIT Rapporteur

MAITRE DE CONFERENCES HDR, LIRMM, CNRS, Université de

Montpellier

Giorgio DI NATALE Examinateur

DIRECTEUR DE RECHERCHE, CNRS, Université Grenoble Alpes

Marie-Laure POTET Présidente

PROFESSEUR DES UNIVERSITES, Université Grenoble Alpes

Athanasios PAPADIMITRIOU Examinateur

ASSISTANT PROFESSOR, University of the Peloponnese, Greece

#### Invités:

#### Christophe DELEUZE

MAITRE DE CONFERENCES, Université Grenoble Alpes

## **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my thesis supervisors: Prof. Vincent Beroulle, Dr. Paolo Maistri, Dr. Brice Colombier, and Dr. Christophe Deleuze. Their invaluable assistance, kindness, and unwavering support throughout these years have been instrumental in my progress. They have broadened my perspective and greatly enhanced my ability to analyze and interpret various aspects.

I would also like to extend my appreciation to my CSI members: Prof. Jean-Max Dutertre and Prof. David Hély, for generously dedicating their time, providing insightful comments, and offering valuable feedback at the start of each year of my PhD journey.

I am also grateful to Prof. Jean-Max Dutertre and Dr. Pascal Benoit for taking the time to review my manuscript. I would also like to thank Prof. Giorgio Di Natale, Prof. Marie-Laure Potet, and Dr. Athanasios Papadimitriou for agreeing to be members of the jury for my defense.

Special thanks go to my colleagues in the LCIS and TIMA labs, particularly the members of the CTSYS team in LCIS and the AMFORS team in TIMA. I am thankful to Carole, Caroline, and Karine for their assistance with administrative matters during my PhD. Also, thanks a lot to Oumayma and Gijs for their contribution to my thesis during their internships.

Last but not least, I would like to express my heartfelt appreciation to my friends here in France and in Palestine, as well as my beloved family in Palestine. To my sister Nour, and my brothers Mohammed, Mohannad, Bahaa, and Tamer, your unwavering support and encouragement mean the world to me.

This thesis has been supported by the LabEx PERSYVAL-Lab (ANR-11-LABX-0025-01) and the French National Research Agency in the framework of the "Investissements d'avenir" program (ANR-15-IDEX-02). Finally, I would like to thank Arm for giving us the opportunity to deal with RTL descriptions for real IP cores under the Arm Academic Access Agreement.

"This thesis is dedicated to the soul of my mother Aisha, to my aunt Fatima, and to my father Basheer" Titre: Analyse multi-niveaux des fautes dans les architectures de processeurs

**Mot clés :** Sécurité matérielle, Attaques par injection de fautes, Modélisation des fautes, Simulation des fautes RTL, Jeu d'instructions de longueur variable, Analyse de vulnérabilités

Avec l'utilisation de plus en plus répandue des systèmes embarqués, les concepteurs matériels et les développeurs de logiciels accordent une attention croissante aux problèmes de sécurité afin de protéger ces dispositifs contre les menaces potentielles. Parmi ces menaces, les attaques physigues représentent un risque important, et les attaques par injection de fautes sont parmis les méthodes les plus puissantes dans ce cadre. Cependant, une mauvaise compréhension de l'impact causé par l'injection de fautes peut conduire à proposer des contre-mesures excessives ou insuffisantes pour ces dispositifs. Cela affecte négativement le rapport performance/coût et/ou la sécurité globale du dispositif. Pour relever ce défi, des modèles de fautes réalistes sont indispensables pour comprendre les effets de l'injection de fautes. Ces modèles jouent un rôle crucial dans l'analyse des vulnérabilités potentielles des codes logiciels et des blocs matériels, ce qui permet de protéger les systèmes numériques contre de telles attaques tout en assurant un surcoût maîtrisé. Cependant, se fier uniquement à des observations empiriques de microprocesseurs où des fautes sont injectées pose des défis lors de l'inférence des modèles de fautes, limitant ainsi notre compréhension des effets causés par ces fautes.

Cette thèse présente des preuves expé-

rimentales qui mettent en évidence les défis liés à la caractérisation et à la modélisation des effets de l'injection de fautes lorsqu'on considère un seul niveau d'abstraction du système. Pour relever cette limitation, une approche d'analyse multi-niveaux est introduite pour combler le fossé entre les études précédentes et permettre une meilleure compréhension des effets des fautes. De plus, cette thèse démontre la mise en œuvre réussie de cette méthodologie, aboutissant à l'inférence de nouveaux modèles de fautes, réalistes et précis, à la fois au niveau logiciel et matériel. De plus, l'applicabilité de ces modèles de fautes est mise en évidence pour différents programmes, cibles matérielles et techniques d'injection de fautes. Enfin, cette thèse illustre comment ces modèles de fautes peuvent être exploités pour effectuer une analyse de vulnérabilité de codes logiciels, permettant ainsi de développer des contre-mesures efficaces pour un coût maîtrisé.

Cette thèse a été réalisée dans le cadre du projet CLAM en collaboration entre le laboratoire LCIS à Valence et le laboratoire TIMA à Grenoble. Cette thèse a été supervisée par Prof. Vincent Beroulle (LCIS) et co-supervisée par Dr. Paolo Maistri (TIMA), Dr. Brice Colombier (LabHC) et Dr. Christophe Deleuze (LCIS).

Title: Cross-Layer Fault Analysis for Microprocessor Architectures (CLAM)

**Keywords:** Hardware security, Fault injection attacks, Fault modeling, RTL fault simulation, Variable-length instruction set, Vulnerability analysis.

**Abstract:** With the widespread use of embedded system devices, hardware designers and software developers started paying more attention to security issues in order to protect these devices from potential threats. Among these threats, physical attacks pose a significant risk, with fault injection attacks being a very powerful attack method. Nevertheless, an inaccurate understanding of the impact caused by fault injection can result in the proposal of either excessive or insufficient protections for these devices. This, in turn, adversely affects the performance/cost ratio and/or the overall device security. address this challenge, realistic fault models are indispensable for comprehending the effects of fault injection. Such models play a crucial role in analyzing potential vulnerabilities in software codes and hardware designs, thereby enabling the protection of digital systems against such attacks while maintaining cost-effectiveness. However, relying solely on limited observations of faulty microprocessors poses challenges when inferring fault models, ultimately limiting our understanding of the effects caused by these faults.

This thesis presents experimental evi-

dence that highlights the challenges in characterizing and modeling the effects of fault injection when considering a single layer of system levels. Therefore, a cross-layer analysis approach is introduced to bridge the gap between previous studies and enable a better understanding of the effects of the faults. Furthermore, the thesis demonstrates the successful implementation of this methodology, resulting in the inference of reliable and novel fault models at both software and hardware levels of abstraction. Moreover, the applicability of these fault models is showcased across various target programs, target devices, and different fault injection techniques. Finally, the thesis illustrates how these fault models can be leveraged to perform vulnerability analysis of software codes, offering the capability to develop suitable and cost-effective countermeasures.

This thesis has been performed under the CLAM project in a joint position between LCIS lab in Valence and TIMA lab in Grenoble. It has been supervised by Prof. Vincent Beroulle (LCIS) and co-supervised by Dr. Paolo Maistri (TIMA), Dr. Brice Colombier (LabHC), and Dr. Christophe Deleuze (LCIS).

## **TABLE OF CONTENTS**

| In | trodu | ction   |                                                           | 11 |

|----|-------|---------|-----------------------------------------------------------|----|

| 1  | Stat  | e-of-th | e-art                                                     | 15 |

|    | 1.1   | Timing  | g constraints in a digital circuit                        | 15 |

|    | 1.2   | Timing  | g-based fault injection                                   | 17 |

|    |       | 1.2.1   | Clock glitch fault injection                              | 17 |

|    |       | 1.2.2   | Voltage glitch fault injection                            | 19 |

|    |       | 1.2.3   | Electromagnetic fault injection                           | 21 |

|    |       | 1.2.4   | Heating fault injection                                   | 22 |

|    |       | 1.2.5   | Summary                                                   | 23 |

|    | 1.3   | Fault i | njection effect analysis and modeling                     | 23 |

|    |       | 1.3.1   | Random fault effect                                       | 24 |

|    |       | 1.3.2   | Fault effect analysis at ISA and microarchitecture levels | 27 |

|    |       | 1.3.3   | Fault effect analysis at lower levels of abstraction      | 30 |

|    |       | 1.3.4   | Summary                                                   | 32 |

|    | 1.4   | Concl   | usion                                                     | 33 |

| 2  | The   | need f  | or cross-layer analysis and proposed methodology          | 35 |

|    | 2.1   | Exper   | imental evidence                                          | 35 |

|    |       | 2.1.1   | Experimental Setup                                        | 36 |

|    |       | 2.1.2   | Experimental results                                      | 40 |

|    |       | 2.1.3   | Discussion                                                | 47 |

|    | 2.2   | Propo   | sed methodology                                           | 50 |

|    |       | 2.2.1   | Physical fault injection                                  | 51 |

|    |       | 2.2.2   | RTL fault simulation                                      | 52 |

|    |       | 2.2.3   | Software fault simulation                                 | 53 |

|    |       | 2.2.4   | Discussion                                                | 54 |

|    | 2.3   | Fault r | models evaluation                                         | 56 |

|    |       | 2.3.1   | Coverage                                                  | 56 |

### TABLE OF CONTENTS

|   |      | 2.3.2   | Fidelity                                                    | 57  |

|---|------|---------|-------------------------------------------------------------|-----|

|   |      | 2.3.3   | Complexity                                                  | 57  |

|   |      | 2.3.4   | Summary                                                     | 58  |

|   | 2.4  | Concl   | usion                                                       | 58  |

| 3 | Prel | iminar  | y RTL simulation and new binary encoding fault models       | 61  |

|   | 3.1  | Prelim  | ninary RTL fault simulation and analysis                    | 62  |

|   |      | 3.1.1   | Internal clock glitch simulation                            | 63  |

|   |      | 3.1.2   | RTL fault simulation using bit manipulation fault models    | 64  |

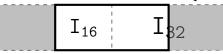

|   | 3.2  | Variab  | ole-length instruction sets                                 | 66  |

|   | 3.3  | Inferre | ed binary encoding fault models                             | 67  |

|   |      | 3.3.1   | Experimental setup                                          | 67  |

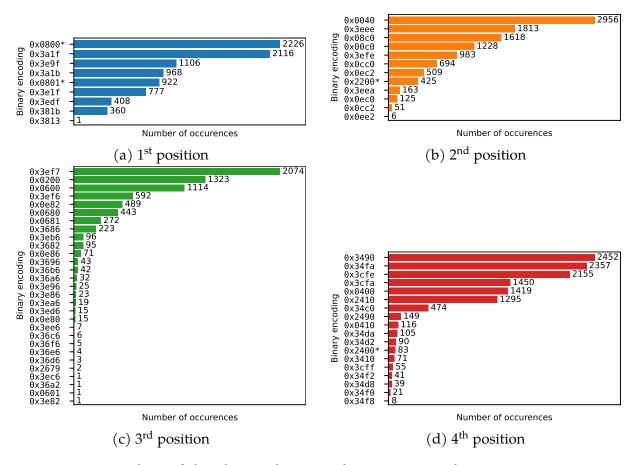

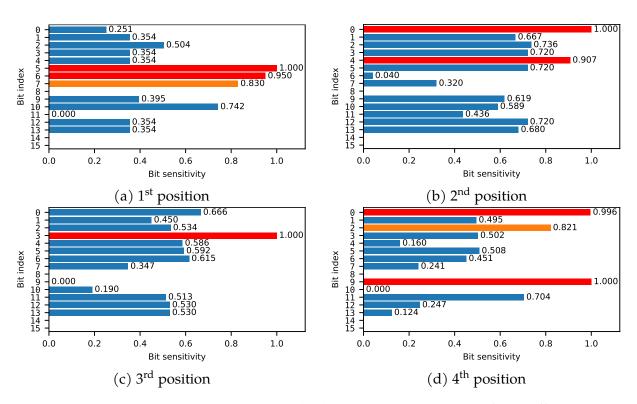

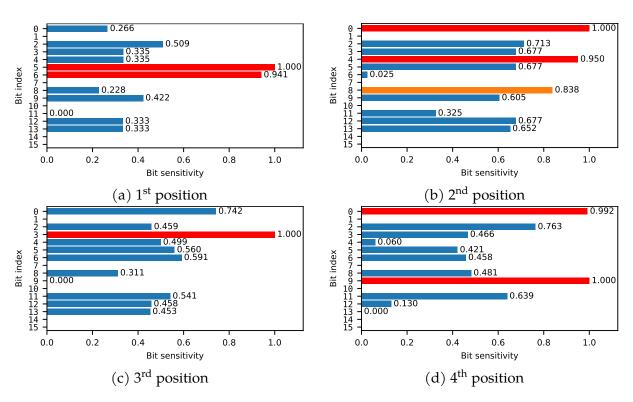

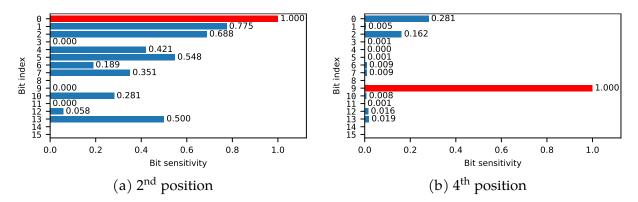

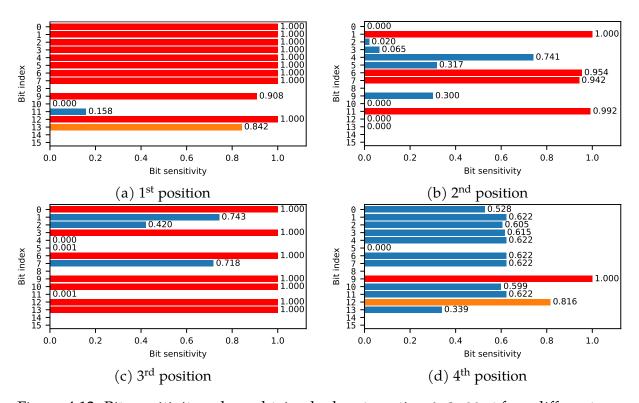

|   |      | 3.3.2   | Experimental results and analysis                           | 71  |

|   | 3.4  | Exploi  | tation and vulnerability analysis                           | 83  |

|   |      | 3.4.1   | Program Counter modification                                | 83  |

|   |      | 3.4.2   | Vulnerability analysis of AES implementations               | 85  |

|   | 3.5  | Fault r | models simulation                                           | 90  |

|   | 3.6  | Fault r | models evaluation                                           | 91  |

|   | 3.7  | Concl   | usion                                                       | 95  |

| 4 | Har  | dware 1 | fault simulation and partial update fault model             | 97  |

|   | 4.1  | Hardw   | vare fault simulation                                       | 97  |

|   |      | 4.1.1   | RTL fault simulation methodology                            | 98  |

|   |      | 4.1.2   | RTL fault models                                            | 100 |

|   |      | 4.1.3   | Post-synthesis timing simulation                            | 101 |

|   |      | 4.1.4   | Summary                                                     | 104 |

|   | 4.2  | Partia  | I update fault model                                        | 104 |

|   |      | 4.2.1   | Inference examples                                          | 105 |

|   |      | 4.2.2   | Sub-cases of partial update fault model                     | 107 |

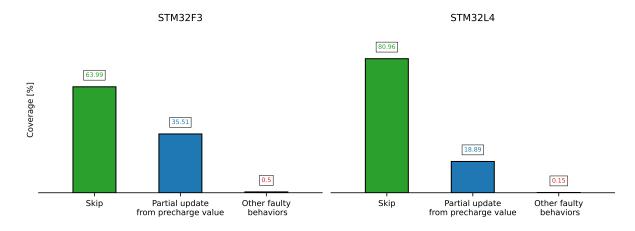

|   |      | 4.2.3   | Experimental results of partial update from precharge value | 109 |

|   |      | 4.2.4   | Experimental results of partial update from previous value  | 118 |

|   |      | 4.2.5   | Conclusion on the results of partial update fault model     | 121 |

|   | 4.3  | Fault r | models evaluation                                           | 122 |

|   | 11   | Concl   | ueion                                                       | 125 |

| 5 Fur  | ther results and details                    | 127 |

|--------|---------------------------------------------|-----|

| 5.1    | Program Counter modification                | 127 |

|        | 5.1.1 Misaligned code                       | 128 |

|        | 5.1.2 Aligned code                          | 129 |

|        | 5.1.3 Countermeasure: register substitution | 130 |

|        | 5.1.4 Trojan                                | 130 |

| 5.2    | Multiple glitch fault injection             | 133 |

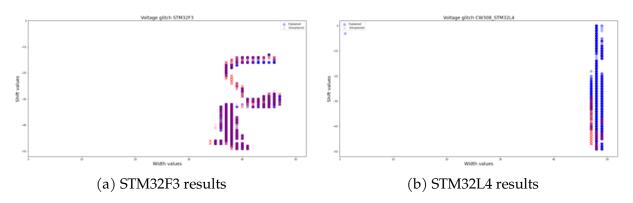

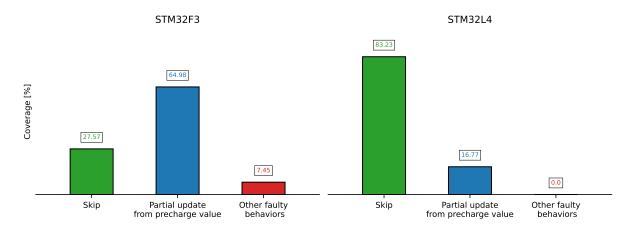

| 5.3    | Voltage glitch fault injection              | 135 |

| 5.4    | Conclusion                                  | 138 |

| Conclu | usion and perspectives                      | 141 |

| Public | ations                                      | 147 |

| Biblio | graphy                                      | 149 |

| Somm   | aire                                        | 172 |

## INTRODUCTION

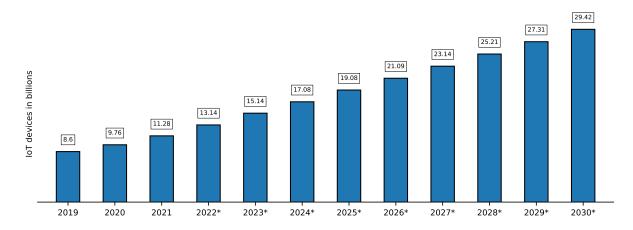

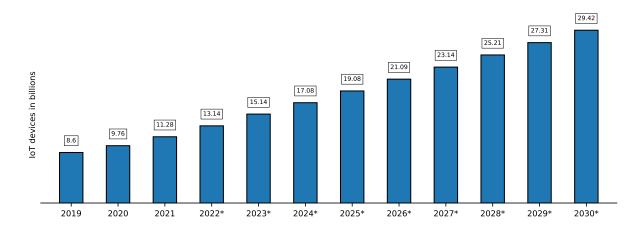

The utilization of embedded system devices is rapidly growing across various spheres of life. For instance, according to forecasts, the number of Internet of Things (IoT) devices in use worldwide is estimated to reach approximately 30 billion by 2030 [1], as depicted in Figure 1. However, the complexity of these devices, along with their running applications, is continuously increasing. This opens the door to two considerations: The need for high performance and new methods to deal with such advances and on the other hand, the emergence of new vulnerabilities exploitable by attackers at different levels. As sensitive data are frequently processed by embedded systems, some form of protection is necessary to prevent information leakage or modification. The actual processing and protection might be vulnerable to attacks that aim at extracting this sensitive information. Physical attacks in particular are a serious threat to embedded systems.

Figure 1: Number of IoT devices worldwide 2019-2021, with forecasts to 2030 (from [1]).

In the context of hardware security, physical attacks refer to various techniques and methods aimed at compromising the security of digital devices. These attacks exploit vulnerabilities in the physical properties or implementation of the device's hardware to delete, modify, gain or prevent access to confidential data.

The most prevalent physical attacks are side-channel and fault injection attacks. Side-channel attacks are passive physical attacks that primarily aim to exploit the unintentional leakage of information from a device's physical characteristics, such as power consumption [2], electromagnetic emissions [3], or timing information [4]. By capturing and analyzing these side-channel signals, attackers can infer sensitive information, such as cryptographic keys.

Fault injection attacks, on the other hand, are active physical attacks, possibly non-invasive, where the attacker will intentionally try to change the normal behavior of a device during program execution by inducing one or more faults, then observing the erroneous behavior. The resulting fault(s) could reveal an interesting behavior that could be further exploited as a vulnerability. Fault injection became an attractive research topic since the well-known Boneh *et al.* attack [5], where they were able to break some cryptographic protocols by inducing faults into the computations.

To inject a fault, a physical interference is applied on the digital device: radiations [6], laser light [7], electromagnetic pulses [8], variations of power supply [9], perturbations of clock signal [10], or changes in the environmental conditions such as the temperature [11] or else. Moreover, recent studies [12]–[14] have demonstrated the capability to perform fault injection attacks remotely by utilizing software to manipulate voltage regulators and/or energy management systems in modern devices. This has brought more attention to fault injection attacks.

In order to analyze vulnerabilities that can be exploited using fault injection attacks and propose effective countermeasures, evaluators, developers, and designers require accurate fault models. These fault models serve as abstract representations of the actual effects caused by faults, and are constructed through analysis and characterization of these effects across various levels of digital systems. It is crucial to ensure proper characterization and understanding of fault injection effects to avoid incomplete fault models. Failure to do so can result in either under-engineered or over-engineered implementations of protection measures. In the former case, security threats may persist, leaving room for exploitation, while in the latter case, unnecessary costs may be incurred, potentially leading to performance degradation.

The main objective of this thesis is to perform cross-layer analysis to examine the effects of fault injection, allowing for a better understanding of these effects at both software and hardware levels. As a result, the research will propose realistic, explainable, and trustworthy fault models across different levels of system abstraction. These

fault models will facilitate comprehensive vulnerability analysis processes and enable the effective design and development of countermeasures.

## **Contributions**

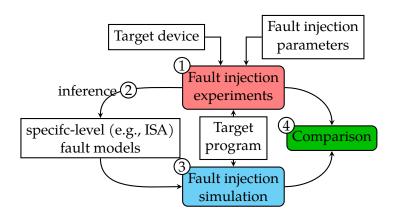

Firstly, this thesis presents a survey of fault injection techniques that utilize timing violations to induce faults in digital systems. It also includes real-world attack examples corresponding to each technique. Additionally, the thesis examines the current state-of-the-art in terms of characterizing and modeling the effects of fault injection attacks. This analysis reveals that previous studies predominantly focused on either software or hardware aspects separately. Although some studies attempted to bridge the gap between the two levels, they only conducted simulations at the Instruction Set Architecture (ISA) and Register-Transfer Level (RTL), without validating their analysis through physical fault injections.

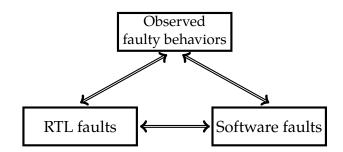

Furthermore, the thesis offers experimental evidence that demonstrates the limitations of characterizing and modeling fault injection effects based on a single level of analysis. As a result, the thesis proposes a comprehensive approach for cross-layer fault analysis, aiming to establish reliable fault models at various levels of abstraction. It also introduces metrics for evaluating the effectiveness of the proposed fault models.

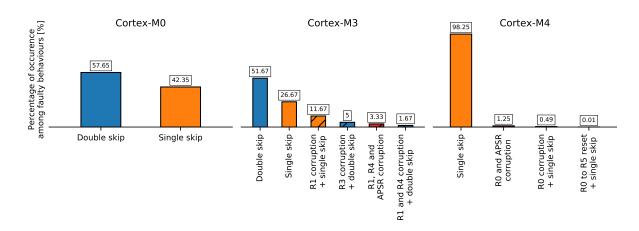

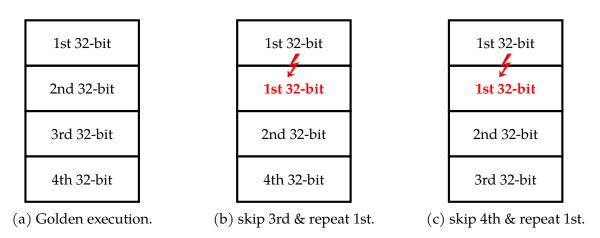

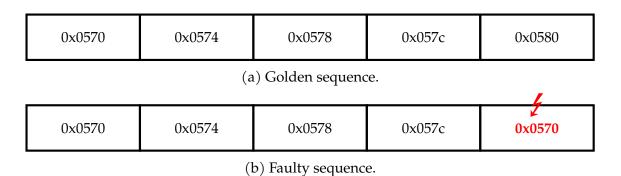

Moreover, implementing the proposed methodology, while involving fault injections and simulations on various Arm Cortex-M processors, led to infer realistic fault models at the binary encoding of the instructions: "Skip", "Skip and repeat", and "non-sequential skip and repeat" for a specific number of bits. These fault models enable to explain a wide range of the obtained faulty behaviors at higher levels of abstraction, including assembly and application levels, regardless of the target instructions and target device. The provided explanations are also applicable to a diverse range of the observed faulty behaviors that have been documented in the literature. Based on the proposed models, the thesis provides exploitation and vulnerability analysis examples. This showcases the high fidelity of the proposed fault models. In addition to that, a tool to simulate these models is also presented.

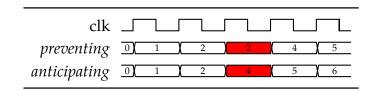

Similarly, analyzing the fault effects at lower levels of abstraction led to derive reliable fault models at RTL: *anticipating the update* and *preventing the update* of a register value at a given clock cycle. By utilizing these fault models, it becomes possible to observe faults that are identical to faulty behaviors obtained by physical fault injection, or

by simulating the aforementioned binary encoding fault models. Additionally, gaining an understanding of the effects of fault injection at the RTL level led to the deduction of a novel fault model known as the *Partial update* fault model. This model offers a significant increase in the ability to explain faulty behaviors.

Finally, the thesis opens up avenues for various research directions. This encompasses utilizing the proposed fault models to assess the vulnerabilities of software based on predefined security properties. Furthermore, the thesis demonstrates the feasibility of developing cost-effective countermeasures by comprehending the potential effects of fault injection. Additionally, the thesis highlights the ability to combine faulty behaviors through the injection of multiple glitches. It also showcases the applicability of the fault models when employing different fault injection techniques.

## **Outline**

The rest of this thesis is organized as follows: chapter 1 provides background on timing-based fault injection techniques with examples of successful attacks. Additionally, it reviews the state-of-the-art for characterization and modeling of the effects of fault injection. Experimental evidence for the need for cross-layer analysis, in addition to the proposed methodology, are demonstrated in chapter 2. Chapter 3 presents preliminary hardware fault simulation experiments. Additionally, it provides a detailed description of the inferred fault models at the binary encoding level. A detailed analysis at the hardware level and the inference of *Partial update* fault model are provided in chapter 4. Chapter 5 offers further analysis and results based on the presented work. The thesis is concluded along with future research perspectives in Conclusion and perspectives.

1

## State-of-the-art

This chapter starts with describing briefly the timing constraints in a digital circuit that ensure correct operation of the circuit. It then displays the main fault injection techniques that could lead to violate these timing constraints, along with practical examples of actual attacks from the literature. These attacks show the efficiency of such injection techniques in real-life. Afterward, it reviews the state-of-the-art in terms of fault injection effects characterization and modeling. Characterizing and modeling the effects of the fault injection are significant for the sake of analyzing possible vulnerabilities of codes or designs. Moreover, this is extremely necessary to develop or design countermeasures against fault attacks. Finally, the chapter is concluded, along with comments on the presented works.

## 1.1 Timing constraints in a digital circuit

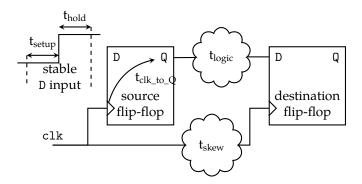

When designing a synchronous digital circuit, timing is of prime importance to guarantee a proper operation of the circuit. A synchronous digital circuit is a type of digital circuit that utilizes a clock signal to synchronize its components. These circuits consist of both sequential and combinational elements, which are interconnected. Combinational elements are made up of logical gates that perform digital computations, while sequential elements are memory cells known as flip-flops. Flip-flops are designed to store stateful data, which is used in the digital computations performed by the combinational elements. A standard flip-flop has an input D, and an output Q. When receiving a rising edge of a new clock cycle, a flip-flop adjusts the output Q to the value of the input D.

Figure 1.1: Timing metrics in a simple digital design.

The clock signal plays a crucial role in coordinating the operation of the sequential and combinational elements in synchronous digital circuits, ensuring that the computations are executed in a synchronized and orderly manner. Additionally, the clock period of a clock cycle (*i.e.*, the time between a rising edge and the next rising edge) must respect the maximum delay needed for the data to be propagated between a source flip-flop and a destination flip-flop. The path that has this maximum delay is known as the critical path in the circuit. In order to ensure correct operation of a synchronous digital design, timing must satisfy the setup and hold equations [15], [16], as presented in Equations 1.1 and 1.2 and illustrated in Figure 1.1 where:

- t<sub>clk</sub> is the clock period,

- t<sub>setup</sub> is the duration for which data on the D input must be stable before the rising edge of the clock signal [17],

- t<sub>hold</sub> is the duration for which data on the D input must be stable after the rising edge of the clock signal [17],

- ullet  $t_{

m logic}$  is the propagation delay in the combinational logic between the source and destination flip-flops,

- t<sub>skew</sub> is the time difference between the arrival of the clock signal at source flip-flop and destination flip-flop,

- t<sub>clk\_to\_Q</sub> is the delay from the rising edge of the clock input to the Q output inside source flip-flop [18].

$$t_{\text{clk\_to\_Q}} + t_{\text{logic}} + t_{\text{setup}} \le t_{\text{clk}} + t_{\text{skew}}$$

(1.1)

$$t_{\text{clk to Q}} + t_{\text{logic}} \ge t_{\text{hold}} + t_{\text{skew}}$$

(1.2)

Performing a timing-based fault injection could result in a violation of the inequalities found in one or both of Equations 1.1 and 1.2, leading to observe a faulty behavior.

## 1.2 Timing-based fault injection

This work primarily focuses on fault injection techniques that can lead to timing violations. Many of the currently employed and established techniques heavily depend on these violations to introduce faults in digital circuits. Moreover, these techniques offer a significant benefit in terms of cost-effectiveness when compared to alternatives like laser or radiation-based methods. Additionally, they require less expertise to successfully carry out the fault injections.

The following subsections describe the major fault injection techniques that can lead to violate the timing constraints in a synchronous digital circuit. For each outlined technique, examples of actual attacks from the literature are also given.

## 1.2.1 Clock glitch fault injection

Applying perturbations to the main clock signal that is fed to the digital circuit is a non-invasive and an effective fault injection technique. Clock glitch is considered as a low-cost fault injection technique compared to other techniques like laser and EM pulses. Also, it is highly controllable with respect to the temporal accuracy, and hence, the instant of the injection. This facilitates the pinpointing of specific instructions within the target program. However, since the glitch is injected in the global clock, there is no particular knowledge about which architectural element could be affected as a result of the injection. In particular, when the target device is a black box for the attacker, so has no knowledge of the device architecture. The ability of achieving the clock glitch in a remote way, as mentioned in [19], gives this kind of technique greater attention, when it comes to designing or developing protections against fault attacks. The remote attack can be accomplished using software-control of the energy management mechanisms in digital systems [19].

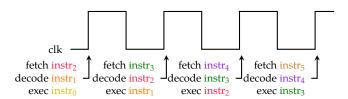

During a normal execution, for example, in a 3-stage pipeline, at every rising edge

of the clock, an instruction(s) is fetched by the microprocessor from the instruction memory, while another instruction (previously fetched) is being decoded or executed in another stage of the pipeline. Figure 1.2 shows a normal behavior when having a regular clock signal.

Figure 1.2: Normal behavior of a 3-stage processor pipeline with a regular clock signal.

When performing clock glitch fault injection, a glitch is injected just before or after the rising edge of the clock. This glitch would appear as a new clock cycle for the microprocessor, disrupting the regular behavior of the clock signal. Thus, resulting in a violation of the inequalities found in one or both of Equations 1.1 and 1.2, leading to various kinds of faulty behaviors.

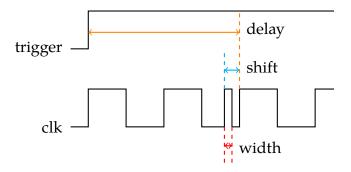

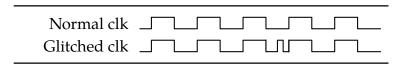

When performing a clock glitch, three parameters must be tuned, as shown in Figure 1.3:

- Delay: the time between the rising edge of the trigger signal (used for synchronization) and the rising edge of the targeted clock cycle.

- Shift: the distance between the rising edge of the glitch and the rising edge of the targeted clock cycle.

- Width: the duration of the glitch itself.

Figure 1.3: Clock glitch parameters.

It is worth mentioning that shift and width values should not be too large or too short. The too short values will not be enough to obtain a timing violation, while too large values will allow an instruction to be executed normally. Therefore, such values will result in non-observing any fault.

## Examples of clock glitch fault injection attacks

Schmidt *et al.* [20] were capable of skipping a square step in the square and multiply algorithm by inducing glitches into the clock signal of an AVR microcontroller. This would facilitate breaking RSA (Rivest-Shamir-Adleman) algorithm [21]. In another work, Yuce *et al.* [10] were able to retrieve the secret key of a fault-protected implementation of the LED block cipher [22]. This is done by performing differential fault analysis attack (DFA), using clock glitch fault injection, on a LEON3 [23] processor implemented on an FPGA. DFA is a side-channel attack under the category of cryptanalysis attacks [24]. It aims at inferring secret keys by collecting several faulty outputs as a result of a fault injection campaign. Furthermore, Dobraunig *et al.* [25] succeeded in breaking different implementations of software and hardware AES (Advanced Encryption Standard) encryption algorithm [26] by carrying out clock glitch fault injection campaigns.

## 1.2.2 Voltage glitch fault injection

Introducing variations to the power supply that feeds a digital circuit is another effective and low-cost fault injection technique. This injection technique provides acceptable controllability in terms of temporal accuracy. However, it is hard to determine the affected part of the digital circuit as a result of the injection. As clock glitch, voltage glitch can also be performed remotely [19].

For the sake of explaining the effect of the power supply variations, or the effect of inducing glitches into the voltage that is provided to a digital circuit, several studies have been carried out. In [27]–[32], the authors showed that the propagation delay of logical gates inside a digital circuit depends on the power supply noise, in particular its average noise. Moreover, [33]–[36] showed that underpowering or introducing negative power supply glitches into a circuit led to timing violations, resulting in faulty behaviors that are identical to the ones resulting from clock glitch fault injection. The timing violation is achieved as a result of increasing the propagation delay of the logical gates, which include t setup and t clk to Q. Similarly, Zussa *et al.* [37] demonstrated

that positive power supply glitches can also lead to violate the timing constraints in the setup Equation 1.1. They explain the violation as a result of negative oscillations that are induced by the voltage pulse edges.

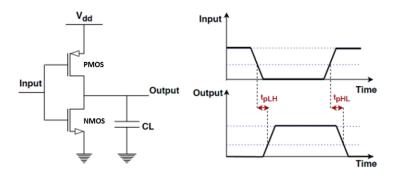

As an example, [34], [35] provided explanations of how the propagation delay of an inverter can be increased as a result of underpowering. Figure 1.4 shows an inverter circuit with its response propagation delay from low to high  $(t_{\rm pLH})$  and from high to low  $(t_{\rm pHL})$ . The propagation delay  $t_{\rm pLH}$  is given in Equation 1.3 [38]. Where,  $V_{dd}$  is the voltage source,  $C_L$  is the load capacitance,  $V_{th,p}$  is the PMOS threshold voltage,  $\mu_p$  is the holes' mobility,  $C_{ox}$  is the gate oxide capacitance, and  $(\frac{W_p}{L_p})$  is the aspect ratio of the PMOS. It is obvious that decreasing the voltage source  $(V_{dd})$  will result in increasing the propagation delay  $t_{\rm pLH}$ . By replacing the PMOS parameters in Equation 1.3 with the corresponding ones for the NMOS  $(e.g., V_{th,p})$  with  $V_{th,n}$ , an equation for  $t_{\rm pHL}$  can be derived.

$$t_{\text{pLH}} = \frac{C_{\text{L}} \left[ \frac{2|V_{\text{th,p}}|}{V_{\text{dd}} - |V_{\text{th,p}}|} + ln \left( 3 - 4 \frac{|V_{\text{th,p}}|}{V_{\text{dd}}} \right) \right]}{\mu_{\text{p}} C_{\text{ox}} \frac{W_{\text{p}}}{L_{\text{p}}} (V_{\text{dd}} - |V_{\text{th,p}}|)}$$

(1.3)

Figure 1.4: Inverter circuit with its propagation delay parameters (from [39]).

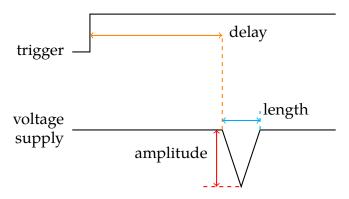

The main tuning parameters of the glitch, that need to be taken into account when performing voltage glitch fault injection, are as the following, and illustrated in Figure 1.5:

• Delay: the required time to determine the moment of injection with respect to a trigger synchronization signal.

- Length: the period of time in which the variation on the power supply will be applied.

- Amplitude: the voltage value of the pulse or the drop that is introduced to the digital circuit.

Figure 1.5: Voltage glitch parameters.

#### Examples of voltage glitch fault injection attacks

Bittner *et al.* [40] were able to retrieve the whole bootloader's code and decryption keys for later boot stages in a Nvidia system-on-chip, which is used in Tesla's autopilot and Mercedes-Benz's Infotainment system. Furthermore, Timmers *et al.* [9] presented voltage glitch-based attacks that led to privilege escalation in a Linux operating system, running on an Arm Cortex-A9 processor [41]. Finally, Takahashi *et al.* [42] were able to recover the full key that is used in an OpenSSL's implementation of Elliptic Curve Digital Signature Algorithm (ECDSA) [43].

## 1.2.3 Electromagnetic fault injection

Applying EM pulses to a digital device is an effective and a highly practical fault injection technique. This technique does not need to decapsulate the device, as the case in laser fault injection [19]. It offers better spatial accuracy than voltage and clock glitches, and roughly comparable temporal accuracy.

The EM pulses generate a magnetic field around the digital device's target part. This field may interfere with the device's normal operation. This interference may cause voltage perturbations in the circuit, leading to a rise in the propagation delay,

and hence, a setup timing violation may occur [44]–[46]. Nonetheless, other works showed that EM pulses can result in faulty behaviors that are not only explained by timing violations [47]–[49]. For example, authors in [47] illustrated that explaining EM faults as only timing violations is not enough to understand all the experimental observed faulty behaviors. This is because they were able to induce faults using EM pulses in a circuit at rest, where timing fault cannot occur.

The main parameters that need to be considered, when performing EM fault injection, are as the following:

- Probe: the coil that is used to generate the EM fields, where its physical design and characteristics play a vital role in EM fault injection [50].

- Delay: determines the time of injection with respect to a synchronized trigger signal.

- Amplitude: the voltage pulse value, which is usually produced by a pulse generator.

- Length: the amount of time in which the pulse is being generated.

- Position: determines the location of the target device with respect to the probe according to X-, Y-, and Z- axes.

#### **Examples of EM fault injection attacks**

Dehbaoui *et al.* [51] managed in recovering the encryption key of an AES software implementation by injecting a short EM pulse on a 32-bit microcontroller. Likewise, Liao *et al.* [52] succeeded in retrieving the full AES key when targeting a PIC16F687 [53]. As another example, Cui *et al.* [54] were able to perform a secure-boot violation attack on a modern multicore 1GHz Arm-based VoIP phone.

## 1.2.4 Heating fault injection

Changing the environmental conditions around a digital circuit, particularly the temperature, is another way to disrupt the circuit's normal behavior, which could result in observable faults. Heating a digital device may lead to an increase in the propagation delay inside it, resulting in timing violations [35], [55]. For example, in Equation 1.3, the

holes' mobility ( $\mu_p$ ) is directly related to the temperature. Thus, decreasing its value as a result of increasing the temperature would lead to increase  $t_{pLH}$  propagation delay [34], [55], [56]. Additionally, in [57], the authors showed that heating the target device while performing clock glitch attacks increases the observable fault rate, and hence, the success rate of the attacks.

## **Examples of Heating fault injection attacks**

By overheating ATmega162 devices [58] beyond their maximum temperature ratings, Hutter *et al.* [59] succeeded in breaking an implementation of CRT-RSA algorithm. In another example, Govindavajhala *et al.* [60] were able to induce multiple multi-bit flips in the contents of memory chips in a desktop computer by increasing the temperature to 100°C.

## 1.2.5 Summary

Table 1.1 summarizes the main characteristics of each of the presented fault injection techniques in terms of: The cost of performing the injection technique, its spatial and temporal accuracy, the possibility of damaging the target device as a result of the injection, the capability of carrying out the injection remotely, and the required technical skill level to carry out the injection. The contents of this table are based on previous works in [19], [61]–[63].

|                |           | Characteristic   |                   |               |        |                 |  |

|----------------|-----------|------------------|-------------------|---------------|--------|-----------------|--|

| Technique      | Cost      | Spatial accuracy | Temporal accuracy | Device damage | Remote | Technical skill |  |

| Clock glitch   | h low low |                  | ns                | no            | yes    | moderate        |  |

| Voltage glitch | low       | low              | ns-μs             | no            | yes    | moderate        |  |

| EM pulses      | moderate  | moderate         | ns-μs             | possible      | no     | moderate        |  |

| Heating        | low       | low              | none              | possible      | no     | low             |  |

Table 1.1: Summary of the characteristics of the presented fault injection techniques.

## 1.3 Fault injection effect analysis and modeling

Securing digital components, such as microprocessors and microcontrollers, against fault attacks requires a thorough understanding of the faults' propagation: on the one

hand, this means characterizing, studying, and analyzing the faults that could lead to exploitable code vulnerabilities. On the other hand, it also requires designing countermeasures at different levels, hardware and software, with an acceptable cost, in terms of overhead and performance.

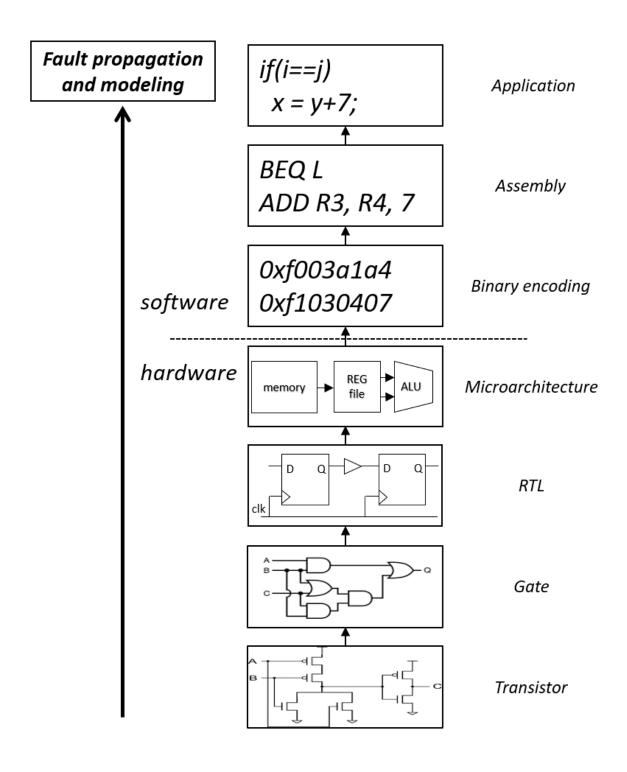

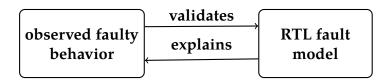

Fault effect analysis and characterization are performed to build the so-called "Fault models". Fault models are abstract representations of the physical fault effect. They provide description for the effects of the fault injection at different abstraction levels of a digital system. These levels refer either to software (high) or hardware (low) layers of a digital system, as shown in Figure 1.6.

Software developers and hardware designers need realistic fault models to evaluate the vulnerabilities of their codes or designs in presence of fault injection attacks. Based on this evaluation, software and/or hardware countermeasures will be developed and/or designed. On the other hand, the sufficiency of using impractical or simply random fault models will result in poor and inaccurate vulnerability analysis. Therefore, over-engineered or under-engineered countermeasures will be developed or designed. The following chapters will go into further details on these themes.

A review of the main works that employed fault injection attacks is given in the following subsections. The focus is on the level(s) at which their fault effect is described. In other words, the fault models they utilized to enable the success of their attacks and/or the fault models they proposed based on their characterization and analysis.

### 1.3.1 Random fault effect

This subsection presents a group of successful fault injection attacks from the literature. In all of these attacks, the employed fault models, that describe the injection effect, were *random* faults at the bit or byte level. In such attacks, the adversary has no control on the faulty bit/byte, and he/she relied on obtaining a random faulty value to allow the success of the attack.

Khelil *et al.* [33], for example, were capable of retrieving the encryption key of an AES implementation on an FPGA chip using voltage glitch fault injection. Their attack relied on faulting only one byte of the 9th round of AES and before the Mix column transformation. To do so, a reduction on the power supply of the FPGA is applied. To explain the obtained fault, they simply refer to the fact that destination flip-flops will capture bad random values as a result of increasing the propagation delay in

Figure 1.6: Fault propagation and modeling layers.

the computational logic between flip-flops. This increase of the delay results from the power supply reduction.

In another example, Tang *et al.* [64], succeeded in breaking the security of Arm Trustzone [65] of a Nexus6 smartphone. They were able to deduce cryptographic keys from the Trustzone. Additionally, they managed in loading self-signed applications into the Trustzone. To perform these attacks, they manipulated the clock frequency and the power supply from the voltage regulators of the Dynamic Voltage and Frequency Scaling (DVFS). DVFS is an energy-management technique that can be found in several digital devices. Such manipulation would result in violating the timing constraints of the digital elements of the target device. They described this violation with the following: an output of a source flip-flop failed in latching properly to the input of a destination flip-flop. Thus, the destination flip-flop continued to operate with stale data, which may be translated as a random bit-flip.

Similarly, Qiu *et al.* [66], exploited an implementation of the DVFS to extract the encryption key of an AES implementation that is executed in an Intel Software Guard Extensions (SGX) enclave [67]. To do so, they induced undervolting perturbations to the processor's power supply. This, as mentioned earlier, will result in violating timing constraints in the digital circuit. Thus, random faulty behaviours could occur. Their voltage glitch fault injection is totally utilized and controlled by a software that manipulates the core's voltage.

Furthermore, Chen *et al.* [68] built VoltPillager, which is a low-cost tool that allows controlling an Intel CPU voltage. They did so by exploiting a 3-wire bus called Serial Voltage Identification (SVID). SVID is responsible for transmitting the required voltage to the voltage regulator that is connected to the CPU. By injecting packets into SVID, using VoltPillager, in order to undervolting the voltage delivered to the CPU, they were able to break the confidentiality and the integrity of the CPU SGX enclaves.

Finally, Buhren *et al.* [69] succeeded in breaking the security of AMD Secure Encrypted Virtualization (SEV) [70] by carrying out voltage glitch fault injection attacks. SEV provides protections for virtual machines when used in insecure environments. As a result of their voltage glitch attack, they were able to deploy a malicious SEV firmware, which allows an attacker to decrypt the memory of the virtual machine. Additionally, they succeeded in retrieving SEV's endorsement keys, which can be used to generate fake certificates, and hence, can be used to perform software-based attacks. To perform the attack, they connect the target bus with a Teensy microcontroller [71].

Then, this microcontroller is used to program the voltage regulator of the target to apply voltage drop.

## 1.3.2 Fault effect analysis at ISA and microarchitecture levels

Dealing with ISA, as a result of fault injection, means involving the assembly instructions and /or their binary encoding in the characterization and analysis process. Additionally, it consists of describing the fault effect at the general-purpose registers of the processor and/or the memory locations of the target device. Several research studies have characterized faults at ISA level, due to the fact that it can be considered as the focal point for bringing high (software) and low (hardware) levels of abstraction together. On the other hand, providing description of fault effect at microarchitectural level, includes determining the faulty microarchitectural component, the pipeline stage, and/or the path inside a microcontroller or a microprocessor, where the fault is propagated. In the following, works dealt with one or both levels together are presented.

Moro *et al.* [72] performed EM fault injection campaigns on a 32-bit microcontroller that embeds an Arm Cortex-M3 processor [73]. They provided a comprehensive study to analyze the effects of EM fault injection on a real microcontroller. To explain the obtained faulty behaviors, they proposed a fault model called instruction replacement. Their approach is based on carrying out an exhaustive instruction simulation to find out which instruction can generate the same result as the observed faulty behavior. It is clear that such fault model is quite generic. Also, performing an exhaustive simulation for each faulty instruction is extremely costly. Additionally, most likely, different instructions could lead to the same result as the faulty one. Thus, uncertainty of the executed instruction would remain. With respect to fault description at microarchitectural level, they claimed that some bits, of the instruction encoding, might become faulty because of either a metastability phenomenon or the precharge value of the microcontroller's bus.

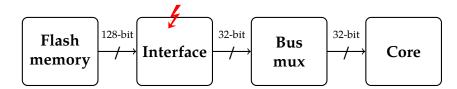

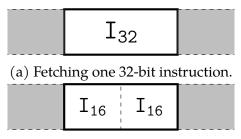

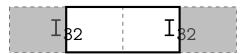

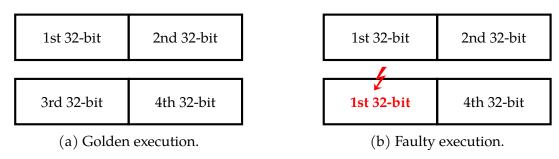

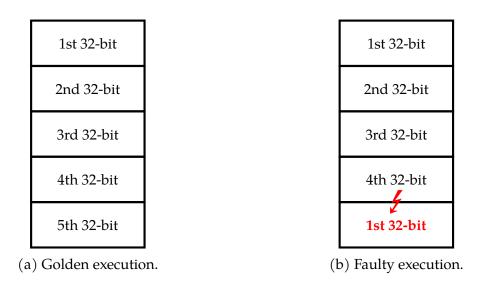

In another work, Rivière *et al.* [74] carried out practical EM fault injection experiments on an Arm Cortex-M4 processor [73]. As a result, they observed a faulty behavior where four complete 32-bit instructions are skipped, while the previous four 32-bit instructions are replayed. Based on that, they proposed a fault model where up to four 32-bit instructions or eight 16-bit instructions can be skipped, while the previous 128 bits of complete instructions are repeated. The reason behind this is the instruction

cache size, which is 128 bits. At the microarchitectural level, they described the injection effect as a fault affects the cache read at a given clock cycle, resulting in preventing the update of the cache contents. In addition to that, they provided some high level applications, where their fault model would lead to a successful attack or at least simplify an existing attack. This includes, for example: performing DFA on AES, and Bellcore [5] attack on CRT-RSA implementation.

Similar work has been presented by Trabelsi *et al.* [75]. Nonetheless, they provided additional faulty behaviors, where a combination of instructions, inside the instruction cache buffer, are affected, resulting in corrupting the value of some general purpose registers. Additionally, faults on special-purpose program status register (xPSR) are reported. In spite of that, they did not explain the rationale behind their obtained faulty behaviors. They also offered analysis at the binary encoding level of instructions, where they noticed that some faults can be explained with a single- or multi-bit reset without further explanation.

In [76], Dureuil *et al.* tried to generalize fault models as a result of performing laser and EM injections on RAMs and Flash memories of smart cards. Then, they simulated faults, based on the inferred fault models, in order to provide a so-called "vulnerability rate" for such faults. Their inferred fault models are: volatile bit set or reset on the instructions' code or data loaded from memory, non-volatile faults that affect a stored value in memory, and instruction skip. They performed their injections on two different architectures: EM injection on ARMv7-M [77], laser on a CISC machine. For evaluation purposes, they target VerifyPIN application.

In a comparable way, Werner *et al.* [78] carried out laser fault injection along with software fault simulation. However, they focused mostly on performing multi-fault attacks rather than proposing new or more thorough fault models. In particular, they aimed at combining complete instruction-skips faulty behaviors as a result of injecting multi-faults at different times. To evaluate their approach, they also target VerifyPIN application.

Moreover, Timmers *et al.* [79] were able to modify the value of the Program Counter register by targeting ARMv7-A architecture [80]. Firstly, they showed, by simulation, how this could lead to violate a secure boot. This is performed by corrupting LOAD instructions to have the Program Counter as a destination register. After that, they illustrated the possibility of doing so by corrupting LOAD instructions in a simple program composed of assembly instructions. In the best case, their success rate reached

2.7%. In their work, they referred to the instruction corruption as bit flips over the binary encoding of the LOAD instructions.

Furthermore, Kelly *et al.* [81] illustrated a well-controlled laser fault injection campaigns on Atmel ATtiny841 8-bit microcontroller [82], which embeds an AVR processor. They focused on targeting codes that manipulate branches. As a result, they noticed different faulty behaviors that can be classified under either instruction skip, multi-registers corruption, memory corruption, or status register corruption. For the sake of vulnerability analysis, they presented areas of vulnerability in a defensive code that is used in smart cards. For instance, certified EMV (Europay, Mastercard, and Visa) cards, and a National ID card scheme.

Another work is [8], where Proy *et al.* succeeded in corrupting the iteration counter of a secure and unsecure implementations of for loops. They carried out EM fault injection campaigns on Arm Cortex-A9 processor. Based on their analysis, they provided characterization at ISA level for the observed faulty behaviors. This includes: complete instruction skip and replay, source operand substitution, control-flow hijacking (the fault breaks the control-flow integrity of the target program), and register corruption. This corruption might correspond to a reset over the most significant 16 bits of the register expected value. At the binary encoding level, they refer to the observed faults as bit flips. Nonetheless, the authors explicitly stated that some of the obtained faults remained unexplained, without a corresponding fault model.

In a different work [83], Given-Wilson *et al.* performed only software simulation on the executable binaries of the target software. This is done for the sake of providing an automated formal process to discover fault injection vulnerabilities. As fault models, they consider a modification of conditional or unconditional Jump instructions, instruction skip, and the ability to reset one or two bytes. They illustrated the efficiency of their method by detecting vulnerabilities in the PRESENT encryption algorithm [84], [85].

Back to practical fault injections, Menu *et al.* [86] conducted EM fault injection campaigns on the flash memory of an 8-bit ATmega328P microcontroller [87]. As a result, they proposed consecutive instructions skip fault model. Consequently, by considering their faut model, they succeeded in bypassing the verification of VerifyPIN application.

Moreover, Trouchkine *et al.* [88] described EM fault campaigns on two modern processors: ArmBCM2837, which embeds Cortex-A53 [89], and Intel Core i3-6100T CPU [90]. The authors also provided characterization at ISA level to propose general fault models for different architectures: one of their proposed models is random register cor-

ruption; moreover, some of their faults were still left unexplained, with unknown fault model. Other proposed fault models include instruction corruption and bit reset. With respect to evaluate the security of high-level applications based on their characterization process, they performed DFA on OpenSSL AES [91] implementation.

Finally, Khaut *et al.* [92] carried out laser fault injection campaigns on a 32-bit microcontroller that embeds an Arm Cortex-M0+ processor [93]. Based on the position of the laser shots, they obtained different faulty behaviors. This includes: complete instructions skip, and complete instructions skip and replay. At the microarchitectural level, they hypothetically refer to skip and replay faults as preventing the update of an instruction buffer with either 32-bit or 64-bit size. On the other hand, they assume that skip faults can be as a result of instructions' opcode corruption, or bit resets while the instruction is propagated from the flash memory till the execute stage in the core pipeline.

## 1.3.3 Fault effect analysis at lower levels of abstraction

Other studies attempted to analyze fault injection effects at lower hardware levels, such as RTL and transistor levels. This is accomplished either by focusing only on a lower level of abstraction, or by including lower levels of abstraction in the analysis along with higher levels. Following are some examples from the literature.

#### Fault effect analysis at RTL

For the sake of better understanding the fault propagation and bridging the analysis gap between high levels and low levels of abstraction, some studies included RTL level in the fault effect analysis process. Including RTL means trying to describe, illustrate, and show how the fault affects a single or a group of flip-flops, *i.e.*, a register or a part of it. Additionally, it shows how the fault effect is propagated between these flip-flops or registers.

Among these studies, Laurent *et al.* [94], [95], where they suggested that fault effect analysis using typical software fault models are no longer enough to characterize the observed faulty behaviors, in particular when targeting complex microprocessors that have numerous internal elements, *i.e.*, registers and combinational logic. In their work, they provided a comprehensive analysis to assess and propose new software fault models. To put into practice, they defined an approach that is based on analyzing

and comparing the results that can be obtained when performing software and RTL fault simulations on a RISC-V microprocessor [96], while executing simple assembly instructions. In terms of used fault models: at RTL, they employed bit flips fault model that is applied to a single or a few flip-flops (up to 5) within the processor pipeline. On the other hand, different versions of instruction skip, test inversion, and forwarding are employed as software fault models. Forwarding fault model corresponds to a fault that affects data forwarding (also called bypassing). Data forwarding is an optimization technique used to solve hazards whenever there are data dependencies between instructions in a program. It has been noticed that a forwarding fault could invert conditional branches. To evaluate their fault models at higher levels, they targeted VerifyPIN and LittleXorKey applications.

In a similar work, Tollec *et al.* [97] presented an automated approach of analyzing hardware and software fault simulation experiments. Their approach is based on formal verification methods by model checking. While modeling the fault effect, they explore all possible next states from a current state. They then check for states that may lead to any vulnerability that could violate a predefined security property. With respect to employed RTL fault models, they utilized bit set, bit reset, bit flip, and bit random fault. For software models, they considered instruction skip, instruction replay, incorrect order of instruction replay, and branch corruption. At application level, they evaluated their approach over four different versions of VerifyPIN application.

It should be noticed that in both previous works, physical fault injections were not performed to validate the realism of their proposed RTL and software fault models. Moreover, different architectures should be taken into account in order to generalize the assumptions of their works.

It is worth noticed that bit fault model at RTL considers disrupting input or output signals of a specific flip-flop inside a specific architectural element, which is not necessarily correspond to a bit within the binary encoding of the instructions' data, for example. It may correspond, for instance, to a control signal as described in [94].

### Fault effect analysis at Transistor level

Other research works provided characterization for the fault injection effects at Transistor level. Two of these studies are presented in the following.

Dutertre et al. [98] conducted laser fault injection campaigns on a specific test chip that consists of CMOS 28 nm technology node, where special D flip-flops were

designed. These flip-flops were assembled in an in-line shift register composed of 10 D flip-flops, and a matrix-shaped shift register composed of 64 D flip-flops. While fault injection, they were able to identify sensitive areas of the transistors that form these flip-flops, where single-bit set/reset or flip faults could be obtained. Additionally, more faulty bits were achievable by increasing the laser pulse energy. At a higher level, they evaluated their analysis on a hardware AES encryption unit embedded on the same chip test.

In another study, Colombier *et al.* [7] carried out laser fault injection campaigns on a 32-bit microcontroller that embeds an Arm Cortex-M3 processor. They provided a comprehensive analysis of how the laser shots could affect connected transistors in parallel between a bit-line and the ground. By exploiting these bit lines, they were able to induce a single bit set or two adjacent bit sets to the binary encoding of the instructions while being fetched from the flash memory. As a result, corruption over either the operands or the opcode of the instruction was observed. As a propagation effect, control-flow corruption was achieved. For high level applications, they performed attacks over an implementation of VerifyPIN, and an implementation of AES encryption algorithm.

## 1.3.4 Summary

To summarize, this section begun by presenting recent fault injection attacks from the literature, which primarily focused on achieving successful fault injection. However, it is worth noting that these attacks typically refer to the resulting fault effect either as random bit or byte faults. In contrast, subsection 1.3.2 and subsection 1.3.3 provided a more detailed characterization of the fault effects and proposed fault models based on the analysis. Obviously, these works focused either on a single level of analysis or on simulation. As a result, they provided quite generic fault models that would make the vulnerability analysis harder. Consequently, insecure and/or costly countermeasures will be designed or developed. Table 1.2 summarizes the presented works, in subsection 1.3.2 and subsection 1.3.3, in terms of the following: the injection type (the employed injection technique and/or the level of the implemented simulation; software or hardware), the target processor or embedded architecture, the high-level target application, the used and/or proposed fault models at ISA, binary encoding of instructions or memory data, and RTL levels. This table clearly indicates that no prior work has

provided a comprehensive cross-layer analysis that combines hardware and software levels while conducting physical fault injection experiments.

| Reference                        | Injection type                   | Target                  | Application                     | ISA                                                                                                     | Binary                                      | RTL                                |

|----------------------------------|----------------------------------|-------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------|

| Moro et al.<br>[72]              | EM,<br>SW simulation             | Cortex-M3               | none                            | instruction replacement                                                                                 | mulit-bit fault                             | none                               |

| Rivière et al.<br>[74]           | EM                               | Cortex-M4               | AES,<br>CRT-RSA                 | multi instructions<br>skip and replay                                                                   | none                                        | none                               |

| Trabelsi <i>et al.</i> [75]      | EM                               | Cortex-M4               | none                            | register, xPSR corruption, opcode operand substitution                                                  | multi-bit reset                             | none                               |

| Dureuil <i>et al.</i> [76]       | EM, laser,<br>SW simulation      | ARMv7-M,<br>CISC        | VerifyPIN                       | instruction skip, (non)-volatile memory fault                                                           | bit (re)set                                 | none                               |

| Werner et al. [78]               | Laser,<br>SW simulation          | Cortex-M4               | VerifyPIN                       | multi-instrucion skip                                                                                   | none                                        | none                               |

| Timmers <i>et al</i> . [79]      | Voltage glitch,<br>SW simulation | ARMv7-A                 | secure-boot                     | instruction corruption                                                                                  | bit flips                                   | none                               |

| Kelly <i>et al.</i> [81]         | Laser                            | AVR                     | defensive code<br>in smartcards | instruction skip, memory<br>& registers corruption                                                      | none                                        | none                               |

| Proy <i>et al</i> . [8]          | EM                               | Cortex-A9               | for loops                       | instruction skip and replay,<br>register corruption,<br>operand substitution,<br>control-flow hijacking | bit flips                                   | none                               |

| Given-Wilson et al. [83]         | SW simulation                    | none                    | PRESENT                         | jump modification,<br>Instruction skip                                                                  | 1 or 2 bytes<br>reset                       | none                               |

| Menu <i>et al.</i><br>[86]       | EM                               | AVR                     | VerifyPIN                       | skip consecutive<br>instructions                                                                        | none                                        | none                               |

| Trouchkine <i>et al.</i> [88]    | EM                               | Cortex-A53,<br>i3-6100T | OpenSSL AES                     | register corruption, instruction corruption                                                             | bit reset                                   | none                               |

| Khaut <i>et al.</i><br>[92]      | Laser                            | Cortex-M0+              | none                            | instructions skip,<br>skip and repaly                                                                   | bit resets                                  | none                               |

| Laurent <i>et al.</i> [94], [95] | HW simulation,<br>SW simulation  | RISC-V                  | VerifyPIN<br>LittleXorKey       | instruction skip,<br>test inversion, forwarding                                                         | none                                        | bit flips                          |

| Tollec <i>et al.</i> [97]        | HW simulation<br>SW simulation   | RISC-V                  | VerifyPIN                       | Instruction skip, replay incorrect order of replay, forwarding, branch corruption                       | none                                        | bit reset,<br>set, flip,<br>random |

| Dutertre et al.<br>[98]          | Laser                            | ASIC                    | hardware AES                    | none                                                                                                    | none                                        | bit(s) set,<br>reset, flip         |

| Colombier <i>et al.</i> [7]      | Laser                            | Cortex-M3               | VerifyPIN<br>AES                | instruction corruption,<br>control-flow corruption                                                      | single bit set,<br>two adjacent<br>bit sets | none                               |

Table 1.2: Summary for the state-of-the-art of fault injection effect characterization and modeling.

## 1.4 Conclusion

To sum up, this chapter presented the timing constraints in a simple digital design. Then, it demonstrated different fault injection techniques that could lead to violating

these constraints, resulting in various faulty behaviors. Several given examples demonstrated how these resulting faulty behaviors could be used to carry out harmful attacks.

After that, this chapter reviewed the state-of-the-art in terms of fault injection effect characterization, analysis, and modeling. It was shown that many works described the effect of the fault injection as random bit or byte faults. Conversely, several studies concentrated on characterizing the fault injection effect only at a single abstraction level, specifically at the ISA level. Nonetheless, some of these works tried to provide additional analysis at the microarchitectural level by considering the faulty architectural component or fault propagation path. However, all of these studies proposed rather broad fault models, such as instruction skip and instruction corruption. These fault models are clearly not enough to evaluate vulnerabilities of software codes or hardware designs. Additionally, they would lead to develop or design non-optimal countermeasures. This certainly will affect either the cost, the performance or the security of the device. A few studies, on the other hand, combined high and low levels of abstraction in an effort to promote comprehension of the effect of fault propagation in a digital system. However, they only carried out fault simulations on a RISC-V processor and no physical injections at all were performed. By incorporating physical fault injections, the realism, and reliability of the proposed models can be better assessed, and the findings can be more applicable to a wider range of system architectures. Finally, other works attempted to focus their analysis at the lowest level of abstraction by describing how the induced fault affects the normal behavior of transistors.

2

# The need for cross-layer analysis and proposed methodology

In the context of the increasing complexity in embedded microprocessors and the associated behaviors in the presence of fault injection attacks, the need for realistic fault models becomes crucial for studying code vulnerabilities and protecting digital systems from these attacks. However, deriving accurate fault models based on limited observations of faulty microprocessors poses significant challenges. In this chapter, we present experimental evidence that highlights the difficulty of characterizing and modeling fault injection effects, in particular when only focusing on a single abstraction level for analysis. From there, we propose a holistic approach for fault analysis that encompasses different abstraction levels of a digital system, aiming to develop comprehensive fault models. This proposed methodology will definitely ease the process of vulnerability analysis and facilitate the design of effective countermeasures at a reasonable cost. Finally, we provide metrics to evaluate the quality of fault models, which can aid in assessing the accuracy and reliability of the proposed models.

## 2.1 Experimental evidence

Previous works usually focus on one single abstraction level of a digital system for fault effect analysis, and model the faulty behaviors at just one level. This section highlights the strong need of addressing several abstraction layers at the same time in order to fully understand the fault occurrence mechanisms. To achieve this, physical fault injection experiments are conducted on various target codes and devices. These

experiments aim to determine if the obtained faulty behaviors can be consistently characterized when making modifications to the target codes or other parts of the program. Additionally, the experiments are carried out to assess if the observed behaviors differ among different target devices.

This section presents the experimental setup, the results of the experiments and the related discussion that followed.

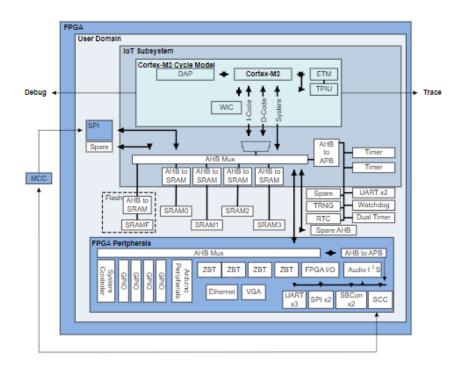

#### 2.1.1 Experimental Setup

Clock glitch fault injection campaigns have been performed as physical fault injection. As mentioned in subsection 1.2.1, it is a low-cost, non-invasive, and effective fault injection technique. In the following, the target devices, the target programs, and the injection parameters are presented.

#### Target devices

The boards that are used for the experiments are the ChipWhisperer [99] boards: CW1173 ChipWhisperer-Lite (Figure 2.1a), ChipWhisperer-Lite Capture (Figure 2.1b), and CW308 UFO baseboard (Figure 2.1c) with different targets (*e.g.*, Figure 2.1d). These ChipWhisperer boards have a dedicated environment for side channel analysis, voltage, and clock glitch of the target Arm core. We will leverage the clock glitch capabilities of this setup in the experiments. During an experiment, the ChipWhisperer-Lite or ChipWhisperer-Lite Capture board is connected to a control computer through a USB cable.

The targets are 32-bit microcontrollers, each of them embeds one of the Arm Cortex-M cores: STM32F0 embeds Cortex-M0 [100], STM32F1 embeds Cortex-M3 [73], and STM32F3 embeds Cortex-M4 [73]. STM32F3 is the connected target in CW1173 ChipWhisperer-Lite board, as shown in Figure 2.1a. The Cortex-M0 core supports the Thumb-1 instruction set [101] and a small part of the Thumb-2 instruction set [102], while Cortex-M3 and Cortex-M4 cores support Thumb-2 entirely.

Each of these Arm cores has 13 general-purpose 32-bit registers; R0 to R12. The cores also include a pipeline with three stages: fetch, decode and execute. Additionally, Cortex-M3 and Cortex-M4 have a hardware integer divide. Cortex-M4 has also additional components compared to the others, for example, it has a floating point unit and a digital signal processing unit.

(a) CW1173 ChipWhisperer-Lite board

(c) CW308 UFO baseboard

(b) ChipWhisperer-Lite Capture board

(d) CW308 target board

Figure 2.1: ChipWhisperer boards used in the experiments.

#### **Target programs**

The injection is performed directly into inline assembly instructions within a C program in order to provide fault effect characterization at ISA level. In order to better analyze the process of the injection, the program is divided into three parts as follows:

- Prologue: instructions for the initialization and putting the processor in a known state before the injection happens.

- Target: instructions targeted by the fault injection, as well as extra instructions that would allow observing any propagation effect.

- Epilogue: instructions for reading general purpose registers [R0-R12] and Application Program Status Register (APSR i.e., Negative (N), Zero (Z), Carry (C) and Overflow (V) flags); the values are transferred through serial communication commands to the control computer.

Two series of NOP instruction are used to isolate the three parts. This is done to ease the process of the injection by limiting the search space of the injection parameters, especially the delay. This also ensured that the prologue and the epilogue are not

affected by the injection. The  ${\tt NOPs}$  were not deleted after compilation, as no optimization option is used for the compiler.

In the injection campaigns, two programs are targeted as shown in Listing 2.1 and Listing 2.2. Specific instructions in the target part of these programs are used to allow observing faulty effects on the control- and/or the data-flow of the program, respectively: any real-life application can be described in terms of its data flow and/or its control flow.

The use of these instructions also allows for observing other things. Firstly, it shows if the resulting faulty behaviors are related to these instructions or not, hence giving a better understanding of what triggers the faulty behavior. Secondly, it allows to check if we will be able to reproduce some faulty behaviors that are already mentioned in the literature. It also aims at obtaining the possible faulty behaviors based on the program flow, either the control flow as in Listing 2.1 or the data flow as in Listing 2.2. This includes, for example, a fault that could break the control-flow integrity, or a fault that could propagate to later instructions, and thus, breaks the data-flow integrity. Finally, it helps to understand if software characterization at the ISA level is sufficient to build realistic fault models based on the observations.

Listing 2.1: Target part in *Program 1*: target control flow.

```

ADD R1, R1, 0x6 // r1 = r1 + 0x6

2 ADD R3, R3, 0xA // r3 = r3 + 0xA

3 ADD R4, R4, 0xB // r4 = r4 + 0xB

4 ADD R5, R6, R3 // r5 = r6 + r3

5 ADD R3, R3, 0xF // r3 = r3 + 0xF

```

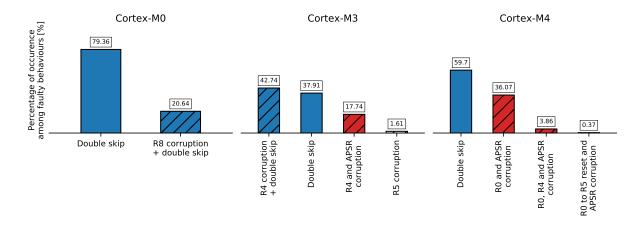

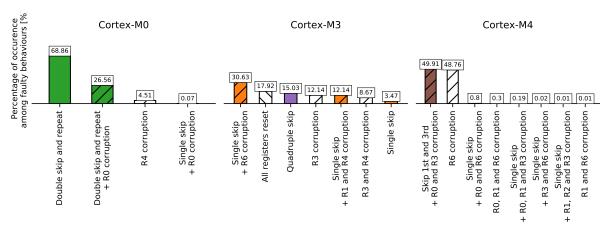

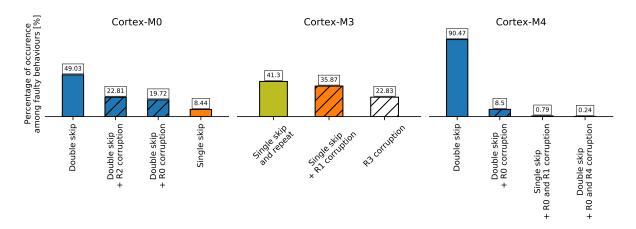

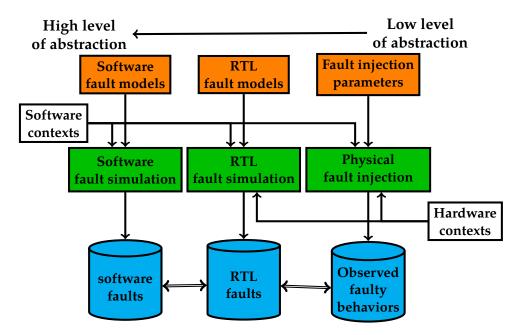

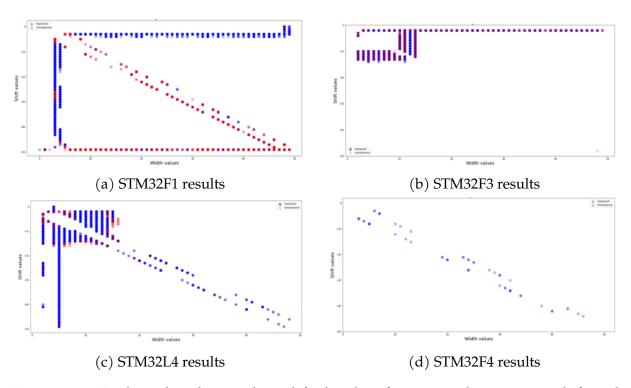

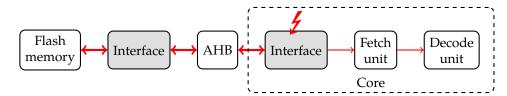

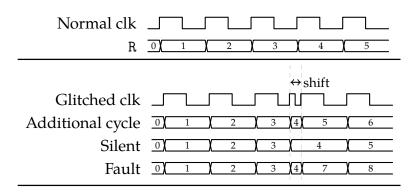

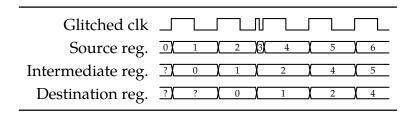

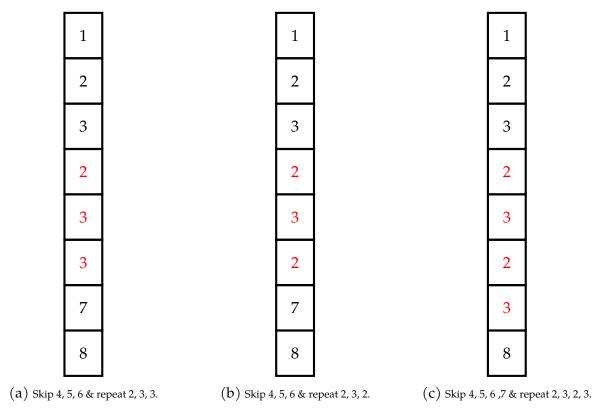

Listing 2.2: Target part in *Program* 2: target data flow and arithmetic operations.