# Towards new memory paradigms: Integrating non-volatile main memory and remote direct memory access in modern systems

Rémi Dulong

#### ▶ To cite this version:

Rémi Dulong. Towards new memory paradigms: Integrating non-volatile main memory and remote direct memory access in modern systems. Computer science. Institut Polytechnique de Paris; Université de Neuchâtel, 2023. English. NNT: 2023IPPAS027. tel-04426035

## HAL Id: tel-04426035 https://theses.hal.science/tel-04426035v1

Submitted on 30 Jan 2024

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Towards New Memory Paradigms: Integrating Non-Volatile Main Memory and Remote Direct Memory Access in Modern Systems

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Université de Neuchâtel (Suisse)

École doctorale n°626 École doctorale de l'Institut Polytechnique de Paris (EDIPP) Spécialité de doctorat : Informatique

Thèse présentée et soutenue à Neuchâtel, le 18 Décembre 2023, par

#### RÉMI DULONG

#### Composition du Jury:

Thomas Clausen

Professeur, École Polytechnique, Institut Polytechnique de Paris Président

Anne-Marie Kermarrec

Directrice de recherche, École Polytechnique Fédérale de Lausanne Rapportrice

Noël De Palma

Professeur, Université Grenoble Alpes Rapporteur

Patrick Eugster

Professeur, Università della Svizzera italiana Examinateur

Pascal Felber

Professeur, Université de Neuchâtel Co-directeur de thèse

Gaël Thomas

Directeur de recherche, Télécom SudParis, Institut Polytechnique de

Paris

Co-directeur de thèse

### **Abstract**

Modern computers are built around two main parts: their Central Processing Unit (CPU), and their volatile main memory, or Random Access Memory (RAM). The basis of this architecture takes its roots in the 1970's first computers. Since, this principle has been constantly upgraded to provide more functionnality and performance.

In this thesis, we study two memory paradigms that drastically change the way we can interact with memory in modern systems: non-volatile memory and remote memory access. We implement software tools that leverage them in order to make them compatible and exploit their performance with concrete applications. We also analyze the impact of the technologies underlying these new memory medium, and the perspectives of their evolution in the coming years.

For non-volatile memory, as the main memory performance is key to unlock the full potential of a CPU, this feature has historically been abandoned on the race for performance. Even if the first computers were designed with non-volatile forms of memory, computer architects started to use volatile RAM for its incomparable performance compared to durable storage, and never questioned this decision for years. However, in 2019 Intel released a new component called Optane DC Persistent Memory (DCPMM), a device that made possible the use of Non-Volatile Main Memory (NVMM). That product, by its capabilities, provides a new way of thinking about data persistence. Yet, it also challenges the hardware architecture used in our current machines and the way we program them.

With this new form of memory we implemented NVCACHE, a cache designed for non-volatile memory that helps boosting the interactions with slower persistent storage medias, such as Solid State Drive (SSD). We find NVCACHE to be quite performant for workloads that require a high granularity of persistence guarantees, while being as easy to use as the traditional POSIX interface. Compared to file systems designed for NVMM, NVCACHE can reach similar or higher throughput when the non-volatile memory is used. In addition, NVCACHE allows the code to exploit NVMM performance while not being limited by the amount of NVMM installed in the machine.

Another major change of in the computer landscape has been the popularity of distributed systems. As individual machines tend to reach performance limitations,

using several machines and sharing workloads became the new way to build powerful computers. While this mode of computation allows the software to scale up the number of CPUs used simultaneously, it requires fast interconnection between the computing nodes. For that reason, several communication protocols implemented Remote Direct Memory Access (RDMA), a way to read or write directly into a distant machine's memory. RDMA provides low latencies and high throughput, bypassing many steps of the traditional network stack.

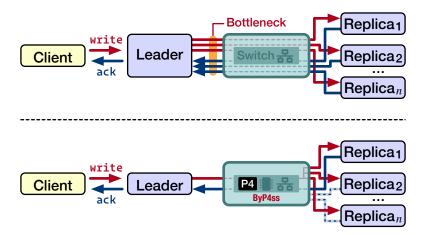

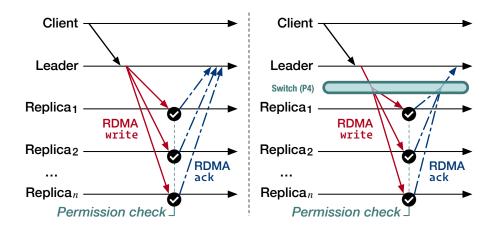

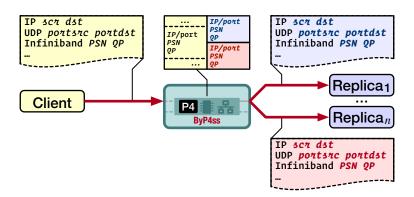

However, RDMA remains limited in its native features. For instance, there is no advanced multicast equivalent for the most efficient RDMA functions. Thanks to a programmable switch (the Intel Tofino), we implemented a special mode for RDMA that allows a client to read or write in multiple servers at the same time, with no performance penalty. Our system called Byp4ss makes the switch participate in transfers, duplicating RDMA packets. On top of Byp4ss, we implement a consensus protocol named DISMU, which shows the typical use of Byp4ss features and its impact on performance. By design, DISMU is optimal in terms of latency and throughput, as it can reduce to the minimum the number of packets exchanged through the network to reach a consensus.

Finally, by using these two technologies, we notice that future generations of hardware may require a new interface for memories of all kinds, in order to ease the interoperability in systems that tend to get more and more heterogeneous and complex.

**Keywords:** Non-Volatile Main Memory (NVMM), Remote Direct Memory Access (RDMA), Memory disaggregation, In-network computing.

## Résumé

Les ordinateurs modernes sont construits autour de deux éléments : leur CPU et leur mémoire principale volatile, ou RAM. Depuis les années 1970, ce principe a été constamment amélioré pour offrir toujours plus de fonctionnalités et de performances.

Dans cette thèse, nous étudions deux paradigmes de mémoire qui proposent de nouvelles façons d'interagir avec la mémoire dans les systèmes modernes : la mémoire non-volatile et les accès mémoire distants. Nous mettons en œuvre des outils logiciels qui exploitent ces nouvelles approches afin de les rendre compatibles et d'exploiter leurs performances avec des applications concrètes. Nous analysons également l'impact des technologies utilisées, et les perspectives de leur évolution dans les années à venir.

Pour la mémoire non-volatile, comme les performances de la mémoire sont essentielles pour atteindre le potentiel d'un CPU, cette fonctionnalité a historiquement été abandonnée. Même si les premiers ordinateurs ont été conçus avec des formes de mémoire non volatiles, les architectes informatiques ont commencé à utiliser la RAM volatile pour ses performances inégalées, et n'ont jamais remis en question cette décision pendant des années. Cependant, en 2019, Intel a commercialisé un nouveau composant appelé Optane DCPMM qui rend possible l'utilisation de NVMM. Ce produit propose une nouvelle façon de penser la persistance des données. Mais il remet également en question l'architecture de nos machines et la manière dont nous les programmons.

Avec cette nouvelle forme de mémoire, nous avons implémenté NVCACHE, un cache en mémoire non-volatile qui permet d'accélérer les interactions avec des supports de stockage persistants plus lents, tels que les SSD. Nous montrons que NVCACHE est particulièrement performant pour les tâches qui nécessitent une granularité élevée des garanties de persistance, tout en étant aussi simple à utiliser que l'interface POSIX traditionnelle. Comparé aux systèmes de fichiers conçus pour NVMM, NVCACHE peut atteindre un débit similaire ou supérieur lorsque la mémoire non volatile est utilisée. De plus, NVCACHE permet aux programmes d'exploiter les performances de NVMM sans être limité par la quantité de NVMM installée sur la machine.

Un autre changement majeur dans le paysage informatique a été la popularité des

systèmes distribués. Alors que les machines ont individuellement tendance à atteindre des limites de performances, l'utilisation de plusieurs machines et le partage des tâches sont devenus la nouvelle façon de créer des ordinateurs puissants. Bien que ce mode de calcul permette d'augmenter le nombre de CPU utilisés simultanément, il nécessite une connexion rapide entre les nœuds de calcul. Pour cette raison, plusieurs protocoles de communication ont implémententé RDMA, un moyen de lire ou d'écrire directement dans la mémoire d'un serveur distant. RDMA offre de faibles latences et un débit élevé, contournant de nombreuses étapes de la pile réseau.

Cependant, RDMA reste limité dans ses fonctionnalités natives. Par exemple, il n'existe pas d'équivalent de multicast pour les fonctions RDMA les plus efficaces. Grâce à un switch programmable (le switch Intel Tofino), nous avons implémenté un mode spécial pour RDMA qui permet de lire ou d'écrire sur plusieurs serveurs en même temps, sans pénalité de performances. Notre système appelé Byp4ss fait participer le switch aux transferts, en dupliquant les paquets RDMA. Grâce à Byp4ss, nous avons implémenté un protocole de consensus nommé DISMU. De par sa conception, DISMU est optimal en termes de latence et de débit, car il peut réduire au minimum le nombre de paquets échangés sur le réseau pour parvenir à un consensus.

Enfin, en utilisant ces deux technologies, nous remarquons que les futures générations de matériel pourraient nécessiter une nouvelle interface pour les mémoires de toutes sortes, afin de faciliter l'interopérabilité dans des systèmes qui ont tendance à devenir de plus en plus hétérogènes et complexes.

Mots-clés: Mémoire principale non volatile (NVMM), Accès direct de mémoire distante (RDMA), Mémoire désagrégée, Réseaux programmables.

## Remerciements

Merci aux Prof. Pascal Felber et Prof. Gaël Thomas, mes deux directeurs de thèse, qui m'ont fait découvrir le monde de la recherche, et qui ont choisi de me faire confiance du début à la fin de ce long parcours. Merci également au FNS (Fonds National Suisse) pour avoir financé cette thèse dans le cadre du projet PersiST (no. 178822). Merci à Valerio, pour son soutien dans tous nos travaux. Merci à Baptiste pour avoir amené un œil nouveau sur mon travail, ce qui a considérablement contribué à la seconde partie de cette thèse. Merci aux membres de mon jury, qui ont pris de leur précieux temps pour considérer et apprécier mon travail.

Merci à tous mes collègues, qu'ils aient été profs, doctorants ou stagiaires. En particulier, merci à Sébastien qui m'a fait découvrir le canton de Neuchâtel mais aussi la Suisse, sa culture, ses traditions, ses particularités linguistiques... Si bien que je n'en partirai pas tout de suite! Merci à Jämes d'avoir toujours été un collègue sur lequel on peut compter, pour les pizze comme pour le travail, et d'avoir assuré quasiment seul la gestion de notre cluster pendant la période d'écriture de cette thèse. Merci à Peterson, l'ingénieur Camerounais dont le pays peut être fier! Merci à Gal, pour son soutien et son humour, malgré la tristesse des évènements qui secouent son pays en ce moment. Merci à Rafael et Dorian, les experts sur lesquels j'ai pu m'appuyer au début de l'aventure. Merci à Isabelly et Catherine, pour leur sympathie et pour avoir réussi le tour de force de me motiver à améliorer mon anglais! Merci à Pedro et Andreia, pour m'avoir guidé dans les arcanes de la NVMM. Merci à Quentin, Gilles et Nathan, pour avoir contribué de manière directe à ces travaux pendant leurs stages. Merci à Afrim, pour son travail mais surtout pour sa bonne humeur! Merci à Lorenzo, pour m'avoir fourni le clavier de sa conception qui a servi à la rédaction de cette thèse (Adm42 pour les curieux). Merci à Pasquale, Victor, Andreas, Simon, Vladimir, et tous ceux que j'ai pu rencontrer au labo au fil de ces cinq années.

Merci à tous les professeurs et encadrants que j'ai pu avoir pendant ma scolarité, et qui ont tous contribué d'une manière ou d'une autre à la personne que je suis aujourd'hui. Merci à tous les étudiants pour lesquels j'ai eu le plaisir d'enseigner, ces quelques heures par semaine me manqueront probablement.

Merci à tous les anciens d'INTech, François, Florian, Victor, Lucas, et plus globalement à toute l'équipe du "Manoir". J'espère que la bande restera encore soudée pendant de nombreuses années! Merci à Matthieu, Pauline, Romain, et tous mes amis de longue date que je ne vois pas aussi souvent que je le voudrais.

Merci à mes grands-parents, Marie-France et Bernard, pour les innombrables heures à refaire le monde sur Skype le Dimanche soir. Merci à mes sœurs, Lucille et Candice, pour les pauses jeux vidéo et les retrouvailles chaque année à l'été, ou aux fêtes de fin d'année. Une pensée aussi pour mon grand-père Jean, avec qui j'ai appris bien plus que ce qu'on trouve dans les livres d'école, et pour mes arrière-grands-parents Lily et Joseph, chez qui j'avais eu mes premiers "cours" d'informatique! S'ils avaient vu jusqu'où tout cela m'a mené... Enfin, merci à toute ma famille, mes parents, mes grands-parents, oncles, tantes, cousines et cousins, pour leur soutien, et pour avoir toujours créé cette ambiance si particulière qu'il est bon de retrouver à chaque réunion de famille. En particulier, merci à mes parents Dominique et Gilles qui m'ont soutenu et m'ont permis d'être guidé dans ce parcours scolaire si privilégié.

# **Contents**

| Ab  | strac   |                                                  | iii      |

|-----|---------|--------------------------------------------------|----------|

| Ré  | sumé    |                                                  | v        |

| Re  | merc    | ements                                           | vii      |

| Lis | st of a | ronyms                                           | xiii     |

| Lis | st of f | gures                                            | χv       |

| Lis | st of t | bles                                             | xvii     |

| 1.  | Intro   | duction                                          | 1        |

| I.  | No      | n-Volatile Main Memory (NVMM)                    | 3        |

| 2.  | A Ne    | v Kind of Memory                                 | 5        |

|     | 2.1.    | Definition and Terminology                       | 5        |

|     |         | History of Persistent Memories                   | 5        |

|     | 2.3.    | Implementations                                  | 7        |

|     |         | 2.3.1. For embedded systems                      | 7        |

|     |         | 2.3.2. For servers                               | 7        |

|     | 2.4.    | Integrating Persistent Memory in Modern Systems  | 10       |

|     |         | 2.4.1. NVMM as RAM extension                     | 10       |

|     |         | 2.4.2. NVMM as a disk                            | 10       |

|     |         | 2.4.3. NVMM as a DAX areas                       | 11       |

|     | 2.5     | 2.4.4. Working with CPU caches                   | 12       |

|     | 2.5.    | Programming With Persistent Memory               | 13<br>13 |

|     |         | 2.5.2. Ordering and durability guarantees        | 15       |

|     |         | 2.5.3. Persistence model                         | 15       |

| 3.  | NVC     | che: A NVMM-based I/O Booster for Legacy Systems | 17       |

|     | 3.1.    | Introduction                                     | 17       |

|     |         | 3.1.1 NVCACHE in a nutshell                      | 17       |

#### Contents

|     |       | 3.1.2.  | NVCACHE features                                    | 17 |

|-----|-------|---------|-----------------------------------------------------|----|

|     |       | 3.1.3.  | Target applications                                 | 19 |

|     | 3.2.  | NVCa    | che: Implementation                                 | 20 |

|     |       | 3.2.1.  | Overview                                            | 20 |

|     |       | 3.2.2.  | NVLog                                               | 20 |

|     |       | 3.2.3.  | Cleanup thread                                      | 25 |

|     |       | 3.2.4.  | Write-only performance                              | 28 |

|     |       | 3.2.5.  | Ensuring consistency                                | 28 |

|     |       | 3.2.6.  | Control structures                                  | 32 |

|     | 3.3.  | Evalua  | ation                                               | 35 |

|     |       | 3.3.1.  | Experimental setup                                  | 35 |

|     |       | 3.3.2.  | Benchmarks                                          | 38 |

|     |       | 3.3.3.  | Read-oriented workloads                             | 38 |

|     |       | 3.3.4.  | Write-oriented workloads                            | 39 |

|     | 3.4.  | Concl   | usion                                               | 45 |

|     |       |         |                                                     |    |

| 4.  |       |         | ne Design: Logging vs. Paging                       | 47 |

|     | 4.1.  |         | ation                                               | 47 |

|     | 4.2.  |         | M-based Caching                                     | 48 |

|     | 4.3.  |         | ation                                               | 50 |

|     | 4.4.  | Concl   | usion                                               | 52 |

| 5.  | Cond  | clusion | on Persistent Memory                                | 53 |

|     | 5.1.  | Lesson  | ns Learned                                          | 53 |

|     |       | 5.1.1.  | Software integration                                | 53 |

|     |       | 5.1.2.  | Hardware integration                                | 55 |

|     | 5.2.  | On the  | e Future of Persistent Memory                       | 56 |

|     |       | 5.2.1.  | The rise and fall of Intel Optane                   | 56 |

|     |       | 5.2.2.  |                                                     | 57 |

|     | 5.3.  | Concl   | usion                                               | 58 |

|     |       |         |                                                     |    |

|     | _     |         |                                                     |    |

| II. | Kei   | mote ש  | Pirect Memory Access (RDMA) & Programmable Networks | 59 |

| 6.  | Intro |         | n to RDMA                                           | 61 |

|     | 6.1.  | RDMA    | A-Capable Protocols                                 | 61 |

|     |       | 6.1.1.  | Infiniband                                          | 61 |

|     |       | 6.1.2.  | RoCE                                                | 62 |

|    | 6.2.                     | RDMA      | -Capable Hardware                                | 63        |

|----|--------------------------|-----------|--------------------------------------------------|-----------|

|    |                          | 6.2.1.    | Switches                                         | 63        |

|    |                          | 6.2.2.    | Network Interface Cards                          | 64        |

|    | 6.3.                     | RDMA      | Concepts                                         | 64        |

|    |                          | 6.3.1.    | Memory region                                    | 65        |

|    |                          | 6.3.2.    | Work request                                     | 65        |

|    |                          | 6.3.3.    | Queue pairs                                      | 65        |

|    |                          | 6.3.4.    | Completion queue                                 | 66        |

|    | 6.4.                     | RDMA      |                                                  | 66        |

|    |                          | 6.4.1.    | Two-sided verbs                                  | 66        |

|    |                          | 6.4.2.    | One-sided verbs                                  | 67        |

|    |                          | 6.4.3.    | Special verbs                                    | 67        |

|    | 6.5.                     | Intel T   | Cofino                                           | 67        |

|    |                          | 6.5.1.    |                                                  | 68        |

|    |                          | 6.5.2.    | Performance guarantees                           | 69        |

| 7  | Dyn                      | leer I at | ency- and Throughput-Optimal Consensus Over RDMA | 71        |

| 1. | Бур <sup>2</sup><br>7.1. |           |                                                  | 71        |

|    | 7.1.<br>7.2.             |           |                                                  | 71<br>73  |

|    | 7.2.                     | 7.2.1.    |                                                  | 73        |

|    |                          | 7.2.2.    | J                                                | 75        |

|    | 7.3.                     |           | <u> </u>                                         | 73<br>77  |

|    | 7.0.                     | 7.3.1.    |                                                  | <br>77    |

|    |                          | 7.3.2.    |                                                  | , ,<br>78 |

|    |                          | 7.3.3.    |                                                  | 79        |

|    | 7.4.                     |           |                                                  | , ,<br>80 |

|    |                          | 7.4.1.    |                                                  | 81        |

|    |                          | 7.4.2.    | <b>U</b>                                         | 83        |

|    |                          | 7.4.3.    |                                                  | 85        |

|    |                          | 7.4.4.    |                                                  | 86        |

|    |                          | 7.4.5.    |                                                  | 88        |

|    | 7.5.                     | Evalua    |                                                  | 89        |

|    |                          | 7.5.1.    |                                                  | 89        |

|    |                          | 7.5.2.    |                                                  | 89        |

|    |                          | 7.5.3.    | = <del>*</del>                                   | 89        |

|    |                          | 7.5.4.    | ~ ·                                              | 92        |

|    |                          | 7.5.5.    | •                                                | 93        |

|    | 7.6.                     | Relate    |                                                  | 95        |

|    | 7.7.                     | Concl     |                                                  | 97        |

|    |                          |           |                                                  |           |

#### Contents

| 8.  | Cond   | lusion         | on RDMA and Programmable Networks   | 99  |  |  |  |

|-----|--------|----------------|-------------------------------------|-----|--|--|--|

|     | 8.1.   | Progra         | ummable Networks                    | 99  |  |  |  |

|     | 8.2.   | RDMA           | in the Computing Landscape          | 100 |  |  |  |

|     |        | 8.2.1.         | A complex programming interface     | 101 |  |  |  |

|     |        | 8.2.2.         | A challenge for performance         | 101 |  |  |  |

|     |        | 8.2.3.         | A unique API                        | 102 |  |  |  |

|     | 8.3.   | Perspe         | ectives                             | 103 |  |  |  |

|     |        | 8.3.1.         | CXL                                 | 103 |  |  |  |

|     |        | 8.3.2.         | The end of the computer-centric era | 104 |  |  |  |

| 9.  | Cond   | lusion         |                                     | 107 |  |  |  |

| Bib | oliogr | oliography 109 |                                     |     |  |  |  |

# **List of acronyms**

| API<br>ADR | Application Programming Interface Asynchronous DRAM Refresh | НРС    | Infrastructure High-Performance Computing |

|------------|-------------------------------------------------------------|--------|-------------------------------------------|

| ACK        | Acknowledgment                                              | IP     | Internet Protocol                         |

| ASIC       | Application-Specific                                        | I/O    | Input/Output                              |

|            | Integrated Circuit                                          | IBoE   | Infiniband over Ethernet                  |

| ALU        | Arithmetic Logic Unit                                       | LPC    | Linux Page Cache                          |

| Al         | Artificial Intelligence                                     | LRU    | Least Recently Used                       |

| BIOS       | Basic Input Output System                                   | LAN    | Local Area Network                        |

| BfRt       | Barefoot runtime                                            | LRH    | Local Route Header                        |

| CPU        | Central Processing Unit                                     | MTT    | Memory Translation Table                  |

| CA         | Channel Adapter                                             | MMU    | Memory Management Unit                    |

| CD-RW      | Compact Disk-Rewritable                                     | MTU    | Maximum Transmission Unit                 |

| CXL        | Compute Express Link                                        | NVRAM  | Non-Volatile RAM                          |

| DBMS       | Database Management                                         | NVMM   | Non-Volatile Main Memory                  |

|            | System                                                      | NVDIMM | Non-Volatile Dual In-line                 |

| DAX        | Direct Access                                               |        | Memory Module (DIMM)                      |

| DIMM       | Dual In-line Memory Module                                  | NAK    | Negative Acknowledgment                   |

| DCPMM      | DC Persistent Memory                                        | NIC    | Network Interface Card                    |

| DDR4       | Double Data Rate 4                                          | NUMA   | Non-Uniform Memory Access                 |

| DRAM       | Dynamic Random-Access                                       | NVMe   | NVM Express, or Non-Volatile              |

|            | Memory                                                      |        | Memory Host Controller                    |

| DMA        | Direct Memory Access                                        |        | Interface Specification                   |

| DPDK       | Data Plane Development Kit                                  | OS     | operating system                          |

| eADR       | External Asynchronous                                       | OSI    | Open Systems Inteconnection               |

|            | DRAM Refresh                                                | PMEM   | Intel Optane Persistent                   |

| FUSE       | Filesystem in Userspace                                     | D0011/ | Memory                                    |

| FIO        | Flexible I/O tester                                         | POSIX  | Portable Operating System                 |

| FPGA       | Field-Programmable Gate                                     | DCA    | Interface                                 |

| CDII       | Array                                                       | PSA    | Protocol-independant Switch               |

| GRH        | Global Route Header                                         | PSN    | Architecture                              |

| GPU<br>HDD | Graphics Processing Unit Hard Disk Drive                    | PSN    | Packet Sequence Number Persistent Fence   |

| HCI        | Hyper-Converged                                             | PSYNC  | Persistent Sync                           |

| пСі        | rryper-Converged                                            | POINC  | reisistem sync                            |

PWB Persistent Write-Back

PCIe Peripheral Component

Interconnect Express

**PMDK** Persistent Memory

Development Kit

**PCM** Phase-Change Memory

**QP** Queue Pair

RAM Random Access Memory RDMA Remote Direct Memory

Access

**ROCE** RDMA over Converged

Ethernet

RTR Ready to Receive

RTS Ready to Send

SSD Solid State Drive

**SATA** Serial Advance Technology

Attachment

**TNA** Intel Tofino Native

Architecture

UDP User Datagram ProtocolWPQ Write Pending Queue

# **List of figures**

| 2.1.         | Comparison between the clittush and clwb instructions              | 14 |

|--------------|--------------------------------------------------------------------|----|

| 3.1.         | NVLog entry example                                                | 21 |

| 3.2.         | NVLog head and tail counters                                       | 22 |

| 3.3.         | State of NVLog while adding 8200 bytes                             | 25 |

| 3.4.         | NVCACHE behavior in case of a cache hit                            | 30 |

| 3.5.         | NVCACHE behavior in case of a cache miss                           | 30 |

| 3.6.         | NVCACHE behavior in case of a "dirty miss"                         | 31 |

| <b>3.7.</b>  | NVCACHE behavior in case of a write                                | 31 |

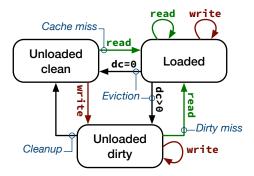

| 3.8.         | State machine of pages (dc: dirty counter)                         | 33 |

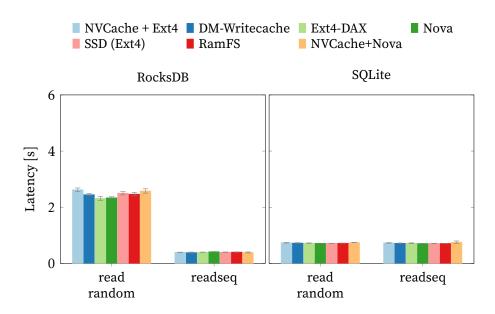

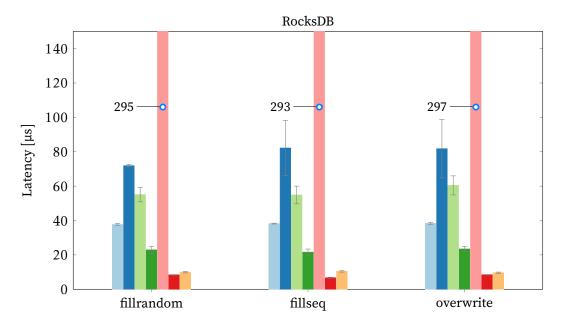

| 3.9.         | SQLite and RocksDB read workloads                                  | 39 |

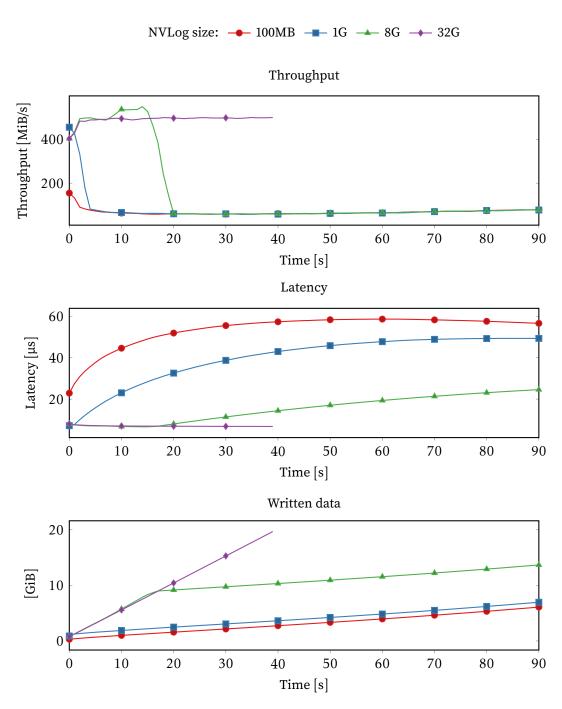

| 3.10.        | Performance of NVCACHE with random writes                          | 40 |

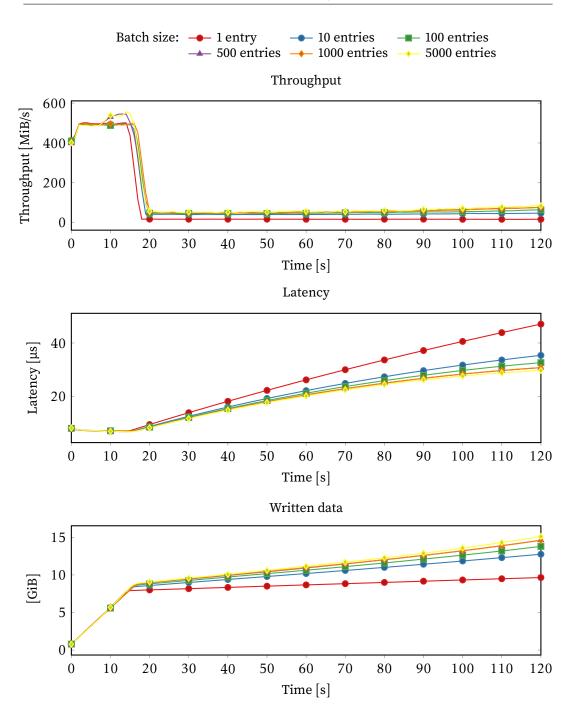

| 3.11.        | Influence of batching and batch size parameter                     | 42 |

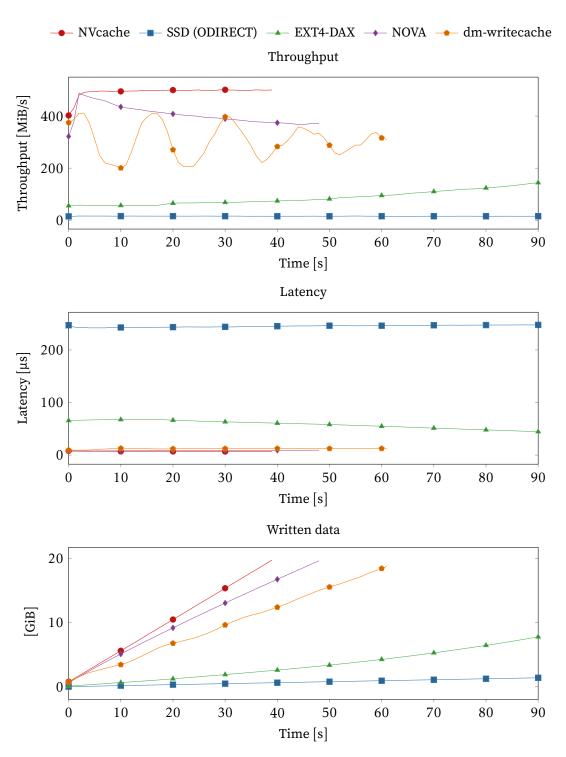

| 3.12.        | Behavior of NVCACHE compared to other systems (FIO)                | 43 |

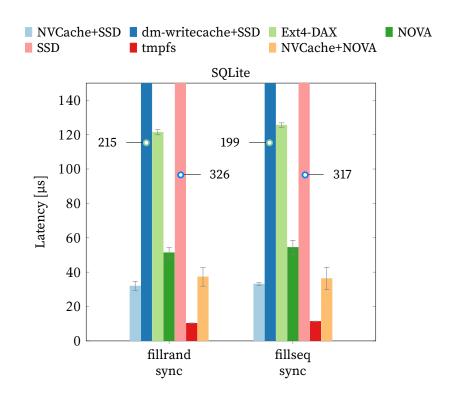

| 3.13.        | Behavior of NVCACHE compared to other systems (SQLite and RocksDB) | 44 |

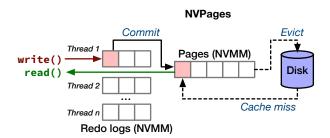

| 4.1.         | Core design of NVPAGES                                             | 48 |

| 4.2.         | Core design of NVCACHE                                             | 49 |

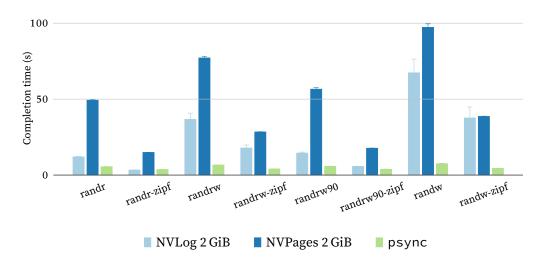

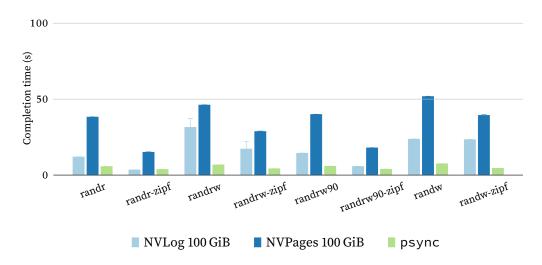

| <b>4.</b> 3. | FIO benchmarks with 2 GiB of NVMM cache                            | 51 |

| 4.4.         | FIO benchmarks with 100 GiB of NVMM cache                          | 51 |

| 6.1.         | A RoCE v1 frame                                                    | 62 |

| 6.2.         | A RoCE v2 frame                                                    | 63 |

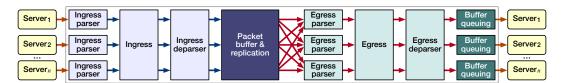

| 7.1.         | Protocol-independant Switch Architecture pipeline                  | 76 |

| 7.2.         | Communication without and with Byp4ss                              | 78 |

| 7.3.         | Communication pattern used for consensus                           | 79 |

| 7.4.         | Principle of packet duplication with Byp4ss                        | 84 |

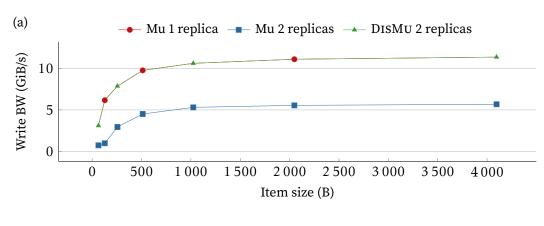

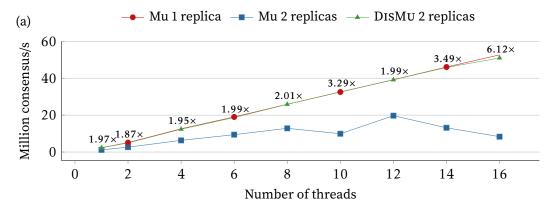

| 7.5.         | Write goodput with different item sizes                            | 90 |

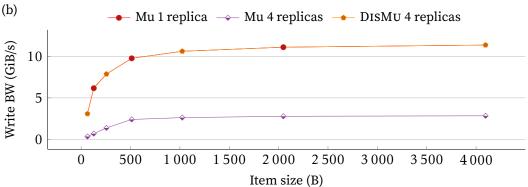

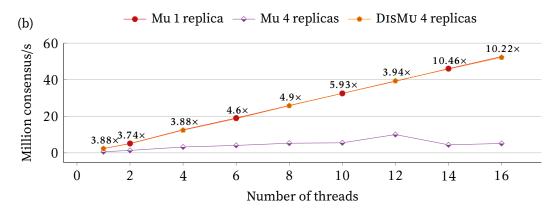

| 7.6.         | Write throughput with 64 B requests                                | 91 |

| 7.7.         | Evolution of latency with 64 B requests vs. per-thread throughput  | 93 |

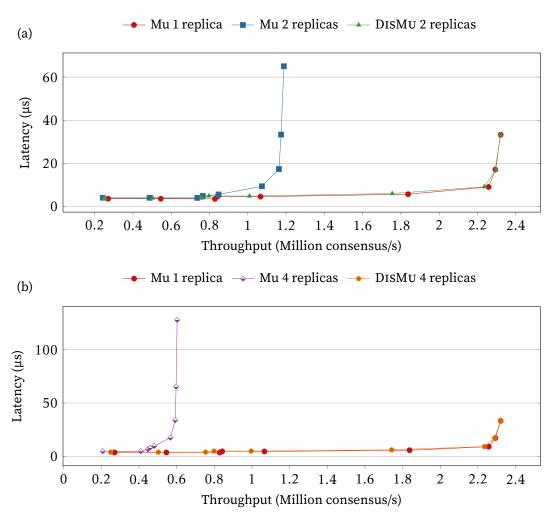

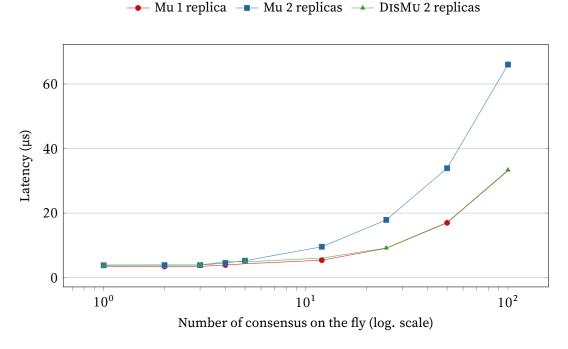

| 7.8.         | Latency with 64 B requests, 1 thread                               | 94 |

# **List of tables**

|      | Properties of several NVMM systems   |    |

|------|--------------------------------------|----|

| 7.1. | Metadata contained in an RDMA packet | 74 |

| 7.2. | Multicast metadata                   | 82 |

| 7.3. | RDMA Connection structure            | 83 |

| 7.4. | Read throughput with 64 B requests   | 95 |

# Chapter 1.

## Introduction

Modern computers are built around two main components: their Central Processing Unit (CPU), and their main memory, *i.e.*, Random Access Memory (RAM). This architecture became standard, and most computers around the world are built within the same pattern. However, we always try to make these machines more powerful, by increasing their computing capacity in various ways. The history of computer science, even rather short, is a constant quest for performance interspersed by physical or technical limitations.

There are numbers of ways to increase the computational capacity of a machine. The first approach is to increase the frequency of its CPU, so that more atomic operations are performed in the same amount of time. This idea is quickly limited, as the power required by a CPU is proportional to the frequency it is running at [134]. Moreover, increasing the frequency of computation does not make a lot of difference if the CPU is constantly waiting for data to process. For that reason, a second approach is to use faster memory. But memory performance has always been a trade-off with price. From this constraint emerged the concept of memory hierarchy. In a nutshell, we used fast volatile memory as main memory in the system, and we added a small amount of extremely fast memory inside CPUs, as close as possible to the core, and used it as a cache for all other memory accesses. This is the highest tier in the memory hierarchy, and also the most expensive. Other kinds of memory are considerably slower but more affordable, and can be used to store data on longer term. At this point, there is not much more that can be done to increase the computational power of a single CPU core, besides adding specific features for specific workloads that would save some CPU cycles on repetitive tasks. Yet, this is only the beginning of the performance quest.

A famous "law" of computer science, called Moore's law in the 1960's [97], made a simple observation: the number of transistors on a CPU chip doubles every two years. By the time it was edicted, Moore's law made a lot of sense, and was actually a good prediction for the next decades. Though, it is clear that this law is destined to dissapear, as CPU manufacturers are reaching the limits of miniaturization. Nowadays, CPU dies are processed with a precision of 3nm, which represents the width

of only 27 atoms of silicon. Additionally, building electrical circuitry at such a small scale even implies to take in consideration quantum tunelling effects. For these reasons, some industrial actors agree on the fact that Moore's law is already over. In this context, maintaining the evolution of computers requires other approaches.

A major revolution in modern computer science has been to use several computing units to exceed the limits of a single CPU core. When several CPU cores are on the same machine, we talk about parallel programming. This has made individual computers more efficient on plenty of workloads, as long as the work can be splitted into several independant parts. In this case, the main memory of the machine is shared between CPU cores. A second idea is to use several independant machines in a network and make them collaborate by splitting the tasks between them through a network. However, this presupose each machine has its own main memory, and does not share it with the others. A considerable part of the efforts to make more efficient computers and supercomputers is now aimed at building better collaboration between machines.

In this context, this thesis presents and uses two new ways of interacting with memory. The first one, non-volatile main memory, proposes to introduce a new stage in the memory hierarchy. By adding an intermediate kind of memory between the fast volatile main memory and the storage memory, we demonstrate how non-volatile memory could take an important place in the way we interact with local memory. The second one, remote direct memory access, makes an attempt to share main memory between machines. With the help of advanced networking components, we propose a way to use remote memory and ease the collaboration between machines within the same cluster.

# Part I. Non-Volatile Main Memory (NVMM)

# **Chapter 2.**

# **A New Kind of Memory**

In 2015, Intel revealed its 3DXPoint non-volatile memory technology would be available on the market in the coming years. This chapter explains why this announcement was a milestone, and how the resulting technology has evolved afterwards.

#### 2.1. Definition and Terminology

Non-Volatile Main Memory (NVMM) is a kind of memory able to retain its content over power loss. Unlike an Solid State Drive (SSD) which must be accessed by blocks, NVMM is byte-addressable. It can be accessed using *load* and *store* instructions with a byte granularity, just as regular Random Access Memory (RAM). From an architectural point of view, NVMM is located on the RAM bus, generally combined with regular RAM modules.

Depending on the context, NVMM can also be referred as Non-Volatile RAM (NVRAM), or Persistent Memory (PMEM). Non-Volatile Dual In-line Memory Module (DIMM) (NVDIMM) is a more general term, as it can also refer to block-addressable persistent DIMM modules.

### 2.2. History of Persistent Memories

The idea of having a persistent main memory in computers originally comes from the first computers ever built in the 1950's. In that time, most computers were built with magnetic-core memory, also called core memory. Basically, a memory core stores bits in rings of ferro-magnetic metal. Copper wires were passing through each ring, so that flowing an electrical current by these wires would change the magnetic orientation of a targetted ring, making the user able to store one bit per ring. To read a ring content, one had to apply a current in the opposite direction. If a resistance was measured, then the ring was storing a 1. Otherwise, it was storing 0. By using this extremely simple and primitive form of memory, the programmers

were already using persistent memory. Indeed, no power supply was required to keep the state of each memory cell and thus, the content stored in that kind of memory. One of the main advantage of such a device is that, in case of a power outage, an ongoing computation could be resumed in the middle, instead of starting from the begining again. However, in the 1970's, that technology was rapidly replaced by faster and more compact forms of memory, due to the popularization of semiconductors. At this time, computer architects chose to give up on the persistence of their main memory, as volatile forms of memory were considerably faster.

During the following decades, a few kinds of persistent memories emerged, in particular in the world of embedded systems. Being exposed to more risks of power losses, these systems were a perfect use case for such memories, as long as computing performance was not the main concern. As the performance and the density of volatile memories was increasing exponentially, these persistent medias were not used in the context of high performance computing.

Suddenly, in 2015, Intel announced a partnership with Micron Technologies, aiming to create the new persistent 3DXPoint memory. This new memory cell would be Phase-Change Memory (PCM), and is based on the use of chalcogenide materials, the same kind of material that was used for the rewritable surface of Compact Disk-Rewritable (CD-RW). On the paper, 3DXPoint was reaching densities and performances that were unheard of, for a persistent device. Several products featuring this memory were about to be available in the public market in the coming years. One of these products is the Intel Optane DC Persistent Memory (DCPMM) module, a non-volatile module to install on the RAM bus, and dedicated to servers. In a device of the size of a RAM module, Intel managed to fit up to 512GB of non-volatile memory, when Double Data Rate 4 (DDR4) Dynamic Random-Access Memory (DRAM) modules hardly reached 128GB.

In early 2019, Intel Optane DCPMM modules became available on the public market. They provide an unprecedented set of features, in particular it is the first device with such high capacity that allow byte addressability. Generally, higher capacity devices are block devices. They communicate with the rest of the system with blocks of data, usually 4KiB blocks. But Intel Optane DCPMM uses a finer granularity of access, as each byte can be accessed individually, as if it was regular DRAM. In terms of performance, Intel also suggested this memory would reach latencies close to DRAM modules, which was the main breakthrough of their 3DXPoint memory cell.

#### 2.3. Implementations

Non-volatile memory is a concept that was implemented in several ways and in different contexts, from embedded systems to high-end servers. The only common point between these technologies is the association of persistence and byte addressability.

#### 2.3.1. For embedded systems

In the world of embedded systems, non-volatile memory is often reffered as NVRAM. The main use case of NVRAM is to remember parameters set by a user, even after rebooting the device. For instance, we can find NVRAM chips in some devices Basic Input Output System (BIOS), in order to keep critical boot settings. This is the case for most Apple Mac computers [119].

However, this thesis will not focus on this kind of NVRAM, as it is not meant to be used for proper computing. These chips are used for their practicality, but their design is not suited to become the main memory of the entire computer, both in terms of performance and compacity.

#### 2.3.2. For servers

After decades of computing based on volatile main memory, new NVMM implementations were released with the hope of covering new use cases for servers.

#### Simulated persistent memory

As a first step, some simulators for NVMM have been created. Before 2018, with the motivation of having the actual hardware in a few years, many simulation tools were developed. Yet, as the details of Intel's implementation were not public, some of these tools had to base their approach on assumptions. These simulators are mostly developed in the architecture community, so they focus on simulating the hardware behavior of several persistent memory cells [131, 108].

Meanwhile in the systems community, the main concern was to find a way to emulate the behavior of persistent memory. For that purpose, since the version 4.2 of the Linux kernel, a compilation flag has been added to support NVMM. Once the kernel is compiled properly, a boot option allows to allocate a part of the DRAM memory and make it behave as if it was persistent memory. This trick is only meant

to test the Application Programming Interface (API) provided by the Linux kernel, while starting the development of applications without access to the hardware. Naturally, using a volatile support for that special memory space does not make it resilient to crashes. Also, the performance measured is considerably better than the one of the actual hardware. Nevertheless, this emulated persistent memory is transparently exposed by the kernel as if it was a module of Intel Optane DCPMM, which makes it a very useful development tool.

#### **Battery backed modules**

The main issue in order to use persistent memory as main memory, was the significant drop of performance of persistent cells (before 3DXPoint). To bypass this physical limitation, some attempts were made to build NVMM modules from other existing technologies. By merging the volatile DDR4 RAM with non-volatile Flash memory (found in SSD), some hybrid modules were created. On these modules, that look like regular RAM modules, one side has DDR4 chips while the other side has Flash memory. In case of a power loss, the module would use a capacitor to stay up and copy the content stored in DDR4 in its Flash memory.

This category of persistent memory is called NVDIMM-N. These modules have the advantage of presenting performances of DDR4 memory while running in normal conditions. However, their conception limits the memory compacity. For one module, the maximum capacity available was 32GB [95].

#### **Intel Optane DCPMM 100 Series**

The first generation of Intel Optane DCPMM, released in 2018, is the first broadly available implementation of the NVDIMM-P category. Optane modules only have 3DXPoint chips, and no battery or capacitor. By design, this new memory is persistent, so it does not require any special process in case of power loss. These characteristics gave the NVDIMM-P category the reputation of being the "real" persistent memory.

Additionally, 3DXPoint memory is denser than DDR4; DCPMM modules were commercialized as either 128, 256 or 512 GB per module. However, these improvements come at the cost of a higher latency, as Optane DCPMM was announced with a 10 times higher latency than typical DDR4.

These modules can be set in two modes from one machine's BIOS:

• The Memory mode

#### • The *AppDirect mode*

The *Memory mode* uses the non-volatile memory as an extension of the machine's RAM. Thanks to its high compacity, NVMM can thus be used as a less expensive way to reach high amounts of RAM in a single machine. In this mode, the persistent memory is not exposed in the OS as a special device. It appears exactly as RAM, with not management of its persistence capability.

The AppDirect mode is the "manual" mode of Optane modules. On a Linux-based operating system (OS), it allows programmers to access the memory the same way they would access a disk (i.e through a file located in dev)

There are then submodes that can be set from the OS, among them:

- fsdax mode

- devdax mode

In *fsdax mode*, the device file of each module appears as devpmemX where X is the module number. It is designed to be used with a Direct Access (DAX) file system. One has to format the device in such a file system before using it. Then, files can be created and used as subdivisions of the NVMM module, as if they were DAX files themselves.

With *devdax mode*, the device appears as devdaxX.0. This submode requires to use the entire module as one DAX file. To use a DAX file, one has to memory-map the file into a program's virtual address space. The resulting memory area will thus be hosted in the persistent memory module.

#### **Intel Optane DCPMM 200 Series**

In 2020, Intel released a new version of the Optane DCPMM modules, called *200 Series*. In essence, these new modules contain the same 3DXPoint memory. They behave the same way from the OS perspective, with some minor improvements in terms of throughput [7].

Hence, the main difference between the two versions resides in the persistence guarantees. Intel Optane DCPMM 200 Series can use a mechanism called External Asynchronous DRAM Refresh (eADR), which is meant to solve the main problem with persistent memory integration. Indeed, there is a major design flaw that prevents integrating PMEM transparently in our common computer architectures: the volatility of Central Processing Unit (CPU) caches. eADR is a mechanism designed to expand the power supply of NVMM and CPU internal caches, with an external

battery located, for instance, on the motherboard [53]. If compatible CPUs were released at the same time (Xeon Scalable Platform v3), such motherboard has never been commercialized. Research papers evaluating the impact of eADR generally used simulation tools [50].

#### 2.4. Integrating Persistent Memory in Modern Systems

Usual servers architecture can be a barrier in the acceptance of NVMM. This section presents the different ways persistent memory has been used since its commercialization, with pros and cons.

#### 2.4.1. NVMM as RAM extension

In *Memory mode*, NVMM can become an extension of RAM in a machine. This mode makes sense from a budget point of view, as NVMM is considerably less expensive per gigabyte than DRAM.

However, as persistent memory is considerably slower than RAM, a caching mechanism is used in order to keep hot memory pages in RAM, while colder pages are stored in NVMM. This system is imperfect[82], but it allows to run large memory-bounded applications.

Thus, from a conceptual point of view, using NVMM this way does not provide anything new.

#### 2.4.2. NVMM as a disk

Persistent memory can also be used as a regular SSD. One can setup an NVMM module in *fsdax mode*, format in a file system, and use that space to store files. On some disk-intensive applications, this can lead to a spectacular speedup, as Optane DCPMM performance is closer to DRAM than SSD.

#### **Software adaptation**

Using NVMM with a standard file system is not the usual way to go with persistent memory. Persistent memory is considered being a new tier of memory in the memory hierarchy, so it does not behave neither as RAM or SSD memories. Its performance stands in between, and considering PMEM as an SSD with no further

adaptation usually results in sub-optimal performance. The explaination resides in software. With time, optimizations have been made to get the full potential of the regular combo DRAM and SSD. We implemented caching mechanisms, such as the Linux Page Cache (LPC) in the Linux kernel. In an SSD file system, it is generally good to have RAM caching, as copying the data to RAM takes a negligible time compared to the actual copy on SSD (around 1,000 times slower). Also, the RAM copy of data can be used as an intermediate interface to modify an isolated byte in a memory mapped file, while the kernel still communicates with the SSD with blocks. Though, when NVMM is used as a disk, copying to RAM is not negligible anymore, as persistent memory is only around 10 times slower than DRAM. Moreover, it is not necessary to "hide" a block-granularity communication with the device, as NVMM can accept direct load and store instructions, with byte granularity. This is a typical case of software optimization that becomes harmful for performance when applied to the wrong hardware.

#### **DAX File systems**

The solution found to use NVMM efficiently in Linux was to add a new feature called DAX (Direct Access). In short, this feature is an option implemented by a file system. When this option is enabled (when the device is mounted), the files located in this file system are not cached by the LPC, avoiding a costly unnecessary copy in DRAM.

Some of the most commonly used file systems have DAX capabilities [32], for instance ext2 [33], ext4 [34] and xfs [35]. The DAX option does not change the inner organization of data inside the file system, as it only requires an additionnal flag when mounting the device.

In addition, when a file system is mounted with the DAX option, its files inherit the DAX flag. A file flagged as DAX can be memory mapped directly into a program's virtual address space, and accessed with the *load* and *store* instructions directly.

#### 2.4.3. NVMM as a DAX areas

Persistent memory being a new tier in the memory hierarchy, it has a unique set of features that makes it usable neither as a disk nor as volatile RAM. This mode of utilization requires to interact with the device as a raw memory space. By setting a persistent memory module in *devdax mode*, it appears to the OS as a raw DAX device.

From a programmer point of view, this DAX device (or DAX file) can be memory mapped into a program's virtual address space, providing a large persistent space to store objects.

For practical reasons, one can also use the *fsdax mode*, format with a DAX-capable file system, mount with the DAX option, create an empty file of an arbitrary size, and use that file as a persistent memory pool. The DAX flag being inherited from the file system, the file can be memory mapped with direct access enabled.

This is the most interesting mode of persistent memory, as it gives the programmer access to all of the features at the same time: persistence and byte addressability. With these two capabilities used simultaneously, one can write programs that store intermediate data in a persistent media, reaching a very high level of crash tolerance. If the program crashes, important data can be retrieved from persistent memory, and the program can continue to run with no data loss at all. However, to use this mode and unlock the full potential of NVMM, existing programs have to be modified.

#### 2.4.4. Working with CPU caches

One of the main challenge regarding NVMM programming is to properly deal with the CPU caches. As these caches have been designed to work with volatile memory, their behavior does not comply with persistent memory requirements.

First, the volatile nature of intermediate caches breaks the persistence guarantee. For example: If you write a value into a variable located in NVMM, you would expect your new value to be immediately stored in the persistent memory. In case of a crash, you would expect to retrieve that new value after restarting the program. In reality, to avoid costly accesses to distant DRAM, the CPU cached your change into its embedded caches. This default behavior is perfectly acceptable with volatile DRAM, as it makes the system faster, and in case of crash or power loss, all of the data stored in DRAM and CPU caches would be lost together. With persistent memory, one could expect that data to be safely saved in the persistent media, while it is in reality still in the volatile cache. If a crash occured, the volatile caches content would be lost, and the initial variable would still appear with its outdated value after a restart.

Then, the way CPUs manage their caches and the communication with DRAM is tainted by this volatility idea. In particular, as CPU caches and DRAM are both volatile, the CPU is free to re-order exchanges between its caches and distant

DRAM. Thus, any crash can let persistent memory in a partially outdated state, likely an incoherent one.

#### 2.5. Programming With Persistent Memory

In order to compensate for this design incompatibility, programmers have to use specific CPU instructions.

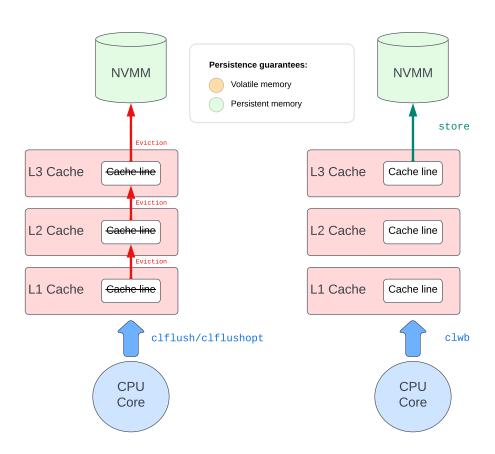

#### 2.5.1. Flushing cache lines

The only way to avoid that CPU volatile caches break the persistence guarantee is to manually evict modified cache lines. To that purpose, two commands already existed on Intel x86 instruction set, before the existence of NVMM. These instructions, clflush [18] (Cache Line Flush) and clflushopt [19] were initially designed to prevent cache pollution. When called, they invalidate the pointed cache line in every level of cache. If the said cache line is marked as containing modifications, the CPU must propagate these changes to the DRAM module before the eviction. By using these instructions with NVMM, one can guarantee the data has indeed been written to the persistent memory.

However, even if these instructions can help with the persistence guarantee, they can severely decrease performance as they completely evict a potentially useful cache line from all of the caches. For instance, imagine a loop of three instructions on the same cache line: store, clflush, load. By evicting the cache line, the clflush operation ensures the load instruction will result in a cache miss, thus in a costly interaction with the NVMM module.

For that reason, Intel introduced a new instruction dedicated for NVMM: clwb (Cache Line Write Back) in their Skylake SP Series CPUs [20]. This instruction would make no sense with DRAM, as it only ensures the modified cache line is propagated to the underlying media, without eviction of the said cache line. But with NVMM, it gives a persistence guarantee with no perturbation to the cache management, thus no performance penalty for the following instructions.

In some special cases, one could also use the ntstore (non-temporal store) instruction, which is designed to write directly into a DRAM module without going through the caches at all. Its primary use is to write data that is known to be useless for some time, and avoid polluting the caches with such data. It can also be used with NVMM, but its behavior requires some special attention when using multithreaded code, as

Figure 2.1.: Comparison between the clflush and clwb instructions.

the visibility of ntstore among threads must be ensured manually. However, in the right conditions, it can result in some performance improvements [139].

#### 2.5.2. Ordering and durability guarantees

By design, clwb instructions are not ordered between themselves. To ensure the CPU does not break the coherence of data in persistent memory, on can use the sfence operation. After using clwb on some cache lines, using sfence ensures later calls to clwb will not be applied before the fence.

The safest way to use persistent memory with these operations is to always combine a call to clwb with a sfence, enforcing the total ordering of all clwb operations. Yet, if some persistent modifications are known to be of the same importance in terms of ordering, a pfence can also be issued after all of these modifications are marked with clwb.

Additionally to sfence, a developer may need a second fence instruction named pfence. This second fence blocks, and waits for all previous written cache lines to be propagated to NVMM. On a modern Intel CPU, pfence is also implemented with a sfence, because these CPUs support Asynchronous DRAM Refresh (ADR) [54]. With ADR, a CPU uses its residual energy to ensure that a cache-line in the memory controller's Write Pending Queue (WPQ) will actually be persisted before power outage [115].

#### 2.5.3. Persistence model

In our implementations, we used a set of primitives inherited from the persistence model used in the Romulus PTM [27]. Basically, the authors used three functions to generalize the guarantees expected from Intel x86 CPUs. These three functions are:

- Persistent Write-Back (PWB): Asks to write-back a specific cache line in NVMM. This is a non-blocking function.

- Persistent Fence (PFENCE): Emits a fence that prevents next PWB calls to be reordered with previous ones. Still a non-blocking function.

- Persistent Sync (PSYNC): Waits for previous PWB calls to be performed. This is a blocking function.

For machines that only support clflush, PWB is set to send a clflush while PFENCE and PSYNC are nop. Indeed, clflush calls are already blocking functions, ordered between themselves.

For more recent hardware, calling PWB emits either clflushopt or clwb (if clwb is available, it is the one to be used). PFENCE and PSYNC are then set to emit a sfence.

# Chapter 3.

# NVCache: A NVMM-based I/O Booster for Legacy Systems

#### 3.1. Introduction

Having Intel Optane DCPMM [59] available in the beginning of 2019 was a milestone for persistent memory researchers. The entire community started to look for meaningfull approaches to use this technology in a concrete context. In comparison with other advanced hardware innovations, Optane had no groundbreaking single feature. Yet, by combining those individual features, and in particular byte addressability with persistence, we obtained a brand new and unique device in the memory hierarchy. This chapter explains how we used Intel Optane DCPMM to build a non-volatile cache, named NVCACHE.

#### 3.1.1. NVCACHE in a nutshell

NVCACHE is a memory cache in userspace. It uses NVMM as a write cache able to receive bursts of data, while the cache content is asynchronously propagated to the main, slower non-volatile media, *i.e.*, Hard Disk Drive (HDD) or SSD. The key idea is to exploit the latency of NVMM, which takes way less time than a regular SSD to acknowledge for the persistence of data. To summarize, NVCACHE does not need to call fsync on the critical path, as the persistence guarantee can be easily obtained in userland by the NVMM device.

#### 3.1.2. NVCACHE features

In order to build a functionnal and practical tool, we decided to fix some ground rules on the final set of features.

First, NVCACHE has to be transparent. We want to avoid, as much as possible, modifications in the original source code of the target application. Ideally, we can even

run compiled programs with NVCACHE without having access to the source code at all.

Second, NVCACHE must use NVMM as the new device it is, and not as a better SSD or a slower RAM. Persistent memory brings a new feature set, we have to use it fully in order to exploit NVMM at its full potential.

Third, NVCACHE must be efficient both on throughput and latency. The quest of lower latencies with NVMM should not be persued on the detriment of the throughput. In particular, using NVCACHE, applications should reach the throughput they could get using batched operations on a regular disk.

The goal of NVCACHE is to propose this new unique set of features, that cannot be achieved with other NVMM solutions. An overview and comparison with other NVMM software tools is compiled in Table 3.1.

### Large storage space

NVCACHE can handle big datasets, as its storage capacity is not limited to the amount of NVMM available. By using NVMM as a simple cache, the limitation depends on the underlying storage media, which can for instance be an SSD or a HDD. These storage medias are usually considerably cheaper per gigabyte than NVMM.

#### Syncronous durability

When using NVCACHE, one can expect the maximum persistence guarantee after each call to the write function. All calls to fsync are unnecessary, and thus redirected to an empty function. The synchronous durability is the default mode. Technically, a more relaxed logic could be implemented, by placing the right memory fences in the fsync function, but this mode has been considered out of scope for the initial development of NVCACHE.

## **Durable linearizability**

Crash consistency is the major feature we expect from the use of NVMM. However, it requires to add more complex guarantee mechanisms, so that the program could crash at any time and not expect any rollback when restarting. In practice, every write function that returns has to be persisted in NVMM, but every incomplete operation must be canceled. Also, there cannot be any reordering among different store operations, or the consistency of the cache content could be compromised.

Table 3.1.: Properties of several NVMM systems, all fully compatible with the POSIX API.

|                                      | Ext4-DAX  | NOVA  | Strata | SplitFS  | DM-WriteCache | NVCACHE |

|--------------------------------------|-----------|-------|--------|----------|---------------|---------|

|                                      | [26, 136] | [138] | [76]   | [66]     | [120]         |         |

| Offer a large storage space          | _         | _     | +      | _        | +             | +       |

| Efficient for synchronous durability | +         | ++    | ++     | ++       | _             | +       |

| Durable linearizability [61]         | +         | +     | +      | +        | _             | +       |

| Reuse legacy file systems            | + (Ext4)  | _     | _      | + (Ext4) | + (Any)       | + (Any) |

| Stock kernel                         | +         | _     | _      | _        | +             | +       |

| Legacy kernel API                    | +         | +     | _      | _        | +             | +       |

That type of guarantee is often reffered as durable linearizability [27, 109].

#### Software compatibility

We wanted NVCACHE to be as portable and easy to use as possible. As a result, using NVCACHE does not require deep changes to work on a regular machine. The cache runs on any modern stock Linux kernel, and does not require any kernel-side modification, nor kernel module. Thus, it uses the regular kernel API.

Moreover, the media cached by NVCACHE can be formatted in any file system. We mostly used the very standard Ext4, but also tested it with more specific file systems such as NOVA [138].

#### 3.1.3. Target applications

By design, NVCACHE is efficient on applications that require a high granularity of persistence guarantees. A software developer has no choice regarding local persistence: to ensure some level of crash resilience, one has to call fsync after each critical write. With NVCACHE enabled, such an application would not suffer from a major Input/Output (I/O) bottleneck even with high persistence requirements.

Current applications tend to leverage this problem by batching modifications, and wait for the batch to be complete before flushing it to disk. That approach dilutes the frequency of fsync calls. However, it does require to find a trade-off between performance and persistence granularity. Indeed, increasing the batch size will tend do increase performance, but it can also result in bigger rollbacks when a crash occurs. Similarly, reducing the batch size makes the system slower, but reduces the likeliness and the importance of potential rollbacks.

Thus, NVCACHE is a perfect fit for applications that are sensitive to the persistence latency, *i.e.*, the time required to ensure a data has been persisted. For instance, a Database Management System (DBMS) with regular updates on a massive database. In an ideal context, the database would be updated on disk for each write or update request. However, under heavy workloads, the time required to wait for the disk to acknowledge after each operation would create a severe bottleneck. If the database fits in Intel Optane DCPMM, one could imagine using this device as the only storage media. But this solution requires to have a lot of NVMM available, which is expensive [45] or even impossible over a certain amount. On the other hand, with NVCACHE we proposes a way to get the latency benefits from NVMM while not being limited by the amount of persistent memory in the server.

## 3.2. NVCache: Implementation

#### 3.2.1. Overview

NVCACHE is available either as a library or as a modified libc [36]. The library that can be included in a target application, providing I/O primitives such as nvopen, nvwrite, nvread, and nvclose. The libc can be dynamically linked to a compiled program. This way, it transparently intercepts calls to basic IO functions, like open, read, write, and close.

In case of a crash, some data might remain in the non-volatile cache. On reboot, after loading NVCACHE again, a synchronisation phase starts, setting the disk in a state that would be considered valid by the application. The program then has to recover its data from disk and restart exactly as it would on a regular machine.

#### 3.2.2. NVLog

The main idea in NVCACHE is to use the NVMM space as a log of pending operations. Each log entry represents a write operation that will eventually be applied on disk.

On startup, a NVMM module in Device DAX is memory mapped, and this virtual space is casted into a data structured that we called NVLog.

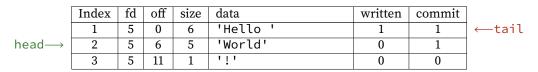

| Index | fd | off | size | data           | written | commit |

|-------|----|-----|------|----------------|---------|--------|

| 1     | 5  | 0   | 12   | 'Hello World!' | 0       | 1      |

Figure 3.1.: NVLOG entry example

## Log entry format

In order to delay the actual write operation, the NVLog has to keep the entire set of metadata provided by the application when the write function was called. A log entry must contain:

- A file descriptor (fd)

- An offset (off)

- · A size (size)

- The data to be written (data)

As log entries are statically allocated to maximize performance, they also come with a fixed size. When a write operation is shorter than the maximal data size (i.e., 4 KiB), the size field guarantees the end of the data buffer will be ignored. When the operation is longer than 4 KiB, it has to be splitted in several parts. For instance, a 9 KiB write will result in two 4 KiB entries, plus a smaller 1 KiB one.

These four fields already ensure that we will be able to execute the write operation later. Though, in order to make NVCACHE crash resilient, we had to add two more fields:

- A commit boolean (commit)

- An reference index for long writes (waiting)

- An ignore boolean for entries already written to disk (written)

The commit boolean is the last field to modify. If a crash occurs, a non-committed entry is considered incomplete, and thus will not be synchronized on disk when the system restarts. The reference index is the index of the first log entry of a long write. With this field, we know what commit flag to look at when a write is splitted in several chunks. Last, the written flag allows to ignore entries that have already been written to disk, for instance if the file has been closed. As writing to an outdated file descriptor could cause errors, there is a specific procedure when the hosted program closes a file. That procedure requires to flag some entries as written.

Figure 3.2.: NVLog head and tail counters

#### **NVLog data structure**

On NVCACHE startup, a DAX space (our NVMM) is memory mapped. This space is then hosting the NVLOG data structure. It stores:

- log entries (the amount is defined at compile time, we call it log\_size)

- A head counter

- A correspondence table between file paths and file descriptors

- A exit\_status boolean

The log itself is circular: when it reaches the end of the N allocated log entries, it starts back at the first one. The head and tail counters respectively keep in NVMM the index of the last entry written, and the index of the last entry already flushed to disk. As head is not mandatory for recovery, this value is kept in volatile memory. A correspondance table gives a path to each file descriptor used in the log, so that the program can open them again even after a crash. Last, the exit\_status flag is set to 1 when NVCACHE starts, and set to 0 after exiting in a normal way. This is basically a crash detector for the recovery procedure.

Essentially, this data structure is designed to store the bare minimum required to recover in case of crash. Every variable that is not absolutely necessary to the recovery procedure is stored in regular volatile memory.

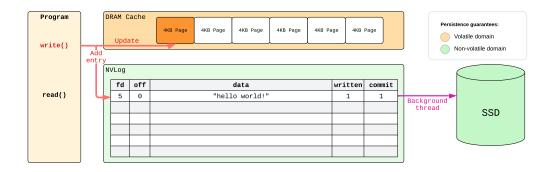

### Adding a new entry

In order to add a new entry in the non-volatile log, the user program calls regular libc functions to write into a file, i.e., pwrite or write. Instead of submitting a write system call immediately to the kernel, the following events are triggered:

- Allocate a new (or recycled) log entry in the log

- Fill the entry content as described previously, except for the commit field

- Emit a PWB per cache line and a PFENCE

- Set the commit boolean to True

- Emit a PWB on the commit boolean cache line, and a PSYNC

This sequence ensures the commit boolean will never be set to True before the log entry content is written in the non-volatile log. Without this security, after a crash, a commit boolean could be set to True while its content was not (or only partially) written in NVMM. However, as we took this precaution, commit can be used as the answer of the question: Is this log entry ready to be written on disk?

#### Log entry allocation

Before storing the content of an entry, NVCACHE has to allocate it. In this context, the objective is to increase the index stored in the head counter.

In order to anticipate multithreaded workloads, this mechanism is implemented in a lock-free fashion. In practice, NVCACHE starts by attempting to atomically decrease the available\_entries counter (this counter is kept in volatile memory). This requires the use of a compare\_and\_swap atomic function, checking that no other thread changed the value of available\_entries in the meantime.

If this greater than zero, meaning there is space left in our log, the thread manages to decrease its value. Otherwise, it spins until the decrement is effective. NVCACHE then calls fetch\_and\_add(1) on the head counter, and returns the new value as the index of the allocated entry.

However, as the fetch\_and\_add function does not take into account the circularity of our log, the head and tail counters are monotonic. Before using them, NVCACHE has to apply a modulo by the log\_size.

One could argue that having these counters monotonic can lead to a problem when they reach overflow. Though, head and tail being implemented as 64 B variables, NVCACHE would have to store  $4KiB*2^64 = 64EiB$  to reach this overflow. Thus, we considered this problem as out of scope for our implementation.

#### **Overlapping entries**

As soon as a write request is longer than the maximum size of a log entry payload (in practice, 4 KiB), NVCACHE has to split it in several log entries. Nonetheless, to prevent partial writes to pollute the disk, an additional mechanism is implemented for overlapping entries.

## Algorithm 3.1.: NVCACHE write function.

```

struct nvram {

// Non-volatile memory

struct { char path[PATH_MAX]; } fds[FD_MAX];

2

struct entry entries[NB_ENTRIES];

3

uint64_t persistent_tail;

}* nvram;

uint64_t head, volatile_tail;

// Volatile memory

void write(int fd, const char* buf, size_t n) {

struct open_file* o = open_files[fd];

10

struct file* f = o->file;

11

struct page_desc* p = get(f->radix, o->offset);

12

uint64_t index = next_entry();

14

struct entry* e = &nvram->entries[index % NB_ENTRIES];

15

acquire(&p->atomic_lock);

17

memcpy(e->data, buf, n);

// Write cache

19

e->fd=fd;

20

e->off = o->off;

pwb_range(e, sizeof(*e));

// Send the uncommited entry to NVMM

22

pfence();

// Ensure commit is executed after

23

e->commit = 1;

25

pwb_range(e, CACHE_LINE_SIZE);

// Send the commit to NVMM

26

// Ensure durable linearizability

27

psync();

atomic_fetch_add(&p->dirty_counter, 1);

// Read cache

29

// Update page if present in the read cache

if(p->content)

30

memcpy(p->content->data + o->off % PAGE_SIZE, buf, n);

31

release(&p->atomic_lock);

32

}

33

int next_entry() {

35

int index = atomic_load(&head);

36

while((index + 1) % NB_ENTRIES == atomic_load(&volatile_tail)) ||

!atomic_compare_and_swap(&head, index, index + 1))

38

index = atomic_load(&head);

39

return index;

// Commit flag at index is 0 (see cleanup thread)

40

41

```

|                        | Index | fd | off  | size | data             | waiting | written | commit |        |

|------------------------|-------|----|------|------|------------------|---------|---------|--------|--------|

|                        | n     | 5  | 0    | 4096 | First 4096 bytes | n       | 0       | 0      | ←—tail |

|                        | n+1   | 5  | 4096 | 4096 | Next 4096 bytes  | n       | 0       | 1      |        |

| $head \longrightarrow$ | n + 2 | 5  | 8192 | 8    | Last 8 bytes     | n       | 0       | 1      |        |

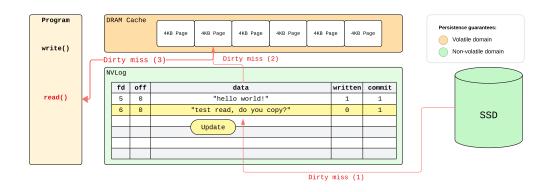

Figure 3.3.: State of NVLoG while adding 8200 bytes.

We leverage this problem by adding the waiting field in each log entry. On single entries, this field is set to -1. On multiple entries, it stores the index of the first one. The first entry of an overlapping entry is the one used as a reference for all of its followers. The sequence to follow to add an overlapping entry is the following:

- Compute the number of log entries to allocate (*k*)

- Allocate these *k* entries

- Write the first entry, with a waiting index pointing to itself, and a commit boolean to False

- Write the k-1 following entries, with a waiting index to the first one, and commit boolean set to True

- · When all entries are written, perform a sfence

- · Change the first entry commit flag to True

- Call sfence and clflush

This sequence allows to keep overlapping writes atomic, as they cannot be partially propagated to disk.

#### 3.2.3. Cleanup thread

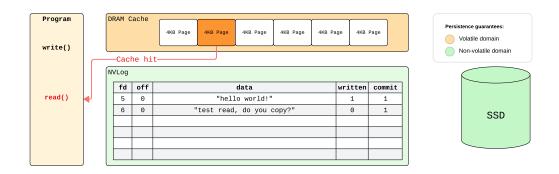

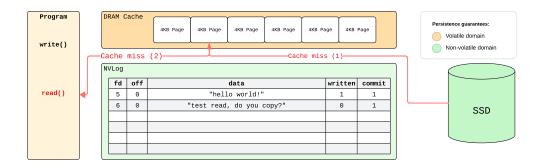

While NVCACHE is writing new entries in the log, a background thread is responsible for flushing these log entries in the actual non volatile storage media.

This thread interacts with three elements of the NVLog:

- The tail counter, index of the last flushed entry

- The written field of log entries

- The available\_entries main counter, keeping track of the number of entries that can be allocated.

As entries are added to the log at the head index, the cleanup thread is responsible for synchronizing these entries with the disk. It uses the tail index, stored in volatile memory, to call the standard libc I/O functions, and submit each entry as a write system call to the backend file system.

#### Interaction with the LPC

When an entry is processed by the cleanup thread, it is sent to kernel space in order to be written on the physical disk. Though, for performance reasons, calling the write system call alone does not give any persistence guarantee. Instead, data is sent to the volatile LPC, opportunistically waiting for a moment to write in non volatile storage. From userland, the usual way to make sure every pending write operation is propagated to disk is to call the sync system call. As this system call returns, the user is guaranteed that its data has been persisted on disk.